# A STUDY OF A SPECIAL PURPOSE AUTOMATIC OPTIMIZER

bу

WILLIAM LAWRENCE WRIGHT

B.A.Sc., University of Waterloo, 1963

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

# MASTER OF APPLIED SCIENCE

in the Department of Electrical Engineering

We accept this thesis as conforming to the required standard.

Members of the Department of Electrical Engineering

THE UNIVERSITY OF BRITISH COLUMBIA

August, 1965

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the Head of my Department or by his representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

| Department    | of  | ELECTRICAL | ENGR   |

|---------------|-----|------------|--------|

| pepar tillent | O I | 11/2/72    | - INGA |

The University of British Columbia Vancouver 8. Canada

Date SEPT 7/65

#### ABSTRACT

Small special purpose digital computers (SPDC) could be used to control processes for which the cost of general purpose digital computers is prohibitive. This thesis describes a SPDC to optimize a process for which an exact mathematical model does not exist. The SPDC could use any of the empirical or trial and error methods originally designed for hand calculations or for use on a large general purpose digital computer. The methods discussed in this thesis are gradient search, direct search and random search.

The overall operation of a SPDC is described in detail using logic block symbols. From the knowledge gained in building and testing the computer, improvements in circuitry and search strategy are suggested.

The logic and circuitry used in a SPDC depends on the nature of the process to be controlled. This is illustrated in the thesis by the description of the optimization of a flotation process.

# TABLE OF CONTENTS

| ·                                               | Page          |

|-------------------------------------------------|---------------|

| List of Illustrations                           | * iv          |

| Acknowledgement                                 | × V           |

| 1. INTRODUCTION                                 | . 1           |

| 2. CONTROL STRATEGIES                           | , 3           |

| 2.1 Nonsequential Strategies                    | • 4           |

| 2.2 Sequential Strategies                       | <b>4</b>      |

| 2.3 Details of a Specific Search Strategy       | . 12          |

| 3. THE COMPUTER                                 | · 19          |

| 3.1 Control Block                               | • 21          |

| 3.2 The SMX and SMY Blocks                      | . 24          |

| 3.3 The CCX, CCY and CCP Blocks                 | å 25          |

| 3.4 The SMP Block                               | <u>.</u> 26   |

| 4. TEST OF COMPUTER                             | , 36          |

| 4.1 Comparators                                 | · 37          |

| 4.2 Dead Band & see see see see see see see see | 42            |

| 5. EXAMPLE OF USE OF SPDC                       | 48            |

| 6. CONCLUSIONS                                  | ş <b>⊌</b> 52 |

| APPENDIX A                                      | 53            |

| DEFEDENCES                                      | . 56          |

# LIST OF ILLUSTRATIONS

| Figur | <b>e</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2=1   | Block Diagram of Direct Optimizing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4          |

| 2⊶2   | Flow Diagram of Command Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15         |

| 2-3   | Flow Diagram of Mode 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16         |

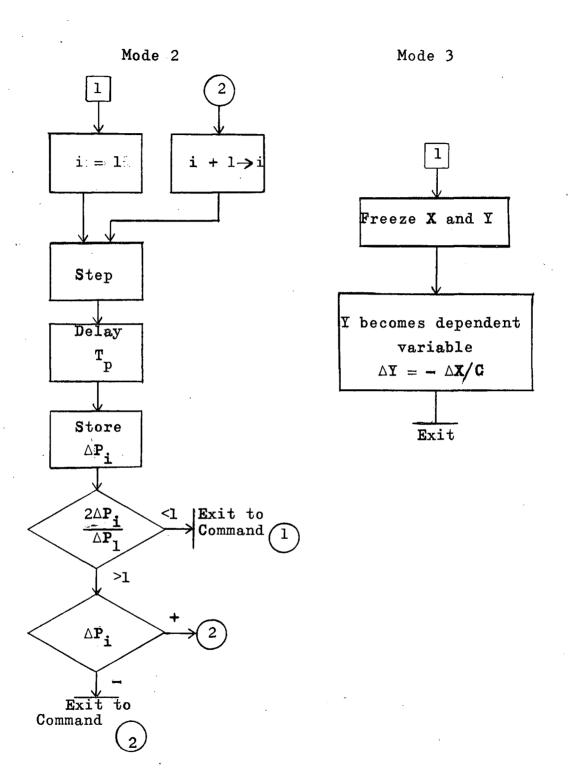

| 2-4   | Flow Diagram of Mode 2 and Mode 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17         |

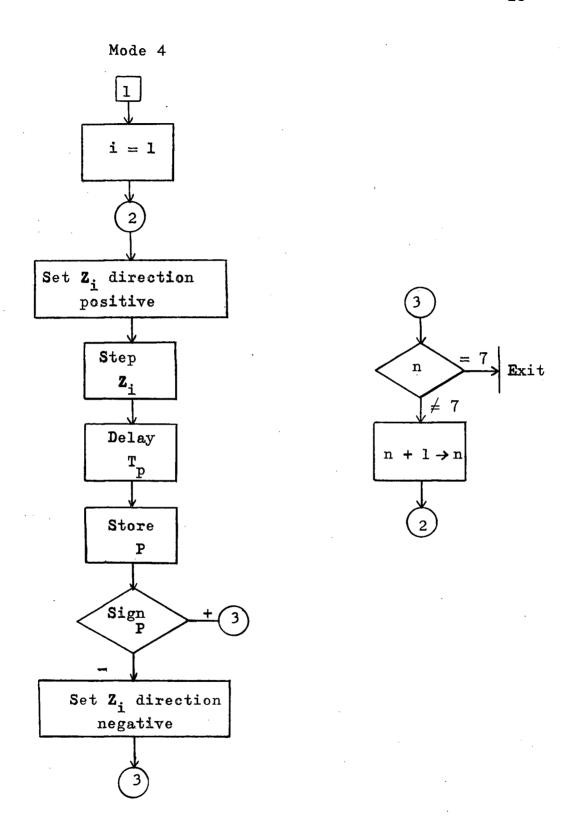

| 2-5   | Flow Diagram of Mode 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18         |

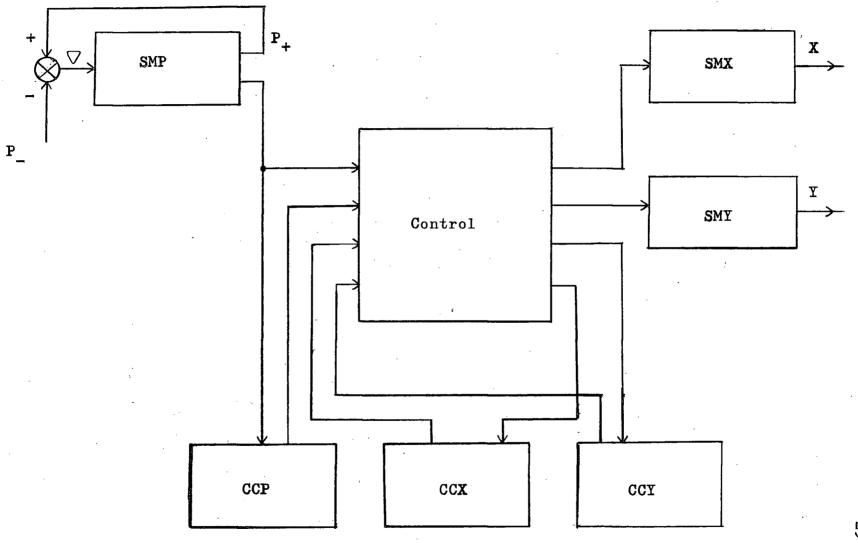

| 3-1   | General Computer Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29         |

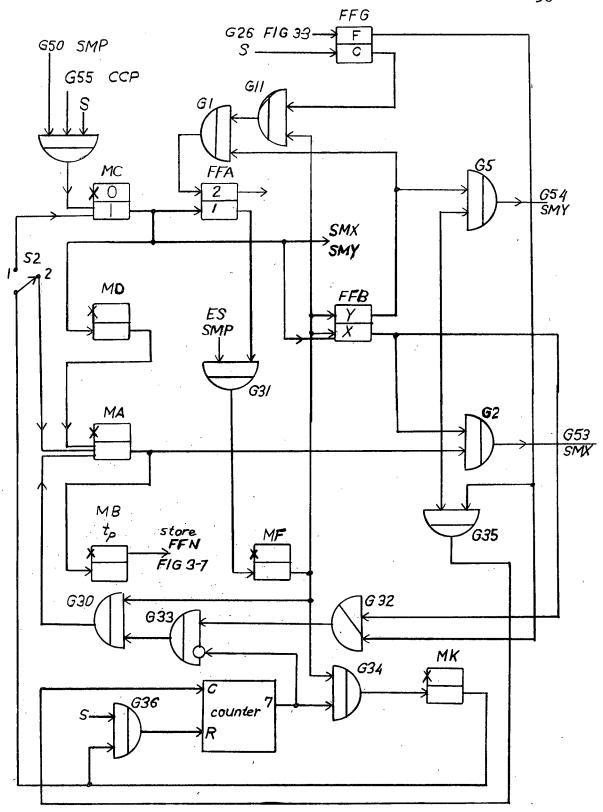

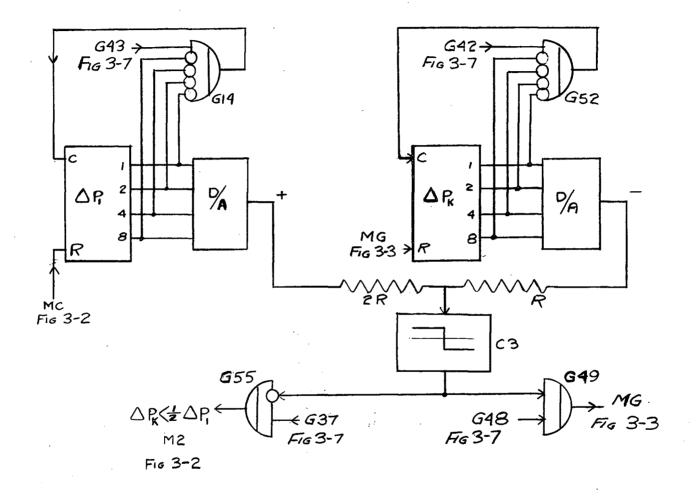

| 3-2   | Control Block - Modes 1 and 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>3</b> 0 |

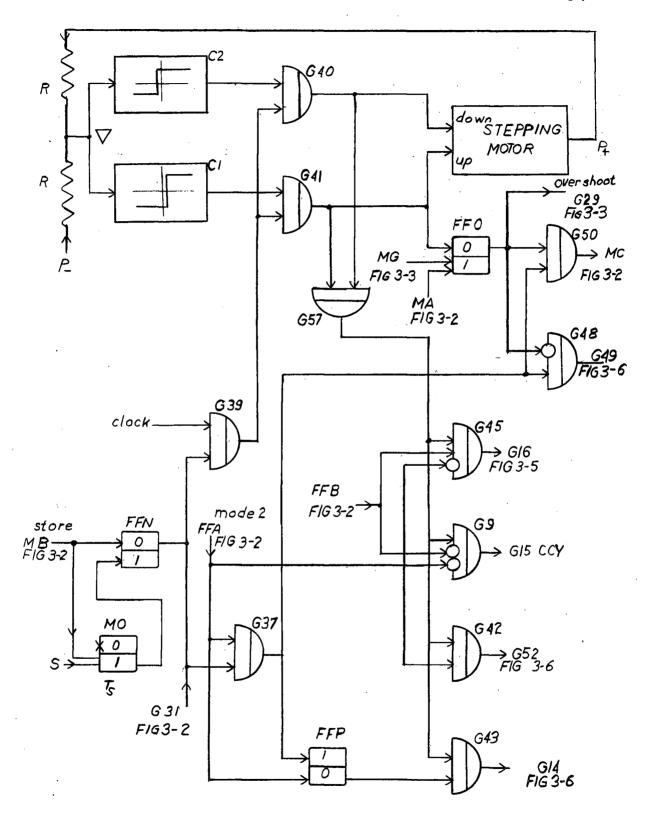

| 3-3   | Control Block - Mode 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31         |

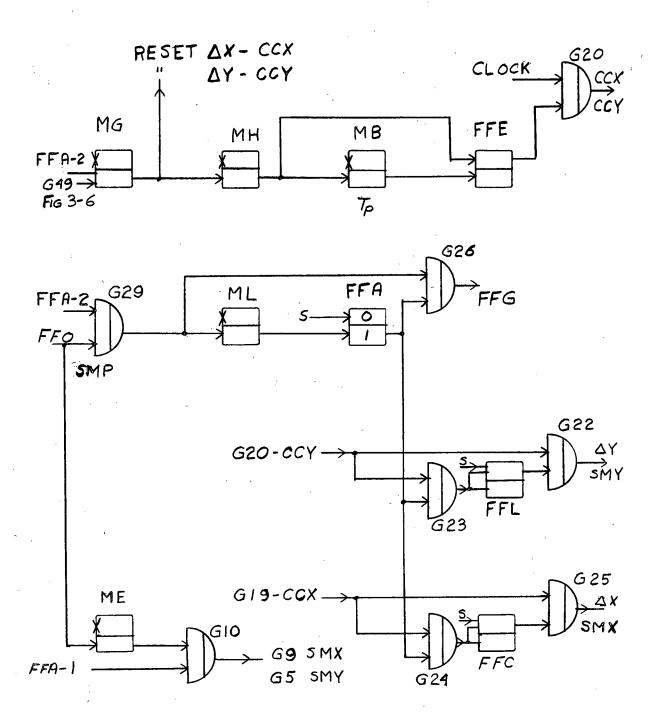

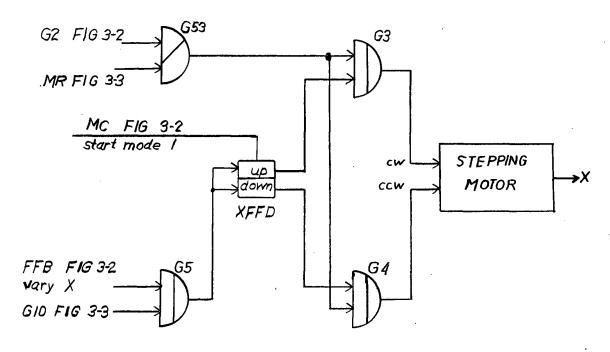

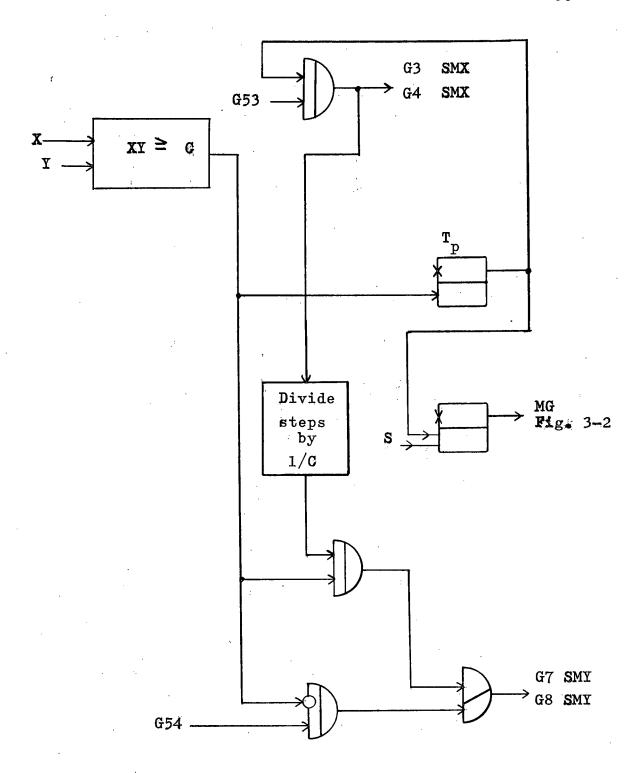

| 3-4   | Block Diagram of SMX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 。32        |

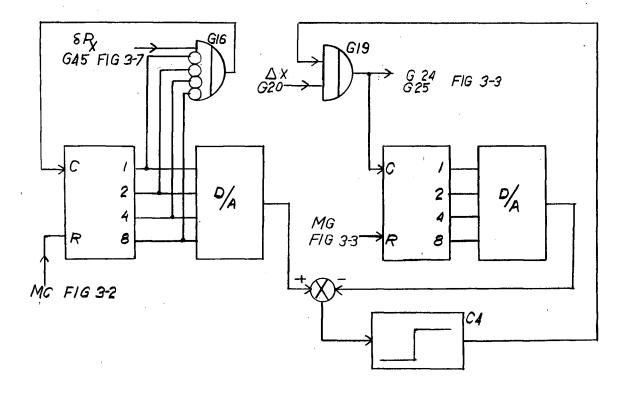

| 3-5   | Block Diagram of CCX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 32       |

| 3-6   | Block Diagram of CCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33         |

| 3-7   | Block Diagram of SMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34         |

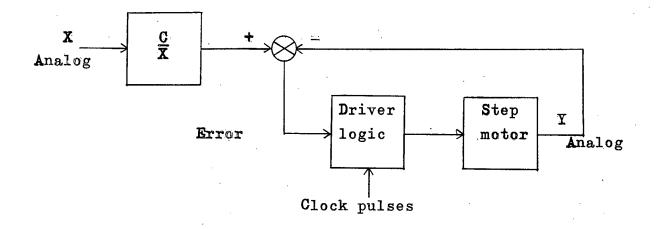

| 3–8   | Block Diagram of Constraint Circuit, XY   C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35         |

| 3-9   | Constraint Circuit with No Accumlative Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28         |

| 4-1   | Comparator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 38       |

| 4-2   | Changes to SMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46         |

| 4-3   | SMP Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47         |

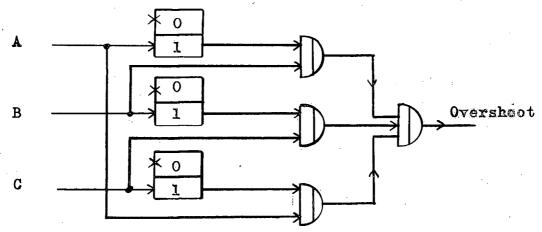

| 4-4   | Digital Overshoot Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40         |

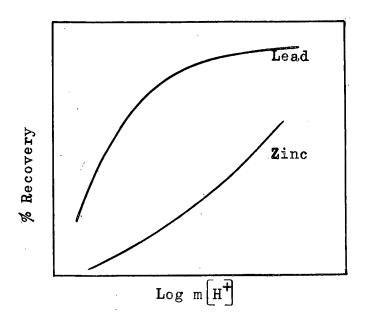

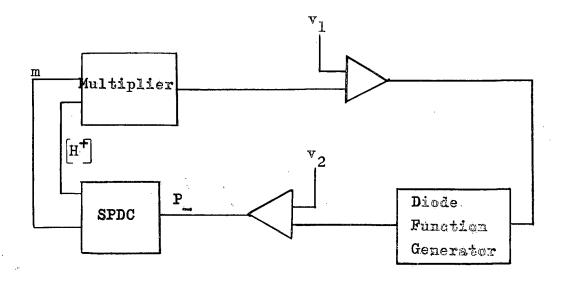

| 5–1   | Percentage Mineral Recovery vs. m [H+]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51         |

| 5-2   | Test Setup was the base of the company of the compa | 51         |

## ACKNOWLEDGEMENT

Grateful acknowledgement is given to Northern Electric Co. for a fellowship awarded in 1963 and to the National Research Council for financial support from Block Term Grant A68.

The author would like to thank the supervisor of this project, Dr. E. V. Bohn, and all other staff members and graduate students of the Electrical Engineering Department for their assistance during the course of this study. The author is also indebted to W. K. Gowans of The Consolidated Mining and Smelting Co. for suggesting the example in Chapter V.

#### A STUDY OF A SPECIAL PURPOSE AUTOMATIC OPTIMIZER

#### I. INTRODUCTION

In the last few years there has been an increase in the number of computers used in industrial controls, and an accompanying expansion of the literature about them. Since many companies are now actively investigating computer use, an even greater increase is anticipated. Despite this widening interest and a general lowering of computer and computer component prices, there are still many processes to which optimal control techniques cannot be applied because of the high cost of available general purpose computers relative to the expected increase in returns due to optimal control.

The object of this thesis is to outline a special purpose low cost digital controller for on-line optimal control. This type of unit could be used to drive a single loop or small process to a steady state optimum. The controller is also applicable to the quasi-static process where the optimum operating point varies with uncontrolled plant parameters which change slowly relative to the dominant response time of the process. This digital controller could also be used in conjunction with a high speed analog computer to control dynamic processes as suggested by Bohn. 3, 4

Alone, or in conjunction with the high speed analog computer, the action of the digital controller will be the same. The process, or plant, would be such that a mathematical model

cannot be completely prepared because of the complexity of the process. Even if a mathematical model can be prepared, it would be too complex to be solved analytically and is complicated further by time varying parameters. The optimum is determined by experimenting with the process, sometimes referred to as the direct method of optimizing.

The changes made by the controller in the controlled variables are based on past responses of the performance function P. Various strategies have been developed to find the optimum under these conditions. The decision of what strategy to instrument would be based on what is known of the process and performance function surface. The Quarie controller and OPCON are commercial controllers using this technique. 5,6,7,8 An analog computer of this type has been suggested by Feldbaum. 9,10

There are several well-documented search strategies for maximizing mathematical functions, usually intended for use on a large general purpose computer. This thesis describes how standard components could be used to instrument one such search strategy for direct process optimization. The general purpose digital computer has a large minimum cost because the same control and arithmetic units are required regardless of computer size. As the digital controller described here requires no program flexibility and works at speeds comparable to the process time constants, a very inexpensive unit should be possible. This thesis shows how the performance of the circuits in the controller may change the basis for choosing a search strategy, and concludes with a description of an industrial process which might use such a controller.

#### 2. CONTROL STRATEGIES

The term "control strategy" is used to describe the procedure by which the control parameters of a process are varied in order to operate the process at the desired optimum. For simplicity, the optimum operating point will be considered a minimum of P. The performance function surface will be considered unimodal (one minimum), a realistic assumption as the multimodal case becomes unimodal once the lowest minimum has been found. Some authors suggest handling the multimodal case by repeated use of a control strategy designed for the unimodal case using different parameter values for starting points. 11 The "no-error" cases where the control parameters and P are assumed to be known exactly will be considered here, as their principles are simple and the control strategies based on them can be used even if the assumption is not quite true. noise and instrumentation error which exist in most industrial cases might necessitate use of a variation (using a statistical technique 12) of the "no-error" strategies. The controlled system as suggested by Bohn 3,4 can be considered error free.

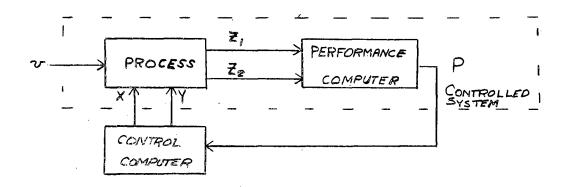

Again for simplicity and ease of description, the process will be considered as shown in Figure 2-1 with X and Y as two controlled parameters, v as one uncontrolled parameter, and the performance function P as the output to the control computer.

The control computer must vary the inputs  $\mathbf{X}$  and  $\mathbf{Y}$  in discrete steps as the effect of changing a variable is not

immediately measurable because of time lags in the process.

Each new control parameter setting must be held until the static response to the change can be measured.

Figure 2-1 Block Diagram of Direct Optimizing

# 2.1 Nonsequential Strategies

In nonsequential strategies the entire performance function is systematically explored. Each new setting of X and Y is independent of past responses. This type of strategy, while useful for multimodal performance surfaces, is not as applicable to the problem outlined in the introduction as the sequential strategies. 13

# 2.2 Sequential Strategies

Sequential strategies are the types of control strategies best suited to a special purpose digital computer (SPDC) with limited memory capacity. Sequential strategies are often referred to as "hillclimbing" because the physical ascent of a hill involves similar decisions. 14

In sequential strategies, each new setting of X and Y is dependent on one or more past responses to step changes in X and Y. Thus the changes in X and Y cannot be predetermined as in nonsequential strategies because they depend on the unknown performance surface and on the starting values of X and Y.

There is extensive literature on sequential control strategies and much overlapping of ideas and terms. In general, the sequential strategies may be divided into three main types: gradient, direct, and random search.

Gradient methods explore the variations of P with respect to parameter changes to find the local gradient or direction of greatest slope of the P surface in the neighbourhood of the starting point and move the control parameters in this direction. In the univariate gradient method all variables except one are held constant and this one is varied to obtain an improvement in Pa Thus X, would be held and Y varied until  $Y_{2}$ , the value of Y which gives the largest possible P ( $X_{1}$ , Y), Then Y is held at Y2 and X is varied, etc. One of the many possible variations is to start varying X if P  $(X_1, Y_2)$ is not found in a specified number of steps of Y. The univariate technique works quite well as long as the control parameter axes are parallel to the axes of the contour surfaces of R15 Even with an advantageous alignment of axes, this method requires many more moves to arrive at the minimum than other methods which move all parameters simultaneously.

Another gradient strategy similar to the univariate

method but which makes simultaneous steps in all control parameters is called relaxation. The local P surface is explored to find the gradient direction and then all control parameters are stepped simultaneously to move the operating point in this gradient direction. These steps are continued until no further improvement in P (local minimum) is possible in this direction and then a new local gradient is found. After the first step there is no reason to assume the moves are still in the direction of the local gradient and this is one of the factors that lead to many variations on this general strategy. For example, the change  $\Delta P_N$  in P for the N<sup>th</sup> step could be monitored and if  $\Delta P_N^{}$  becomes less than a predetermined percentage of  $\Delta P_1^{}$  in the particular direction being moved, a new gradient direction could be found immediately rather than continuing on to find the local minimum. A variation that would not require the storage of  $\Delta P_{\mbox{\scriptsize l}}$  is to use either the finding of the local minimum or the Nth control parameter step as the signal to find a new local gradient.

Perhaps the best known of the gradient methods is "steepest descent" which lets the N of the previous variation be 1. Thus a new local gradient is found after each step. This enables the maximum advantage to be gained from each step of the parameters once the gradient direction is known. If finding the gradient direction is very time consuming, the relaxation method may find the minimum in a much shorter time than steepest descent. In minimizing a mathematical function, the gradient direction is found by calculating the derivatives of the function

by any suitable method. With the process as outlined in the introduction, these derivatives cannot be calculated. The gradient is found by sequentially changing each control a known amount,  $\delta X_{x}$  waiting any required dead time or until all transient effects have settled and then measuring the resulting  $\delta P_{X}$ . Then assuming  $k \delta P_{X} \approx \delta P_{X}/\delta X$ , a move can be made in the gradient direction by simultaneously stepping the control parameters an amount  $\Delta X = -k \delta P_{X}$ ,  $\Delta Y = -k \delta P_{Y}$ .

In most industrial processes the required delay, Tpy between stepping  $\delta x$  and the measurement of  $\delta P_x$  is so much greater than any computation time required by the SPDC that, using a steepest descent strategy, a large percentage of search time is spent finding the gradient direction rather than improving the operating condition of the process. But on any irregular P surface the steepest descent method may arrive at the optimum operating condition in shorter time than the relaxation method. It should be pointed out that any direction of search which improves P can be made the steepest descent direction by a proper change of scale of the control parameters, 11,16,17 This indicates a basic problem of all gradient methods; moving in the gradient direction can be no better or no worse than moving in any other direction. If the contour lines of P are circles, the gradient direction at any operating point will lead directly to the minimum, but, if the P contours are any shape other than circular, there may be very little correlation between the gradient direction at an operating point and the direction from the same operating point to the minimum.

Direct search 18 or trial-and-error 17 strategies are in no way dependent on a gradient direction. The control parameters are stepped in any direction which the previous responses have shown to improve P. One type of direct search is to make simple exploratory moves of each control parameter and use the improvement or lack of improvement of P (no interest in relative sizes of SP, only in sign of SP) as a guide to direction of search. This exploration is followed by a "pattern" step in the direction indicated by the exploration. For any P surface having noncircular contours (which would seem to include many industrial processes), the direct search strategies should be just as good if not better than any gradient method. One advantage of direct search strategies for use in a SPDC is that they tend to use repeated identical arithmetic operations with a simple logic.

In random search strategies the control parameters are stepped in a randomly chosen direction about a base operating point. If P is improved at any chosen operating point, it becomes the new base point for continued random moves. It might seem obvious to prefer a procedure which makes some use of previous responses in planning the next move but a random search strategy is efficient at optimizing very irregular P surfaces. Some tests have shown random strategies better than systematic control strategies for a process with few inputs (less than three) if the process can be described by algebraic equations. With a process as outlined in the introduction where time T<sub>D</sub> is required after each parameter step before SP

can be measured, the random strategies do not perform as well as the gradient methods. 14

All the basic sequential strategies so far considered will operate, with various degrees of success, using only a single step size throughout the entire search for the optimum. A much improved performance (fewer steps to converge to the optimum) is possible if adjustment of step size is used. this substrategy, the usually suggested pattern is to use coarse steps in the initial stages and finer steps in the latter stages of the search to improve resolution and reduce overshoot and hunting losses. There is a large number of criteria for changing step size and most modify the initial step size depending on the success of the previous step taken (if P was improved, the step was a success). The effectiveness of any search strategy is dependent on this initial step size. 20 The "best" initial step size will depend on the particular process under consideration. For an unknown process, an adjustment of step size is very important to correct any initial poor choice of step size.

One possible strategy might be to double the step size if the last step was a success. This could result in rapid convergence to the optimum in the initial search but would overshoot the optimum. In the gradient strategies the steps are proportional to the previous response,  $\Delta X = -k \delta P_X$ , and k can be reduced as the minimum is approached. This could be done by making k smaller for each negative  $\Delta P$  (an overshoot). If k is only made smaller than the initial k, the controller

could spend a long time searching in an area of relatively flat P.

Another possibility is to use the frequency of overshoots shoot as a step size criterion. <sup>12</sup> For example, if four overshoots occur in sequence, the step size is considered too large; if four successes occur in sequence, the step size is considered too small. This type of step size adjustment is used in direct search strategies where the size of  $\Delta P$  is not measured. The step size is adjusted by a predetermined amount dependent only on the success of the previous step.

ments any of the basic sequential strategies such as gradient search or direct search. A constraint is usually a physical consideration which prohibits certain areas of the P surface in which the operating point cannot or should not exist. "Hard constraints" such as maximum temperature or maximum flow obtainable cannot be violated. "Soft constraints" are those which should not be violated as they represent areas of operation where undesirable effects start to appear.

The constraint may be a known function of the system parameters, such as XY \geq C, or some measure might have to be taken directly to sense constraint violation. Two possible methods for handling constraints are "hemstitching" and "riding the constraint". In "hemstitching", as used in a basic gradient search, the control parameters are moved in the direction of the gradient of P if the constraint is not violated.

Once the constraint is violated the parameters are moved in the

direction of the gradient of the constraint. Like all search techniques considered in this thesis, there are many variations on this idea; but basically the parameters are adjusted to improve P until the constraint is violated and then the parameters are adjusted with the aim of satisfying the constraint. Hemstitching requires the constraint to be violated. This violation is not acceptable in any controller empirically optimizing an industrial process with hard constraints. In "ride the constraint" method the gradient direction of P is always found, but in a zone within one step of the constraint (assuming the constraint is a known equation) only a limited parameter step is allowed so that the operating point will tend to follow the constraint line and the constraint is never violated. This nonviolation of the constraint assumes that the process variables (e.g. temperature) follow closely, without overshoot, the corresponding control set point (e.g. thermostat setting). This is part of the overall assumption that, to be effectively optimized, a system must be closely controlled. Unlike hemstitching, the "ride" method does not oscillate about the constraint. would seem to make a search strategy with a "ride" substrategy converge to the optimum in fewer steps than one with a hemstitching substrategy.

For any particular process, some control strategies will be better than others. The choice of what basic control strategy (and substrategies) to implement in a SPDC will depend on the knowledge of the P surface, and on the speed and accuracy required by the control computer. Many detailed comparisons of search strategies over various types of P surfaces are

# 2.3 Details of a Specific Search Strategy

Assume that it is required to operate a process as in Figure 2-1 at a minimum of P and satisfy the constraint  $XY \geq C_r$  and that, based on the knowledge of the process, a relaxation search has been chosen. The search is to be divided into two stages, the initial or coarse stage to quickly locate a neighbourhood of the optimum, and a final or fine stage to obtain and track the optimum operating point. If  $\Delta P_{K^{\bullet}}$  the change in P resulting from the Kth step in the coarse search, is less than  $\Delta P_1/A$  of the same gradient direction, a new The step size is to be made gradient direction is to be found. smaller with each overshoot and, if the coarse search is at its smallest step size, an overshoot causes the change from coarse to fine search. In the fine search stage, the control parameters are to be stepped sequentially n times in the local gradient direction using the smallest possible step which will still produce a recognizable  $oldsymbol{\delta}$  P.

For convenience in the instrumentation the choice A=2, n=7 is made and only two step sizes k and k/2 will be allowed. While this arbitrary choice may not create the best possible gradient search, it is suitable to test the ability of simple SPDC to carry out a specific search strategy. This search is very general and should be able to optimize, to some degree, any type of P surface. It also has the advantage, for this thesis, of being complicated enough that, in instrumenting

a SPDC to carry it out, the type of problems and considerations of instrumenting any search strategy by simple logic units should be encountered.

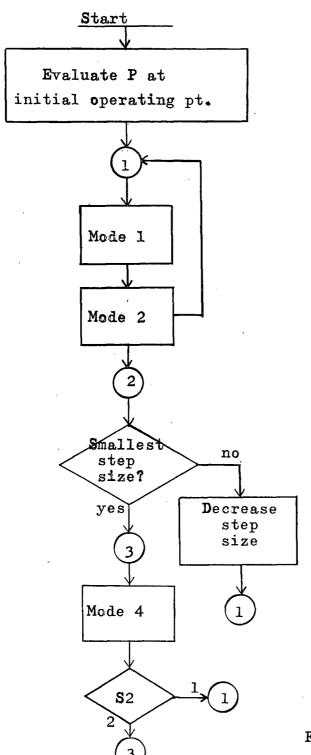

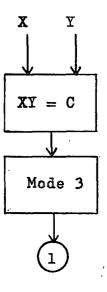

Once the search strategy is chosen, the next step in designing a SPDC is to specify the sequence of operations within the search. The flow diagrams in Figures 2-2 to 2-4 show one possible organization of operations enabling the control computer to carry out the required search. The search is shown broken down into subroutines.

The command subroutine checks whether to continue in coarse search, alternating subroutines mode 1 and mode 2, or to change to mode 4, the subroutine for fine search. When control is transferred from the fine search subroutine back to the command subroutine, the position of switch #2 (S2) determines whether fine search will be continued or the entire search procedure will be repeated (i.e. return to coarse search). If at any time during the search the constraint is violated, control is immediately transferred to mode 3, the constraint handling subroutine. This is shown by a separate flow diagram labelled "priority".

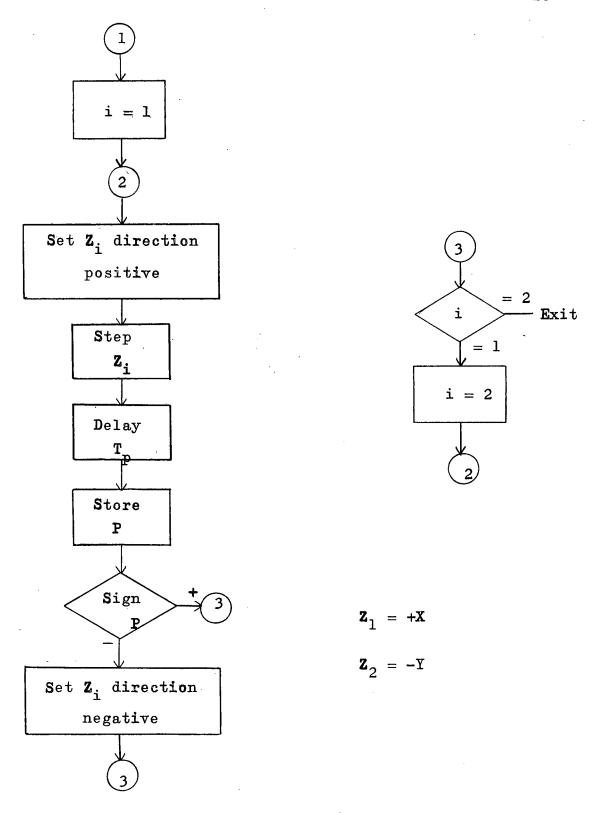

Mode 1 is the subroutine which determines the local gradient direction. X and Y are sequentially perturbed  $\delta$  X and  $\delta$ Y; the size and sign of the resulting  $\delta$ P<sub>X</sub> and  $\delta$ P<sub>Y</sub> are stored.

Mode 2 simultaneously changes X and Y amounts  $\Delta X = -k \delta P_X \text{ and } \Delta Y = -k \delta P_Y. \text{ The step size, k or } k/2, \text{ is}$  chosen by the control subroutine and  $\delta P_X$  and  $\delta P_Y$  are provided by mode 1. These steps are continued until  $\Delta P$  is negative or

$\Delta P_{K} < \frac{1}{2} \Delta P_{1}$

Mode 3 is the constraint handling subroutine. Since the constraint is a known equation of the two control parameters, it is possible to handle this constraint in the same manner as an equality constraint when solving a set of algebraic equations, that is, to reduce the number of variables. As long as XY = C, Y is made a dependent variable. The constraint equation gives the relation between  $\Delta X$  and  $\Delta Y$  and the regular search is continued. This is a variation of the "ride the constraint" substrategy, mentioned in section 2.2, as the search can move along the constraint but never cross it.

Mode 4, the fine search stage, takes seven steps sequentially, stepping X and Y amounts  $\delta$  X and  $\delta$  Y. The directions of the steps are determined by the polarity of the previous  $\delta P_{\rm X}$  and  $\delta P_{\rm Y}$ . These step sizes are used in both mode 1 and mode 4. They should be the smallest step which produces a recognizable change in P.

Priority

Figure 2-2 Flow Diagram of Command Subroutine

Figure 2-3 Flow Diagram of Mode 1

Figure 2-4 Flow Diagram of Mode 2 and Mode 3

Figure 2-5 Flow Diagram of Mode 4

#### 3. THE COMPUTER

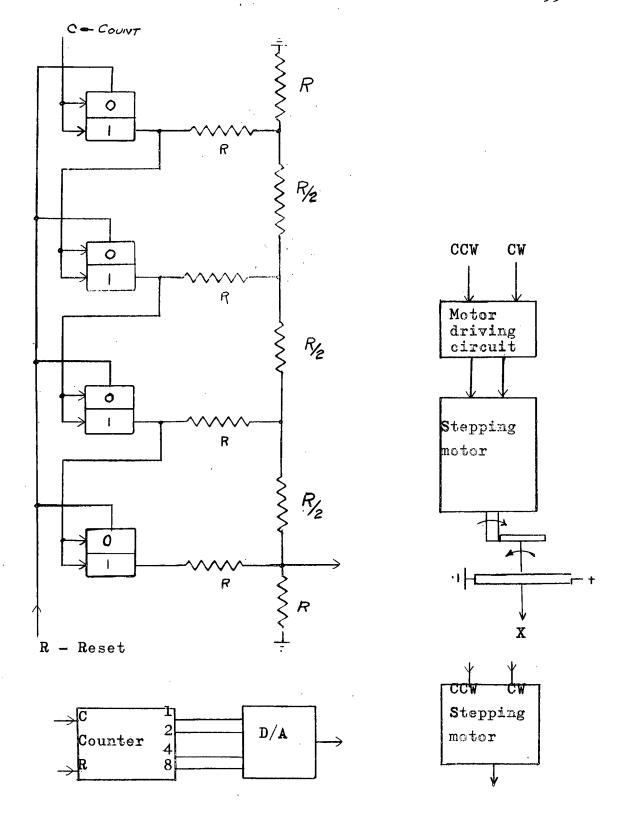

A very inexpensive special purpose digital computer can carry out the search described in section 2.3. The computer design explained in this section uses standard digital logic units such as gates, monostables and flip-flops. The discontinuous nature of empirical optimization and the lengthy storage times required would seem to favour digital rather than analog techniques as would the compatibility of a SPDC with future overall plant digital control or telemetry. A computer using a hybrid of analog and digital techniques could carry out the same search; it might even be argued that the computer described is a hybrid as the outputs of the computer are analog signals obtained from potentiometers driven by step motors. These motors, readily available commercially, are driven by the pulses of the digital equipment. The motors are bidirectional with each input pulse causing a 15° angular displacement of the motor shaft.

Figure 3-1 shows a very simple outline of the computer. The main control unit, labelled Control, co-ordinates the activities of the auxiliary units which are shown as smaller blocks. The computer is termed asynchronous as the controller starts the next operation when the smaller blocks have signalled completion of the current operation rather than waiting a fixed time for the smaller blocks to carry out their operations. P\_ is a negative voltage representing the performance function fed into the control computer by the controlled process, and X and Y are the controlled parameters of the process.

To start the search for the optimum operating point, X and Y are set to some initial values within the limits of the constraint and, when P has reached its steady state value, P (Figure 3-1) is adjusted to equal P. Here P is an internal positive voltage of the computer which is periodically updated to equal the magnitude of P. The SMP block is very much like a sample and hold unit with P as an input and P as an output. As used by the computer, the output of SMP is the change needed to update P.

The change in  $P_+$  is either  $\delta P_X$ ,  $\delta P_Y$  or  $\Delta P$  depending on whether it was caused by  $\delta X$ ,  $\delta Y$  or  $\Delta X$  and  $\Delta Y$ . If the change is  $\delta P_X$ , it is stored in the CCX block; if it is  $\delta P_Y$ , it is stored in the CCY block; and if it is  $\Delta P_Y$ , it is stored in the CCP block.

Upon signal from the Control block, CCX generates a number of pulses proportional to  $\mathcal{S}P_X$  to step X, CCY generates a number of pulses proportional to  $\mathcal{S}P_X$  to step Y. While the circuitry of CCP is much like that of CCX and CCY, its function is different. CCP stores  $\Delta P_1$  in a counter and compares each succeeding  $\Delta P$  with  $\Delta P_1$ . Upon the result of this comparison the search either stays in mode 2 or returns to mode 1.

The block SMX has X as output and the various changes  $\delta$  X and  $\Delta$ X as inputs. The  $\delta$ X input comes directly from the Control block and  $\Delta$ X is routed by the Control block to SMX from CCX. SMY has exactly the same function with Y instead of X. The details of all the blocks are shown in Figures 3-2 to 3-7. The symbols used are explained in Appendix A.

#### 3.1 Control Block

Figure 3-2 and 3-3 are details of the Control block.

Figure 3-2 shows the circuitry for subroutines mode 1 and mode

4. It can be seen from comparing Figures 2-3 and 2-5 that these

two modes are very similar and, as the computer cannot be in

both these modes at the same time, the same equipment is used

for both modes.

The main components of the Control block and their functions are as follows:

- FFA -- selects mode 1 (state 1) or mode 2 (state 2);

- FFG -- selects coarse search (state C) or fine search (state F);

- FFB -- selects, in mode 1 only, whether to change X by a fixed  $\mathcal{S}X$  (state X) or to change Y by a fixed  $\mathcal{S}X$  (state Y);

- MC sets correct logical states of the Control block flipflops to establish the controller in mode 1;

- $MB \longrightarrow produces time delay of T<sub>p</sub> seconds.$

With X and Y at their initial values and P updated, the search routine is initiated by a pulse on all the lines marked S in the figures (start pulse). The computer must first carry out mode 1 as shown in Figure 2-2.

In mode 1 the computer is to:

- move **X** one step,  $\delta$  X, wait T seconds and store  $\delta$  P ;

- move Y one step,  $\delta$  Y, wait T<sub>p</sub> seconds and store  $\delta$  P<sub>Y</sub>;

- -- go to made 2

Referring to Figure 3-2, the S pulse sets FFG to C and sets MC to 1. The MC pulse sets FFA to 1 and sets flip-flops

within SMX and SMY so that any pulses to G53 (Figure 3-4) and the corresponding gate for Y, G54, will step X in a positive direction and Y in a negative direction. The computer is now in mode 1. The MC pulse also sets FFB to X and MD to 1. The MD pulse passes through G2 to G53 and causes X to be stepped by a fixed amount  $\delta X_*$  T<sub>p</sub> seconds later the MB pulse (store) causes SMP to update P<sub>+</sub> to the value of P<sub>-</sub>. The change needed to update P<sub>-</sub>  $\delta P_{X}$  is stored by the CCX block (Figure 3-5). The decision to store this change in P<sub>-</sub> as  $\delta P_{X}$  rather than  $\delta P_{Y}$  or  $\Delta P_{1}$  is based upon the states of FFA and FFB. The sequence is new repeated with Y and is initiated by the end of storage pulse (ES).

The ES pulse from SMP signals that P has been updated. This ES pulse passes through G31 and sets MF. The MF pulse changes the state of FFB (in this case from X to Y), passes through G30 to set MA, and through G11 but not G1. The MA pulse now passes through G6 as FFB has been set to state Y. The G6 pulse causes Y to be changed an amount — SY. The ES signal generated when SPY has been stored passes through G31 and sets MF. The MF pulse does not pass through G30 to continue the mode 1 subroutine; instead, it passes through G11 and then through G1 to set FFA to 2. This setting of FFA to state 2 sets the computer to mode 2 subroutine (Figure 3-3).

Continuing the explanation of Figure 3-2, the operation of the circuitry for mode 4 is the same as that given for mode 1 except that the MC pulse is originated by G50 (SMP) and FFG must have been set to F by G26 (Figure 3-3). In mode 4 the

computer is to move a total of seven fine steps in **X** and **Y**. The directions of the **X** and **Y** steps are determined by the polarity of the previous  $\delta P_{X}$  and  $\delta P_{Y}$ .

The MC pulse originated by G50 sets FFA to 1, determines the direction of the next X and Y steps, and sets FFB to X and MD to 1. The MD pulse passes through G2 stepping  $\delta$  X and in mode 4 this G2 pulse is counted on the seven counter which will now have a count of one. The MB pulse causes SMP to update  $P_+$  T seconds after X has been stepped  $\delta$  X. The ES pulse passes through G31 and sets MF. The MF pulse passes through G30 to continue mode 4.

The G30 pulse sets MA which causes a step  $\delta X$  but the sign (or direction) of this  $\delta X$  is not preset by MC as it was in mode 1. The sign of this  $\delta X$  is determined by the response (sign) of the previous  $\delta P_X$ .

When the counter has received seven pulses, the next MF pulse does not pass through G30 but passes through G34 to set MK. This MK pulse can either continue the mode 4 subroutine or start the entire search routine depending on the position of S2.

The control circuit for mode 2 is shown in detail in Figure 3-3. In mode 2 the computer is to simultaneously step  $\Delta X = -k \delta P_X$  and  $\Delta Y = -k \delta P_Y$ , wait  $T_p$  seconds and record  $\Delta P$ . If  $2\Delta P_k < \Delta P_l$  or if  $\Delta P$  is negative the computer is to return to mode 1. When Gl sets FFA to 2 (Figure 3-2), MG is set to 1. The MG pulse clears the  $\delta X$  and  $\delta Y$  counters of CCX and CCY and

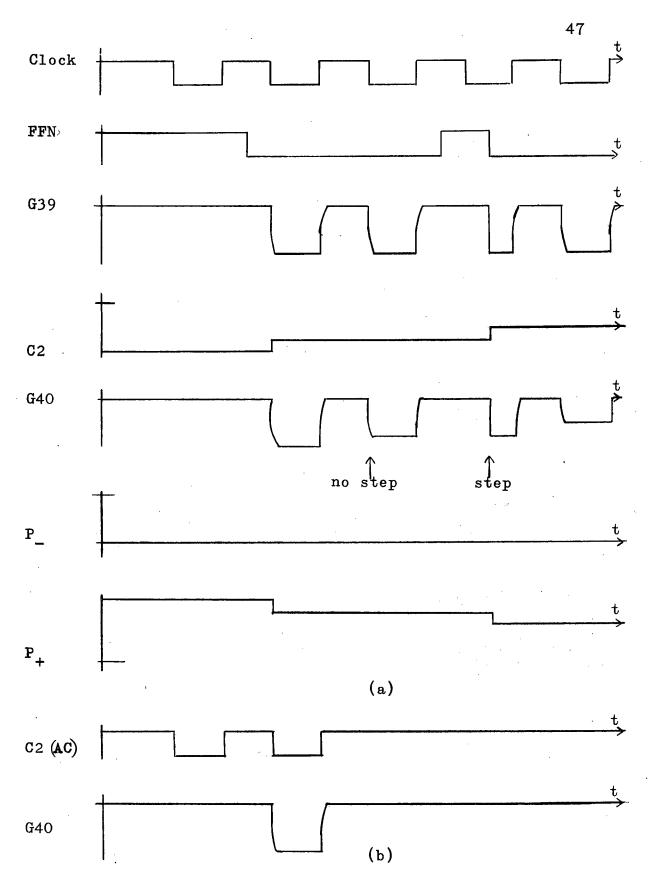

sets MH, MH, MB, and FFE are arranged to allow clock pulses through G20 for  $T_B$  seconds. The MB shown is the same one shown in Figure 3-2 and is repeated only to make the diagram less complicated.  $T_p$  seconds after MB is set, the MB pulse causes SMP to update (store)  $P_+$  in order to find  $\Delta P_*$ . A clock rate of 100 c/s was used in the computer constructed.

CCX passes a number of pulses, proportional to  $\delta P_{X^7}$  to G25. These pulses are passed through G25, or are divided by two, depending on the state of FFH, to SMX where X is changed an amount directly proportional to the number of pulses passed through G25. Equivalent pulses are simultaneously passed through G22 to change Y. The first overshoot signal from SSP during mode 2 sets ML which sets FFH to 1. FFH in state 1 means that one half of G19 pulses pass through G25 cutting the step size  $\Delta X$  in half. The second overshoot during mode 2 passes through G26 to set the Control block to fine search (FFG to F).

ME and G10 are part of the circuitry required for mode 1 but are shown in Figure 3-3 because of limited space in Figure 3-2. An overshoot signal during mode 1 (negative  $\delta P_X$ ) is passed through G10 to SMX so that the direction of  $\Delta X$  will be opposite to that of  $\delta X$ .

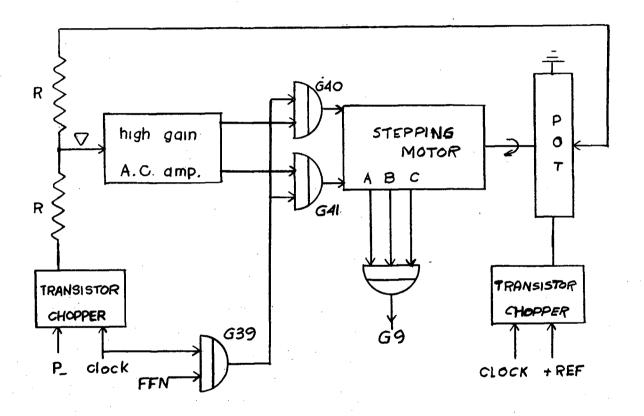

### 3.2 The SMX and SMY Blocks

Figure 3-4 shows SMX, and SMY has exactly the same circuit layout. The function block labelled "Stepping Motor" is explained in Appendix A. The change in X due to one step of the stepping

motor is  $\delta X_s$ . The sign of the change depends on XFFD. The MC pulse at the start of every mode 1 subroutine sets XFFD to "up", but if  $\delta P_X$  is negative a pulse from G10 passes through G5 and changes the state of XFFD.

# 3.3 The CCX, CCY, and CCP Blocks

Figure 3-5 shows CCX, and CCY has exactly the same circuit layout. The counter and the digital to analog converter functional blocks are explained in Appendix A. A number of pulses, proportional to the magnitude of  $\mathcal{S}_{\mathbf{X}^*}$  from G45 passes through G16 and is stored in the counter. Upon a signal from the Control block the CCX block is to produce a number of pulses proportional to the stored  $\mathcal{S}_{\mathbf{Y}^*}$ .