# DEVICES EMPLOYING CONDUCTIVITY MODULATION IN SEMICONDUCTOR FILMS BY FERROELECTRIC POLARIZATION CHARGING

by

#### GEORGE GRIFFITHS TEATHER

B. Eng., McMaster University, 1964

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

#### MASTER OF APPLIED SCIENCE

in the Department of Electrical Engineering

We accept this thesis as conforming to the required standard

Research Supervisor

Members of the Committee

Head of the Department

Members of the Department of Electrical Engineering

THE UNIVERSITY OF BRITISH COLUMBIA

June, 1967

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the Head of my Department or by his representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of

COC. CATE

The University of British Columbia

Vancouver 8 Canada

Dato

~ 20/6M

#### ABSTRACT

Two types of devices employing ferroelectric modulation of a semiconductor thin-film have been realized and studied. The first consists of a cadmium selenide film with electrodes deposited on a barium titanate substrate together with a switching electrode on the other side of the substrate. This gives a two-valued resistor; in effect, a nondestructive readout of the state of the ferroelectric crystal which is regarded as a storage element. The second device is a thin-film transistor (TFT) deposited on a barium titanate crystal. A fourth counterelectrode on the other side of the crystal allows changing between two opposite polarization directions in the crystal, thus giving a TFT with two sets of characteristics, roughly equivalent to a two-valued built-in gate bias.

The read-in, or switching time, of the device is substantially determined by the barium titanate crystal and can be in the microsecond range for high switching fields. Readout of the devices can be continuous or not, as desired.

Characteristics of the TFT, which is considered equivalent to a two-gate device, are analyzed in terms of the gradual channel approximation. Experimental results of the two devices are presented and discussed in relation to the predicted behaviour.

#### TABLE OF CONTENTS

|                                                                    | Page |

|--------------------------------------------------------------------|------|

| ABSTRACT                                                           | ii   |

| TABLE OF CONTENTS                                                  | iii  |

| LIST OF ILLUSTRATIONS                                              | vi   |

| LIST OF TABLES                                                     | viii |

| LIST OF SYMBOLS                                                    | ix   |

| ACKNOWLEDGEMENT                                                    | xiii |

| 1. BASIC PRINCIPLE OF DEVICES                                      | l    |

| 2. THEORY OF DEVICES                                               | 3    |

| 2.1 Field Effect                                                   | 3    |

| 2.2 Two-State TFT - Structure and Operation .                      | б    |

| 2.3 Modified Elementary Theory of the IFT                          | 10   |

| 2.4 Theory of Resistance Modulation Due to Ferroelectric Substrate | 16   |

| 2.5 Effect of Traps on Proposed Devices                            | 18   |

| 3. FERROELECTRIC AND RELATED PROPERTIES OF BARIUM TITANATE         | 22   |

| 3.1 Ferroelectricity                                               | 22   |

| 3.2 Physical Properties of Barium Titanate                         | 24   |

| 3.3 Polarization Reversal                                          | 25   |

| 3.3.1 Introduction                                                 | 25   |

| 3.3.2 Mechanism of Polarization Reversal in Barium Titanate        | 26   |

| 3.4 Experimental Procedure and Results                             | 30   |

| 3.4.1 Crystal Preparation                                          | 30   |

| 3.4.2 Conductivity of Crystals                                     | 31   |

| 3.4.3 Measurement of Remanent Polar-                               | 32   |

|    |     |                                                                    |                             | rage |

|----|-----|--------------------------------------------------------------------|-----------------------------|------|

|    |     | 3.4.4 Slow Speed Switching .                                       |                             | 35   |

|    |     | 3.4.5 High Field Polarization                                      | n Reversal                  | 38   |

| 4. | THE | SEMICONDUCTOR FILM                                                 |                             | 41   |

|    | 4.1 | Introduction                                                       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 41   |

|    | 4.2 | Properties of Cadmium Selenide Sulphide and Effects of Depositions | ition Con-                  | 42   |

|    | 4.3 | Thin Film Evaporation and Mean                                     | surements                   | 44   |

|    |     | 4.3.1 Evaporation Technique                                        |                             | 44   |

|    |     | 4.3.2 Hall Effect Measuremen                                       | ts                          | 46   |

|    |     | 4.3.3 Specimen and Specimen                                        | Holder                      | 48   |

|    |     | 4.3.4 Experimental Results .                                       | 0 a 0 0 a 0 a a 0 0 0 0 0   | 49   |

| 5. |     | IUM SULPHIDE AND CADMIUM SELEN UM TITANATE                         |                             | 52   |

|    | 5.1 | Introduction                                                       |                             | 52   |

|    | 5.2 | Specimen Preparation                                               |                             | 52   |

|    | 5.3 | Electrical Measurements                                            |                             | 53   |

|    |     | 5.3.1 Hall Measurements                                            |                             | 53   |

|    | ,   | 5.3.2 Two-State Resistor                                           |                             | 54   |

|    |     | 5.3.3 Temperature Dependence ductivity                             |                             | 57   |

|    |     | 5.3.4 Stability of Device                                          |                             | 62   |

|    |     | 5.3.5 Photoconductivity Meas                                       | urements                    | 63   |

|    | 5.4 | Cadmium Sulphide Device                                            |                             | 64   |

| 6. | THE | TWO-STATE THIN-FILM TRANSISTOR                                     |                             | 65   |

|    | 6.1 | Fabrication Techniques                                             |                             | 65   |

|    | 6.2 | Electrical Measurements                                            |                             | 65   |

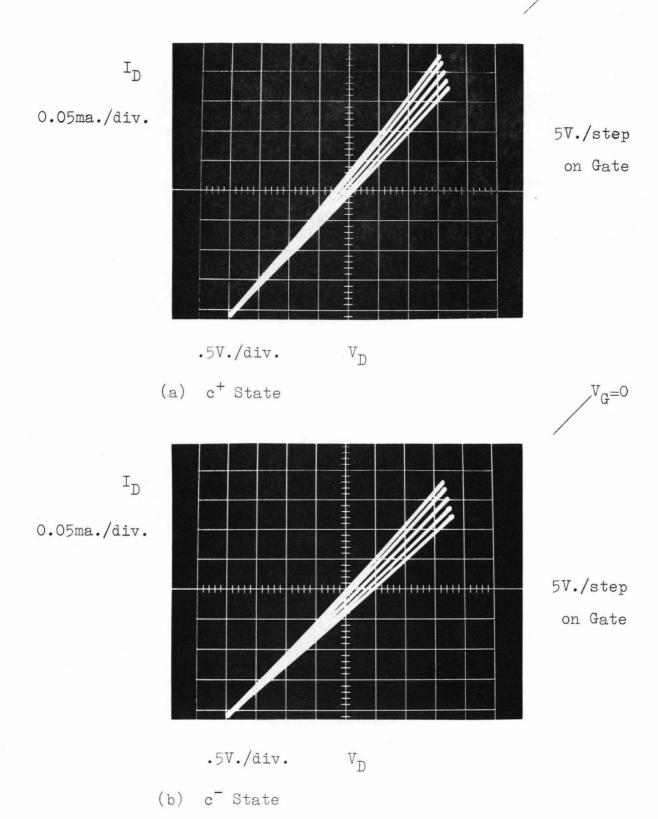

|    | 6.3 | Effect of Silicon Oxide Layer                                      | 0 0 0 0 0 0 0 0 0 0 0       | 70   |

|           |                                                                 | Page |

|-----------|-----------------------------------------------------------------|------|

| 6.4       | Discussion of Results                                           | 70   |

| 6.5       | Comparison of Two Devices                                       | 74   |

| 7. CONCLU | sions                                                           | 75   |

| APPENDIX  | DEVELOPMENT OF MILLER-WEINREICH MODEL OF 180 DOMAIN WALL MOTION | 77   |

| APPENDIX  | II MEASUREMENT OF FILM THICKNESS                                | 81   |

| REFERENCE | s                                                               | 82   |

1

.

### LIST OF ILLUSTRATIONS

| Figure       |                                                                        | Page |

|--------------|------------------------------------------------------------------------|------|

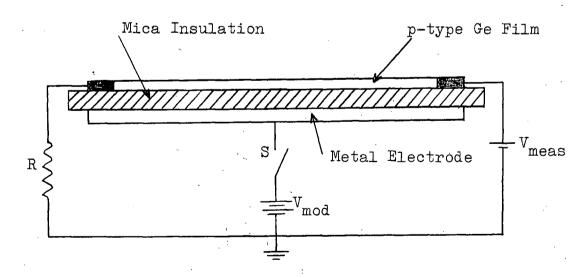

| 2-1          | Modulation of Conductance by Field Effect                              | 3    |

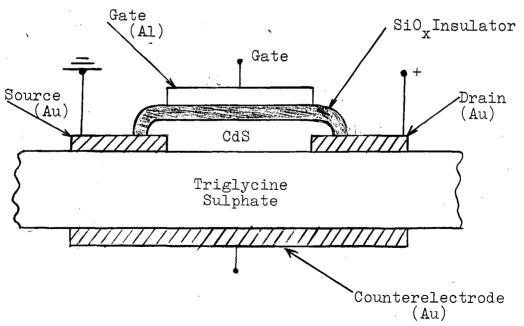

| 2-2          | Cadmium Sulphide TFT on Triglycine Sulphate                            | 5    |

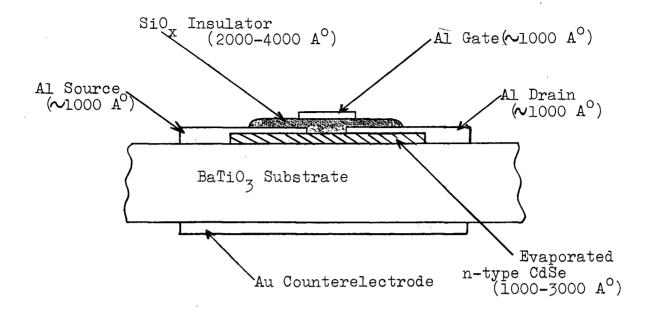

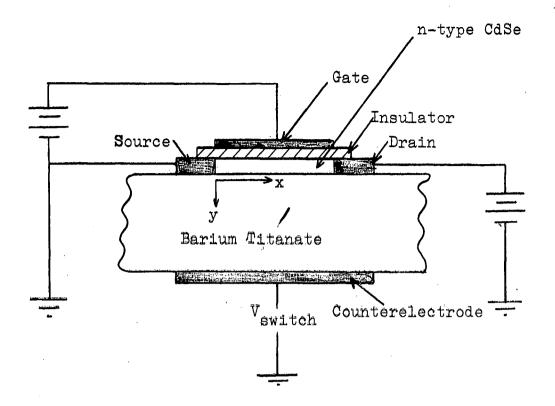

| 2-3          | Cadmium Selenide Two-State Thin-Film Field Effect Transistor           | 7    |

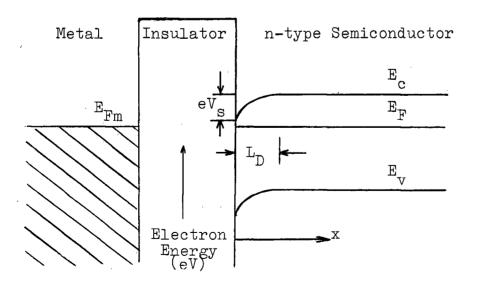

| 2-4          | Metal-Insulator-Semiconductor Energy Level Diagram                     | 7    |

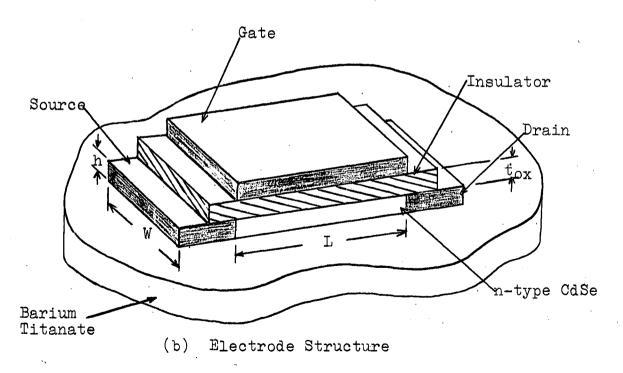

| 2-5          | Idealized Geometry of Cadmium Selenide Two-State TFT                   | 11   |

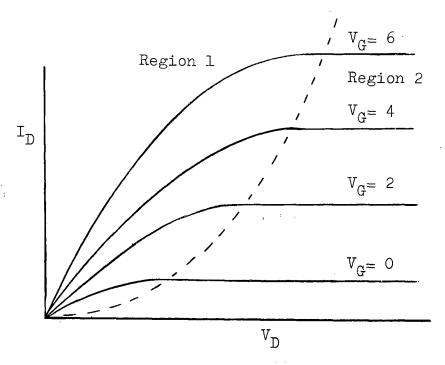

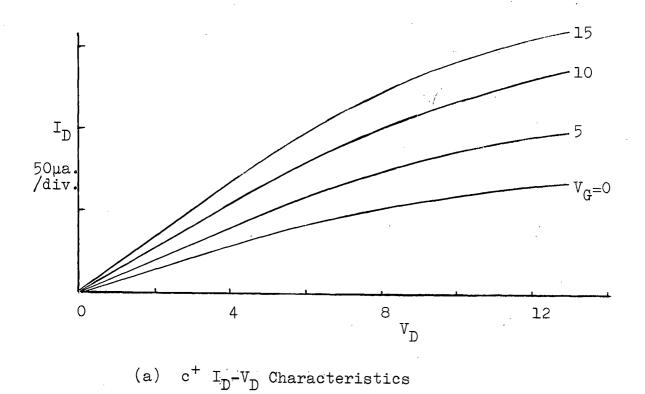

| 2-6          | Representative Drain Characteristics for Two-State TFT                 | 15   |

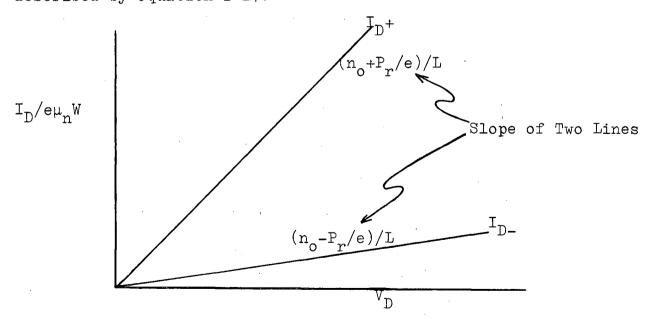

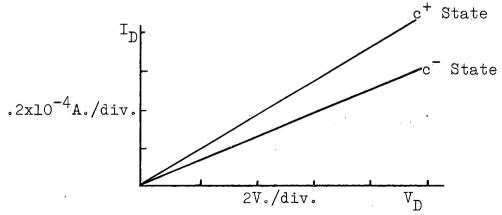

| 2-7          | Typical Characteristics of Two-State Resistor                          | 17   |

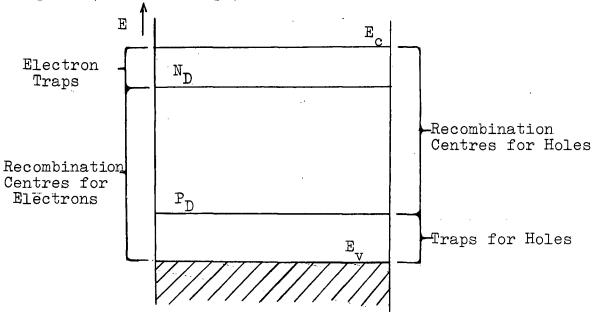

| 2 <b>-</b> 8 | Demarcation Levels in Semiconductor .                                  | 19   |

| 3-1          | Ferroelectric Hysteresis Loop                                          | 23   |

| 3-2          | Cubic Perovskite Structure of Barium Titanate                          | 23   |

| 3-3          | Polarization Reversal of Barium Titanate                               | 27   |

| 3-4          | Voltage Pulse Switching                                                | 28   |

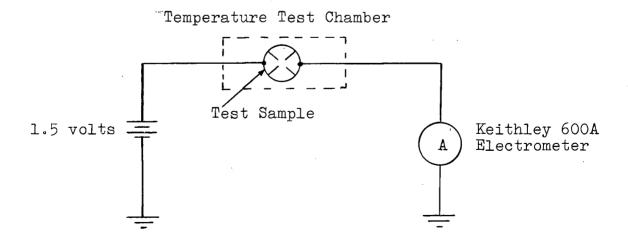

| 3 <b>-</b> 5 | Conductivity Measurement of Barium Titanate Crystals                   | 31   |

| 3 <b>-</b> 6 | Sawyer-Tower Circuit to Determine Remanent Polarization                | 33   |

| 3 <b>-</b> 7 | Experimental P-E Hysteresis Curve of Crystal #1 at Various Frequencies | 34   |

| 3-8          | Slow-Speed Switching Characteristic Measurement Circuit                | 36   |

| 3 <b>-</b> 9 | Slow Voltage Ramp I-V Switching Characteristics                        | 37   |

| 3-10         | High Field Response Measurement Circuit                                | 38   |

| Figure |                                                                                                  | Page |

|--------|--------------------------------------------------------------------------------------------------|------|

| 3-11   | High Field Pulse Measurements                                                                    | 40   |

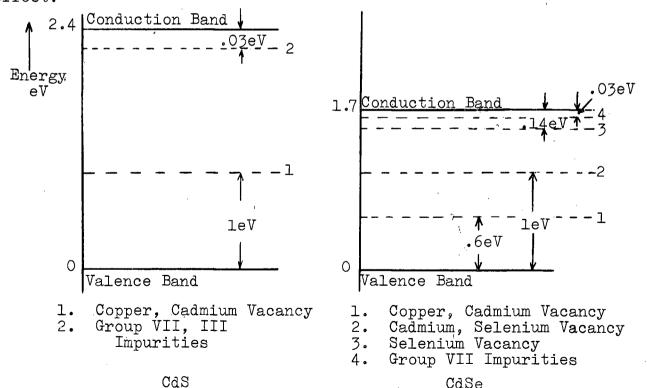

| 4-1    | Imperfection Energy Levels in Cadmium Sulphide and Cadmium Selenide                              | 43   |

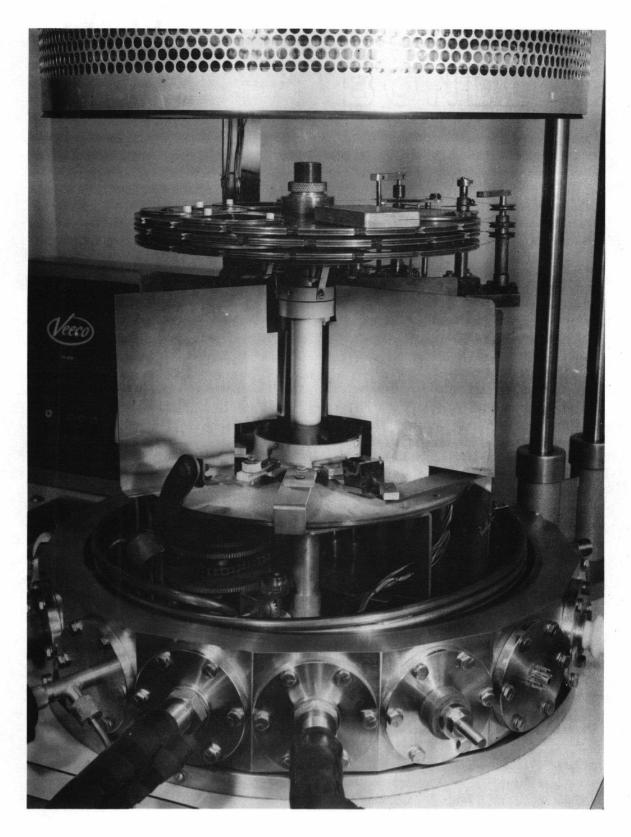

| 4-2    | Veeco Vacuum Deposition Apparatus                                                                | 45   |

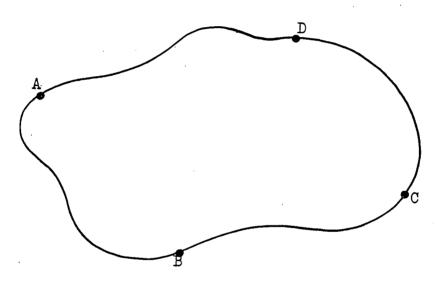

| 4-3    | Hall Sample with Arbitrary Periphery                                                             | 47   |

| 4-4    | Hall Sample of Cadmium Selenide with Aluminum Contacts                                           | 48   |

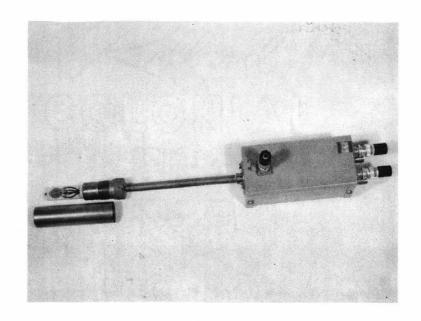

| 4-5    | Hall Specimen Holder                                                                             | 50   |

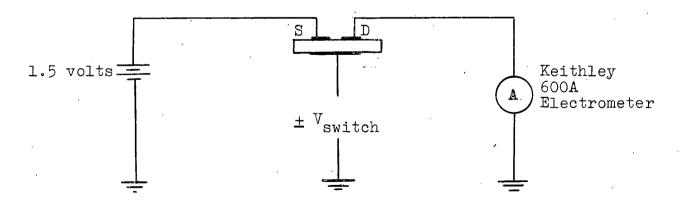

| 5-1    | Semiconductor Film Conductivity Measurement                                                      | 54   |

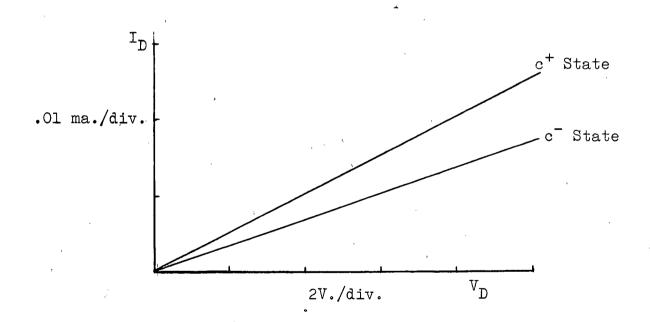

| 5–2    | Operating Characteristics of Two-State Resistor Sample #5                                        | 56   |

| 5-3    | N-Type Semiconductor with Trapping Levels                                                        | 58   |

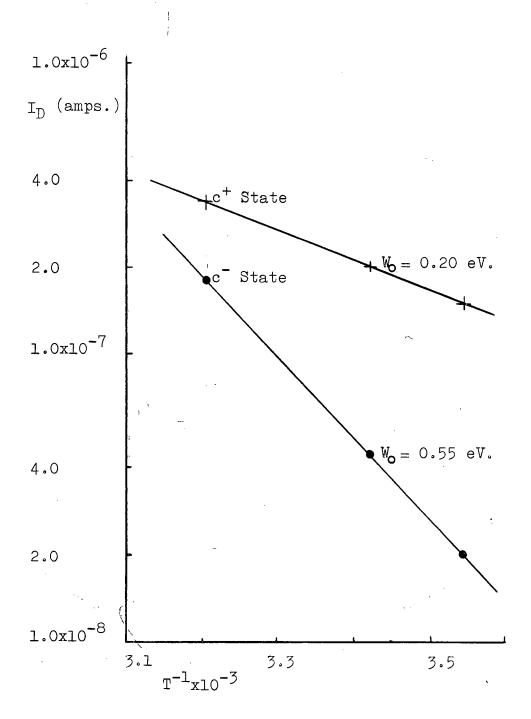

| 5-4    | Temperature Dependence of Conductivity                                                           | 59   |

| 5-5    | $\text{Log}_{10} \text{ I}_{\text{D}}.\text{vs.} \frac{1}{T} \text{ Plot of Sample } \#8 \ldots$ | 61   |

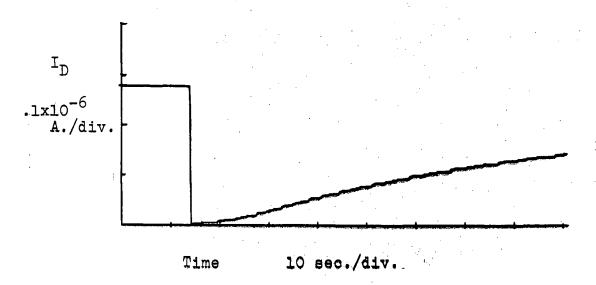

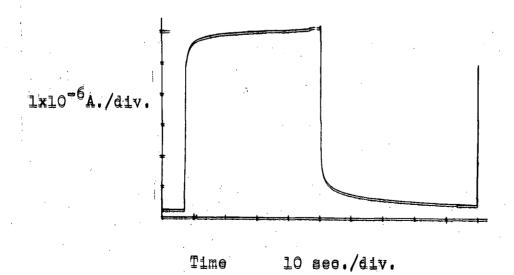

| 5–6    | Back-Switching of Resistance Sample #10                                                          | 62   |

| 5-7    | Photoconductivity Measurement                                                                    | 65   |

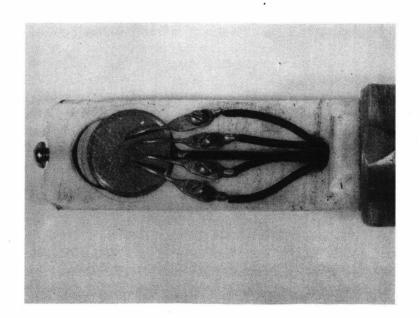

| 6-1    | Cadmium Selenide Two-State TFT                                                                   | 66   |

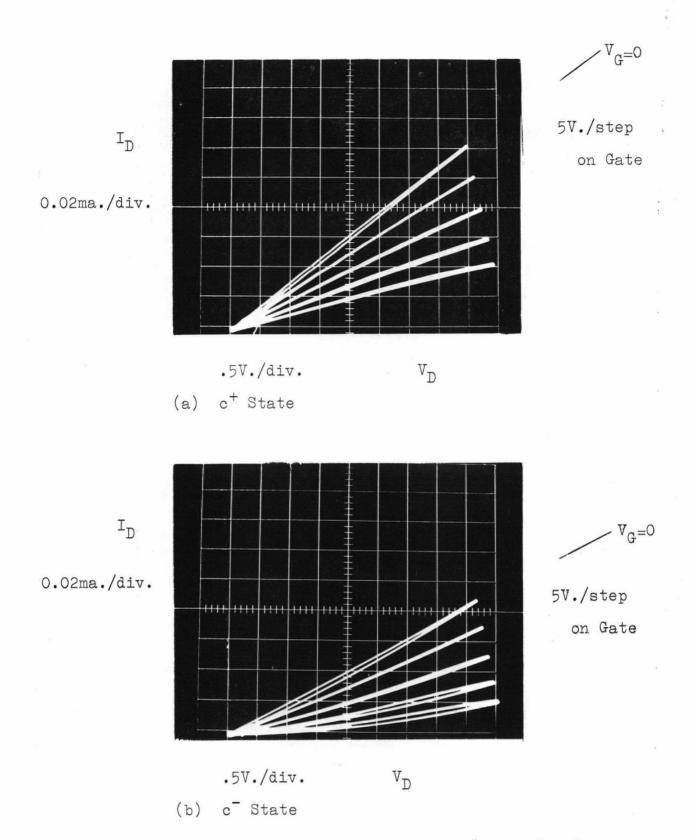

| 6–2    | ${\rm I_D^{-V}_D}$ Characteristic of Sample #14 in Two States with Negative Gate Bias            | 67   |

| 6-3    | ${ m I_D-V_D}$ Characteristics of Sample \$15 in Two States with Positive Gate Bias              | 68   |

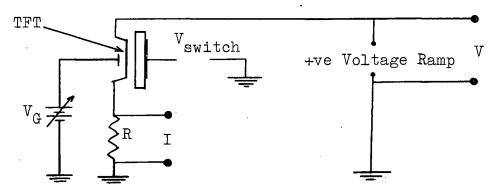

| 6-4    | TFT I <sub>D</sub> -V <sub>D</sub> Characteristic Measuring Circuit                              | 69   |

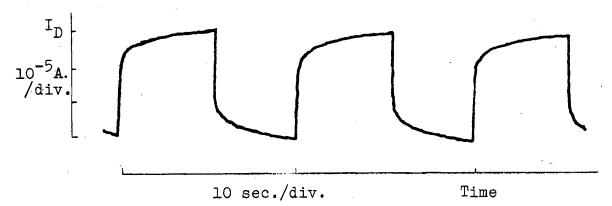

| 6-5    | Output Characteristics of Sample #15                                                             | 71   |

| 6-6    | Response of Sample #14 to Square Wave Input on Gate                                              | 73   |

| AI-l   | Nucleation of Anti-parallel Domain                                                               | 77   |

### LIST OF TABLES

| TABLE |                                                                              | Page       |

|-------|------------------------------------------------------------------------------|------------|

| I     | DEBYE LENGTH FOR CADMIUM SELENIDE AT VARIOUS ELECTRON CONCENTRATIONS         | <u> </u> 9 |

| II    | SUMMARY OF P-E HYSTERESIS LOOP MEASURE-<br>MENTS AT VARIOUS FREQUENCIES      | 32         |

| III   | HALL MEASUREMENT RESULTS OF CADMIUM SULPHIDE AND CADMIUM SELENIDE ON GLASS . | 49         |

| ΙV    | HALL MEASUREMENT RESULTS OF CADMIUM SELENIDE ON BARIUM TITANATE              | 53         |

| V ·   | SUMMARY OF DATA ON TWO-STATE RESISTOR                                        | 56         |

#### LIST OF SYMBOLS

|                           | DIST OF STREETS                                                    |

|---------------------------|--------------------------------------------------------------------|

| $A_{d}$                   | domain wall area                                                   |

| 2a                        | width of antiparallel domain step                                  |

| В                         | magnetic field strength (Kilogaus)                                 |

| b                         | lattice constant parallel to the plane of the crystal              |

| C<br>g                    | gate capacitance per unit area                                     |

| С                         | antiparallel domain step thickness                                 |

| $D_n$                     | normal component of electric displacement (coulombs/cm.2)          |

| $D_1$                     | trapping energy level (eV)                                         |

| d                         | thickness of crystal                                               |

| Ec                        | energy level of conduction band (eV)                               |

| Eco                       | coercive field strength                                            |

| $E_{\mathrm{D}}$          | Electric field strength between source and drain (assume constant) |

| $\mathtt{E}_{\mathbf{F}}$ | Fermi level energy (eV)                                            |

| $\mathbf{E}_{\mathbf{n}}$ | normal component of electric field                                 |

| $\mathrm{E}_{\mathrm{T}}$ | energy difference between trapping level and Fermi level (eV)      |

| E                         | energy level of the valence band (eV)                              |

| $\mathbf{E}_{\mathbf{x}}$ | field strength at any point x between source and drain             |

| е                         | electronic charge                                                  |

| $\mathbf{g}_{\mathrm{m}}$ | transconductance                                                   |

| h                         | thickness of the semiconductor layer                               |

| $\mathtt{I}_{\mathtt{D}}$ | source-drain current                                               |

| i <sub>max</sub>          | maximum current level of switching pulse                           |

| i <sub>s</sub> (t)        | switching current at time t                                        |

| $^{	extsf{i}}\infty$      | experimentally determined constant of the equation                 |

constant of the domain velocity equation  $K_{\tau \tau}$ Boltzman constant k  $\mathbf{L}$ length of source-drain channel L' reduced channel length due to "pinch-off"  $\mathbf{L}_{\mathbb{D}}$ the Debye length 1 height of antiparallel domain step  $^{D}$ electron demarcation level the initial charge concentration in the semiconductor (el./cm. $^2$ )  $N_{o}$  $N_{\mathbf{T}}$ concentration of traps  $\Delta N(x)$ electronic charge induced into the S-D channel at any point x (el./cm.<sup>2</sup>)  $\overline{n}$ unit vector normal to the surface of the capacitor electron concentration per unit area of the semin conductor film (assumed constant) bulk electron concentration in the semiconductor nh (el./cm.3)concentration of conduction band electrons (el./cm.2)  $n_{c}$ concentration of filled traps  $n_{\mathbf{T}}$ electron concentration in the S-D channel at a point x n(x)from the source (el./cm.2)  $\frac{dn}{dt}$ nucleation rate of new antiparallel domains  $P_{D}$ hole demarcation level remanent polarization (coul./cm.<sup>2</sup>) Pr normal component of remanent polarization (coul./cm.2) Prn Preff amount of P effective in causing conductivity modulation Hall constant  $R_{\mathsf{H}}$ S capture crosssection of a trapping centre for electrons  $^{\mathsf{t}}\mathsf{ox}$ thickness of insulator layer ts length of current pulse caused by polarization reversal  $^{\mathrm{t}}\infty$ experimentally determined constant  $\Delta U$ energy change due to nucleation U¥ critical activation energy for nucleation critical activation energy for nucleation of a Մ<sub>7</sub> \* step 1 unit cell wide Ud depolarizing energy thermal velocity of carriers u Ϋ́D source-drain voltage  $V_{G}$ applied gate voltage volume of nucleus  $^{\mathbb{V}}_{\mathtt{p}}$ "pinch-off" voltage necessary to saturate the  $I_D-V_D$ characteristics potential difference between the surface and bulk of the semiconductor  $V_{\mathbf{q}}$ threshold gate voltage needed for the onset of S-D current (x)Vpotential at any point x in the S-D channel reduced potential in the semiconductor (eV/kT) V domain wall velocity P.A W width of S-D channel activation energy of conductivity activation energy for polarization reversal  $\alpha$ fraction of  $P_{r}$  effective in causing conductivity modulation dielectric constant parallel to the plane of the  $\epsilon_{

m a}$ crystal

| εο                                                                                 | permittivity of free space                          |

|------------------------------------------------------------------------------------|-----------------------------------------------------|

| e <sub>ox</sub>                                                                    | permittivity of the ${	t SiO}_{f x}$ layer          |

| $\epsilon_{f r}$                                                                   | dielectric constant of material being considered    |

| $\mu_{\mathbf{n}}$                                                                 | mobility of electrons (cm. <sup>2</sup> /volt-sec.) |

| ρ.                                                                                 | charge density in the semiconductor $(el./cm.^3)$   |

| ρ                                                                                  | conductivity                                        |

| $\sigma_{\!\! n}$                                                                  | S-D channel conductivity                            |

| $\sigma_{\!\scriptscriptstyle  m o}$                                               | experimentally determined constant of the equation  |

| $\sigma_{\hspace{-0.5pt}	extsf{p}}$                                                | constant of the equation                            |

| $\sigma_{\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | wall energy per unit area                           |

| $	au_{\mathtt{T}}$                                                                 | time constant of trapping level                     |

#### ACKNOWLEDGEMENT

The author is indebted to Dr. L. Young for his help and guidance throughout the course of this investigation. Grateful acknowledgement is also given to Dr. D. Akitt for reading the manuscript and for his helpful suggestions.

The author is grateful to Dr. C.A.T. Salama for several helpful discussions; to Messrs. G. Anderson, R. Proudlove, I. Huff, N. Owen, and H. Stuber for their technical help; to Mrs. M. Wein for typing the thesis; and to Messrs. G. Yan, C. Dell'Oca and P. Wilcox for proofreading the manuscript.

Grateful acknowledgement for financial support is given to the National Research Council (Bursary awarded 1964, Block Term Grant A-68) and to the Defence Research Board (contracts ECRDC T65A and T79).

The work described in this thesis was supported by the Defence Research Board under contracts ECRDC T65A and T79 and by the National Research Council.

#### 1. BASIC PRINCIPLE OF DEVICES

The purpose of the work described in this thesis was the study of nondestructive readout of the polarization state of ferroelectric crystals. Possible methods include optical techniques (Ayers, 1967), (Yan, 1964), pyroelectric effect, (Chynoweth, 1960), and conductivity modulation of a semiconductor thin-film deposited on the ferroelectric crystal. The latter is the method to be investigated here.

A ferroelectric crystal has a remanent polarization  $\overline{P_r}$ , the direction of which can be altered by the application of an electric field. This implies that, for a parallel plate capacitor with a ferroelectric dielectric, the charge per unit area on the electrodes is non-zero for zero applied voltage, and is instead equal to  $\overline{P_r}$ .  $\overline{n}$ , where  $\overline{n}$  is a unit vector normal to the capacitor surface. The direction of  $\overline{P_r}$ , and thus the amount of surface charge, can be reversed by application of a switching voltage pulse.

If a semiconducting layer with ohmic contacts is used as one of the electrodes of the capacitor, then the amount of charge in the semiconductor will vary as the ferroelectric is switched by an amount equal to  $2P_r$  per unit area, if  $\overline{P_r}$  is perpendicular to the capacitor surface. Thus the direction of polarization (i.e. the state of the ferroelectric) can be determined by measuring the conductivity of the semiconductor film. It is possible to fabricate semiconductor layers with a concentration of carriers per unit area small with respect

to the ferroelectric remanent polarization of some crystals. This would seem to ensure a large conductivity change. In practice, trapping of charge by surface states and impurities in the semiconductor, mobility changes due to changes in charge concentration, and other effects complicate the behaviour.

If an insulating layer and gate are added to the semiconducting film with electrodes, a thin-film transistor is

formed. This device is expected to have two sets of

characteristics which differ in zero gate voltage current

level, depending on the polarization direction of the ferroelectric crystal.

The devices discussed provide continuous non-destructive readout of the state of the ferroelectric substrate. The readin or storage time is a function of the switching time of the ferroelectric crystal itself, and for high switching field strengths can be in the microsecond range.

#### 2.1 Field Effect

Conductivity modulation of a sample of semiconductor by an electric field perpendicular to its surface is known as field effect. Early references to this effect include those of Lilienfeld, 1933 and Heil, 1935.

Shockley and Pearson, 1948 observed field effect modulation in a germanium film due to a charged field plate parallel to the germanium surface, similar to the case shown in Figure 2-1. In effect, the semiconductor acts as one plate of a capacitor. The electric displacement D<sub>n</sub> of the capacitor system can be described by equation 2-1:

$$D_{n} = \varepsilon_{0} \varepsilon_{r} E_{n} \qquad (2-1)$$

Figure 2-1. Modulation of Conductance by Field Effect

where  $D_n$  is the electric displacement normal to the surface,

$\epsilon_0$  is the permittivity of free space,

$\epsilon_{r}$  is the dielectric constant of mica,

and  $E_n$  is the electric field normal to the surface.

Thus for a given applied field  $E_n$ , the electric displacement is known in terms of the surface charge on the capacitor plates. This field-induced charge, if mobile, will take part in the conduction process. In the particular case shown in Figure 2-1, closing of the switch S will repel holes from the p-type germanium, thus reducing the current through it.

The current modulation observed by Shockley and Pearson was only a small fraction of that expected. The discrepancy was interpreted as evidence for the existence of surface states capable of trapping the induced charge.

Field effect modulation has also been observed by using a ferroelectric insulator between the capacitor plates. An early reference is that of Godefroy, 1952, who observed measureable field effect modulation in tellurium evaporated onto ceramic barium titanate. For the case of a ferroelectric insulator, equation 2-1 is modified to form equation 2-2:

$$D_{n} = \varepsilon_{r} \varepsilon_{o} E_{n} + P_{rn}$$

(2-2)

where  $\epsilon_{\mathbf{r}}$  is the relative dielectric constant of the ferroelectric,

and Pri is the remanent polarization of the ferroelectric normal to the surface.

Field effect modulation of conductivity can be observed even with no applied field since the direction of  $\mathbf{P_r}$  can be changed by a voltage pulse applied across the ferroelectric.

Stadler, 1965, observed a conductance change of 2% in  $100\text{A}^{\text{O}}$  thick gold films on single crystal barium titanate after reversing the polarization direction. Moll, 1963 and Zuleeg and Wieder, 1966, described an active device with variable gain and remanent memory. This device, shown in Figure 2-2, consisted of a cadmium sulphide insulated gate field effect transistor, similar to that developed by Weimer, 1962, deposited

Figure 2-2. Cadmium Sulphide TFT on Triglycine Sulphate (Moll)

on a ferroelectric substrate of triglycine sulphate with a counter electrode on the other side. Moll, 1963 observed a resistance variation of 25%, as the polarization was reversed, for a resistance of  $60 \text{K}\Omega$  between source and drain. Finally, Heyman and Heilmeier, 1966, described a variable resistor using p-type tellurium between ohmic contacts on triglycine sulphate, with a counterelectrode on the other side of the ferroelectric substrate.

In the work to be reported here, cadmium selenide was used as the semiconductor, and barium titanate as the ferroelectric substrate, to form an active device with memory storage. Passive devices with variable resistance are also described using cadmium sulphide and cadmium selenide films deposited on barium titanate.

#### 2.2 Two-State TFT-Structure and Operation

The basic structure of the active device to be considered is shown in Figure 2-3. It consists of a thin film of n-type cadmium selenide deposited onto a barium titanate substrate. Aluminum source-drain electrodes are then evaporated onto the cadmium selenide, followed by an insulating layer of silicon oxide and an aluminum gate electrode. The device operates by modulation of the cadmium selenide film conductivity by both the gate and the ferroelectric substrate. Essentially, therefore, the device can be considered as a two-gate TFT. One of the gates, the barium titanate, has only two possible settings, and the other is continuously variable.

Figure 2-3. Cadmium Selenide Two-State Thin-Film Field Effect Transistor

Figure 2-4. Metal-Insulator-Semiconductor Energy Level Diagram

Consider a one-dimensional model of an n-type semiconductor at thermal equilibrium with an insulator-metal contact as shown in Figure 2-4 (Many, 1965). The potential V in the semiconductor is given by Poisson's equation:

$$\nabla^{2} V = -\frac{\rho}{\varepsilon_{r} \varepsilon_{o}}$$

(2-3)

where  $\rho$  is the charge density in the semiconductor.

For the planar geometry shown and assuming negligible hole concentration in the semiconductor, equation 2-3 reduces to the Poisson-Boltzman equation:

$$\frac{d^2V}{dx^2} = -\frac{e}{\epsilon_r \epsilon_o} n_b (1 - \exp eV/kT)$$

or further,

$$\frac{d^2v}{2} = \frac{e^2}{\varepsilon_r \varepsilon_o kT} n_b (1-\exp v) \qquad (2-4)$$

where  $n_b$  is the semiconductor bulk electron concentration and  $v=\frac{eV}{kT}$ . For  $v\leqslant\frac{1}{2}$ , equation 2-4 can be approximated by equation 2-5:

$$\frac{\mathrm{d}^2 \mathrm{v}}{\mathrm{dx}^2} = \frac{\mathrm{v}}{\mathrm{L}_\mathrm{D}^2} \tag{2-5}$$

where

$$L_{D} = \sqrt{\frac{\varepsilon_{r} \varepsilon_{o} kT}{e^{2} n_{b}}}$$

With boundary conditions:  $v = v_s$  at x = 0, and v = 0 at  $x = \infty$ , equation 2-5 can be integrated directly to yield equation 2-6:

$$v = v_s \exp(-x/L_D)$$

(2-6)

Thus  $\mathbf{L}_{D}$ , the effective Debye length, is the distance into the semiconductor at which the potential  $\mathbf{v}$  is the 1/e of its value at the surface, for small  $\mathbf{v}$ .

The model just developed is analogous to the gateinsulator-semiconductor layer of the device to be considered.

Thus, for small V, modulation of the conductivity of the semiconductor by the gate is confined to a depth in the order of the

Debye length from the surface of the insulator. Similarly,

conductivity modulation at the ferroelectric-semiconductor interface ends at a depth in the order of the Debye length into the

semiconductor.

Table 1 gives the value of  $\mathbf{L}_{\overline{\mathbb{D}}}$  for cadmium selenide with various electron concentrations.

| ${f r}^{ m D}$     |

|--------------------|

| 416 A <sup>O</sup> |

| 1320               |

| 4160               |

| 13200              |

|                    |

TABLE 1

Debye Length for Cadmium Selenide at Various Electron Concentrations

It is also necessary that the carrier concentration be kept small in order to have a large amount of carrier modulation due to the gate and ferroelectric substrate. If the carrier concentrations are too large, then the additional charges injected by the field effect will be negligible in comparison.

The structure of the two-state resistor is similar to that of the active device except the insulating layer and gate are missing. Conductivity modulation is caused only by the ferroelectric polarization change. As for the active device, modulation is greatest when the semiconductor layer has a small carrier concentration and is relatively thin.

# 2.3 Elementary Theory of the Insulated Gate Field Effect Transistor Modified to Include the Ferroelectric Substrate

In this section, the elementary theory of the thin-film field effect transistor (Borkan and Weimer, 1966), (Weimer, 1964), is modified to include the effect of the ferroelectric substrate. It is seen that a two-state TFT results from this analysis. The following assumptions are used in this treatment of the model:

- 1. Carrier mobility is constant, independent of the gate or source-drain field, and of the polarization state of the ferroelectric substrate.

- 2. The gradual channel approximation holds. That is, the rate of change of the source-drain field is small compared to the rate of change of the gate field normal to the channel. Poisson's equation may then be solved in one dimension.

(a) Crossectional View

Figure 2-5. Idealized Geometry of Cadmium Selenide Two-State Transistor

- 3. Trapping effects are neglected.

- 4. Gate capacitance is assumed constant.

- 5. The work function differences between the electrodes and the semiconductor are neglected. Ohmic source and drain contacts are assumed.

- 6. The carrier modulation at each surface of the semiconductor is assumed independent of the other.

The idealized device structure and the co-ordinate axes used in the analysis are shown in Figure 2-5.  $V_G$  and  $V_D$  represent the potentials applied to the gate and drain electrodes respectively. V(x) is the potential of the semiconductor at any point with respect to the source.

Source-drain current  $I_D$  is given by:

$$I_{D} = \sigma_{n}^{E} x$$

$$= e \mu_{n} Wn(x) \frac{d V(x)}{dx}$$

where

$\sigma_n$  is the channel conductivity,

$\mathbf{E}_{\mathbf{x}}$  is the field strength between source and drain,

$\mu_{n}$  is the effective mobility in the source-drain channel

W is the channel width,

n(x) is the electron concentration per unit area in the semiconductor at a distance x from the source,

and e is the electronic charge.

The charge per unit area induced into the semiconductor layer at any point x by the applied gate voltage is given by equation 2-7:

$$\Delta N(x) = \frac{C_g}{WLe} (V_G - V(x))$$

(2-7)

where  $C_g$  is the gate capacitance per unit area,  $C_g = \epsilon_{ox}/t_{ox}$ .

Consider also the ferroelectric substrate which has a permanent polarization charge per unit area of  $\pm$  P<sub>r</sub>, which will cause a compensating charge of  $\pm$  P<sub>r</sub> to be induced into the semiconducting layer.

Thus,

$$n(\mathbf{x}) = \Delta N(\mathbf{x}) + N_o \pm \frac{P_r}{e}$$

$$= \frac{1}{e} \left[ \frac{C_g}{WL} (V_G - V(\mathbf{x})) \right] + N_o \pm \frac{P_r}{e} \qquad (2-8)$$

where N<sub>o</sub> is the initial charge concentration per unit area in the semiconductor, neglecting the effect of the ferroelectric substrate.

Substituting for n(x) in equation 2-6 and integrating from x = 0 to x = L, yields equation 2-10:

$$I_{D} dx = \int_{0}^{V_{D}} e \mu_{n} W n(x) dV(x)$$

$$= \int_{0}^{V_{D}} \left[ \mu_{n} W \frac{C_{g}}{WL} \left[ V_{G} - V(x) \right] + eN_{o} \pm P_{r} \right] dV(x)$$

$$I_{D} = \frac{\mu_{n} C_{g}}{T_{r}^{2}} \left[ (V_{G} - V_{T}) V_{D} - \frac{V_{D}^{2}}{2} \right] \qquad (2-10)$$

$$V_{T} = -\frac{N_{O}eWL}{C_{g}} \pm \frac{P_{r}WL}{C_{g}}$$

(2-11)

The threshold voltage  $V_{\mathrm{T}}$  is the applied voltage required for the onset of drain current. It is negative for depletion mode and positive for enhancement mode devices.

As  $V_{\overline{D}}$  is increased, a condition occurs in which the surface concentration of carriers at a distance x from the source is zero:

$$O = \frac{V_{T}C_{g}}{WL} + \left[V_{G} - V(x)\right] \frac{C_{g}}{WL}$$

(2-12)

This condition occurs first at x = L and the pinch-off voltage  $V_{\mathfrak{p}}$  is given by equation 2-13:

$$V_{p} = V_{G} - V_{T}$$

(2-13)

For drain voltages greater than  $V_p$ , the gradual channel approximation no longer holds, since no channel exists over part of the source-drain region. It is assumed that the gradual channel approximation holds up to the point where  $V(x) = V_p$ . This occurs at L', where L' < L. All charge which arrives at L' is assumed to be swept across the remaining high field region to the drain.

Thus, for  $V_D > V_p$ , equation 2-10 becomes:

$$I_{D} = \frac{\mu_{n}^{C}g}{2T^{2}} (V_{G} - V_{T})^{2}$$

(2-14)

L' is very nearly equal to L. Therefore, the characteristics of the device saturate for  $V_D > V_p$ .

(a) Low-State Characteristics

(b) High-State Characteristics

Figure 2-5. Representative Drain Characteristics for Two-State TFT

Figures 2-6(a) and (b) show representative  $I_{\bar{D}}-V_{\bar{D}}$  characteristics given by equations 2-10 and 2-13 for the two regions of the device and the two states of the ferroelectric crystal.

Transconductance of the device below saturation is given by equation 2-15:

$$\mathbf{g}_{\mathbf{m}} \stackrel{\triangle}{=} \left( \frac{\mathbf{S}^{\mathbf{I}_{\mathbf{D}}}}{\mathbf{S}^{\mathbf{V}_{\mathbf{G}}}} \right)_{\mathbf{V}_{\mathbf{D}}} = \mu_{\mathbf{n}} \frac{\mathbf{C}_{\mathbf{g}} \mathbf{V}_{\mathbf{D}}}{\mathbf{L}^{2}}$$

(2-15)

In this elementary analysis of the device, the reversal of the ferroelectric polarization charge gives two sets of  $\mathbb{I}_D$  -  $\mathbb{V}_D$  characteristics differing only in  $\mathbb{V}_T$ . All other parameters of the device, including mobility and  $\mathbb{g}_m$ , are constant.

For this device, with  $\rm V_D>\rm V_p$ , and constant gate voltage, two current levels may be observed, depending on the polarization state of the ferroelectric substrate. Thus, information about the state of the ferroelectric crystal is given by the current level of the device characteristics.

# 2.4 Theory of Resistance Modulation Due to Ferroelectric Substrate

The following is an elementary treatment of the theory of the two-state resistor. The device structure as described in Figure 2-4 will be assumed with the insulator and gate neglected. For a given voltage  $V_{\rm D}$  across the source-drain gap, assuming ohmic contacts, the drain current  $I_{\rm D}$  is:

$$I_{D} = \frac{V_{D}}{R} = \frac{V_{D}Wh}{L}$$

$$= ne\mu_{n}E_{D}W \qquad (2-16)$$

where  $\rm E_D = \rm V_D/L$  is the electric field strength between electrodes, and n is the electron concentration per unit area of the semiconductor film.

Once again, assume the polarization charge at the surface of the ferroelectric is compensated by an equal and opposite mobile charge in the semiconductor. Then,  $n = n_0 \pm \frac{P_T}{e}$  where  $n_0$  is the electron concentration of the semiconductor assuming no polarization charge. Therefore, the current between the source and drain will be linear with voltage applied, as a resistor, and will have two values which depend on the polarization direction of the ferroelectric substrate as described by equation 2-17:

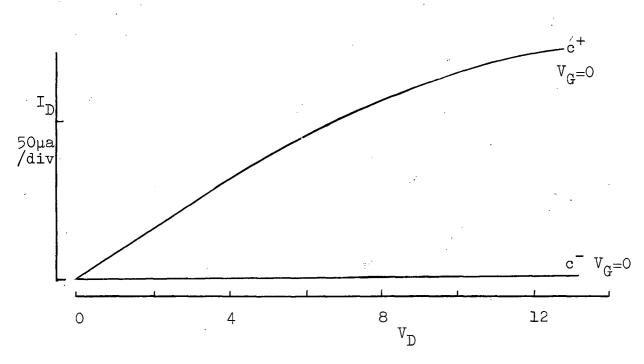

Figure 2-7. Typical Characteristics of Two State Resistor

$$I_{D} = ne\mu_{n} WE_{D}$$

$$= (n_{o} \pm \frac{P_{r}}{e}) e\mu_{n} WE_{D}$$

(2-17)

Note that since  $P_r$  is constant, the modulation efficiency of the device, defined by  $\frac{I_{D^+}}{I_{D^-}}$ , is inversely proportional to  $n_o$ . This device may also be used to give non-destructive readout of the state of the ferroelectric crystal. In this case, the state of the crystal is determined by the resistance level of the device.

#### 2.5 Effect of Traps on Proposed Devices

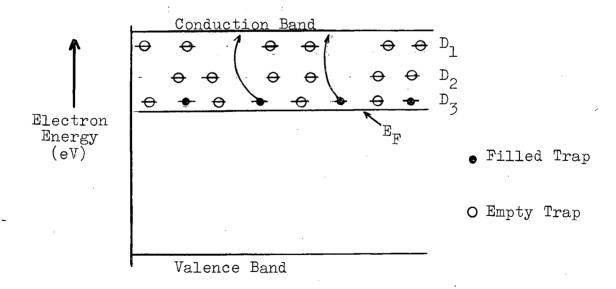

Both within the semiconductor and at its surface there exist centres which can capture one or more electrons from the conduction band. If the captured electron has a high probability of returning to the conduction band rather than recombining with a hole, the centres act as traps (Bube, pg. 273). If there are several levels of centres between the conduction and valence bands, those close to the conduction band act as traps while those further away are recombination centres, since there is a higher probability of combining with a hole than of returning to the conduction band. It is possible to define an electron demarcation level  $N_{\rm D}$  between the two types of centres (Rose, Pg. 28). At this level, the probability of an electron returning to the conduction band and of recombining with a hole is equal. There also exists an equivalent demarcation level for holes,  $P_{\rm D}$ .

The demarcation levels shown in Figure 2-8 hold for only one specific equilibrium condition. As the Fermi level moves,  $N_{\rm D}$  and  $P_{\rm D}$  must change also.

Surface states often act as trapping centres and may be so numerous as to seriously affect the performance of field effect devices such as are considered here (Weimer, 1964). Consider the case where the ferroelectric polarization direction is reversed suddenly to increase the electron concentration in the semiconductor. The charge induced into the semiconductor goes initially into the conduction band. Over a period of time, some of this charge is removed from the conduction band to fill traps. Thus, the carrier concentration decreases until a steady state level is reached where the number of traps being filled equals the number emptying back into the conduction band.

Figure 2-8. Demarcation Levels in Semiconductor

If the number of traps is large, almost all of the induced charge may be trapped.

The kinetics of the trapping process are governed by an equation of the form:

$$\frac{\delta n_T}{\delta t} = uSn_c(N_T - n_T) - Kn_T \exp(-E_T/kT)$$

(2-18)

where u is the thermal velocity of the carrier  $(u=\sqrt{2k\pi n})$ , S is the capture cross section of the centre for electrons,  $n_c$  is the concentration of conduction band electrons,

$n_{\tau\!\!\!/}$  is the concentration of filled traps,

$\textbf{N}_{m}$  is the concentration of trapping levels,

$\mathbf{E}_{\mathrm{T}}$  is the energy between the trap level and the conduction band,

and K is a constant of proportionality.

A single electron trapping level will give an exponential time variation in carrier concentration, the time constant of which is given by:

$$\tau_{\text{T}} = (uSN_{\text{T}})^{-1}$$

However, in most materials, several trap levels are present and the change in carrier concentration with respect to time becomes the sum of many exponentials.

For the case of the proposed devices, a large surface state density at the semiconductor-insulator interface is expected for several reasons. Tamm states, (Tamm, 1932),

which are due to a termination of the periodic potential of the crystal lattice at the semiconductor surface, may be present. Also, there may be a large concentration of impurities on the ferroelectric crystal before the semiconductor film is deposited, due to electrostatic attraction between the ferroelectric crystal and impurity atoms present in the atmosphere. These contaminants, being in intimate contact with the ferroelectric surface, would have very fast trapping time constants, similar to the fast states found in germanium (Heiman and Warfield, 1965).

## 3. FERROELECTRIC AND RELATED PROPERTIES OF BARIUM TITANATE

#### 3.1 Ferroelectricity

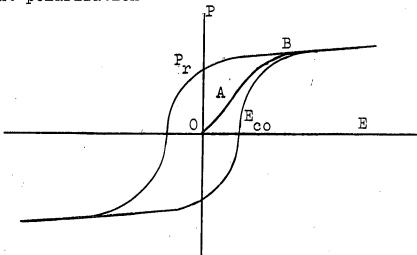

A ferroelectric crystal is defined as one which exhibits a spontaneous electric dipole moment or polarization, the direction of which may be altered by application of an electric field (Dekker, Pg. 184). Total polarization P is related to applied electric field E by a hysteresis loop as in Figure 3-1.

In general, the direction of spontaneous polarization, known as the polar axis, is not the same throughout the crystal. A number of individual domains may exist with different polarization directions which depend on the crystal structure of the material. If a macroscopic sample with zero initial net polarization is considered, application of an electric field will cause the net polarization to increase as the various domains tend to line up with the applied field. This process corresponds to the curve OAB in Figure 3-1. When all domains are aligned with the applied field, further increases in P are small and due only to induced polarization effects.

Ferroelectrics are so named because of the analogy between the P-E hysteresis loop of Figure 3-1 and the B-H loop of ferromagnetic materials (Megaw, Pg. 1). The permanent dipole moment of ferroelectric crystals disappears above a certain temperature  $T_{\rm C}$ , which is known as the Curie temperature. Ferroelectrics are characterized by a non-centric crystal structure with a unique

- polarization(coulombs/cm.<sup>2</sup>) P

- electric field(volts/cm.) E

- E<sub>co</sub> coercive field P<sub>r</sub> remanent polari remanent polarization

Figure 3-1. Ferroelectric Hysteresis Loop

Figure 3-2. Cubic Perovskite Structure of Barium Titanate

polar axis which can be reversed by an electric field. Above the Curie temperature, the crystal class changes to one of higher symmetry.

In their ferroelectric phase, ferroelectric crystals exhibit both pyroelectric and piezoelectric properties.

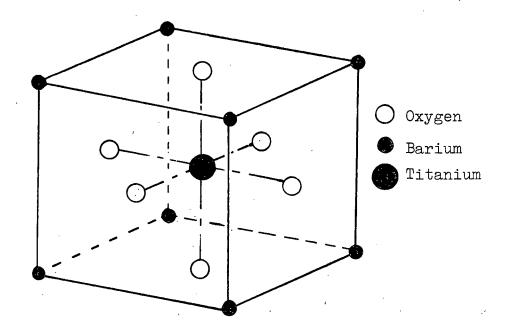

## 3.2 Physical Properties of Barium Titanate

Barium titanate, although only discovered to be ferro-electric in 1945-46, (Wul and Goldman, 1945), (Von Hippel, 1946) has since been widely investigated. Its stability, both mechanical and chemical, a large remanent polarization, and a Curie temperature of over 100°C are some of the reasons for the interest shown barium titanate, especially for practical device applications. The atomic structure of the perovskite crystals, of which barium titanate is the best known, is much simpler than that of other ferroelectrics. Thus, research into the basic phenomenon of ferroelectricity has included much work with barium titanate (Devonshire, 1954).

Barium titanate is crystalline, clear to dark brown in colour depending on the amount of iron dopant present, and has a high refractive index. The Curie temperature is near 120°, the exact transition temperature being dependent on the crystal impurities. The non-polar phase of barium titanate is cubic (point group m3m) and has the cubic perovskite type structure, a unit cell of which is shown in Figure 3-2.

Below the Curie temperature, the crystal becomes tetragonal (point group 4mm). The tetragonal axis may have three possible orientations, which are along one of the three

pseudo-cubic axes. Also, the polar axis, which is parallel to the tetragonal c axis, may be in either direction along the axis. The tetragonal c axis is about 1% longer than the other two. This causes mechanical stresses to occur in the crystal between different domains (Megaw, Pg. 65). In an equilibrium condition, the polar axis lies in a direction to minimize stresses, both mechanical and electrical, on the crystal. Small areas within the crystal tend to align themselves together to form domains, since, over a small area of the crystal, stress conditions are the same. Thus, the ferroelectric domain structure of barium titanate can be very complex, with various individual domains aligning themselves in any one of six possible directions.

Further crystallographic phase changes occur in barium titanate at  $5^{\circ}\text{C}$  and  $-90^{\circ}\text{C}$  (Jona and Shirane, Pg. 109). The crystal remains ferroelectric but with reduced remanent polarization.

### 3.3 Polarization Reversal

#### 3.3.1 <u>Introduction</u>

Unlike uniaxial ferroelectrics such as Rochelle salt and triglycine sulphate (TGS), it is possible to change the direction of polarization of a single domain of barium titanate by either 90° or 180°. Of the two, 180° switching or polarization reversal has been studied most, since many practical applications of barium titanate involving information storage make use of the effect of polarization reversal (Anderson, 1952), (Anderson, 1956), (Campbell, 1957).

Most barium titanate single crystals are grown by the Remeika method (Remeika, 1954). The growth habit of the crystals is such that triangular plates with one pseudo-cubic axis perpendicular to the plane of the plate are formed. When the polar axis of a domain is normal to the crystal surface, the domain is said to be c-domain; when parallel to the surface, the domain is a-domain (Hooton and Merz, 1954). One can differentiate between the two polar directions of a c-domain by using the notation c<sup>+</sup> and c<sup>-</sup>, depending on the direction of the polar axis with respect to the top of the crystal.

180° switching usually involves reversing the direction of polarization in a c-domain crystal by application of an electric field opposite to the existing polarization direction.

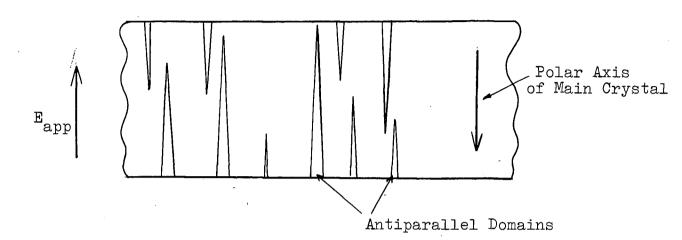

## 3.3.2 Mechanism of Polarization Reversal in Barium Titanate

The thermodynamic theory of barium titanate switching developed by Devonshire (Devonshire, 1949, 1951) predicted the general shape of the P-E relationship found experimentally. However, the predicted coercive field was several orders of magnitude above that obtained experimentally. It was therefore assumed that polarization reversal took place in a small area of the crystal first, then spread out, rather than the whole crystal reversing its polarization state at once as required by the thermodynamic theory, since the energy requirements are much lower for this process than for a total instantaneous change.

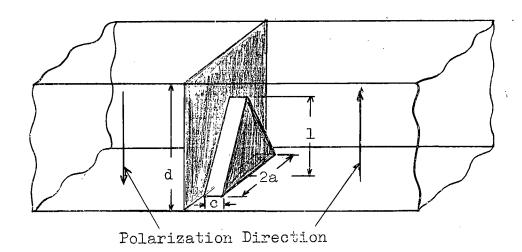

Merz, 1954 and Little, 1955 both reported polarization reversal to occur by the formation of small anti-parallel domains

on the crystal surfaces which then grew through the crystal to form spikes as shown in Figure 3-3.

Figure 3-3. Polarization Reversal of Barium Titanate

The first published data on the rate of polarization reversal and time of reversal was presented by Merz, 1954.

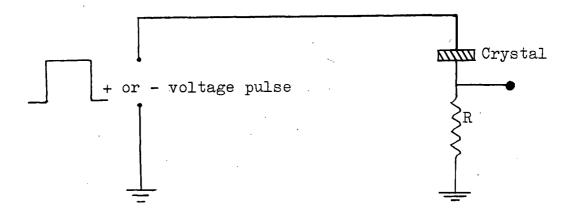

The switching current was recorded as a voltage drop across a resistor in series with the switching voltage source as shown in Figure 3-4(a). Metal electrodes were used on the crystals.

Figure 3-4(b) denotes a typical response curve of a crystal in the c state to a positive voltage pulse. Figure 3.4(c) represents the response of the crystal to a second positive voltage pulse.

At low field strengths, (2 Kv./cm. or less) the experimental results of Merz can be fitted to equations of the form:

$$i_{\text{max}} = i_{\infty} \exp(-\alpha/E)$$

(3-1)

and

$$1/t_{s} = 1/t_{\infty} \exp(-\alpha/E)$$

(3-2)

$i_{\infty}$  and  $t_{\infty}$  are the current and switching time respectively for an infinite field strength E,

(a) Switching Circuit of Merz

(d) Response to Second Pulse

Figure 3-4. Voltage Pulse Switching (Merz)

and  $\alpha$  is termed the switching activation energy and is 1V./cm. for the samples of Merz. Switching times as fast as .2 µseconds were observed for crystals 5 x  $10^{-3}$  cm.thick.

Stadler, 1958, 1962 extended the work of Merz to higher values of field strength and found that for fields up to 100 Kv./cm. equation 3.3 was valid:

$$1/t_s = 1/t_\infty E^{1.4}$$

(3-3)

A theoretical model of polarization reversal which assumes motion of  $180^{\circ}$  domain walls, developed by Miller and Weinreich, 1960, gives results which are consistent with much of the published experimental data. The model assumes that nucleation of antiparallel domains controls domain wall motion. That is, nucleation of new antiparallel domains occurs at the wall boundary preferentially and causes domain wall propagation. This theory, which is developed in Appendix I, yields expressions for nucleation rate  $\frac{dn}{dt}$ , and domain wall velocity  $v_d$ , of the form:

$$\frac{\mathrm{d}\mathbf{n}}{\mathrm{d}t} = \mathbf{K}_1 \quad \exp \quad - \quad \alpha/\mathbf{E} \tag{3-4}$$

and

$$v_{d} = K_{2} \exp - \alpha / E \qquad (3-5)$$

where  $K_1$  and  $K_2$  are independent of E.

These expressions hold for low field strengths (<3Kv./cm.). For higher field strengths, the derivations of Miller and Weinreich were extended by Stadler and Zachmandis, 1964 and yielded expressions of the form:

$$\frac{\mathrm{dn}}{\mathrm{dt}} = K_3 E^{1.4} \tag{3-6}$$

and

$$v_d = K_4 E^{1.4}$$

(3-7)

where  $K_3$  and  $K_4$  are also independent of E.

Stadler and Zachmandis, 1964 also observed experimentally the high field nucleation rate and domain wall velocity and found the same power dependence on E as derived from the Miller-Weinreich theory.

While the theory of polarization reversal is by no means complete, the mechanism of polarization reversal proposed by Miller and Weinreich is promising as a basis for formulating a more complete theory of switching behaviour.

## 3.4 Experimental Procedure and Results

#### 3.4.1 Crystal Preparation

The barium titanate crystals used were thin triangular plates 0.2 to 0.4 mm thick. They were commercially grown by a modified Remeika process.\* The crystals were cleaned by etching for 10-15 minutes in 85% by volume  $H_3PO_4$  at a temperature of 140-160°C, then rinsed in distilled and deionized water. Longer etching periods were used at times to further reduce crystal thickness. The etching was carried out above the Curie temperature in order to prevent preferential etching of the various domains (Hooton and Merz, 1955).

In most cases, no effort was made to obtain single domain crystals before electrode deposition. However, the crystals could be 'poled' to the "c" state by placing the crystals between electrodes in deionized water and applying a

<sup>\*</sup>Semi-Elements Inc. Purity of crystals > 99.95%

large alternating voltage (Campbell, 1957). There was a tendency following this treatment for some of the crystals to revert to a polydomain state because of stresses within the crystal. Circular electrodes of aluminum or gold were deposited on the crystals using standard vacuum deposition techniques in a Veeco vacuum system. Deposition pressures were in the  $10^{-5}$  –  $10^{-6}$  torr. range.

For most measurements, aluminum electrodes were used since they were more durable. However, gold electrodes were used in some instances to ensure good contacts.

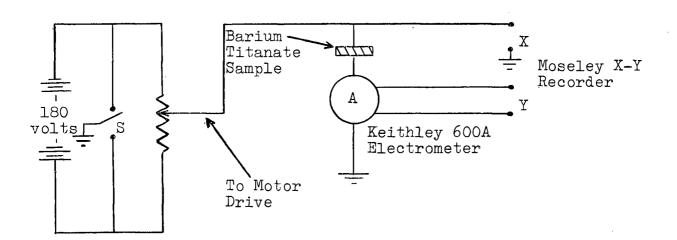

#### 3.4.2 Conductivity of Crystals

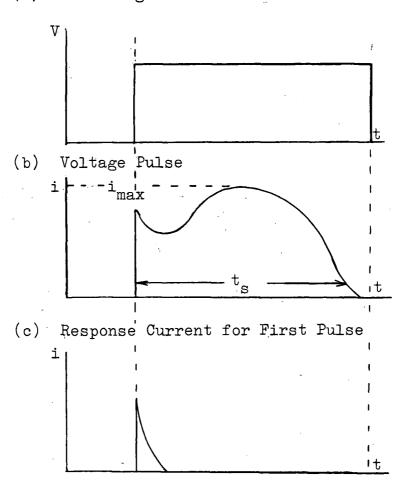

The conductivity of prepoled samples with circular aluminum electrodes was measured at low field strength. The simple circuit used to determine sample resistance is shown in Figure 3-5. The voltage was applied so as not to reverse the domain polarization direction. Conductivity of the crystals was found to vary between 1.0 x  $10^{-9}$  and 2.0 x  $10^{-10}$   $\Omega$ -cm. for

Keithley 600A Electrometer

Figure 3-5. Conductivity Measurement of Barium Titanate Crystals

samples .17 to .32 cm. thick. This compares favourably with previously quoted values (Jona and Shirane, pg. 182).

#### 3.4.3 Measurement of Remanent Polarization

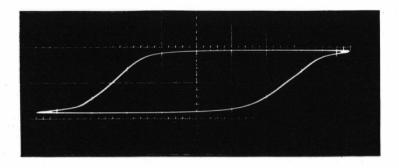

In order to observe the P-E hysteresis loop of the crystals, the modified Sawyer-Tower, 1930 circuit of Figure 3-6, was used. The voltage across the crystal was measured directly by the X deflection of the oscilloscope. The polarization of the crystal, proportional to the voltage across the linear capacitor  ${\bf C_0}$ , is measured by the Y deflection of the oscilloscope. The crystal holder was designed to minimize stray capacitance.

The P-E hysteresis loop of crystal #1 is shown in Figure 3-7 at various frequencies. In Table II are given the values of  $P_{\bf r}$  and  $E_{\bf co}$ , calculated for crystals #1 and #4 at various frequencies.

$X_{TAL}$  #1 thickness: .21mm. Electrode area: 3.0mm.  $X_{TAL}$  #4 thickness: .15mm. Electrode area: 3.0mm. 2

|                     | Frequency cps.                            | 10   | 100  | 250  |

|---------------------|-------------------------------------------|------|------|------|

| X <sub>TAL</sub> #1 | P <sub>r µcoul./cm.<sup>2</sup> ±5%</sub> | 23.6 | 22.2 | 21.0 |

|                     | E <sub>co</sub> volts/cm.<br><u>±</u> 5%  | 2000 | 2350 | 2750 |

| X <sub>TAL</sub> #4 | P <sub>r μcoul./cm.2</sub> ±5%            |      | 24.8 |      |

|                     | E volts/cm.<br>co <u>+</u> 5%             |      | 2400 |      |

TABLE II

Summary of P-E Hysteresis Loop Measurements at Various Frequencies

C<sub>o</sub> - General Radio .7 μfd. Standard Capacitor

Figure 3-6. Sawyer—Tower Circuit to Determine Remanent Polarization

(a) Measurement Frequency 10 c./s.

(b) Measurement Frequency 100 c./s.

(c) Measurement Frequency 250 c./s.

Figure 3.7 Experimental P-E Hysteresis Curves of Crystal #1 at Various Frequencies

Vertical Scale .7 amp./div. Horizontal Scale 20 volts/div. The commonly accepted low frequency value of  $P_r$  for single crystal BaTiO $_3$  is 26 µcoul./cm. $^2$  (Merz, 1953) at room temperature. The slightly lower values obtained here indicate that the crystals used are not entirely single domain, but rather contain small domains which do not switch, possibly because of crystal imperfections.

As the measurement frequency increased, the value of  $P_r$  decreased slowly as shown in Figure 3-7(a), (b) and (c). A possible reason for this effect is that the more highly strained areas of the crystal do not have time to reverse and thus do not contribute to the measured polarization.

The coercive field is also seen to increase in value as the frequency increases. This behaviour is predicted by equation 3-1. At faster switching speeds, the switching current is must be larger in order to complete polarization reversal in time.since

$$2P_{r} = \int_{0}^{t_{s}} i_{s}(t)dt \qquad (3-8)$$

where  $i_s(t)$  is the switching current at time (t). Thus, higher switching voltages are required and  $E_c$  increases as  $t_s$  decreases.

# 3.4.4 Slow Speed Switching

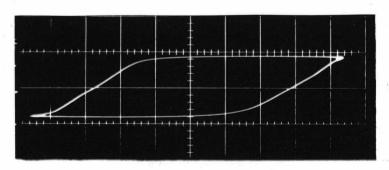

Very slow speed switching characteristics of the barium titanate crystals were recorded using the circuit of

Figure 3-8. Switching occurs at a much better defined voltage at low speeds. Figure 3-9(a), (b) and (c), show the I-V switching curves for three different crystals for a slowly increasing ramp voltage (30 V./min.). The crystal of Figure 3-9(a) is relatively well-behaved. Switching occurs at the same voltage in both directions and  $E_{\rm c}$  is well defined. The switching curve is also very symmetrical. This is typical of an unstrained, single domain crystal. Figures 3-9(b) and (c) show deviations from the ideal. In Figure 3-9(b), the coercive field is ill-defined and the crystal appears to be highly strained and polycrystalline. The crystal of Figure 3-9(c) seems to be preferentially oriented. That is, it would rather be one of the c states than the other.

In all cases, the areas under the curve are equal in both directions from zero volts. This is necessary, since the area under the curve is a measure of the amount of charge

Figure 3-8. Slow-speed Switching Characteristic Measurement Circuit

Figure 3-9. Slow Voltage Ramp I-V Switching Characteristics

being reversed by the applied voltage. If a voltage ramp is followed by a second ramp of the same polarity, negligible current will flow during the second ramp, since the polarization charge has already been reversed and the resistance of the sample is very high  $(> 10^9 \Omega)$ .

The spontaneous polarization of the crystals may be calculated from this graph and the total charge flowing has been found to be equal to  $2P_r$  within the limits of experimental error ( $\sim 20\%$ ).

The coercive field, defined as the field at which the current is maximum, is between 310-550 V/cm for the samples shown. These values are much below those found at the higher switching speeds used to determine the hysteresis loops of Figure 3-7, as expected.

## 3.4.5 High Field Polarization Reversal

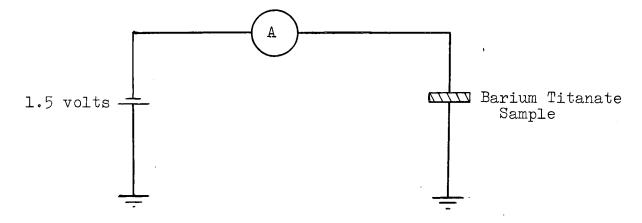

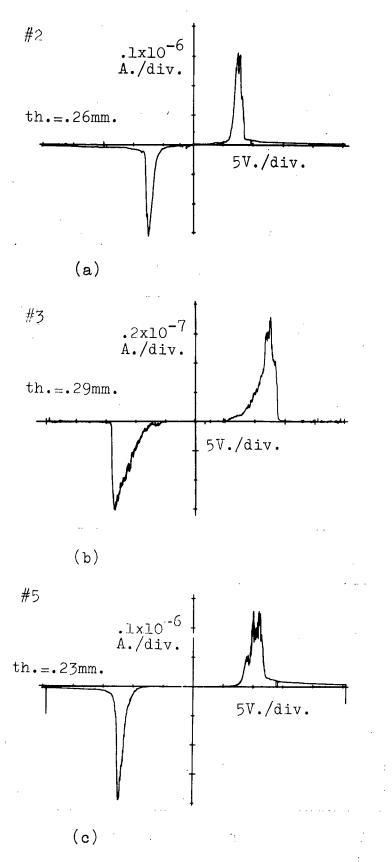

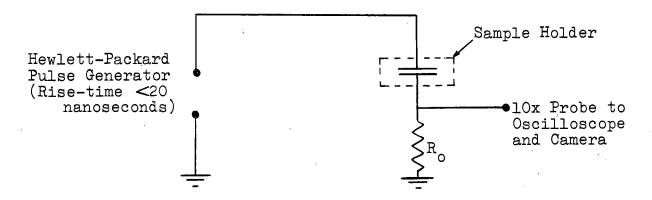

Polarization reversal of the barium titanate crystals was performed using high voltage pulses. The magnitude of the switching current and the switching time were measured using the circuit shown in Figure 3-10.

Figure 3-10. High Field Response Measurement Circuit

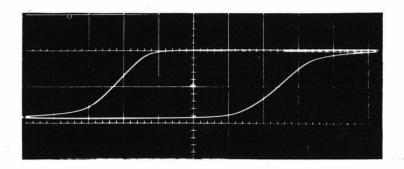

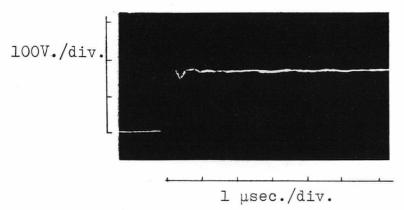

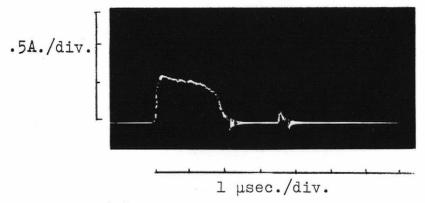

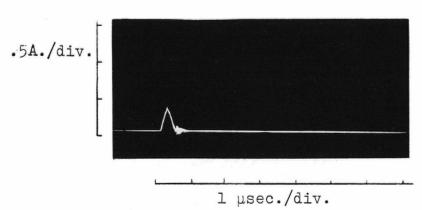

$\boldsymbol{R}_{_{\mbox{\scriptsize O}}}$  must be small in order to keep the system time constant as small as possible. A value of  $10 \Omega$  gave reasonable output voltages for the crystal electrode area used. The crystals tested were prepoled by the slow speed switching technique to ensure single-domain structure, then switched by a single voltage pulse. Figure 3-11(a) and 3-11(b) show the input voltage pulse and polarization reversal current flow respectively for a well behaved crystal. It is seen that the output current pulse is similar to that obtained by Merz, 1954. Figure 3-11(c) shows the current flow caused by a second input pulse of the same sign and magnitude. The area under the second pulse is less than 10% of that under the first. The crystal has been almost completely switched by the first pulse and the second pulse is caused almost totally by the normal capacitive action of the barium titanate crystal (Anderson, 1952).

An instantaneous current level of .7 amps is reached across the crystal during switching. Care must be taken not to destroy the electrodes by rapidly repeated switching at high speeds.

It is also possible to determine  $P_{r}$  from the area under the switching curve at these speeds. A rough calculation from Figure 3-ll(b) yields a value for  $P_{r}$  of 22  $\mu$ coul./cm.<sup>2</sup>, in good agreement with the expected value of 26  $\mu$ coul./cm.<sup>2</sup>.

Switching time of 2 µsec. for crystal thickness of .22mm. and switching voltage of 170 volts has been obtained. For thinner crystals, the switching voltage may be reduced proportionately to maintain the same switching time.

(a) Input Voltage Pulse

(b) Crystal Response to First Pulse

(c) Crystal Response to Second Pulse of the Same Polarity

Figure 3-11. High Field Pulse Measurements

#### 4.1 <u>Introduction</u>

Important requirements on the characteristics of the semiconductor film are high mobility and low carrier concentration (Weimer, 1964). High mobility is needed to give good device gain and frequency response. The carrier concentration must be low enough to allow effective modulation by both the gate and ferroelectric substrate.

Much of the work done with thin-film transistors has employed wide band-gap semiconductors in order to obtain low carrier concentrations. Various semiconductors have this property: silicon of the group IV, gallium arsenide and gallium antimonide of the group III-V, and cadmium sulphide and cadmium selenide of the group III-VI compounds. Of these, cadmium selenide and cadmium sulphide were chosen for the work described here.

The preparation of relatively high mobility, low concentration polycrystalline films of cadmium selenide and sulphide has been reported by many authors. The amount of substrate heating required for deposition of silicon would cause problems, and the techniques of depositing semiconducting gallium arsenide are not well defined. Cadmium selenide was found to be better suited than cadmium sulphide as the semiconductor film for the devices considered since the single crystal mobility of cadmium selenide is higher than that of cadmium sulphide (500 cm.<sup>2</sup>/volt-sec. vs. 200 cm.<sup>2</sup>/volt-sec., Bube, Pg. 269).

Another reason for the use of cadmium selenide is that deposition of this material has been found to be much more uniform and reproducible than cadmium sulphide.

# 4.2 <u>Properties of Cadmium Selenide and Cadmium Sulphide and Effects of Deposition Conditions</u>

Cadmium selenide and cadmium sulphide are group II-VI compounds with an hexagonal crystal lattice structure. The energy band gap for single crystal cadmium selenide has been found to be 1.7 ev. and for cadmium sulphide 2.4 ev. (Bube, Pg. 234).

Preparation of thin films of these compounds is very important in determining their electrical properties. Films deposited onto unheated substrates are highly disordered, of low mobility, and nonstoichiometric because of the nonequilibrium process. The films are usually highly conductive and cadmium-rich. Deposition onto heated substrate reduces these effects but does not remove them. Therefore, post-deposition treatment of the semiconductor films is often desirable (Boer, Esbitt, and Kaufman, 1966) to obtain films with proper characteristics.

Crystal defects are important in determining the properties of the film. Cadmium vacancies act as donors and cation (sulphur, selenium) vacancies act as acceptors. Crystal defects are present in all films and are especially prevalent in polycrystalline films. Impurity atoms affect the electrical properties of the films as well. Group III and VIII impurities act as donors and group I and V atoms as acceptors. Figure

4-1 shows the energy levels of various donors and acceptors of cadmium sulphide and cadmium selenide as shown by Bube, Pg. 159. The acceptor levels are so deep that p-type conductivity is not observed in either cadmium sulphide or cadmium selenide.

Also, Oxygen impurity atoms may act as acceptors in both cadmium sulphide and cadmium selenide.

Post-deposition treatment of the films, if necessary to bring the carrier concentration level to the desired value, may take many forms, but heat treating in an air or sulphur atmosphere at 300-500°C has been found to reduce the conductivity of the material by diffusion of oxygen or sulphur acceptor atoms into the semiconductor (Bube, Pg. 175). Heat treating in vacuum or in cadmium vapour produces the opposite effect.

Figure 4-1. Imperfection Energy Levels in Cadmium Sulphide and Cadmium Selenide

Ohmic contacts are formed by evaporating aluminum onto the cadmium sulphide or cadmium selenide film, or by depositing gold electrodes on the substrate before the semiconductor film is deposited.

#### 4.3 Thin Film Evaporation and Measurement

## 4.3.1 Evaporation Technique

${\rm CdS}^*$  and  ${\rm CdSe}^{**}$  thin films were prepared by evaporating from a heated quartz crucible in the Veeco vacuum system onto a cold or heated substrate. Figure 4-2 shows the experimental set-up for the deposition. Evaporation pressures were in the  $10^{-6}$  -  $10^{-5}$  torr. range. Film thickness was monitored using quartz crystal oscillators (Chaurasia, 1964) inside the vacuum system close to the substrate. Further discussion of thickness measurement is given in Appendix II.

The various film configurations were obtained by evaporating through photo-etched berylium copper masks held with the substrate in a mechanical jig.

Substrate heating, when required, was accomplished by placing a resistive heating element enclosed in a copper holder in thermal contact with the mechanical jig. Temperature was monitored by a thermocouple held in the centre of the mechanical jig which is in contact with the barium titanate crystal.

The evaporation technique consisted of placing the cleaned mechanical holder mask and substrate, already aligned, in place in the vacuum system, closing it and pumping the

<sup>\*</sup>Cadmium Sulphide Powder UHP Eagle Picher Co.

<sup>\*\*</sup> Cadmium Selenide Powder 99.9995% pure A.D. Macay, Inc.

Figure 4-2. Veeco Vacuum Deposition Apparatus

system until the pressure was in the high  $10^{-6}$  torr. range. The resistive heated quartz crucible holding the source material was then heated slowly to outgas the semiconductor evaporant. The source current was then increased until the source material began to evaporate at the proper rate  $(1-10~\text{A}^{\circ}/\text{sec.})$ , then the shutter closing off the substrate from the source was opened and deposition began. Source current, pressure, elapsed time, and thickness crystal monitor reading were all recorded. After evaporation, the system was allowed to cool before exposing the film to atmosphere.

Ohmic contacts were obtained by evaporating aluminum onto the semiconductor film from a tungsten filament source with a vacuum of  $1 \times 10^{-5}$  torr.

#### 4.3.2 <u>Hall Effect Measurements</u>

Hall effect measurements to determine thin-film carrier concentration and mobility were performed using a Van der Pauw, 1958 geometry. The advantage of this geometry is that sample shape is not critical, only sample thickness need be known.

The measuring circuit used was described previously by T. W. Tucker, 1966 of this laboratory. The circuit employs Keithley 600A electrometers and can measure specimen resistances up to  $10^{10}\Omega$  with <5% error.

The resistivity of a sample of arbitrary periphery as shown in Figure 4-3 is calculated by substituting in equation 4-1:

$$\rho = \frac{\pi h}{\ln 2} \left( \frac{R_{ABCD} + R_{BCDA}}{2} \right) f \left( \frac{R_{ABCD}}{R_{BCDA}} \right)$$

(4-1)

where  $\rho$  is resistivity of the sample in  $\Omega$ -cm., h is sample thickness in cm.,

$$R_{ABCD}=rac{V_D-V_C}{I_{AB}}$$

, and  $R_{BCDA}=rac{V_A-V_D}{I_{BC}}$  , where  $V_A-V_D$  is the

potential difference between A and D while current  $\mathbf{I}_{BC}$  is flowing between B and C.

When  $R_{ABCD} \approx R_{BCDA}$ , then  $f(\frac{R_{ABCD}}{R_{BCDA}}) \approx 1$ .

Figure 4-3. Hall Sample with Arbitrary Periphery

The Hall constant  $R_{\rm H}$  is calculated from equation 4-2:

$$R_{H} = \frac{1}{ne} = \frac{10^{8} \Delta(V_{C} - V_{A})h}{B I_{BD}}$$

(4-2)

where B is magnetic field across the crystal in Kilogaus, and  $\Delta(V_C - V_A) \text{ is the change in } V_C - V_A \text{ caused by the magnetic field, under constant current } I_{BD}.$

The mobility is calculated from equations (4-1) and

(4-2), since

$$\mu = \frac{R_{\rm H}}{\rho} \tag{4-3}$$

where  $\mu$  is the mobility in cm.  $^2/\text{volt-sec}$ .

Measurement of  $\rho$  is accurate to  $\pm 5\%$ , if errors in film thickness are neglected, while the accuracy of  $R_H$  is variable depending on the amount of noise superimposed on the Hall voltage  $(\Delta V_C - V_A)$ . The accuracy of  $R_H$  is usually better than  $\pm 15\%$ .

## 4.3.3 Specimen and Specimen Holder

Specimens were evaporated in a four leaf clover configuration, used by Van Daal, 1964, to reduce contact error due to non-infinitesimal contacts. Aluminum electrodes were deposited under vacuum on top of the semiconductor film to form ohmic contacts. Figure 4-2 is a photograph of an evaporated Hall specimen with contacts.

Figure 4-2. Hall Sample of Cadmium Selenide with Aluminum Contacts '

The specimen holder used had four pressure contacts of gold-plated berylium copper to contact the specimen. A fifth electrode consisted of the specimen holder base plate and was used to perform switching experiments on Hall samples of cadmium selenide deposited on barium titanate. This will be discussed further in the next chapter. The specimen holder is pictured in Figure 4-4(a) and (b). All measurements were performed with the light-proof casing in place.

#### 4.3.4 Experimental Results

Hall specimens of cadmium sulphide and cadmium selenide, deposited onto unheated glass substrates, were measured immediately after preparation. The results of these measurements are shown in Table III.

| FILM  | THICKNESS           | RATE OF DÉPOSITION       | $\mu_n$ (cm. 2/volt-sec.) | n<br>(el//cm. <sup>3</sup> ) |

|-------|---------------------|--------------------------|---------------------------|------------------------------|

| CdSe  | 3200 A <sup>0</sup> | 3.3 A <sup>O</sup> /sec. |                           | 5.3x10 <sup>18</sup> ±10%    |

| CdSe* |                     |                          | 55 <u>+</u> 10%           | 2.1x10 <sup>16</sup> ±10%    |

| cas   | 2600 A <sup>O</sup> | 3.3 A <sup>O</sup> /sec. | 40 <u>+</u> 10%           | 2.2x10 <sup>16</sup> ±10%    |

TABLE III

Hall Measurement Results of Cadmium Sulphide and Cadmium Selenide on Glass

These measurements show that the mobility of cadmium selenide is higher than that of cadmium sulphide, even in the

<sup>\*</sup>After standard heat treatment in air at 300°C. for 15 min.

(a) Overall View

(b) Contacts

Figure 4-5. Hall Specimen Holder

polycrystalline form as deposited. Also, the reduction in carrier concentration by heat treatment in air is demonstrated. Cadmium selenide thin films were found to be much easier to deposit and were much more reproducible than those of cadmium sulphide, especially on a barium titanate substrate. Therefore, cadmium selenide was used almost exclusively for the remaining experiments.

# 5. CADMIUM SULPHIDE AND CADMIUM SELENIDE FILMS ON BARIUM TITANATE

#### 5.1 Introduction

Both conductivity and Hall measurements were performed on cadmium selenide films deposited on barium titanate. Film preparation is discussed. The film conductivity modulation obtained experimentally is related to that which was predicted in Chapter 2. Initial conductivity modulation measurements were made with cadmium sulphide as well.

#### 5.2 Specimen Preparation

The barium titanate substrate was etched as described in Section 3.4.1 and cleaned by agitating in trichlorethylene, in alcohol, and in distilled, deionized water consecutively in the Ultrasonic cleaner. A large round gold or aluminum counter or switching electrode was then deposited onto the underside of the substrate. No attempt was made to align the crystal domain structure. The semiconductor film was then deposited, either as a square for resistance measurements, or in a four leaf clover configuration for Hall measurements. At this stage, the sample was usually subjected to a 15 minute heat treatment in air at 300°C to reduce the film conductivity. The mechanism for this effect is assumed to be oxygen absorption as described in Chapter 4. Aluminum electrodes were then deposited onto the film. Electrical measurements were performed as soon as possible after removal from the vacuum system.

For the narrow electrode gap resistance modulation

samples, a  $75\mu$  wire was used to form the source-drain gap, which was 0.6mm. long.

#### 5.3 Electrical Measurements

#### 5.3.1 <u>Hall Measurements</u>

Hall measurements were performed with cadmium selenide films on barium titanate in the same manner as described in Chapter 4. Measurements were taken with the crystal in both the c<sup>+</sup> and c<sup>-</sup> states. As described in Section 3.4.4, switching was performed by applying a slow ramp voltage across the crystal, between the counter electrode, contacted to the copper base of the specimen holder, and the four aluminum contacts of the Hall specimen combined. The top switching electrode is formed by the four aluminum contacts and the semiconductor film.

Conductivity modulation in the cadmium selenide films was observed. Values of mobility and electron concentration in the two states for several samples are given in Table IV.

| SAMPLE | THICKNESS                          | STATE       | MOBILITY (cm.2/volt-sec.)          | ELECTRON CON-<br>CENTRATION<br>(el./cm. <sup>3</sup> ) |

|--------|------------------------------------|-------------|------------------------------------|--------------------------------------------------------|

| #6     | 1850A <sup>°</sup><br><u>+</u> 15% | *           | 66 <u>+</u> 10%                    | 3.0x10 <sup>18</sup> ±10%                              |

| -      | . 6                                | low<br>high | 12 <u>+</u> 15%<br>13 <u>+</u> 15% | 7.0x10 <sup>13</sup> ±20%<br>6.0x10 <sup>13</sup> ±20% |

| #7     | 1700A°<br><u>+</u> 15%             | low         | 33 <u>+</u> 15%<br>36 <u>+</u> 15% | 3.0x10 <sup>13</sup> ±15%<br>1.5x10 <sup>14</sup> ±15% |

TABLE IV

HALL MEASUREMENT RESULTS OF CADMIUM SELENIDE ON BARIUM TITANATE

<sup>\*</sup> Before Heat Treatment

It can be seen that the modulation of the electron concentration is much below that expected from theory. Assuming a one for one compensation of the polarizing charge by the semiconductor film, only 0.03% of the electron concentration change expected occurs for sample #6 and for #7, 6.5x10<sup>-4</sup>%. Possible reasons for this discrepancy are discussed following the next section.

Mobility changes between the two states are negligible. If the charge concentration changes were larger, mobility changes might occur (Haering, 1964). Decreased mobility due to increased scattering at greater electron concentration levels is possible, or the mobility may increase due to reduced scattering by filled traps. However, no changes were observed during these experiments.

## 5.3.2 <u>Two-State Resistor</u>

Conductivity measurements were performed on the two-state resistor with the gap formed by a 75 $\mu$  wire, which gave a gap width of 70 $\mu$ . Measurements were performed using the simple circuit of Figure 5-1. For sample #9, 1000 $\Lambda$ ° thick, heat

Figure 5-1. Semiconductor Film Conductivity Measurement

treated in air, the resistance change between the electrodes for the two polarization states of the ferroelectric was from  $9.5 \text{x} 10^6 \Omega$  to  $1 \text{x} 10^9 \Omega$ . If a mobility of  $20 \text{cm} \cdot 2/\text{volt-sec}$ . is assumed, calculation shows that only 0.01% of the expected charge modulation occurs.

Table V gives changes in resistance for several resistors of varying magnitude. Figure 5-2 shows the two states of sample 5. As predicted, the ratio  $\frac{R_H}{R_L}$  in general increases with increasing resistance. If the charge  $P_r$  were all compensated by free carriers, then the ratio would increase linearly with increasing resistance. It is thus necessary to modify equation 2-17 to include the effect of uncompensated charges as shown in equation 5-1:

$$I_{D} = (n_{o} \pm \gamma \frac{P_{r}}{e}) e\mu_{n} WE_{D}$$

(5-1)

where  $\gamma$  is the amount of free charge modulated by the barium titanate, as a fraction of the total polarizing charge of the crystal.

There are several possible reasons for the discrepancy in magnitude between the actual and predicted conductivity modulation effect. These will be discussed in turn.

There is a possibility that the barium titanate crystal is not switching fully. However, in every case that the switching charge was measured, it was found to be equal to twice the remanent polarization charge, within the accuracy of measurement. Possibly some small areas do not switch, but the discrepancy is much too large to be caused by this effect.

| SAMPLE # | THICKNESS | R <sub>LOW</sub>    | R <sub>HIGH</sub>   | % CHARGE**           | R <sub>H</sub> /R <sub>L</sub> |

|----------|-----------|---------------------|---------------------|----------------------|--------------------------------|

| 5        | 1400*     | 4.2x10 <sup>5</sup> | 6.0x10 <sup>5</sup> | .1                   | 1.33                           |