# A Coupled-Circuit Representation of IGBT Module Geometry for High di/dt Switching Applications

by

Blake Kenton Rablah

B.Eng., The University of Victoria, 2004

## A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

Master of Applied Science

ir

The Faculty of Graduate Studies

(Electrical & Computer Engineering)

The University Of British Columbia January 5th, 2007

© Blake Kenton Rablah, 2007

## Abstract

A coupled-circuit element representation of an IGBT module from Westcode Semiconductors Inc. has been developed, simulated, and experimentally confirmed at TRIUMF in Vancouver, BC. This model can be simulated in PSpice to predict the distribution of current within the IGBT module under high di/dt switching conditions. The goal of the simulations is to determine if the module is an acceptable candidate for implementation in a thyratron replacement switch for high-power pulse-power applications.

The model developed has been shown to agree well with frequency domain measurements, and also with finite element method (FEM) simulations and boundary element method (BEM) simulations of the device.

## Table of Contents

| A  | bstra  | ${f ct}$ ii                                           |

|----|--------|-------------------------------------------------------|

| Ta | able o | of Contents iii                                       |

|    |        | Tables                                                |

| Li | st of  | Figures                                               |

| A  | cknov  | wledgements                                           |

| 1  | Bac    | kground                                               |

|    | 1.1    | Intended Application                                  |

|    | 1.2    | Available Technology                                  |

|    |        | 1.2.1 Thyratrons                                      |

|    |        | 1.2.2 Solid State Thyratron Replacements              |

|    | 1.3    | Switch Selection                                      |

|    |        | 1.3.1 Electrical Criteria 6                           |

|    |        | 1.3.2 Form Factor                                     |

|    |        | 1.3.3 Prior Work                                      |

|    |        | 1.3.4 Westcode Module Specifics                       |

|    | 1.4    | Focus of this Thesis                                  |

| 2  | Sim    | ulation of Current Distribution                       |

|    | 2.1    | Simulation Methods                                    |

|    |        | 2.1.1 Software Tools                                  |

|    |        | 2.1.2 Simulation Geometries                           |

|    | 2.2    | Simulation Workflow                                   |

|    |        | 2.2.1 Workflow 1: Opera 2D Field Solution 20          |

|    |        | 2.2.2 Workflow 2: IES OERSTED Field Solver 23         |

|    |        | 2.2.3 Workflow 3: OERSTED Extraction with PSpice Sim- |

|    |        | ulation                                               |

#### Table of Contents

|                  |       | 2.2.4   | Workflow 4: Fasthenry Extraction with PSpice Simulation | 30 |

|------------------|-------|---------|---------------------------------------------------------|----|

|                  | 0.2   | Cimanla |                                                         | 34 |

|                  | 2.3   |         |                                                         | 34 |

|                  |       | 2.3.1   | Street, Street                                          |    |

|                  |       | 2.3.2   |                                                         | 41 |

|                  |       | 2.3.3   |                                                         | 42 |

|                  |       | 2.3.4   | Pulsed Time Domain Results                              | 45 |

| 3                | Exp   | erime   | ntal Verification                                       | 51 |

|                  | 3.1   | Metho   | od of Analysis                                          | 51 |

|                  |       | 3.1.1   | Frequency Domain                                        | 51 |

|                  |       | 3.1.2   | Resistive Elements (IGBT Replacements)                  | 52 |

|                  |       | 3.1.3   | Current Sensing                                         | 53 |

|                  | 3.2   | Test J  |                                                         | 58 |

|                  |       | 3.2.1   | Requirements                                            | 58 |

|                  |       | 3.2.2   | Design                                                  | 59 |

|                  | 3.3   | AC M    | easurement Results                                      | 63 |

|                  |       | 3.3.1   | Purely Copper Module                                    | 63 |

|                  |       | 3.3.2   | Resistive Module                                        | 65 |

| 4                | Cor   | nclusio | ns and Recommendations for Future Work                  | 68 |

| Bi               | bliog | graphy  |                                                         | 70 |

| $\mathbf{A}_{1}$ | ppen  | dix A:  | IGBT On-state Resistance                                | 74 |

| $\mathbf{A}_{1}$ | ppen  | dix B:  | Frequency Dependance of Parameters                      | 77 |

| Δ.               | nnan  | div C   | Coupled Inductors From Impedance Matrixes               | 81 |

## List of Tables

| 1.1 | Anticipated requirements for a thyratron replacement |  | <br>• | 2  |

|-----|------------------------------------------------------|--|-------|----|

| 2.1 | Modelling and simulation software                    |  | <br>  | 17 |

## List of Figures

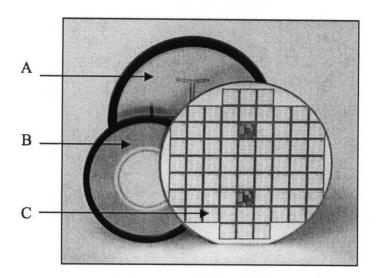

| 1.1  | Silicon wafer comparisons - $A = SCR$ Thyristor, $B = IGCT$ ,               |    |

|------|-----------------------------------------------------------------------------|----|

|      | C = IGBT chip wafer                                                         | 5  |

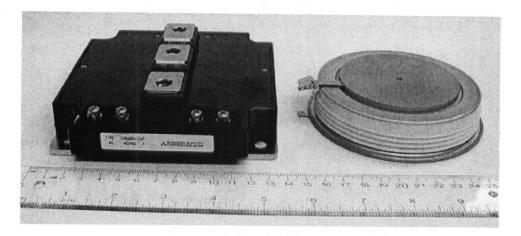

| 1.2  | Comparison of IGBT module packaging options                                 | 7  |

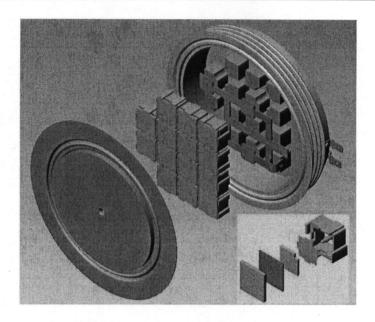

| 1.3  | Rendering of a Westcode press pack IGBT module intended                     |    |

|      | for pulsed power applications                                               | 10 |

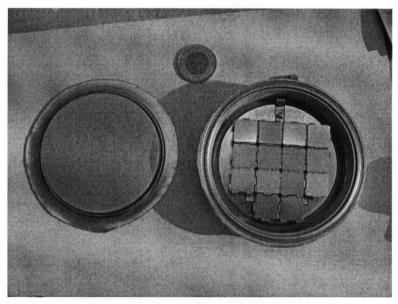

| 1.4  | Photos of a dismantled Westcode module                                      | 11 |

| 1.5  | Rendering of the internals of a Westcode press pack IGBT                    |    |

|      | module with numbered current paths                                          | 12 |

| 1.6  | We<br>stcode provided equivalent circuit of press pack module               | 13 |

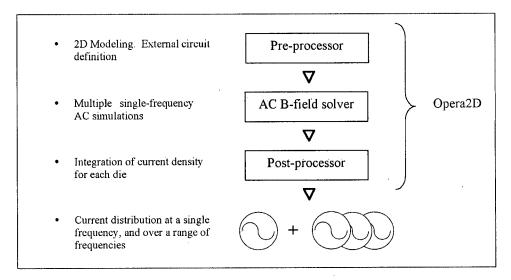

| 2.1  | Opera2D Field Solver workflow                                               | 20 |

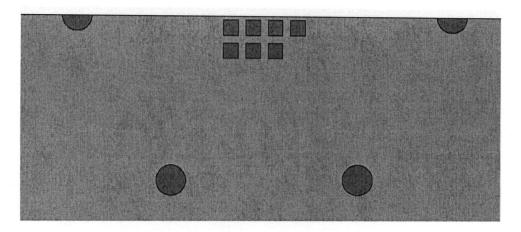

| 2.2  | Modelled geometry - Opera 2D                                                | 21 |

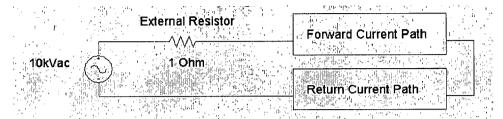

| 2.3  | External circuit for Opera2D AC analysis                                    | 22 |

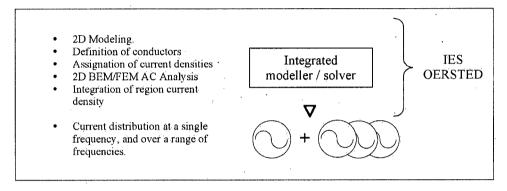

| 2.4  | Workflow 2 - IES OERSTED Field Solver                                       | 23 |

| 2.5  | Modelled geometry - IES OERSTED, IGBT die are shown in                      |    |

|      | red, return paths in blue                                                   | 24 |

| 2.6  | Workflow 3 - OERSTED extraction and PSpice simulation                       | 25 |

| 2.7  | OERSTED geometry for circuit parameter extraction                           | 26 |

| 2.8  | PSpice AC Analysis with OERSTED Circuit Parameters                          | 28 |

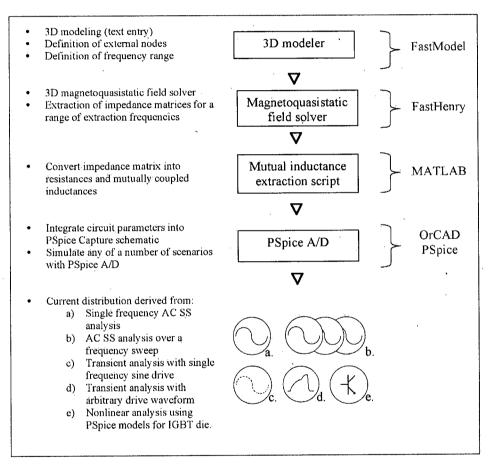

| 2.9  | Workflow 4 - Fasthenry extraction and PSpice simulation                     | 30 |

| 2.10 | Fasthenry 3D geometry for circuit parameter extraction                      | 31 |

| 2.11 | Field solver predictions of steady state current distribution               |    |

|      | for an "all copper" module                                                  | 35 |

| 2.12 | PSpice simulated predictions of steady state current distribu-              |    |

|      | tion for an "all copper" module                                             | 38 |

| 2.13 | Comparison of workflow predicted distributions at low fre-                  |    |

|      | quency and high frequency AC drives                                         | 40 |

| 2.14 | Effect of introducing resistive Si region to model current dis-             |    |

|      | tribution                                                                   | 43 |

| 2.15 | Simulation tool comparison with $2.5 \text{m}\Omega$ Si region resistance . | 44 |

#### List of Figures

| 2.16 | Pulse forming circuit used for time domain pulsed distribution analyses                                                                     | 46 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.17 | Current distribution for simulated module with $12.5 \text{m}\Omega$ onstate resistance and a $10\%$ to $90\%$ rise-time of $300 \text{ns}$ | 47 |

| 2.18 | Effect of varying rise-time and on-state resistance on current distribution for a 8kA pulse                                                 | 48 |

| 2.19 | Predicted current distribution for simulated $12.5 \text{m}\dot{\Omega}$ module with scaled post-heights                                    | 50 |

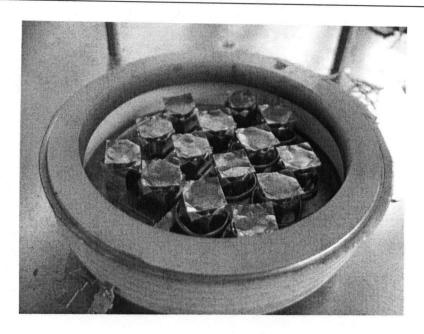

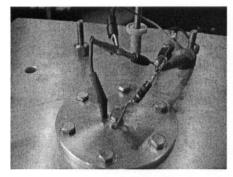

| 3.1  | Resistive elements to replace IGBT die, in place within the Westcode module                                                                 | 53 |

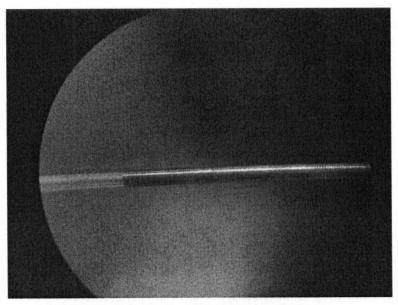

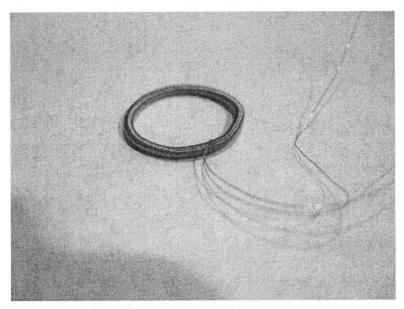

| 3.2  | Rogowski coil construction                                                                                                                  | 5  |

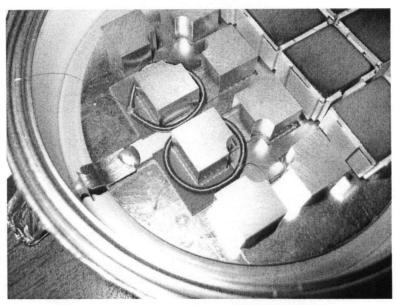

| 3.3  | Rogowski coils in-place within Westcode module                                                                                              | 5  |

| 3.4  | Instrumentation amplifier circuit diagram                                                                                                   | 5  |

| 3.5  | Photograph of the instrumentation amplifier used for AC                                                                                     |    |

|      | measurements                                                                                                                                | 5  |

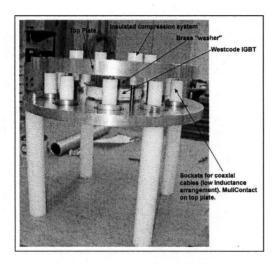

| 3.6  | CERN Prevessin test jig for presspack IGBTs (Note: "Muli-                                                                                   |    |

|      | Contact" (sic) should read "MultiContact")[1]                                                                                               | 6  |

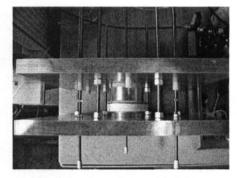

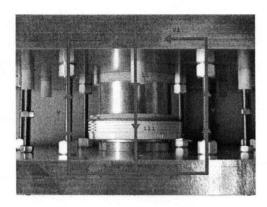

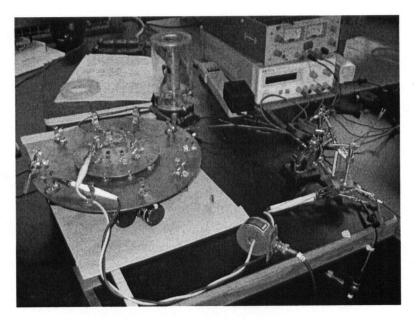

| 3.7  | TRIUMF test jig assembly photos                                                                                                             | 6  |

| 3.8  | Current path through TRIUMF test jig                                                                                                        | 6  |

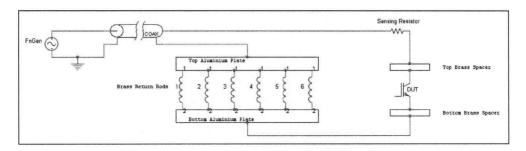

| 3.9  | Test setup electrical layout                                                                                                                | 6  |

| 3.10 | with copper-only module                                                                                                                     | 6  |

| 3.11 | Comparison of simulated and measured current distribution within the IGBT module with $2.5 m\Omega$ of series resistance                    | 6  |

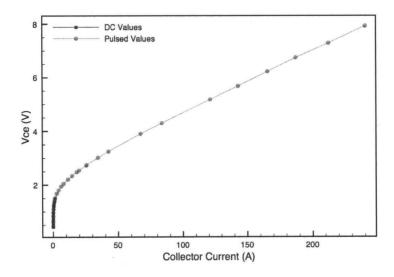

| A.1  | V-I relationship for Westcode IGBT die to determine on-state resistance ( $V_{\rm gate} = 15V$ )                                            | 7  |

| A.2  | Measurement set up for IGBT die on-state resistance measurements                                                                            | 7  |

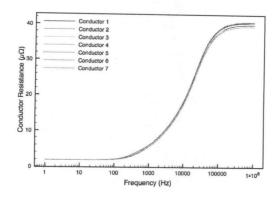

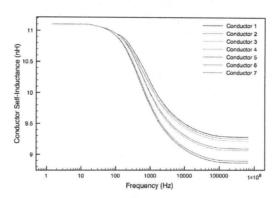

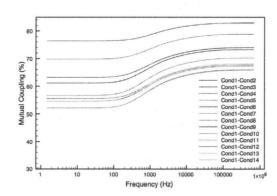

| B.1  | Extracted resistance, inductance and mutual coupling terms for a "copper only" model of the Westcode IGBT module as                         |    |

| B.2  | a function of frequency                                                                                                                     | 7  |

|      |                                                                                                                                             | 0  |

## Acknowledgements

I would like to thank TRIUMF, and in particular Ewart Blackmore, for their continued support, funding and lab-space, dating back to my original co-op placement at the facility. I would also like to thank Mike Barnes and Gary Wait for their mentorship and guidance, without which this work would not have possible.

## Chapter 1

## Background

In the field of high-power pulsed-power, high speed switching is the foundation upon which all else is built. Switches in this field are often required to withstand blocking voltages in the tens of kilovolts and switch several kiloamps in less than a microsecond. One application in which these switches are in frequent deployment is in high energy physics labs around the world. These switches drive kicker magnets that deflect charged beams of particles, or drive klystrons that accelerate these particles.

New developments in semiconductor research are leading to faster solid state switches that are encroaching on other established pulsed-power technologies. However, many of these switches have been designed for larger commercial markets such as traction applications, and have not been designed explicitly with pulsed-power in mind[2]. Pulsed power places an extra burden on the designers of semiconductor switches. Specifically, the high-frequency content of the pulses and the large di/dt and dv/dt that result make the geometry and resulting parasitic components of the devices a particular concern. This puts designers of pulsed semiconductor devices and modules in territory that has historically been the concern of VLSI packaging designers.

#### 1.1 Intended Application

The work described in this document was begun in response to the need for a semiconductor based switch for high pulsed currents with very short risetimes. One potential application of such a switch was for the yet-tobe-funded International Linear Collider to drive klystron modulators. It is envisioned that this semiconductor-switch would be able to turn-on approximately 3kA in approximately 300ns, for a peak di/dt > 10kA/ $\mu$ s, and would be able to be connected in series configurations to permit blocking voltages of at least 75kV[3].

Other thyratron replacement designs cite similar requirements [4], so these figures can be considered general design goals. However, in order to be considered sufficient for application to kicker magnet applications, the requirements become somewhat more demanding. Table 1.1 details the design objectives for which the Westcode module is being considered.

| Criteria                    | Requirement                                 |  |  |

|-----------------------------|---------------------------------------------|--|--|

| Blocking voltage            | Stackable to >65kV                          |  |  |

| Peak current $(I_{pk})$     | >8kA                                        |  |  |

| Risetime (to $I_{pk}$ )     | $<1\mu s \text{ (min. } 10\text{kA}/\mu s)$ |  |  |

| Pulsewidth $(\tau_{pulse})$ | $1\mu s \to DC$                             |  |  |

Table 1.1: Anticipated requirements for a thyratron replacement

#### 1.2 Available Technology

#### 1.2.1 Thyratrons

At the present time, the main devices used for high-power high-speed switching are hydrogen gas filled thyratrons. Similar in design to the more common vacuum tube, a thyratron is a gas-filled device, with an anode and a cathode separated by one or more grids. Switching is achieved when the gas inside the thyratron ionizes and goes from being strongly insulating, to conducting in a very short time. Some thyratrons are capable of blocking over 100kV, and are able to switch tens of kiloamps in just tens of nanoseconds[5]. Typical kicker magnet applications require current rise-times in the neighbourhood of 30ns to peak currents above 3kA. This results in a di/dt in excess of  $100 \text{kA}/\mu\text{s}$ . As an example of one such application: a TRIUMF-designed kicker-magnet for the LHC at CERN featured a thyratron driver that switched a 54kV PFN into a 5 $\Omega$  load: the current rises to a maximum

of 5.4kA with a 10% to 90% rise-time of 30ns, corresponding to a di/dt of  $180\text{kA}/\mu\text{s}[6]$ .

As impressive as these numbers are, thyratrons exhibit some very significant drawbacks when compared to semiconductor devices:

- Spontaneous Turn-on Thyratrons are known to have a finite probability of spontaneous turn-on. Furthermore, this probability goes up considerably as the voltage across a thyratron rises, and also with the length of time this voltage is held. Designers of thyratron circuits sometimes employ fast resonant power supplies to quickly ramp up the voltage on the thyratron shortly before switching, minimizing the thyratron's exposure to high voltage and reducing the chance of spontaneous turn on.[7]

- Switching Control The second disadvantage of thyratrons is the lack of control while switching. Thyratrons latch into the on-state, and will remain latched until they reach zero-current, and the plasma inside the tube is exhausted[5].

- Lifetime Thyratrons also have a limited life span that is dependent both on the number of pulses and the total charge transferred. For any remotely high-frequency high-current application, this can make them expensive to deploy. One such application: as klystron modulators for the International Linear Collider (ILC), would require a team of individuals dedicated to thyratron replacement and adjustment (see below)[8].

- Maintenance In addition to lifetime concerns, thyratrons require frequent adjustment over their lifespan to maintain their switching characteristics. This adds both to the complexity and cost of a thyratron deployment.

#### 1.2.2 Solid State Thyratron Replacements

Even the most advanced solid state devices still have limited voltage and current ratings in comparison to high power thyratrons. Nonetheless, since approximately 1990, considerable effort has been made to produce a solid state replacement for hydrogen gas filled thyratrons. Companies like ABB and Dynex Semiconductor now manufacture thyratron replacement modules constructed from series connected SCR or IGBT devices[4] [9]. However, these devices fall far behind gas thyratrons in terms of switching speed, and as such are not yet suitable "replacements".

#### **SCR Based Solutions**

Both ABB and Dynex, as well as some other manufacturers have developed thyratron replacement stacks from SCR modules. These stacks are capable of di/dt values in excess of  $20\text{kA}/\mu\text{s}$ , and are capable of very high peak currents, with 90kA advertised for one Dynex device (Dynex part #: PT85QWx45).

However, while SCRs fix the lifetime and spontaneous turn-on issues of Thyratrons, they still exhibit some significant drawbacks. SCRs also latch in the on-state and exhibit a similar lack of control during switching as thyratrons. Also, thyristor SCRs require considerable gate currents to switch on. This is especially true when fast switching is desired, where gate currents can exceed 200A[3]. The necessity of a large gate current places strong demands on the gate drive circuit; this can be problematic to implement when each gate drive circuit is floating several kilovolts apart from the next.

#### **IGBT Based Solutions**

IGBTs are bipolar power switching devices that feature a MOSFET-like insulated gate. IGBTs have begun to take over in industry sectors previously dominated by SCRs, especially for medium power applications. The ability to turn-off, even under load, and the simplicity of the gate drive circuit are the two main selling points for IGBT based switches. Additionally, IGBTs can self-limit their current when short circuited[11], which is of interest to a designer looking for some degree of fault tolerance in their design.

Figure 1.1: Silicon wafer comparisons - A = SCR Thyristor, B = IGCT, C = IGBT chip wafer

Controlled switching is also possible with IGBT modules, and active control of series connected modules has been achieved [12].

There are some significant shortcomings associated with current IGBT technologies that limit their applications in the high-power pulsed-power field. While breakdown voltages of individual IGBT die are starting to encroach on territory typically occupied by SCR thyristors, they have relatively lagged in current handling capacity. Part of the reason for this stems from a limitation in the IGBT silicon manufacture that sets the maximum die size at  $\approx 1 \text{cm}^2$ ; many modern SCRs and IGCTs can be constructed on single 91mm diameter wafers (Figure 1.1 Figure 1.1 [10]).

Due to the limitation in die size, high-power IGBT devices are constructed in modules of several IGBT die in parallel. This introduces the problem of ensuring uniform current sharing. Under DC or slow transient conditions, current sharing is dominated by the relative on-state resistances of the various IGBT die within a module. However, under high speed switching conditions, it has been shown that the internal layout of IGBT modules has a marked effect on the current distribution within the module, and cor-

respondingly also the performance and lifetime of the module[2]. Further analysis of IGBT module geometry has identified that parasitic inductances and coupling to the gate circuit within the packaging are largely to blame for current imbalances in some types of module[13][14].

IGBTs are of continued interest for designers of a thyratron replacement switch, but it is apparent that more attention needs to be paid to IGBT module design if such an application is to be realized. ABB manufactures a thyratron replacement that uses stacked IGBT modules, but it's relatively slow switching speed (maximum of  $1.5 \text{kA}/\mu\text{s}$ ) is a testament to the challenge that faces designers of IGBT based solutions[15].

It is possible to boost di/dt performance of a slower switch by adding a saturating magnetic core in series with the switch. This "saturating reactor" will initially appear very inductive and limit the rise of current, until saturation occurs, which results in an effective short circuit. The disadvantage of this approach, to pulsed power applications, is that it adds a considerable amount of parasitic inductance to the circuit and can contribute to impedance mismatches in the system. Additionally, as the characteristics of the non-linear magnetic material are fixed, lower operating voltages will result in slower saturation of the magnetic material, and therefore a significantly reduced di/dt: limiting the useful dynamic operating voltage of the switch.

#### 1.3 Switch Selection

#### 1.3.1 Electrical Criteria

Electrically, the switch must be capable of meeting the requirements already outlined in Section 1.1, specifically the requirements for kicker-magnets outlined in Table 1.1.

#### 1.3.2 Form Factor

IGBT modules come in several different types of packages. Two of the main approaches to package design are shown in Figure 1.2; on the left is a "brick

Figure 1.2: Comparison of IGBT module packaging options

type" package manufactured by Mitsubishi, on the right is a "hockey puck" style of press-type package from Westcode.

Brick Type Modules In the brick-type package the IGBT die are flow-soldered onto a PCB that contains traces for the collector, emitter and gate. Additional interconnections are made with individual wire bonds. This type of arrangement, the most common for power IGBT modules, offers easy connection to external circuits via bolt-on terminals, and is relatively cheap to manufacture. However, for pulsed power applications, this ease of connection comes at a price. [2][13][14] illustrate the difficulties associated with achieving uniform current distribution using this design. Additionally, low inductance series configuration is difficult, as these modules take up a considerable amount of space, and both emitter and collector terminals are on the same side of the device.

One significant advantage of this type of module is that they can be configured such that the return path has a minimal effect on the current distribution within the module. As much of the work detailed in this document deals with this particular subject, it is apparent that this is not of small importance.

Press Pack Modules Devices of this design, are constructed such that the emitter and collector terminals make up the top and bottom of the module. The term 'press pack' comes from the way in which individual die are sandwiched inside the module between the collector and emitter terminals. Electrical contact is achieved by compressing the module under a considerable amount of force (between 20kN and 70kN, depending on the design and application).

Series connection is relatively simple as modules can be stacked one upon the other, and the entire structure compressed to make electrical contact both between and within each individual module. This series configuration also lends itself well to low inductance designs, for the return current path can be constructed to surround the stack: creating a coaxial structure.

One aspect where press pack designs have a distinct advantaged is cooling. Heat is conducted away from both sides of the silicon by the emitter and collector contacts. Cooling solutions can then be applied at these terminals.

Another advantage, perhaps more important to pulsed power application, of the press pack design concerns the mode of failure for the IGBT die. Press pack IGBTs fail to short circuit. This means that, with proper redundancy in a series stack of modules, that a failure in one module (or device within a module) is rarely catastrophic, and the stack usually remains functional [16]. In contrast, brick-type IGBTs often fail violently, severing the wire-bonds within the module and resulting in an open circuit [2]. For even a few individual IGBT die to fail in this fashion would render the entire stack useless.

#### 1.3.3 Prior Work

#### **SLAC Experiments**

TRIUMF's initial investigations into IGBT based thyratron replacements began in conjunction with researchers at the Stanford Linear Accelerator Center (SLAC)[14]. In their attempts to develop a switch to replace thyratrons for klystron modulators they experienced catastrophic failure in some IGBT modules when they were exposed to soft short-circuit conditions[2].

In their attempt to determine the cause of the failures, they performed FEM analyses of the geometry of the device and attributed the failures to an asymmetry of path inductances: contributing to an imbalance of device currents.

#### TRIUMF Current Distribution Analysis

TRIUMF continued the analysis from where SLAC left-off. The TRIUMF contribution was to perform a coupled-circuit element extraction of the IGBT module, and to simulate the conditions which lead to the failure of the device in PSpice. The results of this analysis showed conclusively that, while asymmetric path inductances were a factor, it was inductive coupling to the module's internal gate trace that was largely to blame for the current imbalance and resulting failure of the module. [14] and [17] detail this process.

#### 1.3.4 Westcode Module Specifics

One of the other modules available to the SLAC researchers, and to TRI-UMF was a prototype Westcode module designed specifically for pulsed-power applications. This device features a redesigned gate trace, and other, undisclosed improvements for high di/dt switching. The device is rated at 5.2kV, and 900A DC. However, for the intended application of a thyratron replacement, it is likely to be operated at 60% of the rated blocking voltage, and pulsed at almost 10x the DC current (3.1kV and >8kA, respectively).

Figure 1.3[18] shows a rendering of the internals of this specific module. The image is an exploded view of the device which illustrates the 14 IGBT "cassettes" that house the IGBT silicon die (detailed in the inset, bottom-right), the copper stand-off "posts" that locate the die, and the aforementioned redesigned gate trace.

Figure 1.3: Rendering of a Westcode press pack IGBT module intended for pulsed power applications

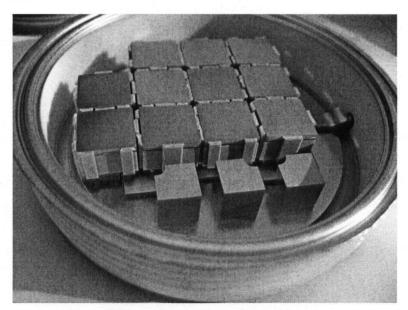

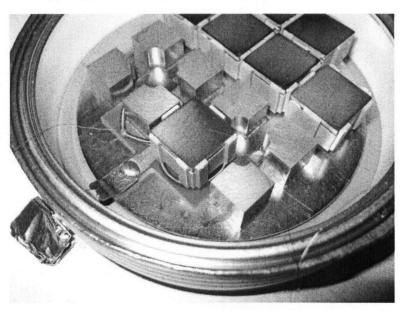

In the course of the research detailed in this thesis, it was necessary to dismantle one of these IGBT modules. Figure 1.4 is a series of photos documenting this process.

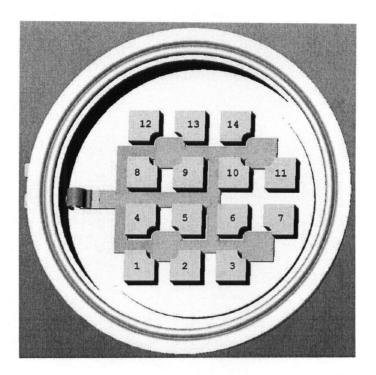

There are 14 IGBT die within the Westcode module. For the rest of this document they will be referred to by number, as labelled on the illustration in Figure 1.5.

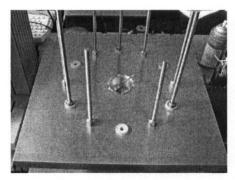

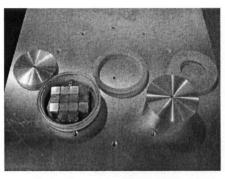

(a) Opened Westcode IGBT module showing 14 parallel IGBT "cassettes".

(b) Detail of Westcode IGBT internals. Visible are the copper posts, IGBT die (in cassettes), and the gate trace.

Figure 1.4: Photos of a dismantled Westcode module

Figure 1.5: Rendering of the internals of a Westcode press pack IGBT module with numbered current paths  $\,$

#### 1.4 Focus of this Thesis

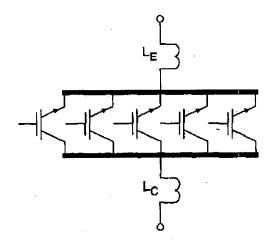

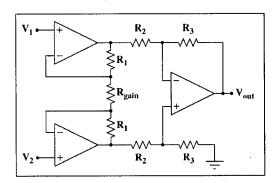

Westcode publishes in their documentation the assertion that, as all of the paths through the IGBT module are of equal-length, that they exhibit equal inductances. Figure 1.6 is an equivalent circuit of the IGBT module, including parasitic inductances, as supplied in their documentation[19]. In this figure these parasitic inductances are lumped into just two parameters, one at the emitter and one at the collector of the device.

Figure 1.6: Westcode provided equivalent circuit of press pack module

When assessing the suitability of this module for a thyratron replacement at TRIUMF, this assumption was called into question. It was suspected that there might be significant issues with uniform current sharing under pulsed conditions, and that these issues might also be strongly influenced by the geometry of the return current path.

The research documented in this thesis covers the creation, simulation and testing of a coupled-circuit model of the Westcode module that explicitly takes into account the inductive coupling that exists, both between the separate current paths through the device and to the return path.

It is hoped that this circuit model will be of great help in the future for the process of prototyping a thyratron replacement switch. One of the biggest advantages of such a circuit is that it allows for new geometries to be quickly and easily tested in PSpice, along with the external circuit and any non-linear switching elements. As PSpice is already used to simulate existing pulsed switches[20], as well as their loads[6], this is the preferred method of implementing the characteristics of the IGBT module

### Chapter 2

## Simulation of Current Distribution

In order to ascertain how the current is distributed within the IGBT module, I undertook to model and simulate the internal structure of the Westcode press pack IGBT module.

Simulation Objective The goal of these efforts was to produce a versatile circuit model of the Westcode IGBT geometry that could be employed in PSpice to predict the current distribution under a wide variety of conditions in a minimal amount of time. Additionally, as the requirements of a thyratron replacement would likely involve pushing any switch to it's physical limits, an accurate model of the IGBT geometry would be of great benefit later in the thyratron-replacement design process to avoid costly failures.

#### 2.1 Simulation Methods

Each electrical path within the hockey-puck IGBT module consists of an IGBT die and a copper post. The ideal software tool to analyse and produce a current distribution for this geometry would be a 3D electromagnetic code, capable of also simulating the non-linearity of the semiconductor die. However, to the author's knowledge, no such code is available. Hence the circuit analysis code PSpice, the de-facto standard for non-linear circuit simulation, is used to simulate the electrical current paths within the IGBT module.

For this, inductance and resistance values are required for each of the electrical paths in the IGBT module: these values are derived from an elec-

tromagnetic code.

Initially a 3D FEM code was used to simulate each IGBT die (as a linear element with the appropriate on-state resistance, see Appendix A) and the copper posts of the module. However, meshing of the model was overly problematic: due both to the excessive number of elements required to perform a high-frequency simulation, and the difficulties associated with meshing mating regions with very different material properties. This approach was abandoned.

Hence, instead, a 2D code is used to model the IGBT. Firstly, the copper post was modelled, with the same current distribution throughout its length, and the inductance per unit length and resistance per unit length, of each post, was determined. The same procedure was used to calculate the inductance per unit length of each on-state IGBT die; and the results are used to assign component values to a PSpice model of the IGBT module to provide a complete model. Such parasitic extractions are performed in the frequency domain.

In order to produce the circuit model, and to be assured of its accuracy, I undertook to model and simulate the Westcode module via several different approaches. As described in the subsequent sections, different software tools were used, and employed several different modelling techniques. These tools were organized into discrete "workflow" which produce a current distribution, given a geometric model of the IGBT module, under certain conditions.

#### 2.1.1 Software Tools

Different software packages were used throughout this process, these are detailed in Table 2.1. Using different software packages with dissimilar solving techniques to solve the same geometry provided us with confidence in the final outcome. This is especially important in our case, where physical measurements to determine the current distribution within the IGBT module, especially under switching conditions, while not impossible, are themselves difficult and prone to error.

| Software Package                              | Usage                                                                                                                                                                           |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vector Fields Opera 2D                        | <ul> <li>2D-FEM Modelling.</li> <li>AC steady state and transient simulation.</li> </ul>                                                                                        |

| Integrated Engineering Software (IES) OERSTED | <ul> <li>2D-BEM/FEM modeling.</li> <li>AC steady state simulation.</li> <li>Circuit parameter extraction.</li> </ul>                                                            |

| Fasthenry                                     | <ul> <li>3D-Magnetoquasistatic Multipole modeling.</li> <li>Circuit parameter extraction.</li> </ul>                                                                            |

| OrCAD PSpice                                  | Flexible time domain and frequency domain simulation of extracted circuit parameters.                                                                                           |

| Matlab                                        | <ul> <li>Scripts to convert impedance matrixes into resistances and coupled inductors.</li> <li>Scripts to extract current densities from simulation tool log files.</li> </ul> |

Table 2.1: Modelling and simulation software.

#### 2.1.2 Simulation Geometries

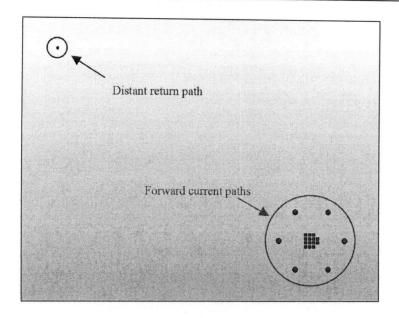

#### Return Path Geometry

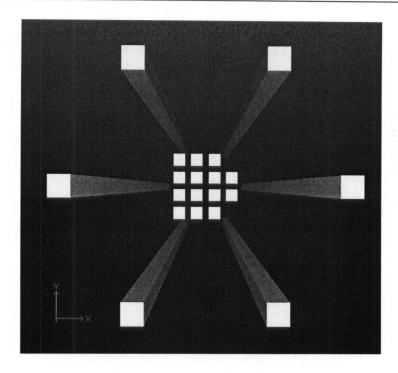

As has been pointed out previously in this document, the geometry and effect of the return path on the current distribution should not be neglected. To attempt to produce the least biased current distribution within the simulated Westcode module, and to lower the inductance of the circuit, a coaxial structure was modelled.

For practical reasons, a fully coaxial return path is unfeasible: there is no way to easily access the device, and the connection of gate drives would become problematic. As such, an array of six rods in a circular shape was simulated, approximating a coaxial structure. The number six was chosen because it has been shown that this number of return rods minimizes the inductance for a geometry[21]. Adding additional paths to further approximate a fully coaxial structure yields little to no benefit to the overall inductance.

The rods are spaced some distance away from the IGBT module (10cm-12cm), as this is indicative of the spacing required for the potential application of a stack of modules, where the voltage difference between the top of the stack and the return path may exceed 75kV.

#### 2D Model

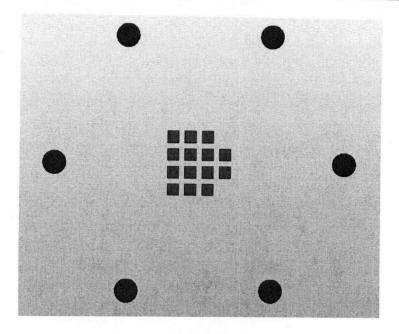

In the following simulations, a 2D model of the Westcode module appears as a cross-sectional slice, viewed from above, of the IGBT module's 14 forward paths, surrounded by the six return paths. Figures 2.2 and 2.5 illustrate how this was implemented. With the first of these taking advantage of the symmetry of the arrangement, and the second modelling a complete 2D 'slice'.

#### 3D Model

The 3D model of the Westcode IGBT module described in Section 2.2.4 is an extruded version of the 2D model described above. The device is modelled

as having 100cm long posts, rather than the actual length of  $\approx 1$ cm. The reason this was done was to minimize the effect of fringing of magnetic field that might be simulated at the ends of the rods. In the actual device these fields would be excluded by the highly-conductive copper emitter and collector contacts.

#### 2.2 Simulation Workflow

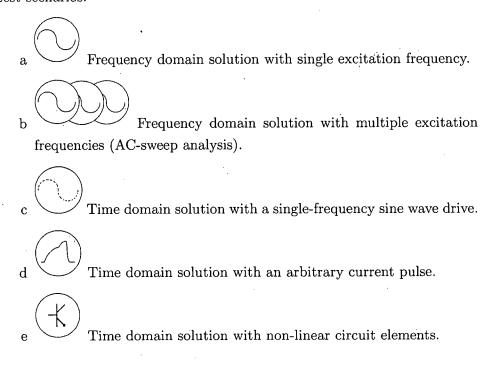

Using various permutations of the tools from the section above, I developed several different workflows to determine the current distribution within the Westcode module. Each of these workflows was capable of producing a solution to one or more scenarios from of a set of test cases. Exploiting the features and capabilities of the different software packages, we were able to cross-check the solutions between workflow techniques, and software packages.

The current distribution within the IGBT was examined for the following test scenarios:

#### 2.2.1 Workflow 1: Opera 2D Field Solution

This technique involves using the Opera2D software package for both modeling, and for solving for the individual die currents at discrete AC drive frequencies.

Figure 2.1: Opera2D Field Solver workflow

The geometry simulated is a cross sectional slice of one half of the symmetrical IGBT module (top, centre); complete with half of the corresponding return path (surrounding), as shown in Figure 2.2. Normal **B** field boundary conditions were applied to the top edge of the model, and the solver set to regard this as the axis of symmetry. The solver considers the device to be infinitely 'long', however a length in the Z-direction is specified for the device, so that the results may be scaled accordingly. Being a 2D model, the material simulated is assumed to be homogeneous over the entire length.

Simulating just half of the IGBT module allowed for a denser mesh to be used while still retaining the same total number of elements. This is important when doing a high-frequency analysis on a highly conductive material, as the skin effect crowds current to a very thin depth along the edge of each conductor, and correspondingly small elements must be used.

Equation 2.1 illustrates how the skin depth  $(\delta)$  depends inversely on both the frequency of simulation (f) and the conductivity  $(\sigma)$ . For the materials under consideration (silicon, copper), the relative permeability  $(\mu_r)$  is near unity, so the total permeability  $(\mu = \mu_r \mu_0)$  will be fixed.

$$\delta = 1/\sqrt{2\pi f\mu\sigma} \tag{2.1}$$

As an extreme example: for a copper bar  $(\sigma = 5.96 * 10^7 Sm^-1)$  with a 10MHz drive frequency,  $\delta$  is a mere  $15\mu m$ . With an accepted minimum of three elements per skin-depth[22], this amounts to an extremely high element count, even when when a graded mesh is employed (as it is in this model).

Figure 2.2: Modelled geometry - Opera 2D

This workflow performs the FEM analysis of the module at a specific frequency while assuming that the geometry being modelled is part of a larger external circuit (detailed in Figure 2.3). The resistance in the external circuit is arbitrarily chosen to be large compared to the impedance of the module. The voltage source can then be scaled to give the appropriate current. In this case, a peak current of 10kA for a complete module was modelled: although, as the model is linear, and we are only concerned with the relative distribution of current, the actual value of the peak current, as

modelled in the electromagnetic simulation, is not important

Figure 2.3: External circuit for Opera2D AC analysis

I ran the simulation with a series of frequencies starting at 1Hz, and extending to 10MHz. Using Opera2D's built-in scripting ability, the current density for each of the die was integrated and extracted at each simulated drive frequency. Matlab was then used to parse the resulting Opera2D log-file, retrieve the die currents, and then normalize these to the total simulated module current.

Simulation Time To perform a single-frequency analysis on this model takes just over five minutes to simulate on a Pentium IV 3.0GHz machine with 2GB of RAM. An additional few minutes is required to perform the post-processing and obtain the current distributions from the model.

Summary With proper implementation, this workflow should be able to produce some of the most accurate simulations of the current density under steady state conditions. However, the length of time required to do a complete FEM simulation at each simulation frequency, combined with the inability to simulate a device that is heterogeneous along its length limits the utility of this workflow to verifying the results produced by other workflow.

#### 2.2.2 Workflow 2: IES OERSTED Field Solver

IES OERSTED features an integrated AC steady state field solver which utilizes the boundary element method, finite element method, or a hybrid combination of the two. IES has integrated their software such that modeling, simulation, and analysis are all performed in the same interface.

Figure 2.4: Workflow 2 - IES OERSTED Field Solver

To simulate the IGBT in OERSTED, a two-dimensional model representing a complete cross-section of the IGBT module was created that did not take account of symmetry (Figure 2.5). Otherwise, the geometry represented by this model was identical to the Opera2D rendering. This was possible as OERSTED's use of 1D boundary elements at the periphery of each conductor negated the necessity for a large number of FEM elements resulting from skin effect (see Section 2.2.1 for an example). As with the Opera2D simulation, the module simulated must be assumed to be made of homogeneous material along its length.

Once the geometry was established, it was a relatively simple matter to assign the total current density in the forward and return conductors, define the drive frequency and set the self-adaptive solver running. Once the solver had finished, the current density was produced for the entire module and integrated over individual regions.

To obtain the current distribution over a range of frequencies, it is necessary to set up a parametric analysis within IES OERSTED. OERSTED

Figure 2.5: Modelled geometry - IES OERSTED, IGBT die are shown in red, return paths in blue  $\,$

has an advantage over Opera2D in that a number of post-processing options can be specified to be run for each parametric case without any additional scripting required. For our model, the post-processing options calculated the total current present in each path at each specified drive frequency.

**Summary** The OERSTED field solver is very similar to the Opera2D field solver, and has the same set of advantages and disadvantages. The ease of use of the IES unified environment is a benefit, but, as with Opera, this method is useful mainly as a comparison tool for the other workflow.

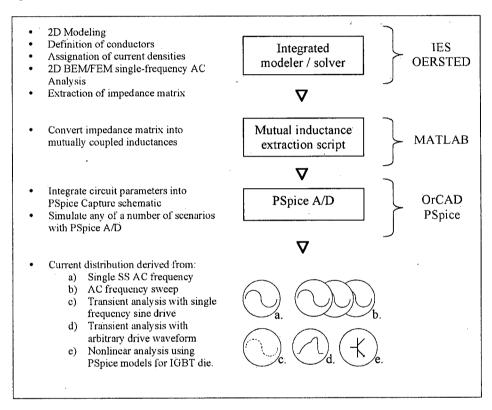

## 2.2.3 Workflow 3: OERSTED Extraction with PSpice Simulation

This method employs IES OERSTED as an extraction tool that produces an impedance matrix at a single extraction frequency. This matrix is converted into mutually coupled circuit parameters which can then be analysed in any PSpice circuit.

Figure 2.6: Workflow 3 - OERSTED extraction and PSpice simulation

The circuit parameter extraction solver uses nearly the same geometric model in OERSTED as the field solver. The only major difference to this model is a result of the method that OERSTED uses to produce circuit parameters: For x forward paths, and y return paths, OERSTED produces an x\*x impedance matrix. This matrix represents the complex impedances

Figure 2.7: OERSTED geometry for circuit parameter extraction

of the forward conductors in the presence of the return conductors. As a result, the return paths are not explicitly represented and expressed as circuit parameters (this is in contrast to Fasthenry; see Section 2.2.4 - below). To render the PSpice model more flexible, it was decided to model all of the conductors in the existing geometric model as forward current paths, and include a separate return path which is relatively distant from the model (Figure 2.7). This permits the actual return path to be modelled from within the circuit simulator, and allows some alterations to be made without requiring re-extraction of parameters.

The impedence matrix, as well as circuit parameters, are produced using BEM/FEM/Hybrid analysis (as with the OERSTED field solver, above) at a single extraction frequency which is determined at the time of simulation.

Extracting circuit parameters at a single frequency, and then using them as linear elements over a wide range of frequencies in PSpice can be problematic, as these values are, in fact, frequency dependent (this effect is covered in Appendix B). Inductance ladders can be constructed to simulate this

effect and have been employed successfully by others[23]. However, construction of these inductance ladders adds considerably to the complexity of the PSpice model and may not be considered necessary. As shown in the aforementioned appendix, it is possible to achieve greater accuracy from a single set of extracted circuit elements by combining resistive and inductive components generated from the same model at different extraction frequencies. The resistive portion is taken from a low frequency extraction, and the inductive portion from a high frequency extraction.

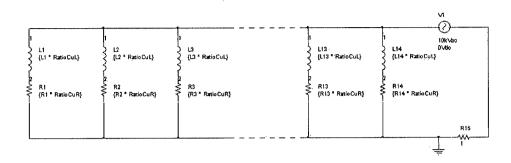

The process of rendering the extracted impedance matrix into coupled circuit parameters is detailed in Appendix C. This conversion process generates a PSpice .include file that contains .PARAM statements for each of the self inductance and resistance values. Also included in this file are the coupling coefficients between each inductor. Attaching this file to a PSpice schematic with appropriately labelled resistors and inductors produces a circuit that electrically mimics the geometric effects of the different current paths.

For a composite structure such as the Westcode module, where different materials (silicon, copper, molybdenum) are layered to make up the complete module, modelling can be accomplished by performing a separate 2D extraction for each distinct layer in the device. The resulting .include files can be included in the PSpice simulation, with the circuit elements for each path are arranged in series within the schematic, thus emulating the previously attempted 3D simulation.

The circuit parameters extracted are per unit length. To adapt these values to represent the real module, the resistances and inductances are linearly scaled accordingly (terms RatioCuR & RatioCuL in Figure 2.8). The coupling terms are expressed as a ratio of the self- and mutual-inductances, and therefore remain independent of the length of the extruded model and need no adjustment.

**Simulation Time** Each single frequency parasitic extraction in OER-STED 2D takes just over 11 hours on the same machine as used for Section 2.2.1.

Figure 2.8: PSpice AC Analysis with OERSTED Circuit Parameters

**Summary** The real advantages of this particular workflow are in the flexibility that PSpice simulation offers:

- It is possible to represent a device that is made of composite materials along its length (as is the case with the Westcode module) by modelling 2D slices of the various materials separately. The resulting circuit parameters are then arranged in series within PSpice and scaled to the appropriate length to simulate the entire device.

- Both AC and transient analyses can be performed much faster than with FEM/BEM analysis alone.

- Non-linear circuit elements can be introduced to represent the IGBT die portions of the module, and switching behaviour can then be explicitly assessed.

- In non-linear analyses the effect of inductive coupling to the gate traces from main current paths can also be simulated. This has been shown to have the potential to significantly alter the current distribution during switching [14].

However, there are drawbacks inherent with this workflow:

• The technique described above to model a composite device by layering the results from independent simulations, works only for specific

geometries. In the case of the Westcode module, it is effective because virtually all the current flow is orthogonal to the 2D plane(s) modelled. This means that there will be very little (magnetic) coupling between layers, and that each set of extracted inductances can be considered coupled only within themselves. For other geometries, this may not be the case.

• Extracting circuit parameters at a single frequency, and then using them as linear elements over a wide range of frequencies may lead to inaccuracy in the simulation. This can be mitigated with additional processing of the extracted circuit elements.

# 2.2.4 Workflow 4: Fasthenry Extraction with PSpice Simulation

This workflow uses the "free of charge" 3D parasitic inductance extraction tool Fasthenry to produce impedance matrixes. These matrixes are then converted into PSpice resistors and coupled inductors which can then be inserted into a PSpice schematic and simulated [24].

Figure 2.9: Workflow 4 - Fasthenry extraction and PSpice simulation

Fasthenry is a magnetoquasistatic multipole parastitic inductance extraction program developed in the mid-90's at MIT[24]. Models are created

Figure 2.10: Fasthenry 3D geometry for circuit parameter extraction

from a text input file by defining nodes and then connecting these nodes with rectangular conductors. The software also has the capability to create conducting planes by meshing together conductors.

Augmenting the text entry system is another, currently free of charge, software product called FastModel <sup>1</sup>. FastModel provides a real-time display of the geometry as it is entered, and can also be used to configure and launch FastHenry. The text entry system, while ill-suited to geometries not constructed entirely of straight-segments, is surprisingly efficient in creating simple models.

External nodes are defined representing ports for the network solver. The solver commences to analyze the effect of an AC drive applied to one port, on all the other ports. What contributes to make FastHenry unique among our solvers is its use of "partial inductances". Partial inductances

<sup>&</sup>lt;sup>1</sup>Available from http://www.fastfieldsolvers.com/

are a mathematical abstraction that permits inductances to be calculated without an explicitly defined return path[25]. Instead, the 'return path' is considered to be infinitely far from the conductor, and the conductor's self-and mutual-inductances are calculated accordingly. Defining conductors in this fashion requires that the mutual terms be considered whenever PSpice simulations are run, as it is through mutual coupling that the effect of the actual return paths are considered.

The result of a simulation in FastHenry is an n \* n complex impedance matrix, where n represents the number of external ports present in the model. Following from the example given in OERSTED circuit parameters section (section 2.2.3, above): for a FastHenry model with x forward paths, and y return paths, n = x + y. Each impedance matrix is valid for a single extraction frequency (see Appendix B).

To convert the impedance matrix to a PSpice include file, a MATLAB script was written. This script is virtually identical to the script used to convert the OERSTED derived impedances and also produces a similar PSpice.include file.

Simulation of the Fasthenry extracted circuit elements in PSpice also follows the same procedure, and they can be used in the same circuits as those generated by OERSTED. While Fasthenry is a 3D simulation program, and therefore able to simulate heterogeneous structures, it is also possible to combine the extracted circuit elements from independent simulations in the same way as with the OERSTED workflow. For the Westcode geometry, we chose to implement the model using the latter of these techniques. This permitted us to examine the silicon and copper regions of the module separately within PSpice and yet avoid forcing Fasthenry to solve the much larger matrix that would result from attempting to include these (largely uncoupled) regions together in one composite model.

Simulation Time The time taken to produce an impedance matrix in Fasthenry varies with the number of ports, conductors and filaments in the model. For our model (20 ports, 20 filamented conductors) of the Westcode module this came to  $\approx 15 \text{m}$  per extraction. For each additional material

layer, or desired frequency, a separate extraction must be performed.

PSpice is able to produce either transient or AC solutions to simple circuits that make use of these extracted circuit elements in <1 minute on average.

**Summary** As this workflow employs PSpice as a simulation tool and uses identically formatted circuit parameters to the previous workflow it follows that it shares all the corresponding advantages. Additionally, being a 3D solver, Fasthenry is capable of modelling geometries that are difficult or impossible for 2D solvers to render[14].

Circuit elements derived by Fasthenry are, like those from OERSTED, produced for a single frequency and have similar limitations and mitigation techniques.

#### 2.3 Simulation Results

This section compares the results of simulations run using the techniques and models described above. As the simulation techniques are themselves experimental, much of the focus of this section is on comparing the results of these techniques. We are especially interested in determining the dependability of the two workflows which use PSpice as a simulation engine (Workflows 3 and 4), for it is these techniques that are the most flexible.

#### 2.3.1 AC Steady State Results

The following simulation results compare the AC magnitude of the current distribution, as derived by the above techniques, over a swept frequency range from 1Hz to 10MHz.

The first section below considers a hypothetical scenario of a "pure copper IGBT module; this simulation allows us to directly compare the results from all of the workflows. The second section details results from a more complex model, which includes a small slice of a material with the resistivity of silicon to represent the sandwiched IGBT die.

#### "Copper Only" Frequency Sweep

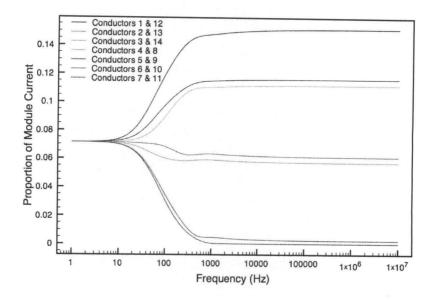

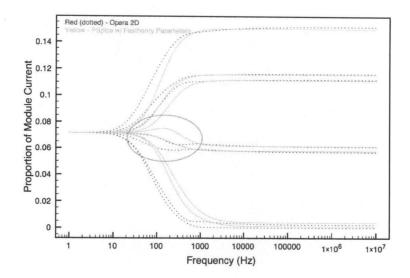

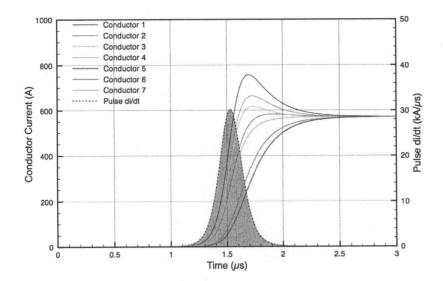

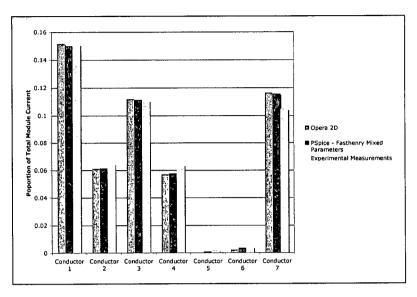

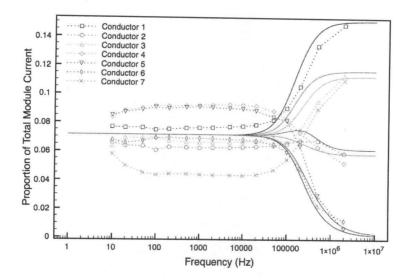

**Field Solvers** Initially the module was modelled using the FEM and BEM field solvers as a hypothetically pure copper device. It was anticipated that these tools would provide the most accurate distribution of the current for this limited model as they perform a complete simulation for each frequency step specified. Figure 2.11 presents the results from the field solvers.

(a) Opera 2D (Workflow 1) prediction for an "all-copper" Westcode IGBT module.

(b) Comparison: Opera 2D (Workflow 1) and OERSTED Field Solver (Workflow 2).

Figure 2.11: Field solver predictions of steady state current distribution for an "all copper" module

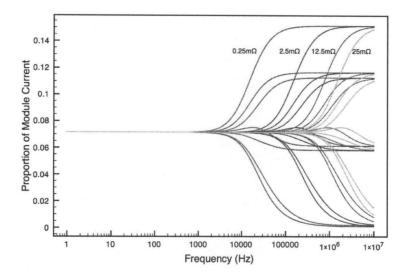

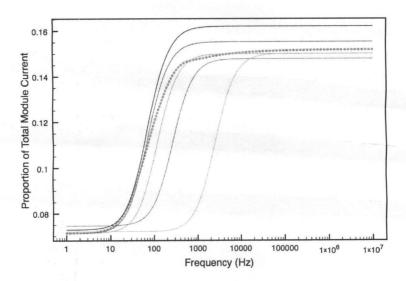

Figure 2.11(a) is a plot of the proportion of the module current predicted to flow through each path by Opera 2d as a function of drive frequency (Note: due to symmetry within the module, each plotted line represents two current paths, refer to Figure 1.5 for numbering). At low frequencies (<10Hz, in this case), the distribution is near-uniform and each conductor assumes  $1/14^{th}$  of the total module current ( $\approx7.14\%$ ). As the frequency increases, the inductive portion of the impedance begins to dominate, and the distribution becomes increasingly less uniform; conductors near the edge of the device take more current as the drive frequency increases while innermost conductors take less. Above a certain frequency ( $\approx1$  kHz in this example) the current distribution becomes almost entirely determined by the relative values of the coupled inductances of the module. At the higher frequencies the innermost conductors (Conductors 5 & 9, and 6 & 10) conduct little to no current, while the conductors at the corners of the device (Conductors 1 & 12) conduct almost twice as much as they do at low frequencies.

The second portion of this figure, 2.11(b), illustrates the very good agreement between the two types of field-solver. Additionally, as the OERSTED model explicitly defines all 14 forward paths through the module without taking advantage of symmetry, and yet still presents only seven discernible lines on the plot, it can be assumed that the assumption of symmetry in the Opera 2D model was correct. As such, for the remainder of this document, reference will only be made to the lower half of the IGBT module (Conductors  $1 \rightarrow 7$ ), with the symmetric top portion assumed to exhibit the same characteristics.

The only readily apparent difference between the distribution as predicted by Opera 2D and the OERSTED field solver, is at very low frequencies (≈2Hz). Here, some anomalies are present in the OERSTED simulation. This is most likely attributable to the solver's use of 1D boundary elements at the surface of the conductors to solve for what is likely to be, at these low frequencies, a bulk distribution of current. For such distributions, FEM modelling is much more appropriate. However, as the discrepancy is small, localized and explainable, it is not considered to be problematic.

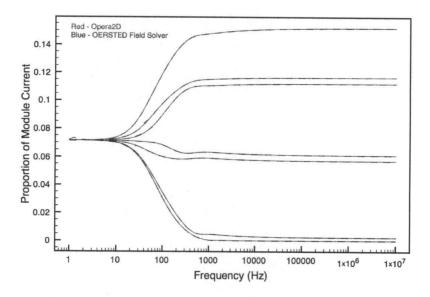

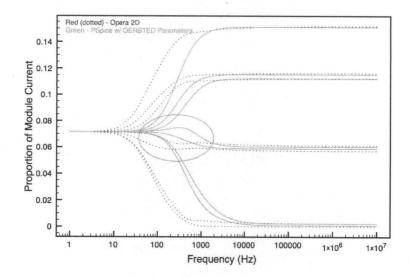

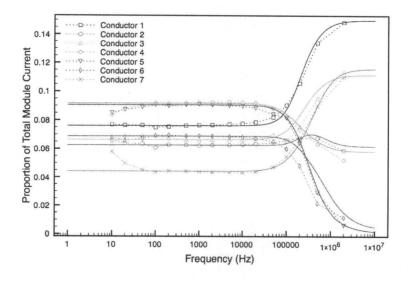

Circuit Solvers The plots in Figure 2.12 compare the distribution obtained through PSpice simulation of extracted circuit parameters to the field solver solution. Figure 2.12(a) presents the distribution obtained from simulating Fasthenry extracted circuit elements, and Figure 2.12(b) the results using OERSTED derived parameters<sup>2</sup>.

The following observations can be drawn from Figures 2.11 & 2.12:

- The four plots all share the same general shape when transitioning from one extreme to the other.

- Additionally, this transition takes place over a similar frequency range for all four techniques: approximately two decades.

- All four workflow produce similar distributions at simulation drive frequencies below approximately 10 Hz; the predicted distributions also plateau to similar values above approximately 10 kHz.

- If the distribution predicted by the field solvers can be assumed to be the most correct, then the two PSpice solved techniques underestimate the magnitude of the imbalance in this hypothetical "copper only" module for approximately one and a half decades spanning upwards in frequency from approximately 10 Hz.

- In both PSpice simulations, Conductors 2 and 4 are predicted to take a considerably higher proportion of the module current between 100Hz and 1kHz (see circled regions). This is notable, as it is the only location where the shape itself of the distribution, as it transitions from resistively dominated to inductively dominated, differs significantly between workflow.

<sup>&</sup>lt;sup>2</sup>It is of note that the extracted circuit elements simulated to produce the following plots (and, unless otherwise specified, all subsequent PSpice-derived results) are amalgamations of two separate extractions. One of these extractions was performed at a low frequency (1Hz), and the other at a high-frequency(1MHz). The circuit elements used combine the resistive values from the low frequency extraction with the inductances and coupling terms of the high frequency extraction, as it was found that this particular combination gave the best 'fit' over the simulated frequency range without resorting to ladder networks. Applendix B details the rationale and methodology behind this decision.

(a) Comparison: Opera 2D field solver (Workflow 1) with PSpice model using Fasthenry extracted parameters (Workflow 4).

(b) Comparison: Opera 2D field solver (Workflow 1) with PSpice model using OERSTED extracted parameters (Workflow 4).

Figure 2.12: PSpice simulated predictions of steady state current distribution for an "all copper" module

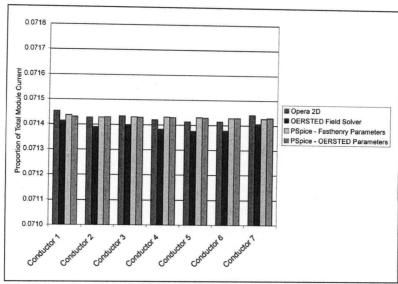

At the extreme ends of the spectrum, the different workflow appear to agree well. In Figure 2.13 a comparison between the simulation techniques is made at 1Hz, and then again at 1MHz. As these particular distributions represent the lower and upper asymptotes, respectively, they are applicable over the majority of the spectra, excepting the two decades of transition mentioned above.

The low frequency distribution in Figure 2.13(a) is identical to well within 1/100<sup>th</sup> of 1% of the total module current. It is interesting to note that, at low frequencies, the PSpice predicted currents are more uniform between die than the field solver values. This is possibly a result of accumulated error from integration in the field solvers, but is too small to be of any concern.

At 1MHz, Figure 2.13(b), the predicted current distribution is also similar across the various workflow. The largest spread is for the predicted current through Conductor 4, and is less than 0.2% of the total module current.

Choice of Workflow If the field solver solutions produced by Workflow 1 and Workflow 2 are to be considered accurate representations of the current distribution within this hypothetical pure-copper IGBT module, then they can be used to determine which of the PSpice simulation workflow is best suited for continued investigation of the Westcode module.

There is relative insignificance in the variation of predicted current distribution in the low and high frequency plateau regions of the AC sweep analysis. Therefore it follows that the choice of extracted parameters should be those that most closely follow the transition from resistively dominated to inductively dominated. It was thus decided to use the Fasthenry parameters, adjusted as described in Appendix B, to perform further analysis of the Westcode IGBT module.

Fasthenry is also attractive as an extraction tool as it is much faster than OERSTED in performing extractions, making it easier to prototype new designs. Additional attractions of FastHenry are its ability to handle 3D geometries, and its low price (free).

(a) Predicted low frequency (1Hz) distribution.

(b) Predicted high frequency (1MHz) distribution.

Figure 2.13: Comparison of workflow predicted distributions at low frequency and high frequency AC drives

#### 2.3.2 Resistive Module Results

With a simulation methodology chosen, it was decided to perform simulations more representative of the actual IGBT module characteristics, while retaining a simple, linear model.

This involved performing a second set of parasitic extractions of the same geometry used for the above copper module, this time with the resistivity of the simulated material adjusted to match that of an IGBT die in the linear on-state. Initially, as neither detailed specifications, nor a dismantled device was yet available, an estimation was made of this value from manufacturer datasheet information then combined with a estimate as to the IGBT die dimensions. Later, the on-state resistance was determined experimentally, the dimensions of the die measured and the models revised. This process is detailed in Appendix A.

As described in Sections 2.2.3 and 2.2.4, the coupled parameters obtained from this second set of extractions are combined with the previously extracted copper elements. The composite structure is then simulated in both the frequency domain, with an AC sweep, and in the time domain, with current pulses of varying rise-times.

Since the measured and calculated values obtained for the IGBT linear on-state resistance exhibit some differences, and are only applicable to IGBT die already conducting a significant amount of current (>≈40A/die), a range of die resistances was analysed. These were derived by scaling the resistive portions of the originally extracted parameters in PSpice to produce an appropriate value for the die resistance. This provides a convenient method to quickly asses the effect on the current distribution of changes in on-state resistance (for example, resulting from an altered gate voltage), or to examine the distribution earlier in the switching process when the IGBT die has not fully turned-on. This approach is also considered valid because the length of the copper post is significantly longer than the length of the IGBT die: hence the effect of the self-inductance of the post is much greater than that of the die. Therefore, the slight change in inductance of the die (at a given frequency), resulting from the altered resistivity, is a comparatively

small effect.

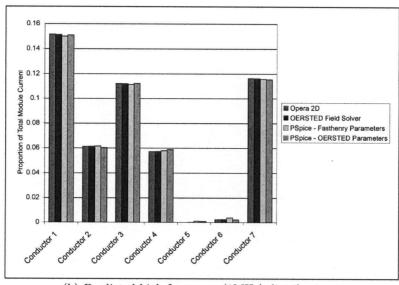

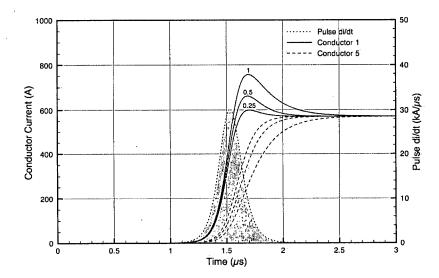

#### 2.3.3 AC Steady State Results

In Figure 2.14(a), the effect of changing the value of the simulated "die" resistance on the steady state current distribution is examined. The resistance values simulated were chosen to represent the possible range of IGBT on-state resistances (the  $12.5 \mathrm{m}\Omega$ , and  $25 \mathrm{m}\Omega$  traces), and to characterize the transition from the copper-only distribution ( the  $0.25 \mathrm{m}\Omega$ , and  $2.5 \mathrm{m}\Omega$  traces).

From this plot, it is apparent that each 10-fold increase in die resistance results in the shifting of the transition point, from a resistively determined distribution to an inductively determined one, by one decade. This is confirmed by examining the phase angle of the module. The frequency at which the phase angle becomes 45°, indicating the inductive portion of the impedance is equal to the resistive portion, also shifts linearly as the die resistance is increased. This is borne out by theory:

$$\theta = \tan^{-1}(2\pi f L/R) \tag{2.2}$$

Therefore a increase in R produces the same effect on the phase  $\theta$  as a proportional increase in f. This frequency also corresponds to the point at which the first sign of divergence in the module current is visible in Figure 2.14(a).

An immediate corollary from this is: increasing the on-state resistance of each path through the IGBT module improves the distribution of current throughout the module. An additional conclusion that can be reached from looking at these plots is that the value of the simulated die resistance has no effect on the final high-frequency current distribution; this distribution appears to be inductively determined by the geometry.

(a) Effect on current distribution of varying resistance of Si region. Resistances shown on plot are per-path.

(b) Phase angle of module impedence as a function of Si region impedance. Red dots indicate  $45^{\circ}$  phase angle

Figure 2.14: Effect of introducing resistive Si region to model current distribution

Figure 2.15: Simulation tool comparison with  $2.5 \text{m}\Omega$  Si region resistance

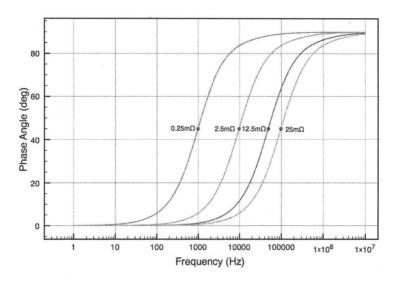

Figure 2.3.3 revisits the choice of workflow. On this plot the current distribution is analysed for the following:

- Workflow 3 & Workflow 4, the two PSpice workflows, using OERSTED and Fasthenry as extraction tools respectively, are compared. Both are using so-called "mixed" parameters with inductive and resistive values combined from 1Hz and 1MHz extractions, respectively.

- A PSpice simulation of a single set of Fasthenry-extracted parameters that represents the combination of the copper and silicon regions. This simulation models the silicon region as a separate slice within the Fasthenry 3D model of the IGBT module.

- An Opera 2D predicted current distribution with a uniform conductivity calculated to reflect a total resistance of  $2.5 \text{m}\Omega$  (the average resistance of the post and IGBT die) for each current path. The value of the conductivity used to create this was  $434 \text{Sm}^{-1}$ .

- A PSpice simulation using circuit elements extracted from a Fasthenry

model with this same value of conductivity. In this model, the IGBT die and post combination is modelled as being one homogeneous volume.

Workflows 3 & 4 and the Unified Fasthenry model, all produce nearly identical current distributions. This hints that the shift in the frequency of divergence, observed between workflows illustrated in Figure 2.12, is likely a result of differences in the extracted resistance values for each copper conductor. Given that any resistance value chosen to represent the IGBT die, will swamp the extracted value for the copper post, this source of error can be considered to be insignificant for this particular application of these circuit elements.

The Opera 2D and PSpice simulations that use homogeneous uniform resistivities, both predict divergence at a lower frequency than the other simulations. These can be viewed as less-correct. The rationale for this is as follows: The current in regions simulated as highly conductive copper is able to redistribute itself within each conductor; it will fringe to the outermost edge. When a uniform resistivity is assumed, the skin depth for this same region is much larger, and the current will fringe much less. This redistribution of current has the effect of reducing the coupling between the IGBT posts and to the return path (by approximately 5%, as predicted by Fasthenry), shifting the divergence point downward in frequency.

#### 2.3.4 Pulsed Time Domain Results

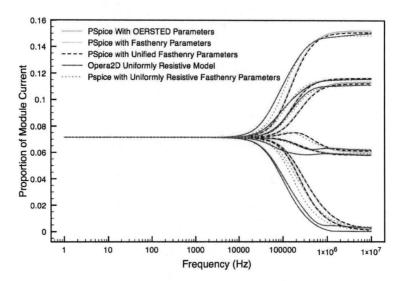

This section investigates the simulated current distribution within the IGBT as it is driven by a current pulse of varying rise-times. The pulse is generated in PSpice by discharging a  $5\Omega$  coaxial cable through the PSpice model of an IGBT module, and into a matched load. Figure 2.16 shows a circuit diagram of this idealized pulse forming network as implemented in PSpice.

The length of the pulse is determined by the delay time of the transmission line. In this case, the line is comprised of two  $2.5\mu$ s segments connected together to form one  $5\mu$ s long cable which will deliver a pulse  $10\mu$ s wide. The rise and fall times of the pulse are determined by the transit time (TTRAN)

Figure 2.16: Pulse forming circuit used for time domain pulsed distribution analyses

of the switch U1. This parameter was adjusted for each simulation case to produce the requisite  $10\% \rightarrow 90\%$  rise-time. The amplitude of a current pulse from a PFN into a matched load is 1/2 of the PFN voltage divided by the characteristic impedance. Here, an 8kA pulse was desired, and was obtained after a small (10%) increase in the PFN voltage from the anticipated 80kV to accommodate for a voltage drop established across the  $100\text{k}\Omega$  resistor by the initial DC bias-point calculation.

Figure 2.17 shows the simulated current in each conductor during turnon when a module with  $12.5 \text{m}\Omega$  on-state resistance is pulsed by an 8kA pulse with a  $10\% \rightarrow 90\%$  rise-time of 300ns. Again, as in the simulations described in the previous section, a linear resistive element was used in place of the IGBT die.

As predicted by the frequency domain measurements, Conductor 1 takes a significant amount more current than the other die during the switching period. In fact, the current in this conductor is predicted to overshoot what would (ideally) have been it's maximum current by  $\approx 180A$ , (30%).

The 8kA pulse requires the switch to conduct a peak di/dt of  $30\text{kA}/\mu\text{s}$ . This is an ambitious figured that, as pointed out in the background portion of this document, has not yet been realized with IGBT switches.

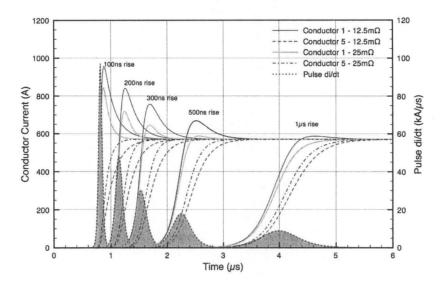

The plots in Figure 2.18 illustrate effect that altering rise-time has on the current distribution within the simulated Westcode module. Also investigated in these plots is the effect of adjusting the simulated on-state resistance of the IGBT die.

Figure 2.17: Current distribution for simulated module with  $12.5 m\Omega$  on-state resistance and a 10% to 90% rise-time of 300 ns

Figure 2.18(a) confirms the results of the frequency domain analyses in Figure 2.14. The linear relation to the on-state resistance observed in the frequency domain plots is again seen here: doubling the on-state resistance permits the rise-time to become halved, while still maintaining the same distribution.

(a) Comparison: Module current spread for different pulse rise-times. Data for  $12.5 \mathrm{m}\Omega$  and  $25 \mathrm{m}\Omega$  on-state resistances shown. Solid traces indicate most-conducting current path, dashed traces indicate the least-conducting path.

(b) Relative proportion of die current within module for various pulse rise-times.  $12.5 m\Omega$  on-state resistance data shown.

Figure 2.18: Effect of varying rise-time and on-state resistance on current distribution for a 8kA pulse

This follows from the relationship between the rise-time and edge bandwidth of a signal. For a single pole circuit such as this, the equivalent edge bandwidth for a given  $10\% \rightarrow 90\%$  rise-time can be estimated from the following approximation[26]:

$$BW \approx \frac{0.35}{T_r} \tag{2.3}$$

Here, BW represents the equivalent edge bandwidth, and  $T_r$  the risetime of the pulse. This approximation is a rule-of-thumb used for determining the choice of measurement equipment for measuring pulses. What is important to note is again the linear relationship between the rise-time and frequency content of the pulse.

In Figure 2.18, we can see that, as the rise-time of the pulse decreases, the relative distribution of current within the device tends towards the inductively dominated distribution: for a 100ns pulse, the distribution is nearly completely inductively determined.

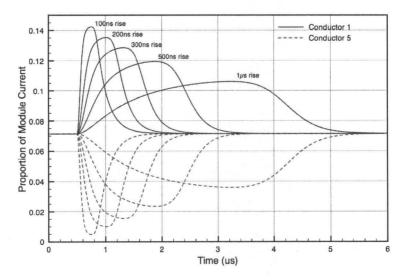

Up until this point, we have assumed that the geometry of the model was fixed. However, as it is a simple matter to investigate in PSpice, illustrating the effect of reducing the height of the copper region in the IGBT module is presented in Figure 2.19.

In this plot the numbers are indicative of the copper stand-off post height in the simulated device relative to the actual post height of the Westcode module. Shortening the height of each post has the effect of reducing L in Equation 2.2 by an equivalent amount. This shifts the frequency of divergence higher, and has the corresponding effect on the rising-edge distribution of the pulse.

Conclusion The results of simulations performed of the Westcode IGBT module present a largely consistent picture of the current distribution within the device. The results of the frequency and time domain simulation corroborate each other well, and the different workflow produce distributions that are largely in agreement.

The sensitivity of the predicted current distribution within the module

Figure 2.19: Predicted current distribution for simulated 12.5m $\Omega$  module with scaled post-heights.

has been established with regards to: pulse rise-time, die on-state resistance, AC drive frequency and copper post height. It has been found that there is a linear relationship between these factors and the uniformity of the distribution. In the case of the pulse rise-time and the die on-state resistance, this relationship is direct. For the remaining two factors, AC drive frequency and copper post height, the relationship is inverse.

# Chapter 3

# **Experimental Verification**

The final step in confirming the simulated model was to subject the physical module to experiments to determine the current distribution within the module.

Measurement Goals As the IGBT module is a compact, closed device, acquiring the current distribution is not a simple procedure. This chapter details the equipment and procedures necessary to produce results that can be compared to the simulations.

# 3.1 Method of Analysis

# 3.1.1 Frequency Domain

It was decided to initially perform measurements in the frequency domain. While the focus of the research is inherently a time-domain problem, in that it is concerned with transients occurring during fast switching, a frequency domain analysis of the problem is advantageous for two major reasons:

- 1. It greatly simplifies the process of acquiring measurements.

- 2. It also aides interpretation of the measurements: allowing the experimental results to be directly compared to simulation results.

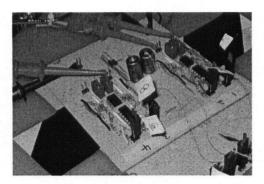

One of the reasons frequency domain measurements are easier to perform than time domain measurements is related to our choice of measurement equipment. Rogowski coils produce an output voltage that is proportional to the *derivative* of current flowing through the 'loop', and as such usually require some form of integration.

However, when the current source is a single frequency AC drive, the output of the Rogowski coil is directly proportional to the current, albeit phase shifted and scaled linearly by the frequency (see Section 3.1.3).