### AN EMBEDDED CALIBRATION TECHNIQUE FOR HIGH-RESOLUTION FLASH TIME-TO-DIGITAL CONVERTERS

by

#### **JAMES CICALO**

B.A.Sc., University of British Columbia, 2002

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

(Electrical and Computer Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

August 2007

© James Cicalo, 2007

### **Abstract**

As CMOS technology continues to advance, device dimensions will continue to decrease, thus enabling the creation of circuits which operate at increasingly greater frequencies. However, this increase in operating frequency has resulted in a reduced tolerance for circuit timing uncertainties. Therefore, techniques capable of measuring the timing characteristics of multi-GHz signals are needed to help address the growing number of timing problems found in modern CMOS circuits. For cost and accuracy reasons, embedded time interval measurement techniques which offer picosecond measurement accuracies and millisecond test-times are required to overcome these challenges.

The "sampling offset" based flash time-to-digital converter (SOTDC) is an embedded time interval measurement technique that has recently garnered much attention due to its attractive properties. These properties include sub-millisecond test times of multi-GHz signals, in addition to the potential for measurement accuracies in the order of picoseconds. However, the accuracy of an SOTDC is strongly dependent upon the capabilities of its calibration technique, and present SOTDC calibration techniques suffer from some very serious limitations. In fact, these limitations are so severe that present calibration techniques are impractical under realistic production test conditions.

This thesis presents the design and analysis of a novel embedded SOTDC calibration technique. The proposed calibration technique offers the potential for both sub-picosecond calibration accuracies and sub-100 millisecond calibration times. However, the main contribution of this work concerns the suitability of the proposed technique with a realistic production test environment. The capabilities of the proposed calibration technique have been proven using both mathematical analysis and behavioural modelling simulations.

# **Table of Contents**

| Abstract                                                            | ii  |

|---------------------------------------------------------------------|-----|

| Table of Contents                                                   |     |

| List of Figures                                                     | vii |

| List of Tables                                                      | vi  |

| Acknowledgements                                                    | x   |

| Chapter 1 Introduction                                              |     |

| 1.1 Time Interval Measurement                                       | 2   |

| 1.2 Thesis Organization                                             | 6   |

| Chapter 2 Flash-Based Embedded Time Interval Measurement Techniques | 7   |

| 2.1 Single Delay Line-Based Flash TDC                               | 9   |

| 2.2 Vernier Delay Line-Based Flash TDC                              | 12  |

| 2.3 Sampling Offset-Based Flash TDC                                 | 14  |

| Chapter 3 Embedded Calibration of a Sampling Offset-Based Flash TDC |     |

| 3.1 Behaviour of a Non-Ideal Arbiter                                |     |

| 3.1.1 A Model of Thermal Noise in an Arbiter                        | 21  |

| 3.1.2 Non-Ideal Arbiters and Time Interval Measurement              | 24  |

| 3.2 Direct Calibration Technique                                    | 25  |

| 3.2.1 Analysis                                                      |     |

| 3.2.2 Conclusions                                                   | 38  |

| 3.3 Relative Offset Calibration Technique                           |     |

| 3.4 Added Noise Calibration Technique                               |     |

| 3.4.1 Analysis                                                      |     |

| 3.4.2 Conclusions                                                   |     |

| Chapter 4 Proposed SOTDC Calibration Technique                      | 50  |

| 4.1 Simplified Proposed Calibration Technique                       | 50  |

| 4.2 Non-Ideal Arbiters and Added Noise                              |     |

| 4.3 Oscillator Non-Idealities                                       | 69  |

| 4.4 Implementation                                                  |     |

| 4.5 Summary                                                         |     |

| Chapter 5 Results and Analysis                                                 | 76  |

|--------------------------------------------------------------------------------|-----|

| 5.1 Theoretical Error Bounds                                                   | 77  |

| 5.2 Realistic Error Bounds                                                     | 84  |

| Chapter 6 Conclusions and Future Work                                          | 102 |

| 6.1 Summary and Contributions                                                  | 102 |

| 6.2 Future Work                                                                | 104 |

| 6.2.1 The impact of non-idealities                                             | 104 |

| 6.2.2 Circuit implementation                                                   | 105 |

| 6.2.3 Additional applications and SOTDC improvements                           |     |

| References                                                                     | 108 |

| Appendix A Circuit Implementation of Proposed Calibration Technique and 16-bit |     |

| SOTDC                                                                          | 112 |

|                                                                                |     |

|                                                                                |     |

|                                                                                |     |

|                                                                                |     |

|                                                                                |     |

# **List of Tables**

| Table 3.1:<br>Table 3.2: | Optimal ratio of $t_{\Delta}$ to $\sigma_t$ given the number of repetitions performed<br>Reported results from Matlab simulation of the added noise-based | 37 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1 4016 3.2.              | calibration technique ( $t_{\Delta} = 40 \text{ ps}$ , $\sigma_t = 250 \text{ ps}$ , N = 100 000) [26]                                                    | 46 |

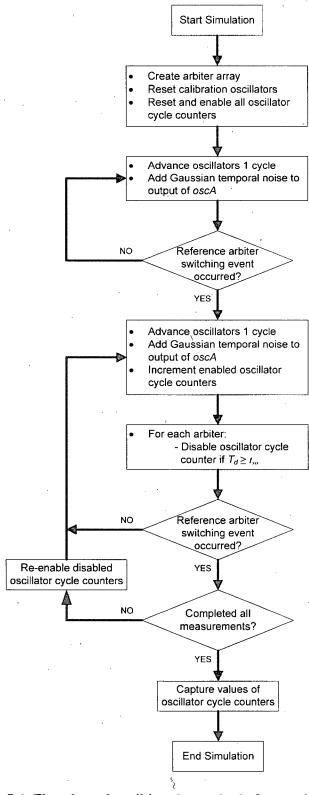

| Table 5.1:               | Properties of the oscillator cycle count histograms illustrated in Figure 5.5.                                                                            | 89 |

| Table 5.2:               | Four PLL divisors (A and B) and their corresponding $T_{\Delta}$ values ( $f_{in} = 50 \text{ kH}$ )                                                      | 98 |

| Table 5.3:               | Time required to calibrate an SOTDC, assuming the PLL divisors of Table 5.2 ( $f_{in}$ = 50 kH) [s].                                                      | 99 |

# List of Figures

| Figure 1.1:  | Timing jitter in a signal under test (SUT).                           | 2  |

|--------------|-----------------------------------------------------------------------|----|

| Figure 1.2:  | Three classifications of jitter                                       | 3  |

| Figure 1.3:  | PDF of random period jitter (a), and a combination of random and      | •  |

|              | deterministic period jitter (b).                                      | 4  |

| Figure 1.4:  | The growth of a random period jitter histogram as the number of       |    |

| ·            | measurement is increased                                              | 4  |

| Figure 2.1:  | The role of a TDC.                                                    | 8  |

| Figure 2.2:  | Single delay line-based flash TDC                                     | 10 |

| Figure 2.3:  | Single delay line-based flash TDC timing waveform.                    | 11 |

| Figure 2.4:  | A Vernier delay line-based flash TDC                                  |    |

| Figure 2.5:  | Vernier delay line-based flash TDC timing waveform                    | 13 |

| Figure 2.6:  | Sampling offset-based flash TDC                                       | 15 |

| Figure 2.7:  | Symmetric CMOS arbiter.                                               | 16 |

| Figure 2.8:  | Behaviour of a perfectly symmetric arbiter.                           | 17 |

| Figure 2.9:  | Behaviour of a positively biased arbiter.                             |    |

| Figure 3.1:  | Voltage domain model of thermal noise in a biased arbiter.            |    |

| Figure 3.2:  | Time domain model of thermal noise in a biased arbiter                |    |

| Figure 3.3:  | PDF of the sampling offset of a biased arbiter taking into account    |    |

|              | thermal noise.                                                        | 23 |

| Figure 3.4:  | Gaussian CDF.                                                         | 23 |

| Figure 3.5:  | Calculation of $t_{so}$ from the CDF of the sampling offset of a      |    |

|              | non-ideal arbiter                                                     | 24 |

| Figure 3.6:  | Sensitivity of the output of an arbiter to $\sigma_t$                 | 25 |

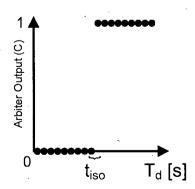

| Figure 3.7:  |                                                                       | 26 |

| Figure 3.8:  | Response of an arbiter to a sequence of increasing time intervals     | 26 |

| Figure 3.9:  | Response of an arbiter to several repetitions of a sequence of        |    |

| S            | increasing $T_d$ s.                                                   | 27 |

| Figure 3.10: | Histogram and CDF of the output of an arbiter.                        | 28 |

|              | Histogram of the output of an arbiter when $t_{\Delta} \leq \sigma_t$ |    |

|              |                                                                       |    |

| Figure 3.12: | Histogram of the output of an arbiter when $t_{\Delta} > \sigma_t$                                                             | 29        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|-----------|

|              | RMS $t_{ce}/\sigma_t$ vs. $t_{\Delta}/\sigma_t$ using the direct calibration technique                                         |           |

|              | Histogram and CDF of the output of a noise-free arbiter.                                                                       |           |

|              | $t_{so}$ versus $t_{ce}$ for a noise-free arbiter using direct calibration                                                     |           |

| _            | t <sub>ce</sub> probability density function                                                                                   |           |

|              | RMS $t_{ce}/\sigma_t$ vs. $t_{\Delta}/\sigma_t$ using the direct calibration technique                                         | 35        |

|              | Log-log plot of RMS $t_{ce}/\sigma_t$ vs. $t_{\Delta}/\sigma_t$ using the direct calibration technique.                        |           |

| -            | Log-log plot of RMS $t_{ce}$ vs. $\sigma_t$ when $t_{\Delta} = 10$ ps, using the direct                                        |           |

|              | calibration technique.                                                                                                         | 37        |

| Figure 3.20: | Gaussian distribution of arbiter sampling offsets due to process variation.                                                    | 41        |

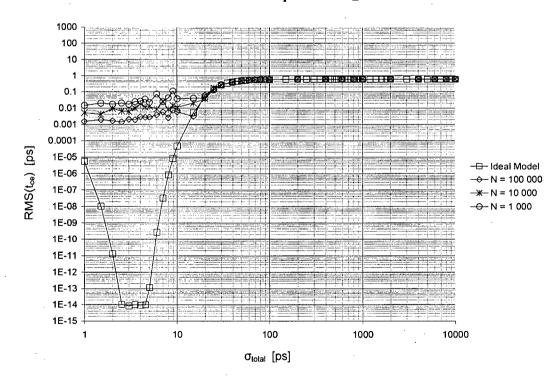

|              | Log-log plot of RMS $t_{ce}$ vs. $\sigma_t$ when N = 100 000, using the direct                                                 |           |

| ,            | calibration technique                                                                                                          | 43        |

| Figure 3.22: | Time domain model of added and thermal noise in a biased arbiter                                                               | 44        |

| Figure 3.23: | Arbiter sampling offset PDF with thermal and added noise                                                                       | 44        |

| Figure 3.24: | Addition of Gaussian temporal noise to a sequence of time intervals in                                                         |           |

| •            | order to create an arbiter sampling offset CDF.                                                                                |           |

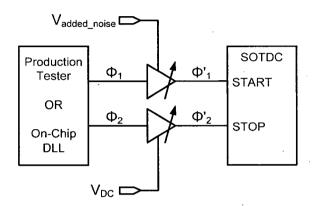

| Figure 3.25: | Added noise calibration technique implementation [26].                                                                         | 46        |

| Figure 3.26: | Log-log plot of RMS $t_{ce}$ vs. $\sigma_t$ when $t_{\Delta}$ = 40 ps and N = 100 000, using                                   |           |

|              | the model of the direct calibration technique described in section 3.2.1                                                       | 47        |

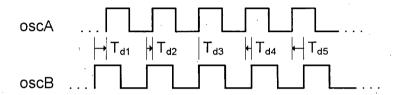

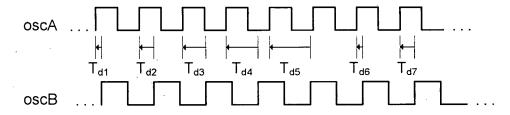

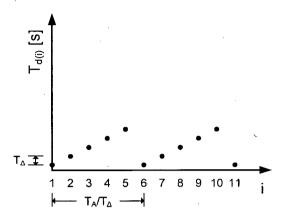

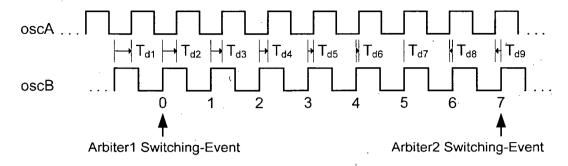

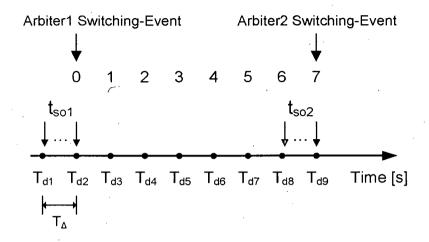

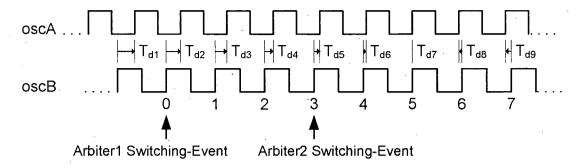

| Figure 4.1:  | Time intervals created by two free-running oscillators.                                                                        |           |

| Figure 4.2:  | Sequence of linearly increasing time intervals.                                                                                |           |

| Figure 4.3:  | Periodic time intervals created by two free-running oscillators.                                                               | 53        |

| Figure 4.4:  | Periodic sequence of time intervals generated from the output of                                                               |           |

|              | $oscA$ and $oscB$ assuming $T_A/T_\Delta = 5$ .                                                                                |           |

| Figure 4.5:  | Determining the relative sampling offsets of two arbiters.                                                                     | 55        |

| Figure 4.6:  | Variation in arbiter sampling offsets while still maintaining a                                                                |           |

|              | constant cycle count                                                                                                           | 56        |

| Figure 4.7:  | Behaviour of a negatively biased arbiter                                                                                       | 57        |

| Figure 4.8:  | Behaviour of a positively biased arbiter (a), and a positively                                                                 | ~ 0       |

|              | biased arbiter with reversed inputs (b).                                                                                       |           |

| Figure 4.9:  | Oscillator cycle count when the inputs to Arbiter2 are reversed                                                                | 60        |

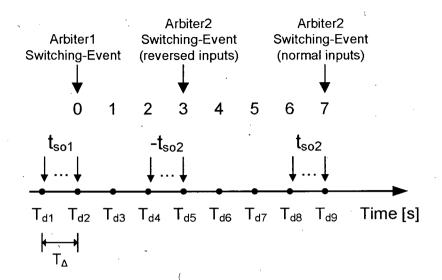

| Figure 4.10: | Summary of the information obtained by counting the number of                                                                  | <b>~1</b> |

| TC: 4 11.    | oscillator cycles elapsed between the switching-events of two arbiters                                                         | 01        |

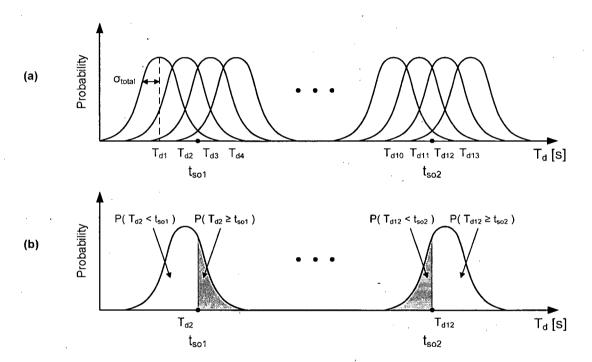

| Figure 4.11: | (a) PDF of several $T_{cs}$ belonging to a sequence of $T_{cs}$ (b) PDF of two                                                 |           |

|              | $T_{cs}$ (Note: the sampling offsets of two arbiters, $t_{so1}$ and $t_{so2}$ , are plotted                                    | 62        |

| Eigen 4 12.  | along the x-axis of both figures).                                                                                             | 03        |

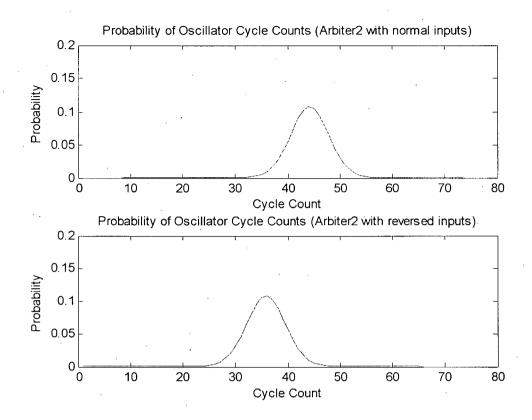

| rigure 4.12: | Probability of oscillator cycle counts when Arbiter2 has both normal and                                                       | 60        |

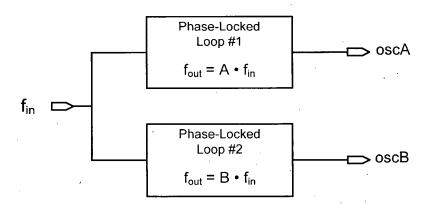

| E            | PLL implementation of oscA and oscB.                                                                                           | 70        |

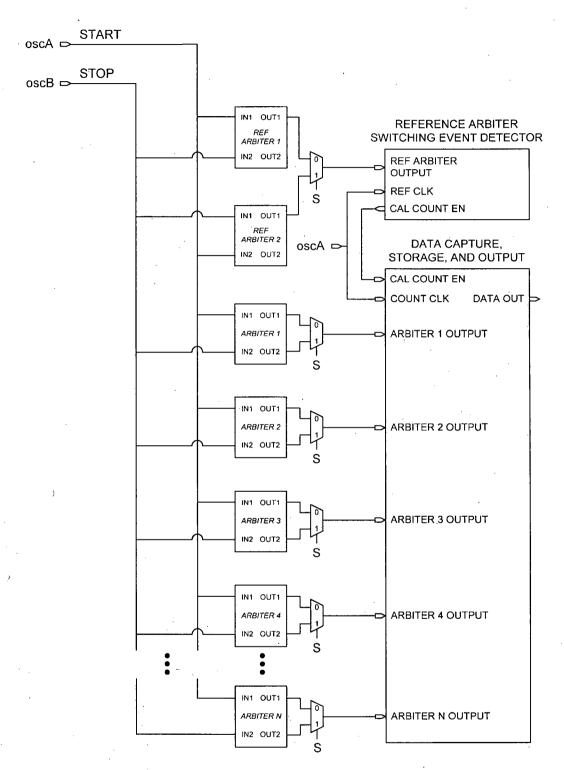

|              |                                                                                                                                |           |

|              | Conceptual circuit view of the proposed calibration technique  Minimum error of the proposed calibration technique across four | 12        |

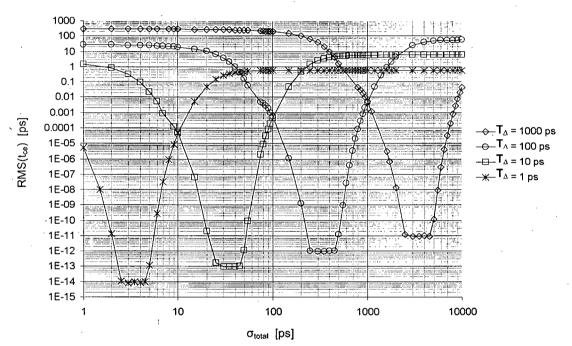

| rigule 3.1.  |                                                                                                                                | 70        |

| Eigens 5.0   | different T <sub>Δ</sub> values.                                                                                               | 19        |

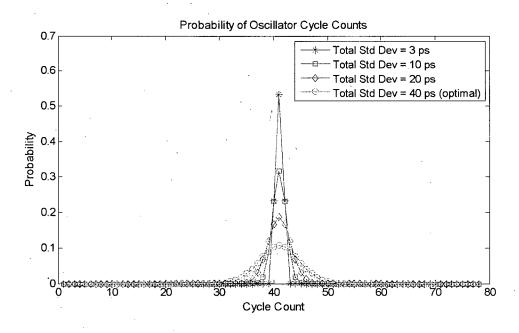

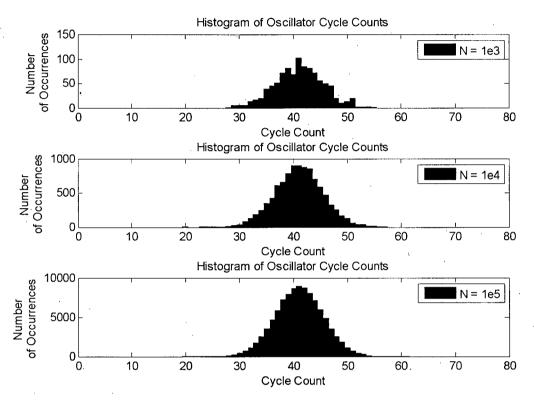

| Figure 5.2:  | •                                                                                                                              | 0.0       |

| E: 5.0       | all of which are $\leq \sigma_{optimal}$ ( $T_{\Delta} = 10 \text{ ps}$ )                                                      | 80        |

| Figure 5.3:  | Oscillator cycle counts PDFs for several different values of $\sigma_{total}$ ,                                                | ۰.        |

|              | all of which are $\geq \sigma_{optimal}$ ( $T_A = 10 \text{ ps}$ )                                                             | 82        |

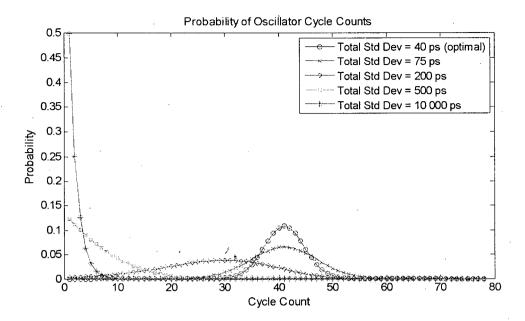

| Figure 5.4: | Flowchart describing the method of operation of the proposed SOTDC calibration technique Matlab model                                                                                | 87            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Figure 5.5: | Three oscillator cycle count histograms, generated using a different number of measurement repetitions                                                                               | 89            |

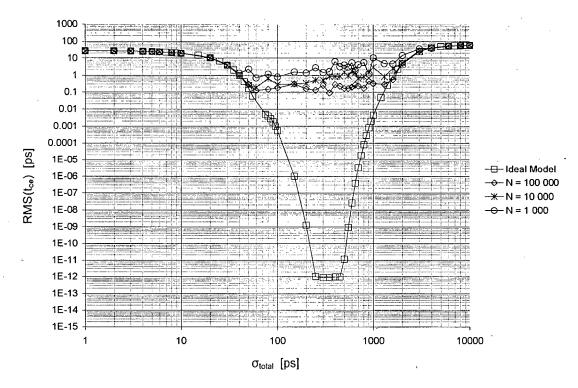

| Figure 5.6: | Comparison of the theoretical and realistic RMS error of the proposed calibration technique when $T_{\Delta} = 10$ ps.                                                               |               |

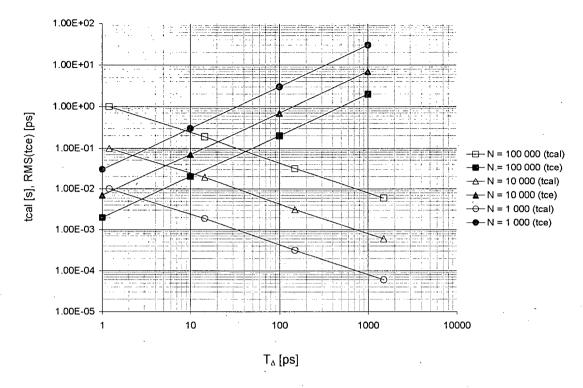

| Figure 5.7: | The RMS error of the proposed calibration technique when $T_{\Delta} = 10$ ps, plotted for three different number of measurement repetitions (N)                                     | 93            |

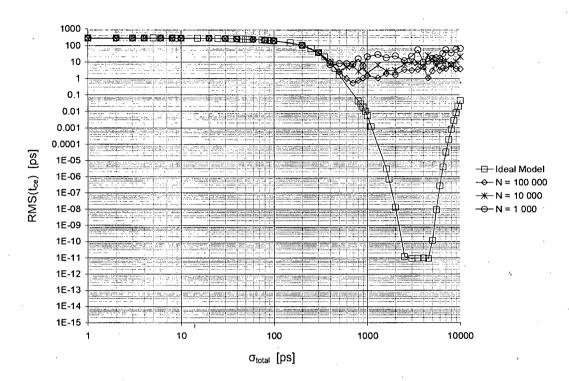

| Figure 5.8: | calibration technique when $T_{\Delta} = 100 \text{ ps.}$                                                                                                                            | 95            |

| Figure 5.9: | calibration technique when $T_{\Delta} = 1$ ns                                                                                                                                       | 96            |

| Figure 5.10 | Comparison of the theoretical and realistic RMS error of the proposed calibration technique when $T_{\Delta} = 1$ ps                                                                 | 96            |

| Figure 5.11 | The effect of varying $T_{\Delta}$ on the calibration time $(t_{cal})$ and the calibration error $(t_{ce})$ (calculated using an optimal value of $\sigma_{total}$ )                 |               |

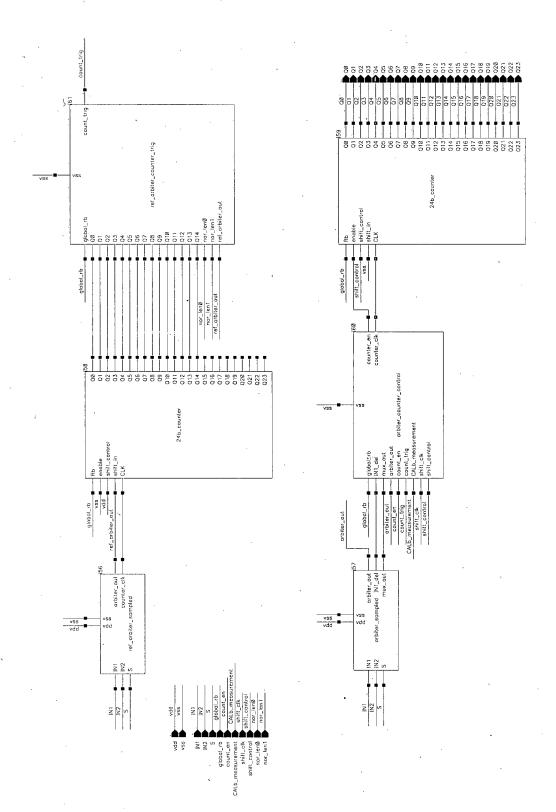

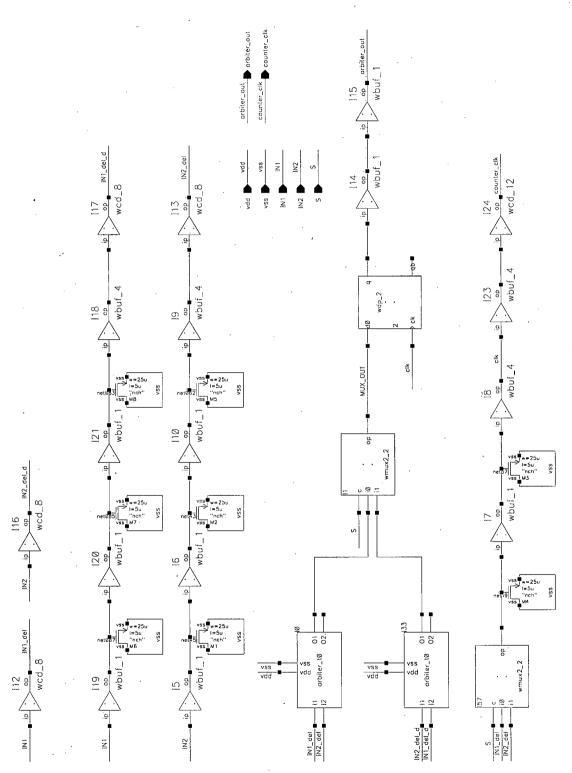

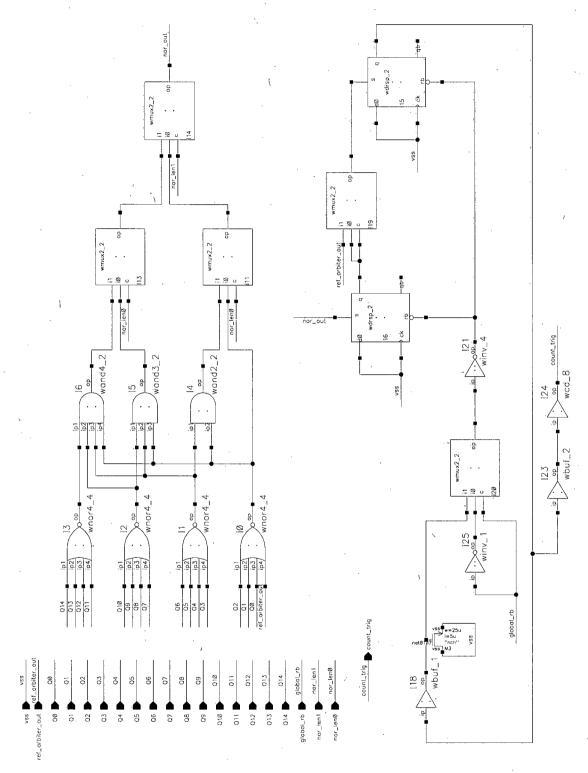

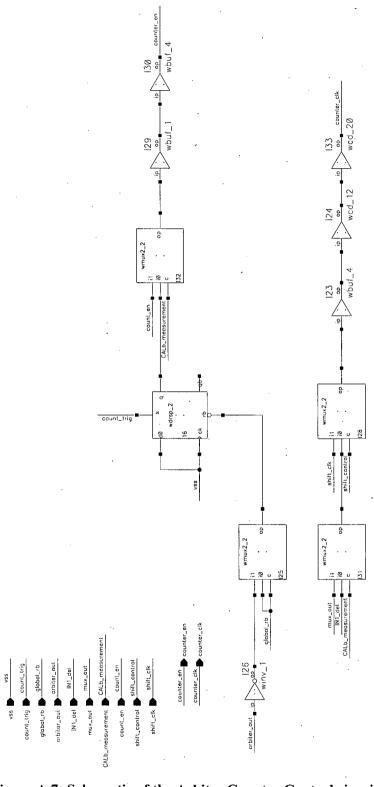

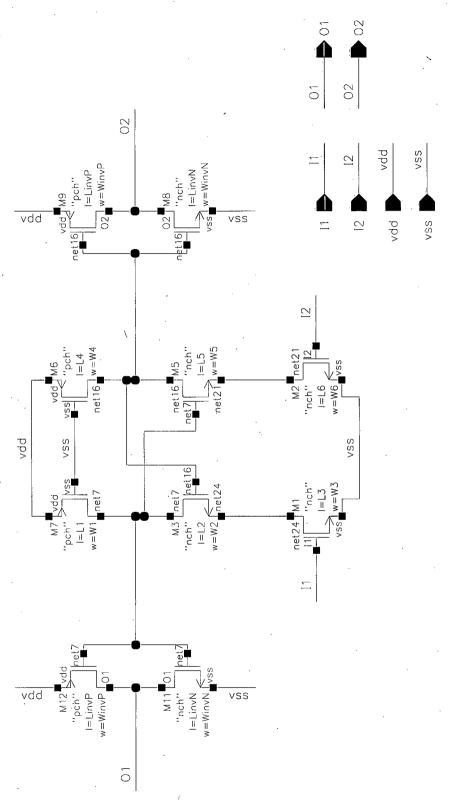

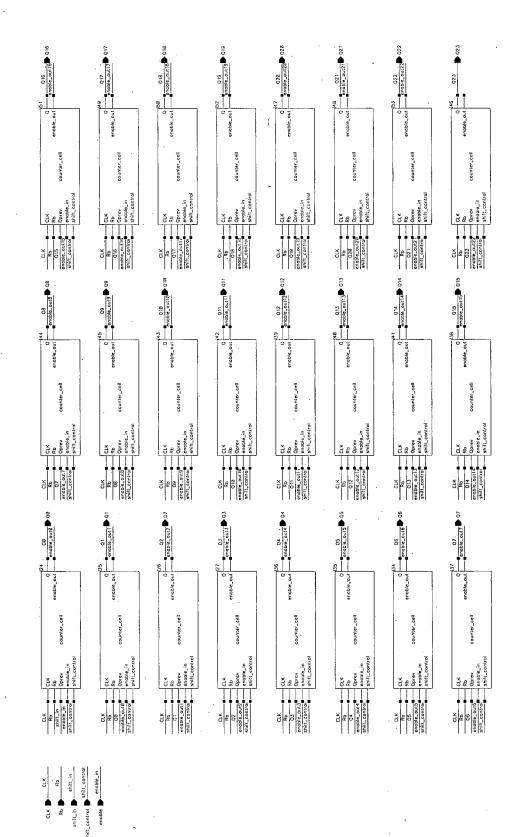

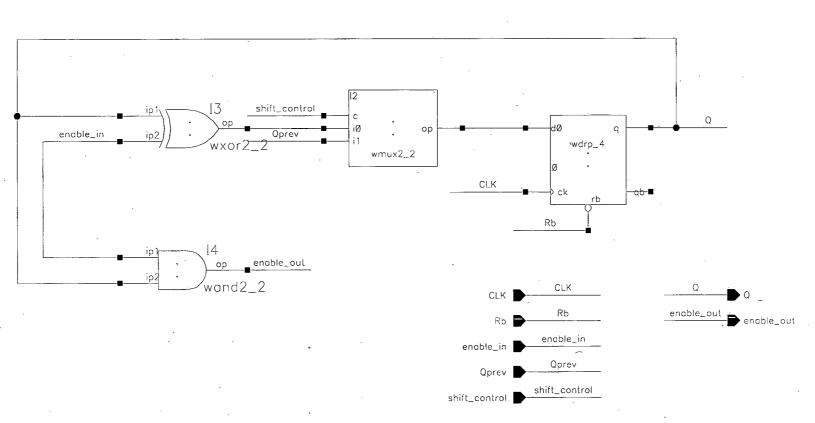

| Figure A.1  | Top-level schematic of the proposed SOTDC calibration circuit (1-bit of 16-bit SOTDC illustrated)                                                                                    | . 113         |

| Figure A.2  | Schematic of the Reference Arbiter Sampling circuit ("ref_arbiter_sampled").                                                                                                         | . 114         |

| Figure A.3  | Schematic of the Arbiter Array Counter Trigger circuit ("ref_arbiter_counter_trig")                                                                                                  | . 115         |

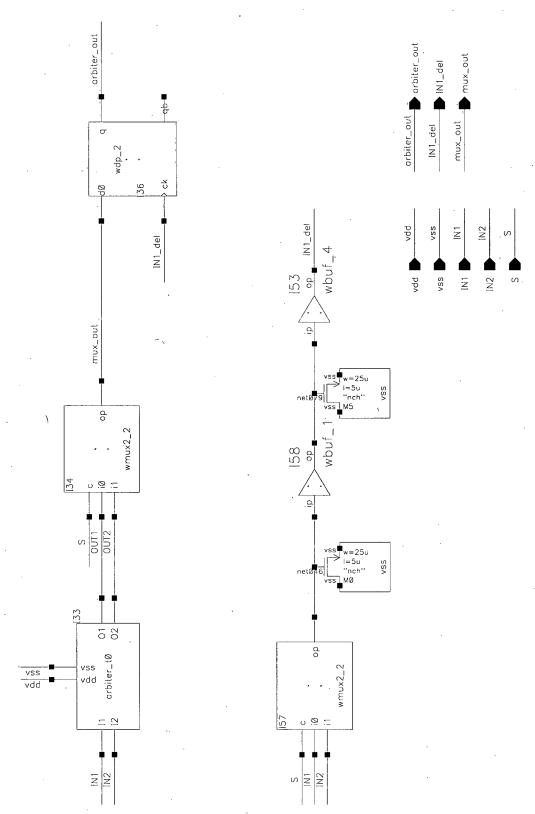

| Figure A.4  | Schematic of the Arbiter Sampling circuit ("arbiter_sampled")                                                                                                                        | . 116         |

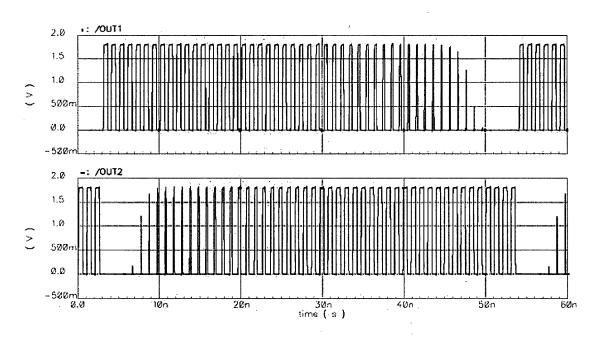

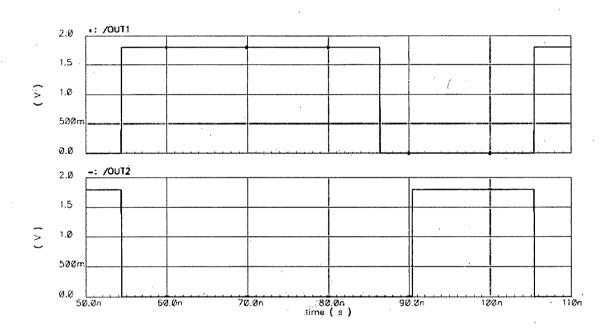

| Figure A.5  | The output of a positively biased arbiter when two free-running oscillators of different frequency, $oscA_c$ and $oscB_c$ , are applied to its inputs ( $T_A = 1$ ns, $T_A = 20$ ps) | . 11 <b>7</b> |

| Figure A.6  | • • • • • • • • • • • • • • • • • • • •                                                                                                                                              | <b>5</b>      |

| Figure A.7  | Schematic of the Arbiter Counter Control circuit                                                                                                                                     |               |

| Figure A &  | ("arbiter_counter_control")                                                                                                                                                          |               |

|             | Schematic of the 24-bit Counter circuit ("24b counter").                                                                                                                             |               |

| _           | 0: Schematic of the 24-bit Counter circuit ( 24b_counter )                                                                                                                           |               |

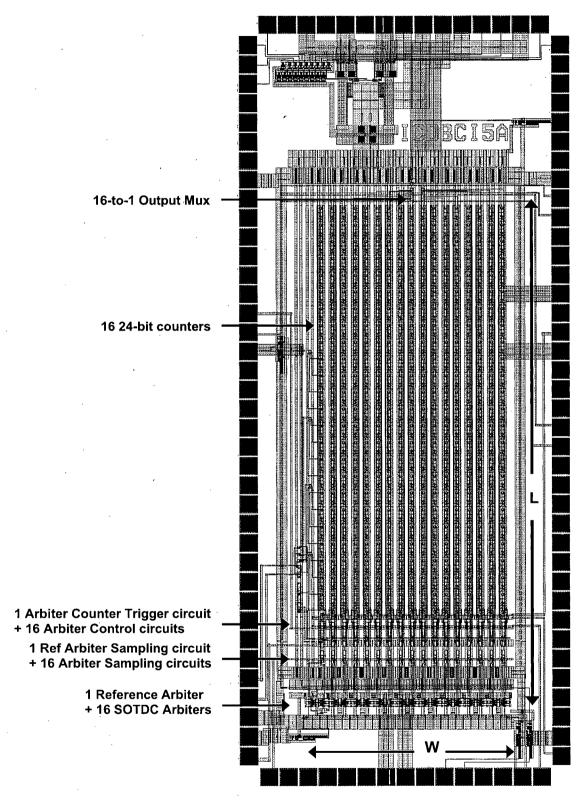

|             | 1: Layout view of a 16-bit SOTDC and proposed calibration circuit in                                                                                                                 |               |

| -9          | 0.35 um CMOS (L = 1930 um, W = 690 um)                                                                                                                                               | . 123         |

# Acknowledgements

I would like to convey my most sincere gratitude to those who have helped me to complete this work. Firstly, I would like to thank my research supervisor, Professor André Ivanov, for providing me with the opportunity to join his research group in addition to the UBC SoC laboratory. Professor Ivanov's continued guidance and support throughout this work was instrumental to its ultimate success. Secondly, I would like to thank my colleagues at the SoC laboratory, and in particular, Zaman Mollah, Andy Kuo, Michael Jones, and Dr. Roberto Rosales. I learned much from our countless discussions, and I will always be grateful for their advice and friendship. I would also like to thank the Canadian Microelectronics Corporation for granting me access to their IC fabrication services, in addition to Micronet, a Canadian Network of Centres of Excellence focused on the design of microelectronic systems, for financial support.

Last, but certainly not least, I would like to thanks my parents, Ken and Teresa, my sister Carolyn, and my fiancée, Linda Zhang, for their immeasurable love and encouragement during the many challenges I encountered over the years.

### Chapter 1

### Introduction

As CMOS technology continues to advance, device dimensions will continue to decrease, thus enabling the creation of circuits which operate at increasingly greater frequencies. However, this increase in operating frequency has resulted in a decreased tolerance for circuit timing uncertainties. In addition, the behaviour of a circuit, and therefore the timing of its signals, is becoming increasingly sensitive to environmental influences. These environmental influences may disturb the operation of a circuit through a number of mechanisms. These mechanisms include capacitive and inductive coupling, as well as the injection of noise into the power-supply or the substrate of a CMOS circuit [1, 2]. As these mechanisms are becoming increasingly prevalent in modern CMOS circuits, critical path signals are increasingly susceptible to unwanted timing variations.

Unintended timing variations in a signal may cause a circuit to become non-functional. Therefore, the ability to detect, diagnose, and if possible, repair timing problems is of the utmost importance if the reliability of a CMOS circuit is to be guaranteed. However, detecting timing problems in multi-GHz signals can be a very challenging task due to the extremely short time intervals that must be measured. For example, a 10% deviation in the

period of a 10 GHz signal translates to a mere 10 ps. Without the ability to detect timing problems in multi-GHz signals, it is not possible to diagnose or repair them. As a result, techniques capable of detecting and diagnosing timing problems in multi-GHz signals are needed to help address the growing number of timing issues found in modern CMOS circuits.

#### 1.1 Time Interval Measurement

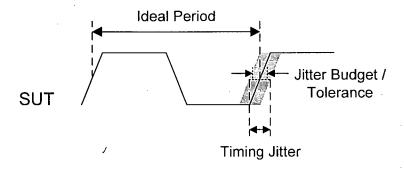

The detection or diagnosis of a timing problem in a CMOS circuit is often accomplished with the help of a time interval (TI) measurement technique. TI measurement is a time domain analysis technique that is often used to deduce the timing characteristics of a signal by estimating its threshold crossings in the voltage domain [3]. Many types of TI techniques exist, however they all share a common goal of quantifying the amount of uncertainty in the timing of a signal. Once this timing uncertainty has been quantified, predictions regarding the probability of a circuit's failure can be made. Timing uncertainty is usually referred to as "timing jitter" or "absolute jitter", which is defined as the deviation from the ideal timing of an event, and can be accumulated over many cycles [4, 5]. This definition is illustrated in Figure 1.1, where the amount of timing jitter in a signal under test (SUT) is indicated by the degree of uncertainty in the temporal location of a signal transition.

Figure 1.1: Timing jitter in a signal under test (SUT).

Another useful definition that is illustrated in Figure 1.1 is that of the jitter budget or tolerance of a design, which is the maximum amount of timing jitter that can exist in a signal before the circuit fails to operate reliably. Two additional classifications of jitter exist, as

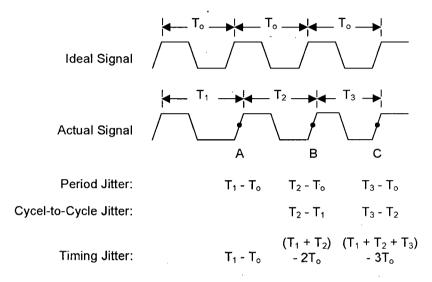

illustrated in Figure 1.2. The first of these classifications is the most common of the three, and is known as "period" jitter. Period jitter is simply the deviation of a single period from its ideal value. The second classification is known as "cycle-to-cycle" jitter, and is a measure of the difference between adjacent cycles.

Figure 1.2: Three classifications of jitter.

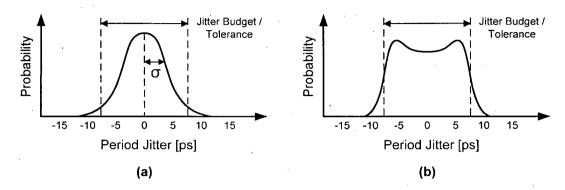

Each of the aforementioned types of jitter may contain both random and deterministic components, depending upon the source of the jitter. In any case, it is possible to predict the probability with which a signal will exceed a circuit's timing margins by constructing the probability density function (PDF) of the period jitter [6]. The PDF of a purely random source of period jitter is illustrated in Figure 1.3 (a). Inspection of Figure 1.3 (a) reveals that random period jitter can be characterized by a Gaussian distribution. Since a Gaussian distribution is unbounded, its peak-to-peak value (the difference between the shortest and longest cycles) is also unbounded, and is highly dependent upon the number of cycles measured. The PDF of period jitter resulting from both random and deterministic sources is illustrated in Figure 1.3 (b). The shape of this PDF is determined by the convolution of the

random and deterministic components' PDFs [7]. As deterministic jitter is bounded in nature, its peak-to-peak value is also bounded.

Figure 1.3: PDF of random period jitter (a), and a combination of random and deterministic period jitter (b).

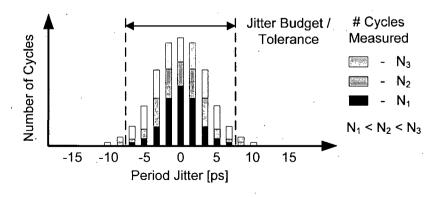

As the function of a time interval measurement technique is to accurately estimate the duration of a time interval, multiple measurements of a signal's period can be performed and subsequently compiled into a histogram. If this histogram is normalized by the number of measurements performed, a PDF of the signal's period jitter can be produced. However, before an accurate PDF can be produced, many cycles need to be measured [8]. This idea is illustrated in Figure 1.4, where the random period jitter of a signal is estimated using three different histograms. Each histogram is drawn using an increasing number of measurement results.

Figure 1.4: The growth of a random period jitter histogram as the number of measurement is increased.

Inspection of Figure 1.4 reveals that both the standard deviation and the peak-to-peak jitter of the histogram may vary as the number of measurement cycles is increased. Although a few thousand measurements are often sufficient to provide an accurate estimate of standard deviation, hundreds of thousands, or even millions of measurements are often required in order to make an accurate prediction of the peak-to-peak jitter in a multi-GHz signal. Such information is frequently used as a metric when determining the probability of circuit failure [8].

While many different time interval measurement techniques exist [9], the choice of which technique to employ for a given application ultimately depends on the measurement requirements. For instance, the measurement of period jitter at giga-bits-per-second (Gbps) data rates necessitates very accurate results, as the jitter budget at these speeds is extremely small. For example, the authors in [20] predict that measurement accuracies of 1 ps or less will be required for bit-error-rate (BER) testing of 10 Gbps integrated circuit (IC) pins.

As previously mentioned, obtaining accurate jitter results may require a large number of measurements. Therefore, as signal data rates increase along with jitter measurement requirements, the total measurement time of TI measurement techniques continues to rise. As a result, only a select group of low test-time measurement techniques are feasible in a volume production test environment, where test time is directly related to product cost [10].

Signal amplitude sampling-based techniques [11] can be used to reconstruct the shape of a voltage-time waveform based on a number of voltage-time samples. While these techniques are not strictly "time interval" based jitter measurement techniques, they have been successfully used to measure jitter with picosecond accuracy [12]. However, signal amplitude sampling-based techniques typically require tens of seconds per measurement, which is far too much time for a volume production test environment [13]. High-frequency production testers can be used to measure jitter with picosecond accuracy in a matter of seconds [14, 15, 16]. However, these testers generally cost millions of dollars. In addition, probing gigaHertz signals for off-chip measurement can introduce significant additional jitter [20]. Therefore, for cost and accuracy reasons, embedded (on-chip) time interval

measurement techniques which offer picosecond measurement accuracies and millisecond test-times are very useful tools to enable the cost-effective analysis of a growing number of timing problems found in modern CMOS circuits [17]. In fact, embedded time interval measurement techniques are currently the subject of research within both academia and industry [18].

One new time interval measurement technique which has recently garnered much attention is the "sampling offset" based flash time-to-digital converter (SOTDC) [23]. This time-to-digital converter (TDC) offers sub-millisecond test times for gigaHertz signals, as well as the potential for picosecond measurement accuracies. However, the accuracy of an SOTDC is strongly dependent on the capabilities of its calibration technique. To date, no feasible embedded calibration technique for an SOTDC has been proposed. This thesis is focused on the design of a novel embedded calibration technique for SOTDCs which offers the potential for sub-picosecond calibration accuracies, and calibration times in the order of milliseconds. While specific reference to the calibration of an SOTDC is made, this calibration technique is applicable to any flash-based TDC.

### 1.2 Thesis Organization

This thesis consists of a total of six chapters. Important background information concerning the evolution of traditional flash-based TDCs into state-of-the-art SOTDCs is presented in Chapter 2. Three previously proposed SOTDC calibration techniques are described in Chapter 3, and the important limitations of each are investigated. Next, the embedded calibration technique proposed in this thesis is described in Chapter 4, followed by an analysis of its capabilities and limitations in Chapter 5. Finally, conclusions regarding the contribution of this thesis are presented in Chapter 6, along with a discussion of future work.

# Chapter 2

### Flash-Based Embedded Time Interval

# **Measurement Techniques**

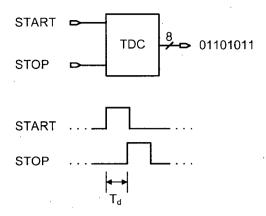

Embedded time interval measurement can be performed using a variety of techniques, and is often realized using a time-to-digital converter (TDC). A TDC is a circuit that outputs a digital codeword when a time interval is applied to its input, as shown in Figure 2.1. The time interval to be measured, referred to from hereon as  $T_d$ , is defined as the difference in time between the rising edge transitions of two signals, which are traditionally referred to as START and STOP. This digital codeword, once interpreted, approximates the duration of the time interval.

Figure 2.1: The role of a TDC.

While many different types of TDCs exist, they can all be evaluated against the following criteria:

#### • Accuracy:

How closely the interpreted digital codeword matches  $T_d$ .

#### • Resolution:

The smallest measurable difference in  $T_d$ .

#### • Precision:

The degree to which a set of measurements of the same  $T_d$  agree.

#### • Measurement rate:

The maximum rate at which different  $T_d$ s can be applied to the TDC's input while still receiving correct codewords at its output.

#### • Dynamic range:

The ratio of the maximum to minimum  $T_d$  measurable by the TDC.

#### • Power and Area requirements:

The area required to implement an on-chip TDC with certain accuracy, resolution, precision, measurement rate, and dynamic range specifications, in addition to the power consumed by this TDC.

As the accuracy, resolution, precision, dynamic range, and measurement rate requirements placed upon TDCs become increasingly stringent, trade-offs are necessary in order to construct a feasible TDC architecture. Many TDC architectures target a reduced measurement rate in order to meet the accuracy, resolution, and precision requirements. Examples of such TDCs include the Vernier oscillator-based TDC [19], and the undersampling-based TDC described in [20]. However, this trade-off can be very costly for integrated circuit (IC) manufacturers, since the resulting increase in production test time increases overall production costs.

This chapter examines the evolution of "flash" TDC architectures. The chapter begins with a description of the most primitive form of a flash TDC, and concludes with a presentation of the state-of-the-art in flash TDC design, where picosecond measurement resolutions are achievable. In general, Flash TDCs are capable of very high measurement rates. In fact, flash TDCs are capable of operating at or near the frequency of the signal or signals under test, from which the START and STOP signals are derived. Flash TDCs are analogous to flash analog-to-digital converters (ADCs), since their output codeword is determined in a single step by a bank of comparators [21]. Therefore, the flash TDC architecture is a very good candidate for embedded time interval measurement in both a production test environment or in a customer application, where measurement time is of comparable importance to measurement accuracy, resolution, and precision.

### 2.1 Single Delay Line-Based Flash TDC

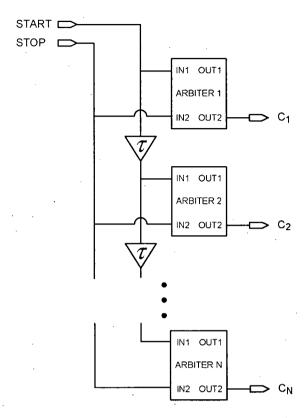

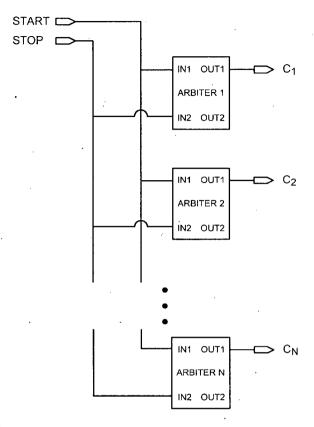

The most basic form of a flash TDC is the single delay line-based flash TDC, which is illustrated in Figure 2.2. This TDC architecture has two primary inputs, namely START and STOP, and a multitude of outputs, labelled  $C_I$  to  $C_N$  in this embodiment.

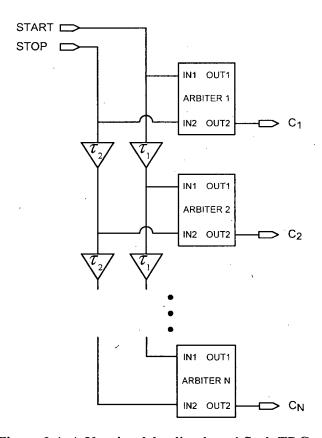

Figure 2.2: Single delay line-based flash TDC.

If we define the instant at which the START signal transitions from a low to a high logic level as  $t_{start}$ , and if we define  $t_{stop}$  analogously for the STOP signal, then we can describe  $T_d$  in mathematical terms with the following equation:

$$T_d = t_{stop} - t_{start} \tag{2.1}$$

As shown in Figure 2.2, the START signal is delayed by a single buffer as it propagates from one arbiter to the next. The delay of each buffer is equal to  $\tau$ . At each stage, an arbiter determines which of its two inputs was the first to transition from a low to a high logic level, i.e., the first to make a "positive" transition. If INI is the first to perform such a transition then OUTI is set to a high logic level and OUT2 to a low logic level, and vice versa if IN2 is the first to arrive. Figure 2.3 illustrates the operation of a single delay line-based flash TDC

consisting of 4 arbiters. This type of TDC can be referred to as a 4-bit single delay line-based flash TDC.

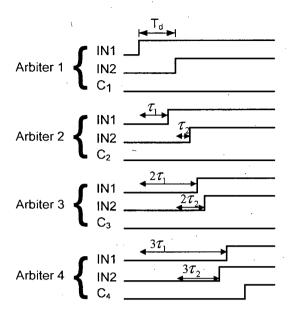

Figure 2.3: Single delay line-based flash TDC timing waveform.

As is shown in Figure 2.3, a single delay line-based flash TDC produces a thermometer code digital output ( $C_4C_3C_2C_1 = 1000$ ).  $T_d$  can be approximated by noting the location of the "0" to "1" transition in the output codeword. In the above example,  $T_d$  is shown to satisfy the following condition:

$$2\tau < T_d \le 3\tau \tag{2.2}$$

The resolution of this TDC is limited by the buffer delay,  $\tau$ . This buffer delay has a practical lower bound due to the physical constraints of the technology in which it is implemented. Therefore, for high-resolution applications, a single delay line-based flash TDC may be inadequate.

#### 2.2 Vernier Delay Line-Based Flash TDC

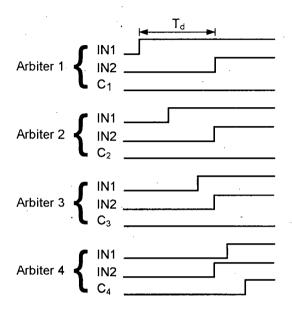

In order to overcome the resolution limitations of a single delay line-based flash TDC, a second delay line can be added, as shown in the Vernier delay line-based flash TDC of Figure 2.4.

Figure 2.4: A Vernier delay line-based flash TDC.

This second delay line is used to incrementally delay the STOP signal as it propagates from one arbiter to the next, as is done to the START signal in the single delay line-based flash TDC. The delay of each buffer in the START signal path is equal to  $\tau_I$ , whereas the delay of each buffer in the STOP signal path is equal to  $\tau_2$ . An example of the method of operation of a 4-bit Vernier delay line-based flash TDC is illustrated in Figure 2.5.

Figure 2.5: Vernier delay line-based flash TDC timing waveform.

As shown in Figure 2.5, a Vernier delay line-based flash TDC also produces a thermometer code digital output ( $C_4C_3C_2C_1 = /1000$ ).  $T_d$  can be found using the same procedure described for the single delay line-based flash TDC, i.e., by noting the location of the "0" to "1" transition in the output codeword. In the example illustrated in Figure 2.5,  $T_d$  is shown to satisfy the following condition:

$$2(\tau_1 - \tau_2) < T_d \le 3(\tau_1 - \tau_2) \tag{2.3}$$

The buffer delay difference, i.e.,  $\tau_l - \tau_2$ , where  $\tau_l > \tau_2$ , defines the resolution of a Vernier delay line-based flash TDC. Therefore, sub-gate delay resolution can be achieved with this architecture.

Calibration of a Vernier delay line-based flash TDC is done to ensure that the buffers in each of the two delay lines provide the required delay, i.e.,  $\tau_1$  or  $\tau_2$ . Normally a delay-locked-loop (DLL) is used to accomplish this, ensuring that integral nonlinearity (INL) errors in the converter are minimized [22]. However, the arbiters are most often constructed from flip-flops, since a flip-flop is essentially an arbiter. While flip-flops make efficient arbiters,

their non-zero setup times may influence the buffer delay difference ( $\tau_l$  -  $\tau_2$ ) and hence contribute to the TDC's differential nonlinearity (DNL) error, as a DLL-based calibration technique cannot be used to perform stage-by-stage calibration. For example, there is no impact on the measurement accuracy of the TDC as long as the flip-flops have identical setup times, in which case they can be treated as a constant and removed from the measurement results. However, the setup times of flip-flops on the same semiconductor die can vary significantly due to process variations. For example, variations as large as 50 ps have been observed in a 0.35  $\mu$ m CMOS process [23]. As the resolution of a Vernier delay line-based flash TDC is increased, the importance of a flip-flop's setup time is amplified, as it is not accounted for during calibration. Therefore, there exists a limit to how small the buffer delay difference can be made before the variability between flip-flop setup times begins to add a significant level of error to the measurement results. For the measurement of 5 and 10 Gbps data rate signals, where the required accuracy is 10 ps or better, a Vernier delay line-based flash TDC is inadequate [20].

#### 2.3 Sampling Offset-Based Flash TDC

A novel concept discussed in [23] attempts to address the time interval measurement accuracy requirements of 10 Gbps data rate signals and beyond. The author in [23] suggests that a TDC with a resolution of 2 ps or less can be constructed by removing the buffers from a Vernier delay line-based flash TDC, thereby making use of the inherent variations in the setup times of the arbiters. This type of TDC, shown in Figure 2.6, is known as a "sampling offset" TDC (SOTDC).

Figure 2.6: Sampling offset-based flash TDC.

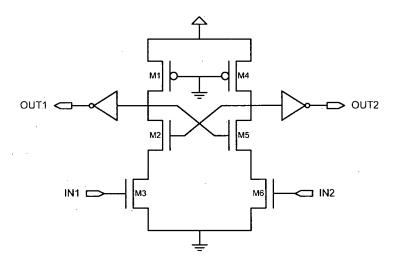

The term "sampling offset TDC" arises from the fact that a time interval is quantized using the difference in the setup times, or sampling offsets, of the arbiters, assuming they are known. This is in contrast to a Vernier delay line-based TDC, which uses a difference in buffer delays to quantize time. Instead of implementing the arbiters or "sampling elements" with flip-flops, the author in [23] chose to use symmetric CMOS arbiters. A symmetric CMOS arbiter schematic is drawn in Figure 2.7. This circuit arbitrates between two inputs, *IN1* and *IN2*, by determining which input was the first to perform a low to high transition, i.e., a positive transition.

Figure 2.7: Symmetric CMOS arbiter.

The operation of a symmetric CMOS arbiter relies on the use of positive feedback. With inputs *IN1* and *IN2* discharged low, transistors M3 and M6 remain in cutoff mode. Therefore, the drains of M2 and M5 remain precharged high through transistors M1 and M4, and outputs *OUT1* and *OUT2* remain predischarged low. Now, if *IN1* is the first input to perform a positive transition, current will flow down the left-hand side of the arbiter as M3 leaves the cutoff mode of operation. If M1, M2, and M3 are properly sized, the voltage on the drain of M2 will fall low enough to cause *OUT1* to switch high. In addition, since the drain of M2 is connected to the gate of M5, M5 will enter the cutoff region, in turn maintaining a high voltage at the drain of M5 and a low voltage at *OUT2*. It is this use of positive feedback between transistors M2 and M5 that allows this arbiter to successfully resolve picosecond-timing differences, as demonstrated in [24].

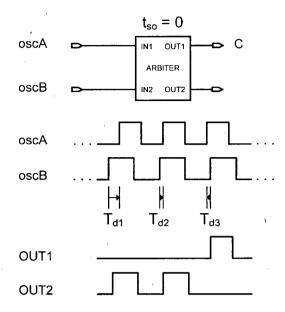

An arbiter such as the one illustrated in Figure 2.7 is said to be perfectly symmetric if its left hand side behaves identically to its right hand side. As a consequence of this perfect symmetry, its sampling offset ( $t_{so}$ ) is equal to zero seconds. An arbiter with a non-zero sampling offset is said to be "biased" towards one of its inputs. Therefore, a perfectly symmetric arbiter does not exhibit a bias towards either input. As a result, the first input to transition from a low to a high logic level is always recorded as such, with the corresponding output set to a high logic level. This behaviour is illustrated in Figure 2.8.

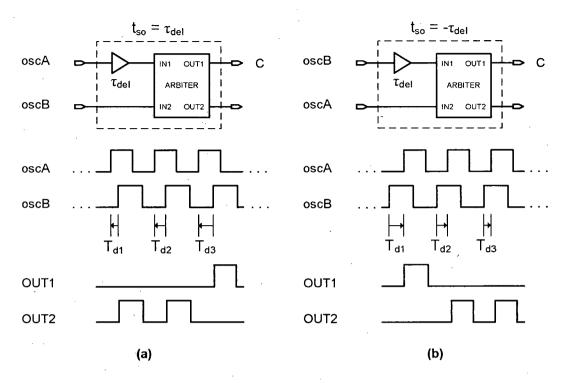

Figure 2.8: Behaviour of a perfectly symmetric arbiter.

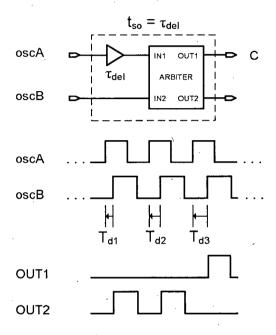

In Figure 2.8, two oscillators, oscA and oscB, are depicted as the inputs to a perfectly symmetric arbiter. The frequency of oscA is slightly greater than that of oscB. Therefore, a sequence of varying time intervals is generated from the rising edge transitions of the two oscillators. If the temporal location of a rising edge transition of oscB is denoted as  $t_{oscB(i)}$ , and if  $t_{oscA(i)}$  is defined analogously for oscA, then each time interval can be expressed mathematically as:

$$T_{d(i)} = t_{oscB(i)} - t_{oscA(i)}$$

(2.4)

The preceding definition allows for the sampling offset of the arbiter in Figure 2.8 to be bound by the following inspection-based equation:

$$T_{d2} < t_{so} \le T_{d3}$$

(2.5)

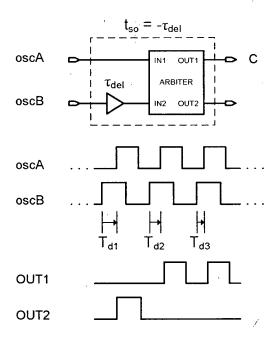

A biased arbiter, however, exhibits a non-zero sampling offset. This bias can be the result of transistor mismatches between the left and right hand sides of the arbiter, and is often attributed to process variations. However, it can be useful to intentionally bias an

arbiter, in which case the transistor mismatches are the result of design intent [25]. The behaviour of a biased arbiter is illustrated in Figure 2.9, where a buffer delay ( $\tau_{del}$ ) has been inserted before input *IN1* of a perfectly symmetric arbiter in order to mimic the behaviour of a biased arbiter.

Figure 2.9: Behaviour of a positively biased arbiter.

Analogously, the sampling offset of the arbiter in Figure 2.9 can be bound with the following inspection-based equation:

$$T_{d2} < t_{so} \le T_{d3} \tag{2.6}$$

In summary, inserting a buffer before input INI of a perfectly symmetric arbiter results in an arbiter that is biased by an amount equal to the delay of the buffer ( $\tau_{del}$ ). For this reason, this type of arbiter is known as a "positively biased" arbiter.

A typical SOTDC can be constructed from several positively biased arbiters, each with a unique sampling offset. If the arbiters are positioned within the SOTDC in order of smallest  $t_{so}$  to largest, then the output codeword will be in the form of a thermometer code.

Therefore, if a time interval,  $T_d$ , where  $T_d > 0$ , is applied to the SOTDC, then the value of  $T_d$  can be approximated by noting the location of the "0" to "1" transition in the output codeword. For example, assume an SOTDC consisting of only 4 positively biased arbiters exists. Now, if a  $T_d$  which is greater than the sampling offset of arbiters 1 and 2, but smaller than that of arbiters 3 and 4, is applied to the SOTDC, then the output codeword will look as follows:  $C_4C_3C_2C_1 = 0011$ . Such an output codeword can be used to approximate the value of the applied time interval,  $T_d$ , as shown in Equation (2.7), where  $t_{so2}$  and  $t_{so3}$  represent the sampling offsets of arbiters 2 and 3, respectively.

$$t_{so2} \le T_d < t_{so3} \tag{2.7}$$

If the sampling offsets of the arbiters are equally spaced, then the error in the above approximation must be bounded by the resolution of the SOTDC, which is defined as the step size of the arbiter sampling offsets. The challenge associated with using an SOTDC for time measurement lies in determining the sampling offsets of the arbiters, as without such information it is impossible to extract useful data from the arbiter outputs. Several calibration techniques have been developed in order to measure the sampling offsets of the arbiters within an SOTDC. The merits and drawbacks of each are presented in the following chapter, and a new calibration technique is proposed in Chapter 4.

### Chapter 3

### **Embedded Calibration of a Sampling**

# Offset-Based Flash TDC

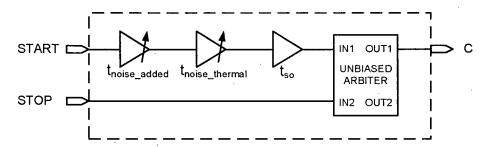

Present SOTDC calibration techniques suffer from some very serious limitations. The most straightforward of these techniques require an accurately known sequence of closely spaced  $T_d$  values, which for a picosecond resolution SOTDC is very difficult to generate onchip. A more sophisticated technique, as described in [23], requires precise knowledge of the mean sampling offset of the SOTDC arbiters. Unfortunately, such information is usually not available. Another technique, as described in [26], requires the use of an external signal generator or an on-chip DLL in order to generate  $T_d$  values which are not necessarily closely spaced, but accurately known nonetheless. Time interval accuracies in the order of picoseconds are required for successful implementation of this technique, and therefore dictate the use of only the most accurate signal generators or on-chip DLLs. In addition, this technique employs two on-chip variable delay elements that must be calibrated with picosecond accuracy in order to resolve any skew introduced between the output of the  $T_d$

generator and the input of the SOTDC, and is therefore not a complete solution. The technique proposed in Chapter 4 is exempt from any of these deficiencies.

#### 3.1 Behaviour of a Non-Ideal Arbiter

Before the aforementioned calibration techniques can be fully understood, a model that incorporates thermal noise in an arbiter must be developed. Such a model has been reported in [26]. This model suggests that the sampling offset of an arbiter is not a fixed number, but should instead be treated as a random variable that changes with time. The preceding implies that the sampling offset of an arbiter at a particular instant in time can only be described as having a certain probability of being a particular value. This "instantaneous" sampling offset is denoted as  $t_{iso}$ .

#### 3.1.1 A Model of Thermal Noise in an Arbiter

An ideal arbiter is assumed to have a deterministic output, i.e., the arbiter's output can be predicted exactly if its input is known. Therefore, a given  $T_d$  will produce a consistent output from an ideal arbiter. However, as discussed in [23, 27, 28], arbiters implemented using CMOS circuit elements are not ideal, and therefore do not behave deterministically. For example, thermal noise generated in the circuit elements of an arbiter can induce nondeterministic behaviour. A model which illustrates the impact of thermal noise in an arbiter has been developed in [29] and is illustrated in Figure 3.1.

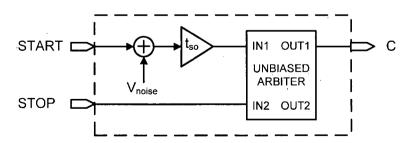

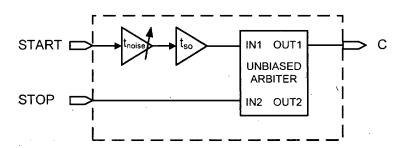

Figure 3.1: Voltage domain model of thermal noise in a biased arbiter.

$V_{noise}$  is a source of noise in the voltage domain, and is the result of thermal noise within the arbiter's circuit elements. This noise is assumed to be white Gaussian noise, with a standard deviation of  $\sigma_v$  and a mean of zero. However, a time domain model of thermal noise in an arbiter is more useful for time interval measurement purposes, since with such a model it is possible to account for the impact of thermal noise in the time domain. A time domain model has been developed in [23, 26], and is illustrated in Figure 3.2.

Figure 3.2: Time domain model of thermal noise in a biased arbiter.

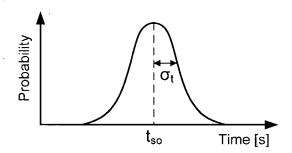

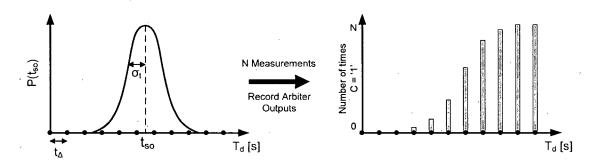

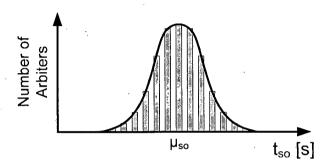

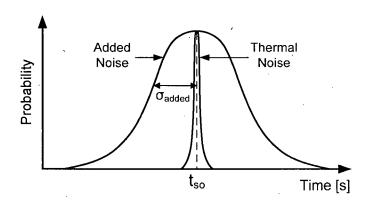

With the time domain model,  $V_{noise}$  has been replaced with  $t_{noise}$ , which functions as a variable delay element. A linear relationship between  $V_{noise}$  and  $t_{noise}$  is assumed in [23, 26], which allows for  $t_{noise}$  to be described by a Gaussian probability density function (PDF), with a standard deviation of  $\sigma_t$  and a mean of zero. Therefore, the time domain model of thermal noise in an arbiter states that the sampling offset of an arbiter is not a single number, but rather a distribution of numbers that can be described with a Gaussian PDF. The mean of this distribution is  $t_{so}$  and the standard deviation is  $\sigma_t$ . The sampling offset of an arbiter according to the time domain model of thermal noise in a biased arbiter is depicted in Figure 3.3.

Figure 3.3: PDF of the sampling offset of a biased arbiter taking into account thermal noise.

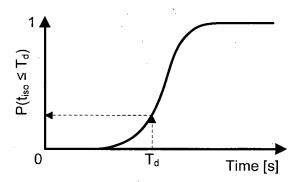

If the Gaussian PDF shown in Figure 3.3 is integrated over time, the Gaussian cumulative density function (CDF) is produced. This is a useful function since it specifies the probability with which  $t_{iso}$  is less than or equal to a specific temporal value, as shown in Figure 3.4, where the temporal value of interest is  $T_d$ .

Figure 3.4: Gaussian CDF.

Therefore, according to the time domain model of thermal noise in an arbiter, the probability that a given  $T_d$  is greater than or equal to the sampling offset of an arbiter is given by the Gaussian CDF:

$$P(C=1) = P(t_{so} \le T_d) = \frac{1}{2} \left[ 1 + erf\left(\frac{T_d - t_{so}}{\sigma_t \sqrt{2}}\right) \right]$$

(3.1)

where erf(x) is the "error function", encountered when integrating a normalized Gaussian function [23, 30].

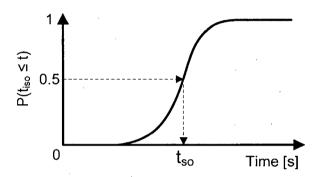

It is interesting to note that the mean sampling offset of an arbiter,  $t_{so}$ , can be found from either the PDF or the CDF of the arbiter's sampling offset. Using the PDF of the arbiter's sampling offset,  $t_{so}$  can be calculated by finding the mean of the distribution. The CDF of the arbiter's sampling offset can be used to find  $t_{so}$  by estimating the value of t that satisfies  $P(t_{iso} \le t) = 0.5$ , as illustrated in Figure 3.5.

Figure 3.5: Calculation of  $t_{so}$  from the CDF of the sampling offset of a non-ideal arbiter.

Of course, if both  $t_{so}$  and  $\sigma_t$  are known, then the PDF and the CDF of the arbiter's sampling offset are easily reproduced.

#### 3.1.2 Non-Ideal Arbiters and Time Interval Measurement

An interesting observation concerning the sensitivity of an arbiter to time intervals near  $t_{so}$  can be explained with the use of Figure 3.6. The aforementioned figure depicts the response of a symmetric CMOS arbiter with thermal noise to various time intervals. However, the x-axis in this figure has been altered to emphasize the extent to which the arbiter's output can vary with respect to the standard deviation of the thermal noise.

Figure 3.6: Sensitivity of the output of an arbiter to  $\sigma_t$ .

From Figure 3.6 it can be seen that the output of an arbiter exhibits a strong sensitivity to time intervals near the arbiter's mean sampling offset,  $t_{so}$ . In fact, a time interval equal to  $t_{so}$  -  $3\sigma_t$  almost always elicits a different response from the arbiter than one equal to  $t_{so}$  +  $3\sigma_t$ . Therefore, the sensitivity of such an arbiter is highly dependent upon the standard deviation of the thermal noise,  $\sigma_t$ . A test chip consisting of a 64-bit SOTDC has been fabricated in a 0.35 µm CMOS, and is described in [23]. Measurements from this test chip report a  $\sigma_t$  of 0.35 picoseconds. This number suggests that a symmetric CMOS arbiter is suitable for time interval measurement when picosecond accuracy is required.

### 3.2 Direct Calibration Technique

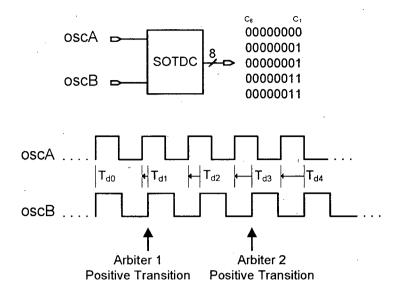

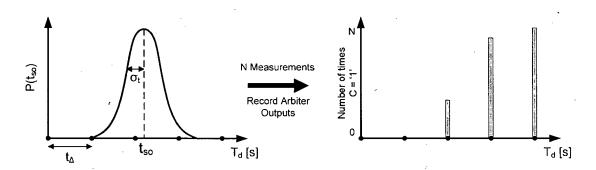

One very intuitive method to calibrate a sampling offset based flash TDC is to input a sequence of increasing time intervals ( $T_d$ s) into the SOTDC, beginning with a known time interval. Each  $T_d$  should differ from its predecessor by a constant amount of time, denoted as  $t_d$ . The instantaneous sampling offset of each arbiter can then be estimated using the value of the first  $T_d$  to produce a positive transition at the arbiter's output. The calibration of an 8-bit SOTDC is illustrated in Figure 3.7. In this figure, two oscillators of slightly different frequency, denoted as oscA and oscB, generate the sequence of  $T_d$ s.

Figure 3.7: Direct SOTDC calibration technique.

The SOTDC shown in Figure 3.7 produces an 8-bit codeword for each  $T_d$ , and this codeword is generated from the concatenation of the arbiter outputs,  $C_8 - C_1$ . Normally the arbiters are positioned in order of smallest  $t_{so}$  to largest. Under such a scenario, if  $\sigma_t$  is much less than the difference in the sampling offsets of adjacent arbiters, then a thermometer code can be expected at the SOTDC output. As previously mentioned, the instantaneous sampling offset of an arbiter within the SOTDC can be estimated using the first  $T_d$  from the sequence of time intervals to produce a positive transition at the arbiter's output, as shown in Figure 3.8.

Figure 3.8: Response of an arbiter to a sequence of increasing time intervals.

Mathematically, the  $t_{iso}$  of an arbiter can be bound with the following equation:

$$T_{d(i-1)} < t_{iso} \le T_{d(i)} \tag{3.2}$$

where  $T_{d(i)}$  indicates the first  $T_d$  to produce a positive transition at the arbiter's output, and  $T_{d(i-1)}$  indicates its predecessor. This equation can be rewritten as follows:

$$T_{d(i)} - t_{\Delta} < t_{iso} \le T_{d(i)} \tag{3.3}$$

Therefore, a reasonable estimate of  $t_{iso}$  is:

$$t_{iso} = T_{d(i)} - t_{\Delta}/2 \tag{3.4}$$

The error in this estimate of  $t_{iso}$  is bound by  $\pm t \sqrt{2}$ .

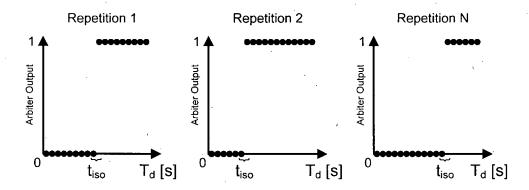

While it is useful to know  $t_{iso}$ , the real objective of any SOTDC calibration technique is to determine the mean sampling offset of an arbiter,  $t_{so}$ . Therefore, repeating the process depicted in Figure 3.7 multiple times may yield different yet useful results, as illustrated in Figure 3.9.

Figure 3.9: Response of an arbiter to several repetitions of a sequence of increasing  $T_d$ s.

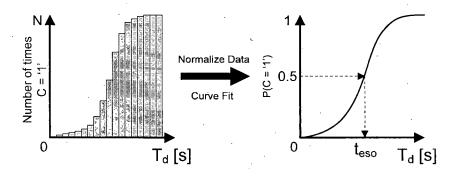

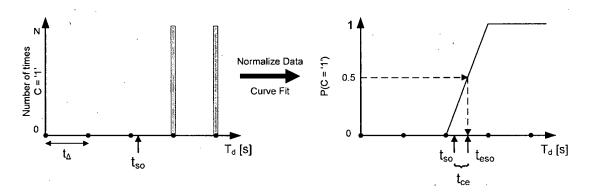

A histogram of an arbiter's response to N repetitions of a sequence of  $T_d$ s can be plotted by summing the number of times the arbiter's output (C) is a logic '1' for each  $T_d$ , as shown in Figure 3.10. Since the variation in  $t_{iso}$  follows a Gaussian PDF, the histogram has

the shape of a Gaussian CDF, assuming a sufficient number of repetitions have been performed. Now, if the histogram data is normalized and an appropriate curve fitting function is used, such as a cubic spline function, a Gaussian CDF may be produced. From this CDF the mean sampling offset of the arbiter ( $t_{so}$ ) can be determined. This is accomplished by finding the point on the CDF curve for which the arbiter's output is a logic '1' exactly half the time. The temporal value that corresponds to this point is the estimated mean sampling offset of the arbiter, or  $t_{eso}$ .

Figure 3.10: Histogram and CDF of the output of an arbiter.

In order to produce an accurate Gaussian CDF from an arbiter's response to a sequence of increasing time intervals,  $t_{\Delta}$  needs to be chosen carefully, as will be discussed in the following section.

#### 3.2.1 Analysis

As noted earlier, experimental results from a 64-bit SOTDC fabricated in a 0.35  $\mu$ m CMOS process indicate that the standard deviation of the thermal noise in an arbiter is approximately 0.35 picoseconds [23]. This result places an important bound on the size of  $t_{\Delta}$ . If the chosen  $t_{\Delta}$  is approximately equal to or less than  $\sigma_t$ , then the histogram and the resulting CDF constructed from the data collected during arbiter offset calibration will closely resemble those shown in Figure 3.10. To further explain, Figure 3.11 may be of use. In this figure, the time intervals used during calibration are plotted on the x-axis of the arbiter

sampling offset PDF. From this PDF a histogram of the arbiter's output for each  $T_d$  input is drawn. This histogram is drawn with the assumption that the number of repetitions (N) is large enough to ensure that the collection of arbiter instantaneous sampling offsets produces an arbiter sampling offset PDF that is nearly Gaussian.

Figure 3.11: Histogram of the output of an arbiter when  $t_{\Delta} \le \sigma_t$ .

The key observation to be made here is that since  $t_{\Delta}$  is approximately of the same magnitude as  $\sigma_t$ , a histogram which closely resembles a Gaussian CDF can be drawn, and curve fitting of this histogram to find the arbiter's sampling offset, as shown in Figure 3:10, can be done with reasonable accuracy.

However, if the chosen  $t_{\Delta}$  is too large, then the histogram may resemble the one shown in Figure 3.12.

Figure 3.12: Histogram of the output of an arbiter when  $t_{\Delta} > \sigma_{t}$ .

It can be observed from Figure 3.12 that there exists only a small number of useful data points to which a curve can be fitted. Applying a curve fitting function to a small number of data points inevitably leads to an error in the estimation of  $t_{so}$  that is much larger than would otherwise be obtainable if  $t_{\Delta}$  had been properly chosen. The error in the estimation of  $t_{so}$ , known as the calibration error, is defined as:

$$t_{ce} = t_{eso} - t_{so} \tag{3.5}$$

As part of this thesis, a quantitative analysis of the relationship between  $t_{\Delta}$  and  $t_{ce}$  has been performed using a software model of the direct calibration technique, one that accounts for thermal noise in an arbiter. This model has been constructed using Matlab, and accepts  $t_{\Delta}$  and  $\sigma_t$  as parameters, in addition to the  $t_{so}$  of each arbiter in the array. Using this information, the model constructs a sequence of  $T_{dS}$  that are applied to the inputs of the array of arbiters. It is also possible to specify the number of repetitions (N) of the sequence of  $T_{dS}$  via an additional parameter. The output of this model is the root-mean-square (RMS) value of  $t_{ce}$  for the calibrated array of arbiters, estimated using a 6-th order polynomial fit of the arbiter output histograms.

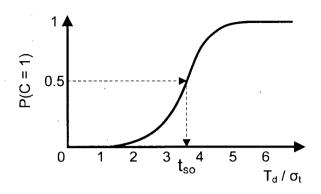

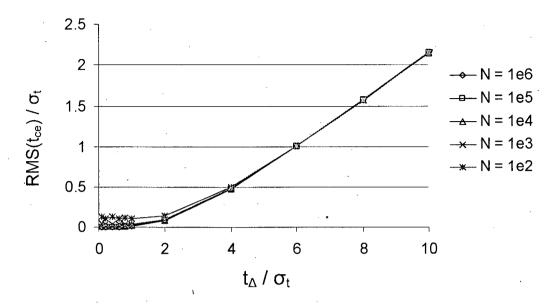

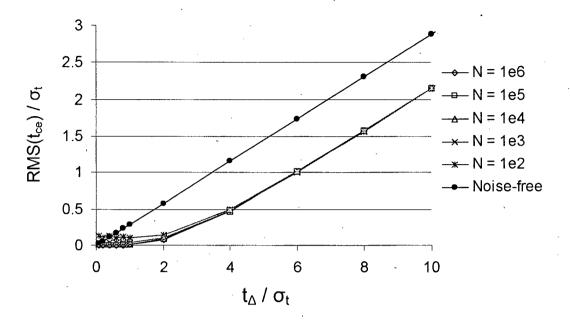

In order to ascertain the capabilities of the direct calibration technique over a range of  $t_{\Delta}$  values, several simulations were performed using the aforementioned model. In each case the array was specified to be 100 arbiters long, and N was varied incrementally in powers of 10, beginning at 100 and ending at 1 000 000. In order to keep the results independent of  $\sigma_t$ ,  $t_{\Delta}$  and the RMS value of  $t_{ce}$  are expressed in terms of  $\sigma_t$ . The results of eleven simulations for five different values of N are shown in Figure 3.13.

Figure 3.13: RMS  $t_{ce}/\sigma_t$  vs.  $t_A/\sigma_t$  using the direct calibration technique.

From Figure 3.13 it can be observed that if  $t_{\Delta} \leq 6\sigma_t$ , then the RMS value of  $t_{ce}$  is approximately bounded by  $\sigma_t$ , for any value of N. However, as  $t_{\Delta}$  continues to increase, so does the RMS value of  $t_{ce}$ . In fact, for  $t_{\Delta} \geq 4\sigma_t$ , the RMS value of  $t_{ce}$  increases linearly with  $t_{\Delta}$ . By the time  $t_{\Delta}$  reaches  $10\sigma_t$ , the RMS value of  $t_{ce}$  has already surpassed  $2\sigma_t$ . For an SOTDC with a resolution of 1 ps, i.e., the sampling offset of each arbiter differs from that of its neighbours by 1 ps, an RMS  $t_{ce}$  equal to  $\sigma_t$  may be tolerable, assuming  $\sigma_t \approx 0.35$  ps. However, an RMS  $t_{ce}$  equal to  $2\sigma_t$  (0.7 ps) may not be tolerable. Therefore, if such an SOTDC is calibrated using the direct calibration technique, the required  $t_{\Delta}$  may be less than 3.5 ps. This requirement may not be practical, as the accurate generation of known time intervals with picosecond temporal resolution is very difficult to achieve on-chip.

One intriguing question which to this point has remained unanswered is the quantitative effect of thermal noise on the accuracy of the arbiter sampling offset estimations obtained using the direct calibration technique. This question can be answered by comparing the RMS  $t_{ce}$  from Figure 3.13 with the theoretical RMS  $t_{ce}$  of a noise-free arbiter that is calibrated using the direct calibration technique. To calculate the theoretical RMS  $t_{ce}$  of the

direct calibration technique, the standard RMS formula for a continuous distribution, as shown in Equation (3.6) [31], may be used.

$$RMS(t_{ce}) = \sqrt{\frac{\int P(t_{ce})t_{ce}^2 dt_{ce}}{\int P(t_{ce})dt_{ce}}}$$

(3.6)

To solve Equation (3.6), the limits of integration must be determined. In order to determine the limits of integration, the curve fitting procedure used in the direct calibration technique to estimate the  $t_{so}$  of a noise-free arbiter must be understood.

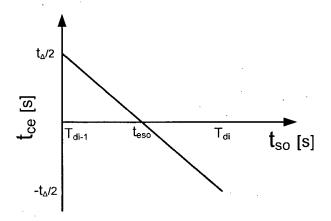

The response of a noise-free arbiter to a sequence of  $T_d$ s is shown in Figure 3.14. As shown in this figure, the histogram of this response resembles a discrete-time step function. Since there are only two useful data points to which a curve can be fitted, the most sensible approach is to linearly interpolate between the two points in order to construct the CDF of the arbiter's sampling offset and approximate  $t_{so}$ .

Figure 3.14: Histogram and CDF of the output of a noise-free arbiter.

The error in this approximation,  $t_{ce}$ , can be described mathematically by recognizing that the sampling offset of a noise free arbiter is estimated as:

$$t_{eso} = (T_{d(i)} + T_{d(i-1)})/2 = T_{d(i)} - t / 2$$

(3.7)

where  $T_{d(i)}$  indicates the first  $T_d$  to produce a positive transition at the arbiter's output,  $T_{d(i-1)}$  indicates its predecessor, and  $t_{\Delta} = T_{d(i)} - T_{d(i-1)}$ . By noting that  $t_{so}$  can fall anywhere in the range  $T_{d(i-1)}$  to  $T_{d(i)}$ , the calibration error is bound by the following equation:

$$-t\sqrt{2} < t_{ce} \le t\sqrt{2} \tag{3.8}$$

This relationship is illustrated in Figure 3.15, where the actual sampling offset of an arbiter is plotted versus its associated calibration error.

Figure 3.15:  $t_{so}$  versus  $t_{ce}$  for a noise-free arbiter using direct calibration.

Now that the limits of integration have been found, the probability density function of  $t_{ce}$  must be determined before integration can be performed. Since the goal of this exercise is to find the RMS calibration error of a noise-free arbiter for a given  $t_{\Delta}$ , the arbiter's sampling offset must fall in the range  $T_{d(i-1)}$  to  $T_{d(i)}$  with equal probability, otherwise the results would be dependent on the actual value of the arbiter's sampling offset. In addition, the integral of this probability over the range  $-t_{\Delta}/2$  to  $t_{\Delta}/2$  must be equal to 1, since the arbiter has a fixed sampling offset that is greater than  $T_{d(i-1)}$  but less than  $T_{d(i)}$ . These two conditions stipulate that for  $-t_{\Delta}/2 < t_{ce} \le t_{\Delta}/2$ ,  $P(t_{ce}) = 1/t_{\Delta}$ , as shown in Figure 3.16.

Figure 3.16:  $t_{ce}$  probability density function.

With this knowledge, the theoretical RMS  $t_{ce}$  of a noise-free arbiter calibrated using the direct calibration technique can be calculated as shown in Equation (3.9).

$$RMS(t_{ce}) = \sqrt{\frac{\int P(t_{ce})t_{ce}^{2}dt_{ce}}{\int P(t_{ce})dt_{ce}}} = \sqrt{\frac{\frac{t_{\Delta}}{2}}{\int_{-\frac{t_{\Delta}}{2}}^{2}}P(t_{ce})t_{ce}^{2}dt_{ce}} = \frac{t_{\Delta}}{2\sqrt{3}}$$

(3.9)

Equation (3.9) is plotted in Figure 3.17 along side the RMS calibration error obtained using the Matlab model described earlier, which incorporates the effects of thermal noise in an arbiter. It should be pointed out that the results of such a model can be highly dependent on the distribution of the arbiter sampling offsets. For example, if the sampling offsets of an array of arbiters fall in a very narrow range, one that is much smaller than the minimum  $t_{\Delta}$  used during simulation, then the RMS calibration error may appear to be independent of  $\sigma_t$ . This result is intuitively wrong since the presence of thermal noise in an arbiter should result in a Gaussian-like CDF, from which a more accurate estimation of  $t_{so}$  can be made. To remove this dependency,  $t_{\Delta}$  was fixed during simulation and  $\sigma_t$  was varied instead. The sampling offsets of the array of 100 arbiters were then assigned fixed values uniformly distributed over the range  $T_{d(t-1)}$  to  $T_{d(t)}$ . This made for a fair comparison with the noise-free scenario.

Figure 3.17: RMS  $t_{ce}/\sigma_t$  vs.  $t_d/\sigma_t$  using the direct calibration technique.

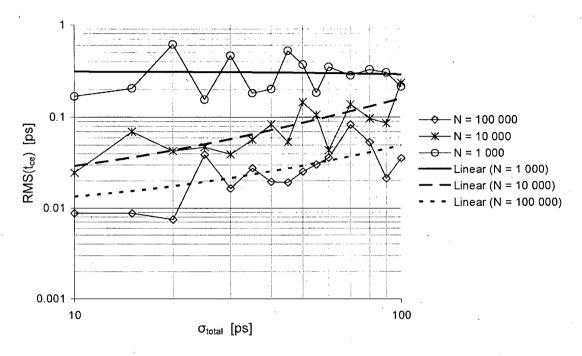

Inspection of Figure 3.17 reveals that for  $2 \le t_A/\sigma_t \le 10$ , the presence of thermal noise in an arbiter significantly increases the accuracy of the arbiter sampling offset estimations obtained using the direct calibration technique. This result is expected since the presence of thermal noise in an arbiter contributes to a Gaussian-like CDF of the arbiter's sampling offset, from which a reasonably accurate estimation of  $t_{so}$  can be made. This is in contrast to the ramp-like CDF of a noise-free arbiter, for which the best approximation is a straight line interpolation, which has a significantly larger RMS error.

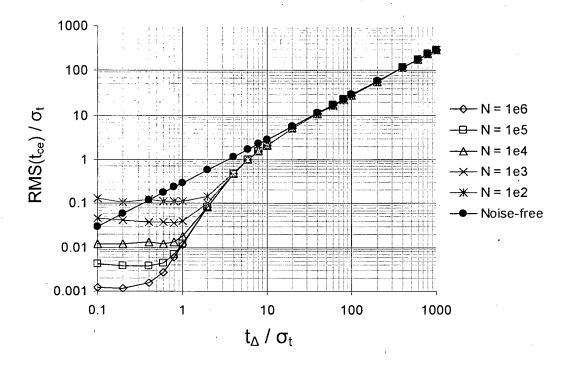

Inspection of Figure 3.17 also reveals that the gain in accuracy from the presence of thermal noise in an arbiter diminishes as  $t_A/\sigma_t$  is decreased from 2. Further insight in to this result can be acquired if Figure 3.17 is redrawn with logarithmic x and y axes, as shown in Figure 3.18.

Figure 3.18: Log-log plot of RMS  $t_{ce}/\sigma_t$  vs.  $t_d/\sigma_t$  using the direct calibration technique.

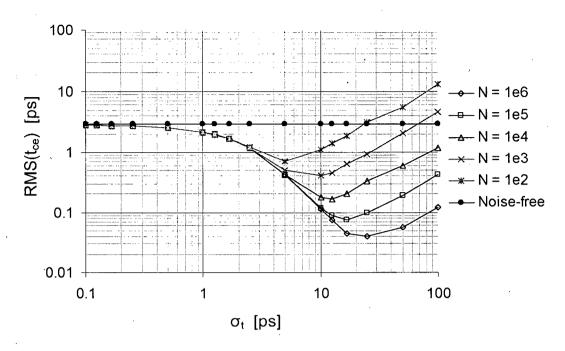

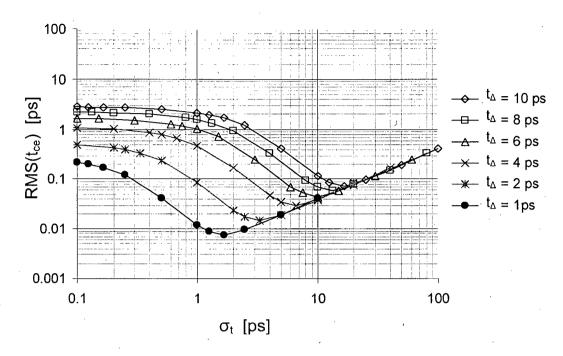

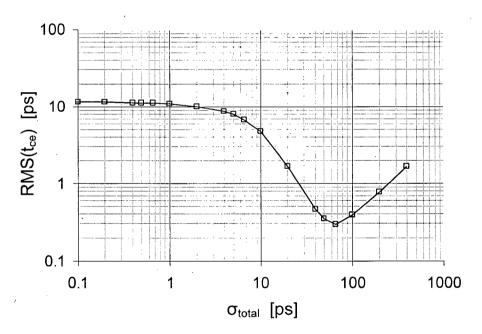

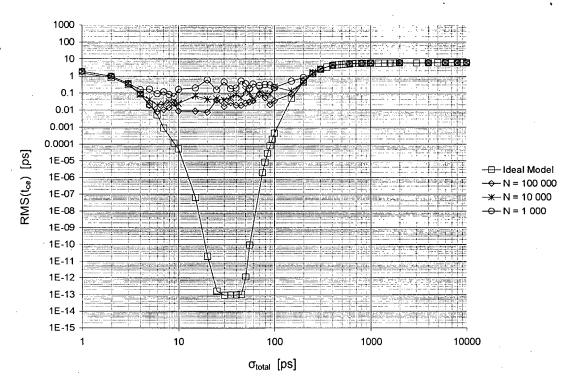

From Figure 3.18, it can be observed that when  $t_A/\sigma_t$  is decreased, the RMS value of  $t_{ce}/\sigma_t$  reaches a saturation point somewhere in the range  $0.2 \le t_A/\sigma_t \le 1$ , depending upon the number of repetitions performed. This implies that the actual RMS value of  $t_{ce}$  increases as one moves deeper into the saturation region, since  $\sigma_t$  increases as one moves closer to the y-axis, and the ratio of  $t_{ce}$  to  $\sigma_t$  is constant. By inspection of Figure 3.18, the rate at which the RMS value of  $t_{ce}$  increases as  $t_A/\sigma_t$  moves deeper into the saturation region is unclear. In order to clarify this, actual values of  $t_{ce}$  can be obtained if  $t_A$  is fixed to a particular value and  $\sigma_t$  varied. For example, the rate at which the RMS value of  $t_{ce}$  increases as  $t_A/\sigma_t$  decreases can be estimated from Figure 3.19, where  $t_A$  has been fixed at 10 ps and  $\sigma_t$  has been varied. The data required to plot Figure 3.19 is actually a special case of data displayed in Figure 3.18. For this reason Figure 3.18 is a more useful plot in a general sense, but not as convenient for a specific scenario.

Figure 3.19: Log-log plot of RMS  $t_{ce}$  vs.  $\sigma_t$  when  $t_{\Delta} = 10$  ps, using the direct calibration technique.

Through inspection of Figure 3.19 it is apparent that an optimal ratio between  $t_{\Delta}$  and  $\sigma_t$  exists, and is dependent upon the value of N. This ratio has been found to hold true for any value of  $t_{\Delta}$ . Therefore, by determining the value of  $\sigma_t$  that minimizes  $t_{ce}$  for each of the five curves displayed in Figure 3.19, it is possible to determine the optimal ratio of  $t_{\Delta}$  to  $\sigma_t$  given the desired number of repetitions. The optimal ratios for five different values of N are summarized in Table 3.1.

Table 3.1: Optimal ratio of  $t_{\Delta}$  to  $\sigma_t$  given the number of repetitions performed.

| N   | $t_{\Delta}/\sigma_{t}$ |  |

|-----|-------------------------|--|

| 1e2 | 2                       |  |

| 1e3 | 1                       |  |

| le4 | 0.8                     |  |

| 1e5 | 0.6                     |  |

| le6 | 0.4                     |  |

This information can be used in the selection of  $t_{\Delta}$  for the direct calibration technique. For example, if  $\sigma_t$  is equal to 0.35 ps [23] and N = 1e5, the value of  $t_{\Delta}$  which would produce the lowest  $t_{ce}$  is 0.35 ps x 0.6 = 0.21 ps. Of course, the accurate generation of time intervals with such a temporal resolution is a very difficult task.

With this knowledge in hand, it is easier to explain why the gain in accuracy from the presence of thermal noise in an arbiter diminishes as  $t_A/\sigma_t$  is decreased from approximately 2. Through inspection of Figure 3.19, it can be seen that the farther one deviates from the optimal  $t_A/\sigma_t$  ratio, the larger the calibration error. For example, if  $\sigma_t$  is much smaller than its optimal value for a given  $t_A$ , hence much smaller than  $t_A$ , the difference between  $t_{ce}$  in this case and that of a noiseless arbiter calibrated using the same  $t_A$  becomes increasingly diminished. This result makes intuitive sense, since as  $\sigma_t$  becomes very small with respect to  $t_A$ , the CDF of the arbiter's sampling offset becomes less Gaussian-like and more ramp-like in appearance as the variation in the arbiter's sampling offset becomes less significant. Similarly, if  $\sigma_t$  is much larger than its optimal value for a given  $t_A$ , hence much larger than  $t_A$ ,  $t_{ce}$  once again exceeds its minimum value. In this case the increased error can be attributed to the incorrect use of a polynomial curve fitting function on the relatively linear histogram that is produced.

#### 3.2.2 Conclusions

In theory, the direct calibration technique can produce very accurate estimations of  $t_{so}$  given a sufficiently small  $t_{\Delta}$ . In fact, the accuracy of this technique is limited only by  $t_{\Delta}$ , which may be determined by the frequency difference of two oscillators. However in practice, this calibration technique has some very serious flaws. For example, any type of oscillator will have some amount of phase noise, and therefore will not have a perfectly stable frequency [32, 33]. Any instability in the frequency of either of the two oscillators can result in an increased error in the estimate of  $t_{so}$ . In fact, it may not even be possible to place a bound on the error as the amount of phase noise in either oscillator may be unknown.

Another problem with this calibration technique concerns the requirement that the sequence of  $T_{a}$ s must begin with a known  $T_{d}$ . One way to accomplish this may involve the use of an arbiter with a known sampling offset to detect alignment between the rising edge transitions of the two oscillators. However, as discussed in [23], the sampling offset of a reasonably sized arbiter may vary from its intended value by as much as 25 picoseconds. An error of 25 picoseconds in the initial  $T_{d}$  will propagate to the estimate of  $t_{so}$  for each arbiter. One way to alleviate this problem is to oversize the transistors in the arbiter that is used for alignment. This will help to reduce the arbiter's sensitivity to process variations. However, even if an arbiter with a known sampling offset is used to detect alignment between the rising edge transitions of the oscillators, there is still a quantization error in the edge alignment of at most  $t_{d}$  seconds due to the finite difference in the frequencies of the two oscillators. Also, any mismatch in the START and STOP signal paths will introduce some skew between them, and this skew will alter the sampling offset of the alignment arbiter by an unknown amount, adding another error to the estimate of  $t_{so}$ .

While the direct calibration technique is conceptually rather simple, it is not used in practice due to its many shortcomings; the most severe being the restriction placed on  $t_{\Delta}$ . The accurate generation of known time intervals with picosecond resolution is very difficult to achieve on-chip, and therefore renders this calibration technique ineffective for embedded applications.

### 3.3 Relative Offset Calibration Technique

A technique capable of determining the relative sampling offsets of an array of arbiters is presented in [23, 25]. This technique analyzes the "bubbles" in the output codeword of an SOTDC. A codeword is said to be "bubble-free" if there is at most one location in the codeword where adjacent bits differ. For example, an 8-bit "bubble-free" codeword may look like the following: "00001111". A codeword is said to contain a "bubble" if there are three locations where adjacent bits differ, as shown in the following codeword: "00101111".

If there are more than three locations in a codeword where adjacent bits differ, then the codeword is said to contain more than one "bubble".

"Bubbles" may appear in an SOTDC codeword when its resolution is comparable to  $\sigma_l$ . For example, if arbiters  $A_l$  and  $A_2$  have sampling offsets of 100 ps and 101 ps, respectively, and a 100.5 ps time interval is applied to the inputs of both arbiters, the most probable outcome is that  $A_l$  will output a logic '1' and  $A_2$  will output a logic '0'. However, there is a significant probability of the reverse scenario occurring, i.e.,  $A_l$  outputs a logic '0' and  $A_2$  output a logic '1'. If this experiment is performed a sufficient number of times, this counter intuitive outcome is inevitable, and will occur with a certain probability. The ratio of these two probabilities can be used to determine the difference in the sampling offsets of arbiters  $A_l$  and  $A_2$ . For example, if the probability of the more likely outcome is denoted as  $P_{AlA2}(10)$ , i.e., the output of  $A_l$  is a logic '1' and the output of  $A_2$  is a logic '0', and the probabilities,  $r = P_{AlA2}(01)/P_{AlA2}(10)$ , depends only on  $\delta$ , which is the ratio of these two probabilities,  $r = P_{AlA2}(01)/P_{AlA2}(10)$ , depends only on  $\delta$ , which is the ratio of the difference in the sampling offsets of the two arbiters to  $2\sigma_l$ , i.e.,  $\delta = (t_{sad2} - t_{sad1})/2\sigma_l$ . The exact relationship between these two ratios is derived in [23], where the following equation is produced:

$$r = \frac{P_{A1A2}(01)}{P_{A1A2}(10)} = \frac{1 + \sqrt{\pi}\delta(erfcx(-\delta))}{1 - \sqrt{\pi}\delta(erfcx(\delta))}$$

(3.10)

The "erfcx" terms in the right hand side of the preceding equation are instances of the scaled complementary error function.