### STUDY OF OSI PROTOCOL PROCESSING ENGINES

$\mathbf{B}\mathbf{y}$

Leonard Yasuhiko Takeuchi

B. A. Sc., University of British Columbia, Canada, 1989

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

MASTERS OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

(DEPARTMENT OF ELECTRICAL ENGINEERING)

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

July 1991

© Leonard Yasuhiko Takeuchi, 1991

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of ELECTRICAL ENGINEERING

The University of British Columbia Vancouver, Canada

Date October 10,1991

#### Abstract

The increases in communication bandwidth provided by fiber optics and high-speed switching technologies have shifted the limiting factor in data throughput from the communication link to the communication processing. The communication processing for open systems interconnection (OSI) in particular is quite heavy due to the inclusion of data transfer syntax conversion in order to assure interoperability between different machine types. In this thesis report, two multiprocessing architectures are considered as protocol processing engines for OSI communications.

The conventional approach is to have the host computer perform the protocol processing especially for the higher layers. However, the protocol processing burden at communication rates of hundreds or even thousands of million bits per second places such a heavy processing burden on the host that this becomes undesirable. The protocol processing engines act as front-end systems performing most of the OSI protocol processing, including the transfer syntax conversion, on behalf of the host. A multiprocessor approach was selected because the required amount of processing power can be supplied using lower processor technology than for an uniprocessor approach.

The protocol engines were designed based on a processing model in which different packets are processed at the same time in different processors. The protocol engines are designed to perform the protocol processing for OSI layers 2 through 6. Results obtained from simulating the designs indicate that a processing throughput of a hundred megabit per second is achievable only for packets which contain very simple data structures.

# Table of Contents

| $\mathbf{A}$   | Abstract              |         |                                            |      |  |  |  |  |  |

|----------------|-----------------------|---------|--------------------------------------------|------|--|--|--|--|--|

| Li             | st of                 | Tables  | 5                                          | vi   |  |  |  |  |  |

| Li             | st of                 | Figure  | e <b>s</b>                                 | viii |  |  |  |  |  |

| $\mathbf{A}$   | ckno                  | wledge  | ement                                      | x    |  |  |  |  |  |

| 1 Introduction |                       |         |                                            |      |  |  |  |  |  |

| 2              | System Requirements   |         |                                            |      |  |  |  |  |  |

|                | 2.1                   | Open    | Systems Interconnection Reference Model    | 5    |  |  |  |  |  |

|                | 2.2                   | Divisio | on of Processing Responsibilities          | 7    |  |  |  |  |  |

|                | 2.3                   | Proces  | ssing Requirement                          | g    |  |  |  |  |  |

|                |                       | 2.3.1   | Data Link Layer                            | 9    |  |  |  |  |  |

|                |                       | 2.3.2   | Network Layer                              | 10   |  |  |  |  |  |

|                |                       | 2.3.3   | Transport Layer                            | 10   |  |  |  |  |  |

|                |                       | 2.3.4   | Session Layer                              | 11   |  |  |  |  |  |

|                |                       | 2.3.5   | Presentation Layer                         | 12   |  |  |  |  |  |

| 3              | System Design Options |         |                                            |      |  |  |  |  |  |

|                | 3.1                   | Proces  | ssing Approach Options                     | 13   |  |  |  |  |  |

|                |                       | 3.1.1   | Design Based on Fast Uniprocessors         | 14   |  |  |  |  |  |

|                |                       | 3 1 2   | Design Based on Custom Integrated Circuits | 14   |  |  |  |  |  |

|   |     | 3.1.3   | Design Based on Protocols for High-Speed Networks | 15 |

|---|-----|---------|---------------------------------------------------|----|

|   |     | 3.1.4   | Design Based on Parallel Processing               | 15 |

|   | 3.2 | Paralle | el Processing Options                             | 16 |

|   |     | 3.2.1   | Processor Per Protocol Layer                      | 16 |

|   |     | 3.2.2   | Processor Per Protocol Function                   | 17 |

|   |     | 3.2.3   | Processor Per Connection                          | 17 |

|   |     | 3.2.4   | Processor Per Protocol Data Unit                  | 18 |

|   | 3.3 | Archit  | ecture Options                                    | 18 |

|   | 3.4 | Design  | Selection                                         | 21 |

| 4 | Sys | tem D   | escription                                        | 22 |

|   | 4.1 | Netwo   | ork Interface                                     | 22 |

|   |     | 4.1.1   | Network Interface Architecture                    | 22 |

| , |     | 4.1.2   | Network Interface Operation                       | 28 |

|   | 4.2 | Host I  | Interface                                         | 30 |

|   |     | 4.2.1   | Host Interface Architecture                       | 31 |

|   |     | 4.2.2   | Host Interface Operation                          | 32 |

|   | 4.3 | Protoc  | col Engine Core Design 1: Mixed Memory Design     | 33 |

|   |     | 4.3.1   | Mixed Memory Architecture                         | 34 |

|   |     | 4.3.2   | System Operation                                  | 38 |

|   | 4.4 | Protoc  | col Engine Core Design 2: Shared Memory Design    | 46 |

|   |     | 4.4.1   | Shared Memory Architecture                        | 46 |

|   |     | 4.4.2   | System Operation                                  | 49 |

| 5 | Sys | tem E   | valuation and Analysis                            | 5( |

|   | 5.1 | Metho   | od for Evaluating Performance                     | 50 |

|   |     | 5.1.1   | Simulation of the Hardware Level                  | 5  |

|     |       | 5.1.2   | Simulation of the Software Level             | 53  |

|-----|-------|---------|----------------------------------------------|-----|

|     | 5.2   | Perfor  | mance Evaluation                             | 56  |

|     |       | 5.2.1   | Evaluation of the Mixed Memory Design        | 57  |

|     |       | 5.2.2   | Evaluation of the Shared Memory Design       | 84  |

|     | 5.3   | System  | n Analysis                                   | 94  |

| ٠   |       | 5.3.1   | Mixed Memory Design                          | 94  |

| •   |       | 5.3.2   | Shared Memory Design                         | 97  |

|     |       | 5.3.3   | General Problem with OSI Protocol Processing | 97  |

| 6   | Con   | clusio  | n                                            | 99  |

| Ap  | pen   | dices   |                                              | 102 |

| A   | Che   | cksum   | Unit Design                                  | 102 |

| В   | Pro   | tocol S | Statistics Sources                           | 104 |

| C   | ASI   | N.1 Sta | atistic                                      | 106 |

| D   | Sim   | ulatior | n Details                                    | 109 |

|     | D.1   | Mixed   | Memory Design                                | 109 |

|     | D.2   | Shared  | l Memory Design                              | 113 |

| Bil | bliog | graphy  |                                              | 118 |

÷.

# List of Tables

| 5.1  | The instruction counts for protocols.                                    | 55  |

|------|--------------------------------------------------------------------------|-----|

| 5.2  | Processing throughput for 1 connection                                   | 58  |

| 5.3  | Processing throughput for 2, 5, 10 and 20 connections                    | 63  |

| 5.4  | Processing throughputs with no ASN.1 processing                          | 66  |

| 5.5  | Throughputs for various ASN.1 encoding/decoding complexities             | 67  |

| 5.6  | Throughputs for various input data rates                                 | 70  |

| 5.7  | Throughput for modified version for 1 connection                         | 73  |

| 5.8  | Throughputs for various ASN.1 encoding/decoding complexities for the     |     |

|      | modified design                                                          | 77  |

| 5.9  | Throughputs for various input data rates for the modified design         | 79  |

| 5.10 | Throughputs for various input data ratios between host and network input |     |

|      | for the modified design.                                                 | 80  |

| 5.11 | Throughput for larger packet size                                        | 84  |

| 5.12 | Processing throughput for 200ns shared memory                            | 86  |

| 5.13 | Processing throughput for 160ns shared memory                            | 87  |

| 5.14 | Processing throughput for 120ns shared memory                            | 88  |

| 5.15 | Processing throughput with entire program in cache                       | 92  |

| D.1  | Parameters for the 5 MIPS configuration                                  | 110 |

| D.2  | Parameters for the 10 MIPS configuration                                 | 111 |

| D.3  | Parameters for the 15 MIPS configuration                                 | 112 |

| D.4  | Parameters for the 5 MIPS configuration                                  | 114 |

| D.5 | Parameters for the 10 MIPS configuration. | <br>115 |

|-----|-------------------------------------------|---------|

| D.6 | Parameters for the 15 MIPS configuration. | <br>116 |

# List of Figures

| 2.1  | OSI layer interaction                                                     | 6  |

|------|---------------------------------------------------------------------------|----|

| 2.2  | PDU formation in OSI                                                      | 7  |

| 2.3  | The layers processed by the protocol engine                               | 8  |

| 4.1  | General system architecture                                               | 23 |

| 4.2  | Network interface architecture                                            | 24 |

| 4.3  | Communication and buffer memory interface                                 | 26 |

| 4.4  | Host interface architecture                                               | 31 |

| 4.5  | Mixed memory architecture                                                 | 35 |

| 4.6  | Communication memory and buffer memory interfacing                        | 36 |

| 4.7  | Shared memory architecture                                                | 47 |

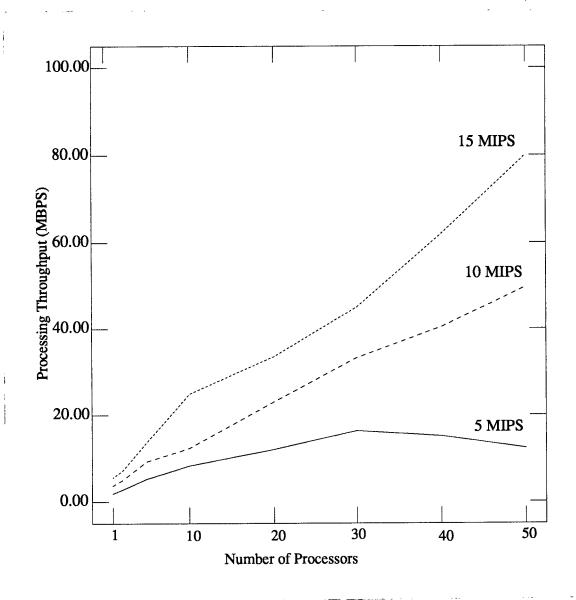

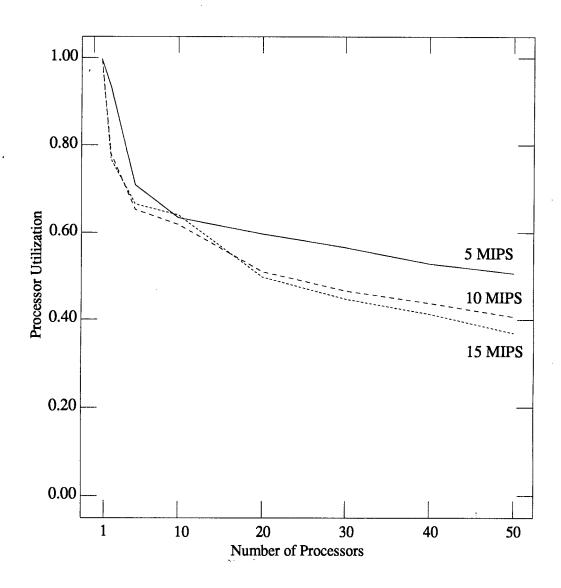

| 5.1  | Throughput vs. processors for 1 connection                                | 60 |

| 5.2  | Processor utilization vs. processor for 1 connection                      | 61 |

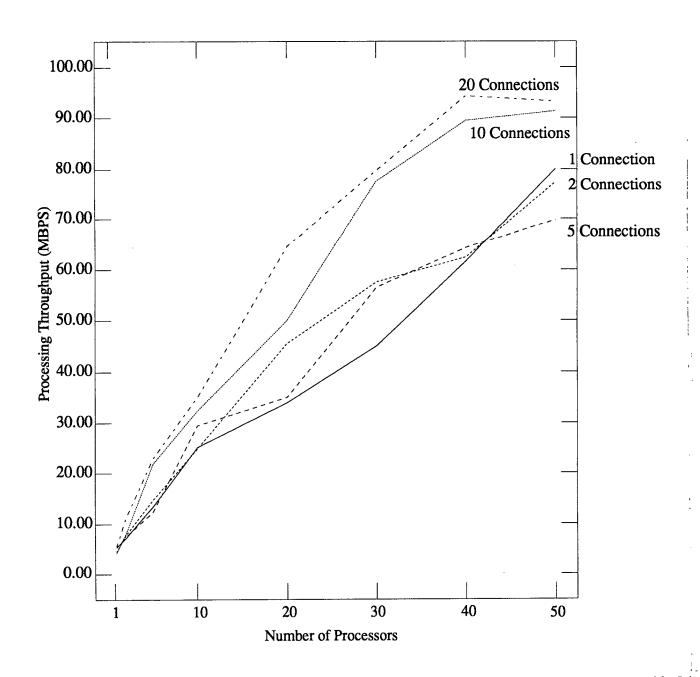

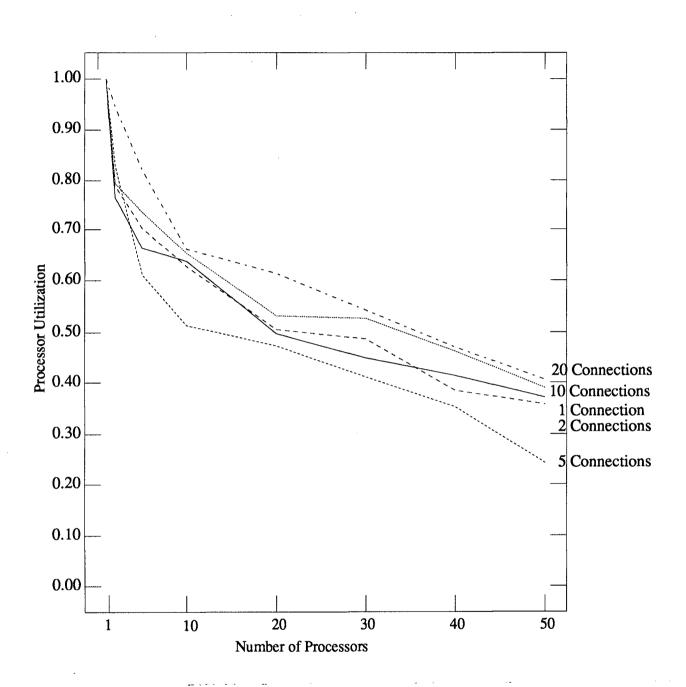

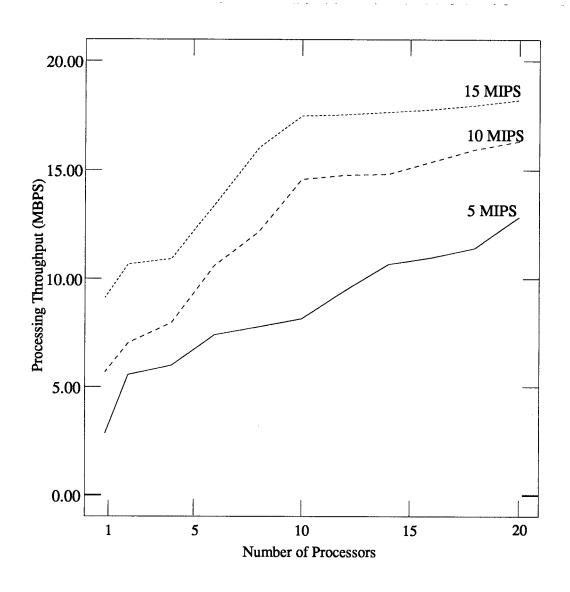

| 5.3  | Throughput vs. processors for multiple connections                        | 64 |

| 5.4  | Processor utilization vs. processors for multiple connections             | 65 |

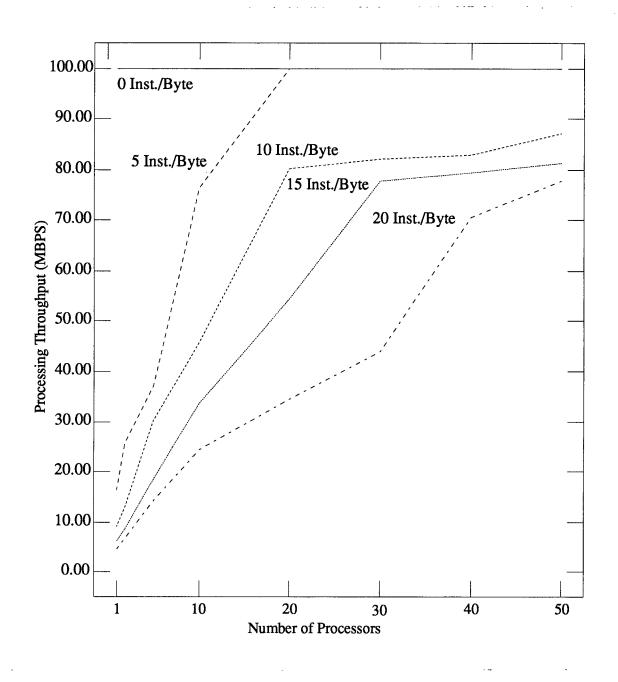

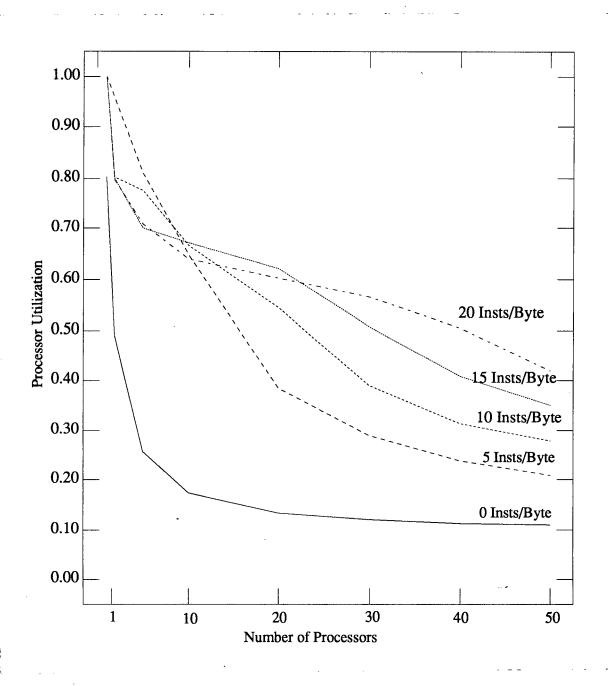

| 5.5  | Throughput for different ASN.1 encoding/decoding complexities             | 68 |

| 5.6  | Processor utilization for different ASN.1 encoding/decoding complexities. | 69 |

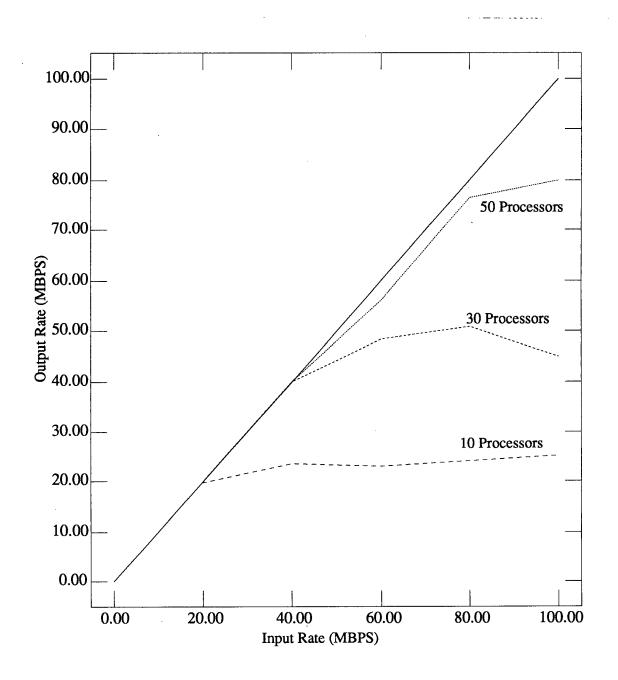

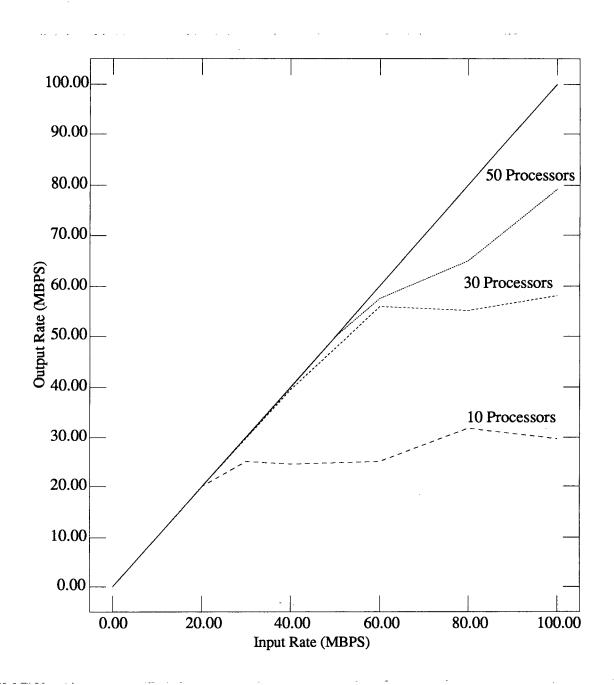

| 5.7  | Output data rate vs input data rate                                       | 71 |

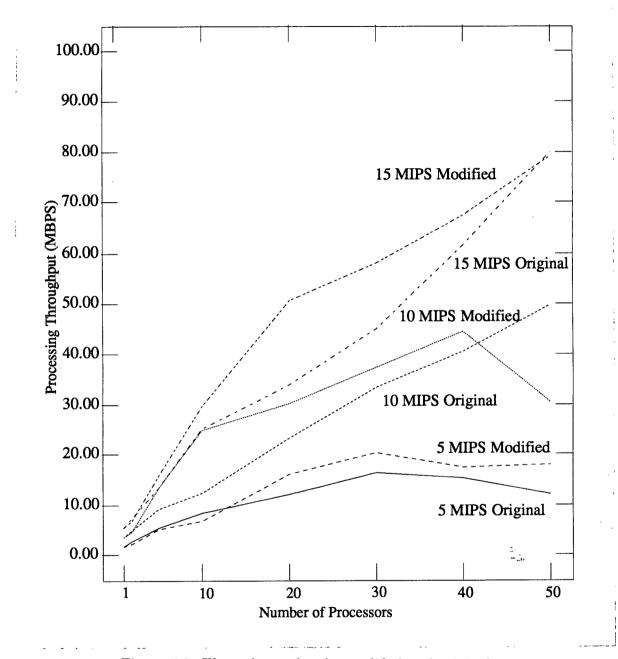

| 5.8  | Throughputs for the modified and original versions                        | 75 |

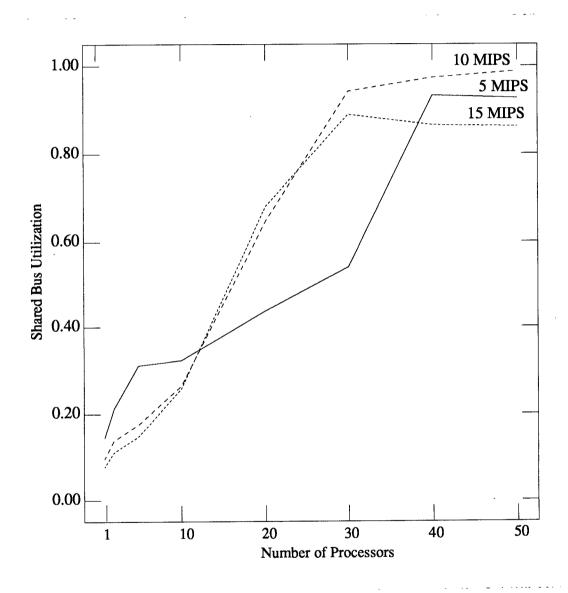

| 5.9  | The shared bus utilization for the modified version                       | 76 |

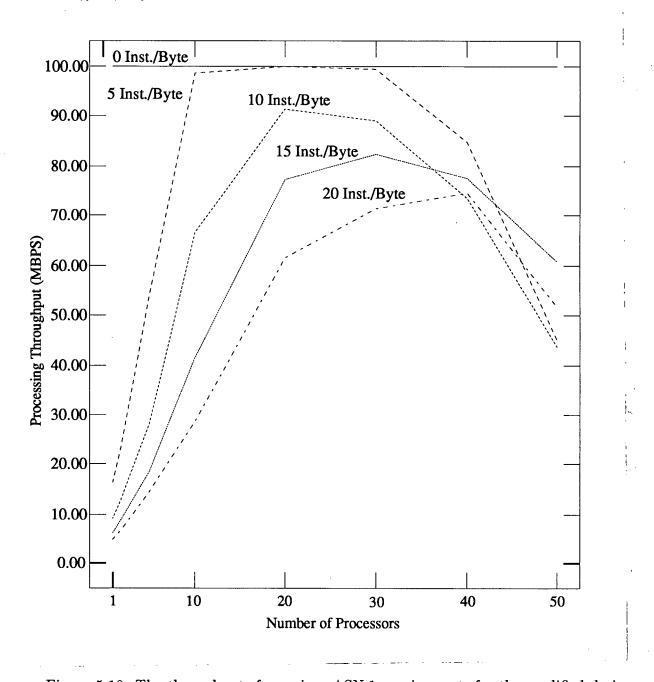

| 5.10 | The throughputs for various ASN.1 requirements for the modified design.   | 78 |

| 5.11 | The output rate versus the input rate for the modified version            | 81 |

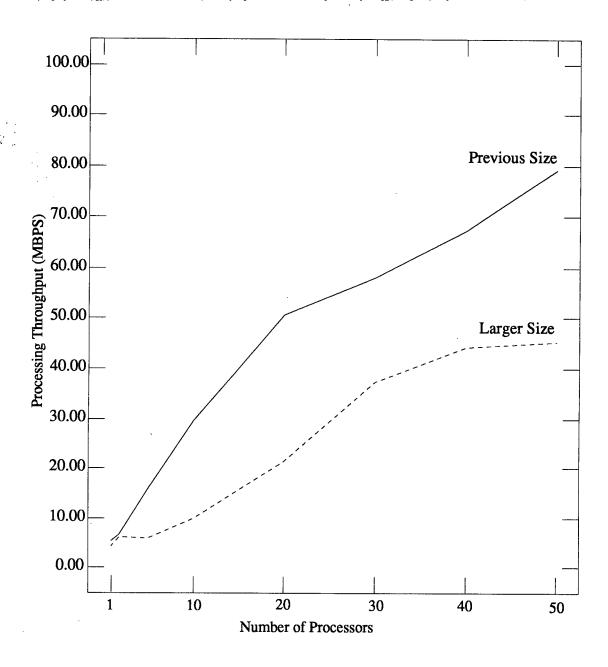

| 5.12 | The throughputs for the original packet size and larger packet size | 83  |

|------|---------------------------------------------------------------------|-----|

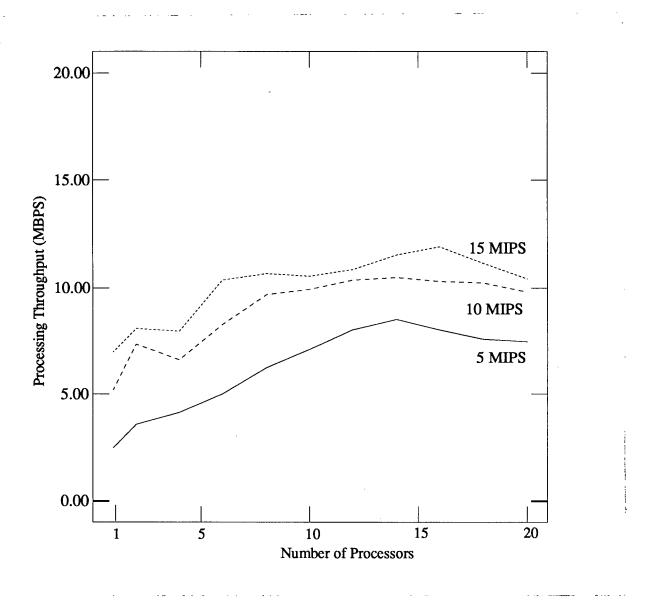

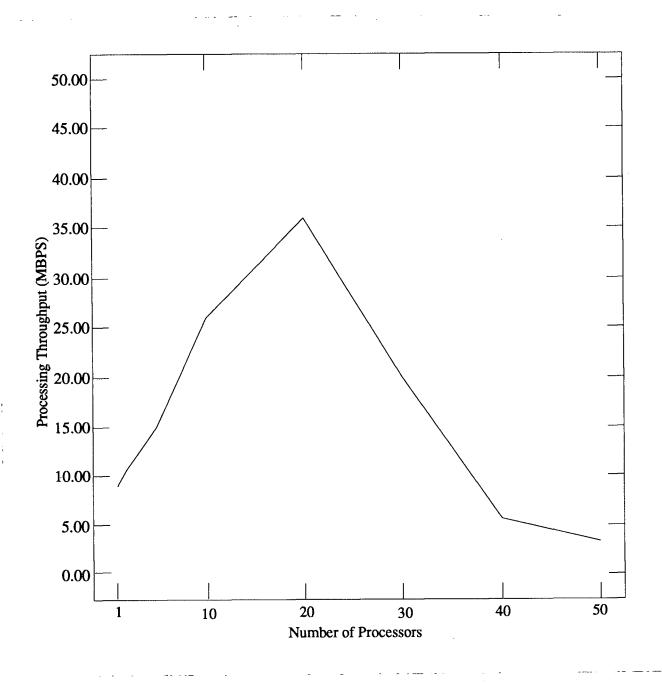

| 5.13 | Processing throughput for 200ns shared memory                       | 89  |

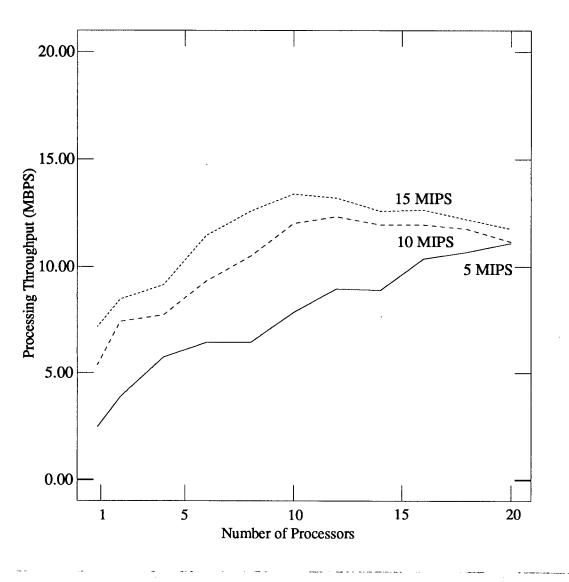

| 5.14 | Processing throughput for 160ns shared memory                       | 90  |

| 5.15 | Processing throughput for 120ns shared memory                       | 91  |

| 5.16 | Processing throughput for entire program in cache                   | 93  |

| A 1  | Checksum unit and adder configuration for OSI TP4 checksum.         | 103 |

## Acknowledgement

I would like to thank Dr. Mabo Ito, my supervisor, for his guidance throughout the course of my research.

I extend my appreciation to the high-speed networking group at UBC, in particular Murray Goldberg and Dr. Gerald Neufeld, for providing the basis for the designs studied in my research. Special thanks goes to Murray Goldberg for his patience in answering my many questions on different aspects of protocol processing. I would also like to thank Mike Sample of the computer science department for providing me with statistics on ASN.1 processing.

I also wish to express my gratitude to my family for their support and encouragement without which my studies could not have been completed.

The work presented was supported by a research grant from the Japan Tobacco Company.

#### Chapter 1

#### Introduction

With the increase in communication bandwidth made available by fiber optics and highspeed switching technologies, the communication processing burden on the end system has also increased. This is especially true for open system interconnection (OSI), which provides reliable communication, transfer syntax conversion and aid to application development. The processing has become the limiting factor in communication throughput rather than the communication bandwidth. In most systems, communication processing is done by the host system. The problem with this approach is that the host system must spend much of its time doing communication processing rather than actual work, and most likely, it is not capable of processing at data rates of hundreds of megabits per second now available. This processing burden can be reduced by having a part of the communication processing performed by a separate system going between the host and the network. There have been work done in developing communication processing systems particularly for the lower layers; however, these systems usually implement no more than two layers at a time. A communication processing system design to perform the processing for more layers, including the processing intensive presentation layer, is required if such a system is to substantially decrease the processing burden on the host.

In this thesis report, two multiprocessor designs are considered for OSI protocol processing engines. The systems are designed to handle processing for OSI layers 2 through 6 [2]. The protocol processing for a packet can include such tasks as encoding and decoding of the packet header and the actual protocol processing according to the packet

type and the operation of the protocol in use. The actual protocol processing required is different for each layer as each layer serves a different function. For OSI processing, the transfer syntax encoding and decoding required at the presentation layer is the most processing intensive element. The transfer syntax encoding process turns data specified in an abstract syntax and represented within a machine in an internal form into a form used for transfer. The decoding process performs the same operations in the opposite direction. The decoding and encoding of data requires a significant amount of processing as each data item must be encoded or decoded. The protocol processing requirements for the layers concerned were taken into account in the design process. The unit of parallelism used is the protocol data unit (PDU) or packet. This means that the processing for a packet is done by a single processor and that several packets are processed concurrently by different processors. This approach is a fairy general purpose one in that the protocol processing is done in software on a multiprocessor platform. The two designs considered are similar with the important difference being where packets are stored while being processed. In the first design, a packet is stored in the local memory of the processor assigned to process that packet. In the second design, packets are stored in shared memory.

The performance of both designs were evaluated through software simulation. The performance of the distributed design, where packets are stored in local memory, was found to vary with the characteristics of the data transfer. This was mainly the result of the processor utilization being sensitive to the characteristics of the data transfer as a result of the serialization effect of the requirement of ordered processing at the higher layers. The processor utilization and throughput was better for smaller packet sizes since the packet is the unit of processing and parallelism for the system. As the number of connections transferring data was increased, the utilization and throughput was found to improve. This was because the contention for connection state information and the

serialization effect of ordered processing was reduced when less packets are received on a per connection basis. The complexity of the data structure was found to have a direct effect on throughput in that the amount of processing required for transfer syntax encoding/decoding is dependent on the data complexity. The data complexity also had an effect of processor utilization in that more complex data required greater amount of processing on a per packet basis thus resulting in higher processor utilization. The processing throughput for outgoing data was much greater than for incoming data. The main factor affecting this was the fact that transfer syntax decoding of data can take as much as twice the processing or more than for encoding for data which is more complex than the basic data types. The distributed design was found to scale fairly well. For the configurations tested, up to about 40 processors could be used without the shared bus becoming a point of contention which limited the performance for the modified operation. It was found that processing throughputs of a hundered megabit per second was achievable only for very simple data types.

The lumped shared memory design was found have similar throughputs as the distributed design when very few processors were used. The system operation for this design was essentially the same as for the distributed design and thus this design should have had similar performance and problems as with the distributed design; however, the effects of the heavy contention for shared memory overshadowed the system performance.

The rest of this thesis report is organized as follows. Chapter 2 describes the processing requirements for the OSI layers handled by the system. Chapter 3 enumerates the options available in designing a communication processing system and describes how the design to be studied were chosen. In chapter 4, the two designs are described in terms of system architecture and system operation. Chapter 5 describes how these designs were evaluated. This chapter also provides the performance of the systems as evaluated

through software simulations as well as analysis on the results provided by the simulations. Chapter 6 provides concluding remarks.

#### Chapter 2

## System Requirements

The protocol engine is designed to handle processing for OSI protocols for layer 2 to 6. This chapter first describes the layer and peer interactions in OSI. This is followed by a description of the division of processing responsibilities between the host system, the protocol engine and the network adapter. The processing requirements for the layers handled by the protocol engine is also discussed.

#### 2.1 Open Systems Interconnection Reference Model

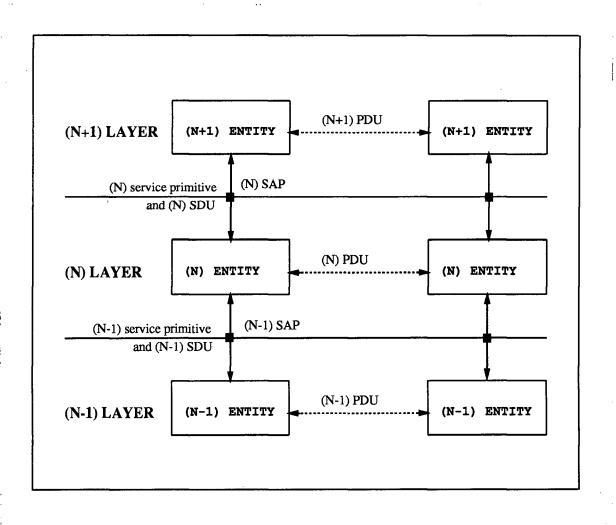

Open System Interconnection is the seven layer reference model defined by the International Organization for Standardization (ISO) for communication between different computer systems [2]. The OSI model defines each of the layers through a service definition and a protocol specification. The service definition specifies the activity between adjacent layers as service primitives. The protocol specification defines the interaction between peer entities. Information is passed between adjacent layers as service data units (SDU) through service access points (SAP). Information is passed between peer entities as protocol data units (PDU). An (N+1) layer entity passes an (N+1) PDU to its peer entity by invoking a (N) service primitive through an (N) SAP. In so doing, the (N+1) entity passes the (N+1) PDU as an (N) SDU to the (N) layer entity. This interaction is illustrated in Figure 2.1.

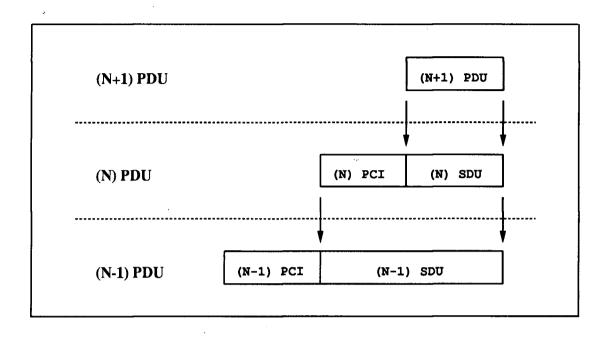

The (N) layer entity creates an (N) PDU by adding protocol control information (PCI), often referred to as the *header*, to be used by its peer entity onto the (N) SDU.

Figure 2.1: OSI layer interaction.

Figure 2.2: PDU formation in OSI.

It then passes the (N) PDU to the (N-1) layer entity as an (N-1) SDU. This continues until the physical layer where information is actually transmitted to the peer. This PDU formation and passage of SDU between layers is depicted in Figure 2.2. On the receiving side, when an (N) layer entity receives the (N) PDU, it performs action as dictated by the (N) PCI according the protocol in use. If the PCI dictates that the PDU be passed on to (N+1) layer, then it is passed as an (N) SDU. In OSI, information passes through the layers but the actual communication occurs between the peer layers entities.

## 2.2 Division of Processing Responsibilities

The system design distributes the processing required for the seven layers between the host system, the protocol engine and the network adapter. The host system is responsible

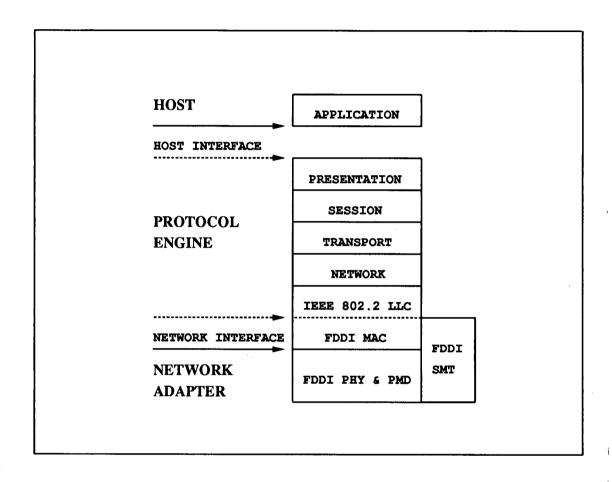

Figure 2.3: The layers processed by the protocol engine.

for the application layer processing. The host interface subsystem of the protocol engine provides the interface between the host system and the protocol engine core. The protocol engine provides the processing for the presentation layer through to the data link layer. The network interface provides the interface between the protocol engine and the network adapter. The network adapter provides the physical layer. This division is illustrated in Figure 2.3.

## 2.3 Processing Requirement

There are two components to the processing at each layer. The first component is the processing required due to the layered organization and peer-to-peer interaction. This component consists of the inter-layer interface processing and the header processing. The second component is the actual protocol processing as dictated by the PDU received or the service request received. This component depends on the functions provided by a layer.

The inter-layer interface processing depends on how the interface is implemented. The implementation options include client/server type interface and procedure calls. The header decoding is done on the receiving side and header encoding is done on the sending side. The encoding process is the creation of the header with the appropriate protocol control information. The decoding process is the process of providing pointers to access the header elements.

In the following sections, the functions of the layers implemented in the protocol engine and some of the protocol processing elements for the layers are described.

#### 2.3.1 Data Link Layer

The data link layer, layer 2, is responsible management of the transmission of data across the physical link. For our system, this layer would consist of the Fiber Distributed Data Interface (FDDI) media access control (MAC) and IEEE 802.2 Logical Link Control (LLC) Type I. The MAC is commercially available as part of a FDDI chipset. The processing requirement for the Type I LLC is minimal as it essentially serves the purpose of providing a uniform interface to the network layer independent of the actual MAC in use.

#### 2.3.2 Network Layer

The network layer, layer 3, provides the switching and routing functions required for the data transfer between end systems. In our system, a connectionless network protocol such as the connectionless-mode network protocol (CLNP) would be utilized. A routing table may be maintained to determine the route on which a packet is to be sent if the network is composed of several subnetworks. The reassembly of packets segmented during transit may also be required.

#### 2.3.3 Transport Layer

The transport layer, layer 4, is responsible for providing a reliable communication channel for the session layer and above. As such, the transport layer provides end-to-end error and flow control. A connection-oriented transport protocol such as transport protocol class 4 (TP4) would be utilized in our system. A connection is a communication context about which information, called connection state information, on the progress of the communication over that context is maintained. The progress of data transfer is monitored through the use of sequence numbers. The transport layer also performs segmentation of packet on the sending side and reassembly of segments on the receiving side.

There are a variety of errors which must be detected and corrected. Corrupted packets are detected through the use of some sort of error detecting code calculated over the packet. Duplicate and missing packets are detected by checking the sequence number. These errors are usually recovered from by having the sender maintain a timer for the time by which an acknowledgement for sent packets should be received. If an acknowledgement is not received by the sender in time, the sender retransmits the unacknowledged packets. In order to detect network problems and host failures, the state of the connection is

periodically checked by exchanging special packets.

End-to-end flow control is usually implemented by maintaining a range of sequence numbers, commonly called a window, for which the sender is allowed to transmit to the receiver without receiving an acknowledgement or credit. The receiver informs the sender of the window by acknowledging received packets and informing the sender how much data it can accept.

The transport layer also provides data blocking functions. This includes segmentation/reassembly and concatenation/separation. Segmentation is the process of splitting up a packet to a size acceptable to the network layer. Reassembly is the opposite process to segmentation on the receiving side. Concatenation is the process of putting together more than one transport PDU into a single network SDU on the sending side. Separation is the opposite process to concatenation on the receiving side.

From a processing standpoint, the maintenance of connection state information and timers, the calculation of data error detection code and the data blocking are some of the important elements. The connection state information for the connection that a packet belongs to must be located from the list of all connection state information. The amount of processing required to maintain timers and to perform basic timer functions can be significant especially if the time resolution required is small and the number of timers maintained is high. The calculation of the error detection code is very costly because processing is required on a per byte or word basis. The processing required for segmentation and reassembly of packets is significant if copying must be done to perform reassembly.

## 2.3.4 Session Layer

The session layer, layer 5, provides services to control the dialogue between applications. This includes the establishment of a session, between two applications. This layer may

also provide checkpointing and synchronization mechanisms for the resumption of communications after failures. For connection oriented session protocol, the processing for a packet consists of encoding/decoding of header information, locating the state information for the connection the packet belongs to and the processing required according to the type of packet, the state of the connection, and the functional units of the protocol in use.

#### 2.3.5 Presentation Layer

The presentation layer, layer 6, provides services related to the representation of the data being transferred including conversion, encryption and compression. The main function of the presentation layer is to convert data specified in an abstract form and represented in an internal format to the transfer syntax used during the data transfer. The abstract syntax, which allows for the application to specify the data structure of the data to be encoded to the presentation layer, and the transfer syntax, which is used to encode the data into a system independent form, can be selected from available syntaxes. Currently, the dominant syntax used for data representation is Abstract Syntax Notation One (ASN.1) and the dominant transfer syntax in use is the Basic Encoding Rules (BER) for ASN.1. The main processing requirement for this layer is the transfer syntax encoding/decoding of the data. The amount of processing, which can considerable since the processing must be done for all data elements being transferred, is dependent on the complexity of the data being encoded/decoded.

#### Chapter 3

## System Design Options

In designing a front-end system to perform the protocol processing for a host system, there are several approaches possible. This chapter describes how the design for our system was selected by considering the different approaches possible. The first part of this chapter describes these approaches. This is followed by the options available for the parallel processing approach chosen for our system. The architecture options for the processing method chosen for our system and the general architecture selected is then discussed.

## 3.1 Processing Approach Options

There are several approaches possible for achieving higher communication processing speed. They include designs based on:

- fast uniprocessors.

- protocols implemented on custom integrated circuits.

- protocols designed for high-speed networks.

- parallel processing.

The advantages and disadvantages of each of the approaches in the context of implementing OSI on a front-end system follows.

#### 3.1.1 Design Based on Fast Uniprocessors

A design based on a uniprocessor has the advantage that the designing of uniprocessor systems and the implementation of communication protocols on uniprocessors are well known. This approach has the disadvantage that the increases in the processing abilities of processors must keep pace with the increases in processing requirements due to increases communication bandwidth. This approach is not very promising for OSI processing especially considering the amount of processing required for transfer syntax encoding/decoding done at the presentation layer and the fact that leading edge processor technology is usually not used in peripheral devices.

#### 3.1.2 Design Based on Custom Integrated Circuits

Many protocols, especially those for the lower layers have been implemented in custom integrated circuits [24]. The implementation of protocols in custom integrated circuits has the advantage of allowing for a more customized implementation than software implementations since any function required can be provided in hardware. These designs usually exploit parallelism to some degree as some functions can be performed at the same time. This method also has the advantage of on-chip delays being much less than delays between chips. The main disadvantage of this approach is that a new integrated circuit must be created for each new protocol and each protocol revision. The use of this approach for OSI processing requires several considerations. One consideration is how the layer interfacing is handled. With each protocol layer implemented on a separate integrated circuit, the interfaces must be designed carefully to avoid copying of packets between layers and at the same time minimize contention for the packets. The other consideration is whether the speed up provided through hardware implementation alone is enough to make this approach viable for high-speed networks.

## 3.1.3 Design Based on Protocols for High-Speed Networks

There has been a number of protocols, particularly transport protocols, designed for high-speed networks [25], [12]. These protocols are designed to provide greater throughput through more efficient connection establishment methods, and better transmission and retransmission strategies. Some of these protocols also are designed for more efficient processing. For example, the XTP protocol has a packet format organized to minimize misalignment so that copying can be avoided during processing [4]. While the majority of these protocols are for the transport layer, other layers are also considered. For example, in [16], a light weight transfer syntax is considered for the presentation layer. These protocols will either eventually be put into general use or have aspects of their designs incorporated into more common protocols. The problems with these protocols is that it usually takes a long time for protocols to be standardized and be accepted for general usage.

## 3.1.4 Design Based on Parallel Processing

A parallel processing approach has the advantage that the processing ability of the system increases with scale. Software implementation on a multiprocessor platform provides flexibility and adaptability in the selection and implementation of protocols. The disadvantage of this approach is that the implementation of protocols in a multiprocessing environment is not well known. Most protocols were not designed with parallel processing in mind, therefore, implementing these protocols in parallel will require some amount of coordination and communication between processors which will reduce the improvement attainable through scaling.

This approach was selected for our system because of its potential for processing increase and the flexibility it offers in the selection and implementation of protocols. It is

desirable for a practical reason in that leading-edge processor technology is usually not used for a peripheral device, such as a network adapter, and this approach could provide a method of providing the required processing power using more common processor technology.

## 3.2 Parallel Processing Options

A parallel processing approach was chosen for our system due to its potential for processing increase with scale. A general multiprocessing approach provides more flexibility than hardware implementation and it offers processing improvement over uniprocessor implementations. There are a number of ways in which the OSI processing can be processed in parallel. The alternatives for the unit of parallelism are:

- protocol layer.

- elements within a protocol layer.

- connection.

- protocol data unit.

The advantages and disadvantages of using each of the above as the unit of parallelism is discussed in the following sections.

## 3.2.1 Processor Per Protocol Layer

In this approach, one processor is assigned for each layer. This approach has the advantage of providing clean interfaces between layers. Since the processing for each layer is handled by a single processor, there are no problems with implementing the protocols. One disadvantage of this method is that the inter-layer interface must be done through

interprocessor communication which is usually much slower than communication within a processor. Another disadvantage is that packets must either be shared between processors or else they must be copied between processors as the packets are passed between layers. There is also a limitation on the parallelism to the number of layers being implemented.

#### 3.2.2 Processor Per Protocol Function

In this approach, the different processing functions within a protocol are assigned to different processors. This method has the advantage of speeding up the processing of each packet. In [33], a method of processing different functions on the send and receive sides for a protocol in parallel was studied, yielding some promising results for conventional speed networks. The main disadvantage of this approach is that there is a significant amount of coordination required in processing different aspects of a protocol. There would also be contention for header information access between processors performing different functions. The amount of parallelism available is also limited to the number of functions within a protocol in general and those function which can be performed in parallel in particular. For example, the header decoding and the connection state information retrieval must be done before any actual protocol processing can take place. This approach would be more suited for implementation using custom integrated circuits since the implementation of the coordination and the actual functions required can be done more efficiently on a custom design than for a general architecture.

#### 3.2.3 Processor Per Connection

In this approach, the processing required for a data connection is assigned to a processor. Each processor would be responsible for processing the packets for a number of connections. One advantage of this approach is that the processing of packets for different connection can be carried out independently so that a design based on this approach

should scale well. Another advantage is that the inter-layer interaction takes place within a processor. The disadvantage of this approach is that at most one processor works on the processing of packets for a connection. As such, the processing improvement obtained by this system depends on the number of connections receiving and sending packets.

#### 3.2.4 Processor Per Protocol Data Unit

In this approach, a PDU is assigned to a processor which performs the processing for all layers concerned. An advantage of this approach is that the processing of PDUs can be carried out independently of each other except for the the need to access the state information for some of the layers. Another advantage is that the inter-layer interaction takes place within a processor. The main disadvantage of this approach is the need to share state information between processors. Some coordination between processors is also required to assure that the ordered processing of packets for the higher layers is preserved. In [18], this approach was studied for the transport layer and the results indicate that this approach may be suitable for high-speed networks.

This approach was chosen for our system because processing can be carried out more independently than the more fine-grain approach of processing different functions of a protocol in parallel, and this approach offers better possibility of processing improvement on a per connection basis than the approach of assigning processors to different connections.

#### 3.3 Architecture Options

A general multiprocessing approach with the processing of different packets in parallel was chosen for our system due to its potential for processing increase and its flexibility in the selection and implementation of protocols. The inter-connection method and memory

organization for our system will be considered in this section.

In order to select the inter-connection method and memory organization for our system, the information which must be stored in the system and the information transferred in and out of the system, and within the system were considered. The three main types of information which must be considered are:

- connection state information.

- protocol data units.

- synchronization information.

Each of these will be considered in turn in terms of storage and transfer. In the design decisions, the more basic approaches were favoured based on the belief that a more complex approaches should be attempted only if a basic approach is found to be inadequate.

All processors must be able to access the connection state information for the transport, session and presentation layers since all processors are responsible for the processing for a packet for all layers concerned. A locking mechanism is required to ensure that the state information is accessed and updated by only one processor at a time. One way in which state information can be maintained is to have a processor act as a server controlling accesses to the state information. Processors needing to access state information would send a message to the server to obtain exclusive access and to obtain any required information. The server would reply to the processor indicating exclusive access has been obtained or with the requested information. The advantage of this approach is that a processor needing to lock state information does not continually have to keep checking the status of the lock until it is unlocked. The disadvantage of this method is that the server could become the bottleneck in accessing the state information. Another way in which state information can be maintained is to have the state information stored in

shared memory and to provide a mechanism of checking and setting a lock in a single step. The second method was selected because this method is simpler to implement than the first and the number of accesses to check lock state can be controlled by an appropriate choice of lock checking interval. The state information for all layers will be kept in a single shared memory connected to the processors by a single bus. There are other methods available which provide for more independent access but they are much more complicated to implement and should be used only if access to state is identified as a bottleneck in our system.

The packets must be stored in our system while being processed and they must be transferred in and out of the system from the network and host. In order to transfer packets in and out of our system, a high-speed burst access type bus will be used. The one major decision which must be made is whether to store the packets in shared memory or local memory of the processor processing the packet. The main advantage of keeping packets in local memory is that there is no contention for accessing packets while they are being processed. From a processing standpoint, this is the better method since the processing of a packet is independent from the processing of other packets except for the access to the state information. One disadvantage of this method is that copying of packets between processors would be required on the reassembly of segmented packets. Another disadvantage is that the processor which is assigned a packet must process it, unless copying is done, and this may result in some processors being idle while other processors have many jobs. One advantage of keeping packets in shared memory is that copying of packets is not required on reassembly of segmented packets. Another advantage is that any processor can process any packet. This is advantageous in that there can be a central job queue from which processors can obtain packets for processing. The disadvantage of this approach is that packet accesses become shared memory accesses even though packets do not need to be shared while being processed. Since there are

significant advantages and disadvantages to each of these alternatives, both approaches will be studied.

Some synchronization between processors is necessary to ensure that packets are processed in sequence at the transport layer and above. The synchronization can be done using a message passing approach or through shared memory. The latter was selected since the bus used for the accessing state information is available for this purpose.

# 3.4 Design Selection

The processing method and the basic system design were selected as described in this chapter. Although many factors were considered, the design selection was done fairly arbitrarily. There are significant advantages to all of the approaches considered in this chapter and this design was selected since it has some significant advantages and is worthy of study. In the next chapter the architecture and the system operation are described in detail.

#### Chapter 4

## System Description

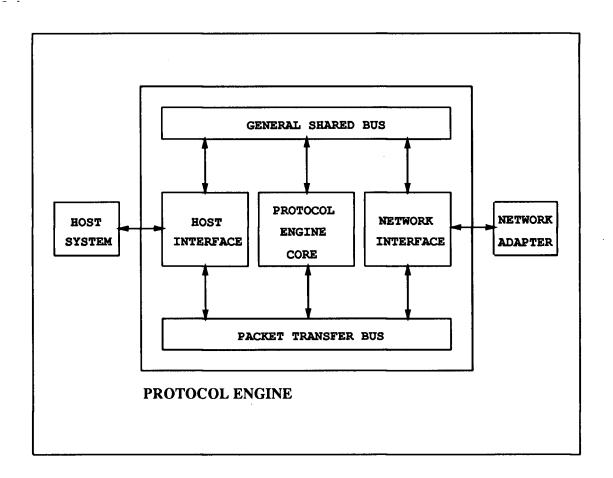

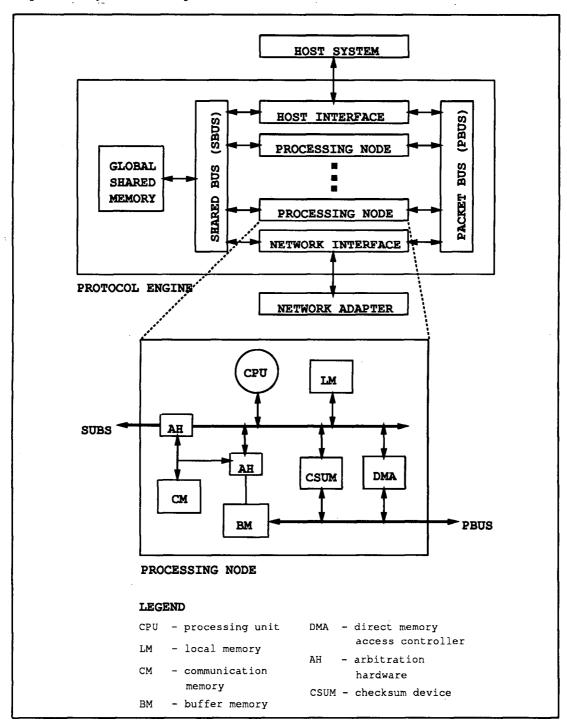

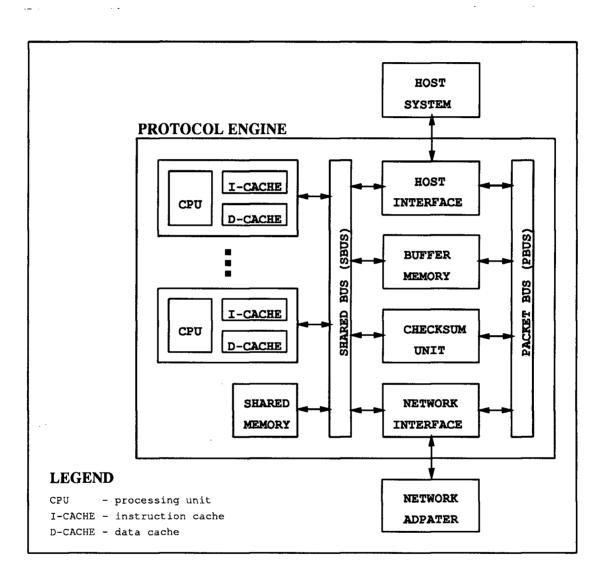

In this chapter the system architecture and system operation of the two designs under consideration are described. The general design of the system is depicted in Figure 4.1. The host interface is responsible for the coordinating packet transfers between the host and the protocol engine processors. The network interface has the same function for the network side. Packet transfers are done through the packet bus (PBUS), a high-speed, burst access bus. The coordination of transfers are done through shared memory using the share bus (SBUS). The first part of this chapter describes the host and network interface components which are common to both designs. This is followed by the description of the two protocol engine cores: the mixed memory design and the lumped shared memory design.

#### 4.1 Network Interface

The network interface provides the components necessary to interface the network adapter to the protocol engine core. The network interface transfers packets received from the network to the protocol engine and vice versa.

#### 4.1.1 Network Interface Architecture

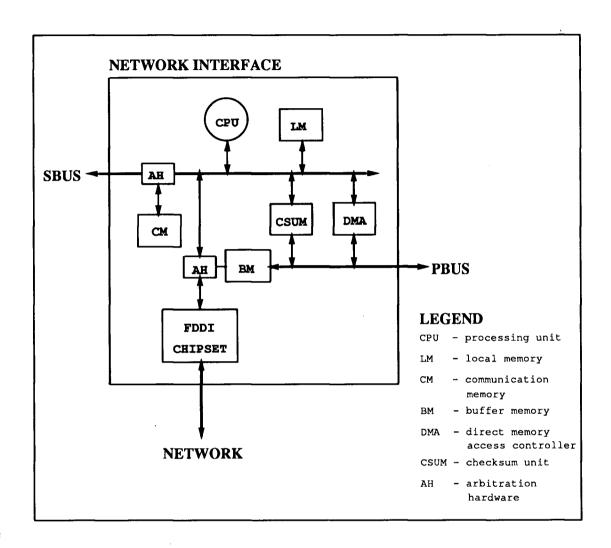

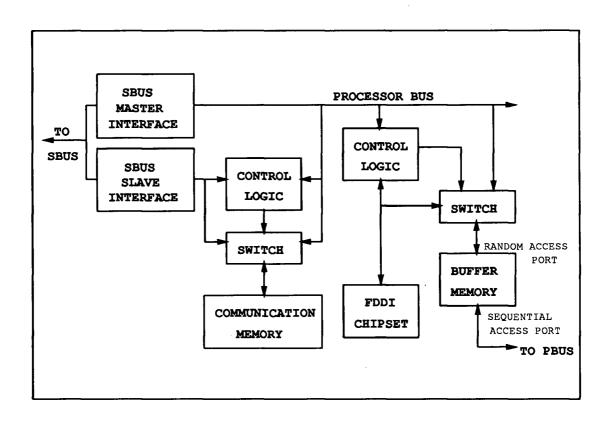

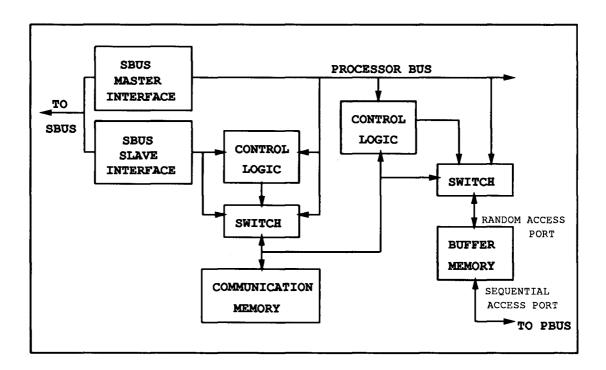

The network interface is composed of the processing unit, local memory, communication memory, buffer memory, checksum unit and the network chipset. The design is depicted in Figure 4.2.

Figure 4.1: General system architecture.

Figure 4.2: Network interface architecture.

This design is for fiber distributed data interface (FDDI) networks and is based on the FDDI chipset manufactured by National Semiconductors [21]. The local memory is for processor's code and data. The communication memory is shared memory used for communication between the network interface and the processors in the protocol engine. The buffer memory is used to temporarily buffer packets coming in from the network and going out to the network. Part of the buffer memory is used to communicate between the processor and the FDDI chipset. The checksum unit is used to calculate the transport layer checksum during the packet transfer from the protocol engine core to the network interface. Descriptions of the communication memory, the buffer memory, the checksum unit, and the FDDI chipset follow.

## Communication Memory

The communication memory is the memory shared between the network interface and the processors in the protocol engine used for communication purposes. It is composed of random access memory connected to the SBUS and the network interface local bus through external, two-way arbitration hardware. The arbitration should give priority to external processor accesses as these accesses occupy the SBUS, a shared resource. The interfacing of the communication memory is depicted in Figure 4.3.

#### **Buffer Memory**

The buffer memory is used to temporarily buffer packets when transferring packets between the protocol engine and the network and vice versa. A part of the buffer memory is used as shared memory between the processor and the FDDI chipset to facilitate communication between the two. Packet buffering is required for two reasons. The first reason is to provide latency time to set up the data transfer between the network interface and protocol engine. The second reason is to adjust for differences in data transfer

Figure 4.3: Communication and buffer memory interface.

rates between the network and the PBUS since the PBUS is capable of transferring data at a faster rate that the data rate of the network. The buffer memory is composed of dual-ported video type memory which has a sequential access port and a random access port. In this type of memory, a shift register built into the memory chip supplies the serial access capability. Any row of the random access portion of the memory can be transferred to/from the shift register. The only access conflict between the ports occurs when a row of memory must be transferred to/from the shift register. The serial access port is attached to the PBUS to facilitate the transfer of packets between the network interface and the protocol engine core. The random access port is attached to the local bus and the FDDI chipset using two-way arbitration hardware. This is depicted in Figure 4.3.

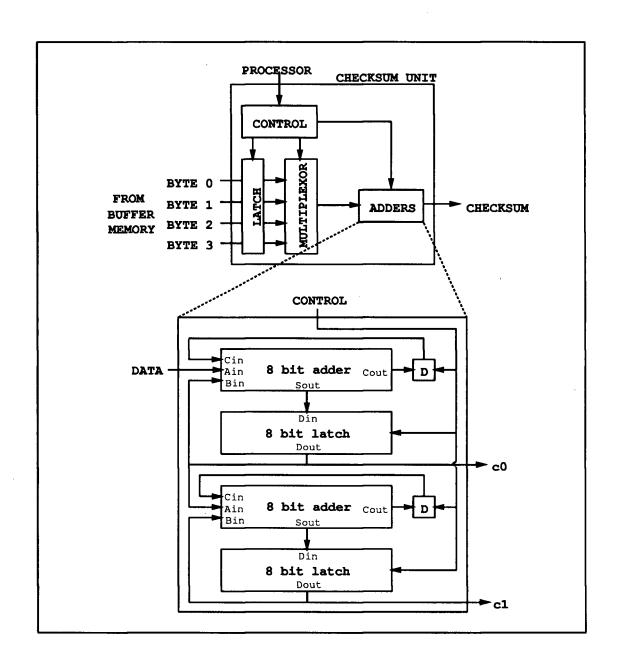

#### Checksum Unit

The checksum unit calculates the transport checksum for a packet as it is received from the external processors. It accesses the packet data through the local extension of the PBUS and receives control information from the local processor. A specific configuration of adders, or possibly other hardware for different types of error detection codes, is required for the particular transport protocol supported. The checksum is calculated in hardware despite the loss of flexibility for two reasons. The first reason is that the checksum can be calculated while packets are being transferred on the PBUS. The other reason is that checksum calculation can require a number of instruction per byte of data. For example, the checksum recommended for OSI transport protocol class 4 (TP4), requires two sums to be calculated per byte of data. Considering that at FDDI rate (100 megabits per second), one instruction per byte requires 12.5 million instructions per second (MIPS) to perform in real time, some loss of flexibility as a result of a hardware implementation is justified. The OSI checksum unit can be implemented very simply as

illustrated in Appendix A. The checksum unit can be made into a module so that the module required for a specific protocol can be inserted.

### FDDI Chipset

The FDDI chipset by National Semiconductor provides the FDDI media access control (MAC) function. The FDDI BMAC System Interface chip provides the FDDI chipset the ability to interface to system receiving or sending the data [22]. The system interface chip communicates with the user system through specific data structures using shared memory. To send data, the user system specifies the locations of parts of the packet to be sent in the data structure expected by the system interface chip. The system interface chip has the ability to gather these parts before the actual transmission of the data. To receive data, the user system specifies the locations of free areas of memory to the system interface chip in the data structure it expects. Upon receiving a packet, the system interface chip scatters the packet data to fit the free areas of memory as specified by the user. It then informs the user system of the locations in which the data are stored through a specific data structure. In our case, the buffer memory provides the memory for the packets as well as the memory for the queues storing the data structures holding transfer information.

## 4.1.2 Network Interface Operation

The network interface processor coordinates the transfer of packets and control information from the network to the protocol engine core and vice versa. It also provides the station management function required for FDDI operation. The FDDI chipset residing within the network interface provides the FDDI media access control (MAC) layer.

The transfer of packets and control information from the protocol engine to the network takes place as follows. A processor in the protocol engine informs the network

3

interface that a packet is to be sent out to the network by placing information about the packet including its location, into a queue located in the communication memory of the network interface through the SBUS. If checksum is to be calculated during the transfer, the bytes to be summed and where to place the checksum are also specified. The network interface processor sets up the transfer by appropriately programming the direct memory access (DMA) controller to transfer the packet over the PBUS from the protocol engine to the network interface. If checksum is to be calculated, the checksum unit is activated while the bytes concerned are transferred, and once done, the checksum bytes are written into the specified location in the packet by the processor through the random access port of the buffer memory. The processor then informs the FDDI chipset about the packet through a portion of the buffer memory reserved for this purpose using the data structure required by the FDDI system interface chip. The FDDI chipset then carries out the task of sending the packet over the network.

The transfer of packets and control information from the network to the protocol engine takes place as follows. The processor keeps the FDDI system interface chip informed about the location of free areas of buffer memory by specifying this information in the required data structure in the area of buffer memory reserved for this purpose. Upon reception of a packet from the network, the FDDI chipset places the packet in the free memory and informs the processor about its location. The processor, who jointly manages the packet storage area in the protocol engine with the protocol engine processors, allocates sufficient memory for the packet in the protocol engine. The processor then sets up the DMA controller with the information required to transfer the packet to the protocol engine. The processor informs the protocol engine about the packet by adding information about the packet including its location in the protocol engine's job queue located in a part of the protocol engine's memory shared with the network interface. It

would be possible to calculate the checksum of packets during the transfer in this direction as well but two factors affect the usability of the checksum result. The first factor is the lack of knowledge of where exactly the transport protocol data unit (TPDU) is located within the packet, which is in fact the datalink protocol data unit. This means that some of the checksumming must be undone for the parts of the packet which is not part of the TPDU. The amount of processing required by the processor in the protocol engine assigned to process the packet to undo the checksumming for the unnecessary parts is high for OSI TP4 checksum because for the second checksum byte, the calculation of the sum is weighted inversely with the position of the byte in the packet. The second factor is that if the original TPDU was segmented at the network level during transit, the checksums calculated for each segment would have to combined. This would be difficult for OSI TP4 checksum due to the weighting of the checksumming inversely with position.

The network interface processor provides the FDDI station management function. The station management function include the administration of addressing, allocation of network bandwidth and network control and configuration. If some of the management information is generated by the host system, this information can be passed from the host to the network interface through the protocol engine.

#### 4.2 Host Interface

The host interface provides the components necessary to interface the the protocol engine core to the host system. The host interface transfers packets from the host to the protocol engine and vice versa.

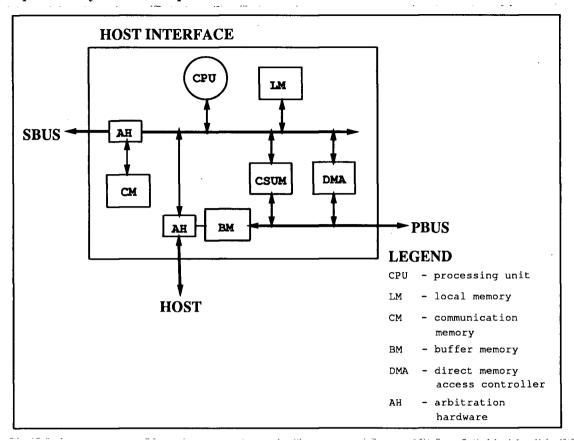

Figure 4.4: Host interface architecture.

#### 4.2.1 Host Interface Architecture

The host interface is composed of the processing unit, the local memory, the communication memory and the buffer memory. The design is depicted in Figure 4.4. The local memory is used for the processor's code and data. The communication memory is used to coordinate transfers between the host and the host interface. The buffer memory is used to buffer packets at the host interface during transfers between the host and the protocol engine.

# Communication Memory

The communication memory is memory shared between the host interface and the processors of the protocol engine used for communication purposes. It is composed of random

access memory connected to the SBUS and the host interface local bus through external, two-way arbitration hardware. The arbitration should give priority to external processor accesses as these accesses occupy the SBUS, a shared resource.

## **Buffer Memory**

The buffer memory is used to temporarily buffer packets when transferring packets between the protocol engine and the host and vice versa. A part of the buffer memory is used as shared memory between the processor and the host facilitate communication between the two. The main reason for buffering the packets is to adjust for any differences in the data transfer rates between the PBUS and the host. The PBUS transfers data faster than the host since the host transfers data using its direct memory access channel during periods when the processor is not using its bus. The buffer memory is composed of dual-ported video type memory which has a sequential access port and a random access port. The serial access port is attached to the PBUS to facilitate the transfer of packets between the network interface and the protocol engine core. The random access port is attached to the host interface processor and the host using two-way arbitration hardware.

# 4.2.2 Host Interface Operation

The host interface processor coordinates the transfer of packets and control information from the host to the protocol engine core and vice versa.

The transfer of packets and control information from the protocol engine to the host takes place as follows. A processor in the protocol engine informs the host interface that a packet is ready to be picked up by the host by placing information about the packet including its location, into a queue located in the communication memory of the host interface through the SBUS. The host interface processor sets up the transfer by

appropriately programming the direct memory access (DMA) controller to transfer the packet over the PBUS from the protocol engine to the host interface. The processor then informs the host about the packet by placing information about the packet including its location and the service primitive with which the packet is associated in the portion of buffer memory reserved for this purpose. The host interface then indicates to the host that a packet is ready for transfer through one of the host's interrupt channels. The host then transfers the packet using one of its DMA channels. The host interface does not necessarily have to transfer the entire packet to the buffer memory. It just has to transfer sufficient data to the buffer memory to stay ahead of the host.

The transfer of packets and control information from the host to the protocol engine takes place as follows. The host specifies the the service primitive associated with packet in the portion of the host interface's buffer memory reserved for this purpose. The host then transfers the packet to the host interface buffer memory using one of its DMA channels. The buffer memory is organized as a buffer ring and it is the responsibility of the host interface to transfer packets to the protocol engine before the ring gets full. The host interface transfers the packet to the protocol engine through the PBUS by programming its DMA controller. The host interface manages the packet buffer along with the processors in the protocol engine. Once the packet is transferred, the host interface processor informs the protocol engine about the packet by placing information about the packet including its location and the service primitive associated with the packet in the protocol engine job queue located in the protocol engine.

# 4.3 Protocol Engine Core Design 1: Mixed Memory Design

The protocol engine core carries out the protocol processing for OSI layers 2 through 6. A packet received from the network interface or host interface are assigned to one of the processors in the protocol engine core. The processor then performs the processing required for the packet for the layers concerned as far possible. When the processing for a packet is completed, it is passed on to the network interface or host interface as appropriate.

The first design is a mixed memory design in that the state information is stored in memory shared by all processors while the packets are stored in memory local to the processor responsible for a packet. The program code and data for each processors are also stored locally. Some aspects of the system architecture and the operation are similar to the system in [18]. Descriptions of the architecture and system operation of this design follows.

### 4.3.1 Mixed Memory Architecture

In the mixed memory design each processing node is connected to all other processors and the host and network interfaces through the SBUS and the PBUS. Shared memory is accessed by all processing nodes through the SBUS. Each processing node has its own local memory for its program code and data and its own buffer memory for storing data packets. Each processing node also has communication memory, which can be accessed by external processors through the SBUS, for communicating with other processors and the host and network interfaces. A checksum unit to calculate the transport protocol checksum is also located within each processing node. This design is depicted in Figure 4.5. A more detailed description of the communication memory, buffer memory, checksum unit, shared bus and packet bus follows.

### **Communication Memory**

The communication memory is shared memory used for communication between the local processor and external processors including the network and host interface processors.

Figure 4.5: Mixed memory architecture.

Figure 4.6: Communication memory and buffer memory interfacing.

The memory used is random access memory with the arbitration between local processor access and external SBUS accesses being done using external hardware. The arbitration should give priority to external SBUS accesses since a shared resource is being used. How the communication memory is connected to the local processor and the SBUS is depicted in Figure 4.6.

# **Buffer Memory**

The buffer memory is used to store packets while being processed. It is composed of dual-ported video type memory which has a sequential access port and a random access port. In this type of memory, a shift register built into the memory chip supplies the serial access capability. Any row of the random access portion of the memory can be

transferred to/from the shift register. The only access conflict between the ports occurs when a row of memory must be transferred to/from the shift register. The serial access port is attached to the PBUS to facilitate the transfer of packets between the network and host interfaces and the protocol engine core. The random access port is accessed by both the local processor and external processors. The arbitration between the two is done externally. This is depicted in Figure 4.6.

#### Checksum Unit

The checksum unit is exactly like the checksum unit in the network interface. There is a slight difference in operation as this device is used for calculating the transport protocol checksum locally for packets received from the network. The buffer memory's ability to cycle sequential data quickly is utilized in the calculation the checksum. To perform the calculation, the local processor programs the direct memory access (DMA) controller to cycle the required bytes through the sequential access port of the buffer memory and activates the checksum device.

#### Shared Bus (SBUS)

The shared bus is used by the processing nodes and the host and network interfaces to communicate with each other. It is also used by the processing nodes to access the global shared memory.

The shared bus is a general multiple master bus. The bus design is dependent to a large degree on the processor chosen. One of the standard busses should be adequate. The choice of a standard bus over a proprietary design has the advantage that bus devices for standard busses are usually commercially available. There is also the possibility of implementing only a subset of the functions of a standard bus as long as requirements are satisfied.

It should be noted that any device connected to the SBUS bus needs to have the bus interface unit for the bus selected. A master type bus interface is required for active devices which take control of the bus. A slave type bus interface is required for passive devices such as memory devices. In our design, the processing nodes and the host and network interfaces require both master and slave type interfaces. The global shared memory only needs slave type bus interface.

# Packet Bus(PBUS)

The packet bus is used for packet transfers between the network and host interfaces and the processing nodes. It is also used to transfer packets between processing nodes. The PBUS is a burst access bus in that the owner of the bus can hold on to the bus for more than one access cycle. Allowing this leads to greater transfer rates.

The packet buffer memories of the network and host interfaces and the processing nodes are composed of dual port memory with one random access port and one sequential access port. By allowing the owner of the bus to hold on to the bus long enough to transfer a complete row of memory, the coordination of transfers is simplified because partially cycled shift-registers, which drive the sequential ports, do not have to be maintained.

The standard multiple master busses usually have burst access modes. For the PBUS, only this mode needs to be implemented. As with the SBUS, all devices connected to the bus needs to have appropriate interfaces. In our design, the processing nodes and the network and the host and network interfaces require both master and slave type interfaces.

### 4.3.2 System Operation

The general processing method of the system is as follows. The network interface or host interface receives a packet for processing from the network or host. The packet is

copied to one of the processors through the PBUS. The processor performs the protocol processing for OSI layers 2 through 6. Once done, the processor informs the host or network interface to pass the packet onto the host or network. The system-oriented issues of locking shared data, inter-layer interfacing, memory management, job management and timer management are first discussed. The method for referencing packet data, shared by all layers, is then discussed. This is followed by a description of how the processing is carried out at each of the layers.

### Data Locking

The are many shared data structures in the system, including the connection state information, which must be accessed by only one processor at a time. In order to assure this, a method of locking a data structure is required. In our system this is done through locks which indicate the access status of the data structure. An entity wanting to access the data structure must check the lock status and if it is allowed to access the data structure it changes the lock to the new status. This checking and changing of the lock status must be done indivisibly. This is done using an instruction provided by many processors which allows a value to be read and written without being interrupted. Any entity trying to access a data structure will have to keep checking the status if the data structure is locked. The interval between checking must be set carefully to avoid ineffective contention for the resource in which the lock is kept.

# Inter-layer Interfacing

In our system, the inter-layer interface takes the form of procedure calls. The only cost incurred in going from layer to layer is the cost of a procedure call. The parameters to the procedure call include the location of the packet, the service primitive being used, and the service access point through which the packet is being passed. Some care must be

taken in the implementation of the layers in order to assure proper operation. One of the precautions is that any processing requiring manipulation of the state information must be completed before a call to another layer is made. The layer procedures themselves must be reentrant, ie the procedures themselves must not have states. The problems associated with this approach and methods to assure proper operation can be found in [8].

## Memory Management

There are four types of memory for which management must be considered. These are the local, communication, shared and buffer memory. For the local memory and communication memory, which contains the job queue, the method of allocating exactly fitting blocks from a list of linked free blocks can be used. The shared memory contains the connection state information for the layers. As such, there are only a few sizes of blocks which have to be allocated. A method of dividing up the memory into regions in which fixed sized blocks are allocated can be used to reduce memory fragmentation and time required to find a free block. The buffer memory, which is used to store packets, will be organized into fixed sized blocks since the serial access port of the dual-port memory does not provide much flexibility in accessing the memory. The block size should be at least as large as the size of the row, which is the size of the shift register which drives the sequential access port of the memory. Memory blocks are chained together to meet allocation requests which are larger than a block size.

### Job Management

One issue related to job management is how the jobs, ie packets, are allocated by the host and network interfaces. In our system, a round-robin method is used for allocating the jobs. The simplicity of this approach comes at the cost of possibly having some processors idle while others have more than one job. A more processing intensive, approach of checking the number of jobs at each processor and allocating it to the processor with the least number of jobs could be used as an alternative.

Each processor has an active job queue and a suspended job queue. The processing of a packet may have to be suspended to assure sequencing and for other reasons. These queues are located in the communication memory of the processing node. The reason that they are not kept in local memory is that an external processor may be required to reactivate a suspended job. This is required when a processing of a packet is resumed when its turn in the sequenced processing arrives. The information kept in the job queue entry consists of the status of the job, the service primitive with which the job was associated, the current layer of the processing and the location of the packet.

# Timer Management

Many timers must be maintained for each connection especially for the transport layer. There can be a substantial processing cost as pointed out in [18]. The processing cost is incurred mainly in either the setting of the timers or the maintaining (counting down) of the timers depending on the method used. The method of keeping timers in a ordered list of time remaining before expiry will be used so that the cost of maintaining the timer can be kept low. This method has the disadvantage of requiring some processing to insert the timer in the ordered list when setting the timer. The costs of different methods of implementing timers is discussed in [30].

In our system, the timers are maintained by one of the processors in its local memory. Other processors must send requests to perform timer functions using the communication memory of the timer processor. The timer processor notifies processor which set the timer through that timer's communication memory. The timer processor also generates an interrupt on that processor.

## Packet Referencing

The data packets are accessed by all layers by reference (use of pointers) to avoid having to copy packets between layers which is generally acknowledged to be poor protocol processing practice as mentioned in [27]. A pointer structure for indicating the locations of the header and data portions of packets for the layers is required. Since buffer memory is allocated in blocks and will not necessarily be contiguous, the protocols have to be implemented with consideration of the way in which blocks are chained. Another concern is the deallocation of the memory blocks which are accessed by more than one layer. A technique known as reference counting in which the number of references to a block is maintained can be used. In this method, the reference count is incremented when a block is referenced and the count is decremented when reference is no longer required. When the reference reaches 0, the block is deallocated.

# Details of the Protocol Processing

The way in which some aspects of the protocol processing for layers 2 through 6 are handled are described.

Data Link Layer The processing required is for the logical link control (LLC) sublayer of the data link layer only since the FDDI chipset provides the media access control sublayer. The connectionless version of LLC is almost a null layer in that its main function is to provide a uniform interface to the network layer independent of the underlying network. As a result, very little processing is required layer and no shared memory access is required.

Network Layer Network layer provides the routing function required for data transfer between end systems. For a connectionless network protocol, there is no connection state information but some shared information may be required. A routing table may be required if the network forms part of a larger network. A list of fragments received for a packet segmented during transit must also be shared. A timer has to be used to detect a lost fragment. If the fragments must be discarded because all fragments weren't received in time, the processor which received the timeout notice is responsible for informing all processors holding fragments through the communication memory job queue that their fragment(s) should be discarded. Only the processor receiving the fragment which completes the network level packet continues processing. If this processor does not have the header portion, it will copy the header only from the processor holding the header using the PBUS. The physical reassembly of fragments is not done at this layer to avoid the possibility of having to copy parts of a packet more than once because further reassembly may be required at a higher layer.

Transport Layer The transport layer is responsible for providing reliable communication channels for the higher layers. Error control and flow control are provided by this layer. Connection-oriented protocols are used for the transport layer and above. A description of how the processing proceeds on the sending side and receiving side follows.

On the receiving side, the transport protocol provides error detection, reassembly of segmented packets, proper sequencing of misordered packets and acknowledgement generation. One form of error detection is the detection of packets corrupted during transport. A processor calculates the checksum for a received packet by activating the checksum unit and programming the direct memory access controller to cycle packet data from the sequential access port of the buffer memory. In order to detect missing or misordered data, a list of the packets received for a connection is maintained. Information on the each packet including the location, service primitive, pointer to a job queue element associated with the packet, and the status of the processing are stored in the list. The packet

with expected sequence number is allowed to continue processing while the processing of other packets are suspended. The processing of a packet is also suspended if it is a segment and all segments have not been received. When the processing for a packet is completed, the list is checked to see if the next packet is waiting to be processed. If so, that job is moved from the suspended queue to the active queue. When all segments of a TSDU are received, the processor receiving the completing segment continues processing the TSDU. If this processor does not have the segment containing the header, the header is copied using the PBUS. The logical reassembly of the segments are performed but the physical reassembly (copying to the buffer memory of a single processor) takes place at the session layer because segmentation may also be supported by the session layer. The acknowledgement and flow control information is also generated using this list. The processor receiving an acknowledgement is responsible for reactivating all suspended transmission jobs which can proceed due to a change in the sending window. It must also inform the processors holding packets for retransmission when those packets have been acknowledged so that the memory for the packets can be deallocated.