# GALLIUM ARSENIDE MATERIALS AND DEVICE FABRICATIONS

by

# KIM WAH TAN

B. ENG. (HONS), McGILL UNIVERSITY, 1983

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

DEPARTMENT OF ELECTRICAL ENGINEERING

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

MAY 1986

KIM WAH TAN, 1986

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of Electrical Engineering

The University of British Columbia 2075 Wesbrook Place Vancouver, Canada V6T 1W5

Date May 22nd 1986.

#### **ABSTRACT**

The purpose of this work was to study certain aspects of device properties of ion **MESFETs** material implanted and semi-insulating LEC GaAs. The fabrication technology and properties of GaAs are presently the chief limitations in the way of application of GaAs ion-implanted devices in high speed circuits. One part of the work involved studies on the effects of etching away the surface layers of the starting semi-insulating LEC GaAs. The point here is that it appears that impurities and other defects can sometimes be concentrated at the surface. A test structure containing MESFETs. Schottky diodes and van der Pauw crosses was fabricated using ion implantation on etched and unetched substrates. Improved activation and device characteristics were found on the etched sample. The second part of the work involved studies of the effects of dislocations on device characteristics. The topic is important because dislocations may give scatter in the threshold voltage of MESFETs which would naturally become a problem for large scale integration. Arrays of devices were fabricated and their characteristics measured. The position of dislocations was located by etching in such a way as to leave the ghost of the devices behind. The results were unfortunately not conclusive because of the difficulty in accurately etching the samples. We were subsequently forced to use fewer samples than planned.

# Table of Contents

| ABST | RACT                                                          | ii   |

|------|---------------------------------------------------------------|------|

| LIST | Of FIGURES                                                    | v    |

| LIST | OF FIGURES                                                    | vi   |

| LIST | OF TABLES                                                     | vii  |

| ACKI | NOWLEDGEMENTS                                                 | viii |

| 1.   | INTRODUCTION                                                  | 1    |

| 2.   | GAAS GROWTH AND FABRICATION TECHNOLOGY                        | 4    |

|      | 2.1 Introduction                                              | 4    |

|      | 2.2 Crystal Growth                                            | 5    |

|      | 2.3 Planar Fabrication Technology                             | 9    |

|      | 2,3,1 Ion Implantation                                        | 11   |

|      | 2,3,2 Annealing                                               | 14   |

|      | 2,3,3 Ohmic Contacts                                          | 15   |

|      | 2.4 Present Problems                                          | 16   |

| 3.   | EFFECTS OF REMOVAL OF SURFACE LAYER ON DEVICE CHARACTERISTICS | 17   |

|      | 3.1 Introduction                                              | 17   |

|      | 3.2 Diagnostic Pattern                                        | 18   |

|      | 3.3 Device Fabrication And Experimental Procedure             | 18   |

|      | 3.4 Schottky Metal Evaluation                                 | 21   |

|      | 3.5 Implant Layer Characterisation                            | 27   |

|      | 3.5.1 Doping Profile                                          | 27   |

|      | 3.5.2 Sheet Resistance                                        | 30   |

|      | 3.5.3 Drift Mobility Profile                                  | 32   |

|      | 3.6 Device Performance                                        | 35   |

|      | 3.7 Backgating Effects                                        | 39   |

| 4.   | EFFECTS OF DISLOCATION ON DEVICE CHARACTERISTICS              | 43   |

|            | 1,1 Introduction                           | 43         |

|------------|--------------------------------------------|------------|

|            | 4.2 Literature Survey                      | 44         |

|            | 4.3 Experiment                             | 49         |

|            | 4.3.1 Mask Design                          | 49         |

|            | 4.3.2 Fabrication Procedures               | 50         |

|            | 4,3,3 Measurement                          | <b>6</b> 2 |

|            | 4.4 Results And Discussions                | 65         |

|            | 4.5 Discussions                            | 73         |

| 5.         | CONCLUSION AND SUGGESTIONS FOR FUTURE WORK | 76         |

| REFERENCES |                                            |            |

| APPE       | NDIX A                                     | 86         |

# LIST Of FIGURES

| Figure |                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------|------|

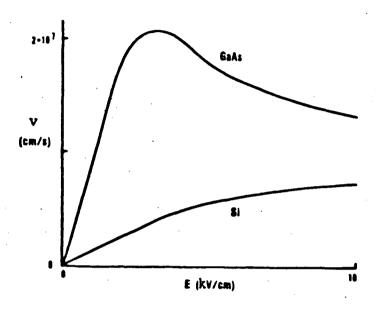

| 1,1,   | Electron velocity as a function of electric field in GaAs and Si                     | 2    |

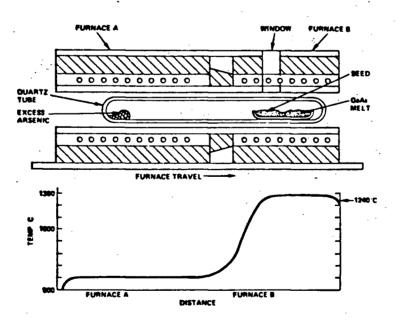

| 2.1.   | Schematic of Bridgman growth                                                         | 6    |

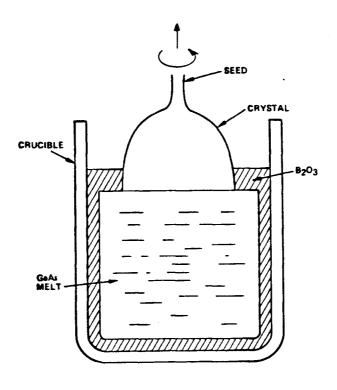

| 2.2.   | Schematic of LEC GaAs growth                                                         | 8    |

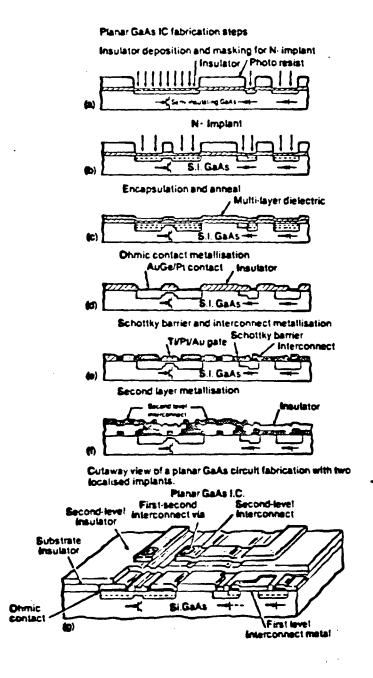

| 2.3.   | Rockwell's planar fabrication process                                                | 11   |

| 2.4.   | SAINT fabrication process                                                            | 12   |

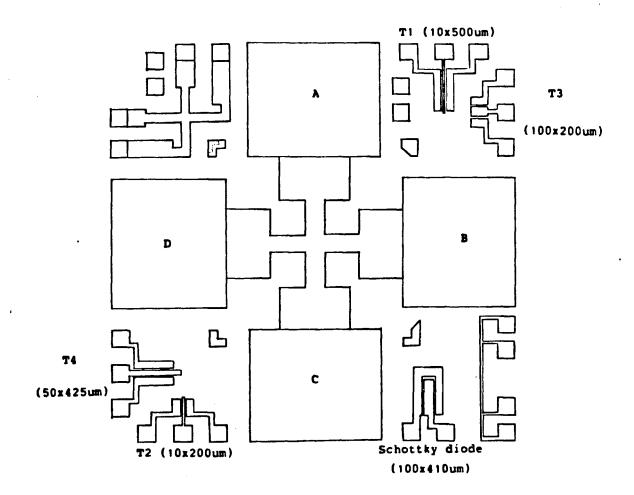

| 3.1.   | Test mask layout                                                                     | 19   |

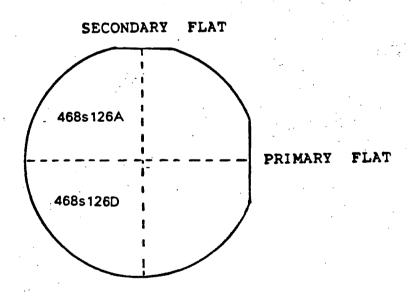

| 3.2.   | Position of the samples on the wafer                                                 | 20   |

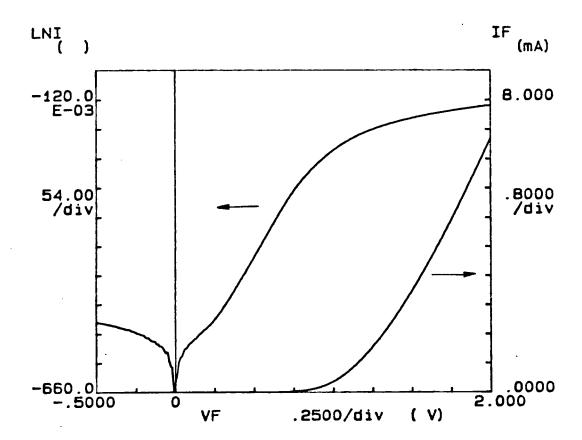

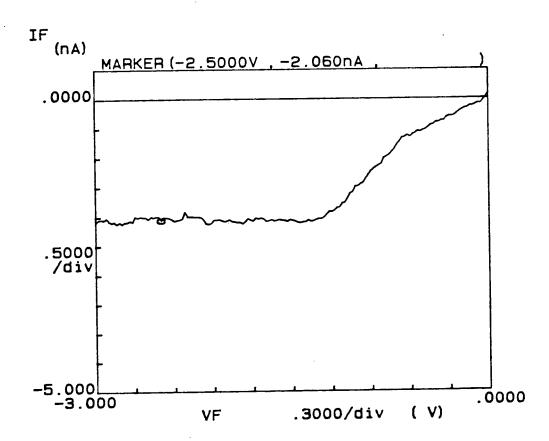

| 3.3.   | Characteristics of the forward diode current                                         | 23   |

| 3.4.   | Characteristics of the reverse diode current                                         | 25   |

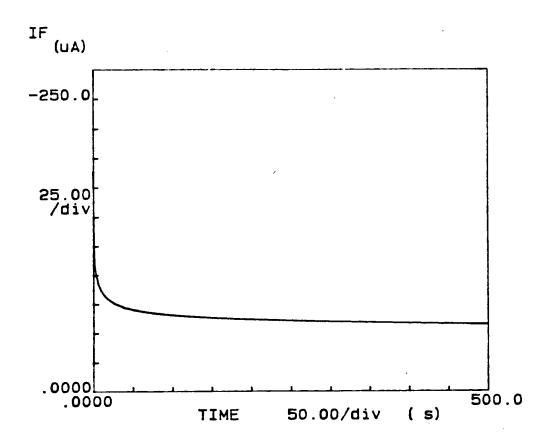

| 3.5.   | Transient in the reverse diode current                                               | 27   |

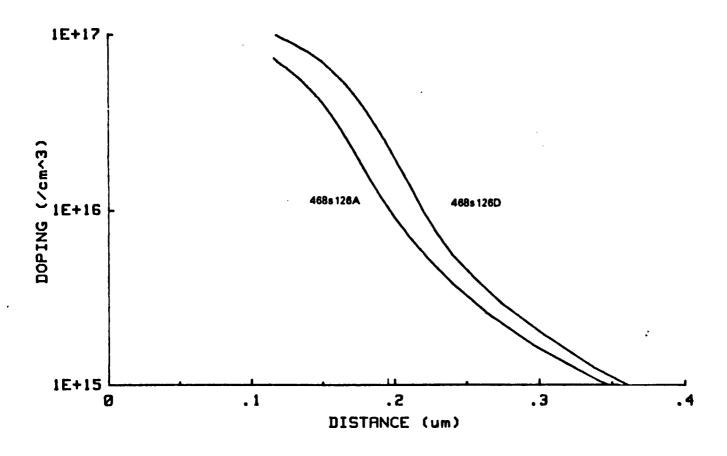

| 3.6.   | Typical doping profiles of samples 468s126A and 468s126D                             | 29   |

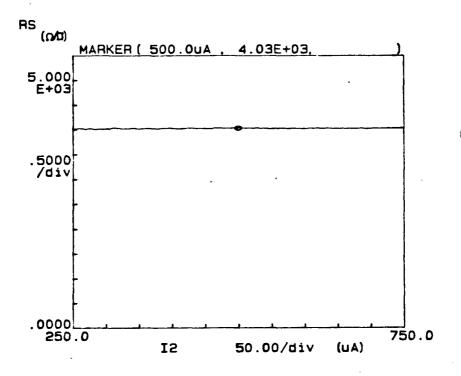

| 3.7.   | Sheet resistance of the implant                                                      | 31   |

| 3,8.   | Drift mobility and doping profile                                                    | 34   |

| 3.9.   | Current voltage characteristics of MESFETs T1, T2, T3 and T4                         | 36   |

| 3.10.  | Measurement set-up for the backgating experiment                                     | 40   |

| 3,11,  | Normalised drain current versus backgate voltage                                     | 41   |

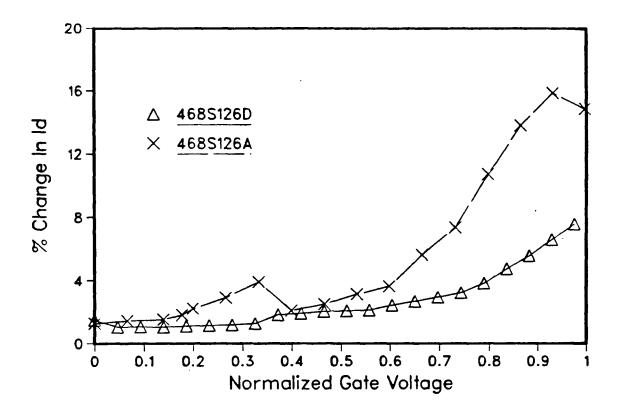

| 3,12.  | Drain current versus normalised gate voltage                                         | 42   |

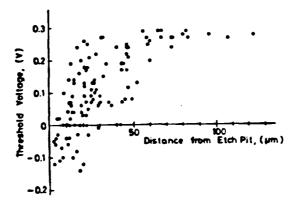

| 4.1.   | Threshold voltage versus distance to nearest dislocation obtained by Miyazawa et al. | 47   |

# LIST OF FIGURES

| Figure |                                                                                               | Page |

|--------|-----------------------------------------------------------------------------------------------|------|

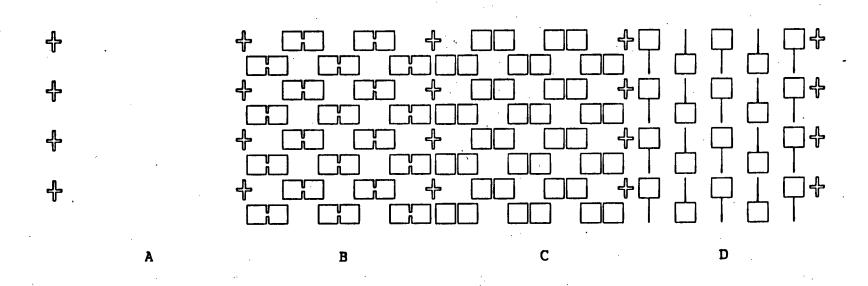

| 4.2.   | MESFET array                                                                                  | 51   |

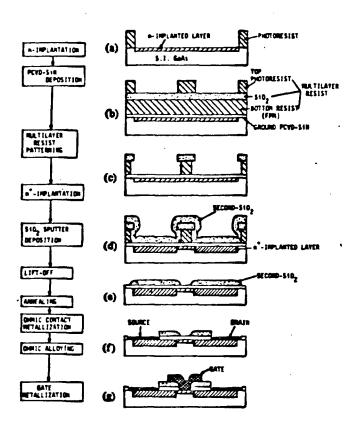

| 4.3.   | Schematic of the fabrication process                                                          | 52   |

| 4.4.   | Fabricated MESFET array                                                                       | 63   |

| 4.5.   | Micro-photograph of the etched sample with the registration marks left behind                 | 65   |

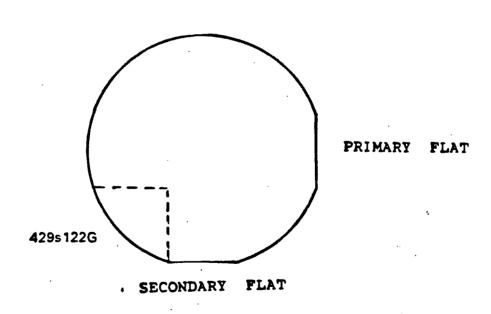

| 4.6.   | Position of sample 429s122G on wafer                                                          | 66   |

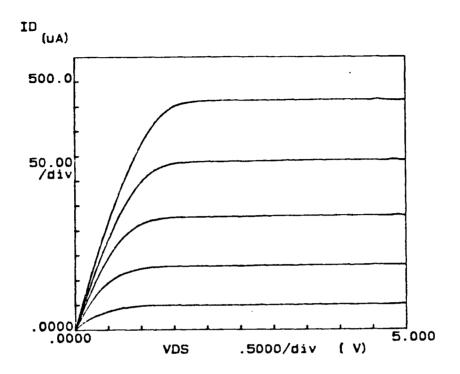

| 4.7.   | Typical MESFET I-V characteristics                                                            | 67   |

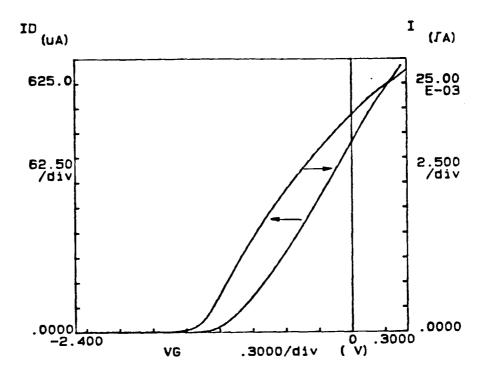

| 4.8.   | I and $\sqrt{I}_d$ versus $V_g$ of the same MESFET in figure 4.7                              | 68   |

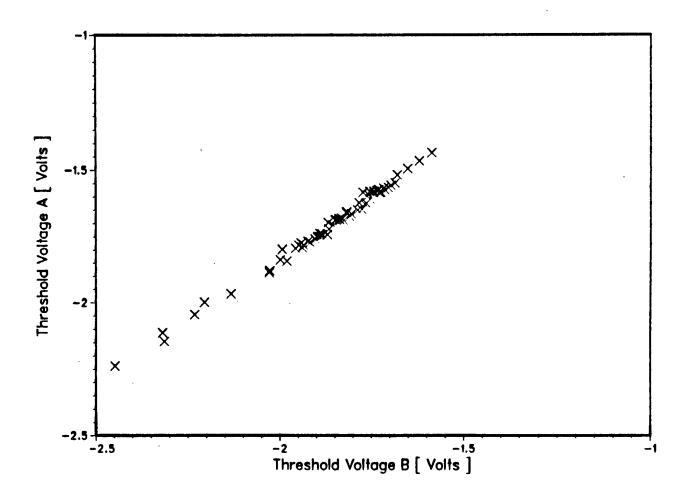

| 4.9.   | Plot of V <sub>tha</sub> versus V <sub>thb</sub>                                              | 69   |

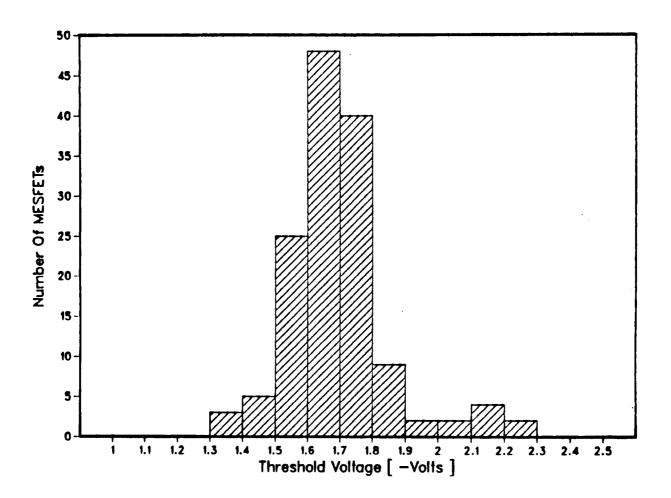

| 4.10.  | Histogram of threshold voltage                                                                | 70   |

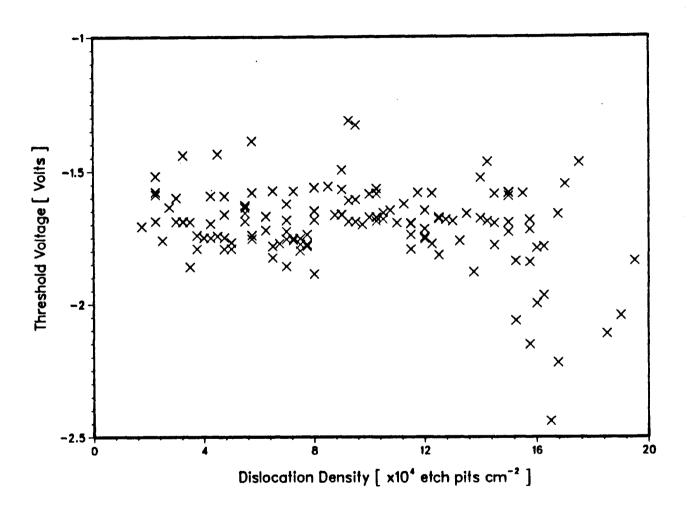

| 4.11.  | Dislocation density versus threshold voltage                                                  | 71   |

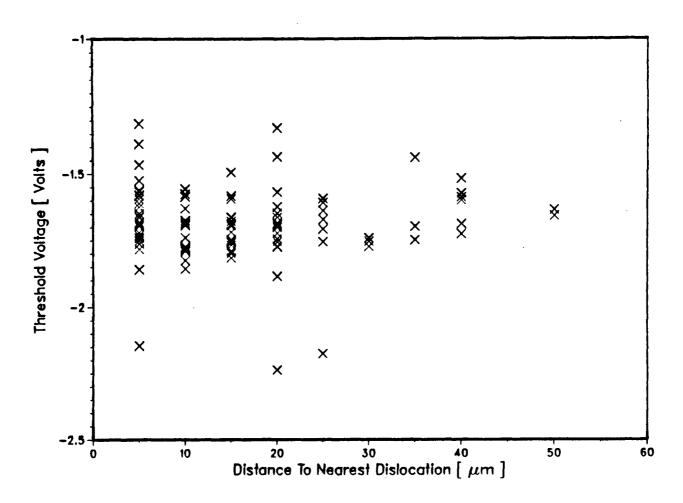

| 4.12.  | Threshold voltage versus distance to nearest dislocation                                      | 72   |

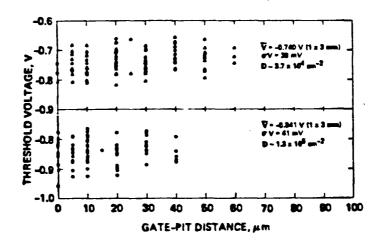

| 4.13.  | Plot of MESFET threshold voltage versus proximity to a dislocation obtained by Winston et al. | 73   |

# LIST OF TABLES

| Table |                                                                       | Page |

|-------|-----------------------------------------------------------------------|------|

| 1.    | Range statistics for Si into GaAs                                     | 14   |

| 2.    | Summary of Schottky metallisation and implanted layer characteristics | 24   |

| 3.    | Summary of MESFETs characteristics                                    | 38   |

| 4.    | Detailed fabrication steps                                            | 55   |

# **ACKNOWLEDGEMENTS**

I would like to thank my supervisor Dr. L. Young for his continual support, patience and guidance during the course of this work. I would also like to thank Dr. P. Yanega for his encouragement and help in the laboratory. Thanks are also extended to W. Tang, D. Hui, P. Townsley, H. Kato, H. Pang, D. Wong and S. Chan for their invaluable discussions.

#### 1. INTRODUCTION

Increasing demand for high speed circuits in digital logic and microwave devices; for example, in real-time signal processing, continuous voice recognition and direct satellite broadcasting has stimulated interest in GaAs [1]. GaAs is electronically superior to Si in that [2]:

- 1. Its 5 to 6 times higher electron mobility than silicon can be exploited for higher speeds.

- 2. The readily available semi-insulating (SI) GaAs substrate reduces interconnect parasitic capacitances and provide a natural way for isolating devices making device isolation simple.

- 3. The low field at which the electron drift velocity saturates in GaAs as compared with Si (figure 1.1) allows the high saturation velocity to be reached at lower voltages than for Si. This lowers power dissipation.

- 4. Other inherent advantages of GaAs over Si include the ability to work at higher temperatures and better resistance to radiation.

However, as with Si technology years ago, GaAs researchers are faced with problems of poor substrate and device uniformity. The fact that GaAs is a compound material makes its processing and synthesis more complicated than those of Si.

Early GaAs devices were fabricated on buffer layers formed using epitaxial techniques. The buffer layer was used to isolate the active layer from the unpredictable substrate. Some problems of the substrate include high residual impurity concentration and surface conversion during thermal treatment [3]. Better control of impurity incorporation during crystal growth has eliminated the need to intentionally dope GaAs with Cr. The Cr compensates shallow donor levels (like that due to Si) rendering the GaAs material SI [4]. The availabilty of purer GaAs wafers has made direct

Figure 1.1: Electron Velocity As A Function Of Electric Field In GaAs and Si [5]

implantation for the formation of the active layer feasible.

Although, the purity of the GaAs substrate has been improved, the substrate requirements for direct ion-implantation are very severe. The work performed here is concerned with processing and materials problems of GaAs. Specifically, (1), the activation process is not fully controllable. This is particularly important for enhancement devices used in direct coupled logic which is the key to very large scale integration (VLSI) as opposed to large scale integration (LSI) for GaAs [6]. (2), as circuits become increasingly complex and dense, the non-uniformity of the substrate can be a problem. Some non-uniformity is commonly attributed to dislocations which are known to follow a W-shaped variation across the wafer [7].

In chapter 2, a brief description of GaAs growth and fabrication technology will be given and two problems associated with the development of GaAs integrated circuits will be identified. In chapter 3, the effects of a surface etch will be studied. Chapter 4 will look into the effects of dislocations in the GaAs crystals on discrete metal semiconductor field effect transistor (MESFET) characteristics. Finally, in chapter 5, a summary of the results obtained and some suggestions for future work will be presented.

#### 2. GAAS GROWTH AND FABRICATION TECHNOLOGY

# 2.1 INTRODUCTION

The first GaAs integrated circuit (IC) was reported by Van Tuyl et al. [8] in 1974. It was made using epitaxial layers on Cr doped SI Bridgman wafers. Since then, GaAs ICs with increasing complexity have been demonstrated. They are based on the availability of large undoped SI liquid-encapsulated Czochralski (LEC) GaAs wafers and the change to direct ion-implantation technology requiring no epitaxial buffer layer.

Undoped GaAs wafers of 3 inch diameter can now be routinely produced with LEC pullers. Current improvements in the growth technology include the use of magnetic field during crystal growth [9] and the addition of In to reduce crystal defects [10]. Lower impurity content and the large size and round shape has made undoped LEC GaAs the preferred substrate over Bridgman GaAs.

Ion-implantation directly into the SI substrate provides reasonably good control of the dopant profile. With the aid of an implant mask, good selectivity of the implant area can be achieved. In addition, planar fabrication using ion implantation to form the active layer has a higher throughput and a lower cost. The emergence of rapid thermal annealing techniques make it possible to cure an implant area in seconds. This reduces impurity diffusion which could prevent the control of the doping in the thin active layer of MESFETs to the extent needed for good device threshold voltage uniformity. Most GaAs logic are still based on depletion devices because of the difficulty of making good enhancement transistors with uniform threshold voltage and high transconductance, Depletion devices, for example in buffered field effect transistor logic (BFL) and Schottky

diode field effect transistor logic (SDFL), require level shifting and could cause power dissipation problems in densely packed circuits [2].

In the next section we will discuss the development of GaAs crystal growth.

# 2.2 CRYSTAL GROWTH

Until recently, most SI GaAs was made by the Bridgman process. In Bridgman growth [11], the polycrystalline GaAs melt is contained in a boat usually made of quartz. To promote crystallisation, the melt is cooled from one end of the crucible to the other. In order to achieve GaAs of a specific orientation, a seed of that orientation is placed at the end of the crucible where the melt is first cooled. Figure 2.1 gives a schematic of the

Figure 2.1: Schematic Of Bridgman Growth [11]

Bridgman growth apparatus. Characteristically, D-shaped slices obtained from Bridgman grown GaAs are a deterrent to achieving a cost effective manufacturing technology because much of the standard processing equipment for silicon technology relies on large round substrates [12]. Although it is true that Bridgman wafers generally have lower and more uniform dislocation density because of less stress due to slower cooling they are plagued with the problem of Cr redistribution as Cr is required to compensate shallow donors such as Si [4].

Fused quartz boats that are used to hold the melt tend to dope the GaAs with Si which is a shallow donor when present on a Ga site. As mentioned above, Cr was added to the melt to compensate the shallow donor level created by Si. However the intentionally introduced impurity, Cr, accumulates at the surface when the material is subjected to temperatures of 800°C or higher, for 30 minutes or longer during post implant anneal [13]. As a result, a deficit of Cr is created just beneath the surface, causing the slice to convert to n-type. In addition, Cr also reduces electron mobility in the channel because of increased impurity scattering [14]. Consequently, an epitaxial buffer layer was used. The channel can be formed either by a n-type buffer layer or by direct ion-implantation into Cr-free epitaxial SI GaAs.

The problems associated with Cr are no longer an issue because the SI property of GaAs can now be attained without Cr. The present state of the art LEC pullers grow undoped SI and high purity ingots by using pyrolytic boron nitride (PBN) crucibles and extremely pure Ga and As. In undoped SI substrates, the SI property is believed to be the result of a deep donor known as EL2 compensating shallow acceptors the most abundant of which is carbon [15]. Although the identity of EL2 is not

established, there is evidence from electron spin resonance (ESR) studies that the antisite defect As on a Ga site formed during post-growth annealing is involved [16]. Midgap level EL2 concentration is strongly affected by melt composition [17].

The LEC process is a variation of the Czochralski method used for pulling silicon ingots [18]. Modifications have to be made to the original Czochralski process because GaAs tends to dissociate into its constituent elements when it is heated over 400°C. This is caused by the high vapour pressure of arsenic at temperatures over 400°C. As the the name implies, LEC growth uses an inert molten layer of B<sub>2</sub>O<sub>3</sub> to cap the melt. To prevent As from bubbling through the B<sub>2</sub>O<sub>3</sub> encapsulant, the growth chamber is pressurised by an inert gas such as Ar or Ne. The B<sub>2</sub>O<sub>3</sub> layer has an added advantage in that a film of that liquid remains on the GaAs as it crystalises preventing As loss from the solidified but still hot crystals. The H<sub>2</sub>O content of the B<sub>2</sub>O<sub>3</sub> encapsulant also has an effect on the purity of resulting ingot. Specifically, the incorporation of C, B and Si can be suppressed by increasing the H<sub>2</sub>O content of B<sub>2</sub>O<sub>3</sub> [19].

The GaAs charge for LEC growth using the high pressure Melbourn pullers (as used by Cominco) is formed in situ because a purer charge is obtained. Essentially, LEC growth involves inserting a GaAs seed of the required orientation through the B<sub>2</sub>O<sub>3</sub> layer into the melt which is contained in a graphite or PBN crucible. The seed is then slowly pulled out of the melt, typically at speeds of 10 millimeters per hour. A schematic of GaAs growth by LEC is given in figure 2.2. The crystal grows by progressive freezing at the liquid-solid interface. To minimise thermal forces during freezing, the liquid-solid interface must be kept as flat as possible. This flatness is obtained by spinning the seed as it is pulled out of the melt

Figure 2,2: Schematic Of LEC GaAs Growth [18]

and often, the crucible is simultaneously counter rotated.

Despite all the recent advances in crystal technology, growth of boules with uniform properties is still not possible. Thomas et al. [20] have found that undoped SI boules grown in PBN crucibles by the high pressure LEC technique exhibit a seed to tail increase in resistivity. Across the wafer, Holmes et al. [21] confirmed the W-shaped of the EL2 profile observed by Martin et al. [22] only at the seed section of the boule. Towards the tail end, the distribution becomes more diffuse and uniform.

# 2.3 PLANAR FABRICATION TECHNOLOGY

The two GaAs based field effect transistors (FETs) are the MESFET and junction field effect transistor (JFET). The MESFET is by far the dominant GaAs device because its Schottky gate is much easier to fabricate than the PN junction in the JFET. The GaAs MESFET was first proposed by Mead [23] in 1966 and subsequently fabricated by Hooper et al. [24] using a GaAs epitaxial layer. Bipolar transistors on GaAs are also possible. The two types of bipolar transistors demonstrated are homojunction [25] and heterojunction [26] transistor. The former can be fabricated using ion implantation but the latter requires sophisticated molecular beam epitaxy to grow the GaAs-AlGaAs heterojunction needed.

In order to achieve the degree of integration of GaAs ICs demonstrated, for example at a recent conference [27], such as the 1K gate array, 12 bit digital to analog converter and 8:1 multiplexer, among others, a controlled and reproducible fabrication technology must exist. Planar fabrication technology, like the one used at Rockwell meets the requirements of such a process [28]. Direct ion-implantation is the key to a viable planar fabrication technology. It provides better selectivity and higher throughput than earlier epitaxial techniques which help to reduce device fabrication cost.

Planar processes rely on ion implantation for the formation of the active layer and the SI substrate for isolation [28] except that if a blanket implant is used activation is followed by an isolation implant or a 'MESA' etch. H or B ions [29] are used to create a damage layer for isolation. In the Rockwell process illustrated in figure 2.3, the SI is used for isolation. Conventional MESFETs such as those produced by the Rockwell process have high gate to source and gate to drain series resistances which limit

Figure 2.3: Rockwell's Planar Fabrication Process [28]

the speed and the tranconductance [30]. To reduce these parasitic resistances, a high concentration region is placed immediately adjacent to the gate. Self-aligned gate (SAG) techniques are used to fabricate devices with extremely low gate to drain and gate to source resistances. The self-aligned implantation for N<sup>+</sup> layer technology (SAINT) process illustrated in figure 2.4 uses a SiO<sub>2</sub>/resist dummy gate to 'align' the gate [31]. Other SAG processes use refractory metal gates because the gate metal, like TiW [32] or PtAu [33], is deposited before annealing.

# 2,3,1 ION IMPLANTATION

Ion implantation (ie the injection of energetic ions into a substrate) dominates over diffusion for doping GaAs. Si, Se, S and Sn are the most commonly used materials to dope GaAs n-type.

To use ion implantation effectively, it is important to know the distribution of the dopant as a function of depth. This information is given by the LSS theory developed by Lindhard, Scharff and Shiott [34]. It is derived for an amorphous target. The dopant density according to the LSS theory is Gaussian in nature and can be written as,

$$N(x) = \frac{\phi}{\sigma_{p} \sqrt{(2\pi)}} \exp\left[-\frac{(x - R_{p})^{2}}{2(\sigma_{p})^{2}}\right]$$

(2.1)

where  $\phi$  is the implant dose, x the depth into the surface,  $R_p$  the mean projected range, and  $\sigma_p$  the standard deviation in the projected range. Hence, given the dose and the energy of an implant, the resulting implant profile can be calculated with the equation above and range statistics data compiled by Gibbon et al. [35] to obtain  $R_p$  and  $\sigma_p$ . Range statistics data for Si into GaAs is given in table 1. This particular set of statistics is

Figure 2.4: SAINT Fabrication Process [31]

given because in the fabrication process used for this thesis, silicon 28 ions are used for the active channel implant.

It has been found that near the edge of the masking material, there is also a lateral dependence to the distribution function. Furukawa et al. [36] have shown that the resulting complex distribution is the product of a Gaussian function and complementary error function. The distribution is represented by the following:

$$N(x) = \frac{\phi}{\sigma_{p} \sqrt{(2\pi)}} \exp\left[-\frac{(x - R_{p})^{2}}{2(\sigma_{p})^{2}}\right] \frac{1}{\sqrt{\pi}} \operatorname{erfc}\left[\frac{y - a}{\sigma_{y} \sqrt{2}}\right] \quad (2.2)$$

where y is the lateral distance from the edge of the mask,  $\sigma_y$  its standard deviation and the rest of the variables have the same meaning as above. This lateral diffusion of the implant can increase the gate parasitic capacitance, especially in the case of SAG MESFET. It is speculated that the extent of this lateral diffusion is also orientation dependent [37].

Table 1: Range Statistics Data For Silicon 28 Into GaAs

| Energy | Projected | Projected | · Lateral |

|--------|-----------|-----------|-----------|

|        | Range     | Standard  | Standard  |

|        |           | Deviation | Deviation |

| (keV)  | (micron)  | (micron)  | (micron)  |

| 60     | 0.0507    | 0.0294    | 0.0399    |

| 80     | 0.0677    | 0.0370    | 0.0508    |

| 100    | 0.0850    | 0.0442    | 0.0615    |

| 120    | 0.1025    | 0.0510    | 0.0717    |

| 150    | 0.1291    | 0.0607    | 0.0866    |

# 2.3.2 ANNEALING

Annealing is necessary after ion implantation to repair lattice damage and to activate the implant. To keep the surface intact during furnace annealing, which is typically performed at temperatures greater than 800°C one of the following steps can be taken:

- 1. Encapsulating the surface with a dielectric.

- 2. As over-pressure.

- 3. Covering the sample with a slice of GaAs.

The most common dielectric encapsulants on GaAs are  $SiO_2$  and  $Si_3N_4$ . Sometimes a combination of both materials has been used to reduce

stress. Stress introduced by encapsulants during annealing has been shown to affect the profile of the dopant [38]. This stress is eliminated in capless annealing where an arsine overpressure is used to minimise arsenic vacancy so that amphoteric Si will activate predominantly on gallium sites. In proximity annealing, the GaAs slice placed on top of the wafer to be annealed presumably supplies the arsine overpressure during annealing to minimise As loss.

In so-called rapid thermal annealing techniques [39], lasers, arc lamps or halogen lamps are used to anneal implants in a few seconds. The short annealing time prevent anomalous impurity and dopant profile diffusion that occur during the longer furnace annealing. Hence, a sharper profile is normally obtained with these newer techniques. What is more, under optimised conditions, the activation efficiency of the newer annealing techniques can be higher than the best figures achieved with the furnace. However, rapid thermal annealing can result in larger DC parameter variations than furnace annealing if uniform heating is not achieved [40].

# 2.3.3 OHMIC CONTACTS

Achieving a good ohmic contact is important for any fabrication process. A eutectic mixture of 12%Ge:88%Au is the most common ohmic contact system for n-type GaAs. Ni is often evaporated on top of the Au-Ge because a smooth contact is obtained [41].

The three mechanisms responsible for current flow in a metal semiconductor contact are thermionic emission, Schottky field emission and tunneling [42]. The dominant mechanism will depend on the barrier height and doping density. The barrier height observed on n-type GaAs is essentially constant (0,8eV) regardless of the metal used. It is therefore not

possible to reduce the barrier height by proper choice of the metal alone. The normal strategy used to achieve good ohmic contacts to n-type GaAs is to dope the GaAs sufficiently high enough so that tunneling becomes dominant.

During alloying of Au-Ge, Ga diffuses out from the surface and Ge from the eutectic Au-Ge mix diffuses into the GaAs occupying vacant Ga sites [43]. Since Ge acts as a donor on Ga sites, a heavily doped n-type region is formed near the surface. As a result, the width of the potential barrier is decreased making tunneling more probable. Interfacial oxide presents a further barrier to current flow.

### 2.4 PRESENT PROBLEMS

Two prevalent problems with current MESFET technology are the non-uniformity of the wafer and reproducibility from ingot to ingot in ion implantation and activation. One aspect of the problems is the surface. Residual impurities and defects appear to be concentrated at the surface and they can affect the activation of implanted dopant. It is of interest to device manufacturers to know if the top layer of the starting substrate should be removed. Another aspect of the problems is the dislocations present in the wafer. Dislocations affect device uniformity and will limit the yields of circuits in the VLSI level because MESFETs threshold voltage cannot deviate by more than 5 per cent [44]. Hence, it is vital that the properties be of dislocations on device understood and effects characterised.

# 3. EFFECTS OF REMOVAL OF SURFACE LAYER ON DEVICE CHARACTERISTICS

# 3.1 INTRODUCTION

Commercially available GaAs wafers have already been chemically and mechanically polished into a high quality mirror finish. In spite of this, our understanding is that they are frequently subjected by device manufacturers to a surface etch before device fabrication. The reason is presumably that this improves device characteristics but little has been published on this topic. However, recently Dzioba [45] in an abstract of a paper has reported the presence of a subsurface damaged layer of 1–2µm on etch (100) LEC GaAs wafers. He also obtained better activation percentage on etched samples. GaAs wafers are sometimes annealed before an etch is performed. Annealing, in addition to producing a more uniform substrate, also drives impurities like Cu, Mg and Mn to the surface [46] so that they can be subsequently removed by a surface etch.

Surface etching plays an essential role in device fabrication technology. For example, it is widely used for patterning the surface for mask alignment and isolation as in 'MESA' etching. Etching normally proceeds by oxidation-reduction-complexing reactions [47]. The GaAs surface can be etched by a variety of etchants. Some of the common etchants include H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O, NaOH:H<sub>2</sub>O<sub>2</sub> and NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O. The resulting surface has been found to be dependent on the etch rate and the specific etchant used.

Most of the work on the surface treatment of GaAs has concentrated on the effects after the active layer has been formed. For example in Schottky or ohmic contacts, it is well reported that a light

surface etch performed just prior to metal evaporation improves the electrical characteristics of the contacts [48]. In this study the effects of a surface layer removal on the Schottky metallisation, the profile of the Si-implant and device characteristics were investigated. Devices were fabricated on undoped LEC (100) GaAs wafers. The wafers were not annealed before etching.

# 3.2 DIAGNOSTIC PATTERN

The test pattern was based on that of Immorlica et al. [49]. These test patterns are commonly incorporated into fabrication masks so that important fabrication data on process steps can be collected. A layout of the pattern with important device dimensions is given in figure 3.1. The pattern contains:

- 1. A Schottky diode, D1, to evaluate the doping profile and gate metallisation.

- 2. Four different MESFETs, T1-T4, to monitor the effects of the etch on device characteristics.

- 3. MESFET T3, known as the FATFET, is also used to obtain the drift mobility profile of the active layer [50].

- 4. A van der Pauw cross to measure the sheet resistance and Hall mobility [51].

# 3,3 DEVICE FABRICATION AND EXPERIMENTAL PROCEDURE

The devices were fabricated on undoped LEC (100) GaAs wafer supplied by Cominco Ltd. The fabrication steps used are listed in Table 4 on page 55. The wafer was first diced and pre-cleaned to step 1b in the table before etching. The etchant used was 5NH<sub>4</sub>OH:2H<sub>2</sub>O<sub>2</sub>:240H<sub>2</sub>O.

Figure 3.1: Test Mask Layout

Approximately  $2\mu m$  of GaAs was removed in a fresh mixture of the etchant which has an etch rate of 2000 angstroms per minute. This etch rate was determined with the aid of the Tencor Alpha Step 200 profiler. The rest of the fabrications steps used are as listed in table 4. The implant energy and dose were fixed, they were 80 keV and 3,37  $\times$  10<sup>12</sup> ions per cm<sup>2</sup> respectively.

Samples 468s126A and 468s126D as depicted in figure 3.2 are made up of two quadrants of slice 468s126. Sample 468s126D has been subjected to a  $2\mu m$  surface etch using the procedures described in the above paragraph. It retained its mirror-like surface after the etch indicating that no visible surface damage was introduced. There were also no abnormal

Figure 3.2: Position Of The Samples On The Wafer

features in the dark field image of the surface. Based on experience in the laboratory, samples have to be pre-cleaned to produce a featureless etch. Also, a fresh solution of the etchant was used each time because its etch rate decreases with time.

# 3.4 SCHOTTKY METAL EVALUATION

The Schottky contact formed between a semiconductor and metal is extremely sensitive to the nature of the interface. Consequently, it has frequently been used to investigate surface damage caused by processing steps. The electrical characteristics of Schottky contacts can be evaluated by measuring their barrier heights, ideality factors, leakage currents or breakdown voltages. Metal or metal systems that have been used to form Schottky barriers for GaAs diodes and MESFET gates include TiW, and Al.

The barrier height  $(\phi)$  and ideality factor (n) were derived by analysing the Schottky diode current in accordance with the thermionic emission model. The model expresses the current, I, as [42]:

$$I = SA^{**}T^{2}exp \left(-\frac{q\phi}{m}\right)\left[exp \frac{qV}{nkT} - 1\right]$$

(3.1)

where V, T, k, S and  $A^{**}$  are the voltage applied, the temperature, the Boltzmann's constant, the Schottky contact area and the Richardson constant respectively. If the diode is slightly forward biased, V > 3kT/q, equation 3.1 can be rewritten as:

$$I = I_{s} exp(\frac{qV}{nkT})$$

(3.2)

where

$$I_{S} = SA^{**}T^{2}exp(-\frac{q\phi}{kT})$$

(3.3)

$I_s$  is the Schottky diode saturation current. The current voltage (I-V) characteristic of a typical forward biased diode is given in figure 3.3. The ideality factor can be determined using the following relation:

$$n = \frac{q}{\Delta kT}$$

(3.4)

where  $\Delta$  is the slope of the  $\iota n(I)$  versus V plot. With the value of the y-intercept,  $I_s$ , the barrier height can be evaluated as follows:

$$\phi = -\frac{kT}{q} \ln\left(\frac{I_S}{SA^{**}T^2}\right)$$

(3.5)

The n,  $\phi$  and leakage current (I<sub>L</sub>) of all the Schotty contacts on samples 468s126A and 468s126D were measured. The equations used to evaluate n and  $\phi$  are equations 3.4 and 3.5 respectively. The leakage current was defined as the diode current when a voltage of -2.5 volts was applied. A plot of the reverse biased diode current is given in figure 3.4. Table 2 gives a summary of the diode characteristics measured.

Figure 3,3: Characteristics Of The Forward Diode Current

Table 2: Summary Of Schottky Metallisation And Implanted Layer

Characteristics

| Sample                                     | 468s126A   | 468s126D |

|--------------------------------------------|------------|----------|

|                                            | (UNETCHED) | (ETCHED) |

| n                                          | 1.31       | 1.79     |

| Scatter in n                               | 0.18       | 0.28     |

| φ (eV)                                     | 0.72       | 0.70     |

| Scatter in $\phi$                          | 0.03       | 0.05     |

| I <sub>L</sub> (μA)                        | 10.77      | 13.71    |

| Scatter in I <sub>L</sub>                  | 1.10       | 1.30     |

| W <sub>o</sub> (A)                         | 1957       | 2160     |

| Scatter in Wo                              | 111        | 90       |

| W, (A)                                     | 3406       | 3623     |

| Scatter in W <sub>1</sub>                  | 229        | 231      |

| $\mu_{\text{peak}}$ (cm <sup>2</sup> /V-s) | 3886       | 3627     |

| Scatter in µ <sub>peak</sub>               | 165        | 166      |

| R <sub>s</sub> (kΩ/m)                      | 3.26       | 2.69     |

| Scatter in R <sub>s</sub>                  | 0.42       | 0.18     |

| $\mu_{\rm H}$ (cm <sup>2</sup> /V-s)       | 4349       | 4406     |

| Scatter in $\mu_{\mathrm{H}}$              | 204        | 385      |

| η (%)                                      | 12.24      | 15.86    |

| Scatter in $\eta$                          | 1.4        | 1.1      |

|                                            |            |          |

Figure 3.4: Characteristics Of The Reverse Diode Current

Figure 3.5: Transient In The Reverse Diode Current

A 30 seconds wait time was incorporated into the measurement routines of all the parameters. This was done to avoid the large transient in the current that occured immediately after a measurement was started. The transient was especially evident when measuring the small leakage current as depicted in figure 3.5.

The average value of n and the leakage current was larger while that of  $\phi$  was smaller on the sample that has received a surface etch. Hence, slightly poorer diode characteristics were obtained on the etched sample. This can be ascribed to surface damage caused by the etchant. The nature of the surface damage introduced cannot be detected using Schottky contacts. The uniformity of the diode characteristics also deteriorated after the etch. This is not surprising because chemical etches are not known for their uniformity.

# 2.5 IMPLANT LAYER CHARACTERISATION

In this section the electrical characteristics of the active layer will be evaluated. They include the doping profile, the sheet resistance, Hall mobility and drift mobility.

### 2.5.1 DOPING PROFILE

The doping profile was evaluated using the C-V [42] technique which expresses the carrier density, N(x) as,

$$N(x) = -\frac{C^3}{q \epsilon A^2} \frac{\partial V}{\partial C}$$

(3.6)

where C, A, q and  $\epsilon$  are the capacitance, the Schottky contact area, the electronic charge and the permittivity respectively. C is related to the depth

of the profile, x by,

$$C(x) = \frac{\epsilon \lambda}{x} \tag{3.7}$$

A depletion layer is present at zero gate voltage because of the work function difference between the semiconductor and the metal and the presence of surface states. To profile very close to the surface, the diode is usually slightly forward biased but the resultant forward current prevents much improvement over scanning from zero volt. This is evident in the doping profiles given in figure 3.6 which were scanned from a gate of 0.25 volt. The profile depth on the other hand is limited by the breakdown voltage of the diode. This constraint is usually not a problem with the implant dose and energy used in active channels of low power MESFETs.

The capacitance of the diode was measured at 1 MHz using a HP 4275A LCR meter. The experimental set up used to obtain the doping profile in addition to the LCR meter included a HP 9816 computer, a Wentworth Labs probe station and an electrically shielded box.

The depth of the peak carrier concentration is directly related to the implant energy used. In all the profiles obtained, the small implant energy, 80 keV, did not allow the peak to be profiled because it lay within the zero gate voltage depletion region. As a result, the depth of the profile when the carrier concentration are  $10^{15}$  and  $10^{16}$  per cm³ ( $W_1$  and  $W_0$  respectively) were recorded and summarised in Table 2. Compared with the unetched sample, the implant on the etched sample on the average went deeper into the substrate. Figure 3.6 gives the typical profile on samples 468s126A and 468s126D. It can be seen that activation was generally higher on the etched wafer. However, the sheet carrier concentration and

Figure 3.6: Typical Doping Profile Of Samples 468s126A and 468s126D

subsequently the percentage activation cannot be calculated from the profiles because the peak carrier concentration and its depth from the surface cannot be determined. The activation efficiency, can be evaluated using the van der Pauw cross in the next section.

#### 2.5.2 SHEET RESISTANCE

The sheet resistance of the implanted layer was evaluated using van der Pauw's method with the aid of the van der Pauw cross (figure 3.1). The sheet resistance is written as [51],

$$R_{S} = \frac{\pi V_{CD}}{in(2)I_{AB}}$$

(3.8)

where  $I_{AB}$  is the current applied between adjacent electrodes, A and B, and  $V_{CD}$  the voltage measured at the other pair of electrodes, C and D. The HP 4145A semiconductor parameter analyser (SPA) was used to both measure the voltage and source the current.

A plot of sheet resistance as a function of applied current is given in figure 3.7. The sheet resistance was defined as the value obtained when the current between electrodes A and B of the van der Pauw cross was  $500\mu$ A. This current was chosen arbitrarily and should not have any bearing on the reading because the sheet resistance is essentially constant as can be seen in figure 3.7.

The sheet resistances of sample 468s126A and 468s126D are given in Table 2. A smaller sheet resistance was obtained for the etched sample. This follows directly from the higher carrier concentration observed in the doping profiles of the etched sample. In addition, the sheet resistance uniformity was also better on the etched substrate.

Figure 3.7: Sheet Resistance Of The Implant

The Hall mobility was also measured using the van der Pauw cross. In this case, the sample was placed on a probe holder instead of the probe station. A magnetic field of 0 to 0.2 tesla was applied perpendicular to the sample using an Alpha Scientific Laboratories magnet. A constant current of  $250\,\mu\text{A}$  was also applied between the opposite ends of the van der Pauw cross while the voltage in the remaining two ends was monitored. The Hall mobility  $\mu_{\text{H}}$  is given by [60],

$$\mu_{\rm H} = \frac{V_{\rm BD}}{(R_{\rm S}BI_{\rm AC})} \tag{3.9}$$

where

$I_{AC}$ ,  $V_{BD}$ , B and  $R_{S}$  is the current applied between electrodes A and C (figure 3.1), the voltage measured between electrodes B and D, the magnetic field applied and the sheet resistance respectively.

The activation efficiency,  $\eta$ , can be calculated using the R and  $\mu_{\rm H}$ .  $\eta$  is defined as:

$$\eta = \frac{N}{D} \tag{3.10}$$

where D is the implant dose and N the undepleted sheet carrier concentration which can be evaluated using the following relation.

$$N = \frac{1}{(q\mu_H R_s)} \tag{3.11}$$

As a result, equation 3.10 can be rewritten as,

$$n = \frac{1}{(Dq\mu_H R_s)}$$

(3.12)

The Hall mobility and the activation efficiency were determined using equations 3.9 and 3.12 respectively. The average value of both parameters obtained were slightly higher on the etched sample (Table 2), implying that the removal of the surface layer resulted in a marginally better substrate for direct ion implantation.

### 2.5.3 DRIFT MOBILITY PROFILE

Because the drift mobility  $(\mu)$  is a function of the traps present in the channel, it can be used to assess the quality of the implanted layer. An approximate  $\mu$  value can be obtained using the technique invented by

Pucel and Krumn [50] which expresses the  $\mu$  as:

$$\mu = \frac{g_m L^2}{(c_q v_{ds})} \tag{3.13}$$

where  $g_m$ , L,  $C_g$ , and  $V_{ds}$  are the transconductance, gate length, gate capacitance and drain source voltage respectively. All the measurements needed to obtain the  $\mu$  profile were performed on FATFET T3. The  $C_g$  was measured using the LCR meter with the drain and source electrodes tied together. To measure the  $g_m$ , the SPA was used. Only 50mv was applied across the drain and source electrodes so that the cross-section of the undepleted channel was essentially constant. The  $g_m$  at a particular voltage is defined as the slope of  $I_d$  as a function of  $V_g$  plot at that voltage.

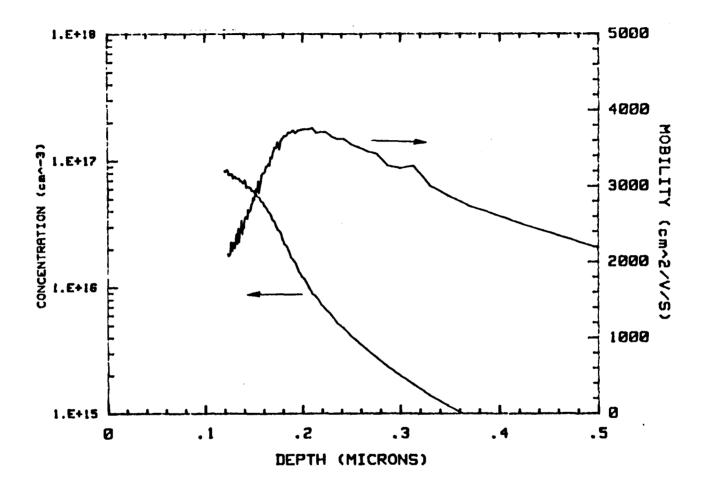

A profile of the  $\mu$  is given in figure 3.8. On the same figure, the corresponding doping profile is also plotted. The same characteristics  $\mu$  profile was seen in all the FATFETs tested. The average peak mobility was calculated from the profiles (Table 2).

The  $\mu$  profile increases to a peak from the surface and decreases from the peak towards the substrate. This agrees with the result of Lee et al. [52]. It has been suggested that the  $\mu$  profiles decrease towards the substrate because of implant damage at the active layer substrate interface that has not been annealed away [53]. Although, a higher carrier concentration was observed on the etched sample, its average peak mobility was smaller. It is not known for certain at this point why this is the case. This discrepancy could be caused by the inferior Schottky diode characteristics obtained on the etched sample.

Figure 3.8: Drift Mobility And Doping Profile

#### 3.6 DEVICE PERFORMANCE

In characterising the fabricated MESFETs, we measured the following parameters:  $V_{th}$ , K,  $I_{dss}$  and  $g_m$ . They are the threshold voltage, the K-factor, the saturation drain current with zero applied gate voltage and the transconductance respectively. A listing of the program used for determining the four parameters is given in appendix A.

Above the saturation region, the dependence of drain current of MESFETs on gate voltage is essentially quadratic and can be written as [42]:

$$I_d = K(V_q - V_{th})^2$$

(3.14)

with the K-factor defined as,

$$K = \frac{\mu \epsilon W}{2aL}$$

(3.15)

where W is the gate width, L the gate length, a the channel thickness  $\mu$  the drift mobility and  $\epsilon$  the permittivity.

The  $I_d^{-V}_g$  characteristics of all the MESFETs were measured for a drain-source voltage of 2.5 volts. The  $V_{th}$  in the program is defined as the gate voltage when the drain current is  $5\mu A$ . The K-factor is the square of the slope of the  $\sqrt{I}_d$  as a function of  $V_g$  plot. The  $g_m$  is defined as the the slope of  $I_d$  versus  $V_g$  plot between a gate voltage of 0 and -0.1 volt.

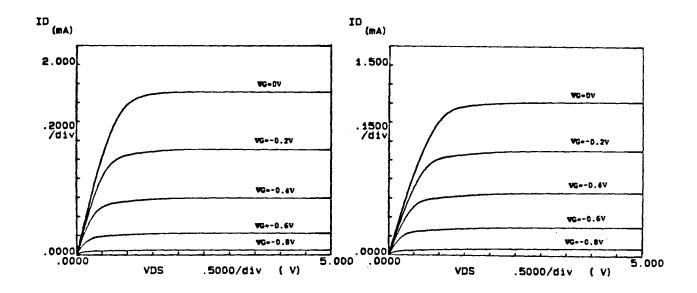

All the DC parameters measured on the MESFETs are listed in table

3. Figure 3.9 gives a plot of the I-V for each of the MESFETs (T1-T4) on

the test structure. On all the MESFETs except T3 the following trends were

T1 T2

T3 T4

Figure 3.9: Current Voltage Characteristics Of MESFET T1, T2, T3 and T4

observed on the sample that has received a surface removal before device fabrications:

- 1.  $V_{\text{th}}$  was more negative

- 2. I des became larger

- 3.  $g_m$  became larger

- 4. K-factor became larger

Although the MESFETs tested were not designed with optimal transistor characteristics, it can still be inferred from the results that the removal of the surface layer just prior to device fabrication improved device characteristics. Since the K-factor is proportional to  $\mu/a$  (equation 3.15) and the channel was deeper on the etched sample in comparison with the unetched sample (from doping profiles), a higher K-factor obtained on the etched sample implies that the implanted channel also has better transport characteristics.

The  $I_{dss}$  of T3 followed the trend of the other transistors but its  ${f V}_{f +\, f h}$  became more negative on the unetched sample despite of the smaller  $I_{dss}$  present. This, the smaller K-factor and  $g_{m}$  have prompted us to speculate that channels of FATFET T3 on 468s126A were the the gates. This can result from a completely covered by misalignment. As can be seen in figure 3.1 which gives a layout of the test mask, the gate of T3 does not overlap its channel as much as the gates of the other MESFETs. Hence, a slight misalignment can in fact result in the channel of MESFET T3 not being entirely covered.

Table 3: Summary Of MESFET Characteristics

|           |       | Vth   | K-factor      | Idss    | Gm      |

|-----------|-------|-------|---------------|---------|---------|

|           |       | (v)   | $(\mu m/V^2)$ | (A)     | (ms/mm) |

| MESFET T1 |       |       |               |         |         |

| 468s126A  | Ave.  | -0.82 | 1.77E3        | 1.17E-3 | ·3.91   |

|           | Sdev. | 0.11  | 0.29E3        | 0.30E-3 | 0.75    |

| 468s126D  | Ave.  | -1.21 | 1.87E3        | 2.38E-3 | 5.99    |

|           | Sdev. | 0.31  | 0.18E3        | 0.55E-3 | 0.56    |

| MESFET T2 |       |       |               |         |         |

| 468s126A  | Ave.  | -0.74 | 9.89E2        | 5.36E-4 | 4.65    |

|           | Sdev. | 0.13  | 0.75E2        | 1.74E-4 | 1.20    |

| 468s126D  | Ave.  | -0.98 | 1.07E3        | 9.93E-4 | 7.25    |

|           | Sdev. | 0.17  | 2.04E2        | 1.91E-4 | 6.82    |

| MESFET T3 |       |       |               |         |         |

| 468s126A  | Ave.  | -2.67 | 23.60         | 1.23E-4 | 1.01    |

|           | Sdev. | 1.25  | 22.73         | 0.68E-4 | 0.45    |

| 468s126D  | Ave.  | -1.12 | 2.05E2        | 2.60E-4 | 1.84    |

|           | Sdev. | 0.12  | 0.30E2        | 0.55E-4 | 0.25    |

| MESFET T4 |       |       |               |         |         |

| 468s126A  | Ave.  | -0.79 | 7.20E2        | 4.68E-4 | 1.94    |

|           | Sdev. | 0.14  | 1.02E2        | 1.59E-4 | 0.53    |

| 468s126D  | Ave.  | -1.08 | 8.10E2        | 9.09E-4 | 3.18    |

|           | Sdev. | 0.19  | 0.87E2        | 2.17E-4 | 0.51    |

#### 2.7 BACKGATING EFFECTS

Backgating is the effect of a negative voltage applied to a nearby electrode on MESFET characteristics. The backgate voltage modulates the space charge region at the interface between the channel and the substrate which subsequently affects the drain current. With sufficient negative backgate voltage applied, the channel can be completely pinched-off. Backgating can seriously degrade device performance. For instance, the slow drift in I-V characteristics [54] and the frequency dependence of g<sub>m</sub> at low frequency have both been attributed to backgating [55].

The possible mechanisms responsible for backgating effects include the traps in the underlying material [56] and the presence of a p-type conversion layer [57]. The threshold voltage,  $V_{bg}$ , for backgating is defined as the the backgate voltage at which backgating effects are first observed. In practice,  $V_{bg}$  is not always seen. It can be increased by using isolation implants with ions such as H, O and B [58], a p-type guard ring around the device [59] or a negatively biased Schottky contact between the devices [60].

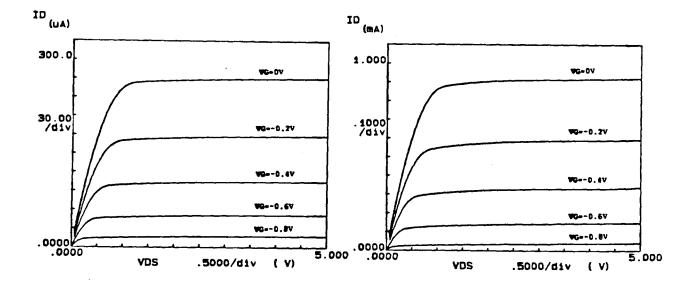

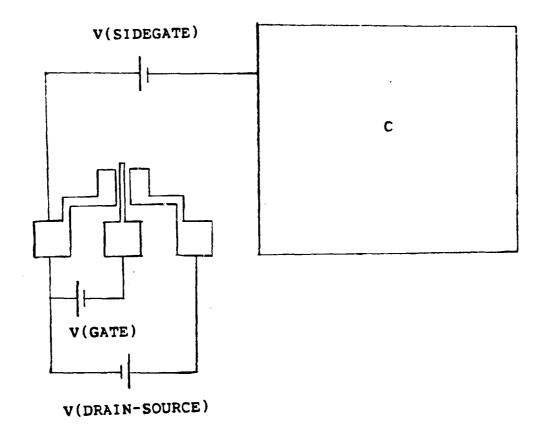

The test structure and measurement set-up for this experiment is shown in figure 3.10. As shown in the figure, the measurements were taken with MESFET T2 using pad C of the van der Pauw structure as the sidegate. The side gate is  $400\mu m$  away from the MESFET T2.

The backgating effects on both samples were found to vary from region to region. Hence, an overall trend of the effects of the surface etch cannot be detected. But, when devices at approximately the same relative location were compared, those on the etched wafer show less backgating effects. This can clearly be seen in figure 3.11 where the normalised drain current (normalised with  $I_{\rm dss}$ ) is plotted as a function of the backgate

Figure 3.10: Measurement Set-up For The Backgating Experiment . voltage

From the plot of percent change in  $I_{\hat{d}}$  versus normalised gate voltage (normalised with  $V_{th}$ ), given in figure 3.12, the backgate effect becomes more pronounced as the gate voltage approaches the threshold voltage. This evidence supports the claim that the existence of a space charge region at the active layer substrate interface is reponsible for backgating. In undoped LEC GaAs substrate, the width of this depletion layer is dependent on the compensation of the EL2 level and residual impurities like carbon.

1.500 E+00 Using 1500 /div 468s 126D /div 468s 126A VB 4.000/div (V) Backgate Voltage

Figure 3.11: Normalised Drain Current Versus Backgate Voltage

Figure 3.12: Drain Current Versus Normalised Gate Voltage

#### 4. EFFECTS OF DISLOCATION ON DEVICE CHARACTERISTICS

#### 4.1 INTRODUCTION

Non-uniformity of GaAs wafers has been observed using SEM-EBIC [61], cathodoluminescence [62], photoluminescence [63], bulk resistivity variation [64] and infrared photo-absorption [65]. These phenomena have been correlated with dislocation density variation across the wafer. The dislocation density in 2" and 3" GaAs wafers can range from 104 to more than 105 per cm<sup>2</sup>.

As the complexity of GaAs ICs increases, the possible adverse effects of dislocations on device performance and reliability become an important question, it has been known for a long time that dislocations cause the formation of dark-line defects in lasers and light emitting diodes [66]. Work published only recently has shown that the dislocation density of GaAs substrates affects the electrical characteristics of MESFETs [67]. The activation efficiency and thus the channel doping density and the threshold voltage of MESFETs are affected by their local dislocation density. However, studies on the influence of proximity of dislocation on MESFET threshold voltage have not been in agreement [68,69], in addition, the scatter of threshold voltage has also been found to be dependent on the structure of the dislocation pattern [70]. Clearly, there is an ambiguity as to the origin of the MESFET threshold voltage scatterings.

The generally held opinion now is that dislocations affect device characteristics but the exact origin of the effect is not known. The object of this study was to help determine whether local dislocation density, proximity to a dislocation centre, or the structure of dislocation pattern controls the scatter of threshold voltage. The method used involved the

design, the fabrication and the measurement of a MESFET array of pitch  $200\mu m$  x  $146\mu m$ . After measurement, the sample was etched to reveal dislocation centres. Exact local dislocation density and distance to the nearest dislocation centre of MESFETs were obtained with the aid of micro-photographs taken of the sample after the etch.

Following this introduction, a literature survey will be given. In sections 4.3 and 4.4, fabrication procedures and experimental results will be discussed respectively.

#### 2.2 LITERATURE SURVEY

Direct implantation into GaAs for the formation of the active channel places stringent requirements on the substrate quality. One of the requirements is the homogeneity of the substrate. Although it has been well known for some time that there is significant resistivity and dislocation variation along the length of a GaAs boule, it was not until 1982 that the variations of these parameters across a wafer were studied [71]. This is because it was commonly believed then that a dislocation density as high as 3 X 104 per cm<sup>2</sup> does not affect device characteristics.

The dislocation variation across a SI GaAs wafer can be obtained by counting the etch pits on it after an A/B [72] or molten KOH [73] etch is done. The etch creates a hexagonal pit on the surface of the wafer at the point where a dislocation line meets it. The dislocation density along the diameter of a GaAs wafer follows a W-shaped variation near the seed end [21]. The dislocation density increases and its W-shaped variation become less pronounced towards the tail end of the ingot. Dislocations are formed as a partial relief to the axial and radial stress which arise during crystal growth. Jordan et al. [74] has theoretically predicted the W-shaped variation

using a thermo-elastic model. Dislocations often appear in cell networks which are typically a few hundred  $\mu m$  in size [70]. The cells contain a dislocation and point defect free region because dislocation centres act as sinks for those defects. This creates what is known as the Cotterell atmosphere around the dislocation centres [75].

Many attempts have been made to reduce the dislocation density and its scatter in SI GaAs wafers. Terashima et al. [9] and Osaka et al. [76] have used a vertical magnetic field during growth to reduce melt temperature fluctuations which produce growth striations. Shimada et al. [77] heated the B<sub>2</sub>O<sub>3</sub> encapsulating layer through a window on the susceptor to reduce its temperature gradient. Using this technique, a 2° GaAs wafer with a dislocation density as low as 1000 etched pits per cm<sup>2</sup> was obtained. Impurity hardening using In can also reduce the dislocation density of GaAs wafers [10]. The In atoms increase the crystal's resistance to the generation and propogation of dislocations. Although it is true that very high concentration, 5 to 10 X 10<sup>19</sup> atoms per cm<sup>3</sup> of In is used, in In-alloyed GaAs, no degradation of Hall mobility is found.

The high resistivity, 10<sup>7</sup> to 10<sup>8</sup>  $\Omega$ -cm, of SI GaAs is obtained by the compensation of shallow levels, like Si and C, with deep levels, like Cr and EL2 [4,15]. This sensitive balance can be changed by dislocations. Thus it is not surprising that the resistivity variation should closely follow that of the dislocation density. However estimates of the resistivity variation seems to be dependent on the measurement technique used. Brozel et al. [78] using Van der Pauw method found the resistivity variation across a (100) oriented undoped SI GaAs to be M-shaped whereas Blunt et al. [71] found a W-shaped variation on a similarly oriented wafer using the dark spot method. The reason for the different profiles obtained is not known.

Leakage current measured under illumination gave a M-shaped profile in undoped SI GaAs wafers [79]. The same measurement along the diameter of Cr-doped SI GaAs wafers did not result in a similar profile. This is because in Cr-doped substrates, there are still plenty of Cr atoms left to compensate shallow donors after the sinking action of the dislocation centres.

High resolution infrared absorption at  $1\mu m$  showed that EL2 on SI GaAs wafers also follows the well known W-shaped profile [22]. Tajima et al. [80] using photoluminescence found that two emission bands, one at 0.65 eV and the other at 0.8 eV, consistently appeared in both undoped and lightly doped SI GaAs. The 0.6 eV band coincides with the etch pit density distribution and is believed to be due to the EL2 level. The other band is inversely related to the etch pit density variation and is postulated to be due to microdefects which are generated in regions where the dislocation density is low.

Post growth heat treatment can improve the uniformity of SI LEC GaAs substrates and the same result can be obtained either by annealing individual wafers or the whole ingot. The improvement is brought about through diffusion involving an As-vacancy [81]. Illuminated leakage current, bulk resistivity and cathodoluminescence intensity line variation have all been shown to improve after annealing [82]. HB grown GaAs crystals are generally more uniform in comparision with LEC crystals. For example, HB GaAs shows smaller photoluminescence and cathodoluminescence at a dislocation. This more uniform characteristics of HB crystal is due to the thermal treatment during growth.

The inhomogeneous dislocation density distribution across GaAs wafers affects device characteristics. Nanishi et al. [83] have shown that

MESFETs fabricated on high dislocation regions have higher drain source current and a larger negative threshold voltage than those fabricated on low dislocation regions. Wang et al. [84] showed that mobility transconductance vary directly with etch pit density. Miyasawa et al. [85] also found that the threshold voltage of MESFETs was influenced by their proximity to a dislocation. MESFETs less than a critical distance of 20-30 µm away exhibit a lower threshold voltage than those further away (figure 4.1). Below this critical distance, threshold voltage also shows more scatter. This critical distance is in agreement with the radius of the so-called denuded zone surrounding dislocation revealed by photoluminescence [63] and cathodoluminescence studies [62]. Recent work

Figure 4.1: Threshold Voltage Versus Distance To Nearest Dislocation Obtained By Miyasawa et al. [85]

by Ishii et al. [72] has shown that threshold voltage scatter is strongly influenced by cell network structure. At a high threshold voltage scatter region, a strongly networked structure was found and threshold voltage scatter was small for randomly networked structure despite its high dislocation density. To complicate matters, the threshold voltage scatter was also found to be dependent on the implant dose and annealing method used [86]. Winston et al. [87] did not find any correlation between the MESFET threshold voltage and its proximity to a dislocation.

Hyuga et al. [88] using completely dislocation free In-alloyed GaAs reported that the sheet carrier concentration of an implanted layer formed by a direct silicon 28 (<sup>28</sup>Si) implant at 60keV with a dose of 5 x 10<sup>12</sup> per cm² was reduced to one fifth that of conventional GaAs wafers. Dobrilla et al. [89] showed that the local concentration of neutral EL2 in the substrate is a key factor in controlling device properties and suggested that the EL2 concentration uniformity may be more important than the dislocation uniformity. Tamura et al. [90] using wafers from three suppliers showed the existence of two types of undoped SI GaAs crystals. One group showed strong correlation between etch pit density and Hall mobility and resistivity and the other displayed little correlation between these parameters. SEM-EBIC [61] studies showed that two types of dislocation exist and this has been postulated to be due to the temperature at which dislocations were formed. Dislocations formed at high temperature have a Cottrell atmosphere whereas those formed at low temperature do not.

#### 4.3 EXPERIMENT

This experiment involved the fabrication of dense arrays of MESFETs. Invariably, the fabrication process will introduce some inhomogeneity to the device characteristics measured. To study the influence of the substrate inhomogeneity, the process induced scatter must be minimised. With regards to this we chose a simple four mask fabrication process and 2µm gate length MESFETs. An earlier attempt at this work was performed in this laboratory by W. Tang [91]. In that study, the active channel was formed by implanting through a Si, N<sub>4</sub> layer which was deposited at the beginning of fabrication to protect the sensitive GaAs surface. This step was avoided in our fabrication procedures because of the difficulty involved in obtaining a uniform Si<sub>1</sub>N<sub>4</sub> layer. Short gate length and narrow gate width provide better definition of the active channel position. We decided to use 2 µm instead of the shorter 1 µm ones to achieve better yields. gates Furthermore it is impossible to obtain good gate length uniformity for the shorter gates using conventional optical lithography.

#### 4.3.1 MASK DESIGN

In order to look at microscopic effects of dislocation networks a few hundred  $\mu$ m in size, a MESFET array of pitch  $200\mu$ m x  $146\mu$ m was used. The bulk of the area is occupied by the three  $80\mu$ m squares used to probe the transistor. The distance between the drain and source pads is  $10\mu$ m which gives a nominal spacing of  $4\mu$ m between the gate and source or gate and drain. This makes alignment of the gate metal mask easier. The designed mask pattern is depicted in Figure 4.2 below. Pattern A is the registration mark, pattern B the channel implant, pattern C the  $n^+$  implant and ohmic contact, and pattern D the gate. For economical reasons,

all the fabrication levels were placed on the same mask,

#### 2.3.2 FABRICATION PROCEDURES

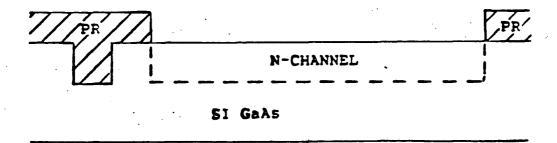

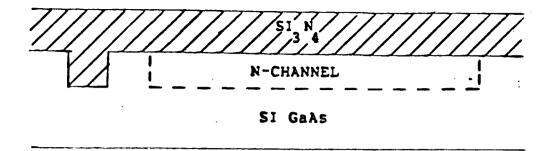

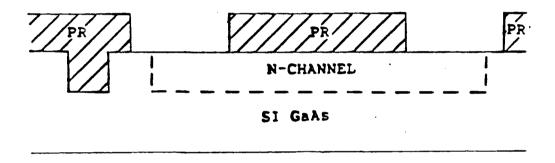

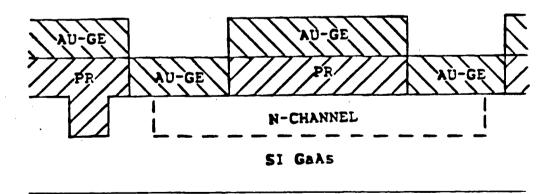

An overview of the fabrication process is schematically illustrated in figure 4.3. The details of the process are listed in Table 4.

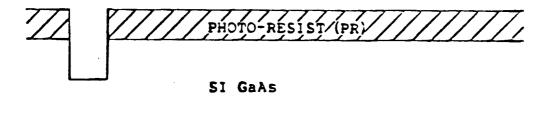

Step 1 removes the grease from the samples. The samples were also etched to remove the top 500A of the surface. This ensures the removal of the surface oxide layer and the 'disordered' region right under the surface.

Steps 2 to 7 etch the registration pattern necessary for the higher levels of the mask. To ensure easier alignment in later stages of fabrication, proper resist development must be obtained. It is advisable to repeat steps 2 to 7 till a good resist pattern is obtained. This advice also applies to later resist development.

Steps 8 to 13 involve laying down the resist mask for selective implantation of the channel regions.  $^{28}$ Si ions were used to make the channel n-type. During ion implantation, the (100) orientated sample was tilted 7° away from its <100> axis to any <110> direction. This made the substrate appear amorphous to the incoming ions, preventing axial channeling [92]. To minimise planar channeling and also to increase the uniformity of the implant, the sample was rotated  $20^{\circ}$  from the fundamental axis. An implant dose of  $3.37 \times 10^{12}$  at 80 keV was used.

Figure 4.2: MESFET Array

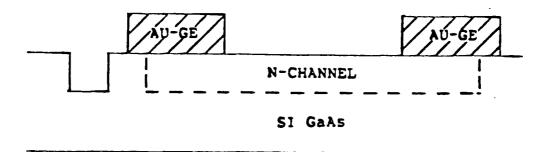

### SI GaAs

# (A) Wafer pre-clean

## (B) Registration mark etch

# (C) Opening windows for ion-implantation

Figure 4.3: Schematics Of The Fabrication Process

# (D) Encapsulation and annealing

# (E) Opening windows for gold-germanium contacts

# (F) Evaporation of gold germanium

Figure 4.3: Continued

(G) Liftoff of photo-resist, and alloying

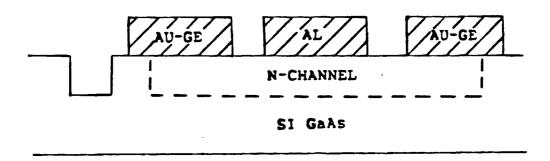

(H) evaporation of aluminium.

Figure 4.3: Continued

#### Table 4: Detailed Fabrication Steps

#### No Process Description

#### 1. Pre-implant cleaning

- a. Degrease

- 5 minutes rinse each in warm trichloroethylene, acetone and iso-propanol.

- b. GaAs etch

Soak for 4 minutes in 1% filtered alconox (monosodium dihydrogen phosphate). 15 seconds DI  $H_2O$  rinse and  $N_2$  blow dry.

c. Oxide etch

Immerse for 30 seconds in  $1H_2O_2$ :5NH<sub>4</sub>OH:240DI H<sub>2</sub>O, 15 seconds DI H<sub>2</sub>O rinse and N<sub>2</sub> blow dry.

#### 2. Clean

2 minutes acetone rinse, 2 minutes iso-propanol rinse and  $N_2$  blow dry.

#### 3. Resist coat

Spin Shipley AZ1400-30 resist at 4500 rotations per minute (RPM) for 20 seconds (approximately  $1.7\mu m$  thick). Soft bake at  $95^{\circ}C$  for 25 minutes.

#### 4. Registration mark level exposure

1 minute under ultra violet (UV) light (Karl-Suss MJB3).

#### 5. <u>Develop</u>

Develop in 50% Shipley Microposit MF312 developer. Developing time is approximately 45 seconds.

#### 6. Registration mark etch

Rinse for 1 minute in 10%HCL, 1 minute in DI  $H_2O$ , 50 seconds in  $5\%H_3PO_4$ :2.5% $H_2O_2$ :92.5%DI  $H_2O$ , 5 minutes in DI  $H_2O$  and  $N_2$  blow dry.

#### 7. Resist removal

Soak in warm acetone.

#### 8. Clean

2 minutes warm acetone rinse, 2 minutes iso-propanol rinse and  $N_2$  blow dry.

#### 9. Resist coat

Spin Shipley AZ1400-30 resist at 4500 RPM for 20 seconds. Soft bake at 95°C for 25 minutes.

#### 10. Channel level exposure

1 minute under UV light.

#### 11. <u>Develop</u>

Rinse in 50% Shipley Microposit MF312 developer.

#### 12. Channel implant

$^{28}$ Si at 80keV and dose of 3.37 x 10 $^{12}$  per cm<sup>2</sup>.

#### 13. Resist removal

Soak in warm acetone. O<sub>2</sub> plasma 200W, 200SCCM of O<sub>2</sub>, 120°C, 250mTorr for 25 minutes.

#### 14. Clean

2 minutes warm acetone rinse, 2 minutes iso-propanol rinse and N, blow dry.

#### 15. Si,N<sub>4</sub>

Preclean surface with NH<sub>3</sub> plasma at 100W, 37,6SCCM of NH<sub>3</sub>, 308°C, 500mTorr for 5 minutes. Without breaking vacuum deposit Si<sub>3</sub>N<sub>4</sub> at 100W, 37,6SCCM of NH<sub>3</sub>, 500SCCM of He, 550SCCM of 5%SiH<sub>4</sub>/He, 308°C, 1500mTorr for 7 minutes (about 800A).

#### 16. Channel implant anneal

$825^{\circ}$ C for 25 minutes under flowing  $N_2$  gas. Place sample at edge of furnace for 5 minutes. Push sample into the furnace. On the way out, place sample at edge of furnace for 5 minutes before removing from the furnace.

#### 17. Si<sub>3</sub>N<sub>4</sub> removal

Freon plasma at 200W, 200SCCM of CF<sub>4</sub>, 125°C, 500mTorr for 4 minutes.

#### 18. Clean

2 minutes warm acetone rinse, 2 minutes iso-propanol rinse and N, blow dry.

#### 19. Resist coat

Spin Shipley AZ1400-30 at 4500 RPM for 20 seconds. Bake at 95°C for 25 minutes.

#### 20. Ohmic level exposure

1 minute under UV light.

#### 21. Chlorobenzene soak

Soak for 2.5 minutes in chlorobenzene.

#### 22. <u>Develop</u>

Rinse in 50% MF312 developer.

#### 23. Oxide etch

Rinse for 15 seconds in  $1NH_4OH:10H_2O_2$ , 30 seconds in DI  $H_2O$  and  $N_2$  blow dry.

#### 24. Ohmic metal evaporation

1500A of Au-Ge.

#### 25. <u>Liftoff</u>

Soak in warm acetone and agitate.

#### 26. Alloy

2 minutes at  $450^{\circ}$  in flowing  $N_2$  gas.

#### 27. Ohmic contact

Check drain source current at  $V_{qs} = 2.5$  volts.

#### 28. Resist coat

Spin Shipley AZ1400-30 at 4500 RPM. Soft bake at 95°C for 25 minutes.

#### 29. Gate level exposure

1 minute under UV light.

#### 30. Chlorobenzene soak

Soak for 2.5 minutes in chlorobenzene.

#### 31. <u>Develop</u>

Rinse in 50% MF312 developer.

#### 32. Oxide etch

Rinse for 15 seconds in  $1NH_4OH:10DI\ H_2O$ , 30 seconds in  $DI\ H_2O$  and  $N_2$  blow dry.

#### 33. Gate metal evaporation

2000A of Al.

### 34. <u>Liftoff</u>

Soak in warm acetone and agitate.

## 35. DC measurements

The MESFET DC characteristics can now be measured.

To prevent As loss during a high temperature (825°C) anneal (which is required to repair lattice damage as well as to electrically activate the dopants) a Si<sub>3</sub>N<sub>4</sub> film of about 800A was used to encapsulate the surface. Si<sub>3</sub>N<sub>4</sub> was chosen over SiO<sub>2</sub> because it is more impermeable to gallium atoms [93]. Furthermore, a good quality plasma enhanced chemical vapour deposited (PECVD) Si<sub>3</sub>N<sub>4</sub> film can be easily and quickly deposited using the Plasma-Therm.

Early attempts to anneal with  $Si_3N_4$  as the encapsulant resulted in its dissociation. The resulting film was impossible to remove; hence, further work on the sample had to be abandoned. We solved this problem by exposing the implanted sample to 5 minutes of NH<sub>3</sub> plasma before depositing the  $Si_3N_4$  film. The NH<sub>3</sub> plasma removed the surface oxide layer and promoted better adhesion between the film and the GaAs surface [94].

Annealing was performed in the Mini Brute furnace in flowing  $N_2$ . The annealing procedure described in step 16 was followed to avoid introducing excessive strain between the  $Si_3N_4$  film and the GaAs surface. Samples were sometimes sandwiched between two pieces of clean silicon wafers to make sure that the  $Si_3N_4$  film did not crack during annealing. After annealing, the  $Si_3N_4$  film was removed by freon plasma. 10% HF solution can also be used.

For ohmic metal (Au-Ge) and gate metal (Al) liftoff, the resist was soaked in chlorobenzene for 2.5 minutes before developing. The chlorobenzene hardened the surface of the resist and upon development, an 'overhang' was produced in the resist which was found to aid the liftoff process [95].

Ohmic metal, Au-Ge, is evaporated in step 24. It is important to soak the sample in 1NH<sub>4</sub>OH:10H<sub>2</sub>O mixture prior to evaporation. This mixture

helps remove the surface oxide layer and resist that was not removed during development. This same soak was also performed prior to gate metal deposition. It has been shown that the 1NH<sub>4</sub>OH:10H<sub>2</sub>O treatment before Schottky contact metal evaporation gave better diode characteristics [47].

Alloying was performed in the Mini Brute furnace in flowing  $N_2$ . The alloying temperature was  $415^{\circ}$ C and the duration was 2 minutes. The SPA was used to check the drain source current. This is a very simple method to determine if there is a channel or not. Further fabrication is futile if there is no channel between the drain and source pads.

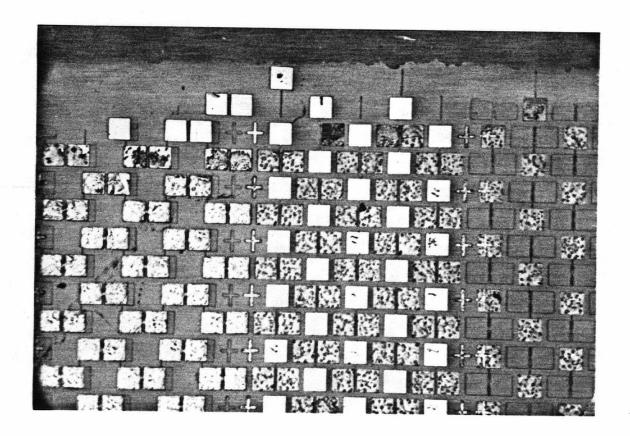

The final few fabrication steps, 30 to 36, involve the deposition of the gate metal. Here no alloying is needed to obtain the Schottky characteristics of the gate. After the gate metal deposition, fabrication is complete and the MESFETs are now ready for measurement. A photograph of a fabricated array of MESFETs is given in figure 4.4. The dark region at the top of the photograph is the edge of the wafer. The MESFET array is flanked by regions that are formed because all the fabrication levels are placed on the same mask.

#### 4.3.3 MEASUREMENT

Measurements were performed using a HP9816 computer, a HP 4145A semiconductor parameter analyser and a Wentworth Labs probe station. The probe station was placed in an electrically shielded box which also acted as a light shield. This is important for ensuring reliable measurements because the channel current is extremely sensitive to light. Since an automatic prober is not available, the probes had to be manually moved. Precautions were taken to make sure that the probes were applied with

Figure 4.4: Fabricated MESFET Array

light and consistent pressure on each set of pads as the threshold voltage varied as much as 25mv due to pressure.

Only the threshold voltage of the fabricated devices was measured. The threshold voltage was measured with 2.5 volts applied between the drain and source, to ensure that the MESFETs were operating in the saturation region. Two techniques were used to determine the threshold voltage. In the first method, the threshold voltage was defined as the gate voltage at which the drain source current was  $5\mu A$  with 2.5 volts applied

between the drain and source. In the second method, a square root drain source current versus gate voltage was assumed. The threshold voltage here was defined as the zero current intercept of a line drawn through  $\sqrt{I}_{dss}$  at zero gate voltage and  $0.1\sqrt{I}_{dss}$  at the appropriate gate voltage ( $I_{dss}$  is the drain to source current at zero gate voltage). In the second technique, 2.5 volts was also applied between the drain and source pads. Both the threshold voltage were computed and stored onto the hard disk of the HP9816 before the next transistor was measured. The program used is similar to the one given in appendix A.

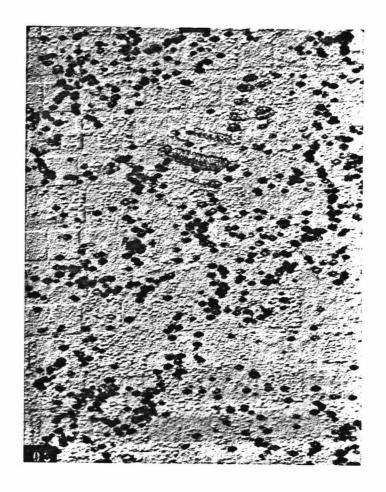

To correlate the measured device characteristics with dislocations, the samples have to be etched in molten KOH to reveal etch pits corresponding to the dislocations. The molten KOH etch was done at Cominco in Trail. The sample was first placed in a nickel crucible, then a pre-determined (from trial runs using dummy samples) amount of KOH beads were placed in the crucible before covering it with a lid and placing it in an oven. After an etch time of about 5 minutes, the sample was removed from the oven, cooled and rinsed in DI H<sub>2</sub>O.

The MESFET metallisation was removed by the etch but the registration marks and the ohmic and gate pads are still clearly outlined (figure 4.5). These features were used to deduce the location of the MESFETs on micro-photographs taken of the MESFET array. The micro-photographs were taken at 100X magnification. The distance between the MESFET and the nearest dislocation and the etch pit densities were all obtained using the micro-photographs. The etch pit density was calculated from a 200 µm x 200 µm square area centred on the MESFET.

Figure 4.5: Micro-photograph Of Etched Sample With Registration Marks Left Behind

# 4.4 RESULTS AND DISCUSSIONS

The slice tested, 429s122G, is from wafer 429s122 supplied by Cominco Limited. Its position on the wafer is as depicted in figure 4.6. MESFETs fabricated on the sample, which is roughly the size of a 1.7cm radius quadrant, have gates perpendicular to the major <110> flat. 10 columns of transistors, about 800 in number, were measured. However, only two columns were included in this study because the sample was slightly over-etched by Cominco. Three other samples sent to Cominco were

completely over-etched. The molten KOH etch should ideally reveal hexagonal pits at locations where dislocations meet the surface, and at the same time leave a 'ghost' of the devices behind (figure 4.5). But, when a sample is over-etched, no trace of the original devices is left behind making it impossible to pin point their original position.