#### GaAs MATERIAL INVESTIGATION FOR INTEGRATED CIRCUITS FABRICATION

By

#### SALAM DINDO

B.A.Sc., The University of British Columbia, 1982

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES Department of Electrical Engineering

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

October 1985

© Salam Dindo, 1985

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of Electrical Engineering

The University of British Columbia 1956 Main Mall Vancouver, Canada V6T 1Y3

1 INOV 11985 Date

#### ABSTRACT

The primary objective of the work described in this thesis was to study the influence of undoped LEC GaAs substrate material from various suppliers on the performance of ion implanted and annealed active layers. Optical transient current spectroscopy (OTCS) was investigated as a qualification test for GaAs substrates. Deep level spectra of the substrates before ion implantation were obtained. It was found that while the OTCS spectra of high pressure grown GaAs from two suppliers were similar, that of the low pressure material showed different relative concentration of traps. The use of OTCS was further extended to study trap concentration as a function of surface treatment. It was found that the use of chemical etchants reduces the concentration of some levels, possibly those located on the surface as opposed to bulk traps. Surface damage was found to enhance the negative peak in the OTCS spectrum. The deep levels spectra were found to be affected by the geometry of the device and the type of electrode material.

Channel current deep level transient spectroscopy (DLTS) was used to study both process- and substrate-induced deep levels in ion implanted MESFET channels. The spectra of process-induced traps were found to be different according to the encapsulant used. Silicon dioxide (both RF sputtered and plasma enhanced chemically vapor deposited (PECVD)) was found to induce a variety of process related defects. This is believed to be because silicon dioxide is permeable to gallium and hence does not preserve the stoichiometry

- ii -

of ion implanted GaAs during high temperature anneals. Deep level spectra of MESFETs annealed using silicon nitride, on the other hand, were found to contain single traps related to the defects in the starting material. For implants through silicon nitride, a high concentration of the main electron trap EL2 was found, whereas implants directly into the surface resulted in the level EL12.

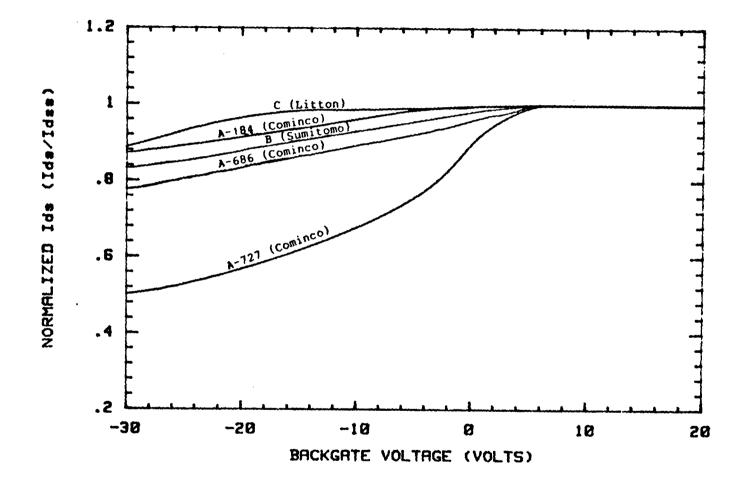

Comparison of the characteristics of the variety of LEC undoped GaAs material show that they differed widely and had inhomogeneous properties. For example, compared to the high pressure grown GaAs, the Litton's low pressure substrate had lower activation, mobility, drain current and threshold voltage, good confinement of the scatter in the same characteristics, low concentration of deep levels, and the least backgating effect which makes it promising for IC fabrication. Comparison of the high pressure grown material from two suppliers showed that Cominco's recent material had good mobility, activation, relatively high scatter of threshold voltage, high concentration of deep levels, and was affected by backgating. In comparison, Sumitomo's material showed thermal instability, less scatter of threshold voltage, less mobility and deep level concentrations, and similar backgating characteristics. Substrate grown three years earlier showed higher diffusion of dopant, different deep levels, and better backgating characteristics. Finally, a substrate which had failed the qualification test by a device manufacturer showed minimal diffusion tails and threshold voltage scatter, the highest concentration of deep levels, and substantial backgating.

- iii -

#### TABLE OF CONTENTS

- iv -

| ABSTRACT                                                   | 11  |  |

|------------------------------------------------------------|-----|--|

| LIST OF TABLES                                             | vi  |  |

| LIST OF FIGURES v                                          | rii |  |

| ACKNOWLEDGEMENTS                                           | ix  |  |

| INTRODUCTION                                               | 1   |  |

| GROWTH AND PROPERTIES OF SEMI-INSULATING GALLIUM ARSENIDE  | 3   |  |

| Introduction                                               | 3   |  |

| GaAs Crystal Growth Techniques                             | 3   |  |

| Impurities and Their Role in Undoped LEC GaAs              | 6   |  |

| Relation of Melt Stoichiometry to Compensation and         |     |  |

| Thermal Stability of GaAs                                  | 8   |  |

| 2.5 Recent Advances in the Growth of Undoped LEC GaAs      | 10  |  |

| 3. OPTICAL TRANSIENT CURRENT SPECTROSCOPY INVESTIGATION OF |     |  |

| VARIOUS GaAs SUBSTRATES 13                                 |     |  |

| 3.1 Introduction to Optical Transient Current Spectroscopy | 13  |  |

| 3.2 Theory of Optical Transient Current Spectroscopy       | 14  |  |

| 3.3 Experimental Procedure                                 | 19  |  |

| 3.4 Results                                                | 21  |  |

| 3.4.1 OTCS Spectra of GaAs Substrates From Three Vendors   | 24  |  |

| 3.4.2 Identification of the Peaks                          | 27  |  |

| 3.4.3 Effects of Varying Sample Geometry on OTCS Spectra   | 33  |  |

#### 3.4.4 Effect of Varying the Electrode Material..... 35 3.4.5 Effect of GaAs Surface Damage on the OTCS Spectrum... 39 Summary..... 44 3.5 INVESTIGATION OF PROCESS-INDUCED DEEP LEVELS IN ION 4. 45 IMPLANTED MESFETS..... 4.1 Introduction...... 45 47 4.2 Principle of Channel Current DLTS..... 4.3 Experimental Procedure..... 52 Results..... 54 4.4 5. INFLUENCE OF VARIOUS LEC UNDOPED GAAS SUBSTRATES ON THE CHARACTERISTICS OF ION IMPLANTED AND ANNEALED ACTIVE LAYERS..... 66 5.1 Introduction..... 66 69 5.2 Description of the Diagnostic Test Pattern...... 5.3 Diagnostic Pattern Fabrication..... 69 5.4 Measurements on the Diagnostic Test Pattern..... 75 5.5 78 Results of Active Layer Evaluation..... Results on Deep Levels..... 89 5.6 5.7 Results on Backgating..... 98 Discussion of Results..... 101 5.8 Summary..... 106 5.9 CONCLUSIONS AND SUGGESTIONS FOR FURTHER WORK..... 107 6.

#### Page

#### - vi -

#### LIST OF TABLES

### Page

| 2.1 | Order of magnitudes of some common impurities found in SI, undoped, LEC GaAs                                                                                                                   | 7   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Activation energies, capture cross sections, and<br>possible identities of the deep levels found using<br>OTCS (P1-8) in SI, undoped, LEC GaAs                                                 | 29  |

| 3.2 | Deep levels in SI GaAs reported in the literature (as<br>detected by OTCS (PITS)). VPE = Vapour Phase Epitaxy                                                                                  | 30  |

| 4.1 | Activation energies, capture cross sections, and<br>possible identities of the deep levels found using<br>channel current DLTS in MESFETs fabricated using four<br>processes (Q1-4,R1,S1,T1-4) | 62  |

| 4.2 | Some deep levels in silicon implanted GaAs reported in the literature                                                                                                                          | 64  |

| 5.1 | Comparison of the active ion implanted layers parameters of five GaAs samples                                                                                                                  | 80  |

| 5.2 | DLTS data on the traps found by channel current DLTS                                                                                                                                           | 96  |

| 5.3 | Concentration of traps found by channel current DLTS                                                                                                                                           | 96  |

| 5.4 | Comparison of the calculated values of effective straggle ( $\Delta R$ "), diffusion coefficient (D'), pinchoff voltage ( $V_p$ ), and threshold voltage ( $V_{th}$ ) of five GaAs samples     | 105 |

-

.

.

#### - vii -

#### LIST OF FIGURES

|   | 3.1  | Geometry of (a) planar and (b) sandwich structures<br>used in OTCS                                                                                     | 20 |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 3.2  | Block diagram of the OTCS setup                                                                                                                        | 22 |

|   | 3.3  | Vacuum chamber used in the OTCS experiment                                                                                                             | 23 |

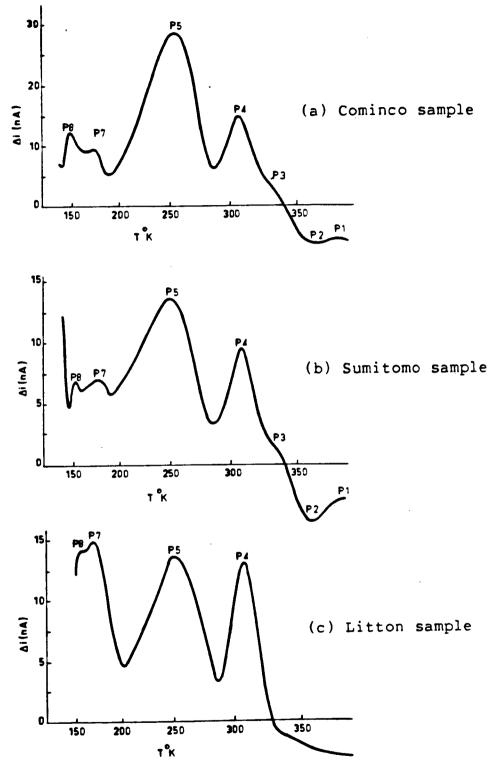

|   | 3.4  | OTCS spectra of SI undoped LEC GaAs from three vendors<br>(Rate Window = 8.5 msec)                                                                     | 25 |

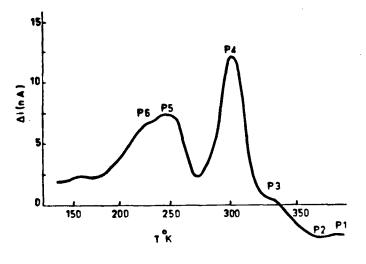

|   | 3.5  | OTCS spectra of SI undoped LEC GaAs substrates from<br>two vendors subjected to chemical etch (Rate Window =<br>8.5 msec)                              | 26 |

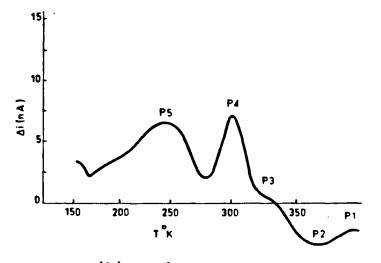

|   | 3.6  | Activation energy plots for traps detected using OTCS                                                                                                  | 28 |

|   | 3.7  | OTCS spectra of different planar sample geometries<br>(Rate Window = 18.9 msec)                                                                        | 34 |

|   | 3.8  | OTCS spectra of samples prepared with different<br>electrodes (Rate Window = 38.8 msec)                                                                | 36 |

|   | 3.9  | Current vs. voltage for planar specimens with different electrodes                                                                                     | 38 |

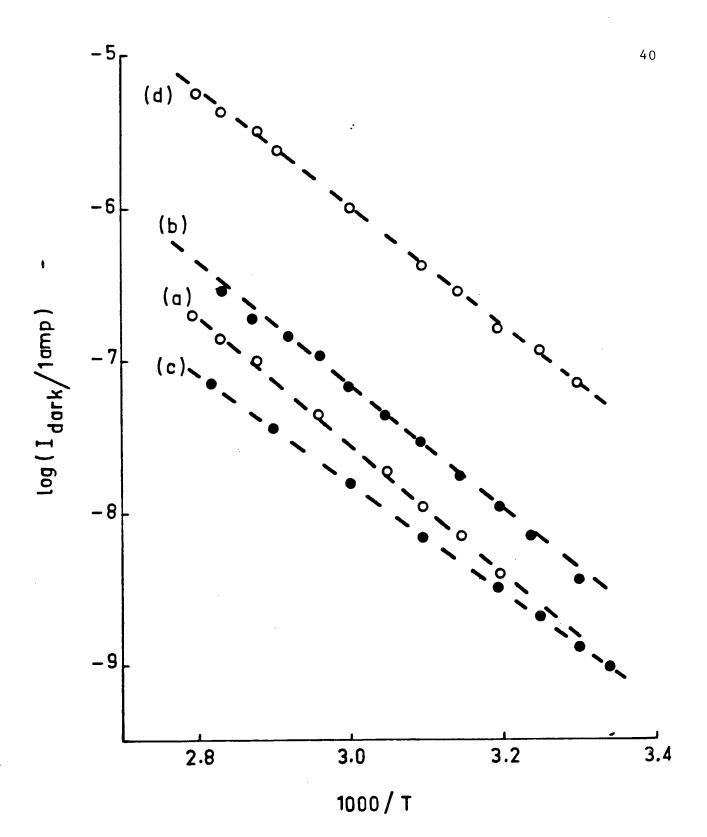

|   | 3.10 | Signature line plots for the data of figure 3.9<br>(Labels same as in figure 3.9)                                                                      | 40 |

|   | 3.11 | OTCS spectra of sandwich structures with a negative<br>bias on the top illuminated electrode (Rate Window =<br>75.5 msec)                              | 42 |

|   | 3.12 | OTCS spectra of a planar structure (a) before and<br>after chemical etch (b) after light abrasion (c) after<br>chemical etch (Rate Window = 75.5 msec) | 43 |

|   | 4.1  | Schematic diagram showing the channel current DLTS measurement system                                                                                  | 48 |

|   | 4.2  | Transient responses of the drain current to an applied gate voltage                                                                                    | 49 |

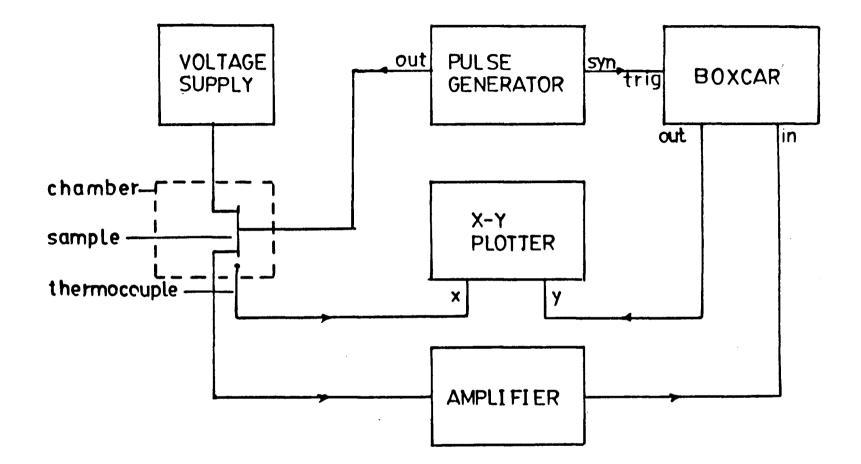

| ~ | 4.3  | Block diagram of channel current DLTS system                                                                                                           | 55 |

|     | V                                                                                                     |            |

|-----|-------------------------------------------------------------------------------------------------------|------------|

|     |                                                                                                       | Page       |

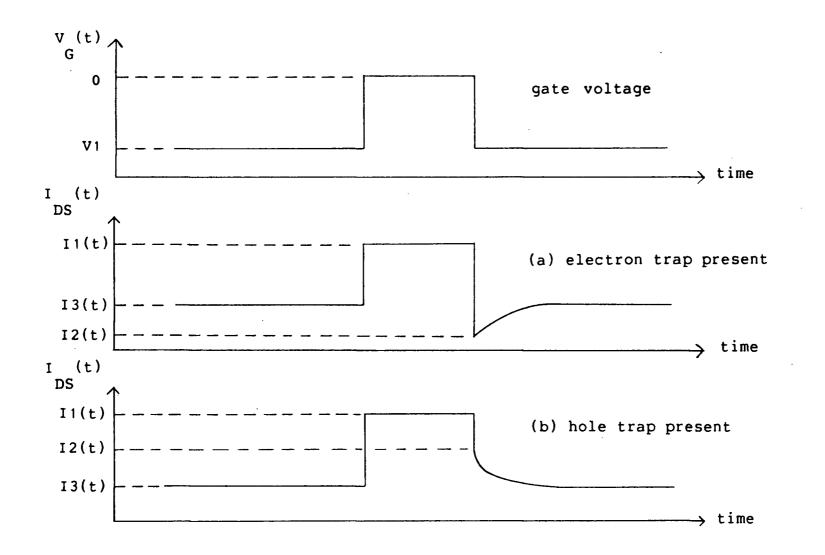

| 4.4 | Channel current DLTS spectrum for MESFETs prepared using process I                                    | 56         |

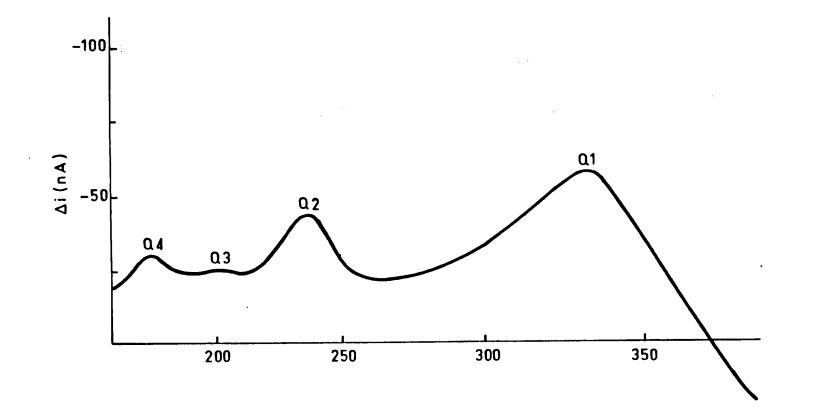

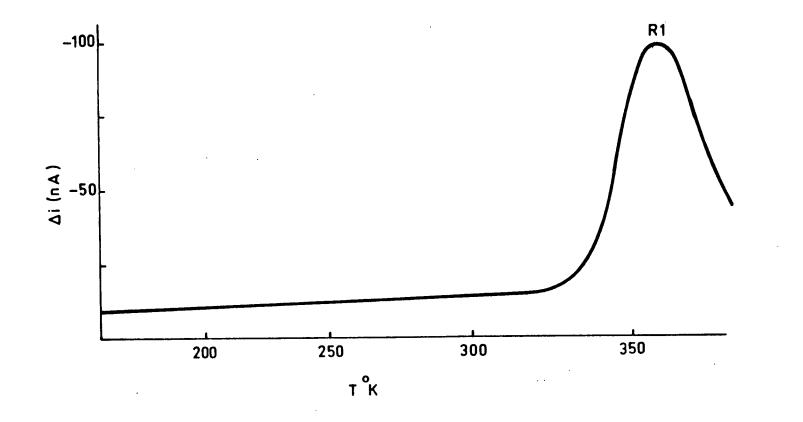

| 4.5 | Channel current DLTS spectrum for MESFETs prepared<br>using process II                                | 57         |

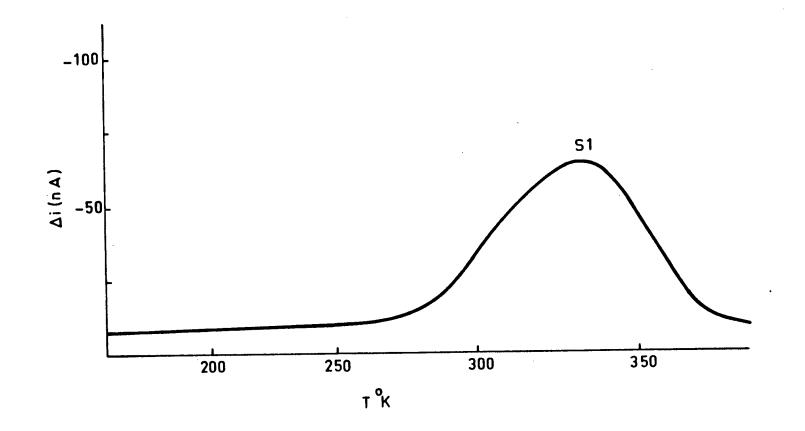

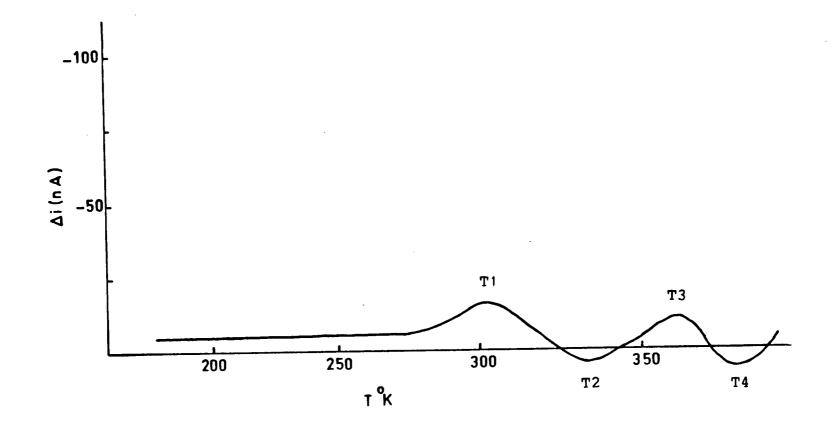

| 4.6 | Channel current DLTS spectrum for MESFETs prepared<br>using process III                               | 58         |

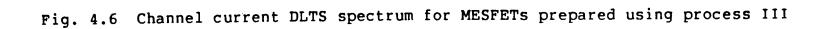

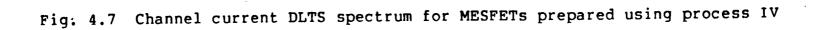

| 4.7 | Channel current DLTS spectrum for MESFETs prepared<br>using process IV                                | 59         |

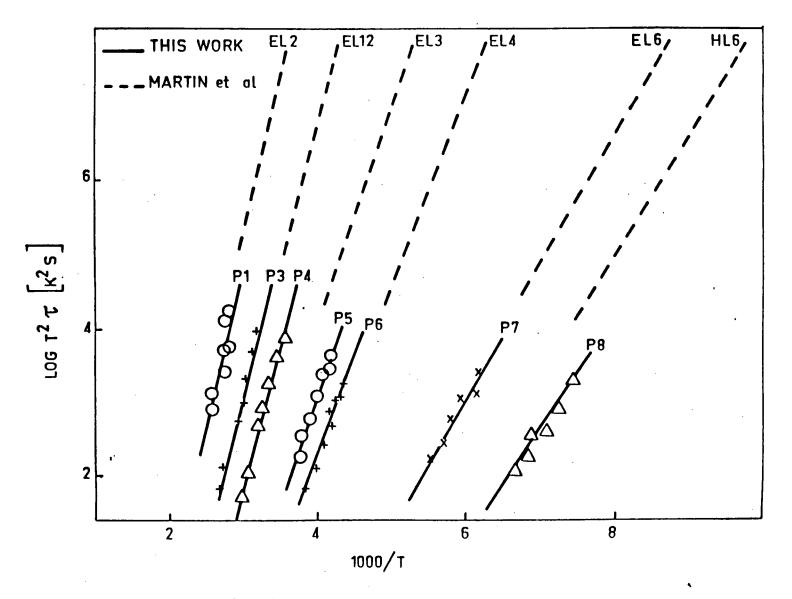

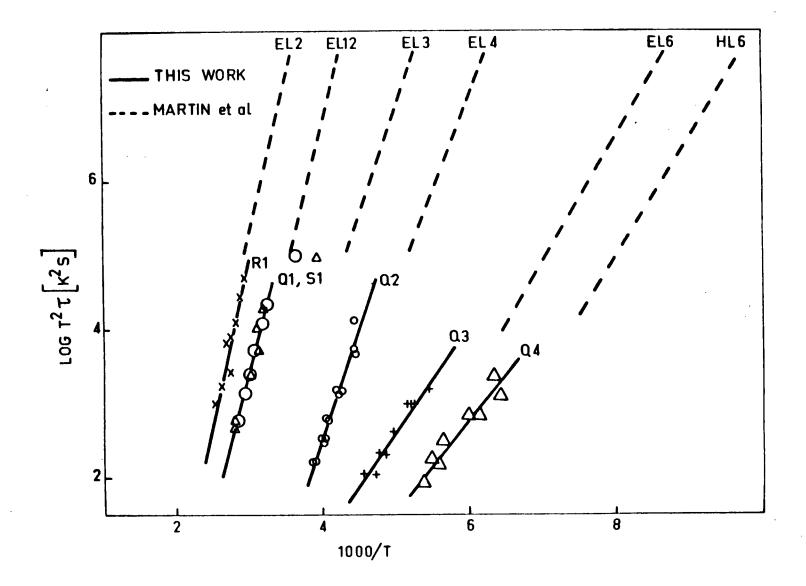

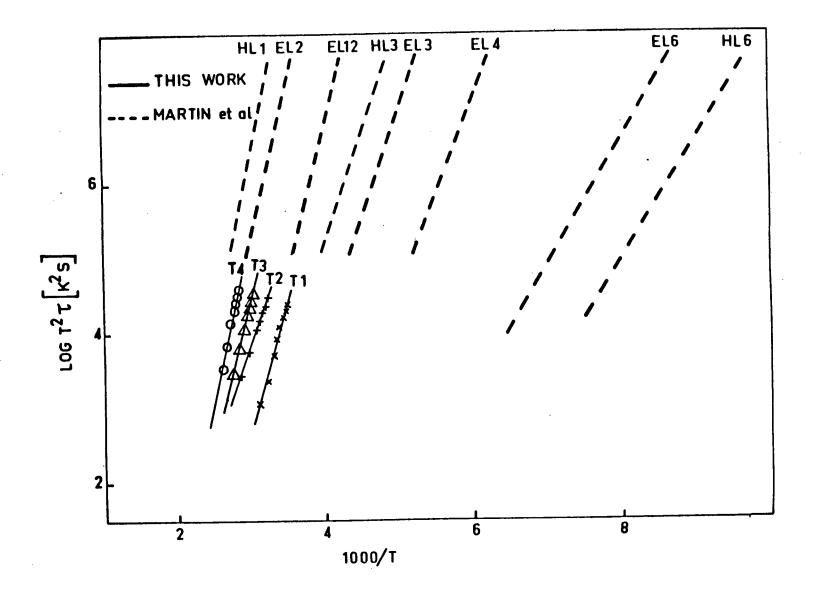

| 4.8 | Signature line plots for channel current DLTS data of processes I-III                                 | 60         |

| 4.9 | Signature line plots for channel current DLTS data of process IV                                      | 61         |

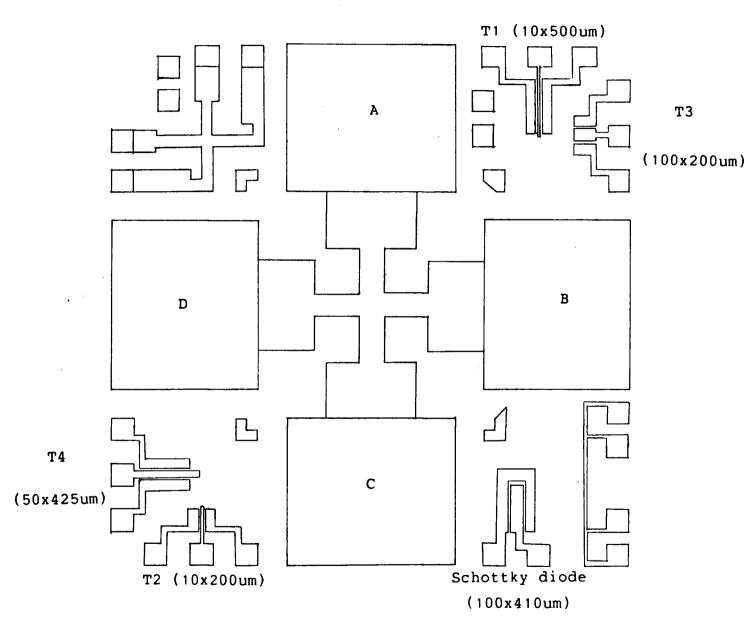

| 5.1 | The diagnostic test pattern                                                                           | 70         |

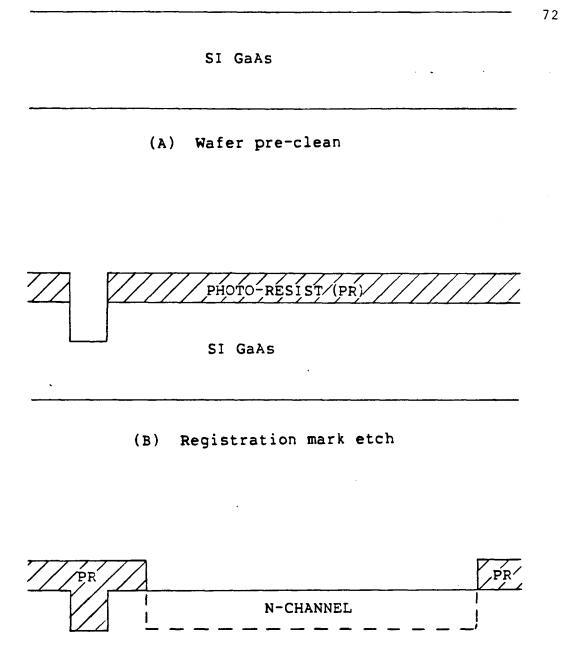

| 5.2 | Fabrication sequence for the diagnostic test pattern                                                  | 72         |

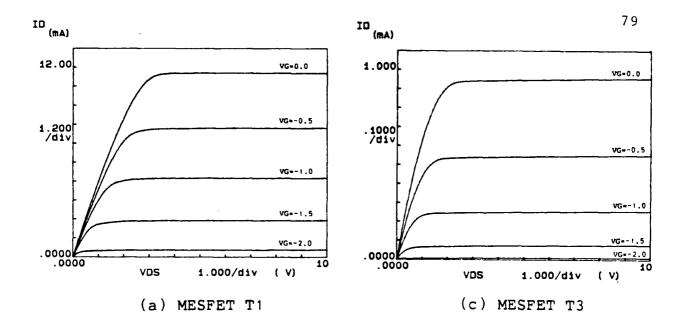

| 5.3 | Typical I <sub>DS</sub> - V <sub>DS</sub> characteristics of MESFETs in the<br>diagnotic test pattern | 79         |

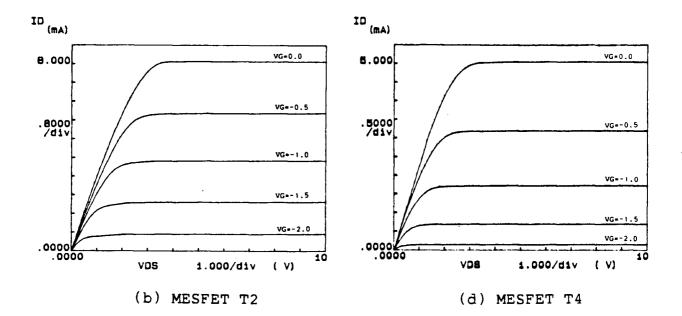

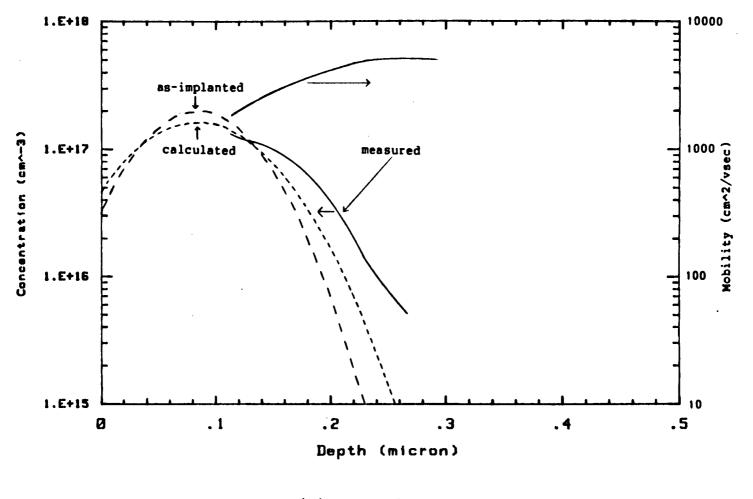

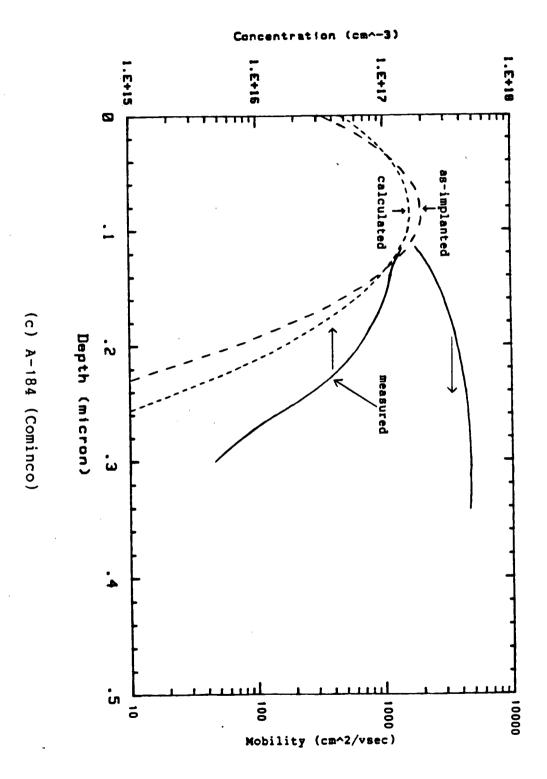

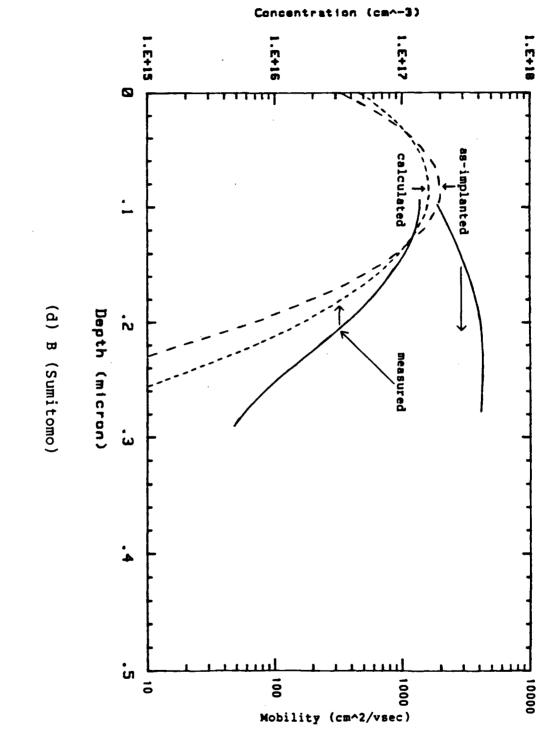

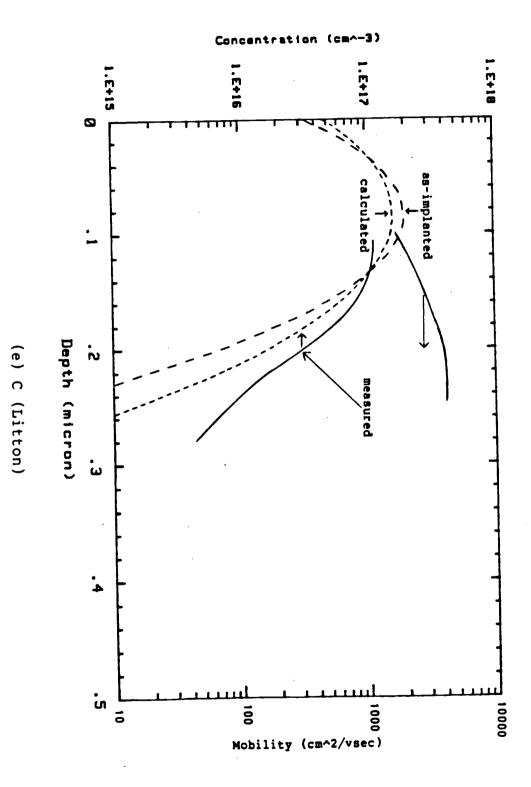

| 5.4 | As-implanted, calculated, and measured carrier density<br>profiles and drift mobility profiles        | 82         |

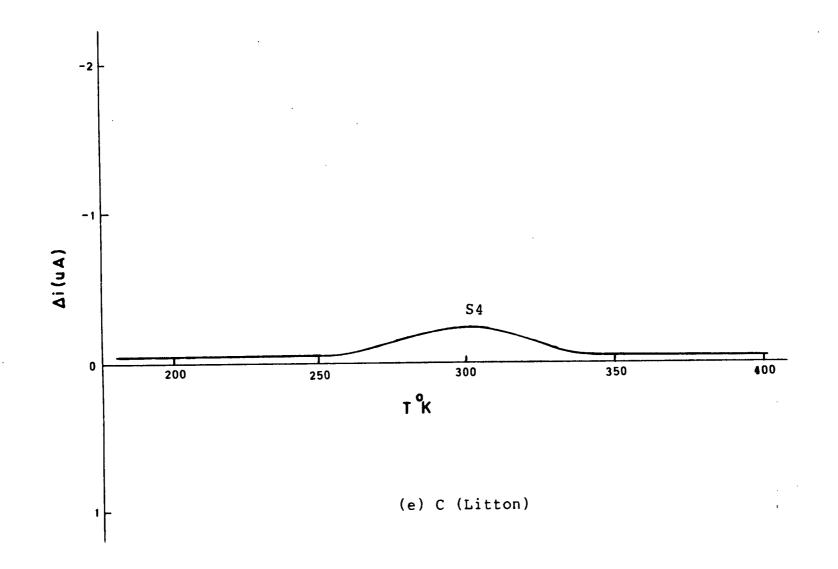

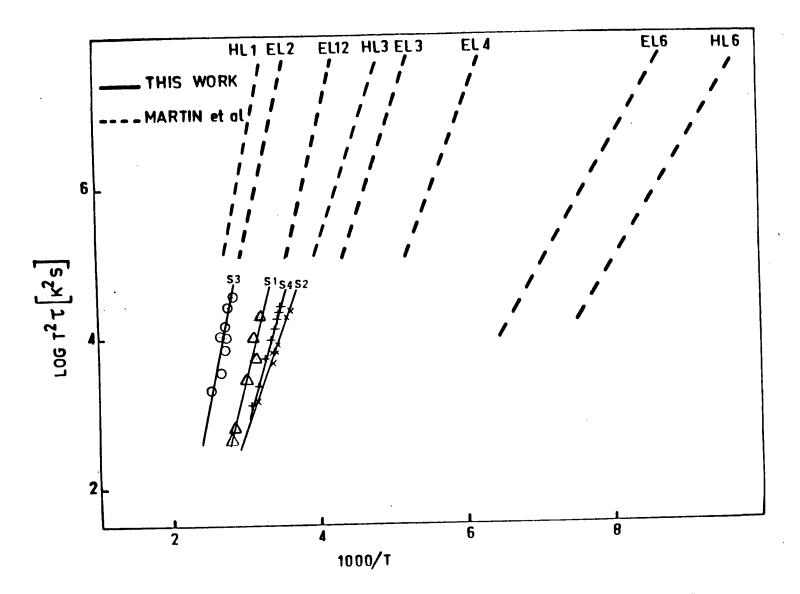

| 5.5 | Channel current DLTS spectra for MESFETs fabricated on<br>five substrates (Rate Window = 49.7 msec)   | <b>9</b> 0 |

| 5.6 | Signature line plots of the channel current DLTS data                                                 | 95         |

| 5.7 | Comparison of normalized drain current versus<br>backgating voltage for five GaAs samples             | 100        |

#### ACKNOWLEDGEMENTS

I thank my supervisor, Dr. L. Young, for his guidance and for suggesting many of the ideas of my work.

Mr. Wade Tang is to be thanked for his assistance in the DLTS experiments and for his helpful discussions.

I also thank Messrs. I.A. Motaleb, P. Townsley, and K. Tan for their assistance in fabrication; D. Hui for writing the software routines used to prepare some of the figures; W.C. Rutherford for proofreading my thesis; and W. Durtler, M. LeNoble, N. Jaeger, and P. Neilson for the helpful discussions.

Appreciation is also due to Messrs. R.F. Redden and R.P. Bult of Cominco Ltd., and K. Lowe of Bell Northern Research for supplying some GaAs wafers; A. Lakhani of Allied Bendix Aerospace for preparing some of the samples used in the channel current DLTS measurements; A. Leugner and L. Kjolby, who maintained the equipment in the lab; and Ms. M. Depuit who typed the manuscript.

Financial support provided by the British Columbia Science Council and by the Natural Sciences and Engineering Research Council of Canada is also acknowledged.

- ix -

#### CHAPTER 1

#### INTRODUCTION

Formation of uniformly doped impurity layers in bulk grown GaAs substrates for integrated circuit (IC) fabrication by ion implantation offers more advantages than the use of doped epitaxial grown layers because of the ease, precise control and reproducibility of the implantation process. Of the two available bulk crystal growth methods, Horizontal Bridgman (HB) and Liquid-Encapsulated Czochralski (LEC), the former has found decreasing applications in IC fabrication because of the limitation of the size and shape of HB substrates, and because of low device yield. LEC grown GaAs, on the other hand, is becoming the dominant choice for IC fabrication because two to four inch diameter wafers can be grown, and because semi-insulating (SI) GaAs can be made without intentional addition of impurities.

The objectives of this thesis are to investigate undoped LEC GaAs substrates for IC fabrication. GaAs wafers from different vendors were obtained. The deep trapping levels in SI GaAs wafers were investigated using Optical Transient Current Spectroscopy (OTCS). Deep levels in ion implanted MESFETs fabricated using several different processing techniques were investigated by channel current Deep Level Transient Spectroscopy (DLTS). The processing techniques applied for MESFET fabrication included: (1) ion implantation directly into GaAs; and (2) ion implantation through Plasma Enhanced Chemically Vapor Deposited (PECVD) silicon nitride film. Several dielectric capping materials for high temperature anneals were used: (1) RF sputtered silicon dixoide; (2) PECVD silicon dioxide; and (3) PECVD silicon nitride. Active layer parameters of various ion implanted substrates were investigated and compared. The measurements used to assess the MESFETs were: (1) threshold voltage and drain current magnitudes and scatter; (2) sheet resistance, Hall mobility and undepleted carrier concentration; (3) carrier and drift mobility profiling, and (4) backgating.

The contents of the thesis are as follows: Chapter 2 gives an overview of SI GaAs crystal growth techniques with particular emphasis on undoped LEC GaAs technology. In Chapter 2, a review is presented on deep levels in the starting SI GaAs materials, and a comparison is made of the OTCS spectra of GaAs substrates from different suppliers. Influence of surface treatment on the OTCS spectra is also investigated. Chapter 4 details the results of deep level investigation in the MESFETs fabricated by the four different processing techniques described above. The objective being to find and compare process-induced deep levels. Chapter 5 contains a comparison of MESFETs made by the same process at the same time on GaAs wafers from three suppliers, including: (1) low and high pressure grown substrates; (2) high pressure grown substrates from two suppliers; and (3) two high pressure grown substrates from the same supplier which were grown at two different time periods. In addition, a substrate is investigated which did not pass qualification tests by a device manufacturer. Finally, Chapter 6 gives conclusions and suggestions for future work.

#### CHAPTER 2

#### GROWTH AND PROPERTIES OF SEMI-INSULATING GALLIUM ARSENIDE

#### 2.1 Introduction

Semi-insulating GaAs is used for the production of high performance electronic devices such as high speed digital integrated circuits, field effect transistors, charge coupled devices and monolithic microwave integrated circuits. For large scale integrated circuit GaAs technology to develop reliably many problems related to the reproducible growth of high quality crystals remain to be solved. To achieve high electrical yields of GaAs ICs [1] it is essential to develop GaAs subtrates with low density of dislocations and impurities, high resistivity and good thermal stability, high activation of the implanted species, and homogeneous doping profiles.

#### 2.2 GaAs Crystal Growth Techniques

There are two main GaAs crystal growth techniques: the Horizontal Bridgman (HB) and the Liquid-Encapsulated Czochralski (LEC) [2,3,4]. In the former, a quartz boat which contains gallium is sealed inside a quartz ampoule filled with an inert gas. Arsenic is placed at the neck of the ampoule, and a temperature gradient is established such that the arsenic starts to sublimate (614°C) and the temperature of gallium is held at 1235°C, the melting point of GaAs. After the arsenic evaporates and reacts with gallium to form a GaAs melt, either the ampoule or the heaters are slowly moved so that the GaAs is cooled at one end as the temperature gradient moves

along the boat; the growth then proceeds in the <111> direction. The resulting ingot takes the shape of the boat truncated by the liquid surface i.e., it is D shaped. The wafers have to be cut at an angle to yield  $\langle 100 \rangle$ material. A variety of impurities are introduced into the ingots in the quartz silica boat container. The predominant type of impurity is silicon, usually in the  $10^{16} - 10^{17}$  cm<sup>-3</sup> range [5]. To make the HB GaAs semi-insulating, a deep acceptor impurity, usually chromium, has to be incorporated into the melt at approximately  $10^{17}$  cm<sup>-3</sup> so as to balance the donor impurity level. Problems arise because of inhomogeneous FET performance in HB GaAs because of the nonuniformity in the chromium concentration resulting from the disagreement between the cutting plane and the growth plane [6]. As an alternative to quartz boats, Pyrolitic Boron Nitride (PBN) boats have been used in an attempt to achieve higher purity GaAs [5], somewhat better performance was reported, but nevertheless, the resulting electrical yields for ion implantation remain generally low [1].

The LEC technique [7] is used for the growth of III-V compounds with one volatile constituent. In this method, the melt is prepared by a compounding process [3] where gallium and arsenic are placed below a boric oxide  $(B_2 O_3)$  encapsulant and the entire assembly is heated. The temperature is held at the melting point of GaAs, and the seed is lowered through the molten encapsulant into the GaAs melt. In addition, an overpressure of an inert gas, typically argon, is applied to prevent the arsenic from bubbling through the boric oxide. Both the seed and the crucible are rotated slowly in the opposite directions at predetermined rotational speeds so as to reduce radial and slice-to-slice nonuniformities [8]. A slow pull rate is applied

to the seed and <100> GaAs round ingots 2-4 inches in diameter are grown.

To reduce contamination of GaAs with silicon, PBN rather than quartz crucibles are used [9]. The resulting silicon concentration is reduced from  $10^{16}$  to  $10^{15}$  cm<sup>-3</sup>. Another reason for not using quartz is that the boric oxide reacts with silicon resulting in losing the clear visibility through the encapsulant which is an essential requirement in GaAs melt growth. With a quartz crucible, the boric oxide turns grey, opaque, and becomes full of bubbles [9], evidence of undesirable reaction of the melt with the surroundings. With a PBN crucible, the boric oxide remains clear and scum free. Growth of highly resistive GaAs depends directly on the boric oxide preparation before growth; the encapsulant has to be heat treated and vacuum baked to reduce the water content and prevent contamination of the melt with oxygen.

Unlike HB GaAs ingots, LEC GaAs ingots are round, cylindrical and can be semi-insulating without intentional doping. Though it is necessary to add chromium to the GaAs melt when grown with quartz crucibles, the same material grown with PBN crucibles is sufficiently high in resistivity to make it acceptable for device fabrication. The major advantages of undoped over chromium doped LEC GaAs are the following: (1) the lower concentration of the ionized impurities leads to higher electron mobilities in the ion implanted region; and (2) the absence of large resistivity changes which are typically caused by the redistribution of chromium during high temperature annealing. Undoped LEC GaAs is gradually emerging as a high quality and reproducible material for fabrication of ion implanted active layers.

#### 2.3 Impurities and Their Role in Undoped LEC GaAs

The principal source of residual impurities in undoped LEC GaAs is the interaction of the melt with the crucible and the boric oxide encapsulant [10]. Investigation of the various impurities using spectroscopic techniques [1,11,12] revealed the existence of contaminants in undoped LEC GaAs grown with PBN crucibles, and substrate-to-substrate as well as ingot-to-ingot variations in concentration. Table 2.1 shows the order of magnitude of some of the impurities.

Boron, which is believed to be inactive in GaAs [11], is introduced into the melt through reaction with the boric oxide. Oxygen is believed to be substitional in the arsenic sublattice giving rise to a deep donor level. Its origin is traced to the water levels ("wetness") of the boric oxide. It was only recently concluded [13] that oxygen is not associated with the main electron trap EL2 which is responsible for the semi-insulating property of GaAs. Chromium, an unintentional impurity, creates a deep acceptor level [4] when it occupies substitutional sites in the gallium sublattice. Silicon is a shallow donor and has consistently lower concentration when a PBN rather than a quartz crucible is used. Carbon is observed at high concentrations in GaAs, and is believed to arise from the PBN crucible and from the close proximity of the melt to the hot graphite furnace parts [10]. This impurity forms a shallow acceptor and together with the deep donor antisite defect [14] tends to compensate the GaAs. Sulfur arises from the arsenic source element [1] and forms a shallow donor. Magnesium and manganese are shallow acceptors introduced from the silicon nitride coracle [1] and the bulk material [2] respectively. Iron and copper impurities are deep acceptors

# Table 2.1. Order of magnitudes of some common impurities found in SI, undoped, LEC GaAs

| Impurity  | Log (concentration/cm <sup>3</sup> ) |

|-----------|--------------------------------------|

| Boron     | 15                                   |

| Oxygen    | 16                                   |

| Chromium  | 14                                   |

| Silicon   | 15                                   |

| Carbon    | 16                                   |

| Sulfur    | 15                                   |

| Magnesium | 15                                   |

| Manganese | 15                                   |

| Iron      | 15                                   |

| Copper    | 15                                   |

| Selenium  | 15                                   |

| Tellurium | 15                                   |

with potentially degrading effects on the ion implanted layer. The former has been demonstrated to cause interface traps between the active layer and the substrate [15] whereas the latter moves rapidly at low temperatures causing effective reduction of the diffusion length of n-type GaAs [4]. Copper contamination of GaAs takes place during crystal growth as a result of contact with the puller's brass material [5].

# 2.4 Relation of the Melt Stoichiometry to Compensation and Thermal Stability of GaAs

GaAs melt composition is an important growth parameter which affects both resistivity [10,16] and the concentration of the midgap level EL2 [16] which is now believed to be the antisite defect arsenic on gallium site [14]. Stoichiometry variations in GaAs substrates generate various native defects which recently have been found to influence the ion implanted carrier concentration profiles and electrical activation [17]. Recent results on resistivity data [16] have shown that using dry boric oxide (500 ppm  $H_2^{0}$ ), and above a critical arsenic concentration of 0.48 atom fraction of the melt, the GaAs material is semi-insulating and thermally stable up to about 0.53 (As atomic fraction). For compositions where the arsenic atom fraction is above 0.53, the resistivity drops due to increase in the free electron concentration. On the other hand, below the critical arsenic concentration, GaAs turns p-type. This can be explained by reasoning that the EL2 concentration increases with increasing As/Ga and  $V_{GA}/V_{AS}$  ratios [14], and a balance is made with the residual carbon acceptors [18] so as to make the material semi-insulating. The material becomes p-type below the critical composition because the EL2 concentration becomes lower than that of the

shallow acceptors, and becomes n-type for compositions above 0.53 As atom fraction because the EL2 concentration is higher than the shallow acceptors concentration.

Significantly different results are obtained when using wet boric oxide (2000 ppm  $H_2$ 0). Recent results [19] have shown that in this case above a critical arsenic concentration of 0.42 atom fraction of the melt, the GaAs material remains semi-insulating up to an arsenic atom fraction of 0.48. The impurities concentration in the melt for boron, oxygen, and carbon are different from typical levels obtained with dry boric oxide. Lower concentration for both boron and carbon were found, but the concentration of oxygen predictably was larger. The compensation in this case is expected to be different because of the lowering in the concentration of both EL2 (due to different melt composition) and carbon and the increase in the density of oxygen donors.

The thermal stability of undoped SI GaAs is also strongly influenced by the stoichiometry of the melt. Conversion of the thin surface layer of GaAs to a conducting state, believed to be p-type, after thermal treatment was previously attributed to out-diffusion and pileup of residual acceptors, such as, manganese [20], and an increase in carbon levels due to solvents used during substrate preparation [12]. Recent results indicate that high thermal stability for undoped LEC GaAs can only be achieved with stoichiometric or arsenic rich compositions [10]. For gallium rich melts and dry boric oxide, the sheet resistance is observed to decrease rapidly following high temperature anneal. Surface conversion results when the EL2 concentration at the surface falls below the residual acceptor concentration,

and the surface becomes p-type. This mechanism is probably enhanced by the outdiffusion of gallium and/or arsenic defects to the surface.

#### 2.5 Recent Advances in the Growth of Undoped LEC GaAs

Major efforts in the past few years have been concentrated on developing a controlled and reproducible growth technique of high quality undoped LEC GaAs crystals. One such effort aims at purifying the material using a special computer controlled distillation process [21]. In this technique, the arsenic pressure inside the growth chamber is abruptly decreased to near one atmospheric pressure; this creates bubbling in the boric oxide encapsulant as gases which include water, compounds of carbon and water, compounds of silicon and water, and excess arsenic are released from the melt. This bubbling process is repeated until the electrical conductivity of the melt is appreciably decreased. GaAs crystals are grown at low pressure (6 atm), and low temperature gradient in the melt ( $50^{\circ}$ C/cm) is achieved by using thermal reflectors. With both silicon dioxide and PBN crucibles, highly homogeneous and highly resistive ( $1 \times 10^{8}$  ohm-cm) ingots were obtained. The wafers are characterized with low dislocation density ( $8 \times 10^{3} - 1 \times 10^{4} \text{ cm}^{-2}$ ) with a U-shaped distribution.

An alternative to the high pressure growth synthesis which is in common use is a recent low pressure growth technique which is said by its advocates to be more efficient [22]. The advantages of low pressure growth techniques are that the cycle times are significantly shorter, the maximum crucible temperature is lower, the melt capacity is larger, and the melt stoichiometry can be better controlled. Though the quality of the material has not been fully proven, recent results of GaAs grown using quartz crucibles indicate similar thermal stability for arsenic rich melts (As/Ga = 1.02-1.04 atomic) and dry boric oxide (500 ppm water). The activation and mobility of silicon implanted material indicates similar results compared to the high pressure grown GaAs. The work for this thesis includes tests on a GaAs wafer grown at low pressure.

More recently, attempts were made to reduce the dislocation density in semi-insulating GaAs crystals [23,24]. The principle involved is to grow the crystal under a low temperature gradient and under a low pressure (5 atm), as this further lowers the temperature gradient by decreasing the convection heat transfer. The improvements made are found in: (1) reducing the arsenic escape by increasing the thickness of the boric oxide encapsulant; (2) reducing the temperature gradient at the boric oxide and the GaAs melt interface; (3) reducing the temperature gradient of the boric oxide itself by opening windows bored in the susceptor cylinder to directly heat this layer [24], and by setting a thermal baffle above the crucible [23]. As a result of those improvements, very low dislocation densities of approximately  $1000/cm^2$  with uniform distribution, and homogeneous high resistivities ( $10^8$ ohm-cm) were obtained for two inch diameter wafers.

Another technique which is successfully applied to obtain dislocation free crystals is based on adding large amounts of indium or indium arsenide (0.1 mol% - 0.4 mol%) to the GaAs melt [12]. Those additions are found to be effective in suppressing the generation of microdefects which are responsible for the formation of dislocations. This improvement, along with reducing the temperature gradient at the solid/liquid interface, is necessary to prevent

the generation and multiplication of dislocations from localized thermal stresses. The resulting quality of the ion implanted layers' uniformity indicate better homogeneity than conventional undoped LEC GaAs crystals.

Finally, the application of a vertical magnetic field [25,26] has been attempted recently to enhance the uniformity and to reduce the dislocation density of high pressure LEC PBN grown GaAs. The effect of the magnetic field, which is supplied by a super-conducting coil, is to suppress the temperature fluctuations through the molten GaAs. More importantly, laminar thermal convection which degrades both the microscopic and macroscopic homogeneity of crystals has been reduced. Uniformity in the GaAs melt is enhanced by optimizing the seed rotation as this adds forced convection to the melt. It is expected that those improvements can enhance the quality of the GaAs substrates for ion implantation.

#### CHAPTER 3

## OPTICAL TRANSIENT CURRENT SPECTROSCOPY INVESTIGATION OF VARIOUS GaAs SUBSTRATES

#### 3.1 Introduction to Optical Transient Current Spectroscopy

Optical Transient Current Spectroscopy (OTCS), often referred to as Photo Induced Transient Spectroscopy (PITS) [27], is a member of the class of Deep Level Transient Spectroscopy (DLTS) techniques. Its advantage is that it can be applied to semi-insulating GaAs (which is the starting material for integrated circuit (IC) fabrication). The aim is to obtain information on deep trapping levels which may be of fundamental interest and would certainly be of practical interest if it could help in diagnosing the suitability of the material for IC fabrication.

The OTCS method was introduced by Hurtes, Boulou, Mitonneau, and Bois [28], by Fairman, Morin and Oliver [29], and by Martin and Bois [30]. This method is suitable for the investigation of deep trapping levels in high resistivity epitaxial layers and semi-insulating GaAs substrates to which other deep trapping level spectroscopy methods [31] are not applicable. Several GaAs materials have been investigated using OTCS; for example, chromium doped Bridgman GaAs was investigated by Hurtes [28], Devaeaud [32], Fairman [1,29,33], and Martin [30], Chromium doped LEC GaAs was investigated by Fairman [1,29,33], whereas undoped LEC GaAs was examined by Oliver [34], K. Lowe [35], and W. Tang [36]. GaAs grown by Vapor Phase Epitaxy (VPE) on chromium doped substrates was investigated by Itoh [37], Fairman [1,29,33], and Hurtes [28]. OTCS was further used to search for deep levels in other materials such as, indium phosphide (InP) [27], and lead iodide (PbI<sub>2</sub>) [38] which is an insulator.

As a result of the application of OTCS to the study of GaAs substrate material, several significant deep levels were observed. For example, the deep level EL2 [39,40] has been observed by Martin [30], and Tang [36]. Chromium related deep levels which are responsible for the semi-insulating behaviour of chromium doped GaAs were detected (as HL1) by several investigators [1,28,29,32,33,37,41]. Other deep levels due to impurities or native defects [42] (and with distribution affected by dislocations [43]) were also detected, and are believed to cause problems of variable threshold voltage [44], hysteresis [45], frequency dependent transconductance [46], and noise [47] in GaAs ICs.

#### 3.2 Theory of Optical Transient Current Spectroscopy

The theory of OTCS was proposed by Hurtes et al. [28] and then developed by Martin et al. [30]. It is based on a depletion layer model where the current is determined by the charge transport across a depletion layer by electrons or holes released from traps. Thus an electron trap (i.e. a centre which communicates only with the conduction band) may capture an electron during illumination and lose it afterwards. The contribution which the electron makes to the terminal current as it crosses the depletion layer is as if this layer acted as an insulator separating the conducting (or semi-conducting region) from the electrodes. A hole trap behaves similarly. Once gone the carriers are not replaced because the concentration of electrons and holes in the reverse biased junction depletion region are low. Assuming that the probability f that a trap is occupied by an electron, the following rate equations are defined [48]:

rate of electron capture =  $r_a = n N_T (1-f) V_{\sigma} \sigma_{n n}$

rate of electron emission =  $r_b = N_T f e_n$

rate of hole capture =  $r_c = p N_T f V_p \sigma_p$

rate of hole emission

$$= r_d = N_T(1-f) e_p$$

where n(p) is the density of electrons (holes),  $V_n(V_p)$  is the thermal velocity of electrons (holes),  $\sigma_n(\sigma_p)$  is the electron (hole) capture cross section, and  $N_T$  is the total population of the trap. Imposing the steady state condition that  $r_a - r_b = r_c - r_d$  yields:

$$f_{ss} = \left(1 + \frac{e_n + \sigma_p V_p p}{e_p + \sigma_n V_n}\right)^{-1}$$

Given that the current during illumination has reached a steady value and that at time t=0 the illumination is removed one finds:

$$f(0) = \left(1 + \frac{e_n + \sigma_p V_p (p_{\infty} + \delta_p)}{e_p + \sigma_n V_n (n_{\infty} + \sigma_n)}\right)^{-1} \approx \left(1 + \frac{\sigma_p V_p}{\sigma_n V_n}\right)^{-1}, \text{ for } \delta_n = \delta_p \text{ large enough}$$

$$f(\infty) = \left(1 + \frac{e_n + \delta V_p p}{e_p + \sigma V_n}\right)^{-1} \approx \left(1 + \frac{e_n}{e_p}\right)^{-1}, \text{ for no recapture in the dark.}$$

where n(p) is the equilibrium concentration in the dark of electrons (holes) and  $\delta_n \approx \delta_p$  is the excess number of electrons and holes generated by the light.

The current i(t) is given by  $r_b$  and  $r_d$ , i(t) =  $\frac{q \land W}{2} N_T (e_n f(t) + e_p (1-f(t)))$

where A is the area of the contact and W is the width of the layer. So

$$\Delta \mathbf{i}(\mathbf{t}) = \mathbf{i}(\mathbf{t}) - \mathbf{i}(\infty) = \frac{\mathbf{q} \wedge \mathbf{W}}{2} N_{\mathrm{T}} \left( e_{\mathrm{n}}(\mathbf{f}(\mathbf{t}) - \mathbf{f}(\infty)) \right) + e_{\mathrm{p}} \left( (1 - \mathbf{f}(\mathbf{t})) - (1 - \mathbf{f}(\infty)) \right)$$

From  $\frac{df}{dt} = -fe_n + (1-f)e_p$  with solution

$$f(t) = f(\infty) + (f(0) - f(\infty)) \exp -t/\tau$$

where  $1/\tau = e_n + e_p$ , we obtain:

$$\Delta \mathbf{i}(t) = \frac{q \ A \ W}{2} \ N_{\mathrm{T}}(\mathbf{e}_{\mathrm{n}} - \mathbf{e}_{\mathrm{p}}) \left(1 + \frac{\mathbf{e}_{\mathrm{n}} + \sigma_{\mathrm{p}} \nabla_{\mathrm{p}}(\mathbf{p} + \delta_{\mathrm{p}})}{\mathbf{e}_{\mathrm{p}} + \sigma_{\mathrm{n}} \nabla_{\mathrm{n}}(\mathbf{n} + \delta_{\mathrm{n}})}\right)^{-1}$$

$$- \left(1 + \frac{\mathbf{e}_{\mathrm{n}} + \sigma_{\mathrm{p}} \nabla_{\mathrm{p}} \mathbf{P}_{\mathrm{m}}}{\mathbf{e}_{\mathrm{p}} + \sigma_{\mathrm{n}} \nabla_{\mathrm{n}}}\right)^{-1} \ \exp(-t/\tau)$$

Hurtes et al. treated the case of large  $\delta_n = \delta_p$  during illumination and no recapture in the dark to obtain:

$$\Delta \mathbf{i}(\mathbf{t}) = \frac{\mathbf{q} \ \mathbf{A} \ \mathbf{W}}{2} \ \mathbf{N}_{\mathrm{T}}(\mathbf{e}_{\mathrm{n}} - \mathbf{e}_{\mathrm{p}}) \left[ \left( 1 + \frac{\sigma \ \mathbf{V}}{\sigma \ \mathbf{V}_{\mathrm{p}}} \right)^{-1} - \left( 1 + \frac{\mathbf{e}_{\mathrm{n}}}{\mathbf{e}_{\mathrm{p}}} \right)^{-1} \right] \ \exp \left(-t/\tau\right)$$

For electron traps where  $\sigma_n/\sigma_p >> 1$  and  $e_n >> e_p$ , and for hole traps where  $\sigma_p/\sigma_n >> 1$  and  $e_p >> e_n$ , then the current reduces to:

$$\Delta i(t) = \frac{q A W}{2} N_T \tau^{-1} \exp(-t/\tau)$$

where  $\tau = 1/e_n$  for electron traps, and  $\tau = 1/e_p$  for hole trap. For the case of a boxcar's sampling whose output is

$$\Delta \mathbf{i}(\mathbf{t}) = \mathbf{A}_{\mathbf{B}}(\mathbf{i}(\mathbf{t}_1) - \mathbf{i}(\mathbf{t}_2))$$

where  $A_{B}$  is the boxcar's amplification, the current difference is:

$$i(t) = A_B \frac{q A W}{2} N_T \tau^{-1} \left( \exp(-t_1/\tau) - \exp(-t_2/\tau) \right)$$

By differentiating the current difference with respect to  $\tau$  and setting the result to zero, the value of maximum  $\tau_m$  can be solved:

$$\frac{\delta\Delta i(t)}{\delta(\tau)} = 0 = (1-t_1/\tau_m) \exp(-t_1/\tau_m) - (1-t_2/\tau_m) \exp(-t_2/\tau_m)$$

can be solved for once  $t_1$  and  $t_2$  are set; and when the boxcar's time constant is set to this value, a maximum  $\Delta i(t)$  is registered at a characteristic temperature  $T_m$ . Data on the activation energy  $\Delta E$  and capture cross section  $\sigma$ can be obtained by inserting the sets of characteristic temperatures for each time constant into the equation defining the time constant of traps:

$$\tau = (\sigma \gamma T)^{-1} \exp(\Delta E/kT)$$

where  $\Delta E$  is the difference from the conduction band to the trapping level energy for electron traps, and is the difference between the trapping level and the valence band for hole traps.  $\gamma$  is a constant defined as  $2.28 \times 10^{20}$ cm<sup>-2</sup> S<sup>-1</sup> k<sup>-2</sup> for electron traps and  $1.70 \times 10^{21}$  cm<sup>-2</sup> S<sup>-1</sup> k<sup>-2</sup> for hole traps.

While electron and hole traps give rise to positive peaks as the boxcar's output is swept through a temperature range of 150K to 400K, nevertheless, negative peaks are seen in various undoped LEC GaAs samples. They are obtained if  $e_n > e_p$  and  $(\sigma_p V_p / \sigma_n V_n) > (e_n / e_p)$ , or if both inequalities are reversed. The possible mechanism [49,50] is that a centre which gives a negative peak gives a steady state dark current due to its pumping out first an electron then a hole. When the illumination ceases, one of these events occurs more slowly, and if the traps are left in the condition which requires the slow process as the next step, the current will initially be low i.e. a negative peak is produced.

#### 3.3 Experimental Procedure

Semi-insulating GaAs starting substrate materials investigated in this work were obtained from Cominco Ltd. and Bell Northern Research (BNR). All the substrates were LEC undoped wafers grown in the <100> direction. Three wafers labelled 344S10 (sheet resistivity =  $2.8 \times 10^8$  ohms/square, mobility =  $6700 \text{ cm}^2/\text{v}$  sec, etch pits =  $27000/\text{cm}^2$ ), 453874 and 453875 (sheet resistivity =  $3.1 \times 10^8$  ohms/square, mobility = 6100 cm<sup>2</sup>/v sec, etch pits =  $39000/\text{cm}^2$ ) were obtained from Cominco. The first number in the label represents the ingot number, and the letter S (for seed) indicates that the last number stands for the slice number in the ingot counted from the seed end. Wafer #453874 was reported (by BNR) to have been etched about 10 um using the following chemical etch:  $H_2 SO_4 : H_2 O_2 : H_2 O$  (4:1:1 by volume). A single wafer from Sumitomo was obtained which was grown at high pressure the same way as those from Cominco. The wafer was labelled 400600-1, and resistivity  $> 10^7$  ohm.cm. No data were obtained for mobility and etch pit density. A single wafer from Litton was obtained. This was grown at low pressure. The wafer was taken from boule 2052, slice 2-9, and had the following specifications: resistivity =  $1.37 \times 10^8$  ohm.cm, mobility = 2810 cm<sup>2</sup>/v sec, and etch pit density =  $30000/cm^2$ . All wafers were 2 inches in diameter.

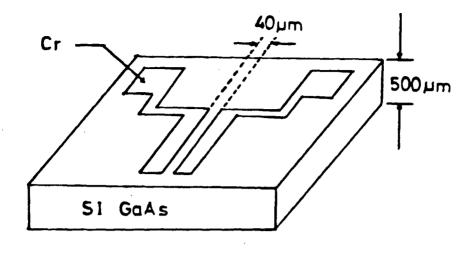

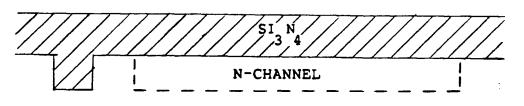

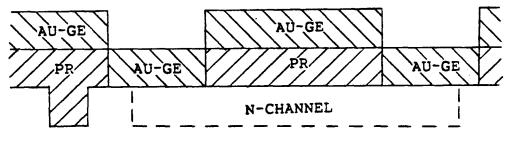

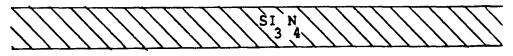

Two types of test devices for OTCS were used. These were the planar and the sandwich type (figure 3.1). In the planar type the electrodes were evaporated side by side on one surface, and in the sandwich type they were evaporated on opposite surfaces. The electrodes were [3] either chromium or gold-germanium (Ge = 12%wt + Au=88%wt) unalloyed or alloyed at 450°C in flowing nitrogen. The chromium and unalloyed Au/Ge form a Schottky barrier.

(Ъ)

Fig. 3.1 Geometry of (a) planar and (b) sandwich structures used in OTCS

-

The alloyed Au/Ge produces an n+ layer just under the contact (due to Ge). Some samples were thinned by grinding them in a silicon carbide slurry on a glass plate followed by a chemical etch in a solution of  $H_2SO_4+H_2O_2+H_2O_4$ (4:1:1 by volume) for two minutes.

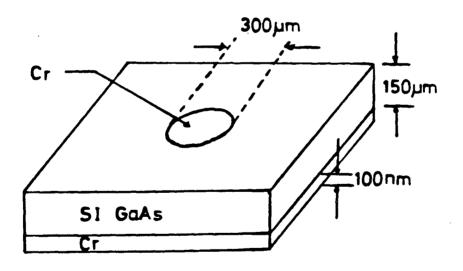

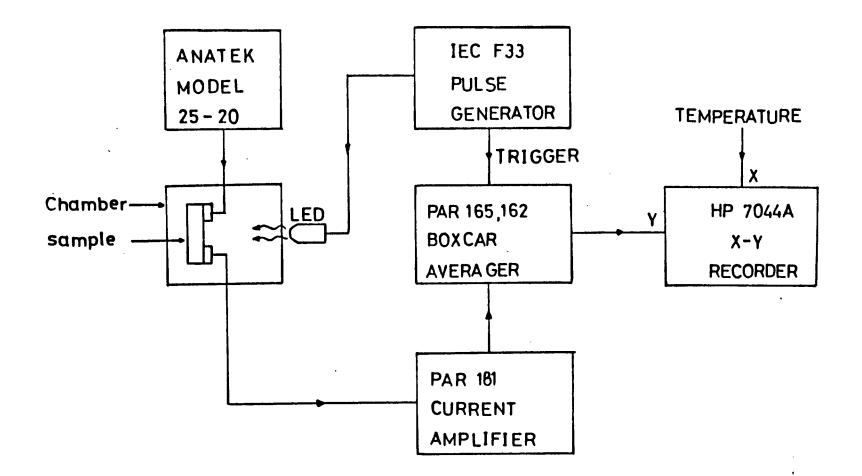

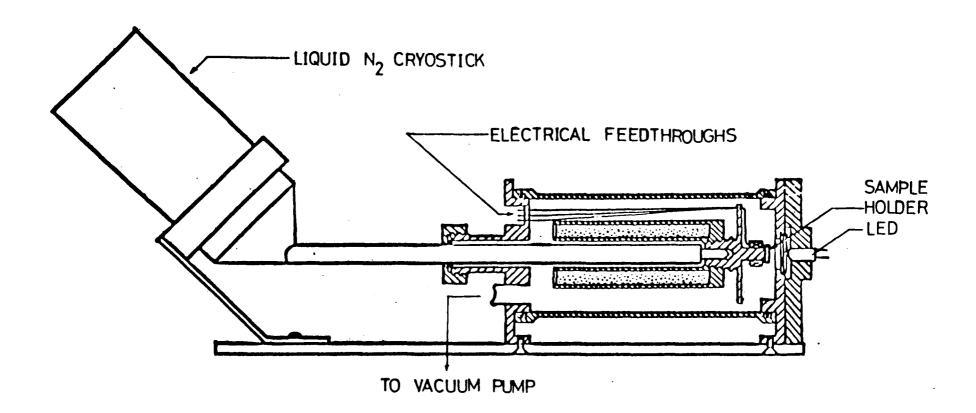

The block diagram of the experimental setup is shown in figure 3.2. The samples were mounted on a liquid nitrogen cooled finger (KRYOSTIK model 1320H) in an evacuated light-tight chamber as shown in figure 3.3 with contact probes for electrical connections. A power transistor was used to heat the samples. A copper-constantan thermocouple for temperature measurement was mounted on the sample holder close to the device. Light pulses were provided by a GaAsP 670 nm LED. A fixed voltage bias (typically ±7 VDC) was applied to the sample, and the current was amplified with an EG&G 181 current sensitive amplifier followed by an EG&G dual gate boxcar. The output of the boxcar and of the thermocouple (through an amplifier) were recorded on an X-Y recorder.

#### 3.4 Results

The main practical question about the OTCS technique is whether it can usefully be employed to test the suitability of a particular batch of material for device fabrication. In addition to obtaining information about deep trapping levels, the use of OTCS here is further extended to investigate several effects on the DLTS spectrum, such as, the effects of chemical etch, surface damage, different test structures, varying contact geometry, and choice of electrode material.

,

Fig. 3.3 Vacuum chamber used in the OTCS experiment

#### 3.4.1 OTCS Spectra of GaAs Substrates From Three Vendors

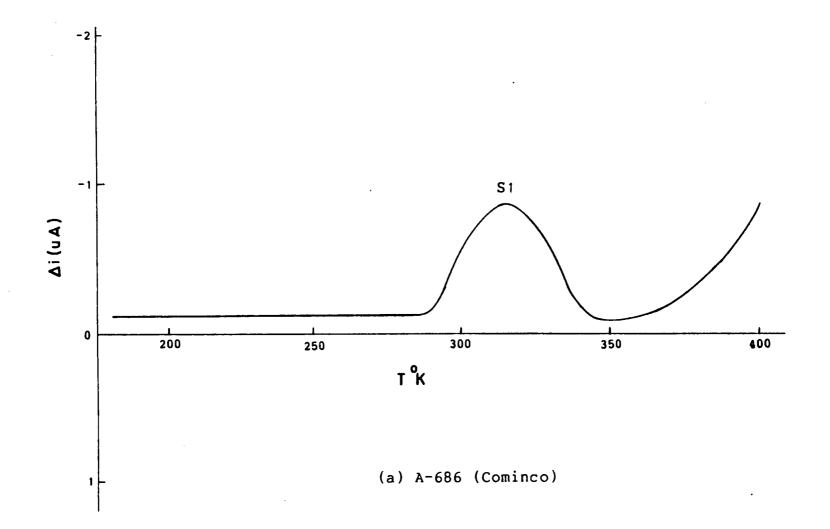

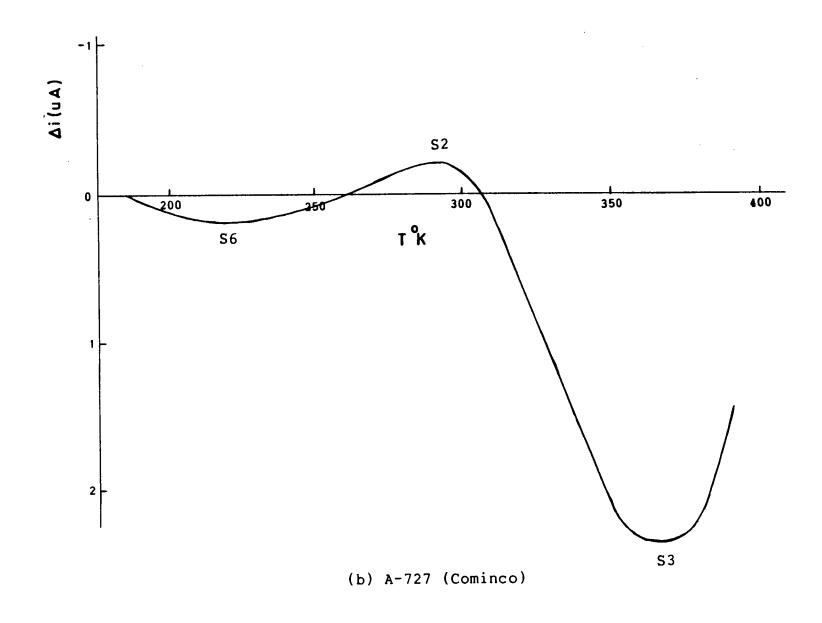

Figure 3.4(a,b,c) shows the OTCS spectra of devices made on slices of Cominco's, Sumitomo's, and Litton's GaAs respectively. The test samples used here were the planar type with chromium electrodes (length = 30 um, width = 600 um). The spectrum of Cominco's GaAs was similar to test devices tested earlier [36] except in the high temperature range where the magnitude of the negative peak was larger, and peak 1 appears much smaller in magnitude. No information on how typical the GaAs substrates from Sumitomo and Litton is known. The OTCS spectra of Cominco and Sumitomo GaAs substrates show the same traps and with similar relative heights. Both substrates were high pressure LEC material. The OTCS spectrum of the Litton substrate, low pressure grown LEC, was considerably different in that although it shows a similar set of peaks, the relative peak heights are different. Figures 3.5(a,b) show the DLTS spectra of samples of both Cominco and Sumitomo before and after chemical etch in a mixture of sulfuric acid, water, and hydrogen peroxide (4:1:1 by volume). Though peaks 1 to 4 are unaffected by the surface etch, peaks 5 to 8 were considerably reduced in amplitude. This indicates that the unaffected peaks were due to deep levels present in the bulk of the substrates, whereas the affected defects were enhanced by surface conditions such as damage, oxides, and chemical treatment. These results demonstrate that the OTCS technique is useful in the investigation of surface etching treatments much as are used in the fabrication of devices to remove damage or contaminated surfaces.

Fig. 3.4 OTCS spectra of SI undoped LEC GaAs from three vendors (Rate Window = 8.5msec)

(a) Cominco sample

(b). Sumitomo sample

Fig. 3.5 OTCS spectra of SI undoped LEC GaAs substrates from two vendors subjected to chemical etch (Rate Window = 8.5msec)

# 3.4.2 Identification of the Peaks

Table 3.1 shows activation energies and capture cross sections of all the OTCS peaks found in this work. Figure 3.6 shows the signature lines of the OTCS peaks. Table 3.2 shows the data on traps found by previous investigators. The peak labelled 1 was identified from its signature line in figure 3.6 by comparison with the well known compilation of data given by Martin et al. [51] as being due to the main electron trap EL2. This peak has been reported many times using various forms of DLTS on conducting material but curiously not too often for semi-insulating material. This is presumably because most authors have used Au+Ge electrodes and these, as opposed to chromium, give inconveniently high dark currents at the temperatures necessary to observe EL2.

Peak 3 and the broad peak 4 have signature lines on either side of Martin et al.'s EL12. According to Martin, Lang et al. [52] have also observed this level which is probably due to an impurity. Polarity change on the sandwich type specimen [36] gave a greater peak for negative voltage on the illuminated electrode indicating an electron trap.

The broad peak 5 is often found with another peak 6 (for example figure 3.5a). Those two peaks are closest to EL3 and EL4 respectively in Martin et al.'s DLTS data. They used capacitance DLTS [48] on conducting as-grown MBE (molecular beam epitaxy) material to obtain the level EL4. Fairman et al. [33] identified as EL4 a centre which gave one of the two negative OTCS peaks which they observed in Cr-doped semi-insulating Bridgman slices. Peak 7 is found to closely resemble Martin et al.'s EL6, while peak 8 is found to be a hole trap from polarity measurement on thin samples [36].

Fig. 3.6 Activation energy plots for traps detected using OTCS

| label | activation energy<br>(ev) | capture cross section<br>(cm <sup>2</sup> ) | possible identity |

|-------|---------------------------|---------------------------------------------|-------------------|

|       |                           |                                             |                   |

| P1    | 0.87                      | $1.05 \times 10^{-12}$                      | EL2               |

| P2    | 0.65                      | $3.00 \times 10^{-12}$                      | negative peak     |

| Р3    | 0.79                      | $3.69 \times 10^{-12}$                      | EL12 ?            |

| P4    | 0.76                      | $2.12 \times 10^{-12}$                      | EL12 ?            |

| P5    | 0.59                      | $3.46 \times 10^{-12}$                      | EL3 ?             |

| P6    | 0.52                      | $2.90 \times 10^{-13}$                      | EL4               |

| P7    | 0.38                      | $3.20 \times 10^{-14}$                      | EL6               |

| P8    | 0.32                      | $2.50 \times 10^{-13}$                      | HL6               |

|       |                           |                                             |                   |

Table 3.1 Activation energies, capture cross sections, and possible identities of the deep levels found using OTCS (P1-8) in semi-insulating, undoped, LEC GaAs.

.

| Authors        | W <sub>0</sub> | σ(cm <sup>2</sup> )    | Identi-<br>fication | Materials                 |

|----------------|----------------|------------------------|---------------------|---------------------------|

|                |                |                        |                     |                           |

| Martin et al.  | 0.9            | $2.2 \times 10^{-14}$  | HL1                 | Cr-doped Bridgman GaAs    |

| [30]           | 0.74           | 6.3×10 <sup>-15</sup>  | EL2                 |                           |

|                | 0.57           | $5.4 \times 10^{-13}$  | EL3                 |                           |

|                | 0.35           | 5.5×10 <sup>-15</sup>  | EL5                 |                           |

|                | 0.34           | $2.7 \times 10^{-14}$  | EL6                 |                           |

|                | 0.27           | 2.05×10 <sup>-14</sup> | EL12                |                           |

|                |                |                        |                     |                           |

| Fairman et al. | 0.9            | 2×10 <sup>-14</sup>    | HL1                 | A11*                      |

| [1,29,33]      | 0.83           | 2×10 <sup>-13</sup>    | HL10                | Cr-doped LEC GaAs         |

|                | 0.65(N)**      | 1×10 <sup>-13</sup>    |                     | A11*                      |

|                | 0.60           | 1×10 <sup>-12</sup>    | EL3                 | Cr-doped LEC GaAs         |

|                | 0.51(n)**      | 1×10 <sup>-12</sup>    | EL4                 | Cr-doped Bridgman GaAs    |

|                | 0.34           | 4×10 <sup>-14</sup>    | EL6                 | A11*                      |

|                | 0.34           | 6×10 <sup>-13</sup>    |                     | VPE layer on Cr-doped Gal |

|                | 0.30           | 7×10 <sup>−14</sup>    | HL12                | Cr-doped LEC & Bridgman   |

|                |                |                        |                     | GaAs                      |

Table 3.2 Deep levels in SI GaAs reported in the literature (as detected by OTCS (PITS)). VPE = vapour phase expitaxial layer.

|                | 0.26       | 2×10 <sup>-12</sup>   |      | Cr-doped Bridgman GaAs            |

|----------------|------------|-----------------------|------|-----------------------------------|

| •              | 0.15       | 8×10 <sup>-14</sup>   |      | Cr-doped LEC GaAs                 |

|                | 0.14       | 1×10 <sup>-16</sup>   |      | VPE layer on Cr-doped GaAs        |

|                | **negative | peak                  |      | *Cr-doped LEC & Bridgman          |

|                |            |                       |      | GaAs and VPE layer on             |

|                |            |                       |      | Cr-doped GaAs                     |

|                |            |                       |      |                                   |

| Deveaud et al. | 0.87       | 1.3×10 <sup>-17</sup> | HL1  | Cr-doped Bridgman GaAs            |

| [32]           | 0.5        | 3×10 <sup>−19</sup>   |      |                                   |

|                |            |                       |      |                                   |

| Itoh et al.    | 0.98       | $1.3 \times 10^{-13}$ | HL1  | VPE(n-)                           |

| [37]           | 0.89       | 1.8×10 <sup>-14</sup> | HL1  |                                   |

|                | 0.75       | $2.7 \times 10^{-14}$ | EL2  |                                   |

|                | 0.62       | 1.5×10 <sup>-14</sup> | HL3  |                                   |

|                | 0.60       | 8.6×10 <sup>-13</sup> | EL3  |                                   |

|                | 0.42       | Not Given             |      | ;                                 |

|                | 0.41       | 1.4×10 <sup>-15</sup> | HL4  |                                   |

|                |            |                       |      |                                   |

| Rhee et al.    | 0.90       | $2.1 \times 10^{-12}$ |      | Cr-doped GaAs                     |

| [27]           | 0.85       | $1.3 \times 10^{-13}$ | HL1  |                                   |

|                | 0.73       | 1.3×10 <sup>-17</sup> |      |                                   |

|                | 0.17       | 3.9×10 <sup>-22</sup> |      |                                   |

|                |            |                       |      |                                   |

| Oliver et al.  | 0.83       | Not Given             | HL10 | undoped LEC GaAs grown with       |

| [34]           |            |                       |      | dry B <sub>2</sub> 0 <sub>3</sub> |

|               | 0.65(N) |           |     | undoped LEC GaAs grown with |

|---------------|---------|-----------|-----|-----------------------------|

|               |         |           |     | wet $B_2 O_3$               |

|               | 0.57    |           |     | undoped LEC GaAs            |

|               | 0.34    |           |     |                             |

|               | 0.28    |           |     |                             |

|               | 0.15    |           |     |                             |

|               |         |           |     |                             |

| Hurtes et al. | 0.90    | Not Given | HL1 | high resistivity VPE layer  |

| [28]          |         |           |     | on Cr-doped Bridgman        |

|               | 0.81    |           | EL2 | n-VPE layer with high       |

|               |         |           |     | Cr-doped Bridgman           |

|               | 0.56    |           | HL8 | high resistivity VPE buffer |

|               |         |           |     | layer on Cr-doped Bridgman  |

|               | 0.54    |           | EL3 | n-VPE layer with high       |

|               |         |           |     | resistivity buffer layer on |

|               |         |           |     | Cr-doped Bridgman           |

|               | 0.41    |           | HL4 | n-VPE layer with high       |

|               |         |           |     | resistivity buffer layer on |

|               |         |           |     | Cr-doped Bridgman           |

|               | 0.32    |           | EL6 | both type of samples        |

The peak labelled 2 is the negative peak and uncritical application of the equations for positive peaks gave activation energy 0.65 eV and capture cross section of  $3 \times 10^{-15}$  cm<sup>2</sup>. Oliver et al. [34] found using OTCS (their PITS) a strong negative peak with planar specimens made from undoped LEC GaAs grown with wet boric oxide, but not in slices grown with dry boric oxide. They found  $\Delta E = 0.65$  eV and suggested that this level was related to oxygen impurity and was partly responsible for the semi-insulating condition (since this was enhanced when wet boric oxide was used). Fairman et al. [33] using vapor phase epitaxial layers and Cr-doped Horizontal Bridgman crystals obtained similar results with  $\Delta E = 0.65$  eV and  $\sigma = 3 \times 10^{-13}$  cm<sup>2</sup>. Ogawa et al. [49] also using OTCS found a minor negative peak in samples of unstated geometry using undoped LEC. In the previous paper by Itoh et al. [37] using OTCS on Cr-doped Horizontal Bridgman slices no such negative peak or even low valley is seen (their figure 4) using an ungated FET with one Au+Ge contact on n+ gate pad and the other on semi-insulating sustrate with or without a semi-insulating buffer layer.

# 3.4.3 Effects of Varying Sample Geometry on OTCS Spectra

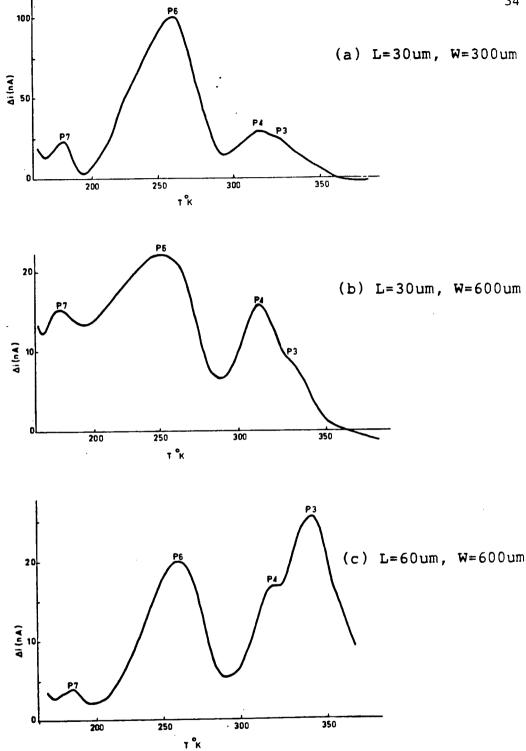

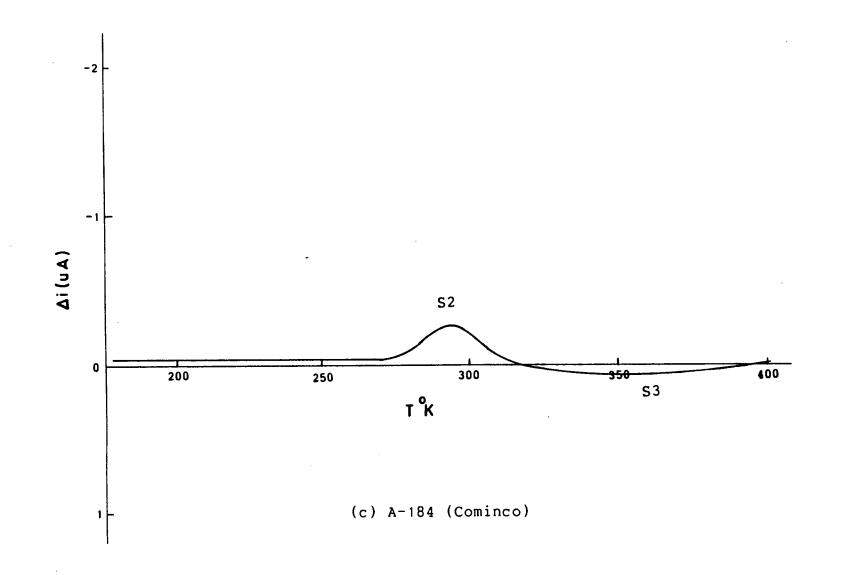

The effect of varying the contact spacing and width of the planar samples was investigated. Other authors have used varying spacings e.g. 500 um (Hurtes et al. [53]), 5 um (Fairman et al. [33]), 20 um (Itoh et al. [37]) and a little over 10 um (Rhee et al. [41]). Results of OTCS spectra for two different widths W = 300 and 600  $\mu$ m and two different spacings L = 30 and 60  $\mu$ m are shown in figures 3.7(a,b,c). With L = 60  $\mu$ m (Figure 3.7c) the right hand peak is very pronounced where it was a mere shoulder with L = 30 um.

OTCS spectra of different planar sample geometries Fig. 3.7 (Rate Window = 18.9msec)

(It lies between peak 1 (not appearing at higher temperature) and peak 4.) The negative peak was even less pronounced for L = 60 um than for L = 30 um, perhaps because the positive peak which was more pronounced is close enough to interfere by giving a reduction in the net increase in current with time after illumination. Peak 4 which is the prominent peak on the two L = 30devices, is now a mere shoulder on the 60 um device. The difference in the spectra for different geometries can be associated with the different sampling regions due to the different geometry.

### 3.4.4 Effect of Varying the Electrode Material

In the first work by Hurtes et al. [28], alloyed Au+Ge electrodes were used, whereas Martin et al. [30] used chromium electrodes for his sandwich sample structures because they noted that gold-germanium electrodes gave more complicated results. In earlier work [35] in this laboratory, alloyed gold-germanium electrodes were used, and they were found to result in too large dark currents which made OTCS measurements above room temperature very difficult. In later work [36], chromium electrodes were used and resulted in reduced leakage currents.

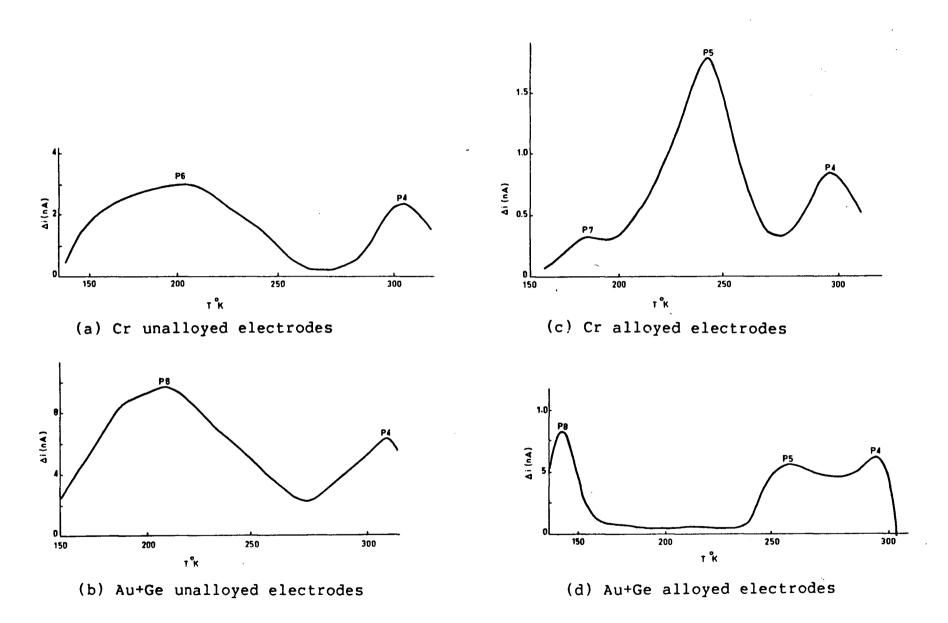

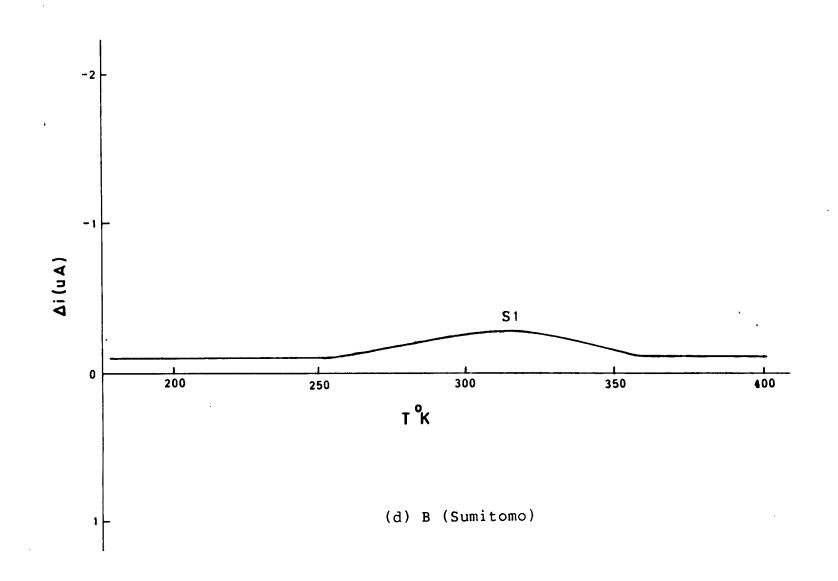

To investigate the difference in electrode material and preparation on the OTCS spectrum, four samples were prepared with two types of electrode material, Cr and Au+Ge. All devices were of planar type using a gateless MESFET structure with L = 30 um, and W = 600 um. Two samples with Cr and Au+Ge contacts were alloyed for ten minutes at 450°C. The OTCS spectra of the four devices which were made from Cominco's GaAs material are shown in Figure 3.8(a,b,c,d). The range of the OTCS scans were limited to those

Fig. 3.8 OTCS spectra of samples prepared with different electrodes (Rate Window = 38.8msec)

obtained for Au+Ge scans. The unalloyed Cr and Au+Ge electrodes gave the same two broad peaks but with different amplitudes. On alloying the Cr sample, the peak heights were all reduced, and the broad peak (combination of peaks 5 and 6) on the unalloyed sample, has now become distinct with peak 5 dominating. The Au+Ge specimen on alloying gave also an OTCS spectrum with some of the peaks such as, peak 6, reduced much in amplitude. In addition, the two low temperature peaks 7 and 8 amplitudes were different in both types of alloyed samples: whereas peak 7 (electron trap) remained in the Cr alloyed sample, peak 8 (hole trap) remained in the AuGe alloyed samples.

The results indicate that the deep levels are affected by the high temperature treatment upon alloying, and that the type of electrode seems to influence the results. One might also expect unalloyed Au+Ge and chromium to behave similarly, both acting as Schottky diodes. Au electrodes, used by some authors [41] would presumably be similar. On alloying the Au+Ge, the n+ layer due to Ge doping may be presumed to act as an efficient source of electrons. The heat treatment of the chromium electrodes was done for completeness and because chromium or related metal gates on MESFETs would quite normally receive the heat treatment applied to the Au+Ge source and drain electrodes.

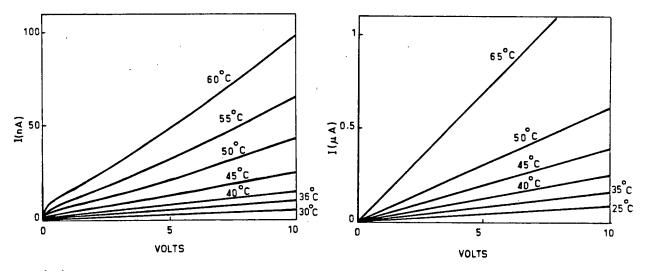

To help elucidate the effects of the nature of the contacts on the spectrum observed by OTCS, dark current vs. voltage curves were obtained using an HP 4145A semiconductor parameter analyzer. Data for Au+Ge and Cr electrodes before and after heat treatment at 450°C for 10 minutes are given in figures 3.9(a,b,c,d) for various temperatures. The current voltage curves for Cr (fig. 3.9a and 3.9c) are consistent with back to back diodes with

(a) Cr unalloyed electrodes

(c) Cr alloyed electrodes

(b) Au+Ge unalloyed electrodes (d) Au+Ge alloyed

(d) Au+Ge alloyed electrodes

Fig. 3.9 Current vs. voltage for planar specimens with different electrodes

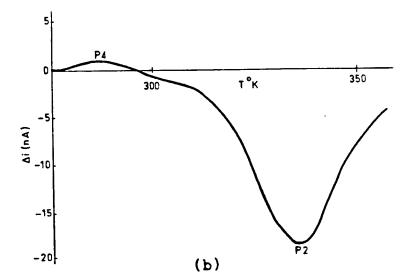

poorly saturating reverse current. On heat treatment the current decreased considerably. Those for Au+Ge (figure 3.9b and 3.9d) before heat treatment also appeared consistent with back to back poorly saturating diodes but still giving more current than Cr. After heat treatment the Au+Ge, the current voltage curves were fairly linear up to 0.5 uA with 10 volts between electrodes separated by 60 um. Arrhenius plots of log  $I_{dark}$  at 7 volts (as used in OTCS) vs. 1/T in figure 3.10 show the relative values of the currents and the activation energies. The slope of the data for Au+Ge changed slightly on alloying giving apparent activation energies of about 0.76 eV and 0.8 eV before and after. With chromium the slope changed from a value corresonding to 0.84 eV to one giving 0.72 eV.

# 3.4.5 Effect of GaAs Surface Damage on the OTCS Spectrum

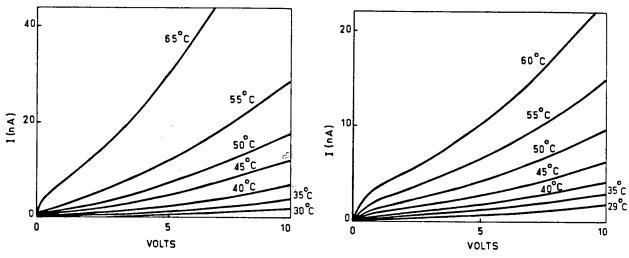

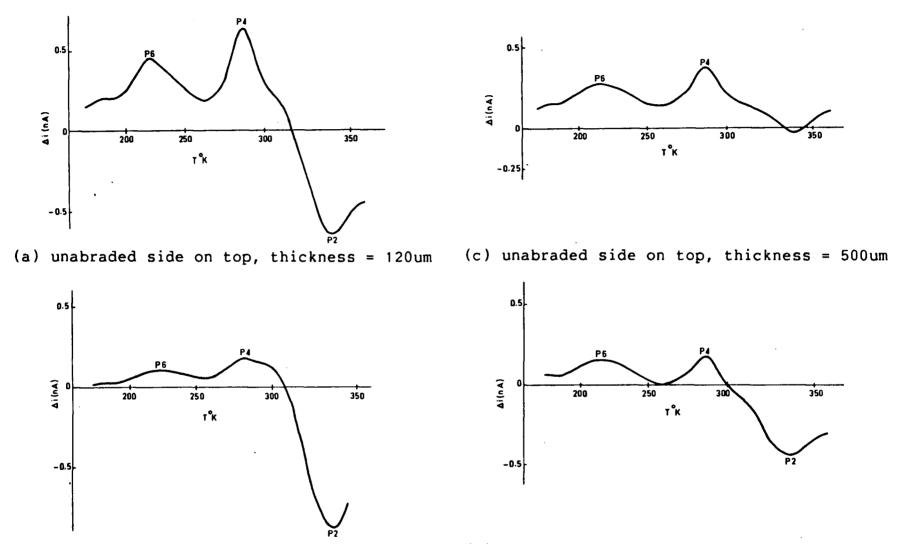

Previous work by Tang [36] has revealed that the relative peak heights changed for sandwich specimens than from planar ones. In particular, he found that the negative peak was much more accentuated for the sandwich than the planar sample. The question that arises then is whether the difference between sandwich and planar specimens were due to the geometry or whether the fabrication process affected the results (since Tang prepared his thin samples by abrading it so that the surface was damaged). To investigate these factors, thin sandwich samples were prepared by mounting the wafer fragment on a silicon slice with black wax and then abrading with a slurry of 400 grade carborundum. The specimens were then removed from the silicon with hot trichloroethylene and etched briefly in the sulfuric acid and hydrogen peroxide mixture used previously. Two such thin sandwich samples were

Fig. 3.10 Signature line plots for the data of figure 3.9 (Labels same as in figure 3.9)

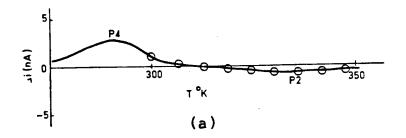

prepared with the top electrode in each case either on the abraded side or the polished side. In additon, another two thick sandwich sructures (i.e. starting wafer thickness = 450 um) were prepared where one of them was given a token grind, while the other merely degreased. The results of the OTCS spectra are shown in figure 3.11(a,b,c,d) for each of the above stated cases. In the case of the thin sandwich structures (figure 3.11a and 3.11b), for the sample where the abraded side was on top, the positive peaks were somewhat attenuated whereas the negative peak increased somewhat in amplitude compared to the sample with the polished side on top. This effect is attributed to grinding which was followed by surface etch. To demonstrate the effect of surface abrasion only (no etch), figure 3.11d shows the spectrum of the thick sandwich sample which was given a token grind. Compared to the thick sandwich structure which was merely degreased (figure 3.11c), the positive peaks were slightly attenuated whereas the negative peak has increased significantly in magnitude. To verify that the negative peak was affected by surface damage, and to investigate separately the effect of surface etch on the negative peak, a planar specimen was prepared this time. To start with, the spectrum of the sample, as is, (i.e. with no etching or grinding) was recorded as shown in figure 3.12a. The same sample was then etched by about 1 um using a mixture of sulfuric acid, hydrogen peroxide, and water (4:1:1) by volume). The OTCS spectrum indicated no difference (shown in circles in figure 3.12a). The sample was then lightly abraded using a carborundum slurry. The negative peak, figure 3.12b, was significantly accentuated. The sample showed almost the same starting OTCS spectrum, figure 3.12c, after the sample was etched. From these findings it can be concluded that the negative

(b) abraded side on top, thickness = 120um

(d) abraded side on top, thickness = 500um

Fig. 3.11 OTCS spectra of sandwich structures with a negative bias on the top illuminated electrode (Rate Window = 75.5msec)

Fig. 3.12 OTCS spectra of a planar structure (a) before and after chemical etch (b) after light abrasion (c) after chemical etch (Rate Window = 75.5msec)

peak is associated with the damage done to GaAs by the abrasion process.

## 3.5 Summary

From the above study, it was shown that the OTCS technique is a useful tool for the evaluation of GaAs material. The OTCS spectra were shown to be different for high and low pressure LEC grown GaAs. Some of the peaks were found to be dependent on the surface condition, as it was shown that the concentration of some of the deep levels were attenuated after the top surface layer was removed. The nature of the OTCS spectrum was found to be influenced by the electrodes, sample geometry, and fabrication method. Finally, surface damage was shown to affect the negative peak.

Before this chapter is concluded, it is useful to point out that the theory of OTCS based on the depletion layer model of Hurtes [28] (described in section 3.2) may not be totally applicable for the study of transients. For example in the case of transients resulting from a sandwich structure, the depletion layer will be confined to a small depth below the surface, while the bulk remains undepleted. Other models are now available [50] which provide for possible alternative description of the observed transients.

#### CHAPTER 4

## INVESTIGATION OF PROCESS-INDUCED DEEP LEVELS IN ION IMPLANTED MESFETS

#### 4.1 Introduction

Despite the recent advances which have been made in the field of MESFETs IC technology, there are still many problems concerning the stability of such devices due to the presence of deep level defects and impurities both those initially present in the substrate material and those induced by the fabrication process. It has been widely reported [5,54-59] that traps in the MESFET channel and in particular those at the interface of the channel and the semi-insulating substrate can cause such effects as looping in the drain I-V characteristics, low transconductance at saturation, low drain-source breakdown, low power gain, and large noise figures. Those effects were found in particular for active layers made by epitaxial growth over chromium doped gallium arsenide substrates because chromium tended to react with the active layer and form hole traps which contribute to the formation of an interface space charge region which in turn affect the channel width [59]. To isolate the active layer from the substrate, high purity epitaxial buffer layers were used to keep the deep levels in the substrate from diffusing into the MESFET channel. However, it was found [60] that for all buffer layer thicknesses  $(1-3 \mu m)$ , chromium, copper, and iron still were able to diffuse and resulted in a large number of deep levels at the active layer and buffer (A/B)interface.

Some of the problems with deep trapping levels in epitaxial layers and

at the A/B interface are no longer present in the case of ion implantation in undoped LEC GaAs substrates. Nevertheless, the problems of the newer technology still include those due to the presence of the many impurities [33,8] in undoped LEC GaAs substrates, and due to defects either present in the starting material or induced by the process steps. Process-induced defects in MESFET channels arise from several factors: (1) irradiation damage due to silicon ion implantation (used as n-type dopants), and whether the implantation was done directly into the surface or through a thin dielectric film; (2) the high temperature annealing stage required to remove the implantation damage and allow silicon to reach vacant gallium sites; (3) the type of encapsulant used; and (4) the chemical treatment of the surface. Of those factors, the first factor is important, since implants through silicon dioxide or silicon nitride can introduce unwanted atoms such as oxygen and nitrogen into the active layer by knock-on mechanisms [61] inducing serious defects. Also, the type of encapsulant which is used to preserve the GaAs stoichiometry during high temperature anneal is important. Studies have shown [62] that the implanted atoms redistribute by diffusion more with a silicon dioxide than a silicon nitride cap. Also, the silicon dioxide encapsulant does not preserve the substrates stoichiometry as well as silicon nitride since it is known that gallium can diffuse through the silicon dioxide. Problems of enhanced diffusion of defects are also caused by the encapsulants as a result of stresses due to thermal expansion mismatch between the dielectric cap and GaAs.

There is an extensive literature on electron and hole deep levels in GaAs [63] and on their effects on device characteristics. Recent papers

specifically on deep levels in ion implanted undoped semi-insulating GaAs include Sriram et al. [64,65], Rhee et al. [41,66] and Hickmott [45]. In this chapter, deep levels in silicon implanted MESFETS fabricated by four procedures are investigated by channel current DLTS. The four cases include effects of implants directly into GaAs and through silicon nitrde film, and also effects of three types of encapsulants.

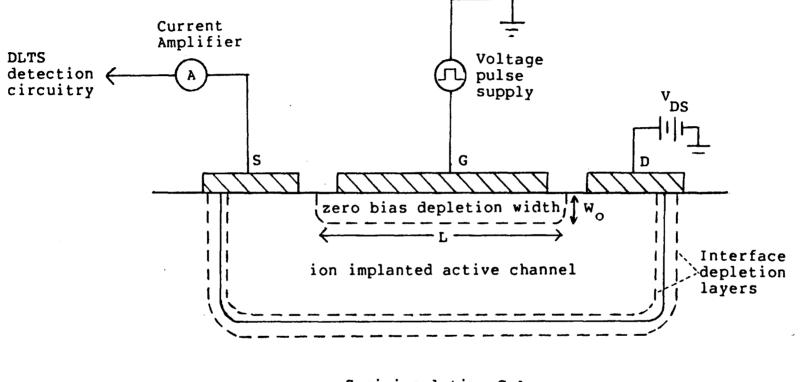

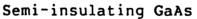

# 4.2 Principle of Channel Current DLTS

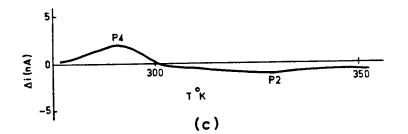

Channel current DLTS is a technique which allows the investigation of the deep level traps in ion implanted MESFET channels. The principle is illustrated in figure 4.1. A small bias (50 mV DC) is applied between the drain and source so that the FET operates in the linear region. A reverse bias voltage is placed on the gate such that the channel is nearly pinched off. Pulses of voltage taking the gate to near zero bias are applied. The basic idea is that majority carrier traps are filled by carriers which are allowed to enter the previously depleted channel during the positive going voltage pulse. When the gate voltage returns to its more negative value the negative charge due to the trapped electrons partially compensates the positive space charge density in the depleted region. To maintain the fixed voltage drop across the region it must therefore become initially wider than before. The channel is therefore narrowed and the drain current is less. As the occupancy returns to normal the drain current increases (with the time constant depopulation emission process) as illustrated in figure 4.2. Hole traps give the reverse sign of effect (the hole trap occupancy can be changed because the quasi Fermi level for holes communicates with the gate Fermi

level).

The depletion width which is modulated by the traps is obtained for any time t after the lapse of the zero bias pulse [64] as:

$$\Delta W(t) = W_{\infty} - W(t)$$

$$\Delta W(t) = \frac{-N_{T}}{2 W_{\infty} N_{D} |_{\infty}} (W_{\infty}^{2} - W_{O}^{2}) \exp(-e_{n}t) \qquad (4.1A)$$

for an electron trap. The corresponding expression for a hole trap:

$$\Delta W(t) = \frac{+ N_T}{2 W_{\infty} N_D |_{\infty}} (W_{\infty}^2 - W_o^2) \exp(-e_p t)$$

(4.1B)

where N is the total concentration of the trap,  $N_D \mid_{\infty}$  is the donor level T density at steady state depletion width,  $W_O$  and  $W_{\infty}$  are the depletion widths at zero gate and steady state depletion widths respectively.

The channel current for an arbitrary doping profile is:

$$I_{DS} = \int_{w_0}^{k} (q u(x) n(x)) (Z/L) V_{DS} dx \qquad (4.2)$$

where u(x) is the drift mobility in the channel, n(x) is the free carrier concentration, Z is the channel width, L is the effective channel length, and k is the channel thickness. For a small change in depletion width, (4.2) becomes:

$$\Delta I_{DS} = (q u(x) n(x)) (Z/L) V_{DS} \Delta W$$

(4.3)

This expression can be combined with (4.1A) to obtain the transient current equation for an electron trap:

$$\Delta I_{\text{DS}} = \frac{-(q u(x))|w_{\infty}}{2W_{\infty}} (Z/L)V_{\text{DS}} N_{\text{T}} (W_{\infty} - W_{\text{O}}^{2}) \exp(-e_{\text{n}}t)$$

(4.4A)

The corresponding expression for a hole trap:

$$\Delta I_{DS} = \frac{(q u(x))|w_{\infty}}{2W_{\infty}} (Z/L)V_{DS} N_{T} (W_{\infty} - W_{o}^{2}) exp(-e_{p}t)$$

(4.4B)

The current is sampled at two time instants,  $t_1$  and  $t_2$  by the boxcar averager which gives an output:

$$v_0(t) = A_B R (I_{DS}(t_1) - I_{DS}(t_2))$$

(4.5)

where  $A_B$  is the amplification of the boxcar, and R is the current to voltage conversion factor in the current amplifier. Utilizing the expressions in equation (4.4A), the output current becomes:

$$v_{0}(t) = -A_{B}R \frac{(q u(x))|w_{\omega}}{2W_{\omega}} (Z/L)V_{DS} N_{T} (W_{\omega}^{2} - W_{O}^{2}).$$

$$(exp(-t_{1}/\tau)-exp(-t_{2}/\tau))$$

(4.6)

The information about the traps is obtained by the DLTS circuitry as in section 3.2. The trap activation energy and capture cross section are obtained by plotting  $(T_m^2 \tau)$  vs.  $(1000/T_m)$ , where  $T_m$  is the characteristic temperature of the peak in the DLTS spectrum. The boxcar rate window in the case of channel current DLTS is obtained by differentiating (4.6) with respect to  $\tau$ , setting the result to zero, and solving for  $\tau_m$ :

$$\tau_{\rm m} = 1/e_{\rm n} = (t_1 - t_2) / \ln(t_1/t_2)$$

(4.7)

Unlike OTCS, positive peaks in channel DLTS correspond to hole traps, while negative peaks indicate electron traps. This technique is therefore unambiguous with respect to the type of the deep level. Also, in contrast to OTCS where the concentration of the traps are difficult to obtain because not all the levels are occupied during optical excitation, the concentration of traps in channel current DLTS can be estimated since during electrical excitation all the deep levels in the sampled region undergo periodical filling and emptying. The concentration can be estimated by solving for  $N_T$ in equation (4.6).

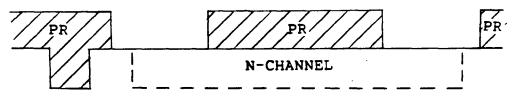

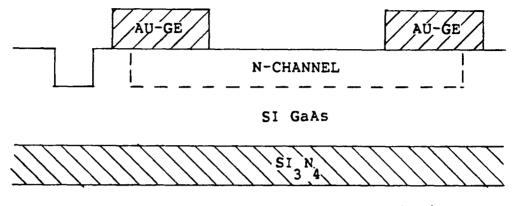

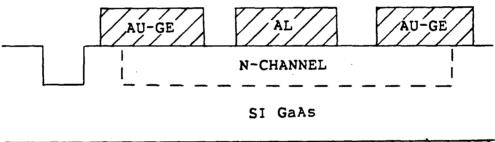

#### 4.3 Experimental Procedure

Four sets of long channel devices ("Fat FETs") were used for channel

current DLTS, each fabricated using a different procedure. Substrates from the following ingots of Cominco were used: #43, #51, #123, #175 and #344. The first set of fat FETs were fabricated by Lowe [35] with a gate length of 100 um and a gate width of 200 um. The channel was implated with  $3 \times 10^{12}$  cm<sup>-3</sup> <sup>28</sup>Si at 100 keV directly into the GaAs surface. A 600 nm RF sputtered silicon dioxide mask was used to block the silicon implant where isolation was needed. The implant damage was furnace annealed at 850°C for 20 minutes using a 170 nm RF sputtered silicon dioxide as an encapsulant.