### ION IMPLANTED GaAs MESFET TECHNOLOGY

by

KERRY STEVEN LOWE

B.A.Sc., The University of British Columbia, 1981

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

in the Department

of

Electrical Engineering

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

August 1983

© Kerry Steven Lowe , 1983

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of Electrical Engineering

The University of British Columbia 1956 Main Mall Vancouver, Canada V6T 1Y3

Date Aug. 19, 1983

### ABSTRACT

The availability of high quality semi-insulating GaAs substrates is essential to the development of GaAs metal semiconductor field effect transistor (MESFET) integrated circuits. Problems have been encountered with horizontal Bridgman grown substrates since, for example, these must be doped with Cr to make then semi-insulating and the Cr tends to diffuse during device processing. Undoped semi-insulating GaAs substrates can be grown by the Liquid Encapsulated Czochralski (LEC) technique and allow the possibility of forming active regions by the process of implanting dopants directly into the substrate.

The purpose of this thesis was to develop at the University of British Columbia a GaAs MESFET technology based on direct ion implantation and to develop methods to assess undoped LEC substrates for Cominco Limited, Trail, B.C. A test device array consisting of structures for process, material, and device characterization was designed and then fabricated on Cominco wafers by a direct implantation process. Measurements on the test device array elements showed that this initial process could be used to produce MESFET's operational up to 3° GHz and that the test device array will be useful for monitoring future process developments and improvements. In addition, a channel conductance deep level transient spectroscopy system, a photocurrent deep level transient spectroscopy system, and a novel MESFET drain current hysteresis analysis system were developed to examine deep levels in GaAs and deep level trapping effects in GaAs MESFET's.

# TABLE OF CONTENTS

|                                             | Page                 |

|---------------------------------------------|----------------------|

| ABSTRACT                                    | ii                   |

| LIST OF TABLES                              | v                    |

| LIST OF FIGURES                             | vi                   |

| ACKNOWLEDGEMENTS                            | viii                 |

| 1. INTRODUCTION                             | 1                    |

| 2. OVERVIEW OF GaAs MESFET TECHNOLOGY       | 3                    |

| 2.1 Introduction                            | 3<br>3<br>6<br>8     |

| 3. THE TEST DEVICE ARRAY                    | 9                    |

| 3.1 Description                             | 9<br>13              |

| 3.2.1 Substrate Preparation                 | 13<br>14<br>15<br>15 |

| 4. MEASUREMENTS ON THE TEST DEVICE ARRAY    | 21                   |

| 4.1 Active Layer Evaluation                 | 21<br>31<br>35<br>35 |

| 5. DEEP LEVEL TRANSIENT SPECTROSCOPY (DLTS) | 40                   |

| 5.1 Basic Principles                        | 40<br>43<br>50<br>53 |

|      |         | <u>-</u>                                  | Page           |

|------|---------|-------------------------------------------|----------------|

| 6.   | HYSTER  | ESIS-FREQUENCY SPECTROSCOPY               | 66             |

|      | 6.2 A   | heory pparatus easurements                | 66<br>73<br>75 |

| 7.   | SUMMAR  | Y AND CONCLUSION                          | 79             |

| REF  | ERENCES | •••••                                     | 81             |

| APPI | ENDIX A | Substrate Compensation Considerations     | 85             |

| APPI | ENDIX B | Some Ion Implantation Processes Used for  | 88             |

| APPI | ENDIX C | Some Deep Levels in GaAs Detected by DLTS | 89             |

# LIST OF TABLES

|     |                                    | Page |

|-----|------------------------------------|------|

| 3.1 | Test device array structures       | 9    |

| 4.1 | Active layer properties            | 30   |

| 4.2 | Metallization properties           | 33   |

| 4.3 | MESFET yield                       | 36   |

| 4.4 | Device parameters of 3 µm MESFET's | 39   |

| 5.1 | Deep levels detected by CDLTS      | 54   |

| 5.2 | Properties of Cominco GaAs         | 60   |

| 5.3 | Deep levels detected by PDLTS      | 64   |

# LIST OF FIGURES

|      |                                                                                           | Page |

|------|-------------------------------------------------------------------------------------------|------|

| 2.1  | GaAs MESFET                                                                               | 4    |

| 2.2  | Comparison of active layer formation processes                                            | 7    |

| 3.1  | Layout of the test device array                                                           | 11   |

| 3.2  | The masks for the test device array                                                       | 12   |

| 3.3  | Fabrication sequence for the test device array                                            | 17   |

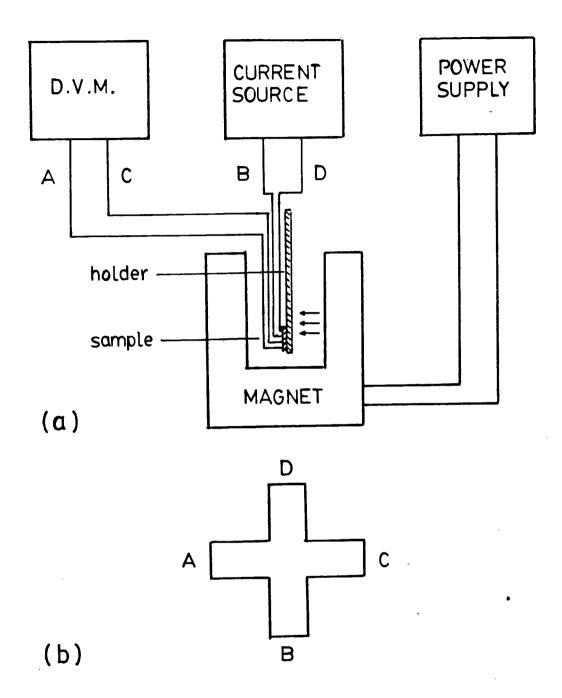

| 4.1  | Experimental arrangement used for van der Pauw measurements                               | 22   |

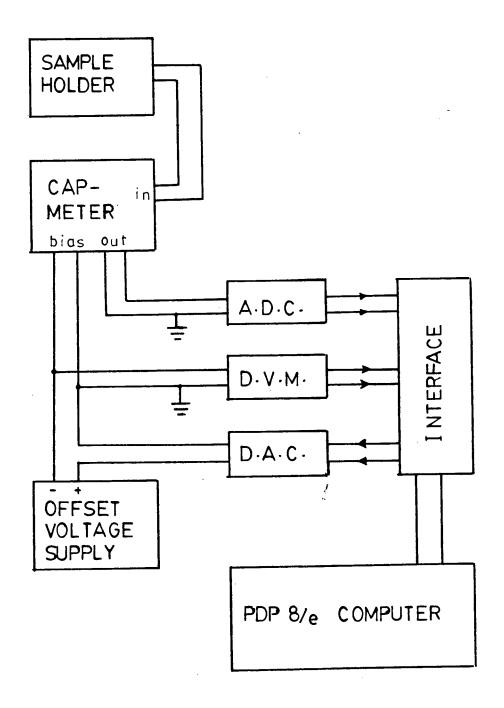

| 4.2  | Experimental arrangement used for C-V measurements                                        | 24   |

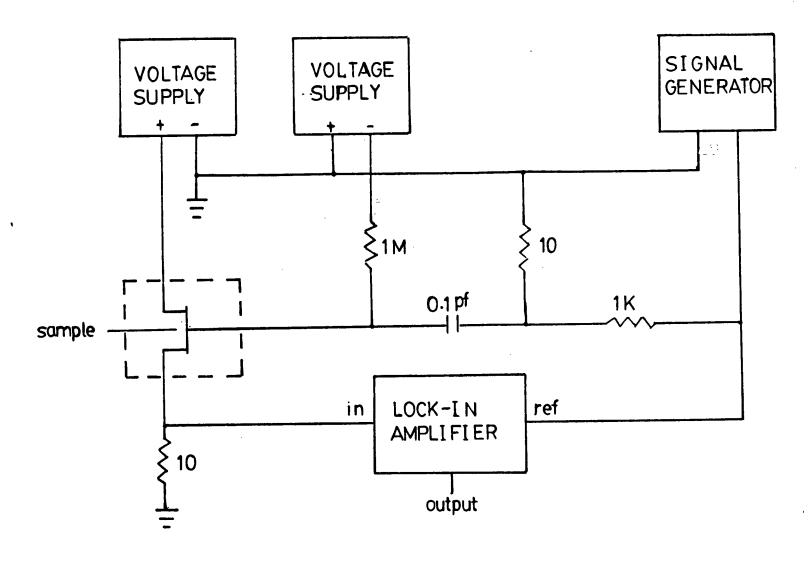

| 4.3  | Experimental arrangement used for drift mobility profiling                                | 26   |

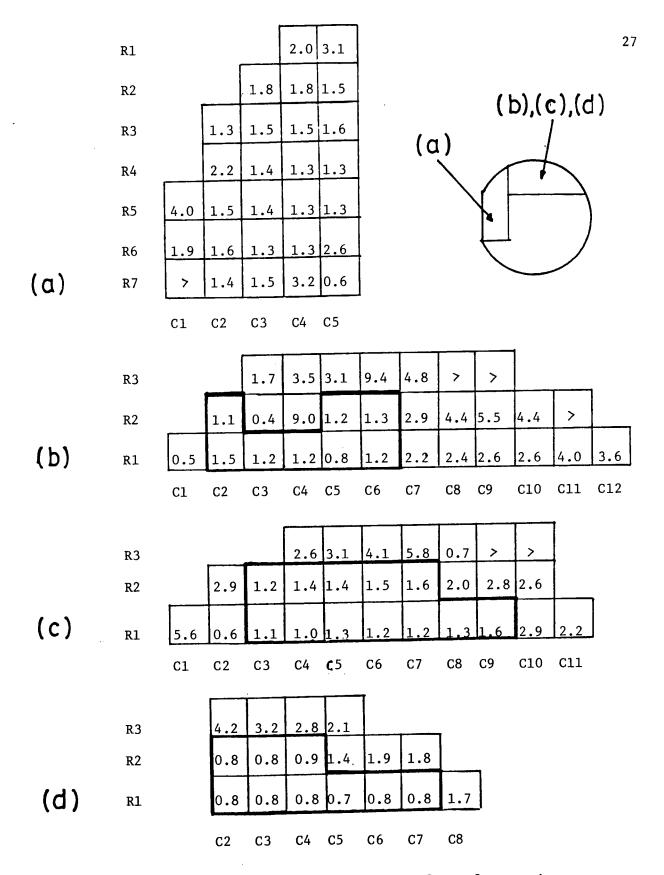

| 4.4  | Active layer sheet resistance values for wafersections fabricated                         | 27   |

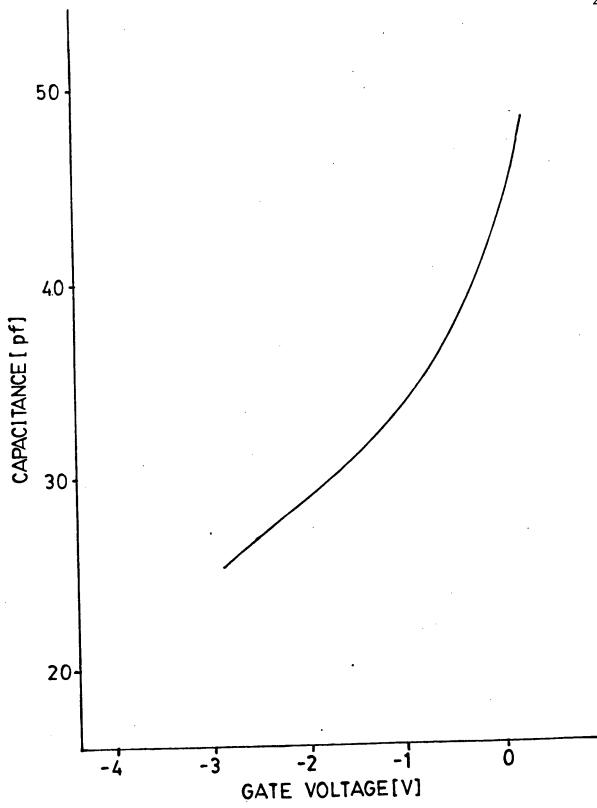

| 4.5  | C-V plot for sample 123-S131(R1-C5)                                                       | 28   |

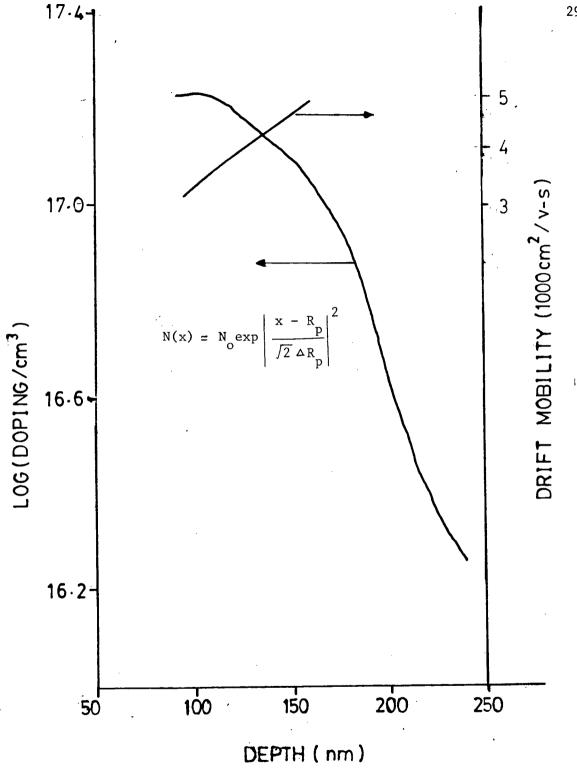

| 4.6  | Carrier density and drift mobility profile forsample 123-S131(R1-C5)                      | 29   |

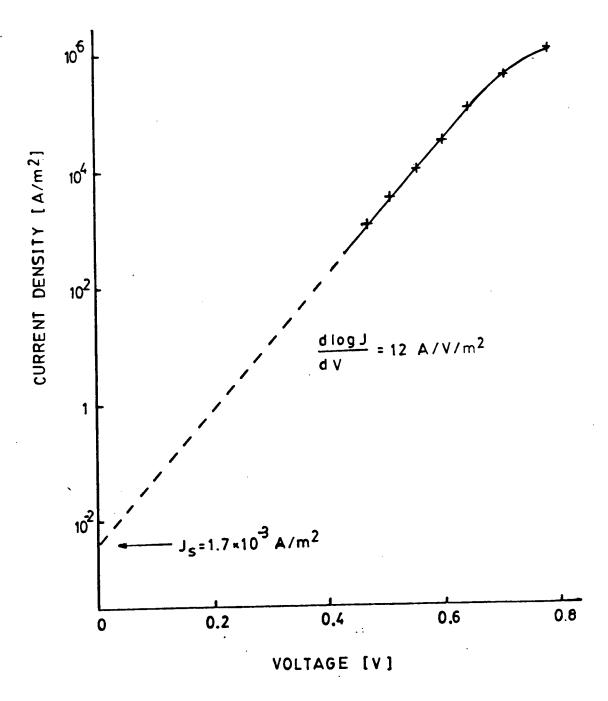

| 4.7  | Schottky diode current-voltage plot forsample 123-S131(R1-C5)                             | 32   |

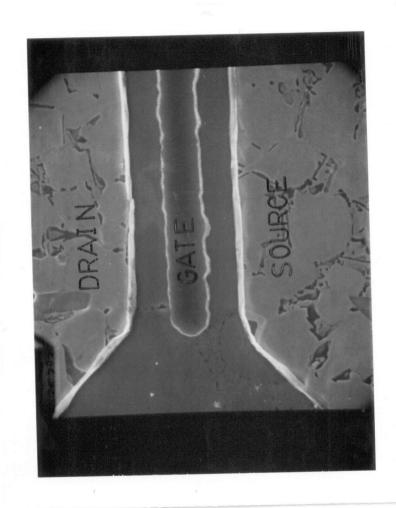

| 4.8  | SEM photograph (2000x mag.) for 3 µm MESFETsample 123-S131(R2-C5)                         | 34   |

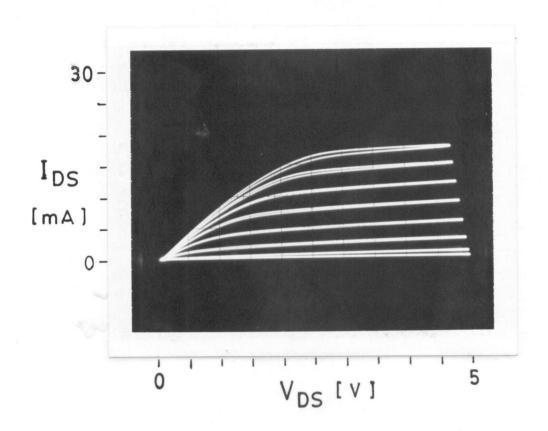

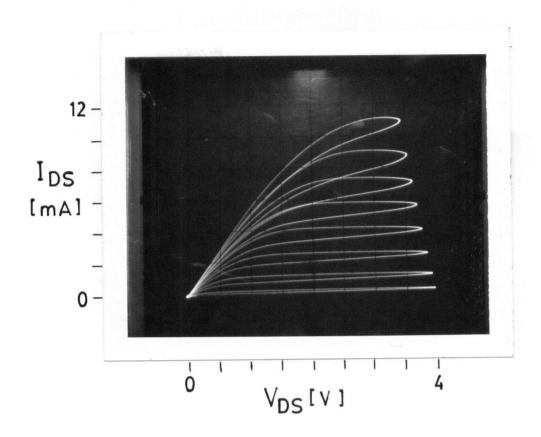

| 4.9  | $I_{\rm DS}\mbox{-V}_{\rm DS}$ characteristics for 3 $\mu m$ MESFETsample 123-S131(R1-C5) | 37   |

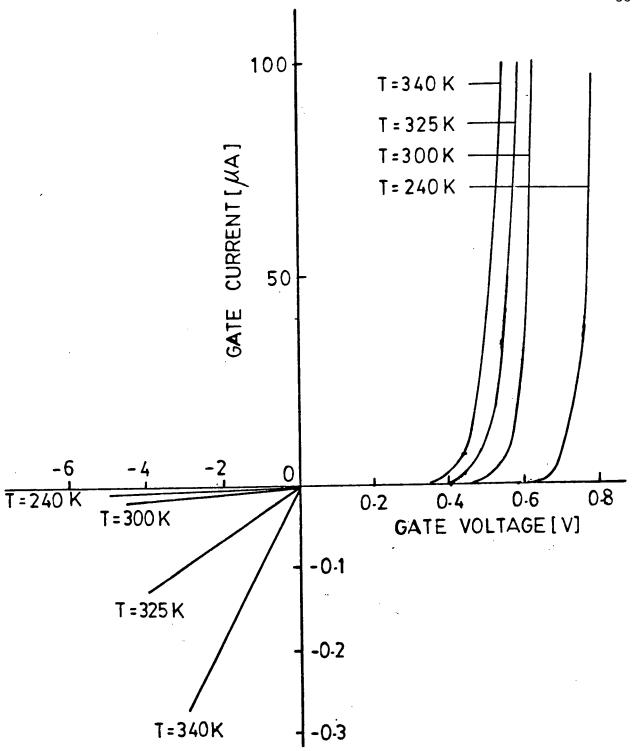

| 4.10 | $I_{GS}\mbox{-}V_{GS}$ characteristics for 3 $\mu m$ MESFETsample 123-S131(R1-C5)         | 38   |

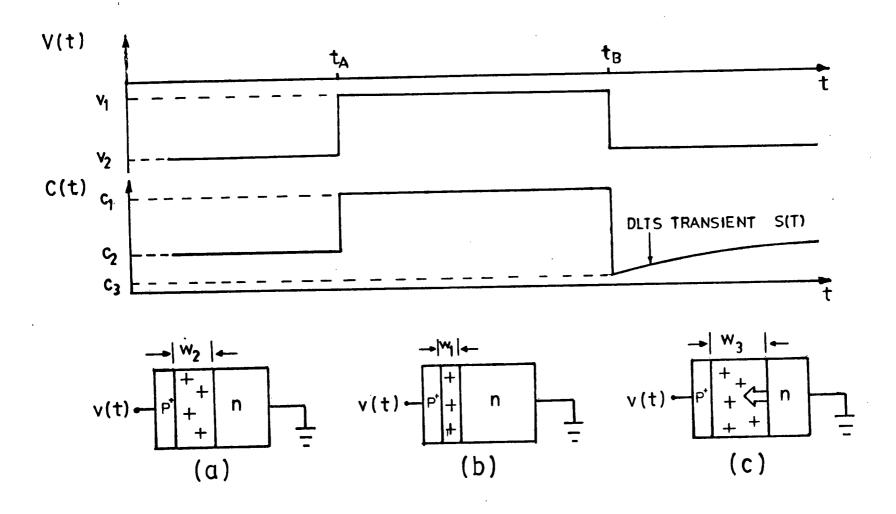

| 5.1  | Basic principle of DLTS transient generation                                              | 42   |

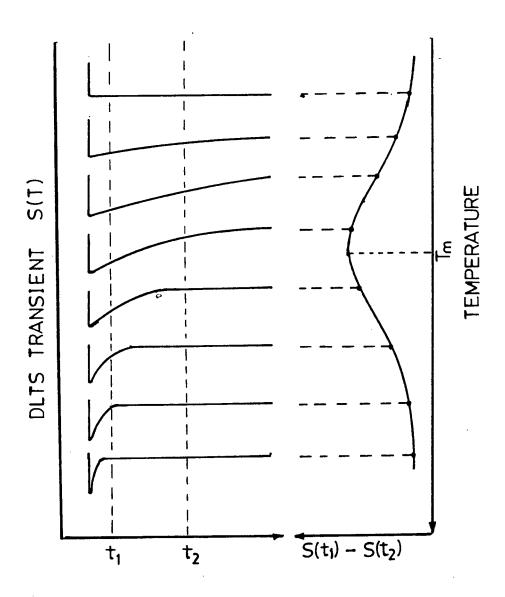

| 5.2  | Basic principle of dual channel boxcar sampling of  DLTS transient                        | 43   |

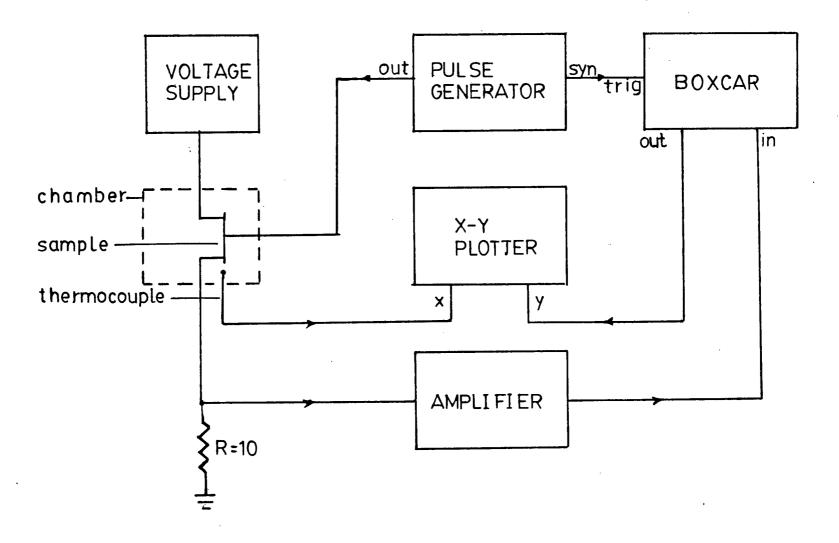

| 5.3  | Block diagram of channel conductance DLTS arrangement                                     | 46   |

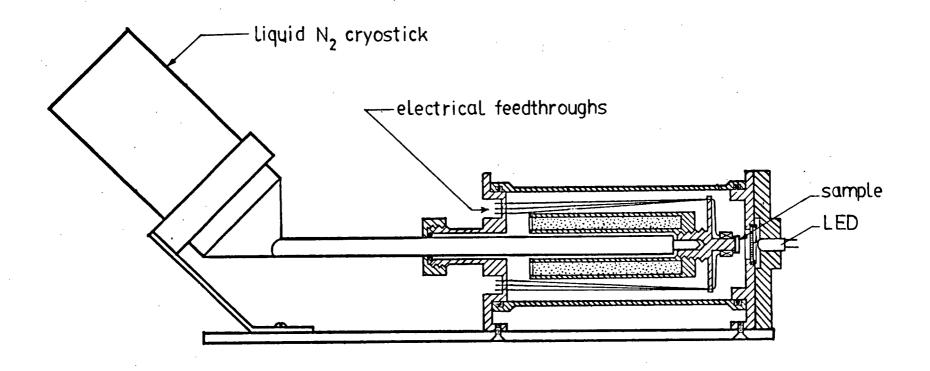

| 5.4  | Sample holder used for DLTS measurements                                                  | 47   |

|      |                                                                                                                                                                               | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

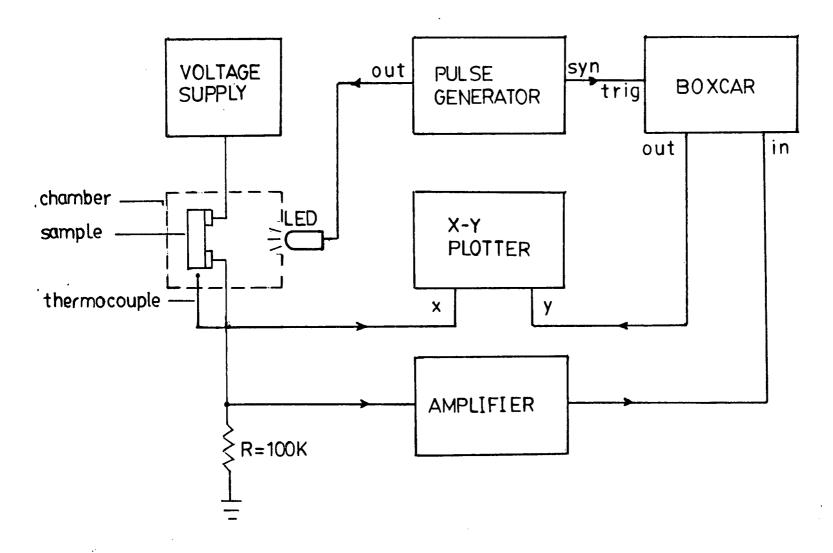

| 5.5  | Block diagram of photocurrent DLTS arrangement                                                                                                                                | 52   |

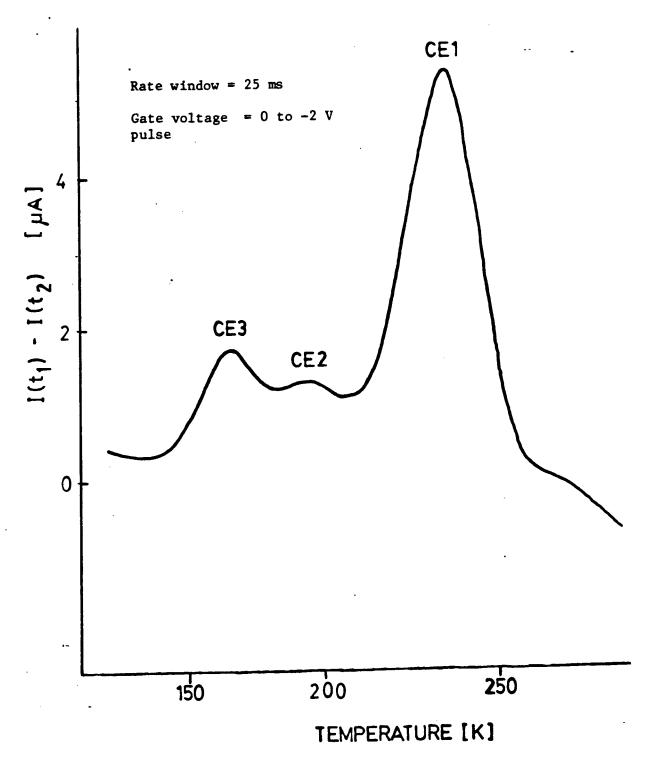

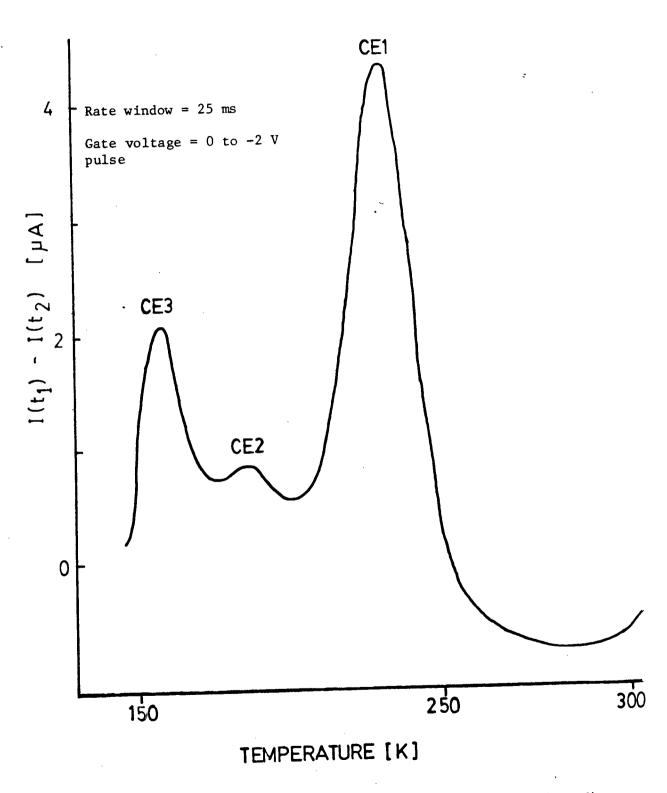

| 5.6  | A CDLTS spectrum for 3 µm MESFET sample 123-S131(R1-C5)                                                                                                                       | 55   |

| 5.7  | A CDLTS spectrum for 3 µm MESFET sample 43-S10(R2-C6)                                                                                                                         | 56   |

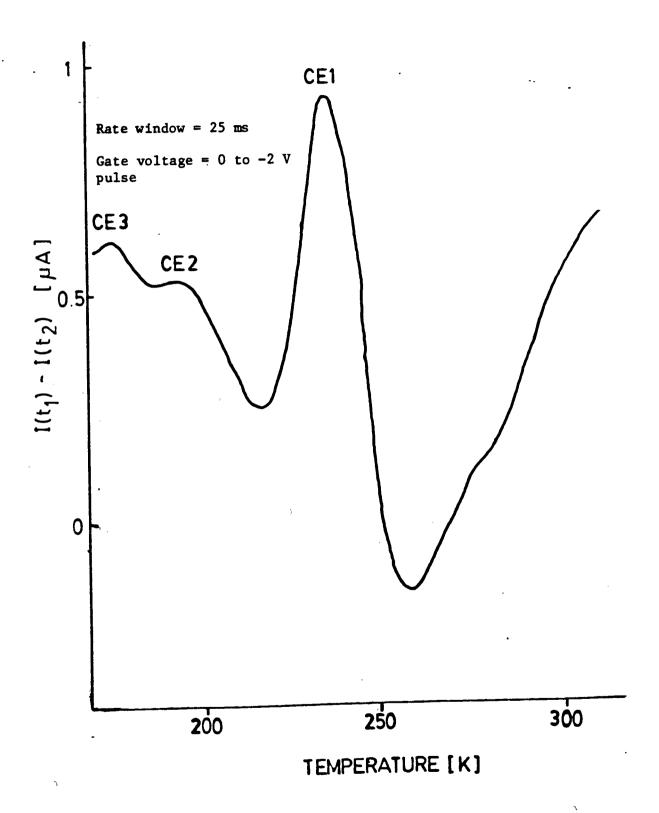

| 5.8  | A CDLTS spectrum for 3 µm MESFET sample 51-T132(R1-C3)                                                                                                                        | 57   |

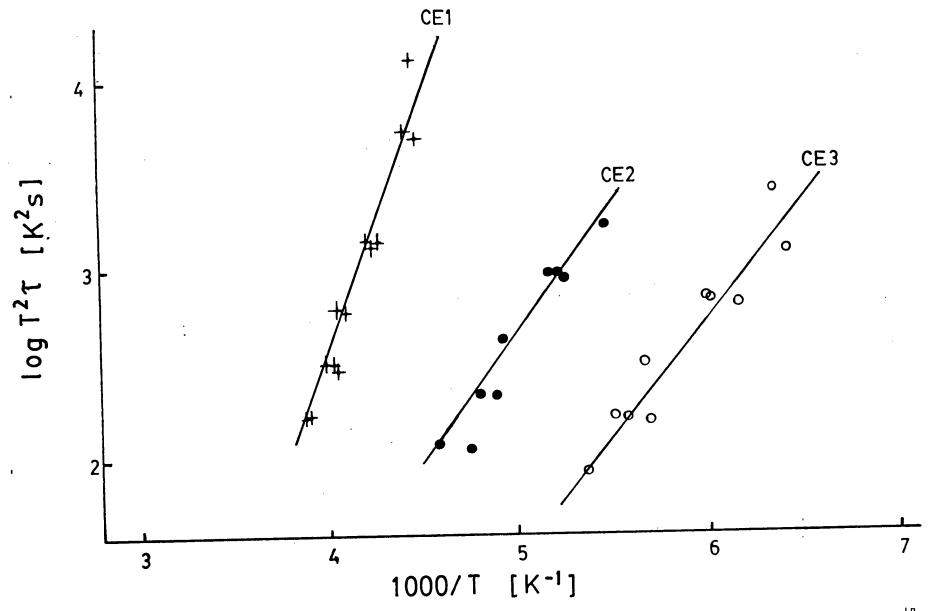

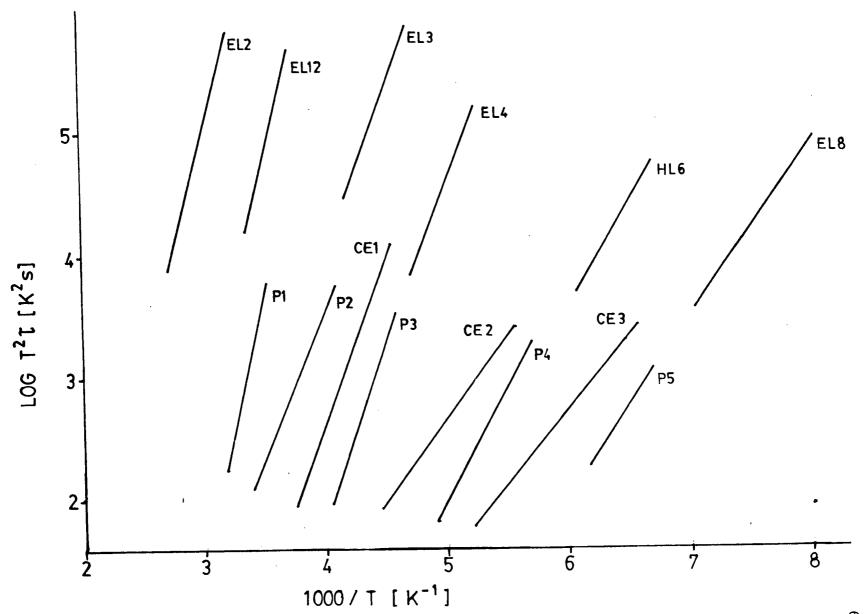

| 5.9  | Activation energy plot for traps detected by CDLTS                                                                                                                            | 58   |

| 5.10 | I-V characteristics for 3 μm MESFET sample 51-T132(R1-C3)                                                                                                                     | 59   |

| 5.11 | A PDLTS spectrum for sample 63-T42(A)                                                                                                                                         | 61   |

| 5.12 | A PDLTS spectrum for sample 82-S14(A)                                                                                                                                         | 62   |

| 5.13 | Activation energy plot for traps detected by PDLTS                                                                                                                            | 63   |

| 5.14 | Comparison of trap signatures                                                                                                                                                 | 65   |

| 6.1  | Ionization of traps in the depletion region due to the sweep of gate voltage with a sawtooth waveform                                                                         | 67   |

| 6.2  | The difference ( $\Delta L$ ) between the normalized depletion width when V <sub>G</sub> changes from zero to -1/2 V <sub>m</sub> as a function of normalized sweep frequency | 72   |

| 6.3  | Experimental arrangement for hysteresis measurements                                                                                                                          | 74   |

| 6.4  | I-V characteristics for MESFET 45-S93 (R4-C3)                                                                                                                                 | 76   |

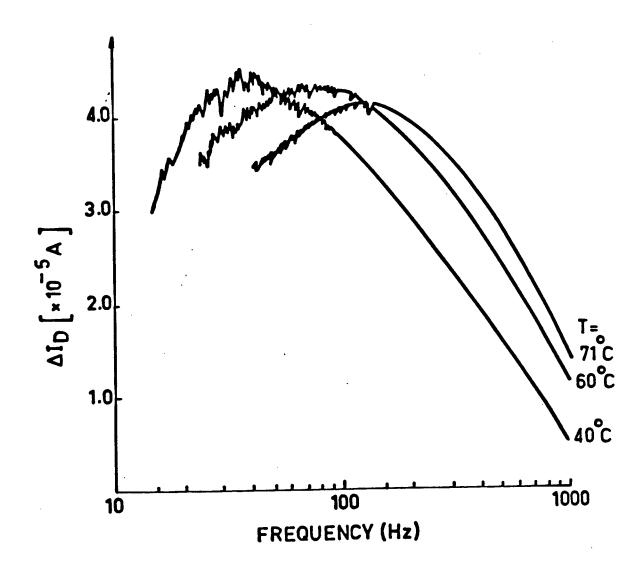

| 6.5  | Hysteresis spectra for MESFET 45-S93(R4-C3)                                                                                                                                   | 77   |

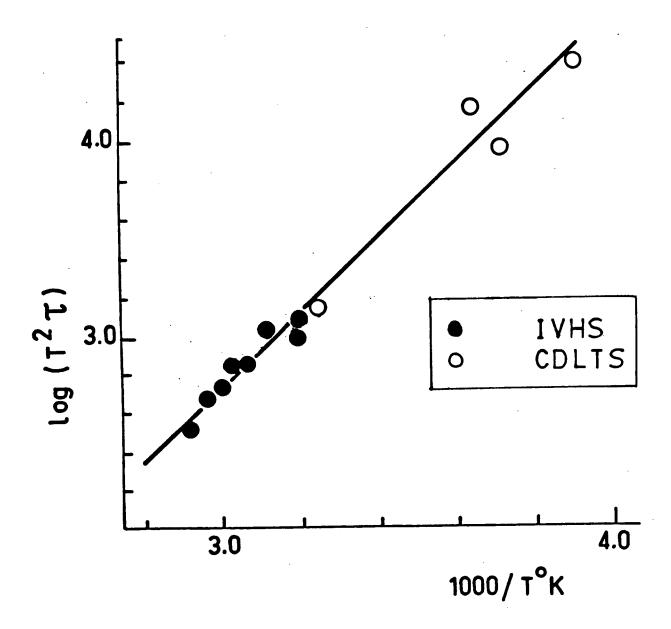

| 6.6  | Activation energy plot for MESFET 45-S93(R4-C3) as obtained by hysteresis and CDLTS measurements                                                                              | 78   |

### **ACKNOWLEDGEMENTS**

I would like to thank my supervisor, Dr. L. Young, for his guidance and encouragement during the course of my work.

I am grateful to Mr. Ji Lijiu and Dr. W. Lau for their numerous help-ful discussions and for their work on the hysteresis technique.

Dr. N. Tarr, now at Carleton University, Ottawa, is thanked for his work on device fabrication and the DLTS system and Mr. D Hutcheon for preparing the test device array masks.

The assistance of Messrs. D. Madge and R. North of Optotek Limited,

Ottawa in implanting the wafers is appreciated as is Mr. G. Needham of

Cominco Limited, Trail, B.C., who supplied the GaAs wafers.

Several others have aided this work and are acknowledged. These individuals include Drs. D. Smith, and R. Koyama, Mr. M. Major,

Messrs. F. Berry, A. Leugner, F. Kschischang, W. Tang, and F. Wan.

I also thank Gail Schmidt for typing the manuscript and I am indebted to W. Tang for his assistance in preparing the figures.

$\label{thm:columbia} \begin{tabular}{ll} Financial support was provided by the British Columbia Science Council and by NSERC. \end{tabular}$

### 1. INTRODUCTION

Gallium arsenide metal semiconductor field effect transistors (GaAs MESFET's) have shown considerable potential for use in high speed digital and monolithic microwave integrated circuits (IC's). For example, 8-12 GHz three and four stage amplifiers have been integrated (Wisseman et al., 1983) and large scale (> 10<sup>3</sup> gates) digital circuits realized (Eden, 1981), but before such IC's can become commercially viable and others of greater complexity developed, improved substrate growth and device fabrication techniques are required. One GaAs MESFET process technology (others are dicussed in Chapter 2) that appears very promising involves the use of multiple selective ion implantation directly into undoped semi-insulating GaAs substrates grown by the Liquid Encapsulated Czochralski (LEC) method.

The objectives of this thesis were to develop at the University of British Columbia a GaAs MESFET technology based on direct ion implantation and in conjunction with Cominco Limited, Trail, B.C. (a supplier of undoped LEC substrates) to develop methods to assess their GaAs for suitability in device fabrication. A test device array consisting of structures for process, material, and device characterization was designed. Undoped LEC substrates were obtained from Cominco and used to fabricate the array by a direct ion implantation process. Measurements were then performed on the array elements to assess the fabrications.

To further assist in material and process development three techniques for characterizing deep levels in GaAs were investigated as deep levels play an important role in substrate compensation (Appendix A) and can also cause

deep level transient spectroscopy for characterizing deep levels in implanted material, photocurrent deep level transient spectroscopy for characterizing deep levels in semi-insulating material and a novel technique for characterizing deep levels which cause the commonly observed effect of hysteresis (looping) in GaAs MESFET I-V characteristics.

Chapter 2 gives a brief overview of GaAs MESFET technology. Chapter 3 describes the test device array and the direct implantation process used in its fabrication while Chapter 4 describes the measurements performed to assess the fabrications. Chapter 5 describes the operation of and measurements performed with the DLTS systems and Chapter 6 the operation of and measurements performed with the hysteresis analysis system. Chapter 7 gives the summary and conclusions of this thesis.

#### 2. OVERVIEW OF GaAs MESFET TECHNOLOGY

# 2.1 Introduction

Integrated circuits capable of operating at speeds in excess of 1 GHz are needed in microwave communication systems, high speed computers, optical fibre systems, and high speed test equipment. It is becoming increasingly difficult to extract more speed from Si devices and it is doubtful whether Si IC's can satisfy these needs. GaAs IC's have a two to six times potential speed advantage over Si IC's due in part to GaAs's higher electron mobility. Furthermore, since GaAs substrates may be grown in a semi-insulating state with resistivity near  $10^8~\Omega cm$  (compared with a theoretical  $10^5~\Omega cm$  for Si) and the GaAs retains its high resistivity after device processing, GaAs IC's can have low inter-device parasitic capacitances and simple inter-device isolation structure.

# 2.2 Device Considerations

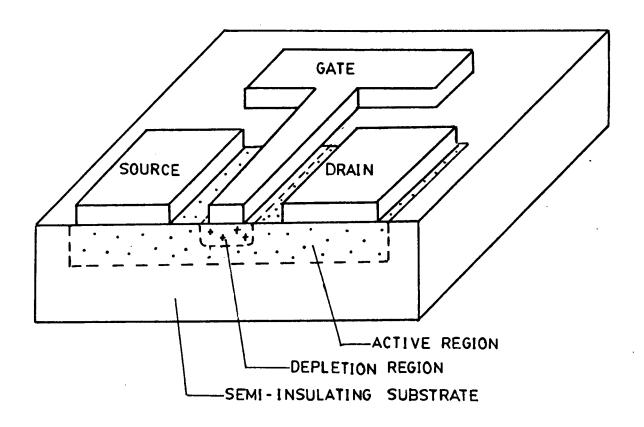

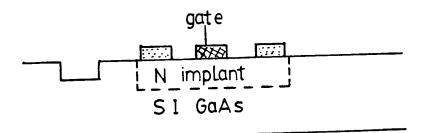

GaAs MESFET's were proposed by Mead (1966) and first realized by Hooper and Lehrer (1967). They are the most widely used transistor in GaAs IC's. (Other choices include junction field effect transistors (JFET's) and metal insulator field effect transistors (MISFET's)). The basic structure of a GaAs MESFET consists of an n-type channel on a semi-insulating GaAs substrate, source and drain ohmic contacts and a metal gate contact which forms a Schottky junction with the channel (Fig. 2.1). The gate to source voltage governs the depth of the gate depletion region and hence the conductance of the channel. As the gate voltage is decreased, the depletion

Fig. 2.1 GaAs MESFET

region expands and the channel conductance is reduced until eventually the channel becomes pinched-off. The maximum voltage on the gate (with respect to the source) required to cause pinch-off is called the threshold voltage  $\mathbf{V}_{\mathbf{T}}$  and is negative for a depletion (normally on) MESFET and positive for an enhancement (normally off) MESFET.

The first GaAs MESFET IC was reported by Van Tuyl and Liechti (1974). The circuit was a NAND/NOR logic gate and it operated three times faster than the fastest Si logic gate (at that time) thus demonstrating the high speed potential of GaAs IC's.

The structure and operation of a GaAs JFET is similar to that of the MESFET except that in a JFET a ptn junction gate is used. MESFET's have been preferred over JFET's because JFET's have a larger gate sheet resistance and are more difficult to fabricate. Since the first GaAs JFET IC was reported by Notthoff and Zuleeg (1975), only relatively coarse gate length JFET IC's have been reported (i.e. 1.3 um by Kato et al., 1981) while 0.5 um gate length MESFET IC's have been fabricated (Barna and Liechti, 1979, Yamasaki et al., 1982). JFET's have a higher gate to channel built-in voltage than MESFET's (typically 1.4 V for JFET's to 0.8 V for MESFET's) and so (Lehovec and Zuleeg, 1980) can accommodate a larger forward bias and thus in digital circuits permit a larger logic voltage swing and noise margin, but again as pointed out by Lehovec and Zuleeg (1980) this advantage of JFET's over MESFET's will disappear if power supply levels in digital circuits are below 0.7 V as will be required for ultra-large scale (>105 gates) circuits. GaAs MISFET's have an insulating film between the gate and channel. The insulator must give good isolation, low surface state density, and long term device

stability. Several dielectrics have been tried, as reviewed by Boyd (1981), but a satisfactory insulator has not been found.

# 2.3 Substrate Considerations

Semi-insulating GaAs substrates have been grown by the horizontal Bridgman technique since the early 1960's. GaAs is synthesized in a quartz boat with elemental Ga and As vapour inside a furnace. The GaAs melt is then cooled by slowly moving the boat away from the furnace. Prior to cooling Cr is added to the melt. The Cr introduces a deep level in GaAs which compensates the shallow impurities found to contaminate the melt (Martin et al., 1980).

In the LEC substrate growth technique a GaAs melt is contained in a quartz or pyrolitic boron nitride (PBN) crucible. The melt is encapsulated with  $B_2 0_3$ . To grow a GaAs ingot a seed is immersed into and then slowly pulled from the melt. The LEC technique was used more than twenty years ago by Metz et al. (1962) but commercial LEC crystal growth equipment has only recently been available (1979).

An attractive feature of the LEC method is that round wafers are produced compared to the D shaped wafers produced by the Bridgman method. A second feature of the LEC method is that semi-insulating wafers may be reproducibly attained without the need for intentional Cr doping as shallow impurities in this material are compensated via an intrinsic deep level formed during crystal growth (Appendix A).

n-epi

////epi-buffer////

SI GaAs

(b)

n-implant \_\_\_\_i/ ////epi-buffer////// SI GaAs (c)

SI GaAs (d)

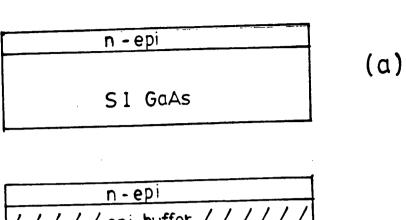

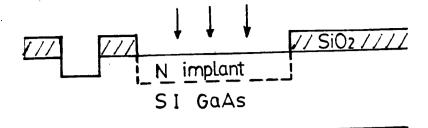

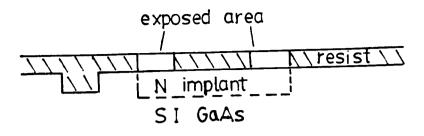

Fig. 2.2 Comparison of active layer formation processes (a) Epitaxial growth (b) Epitaxial growth on buffer layer (c) Implantation into buffer layer (d) Direct ion implantation

# 2.4 Process Considerations

Difficulties encountered with Bridgman substrates (such as the degradation of active layer properties due to Cr impurity diffusion, Udagawa et al., 1980) lead to the development of GaAs MESFET fabrication processes in which high resistivity epitaxial buffer layers are grown on a substrate and active layers formed by a second epitaxial growth (Fig. 2.2b) or by ion implantation into the buffer layer (Fig. 2.2c). With LEC substrates, however, active layer formation by direct ion implantation (Fig. 2.2c) appears possible (Welch et al., 1980).

Attractive features of direct ion implantation include: high throughput (no epitaxial growth required), the fact that selective implantation may be performed (in which only certain parts of a wafer are implanted) alleviating the need for inter-device isolation procedures ("planar" technology), and the fact that multiple and multiple selective implantations may be performed. Recently reported direct implantation processes are summarized in Appendix B.

### 3. THE TEST DEVICE ARRAY

# 3.1 Description

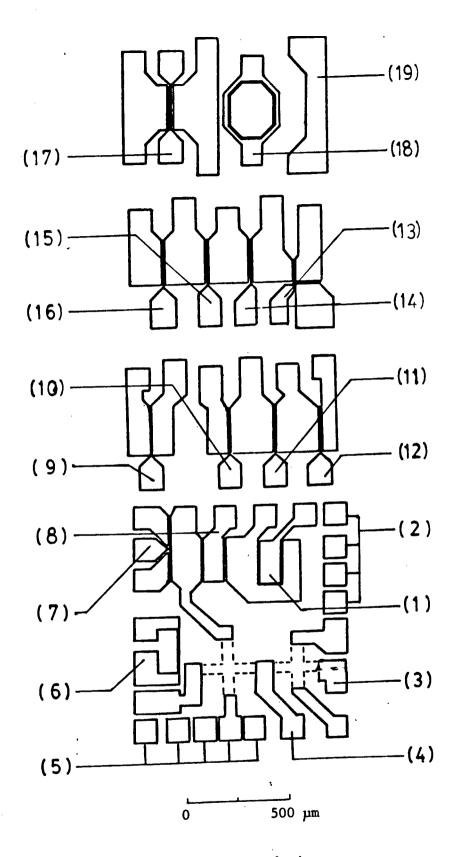

A test device array designed for use in evaluating GaAs integrated circuit processing and material properties is illustrated in Fig. 3.1.

Included in the array, which is partly based on that of Immorlica et al. (1980), are a Schottky diode for carrier density profiling, van der Pauw cross structures for use in Hall effect measurements, (David and Buehler, 1977), a long gate MESFET ("fat FET") for drift mobility profiling, pads for checking substrate isolation and ohmic contact resistance, a structure for measuring gate metal resistance, and a set of narrow gate length MESFET's (1-10 µm) for use in device characterization (Table 3.1).

Table 3.1 - Test Device Array Structures

| STRUCTURE | NAME                          | PURPOSE                                                                               | DESCRIPTION                                                                             |

|-----------|-------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 1         | Schottky diode                | n-implant carrier<br>density profiling                                                | Gate dimension=100x200 μm                                                               |

| 2         | Substrate isola-<br>tion pads | Test of substrate<br>isolation                                                        | (Ohmic) metal pads on SI substrate Pad dimension=100x100 µm Pad separations=40,20,10 µm |

| 3         | van der Pauw<br>cross         | Measurement of Hall<br>mobility and sheet<br>resistance of<br>n-implant               | Length of cross=200 μm<br>Width of cross=40 μm                                          |

| 4         | van der Pauw<br>cross         | Measurement of Hall<br>mobility and sheet<br>resistance of<br>n <sup>+</sup> -implant | Length of cross=250 μm<br>Width of cross=40 μm                                          |

|     | NAME                          | PURPOSE                                          | DESCRIPTION                                                                                |

|-----|-------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------|

| 5   | Ohmic contact<br>pads         | Measurement of ohmic contact resistance          | Ohmic metal pads on implanted layer Pad dimension=100x100 µm Pad separations=40,20,10,5 µm |

| 6   | Gate metal<br>structure       | Measurement of gate<br>metal sheet<br>resistance | Number of squares=50                                                                       |

| 7   | Split gate<br>MESFET          | Device Characteriza-<br>tion                     | - Gate length=4 μm                                                                         |

| , 8 | Fat FET                       | Drift mobility profiling                         | Long gate MESFET<br>Gate dimension=100x200 µm                                              |

| 9   | 1 μm MESFET                   | Device characteriza-<br>tion                     | -Gate width=200 μm                                                                         |

| 10  | 2 μm. "                       |                                                  | " "                                                                                        |

| 11  | 3 µm. "                       |                                                  | " "                                                                                        |

| 12  | 4 բառ "                       |                                                  |                                                                                            |

| 13  | 4 բառ "                       |                                                  | 11 11                                                                                      |

| 14  | 6 µm. "                       |                                                  | " "                                                                                        |

| 15  | 8 դառ "                       | ., .,                                            |                                                                                            |

| 16  | 10 μm. "                      | "                                                | " "                                                                                        |

| 17  | Dual gate MESFET              | "                                                | Gate length=4 µm                                                                           |

| 18  | MIM capacitor                 | Test of dielectric<br>properties                 |                                                                                            |

| 19  | Coarse registra-<br>tion mark | Mask alignment aid                               |                                                                                            |

Six masks were designed for use in fabricating the array via a multiple direct selective ion implantation approach (registration etch mask,

Fig. 3.1 Layout of the test device array

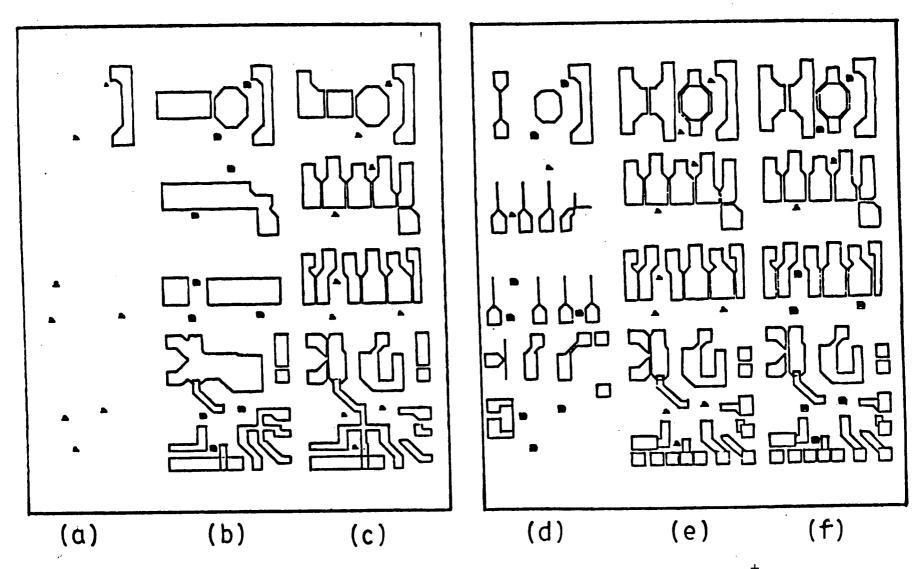

Fig. 3.2 The masks for the test device array (a) Registration marks (b) n-implant (c)  $n^+$ -implant (d) Gate metal (e) Ohmic contacts (f) 2nd layer metal

n-implant mask, n<sup>+</sup>implant mask, ohmic contact metallization mask, gate metallization mask, and second level metallization mask). To prepare the masks, designs were entered into the U.B.C. Computing Centre's Amdahl using a program written by G. Cheng. The files were then downlinked to a PDP8e in the Electrical Engineering Department and a rubylith master cut under control of this program. The rubylith was sent to Precision Photomask, Quebec, for fabrication of the photographic (stepped and repeated) masks. To reduce production costs the required six pattern were grouped into two masks as shown in Fig. 3.2. With this arrangement about 150 replications of the 1.0 x 3.3 mm array can be made on a 50 mm diameter wafer.

# 3.2 Fabrication

## 3.2.1 Substrate Preparation

Semi-insulating GaAs wafers were obtained from Cominco Limited in order to carry out an initial fabrication run of the test device array. The wafers were LEC grown and undoped. The diameter of each wafer was 50 mm, the thickness 0.50 mm, and the crystal orientation (100).

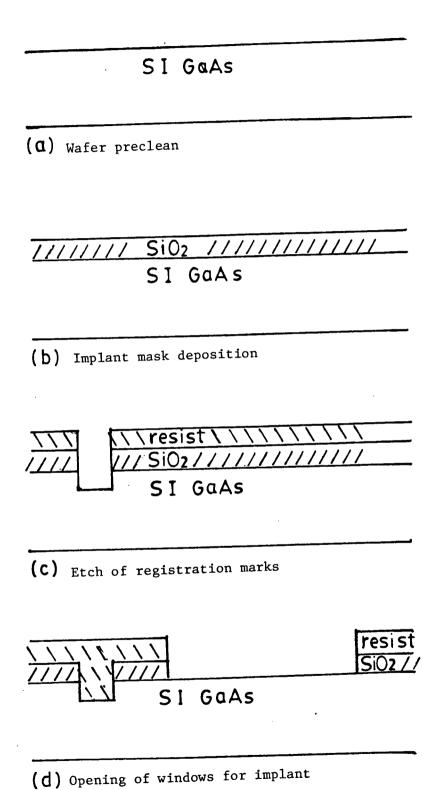

The process used to fabricate the wafers began with the following precleaning procedure (Fig. 3.3a).

- 1. A three part degreasing consisting of a 5 minute trichlorethylene bath, a 5 minute boiling acetone bath, and finally a 5 minute boiling isopropanol bath.

- 2. An etch to remove any work damage introduced during wafer sawing and polishing. The etch consisted of a 3 minute immersion in 4H<sub>2</sub>SO<sub>u</sub>:1H<sub>2</sub>O<sub>2</sub>:1H<sub>2</sub>O followed by a 10 minute DI water rinse.

3. A native oxide etch consisting of a 10 minute immersion in boiling concentrated HCl followed by a 10 minute DI water rinse.

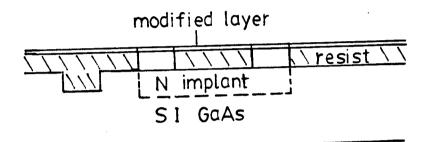

# 3.2.2 Selective Ion Implantation

Following cleaning, an  $\mathrm{Si0}_2$  film of 0.6  $\mu\mathrm{m}$  thickness was deposited on the wafers to serve as a mask in the selective ion implantation process (Fig. 3.3b). A Perkin-Elmer 3140 RF sputtering system was used with an  $\mathrm{Si0}_2$  target. The sputtering gases were Ar, 34 millitorr, and  $\mathrm{O}_2$ , 4 millitorr. ( $\mathrm{O}_2$  helps preserve the stoichiometry of the films). For a forward power of 150 W the deposition rate was found to be about 0.15  $\mu\mathrm{m/hr}$ .

In the next process step, windows were opened in the SiO<sub>2</sub> to permit the etching of registration marks in the substrates (Fig. 3.3c). These marks are necessary in order to locate those regions of the wafer which have been implanted. The following procedure was used:

- 1. A photoresist procedure (using the registration mark mask) consisting of photoresist deposition (Shipley AZ1350J), a 30 minute 70° bake, mask alignment and exposure using a Kasper aligner, photoresist development, a 10 minute DI water rinse, and finally a 60 minute 120°C bake.

- 2. An  ${\rm SiO}_2$  etch consisting of a 5 minute immersion in a buffered oxide etch (NH<sub>L</sub>+HF) and an immersion in acetone to remove the photoresist.

- 3. A substrate etch consisting of a 1 minute immersion in 10% HCl, a 1 minute DI water rinse, a 50 s immersion in 5%  $\rm H_3PO_4$  2.5%  $\rm H_2O_2$  (to remove approximately 0.1  $\mu$ m of the substrate), and a 5 minute DI water rinse.

Next, a second set of windows were opened in the  ${\rm Si0}_2$  to define the regions of the wafers to be implanted (Fig. 3.3d). This was accomplished

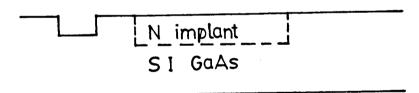

using the photoresist procedure (with the n-implant mask) and the SiO<sub>2</sub> etch procedure described above. <sup>29</sup>Si was implanted at an energy of 100 keV to a dose of  $3x10^{12}$ cm<sup>-2</sup> (Fig. 3.3e). The implantations were done by Optotek Limited, Ottawa, using an Extrion 200 (since facilities were not yet available at U.B.C). To reduce fabrication time and complexity n<sup>+</sup> implantations and second level metallization were not done. (n<sup>+</sup> implantation is used to reduce ohmic contact resistance. Second level metallization is used to achieve low resistance interconnects).

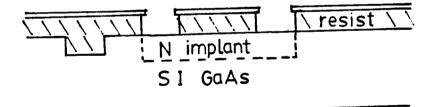

### 3.2.3 Post-Implant Anneal

Following implantation the implant mask was stripped using a 10 minute buffered oxide etch. An SiO<sub>2</sub> layer, 0.17 µm thick, was then deposited (by RF sputtering) to serve as an anneal cap (Fig. 3.3f). Annealing was done in a Mini Brute furnace in the following manner:

- 1. The furnace temperature was set to 850° and gas flow 14 liter/minute  $\rm N_2$  and 1 liter/minute  $\rm H_2$  established.

- 2. The wafers were placed at the front of the furnace for 5 minutes.

- 3. The wafers were placed at center of the furnace for 20 minutes.

- 4. The wafers were placed at the front of the furnace for 5 minutes to complete the anneal.

The encapsulant was then stripped using buffered oxide etch (Fig. 3.3g).

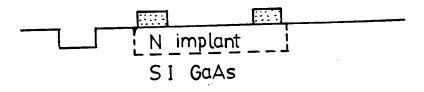

## 3.2.4 Metallization

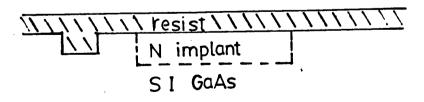

In the next stage, ohmic metallization, the single step liftoff technique of Hatzakis (1980) was used. The following steps were performed:

- 1. Degreasing (as described in Section 3.2.1),

- 2. Photoresist deposition, Shipley AZ1350J, (Fig. 3.3h),

- 3. A prebaking at 70°C for 30 minutes,

- 4. Ohmic contact mask alignment and exposure (Fig. 3.3i),

- 5. A soaking in 26.0°C chlorobenzene for 2 minutes followed by photoresist development. (The chlorobenzene increases the strength of the top layer (Fig. 3.3j) to the developer so that an undercut edge profile (Fig. 3.3k) results upon photoresist development.)

- 6. Thermal evaporation of AuGe (88% Au, 12% Ge) to thickness of 300 nm using VEECO VE400 (Fig. 3.31).

- Removal of unnecessary metal by immersion in acetone, liftoff, (Fig. 3.3m).

The ohmic contacts were then alloyed for 1 minute in a Mini Brute furnace preheated to  $450^{\circ}$ C (to create an n<sup>+</sup> region beneath the contacts).

In the final process step, gate metallization, the liftoff procedure was used with the gate metal mask. In this process Al was deposted to 0.5  $\mu$ m thickness by thermal evaporation using a VEECO VE400 (Fig. 3.3n).

Fig. 3.3 Fabrication sequence for the test device array

(e) Implantation

(f) Encapsulation and annealing

(g) Wafer clean

(h) Photoresist deposition

Fig. 3.3 cont'd.

(i) Photoresist exposure

(i) Chlorobenzene soak

(k) Photoresist development

( ) Source-drain metallization

Fig. 3.3 cont'd.

(m) Removal of photoresist

(n) Gate metallization

Fig. 3.3 cont'd.

### 4. MEASUREMENTS ON THE TEST DEVICE ARRAY

## 4.1 Active Layer Evaluation

To assess the direct implantation and annealing process described in Sections 3.2.2 and 3.2.3 the following properties of the implanted regions were examined: sheet resistance, Hall mobility, activation, carrier density profile, and drift mobility profile.

Sheet resistance, Hall mobility, and activation measurements were made using the van der Pauw cross (structure #3, Fig. 3.1). Samples were placed in a magnetic field B (0.2T) directed normal to the cross (Fig. 4.1a). An Alpha Scientific 7500-W magnet and power supply were used. A current I (200  $\mu$ A) was established between opposite terminals of the cross (i.e. between terminals B and D, Fig. 4.1b) using a HP 6186B current source and the Hall voltage  $V_H$  across the other terminals (i.e. between terminals A and C) measured (with a Fluke 8050 voltmeter). Average Hall mobility  $\mu_H$  was then calculated using

$$\mu_{\rm H} \approx \left| \frac{\rm v_{\rm H}}{\rm R_{\rm s}BI} \right|$$

(4.1)

where  $R_{_{\rm S}}$  is the active layer sheet resistance (van der Pauw, 1958). To determine  $R_{_{\rm S}}$  a current I' (0-1 mA) was established across adjacent terminals (A and D) (with no applied magnetic field) and the voltage V' across the other terminals (B and C) measured.  $R_{_{\rm S}}$  was then calculated using (van der Pauw, 1958)

Fig. 4.1 Experimental arrangement used for van der Pauw measurements (a) Apparatus (b) van der Pauw cross

$$R_{s} \simeq \left| \frac{\pi}{\ln 2} \frac{V'}{I'} \right| . \tag{4.2}$$

Activation, n, was estimated using

$$\eta = \frac{\text{measured sheet}}{\text{implanted dose}} = \frac{1}{Dq \, \mu_H R_c} \tag{4.3}$$

where q is the elementary charge and D the implanted dose.

Carrier density profiles were determined by the capacitance-voltage technique in which the capacitance of a Schottky diode (structure #1, Fig. 3.1) was measured as a function of reverse bias, V, and the profile, N(x), then given by (e.g. Sze, 1981)

$$N(x) = \frac{2}{a s^{A/2}} \left[ \frac{d(1/C^2)}{dV} \right]^{-1}$$

(4.4)

where  $\varepsilon$  is the permittivity of GaAs (~1.16 x 10<sup>-10</sup> F/m), A the diode area and x the depth below the surface (x =  $\varepsilon$ A/C). C which was measured with a 1 MHz capacitance meter (Boonton 71A) was recorded under PDP8e computer control using the system of Boyd (1980) and program MESCV written by Ji Lijiu. The arrangement used to perform the profilings is shown in Fig. 4.2.

Drift mobility profiles were measured with the fat FET's (structure #8, Fig. 3.1) using the method of Pucel and Krumm (1976). A fat FET was biased in its linear region ( $V_{DS} = 50$  mV) and the modulation  $i_d$  in its drain current resulting from the application of a small-signal gate-source voltage

Fig. 4.2 Experimental arrangement used for C-V measurements

$v_{gs}$  (20 mV $_{RMS}$ ) recorded as a function of the DC gate-source bias  $V_{GS}$ . Drift mobilities  $\mu_n(x)$  were then calculated using

$$\mu_{\rm n}(x) = \frac{L^2 i_{\rm d}}{CV_{\rm DS} v_{\rm gs}}$$

(4.5)

where L is the gate length and C the gate capacitance (determined by C-V measurements).  $v_{gs}$  was derived from a sine wave generator (IEC F63) while a lock-in amplifier (PAR 5204) was used to provide an output proportional to  $i_d/v_{gs}$ . The apparatus used to implement the profilings is shown in Fig. 4.3.

Sheet resistance values are tabulated in Fig. 4.4. A typical C-V plot is shown in Fig. 4.5 and carrier density and drift mobility profile in Fig. 4.6. Table 4.1 summarizes the active layer parameters. From the results the following comments can be made:

- 1. Drift mobility is seen to increase towards the substrate. This behaviour has been shown by Immorlica et al. (1981) to correlate with good RF performance in their ion implanted GaAs power MESFET's while devices which displayed a decreasing drift mobility profile were found to exhibit slow pulse response of drain current to applied gate voltage and premature saturation of output power.

- 2. Liu et al. (1980) have calculated the theoretical implant range  $R_p$  and straggle  $\Delta R_p$  for 100 KeV Si implantation into GaAs to be 86 nm and 38 nm respectively, so that it appears that broadening has occurred during annealing.

Fig. 4.3 Experimental arrangement used for drift mobility profiling

Fig. 4.4 Active layer sheet resistance values for wafer sections fabricated (in  $k \mathbb{A}/\square$ , > =R >10  $k \mathbb{A}/\square$ ) (a) Wafer 94-S13 (b) Wafer 43-S10 (c) Wafer 123-S131<sup>S</sup> (d) Wafer 51-T132

Fig. 4.5 C-V plot for sample 123-S131 (R1-C5)

Fig. 4.6 Carrier density and drift mobility profile for sample 123-S131 (R1-C5)

| Table | 4.1 | - | Active | Layer | Properties |

|-------|-----|---|--------|-------|------------|

|-------|-----|---|--------|-------|------------|

| Sample                                               |                     | 43-S10<br>(R2-C6)          | 123-S131<br>(R1-C5)        | 51-T132<br>(R1-C3)         |

|------------------------------------------------------|---------------------|----------------------------|----------------------------|----------------------------|

| Sheet Resistance, R <sub>s</sub><br>Hall Mobility, դ | [kΩ/□]<br>[cm²/Vs]  | 1.3<br>3.3x10 <sup>3</sup> | 1.3<br>3.3x10 <sup>3</sup> | 0.8<br>3.6x10 <sup>3</sup> |

| Percent Activation, η                                | [%]                 | 49                         | 50                         | 74                         |

| Peak Doping, No                                      | [cm <sup>-3</sup> ] | 1.5x10 <sup>17</sup>       | 1.6x10 <sup>17</sup>       | 1.9x10 <sup>17</sup>       |

| Implant Range, R                                     | [nm]                | 102                        | 100                        | 107                        |

| Implant Staggle, ΔR p                                | [nm]                | 69                         | 54                         | 69                         |

- 3. Activations obtained can be compared to those of Immorlica et al. (1980) for  $3 \times 10^{12} \text{cm}^{-2}$  Si implants who report  $\eta$ 's from 67-74%.

- 4. The average  $R_s$  for wafer 51-T132 is lower than of wafers 43-S10 and 123-S131. (The first number in the wafer designation specifies the ingot from which the wafer was cut while the second number specifies the wafer position with respect to either the seed S or tail T of the ingot). This result may reflect the fact that ingot 51 was found by Cominco to be thermally unstable showing a resistivity drop from  $1.8 \times 10^8 \ \Omega cm$  to  $1.1 \times 10^4 \ \Omega cm$  following a 30 minute  $850^{\circ} C$  anneal.

# 4.2 Gate Metallization Evaluation

To assess the gate metallization process described in Section 3.2.4 the following properties were examinated: current-voltage characteristics, barrier height, ideality factor, (gate metal) sheet resistance, lithographic definition.

Schottky diode current-voltage characteristics were measured on a Tektronix 577 curve tracer. Barrier heights  $\phi_B$  and ideality factors n were then derived from the forward characteristics since for V>3kT/q Schottky diode current density J is approximated by:

$$J = A*T^{2}exp\left(\frac{-q \phi_{B}}{kT}\right) exp\left(\frac{qV}{nkT}\right)$$

(4.6)

where A\* is an effective Richardson constant (A\*=8.7  $Acm^{-2}K^{-2}$  for n type GaAs, Crowell et al., 1965) T the diode temperature, and k Boltzmann's constant so that

$$\phi_{\rm B} = \frac{2.30 \text{ kT}}{\rm q} \log \frac{\rm A*T^2}{\rm J_s} \tag{4.7}$$

and

$$n = \frac{q}{2.30 \text{ kT}} \cdot \frac{dV}{d(\log J)}$$

(4.8)

where  $J_s$  is an extrapolated current density at zero bias (Fig. 4.7). Gate

Fig. 4.7 Schottky diode current-voltage plot for sample 123-S131 (R1-C5).

metal sheet resistances  $R_{SG}$  were estimated by measuring the resistance between the terminals of the gate metal structure (structure #6, Fig. 3.1) (by a current voltage technique). Photolithographic definition of the gate metallization was checked using a scanning electron microscope (SEM).

Table 4.2 lists values of barrier height, ideality factor and sheet resistance. An SEM photograph of a 3 µm MESFET (structure #11, Fig. 3.1) is shown in Fig. 4.9. The following comments can be made:

- 1. The high ideality factors obtained may be a result of improper cleaning prior to metallization as Miers (1982) has found that ideality factors varied from 1.08 to 1.33 depending on surface treatment.

- 2. Barrier heights obtained are consistent with the commonly accepted values for metals on n-type GaAs (see, for example, Sze, 1981).

- 3. The gate length of the 3  $\mu m$  MESFET is close to 4  $\mu m$  and the gate definition is poor indicating the need for an improved mask alignment technique.

Table 4.2 - Metallization Properties

| Sample                                                                             |          | 43-S10<br>(R2-C6) | 123-S131<br>(R1-C5) | 51-T132<br>(R1-C3) |

|------------------------------------------------------------------------------------|----------|-------------------|---------------------|--------------------|

| Schottky Barrier Height, $\phi_{	extbf{B}}$<br>Schottky Barrier Ideality Factor, r | [eV]     | 0.74<br>1.3       | 0.73<br>1.4         | 0.73<br>1.3        |

| Gate Metal Sheet Resistance, R <sub>SG</sub>                                       | [ 0/ 🗆 ] | 0.2               | 0.2                 | 0.2                |

| Ohmic Contact Resistance, R                                                        | [m (2]   | 0.27              | 0.32                | 0.22               |

10 µm

Fig. 4.8 SEM photograph (2000X mag.) for  $3\mu m$  MESFET sample 123-S131 (R2-C5)

## 4.3 Ohmic Contact Metallization Evaluation

To assess the ohmic contact metallization process described in Section 3.2.4 measurements were made of specific ohmic contact resistance by the method of Berger (1972). The resistance  $r_{ij}$  between adjacent ohmic contact pads i and j (structure #5, Fig. 3.1) was measured and  $R_{c}$  (the contact resistance of a pad) determined by a linear regression of

$$r_{ij} = 2R_c + \frac{R_s}{w} \ell_{ij}$$

(4.9)

where  $\ell_{ij}$  is the separation between pads i and j and w is the width of the pads.

Values obtained for specific contact resistance are listed in Table 4.2. Since for microwave FET's specific contact resistances of  $10^{-5} \, \Omega \text{cm}^2$  or less are desirable (Gupta et al. 1983) ohmic contacts of lower resistance are required. Use of the high dose n<sup>+</sup> implant under source and drain regions (i.e. mask C Fig. 3.2) should rectify the situation.

#### 4.4 MESFET Evaluation

To test the operation of the devices produced in the fabrications, characteristics of the narrow gate MESFET's (structure #9-12, 14-16, Fig. 3.1) were checked on a Tektronix 577 curve tracer. From these measurements it was found that operational 2-10  $\mu$ m devices can be produced but that improved photolithographic tools are required to produce the 1  $\mu$ m devices (Table 4.3). (A device was deemed operational if it showed I<sub>DS</sub> saturation

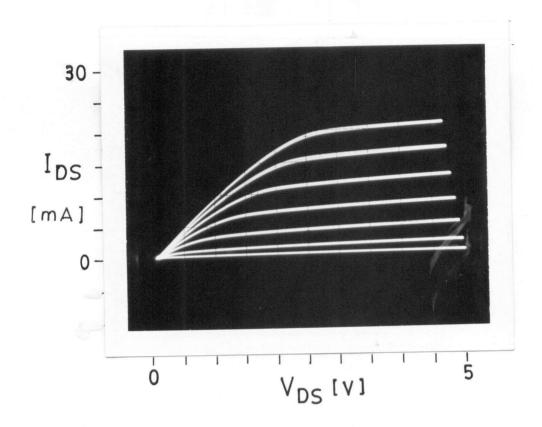

and could be pinched-off to 100  $\mu\!A)$  . Fig. 4.9 shows a typical  $I_{DS}^{}-V_{DS}^{}$  characteristic and Fig. 4.10 a  $I_{GS}^{}-V_{GS}^{}$  characteristic.

Table 4.3 - MESFET Yield

| Wafer      | 94-S13 | 43-S10 | 123-S131 | 51-T132 | Total |

|------------|--------|--------|----------|---------|-------|

| # Devices  | 27     | 26     | 25       | 17      | 95    |

| 10 µm Gate | •70    | •50    | .84      | •88     | .72   |

| 8 " "      | •52    | •38    | .76      | •94     | .62   |

| 6 " "      | .48    | •23    | .80      | .76     | •54   |

| 4 " "      | •59    | •50    | .72      | .71     | .62   |

| 3 " "      | •59    | •46    | .76      | .76     | .63   |

| 2 " "      | •48    | •35    | •64      | .76     | •54   |

| 1 " "      | 0      | 0      | 0        | •12     | •02   |

| TOTAL      | •48    | •35    | •65      | •71     | •53   |

Table 4.4 lists the DC characteristics of various 3 µm MESFET's. The AC behaviour of three of these devices (123-S131 R1-C8, 51-T132 R1-C6, and 43-S10 R2-C5) were checked over the frequency range 2-5 GHz on a HP8409 network analyzer (at Microtel Pacific Research, Burnaby, B.C.) and found to have a cutoff frequency of about 3 GHz. This result is reasonable considering the high ohmic contact resistance and large gate-source separation (~ 4 µm) in the devices. The theoretical cutoff frequency for an intrinsic 3 µm MESFET having no parasitic components is about 10 GHz (Pucel et al., 1975).

Fig. 4.9  $~I_{\rm DS}^{}-V_{\rm DS}^{}$  characteristics for 3  $\mu m$  MESFET sample 123-S131 (R1-C5).  $~V_{\rm GS}^{}$  bias step =-0.5 V

Fig. 4.10  $I_{GS}^{-V}_{GS}$  characteristics for 3  $\mu m$  MESFET sample 123-S131 (R1-C5)

| Sample                                      |       |      |      |      | 123-S131<br>(R1-C8) |      |      |

|---------------------------------------------|-------|------|------|------|---------------------|------|------|

| I <sub>DSAT</sub> @ V <sub>DS</sub> =4V [   | mA]   | 13   | 13   | 16   | 15                  | 19   | 19   |

| V <sub>GS</sub> @ I <sub>DS</sub> =100 μA [ | -v]   | 2.74 | -    | 2.97 | 2.54                | 3.10 | 3.12 |

| V <sub>GS</sub> @ I <sub>DS</sub> =10 μA [  | -v]   | 3.14 | 2.82 | 3.19 | 2.74                | 3.30 | 3.34 |

| V <sub>GS</sub> @ I <sub>DS</sub> =1 μA [   | -v]   | _    | 3.55 | 3.35 | 2.91                | 3.44 | 3.48 |

| G <sub>m</sub> @ V <sub>DS</sub> =4V [      | mA/V] | 5    | 6    | 5    | 6                   | 8    | 8    |

Table 4.4 - Device Parameters of 3 um MESFET's

To check MESFET drain current stability 3  $\mu$ m device 123-S131 (R1-C5) was biased at  $V_{DS}$ =1V and a gate voltage applied of sufficient magnitude ( $V_{GS}$  ~-3V) to reduce  $I_{DS}$  to 100  $\mu$ A.  $I_{DS}$ , following the application of the gate voltage, was then monitored on a chart recorder.  $I_{DS}$  was found to be stable to within ±5% of 100  $\mu$ A over a period of 30 minutes a result that differs from those Itoh and Yanai (1980) and Itoh et al. (1981) who reported drain current drifts of 20-40% (attributed to Cr trapping levels) for MESFET's formed by epitaxy on Bridgman substrates.

#### DEEP LEVEL TRANSIENT SPECTROSCOPY

### 5.1 Basic Principles

Since its introduction by Lang (1974), deep level transient spectroscopy (DLTS) has proven a very useful technique for investigating deep levels in semiconductor devices. It enables a non-destructive evaluation of the energy level  $\mathbf{E}_T$  and electron (hole) capture cross section  $\sigma_n(\sigma_p)$  of the major deep states in a sample. Deep level concentrations may also be determined.

DLTS is based on the modulation and measurement of the depletion region capacitance C(t) of a pn junction or Schottky diode. To analyze, for example, a p<sup>+</sup>n diode for majority carrier traps in the n region, sample temperature T is varied and a voltage V(t) applied (Fig. 5.1). During period  $t_B^-t_A$  traps in the undepleted n region are filled with electrons. When the bias is changed from  $V_1$  to  $V_2$  the depletion region width expands from  $W_1$  to  $W_3$  while the capacitance drops from  $C_1$  to  $C_3$ . Traps at a depth between  $W_3$  and  $W_1$  which were filled are now emptied at a rate dependent on the trap's energy level and electron capture cross section. The release of trapped carriers results in a relaxation of the depletion width from  $W_3$  to the steady state value  $W_2$  and hence a relaxation of the capacitance from  $C_3$  to  $C_2$ .

The transient signal S(t) is processed with a dual channel boxcar averager. The choice of boxcar sampling times  $t_1$  and  $t_2$  fixes the so called rate window RC of the system (Eq. 5.12). When the decay constant  $\tau$  of S(t) is equal to the rate window, the output of the boxcar registers a maximum. As the sample temperature is scanned, a DLTS spectrum of  $S(t_1)-S(t_2)$  versus T is obtained (Fig. 5.2). If more than one type of deep level is present in

Fig. 5.1 Basic principle of DLTS generation (a) Steady state (b) Trap filling (c) Trap emptying

Fig. 5.2 Basic principle of dual channel boxcar sampling of DLTS transient  $\,$

the sample, several peaks will appear in the spectrum. By selecting various rate windows and repeating the temperature scan a family of DLTS spectra are obtained from which trap data may be calculated (as described in Section 5.2).

# 5.2 Channel Conductance DLTS

Channel conductance DLTS (CDLTS) is a useful technique to assess the deep levels in the channel of a MESFET (Alderstein, 1976). A small drain to source voltage ( $V_{DS} \approx 50$  mV) is applied.  $V_{GS}$  is set to zero to allow electron traps in the channel to be filled.  $V_{GS}$  is then stepped to  $V_{G}$  ( $V_{T} < V_{G} < 0$ ). The gate depletion region widens and a transient channel current develops due to the release of electrons from the expanded depletion region.

An expression for the channel conductance transient may be derived for a MESFET of gate length L, gate width Z, and zero gate voltage channel depth a. It is assumed that a uniform active layer shallow donor density  $N_{\rm D}$  exists and that a single electron trap of density  $N_{\rm T}$  is present. Neglecting the resistance of the unmodulated channel regions, the conductance of the MESFET G(t) is

$$G(t) = \frac{Z\sigma[a-X_d(t)]}{L}$$

(5.1)

where  $\sigma$  is the conductivity of the active layer and  $X_d(t)$  is the gate depletion region depth measured from the zero gate bias value. If at time t=0 the gate bias is stepped from 0 to  $V_G$  and the steady state conductance for large

t is  $G_0$  (with a corresponding depletion depth of  $X_{do}$ ), then the conductance difference signal  $\Delta G(t)$  ( $\Delta G(t) = G_0 - G(t)$ ) is

$$\Delta G(t) = \frac{Z \sigma[X_d(t) - X_{do}]}{L} \qquad (5.2)$$

Since  $X_d(t)$  can be assumed to be given by

$$X_{d}(t) = \left\{ \frac{2 \varepsilon V_{G}}{q[N_{D} + N_{T}(1 - \exp(-t/\tau))]} \right\}^{1/2}$$

(5.3)

where  $\tau$  is a time constant, one finds that

$$\frac{X_{d(t)}}{X_{do}} = \left[ \frac{1}{1 - \frac{N_{T}}{N_{D} + N_{T}}} \exp(-t/\tau) \right]^{1/2}$$

(5.4)

Now if  $N_T \le N_D$  Eq. (5.4) becomes

$$\frac{X_{d}(t)}{X_{do}} \approx 1 + \frac{N_{T} \exp(-t/\tau)}{2N_{D}}$$

(5.5)

so Eq. (5.2) can be written as

$$\Delta G(t) = \frac{Z \sigma X_{do}^{N_T}}{2LN_D} \exp(-t/\tau)$$

(5.6)

which is the desired expression for the channel conductance transient.

A block diagram of the CDLTS system of this thesis is shown in Fig. 5.3. The drain voltage to the FET is derived from a regulated power supply while the periodic gate bias is supplied by an IEC F33 pulse generator. A small resistor R (10  $\Omega$ ) converts the channel current into a voltage signal which is subsequently amplified by a PAR 113 amplifier. The output from the amplifier goes to the input of a PAR 162/165 dual channel boxcar arrangement. The boxcar output goes to the Y channel of an HP 7044A X-Y plotter. The X channel of the plotter records the thermocouple voltage of the sample.

The sample is housed in a light tight chamber. The chamber, which was adapted for use from a previous study (Lester, 1982) is illustrated in Fig. 5.4. After the chamber is evacuated to a pressure of less than 10 torr, sample temperature is lowered to 100 K via liquid nitrogen cooling. A power transistor is used to heat the sample. A copper-constantan thermocouple, soldered to the device package, is used to monitor the temperature.

The input signal transient  $V_{i}(t)$  to the boxcar is given by

$$V_{i}(t) = A_{A}RG(t)V_{DS}$$

(5.7)

where  $A_A$  is the amplifier gain and where it is assumed that  $R \leq [G(t)]^{-1}$ . The output of the boxcar  $V_0$  (as a function of temperature T) can then be expressed as

$$V_0(T) = A_R[V_i(t_1) - V_i(t_2)]$$

(5.8)

Fig. 5.3 Block diagram of channel conductance DLTS arrangement

Fig. 5.4 Sample holder used for DLTS measurements

where  $A_B$  is the voltage gain of the boxcar. Then from Eq.'s (5.6) and (5.7) Eq. (5.8) can be rewritten as

$$V_{o}(T) = \frac{A_{A}^{A}B^{RZ oV}DS^{N}T^{X}do}{2LN_{D}} \left[ \exp(-t_{2}/\tau) - \exp(-t_{1}/\tau) \right]$$

(5.9)

The temperature dependence of  $V_0$  in Eq. (5.9) can be derived from the temperature dependence of  $\tau$ . From the principle of detailed balance the time constant (reciprocal emission rate) for an electron trap can be shown to be

$$\tau = (\sigma_n v_n N_c)^{-1} \exp\left[\frac{E_c - E_T}{kT}\right]$$

(5.10)

where  $\sigma_n$  is the capture cross section,  $v_n$  the thermal velocity of electrons,  $E_c$  the conduction band energy, and  $N_c$  the conduction band density of states. A trap level of single degeneracy is assumed. Since  $v_{th}$  and  $N_c$  vary markedly with T, Eq. (5.10) is more appropriately expressed as

$$\tau = (\sigma_n \gamma T^2)^{-1} \exp\left(\frac{E_c - E_T}{kT}\right)$$

(5.11)

where  $\gamma$  is equal to 2.28x10<sup>20</sup>cm<sup>-2</sup>s<sup>-1</sup>K<sup>-2</sup> for electron traps in GaAs and to 1.7x10<sup>21</sup>cm<sup>-2</sup>s<sup>-1</sup>K<sup>-2</sup> for hole traps in GaAs (Martin et al., 1977, Mitonneau et al., 1977).

For a certain value of  $\tau$ , called  $\tau_m$ ,  $V_o$  peaks. By differentiating Eq. (5.9) with respect to  $\tau$  and setting the result equal to zero one finds that

$$\tau_{\rm m} = \frac{t_1 - t_2}{\ln t_1 / t_2} \tag{5.12}$$

which is defined as the rate window RC of the CDLTS scan. Since the temperature  $T_{\rm m}$  corresponding to the peak in  $V_{\rm o}$  is obtained from the DLTS spectrum (Fig. 5.2) and  $t_1$  and  $t_2$  are known, one may write

$$\tau_{\rm m} = (\sigma_{\rm n} \gamma T_{\rm m}^2)^{-1} \exp\left(\frac{E_{\rm c}^{-E} T}{k T_{\rm m}}\right)$$

(5.13)

If a second spectrum is obtained for a different rate window,  $\sigma_n$  and  $E_c^{-E}_T$  are uniquely determined. Usually several scans are made and a plot of  $\log T^2 \tau$  versus 1/T (activation energy plot) made. Trap parameters are then given by

$$E_c - E_T = 2.30 \text{ km}$$

(5.14)

and

$$\sigma_{\rm p} = (\gamma \, 10^{\rm b})^{-1}$$

(5.15)

where m and b are the slope and intercept, respectively, of the best linear fit to the above plot.

The concentration of a trap is derived from the height  $V_{O}(T_{m})$  of the CDLTS peak. From Eq. (5.9)  $N_{T}$  can be calculated as

$$N_{T} = \frac{2LN_{D}V_{O}(T_{m})}{A_{A}A_{B}RZ \sigma V_{DS}X_{dO}} \left[ exp\left(\frac{-t_{2}}{\tau_{m}}\right) - exp\left(\frac{-t_{1}}{\tau_{m}}\right) \right]$$

(5.16)

where  $\tau_m$  is given by (5.12).

If the active region of a MESFET is formed by ion implantation the assumption of a uniformly doped channel region is violated. Nevertheless, Eq.'s (5.14) and (5.15) can still be expected to give a reasonable estimate of  $E_c$ - $E_T$  and  $\sigma_n$  in most cases. Since the conductivity of an implanted channel can be taken to be proportional to an average  $N_D$  it is interesting to note that Eq. (5.16) reveals that  $N_T$  may be calculated simply from a knowledge of  $X_{do}$  (which can be deduced from a capacitance voltage measurement).

#### 5.3 Photocurrent DLTS

Photocurrent DLTS (PDLTS) is a useful technique to assess the deep levels in a semi-insulating sample (Fairman et al., 1979, Hurtes et al., 1978). The device structure that is used in PDLTS consists of two closely spaced ohmic contact pads. A bias V is established between the pads and the sample is illuminated with bandgap light. Electron/hole pairs are generated which populate traps in the sample. If the sample is illuminated for a sufficient length of time the current flow between the pads approaches a steady state value  $i_s$ . If the sample contains a trap of density  $N_T$ , the occupation of the trap  $n_T$  during steady state is given by

$$n_{T_{s}} = N_{T} \left( 1 + \frac{e_{n} + \sigma_{p} v_{p}}{e_{p} + \sigma_{n} v_{n}} \right)^{-1}$$

(5.17)

where  $e_n/e_p$ ,  $\sigma_n/\sigma_p$ ,  $v_n/v_p$ , and n/p are the electron/hole rate constant, capture cross section, thermal velocity and concentration, respectively

(Hurtes et al., 1978).

When the light is removed (at t=0) the current does not immediately fall to  $\mathbf{i}_L$  (the leakage flow) but instead gradually decays to this level due to the slow release of trapped carriers. The decay current  $\mathbf{i}_p(t)$  is given by

$$i_p(t) = C \{e_n n_T(t) + e_p[N_T - n_T(t)]\}$$

(5.18)

where  $n_T$  is the density of occupied traps, C is a constant dependent on contact geometry (Martin and Bois, 1978) and where  $i_L$  has been neglected. If it is assumed that  $i_p(t)$  decays exponentially with time constant  $\tau$  and that  $n_T(0)$  is equal to  $n_T$  Eq. (5.18) becomes

$$i_{p}(t) = Ce_{n}N_{T}\left[\left(1 + \frac{\sigma_{p}v_{p}}{\sigma_{n}v_{n}}\right)^{-1} - \left(1 + \frac{e_{n}}{e_{p}}\right)^{-1}\right] \exp\left(\frac{-t}{\tau}\right).$$

(5.19)

For an electron trap  $\sigma_n >> \sigma_p$  and  $\tau^{-1} = e_n >> e_p$  so that

$$i_{p}(t) = C \tau^{-1} N_{T} \exp\left(\frac{-t}{\tau}\right). \tag{5.20}$$

A block diagram of the photoconductance DLTS (PDLTS) system of this thesis is shown in Fig. 5.5. The system utilizes the same apparatus as the CDLTS arrangement of Fig. 5.3 except that a type ME7021IR light emitting diode (900 nm, 1.0 mW @100 mA) mounted on the sample chamber is used to

Fig. 5.5 Block diagram of photocurrent DLTS arrangement

illuminate the sample through a window (Fig. 5.4). The transient signal input  $V_i(t)$  to the boxcar is

$$V_{i}(t) = A_{A}R i_{p}(t)$$

(5.21)

while the boxcar output  $V_0(T)$  derived from Eq. (5.20) is

$$V_{o}(T) = A_{A}A_{B}RC \tau^{-1}N_{T} \left[ exp\left(\frac{-t_{1}}{\tau}\right) - exp\left(\frac{-t_{2}}{\tau}\right) \right]$$

(5.22)

where  $A_A$ ,  $A_B$  and R are as defined previously. If  $V_O(T)$  is differentiated with respect to  $\tau$  and the result set equal to zero  $\tau_m$  is found to satisfy (Itoh and Yanai, 1981)

$$\left(1 - \frac{\mathsf{t}_1}{\mathsf{\tau}_{\mathsf{m}}}\right) \exp\left(\frac{-\mathsf{t}_1}{\mathsf{\tau}_{\mathsf{m}}}\right) = \left(1 - \frac{\mathsf{t}_2}{\mathsf{\tau}_{\mathsf{m}}}\right) \exp\left(\frac{-\mathsf{t}_2}{\mathsf{\tau}_{\mathsf{m}}}\right). \tag{5.23}$$

Once  $\tau_m$  is calculated,  $\sigma_n$  and  $\text{E}_c\text{--}\text{E}_T$  can be determined from Eq. (5.13) as in CDLTS.

#### 5.4 Measurements

CDLTS measurements were made with the system described in Section 5.2 to obtain information on the deep levels in the channel region of the MESFET's fabricated in Chapter 3. 3 µm MESFET's were examined over the temperature range 100-350 K with rate windows 1-100 ms.

CDLTS spectra for devices 123-S131 (R1-C5), 43-S10 (R2-C6), and 51-T132 (R1-C3) are shown in Fig.'s 5.6-5.8. Three electron traps, labelled CE1, CE2, and CE3 are resolved in each sample. The activation energy plot (or DLTS "signature", Martin et al., 1977) of each trap is shown in Fig. 5.9. Table 5.1 lists data on trap energy, cross section, and concentration calculated via Eq.'s 5.14-16. Trap concentrations in 51-T132 (R1-C3) (especially CE1) are lower than in the other two devices. In addition the I-V characteristics of 51-T132 (R1-C3) show less hysteresis than that of 123-S131 (R1-C5) (or 43-S10 R2-C6) (compare Fig. 4.9 with Fig. 5.10) suggesting that one or more of these traps are responsible for hysteresis.

Table 5.1 - Deep Levels Detected by CDLTS

| Label | Activation Energy [eV] |    | Log (o <sub>n</sub> [cm <sup>2</sup> ]) | τ@ 300 K<br>[μs] | N <sub>T</sub> [10 <sup>16</sup> cm <sup>-3</sup> ] |                     |     |

|-------|------------------------|----|-----------------------------------------|------------------|-----------------------------------------------------|---------------------|-----|

|       | [EV]                   |    |                                         | [ P2 ]           |                                                     | 123-S131<br>(R1-C5) |     |

| CE1   | 0.50 ±0.               | 01 | -12.8                                   | 77               | 2.5                                                 | 2.5                 | 0.5 |

| CE2   | 0.27 ±0.               | 02 | -16.3                                   | 27               | 1.0                                                 | 0.5                 | 0.3 |

| CE3   | 0.20 ±0.               | 01 | <b>-17.</b> 2                           | 13               | 0.5                                                 | 0.4                 | 0.3 |

To investigate semi-insulating properties, substrate samples were prepared so that PDLTS measurements could be made. On each sample AuGe ohmic contact pads were defined. The separation of the pads was 50  $\mu$ m and the width of each pad 250  $\mu$ m.

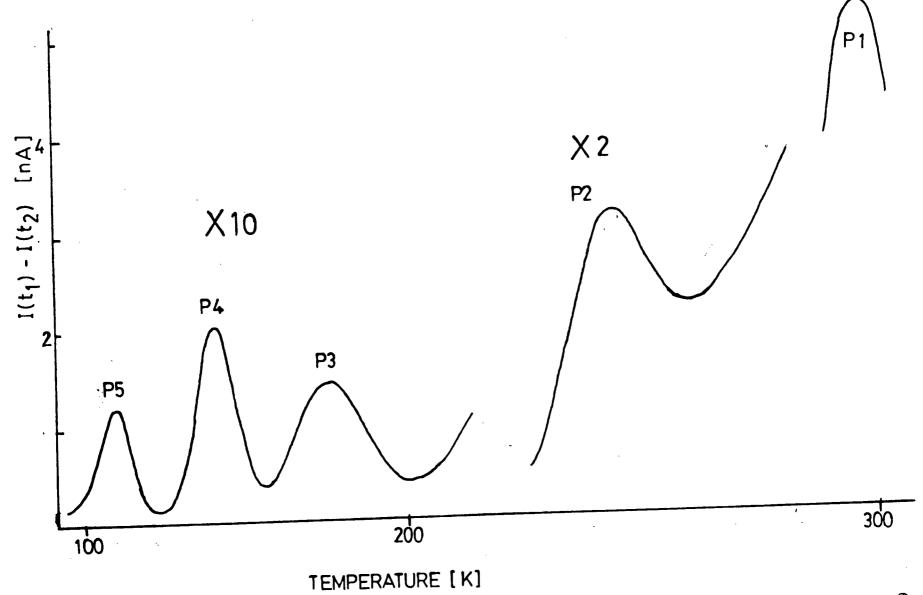

Fig. 5.6 A CDLTS spectrum for 3 µm MESFET sample 123-S131 (R1-C5)

·Fig. 5.7 A CDLTS spectrum for 3  $\mu m$  MESFET sample 43-S10 (R2-C6)

Fig. 5.8 A CDLTS spectrum for 3 µm MESFET sample 51-T132 (R1-C3)

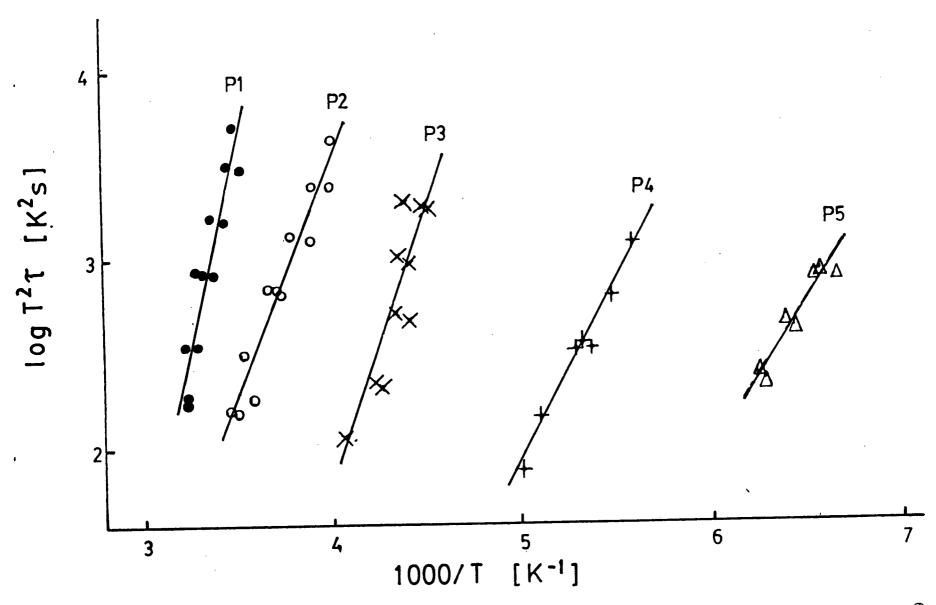

Fig. 5.9 Activation energy plot for traps detected by CDLTS

Fig. 5.10  $\rm I_{DS}^{-V}_{DS}$  characteristics for 3  $\mu m$  MESFET sample 51-T132 (R1-C3).  $\rm V_{GS}$  bias step = -0.5 V

PDLTS measurements were conducted using the system described in Section 5.3. The temperature range investigated was 100-330K. Rate windows were varied from 1 ms to 50 ms. An inter-pad bias of 4V and a light intensity sufficient to give a peak photocurrent of 500 nA (at room temperature) were used.

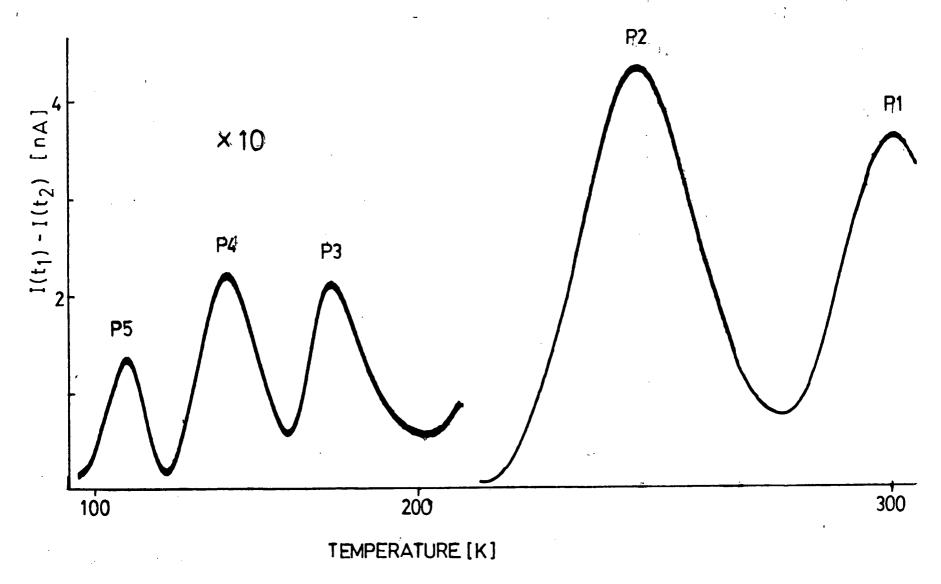

A PDLTS spectrum for sample 63-T42(A) is shown in Fig. 5.11. Five deep levels labelled Pl to P5 are resolved. The PDLTS spectrum for sample 82-S14(A) shown in Fig. 5.12 shows the same five levels but the relative concentration (peak height) of the Pl to P2 level in this sample is apparently higher. Of note is the fact that ingot 82 (like 51) was found by Cominco to be thermally unstable upon 850°C anneal (Table 5.2). Trap signatures are shown in Fig. 5.13 and trap data listed in Table 5.3.

Table 5.2 - Properties of Cominco GaAs

| Wafer Obtained<br>From Cominco | Wafer Assessed<br>By Cominco | Resistivity Before<br>Anneal [Ωcm] | Resistivity After<br>Anneal [Ωcm] |  |

|--------------------------------|------------------------------|------------------------------------|-----------------------------------|--|

| 43-S10                         | 43 <b>–</b> 87               | 9.6 x 10 <sup>7</sup>              | 1.8 - 2.1 x 10 <sup>7</sup>       |  |

| 45 <b>-</b> S93                | 45-S96                       | $3.9 \times 10^7$                  | 1 x 10 <sup>7</sup>               |  |

| 69-T42                         | 63-T27                       | 1.2 x 10 <sup>7</sup>              | 8 - 9 x 10 <sup>6</sup>           |  |

| 94-813                         | 94-S22                       | 2.0 x 10 <sup>5</sup>              | 1.9 x 10 <sup>7</sup>             |  |

| 123-S131                       | 123-S195                     | _                                  | 2.8 x 10 <sup>7</sup>             |  |

| 51-T132                        | 51-T181                      | 1.8 x 10 8                         | 1.1 x 10 <sup>4</sup>             |  |

| 82 <b>-</b> S14                | 82 <b>-</b> S11              | 4.3 x 10 <sup>8</sup>              | $6.1 \times 7.1 \times 10^3$      |  |

|                                |                              |                                    |                                   |  |

Fig. 5.11 A PDLTS spectrum for sample 63-T42(A) (Rate window = 10 ms)

Fig. 5.12 A PDLTS spectrum for sample 82-S14(A) (Rate window = 10 ms)

Fig. 5.13 Activation energy plot for traps detected by PDLTS

| Table 5.3 - Deep Levels Detected By PDI |

|-----------------------------------------|

|-----------------------------------------|

| Label                | Activation Energy<br>[eV]    | τ@ 300 K<br>[s]                                                                     | Log(o <sub>n</sub> [cm <sup>2</sup> ]) | Log(σ <sub>p</sub> [cm <sup>2</sup> ]) |

|----------------------|------------------------------|-------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|

| P1<br>P2<br>P3<br>P4 | 0.87<br>0.50<br>0.59<br>0.38 | $7.5 \times 10^{-3}$ $7.3 \times 10^{-3}$ $6.1 \times 10^{-6}$ $5.3 \times 10^{-6}$ | -8.6<br>-13.8<br>-10.3<br>-12.7        | -9.5<br>-14.6<br>-11.1<br>-13.5        |

| P5                   | 0.32                         | 4.6 x 10 <sup>-9</sup>                                                              | -12.6                                  | -13.5                                  |

PDLTS and CDLTS trap signatures are compared in Fig. 5.14 along with various levels from the review of Martin et al. (1977) and Mitonneau et al. (1977). Possible associations are P1 with EL12, P2 with EL3, P3 with EL4, P4 with HL6 and P5 with EL8. EL2, a very commonly reported trap in bulk GaAs (Appendix A) was not detected in this work. CE1, CE2, and CE3 could not be identified with any of the levels from the reviews (which report on traps detected by DLTS in bulk and/or epitaxial GaAs) or with any of the PDLTS levels suggesting that the CDLTS levels are introduced during the implantation annealing process. (A similar conclusion has been made by Rhee et al., (1982) who detected a 0.52 eV electron trap in Si implanted GaAs not detected in the substrate). The complete list of traps of Martin and Mitonneau is given in Appendix C along with the results of subsequent DLTS studies reviewed by this author.

Fig. 5.14 Comparison of trap signatures

## 6. HYSTERESIS-FREQUENCY SPECTROSCOPY

# 6.1 Theory

A useful procedure to study the hysteresis effect seen in the I-V characteristics of GaAs MESFET's is to vary the voltage sweep frequency. For sweep frequencies  $f >> \tau^{-1}$  (where  $\tau$  is the time constant of the traps causing hysteresis) traps cannot respond to the change in voltage so current looping can be expected to be negligible. For sweep frequencies  $f << \tau^{-1}$  traps can completely follow the change in voltage so current looping can again be expected to be negligible. Therefore, for a sweep frequency  $f_m \approx \tau^{-1}$  current looping should be a maximum.

Hysteresis in MESFET drain current vs. gate voltage ( $I_D^{-V}G$ ) characteristics is analyzed with the following approximations and assumptions.

We assume that there is only one donor-electron trapping level in the active region of the transistor. Its concentration is  $N_T$ , where  $N_T^{<< N_D}$  ( $N_D^{< N_D}$  is the shallow donor concentration of the n-type active region). Both traps and doping are taken to be uniform. When the depletion region is expanded to include occupied and, hence, neutral traps, their concentration is assumed to start decaying exponentially (as electrons leave them).

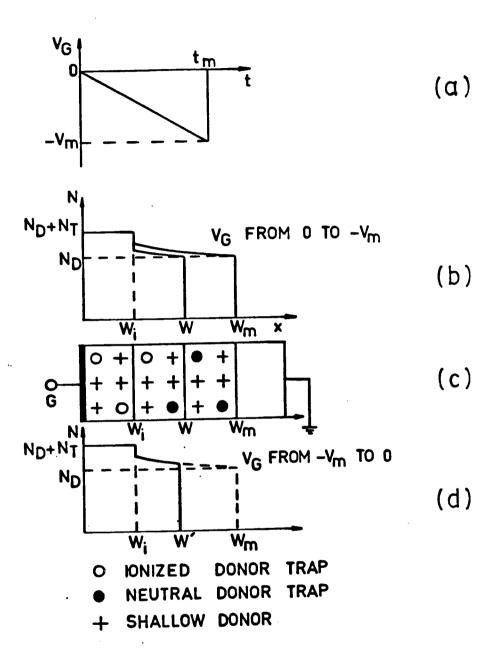

As shown in Fig. 6.1(a), a saw-tooth waveform is used to sweep  $V_G$  linearly from zero to  $-V_m$ , i.e.,  $V_G^{=}-V_m$  t/t<sub>m</sub>, where  $V_m$  is the amplitude and  $t_m$  is the period of the saw-tooth waveform.  $V_G$  is assumed to return to zero so rapidly that the occupation of the traps in the depletion region is frozen during this process.

Fig. 6.1 Ionization of traps in the depletion region due to the sweep of gate voltage with a saw-tooth waveform (a) Saw-tooth waveform (b) Concentration of ionized donors for  $V_G$  from 0 to  $-V_m$  (c) Ionization in Schottky gate depletion region (d) Concentration of ionized donors for  $V_G$  from  $-V_m$  to 0.

The depletion width at zero gate bias,  $W_i$ , corresponds to the built-in voltage  $V_{bi}$ . For negative gate biases, the depletion width is always greater than  $W_i$  and the traps inside  $W_i$  can hence be considered to be completely ionized, so that

$$W_{i} = \left(\frac{2 \varepsilon V_{bi}}{q(N_{D} + N_{T})}\right)^{1/2}, \qquad (6.1)$$

where  $\epsilon$  is the permittivity of the semiconductor. As the gate voltage changes from zero to  $V_G$ , the depletion width increases to W (Fig. 6.1b). The space charge concentration N(x) in the region  $W_i$  < x < W can be expressed as

$$N(x) = N_D + \delta(x) , \qquad (6.2)$$

where  $\delta(x)$  is the ionized trap concentration within this depletion region.

The relation between the depletion width W and the gate voltage  $\boldsymbol{v}_{\boldsymbol{G}}$  can be found by solving

$$\int_{W_{i}}^{W} N(x) x dx = - \int_{O}^{V_{G}} \frac{\varepsilon}{q} dV . \qquad (6.3)$$

Since  $N_T \ll N_D$ ,  $\delta(x)$  in Eq.(6.2) will be much smaller than  $N_D$ . Hence an iterative method can be used. At first, the ionized traps in the depletion region  $W_i \ll x \ll W$  are ignored, i.e., the second term of Eq. (6.2) is neglected. From Eq. (6.3).

$$W = \left( \left( \frac{2 \varepsilon V_{m}}{q N_{D}} \right) \left( \frac{V_{bi}}{V_{m}} \frac{N_{D}}{N_{D} + N_{T}} - \frac{V_{G}}{V_{m}} \right) \right)^{1/2} . \tag{6.4}$$

Eq. (6.4) is a first approximation to the relation between W and  $V_{G}$ .

The moment t at which position W starts to deplete can be obtained from Eq. (6.4)

$$t = \left(\frac{W^2}{\frac{2 \varepsilon V_m}{q N_D}} - \frac{V_{bi}}{V_m} \frac{N_D}{N_D + N_T}\right) t_m . \qquad (6.5)$$

A better approximation of N(x) at  $V_G$  in the region  $W_i < x < W$  can then be made. Since the concentration of the neutral traps in this region is considered to be decaying exponentially,  $\delta(x)$  of Eq. (6.2) can be expressed as

$$\delta(x) = N_{T} \left(1 - \exp\left(-\left(-\frac{V_{G}}{V_{m}} t_{m} - \left(\frac{X^{2}}{2 \epsilon V_{m}} - \frac{V_{bi}}{V_{m}} \frac{N_{D}}{N_{D} + N_{T}}\right) t_{m}\right) / \tau\right)\right) . \quad (6.6)$$

The time when the gate voltage changes to  $V_G$  is  $-V_G t_m/V_m$  and the moment when position x depleted is estimated with Eq. (6.5). Hence, N(x) can be obtained by substituting Eq. (6.6) into Eq. (6.2). This new N(x) is substituted into Eq. (6.3) the solution of which is a closer approximation of the relation between the depletion width W and the gate voltage  $V_G$  and can be written as

$$W^{2} \, \frac{q^{N}_{D}}{2 \, \epsilon V_{m}} \, - \, \frac{V_{\text{bi}}}{V_{m}} \, \frac{N_{D}}{N_{D} + N_{T}} \, - \, \frac{N_{T}}{N_{D} + N_{T}} \big( exp \, \big( \, \frac{V_{G}}{V_{m}} \, \frac{t_{m}}{\tau} \, \, \big) \big) \big( exp \, \big( \frac{t_{m}}{\tau} \, \, \big( W^{2} \, \frac{q^{N}_{D}}{2 \, \epsilon V_{m}} \, - \, \frac{V_{\text{bi}}}{V_{m}} \, \frac{N_{D}}{N_{D} + N_{T}} \big) \big) - 1 \, \big) \, \frac{\tau}{t_{m}} \, \frac{T_{M}}{T_{M}} \big( W^{2} \, \frac{q^{N}_{D}}{T_{M}} \, - \, \frac{V_{\text{bi}}}{V_{m}} \, \frac{N_{D}}{N_{D} + N_{T}} \big) \big) - 1 \, \big) \, \frac{\tau}{t_{m}} \, \frac{T_{M}}{T_{M}} \big( W^{2} \, \frac{q^{N}_{D}}{T_{M}} \, - \, \frac{V_{\text{bi}}}{V_{m}} \, \frac{N_{D}}{N_{D} + N_{T}} \big) \big) - 1 \, \big) \, \frac{\tau}{t_{m}} \, \frac{T_{M}}{T_{M}} \big( W^{2} \, \frac{q^{N}_{D}}{T_{M}} \, - \, \frac{V_{\text{bi}}}{V_{m}} \, \frac{N_{D}}{N_{D} + N_{T}} \big) \big) - 1 \, \big( W^{2} \, \frac{q^{N}_{D}}{T_{M}} \, - \, \frac{V_{\text{bi}}}{T_{M}} \, \frac{N_{D}}{N_{D} + N_{T}} \big) \big) - 1 \, \big( W^{2} \, \frac{q^{N}_{D}}{T_{M}} \, - \, \frac{V_{\text{bi}}}{T_{M}} \, - \,$$

$$= -\frac{V_G}{V_m} \left(1 - \frac{N_T}{N_D + N_T}\right) . \qquad (6.7)$$

By setting L = W(  $\frac{qN_D}{2\,\epsilon V_m}$  ) ,  $\alpha = \frac{N_T}{N_D + N_T}$  and  $\beta = \frac{V_{bi}}{V_m} \frac{N_D}{N_D + N_T}$ , Eq. (6.7) can be simplified to

$$L^{2} - \beta - \alpha \left( \exp \left( \frac{V_{G}}{V_{m}} \frac{t_{m}}{\tau} \right) \right) \left( \exp \left( \frac{t_{m}}{\tau} \left( L^{2} - \beta \right) \right) - 1 \right) \frac{\tau}{t_{m}} = -\frac{V_{G}}{V_{m}} \left( 1 - \alpha \right) . \quad (6.8)$$

L, which is referred as the normalized depletion width later, can be estimated as a function of  $V_G/V_m$  and  $t_m/\tau$  by using Newton-Raphson iteration.

When the gate voltage reaches  $-V_{\rm m}$ , the depletion width is defined as W which can be obtained by substituting  $-V_{\rm m}$  to V Gin Eq. (6.7).

We now consider the return of the gate voltage from  $-V_{\rm m}$  to zero (Fig. 6.1d). The relation between the depletion width W' and the gate voltage  $V_{\rm G}$  can be obtained similarly by solving

$$\int_{W_{m}}^{W'} N(x) x dx = -\int_{-V_{m}}^{V_{G}} \frac{\varepsilon}{q} dV . \qquad (6.9)$$

Since the trap occupancy is assumed to be frozen during this process, N(x) can be obtained by substituting Eq. (6.6) to Eq. (6.2) with  $V_G = -V_m$ . The solution of Eq. (6.9) is

$$L_{m}^{2} - L^{\prime 2} - \alpha \left(\exp\left(-\frac{t_{m}}{\tau}\right)\right) \left(\exp\left(\frac{t_{m}}{\tau}\left(L_{m}^{2}\beta\right)\right) - \exp\left(\frac{t_{m}}{\tau}\left(L^{\prime 2}-\beta\right)\right)\right) \frac{\tau}{t_{m}} = \left(1 + \frac{V_{G}}{V_{m}}\right) (1-\alpha)$$

$$(6.10)$$

where

$$L_{m} = W_{m} \left( \frac{qN_{D}}{2 \varepsilon V_{m}} \right)^{1/2}$$

and

$$L' = W' \left( \frac{qN_D}{2 \varepsilon V_m} \right)^{1/2} .$$

L' can then be calculated as a function of  ${\rm V}_{\rm G}/{\rm V}_{\rm m}$  and  ${\rm t_m}/\tau_{\bullet}$

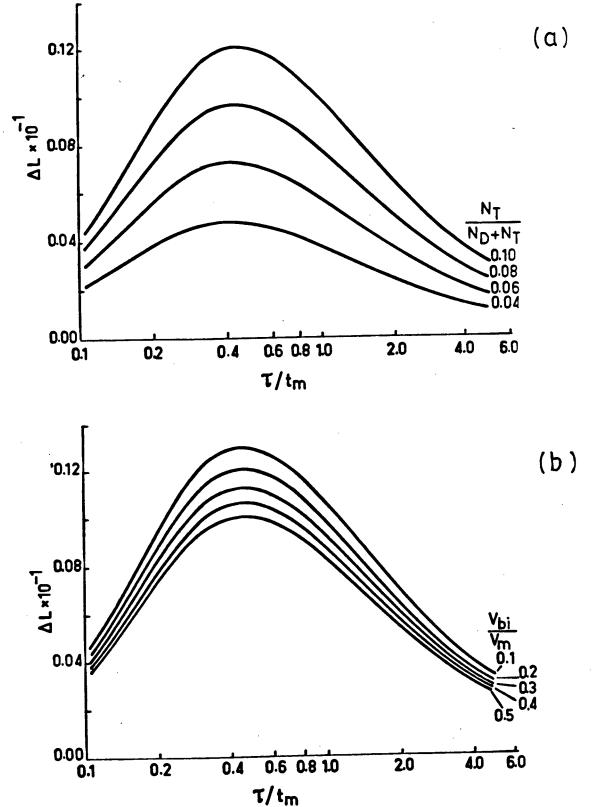

The extent of hysteresis observed in the  $I_D^{-V}_G$  characteristics is defined as the difference ( $\Delta I_D$ ) between the current  $I_D$  (when the gate voltage changes from zero to  $V_G$ ) and  $I_D^{\prime}$  (when the voltage returns to this  $V_G$  after reaching  $-V_m$ ). With the preceding formulation, the hysteresis can be interpreted as a consequence of the inequality of L and L' at the same gate voltage because since  $I_D$  is considered to be proportional to the channel width,  $\Delta I_D$  is proportional to  $\Delta L = L - L'$ .  $\Delta L$  at  $V_G = -\frac{1}{2} V_m$  has been calculated as a function of  $\tau/t_m$  for different concentrations of deep level traps (Fig. 6.2a). Fig. 6.2b shows five more curves of  $\Delta L$  (at  $V_G = -\frac{1}{2} V_m$ ) vs.  $\tau/t_m$  with different  $V_m$  values. These results suggest that the position of the maximum of the curve,  $\Delta L$  vs.  $\tau/t_m$ , does not depend significantly on the values of  $N_T$  and  $V_m$  in the indicated range. The maxima of these curves which correspond to the maximum extent of hysteresis at the indicated conditions always occur at  $\tau/t_m \approx 0.4$ . The occurrence of a maximum logically follows the two qualitative considerations: (1) if  $t_m^{-1} << \tau$  the traps in the

Fig. 6.2 The difference ( L) between the normalized depletion width when  $V_G$  changes from zero to  $-V_m/2$  as a function of normallized sweep frequency (a) for different  $N_T$  (b) for different  $V_m$

depletion region can completely ionize and (2) if  $t_m^{-1} >> \tau$  the traps cannot respond to the sweep in voltage and remain neutral. In both cases no hysteresis results.

$\Delta I_D$  can be measured experimentally by sampling and comparing the current  $I_D$  and  $I_D'$  at the same  $V_G$ . The resultant plot of  $\Delta I_D$  vs. sweep frequency (1/t<sub>m</sub>) will be referred to as an I-V hysteresis spectrum (IVHS) by analogy with DLTS. Since  $\Delta I$  is proportional to  $\Delta L$ , the frequency at which the spectrum peaks gives the time constant of the traps

$$\tau \simeq 0.4 t_{\rm m} = (2.5 f_{\rm m})^{-1}$$

(6.11)

In addition, the energy level of the traps can be estimated by measuring time constants at different temperatures and using Eq. (5.11).

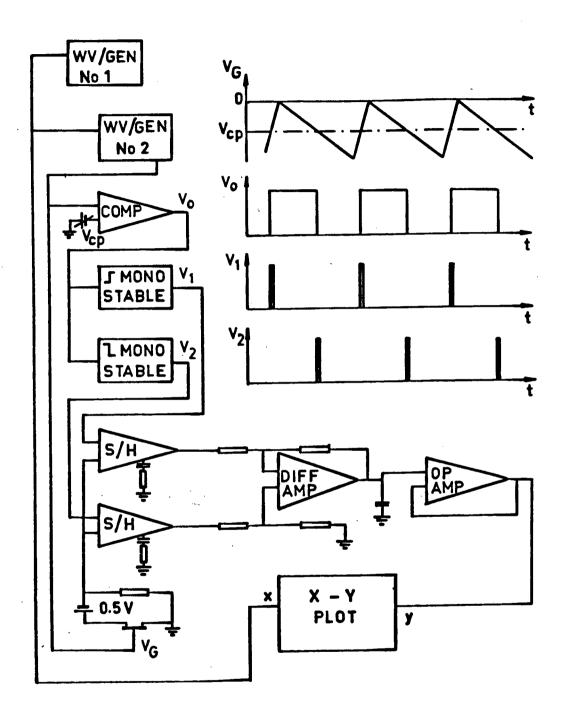

## 6.2 Apparatus

The system shown in Fig. 6.3 was assembled to record the frequency behaviour of MESFET  $I_D^{-V}_G$  hysteresis. Waveform generator 1 (Servomex LF51) generates a voltage ramp to control the frequency of the (saw-tooth) waveform generated by waveform generator 2 (IEC F63) and also drives the X-axis of a X-Y plotter (Moseley 135). The saw -tooth waveform is input to the gate of the MESFET sample and a comparator. The other input of the comparator is connected to a DC supply used to adjust the  $V_G$  at which drain current is sampled. Two pulses are derived from the output of the monostable multivibrators (MC 74121) and used to trigger the two LF398 sample and holds. Hence  $I_D$  and  $I_D^{\bullet}$  are measured at a desired  $V_G$  and input to a differential

Fig. 6.3 Experimental arrangement for hysteresis measurements

amplifier. The output, a voltage proportional to  $\Delta I_{\mbox{\scriptsize D}}$  is sent to the Y-axis of the plotter.

### 6.3 Measurements