# Bridging the Gap between Soft and Hard eFPGA Design

by

Victor Olubunmi Aken'Ova

B.A.Sc. University of British Columbia, 2002

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Applied Science Degree

in

The Faculty of Graduate Studies

Electrical and Computer Engineering

The University of British Columbia

March 2005

© Victor Olubunmi Aken'Ova 2005

### **Abstract**

# Bridging the Gap between Hard and Soft eFPGA Design

by

#### Victor Olubunmi Aken'Ova

Potential cost savings that come from the ability to make *post* fabrication changes in System-on-Chip (SoC) designs make embeddable Field Programmable Gate Array (eFPGA) cores an attractive design option. However, they are only available as "hard" macros from vendors as a small number of fixed size cores, and may not be optimal in terms of area, power or delay for a given SoC. A "soft" eFPGA methodology [01][02] based on the ASIC design flow was used to create small amounts of programmable logic but incurs significant overhead. In this thesis, it is shown that this overhead can be reduced by deploying architecture-specific tactical standard cells in the ASIC flow, making eFPGA generation configurable, and imposing a regular structure on eFPGA architectures.

For the set of benchmarks considered, the use of tactical standard cells resulted in area and delay savings of 58% and 40% respectively, when compared to cores implemented with generic standard cells [02]. Also, a proposed IP-generator-based approach for eFPGA design is shown to achieve results that are competitive with commercial full-custom hard eFPGA cores. For example, for some large benchmark circuits (over 1000 4-LUTs) the generated eFPGA fabrics were up to 40% smaller than available hard eFPGA cores. Finally, it is shown that a regular structured architecture makes it possible to generate fabrics with logic capacities that greatly exceed what was previously possible [02] [15]. In addition, a structured layout approach yielded a 36% reduction (average) in wire lengths.

# Table of Contents

| Abstract                                                         |     |

|------------------------------------------------------------------|-----|

| Table of Contents                                                | iii |

| List of Figures                                                  | vi  |

| List of Tables.                                                  |     |

| Acknowledgments                                                  |     |

| Chapter 1 Thesis Introduction                                    |     |

| 1.1 Research Motivation                                          |     |

| 1.2 Research Objectives                                          | 3   |

| 1.3 Thesis Organization                                          | 5   |

| Chapter 2 Background and Related Previous Research               | 6   |

| 2.1 Overview of Integrated Circuit (IC) Design Techniques        | 6   |

| 2.2 Embedded Programmable Logic IC Design Techniques             | 12  |

| 2.2.1 Embedded Field Programmable Gate Array (eFPGA)             | 13  |

| 2.2.2 Embedded Mask Programmable Gate Array (MPGA)               | 17  |

| 2.2.3 Example Application: Bluetooth Base-band System-on-Chip    |     |

| 2.3 Embedded Programmable Logic as an Intellectual Property (IP) | 21  |

| 2.3.1 Hard eFPGA IP                                              | 21  |

| 2.3.2 Soft eFPGA IP                                              |     |

| 2.4 Research Problem Definition and Thesis Research Focus        |     |

| Chapter 3 An Embedded Programmable Logic Architecture Family     | 27  |

| 3.1 Island-Style eFPGA Architectures                             | 27  |

| 3.1.1 Bidirectional Routing Architectures for eFPGA design       | 28  |

| 3.2 Architectural Issues                                         | 32  |

| 3.2.1 Input/Output Design                                        | 32  |

| 3.2.2 Design for Testability                                     | 36  |

| 3.2.3 SRAM Power up State                                        |     |

| Chapter 4 Island-Style eFPGA Design with Generic Standard Cells  | 40  |

| 4.1 The Existing Design flow                                     | 40  |

|     | 4.1.1 Front-End Flow                                         | 42  |

|-----|--------------------------------------------------------------|-----|

|     | 4.1.2 Back-End Flow                                          |     |

| 4.2 | Design Flow Issues and Solutions                             | 44  |

|     | 4.2.1 Combinational Loop-back                                | 44  |

|     | 4.2.2 Architecture Discrepancies                             | 49  |

|     | 4.2.3 Static Timing Exceptions                               |     |

|     | 4.2.4 Configuration Power                                    |     |

| 4.3 | , <del>~</del>                                               |     |

| Cha | apter 5 Island-Style eFPGA Design with Custom Standard Cells | 63  |

| 5.1 | An Improved Design flow                                      | 63  |

| 5.2 | Design of Custom Cells                                       | 65  |

|     | 5.2.1 SRAM Cell Circuit Design                               | 65  |

|     | 5.2.2 Multiplexer Circuit Design                             | 66  |

| 5.3 | Layout Design                                                | 72  |

| 5.4 | Layout Improvements                                          | 75  |

| 5.5 | 5.5 eFPGA Design Results                                     |     |

|     | 5.5.1 Area Improvements                                      | 76  |

|     | 5.5.2 Delay Improvements                                     |     |

| 5.6 | Comparison to GILES                                          | 82  |

| 5.7 | Sensitivity Case Study                                       | 85  |

| 5.8 | Mux Switch Evaluation                                        | 89  |

| Cha | apter 6 The Implications for eFPGA IP Design                 | 90  |

|     | 6.1.1 Some "Real world" Case Studies                         | 91  |

| 6.2 |                                                              |     |

|     | 6.2.1 "Open" Architecture IP Library                         | 95  |

|     | 6.2.2 Configurable Architecture IP                           | 96  |

|     | 6.2.3 Domain-driven IP generation                            |     |

|     | 6.2.4 Automated Layout generation                            | 98  |

|     | 6.2.5 Summary                                                | 100 |

| Cha | apter 7 Final Conclusions and Future Research Work           | 101 |

| 7.1 | Conclusions                                                  | 101 |

| 72  | Future Work                                                  | 104 |

| 7.3 Contributions                                                         | 104 |

|---------------------------------------------------------------------------|-----|

| Appendix A Standard Cell Based eFPGA implementation Results               | 107 |

| Appendix B Area Model for Standard Cell based eFPGA area Estimation       | 111 |

| Appendix C Details of Circuit Analysis Solutions for Multiplexer Circuits | 113 |

| Appendix D Area estimation method for GILES and Full-custom eFPGAs        | 116 |

| Appendix E A sample structured eFPGA layout and Bluetooth SoC Floorplan   | 123 |

| Bibliography                                                              | 125 |

# **List of Figures**

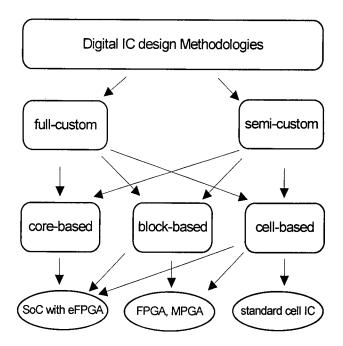

| Figure 2.1: A general overview of existing integrated circuit design techniques      | 7  |

|--------------------------------------------------------------------------------------|----|

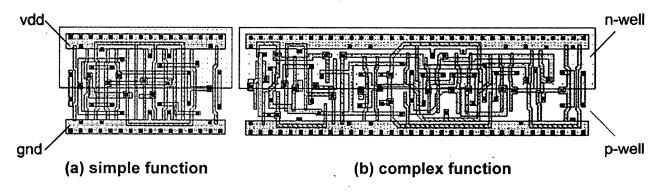

| Figure 2.2: Sample generic standard cell layout for two CMOS logic functions         | 8  |

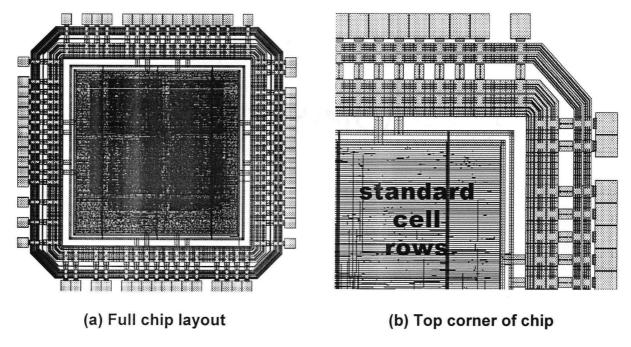

| Figure 2.3: Typical standard cell chip layout and a closer view of cell rows in chip | 9  |

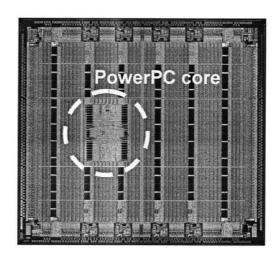

| Figure 2.4: A programmable platform IC with an embedded PowerPC® processor           | 10 |

| Figure 2.5: Typical flow for semi-custom cell, block, and core based ASIC design     | 11 |

| Figure 2.6: 2x2 island style eFPGA core architecture and regular tile architecture   | 13 |

| Figure 2.7: programmable logic CLB of size 4 and a disjoint switch block topology    | 14 |

| Figure 2.8: Input and output connection blocks in the eFPGA routing architecture     | 15 |

| Figure 2.9:VPR placement and routing of a sample user circuit in a 6x6 logic array   | 16 |

| Figure 2.10: A MPGA logic tile layout, and a connectivity fabric of top metal layers | 18 |

| Figure 2.11: A System-on-a-Chip platform that implements the Bluetooth Protocol      | 20 |

| Figure 2.12: An example of architectural inefficiencies in existing hard eFPGA IP    | 23 |

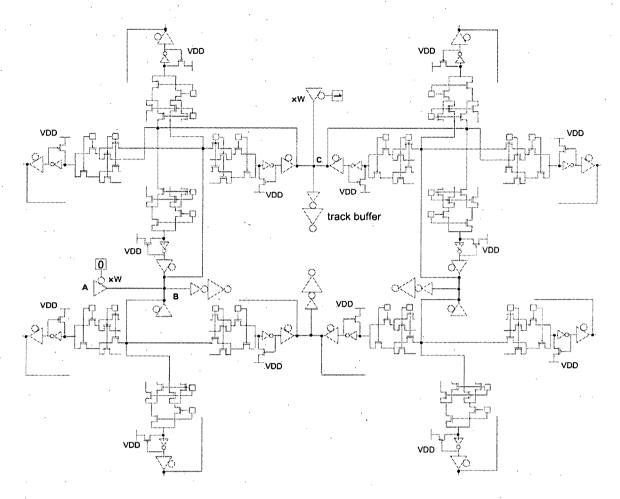

| Figure 3.1: An island style eFPGA tile architecture with tri-stated routing switches | 28 |

| Figure 3.2: Island style eFPGA tile architecture with multiplexed routing switches   | 29 |

| Figure 3.3: Island style eFPGA tile with improved multiplexed routing switch 1       | 30 |

| Figure 3.4: Island-style eFPGA tile with improved multiplexed routing switch 2       | 31 |

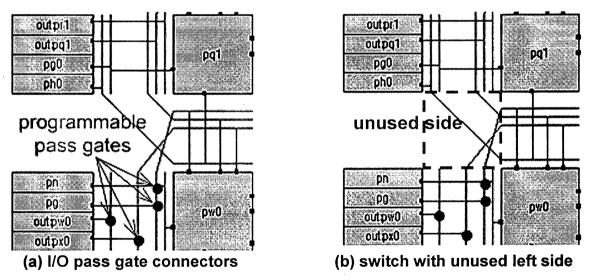

| Figure 3.5: Programmable I/O pad connections and unused switch connections           | 33 |

| Figure 3.6: Equivalent external input routing in standalone and embedded FPGA        | 34 |

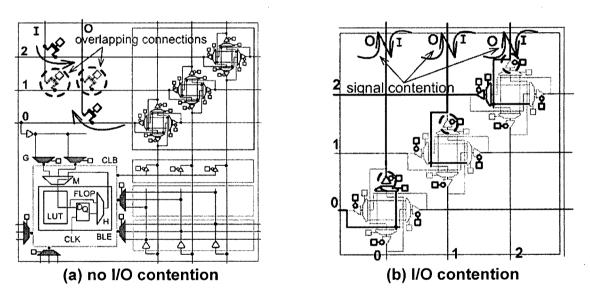

| Figure 3.7: A limitation of the novel embedded FPGA external I/O architecture        | 35 |

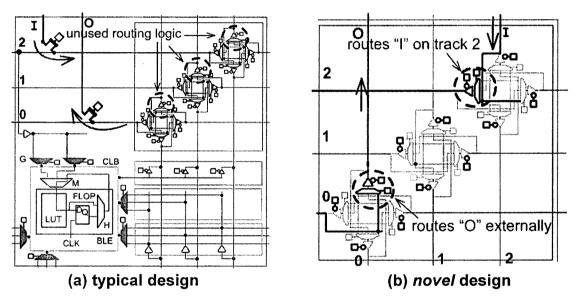

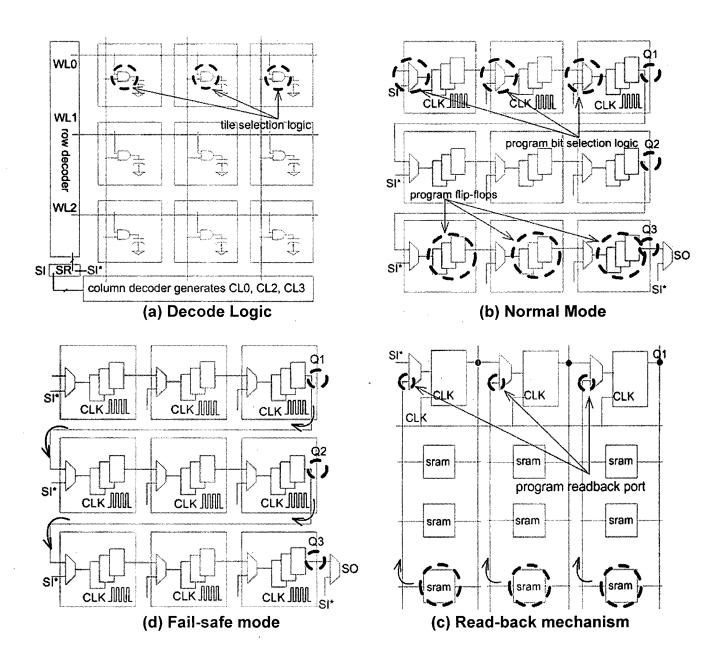

| Figure 3.8: An embedded FPGA IP configuration architecture designed for test         | 37 |

| Figure 3.9: Logic to prevent driver contention in bidirectional routing architecture | 39 |

| Figure 4.1: Typical flow for semi-custom cell, block, and core based ASIC design     | 42 |

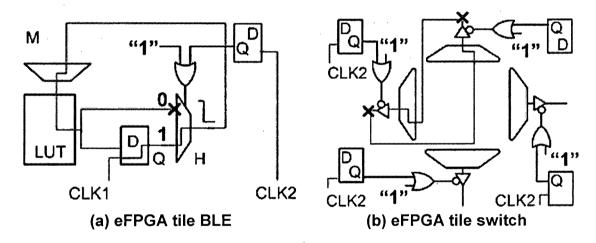

| Figure 4.2: Combinational and sequential loops in an island-style eFPGA tile BLE     | 45 |

| Figure 4.3: Example of combinational loops path in a multiplexed routing switch      | 46 |

| Figure 4.4: Technique to avoid loop breaking during synthesis and verification       | 47 |

| Figure 4.5: VPR critical timing path trace for "golden-20" benchmark circuit apex4   | 50 |

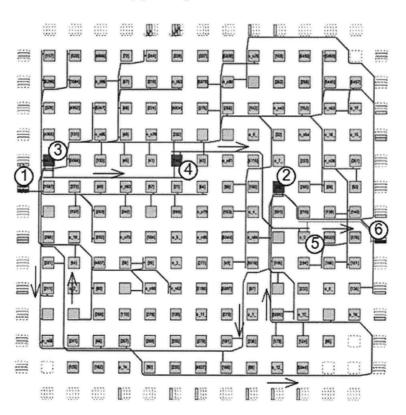

| Figure 4.6: Proposed configuration scheme targeting a single tile and row of tiles   | 51 |

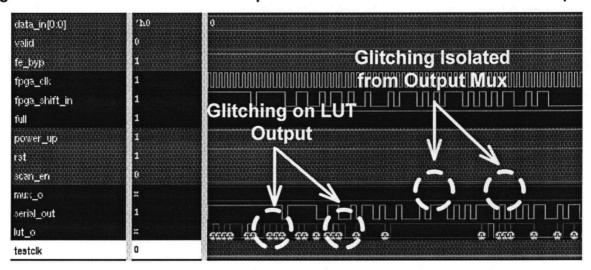

| Figure 4.7: Proposed scheme for glitch isolation during soft eFPGA configuration                 | . 53       |

|--------------------------------------------------------------------------------------------------|------------|

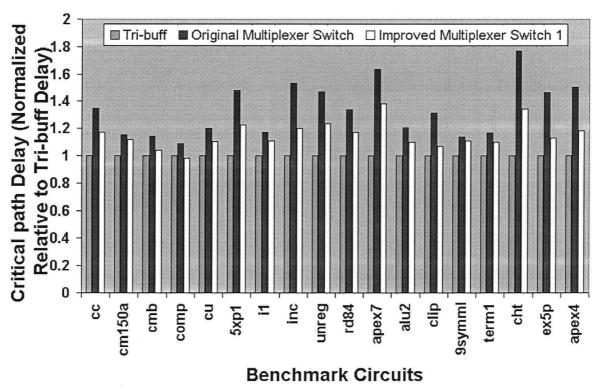

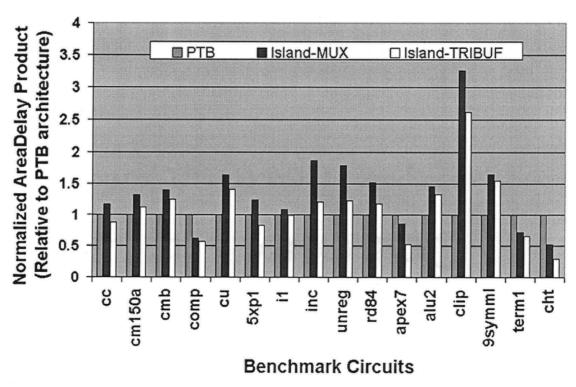

| Figure 4.8: Critical path delay comparison of three soft island-style architectures              | . 55       |

| Figure 4.9: Overall core area comparison of three soft island-style architectures                | . 56       |

| Figure 4.10: Comparison of CMOS logic and pass transistor based multiplexers                     | . 60       |

| Figure 4.11: transistor level illustration of a simple single-edge-triggered flip-flop           | . 61       |

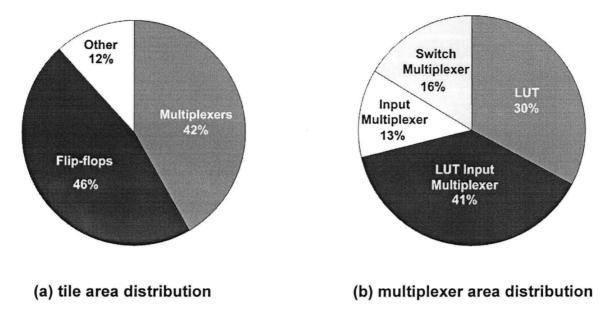

| Figure 4.12: pie charts showing area distribution in a soft island-style eFPGA tile              | . 62       |

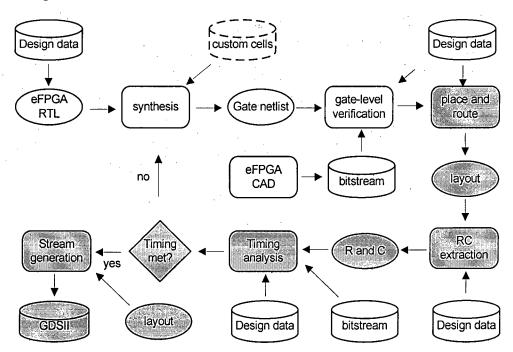

| Figure 5.1: an enhanced ASIC design flow for eFPGA design and implementation                     | . 64       |

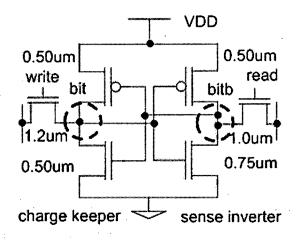

| Figure 5.2: SRAM transistor sizing for embedded FPGA configuration memory                        | . 66       |

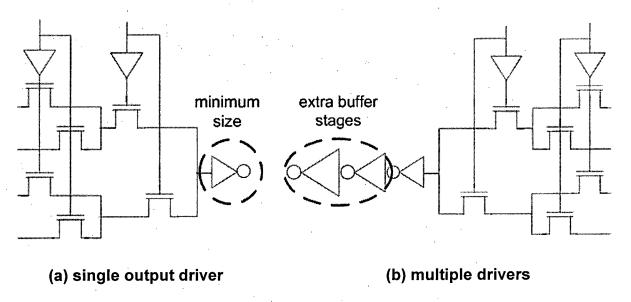

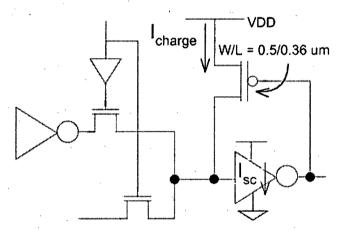

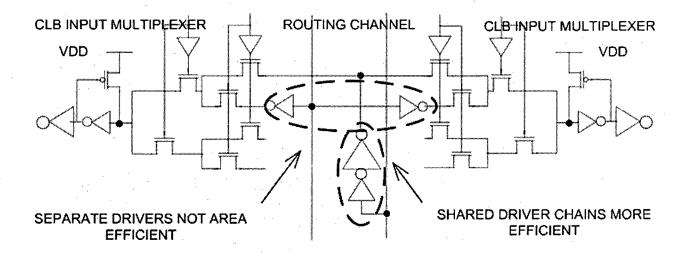

| Figure 5.3: multiplexer with minimum size output buffer and extra buffer stages                  | . 66       |

| Figure 5.4: a level restoring circuit for pass-transistor-based multiplexing logic               | . 67       |

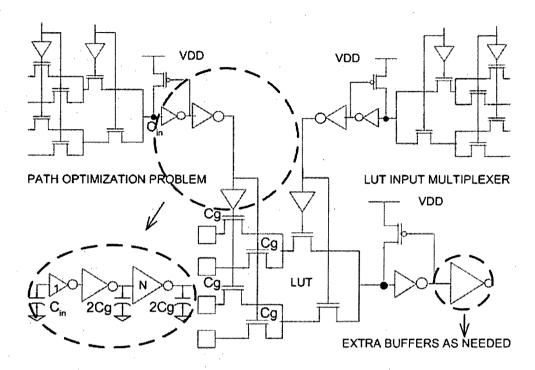

| Figure 5.5: Delay optimization problem specification for LUT input-selection paths               | . 68       |

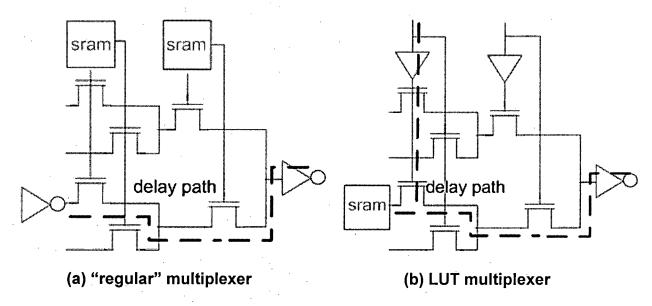

| Figure 5.6: Critical delay paths for the different multiplexing circuits in an eFPGA             | . 69       |

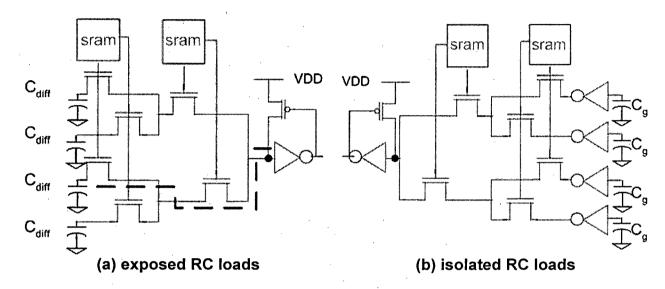

| Figure 5.7: Issues around input loading for pass tree networks in the ASIC flow                  | . 70       |

| Figure 5.8: two possible multiplexing-logic buffering schemes for eFPGA design                   | . 71       |

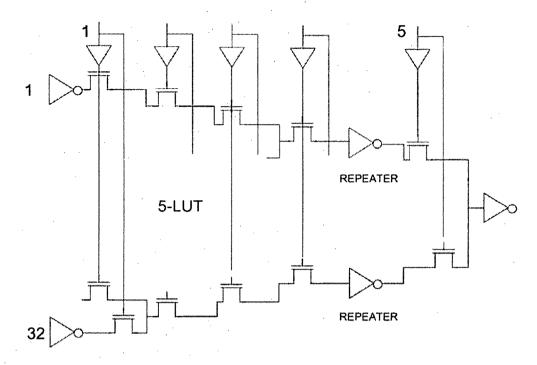

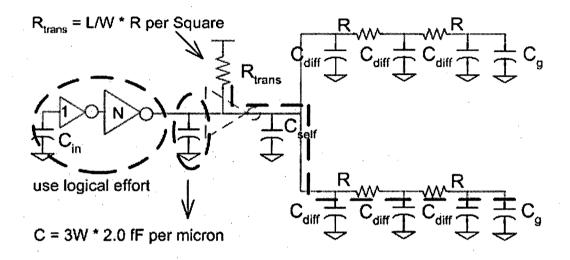

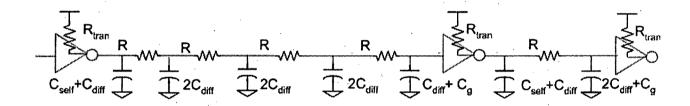

| Figure 5.9: RC network representation of repeater insertion in an eFPGA 5-LUT                    | . 72       |

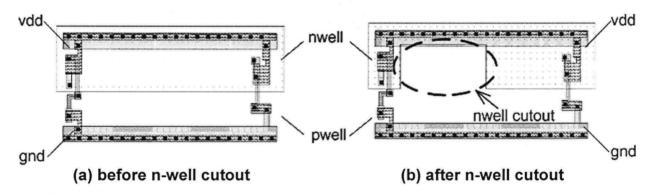

| Figure 5.10: standard cell layout structure before and after n-well cutout is made               | . 73       |

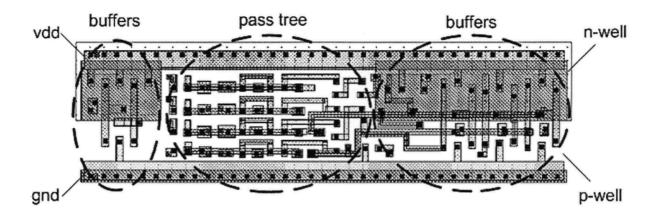

| Figure 5.11: illustration of resource allocation in a multiplexer standard cell layout           | . 74       |

| Figure 5.12: double height standard cell layout of 32:1 multiplexer (2 metal layers)             | . 74       |

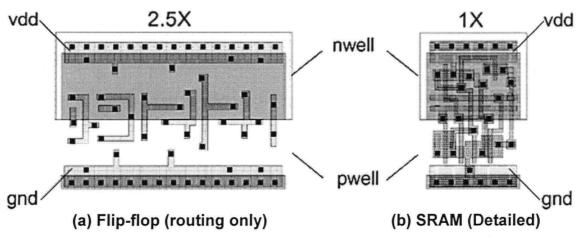

| Figure 5.13: I flip-flop used for configuration memory in the previous approaches                | . 75       |

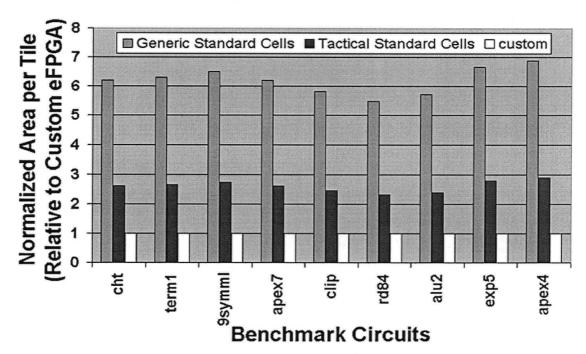

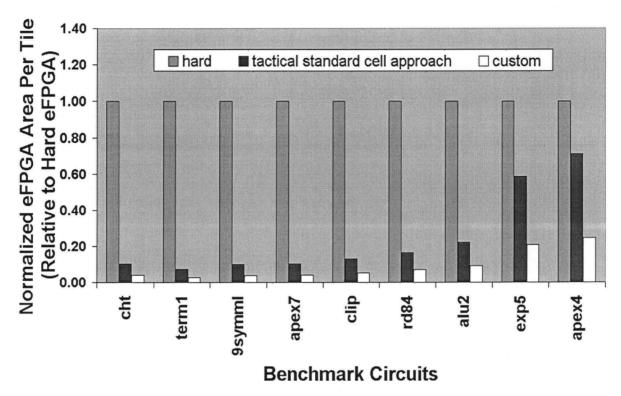

| Figure 5.14: area comparisons of customized tactical standard-cell-based eFPGA implementation    | . <b>S</b> |

| with generic standard cell, and full-custom implementations                                      | . 77       |

| Figure 5.15: illustration of SPICE simulation setup to measure logic block delay                 | . 79       |

| Figure 5.16: SPICE simulation setup to measure the routing switch element delay                  | . 80       |

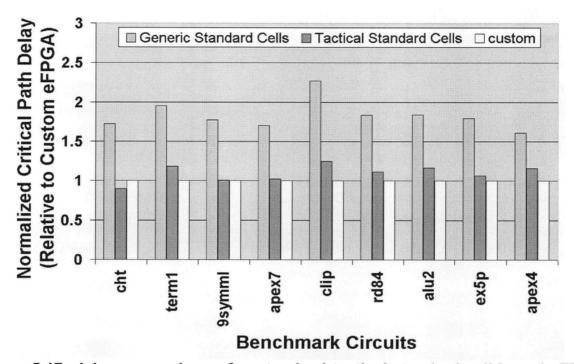

| Figure 5.17: delay comparison of customized tactical standard-cell-based eFPGA implementation    | ιS         |

| with generic standard cell, and full-custom implementations                                      | . 81       |

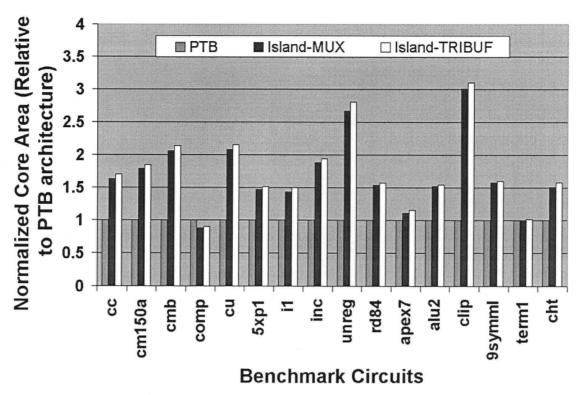

| Figure 5.18: Core area comparison of product-term and island-style architectures                 | . 86       |

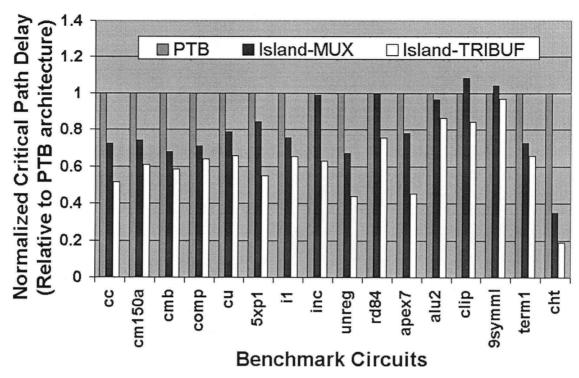

| Figure 5.19: delay path comparison of product-term and island-style architectures                | . 88       |

| Figure 5.20: Area-delay-product comparison of product-term and island-style core                 | . 88       |

| Figure 6.1: logic efficiency comparisons of a standard-cell-based eFPGA IP generator approach to | o a        |

| commercial hard IP approach for 9 MCNC benchmarks                                                | . 92       |

| Figure A.1: Block level diagram of the test interface module with an eFPGA fabric |

|-----------------------------------------------------------------------------------|

| Figure A.2: simulation waveform capture of eFPGA state transitions and response   |

| Figure A.3: simulation waveform capture of glitches and glitch isolation in a BLE |

| Figure C.1: RC network representation of shared buffering scheme in an eFPGA      |

| Figure C.2: RC network representation of repeater insertion in an eFPGA 5-LUT     |

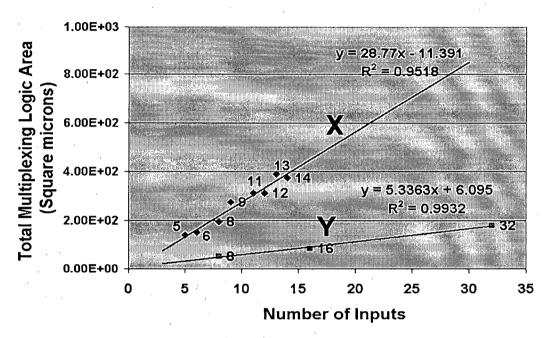

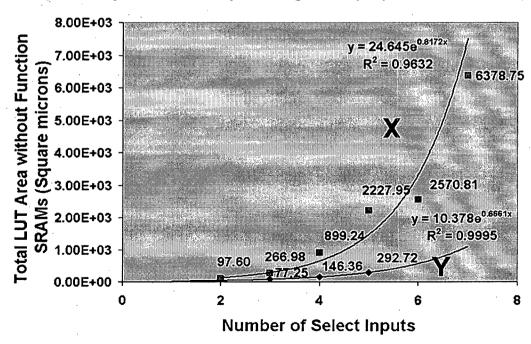

| Figure D.1: plot of layout area vs. inputs for general-purpose eFPGA multiplexers |

| Figure D.2: Plot of layout area (excluding the SRAMs) vs. select inputs for LUT   |

| Figure D.3: Plot of layout area (excluding the function SRAMs) vs. inputs for LUT |

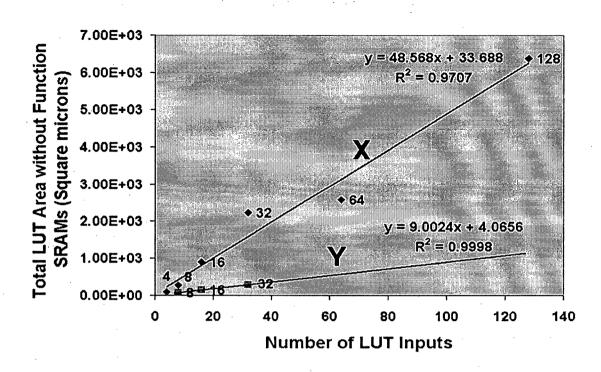

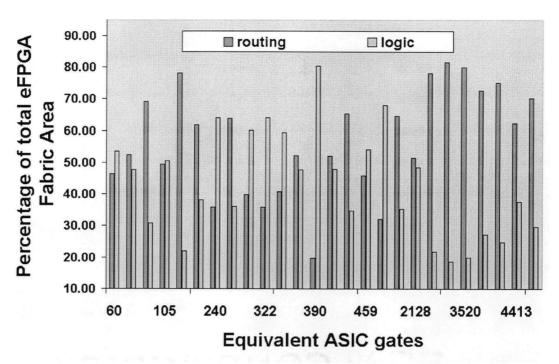

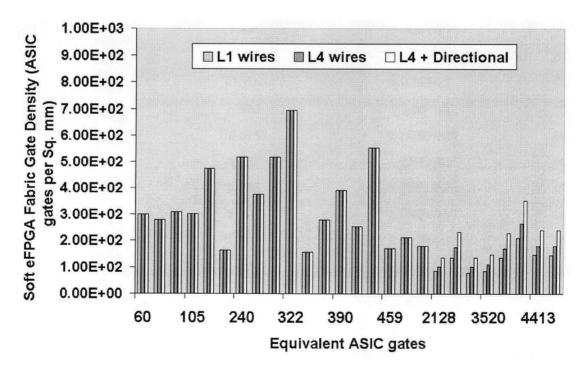

| Figure D.4: Area distribution between logic and routing components of eFPGA119    |

| Figure D.5: ASIC gate density scaling after estimated improvements to routing     |

| Figure E.1: Structured eFPGA layout for Bluetooth Baseband Encryption Module      |

| Figure E.2: Bluetooth baseband SoC showing underutilized area around the core     |

# List of Tables

| Table 2.1: Comparison of eFPGA, MPGA and standard cell logic design methods          | 18  |

|--------------------------------------------------------------------------------------|-----|

| Table 4.1: Area overhead of "soft" eFPGA design relative to full-custom approach     | 58  |

| Table 4.2: Delay overhead of "soft" eFPGA design relative to a full-custom design    | 59  |

| Table 5.1: layout area improvements with tactical cells vs. generic standard cells   | 75  |

| Table 5.2: The scaling factors for multiplexer logic bloating in GILES Virtex-E tile | 84  |

| Table 6.1: Summary of Soft, Firm and Hard eFPGA implementation methodologies         | 100 |

| Table A.1: Design results for 18 eFPGA cores with tri-state buffer based switches    | 109 |

| Table A.2: Design results for 18 eFPGA cores with original multiplexer switches      | 110 |

| Table A.3: Design results for 18 eFPGAs using the speedy multiplexer switch 1        | 110 |

# Acknowledgments

I would like to thank my supervisor Dr. Resve Saleh for the opportunity to work with him. His enthusiasm and support over the years are unmatched. He was easily my most vocal Cheerleader. I also would like to thank Dr. Guy Lemieux for teaching me everything I know about FPGAs.

I am also grateful to all the other professors of the SoC research Lab because I learned something from all of them. I especially would like to thank Dr. Steve Wilton who spearheaded the Soft eFPGA concept at UBC that ultimately led to my research topic. Thanks for all the comments and insight.

I would also like to thank the staff of the SoC lab. Roozbeh our CAD manager was a tremendous help and always tried his best to cater to my *many* requests. Roberto our Test Lab manager was always fantastic with the test lab equipment and great at finding solutions to all kinds of vexing problems. Sandy Scott our administrative assistant was always cheerful and happy to help. I am grateful to you all.

I would also like to thank past and present student members of the SoC lab for their support. I especially thank Pedram Sameni, James Wu, Ronald Fung, Louis Hong, Mohsen Nahvi, Marvin Tom, Zion Kwok, Neda Nouri, Noha Kafafi, Julien Lamoureux, Rod Foist, Brad Quinton, and Kara Poon.

Almost last, but certainly not least, I would like to thank my entire family for the tremendous love and support they have shown me my entire life. I am thankful to them for teaching me the value of hard work and dedication. A very gigantic hug also goes to my dear Laura for easily being my best friend.

Many thanks to NSERC, PMC-Sierra, the Canadian Microelectronics Corporation and the University of British Columbia for the financial and tool support that made all this work possible. Viva Canada.

In loving memory of my dearest Mama

# Chapter 1

#### **Thesis Introduction**

#### 1.1 Research Motivation

The increasing density of integrated circuit (IC) designs due to shrinking transistor sizes has led to the emergence of System-on-Chip (SoC) design to cope with the resulting increase in design size and complexity. However, this has resulted in significant increases in the cost of IC designs due to corresponding increases in engineering and mask costs in the order of tens of millions of dollars. Therefore, designers are pursuing software and hardware methods to build programmable SoCs and avoid the extra costs of chip re-spins. A programmable device can be used to compensate for errors, adapt to changes in standards or design specifications and amortize costs over design derivatives.

Embedded Programmable Logic Cores (ePLCs) have emerged as a natural hardware solution to meet this growing challenge because they allow logic functionality to be changed after fabrication. Such cores are generally suited to small and medium on-chip logic functions such as accelerator functions for on-chip processors to speed up embedded software, data encryption circuits in wireless devices that need to be changed from time to time, packet routing switches for the newly emerging Network-on-Chip design paradigm [71], and I/O standards for data communication.

In spite of the potential cost benefits and useful applications of ePLCs in SoC design, commercial success has been limited by a number of difficult issues that arise. These range from design and implementation issues [14] to issues related to the nature of commercial ePLCs devices in general. For example, common design problems concern the selection of blocks to make programmable, the

integration of fixed and programmable blocks and the size of the programmable block. However, by far the biggest issue with ePLCs is the high area, power and delay overhead that they generally incur.

These overhead issues are not unique to ePLCs alone; it has also become an important issue for stand-alone programmable logic devices like Field Programmable Gate Array (FPGA) chips. However, this issue is more critical for ePLCs because they are needed in high performance IC designs that have stringent area, speed, and power requirements. Further, this problem is made even worse because ePLCs, like FPGA chips, are available in limited sizes and ranges, and so designers must select the smallest core or chip that will accommodate their circuit(s). The selected ePLC could be much bigger than needed, slower, and consume more power, because vendors include excess resources for potential circuit implementations. As a result, prospective users are sometimes forced to abandon ePLCs altogether, and this has resulted in a general lack of interest in these devices.

Current commercial programmable logic design techniques do not afford vendors much opportunity to address some of the reasons for the overhead in ePLCs because they use expensive full-custom design techniques to build ePLCs, and so have to find a cost effective tradeoff when designing their products. Hence, for cost reasons, these vendors design a minimum set of cores that can serve the broadest range of user applications possible while keeping the device performance overhead within tolerable bounds. This model works well for standalone FPGA chips because they are not used in high performance situations and therefore users can tolerate the additional performance overhead.

The above model is unsatisfactory for ePLCs because higher performance is often required. Furthermore, because their application space is limited and target user circuits often share common characteristics, surplus resources on the same scale as FPGA chips is not required. For example, if a

designer uses an ePLC for the purpose of allowing future "bug fixes" or design revisions, then it is reasonable to assume that potential future circuit implementations will be of about the same size. The existing model for ePLC design cannot take advantage of domain information, since tailoring ePLCs for application specific scenarios is expensive for vendors. However, if ePLCs are to make inroads into mainstream digital design, domain knowledge should be exploited [01] in some fashion.

The potential benefits and the difficulties associated with embeddable programmable logic design motivate the research work presented in this thesis report. For most of the benefits to be realized, current ePLC design methodologies must be revisited. For example, rather than a "one-size-fits-all" model for designing programmable logic cores, an alternative approach that tailors cores to a particular application domain might be more appropriate. Therefore, in this research, we explore some new techniques that could make a "one-size-fits-few" design model feasible for ePLC design.

## 1.2 Research Objectives

Given the inherent difficulties associated with using ePLCs in high performance chip design, this work proposes some new ways to reverse the current trends and make the use of ePLCs more attractive to users. To achieve this goal, some important observations about current methodologies for embedded programmable logic design will be made and solutions investigated and evaluated.

First, the advantages and disadvantages of the "soft" [02] and "hard" [44] ePLC design methodologies are evaluated. Following from this, an embeddable programmable logic architecture is implemented in a way that combines the best characteristics of the existing design methodologies.

Second, inefficiencies in area and speed that result from implementing a ePLC within an automated, generic-cell-based design flow [02] are investigated, and the compared to previous research results. The goal here is to pinpoint areas of the design flow that could benefit the most from optimization.

Third, architecture-specific tactical cells are designed to replace generic cells and eliminate inefficiencies resulting from the use of a generic-cell-based IC design flow [02] [14] [15]. ollowing custom cell design, area and speed improvements that can be achieved as a result of implementing an embeddable programmable logic architecture with custom cells in an automated design flow are reported. The results obtained are then compared with other previous approaches [02][15][68].

Fourth, certain inefficiencies that exist in current commercial design approaches are investigated by comparing our design results for area and speed to an existing commercial hard ePLC library [44].

Lastly, a new paradigm is introduced for embedded programmable logic design that combines domain driven architectural exploration with a flexible and efficient semi-custom circuit design flow.

# 1.3 Thesis Organization

Chapter 2 of this thesis presents some general background on the research subject, summarizes work done in this area to date, describes benefits and difficulties associated with existing ePLC technologies and design methods, illustrates potential uses of programmable technology on a wireless IC (Bluetooth) and then introduces an approach for ePLC design explored in this thesis.

Chapter 3 describes variants of a well-known architecture to be used in the proposed approach for embedded PLC design. This chapter includes a detailed description of some design issues that were resolved during architecture specification in order to ensure proper ePLC operation.

Chapter 4 presents results obtained after implementing our ePLC in a "soft" design flow as described in [14]. In Chapter 5, an alternative approach similar to work presented in [01][68][69] which requires the design and implementation of architecture-specific tactical cells is explored. The details of design and implementation issues related to this work are presented. Next, our results are compared with earlier results obtained using architectures and approaches described in [14][15][68].

Chapter 6 compares the results obtained in Chapter 5 with estimates for commercial hard eFPGAs [41], to illustrate key problems related to current design approaches. In addition, two blocks in a Bluetooth baseband SoC are used to investigate the impact of eFPGA cores on area. Finally, a novel design paradigm, for automatic embedded programmable logic generation is presented.

Chapter 7 summarizes the work presented, suggests topics for future work and lists contributions.

# Chapter 2

## **Background and Related Previous Research**

This chapter begins with a general overview of logic design methodologies and then focuses on programmable logic design. In particular, two commercial technologies for embedded programmable logic design are described. The description focuses on important features of both approaches and highlights their advantages and disadvantages. Next, a wireless SoC platform is used to illustrate potential applications of programmable logic in IC design. Also, issues related to different methodologies for *re*programmable logic implementation are discussed. Finally, a description of the research problem and an outline of the focus of this thesis report are presented.

## 2.1 Overview of Integrated Circuit (IC) Design Techniques

Over the last three decades, several logic design methodologies have evolved to cope with technological advancements in semiconductor circuit design. As shown in Figure 2.1, these methodologies tend to fall into two main groups: full-custom and semi-custom IC design methods.

Full-custom design relies to a large extent on manual effort for most design decisions. For example, design decisions such as transistor sizing, transistor layout, device placement and routing are all carried out manually with the aid of rudimentary Computer-Aided Design (CAD) tools. This technique offers the greatest flexibility from a designer perspective, because circuits can be tailored to specifications with superior performance in terms of area, delay or power. However, there is a high engineering cost overhead involved. Furthermore, given shrinking time-to-market windows and

shelf-life of IC products, it becomes more difficult to depend on full-custom techniques for IC design. For example, a large IC design house like Intel® requires large teams of designers working for the equivalent of hundreds of man-years to deliver high-performance full-custom products such as the Pentium® chip on schedule. This results in a huge expense that has an impact on the pricing of such chips and the products that use them (e.g., personal computers). Similarly, well-known programmable logic device vendors like Xilinx® and Altera®, use full-custom techniques to design their Field Programmable Gate Array (FPGA) devices, and this is part of the reason some of these devices can cost anywhere from a few hundred dollars to a few thousand dollars per chip.

Figure 2.1: A general overview of existing integrated circuit design techniques

In order to reduce engineering effort of full-custom IC designs, some vendors resort to semi-custom design techniques to deliver new products much faster and at lower cost. Semi-custom design relies more on automated flows and Electronic Design Automation (EDA) tools to implement circuits. These EDA tools use libraries of pre-designed logic cells, blocks, and or cores to implement circuits in much shorter time but with some overhead costs, and certain restrictions on the IC designer.

Some examples of semi-custom design include: cell-based, block-based and or core-based ICs. However, it is important to notice from Figure 2.1 that semi-custom designs do have elements of full-custom design and vice-versa. In other words, some components like cells, blocks, or cores in a semi-custom design, are implemented using full-custom techniques to some degree. The extent to which this "crossover" occurs depends upon performance requirements and time-to-market constraints. Furthermore, full-custom designs can also make use of cells, blocks and cores as needed.

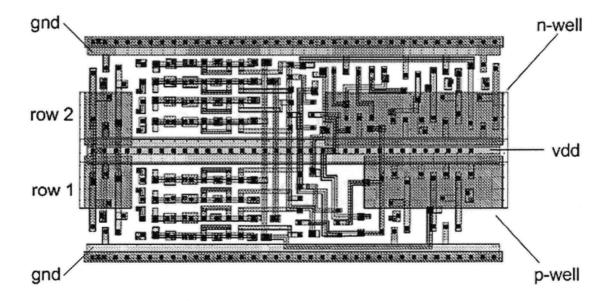

In standard-cell-based semi-custom designs, vendors develop cell libraries that implement generic logic gates such as NORs and NANDs with different drive strengths and in accordance with a constrained physical layout format. These libraries of logic gates are supplied to designers who then map Register Transfer Level (RTL) descriptions of desired hardware behavior written in VHDL or Verilog, into gates using logic synthesis tools such as Design Compiler® and Cadence-PKS®. A more aggressive form of cell-based design allows designers to build custom cells and tools according to their own specifications and tailored for a particular circuit or group of circuits [46] [48] [53] [55]. Figure 2.2(a) and 2.3(b) below shows typical standard cell physical layouts. Usually PMOS devices are in the top part of the cell near Vdd and NMOS devices are in the lower part of the cell near Gnd. Figure 2.3(a) and 2.3(b) show a chip implementation of [19] that uses standard cells.

Figure 2.2: Sample generic standard cell layout for two CMOS logic functions

Figure 2.3: Typical standard cell chip layout and a closer view of cell rows in chip

In order to implement the standard cell ASIC shown in Figure 2.3(a), special EDA tools are used for placement and routing. Placement involves reading a net-list of gates generated through logic synthesis and then arranging the corresponding standard cells in rows as shown in Figure 2.3(b). Placement is automated and can be constrained for area and performance. Standard cells are arranged in rows so that power (Vdd) and ground (Gnd) rails of adjacent cells are connected by abutment. Routing tools connect nodes (with metal wires) to implement the desired logic function.

In semi-custom *block-based* designs, vendors implement larger functions like arithmetic logic units (ALUs), multipliers, and adders as blocks that designers can also include in a standard cell design. One reason for doing this is that certain elements in a cell-based design are not efficiently implemented with generic standard cell-based logic gates like NANDs and NORs. Therefore, circuit blocks like ALUs, adders and multipliers would be included in a cell design to improve performance.

In *core-based* designs, vendors implement even larger and more complex circuits called cores, for inclusion with cells and blocks in ICs. The most common cores are microprocessor cores such as the ARM7®, MIPS, and PowerPC® cores. For example, Figure 2.4 shows a Virtex-II Pro® programmable platform IC [72] with an embedded PowerPC® microprocessor core (highlighted).

Figure 2.4: A programmable platform IC with an embedded PowerPC® processor

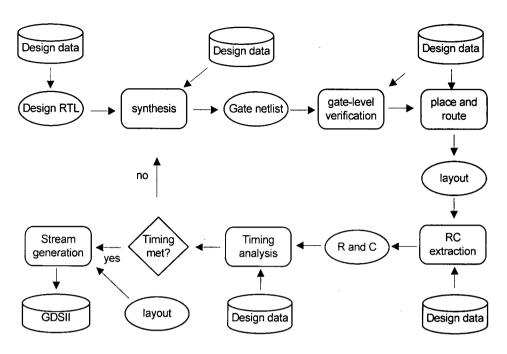

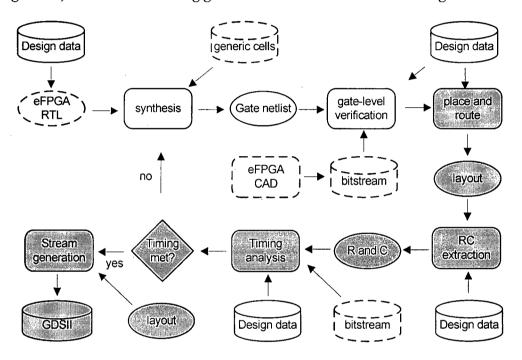

In order to design a *semi-custom* IC, designers often use a flow similar to the one shown in Figure 2.5. This flow is known as the ASIC flow [73]. As shown in Figure 2.5, design data that contains dimensions, timing, drive-strength, and power requirements for cells, blocks, and cores are used in EDA tools at all stages of the design flow. For example, during timing verification, timing and drive strength data for cells, blocks, and cores used in a design are combined with resistance and capacitance values extracted from metal traces after routing, and used to estimate the timing characteristics of all valid signal paths. If a placed and routed design satisfies all timing requirements, it is converted into a special layout file format called GDSII. A GDSII file contains all the design data required to manufacture a chip. If a design does not meet timing, a new and improved net-list must be created, placed, routed and again verified for timing until design goals are met (Figure 2.5).

Figure 2.5: Typical flow for semi-custom cell, block, and core based ASIC design

Full-custom cell, block, and core based design flows includes most of the steps shown in Figure 2.5. Designs are created and tested at the transistor level via circuit schematics and analog simulations. In addition, full-custom designs are often hierarchical and structured so that complex circuit designs can be better managed and optimized. Designers often begin full-custom designs by first building cell-like entities that are then combined to form larger structures like blocks and cores. Placement of cells, blocks and cores relative to one another is done manually along with routing of interconnects. Manual place and route often gives the best results but it is very time consuming. Microprocessor chips and programmable logic devices are often designed in this manner. For example, programmable logic devices like FPGAs, are built from a single, highly-optimized full-custom programmable logic block or tile, that is replicated to form a two-dimensional logic array.

## 2.2 Embedded Programmable Logic IC Design Techniques

Programmable logic ICs in the form of Field Programmable Gate Arrays (FPGA) have been available for over two decades. In the last few years, there has been a push to develop embedded FPGA cores that reside in a chip alongside hardwired or fixed logic. The idea is that the exact logic function of a programmable core can be defined after fabrication, much like any stand-alone FPGA.

The advantages of this approach include the ability to cater to multiple customers with a single programmable chip, accommodate changes in standards or design specifications, or allow designers to fix design errors that are caught after chip tape-out (if they are suitable for correction by the embedded FPGA). An embedded FPGA or *programmable fabric* is usually arranged as a structured array of logic blocks, switches and routing tracks. A logic function is implemented on the array by using SRAM cells set to 0 or 1 to define logic functionality as well as define routing connections.

While programmable fabrics afford designers a tremendous amount of flexibility, there is significant overhead associated with this approach when compared to fixed logic (hardwired) ASICs. Specifically, the area of programmable fabrics can be 50 to 100 times higher, speeds can be 2 to 10 times worse, and power dissipation is substantially higher. Over the past few years, the creation of efficient programmable logic cores has been an active area of research and development in an effort to reduce overhead, improve ease of use, and make this option more attractive to chip designers.

So far, leading approaches for embedded programmable logic implementation include embedded Field Programmable Gate Arrays (eFPGAs) [08] [41] [44] and Mask Programmable Gate Arrays (MPGAs) [45] [60]. This section presents a general architectural overview of programmable logic

devices within an eFPGA context, followed by a general description of MPGAs. The important features of each technology are emphasized, as well as their associated advantages and disadvantages.

### 2.2.1 Embedded Field Programmable Gate Array (eFPGA)

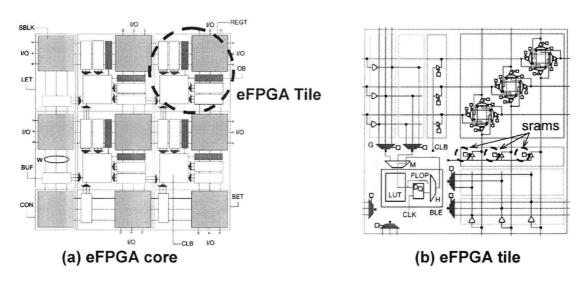

In this section, an overview of the popular island-style FPGA architecture [11] is presented. This architecture (Figure 2.6) is the basis for many commercial programmable logic devices used today.

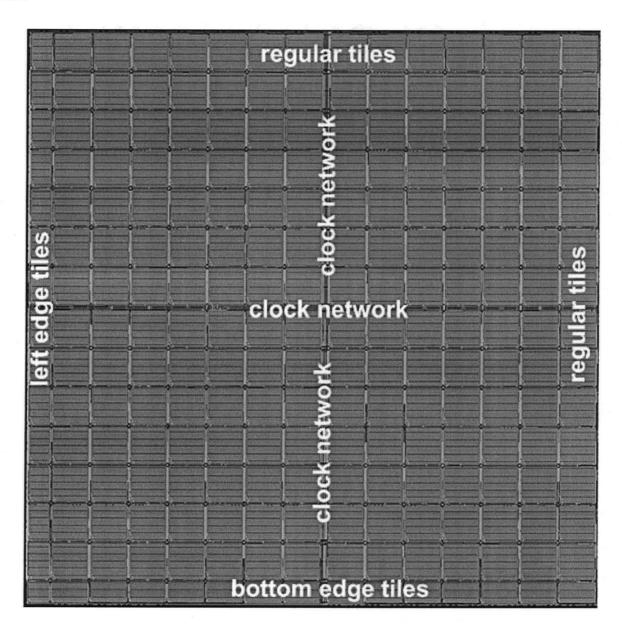

Figure 2.6: 2x2 island style eFPGA core architecture and regular tile architecture

In Figure 2.6(a), CLB is a configurable logic block, SBLK is a routing switch block, LET is a left edge tile, BET is a bottom edge tile, CON is a corner tile, REGT is a regular tile, BUF contains track buffers for input connection blocks, and OB is an output connection block. Also, Figure 2.6(a) shows an eFPGA core as a structured array of logic clusters, switches and routing tracks of width W. The enlargement in Figure 2.6(b) shows that each regular tile contains a CLB, a switch block, connection blocks and SRAM cells for configuration. The left and bottom edge tiles only contain switch-blocks and connection blocks for routing. The corner tile connects the LETs and BETs.

Because logic blocks implement logic functions, they constitute the *logic architecture* of a programmable fabric. Similarly, switch blocks and connection blocks constitute the *routing architecture* because they route signals between tiles, and between the eFPGA and external logic via I/O ports. SRAMs and decoders constitute the *configuration architecture* since they configure the fabric. In essence, programmable logic devices are a combination of logic, routing, and configuration architectures.

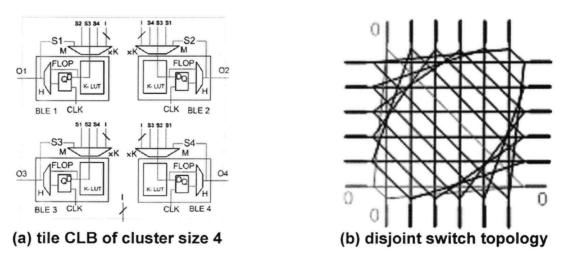

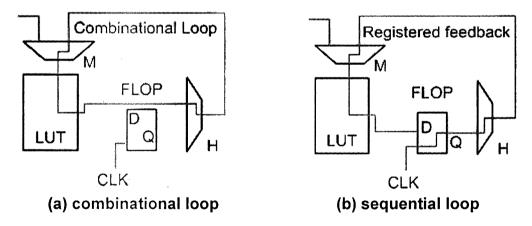

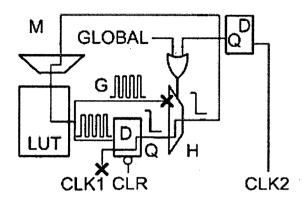

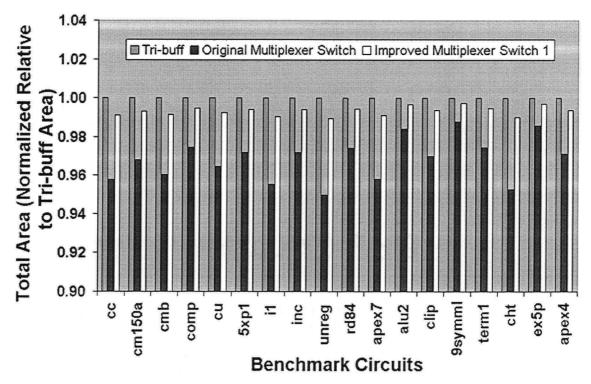

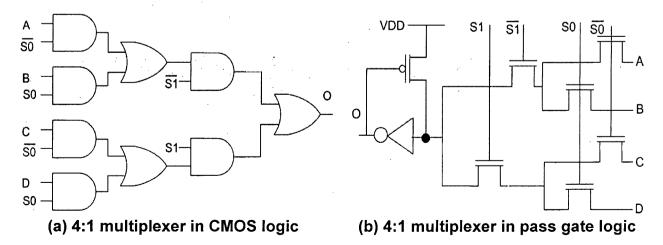

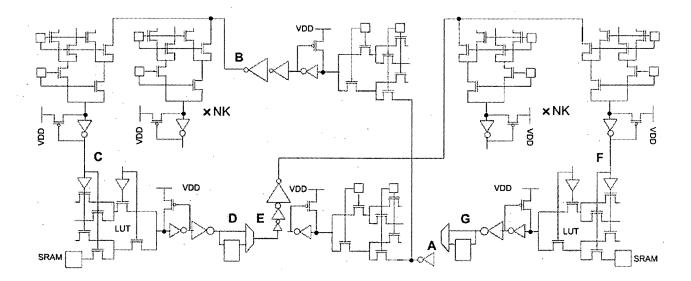

Within the logic architecture, CLBs comprise one or more basic logic elements (BLEs). The number of BLEs in a CLB is its cluster size, N. For example, in Figure 2.7(a) the cluster size is 4. Each BLE in a CLB is comprised of a K-input look-up-table (K-LUT), an edge-triggered flop (LUT-flop) to generate a registered copy of the LUT output, and an output selection multiplexer ("H" in Figure 2.6(b)) to select between registered and unregistered LUT outputs. LUT input multiplexers ("M" in Figure 2.7(a)) are used to drive K inputs of all N LUTs in a CLB of size N (4 in this example).

Figure 2.7: programmable logic CLB of size 4 and a disjoint switch block topology

The switch block design of the routing architecture is typically based on a disjoint topology [11] as shown in Figure 2.7(b). This means a given net cannot hop between track "lanes". For example, a net that enters a switch on routing track 0 as shown in Figure 2.7(b) will exit and continue on track 0

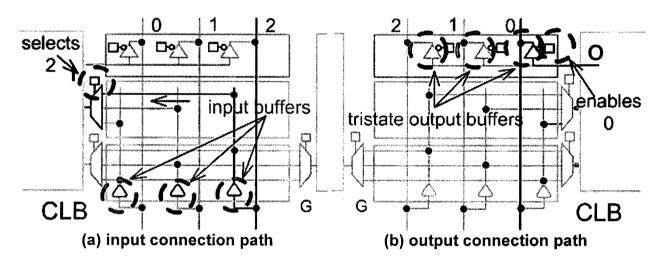

until it terminates. Connection blocks connect CLB inputs and outputs to adjacent routing channels. For example, in Figure 2.8(a) an input connection block multiplexer, G, selects a net from track "2" in the routing channel to drive a cluster input I (the input track buffers are used to minimize loading). Output connection blocks drive cluster outputs (O in Figure 2.8) onto the routing channel. An output connection block has a tri-state driver for each track that it can drive. The value in the SRAM on the enable input of the tristate-driver determines whether or not a routing track is driven.

Figure 2.8: Input and output connection blocks in the eFPGA routing architecture

The configuration architecture includes configuration SRAMs, decoders, and a configuration finite state machine. A row decoder selects a row in Figure 2.6a for programming, and combined with the column decoder, can select a single tile for programming. A state machine controls configuration.

The bits (sequence of zeros and ones) needed to configure a programmable logic device are generated using specialized CAD tools such as VPR [11]. The details of this tool are outside the scope of this work. However, at a high level, these CAD tools contain detailed models of programmable logic architectures like the one shown in Figure 2.6. These models are used to decide suitable placements for circuits that have been mapped into LUTs [11]. Once a suitable placement

for a circuit is found, it is routed [11]. FPGA routing involves finding suitable paths between all the connected nodes (sources and sinks)in a circuit implementation given the available routing resources in the target programmable logic device and any user-supplied path timing constraints.

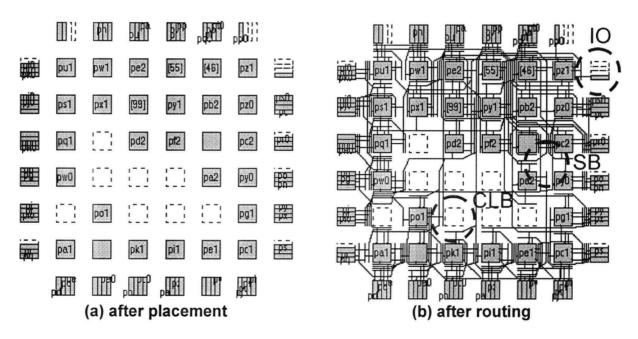

Figure 2.9(a) shows a VPR screen capture of a 6x6 programmable logic device after placement. The darker blocks represent occupied logic clusters. Figure 2.9(b) shows the same architecture after routing. Figure 2.9(b) shows just routing tracks that are used. Placement and routing files for a given circuit implementation are generated within VPR and used in software programs that generate the appropriate sequence of zeros and ones needed to program a circuit on a programmable device.

Figure 2.9:VPR placement and routing of a sample user circuit in a 6x6 logic array

An eFPGA is essentially an unpackaged standalone FPGA (Figure 2.9) that has been stripped of its I/O pad ring and adapted to function as an embeddable IP core. Like a standalone FPGA, the exact logic function of the eFPGA can be decided after fabrication. Typically, an eFPGA would be used to implement small to medium logic functions like microprocessor accelerator functions or hardware data encryption algorithms that need to be reprogrammed periodically to adapt to changes.

### 2.2.2 Embedded Mask Programmable Gate Array (MPGA)

More recently, MPGA devices like the eASIC® core [45] were introduced to eliminate some of the shortcomings of eFPGA cores. An eASIC core is modeled on SRAM programmable look-up-tables but the routing infrastructure between look-up-tables is quite different from eFPGAs. In particular, the routing interconnect is either metal/via or just via programmable (one-time programmable). The advantage here is that the extra logic needed for switch elements in the routing of a typical eFPGA are no longer required. Therefore MPGAs tend to be are smaller, faster and more power efficient.

Furthermore, the wafers associated with a particular design can be processed in advance of final metal/via programming. Therefore, the turnaround time for a programmed design is only about a week or two compared to a few months for so-called hardwired ASICs that are not programmable.

Although current MPGA cores are denser, faster, and more power efficient than an eFPGA, there is a loss of flexibility because the routing interconnect is not *re*programmable. For example, once via connections between metal layers for a particular circuit implementation are made, they cannot be changed. Any further changes to the routing interconnect will require a new silicon die with an unprogrammed embedded MPGA. Although changes in LUT functionality is possible (reprogrammable SRAMs), the scope of such changes is limited once the routing has been finalized.

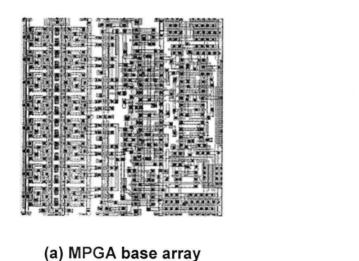

Figure 2.10(a) below shows a transistor-level full-custom layout of an MPGA tile [45] modeled on the popular island-style architecture, and similar in many respects to the eFPGA tile shown in Figure 2.6(b). For example, the LUTs in an MPGA CLB are also programmable using SRAMs. The main difference however, is the absence of reprogrammable routing switches in the MPGA tile. Instead,

an upper metal layer grid of potential global routing connections is used to form an interconnect mesh or *connectivity fabric* [45] as Figure 2.10(b) shows. After fabrication, this grid has no connection to lower layers of metal. Instead connections are only made after it has been determined what circuit will be implemented in the MPGA, and which connections to the lower metal layers (hardwired) will be needed to implement a logic function. Such connections are made with a via mask layer that connects the uncommitted connectivity fabric to the hardwired "base array" [45] in Figure 2.10(a).

(b) Connectivity Fabric

Figure 2.10: A MPGA logic tile layout, and a connectivity fabric of top metal layers

Table 2.1: Comparison of eFPGA, MPGA and standard cell logic design methods

| 0.18 micron CMOS    | eFPGA | MPGA(eASIC®) | Standard Cell IC |

|---------------------|-------|--------------|------------------|

| Density (gate/mm²)  | 1.5K  | 30K          | 60K              |

| Performance(MHz)    | 100   | 400          | 600              |

| Power(nW/Gate/MHz)  | 1000  | 40           | 20-30            |

| NRE (\$)            | 0     | 30K          | 500K             |

| Prototype TAT(days) | 0     | 5-10         | 20-40            |

Table 2.1 [45], presents useful data on key features of eFPGA and MPGA technology that further illustrates important differences between these embedded programmable logic solutions. For example, the absence of reprogrammable routing in MPGAs makes them 20 times smaller than an

eFPGA of the same logic size. The Non-Recurring Engineering (NRE) costs and development turn-around-times (TAT) for an eFPGA is more or less zero because a designer simply needs to load the appropriate bitstream to get a working chip. On the other hand, designs with MPGA cores require one or two metal and or via mask sets to program a core. In this case, IC manufacturing services are needed and accounts for the NRE and TAT overhead. The NRE costs and TAT for standard cell IC (non-programmable) designs are even higher because all IC layers must be fabricated to realize a working chip. However, standard cell IC designs have superior area, speed, and power efficiency.

An MPGA offers "static" or one-time programmability that is suited to designs that do *not* require "on the fly" reprogrammability for bug fixes, or hardware adaptability to changing standards. For designers, who require reprogrammability, the eFPGA is a better design choice, but as already mentioned there are large area, performance, and power issues associated with this design approach.

## 2.2.3 Example Application: Bluetooth Base-band System-on-Chip

To illustrate potential applications of eFPGA and MPGA cores in a real chip design, we use a Bluetooth SoC platform to show on-chip components that could be made hardware programmable.

Bluetooth is another name for the IEEE standard, 802.15, a 2.4GHz wireless radio frequency (RF) communication protocol with an operational range of about 10–100 meters. A Bluetooth SoC platform implements hardware and software components of the Bluetooth protocol as specified by the Bluetooth Special Interest Group (SIG) [74]. As in most wireless SoCs, the Bluetooth SoC has a microprocessor core, interface peripherals such as General Purpose I/O (GPIO), system buses, radio

codecs, an RF interface and a dedicated ASIC core that implements the Bluetooth baseband protocol. When fully implemented this SoC is a multi-million-transistor IC design with over 200 I/O pins.

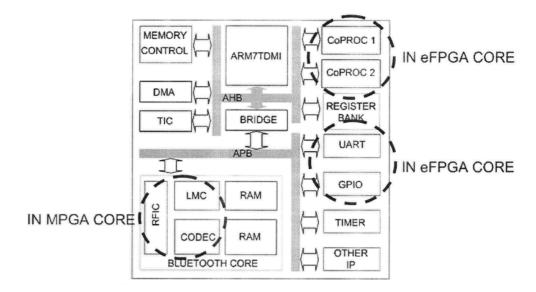

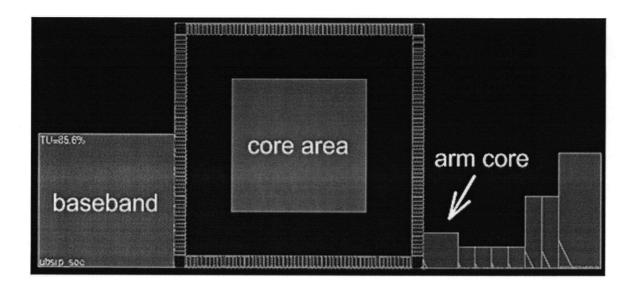

Figure 2.11: A System-on-a-Chip platform that implements the Bluetooth Protocol

Figure 2.11 above shows a typical system level illustration of a Bluetooth SoC design. In this figure, the larger blocks in the Baseband, such as the Link Management Controller (LMC), Radio Frequency Interface Controller (RFIC), or radio encoder-decoder (CODEC) could be replaced with one MPGA fabric. The LMC is a good candidate for programmability, because it changes as the Bluetooth standard is revised. Furthermore, the RFIC and radio CODEC implementation depends on the RF front-end chip and radio that a customer supports and so should also be adaptable. MPGAs facilitate standards revisions and or product differentiation for customers because stockpiles of unprogrammed chip die can be produced and then later programmed and repackaged as needed. Using an eFPGA in this case would result in an unacceptably high area, power and speed penalty. Instead, eFPGAs are best suited to small and medium functions like processor accelerators, also known as coprocessors (CoPROC1 and CoPROC2 in Figure 2.11) and perhaps low speed I/O protocols such as General Purpose I/O (GPIO) and Universal Asynchronous Receiver Transmitter

(UART). Accelerator eFPGAs can be used to speedup execution of parts of the Bluetooth software Protocol Stack and I/O eFPGAs can be used to implement updated communication protocols.

## 2.3 Embedded Programmable Logic as an Intellectual Property (IP)

SoCs (like the Bluetooth chip) are not designed entirely by a single design team; instead, parts of the chip are comprised of Intellectual Property (IP) obtained from third-party vendors. In other words, parts of, and in some cases, the entire SoC, could be designed with in-house or third-party IP. The aim of this paradigm shift, sometimes called the SoC revolution [07], is to boost productivity through IP reuse. Productivity gains for derivative designs come from the ability to incorporate pre-designed and pre-verified IP like MPGA and eFPGA cores, into new designs relatively quickly.

In the IC design industry, there currently exists one way of embedding hardware programmable logic in a SoC design such as the Bluetooth IC of Figure 2.11, namely, as hard Intellectual Property or hard IP [41][44]. More recently in [02][14], a somewhat new approach for embedded programmable logic design that was first used in [01], was introduced as soft Intellectual Property or soft IP. Since the focus of the rest of this thesis will be on embedded FPGA design, the following sections, describe the hard and soft IP approaches within an embedded FPGA design context.

#### 2.3.1 Hard eFPGA IP

The current approach for eFPGA usage is to purchase a core as a hard IP block from a vendor and integrate the block into the design flow with the rest of the design circuitry. Hard IP implies that the user cannot change the eFPGA design in any way because physical dimensions, speed, power

efficiency, and other characteristics are already fixed. The major advantage of this approach is that the user does not need to design and build the programmable core or fabric, because a vendor has already pre-designed a number of fabrics of differing sizes using structured, full-custom layout techniques. Full-custom design techniques ensure that every hard eFPGA core is highly optimized.

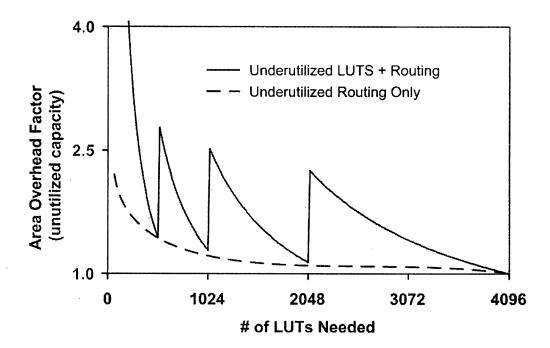

However, in an effort to reduce design and support costs, hard eFPGA vendors offer as few variations of the eFPGA core as possible. As a result, there are numerous sources of inefficiency or underutilization. First, vendors typically offer a single eFPGA architecture that may not be ideal for a particular application. Second, some eFPGA architectural parameters, such as the number of inputs to a LUT, are determined by implementing a large number of proprietary benchmark circuits and "choosing the one which gives the best performance on average". While this approach makes sense for potentially broad ranges of applications, it is not necessarily the best approach for a specific application domain. Third, for a given architecture, the vendor can only offer a limited selection of logic capacity or core sizes. For example, Actel's Varicore [44] is offered only in sizes of 512, 1024, 2048, and 4096 four-input LUT. As a result, if the logic gate requirements just slightly exceed a given core size, the user must buy the next-largest core which is 2x larger. Fourth, the smaller eFPGA cores are sometimes based on the same "layout tile" as the larger cores, leading to unnecessary interconnect (routing) capacity for core sizes with fewer LUTs and logic capacity.

To illustrate these last two problems, the area overhead arising from having too many LUTs and too many wires is shown in Figure 2.12. The x-axis is the desired number of LUTs for a given application. The y-axis is the overhead or how much larger than necessary the smallest available hard eFPGA core is with logic and routing considered. As the number of LUTs needed increases along the x-axis (including any spare LUTs the user may wish to reserve), the overhead decreases. Once

the logic capacity of a given core size is reached, e.g., 512 LUTs, the overhead drops to 1.5X (now due to routing overhead only). However, if more LUTs are needed, the next larger size of eFPGA is needed and the overhead jumps to almost 2.8X. The saw-tooth pattern in Figure 2.12 is repeated as each eFPGA core size becomes fully utilized and the next larger eFPGA core size is selected.

Figure 2.12: An example of architectural inefficiencies in existing hard eFPGA IP

#### 2.3.2 Soft eFPGA IP

Given the disadvantages of the hard IP approach, an efficient and less restrictive approach would be preferable. A relatively new approach has been used to automatically generate an eFPGA fabric within the ASIC design flow [01][02][15]. This is referred to as the soft PLC [02] [14] approach. The main idea here is that an eFPGA architecture is described in behavioral RTL using Verilog or VHDL, and implemented alongside the rest of the user logic. Users implement the eFPGA using logic synthesis tools that map the behavioral RTL to a standard cell library within the ASIC design

flow. ASIC place and route is performed as usual to create the physical IC layout. The main advantages of this approach are flexibility and ease of use. Furthermore, this approach does not restrict a designer to certain foundries, as may sometimes be the case with hard eFPGA cores.

Although the soft IP approach affords a designer much flexibility, significant inefficiencies exist in this approach. For example, because this flow relies exclusively on logic synthesis for technology mapping (mapping of RTL constructs to logic gates in a standard cell library) some elements of the architecture are not efficiently built. For example, SRAMs that are used to hold program bits in an FPGA do not exist in standard cell libraries and so flip-flops (much larger cells) are used instead. Similarly, multiplexers for implementing LUTs and other large multiplexers in an eFPGA architecture are built from discrete CMOS logic gates like NANDs and NORs. As a result of these logic implementation inefficiencies in soft IP, significant overheads in area, delay, and power occur.

Furthermore, there is no structure or regularity imposed during logic synthesis or layout of soft eFPGA cores [02]. Consequently, it is possible that even identical repeated structures in the layout have different path delays [14]. This is not necessarily a flaw, but it makes timing characterization of eFPGA CAD tools more difficult. The tools and flow are made more complex because each timing arc in the architecture must now be considered separately. In addition, wires may be longer than necessary and thus increase delay. This is in contrast with the hard eFPGA IP approach that uses architectures with well-defined repeated structures to simplify physical layout and CAD tool design.

Finally, although the flexibility and ease-of-use afforded by the "soft" eFPGA [02] [14] [15] design methodology is highly desirable, design improvements that minimize the area, delay and power overhead [01] [02] [14] associated with standard cell based embedded FPGAs are clearly needed.

### 2.4 Research Problem Definition and Thesis Research Focus

Following from preceding descriptions, hard and soft eFPGA IP design methodologies can be viewed as two separate extremes of a design spectrum. On one extreme lies the hard eFPGA IP methodology, based on full-custom design and with *limited flexibility* but *relatively* high density, speed, and energy efficiency. On the other extreme is soft IP, which affords ample flexibility (due to a semi-custom ASIC flow) but has much lower density, speed and energy efficiency relative to hard eFPGA IP. Given these problems with both approaches, an optimum solution should aim to combine their best features by: retaining the design flexibility afforded through design automation (e.g. ASIC flow), and, at the same time, incurring significantly less area, speed and power overheads.

Following from the above problem description, the focus of this research is to investigate possible improvements in the quality (area, speed and power efficiency) of eFPGA circuits implemented within an automated design framework. An automated framework such as the ASIC flow ensures that the flexibility afforded by the soft IP approach is preserved. In addition, it has previously been shown that the quality of standard-cell-based designs implemented with the ASIC flow can be improved significantly through customization. For example, a study in [46] showed that the replacement of generic standard cells with so-called "crafted" (architecture specific) standard cells in a datapath circuit design reduced area and delay overhead factors to within 1.64 and 1.11 respectively relative to an identical full-custom implementation. Furthermore, in [27] [68] [69] [70], an area overhead factor of 1.36 relative to a full-custom implementation was reported using a flow similar to the ASIC flow but instead using custom designed "FPGA-centric" EDA tools and non-standard custom cells.

In this work, the ASIC flow is also used for eFPGA design and implementation. For this research, an island-style programmable logic architecture has been selected as the reference platform because such a choice has numerous benefits. For example, this architecture is the basis for most of the programmable logic devices in use today, hence comparisons to commercial (full-custom) devices are more relevant. Similarly, the CAD tools for this type of architecture are more widespread and mature (e.g., VPR tool) hence, they can be leveraged directly without any need for new CAD tools.

Next, the impact of tactical architecture-specific cells on the design quality of standard-cell-based eFPGAs is investigated. In particular, after the island-style architecture has been implemented using generic standard cells and the ASIC digital design flow, key sources of area, speed, and power inefficiency are identified and improved through circuit design and customization. This involves creating new standard cells called tactical cells that can be incorporated in the ASIC design flow.

Furthermore, the implications of such an approach (as described above) for eFPGA IP design are investigated. Specifically, design results obtained for a set of benchmarks are compared with results that would be obtained if the same benchmarks were implemented using the hard IP approach. In addition, two modules in an actual Bluetooth Baseband SoC, namely, the base-band *frequency* hopping module and data encryption module are implemented in a standard-cell-based eFPGA. This study gives an idea of the impact these eFPGAs can have on the area of a "real-world" design.

Finally, the ASIC flow was chosen for this research because it was decided that it would be useful to fully investigate the appropriateness of existing ASIC tools for eFPGA design before embarking on the expensive process of designing a new set of EDA tools for automatic eFPGA circuit generation.

## Chapter 3

## An Embedded Programmable Logic Architecture Family

### 3.1 Island-Style eFPGA Architectures

Any eFPGA design approach that is flexible (like the soft approach) must include a basic architecture that is configurable. The popular island-style architecture provides such an opportunity. Therefore, in order to explore the impact of configurable architectures on eFPGA IP design, this chapter describes some variations of the island-style architecture so that area and speed tradeoffs can be investigated over a set of benchmarks. The goal here is not necessarily to design the "best" architecture because this is to some extent a function of the application domain [01][03]. However, there are cases where there exists a clear advantage of one architecture over another. For example, data in [20] suggests that the area of LUT-based island FPGA architectures could be improved by making the routing interconnect directional rather than bidirectional. Implementing this, and other potential eFPGA architectures, is beyond the scope of current work since we focus on block-level (lower level) architecture optimizations. Architecture optimizations of the kind presented in [20] are left to future research work. Consequently, the eFPGA architectures presented in the following subsections are really derivative architectures of the well-known island-style FPGA architecture.

The research work presented in this section focuses on switch element circuit design (switch block design) as well as resolving some problems normally associated with programmable logic design and implementation, such as I/O design, design for testability issues, and power-up issues. The purpose of revisiting some of these issues is to determine if any improvements can be made with

better circuit design. In addition, the total cost and overhead due to these architecture components can be properly assessed when more typical design considerations are taken into full account.

#### 3.1.1 Bidirectional Routing Architectures for eFPGA design

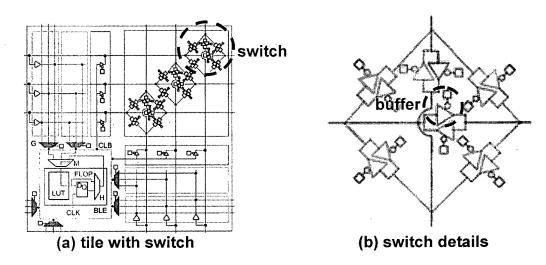

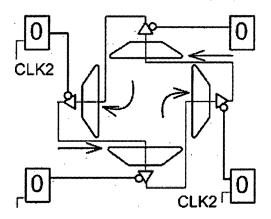

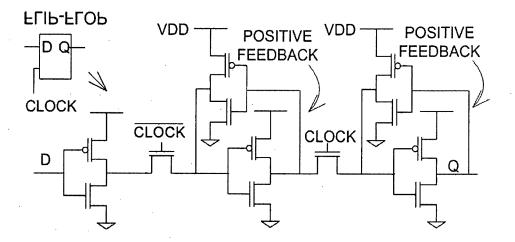

In this section, four derivative architectures with bidirectional routing tracks are presented. The architectures differ only in the switch used in the switch-block. These architectures are suitable for implementing sequential and combinational circuits. The first architecture uses tri-stated routing switches [11]; the second uses a multiplexed switch from [49], the third and fourth are based on novel multiplexed switches that were designed to improve the speed of the original design from [49].

Figure 3.1(a) shows a tile architecture based on tri-state routing switches [11][49]. As the enlarged Figure 3.1(b) shows, each potential net route is controlled by a tri-state buffer pair. If a net is routed from left to right across a switch, only one of two tri-state buffers (highlighted by the circle in Figure 3.1(b)) in that path can be turned on or enabled. The other buffer must remain turned off or else a local combinational feedback loop will be created. Therefore, for every active route through the switch, only one tri-state buffer is turned on. If no net is routed, both buffers in a pair are disabled.

Figure 3.1: An island style eFPGA tile architecture with tri-stated routing switches

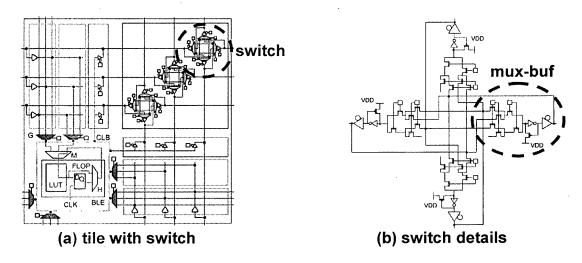

The *logic* architecture of the second derivative architecture shown in Figure 3.2(a) is identical to the tri-buffered island architecture in Figure 3.1(a). However, the routing architecture is based on the multiplexed-switch presented in [49]. Each of the four multiplexers in this switch element routes a net from *one* of *three* possible inputs to a *fourth* and different direction. For example, in Figure 3.2(b), a multiplexer and buffer pair (mux-buf) on the right side of the switch element (highlighted by the circle in Figure 3.2(b)) can route nets from either the bottom, left, or topside of the switch to the right output. The unused (floating) multiplexer inputs in Figure 3.2(b) can be tied to ground [20].

Figure 3.2: Island style eFPGA tile architecture with multiplexed routing switches

Figure 3.2(b) also shows that a net routed from left to right (or from any of the other two valid sources) must traverse two levels of a pass transistor tree network and buffers before exiting. When compared to the tri-buffered switch presented earlier, this architecture would have a higher delay overhead due to the NMOS pass-transistor multiplexing logic. However, previous work [49] showed this design to be more area efficient. These tradeoffs are examined further in the next chapter.

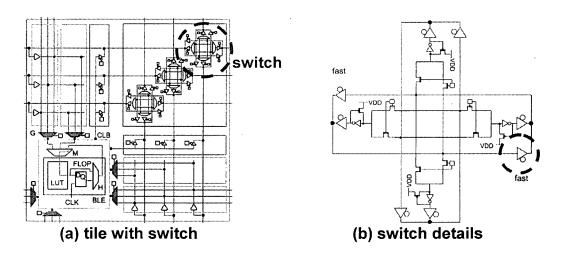

The architecture in Figure 3.3(a) is based on a novel switch element called "Improved multiplexer switch 1". It is similar to the original multiplexed switch presented earlier but with some important modifications. As in the previous design, each of the four multiplexers in this switch routes a signal from one of three possible directions to a fourth direction. The difference here is that nets routed from left to right (or vice-versa) and from top to bottom (or vice-versa) across a switch are faster because multiplexing logic is bypassed. Therefore, any critical nets that are routed vertically or horizontally across several tiles in an eFPGA would have reduced delay. However, there is now an extra tristate buffer for each of the four exit routes in a switch, and this contributes to the switch area overhead.

Figure 3.3: Island style eFPGA tile with improved multiplexed routing switch 1

Figure 3.3(b) shows that a smaller delay overhead would be experienced by a net routed from left to right in the new multiplexed switch compared to the original switch design in Figure 3.2(b). For example, a net routed from left to right across the switch experiences a single tri-state buffer delay (circled in Figure 3.3(b)) by completely bypassing the extra multiplexer delay overhead. The same is true for the reverse route (right to left) and also for vertical routes (top to bottom and reverse). Only routes changing direction (e.g., turning from top to left) incur a multiplexer delay overhead. Furthermore, only a single level multiplexer is used and this results in a smaller delay overhead.

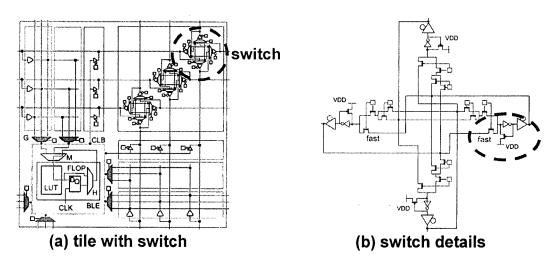

A second novel switch configuration called "Improved multiplexer switch 2" was devised to reduce the area overhead of the previous design and improve the speed of the original multiplexer switch architecture [49]. In the novel tile architecture shown in Figure 3.4(a) below, an attempt is made to combine the area efficiency of the original multiplexer switch design with the speed of "Improved multiplexer switch 2". In particular, it was observed that the speed of the original multiplexed switch could be improved without any area penalty, simply by rearranging internal routes. To achieve this, an "unbalanced" NMOS pass transistor network can be constructed as shown in Figure 3.4(b). Similar to the previous novel switch design, horizontal and vertical routes are connected to the "fast" route through the pass-transistor tree network, thus speeding up these switch routes.

Figure 3.4: Island-style eFPGA tile with improved multiplexed routing switch 2

#### 3.2 Architectural Issues

During architecture specification, a number of practical design issues were considered so that this design could be used in an actual SoC implementation at some point in the future. These issues include I/O design, design-for-testability (DFT) issues and configuration SRAM power-up issues. In the following subsections, each problem is described and possible design solutions are presented.

#### 3.2.1 Input/Output Design

In stand-alone FPGA chips, an I/O pad ring surrounds the programmable core as shown in Figure 2.9. The large size of these pads means that the number of I/O on an FPGA device must be kept somewhat low in order to save area. In embedded FPGAs, these large I/O pads are not needed and therefore more I/O can be included without any significant increase in core area or delay. In fact, eFPGA I/O are simply tiny metal segments around the core edges that serve as "contacts" for external nets. It is important for eFPGA fabrics to be rich in I/O because some applications may be very I/O intensive compared to their logic size. It would be undesirable to select a much larger eFPGA fabric simply to gain access to more I/O. This is a problem that standalone FPGA users sometimes face. Moreover, any unused I/O in the eFPGA adds very little to the area overhead.

In a typical implementation of a generic island style FPGA architecture [11] [13] [49], I/O pads are connected to the channel routing tracks via programmable pass-gates (shown as darkened circles in Figure 3.5(a)). Figure 3.5 is a section of the left edge of the programmable device shown earlier in Figure 2.9 where "pq1" and "pw0" are CLBs. The remainder of the shaded rectangles in the figure such as "pn", and "out:pq1" are input and output pads respectively. The pass-gates used to connect

I/O pads to the routing channel contribute to the area overhead, and their number increases as the number of connections, routing channel width (W), and number of I/O increase. To avoid this, the embedded FPGA I/O need to be redesigned in a more area-efficient manner. Rather than have extra logic like pass gates to connect I/O to routing tracks, the switch-blocks around the edges of the embedded FPGA could be used to implement the I/O. This is possible because some of the logic in switch-blocks around the edges of an FPGA chip are unused (after place and route). For example, Figure 3.5(b) is a section of the *left edge* of the placed and routed device in Figure 2.9(b). In Figure 3.5(b) no nets are routed to the *left* of the switch-block (the switch-block is the region enclosed by dashed lines). Similarly, along the *top edge* of the FPGA (refer back to Figure 2.9(b)), no nets are routed to the *topside* of the switch blocks, and likewise for the bottom and right edges.

Figure 3.5: Programmable I/O pad connections and unused switch connections

As a result, unused "free" routing logic in the switch blocks around the edges of the FPGA could be used for routing I/O. Typically, an external input such as "I" in Figure 3.6(a) would be routed into the tile via the programmable pass-transistor that connects to routing track "2". Similarly, an external output such as "O" would typically be routed through the pass transistor that connects to routing track "0". Assuming that the tile in Figure 3.6(a) is situated on the top edge of an eFPGA

fabric, there would be no reason to route any nets, except external nets, through the top edge of the switch-block. Figure 3.6(b) illustrates how the connectivity for input "I" and output "O" could be implemented using the "free" routing logic along the top edge of a switch. As shown, the external input "I" can be routed from the top port of the switch element that controls routing track "2" because the top port is unused. Further, this signal can exit from the left port of the same switch (see Figure 3.6(b)), since this segment of track is already "reserved" for input "I" in Figure 3.6(a).

Figure 3.6: Equivalent external input routing in standalone and embedded FPGA

Similarly, as shown in Figure 3.6(b) the external output "O", is driven by a net that is routed from the left port of the switch element on routing track 0 to its top port (the external output). This *novel* design approach eliminates the need for the programmable pass-transistors used in Figure 3.6(a) which contribute to the area overhead in standalone FPGAs. In essence the I/O logic in Figure 3.6(a) has been "squeezed" into a single switch block in Figure 3.6(b) due to reuse of "free" routing.

However, the I/O implementation described above places a restriction on the eFPGA architecture. In particular, there can be no overlapping IO connections. For example, as shown in Figure 3.7(a),

in a typical FPGA I/O implementation, external inputs and outputs *can* have overlapping programmable connections to the routing track since both will never be enabled at the same time. Therefore, if input "I" is driven on routing track 1 (via pass gate), then output "O" cannot be driven on track 1 (pass gate is disabled to prevent signal contention). In the new design in Figure 3.7(b), such overlaps would *always* lead to signal contention because there are no programmable pass gates to use to isolate external nets from each other. To see how this occurs, consider that in Figure 3.7(a), "I" can potentially be driven onto tracks 1 and 2, and so in the equivalent novel implementation in Figure 3.7(b), the output of the tri-state on the topside of the switch on track 1, would be "wired" to the output of the tri-state on the topside of the switch on track 2. Regarding output "O" which can connect to track 0 or 1, the outputs of the respective topside tri-states would be "wired" together.

Figure 3.7: A limitation of the novel embedded FPGA external I/O architecture Notice from the above description of the novel I/O implementation in Figure 3.7(b), that "I" and "O" are actually "shorted" due to their shared connection to the output of the tri-state on the topside of the switch on routing track 1. Basically, the outputs of all tri-states circled in Figure 3.7(b) are shorted together so that signals "I" and "O" are driven on all three tracks. This clearly leads to signal contention. Therefore, only non-overlapping connections such as in Figure 3.6 can exist.

#### 3.2.2 Design for Testability

Once a chip with an embedded FPGA is fabricated, it must be tested along with other blocks on the chip. In particular, it should be possible to test the embedded FPGA fabric in isolation, as well as within the context of the chip in which it is embedded. For testing to be successful, the embedded fabric itself must be designed to be testable. Otherwise, it will be difficult to determine whether it functions as expected. Testing an eFPGA core involves testing the logic, routing, and configuration architectures. However, a configuration architecture that is testable is of crucial importance, because if correct eFPGA configuration cannot be assured, then logic and routing architecture tests become meaningless. Therefore, in this work a configuration architecture that is testable has been designed.

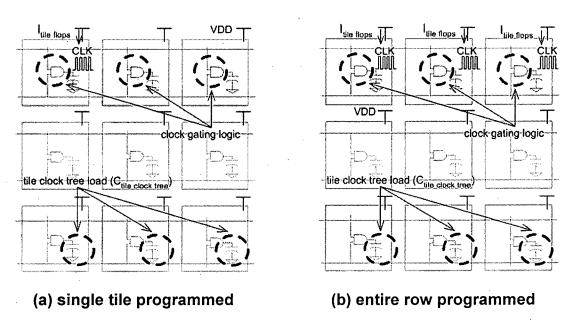

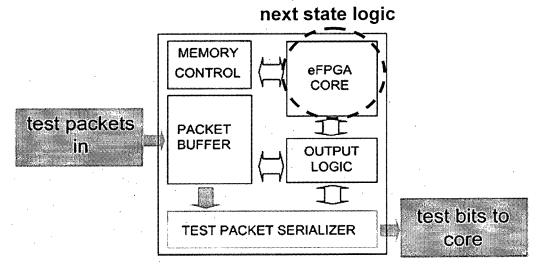

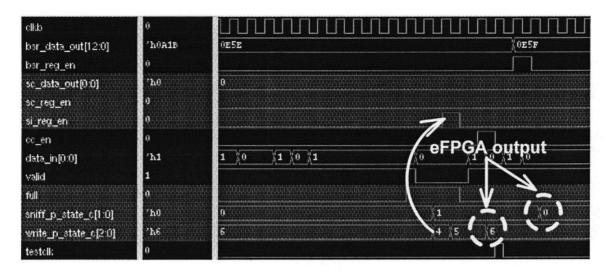

A testable design must be both controllable and observable. Control is needed to put the design under test into a desired state, and observable nodes or outputs are needed for comparison with expected results. Therefore, techniques and structures that facilitate controllability and observability during configuration are necessary. Figure 3.8(a) is a high level illustration of the main parts of a design solution. The serial input (SI) is used to load program and address bits. The address shift register (SR) is used to shift in row and column addresses. Row and column address decoders are used to assert word-lines (WL0, WL1, WL2) and column lines (CL0, CL1, CL2) based on target row and column addresses. Clock gating logic in each tile (not shown) is used to turn on or off clocks to configuration flip-flops based on the target row and column addresses. All configuration flip-flops are also linked in a shift chain that can be routed through a multiplexer to an external output (SO).

Figure 3.8: An embedded FPGA IP configuration architecture designed for test The contents of the address shift register can also be routed to SO. Q1, Q2, and Q3 (highlighted in Figures 3.8(b) and 3.8(d)) are serial outputs of the programming shift chain of their respective rows. Finally, a finite state machine controller (not shown for simplicity) is used to arbitrate configuration.

This architecture facilitates control and observation during testing of the configuration architecture.

For example, a row decoder activates the word-line [56] of a target row of tiles based on a row address, and tile selection logic in each tile (simplified in Figure 3.8(a)) decides which tiles can be targeted for programming. Figure 3.8(b) shows a single row being targeted for programming (top row); hence, only the clock in that row is activated during programming. Individual tiles can also be targeted for programming. Serial outputs from each row (Q1, Q2, Q3) facilitate observation of the configuration bits for correctness because the program bits for each row can be shifted in, and then shifted out and analyzed. Also, SRAM storage cells could be programmed and then read (see Figure 3.8(c)) to ensure proper functionality. A similar approach called read-back is used in commercial SRAM-programmable logic devices [56][57]. Also, the scan output in the proposed architecture, SO, allows the output from the programming shift chain, or address shift register to be analyzed.

To conclude, there are two modes of operation in the proposed configuration architecture: normal mode and fail-safe mode. In normal mode, the finite state machine is functional and program bits can be loaded into tiles individually or in rows. In fail-safe mode, the finite state machine is not functional (also deactivated), and so a single shift chain is used for programming and all shift registers are activated during configuration (Figure 3.8(d)). The output of this shift chain can be observed at SO in fail-safe mode. In essence, this design is robust enough that limited testing of the configuration architecture can still continue even if the configuration state machine is not working.

## 3.2.3 SRAM Power up State

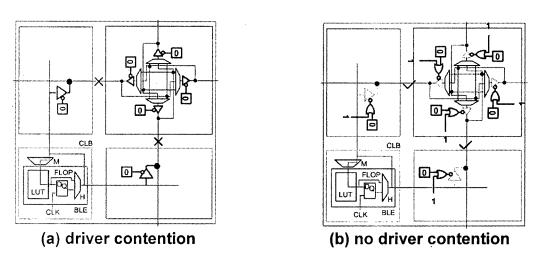

The embedded FPGA architectures used in this research have bidirectional routing, which in our case means there can be multiple potential drivers per routing track. In order to prevent contention, these drivers are tri-stated. Furthermore, after configuration, there can be just one driver per active

(driven) routing track. In other words, the SRAMs or flip-flops that are used to enable or disable these tri-state drivers must hold the appropriate values. However, upon power up, and prior to configuration, it is impossible to know what value the configuration cells (flip-flops or SRAMs) will hold initially [56]. It is important to consider this because a situation could arise where all potential drivers of a tri-stated routing track are enabled and driving opposing logic values on a routing track (denoted by "X" in Figure 3.9(b)). This can create high-current short circuit paths from power to ground through the tri-state devices. Such high current paths through transistors can cause irreversible damage and result in a bad chip (unusable routing tracks). Therefore, as a safeguard, it is necessary to disable all tri-state drivers upon power-up. One possible solution is shown in Figure 3.9(b), where a NOR gate is used to disable all the tri-state drivers upon power-up. One input is set to a high value (depends on the polarity of tri-state enable input) so that when the chip is powered up, this signal is asserted and the tri-state enable logic disables all tri-state buffers. The other input from the SRAM/Flip-flop ("0" input in Figure 3.9(b)) has no control over the tri-state buffer.