# FABRICATING SILICON MESH BOLOMETERS FOR BAM

By

# Karen Chen

B. Sc. (Physics) University of British Columbia, 1997

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

DEPARTMENT OF PHYSICS AND ASTRONOMY

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

February, 2000

© Karen Chen, 2000

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of Physics and Astronomy

The University of British Columbia

6224 Agricultural Road

Vancouver, B.C., Canada

V6T 1Z1

Date:

Feb. 4, 2000.

#### Abstract

Silicon membranes have been fabricated and etched into mesh structures using both wet and  $\text{Cl}_2$  plasma etching. The most repeatable process involoved wet etching triple bonded wafers with a buried oxide layer. A recipe to build Si meshes, with a grid spacing of 375  $\mu$ m and leg cross-sections of 5  $\mu$ m by 30  $\mu$ m, from 5  $\mu$ m thick membranes is described. The meshes are supported by 4 legs that are each 30  $\mu$ m wide and 1 mm long. Also, the resistivity of thin gold films was measured for temperatures ranging from 4.2 K to 300 K. It was found that the ideal thickness, that leads to a sheet resistance of  $188\,\Omega/\Box$  at 300 mK for of 5  $\mu$ m by 385  $\mu$ m gold lines, was 150 Å. A bolometer building process that incorporates the gold evaporations with the mesh building procedure is given, although preliminary attempts to produce bolometers have been unsuccessful.

# **Table of Contents**

| A  | bstra  | et                                  | ii  |

|----|--------|-------------------------------------|-----|

| Ta | able ( | of Contents                         | iii |

| Li | st of  | Tables                              | vi  |

| Li | st of  | Figures                             | vii |

| A  | ckno   | wledgments                          | ix  |

| 1  | Intr   | roduction                           | 1   |

|    | 1.1    | Bolometers                          | 2   |

|    | 1.2    | Impedance Matching to Free Space    | 4   |

|    | 1.3    | Thermal Properties of the Bolometer | 9   |

|    | 1.4    | Responsivity                        | 13  |

|    | 1.5    | Noise                               | 15  |

|    | 1.6    | Bolometer Design and Constraints    | 20  |

| 2  | Sili   | con Micromachining Basics           | 26  |

|    | 2.1    | Photolithography                    | 26  |

|    |        | 2.1.1 A Note on Mask Making         | 29  |

|    | 2.2    | Wet Si Etchants                     | 30  |

|    | 2.3    | Plasma Etching                      | 33  |

|    | 2.4    | Metallization                       | 34  |

|    |       | 2.4.1    | Metal Lift-off Process                              | 36 |

|----|-------|----------|-----------------------------------------------------|----|

| 3  | Fab   | ricatin  | g the Mesh Structure                                | 38 |

|    | 3.1   | Using    | Etch Stop Layers to Form Thin Membranes and Meshes  | 38 |

|    |       | 3.1.1    | Heavily Boron Doped Si                              | 39 |

|    |       | 3.1.2    | Buried Oxide Layer                                  | 44 |

|    | 3.2   | Formi    | ng Mesh Structures via Plasma Etching               | 47 |

|    |       | 3.2.1    | Etching Mesh Structures                             | 48 |

| 4  | Res   | istivity | Measurements of Thin Gold Films                     | 51 |

|    | 4.1   | The R    | esistivity of Thin Metal Films                      | 51 |

|    | 4.2   | Prepar   | ration of Thin Gold Films                           | 53 |

|    |       | 4.2.1    | Preliminary Test Runs                               | 55 |

|    | 4.3   | Au on    | Si                                                  | 58 |

| 5  | Con   | clusio   | ns                                                  | 63 |

|    | 5.1   | First A  | Attempt at Using This Recipe to Build Bolometers    | 66 |

| Bi | bliog | graphy   |                                                     | 72 |

| A  | Clea  | anroon   | n Process Recipes                                   | 75 |

|    | A.1   | RCA (    | Clean *                                             | 75 |

|    | A.2   | Oxida    | tion Recipe for a $0.3 \mu\mathrm{m}$ Oxide Layer * | 76 |

|    | A.3   | Boron    | Diffusion *                                         | 77 |

|    | A.4   | Gener    | al Photolithography *                               | 78 |

|    | A.5   | Metal    | Lift-off **                                         | 79 |

|    | A.6   | The E    | CR PlasmaQuest System *                             | 80 |

|    | Δ7    | Achine   | r Photoresist with the Technics Plasma Etch II      | 81 |

|              | A.8 E-Beam Evaporation Using the Balzers Evaporator ** | 82 |

|--------------|--------------------------------------------------------|----|

|              | A.9 Thermal Evaporation in the BAM Lab Bell Jar        | 83 |

|              | A.10 Anisotropic Si Etch: EDP or TMAH *                | 84 |

|              | A.11 Oxide Etch: HF *                                  | 84 |

| В            | Si Wafers and Processing Chemicals Suppliers           | 85 |

| $\mathbf{C}$ | NTD Ge Thermistors                                     | 86 |

# List of Tables

| 1.1 | Specific Heats of Materials Commonly Used for Bolometers                    | 13 |

|-----|-----------------------------------------------------------------------------|----|

| 1.2 | Thermal conductance to the heat sink at 270 mK                              | 24 |

| 1.3 | Heat capacity of bolometer components at 270 mK                             | 25 |

| 2.1 | Etch rates and selectivity ratios for TMAH and EDP                          | 33 |

| 3.1 | BOX wafer specifications                                                    | 45 |

| 4.1 | Room temperature resistance of thin gold films on two different substrates. | 56 |

| C.1 | Fitted values of R                                                          | 87 |

# List of Figures

| 1.1 | Schematic drawing of the 1998 BAM bolometers                             | 3  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | Infinite transmission line with a resistive short                        | 6  |

| 1.3 | A schematic diagram of the bolometer and the equivalent thermal circuit. | 11 |

| 1.4 | I–V curves for the bolometer used in the 1998 BAM flight                 | 16 |

| 1.5 | Modeling bolometer response to cosmic ray hits                           | 17 |

| 1.6 | Block drawing of bolometer noise sources                                 | 19 |

| 1.7 | The number of cosmic ray hits during the 1995 BAM flight                 | 21 |

| 1.8 | The silicon micromesh bolometer design                                   | 23 |

| 2.1 | Basic steps to photolithography                                          | 27 |

| 2.2 | Bloated lines on masks generated with linotronic films                   | 30 |

| 2.3 | Hole geometries produced from wet etching silicon                        | 31 |

| 2.4 | Metal Lift-off lithography                                               | 37 |

| 3.1 | First free standing mesh made from a heavily doped Si membrane           | 43 |

| 3.2 | Thicker free standing mesh made from a heavily doped Si membrane         | 44 |

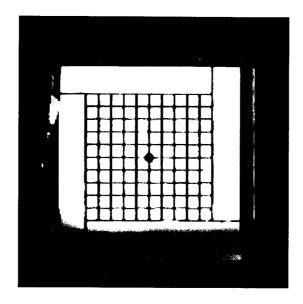

| 3.3 | Free standing mesh made from a $6.5\mu\mathrm{m}$ Si membrane            | 46 |

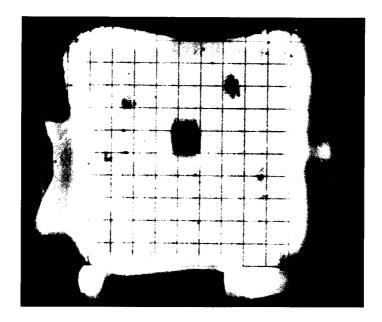

| 3.4 | Free standing mesh plasma etched from a 2.2 $\mu m$ Si membrane          | 50 |

| 4.1 | Gold path for thin film resistivity tests                                | 54 |

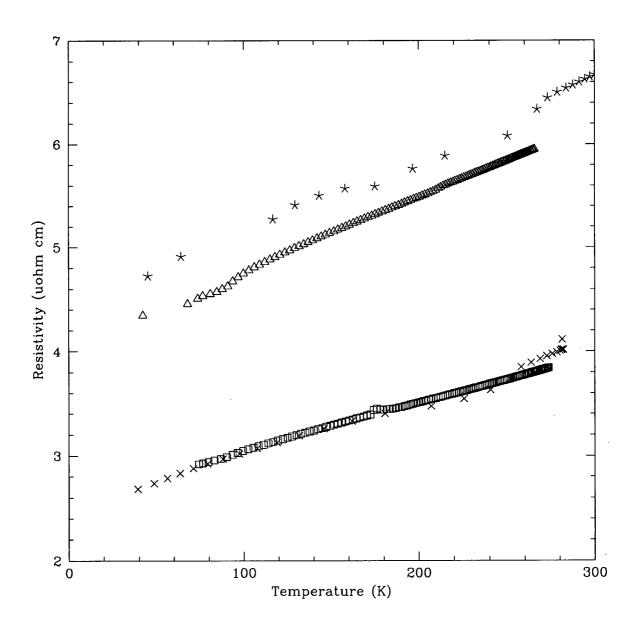

| 4.2 | Resistivity of gold films on different substrates                        | 57 |

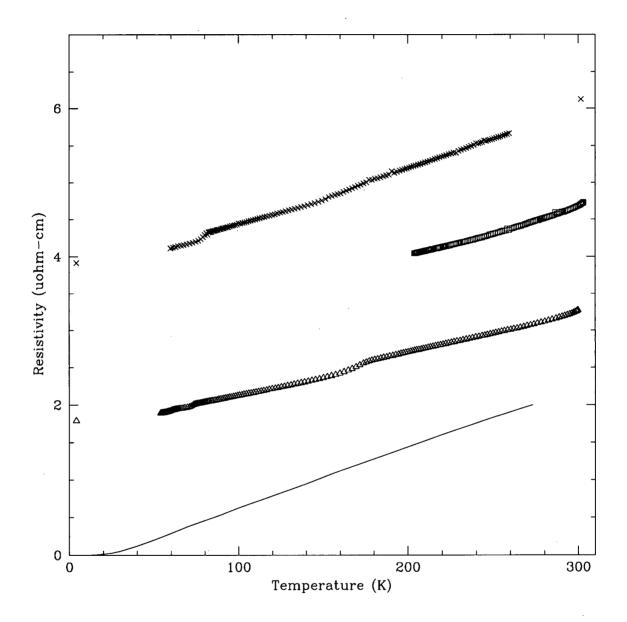

| 4.3 | Resistivity of thin gold films at various temperatures                   | 61 |

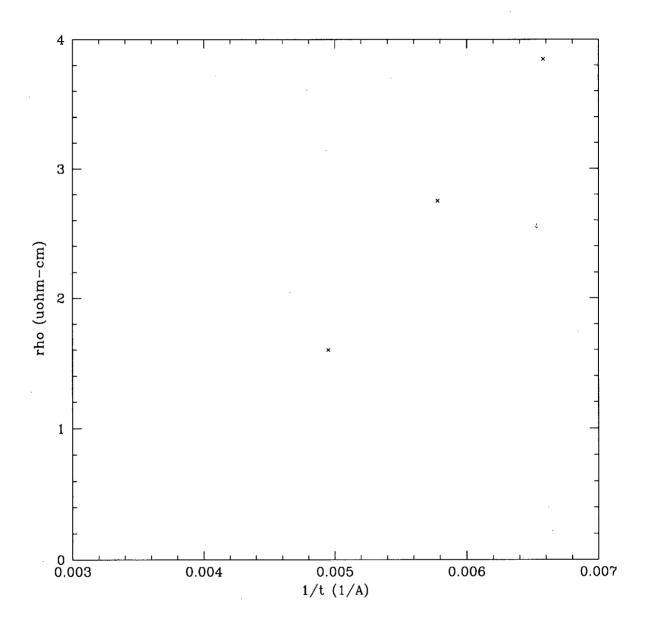

| 4.4 | Film thickness dependence of the resistivity of thin gold films          | 62 |

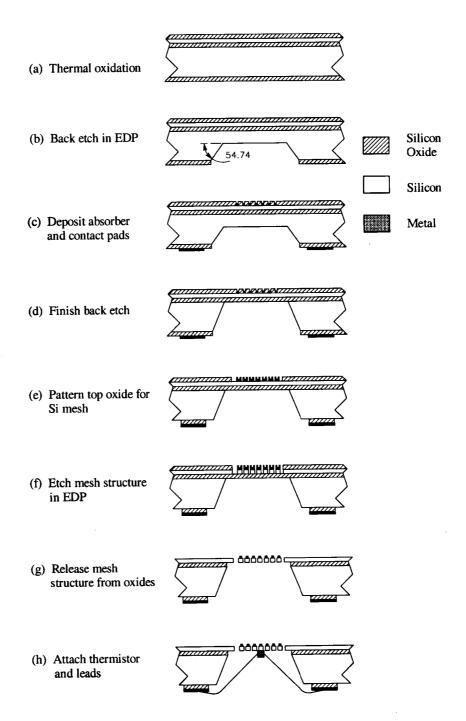

| 5.1 | Basic steps to build a micromesh bolometer                         | 65 |

|-----|--------------------------------------------------------------------|----|

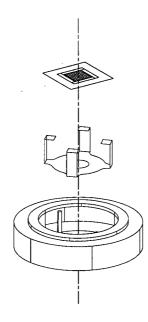

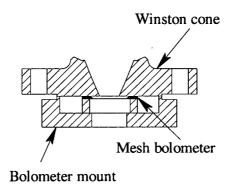

| 5.2 | Bolometer holder assembly                                          | 66 |

| 5.3 | The bolometer at the output of a Winston cone                      | 67 |

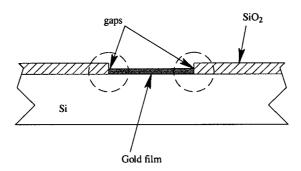

| 5.4 | Gaps between the gold film and protective oxide                    | 71 |

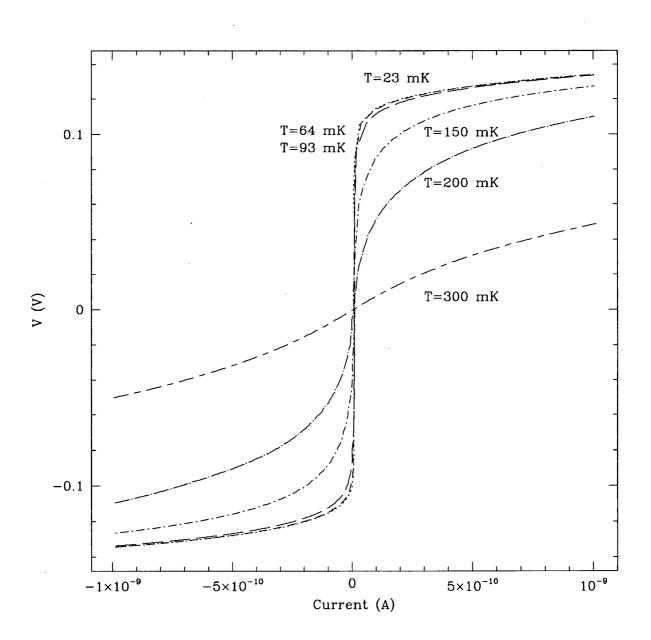

| C.1 | I–V curves for NTD Ge thermistors at various temperatures          | 88 |

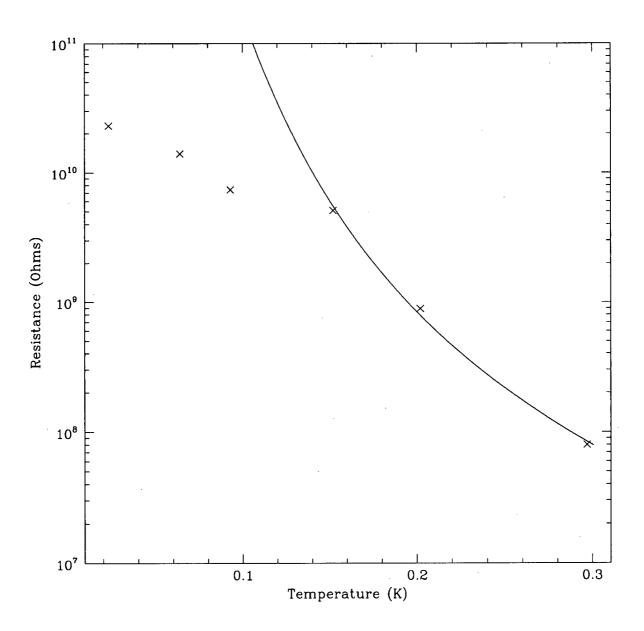

| C.2 | R(T)                                                               | 89 |

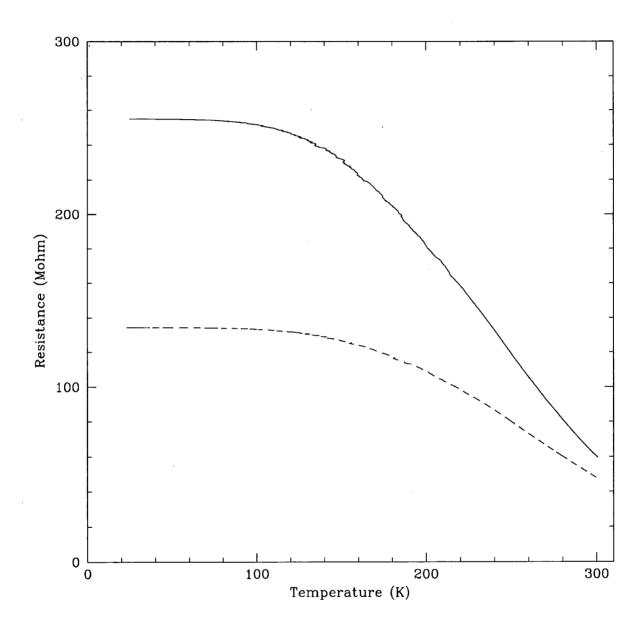

| C.3 | Temperature sweep of thermistor biased with a constant current     | 90 |

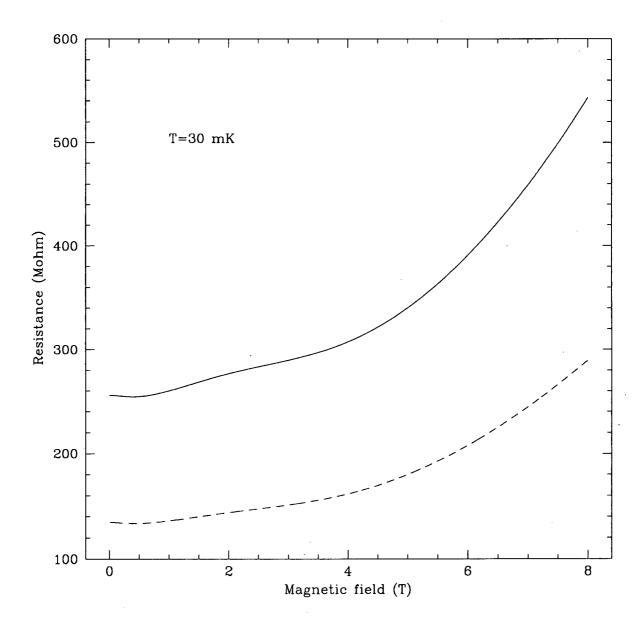

| C.4 | Thermistor resistance vs applied magnetic field at $30\mathrm{mK}$ | 91 |

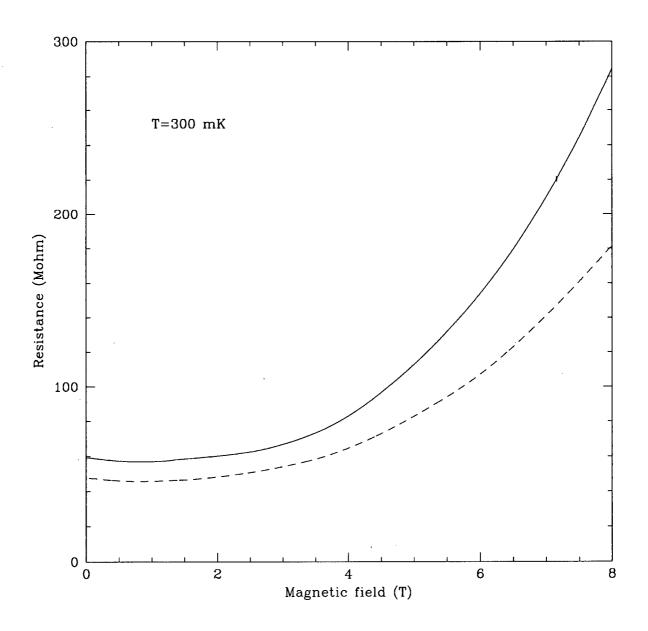

| C.5 | Thermistor resistance vs applied magnetic field at 300 mK          | 92 |

# Acknowledgments

This thesis could not have been completed without the help of many people. In particular, much of this work involved extensive use of cleanrooms at both UBC and at SFU. A special thanks must go to those at SFU: Bill Woods, Eva Czyzewska and especially Glenn Chapman for providing expert advice on silicon micromachining. During this project's initial stages, Glenn spent countless hours going over micromachining techniques with me and continued to provide useful advice for the duration of this work. Bill and Eva were indispensable for their knowledge and hands-on experiences with the finicky cleanroom equipment and also for sharing humorous stories during long work days in the cleanroom.

Here at home, Mark Halpern gave me the opportunity to design and build a novel bolometer. This was a cool yet daunting project, but Mark was a great supervisor who was always encouraging and ready to give helpful advice on any problem, thesis related or not.

Colin Borys and Chris Padwick should also be commended for managing to drag me out of my shell. I would also like to thank Mitzi for being the first person to actually ask to proofread this work while it was being written and for providing many stylistic comments. Saving the best for last, thanks to Chris White for always being there to console me when I was suffering from thesis woes and to celebrate with me after cleanroom breakthroughs. He always knows when to bring me chocolate.

## Chapter 1

# Introduction

The Balloon-borne Anisotropy Measurement (BAM) is designed to measure the temperature fluctuations, or anisotropies, in the cosmic microwave background (CMB) at medium angular scales. Such measurements can provide information about the basic nature of our universe, including its age, density and geometry. Unfortunately, these anisotropies from the CMB mean temperature of 2.7286 K are small; the signal level is a mere  $\frac{\Delta T}{T} \approx 10^{-5}$ . To be able to detect such small differences in temperature across the sky, any experiment must have very sensitive detectors. What makes BAM unique from other balloon-borne CMB experiments is the sensitive differential Fourier transform spectrometer (FTS), previously used to measure the CMB intensity spectrum from a sounding rocket [1, 2]. Housed within a cryostat at  $\sim$ 2 K so that there are no warm moving parts, the FTS measures the difference in intensity between two 0.7° regions of the sky separated by 3.6°. Each optical output of the spectrometer is independently coupled to a bolometric detector, held at 0.27 K, that measures the total power, incident on it. Thus, each bolometer returns an interferogram proportional to the brightness difference between the two input beams [3].

This thesis describes a program to build novel detectors sensitive enough for the BAM experiment which are less sensitive to cosmic rays and could be frequency tunable. By using common micromachining methods many bolometers of this type could be made in one production cycle. The rest of this chapter is devoted to a brief discussion of bolometer theory and design. Chapter 2 describes the micromachining techniques that

were used in the fabrication process. Chapters 3 and 4 describe experiments to construct the substrate and absorption layer components of the bolometer while the final chapter describes a possible process to build a fully functional bolometer.

#### 1.1 Bolometers

Bolometers are broadband thermal radiation detectors commonly used in astronomical applications to detect far infrared and millimeter wavelength radiation. They can be placed at the receiving end of a horn as the BAM experiment does, or at the end of a waveguide or in a focal plane, where the incident radiation will be absorbed. The detection is made by measuring the the temperature changes in the absorbing material. They are different from other thermal radiation detectors in that they rely on a thermistor whose electrical resistance is heavily dependent on temperature. Once the incident power is absorbed, the temperature of the detector element rises causing a change in the thermistor resistance R. If a constant current or voltage is applied, the change in R can be measured (since it is easier to amplify small voltages, the BAM experiment uses the constant current configuration). Thus, the output of the detector is directly proportional to the bolometric intensity of the radiation incident on it. Some examples of thermistors include carbon resistors, heavily doped Ge and ion implanted Si [4]. For semi-conductor materials and superconducting films near  $T_c$ , dR/dT < 0, while for metals, dR/dT > 0.

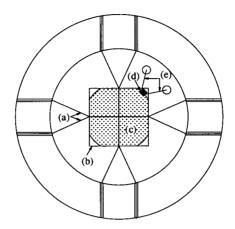

Composite bolometers are composed of several key components that can be individually tailored to provide optimal performance for various applications. In contrast, in monolithic bolometers, all the components are integrated into one structure so that the thermistor element is part of the substrate structure [4]. Those previously used on BAM, as shown in Figure 1.1, are composite bolometers consisting of a radiation absorbing bismuth layer on a sapphire support structure and a neutron transmutation doped (NTD)

Figure 1.1: A schematic drawing (not to scale) of the 1998 BAM composite bolometer, suspended inside a copper ring: a) nylon support legs b) sapphire substrate, c) thin bismuth film, d) NTD Ge thermistor, and e) brass electrical leads.

germanium thermistor [5]. The bolometer is suspended within a copper ring by 4 twisted pairs of nylon surgical threads. For an effective bolometer, the radiation absorber should have a large absorptivity over the desired frequency range and be of an appropriate size for the optical system. As well, the thermistor's electrical resistance should have an strong temperature dependence and have low electrical noise. The supporting substrate should not only be mechanically rigid and have a large thermal conductivity so that it remains isothermal during operation, but also, it should be thermally isolated from its surroundings. The mechanical support for the device should have low thermal conductivity and provide a weak link to the heat sink. All of the above components should have a low heat capacity to reduce the thermal time constant of the device.

The next four sections will briefly describe how the bolometer responds to incident electromagnetic waves.

# 1.2 Impedance Matching to Free Space

When radiation is incident on the bolometer, its initial function is to absorb as much power as it can and dissipate it thermally. Since the absorber is typically a thin metallic film, whose thickness is much thinner than a mm wavelength, deposited on a dielectric substrate, the optical properties of this system are easily described by comparing the bolometer to a resistive short in a transmission line. The reader is directed to Ulrich's article on the far infrared properties of metallic mesh structures [6] for greater detail.

Imagine a transmission line composed of two slightly separated parallel conductors along the z-direction connected by an AC source. There is a capacitance C and inductance L per unit length of the wires. As the circuit is driven by an AC signal, the time varying current produces a counter emf dV proportional to the inductance, which in turn produces a current dI since the wires are also coupled by their capacitance. That is,

$$dV = \frac{\partial V}{\partial z}dz = -Ldz\frac{\partial I}{\partial t},$$

(1.1)

$$dI = \frac{\partial I}{\partial z}dz = -Cdz\frac{\partial V}{\partial t}.$$

(1.2)

These two equations lead to the following coupled differential equations,

$$\frac{\partial V}{\partial z} = -L \frac{\partial I}{\partial t}, \tag{1.3}$$

$$\frac{\partial I}{\partial z} = -C \frac{\partial V}{\partial t}. \tag{1.4}$$

Differentiating (1.3) with respect to z and (1.4) with respect to t gives,

$$\frac{\partial^2 V}{\partial z^2} = -L \frac{\partial^2 I}{\partial t \partial z},\tag{1.5}$$

and

$$\frac{\partial^2 I}{\partial z \partial t} = -C \frac{\partial^2 V}{\partial t^2}.$$

(1.6)

Substitution of (1.5) into (1.6), or vice versa leads to two second order differential equations that are easily recognized as one dimensional wave equations for the voltage and the current:

$$\frac{\partial^2 V}{\partial z^2} = LC \frac{\partial^2 V}{\partial t^2},\tag{1.7}$$

$$\frac{\partial^2 I}{\partial z^2} = LC \frac{\partial^2 I}{\partial t^2}. (1.8)$$

The propagation speed of the current and voltage down the line is just  $v^2 = 1/LC$  or,

$$v = \frac{1}{\sqrt{LC}}. (1.9)$$

The solution to (1.7) is a superposition of two traveling waves,

$$V(z,t) = V_{-} + V_{+}, (1.10)$$

where  $V_{-} = V_{-}(t + z/v)$  describes a wave moving to the left and  $V_{+} = V_{+}(t - z/v)$  describes a wave moving to the right. To find I(z,t), use (1.3) and differentiate V(z,t) with respect to z, then integrate with respect to t. This gives

$$I(z,t) = \frac{1}{vL}(V_{+} - V_{-}). \tag{1.11}$$

In order to get the characteristic impedance of the transmission line  $Z_{\ell}$ , one only needs to take the ratio between V and I for either of the traveling waves. Then,

$$Z_{\ell} = \frac{V}{I} = \sqrt{\frac{L}{C}}. (1.12)$$

If the line is terminated by a load whose impedance matches  $Z_{\ell}$ , then the signal will not be reflected by the load, but instead, all the power will be transferred to the load.

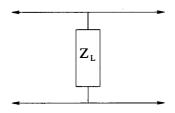

Now consider a resistive load with impedance  $Z_L$  shorting an infinite transmission line as in Figure 1.2. Since the load acts like an impedance in parallel with the line, the equivalent impedance  $Z_T$  of the circuit becomes,

$$Z_T = \frac{Z_L Z_\ell}{Z_L + Z_\ell}. (1.13)$$

Figure 1.2: Infinite transmission line with a resistive short.

A signal,  $I_o$  traveling down the line, once encountering the short, will be partially reflected,  $I_r$ , and partially transmitted,  $I_t$  past the load to the remainder of the line. The voltage  $V_o$ , is the sum of the reflected and transmitted waves, that is,

$$V_{\circ} = V_t - V_r. \tag{1.14}$$

What is of interest is the power dissipated in the load. The current through the load  $I_L$  is given by:

$$I_L = \frac{V_L}{Z_L}, \tag{1.15}$$

$$I_L = I_o + I_r - I_t \tag{1.16}$$

$$= \frac{V_{\circ}}{Z_{\ell}} - \frac{V_r + V_t}{Z_{\ell}},\tag{1.17}$$

where  $V_L=V_t$  since the drop across the load is the same as the drop across the rest of the line. Substituting (1.14) into (1.15) and (1.17) leads to,

$$\frac{V_{\circ}}{Z_L} = -V_r \frac{2Z_L + Z_{\ell}}{Z_L Z_{\ell}} \tag{1.18}$$

The ratios  $V_r/V_o$  and  $V_t/V_o$  are useful quantities called the reflection and transmission coefficients  $\rho$  and  $\tau$  respectively and  $\tau - \rho = 1$ . From (1.18),

$$\rho = -\frac{Z_{\ell}}{2Z_L + Z_{\ell}}.\tag{1.19}$$

$$\tau = \frac{2Z_L}{2Z_L + Z_\ell}. ag{1.20}$$

The fractional reflected power is the ratio  $P_R = P_r/P_o$ , where  $P_r = V_r^2/Z_\ell$  is the power in the reflected wave and  $P_o = V_o^2/Z_\ell$  is the power in the source signal. It can be immediately seen that

$$P_R = \frac{V_r^2}{V_o^2} = \rho^2. {(1.21)}$$

Similarly, the fractional transmitted power  $P_T = \tau^2$ . From conservation of energy, the power dissipated through the load,  $P_L$  is

$$P_L = 1 - \rho^2 - \tau^2 \tag{1.22}$$

Combining (1.19), (1.20) and (1.22) lead to the following equation for  $P_L$  in terms of  $Z_L$  and  $Z_\ell$ ,

$$P_L = 1 - \frac{Z_\ell^2 + 4Z_L^2}{(2Z_L + Z_\ell)^2} \tag{1.23}$$

The value of  $Z_L$  which maximizes (1.23) can be found with first year calculus,

$$\frac{dP_L}{dZ_L} = Z_{\ell}(Z_{\ell} - 2Z_L) = 0. \tag{1.24}$$

Thus,

$$Z_L = \frac{Z_\ell}{2}, 0. {(1.25)}$$

A quick check with the second derivative shows that  $Z_L = Z_{\ell}/2$  is in fact the maximum. Clearly, to maximize the power dissipated in the load, its impedance should be half the transmission line impedance. Returning to (1.19), (1.20) and (1.22), one finds that half of the signal power is dissipated in the load, while a quarter is reflected and the remaining quarter is in the rest of the line.

Electromagnetic waves traveling through free space and encountering the absorbing layer of the bolometer at normal incidence can be thought of as signals encountering parallel admittances on a transmission line. In fact, this optics system is completely analogous to the shorted transmission line described above, and one only has to replace V with the electric field  $E_x$ , I with the magnetic field  $B_y$ , L with  $\mu_o$  and finally C with  $\varepsilon_o$ .

Then, the wave equations for the optics case is just the results of Maxwell's equations for the electric and magnetic fields traveling through free space:

$$\frac{\partial^2 E_x}{\partial z^2} = \varepsilon_0 \mu_0 \frac{\partial^2 E_x}{\partial t^2}, \tag{1.26}$$

$$\frac{\partial^2 B_y}{\partial z^2} = \varepsilon_0 \mu_0 \frac{\partial^2 B_y}{\partial t^2}. \tag{1.27}$$

The propagation speed is just  $v = 1/\sqrt{\varepsilon_{\circ}\mu_{\circ}} = c$  which is the speed of light in a vacuum. The impedance of free space,  $Z_{\circ}$  is given by (1.12) with the proper substitutions, giving

$$Z_{\circ} = \sqrt{\frac{\mu_{\circ}}{\varepsilon_{\circ}}}$$

$$= 377 \,\Omega. \tag{1.28}$$

So, for the bolometer to absorb the maximum amount of power, its absorbing medium should have an impedance of  $Z_{bolo} = Z_{\circ}/2 = 188.5 \,\Omega$ . If the absorbing medium consists of a metallized mesh made up of  $N \times N$  leg segments with each leg having an impedance  $Z_l$ , the impedance of the entire mesh,  $Z_{mesh}$ , can be calculated. If a voltage is applied from one side of the mesh to the other, there are N legs in series and N legs in parallel so that

$$Z_{mesh} = (N \times \frac{1}{NZ_I})^{-1} \tag{1.29}$$

$$= Z_l. (1.30)$$

Therefore, each metallized leg of the absorbing grid in our bolometer should have an impedance of  $188.5 \,\Omega$ . The above works well for meshes with a grid spacing much less than the wavelengths being detected and so it is possible to build frequency tuned bolometers [16].

# 1.3 Thermal Properties of the Bolometer

As the bolometer absorbs power from some radiant source  $P_{\gamma} = P_{\circ} + P_{1}(t)$ , where  $P_{\circ}$  is time independent and  $P_{1}(t)$  is the time dependent part, the temperature of the bolometer

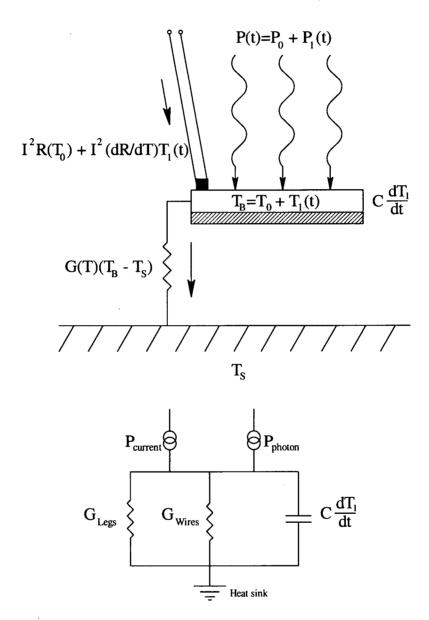

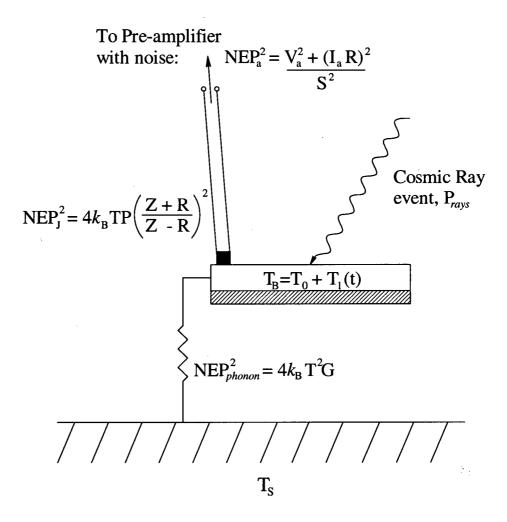

will vary,  $T_B = T_o + T_1(t)$ . The electrical power input to the constant current biased thermistor varies since the resistance depends on  $T_B$ . To first order,  $P_R = I^2 R(T_o) + I^2(dR/dT)T_1(t)$ . Some power will be stored in the heat capacity,  $P_C = C dT_B/dt = C dT_1/dt$  while the rest flows through a thermal link with conductance, G(T), to the heat sink held at temperature  $T_S$ . To first order,  $P_G = G(T)(T_o - T_S) + \frac{dP}{dT}T_1$ . The thermal circuit is sketched in Figure 1.3 and can be written as:

$$\sum P_{i} = C \frac{dT_{1}}{dt}$$

$$P_{\circ} + P_{1}(t) + I^{2}(R(T_{\circ}) + \frac{dR}{dT}T_{1}) = G(T_{\circ})(T_{\circ} - T_{S}) + G_{D}T_{1} + C \frac{dT_{1}}{dt}. \quad (1.31)$$

$G_D = dP/dT$  is the dynamical thermal conductance which arises since the thermal conductivity changes rapidly with T at low temperatures. From the time independent terms of (1.31) one arrives at the steady state heat flow equation where the bolometer is in thermal equilibrium with the heat sink and a constant background power loading  $P_o$ .

$$P_{\circ} + I^{2}R(T_{\circ}) = G(T_{\circ})(T_{\circ} - T_{S})$$

(1.32)

The time dependent terms give

$$P_1(t) - C\frac{dT_1}{dt} = T_1(t)(G_D - I^2\frac{dR}{dT}). \tag{1.33}$$

Thus, the temperature change  $T_1$  is influenced by the thermal feedback from the thermistor element. Defining

$$\alpha = \frac{1}{R} \frac{dR}{dT},\tag{1.34}$$

(1.33) can be rewritten as

$$P_1(t) - C\frac{dT_1}{dt} = T_1(t)(G_D - \alpha P_{\circ}).$$

(1.35)

Figure 1.3: A schematic diagram of the bolometer and the equivalent thermal circuit.

The quantity  $G_D - \alpha P_o$  is sometimes called the effective thermal conductance  $G_e$ . For neutron transmutation doped (NTD) germanium thermistors,  $\alpha < 0$  and so  $G_e > G_D$ . Rewriting (1.33), the resulting first order differential equation is just,

$$C\frac{dT_1}{dt} + G_e T_1(t) = P_1(t). (1.36)$$

If the radiant power is constant,  $P_1(t) = 0$ , with the initial condition  $T_1(0) = T'$ ,  $T' > T_o$ , then the solution to (1.36) is simply  $T_1(t) = T'e^{-\frac{G_e}{C}t}$ . The time it takes for the bolometer temperature to decay to 1/e of its peak value is  $\tau = C/G_e$ . This quantity is called the characteristic thermal time constant of the device.

For a sinusoidal power input  $P_1(t) = pe^{i\omega t}$ , the solution to (1.36) is

$$T_1(t) = \frac{p}{G_e + i\omega C} e^{i\omega t}. (1.37)$$

Both C and G depend on the physical properties of the material and its temperature. The heat capacity is a product of the body's mass m and the specific heat  $\kappa(T)$ , where  $\kappa(T) = \gamma T + \beta T^3$  for metals and  $\kappa(T) = \beta T^3$  for insulators. Here,  $\gamma$  is the electronic contribution to the material's heat capacity and  $\beta$  is the lattice contribution due to phonons. Table 1.1 shows estimated specific heats for materials typically used in bolometer construction.

The thermal conductance is proportional to the cross-sectional area A through which the heat flows, and inversely proportional to the length l, so that G = k(T)A/l, where k(T) is the thermal conductivity of the material. However, since for some materials k(T) depends rapidly on T, especially at low T, it is common to define and use the average thermal conductance,

$$\bar{G} = \frac{A}{l} \frac{1}{T_s - T_o} \int_{T_o}^{T_s} k(T) dT$$

(1.38)

| Material    | $\gamma$               | β                      | $\kappa(0.270)$       |  |  |

|-------------|------------------------|------------------------|-----------------------|--|--|

|             | $(\mathrm{J/cm^3K^2})$ | $(\mathrm{J/cm^3K^4})$ | $(J/cm^3 K)$          |  |  |

| Pd          | $1.1 \times 10^{-3}$   | $1.1 \times 10^{-5}$   | $2.97 \times 10^{-4}$ |  |  |

| Au          | $6.8 \times 10^{-5}$   | $4.5 \times 10^{-5}$   | $1.92\times10^{-5}$   |  |  |

| Ge          | $2.0 \times 10^{-9}$   | $3.0 \times 10^{-6}$   | $2.93 \times 10^{-7}$ |  |  |

| Brass       | $9.7 	imes 10^{-5}$    | $7.9 \times 10^{-6}$   | $2.63\times10^{-5}$   |  |  |

| Bi          | $3.8 \times 10^{-7}$   | $5.3 \times 10^{-5}$   | $1.15 \times 10^{-6}$ |  |  |

| Ti [7]      | $1.6\times10^{-5}$     | $1.2 \times 10^{-7}$   | $4.32 \times 10^{-6}$ |  |  |

| Si [8]      | $2.1 	imes 10^{-5}$    | $6.8 \times 10^{-6}$   | $8.78 \times 10^{-8}$ |  |  |

| $SiO_2$ [9] | ı                      | $3.7 \times 10^{-5}$   | $7.28 \times 10^{-7}$ |  |  |

Table 1.1: Estimated specific heats for materials commonly used in bolometers.  $\kappa(T) = \gamma T + \beta T^3$  (from [10] unless otherwise noted.)

At cryogenic temperatures, most of the thermal transport in insulators is carried by phonons and  $k(T) \propto T^3$ . On the other hand, in pure metals, electrons carry most of the heat current and  $k(T) \propto T$ . In this last proportionality there is a nearly universal value for how the proportionality constant scales with electrical conduction given by the Wiedemann-Franz law,

$$k(T) = \frac{\pi^2 k_B^2}{3e^2} \sigma T$$

$$= \mathcal{L}\sigma T. \tag{1.39}$$

$\mathcal{L}=25~\mathrm{nW}\Omega/\mathrm{K}^2$  is the Lorentz constant and  $\sigma=\sigma(T)$  is the electrical conductivity. This relation allows one to calculate the thermal conductivity of a metal after measuring its electrical conductivity at temperature T.

# 1.4 Responsivity

The absorbed power responsivity of a bolometer is defined to be the change in voltage per watt of absorbed signal power, i.e.,  $S_A = V_1/P_1$ . Since  $V_1 = I(dR/dT)T_1$  and given

(1.36), one can write

$$S_A = \frac{\alpha T_1 V}{G_e T_1 + C \frac{dT_1}{dt}}. (1.40)$$

Another useful quantity that is more easily measurable is the electrical responsivity,  $S_E = V/P_E$ , which characterizes how the bolometer responds to changes in the electrical power dissipated in the thermistor. Rewriting (1.40) in terms of the voltage V across the resistor,

$$S_E = \frac{\alpha V}{G_D - \alpha P}. (1.41)$$

Assuming there is no radiant power on the bolometer (although the result is valid if there is a constant background power loading  $P_o$  [11]) and using dV = d(IR) = RdI + IdR and  $dP = d(IV) = 2VdI + P\alpha dT = GdT$ , one can solve for dV and dI.

$$dV = RdI + V\alpha dT (1.42)$$

$$dI = \frac{(G - \alpha P)dT}{2V}. (1.43)$$

Letting Z = dV/dI,

$$Z = R \frac{G + \alpha P}{G - \alpha P}. ag{1.44}$$

Solving for G,

$$G = \alpha P \frac{Z+R}{Z-R} \tag{1.45}$$

$$= I^2 \frac{dR}{dT} \frac{Z+R}{Z-R},\tag{1.46}$$

and substituting (1.45) into (1.41),

$$S_E = \frac{Z - R}{2IR}. ag{1.47}$$

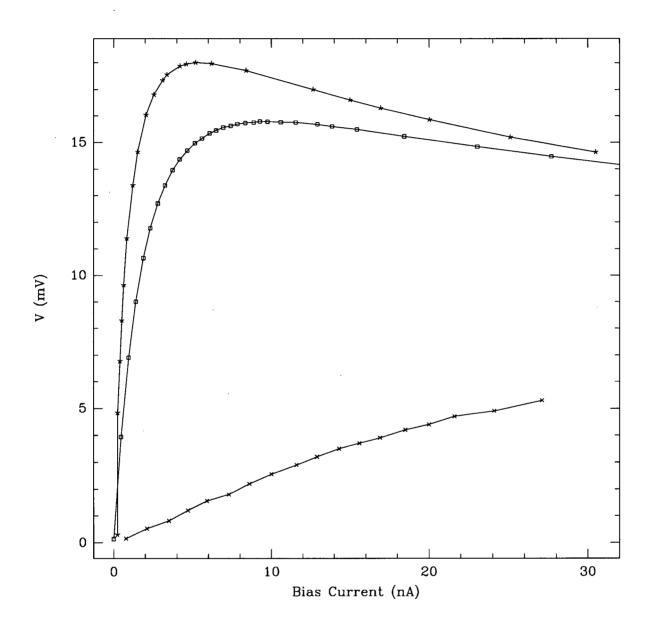

I-V curves for one of the composite sapphire chip bolometers we made for the 1998 BAM flight are graphed in Figure 1.4. The resistance R = V/I depends on the temperature (as can be seen from the upper two curves of the bolometer held at slightly different temperatures.) and on the radiative load (comparing the lower two curves for the bolometer held at the same temperature). Thus, if the bolometer is cooled to its operating temperature and one measures its I-V curve,  $S_E$  can be determined for various bias currents. As well, once R(T) is known, G(T) can be calculated from (1.46).

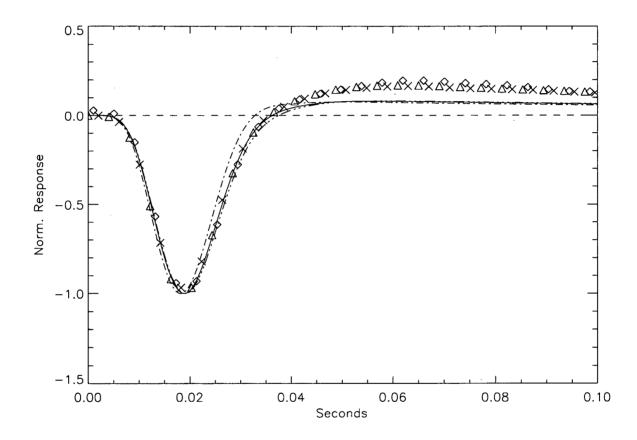

By changing the bias current with a large step function and observing the resulting voltage change, one can measure  $\tau$  and hence arrive at a value for C. To determine the time constant of the same bolometer used in the 1998 BAM flight, we examined the detector response to 3 normalized cosmic rays hits. The optical system and electronics of the experiment was modeled and fitted to the 3 cosmic rays. The solid line in Figure 1.5 is the model with a time constant of  $\sim 5.5$  ms, which seems to fit the detector response fairly well. The tail end of the response is set by filters in the electronics which were not included in the model.

#### 1.5 Noise

It is useful to scale the various noise sources in a bolometer by the appropriate sensitivity and express the quadrature sum as the noise equivalent power, or NEP. This is the incident power which produces a signal equal to the noise in a one Hz bandwidth. The dominant sources of noise in bolometers, as shown in Figure 1.6, include Johnson noise, amplifier noise, and phonon or thermal fluctuation noise. For greater detail on the noise terms presented here, the reader is directed to Mather's articles [12, 13]. Other

Figure 1.4: I-V curves for one of the sapphire and NTD Ge chip bolometers used in the 1998 BAM flight. Bolometer cooled to  $T=0.263\,\mathrm{K}$  and looking at a cold load calibrator (\*), bolometer cooled to  $T=0.269\,\mathrm{K}$  and looking at the same cold load ( $\square$ ), bolometer cooled to  $T=0.269\,\mathrm{K}$  looking at the room (×). Solid lines are not fits but are just to lead the eye.

Figure 1.5: Modeling the 1998 flight bolometer's response to cosmic ray hits to determine the thermal time constant. The lines are for the model with  $\tau = 4 \, \text{ms}(-\cdot -)$ ,  $\tau = 5.5 \, \text{ms}(-)$ ,  $\tau = 6 \, \text{ms}(-\cdot \cdot \cdot)$  and three different cosmic ray hits  $(\triangle, \diamondsuit, \times)$  occurring at t = 0.

contributions to the noise include cosmic rays and microphonics.

In simple bolometer theory, the Johnson noise, from voltage fluctuations in the resistive thermistor element arises in the form  $NEP_J^2 = V_J/S^2 = 4k_BTR/S^2$ . However, this ignores the electrothermal feedback since the bias current does work on the Johnson noise source. Since any increase in  $V_J$  increases the temperature of the bolometer, which lowers the resistance and decreases the output voltage, the Johnson noise is actually reduced by as much as 60% [12]. This can be described by the equivalent Johnson noise source,  $V_J' = V_J(Z+R)/2R = \sqrt{4k_BTR}(Z+R)/2R$ . Thus, combined with (1.47),

$$NEP_J^2 = 4k_B TP \left(\frac{Z+R}{Z-R}\right)^2. \tag{1.48}$$

The noise in the first stage of amplification, at the amplifier input, is described by  $NEP_a^2 = (V_a^2 + (I_aR)^2)/S^2$ . In order for the noise in the amplifier to be unimportant, the temperature  $T_N$  at which the  $NEP_a = NEP_J$  should be less than the operating temperature of the bolometer.

Because the bolometer is connected to a heat sink at temperature  $T_S$  via an average thermal conductance  $\bar{G}$ , there are energy fluctuations in the bolometer caused by traveling phonons or electrons. When the system is in thermal equilibrium, the noise fluctuations are described by,

$$NEP_{phonon}^2 = 4k_B T^2 \bar{G}. (1.49)$$

If there is a large responsivity S, then both  $NEP_J$  and  $NEP_a$  become negligible, and the phonon noise term dominates the total NEP of the bolometer.

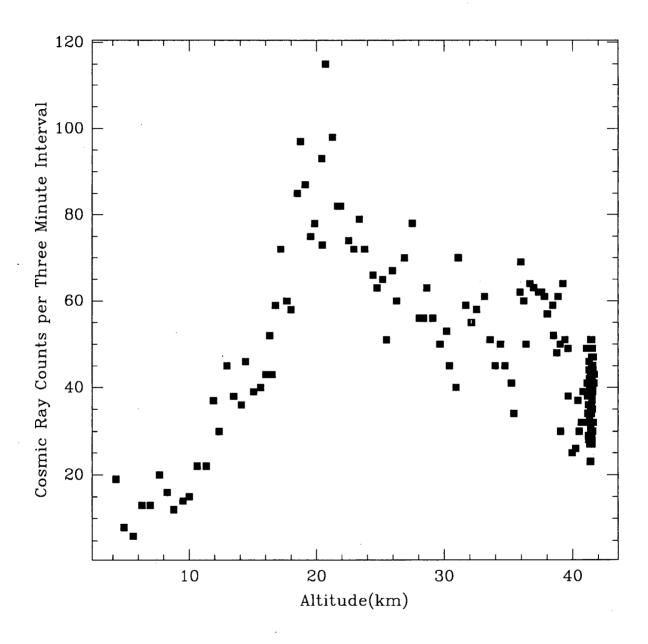

Another concern in balloon borne CMB experiments is the bolometer's sensitivity to cosmic ray hits in the upper atmosphere. These hits leave power spikes in the data and are a major source of noise. Figure 1.7 shows the number of cosmic ray hits during the

Figure 1.6: Block drawing of bolometer noise sources.

1995 BAM flight. The float altitude was 41.5 km and remained at that position for 4 hours, for which 8.7% of the data was lost due to cosmic rays. Notice that there are many cosmic ray hits in every minute of the flight, posing a large data editing problem. An improvement then would be to reduce the geometric cross-section (also lowering the total heat capacity) of the radiation absorber without compromising the sensitivity of the device.

# 1.6 Bolometer Design and Constraints

On its previous two flights, BAM used bolometers that were individually hand-made (see Figure 1.1) with a 200 Å layer of evaporated bismuth on a solid sapphire chip suspended by surgical nylon threads. The thermistor element was a 250  $\mu$ m cube of neutron transmutation doped (NTD) germanium whose resistance near 0.3 K is heavily dependent on temperature. This was glued to the non-metallized side of the sapphire with a trace amount of epoxy. The electrical connection consisted of 0.0003" diameter brass leads which were indium soldered to gold pads on opposing sides of the NTD Ge chip.

Several improvements can be made to this bolometer design. As previously mentioned, these detectors are subject to cosmic ray hits whose effects can be reduced by decreasing the geometric cross-section of the device. This can be achieved by fabricating web or mesh structures that have grid spacings suitable to the appropriate wavelengths to be measured. Previously, the BAM bolometers used solid sapphire chips and NTD Ge thermistors which have volumes of  $3.1 \times 10^8 \ \mu\text{m}^3$  and  $1.7 \times 10^7 \ \mu\text{m}^3$  respectively. A  $16 \ \text{mm}^2$  mesh with  $40 \ \mu\text{m}$  wide and  $5 \ \mu\text{m}$  thick lines effectively reduces the cosmic ray cross-section by a factor of  $\sim 20$ . Reducing the volume of the mesh further does not significantly reduce the cross-section to cosmic rays due to the presence of the thermistor.

Also, the current composite bolometers are individually hand-made, leading to devices

Figure 1.7: The number of cosmic ray hits during the 1995 flight. [14]

with slightly different characteristics depending on the craftsmanship, and having a longer production time. It would be preferable to build many bolometers, all with identical characteristics, in one production cycle. This is possible if one applies micromachining techniques to bolometer construction.

Such improvements have already been made by Mauskopf et al. using a  $Si_3N_4$  membrane  $1\,\mu\rm m$  thick etched into a spiderweb pattern [15]. Generally, however,  $Si_3N_4$  processing capabilities are less accessible whereas most cleanrooms support basic silicon processing techniques. If Si wafers are used, one could also develop tuned bolometers that are frequency selective [16]. Thus, it is of interest to build micromesh bolometers from easily obtainable silicon wafers.

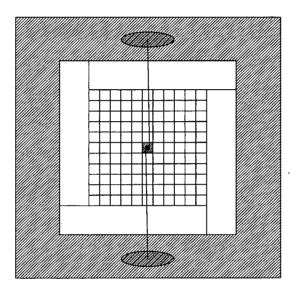

The proposed design is shown in Figure 1.8. The center grid will be patterned from a free-standing silicon membrane held in place to a surrounding silicon frame (the heat sink) by four silicon legs. A thin (~200 Å) metal layer will be evaporated onto the grid area to act as the radiation absorber, while the NTD Ge thermistor is glued to the center of the mesh on the side opposite the gold layer. Two brass electrical leads will run from the thermistor to gold contact pads located on the Si frame.

From the previous noise and responsivity discussions, one can design a bolometer optimized for the BAM experiment. The maximum noise at the bolometer input is  $NEP_{max} = 10^{-16} \,\mathrm{W/Hz^{\frac{1}{2}}}$ . Since this quantity is dominated by the phonon noise, (1.49) gives an upper limit for the thermal conductance to the heat sink, held at 0.27 K, to be  $G = 2.48 \times 10^{-9} \,\mathrm{W/K}$ . The thermal conductivities of brass and silicon are  $2 \times 10^{-3} \,\mathrm{W/cmK}$  [9] and  $2.4 \times 10^{-5} \,\mathrm{W/cmK}$  [17] respectively (see Table 1.2). If the same NTD Ge thermistors are used on the mesh bolometers, then the two 4 mm long, 0.0003" diameter brass leads dominate the thermal conductance with  $G_{Brass} = 4.5 \times 10^{-9} \,\mathrm{W/K}$ . This exceeds the noise budget and leads to a total  $NEP_{Brass} = 1.4 \times 10^{-16} \,\mathrm{W/Hz^{\frac{1}{2}}}$ . A similar calculation for 4, 1 mm long Si support legs does not add significantly to the total

Figure 1.8: The proposed Si micromesh bolometer design to detect the CMB. The entire device is  $10\,\mathrm{mm^2}$ . The bolometer element is an NTD Ge thermistor with  $\sim 4\,\mathrm{mm}$  long brass electrical leads while the absorbing layer consists of a Au grid with  $R=188\,\Omega/\Box$ .

thermal noise if the cross-sectional area of each leg does not exceed  $150 \,\mu\text{m}^2$ . This upper limit contributes  $G_{legs} = 1.44 \times 10^{-9} \,\text{W/K}$  and brings the phonon noise total to  $NEP_{phonon} = 1.55 \times 10^{-16} \,\text{W/Hz}^{\frac{1}{2}}$  at  $270 \,\text{mK}$ . The value of k for thin legs of Si is less than the bulk value since the mean free path of the phonons is greater than the leg dimensions [17]. If this was not the case then the Si support legs would have to undergo ion bombardment to destroy the crystal structure. It is possible to reduce the total phonon noise by increasing the length of the brass wires or by forming gold contact lines on the substrate to which the thermistor could be attached.

| Material                  | k(0.27)                 | Dimensions (cm)     |                     |        | $A/\ell$            | # | $G_{270mK}$           |

|---------------------------|-------------------------|---------------------|---------------------|--------|---------------------|---|-----------------------|

|                           | (W/cm K)                | $w 	ext{ or } r$    | t                   | $\ell$ | (cm)                |   | (W/K)                 |

| Brass                     | $2.0 \cdot 10^{-3}$     | $3.8\cdot 10^{-4}$  | _                   | 0.4    | $1.1\cdot 10^{-6}$  | 2 | $4.5\cdot 10^{-9}$    |

| Si <sub>support leg</sub> | $2.4 \cdot 10^{-5}[17]$ | $3.0 \cdot 10^{-3}$ | $5.0 \cdot 10^{-4}$ | 0.1    | $1.5 \cdot 10^{-5}$ | 4 | $1.4 \cdot 10^{-9}$   |

| Si <sub>bulk</sub>        | $\sim 4\cdot 10^{-4}$   | $3.0 \cdot 10^{-3}$ | $5.0 \cdot 10^{-4}$ | 0.1    | $1.5\cdot 10^{-5}$  | 4 | $\sim 2\cdot 10^{-8}$ |

| Si <sub>mesh leg</sub>    | $2.4 \cdot 10^{-5}[17]$ | $3.0 \cdot 10^{-3}$ | $5.0\cdot 10^{-4}$  | 0.4    | $3.75\cdot 10^{-6}$ | 1 | $9.0 \cdot 10^{-11}$  |

| Au <sub>mesh leg</sub>    | $1.8 \cdot 10^{-3}$     | $5.0 \cdot 10^{-4}$ | $1.5 \cdot 10^{-6}$ | 0.4    | $1.9 \cdot 10^{-9}$ | 1 | $3.4 \cdot 10^{-12}$  |

Table 1.2: Estimated thermal conductance at  $270 \,\mathrm{mK}$ , for bolometer components with the listed dimensions. Values of k from [9] unless otherwise noted.

To keep the thermal time constant lower than  $\tau = 5.5$  ms, the total heat capacity of the bolometer cannot exceed  $C_{max} = 0.0055 \times 6.0 \times 10^{-9}$  J/K=  $3.3 \times 10^{-11}$  J/K. Using the data in Table 1.1, one can estimate the heat capacity of each bolometer component, at 270 mK as shown in Table 1.3. Clearly the thermistor and brass leads dominate the heat capacity of the entire device, however the total heat capacity is well below  $C_{max}$  and  $\tau \approx 2$  ms.

When determining the particular dimensions of the remaining bolometer components, the only constraint is to keep the cross section of the support legs under  $150 \,\mu\text{m}^2$ . From researching micromachining techniques, fabricating Si membranes with thicknesses of the

order of a few microns seemed fairly common. So, the initial thickness of the support legs was taken to be  $5 \mu m$ , leading to a width of  $30 \mu m$ .

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |                      | Dimensions (cm)     |        | Volume             | #                      | $C_{270mK}$ |                         |

|--------------------------------------------------------|----------------------|---------------------|--------|--------------------|------------------------|-------------|-------------------------|

|                                                        | (J/cc K)             | $w 	ext{ or } r$    | $\ell$ | t                  | (cc)                   |             | (J/K)                   |

| Pd                                                     | $2.97\cdot 10^{-4}$  | 0.025               | 0.025  | $2.0\cdot 10^{-6}$ | $1.25 \cdot 10^{-9}$   | 2           | $7.43 \cdot 10^{-13}$   |

| Au                                                     | $1.92 \cdot 10^{-5}$ | 0.025               | 0.025  | $2.5\cdot 10^{-5}$ | $1.56 \cdot 10^{-8}$   | 2           | $6.00 \cdot 10^{-13}$   |

| NTD Ge                                                 | $2.93\cdot 10^{-7}$  | 0.025               | 0.025  | 0.0275             | $1.72 \cdot 10^{-5}$   | 1           | $5.03 \cdot 10^{-12}$   |

| Brass                                                  | $2.63\cdot 10^{-5}$  | $3.8\cdot 10^{-4}$  | 0.4    |                    | $1.82 \cdot 10^{-7}/2$ | 2           | $4.80 \cdot 10^{-12}$   |

| Bi *                                                   | $1.15 \cdot 10^{-6}$ | $3.0 \cdot 10^{-3}$ | 0.4    | $2\cdot 10^{-6}$   | $2.9 \cdot 10^{-9}$    | 22          | $ 6.07 \cdot 10^{-14} $ |

| Au                                                     | $1.92 \cdot 10^{-5}$ | $5.0 \cdot 10^{-4}$ | 0.4    | $2\cdot 10^{-6}$   | $4.0 \cdot 10^{-10}$   | 22          | $1.69 \cdot 10^{-13}$   |

| Ti *                                                   | $4.32 \cdot 10^{-6}$ | $5.0 \cdot 10^{-4}$ | 0.4    | $5 \cdot 10^{-7}$  | $1.0 \cdot 10^{-10}$   | 22          | $9.50 \cdot 10^{-15}$   |

| Si <sub>support</sub>                                  | $8.78 \cdot 10^{-8}$ | $3.0 \cdot 10^{-3}$ | 0.1    | $5.0\cdot 10^{-4}$ | $1.5 \cdot 10^{-7}$    | 4           | $5.27 \cdot 10^{-14}$   |

| Si <sub>mesh leg</sub>                                 | $8.78 \cdot 10^{-8}$ | $3.0 \cdot 10^{-3}$ | 0.4    | $5.0\cdot 10^{-4}$ | $6.0 \cdot 10^{-7}$    | 22          | $1.16 \cdot 10^{-12}$   |

| SiO <sub>2</sub> *                                     | $7.28 \cdot 10^{-7}$ | $3.0 \cdot 10^{-3}$ | 0.4    | $3.0\cdot 10^{-5}$ | $3.6 \cdot 10^{-8}$    | 22          | $5.77 \cdot 10^{-13}$   |

Table 1.3: Estimated heat capacities of bolometer components at 270 mK with the listed dimensions. The first three materials form the thermistor element. Materials marked with \* are not used in the final bolometer design.

Several constraints were considered in the initial mesh structure design. The overall size of the mesh needs to be at least the area of the optical output of the Winston cones  $(9.6\,\mathrm{mm^2})$  and have a suitable grid spacing to absorb millimeter wavelengths. The mesh was chosen to be a square with  $16\,\mathrm{mm^2}$  and a grid spacing of  $385\,\mu\mathrm{m}$ . The widths of the mesh legs were kept at  $30\,\mu\mathrm{m}$ , to remain consistent with the width of the support legs. The thickness of the mesh should be the same as that of the support legs. These dimensions are not at all engraved in stone and, as will be seen in later chapters, the structural dimensions were varied, but kept within the noise parameters, as different micromachining processes were performed. The dimensions of the Au absorbing layer are addressed in Chapter 4 as is the question of whether or not to include an insulating  $\mathrm{SiO}_2$  layer and a Ti adhesion layer.

### Chapter 2

# Silicon Micromachining Basics

Micromachining techniques provide a reproducible process for fabricating three dimensional microstructures from single crystal silicon wafers (SCS). Here the basic processes involve photolithography, anisotropic etching and metallisation.

Note that all process parameters and recipes used in this thesis are included in more detail in Appendix A.

# 2.1 Photolithography

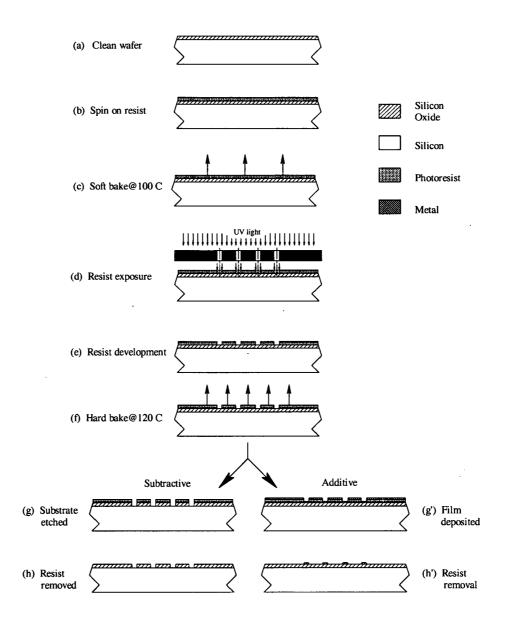

Photolithography uses photoemulsion techniques to create three dimensional structures from a substrate. A masking layer of light sensitive photoresist is exposed with UV light to a particular pattern from which structures can be defined. These structures are commonly formed by subtractive or additive pattern transfers as illustrated by Figure 2.1. In the subtractive method, the film to be patterned is first grown or deposited onto the SCS. Then, the pattern is etched into the film using photolithograpy. The additive process involves the same lithographic steps, but in the reverse order; that is, the masking resist layer is first patterned on the SCS followed by the film deposition. Afterwards, the photoresist layer is stripped, lifting off the undesired film deposits and leaving the desired pattern behind. The two processes could be used to reach identical final states, but more often, they lead to two different final states as in Figure 2.1. Generally, the subtractive method is used more often in SCS processing, but in both cases, photolithography defines the shape and the precision of the final structure.

Figure 2.1: Basic steps to additive or subtractive photolithography. (a)Grow or deposit the film to be patterned. (b)Apply photoresist. (c)Soft bake. (d)The mask is aligned and exposed. (e)The exposed resist is removed. (f)Hard bake. (g)The exposed film is etched or (g') another layer is deposited. (h)Photoresist removal.

Figure 2.1 shows the cross-section of a wafer during the basic eight steps of photolithography when used as either part of a subtractive or additive pattern transfer process. Step (a) shows a SCS wafer with a thermally grown layer of SiO<sub>2</sub> that is ready to be patterned. First, a thin layer of photoresist, a few microns thick, is spun unto the wafer as in (b). The resulting resist thickness depends on the type of resist, time and rotational speed. After the wafer is lightly baked at 100°C (c) to promote resist adhesion and to remove solvents in the resist, a mask (analogous to a negative in photography) is precisely aligned to the wafer. The wafer is then exposed to ultraviolet light through the mask as in (d). The resist which is exposed to the UV light is polymerised and then removed in the developer (e), while the unexposed portions remain. Then in (f), the wafer is baked again, this time at 120°C to harden the remaining resist. The exposed areas are then inspected under the microscope. If there are resist residues on the oxide or other resist defects, then the photoresist is stripped in acetone, and steps (a) through (f) are repeated. Once it is determined that the pattern is correctly masked into the resist layer, step (g) is performed. (g) shows the result of a subtractive process where the wafer is placed into a wet or dry etch process so that the exposed areas of the oxide are etched. On the other hand, an additive process, such as metallisation, is shown in (g') where a metal has been deposited over the entire surface. The remainder of the photoresist is then removed in acetone leaving the desired pattern etched *into* the oxide (h) or patterned *onto* it with another material (h'). Depending on the purpose of the etched layer the patterned film could be the final structure desired, or it could act as a mask for additional processes such as doping or etching of the silicon substrate.

During the photolithography process the mask and wafer must remain dust free. If either have defects such as dirt or cracks, then the photoresist exposure will be compromised. Unwanted pinholes in the photoresist layer will be transferred to other layers in subsequent processes. As a preventive measure, all procedures are performed in a Class 100 cleanroom, on wafers and samples that have been cleaned first with acetone, then deionized water and finally, methanol. Before certain processes such as oxidation and doping, wafers must been cleansed thoroughly with an RCA clean. The RCA cleaning procedure removes trace metals, organics and surface oxides from the wafer, as described in Appendix A.

### 2.1.1 A Note on Mask Making

Each layer of patterning requires a mask (analogous to a negative in photography) that will expose the photoresist to UV light in the regions to be removed. These high resolution masks, drawn with the computer design tool XKic, define the device onto the wafer. XKic allows all the different masks, or layers, of the design to be drawn on the same layout and can distinguish between each layer so that if desired, any number of layers can be shown. From the XKic designs, either a .CIF file or individual postscript files of each layer are created. .CIF files can be professionally transferred to 5" chrome emulsion masks, while postscript files are printed onto linotronic films which are usually used in printing companies as proofs. The linotronic films are then used as a negative to transfer the pattern onto 5" Kodak photographic emulsion plates.

Two important aspects arise when making masks. First, the final mask image can be either a positive or a negative of the design. Secondly, one must note which way the emulsion is facing so that the proper image, not a mirrored one, is patterned on the wafer at the end. The image should be such that the emulsion is face down on the wafer when exposing the photoresist.

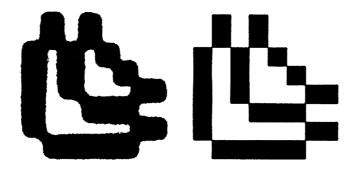

Theoretically, the highest resolution of the linotronic film output is 5080 dpi or  $5 \mu m$  resolution. Unfortunately,  $10 \mu m$  lines on the linotronic films are actually bloated as in Figure 2.2. As a result, darkened areas of the mask are generally bloated by  $\sim 10 \mu m$  on each side. Thus if greater resolution is desired, laser or E-Beam written chrome masks

are used. The choice to use emulsion masks at all is because they are at least 30 times cheaper in cost to purchase.

Figure 2.2: Dark lines appear bloated on the printed masks as can be seen from the resolution marks. The left resolution mark ( $\sim 50 \,\mu\mathrm{m}$  wide) is a scanned image of the printed mask, while the right is a scaled image of the original mark ( $30 \,\mu\mathrm{m}$  wide) from the postscript file of the computer design. Note that the edges of the marks are actually sharp and the fuzziness in the right hand pattern is a result of the bitmap graphics on this page.

#### 2.2 Wet Si Etchants

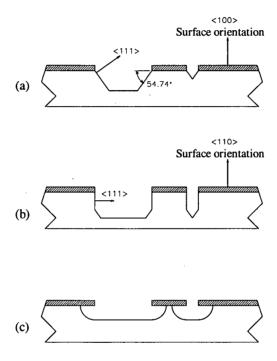

Once the photolithographic steps are completed, the silicon wafer is ready for further processing. For example, the wafer can be etched to create 3D structures. Silicon may be etched either isotropically or anisotropically with various wet etchants. The degree of etch selectivity for an etchant to etch silicon over other materials, determines the appropriate masking material. Figure 2.3 shows various hole geometries common to silicon etches. Isotropic etches, in c), produce holes which drastically undercut the masking material since the etch proceeds in all directions. On the other hand, anisotropic etches proceed along silicon's crystalline planes, for example, etching <100> and <110> planes much faster then the <111> plane. In this case, as shown in a), <100> wafers will have etched grooves with sloped walls bounded by the <111> plane, inclined at  $54.75^{\circ}$ , with a minimal amount of mask undercutting.

Figure 2.3: Etched hole geometries commonly used in micromechanical devices. The shaded regions indicate the masking material. a) Anisotropic etching on <100> surfaces. b) Anisotropic etching on <110> surfaces. c) Isotropic etching.

A common anisotropic etchant is Ethylene diamine pyrocatecol (EDP) diluted with water. This etchant is highly selective and attacks silicon but not SiO<sub>2</sub>, Al, Au or heavily boron doped Si. Thus any of these materials may be used either as a masking layer or an etch stop layer. When comparing selectivities, SiO<sub>2</sub> is the safer choice as a masking layer during long duration etches in EDP.

Previous tests [18] on SCS have shown that the EDP etch rate of the  $\langle 100 \rangle$  plane varies from 61  $\mu$ m/hr to 100  $\mu$ m/hr over the surface of the wafer during a long (>6 hours) etch. The etch rate depends heavily on fluid flow, temperature and etchant freshness. The fluid flow over a wafer in the EDP reactor varies from top to bottom, and left to right, hence etch rates across the wafer also vary. This is problem when one is timing the etch in order to reach a specific etch depth. Preferably, an etch stop layer is used so that it is unnecessary to monitor the progress of the etch. If the wafer is constantly pulled from the EDP reactor in order to check the etch depth, the repeated temperature change between the EDP and the deionized water rinse tends to crystallize a white Si based substance onto the etched areas. It is thought that the dissociated pyrocatecol molecules form bonds with excess Si atoms and subsequently crystallize into the white compound at room temperature [19]. Although these white deposits are removable with buffered HF, their presence interferes with subsequent etches and leaves the underside of the Si membrane roughened and uneven. Therefore when using EDP the micromachine 3D structures, it is important to employ some sort of etch stop layer such as heavily boron doped Si or SiO<sub>2</sub>.

Another anisotropic silicon wet etchant is tetramethylammonium hydroxide (TMAH), which has a slower etch rate (see Table 2.1) when compared to EDP. However, TMAH does etch heavily doped Si so that doped areas can also be micromachined. A detailed review of these and other anisotropic and isotropic etchants may be found in [20].

| Silicon Etchant                            | TMAH   | TMAH  | EDP     |

|--------------------------------------------|--------|-------|---------|

| Temperature (°C)                           | 80     | 90    | 95      |

| Etch rate of $< 100 > Si (\mu m/hr)$       | 40     | 65    | 60-100  |

| Selectivity ratios                         |        |       |         |

| Si: SiO <sub>2</sub>                       | 1190:1 | 800:1 | >2000:1 |

| Si: B doped Si (10 <sup>20</sup> atoms/cc) | 27:1   | 20.1  | >500:1  |

| Si: B doped Si (10 <sup>21</sup> atoms/cc) | 100:1  | 92:1  | >500:1  |

Table 2.1: Estimated etch rates and selectivity ratios for TMAH and EDP[21].

## 2.3 Plasma Etching

Dry or plasma etching is a common alternative to etch silicon selectively over other materials. In plasma etching, corrosive liquids are replaced with plasmas that can etch via three processes: sputtering, chemical reaction and ion-enhanced etching. In sputtering, substrate atoms are forcibly ejected from the surface by the impinging ions, while chemical reactions rely on the reactivity of the surface atoms to those in the plasma. Both these processes are relatively slow when performed separately, but increased etch rates are observed when performed together [22]. This latter is the condition for ion-enhanced etching. The most widely accepted model for this phenomenon is that the slow chemical reactions at the surface provide a larger sputtering yield to impacting ions. The energy provided by the impacting ions subsequently goes into the reaction layer and increases the formation of volatile products which desorb from the surface.

Anisotropic etching of silicon is possible with Cl plasmas. Although the etch rate is faster, the more common fluorine based chemistries are typically isotropic, unless cryogenically cooled or side-wall passivation polymers are introduced into the system [23]. Successful anisotropic etching of Si with Cl has been performed by Juan and Pang [23, 24]. The typical dry etching recipe requires high microwave and RF power coupled with high chamber pressure and a reasonable high flow of pure Cl gas.

In this work, all attempts to plasma etch silicon were with a PlasmaQuest electron cyclotron resonance (ECR) source coupled with an RF field through chlorine gas. The ECR source couples a 2.45 GHz microwave power source with electrons accelerated by a magnetic field to large velocities. The Lorentz force causes the electrons to circulate around the magnetic field lines with the cyclotron frequency given by  $w = eB/m_e$ . For a magnetic field strength of 875 gauss, w = 2.45 GHz. As the energy coupling becomes resonant, the electrons ionize the gases present in the chamber. In the process chamber, the wafer is RF biased to control the energy of the the impinging ions across the plasma sheath.

The etchant gases are continuously fed into the chamber through mass flow controllers while a turbo pump regulates the chamber pressure. The wafer is cooled to process temperatures with a back flow of He and water cooling lines. These process parameters as well as the microwave and RF power are controlled via computer.

#### 2.4 Metallization

Thin metal films can be grown onto a substrate with a variety of methods. Common procedures include thermal evaporation and electron beam (E-Beam) evaporation. The former process involves heating and melting the metal on a resistance heater so that the evaporated atoms collect on the surface of the substrate. The metal source is usually placed into a tungsten boat or wrapped around a tungsten wire filament. A current is passed through the boat or wire, heating it and the source until the source begins to evaporate. The rate at which the metal condenses on the substrate depends on the amount of current passing through the boat and on the height above the boat at which the substrate is placed.

E-beam evaporations involve a similar process except the source is heated via a beam

of electrons. Here, the current is passed through an isolated filament and the ejected electrons are directed, with magnetic fields, towards the metal contained in a crucible. This deposition method is useful for materials with higher boiling points, like platinum (3800 °C) and titanium (3260 °C) that cannot be evaporated in tungsten resistance heaters, but require crucible s. Again, the rate of deposition depends on the location of the substrate, the current flowing through the tungsten wire, and the resulting energy in the E-beam.

The deposition takes place within an evacuated bell jar, typically at pressures  $< 3 \,\mu$ torr. The substrate is cleaned inside the chamber during evacuation with a plasma discharge. A high voltage rod in the chamber discharges electrically, ionizing all the gases in the chamber. The walls and substrate are bombarded by the highly ionized air and all excess materials are ejected off their surfaces. Usually, the evacuated chamber is backfilled with Argon gas and subsequently ionized. Because Ar is a noble gas and the atoms are heavier, the plasma scrubs the substrate more efficiently and leaves a cleaner surface. If only air is present during the discharge in the chamber, hydrogen or oxygen atoms can still cling or bond to stray molecules (eg. hydrocarbons) on the substrate without removing them from the surface.

The easiest method to measure the deposition rate as well as the thickness of the metal film is with a crystal thickness monitor. This device measures the frequency of oscillation of a quartz crystal which is placed as close to the substrate as possible. As materials are deposited onto the crystal, the frequency of oscillation changes slightly depending on the thickness of the film. Using this device during deposition, it is possible to monitor the deposition rate (and to control the rate by adjusting the current through the boat or wire) and measure the thickness of film to within a few angstroms. Once the desired thickness is achieved, the evaporation can be stopped immediately with a manually controlled mechanical shutter that is moved in front of the substrate.

#### 2.4.1 Metal Lift-off Process

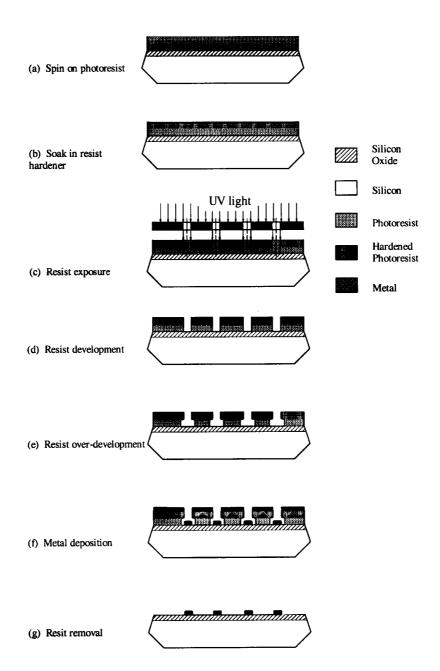

To metallize detailed structures onto the substrate, slightly modified additive photolithography, sometimes called the metal lift-off process, is used. The changes to the lithography process (as shown in Figure 2.4) occur during the photoresist exposure and development stages, before the metal is deposited.

Prior to the soft bake and exposure to UV light, the wafer can be soaked in a hardening solution so that the upper portion of the photoresist layer becomes more resistive to the developer as indicated by the heavier crosshatch in (b). Once baked and exposed (c), the polymerised regions are removed in the developer (d). Letting the wafer soak in the developer (e) for an extra 2-3 minutes overdevelops the lower unhardened portions of the resist, leaving the upper portions to form a small overhang. The opening remains the same thickness as what was on the mask, but the overdevelopment ensures that the final metallized pattern (f) is not in physical contact with the resist layer. This allows an easy removal of the resist (g) in acetone. Note that in Figure 2.4, the photoresist layer has been drawn thicker for clarity and is not drawn to scale. In fact, we do not always overdevelop the resist so that we can strip out the SiO<sub>2</sub> layer and deposit the metal directly onto the Si.

Figure 2.4: Modified additive photolithography for a metal lift-off process. See text for details. (Not drawn to scale)

### Chapter 3

# Fabricating the Mesh Structure

The main goal of this work is to produce bolometers that would be less susceptible to cosmic ray hits, but remain as sensitive to microwaves as the BAM sapphire chip bolometers. Consequently, a large part of this work involves investigating micromachining techniques which would lead to a thin free standing mesh held in place by a few supports with low thermal conductance. While it is possible to obtain whole Si wafers of thicknesses down to  $2\,\mu\text{m}$ , it is much easier and cheaper to work with regular wafers (with thicknesses  $\sim 450\,\mu\text{m}$ ) that are less fragile. In this case, it is necessary to remove the majority of the wafer thickness over a small area to leave a thin membrane, surrounded by a thicker frame for handling. From the suspended thin membrane, the bolometer substrate can be defined into a mesh structure like that of Figure 1.8.

This chapter details various attempts, via wet etching, to construct suspended membranes ranging in thickness from  $2\,\mu\mathrm{m}$  to  $\sim\!100\,\mu\mathrm{m}$ . The subsequent steps to micromachine the mesh structures via wet etching and plasma etching are also examined for meshes of various dimensions. The suppliers from whom the wafers were purchased are listed in Appendix B.

#### 3.1 Using Etch Stop Layers to Form Thin Membranes and Meshes

It is easiest to thin the wafer in small areas with an anisotropic wet etch. Square openings made into one side of a <100> wafer will etch into the wafer leaving straight but sloped side walls and will only stop at the etch-stop layer if one is present as a part of the wafer.

The result is a thin square membrane with a frame which is as thick as the original wafer.

One possible method to stop the wet etch is to have the membrane layer be of material that will not be etched. This can be achieved by depositing the bolometer substrate material directly onto the Si wafer as Mauskopf et. al. do by depositing a uniform layer of Si<sub>3</sub>N<sub>4</sub> to a specific thickness [15]. Due to a lack of facilities, this was not an option for us. One could however, heavily dope the wafer with boron atoms prior to backetching. Since heavily doped Si is not etched by EDP, but can be etched with TMAH, the membranes can be defined with an EDP etch, and the square grid structures with the TMAH.

A different approach to the problem involves processing a triple-layered wafer rather than a simple double-side polished wafer. Commercially available triple-layered wafers have an additional layer of oxide between the bulk (handle) wafer and the membrane (device) layer. Thus, the thin membrane is already present and the bulk wafer may be removed in EDP with the intermediate oxide layer acting as the etch-stop layer which can be removed at a later step.

While these processes seems fairly straight-forward, the question of how to regulate the thickness of the membrane remains unresolved. Boron doping generally penetrates the wafer to a depth of 5  $\mu$ m, but the concentration of the doping drops off with the depth, so the thickness is variable. The second method involving a buried intermediate layer is more promising as the device layer thickness can be specified to the wafer manufacturer. The following sections describe the experiments performed to evaluate both methods.

#### 3.1.1 Heavily Boron Doped Si

Silicon wafers can be doped by baking them in a furnace at high temperatures next to an activated boron source. The source ejects boron atoms which lodge themselves into the silicon crystal structure. A subsequent oxidation step drives the boron atoms into the wafer and also forms protective oxide layers for the later EDP and TMAH etches.

Initially, 3 single side polished (SS) wafers and 3 double side polished (DS) wafers were cleaned in a series of hot baths containing hydrogen peroxide with ammonium hydroxide, buffered hydrofluoric acid, and finally hydrogen peroxide with hydrochloric acid. This cleaning procedure removes organic materials, native oxides and metals from the surfaces of the wafers and should be performed immediately prior to placing the wafers in the furnace for doping and oxidation.

Once cleaned, the wafers were loaded into a furnace boat, containing boron sources. Two wafers were placed on either side of each source with the the polished surfaces facing the source. Dummy scrap wafers were placed in the unused boat slots next to the extra boron sources. The boat was slowly pushed into the furnace after which the furnace was ramped to an operating temperature of 975 °C. The boron diffusion was stopped 40 minutes after the temperature stabilized. The furnace temperature was then ramped down to 750 °C and the boat slowly pulled out. The target doping concentration was  $10^{19}$  atoms/cc, but the actual average concentration for the six wafers was determined from 4-probe resistance measurements to be  $\sim 10^{18}$  atoms/cc. This was thought to be an acceptable doping level to act as an etch stop layer so the wafers were removed from the boron furnace boat and placed into the oxidation boat. The boat was then slowly pushed into the furnace and oxidized in a wet oxygen environment. A 0.3  $\mu$ m layer was grown onto the wafers.

Each wafer was then processed individually with various micromachining steps in order to find a repeatable process that would lead to the desired free standing grid structure (with a grid spacing of  $385 \,\mu\mathrm{m}$  and  $35 \,\mu\mathrm{m}$  wide lines) held to the support frame by 4 legs, 1 mm long, running diagonally from the outside corners of the mesh to the frame.

For the first SS wafer, large open areas were patterned and etched into the unpolished

side for 6.75 hours in EDP. It was believed that the etch would proceed through the wafer, forming sloped sidewalls until it encountered the heavily boron doped Si where the EDP would cease etching. When the wafer was pulled from the solution, it was observed that for the majority of the open areas, there was a thin membrane of uneven thickness that transmitted reddish wavelengths. However in some locations, the membranes had either been etched through or had many tiny pinholes. This was attributed to uneven doping levels across the wafer. Next, the polished side of the wafer was patterned to create the mesh structure. Since EDP does not etch the doped membrane, the wafer was placed in a hot bath of TMAH instead. Due to lack of foresight, the TMAH proceeded to etch the membrane from both sides and as a result, the membranes were eaten through before the mesh was well defined.

The second SS wafer was patterned to open up the back windows but for unknown reasons, the doped layer was insufficient as an etch stop layer and the etch ate through the entire wafer after 6.5 hours. It was suspected that the boron source was the culprit because the DS wafer on the other side of the same source also exhibited strange reactions to conventional etches. With this DS wafer, the oxide on the doped side of the wafer would not etch in HF (possibly some kind of borosilicate glass was formed) so the mesh pattern could not be defined into the membrane. This was not investigated further and we proceeded with the second DS wafer.

It was thought that the middle oxidation step could be skipped if the mesh was first patterned, and then the backside opened up and etched. In this manner, the EDP would only attack the open areas from the back, and would not laterally etch the mesh legs. The boron doped side of the second DS wafer was successfully patterned and etched in TMAH however the back side was not etched in EDP. It was unclear how it would be known when the meshes were released from the back silicon because the etch could not be monitored. Also, because the support legs of the mesh were diagonal, they would be

etched away by the EDP. So this step-saving idea was abandoned and we returned to the original plan. The last DS wafer was opened up in the back and etched for 6.75 hours. Some membranes were etched through, but the majority were intact and transmitted red light evenly. The wafer was cleaned, reoxidized and the doped side patterned for the mesh. After 42 minutes in the TMAH, a few grids were defined and held in place by the support legs and the back oxide. The wafer was pulled from the bath and the oxides removed with a 10 minute dip in HF.

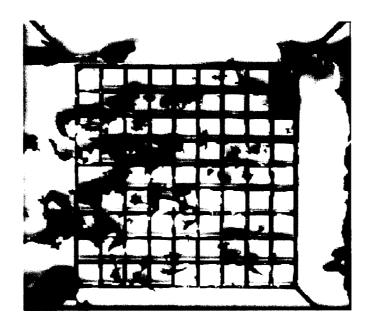

Of the 54 devices patterned into it, only 2 membranes led to free standing meshes. The rest of the devices were either under etched or over etched. Figure 3.1 is a scanned photo of one of the meshes. Clearly, these were not entirely etched to completion and there is still residual Si to be removed from the backside of the mesh. However, the result seemed promising. One reason that more than half the grids were lost was due to the fact that the 4 mesh support legs were patterned to be diagonal instead of square and so were being laterally etched by the TMAH. This could be remedied by remaking masks with a grid design like that of Figure 1.8.

A new mask was made and printed on linotronic film. The mesh consisted of  $35 \,\mu\text{m}$  wide lines with a  $385 \,\mu\text{m}$  grid spacing and four, 1 mm long, square support legs arranged as in Figure 1.8. The unpolished side of the wafer was patterned and etched in EDP, for 6.75 hours, to open up large square windows as before. However, in this instance, the membranes seemed rather thick and did not transmit red light. The second oxidation step used before to protect the back side of the membrane was skipped so that the membrane could be thinned out as the mesh was defined.

Once the polished side had been patterned for the mesh structure, the wafer was placed in TMAH for a total of 3.25 hours. Because the TMAH etchant is clear, the progress of the etch could be monitored without pulling the wafer from the bath. After the first 2.5 hours, the etch seemed to be progressing unevenly across the entire wafer and

Figure 3.1: First free-standing Si mesh made by back etching a wafer to a heavily boron doped Si etch stop layer. The mesh defining etch was not quite complete as there is still some leftover Si on the backside of the grid area. The outside Si frame is not shown.

even across individual membranes. Approximately 1/3 of the devices located randomly across the wafer, had already etched completely through from the back side, while the remaining membranes were wholly intact, that is, the mesh structures could be seen etched into the membrane, but the backside was not yet cleared out. When the etch was stopped, there were 2 fully intact and free-standing meshes, while 12 other devices required a longer etching period. The wafer was diced and the other chips were etched individually in the TMAH, until their grids were fully released from the back silicon.

Pictures were taken of some of these free standing meshes. While the etched membrane appears cleaner than those in Figure 3.2, the uneven etch from one side of the membrane to the other cannot be ignored. The wider legs in the lower left hand side are a result of an uneven membrane thickness. The mask that defined the lines were all  $35 \,\mu\mathrm{m}$  wide, but since the etch progresses at a sloped angle, the backside of the legs are much wider. Thus the difference in width is an indication of a difference in the membrane

thickness from the lower left hand side to the upper right hand side of the mesh. When examined with a profilometer, the thickness of the membranes were close to  $90\,\mu\mathrm{m}$  at the thickest regions. Clearly this is not a repeatable nor controllable process. The thickness of the membrane cannot be predetermined and the quality of the resulting grids are variable. This method of mesh fabrication is not at all useful for building bolometers with controlled dimensions and so it was abandoned.

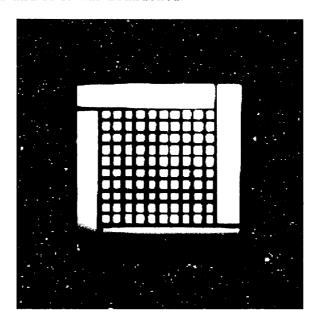

Figure 3.2: A mesh and it surrounding Si frame from the second successful attempt to make free standing meshes from a doped Si membrane. The uneven etching is apparent from the wider legs in the lower left hand corner as compared to the upper right hand corner. The membrane was measured to be as thick as  $\sim 90 \, \mu \text{m}$ .

### 3.1.2 Buried Oxide Layer

Because of the demands of the silicon integrated circuits technology, newer wafers are now available which have insulator layers sandwiched between two single crystal silicon layers. Such wafers consist of a regular handle wafer  $450-500 \,\mu\mathrm{m}$  thick, bonded to an insulating material such as silicon nitride or silicon dioxide. A second Si wafer is bonded to the

insulator and polished down to the desired device layer thickness. These wafers can be purchased with a variety of specifications including handle and device layer thicknesses, crystal orientations and resistivities, as well as the type of insulator material and its thickness.

We were able to acquire three types of these triple layer wafers that had buried oxide (BOX) layers. Their specifications are given in Table 3.1. Because we were ordering in small quantities, we purchased < 100 > wafers that had appropriate device layer thicknesses and that were readily available from stock inventory.

| Device             | Layer                   | Handle Wafer       |                         | BOX               |  |

|--------------------|-------------------------|--------------------|-------------------------|-------------------|--|

| thickness          | ρ                       | thickness          | ρ                       | thickness         |  |

| $(\mu \mathrm{m})$ | $(\Omega  \mathrm{cm})$ | $(\mu \mathrm{m})$ | $(\Omega  \mathrm{cm})$ | $(\mu\mathrm{m})$ |  |

| 2.25               | 10-20                   | 381                | 10-20                   | 0.2               |  |

| 6.5                | 20-30                   | 375                | 10-20                   | 0.2               |  |

| 5.0                | 150-250                 | 525                | 2-30                    | 1.0               |  |

Table 3.1: Relevant specifications for the three BOX wafers used in this work.