# ON THE FEASIBILITY OF USING STARLAN TO IMPLEMENT THE FASTBUS SERIAL NETWORK

$\mathbf{B}\mathbf{y}$

Richard Cam

B. A. Sc. (Engineering Physics) University of British Columbia

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

PHYSICS

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

October 1988

© Richard Cam, 1988

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of PHYSICS

The University of British Columbia Vancouver, Canada

Date 28 OCTOBER 1988

#### Abstract

During the inception of FASTBUS, an autonomous data link, informally known as the FASTBUS Serial Network, was conceived as an auxiliary communications channel to be used in diagnostic applications for debugging FASTBUS systems. Since then, there have been several attempts at implementing this serial network, all of which have produced somewhat mixed results.

This thesis describes the latest attempt to implement a prototype FASTBUS serial network. By using a new LAN specification called StarLAN, some promising results have been obtained. These results show that StarLAN can be successfully adapted to implement the serial network without requiring major modifications. Furthermore, StarLAN seems to have the desirable characteristics of simplicity, low cost, an 'acceptable' data rate, and having multiple vendor support — advantages that previous implementation attempts had not possessed simultaneously. As such, StarLAN is the most promising solution to the serial network problem to have appeared so far.

This document will begin with a background discussion of FASTBUS, the FASTBUS Serial Network, and StarLAN. It will then discuss, in detail, how the prototype network was built, followed by a description and analysis of the performance measurements that were taken. It will also discuss considerations and options for a practical implementation of the serial network, based on experience from the work done with the prototype. Finally, a summary of the key results and an assessment of the StarLAN approach is given to conclude the thesis.

It is hoped that this document will be able to resolve many outstanding questions about a StarLAN-based serial network. Perhaps, FASTBUS users can now decide on

whether or not to use StarLAN to implement the FASTBUS Serial Network.

### Table of Contents

| A  | Abstract     |         | ii                                                           |            |

|----|--------------|---------|--------------------------------------------------------------|------------|

| Li | st of        | Table   | S                                                            | vi         |

| Li | st of        | Figur   | es                                                           | vii        |

| A  | cknov        | wledge  | ment                                                         | xi         |

| 1  | Introduction |         | 1                                                            |            |

|    | 1.1          | FAST    | BUS                                                          | 1          |

|    |              | 1.1.1   | Basic Operational Description of FASTBUS                     | 2          |

|    |              | 1.1.2   | Motivation for the FASTBUS Serial Network                    | 5          |

|    |              | 1.1.3   | Historical Background of the FASTBUS Serial Network          | 7          |

|    | 1.2          | StarL.  | AN                                                           | 14         |

|    |              | 1.2.1   | StarLAN in the Framework of the OSI Model and Other IEEE 802 |            |

|    |              |         | Protocols                                                    | 15         |

|    |              | 1.2.2   | Basic Operational Description of StarLAN                     | 21         |

|    |              | 1.2.3   | StarLAN and the FASTBUS Serial Network                       | 32         |

| ٠  |              | 1.2.4   | Variations to Standard StarLAN                               | <b>3</b> 6 |

| 2  | Bui          | lding 1 | the Prototype Serial Network                                 | 40         |

|    | 2.1          | A Sim   | ple StarLAN Network                                          | 40         |

|    | 2.2          | Using   | StarLAN in a FASTBUS Environment                             | 43         |

| 3            | Mea            | surements                                                              | <b>5</b> 5 |

|--------------|----------------|------------------------------------------------------------------------|------------|

|              | 3.1            | Electrical Characteristics of StarLAN Signals in the FASTBUS Backplane | 55         |

|              | 3.2            | Network Performance Measurements                                       | 65         |

| 4            | Syst           | em Implementation Options                                              | 97         |

|              | 4.1            | Topology                                                               | 97         |

|              | 4.2            | Bit Rate                                                               | 99         |

|              | 4.3            | Access Scheme                                                          | 100        |

| 5            | Sun            | nmary of Results and General Assessment                                | 103        |

| Aı           | ppen           | dices                                                                  | 105        |

| A            | PAI            | LASM Listing, Notes on Transceiver and Hub Circuits                    | 105        |

|              | <b>A</b> .1    | PAL Device Logic Equations                                             | 105        |

|              | A.2            | Functional Description of the StarLAN-FASTBUS Transceiver              | 105        |

|              | A.3            | Functional Description of the StarLAN Hub Circuit                      | 107        |

| В            | Pho            | tographs and Table of Electrical Measurements                          | 109        |

| C            | Tab            | les of Preliminary Performance Data                                    | 129        |

| <b>D</b>     | Cal            | culation of Software Overhead Time                                     | 135        |

| $\mathbf{E}$ | Not            | es on the Automated Network Driver Program                             | 138        |

| Bi           | Bibliography 1 |                                                                        | 152        |

### List of Tables

| B.1 | Propagation delay and pulse jitter measurements                    | 110 |

|-----|--------------------------------------------------------------------|-----|

| C.2 | Network configurations for preliminary performance measurements    | 129 |

| C.3 | General transmission data for 72-byte frames                       | 130 |

| C.4 | General transmission data for 532-byte frames                      | 131 |

| C.5 | General transmission data for 1526-byte frames                     | 131 |

| C.6 | Distribution of Collision Resolution Interval for 72-byte frames   | 132 |

| C.7 | Distribution of Collision Resolution Interval for 532-byte frames  | 133 |

| C.8 | Distribution of Collision Resolution Interval for 1526-byte frames | 134 |

| D.9 | Overhead times for different field lengths                         | 137 |

## List of Figures

| 1.1  | FASTBUS Segments                                      | 3          |

|------|-------------------------------------------------------|------------|

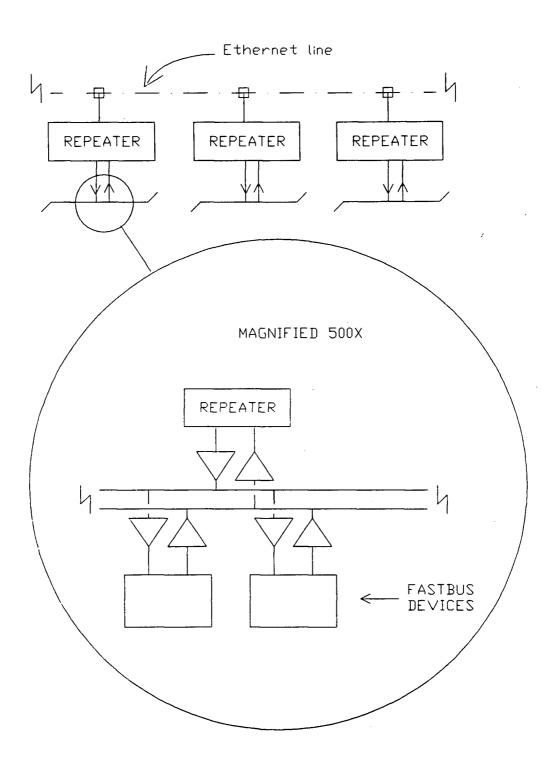

| 1.2  | Interconnected FASTBUS Segments                       | 6          |

| 1.3  | Single line direct routing scheme                     | 8          |

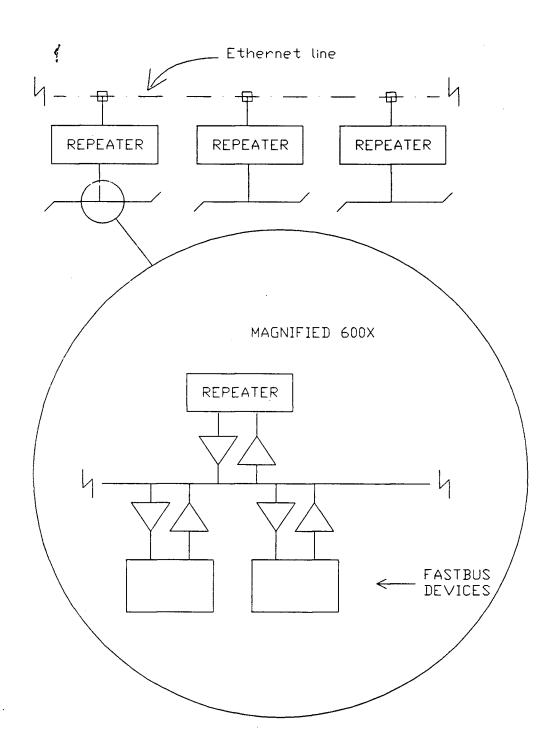

| 1.4  | Single line repeater-based scheme                     | 9          |

| 1.5  | Two-line connection                                   | 11         |

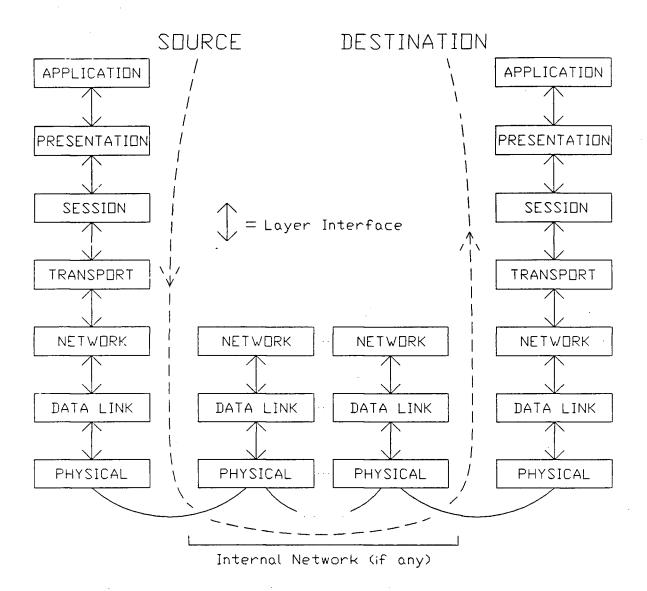

| 1.6  | OSI 7-Layer Reference Model                           | 17         |

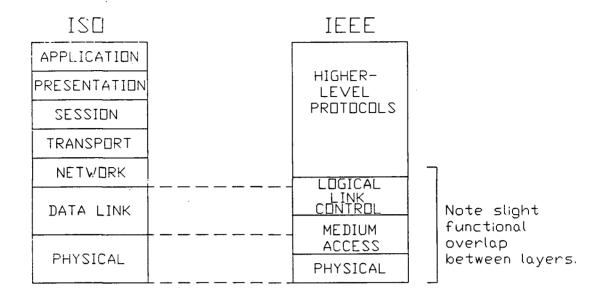

| 1.7  | IEEE Local Area Network Architecture.                 | 19         |

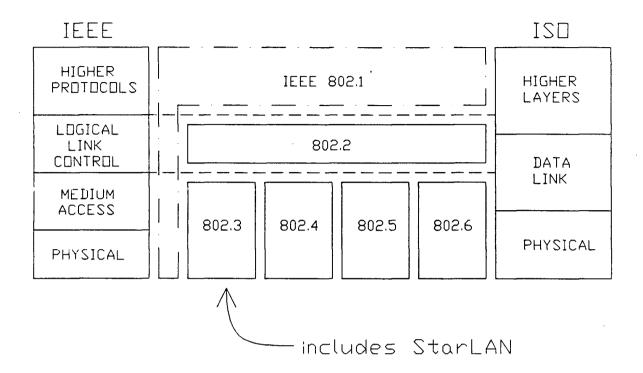

| 1.8  | IEEE 802 Protocols                                    | <b>2</b> 0 |

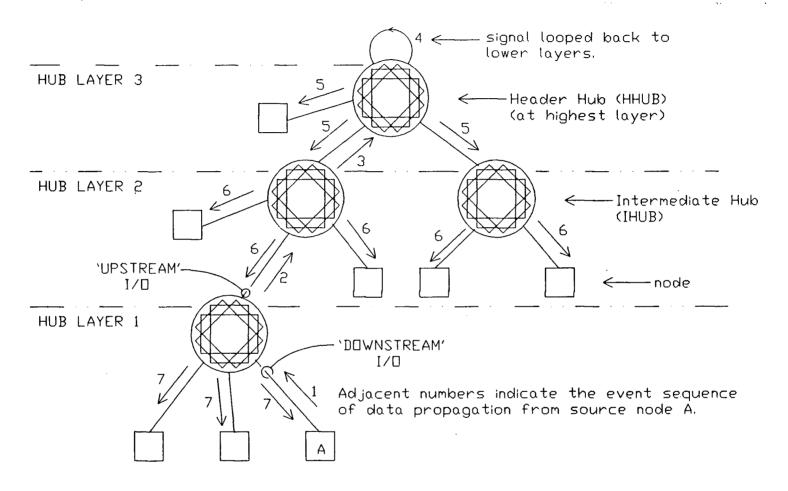

| 1.9  | Star Topology                                         | 22         |

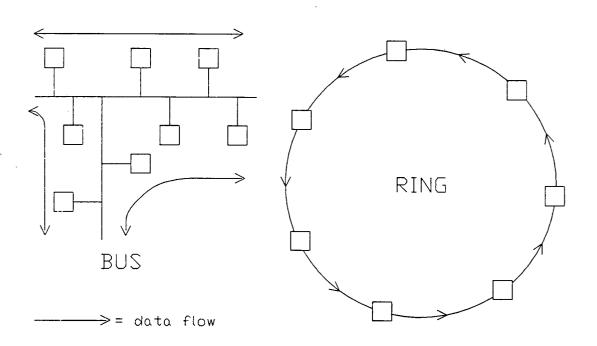

| 1.10 | Bus and Ring Topologies                               | 23         |

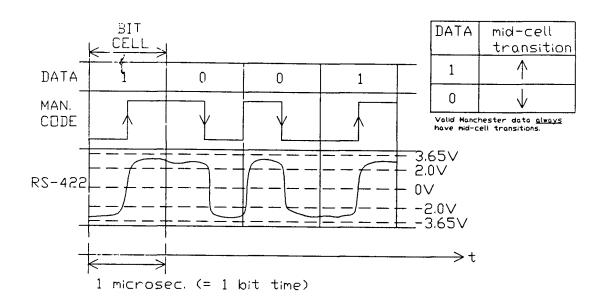

| 1.11 | Manchester Encoding and RS-422 Voltage Levels         | 24         |

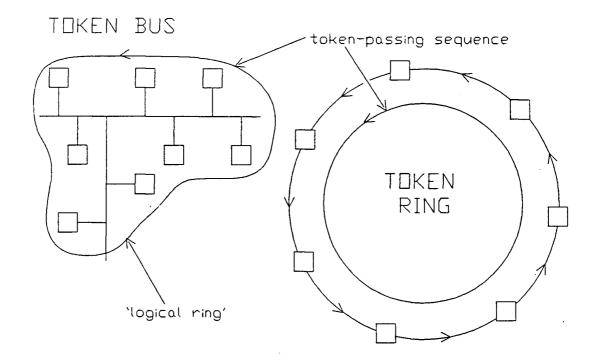

| 1.12 | Token-passing Access Method                           | 26         |

| 1.13 | StarLAN framing format                                | <b>2</b> 6 |

| 1.14 | Worst-Case Scenario for Collision Detection           | 28         |

| 1.15 | Collision Presence Signal                             | <b>3</b> 0 |

| 1.16 | Infinite Loop in a StarLAN Network                    | <b>3</b> 1 |

| 1.17 | StarLAN in an integrated office                       | 33         |

| 1.18 | StarLAN network using intra-building telephone cables | 34         |

| 1.19 | StarLAN-based serial network on FASTBUS               | 35         |

| 1.20 | Bussed StarLAN network                                | <b>3</b> 6 |

| 1.21 | Node connection schemes for bussed StarLAN            | 37         |

| 1.22 | Bussed StarLAN in the FASTBUS Serial Network                           | 39         |

|------|------------------------------------------------------------------------|------------|

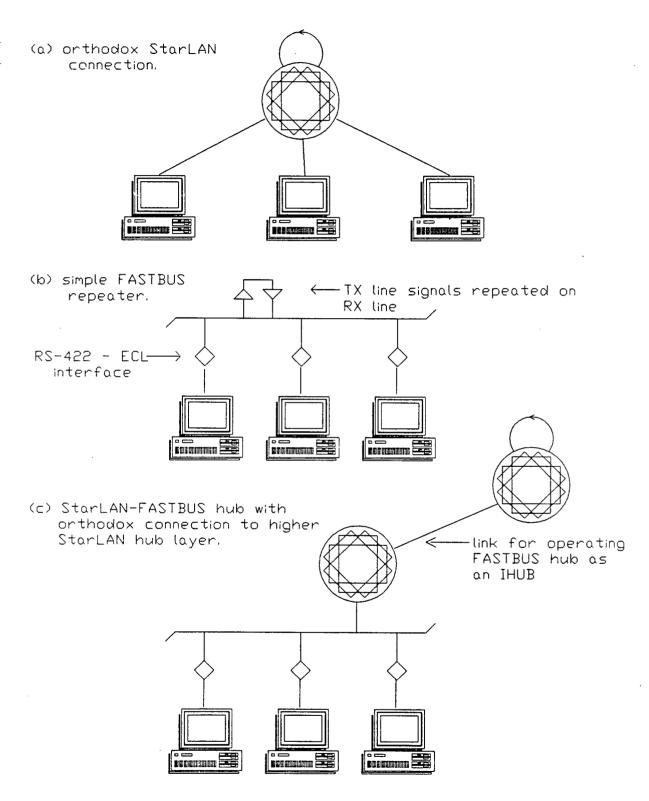

| 2.23 | StarLAN Network Configurations                                         | 42         |

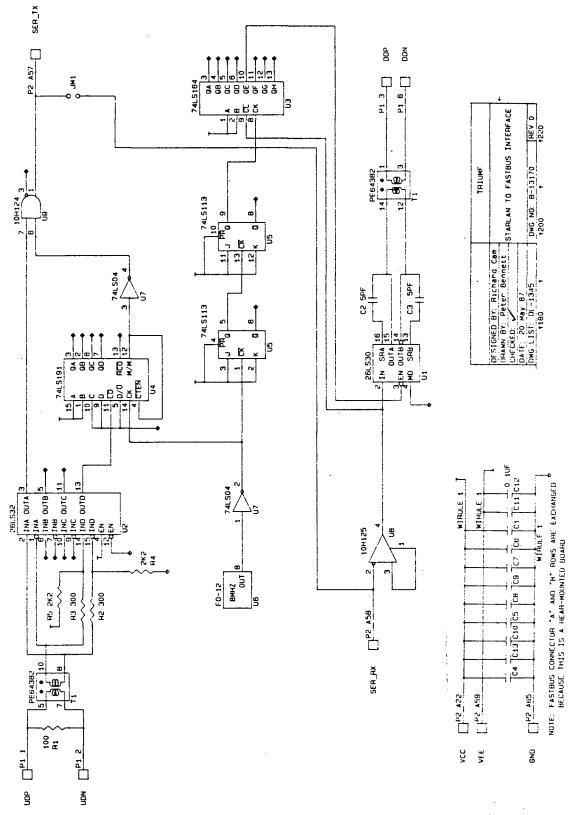

| 2.24 | Schematic diagram of the StarLAN-FASTBUS tranceiver                    | 45         |

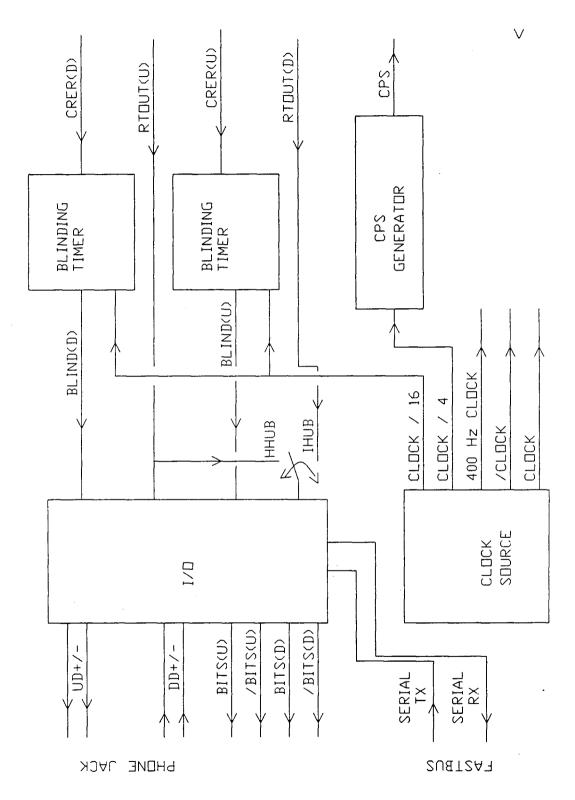

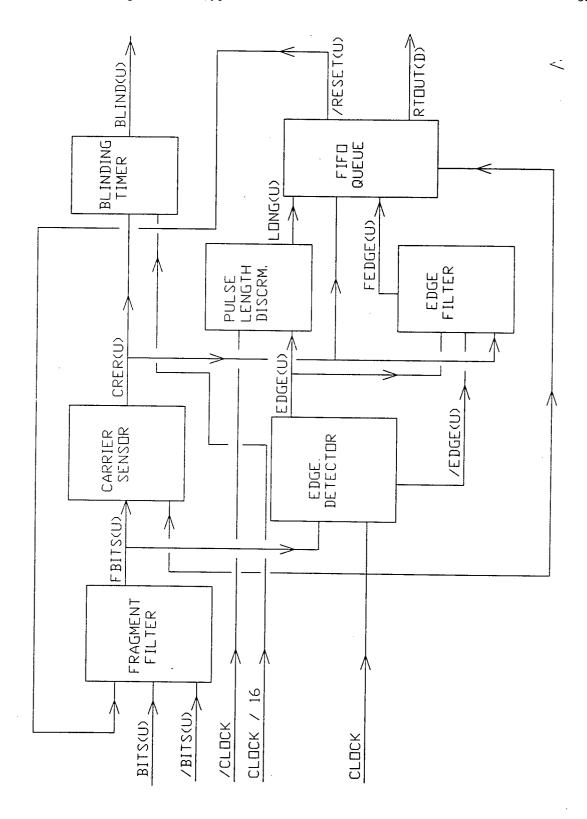

| 2.25 | Block Diagram of Hub Circuit: I/O Section                              | <b>5</b> 0 |

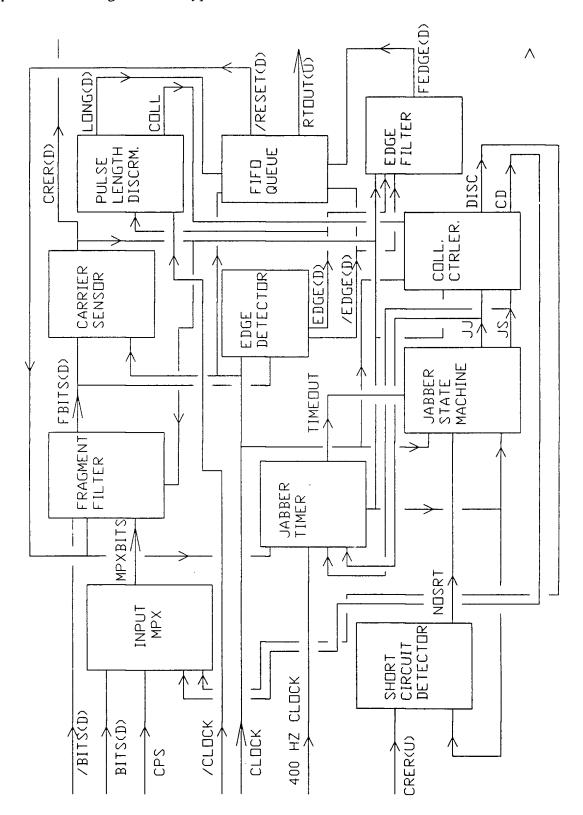

| 2.26 | Block Diagram of Hub Circuit: Downstream Section                       | 51         |

| 2.27 | Block Diagram of Hub Circuit: Upstream Section                         | 52         |

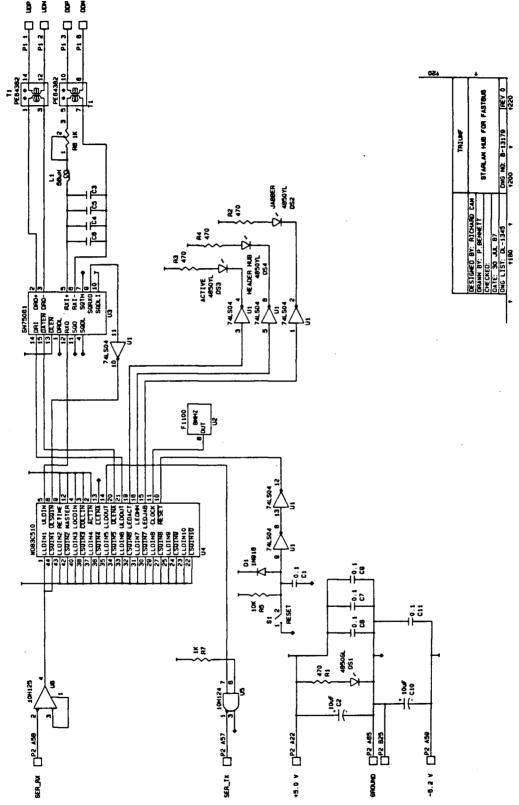

| 2.28 | Schematic Diagram of Hub Circuit with WD83C510 Controller              | 53         |

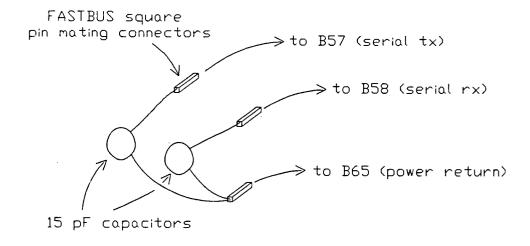

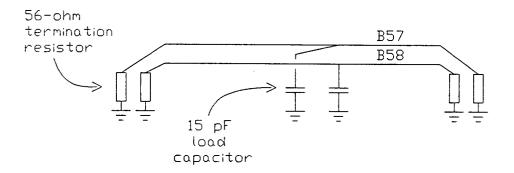

| 3.29 | Sample capacitor load for the FASTBUS backplane                        | 58         |

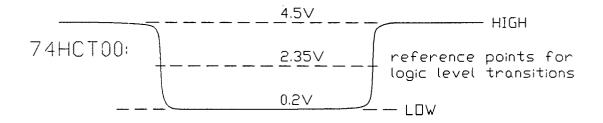

| 3.30 | Reference points for edge transitions                                  | <b>6</b> 0 |

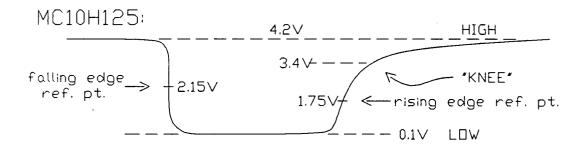

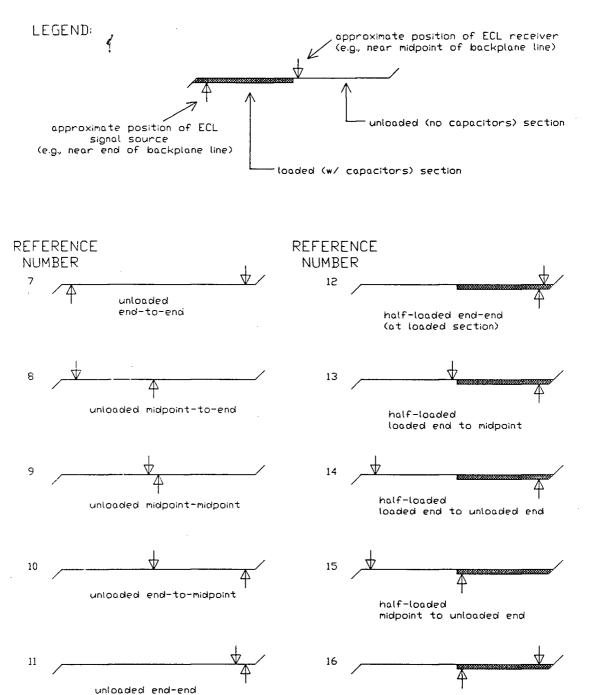

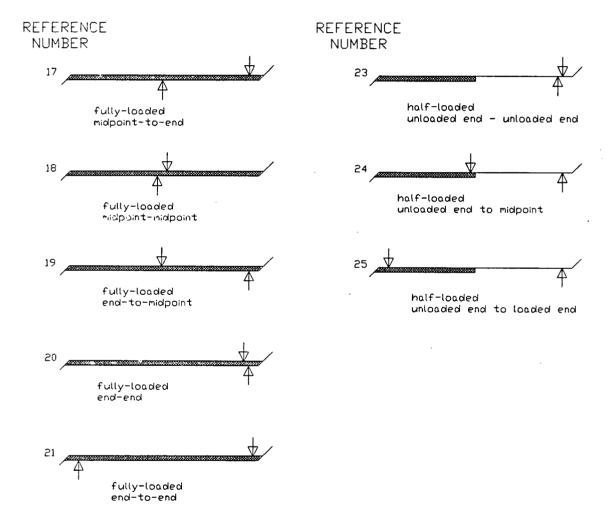

| 3.31 | Schematic diagram of electrical measurements                           | 62         |

| 3.32 | Schematic diagram of electrical measurements (continued)               | 63         |

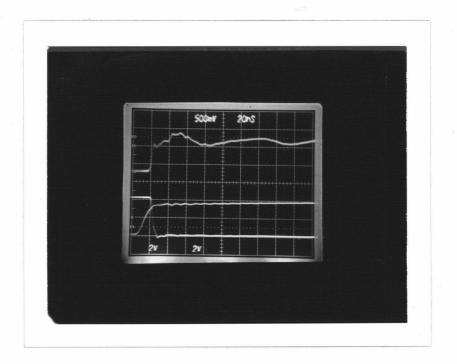

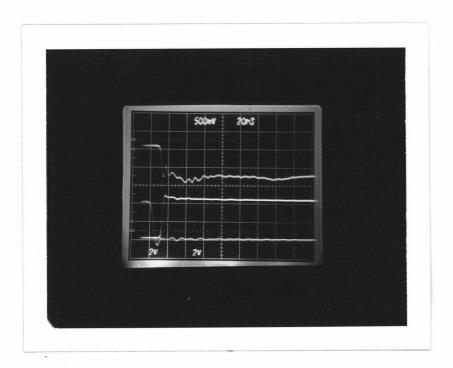

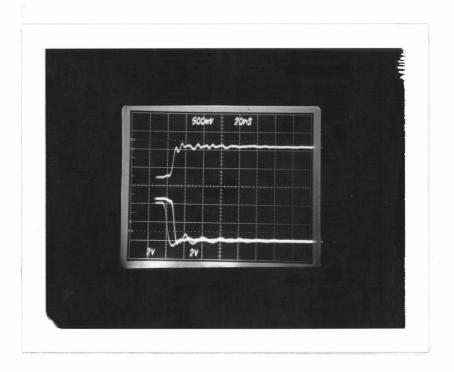

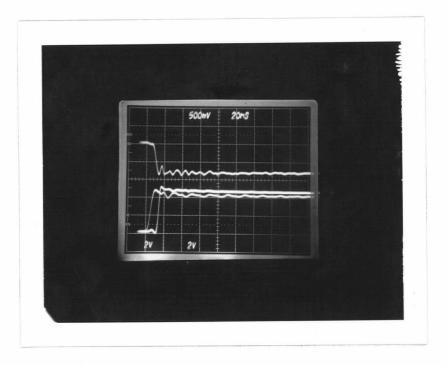

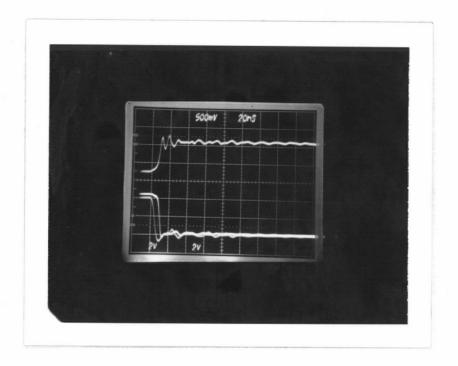

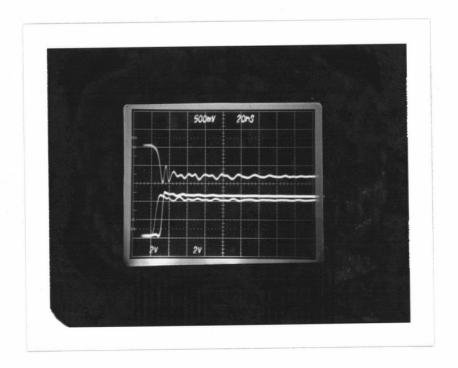

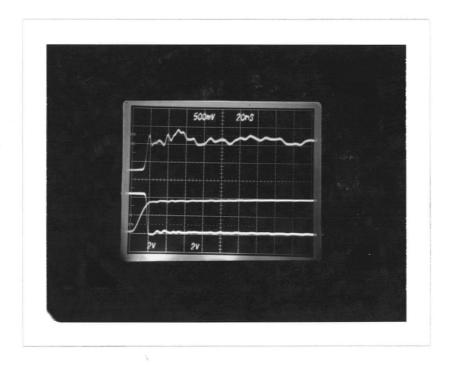

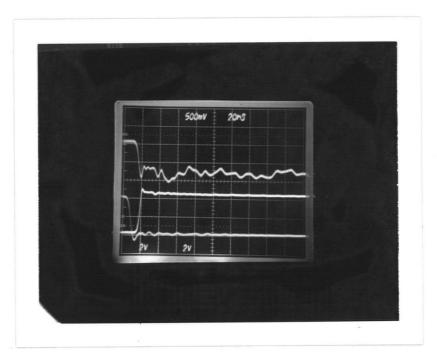

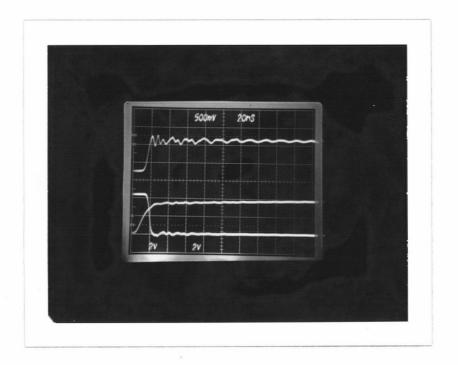

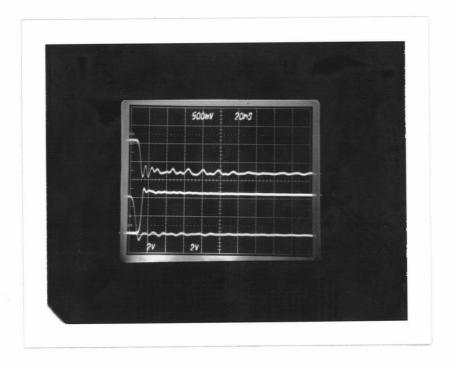

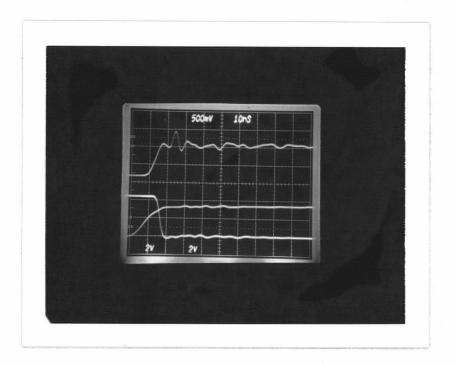

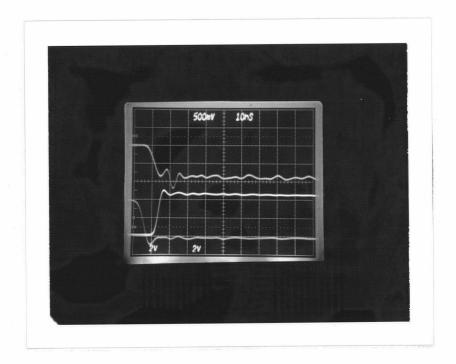

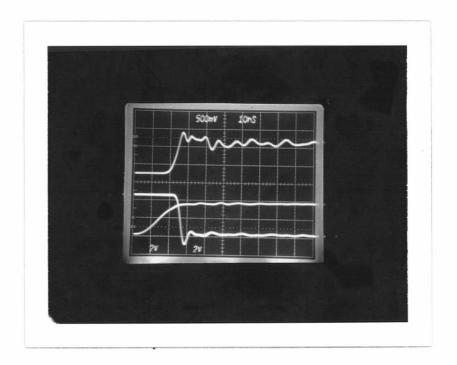

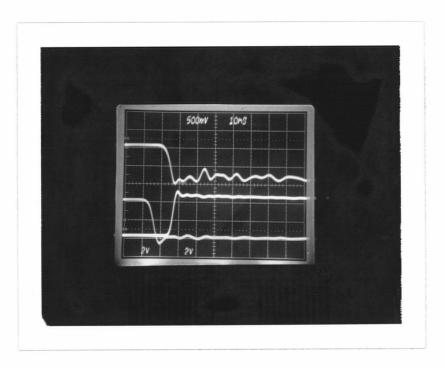

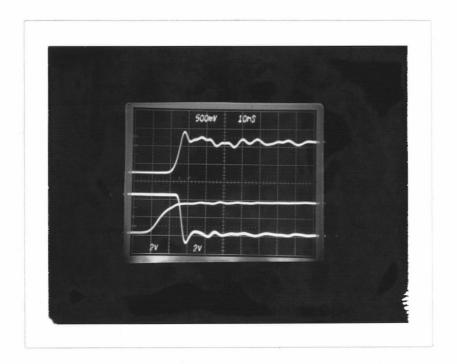

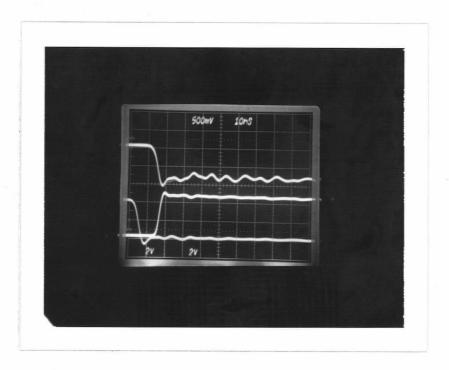

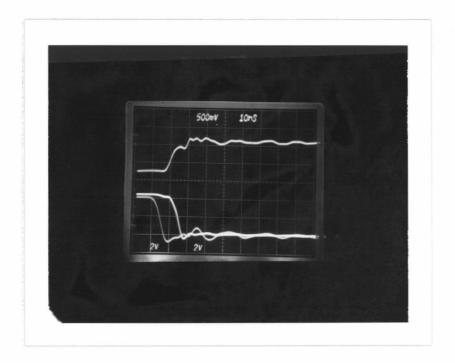

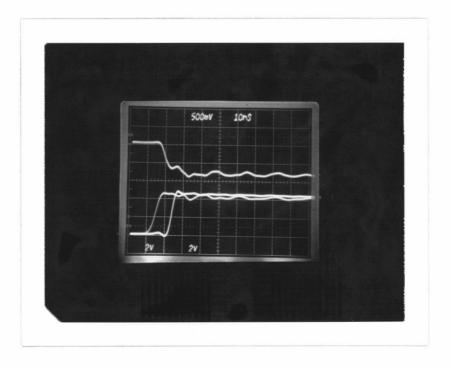

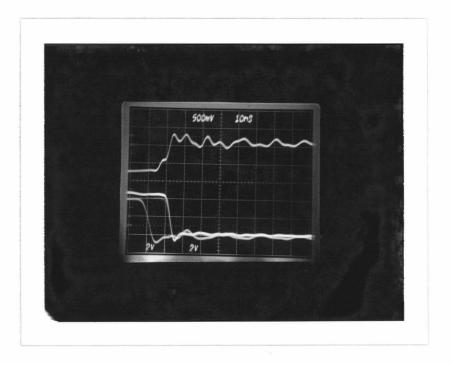

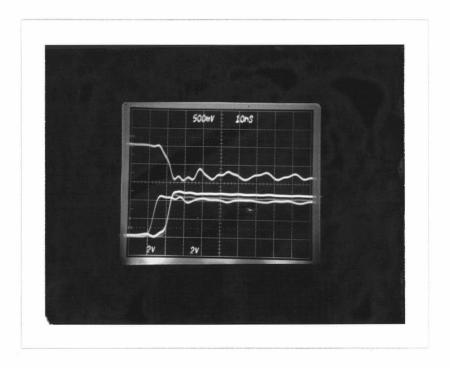

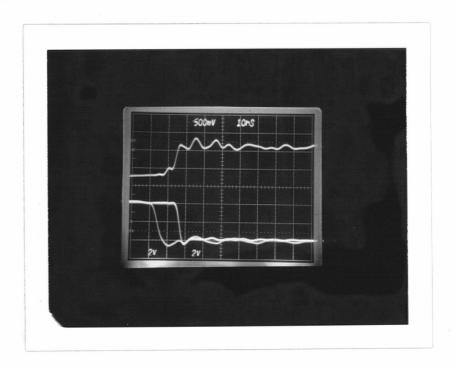

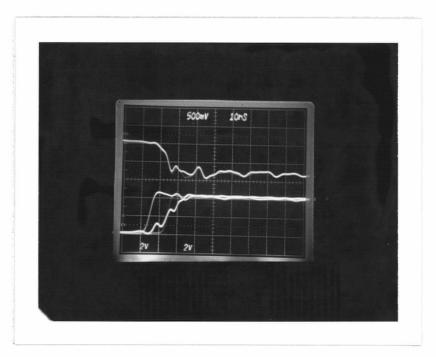

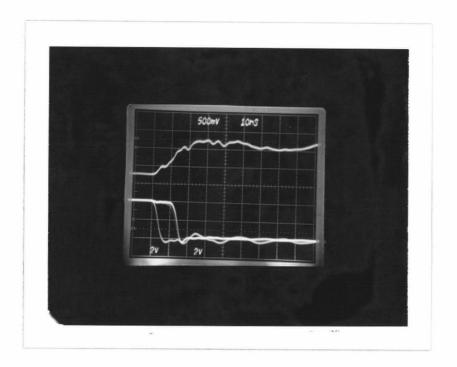

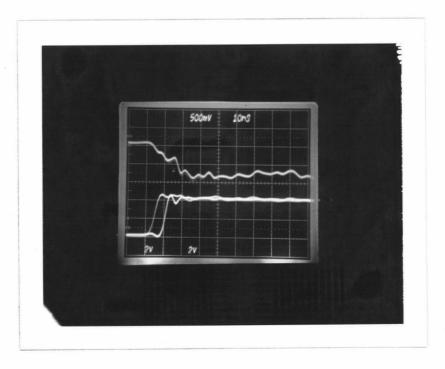

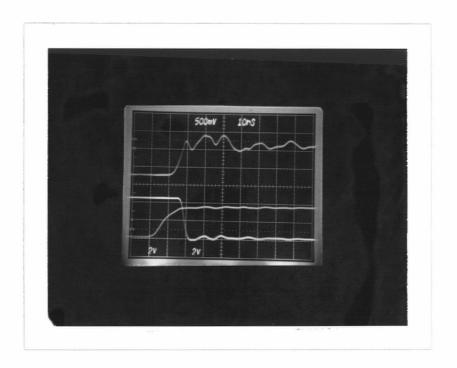

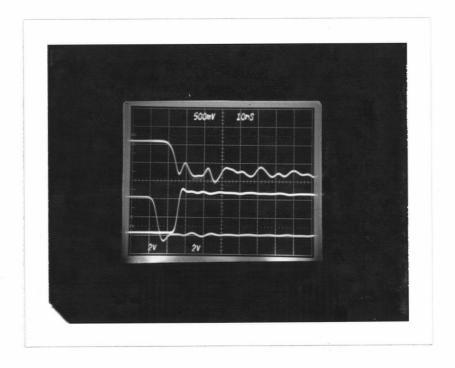

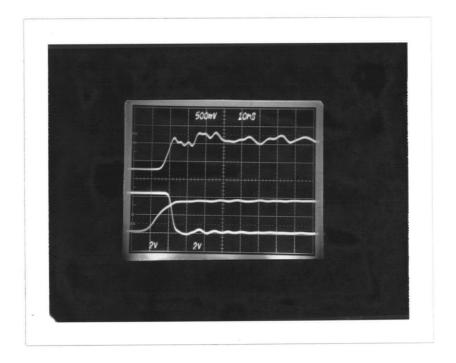

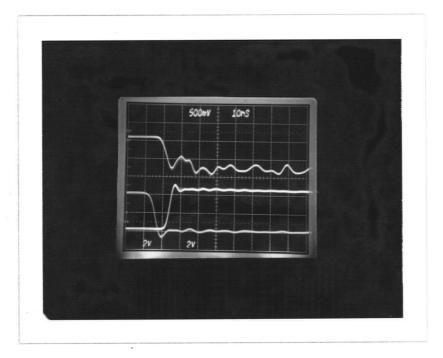

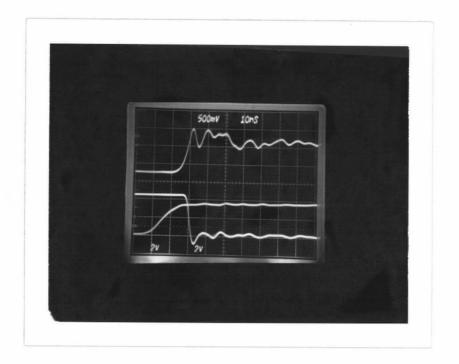

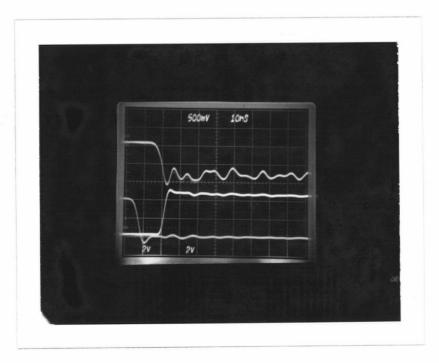

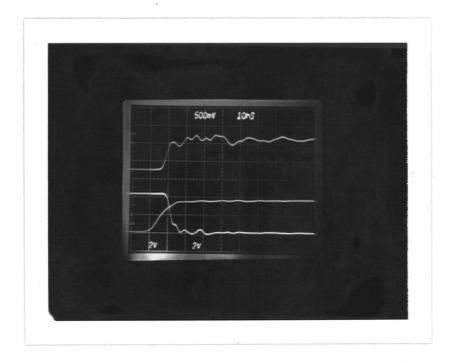

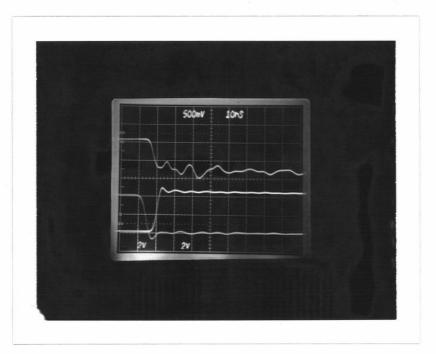

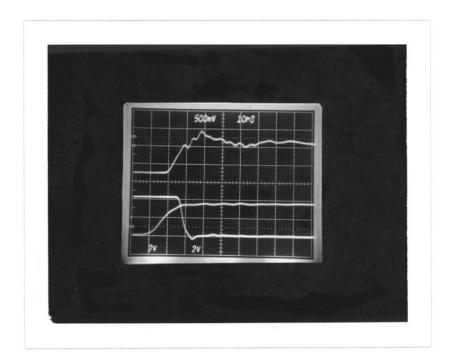

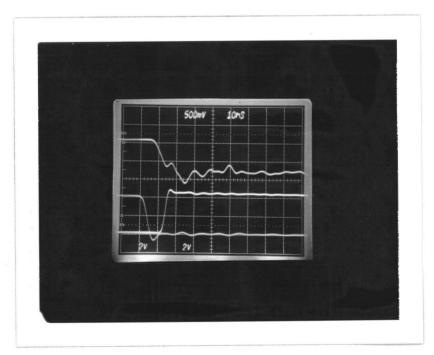

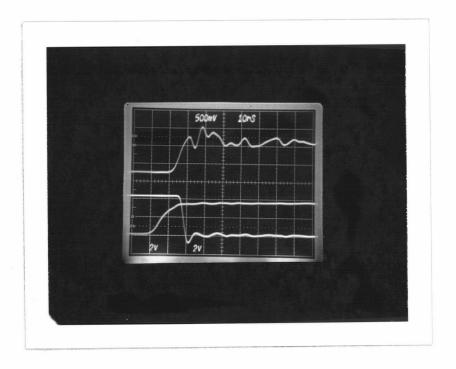

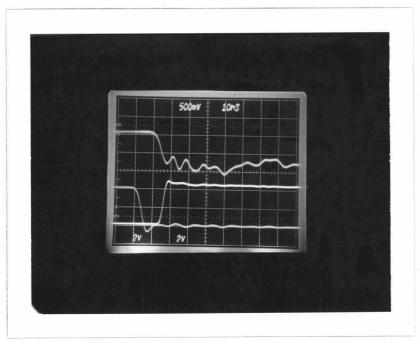

| 3.33 | Typical oscilloscope traces (ref. 25)                                  | 64         |

| 3.34 | Oscilloscope trace of bumpy edge transition (ref. 17)                  | 65         |

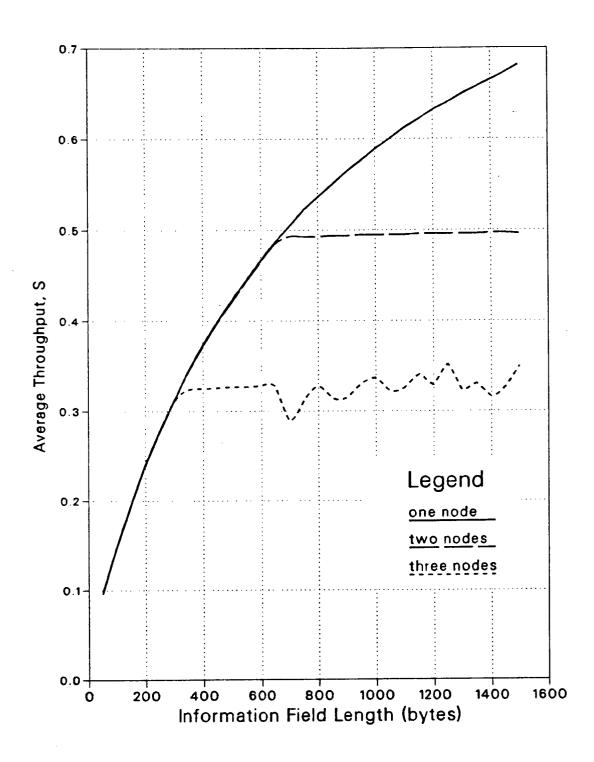

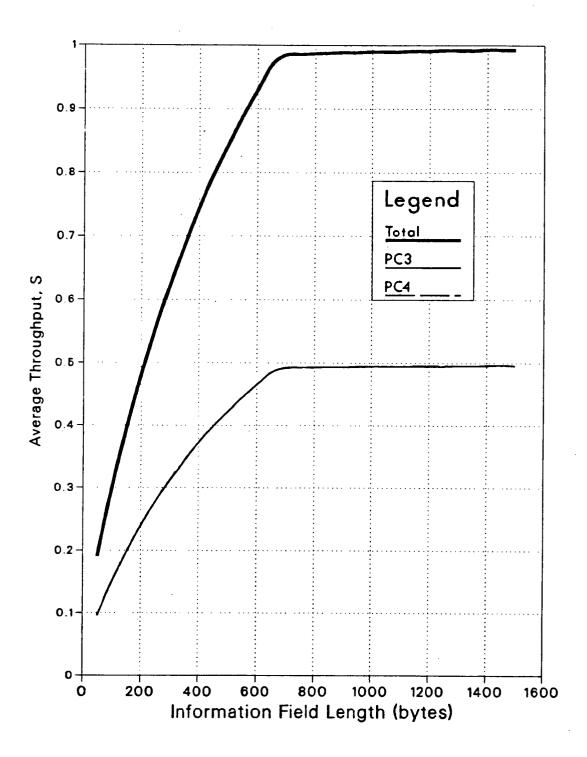

| 3.35 | Average throughput for a single-PC network                             | 72         |

| 3.36 | Average throughput for a 2-PC network                                  | 74         |

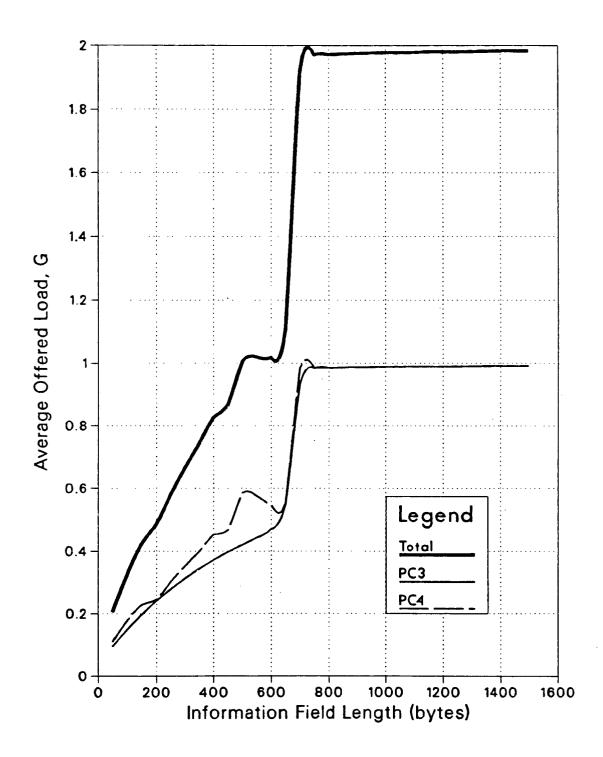

| 3.37 | Average offered load for a 2-PC network                                | 75         |

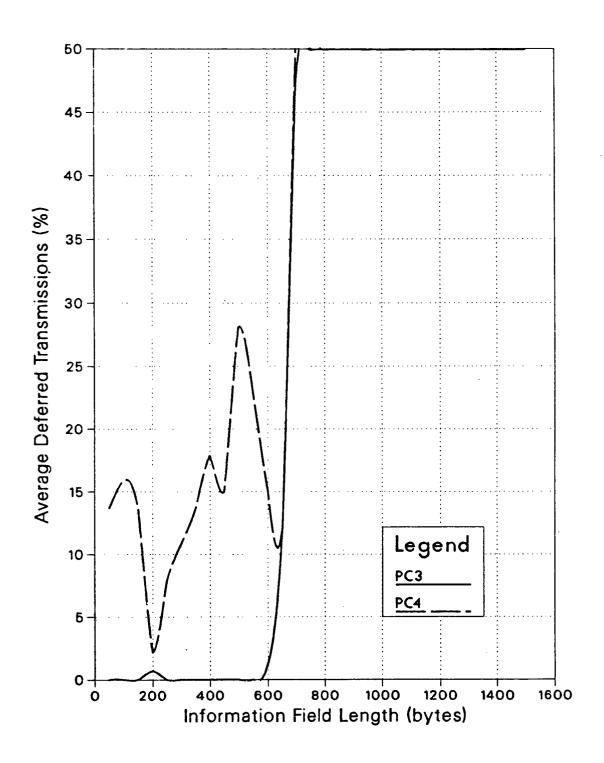

| 3.38 | Number of deferrals expressed as a fraction of offered load            | 76         |

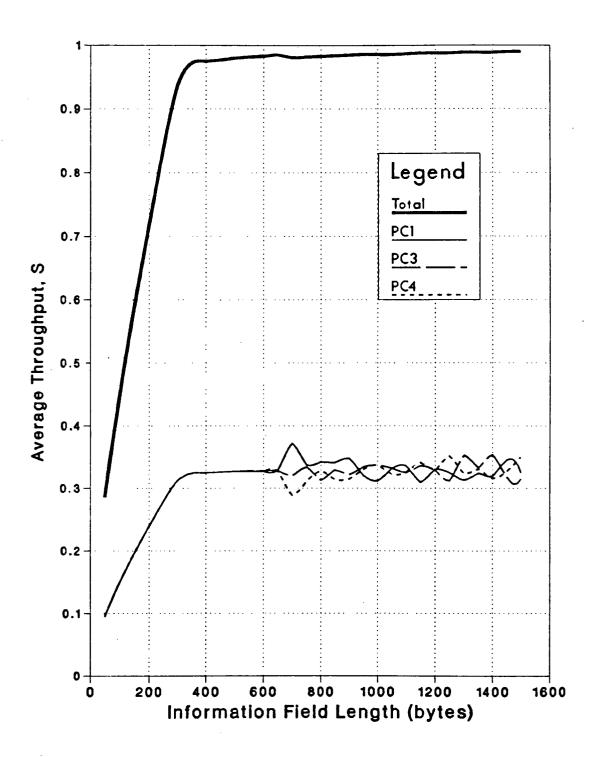

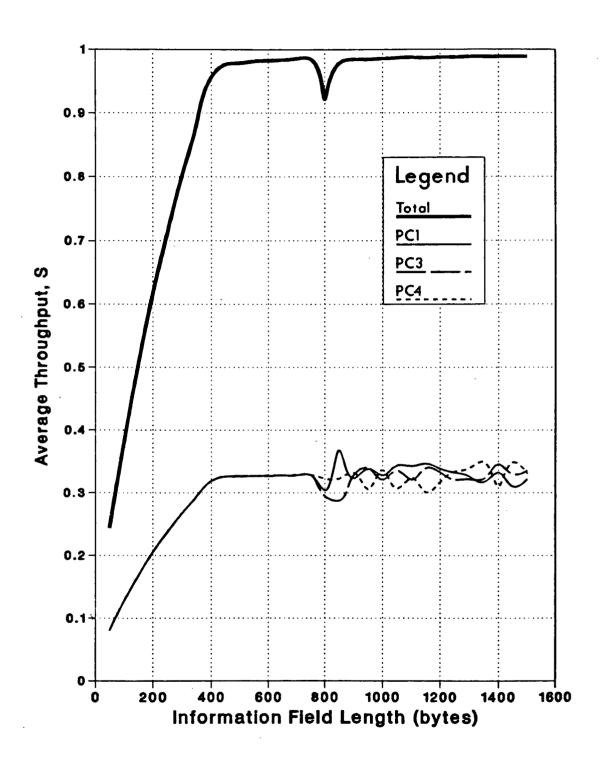

| 3.39 | Average throughput for a 3-PC network without frame receptions         | 80         |

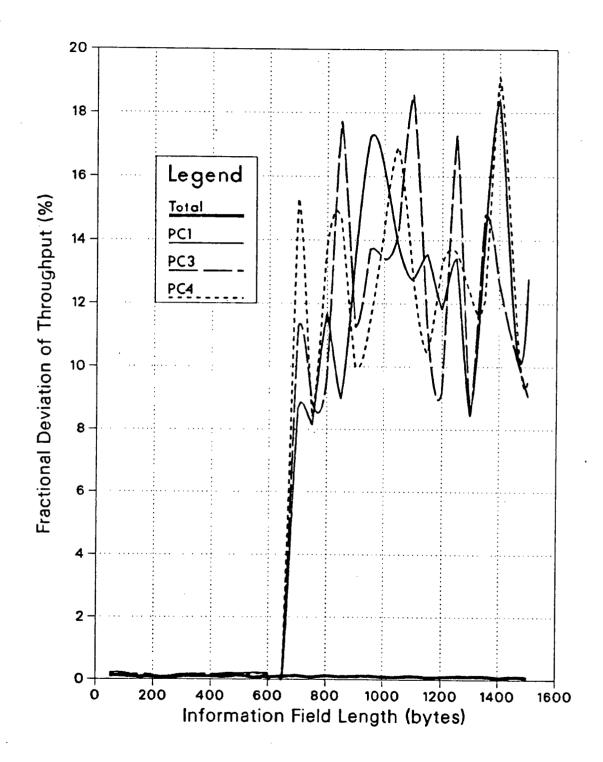

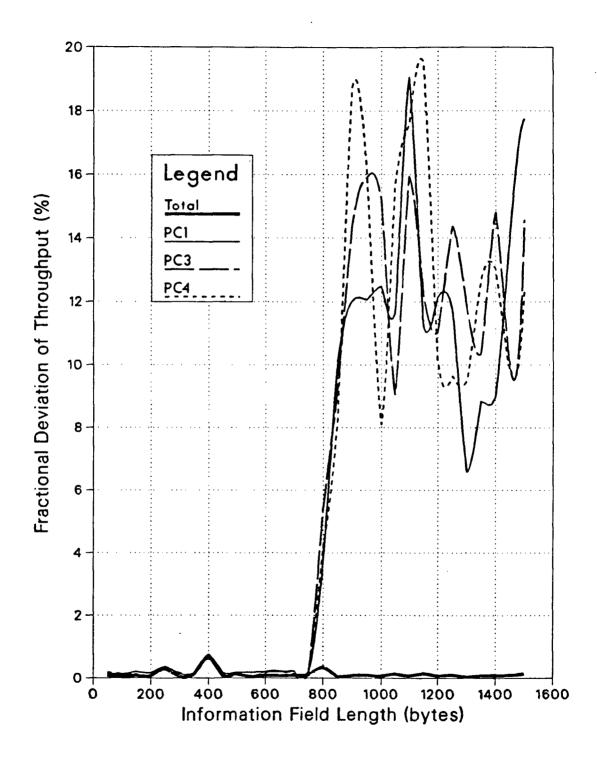

| 3.40 | Fractional standard deviation of throughput                            | 81         |

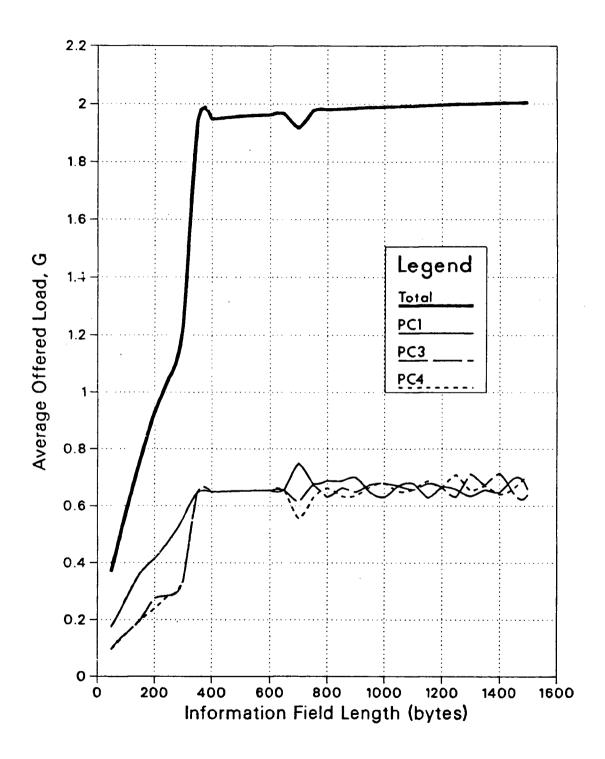

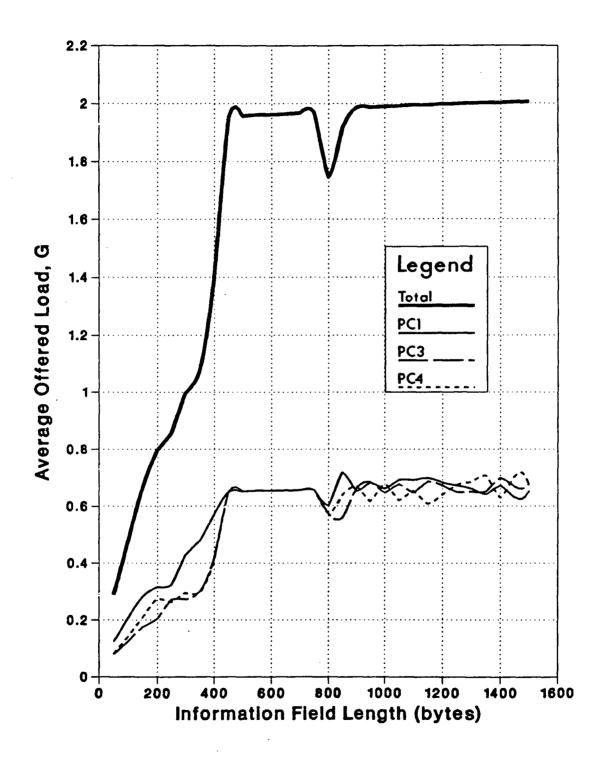

| 3.41 | Average offered load for a 3-PC network without frame receptions       | 82         |

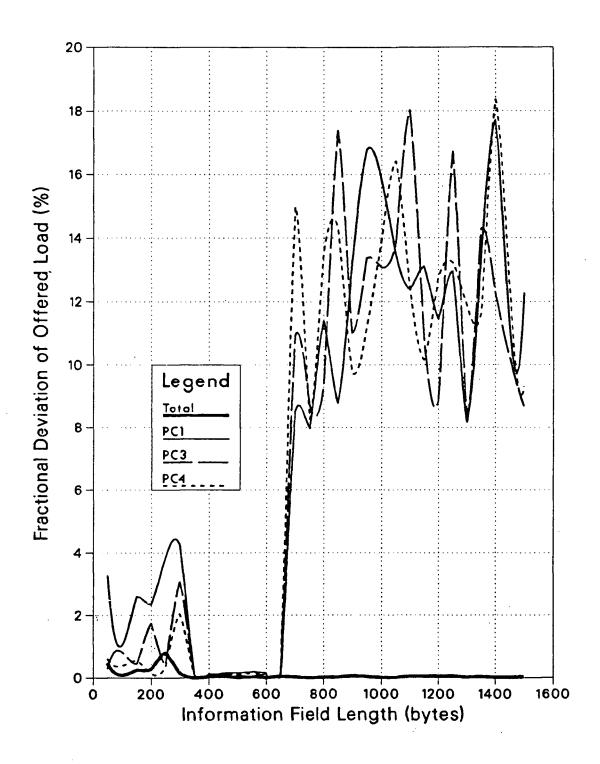

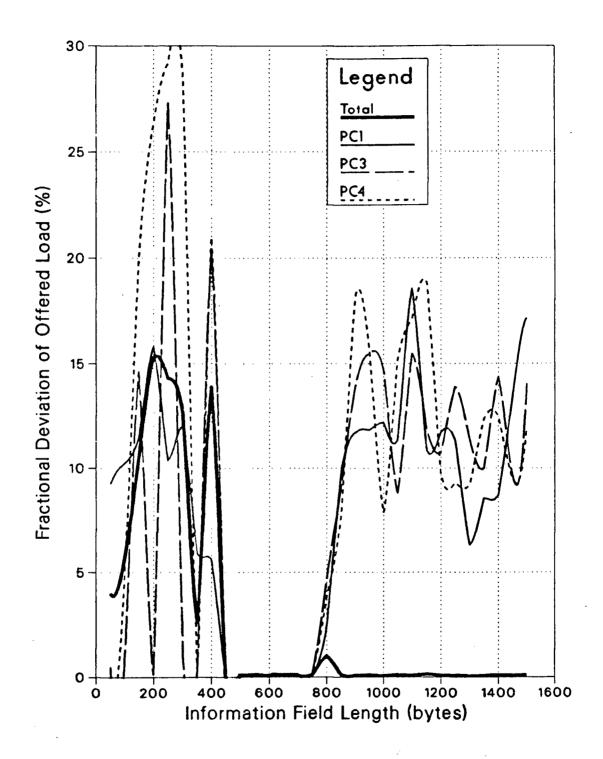

| 3.42 | Fractional standard deviation of offered load                          | 83         |

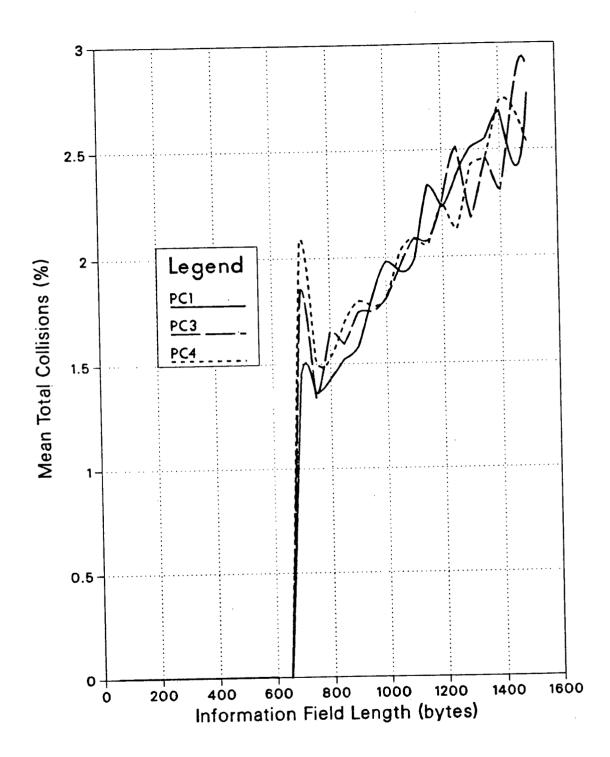

| 3.43 | Number of collisions expressed as a fraction of offered load           | 84         |

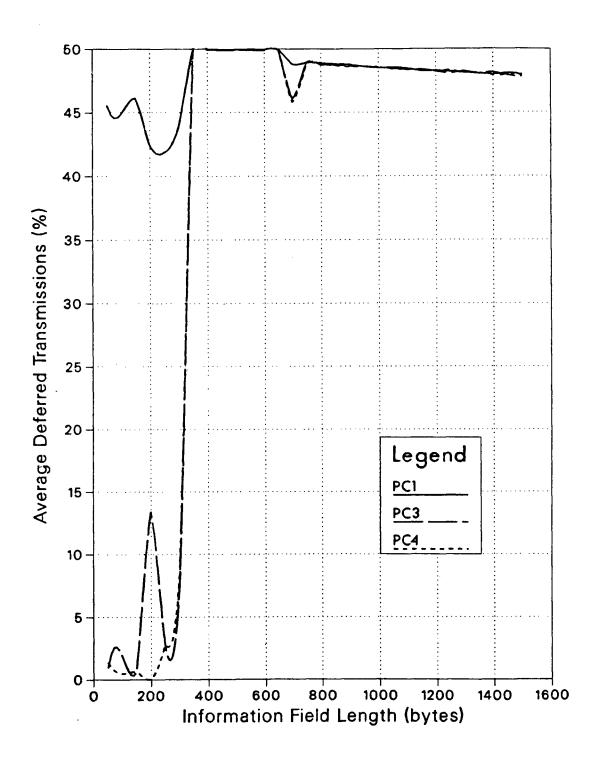

| 3.44 | Number of deferrals expressed as a fraction of offered load            | 85         |

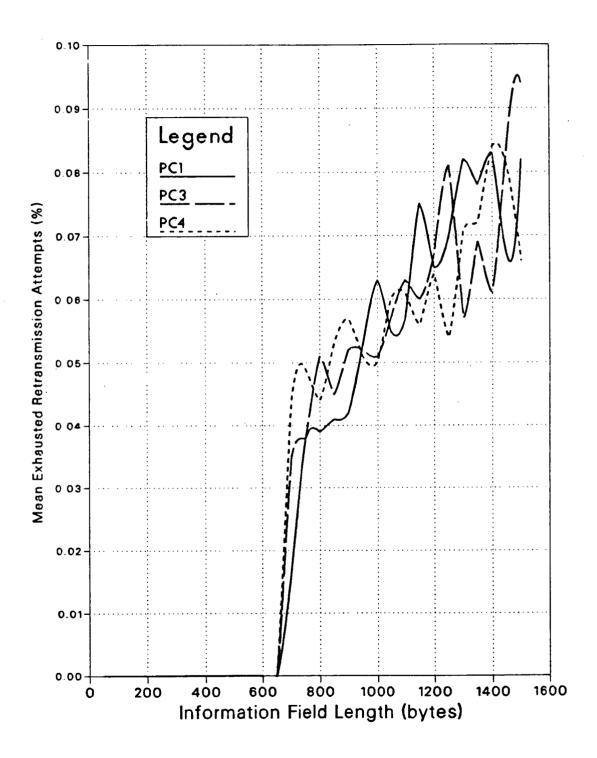

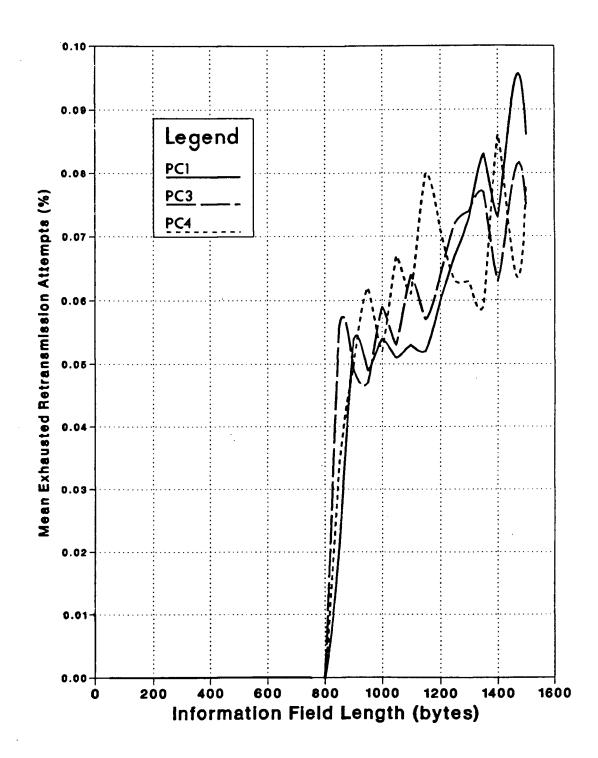

| 3.45 | Number of unresolved collision intervals as a fraction of offered load | 86         |

| 3.46 | Average throughput for a 3-PC network with frame receptions            | 87         |

| 3.47 | Average offered load for a 3-PC network with frame receptions               | 88  |

|------|-----------------------------------------------------------------------------|-----|

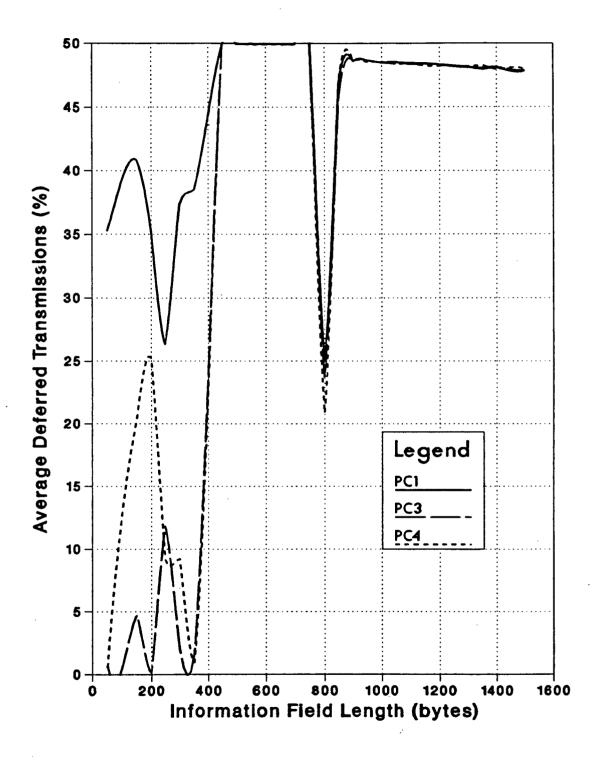

| 3.48 | Deferred transmissions expressed as a fraction of the offered load          | 89  |

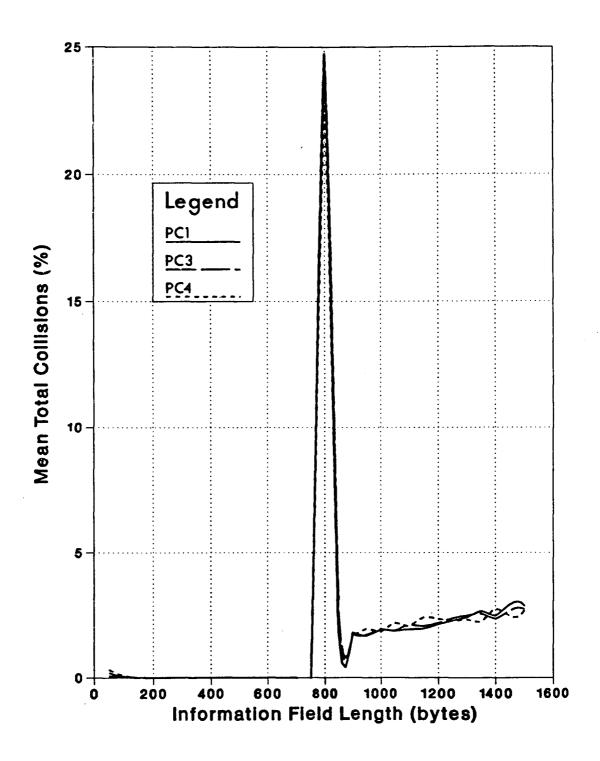

| 3.49 | Collisions expressed as a fraction of the offered load                      | 90  |

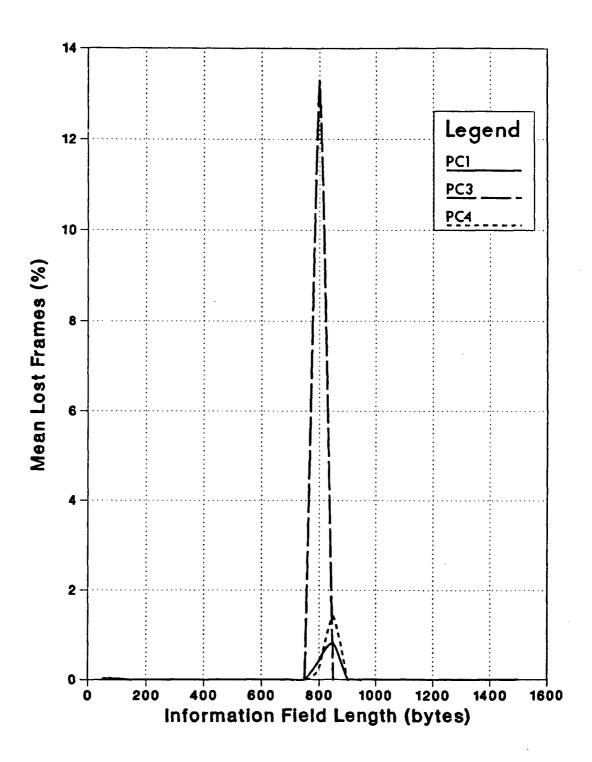

| 3.50 | Lost frames expressed as a fraction of the total number of received frames. | 91  |

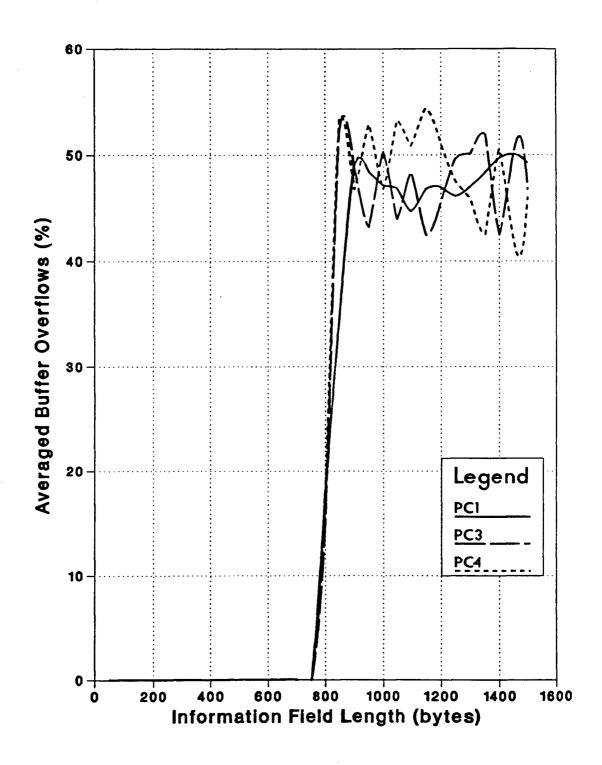

| 3.51 | Buffer overflows expresssed as a fraction of the total number of received   |     |

|      | frames                                                                      | 92  |

| 3.52 | Number of unresolved collision intervals as a fraction of offered load      | 93  |

| 3.53 | Fractional standard deviation of throughput                                 | 94  |

| 3.54 | Fractional standard deviation of offered load                               | 95  |

| A.55 | Logic Equations for PAL device of Intel StarLAN board                       | 106 |

| B.56 | Reference number 7                                                          | 111 |

| B.57 | Reference number 8                                                          | 112 |

| B.58 | Reference number 9                                                          | 113 |

| B.59 | Reference number 10                                                         | 114 |

| B.60 | Reference number 11                                                         | 115 |

| B.61 | Reference number 12                                                         | 116 |

| B.62 | Reference number 13                                                         | 117 |

| B.63 | Reference number 14                                                         | 118 |

| B.64 | Reference number 15                                                         | 119 |

| B.65 | Reference number 16                                                         | 120 |

| B.66 | Reference number 17                                                         | 121 |

| B.67 | Reference number 18                                                         | 122 |

| B.68 | Reference number 19                                                         | 123 |

| B.69 | Reference number 20                                                         | 124 |

| B.70 | Reference number 21                                                         | 125 |

| B.71 | Reference number 23                                   | 26         |

|------|-------------------------------------------------------|------------|

| B.72 | Reference number 24                                   | 27         |

| B.73 | Reference number 25                                   | <b>2</b> 8 |

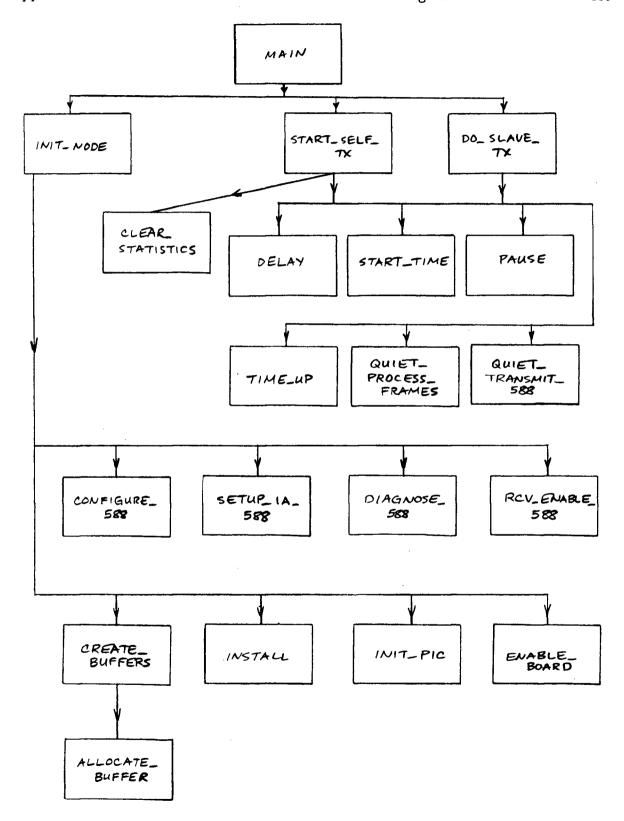

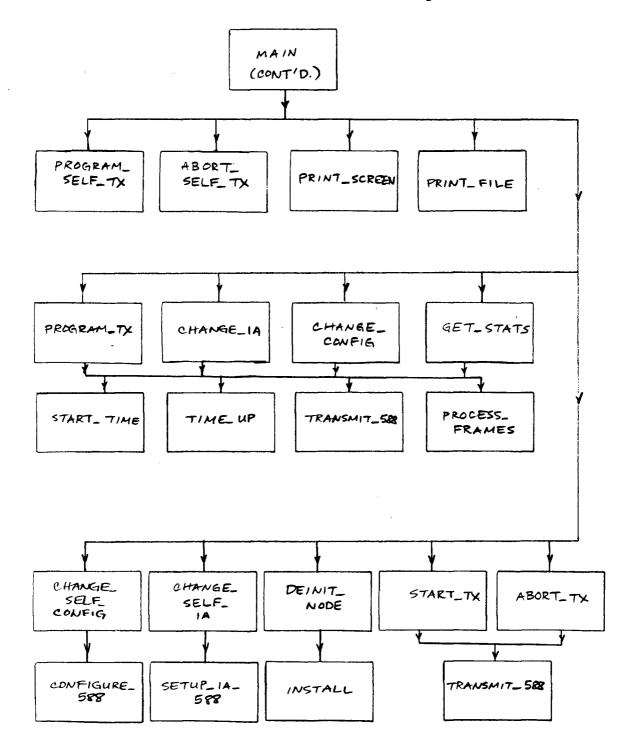

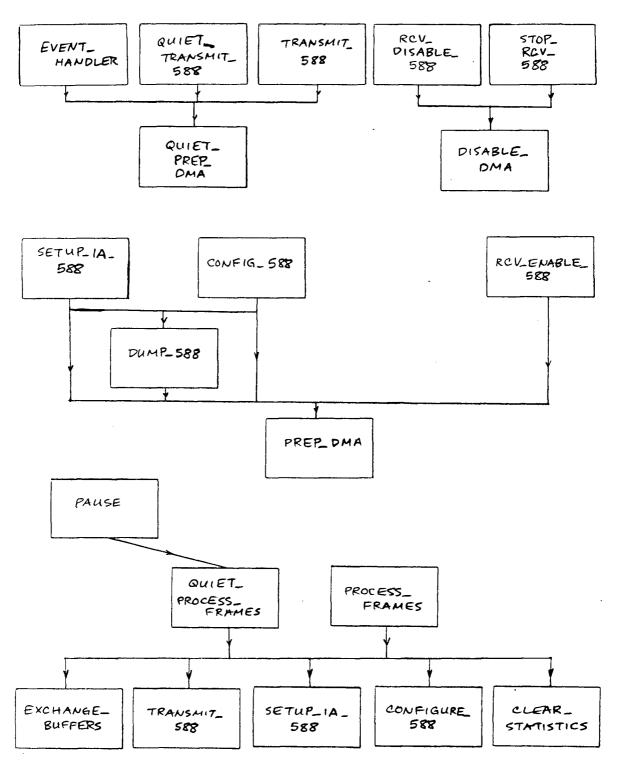

| E.74 | Subroutine Flowchart of Driver Program, Part 1 of 3 1 | <b>3</b> 9 |

| E.75 | Subroutine Flowchart of Driver Program, Part 2 of 3 1 | <b>4</b> 0 |

| E.76 | Subroutine Flowchart of Driver Program, Part 3 of 3 1 | 41         |

| E.77 | Header Files                                          | 42         |

| E.78 | Header Files (continued)                              | 43         |

| E.79 | Header Files (continued)                              | 44         |

| E.80 | Header Files (continued)                              | 45         |

| E.81 | Header Files (continued)                              | 46         |

| E.82 | Header Files (continued)                              | 47         |

| E.83 | Header Files (continued)                              | 48         |

| E.84 | Sample Master Program                                 | 49         |

| E.85 | Sample Slave Program                                  | 50         |

| E.86 | Sample Output File                                    | 51         |

#### Acknowledgement

The author gratefully acknowledges the contributions of the following individuals for their assistance in the course of the project that has culminated in this thesis. Of the staff at TRIUMF's microprocessor laboratory, Brian Evans and David Morris gave useful technical advice. The work area in the lab was borrowed from Robert Skegg. Layouts of all the printed circuit boards were done by Peter Bennett. Graham Waters was most helpful in showing how to access the laser printer through the network. PC's for the later performance measurements were generously provided by Prof. Glen Young and the Department of Harvesting and Wood Science at UBC. Consultation was sought on several occasions from Dr. H. Lee, formerly with the Department of Electrical Engineering at UBC, but who has since moved to Carleton University. Finally, I would like to thank my three supervisors, Bob Dobinson (now at CERN), Ken Dawson of TRIUMF, and Dr. Ed Auld of the Department of Physics at UBC, for guiding me safely through the past two years.

#### Chapter 1

#### Introduction

#### 1.1 FASTBUS

FASTBUS is a data bus system used primarily in nuclear and particle physics experiments for high-speed data acquisition, processing, and control. It was developed from the late seventies through the early eighties in response to requirements from the high-energy physics community for a bus system with higher throughput in data acquisition and processing. Its development was prompted by the realization that existing data busses would be unable to cope with requirements imposed by future experiments. Improvements in accelerator technology as well as the increasing complexity of many experiments were leading to faster event rates and more measurements for individual events—factors which demanded higher data throughput than ever before in spite of the fact that most of the events measured in those experiments did not contain relevant data. FASTBUS was designed to alleviate this problem through two routes: first, by having higher data transmission rates (i.e., by 'brute force'), and second, by offering a multisegment architecture that allowed simultaneous data acquisition and processing (and therefore, real-time data reduction), thus reducing the load placed on the bus by the transmission of largely irrelevant data.

FASTBUS has been and still is used in many experiments at virtually all major nuclear and particle physics research facilities around the world. Although FASTBUS was designed for high-energy physics experiments, its capabilities do not limit it to those applications. In general, it is feasible for any system that requires a bus with high data rates and multiprocessing capability. In 1984, FASTBUS was adopted as a formal ANSI and IEEE specification, the ANSI/IEEE 960 Standard.

#### 1.1.1 Basic Operational Description of FASTBUS

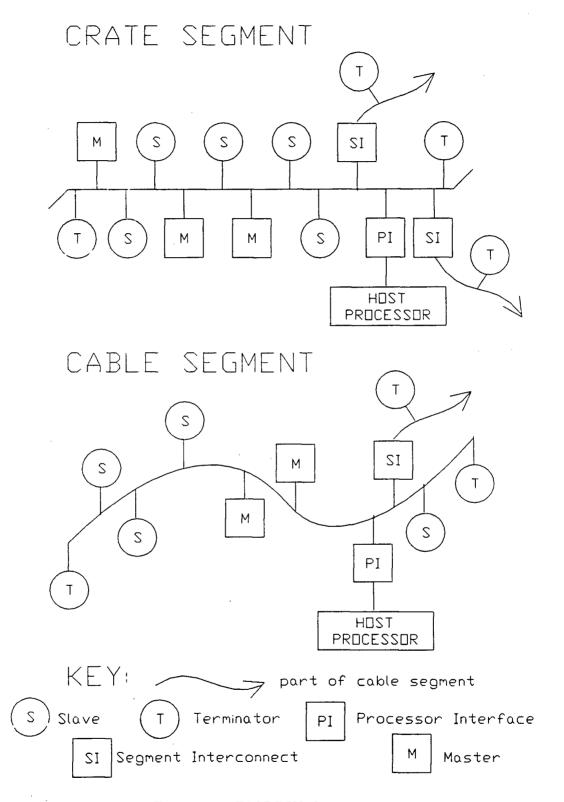

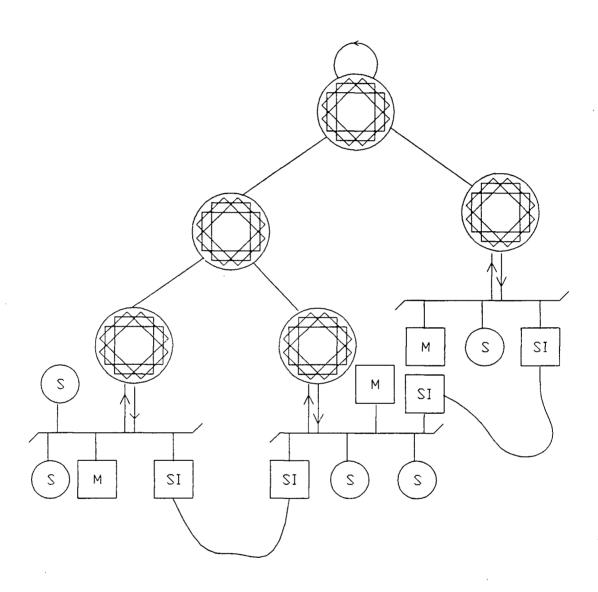

FASTBUS is a modular, segmented bus system: a typical application might have several 'Segments', each with its own set of devices. Each of these Segments operate independently but can also dynamically link with other Segments for inter-segment operations. A Segment has 32 multiplexed address/data lines plus additional lines for power distribution, control, timing, arbitration, and other functions. There are two types of Segments: One is a 'Crate Segment' where devices (i.e., electronic circuit cards) plug into connectors on a backplane in much the same way as peripheral cards plug onto the motherboard of a microcomputer. The other is called a 'Cable Segment' which, as the name suggests, links attached devices by multi-conductor cable. There are five types of devices which can attach onto a segment: 'Masters', 'Slaves', 'Processor Interfaces', 'Segment Interconnects', and 'Terminators'. A Master is a device which can acquire control of a segment (or other segments, in the case of inter-segment operations) and initiate operations. Slaves can only respond to instructions issued from Masters and cannot independently take control of the bus. Processor Interfaces link a Segment to a host processor (e.g., an external computer). Segment Interconnects link two or more Segments together temporarily so that inter-segment operations can be done. Segments are terminated at both ends by Terminators, which provide impedance-matching (to reduce reflections on signal lines). Crate segment Terminators are usually mounted on cards which contain electronic circuits to support functions related to timing, control, and addressing. Figure 1.1 shows the simple schematic diagrams of these two segments along with some attached devices.

<sup>&</sup>lt;sup>1</sup>see [1], [2], and [3] for more details.

Figure 1.1: FASTBUS Segments

FASTBUS is different from many other busses in that more than one Master can be attached to the bus. This allows independent multiprocessing operations but complicates the system since a bus arbitration scheme is needed to decide which Master takes control of the Segment(s) in the event that more than one Master wants to use the bus at the same time. Furthermore, there is the possibility of 'starvation' among other Masters if one Master controls the bus for a disproportionate amount of time. Such a situation can occur because a bus Master may not be interruptible. (In FASTBUS, this problem can be avoided if all masters abide by the Assured Access protocol.) Nevertheless, the advantages of a multiple-master bus outweigh the added complexity by such a large margin that the current trend of high-performance busses is towards multiple-master systems (e.g., NuBus, used in the Apple MacIntosh II microcomputer).

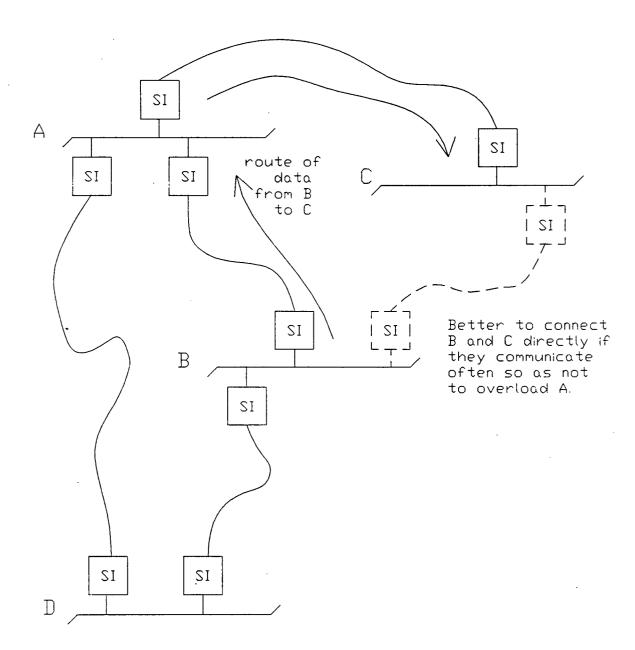

Inter-segment communications are dynamically established by Segment Interconnects attached to the corresponding Segments. A Segment Interconnect physically couples a Backplane to a Cable Segment. These devices are responsible for handling inter-segment information traffic in a 'transparent' manner such that devices in different segments can be accessed as if they were intra-segment devices. They perform the dual tasks of isolating a segment from the rest of the system during intra-segment operations and connecting two or more segments together as if those were one contiguous segment when inter-segment operations are required. Route tables are used to determine the data path during inter-segment operations. The capability of inter-segment operations allows a multiple-master system to exploit its multiprocessing power not just within isolated segments (with their limited number of attached devices) but to the whole system. Furthermore, FASTBUS does not specify the topology for Segment interconnections. It does not specify which Segments should be linked or which should not. This gives the system designer maximum flexibility in adding inter-segment connections to suit the particular application and to maximize system throughput. For example, segments which often communicate with

each other should be grouped closely together so as to reduce inter-segment propagation delay. In addition, they should also have direct links to each other instead of indirect links (which pass over other Segments) so as not to disrupt intra-segment operations in those Segments. Figure 1.2 shows schematic diagrams of several interconnected Segments.

The number of Segments used in a FASTBUS application can run from as few as one to as many as several hundreds.

#### 1.1.2 Motivation for the FASTBUS Serial Network

Regardless of the number of Segments, problems with a FASTBUS system can occur. Because of its complexity, it is usually not a trivial task to debug the bus system, especially if there are many inter-connected Segments and a large number of attached devices. Hence, as FASTBUS evolved, the FASTBUS Serial Network (FSN) was conceived to provide a system-wide communication network for diagnostic purposes. This network is autonomous from the rest of the bus system. Hence, it can remain effective even when the remainder of the system is not functional.

A typical FASTBUS diagnostic scenario might occur as follows: A faulty Segment Interconnect device is suspected to be causing problems with inter-segment operations. Data traffic between the affected Segments must be examined to determine if this is indeed the case. However, the FASTBUS system cannot be used to transfer data between those Segments because it is not operating properly—a broken FASTBUS system cannot be used to diagnose itself. Hence, the data must be sent either through an external facility or through an unaffected, internal, autonomous communication link.

Although the FASTBUS Serial Network was originally conceived for diagnostic purposes, its scope of application is not restricted to that area alone. The FSN can be used as the data channel in a 'backdoor initialization' scheme for starting up a FASTBUS system. For example, data for initializing route tables could be sent through the serial

Figure 1.2: Interconnected FASTBUS Segments

network. Another application that could use the FSN is a system sentinel which monitors the FASTBUS system for abnormal operating temperature and power supply voltages. FASTBUS devices could periodically send data through the serial network to inform the sentinel of their operating conditions without placing an additional load on the intersegment links. The FSN can also be used for remote switching of FASTBUS devices. A device can be controlled from a remote terminal through the serial network, which would be used to transmit programming data to the device and send back status information to the terminal. An operator would no longer have to open a crate and physically access the device to change its switches or read its status lights.

In spite of the wealth of applications which could use a separate data network, the FASTBUS Serial Network is, as of 1988, not yet operational. Formal specifications have not yet been given or agreed upon for either its implementation or applications. A brief history of the FSN (from [4]) is given in the next paragraphs to summarize past efforts and to put the current work into perspective.

#### 1.1.3 Historical Background of the FASTBUS Serial Network

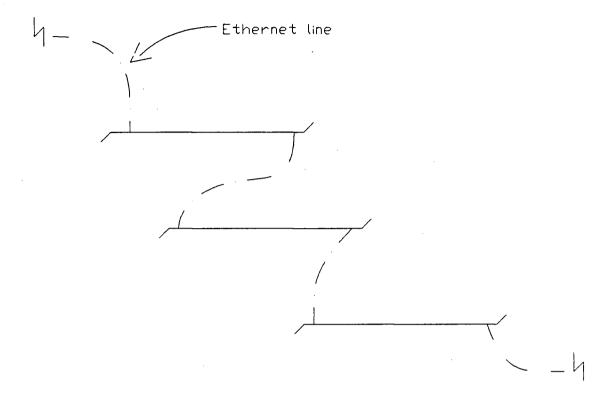

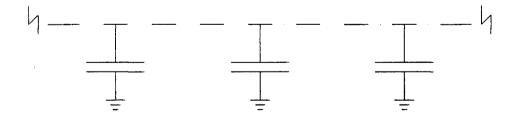

In mid-1979, a single line (SL) on the Crate backplane Segment was reserved for the FASTBUS Serial Network. This was done with the idea that some single-line, industry-standard network, such as Ethernet, could be used. However, there were problems with using only one line. For example, it was not practical to route the serial links in from one end of the Segment and out at the other end because each Segment would then contribute a large lumped capacitance to the line, resulting in impedance mismatches which, in turn, would cause enormous signal reflections (see figure 1.3). The line capacitance of the network would be very high since all transmitters and receivers (along with their load capacitances) were connected to the same line. A repeater could be used to link the external line to the Segment (figure 1.4). It would act essentially as a bridge, relaying

## EQUIVALENT CIRCUIT:

Large capacitances due to devices attached to each segment.

Figure 1.3: Single line direct routing scheme

Figure 1.4: Single line repeater-based scheme

signals between the line and the Segment, while isolating the Segment's capacitive load. This was an expensive solution. Moreover, Ethernet, the candidate standard at that time, limited the number of such repeaters to only two per network. So, by October 1980, a second line (SLR) was added. (The current FASTBUS standard refers to these lines as 'Serial TX' and 'Serial RX'.) With this scheme (figure 1.5), one line would be used by all devices for transmitting while the other line would be used for receiving. A network 'bridge' would link data between the two lines and an external line. Overall capacitance load on the transmit and receive lines was also reduced since transmitters and receivers in each Segment were now connected to their respective lines instead of having to share one line.

At this point, Ethernet looked to be a very promising standard for the FASTBUS Serial Network. If integrated circuits that implemented Ethernet became available (as usually happens for popular industry standards), then it would be an easy task to use Ethernet for the FSN. However, Ethernet was also an evolving local area network (LAN) standard at that time and its specifications were not yet fixed. The data rate of Ethernet was initially set at 1 Mbps. This would have been ideal for the FSN since simple collision-detection circuitry could be used. However, that data rate was changed to 10 Mbps for higher LAN throughput, complicating not only the task of detecting collisions but also that of processing data faster. It was still possible, in principle, to use Ethernet, but it would require more expensive electronic circuits and, more significantly, more circuit board area. Hence, the idea of using Ethernet for the FASTBUS Serial Network was dropped and the search was on for suitable alternatives.

In October 1980, a research group at the Stanford Linear Accelerator Center (SLAC) began to develop a prototype serial communication network based on an SDLC (Serial Data Link Control) chip (the Zilog Z80-SIO). This system had a data rate of up to several hundred kbps and occupied only 13 cm<sup>2</sup> of circuit board area. The hardware was built in

Figure 1.5: Two-line connection

1981 and some support software was developed shortly afterwards. However, the SLAC group was reluctant to implement the prototype because they were still hoping for an industry standard network to evolve that would fit their needs.

The same group then tried to use the AppleTalk(tm) network. This network was based on a newer SDLC chip, the Zilog Z8530, and required only  $1 in^2$  of board area. It had a data rate of 230400 bps, which was slow enough for data processing without using a DMA (Direct Memory Access) controller (which would have been required for higher data rates, such as that of Ethernet). It was also compatible with the two-line serial network scheme and was already supported by commercial software for data transfer. This system was not implemented either, in spite of its promising characteristics, because the group wanted to delay standardization until the 'last possible moment' just in case a better system became available.

And, perhaps, a better system may have arrived. StarLAN, a new LAN standard, seems to have most, if not all of the features desired for the FASTBUS Serial Network. It has a data rate of 1 Mbps, which is not too slow, but slow enough to allow the use of simpler collision detection schemes and less expensive electronic circuitry. It still requires DMA support, but DMA controllers are less expensive now than they were before. Furthermore, CPUs with built-in DMA controllers are now available. But the most important aspect of StarLAN is that it is an industry standard, with wide multivendor support. StarLAN is similar in many respects to Ethernet (already a very popular and widely used LAN standard) and hence, can be easily connected to that network by a StarLAN-Ethernet 'bridge'. Many integrated circuit manufacturers have developed chips for StarLAN controllers, making it possible to build circuits occupying very little board space. Although StarLAN is more expensive than AppleTalk(tm), it has better prospects for long-term use and expansion. As of this time (late 1988), a better alternative to StarLAN has yet to come. StarLAN is a fairly young standard (it was standardized in

early 1987) and thus, is not expected to become 'obsolescent' at least for the next few years. Preliminary work on a StarLAN-based serial network has been done at TRIUMF (and perhaps also in other places). The contribution from TRIUMF is the subject of this thesis.

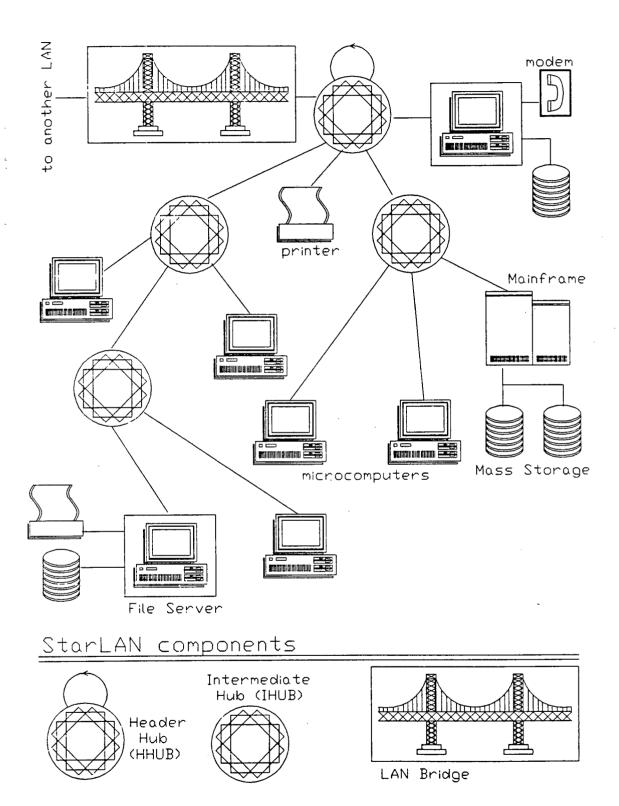

#### 1.2 StarLAN

StarLAN, officially known as the IEEE 802.3 1BASE5 standard 2, is a new local area network (LAN) standard designed for office integration and automation. (Local Area Networks are short-distance data communication facilities connecting computers at distances of between a few meters to several kilometers apart, typically within a single or a localized cluster of buildings.) It was developed as a low-cost alternative to Ethernet (an earlier LAN standard) 3 for use in systems based on personal computers. These systems typically do not require the high performance of Ethernet, and consequently, cannot justify the higher connection costs associated with those networks. At that time (early 80's), existing LAN standards were designed primarily for centralized mainframe and minicomputer systems. A study done in 1985 [7] showed that only a small fraction of the estimated 10 million PCs being used were networked. This finding was especially significant in office environments, where PCs have become increasingly popular but function more efficiently when networked together with other resources in the office such as printers and mass storage media (data bases). These unconnected PCs represented a huge, untapped base of users waiting for a more affordable LAN. With the number of PCs expected to reach up to 20 million units by 1990, the development of cheaper LAN's became ever more urgent—and lucrative. StarLAN is one of the most recent entries in this class of LAN's.

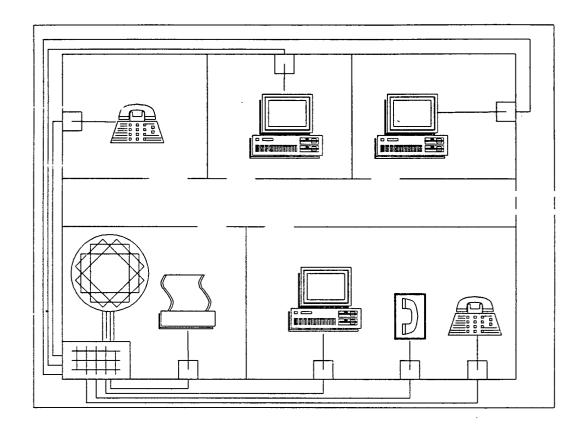

StarLAN derives its lower costs from three characteristics. Firstly, it uses a relatively low data rate (1 Mbps), so that slower, and therefore cheaper, electronic circuits can be used. Secondly, it is designed to use, as the transmission medium, existing spare telephone cables in a building, eliminating additional costs of routing new cable. Telephone companies typically put more telephone wiring in a building than is initially required

<sup>&</sup>lt;sup>2</sup>see [6]

<sup>&</sup>lt;sup>3</sup>see [5]

because it is cheaper and easier to tap spare telephone wires than to route new cable through the building when more telephone lines are needed. Finally, StarLAN is an international standard with wide, multi-vendor support. Users can select StarLAN products from many manufacturers instead of being 'captive' customers, which usually happens with communication protocols developed by a single vendor (because they are not compatible with those of other vendors).

# 1.2.1 StarLAN in the Framework of the OSI Model and Other IEEE 802 Protocols.

A complicated series of operations is usually required when data are sent between computers. These operations comprise two basic sections: coding and routing. The coding section is concerned with how data from the source computer is presented or 'shown' to the destination computer. Source and destination computer systems may use different internal character collating sequences (e.g., ASCII and EBCDIC), in which case text messages will have to be translated so as to have the same appearance in the destination computer. Data containing confidential material may have to be encrypted for the purpose of privacy. The routing section is responsible for sending the coded data reliably and efficiently from source to destination. Error detection and/or correction codes are usually appended for use by the destination system to check for integrity of the message received. In a complicated network, the source data must be sent through intermediate points before reaching its final destination. Efficient and robust routing algorithms are required in such cases to select the (sub-)optimal path through the available intermediate points. The physical media for data communications are diverse and include, to mention a few, coaxial or fibre-optic cable, point-to-point radio-frequency links, and microwave satellite channels. Protocols, or sets of rules, are agreed upon between the sender and receiver for all aspects of data transfer such as the operations described above, as well as

for initiating and terminating transfers and recovering from situations where some part of a message is either lost or received with error(s).

The operations involved in moving data from one point to another are components in a communication system which help to implement its only goal: to send data reliably from the source to its destination. The sheer complexity involved in sending computer data (of which only the essential details were outlined above) requires a 'structured' scheme for all data-transfer operations. Several computer corporations, as well as national and international organizations have developed schemes, or 'architectures', for organizing these data-transfer operations. Of these, two will be discussed briefly as they are very closely related to StarLAN. The first is the OSI (Open System Interconnection) 7-Layer Reference Model specified by the International Standards Organization (ISO) and the second comprise the IEEE protocols, which are being developed by the IEEE 802 Standards Committee of the Institute of Electrical and Electronics Engineers (IEEE) in the United States.

#### The OSI Reference Model

OSI is a complete architecture for data communication. It is defined by a hierarchy of seven operational 'layers', each of which has its own set of functions, independent of the other layers. OSI does not specify the protocols for these layers, it only outlines the duties and responsibilities for those protocols. Figure 1.6 shows a schematic diagram of the seven layers. The application layer contains application-specific programs for the data communication requirement at hand. The presentation layer is responsible for functions such as character code conversion, text compression, and data encryption. The session layer sets up and maintains connections between applications. It is responsible for user authentication and for re-establishing interrupted or lost connections. The transport layer makes data transfer between applications as independent of the underlying network

Figure 1.6: OSI 7-Layer Reference Model.

as possible. These four highest layers cover 'end-to-end' protocols because they concern source and destination applications only and are independent of the network used to physically connect them.

The lowest three layers specify network access protocols, whose functions concern only the network, independent of the particular application involved on the higher layers. The network layer provides services for setting up and maintaining the flow of messages in a network. It is responsible for directing message packets towards their destinations. Since source and destination users may not be connected by a direct physical link, the network layer is also responsible for routing and switching data messages through any intermediate junction in a network. The data link layer is responsible for message frame synchronization as well as error detection and correction. It is responsible for retransmission of message frames received in error. In general, it provides an apparently error-free connection between a transmitter and receiver. The physical layer specifies electrical and mechanical parameters for a direct physical link. These include the type of medium used (such as coaxial or fibre-optic cable), the signalling method (modulation technique, amplitude and period of electrical signals, etc.), as well as the connection scheme (e.g., number of connector pins, types of connectors or plugs). It is concerned with transmitting and receiving bit streams of message frames sent by the data link layer.

A communication network may not require all of the layers. Local area networks for example, typically do not use the transport, session, and presentation layers. Each layer must be 'open' to adjacent layers, that is, a protocol implemented at any one layer should be able to interface to any protocol of the adjacent layers. This means that a protocol at a layer should not have to know the implementation details of the other layers. If the implementation of one layer has to be changed for any reason, only the interfaces connecting that layer to adjacent layers will have to be changed, while protocols for the other layers remain unchanged. The OSI reference model provides an architecture for

Figure 1.7: IEEE Local Area Network Architecture.

easing the task of developing and, just as important, maintaining a data communication system.

#### The IEEE 802 Protocols

The IEEE, through its 802 Standards Committee, has developed protocols for local area networks. These protocols are designed to resolve incompatibilities that could exist in LAN equipment supplied by different vendors. They do not conform exactly to the OSI model but are based on a closely related architecture shown in figure 1.7. As can be seen, the differences involve primarily the network access protocols.

The IEEE model essentially splits the OSI data link layer into two sublayers, one responsible for logical link control (LLC), the other for medium access control (MAC). The MAC layer implements the access method used in the network, which may be CSMA/CD, token ring, or token bus (to be discussed later). The LLC layer provides the remaining

Figure 1.8: IEEE 802 Protocols

data link services, independent of the medium access technique used. IEEE 802 protocols conform to this modified architecture. They are enumerated below and a diagram showing where these protocols lie in the IEEE local network reference model is given in figure 1.8.

IEEE Standard 802.1 Describes the relationship between other 802 protocols and their relationship to the OSI reference model.

IEEE Standard 802.2 Common logical link control.

IEEE Standard 802.3 Group of protocols that use the CSMA/CD access method.

IEEE Standard 802.4 token-passing access method, bus topology.

IEEE Standard 802.5 token-passing access method, ring topology.

#### IEEE Standard 802.6 metropolitan area network.

StarLAN is a subset of the 802.3 group. It defines the implementation for a local area network at the physical and MAC layers. As such, it defines parameters for physical connections and the access method which, in the case for 802.3 protocols, is CSMA/CD.

#### 1.2.2 Basic Operational Description of StarLAN

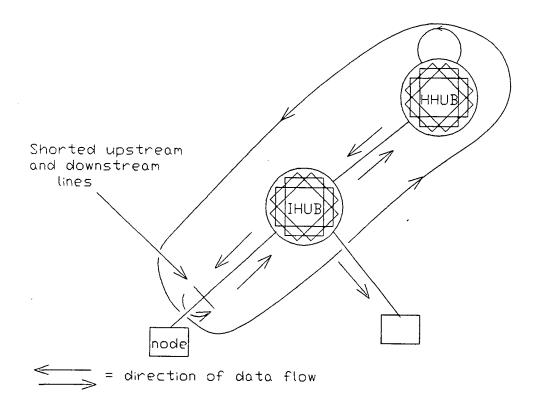

StarLAN, as the name suggests, has a star topology as shown in figure 1.9. The simplest form of the star topology is analogous to a bicycle wheel with a hub at the center, from which spokes radiate outwards. Message frames transmitted by connected nodes are sent to 'hubs' which in turn relay them to higher-level hubs in the network. Of course, there are a finite number of hub levels. The single hub at the highest level, at which there is no further connection to a topologically 'higher' level, is called the header hub. All other hubs are called intermediate hubs. When a message reaches the header hub, it is sent back down by that hub to be propagated to the rest of the network by lower-level hubs.

There are essentially two other network topologies for interconnecting nodes in a network. These are the bus and ring topologies, shown in figure 1.10. Two IEEE standards, 802.4 and 802.5, use bus and ring connection schemes respectively. Ethernet, another IEEE 802.3 protocol, also uses the bus topology. This is one significant difference between Ethernet and StarLAN.

StarLAN does not specify which transmission medium should be used to connect hubs and nodes in the network. It only requires any node-node or hub-node link to have a maximum propagation delay of 4 bit times and no more than 6.5 dB attenuation in the signal frequency spectrum between 500 kHz and 1 MHz. There is no limit to the number of connections at each hub layer but a maximum of only five hub layers are allowed in the network. Data bits are transmitted at a rate of 1 Mbps using Manchester encoding

Data direction towards HHUB => upstream direction.

Data direction away from HHUB => downstream direction.

Note: <u>seperate</u> upstream and downstream links are shown as single lines connecting hubs to nodes or other hubs.

Figure 1.10: Bus and Ring Topologies

Figure 1.11: Manchester Encoding and RS-422 Voltage Levels.

and RS-422 voltage levels as shown in figure 1.11.

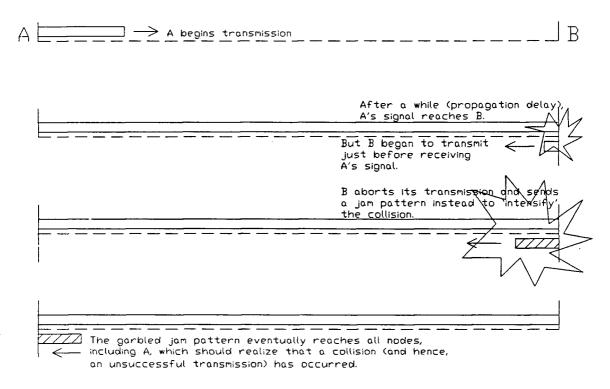

Since no signal multiplexing scheme is used, only one channel is available for all users connected to the network. It has to be shared and this means that only one user or node can be in the process of transmitting a message frame at any given time. Two or more simultaneous transmissions will result in a 'collision' where the messages involved become superimposed and consequently garbled. In StarLAN (and Ethernet as well), all nodes employ an access method called CSMA/CD (Carrier Sense Multiple Access with Collision Detection) when sending message frames. This method is described below.

When a node has a message to send, it first checks its receive line to make sure that no other node is transmitting. If no one else is using the network, the node begins transmission. Otherwise, it waits for the other node to complete transmission first. That was the 'carrier sense' part of the access method. The 'collision detection' part' now follows. Because there is a finite propagation delay (due to hub processing and cable transmission delays) for a signal from one node to reach all the others, the remaining

nodes in the network will, for a brief interval, not know that a transmission has already started. If one or more of those nodes begin transmission on the erroneous assumption that no one else is transmitting, then a collision will occur. When a transmitting node detects a collision (by monitoring the signal on its receive line), it halts its current transmission and sends a brief jam pattern to enforce the collision (i.e., increase the level of collision) so as to ensure its detection by other nodes involved with the colliding transmissions. After the jam pattern has been transmitted, each node 'backs off' by ceasing transmission for a random length of time before retransmitting the entire message. This reduces the probability of having two or more nodes with the same back-off period, which will result in another collision when those nodes begin retransmission. When the backoff period expires, the node then waits until the channel is free before retransmitting its message frame. A collision can occur again during any retransmission attempt. If that happens, the backoff process described earlier is repeated again.

CSMA/CD belongs to a class of access methods which rely on channel contention or 'channel grabbing' to send messages. Another way for accessing a common channel avoids contention altogether by providing a transmission sequence for users connected to the network. This technique, called token passing, involves the passing of a 'token' (a special message frame giving the node receiving it the sole right to transmit) around the network (see figure 1.12). A node possessing the token uses the network during its allocated time for any messages to be transmitted. When its time is up, the node passes the token onto the next node in the ring. In that way, only one node transmits at a time, avoiding collisions. As mentioned before, this is the access method used in two related IEEE protocols, 802.4 and 802.5.

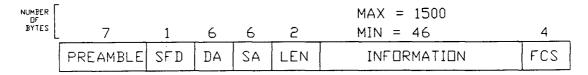

A StarLAN message frame is composed of several fields as shown in figure 1.13. Message transmission always starts with the preamble which is used for synchronization. The end of the preamble is marked by a start-of-frame delimiter (SFD). Source and

Figure 1.12: Token-passing Access Method.

PREAMBLE: SERIES DF 10101010....

SFD = Start of Frame Delimiter: 10101011

DA = Destination Address

SA = Frame Address

FCS = Frame Check Sequence

LEN = Length of Information Field

Figure 1.13: StarLAN framing format

destination address fields then follow the SFD. These identify the node from which the message originated and the node to which the message is intended respectively. All nodes check the destination address field of an incoming frame to determine whether or not they should receive the remainder of the frame, which consists of the information field followed by the frame check sequence (FCS). The information field contains data used for the particular communication application while the FCS is a cyclic redundancy check (CRC) code which is calculated by an algorithm that uses the bits of the address and information fields. When a node receives a frame, the CRC is recalculated and compared with the FCS, which was calculated when the message was originally transmitted. If the two do not match, then an error exists in the frame (which may have been caused by, among others, noise in the transmission medium). Not all errors can be detected by a CRC. The effectiveness of a CRC (and FCS) depends on the algorithm as well as the amount and distribution of bit errors in a message. 100% error detection cannot be guaranteed for all circumstances by any CRC algorithm.

StarLAN specifies a minimum interframe spacing (IFS) of 96 bit times (96  $\mu sec.$ ). This is the minimum time between adjacent frames sent in the network. Its purpose is to give processors in receiving nodes enough time to 'recover' between receptions of back-to-back frames. Received frames are usually not processed immediately on reception, but are temporarily stored in buffers. The interframe spacing gives receivers some time to do short tasks after receiving a frame such as switching receive buffers so that each received frame is stored in its own buffer area. A node waiting for another one to complete transmission has to wait an additional IFS period before transmitting, to ensure that all frames are spaced apart by at least this minimum separation time. When a StarLAN node detects the absence of carrier (when no other node is transmitting), it waits for an additional IFS period, after which it transmits regardless of whether or not the channel has become busy (by another transmitting node) after that period.

Figure 1.14: Worst-Case Scenario for Collision Detection.

StarLAN specifies several parameters related to collision detection and recovery. Minimum jam time (set at 32 bit times), is the minimum length of time that a node transmits a jam pattern when a collision is detected. Slot time (set at 512 bit times), determines the backoff times when a collision occurs as well as the minimum message frame length. The slot time is computed as the jam time plus the longest time taken for a signal to reach the farthest node and return back (the 'round-trip' propagation delay). It is the worst-case time for a collision to be detected. Figure 1.14 shows how this conclusion is arrived at. A node must still be in the process of transmitting a message to detect a collision. If it completes its transmission without detecting a collision and a collision actually occurred, the frame is not retransmitted and is lost. For this reason, message

frames sent in a CSMA/CD environment must be longer than the slot time. A colliding node backs off an integral number of slot times so as to avoid overlapping into any collision interval that might occur with nodes retransmitting (and still colliding) at an earlier time. This number is determined in StarLAN by what is called a 'truncated binary exponential backoff' algorithm. The number of slot times to back off after the kth retransmission attempt (of the same frame) is randomly selected from the range of  $[0, 2^n)$ , where n is the smaller of k and 10. Hence, the range of slot times from which a colliding node randomly selects its backoff time is doubled each time a backoff period fails to resolve the initial collision. This doubling stops after the 10th retransmission attempt to simplify the algorithm's implementation. Clearly, the probability of having a collision on retransmission decreases as the range for selecting the backoff period increases. StarLAN limits the number of retransmission attempts (stemming from the original collision) to 15. In other words, a node has up to 16 chances to successfully transmit a frame. If that limit is reached, the node ceases further retransmission and informs the higher layer protocol of the unsuccessful frame transmission, otherwise, it indicates that the frame was successfully transmitted.

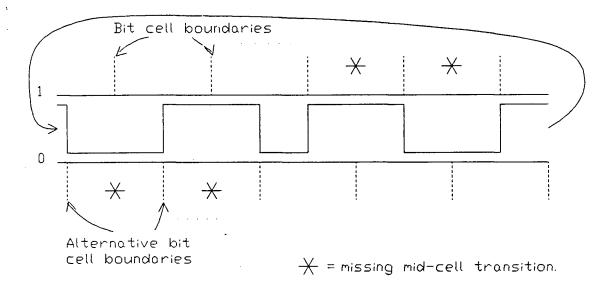

In a StarLAN network, collision detection is performed first by the hubs. When a hub senses that more than one of its 'downstream' input lines is transmitting simultaneously it begins to transmit a collision presence signal (CPS). This is nothing more than a bit stream with Manchester code violations (see figure 1.15). Other hubs higher up in the network will receive this signal and transmit their CPS upstream. The header hub then relays this signal back down the network so that all nodes receive the CPS and are thus informed that a collision has occurred. Collision enforcement and backoff is then performed by the nodes which transmitted the colliding frames. Hubs stop transmitting their CPS when transmission ceases on all of their downstream inputs.

Hubs are also responsible for jabber inhibition— a hub should shut off its link to

Ensures two missing mid-cell transitions will occur every 5 microseconds (cycle time) for either bit cell reference point.

Figure 1.15: Collision Presence Signal

Figure 1.16: Infinite Loop in a StarLAN Network.

any downstream input that transmits for an inordinately long time. This prevents long transmissions from tying up the network. Such a situation can occur if an upstream and downstream line are accidentally connected together. When that happens, the downstream signals will be coupled upstream and be transmitted through the network in an infinite loop (see figure 1.16). When one of a hub's downstream inputs is transmitting much longer than it should, the hub responds by sending a CPS (forcing a collision back-off sequence) to get all nodes to cease transmission momentarily. If its offending input does not cease transmission, then that input is logically disconnected from the network

(by simply being ignored by the hub). An inhibited input will be readmitted to the network only when the hub receives a transmission from that input while no signal is being sent downstream from the higher hub layers—this will never occur if the upstream and downstream lines are short-circuited together as discussed previously.

Figure 1.17 gives a schematic diagram of a 'typical' StarLAN network in a hypothetical office. Users can up/download files and application programs from remote data bases and computer systems. Electronic mail can be sent between users while output devices such as printers can be shared. The wiring details for a sample office are shown in figure 1.18. Note how the star topology blends neatly with the structure of the telephone wiring system. StarLAN was designed with this environment in mind.

#### 1.2.3 StarLAN and the FASTBUS Serial Network

As mentioned earlier, StarLAN also seems to be a very promising candidate for implementing the FASTBUS Serial Network. One more reason for why this is so is the star topology, which allows FASTBUS crate segments to be easily connected to a StarLAN network. Figure 1.19 shows a schematic diagram of a StarLAN-based serial network on a hypothetical FASTBUS system. Masters, Slaves, and Segment Interconnects attach to the serial network as StarLAN nodes. The SERIAL TX line is used by the nodes for transmission while the RX line is used for reception. A StarLAN hub, mounted on a card, is plugged at a slot in the back of each FASTBUS crate segment. These hubs are connected to higher-level hubs as in an orthodox StarLAN network. So, it can be seen that the serial network is just like an ordinary StarLAN network except for the lowest hub level (at each FASTBUS crate), where the nodes and hubs' downlink portions are connected in a bus topology, using different voltage levels (ECL as opposed to RS-422 for orthodox StarLAN). Crate segments can be easily connected to or disconnected from the network by adding or removing their own link to the higher-level hubs. Although

Figure 1.17: StarLAN in an integrated office

Telephone System Components

Figure 1.18: StarLAN network using intra-building telephone cables

Figure 1.19: StarLAN-based serial network on FASTBUS

Figure 1.20: Bussed StarLAN network

FASTBUS segments can be connected in an arbitrary fashion, data paths during intersegment operations are determined by route tables which prevent crosspoints and loops from occurring (they do not occur in StarLAN because of jabber inhibition as well as the star connection topology). Hence, operations in the StarLAN-based serial network and inter-segment operations in a FASTBUS system function with equivalent topologies.

#### 1.2.4 Variations to Standard StarLAN

### StarLAN without Hubs

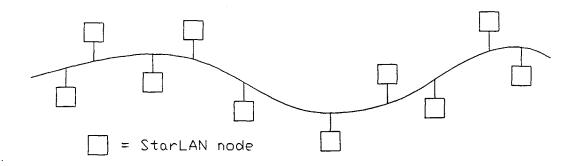

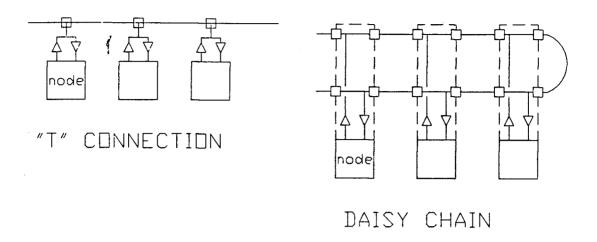

Spurred by the drive to reduce network connection costs even further, some designers, principally at Advanced Micro Devices (AMD), took the step of designing a variant of StarLAN which eliminated hubs entirely ([18], [19]). This variation, known as 'bussed' or 'hubless' StarLAN, eliminates hubs, the most expensive component in a standard StarLAN network. In this scheme, all nodes are connected together in a bus topology as shown in figure 1.20. Figure 1.21 shows two possible ways for connecting the nodes

Figure 1.21: Node connection schemes for bussed StarLAN

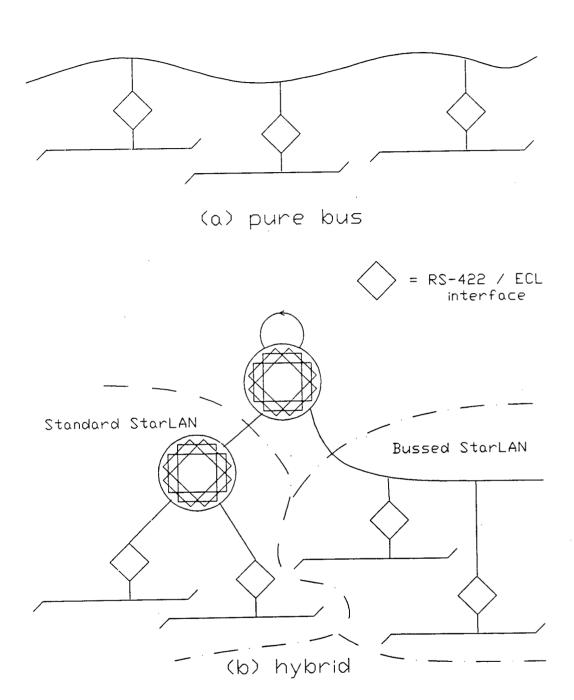

together. In the T connection, the cable (typically coaxial cable) is tapped by a connector which penetrates the insulation and outer shield to make contact with the inner conductor (which carries the signal). In the daisy-chain configuration, adjacent nodes are connected by pieces of cable. Each node splits the cable terminations into two, one for the node itself, the other for connection by another length of cable to the next node in the chain. As of this time, the daisy chain configuration seems to be the more feasible mode of connection. Two observations can be made immediately about a bussed StarLAN network. First, intra-building telephone cable can no longer be used because of the bus topology. This means that additional wiring has to be used, increasing network connection costs to some extent. Second, node connection and disconnection is now more complicated, especially for the daisy chain scheme favored by AMD. Furthermore, bussed StarLAN is not yet an official IEEE standard. Detailed specifications are still being developed for approval by the IEEE 802 Standards Committee. At any rate, bussed StarLAN may have some useful features in the context of the FASTBUS Serial Network. Two possible connection

schemes are shown in figure 1.22. Figure 1.22a shows a completely bussed network while figure 1.22b shows a hybrid scheme using both standard and bussed StarLAN. Finally, it must be emphasized that, unlike the connection scheme illustrated in figure 1.19 (using standard StarLAN), the bus schemes have not yet been prototyped for feasibility studies and performance evaluation.

### 10 Mbps StarLAN

In the latest twist to the StarLAN saga, a high-speed, 10 Mbps version of standard StarLAN is being developed [8]. This version was conceived in response to consumer demand for a local area network that was faster than StarLAN but could still use intrabuilding telephone cable. Apparently, many LAN users (or budding LAN users) prefer the data rate set by Ethernet at 10 Mbps and are unwilling to use a cheaper 1 Mbps LAN even though the lower data rate is perfectly suitable for their applications. The 10BaseT Study Group of the IEEE 802.3 Standards Committee is in charge of the development for this new LAN standard and has discussed specifications to be adopted. The Electronic Industries Association (EIA) is expected to publish the maximum running length of unshielded twisted-pair wire for 10 Mbps StarLAN soon.

Figure 1.22: Bussed StarLAN in the FASTBUS Serial Network.

# Chapter 2

# Building the Prototype Serial Network

### 2.1 A Simple StarLAN Network

At the start of the research (early 1987), StarLAN was still an emerging local area network (LAN) standard. Nobody in the laboratory staff had any working knowledge of StarLAN in both hardware and software. Hence, two StarLAN design kits were procured from Intel to expedite the task of building a working network. These kits contained a total of four printed circuit boards designed to plug into IBM PC expansion slots. The kits also included some components (such as the Intel 82588 LAN controller chip), software for driving the boards, as well as documentation that proved to be helpful for newcomers to StarLAN ([9], [7], [10]). Other parts, including wiring and a StarLAN hub, were obtained separately. A PAL (Programmable Array of Logic gates) chip was also required for each board. This chip's programming instructions were given in the Abel PAL programming language. However, only one PAL 'compiler', called PALASM2 (from Monolithic Memories), was available at the laboratory. Hence, the programming instructions had to be translated to PALASM2 code before the chips could be programmed. A short simulation program was also written to verify the translated code. A listing of the programming code and simulation results is given in appendix A.1.

Experience in electronics hardware development had shown, time and time again, that hardware bugs could be very difficult to solve (much more so than software bugs). Hence, a very cautious approach was taken which, though somewhat tedious, greatly reduced

the chances of unpleasant surprises and frustration when everything was soldered and plugged in. The Intel circuit design was thoroughly checked so that the circuit's operation was understood in detail. The schematic was also cross-checked with the printed circuit layout. All minor board components were tested before being soldered or plugged in. Intermediate hardware tests were done at various stages of assembly. Nothing (well, almost nothing) was left to chance. All of these precautionary steps were also taken during the construction of other electronic circuits that followed. The boards were carefully assembled and then tested with three IBM XT compatible computers using the software supplied with the kits (see [9] for more details). No problems, major or minor, were encountered. A diagram of the network connections for the tests is shown in figure 2.23a. Three sets of twisted-pair telephone cable, each 25 feet long, were used to connect the Intel boards from their telephone jacks to the telephone jacks of a Retix HB-6 StarLAN hub. <sup>1</sup> This hub could connect up to six nodes together. It could also be switched to function as either an intermediate or a head hub.

With this rudimentary StarLAN network, message frames could be sent from one PC to another. The Intel software allowed the user to load a message in hexadecimal or ASCII format and to set the message length. Another useful feature was a 'repeat transmit' mode which was used to continuously send messages. However, the transmission rate could not be altered. StarLAN parameters, such as source and destination addresses, could also be set by the user. A 'transmission session' could be initiated by starting transmissions in repeat-transmit mode and terminated at any time by keyboard entry. Statistics from transmission and reception of frames were updated in real time on the terminal screen. Detailed collision data (i.e., the distribution of the number of retransmission attempts to resolve a collision) could be displayed at the end of a transmission session. To check the system for reliable operation, each PC was set to transmit

<sup>&</sup>lt;sup>1</sup>see [11] for more details.

Figure 2.23: StarLAN Network Configurations

to another PC in a circular fashion. Three transmission sessions were done, one each for information field lengths of 48, 512, and 1500 bytes. The 48-byte length corresponds to the shortest field length that can be transmitted without producing a 'short frame' error in the program. Although the shortest field length allowed by StarLAN is 46 bytes, a small bug in the LAN controller chips restricted the shortest length to 48 bytes. The 1500-byte length corresponds to the longest field length for StarLAN frames while a 512byte length was chosen to be the 'intermediate length' frame. A transmission session was started by programming each PC, one by one, to transmit repeatedly. After some time had elapsed, say 5 minutes, the PC transmissions were stopped in the same sequence as they were started. The statistics displayed on each terminal were first checked for unusually large transmit or receive errors. Only a few errors were observed, so they were assumed to be caused by random processes in the course of the transmission session. Next, the number of 'good' transmissions from each PC was compared to the number of 'good' receptions at the corresponding destination PC. The good receptions were either equal to the good transmissions or were slightly less by only a very small amount. These implied that the number of lost frames were miniscule in comparison to the total number of transmissions that were reported as being 'good'. Hence, it was concluded from the tests that reliable communications were established in the network.

## 2.2 Using StarLAN in a FASTBUS Environment

After the completion of this rudimentary StarLAN network, an interface system that would enable StarLAN signals to be routed through a FASTBUS backplane was developed after verification tests on the basic StarLAN network were completed. The interface system consisted of two major parts: the first was a StarLAN-FASTBUS transceiver (essentially an RS-422-ECL signal translator; the FASTBUS backplane uses ECL logic

whereas StarLAN uses RS-422 voltage levels) and the second was a StarLAN hub designed to work on the FASTBUS backplane.

#### A Transceiver Between StarLAN and FASTBUS

A schematic diagram of the StarLAN-FASTBUS transceiver is shown in figure 2.24. This circuit is a transceiver between standard StarLAN and the FASTBUS backplane that provides a transparent interface between three-state RS-422 StarLAN signals and two-state ECL voltage levels. Figures 2.23b and 2.23c shows how The transceiver is used to connect the Intel StarLAN boards (constructed earlier) to a FASTBUS backplane. Standard StarLAN signals are fed into the transceiver, converted to ECL voltage levels, and sent through a line in the backplane. Signals received from the corresponding backplane line are converted back to StarLAN-specification RS-422 signals and relayed to the StarLAN board.

A not-too-small part of the transceiver's design was borrowed from a section of the Intel StarLAN boards. The task of incorporating some of Intel's design was not too difficult after some reverse-engineering was done on the board's schematic diagram. A TTL-to-ECL translator chip was used to drive the backplane while an ECL-to-TTL translator received the backplane signals. Special ECL bus driver and receiver chips were not used because other FASTBUS circuits developed in the laboratory were known to work without the use of these chips. A description of how the transceiver works is given in appendix A.2.

The transceiver is more than just a voltage level translator. ECL logic has two states: high (1) and low (0), and the low logic level is used for the quiescent state when nothing is being transmitted. On the other hand, StarLAN RS-422 signalling for twisted-pair telephone cable has three states: differential high (1) (when the voltage difference between the reference wire to its pair is positive), differential low (0) (when the difference

Figure 2.24: Schematic diagram of the StarLAN-FASTBUS tranceiver.

is negative), and inactive (when the line is released to its quiescent state by shutting off the RS-422 driver's output). StarLAN transmissions begin with a differential low from the inactive state and voltage swings occur as defined by the Manchester-encoded bit stream, whose end is marked by a differential high lasting approximately two microseconds long, after which the line is released back to its inactive state. Hence, it takes more than just a simple voltage translation to map the three StarLAN RS-422 signal states to the corresponding ECL logic levels and vice versa.

Four boards were made, one for each Intel StarLAN board. A simple backplane repeater was constructed as well. This repeater would simply relay the logic levels at the transmit line (B57) to the receive line (B58). Thus, the backplane could be tested as a bus topology network without a hub. The repeater consisted of an ECL-to-TTL translator which was cascaded to a TTL-to-ECL translator. The input of the first chip was connected to the transmit line while the output of the second chip was connected to the receive line. Those particular chips were chosen simply because they happened to be immediately available (spare chips for the transceiver boards).

The connection diagram for this simple bussed network is shown in figure 2.23b. Three XT compatible microcomputers were used, as was done before when the StarLAN boards themselves were tested. The transceiver boards and repeater were plugged into the rear section of an unused FASTBUS crate. Three sets of 25-foot telephone cable were used to connect the telephone jacks of the transceivers to similar jacks on the StarLAN boards. Again, the tests of the simple StarLAN network were repeated in this network. No anomalies were observed and, as with the previous network, it was concluded that reliable communications were achieved.

# A StarLAN Hub for the FASTBUS Backplane

The development of the StarLAN-FASTBUS hub (or 'crate hub') was complicated because it was not at all certain that one could obtain, in a reasonable time, an integrated circuit which would implement the functions of a StarLAN hub. This chip, the Western Digital WD83C510<sup>2</sup>, was just about to be introduced to the market at that time (May-June 1987). It was not possible to obtain this chip from local sources or even directly from Western Digital. No other semiconductor company was known to be closer to mass-production of a StarLAN hub IC than Western Digital. An attempt was made to obtain this chip indirectly through an associate at the University of Illinois Center for Supercomputing. Nevertheless, the possibility of obtaining even one sample chip was not assured. So, in the mean time, a crate hub that did not use the WD83C510 was designed.

In general, standard StarLAN hubs cannot be coupled directly to a bussed line. This is because a collision in StarLAN is defined as the condition where more than one node is transmitting at the same time. Since collision detection is a function of the hub and only one node is assumed to be connected to each 'downstream' input channel, a hub would only have to watch out for simultaneous transmissions from any of its 'downstream' channels in order to detect collisions. In the case of a FASTBUS backplane, the transmit line can be connected to several nodes. If the signals on this line were simply connected to a standard StarLAN hub by, say, the transceiver circuit described previously, the StarLAN hub would 'see' only one channel and erroneously assume that only one node was connected to that channel even though that would not generally be the case. It is possible that a collision involving any of the nodes in a FASTBUS backplane could slip through without being detected by the hub. That of course depends on the particular

<sup>&</sup>lt;sup>2</sup>details given in [12]

hub's design. The only way to 'rigorously' catch these bus collisions as well as any anomalous signals in the backplane is to detect them by a separate circuit that watches for missing mid-cell transitions and pulses of improper width. The output of such a circuit could then be connected to another hub input. It would transmit an arbitrary StarLAN signal to that input upon detecting a collision. The hub would then sense at least two inputs transmitting simultaneously (one from the backplane line, the other from the auxilliary collision detection circuit) and flag the collision. This scheme would require two hub inputs per FASTBUS crate, a somewhat clumsy, but nevertheless feasible idea. Later on, it became clear that a rigorous collision detection function was a major design component of a crate hub anyway and the decision was made to design a complete self-contained crate hub for the FASTBUS backplane rather than implement the separate collision detector – external hub scheme as described above. The effort required to go all the way and design a crate hub was justified by the hub's elegance. The crate hub would be connected to all the nodes of the crate in a bus topology and itself would connect with a higher-layer hub as part of a star topology network.

The first version of the hub (that did not use a StarLAN hub chip) was a fully synchronous digital circuit whose block diagram is shown in figures 2.25, 2.26, and 2.27. An initial attempt was made to design the entire circuit heuristically, but it soon proved to be not only an awkward but ultimately, an impossible method given the complexity involved. So, the circuit was designed with a combination of formal and heuristic digital design techniques. One technique would be used when the other seemed to be more complicated. This circuit never got past the design phase because a prototype sample of the WD83C510 arrived, thanks to the efforts of Bob Downing from the University of Illinois. The hub controller chip probably saved at least a month of work to get a functioning hub, even though this meant starting over to design a new circuit based on the WD83C510. Figure 2.28 shows a schematic diagram of the resulting circuit, showing

a dramatic simplification of this implementation over the design that did not use the a hub chip. This was due, in part, to the design of the WD83C510 itself, which 'rigorously' detected collisions in each of its inputs, eliminating the need for a robust external collision detector (the 83C510 will flag a collision if an input receives pulses of improper widths or with missing mid-cell transitions, as well as if more than one input is receiving data). Another chip used in the circuit that is worth mentioning here is the SN75061 from Texas Instruments. This chip is a TTL-RS-422 transceiver designed especially for StarLAN applications. It provides the functions that would have previously required two separate chips (e.g., Am26LS30 and Am26LS32, which were used by the transceiver circuit when the TI chip was not yet obtained). Appendix A.3 explains how the hub circuit works. The circuit was built (very carefully, since only one WD83C510 was available and it was unlikely that another one could be quickly obtained) and tested. Figure 2.23c shows a diagram of the system used to test the circuit. As was done during previous tests, three XT compatibles with Intel StarLAN boards were used. Twenty-five-foot lengths of telephone cable coupled the StarLAN boards to their corresponding StarLAN-FASTBUS tranceivers, which were plugged at the back of a FASTBUS crate. The hub circuit was also plugged into the back of the FASTBUS crate to connect its 'downstream' channel to the transceivers. Its 'upstream' channel was connected to the Retix HB-6 StarLAN hub. This system allowed one to test the hub circuit for proper operation either as an intermediate or a header hub (by leaving the 'upstream' link connected or disconnecting it respectively). It also allowed the hub-detection logic of the WD83C510 to be tested.

Briefly, the hub-detection logic is used by the WD83C510 to sense if it is connected to a hub at a higher level in a StarLAN network. The hub-detection logic works as follows. Suppose the chip is functioning as an intermediate hub. If, after a short waiting period, no signal is received from its upstream channel, it assumes that it is not connected to a higher hub level and automatically proceeds to function as a header hub (if there was a higher

Figure 2.25: Block Diagram of Hub Circuit: I/O Section

Figure 2.26: Block Diagram of Hub Circuit: Downstream Section

Figure 2.27: Block Diagram of Hub Circuit: Upstream Section

Figure 2.28: Schematic Diagram of Hub Circuit with WD83C510 Controller

hub level, the higher hub would have either repeated the lower hub's transmission or, in the event of a collision, sent a collision presence signal (CPS) ). When the chip operates as a header hub, all downstream signals are immediately looped back. Now suppose that signals are received on the upstream channel of the hub chip in header hub mode. The hub-detection logic assumes that these signals must have come from a higher-level hub and the hub chip switches its operation from a header hub to an intermediate hub. A frame will be lost if it is transmitted during an intermediate-to-header hub transition because the hub chip will loop back only the remainder of the frame downstream when it switches to a header hub. This usually results in a CRC error. Two or more frames may be involved in a collision during a header-to-intermediate hub transition if a frame is received on the upstream channel while the hub is looping back a downstream frame.

As before, the Intel program was used to drive the system and collect performance statistics. Fortunately, everything worked perfectly right away without any problems. The on-chip hub-detection logic was tested by alternately connecting and disconnecting the link to the Retix StarLAN hub. The hub chip was observed to switch properly without causing a major disruption. The tests showed that data could be transferred reliably when the circuit was operating in either intermediate or header-hub mode. For the first time, data communications were successfully established in a prototype of the envisioned two-line StarLAN-based serial network.

### Chapter 3

#### Measurements

# 3.1 Electrical Characteristics of StarLAN Signals in the FASTBUS Backplane