## DESIGN, ANALYSIS, AND IMPLEMENTATION OF A DSP-BASED MODEM FOR CODE-PHASE-SHIFT KEYING

by

### ROBERT G. LINK

Ph.D.(Physics), The University of British Columbia, 1989

## A THESIS DRAFT SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF APPLIED SCIENCE

in

### THE FACULTY OF GRADUATE STUDIES DEPARTMENT OF ELECTRICAL ENGINEERING

We accept this thesis as conforming to the required standard

### THE UNIVERSITY OF BRITISH COLUMBIA

© Robert G. Link, October 1996

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Engineering Department of

The University of British Columbia Vancouver, Canada

Date Oct. 15, 1996

a de la compañía de l

DE-6 (2/88)

## Abstract

This thesis presents the design, analysis, and implementation of a radio-frequency modem which employs the Code-Phase-Shift Keying (CPSK) method of Direct-Sequence Spread-Spectrum (DS-SS) signaling. A correlation receiver is designed for a DSP based implementation. The received RF signal is brought to a digitally represented base-band signal by product demodulation at the nominal RF frequency, followed by low-pass filtering and dual-channel 8 bit sampling at 2 MSPS. Base-band signal processing is done on a quad TI TMS320C40 general purpose DSP. The SS spreading factor is user selectable from a range of 7 to 127; with corresponding data rates in the range 100 to 9.4 KBPS.

The herein designed tracking and acquisition algorithms are adapted from those of conventional DS-SS systems; while the carrier-phase tracking problem is solved by a new method hereby called Phase-Invariant-Reception (PIR).

Extensive bit-error-rate (BER) measurements have been made in Additive White Gaussian Noise (AWGN) and in the presence of single tone interference. All measured BER vs SNR or BER vs JSR curves are compared to those of an ideal optimal receiver. The implementation loss, with respect to the optimal receiver, for single-channel data flow in AWGN is approximately 1.8 dB in power efficiency when the stationary receiver and transmitter use local oscillators of the same nominal frequency. The additional BER power efficiency loss as a function of the difference in frequency of the latter two oscillators, is obtained exactly analytically and is confirmed experimentally.

The main contributions to the suboptimal BER performance are due to approximating the optimal correlator with an analog filter plus digital correlator, to tracking the timing slippage, and to using PIR instead of optimal coherent reception. The performance of the analog filter/digital correlator combination is obtained approximately analytically, and found to be independent of the signal-to-noise ratio. The BER degradation incurred by the tracking is derived analytically and found to be negligible for the timing error induced by the typical present day TTL clock oscillators, unless the SNR is very high. The theoretical BER performance of PIR is obtained exactly analytically, and found to approach that of coherent reception as the SNR increases.

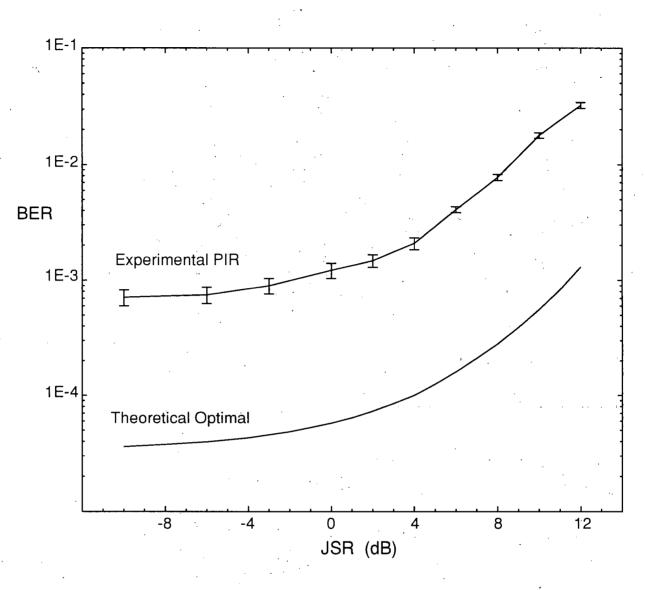

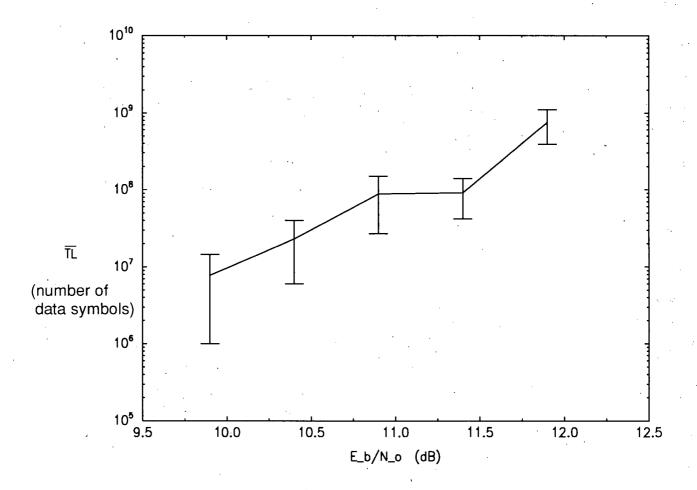

In addition, measured data for the mean time-to-acquire and the mean time-to-loselock in AWGN is presented; along with an outline on how these curves could be obtained analytically, and their implications for packet transmission.

ii

## Table of Contents

| Abstract          |                                                        |

|-------------------|--------------------------------------------------------|

| List of Figures . |                                                        |

| List of Tables    |                                                        |

| Acknowledgment    | s                                                      |

| Chapter 1         | Introduction                                           |

| Section 1         | Spread-Spectrum Communications: Motivation and         |

|                   | Applications                                           |

| Section 2         | Objective and Outline of This Thesis 2                 |

| Chapter 2         | Introduction to DS-SS and CPSK 4                       |

| Section 1         | Standard Direct-Sequence Spread-Spectrum with          |

|                   | Binary-Phase-Shift Keying                              |

| Section 2         | Code-Phase-Shift Keying DS-BPSK-SS 7                   |

| Chapter 3         | The Modem Implementation on a DSP Platform11           |

| Section 1         | General Architecture and Implementation                |

| Section 2         | The C40 Based IF Transmitter                           |

| Section 3         | The IF Receiver                                        |

| Section 4         | The Digital Demodulator                                |

| Section 5         | The Tracking and Acquisition Algorithms                |

| Section 6         | DSP On Board Results                                   |

| Section 7         | Experimental Setup                                     |

| Chapter 4         | Steady-State Performance of the Coherent Receiver 23   |

| Section 1         | Approximating The Optimal Correlator                   |

| Section 2         | BER Performance In The Presence of Timing Slippage 28  |

| Section 3         | Experimental BER in AWGN Performance with Carrier-Wave |

|                   | Synchronization Imposed Externally                     |

| Chapter 5    | Solving the Carrier-Wave Synchronization Problem by PIR for |

|--------------|-------------------------------------------------------------|

|              | CPSK                                                        |

| Section 1    | Phase-Invariant Reception                                   |

| Section 2    | BER For Real Data over the Complex Channel with AWGN        |

|              | - Theoretical Analysis and Experimental Results             |

| Section 3    | BER Performance of PIR for Time Varying Phase 42            |

| Section 4    | BER For Complex Data Flow with AWGN                         |

| Chapter 6    | The BER Performance of CPSK in the Presence of              |

|              | Single-Tone Interference                                    |

| Section 1    | Theoretical Analysis for Coherent Reception                 |

| Section 2    | Theoretical Analysis and Experimental Results for PIR 50    |

| Chapter 7    | Tracking and Acquisition in AWGN                            |

| Section 1    | Mean Time to Acquire                                        |

| Section 2    | Mean Time to Lose Lock                                      |

| Chapter 8    | Conclusions                                                 |

| Bibliography |                                                             |

| Appendix A   | Maximal Length PN Sequence Generation 61                    |

| Appendix B   | IF Transmitter Modules                                      |

| Section 1    | Digital Communication Port Interface                        |

| Section 2    | Level Shifter and Amplifier                                 |

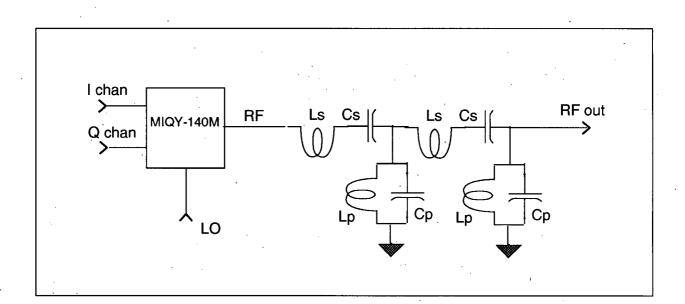

| Section 3    | BPSK Modulator and Bandpass Filter                          |

| Appendix C   | IF Receiver Modules                                         |

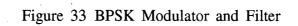

| Section 1    | BPSK Demodulator and Low Pass Filter                        |

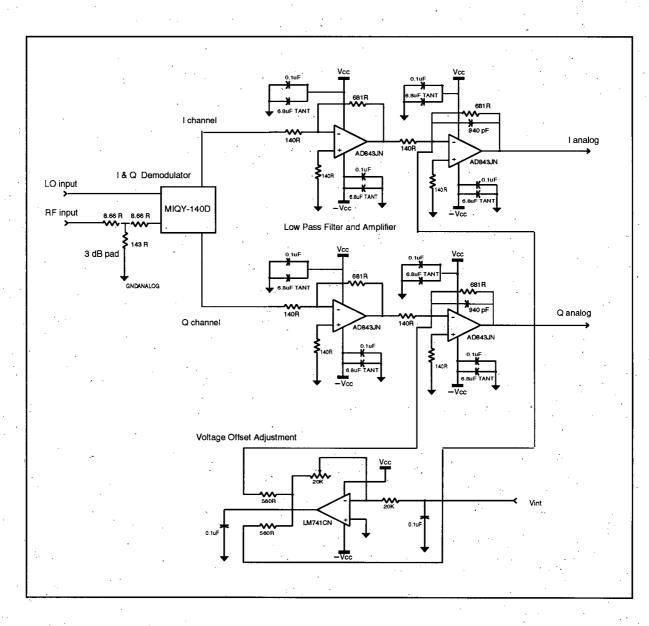

| Section 2    | Analog/Digital Converter                                    |

| Section 3    | ADC Converter Control                                       |

| Section 4    | FIFO Memory Banks                                           |

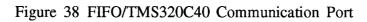

| Section 5    | FIFO/TMS320C40 Communication Port                           |

| · · ·      |                             |  |  |  |  |

|------------|-----------------------------|--|--|--|--|

| Appendix D | DSP Code Listings           |  |  |  |  |

| Section 1  | Master Receiver             |  |  |  |  |

| Section 2  | Pair of Complex Correlators |  |  |  |  |

| Section 3  | Tracking Correlators        |  |  |  |  |

| Section 4  | Transmitter Code            |  |  |  |  |

| Section 5  | Application Configuration   |  |  |  |  |

|            |                             |  |  |  |  |

|            |                             |  |  |  |  |

|            |                             |  |  |  |  |

|            |                             |  |  |  |  |

| • · · ·    |                             |  |  |  |  |

|            |                             |  |  |  |  |

v

.

. • •

# List of Figures

| Figure 1                                                                                             | Conventional DS-BPSK-SS System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2                                                                                             | CPSK Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 3                                                                                             | Synchronized CPSK Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

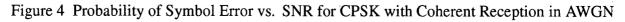

| Figure 4                                                                                             | Probability of Symbol Error vs. SNR for CPSK with Coherent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                      | Reception in AWGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

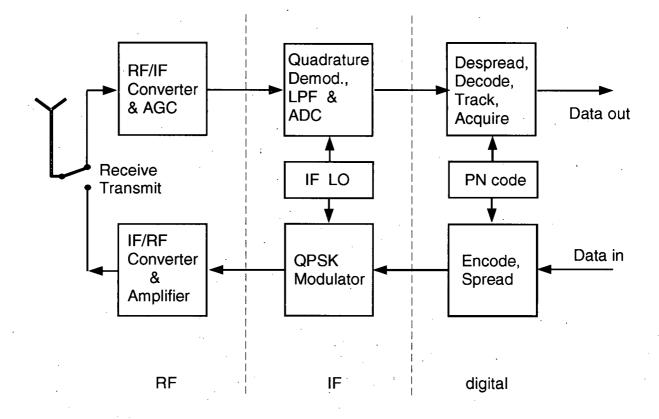

| Figure 5                                                                                             | Wireless Spread-Spectrum Modem Block Diagram 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

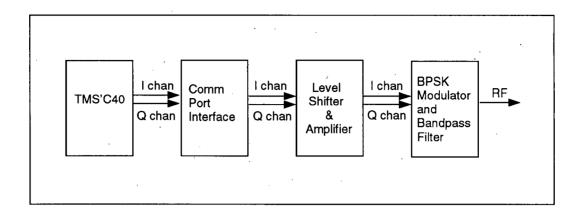

| Figure 6                                                                                             | C40 Based IF Transmitter Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

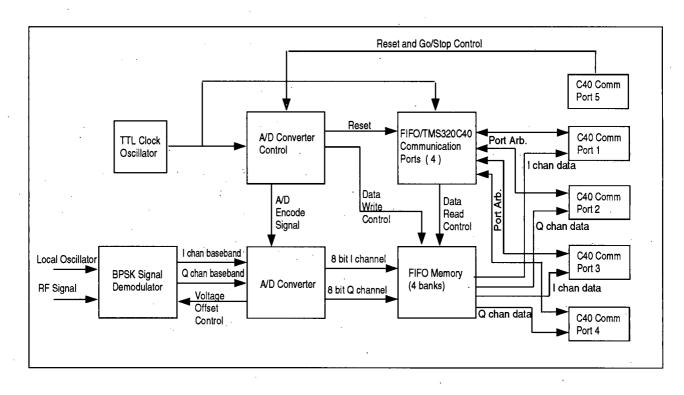

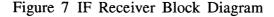

| Figure 7                                                                                             | IF Receiver Block Diagram14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 8                                                                                             | Digital Demodulator Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

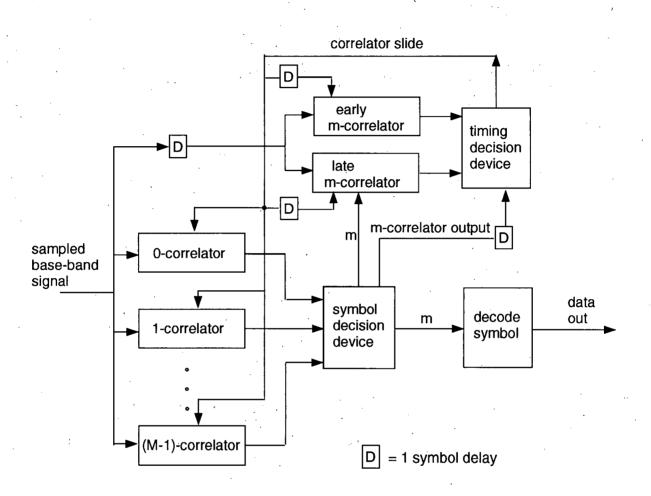

| Figure 9                                                                                             | Timing Decision Algorithm in Acquisition Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

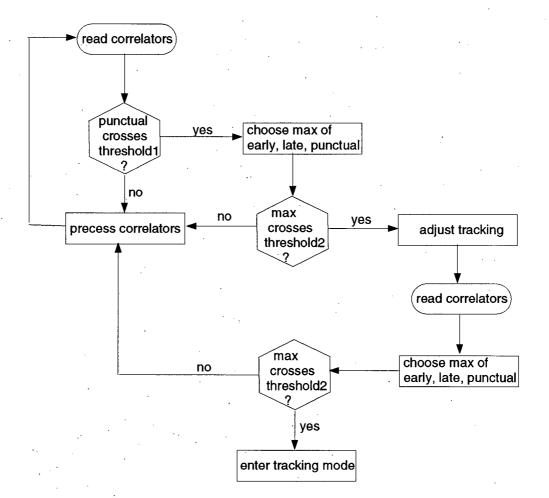

| Figure 10                                                                                            | Timing Decision Algorithm for Tracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 11                                                                                            | Experimental Setup for Measuring BER in AWGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 12                                                                                            | Analog Correlator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 13                                                                                            | Analog Filter with Digital Correlator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 14                                                                                            | LPF Response To a Square Pulse Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 15                                                                                            | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                      | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

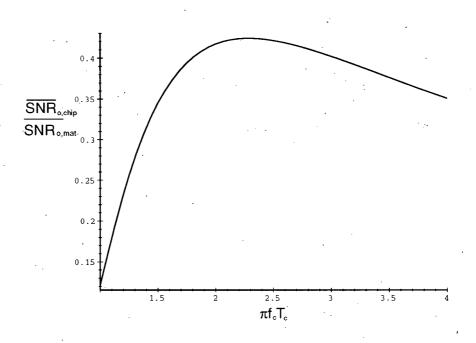

| Figure 15                                                                                            | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chip<br>as a Function of LPF Cut-off Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                      |

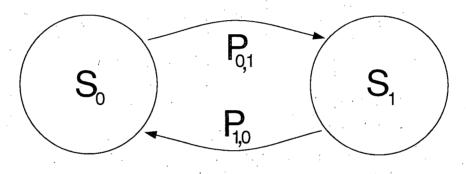

| Figure 15<br>Figure 16                                                                               | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chipas a Function of LPF Cut-off Frequency28Two-State Markov Chain29                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 15<br>Figure 16<br>Figure 17                                                                  | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chipas a Function of LPF Cut-off Frequency28Two-State Markov Chain29Signal Space for Tracking Performance Calculation31                                                                                                                                                                                                                                                                                                                                                             |

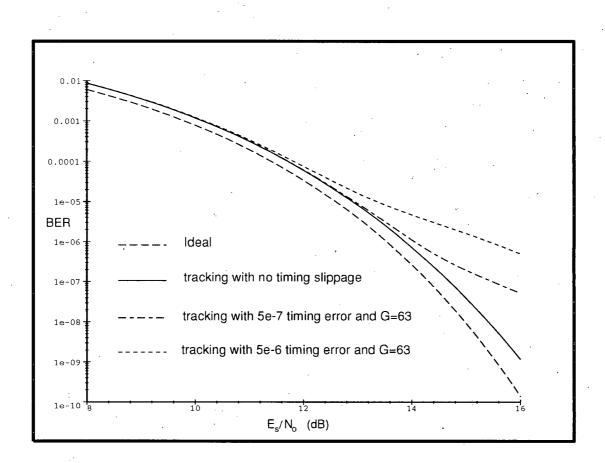

| Figure 15<br>Figure 16<br>Figure 17<br>Figure 18                                                     | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chipas a Function of LPF Cut-off Frequency28Two-State Markov Chain29Signal Space for Tracking Performance Calculation31BER Performance in AWGN with Tracking33                                                                                                                                                                                                                                                                                                                      |

| Figure 15<br>Figure 16<br>Figure 17<br>Figure 18                                                     | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chipas a Function of LPF Cut-off Frequency28Two-State Markov Chain29Signal Space for Tracking Performance Calculation31BER Performance in AWGN with Tracking33Bit Error Rate vs Signal-to-Noise Ratio for M=2 and M=4 CPSK                                                                                                                                                                                                                                                          |

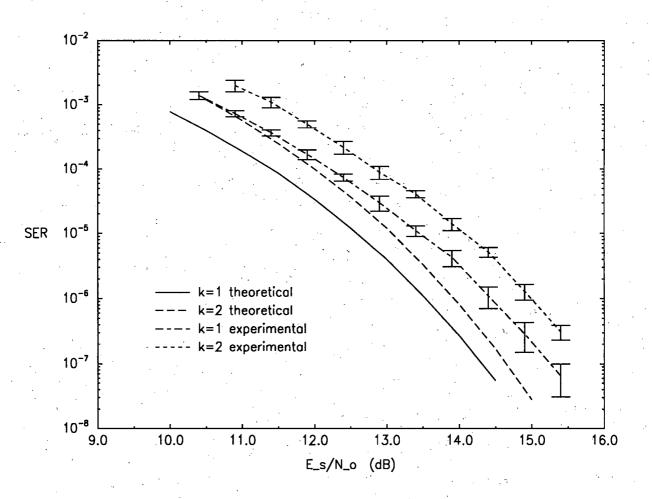

| Figure 15<br>Figure 16<br>Figure 17<br>Figure 18<br>Figure 19                                        | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chip<br>as a Function of LPF Cut-off Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 15<br>Figure 16<br>Figure 17<br>Figure 18<br>Figure 19<br>Figure 20                           | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chipas a Function of LPF Cut-off Frequency28Two-State Markov Chain29Signal Space for Tracking Performance Calculation31BER Performance in AWGN with Tracking33Bit Error Rate vs Signal-to-Noise Ratio for M=2 and M=4 CPSKwith Carrier-Wave Synchronization Imposed Externally34Quadrature CPSK Transmitter35                                                                                                                                                                       |

| Figure 15<br>Figure 16<br>Figure 17<br>Figure 18<br>Figure 19<br>Figure 20<br>Figure 21              | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chipas a Function of LPF Cut-off Frequency28Two-State Markov Chain29Signal Space for Tracking Performance Calculation31BER Performance in AWGN with Tracking33Bit Error Rate vs Signal-to-Noise Ratio for M=2 and M=4 CPSKwith Carrier-Wave Synchronization Imposed Externally34Quadrature CPSK Transmitter35Quadrature Demodulation followed by Complex Correlation36                                                                                                              |

| Figure 15<br>Figure 16<br>Figure 17<br>Figure 18<br>Figure 19<br>Figure 20<br>Figure 21              | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chip<br>as a Function of LPF Cut-off Frequency 28<br>Two-State Markov Chain 29<br>Signal Space for Tracking Performance Calculation 31<br>BER Performance in AWGN with Tracking 33<br>Bit Error Rate vs Signal-to-Noise Ratio for M=2 and M=4 CPSK<br>with Carrier-Wave Synchronization Imposed Externally 34<br>Quadrature CPSK Transmitter 35<br>Quadrature Demodulation followed by Complex Correlation 36<br>BER vs. Signal to Noise Ratio for PIR with Real Data over          |

| Figure 15<br>Figure 16<br>Figure 17<br>Figure 18<br>Figure 19<br>Figure 20<br>Figure 21<br>Figure 22 | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chipas a Function of LPF Cut-off Frequency28Two-State Markov Chain29Signal Space for Tracking Performance Calculation31BER Performance in AWGN with Tracking33Bit Error Rate vs Signal-to-Noise Ratio for M=2 and M=4 CPSKwith Carrier-Wave Synchronization Imposed Externally34Quadrature CPSK Transmitter35Quadrature Demodulation followed by Complex Correlation36BER vs. Signal to Noise Ratio for PIR with Real Data over42                                                   |

| Figure 15<br>Figure 16<br>Figure 17<br>Figure 18<br>Figure 19<br>Figure 20<br>Figure 21<br>Figure 22 | Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chipas a Function of LPF Cut-off Frequency28Two-State Markov Chain29Signal Space for Tracking Performance Calculation31BER Performance in AWGN with Tracking33Bit Error Rate vs Signal-to-Noise Ratio for M=2 and M=4 CPSKwith Carrier-Wave Synchronization Imposed Externally34Quadrature CPSK Transmitter35Quadrature Demodulation followed by Complex Correlation36BER vs. Signal to Noise Ratio for PIR with Real Data over42Output SNR As a Function of Rx and Tx LO Frequency |

| Figure 25 | Theoretical and Experimental BER versus JSR at SNR=12.0                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|           | dB with $\delta \omega = 0.1 \omega_c \ldots 52$ |

| Figure 26 | Mean Time-to-Acquire Measured in Data Symbol Durations                                                                                      |

|           | vs SNR for G=63                                                                                                                             |

| Figure 27 | Markov Chain for Tracking Loss Calculation                                                                                                  |

| Figure 28 | Mean Time-to-Lose-Lock Measured in Number of Data                                                                                           |

| · · ·,    | Symbols vs. SNR                                                                                                                             |

| Figure 29 | Three-Stage Maximal Generator                                                                                                               |

| Figure 30 | I-Sequence Autocorrelation Function                                                                                                         |

| Figure 31 | Communication Port Interface (one channel)                                                                                                  |

| Figure 32 | Level Shifter and Amplifier                                                                                                                 |

| Figure 33 | BPSK Modulator and Filter                                                                                                                   |

| Figure 34 | BPSK Demodulator and Low Pass Filter                                                                                                        |

| Figure 35 | Dual Channel 8–Bit ADC                                                                                                                      |

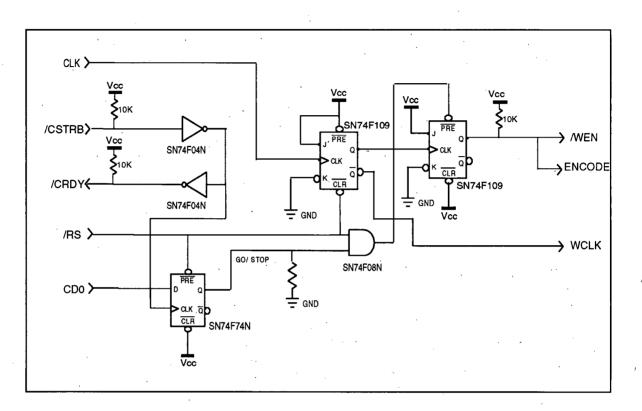

| Figure 36 | ADC Converter Control                                                                                                                       |

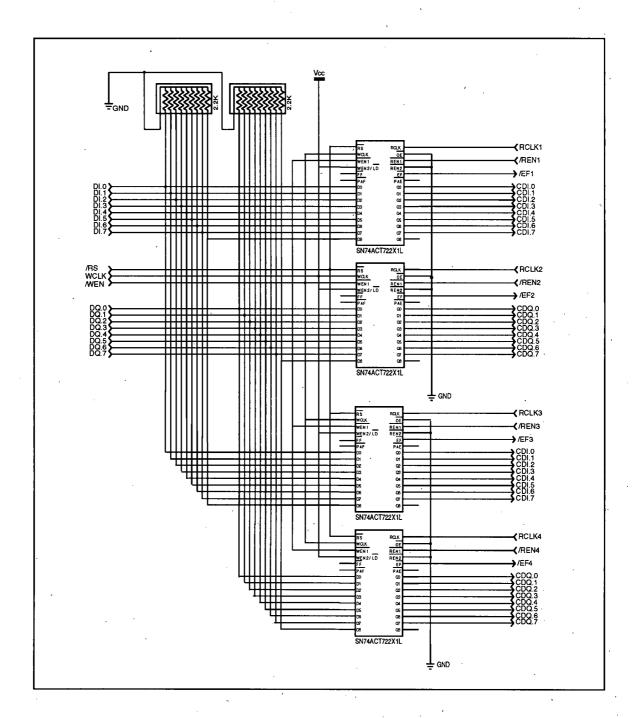

| Figure 37 | FIFO Memory Banks                                                                                                                           |

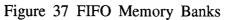

| Figure 38 | FIFO/TMS320C40 Communication Port                                                                                                           |

## List of Tables

viii

## **Acknowledgments**

I wish to thank my research supervisor Dr. Victor C.M. Leung for the direction he gave me, and for the leadership that he gave to the WLAN project, of which this work forms part.

I thank the professors from whom I have learned about the theory of modern day telecommunication systems — these are Prof. Samir Kallel, Prof. Takis Mathiopoulos, and Prof. Victor C.M. Leung. I also thank Professor Robert W. Donaldson for advice on my program and for having me on two earlier research projects, before letting me go to the WLAN project.

A very special thanks go to our scientific engineer Hansen Wang for designing a portion of the modem hardware, for doing the PCB layout, for assistance with the modem testing, and for very valuable help in general. Thanks also go to Amiee Chan for assisting Hansen and I with the RF portion of the hardware design and construction.

This work was supported by the Science Council of British Columbia through a Technology B.C. Grant.

## Chapter 1 Introduction

## **1.1 Spread-Spectrum Communications:** Motivation and Applications

A spread spectrum communication system is defined to be one for which the transmitted signal occupies a bandwidth much larger than the minimum bandwidth necessary to send the information [1]. Every information signal modulates a spreading signal, called the code signal, which is independent of the data. At the receiver, recovery of the original signal is accomplished by despreading; whereby the received spread signal is correlated with a synchronized replica of the spreading signal. The signal thus recovered is then processed by the usual techniques for communication signal reception. The techniques for spreading are direct sequencing, frequency hopping, time hopping, and hybrids of these.

The use of spread-spectrum techniques originated in the development, by the military, of communication systems highly immune to intentional interference by a jammer. The idea is that if many orthogonal signal coordinates are available to a communication link, and if only a small subset of these coordinates are used at any one time, a jammer who cannot determine the signal subset currently in use would be severely handicapped. Because the error performance of the system is a function of the received signal to noise ratio, against infinite power gaussian noise, increasing the bandwidth does not improve performance. However, when the noise comes from a jammer with fixed finite power, and with uncertainty as to where in the signal space the transmission is presently located, the error performance is significantly improved.

The energy density of a spread signal can be made very low because the signal power is on average spread uniformly over the enlarged number of signalling coordinates. This makes the signal very difficult to detect; and in fact, to anyone who does not posses a synchronized replica of the spreading signal, the spread signal will appear to be random noise.

These properties of high interference rejection and low probability of interception have been exploited to give rise to the multiple access technique called code-division multiple access (CDMA) wherein each user of the communication channel employs a unique spreading signal to locate herself in the common transmission band. In fact, the method has become the basis for the development of new cellular radio systems for personal communications

networks. The spreading signal is based on a pseudorandom sequence called a key. Each radio uses its own unique key for receiving transmissions, and each radio can transmit waveforms with the key corresponding to some other radio. The different keys correspond to sequences designed to have low cross-correlation and low autocorrelation properties.

The low cross-correlation of two different keys insures that a receiver locked on to a signal will experience relatively little interference from any other signal of the same channel based on a different key. Similarly, the low autocorrelation of a key will mitigate multipath effects, because a signal due to a multipath component which arrives with a delay with respect to the signal to which the receiver is synchronized, will be strongly attenuated.

Direct sequencing is discussed in detail in the next chapter. In the frequency hopping technique, the spreading is done by changing the carrier frequency of the transmitted signal, at a rate called the hop rate, according to the code sequence. With the time hopping technique, the code sequence is used to key the transmitter on and off.

### **1.2 Objective and Outline of This Thesis**

The objective of this thesis is to present the design, analysis, and implementation of a new radio-frequency (RF) direct-sequence spread-spectrum (DS-SS) modem which can enhance both the power efficiency and the bandwidth efficiency of the present day conventional DS-SS systems. It uses a technique called Code-Phase-Shift Keying (CPSK), which is first proposed in [2].

The presentation is organized as follows: In Chapter 2 an introduction is given to the code-phase-shift keying method of direct-sequence spread-spectrum signaling. The remaining chapters describe work by the author which constitutes original contribution.

Chapter 3 documents both the design and the implementation on a digital signal processing (DSP) platform, of the modem. A correlation receiver is designed, and the problem of synchronizing the receiver to the baseband signal is solved. The synchronization to the bit intervals is achieved by an acquisition scheme which is a generalization of the simplest acquisition scheme for conventional DS-SS. A timing recovery algorithm to maintain the bit interval synchronization, called tracking, has been realized in a hardware efficient manner by a novel design.

Optimal correlating has been approximated by a combination of analog filtering and digital correlating; and in Chapter 4, an analysis of the signal-to-noise ratio (SNR) degradation

incurred by this approximation has been estimated analytically. This chapter also contains theoretical analysis of the bit-error-rate (BER) in additive white gaussian noise (AWGN) performance of the herein designed signal tracking scheme. The implementation loss associated with the tracking scheme has been analytically estimated and found to be negligible for BERs less than  $10^{-6}$  for the timing slippages induced by typical TTL clock oscillators. To close Chapter 4, measured BER performance in AWGN, of the receiver with the carrier-wave synchronization imposed externally, is presented. These measurements were performed to test the design, and to obtain an experimental confirmation of the analytic performance estimate thus far.

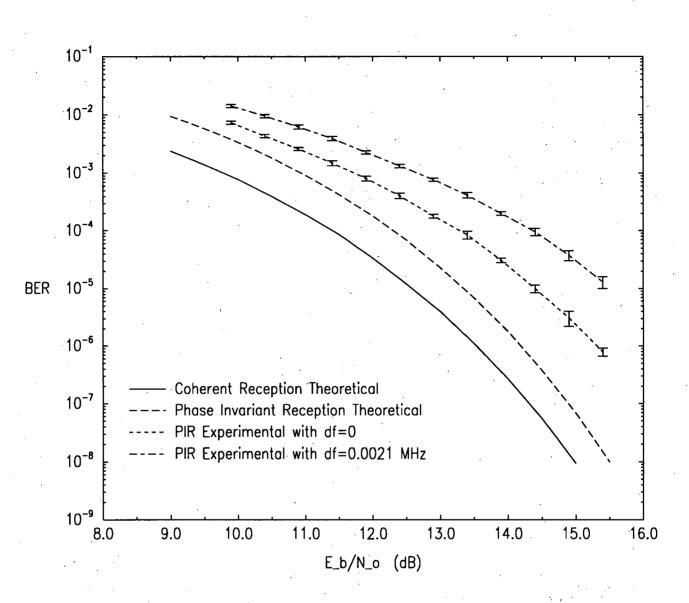

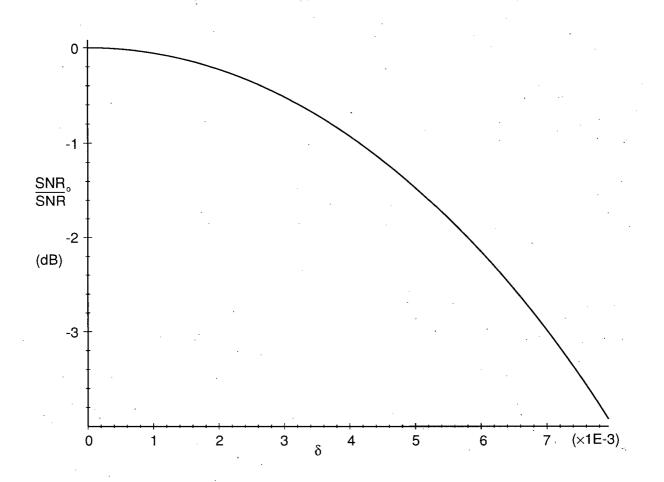

The synchronization to the phase of the carrier wave problem is solved by a new method which is hereby named Phase-Invariant-Reception (PIR). This is presented in Chapter 5 along with a theoretical performance analysis and experimental results for the BER in AWGN. The degree to which PIR approximates optimal reception has been obtained exactly analytically as a function of the frequency difference between the carrier-wave and the local oscillator (LO) of the receiver.

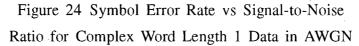

Chapter 6 gives theoretical analysis and experimental results on system performance in the presence of single-tone interference. A numerical expression for the BER performance of the coherent CPSK receiver has been obtained in AWGN and single tone interference. This is compared to the measured performance of the CPSK receiver employing phase-invariant reception. All claims to receiver performance have been verified, to within experimental uncertainty, by the bit error rate measurements.

Chapter 7 presents experimental results on the acquisition and tracking performance of the receiver, and outlines the mathematical problems which need to be solved in order to predict these results theoretically. Mean time-to-acquire and mean time-to-lose-lock in AWGN data is reported, along with the implications for transmission data packet format.

Chapter 8 finishes with the conclusions and discussion of future development.

## Chapter 2 Introduction to DS-SS and CPSK

# 2.1 Standard Direct-Sequence Spread-Spectrum with Binary-Phase-Shift Keying

At the modulator of a generic direct-sequence system, the information signal, of data rate  $R_d$ , is multiplied by a code signal with symbol rate  $R_c$ , called the code chip rate. The ratio  $G = R_c/R_d$  is equal to the factor by which the signal transmission bandwidth is spread. It is usually much greater than unity, and is called the processing gain.

Since multiplication in the time domain transforms to convolution in the frequency domain, provided the information signal is relatively narrow-band, the product signal will have approximately the bandwidth of the spreading signal. At the demodulator, the received signal is multiplied by a synchronized replica of the code signal; thus collapsing the desired signal to its original bandwidth, while spreading any undesired signal in the same way that the transmitter spread the desired signal originally. The signal is subsequently passed through a bandpass filter, whose passband corresponds to the spectrum of the information signal, resulting in a high rejection of the interfering signal. The difference in output and input signal-to-noise ratios, in dBs, for a narrow band interferer is equal to the processing gain in dB. To see this in detail, refer to Figure 1 and consider the following analysis for the conventional coherent DS-BPSK-SS system. More details can be found in [3].

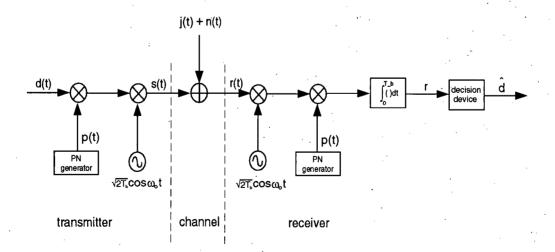

Figure 1 Conventional DS-BPSK-SS System

The information sequence to be sent over the channel is represented by an antipodal pulse stream, d(t), where a pulse value of +1 represents a 0 bit, a pulse value of -1 represents a 1 bit, and the bit duration is  $T_b$ . This information signal is spread by multiplication with the antipodal chip stream p(t), with chip duration  $T_c = T_b/G$ . p(t) represents a periodic pseudorandom sequence called a pseudonoise (PN) sequence; the generation of which is discussed in Appendix A. It is required that p(t) be synchronized with d(t), so that each bit period accommodates precisely G chips. Finally, the spread signal modulates the carrier, to produce the transmitted signal:

$$s(t) = \sqrt{2P}d(t)p(t)\cos\omega_o t; \qquad (2.1)$$

where  $P = E_b/T_b$  is the transmitter power,  $E_b$  is the energy of the signal representing one bit, and  $\omega_o$  is the carrier frequency in radians.

With the receiver exactly synchronized to the bit interval, and to the carrier phase, the delay for the communication link can be taken to be zero, and the simplified block diagram, omitting the synchronization modules, of the system is as in Figure 1. We wish to consider the error performance of the idealized receiver for a channel which adds noise and interference to the transmitted signal.

The channel output is

$$r(t) = s(t) + j(t) + n(t);$$

(2.2)

where j(t) is narrow-band interference, centered at the carrier, of total average power  $J_{av}$ , and n(t) is additive white gaussian noise of power spectral density  $N_o$ . Denoting the spread signal bandwidth as W, the value of the power spectral density of an equivalent wide-band interference is  $J_o = J_{av}/W$ .

The received signal is despread, by correlating against p(t), and demodulated by correlating against  $\sqrt{2/T_b} \cos \omega_o$ . Thus, after every  $T_b$  seconds, the BPSK detector outputs

$$r = d\sqrt{E_b} + J + N; \tag{2.3}$$

where  $d (= \pm 1)$  is the data bit for the  $T_b$  second interval, and the interference and noise components are respectively:

$$J = \sqrt{\frac{2}{T_b}} \int_0^{T_b} p(t)j(t) \cos \omega_o t \, dt \tag{2.4}$$

$$N = \sqrt{\frac{2}{T_b}} \int_0^{T_b} p(t)n(t) \cos \omega_o t \, dt.$$

(2.5)

The white noise has zero mean and variance  $E[N^2] = N_o/2$ ; while the interference has zero mean, and in the limit of zero bandwidth, variance  $E[J^2] = J_o/2$ .

The BPSK decision rule is to choose  $\hat{d} = +1$  if r > 0, and choose  $\hat{d} = -1$  if  $r \le 0$ . Assuming that  $d = \pm 1$  are transmitted with equal probability, one may take, without loss of generality, d = -1; to compute the probability of bit error  $P_{\epsilon}$ .

$$P_{\epsilon} = \Pr\{r > 0 | d = -1\} = \Pr\{J + N > \sqrt{E_b}\}$$

(2.6)

With the statistics of the interference gaussian and independent of the thermal noise statistics, the bit error probability is given by

$$P_{\epsilon} = \frac{1}{2} \operatorname{erfc}\left(\sqrt{\frac{E_b}{N_o + J_o}}\right); \tag{2.7}$$

where erfc is the complementary error function.

Therefore; as previously mentioned, the spreading does not improve the error rate performance of Coherent BPSK in white noise. However, the effects of the narrow-band interferer are reduced by a factor equal to the processing gain.

To implement Forward Error Correction (FEC) encoding in conventional DS-SS, the data stream is first encoded to a higher rate symbol stream by block or by convolutional encoding; which is then transmitted by the same transmitter as in Figure 1. The receiver structure for coherent reception is also the same except that the integration is now over the symbol period; and the resulting stream of decision variables is used by a more general decision device to form an estimate of the original data stream.

To increase the data rate without increasing the required transmission bandwidth, while maintaining the high interference rejection capability, one can use M-ary modulation, in which a signaling alphabet of M different code sequences is used to transmit alphabet symbols representing multiple bit sequences. One such method, which offers the performance advantages of conventional M-ary DS-SS systems; but also many implementation advantages over other M-ary DS-SS systems, is the CPSK method described in the next section.

### 2.2 Code-Phase-Shift Keying DS-BPSK-SS

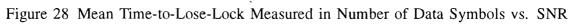

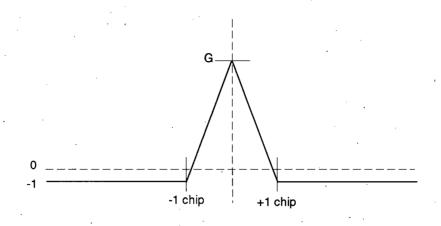

In the CPSK method, each of the  $M = 2^k$ , where the word length k is the number of bits per symbol, signaling waveforms is obtained by a different phase shift (an integer number of chips) of a single PN maximal length code sequence p(t). It's autocorrelation function is

$$R(\tau) = \sum_{i=0}^{i=G-1} p(iT_c)p((i+\tau)T_c) = \begin{cases} G, & \text{if } \tau = 0, G, 2G, \dots; \\ -1, & \text{otherwise.} \end{cases}$$

(2.8)

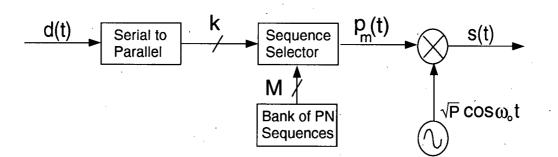

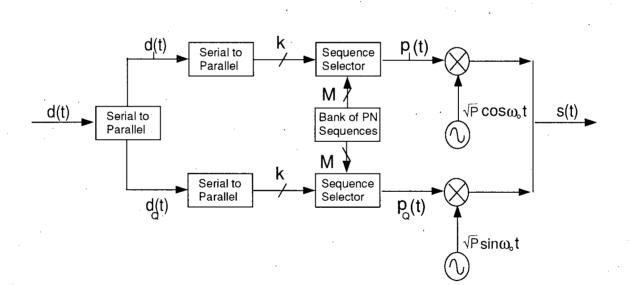

The transmitter, shown in Figure 2, groups the data into k-bit data symbols of duration  $T_s$ . Each of these are represented by an integer m,  $0 \le m \le M - 1$ , which is used to select the signaling waveform  $p_m(t) = p(t - m_c T_c)$ ; which is the phase shift by  $m_c = m(G+1)/M$  chips of the non-shifted PN sequence p(t). The final up-conversion for transmission at carrier frequency  $\omega_o$  results in transmitter output

$$s(t) = \sqrt{2P} p_m(t) \cos \omega_o t; \qquad (2.9)$$

where  $P = E_s/T_s$  is the transmitter power, and  $E_s$  is the energy of the signal representing a symbol (a PN sequence).

Figure 2 CPSK Transmitter

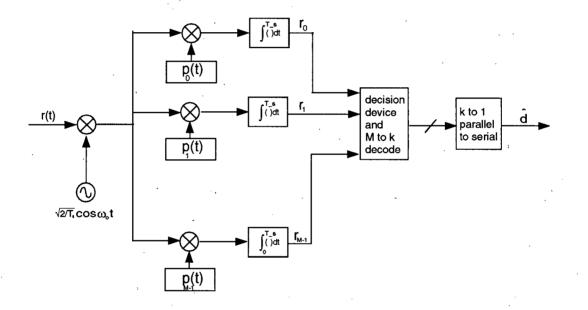

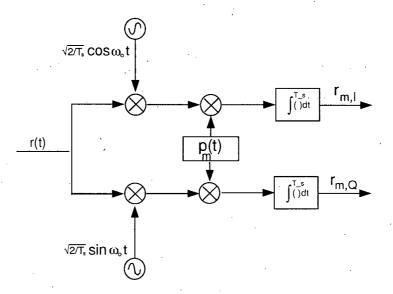

For now, assume synchronization, so that the CPSK correlation receiver for coherent reception is as in Figure 3. The received signal, r(t) = s(t) + j(t) + n(t), is fed to a bank of M correlators, one for each alphabet member PN sequence  $p_m(t)$ . When the m-th symbol is sent, the output of the m-th correlator, after every symbol period, is

$$r_m = \sqrt{E_s + J_m + N_m}; \tag{2.10}$$

while the output of the other correlators,  $r_i$  for  $i \neq m$ , are

$$r_{i} = \frac{-1}{G}\sqrt{E_{s}} + J_{i} + N_{i}.$$

(2.11)

The noise and interference terms are  $(\forall i \mid 0 \leq i \leq M - 1)$ :

$$J_i = \sqrt{\frac{2}{T_s}} \int_0^{T_s} p_i(t)j(t) \cos \omega_o t \, dt \tag{2.12}$$

$$N_i = \sqrt{\frac{2}{T_s}} \int_0^{T_s} p_i(t)n(t) \cos \omega_o t \, dt.$$

(2.13)

Figure 3 Synchronized CPSK Receiver

The decision device decides in favor of the symbol corresponding to the correlator with the largest output. When the interference is a single tone jammer at the carrier wave frequency,

$$j(t) = A\cos(\omega_o t + \phi), \qquad (2.14)$$

the terms  $J_i$  are equal for all *i*, and therefore do not affect the decision. Thus, the effects of a carrier-wave jammer are completely mitigated by CPSK signaling. When the single-tone interference is not precisely at the carrier-wave frequency, the decision is affected, and the noise performance of the receiver is degraded (but still much better than for conventional DS-SS). The analysis of this more complicated situation is left for Chapter 6. The white noise terms are independent, zero-mean, gaussian random variables with variances  $E[N_i^2] = N_o/2$ ; and therefore, when the spreading factor is much greater than unity, G >> 1, the probability of symbol error in AWGN,  $P_{\varepsilon}$ , is precisely that for coherent reception of M orthogonal signals [4]:

$$P_{\varepsilon}(M, E_s/N_o) = 1 - \int_{-\infty}^{+\infty} f(\alpha - \sqrt{E_s}) \left( \int_{-\infty}^{\alpha} f(\beta) \, d\beta \right)^{(M-1)} d\alpha; \qquad (2.15)$$

where

$$f(\alpha) = \frac{1}{\sqrt{\pi N_o}} \exp\left(\frac{-\alpha^2}{N_o}\right).$$

(2.16)

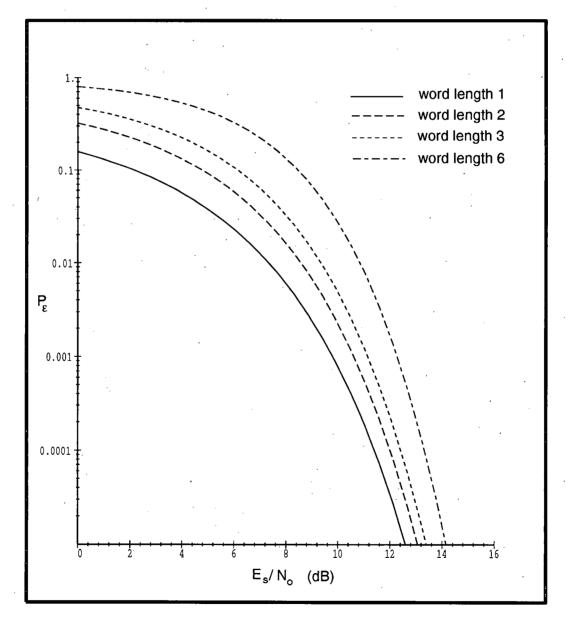

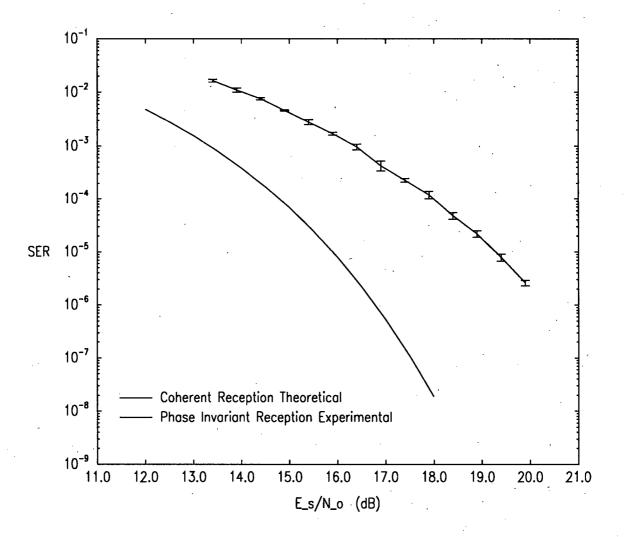

Figure 4 shows a plot of the probability of symbol error as a function of symbol signalto-noise ratio (SNR =  $E_s/N_o$ ) for several values of M. Using the fact that an M-ary symbol represents  $k = \log_2 M$  bits, and that the energy of a bit is  $E_b = E_s/k$ ; the symbol error probability as a function of symbol SNR can be converted to a bit error probability as a function of bit SNR. The BER (equal to the bit error probability), at a given bit signal-to-noise ratio decreases with increasing word length k. The power efficiency of a communication system operating at a certain BER is defined as the SNR required to attain the specified BER. The power efficiency of optimal coherent M-ary signaling for word length 1 is 3 dB poorer, for word length 2 is slightly poorer, and for word length 3 is better than that of coherent BPSK (at any BER). At word length 6, M-ary signaling outperforms BPSK by 3.5 dB at a BER of  $10^{-5}$ . In other words, at word length 6, in thermal noise, CPSK outperforms conventional DS-SS by 3.5 dB.

The system discussed thus far is an idealization whose performance represents the upper limit which an implementation could realize. Synchronization of the receiver to the phase of the carrier wave, and to the time of the bit and chip intervals has been assumed for coherent reception. Hereafter, a set of synchronization modules are designed, and optimal correlators are approximated, to realize a complete receiver which approximates optimal coherent reception.

## Chapter 3 The Modem Implementation on a DSP Platform

### 3.1 General Architecture and Implementation

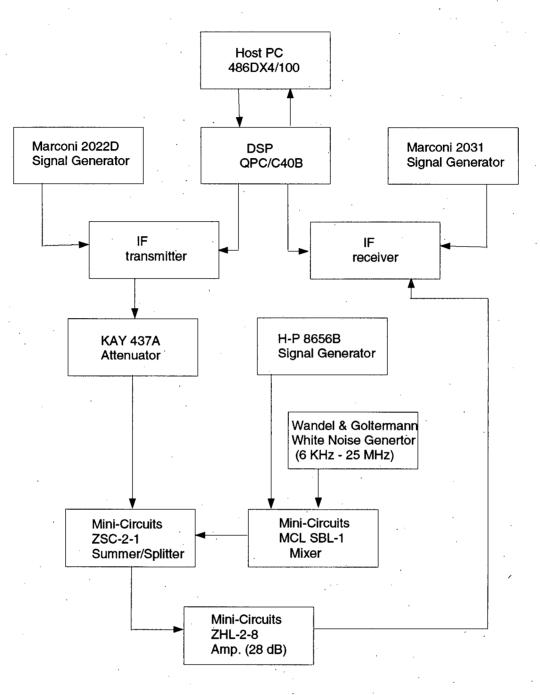

The development is aimed towards the construction of a wireless, high processing gain, high data throughput modem which transmits at radio frequency in an ISM band. (ISM bands are the industrial, scientific and medical bands in the gigahertz range over which unlicensed spread spectrum systems are employed.) See Figure 5 for the high level block diagram illustrating the general architecture. The signal processing unique to CPSK is done at the digital stage, which is implemented on a general purpose DSP. To test this system, we have developed a prototype which operates at IF (chosen to be 140 MHz) thus allowing the performance to be evaluated by measurements taken with an RF channel simulator inserted into the IF link. An eventual RF modem could be built and on-air tested by integrating the present system with IF/RF up/down converters and RF transceivers.

The general purpose DSP used is the QPC/C40B, built by Loughborough Sound Images, which is comprised of four TI TIM-40 modules, each of which hosts a TI TMS320C40 and 96 kilowords of SRAM [5]. Of the four C40s; three are dedicated to the receiver, and one is dedicated to the transmitter.

An optimizing C compiler along with a substantial run-time library has been purchased from 3L Software of Edinburgh [6]. However, the TMS320C40 C compiler does not produce satisfactory code for many of the time critical operations; as it does not seem to be aware of all of the hardware — in particular, the circular addressing modes of the C40. Therefore, it was found necessary to code many of the software modules directly in TMS assembler. The code listings, (either in C40 C or assembler, depending on the module), are given in Appendix D.

Figure 5 Wireless Spread-Spectrum Modem Block Diagram

### 3.2 The C40 Based IF Transmitter

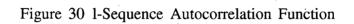

The digital modulator implementing the code-phase-shift keying, direct-sequence spreadspectrum signaling technique, as described in the previous chapter, uses a C40 to produce an asynchronous chip stream from the data file to be transmitted. During the transmission, the software is responsible for maintaining the C40 output communication port FIFO nonempty; while an interface reads from the C40 fifo and clocks the data into a level-shifter (converts TTL to bipolar) and amplifier. The resulting chip stream is then BPSK modulated onto the IF carrier by Mini-Circuits MIQY-140M quadrature modulator. This is followed by a bandpass LC filter (in-house constructed by the author due to the unavailability of an off-the-shelf unit) to remove the signal replicas produced at harmonics of the carrier by the modulator. See Figure 6 for the block diagram of the C40 based IF transmitter. The indicated modules are built on a PCB copperboard, and connected to the C40 by a high density, 0.025" pitch ribbon cable. A description and a circuit schematic for each of these modules is given in Appendix B.

Figure 6 C40 Based IF Transmitter Block Diagram

### 3.3 The IF Receiver

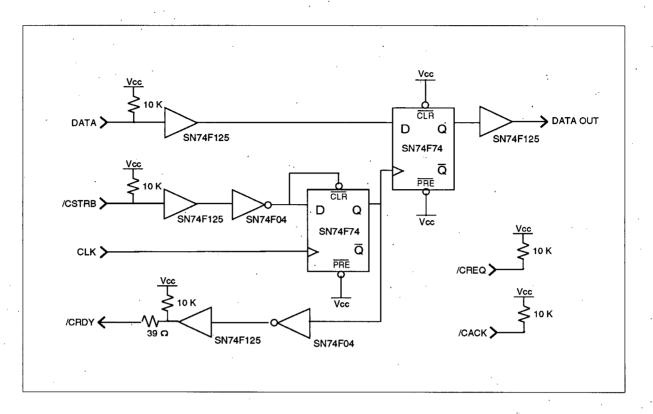

The incoming IF signal is product demodulated and low-pass filtered so as to recover the baseband signal. The BPSK product demodulation is done with Mini-Circuits MIQY-140D quadrature demodulator. The ensuing low-pass filter not only removes the second and higher harmonics of the IF signal resulting from the product operation; but has a bandwidth chosen low enough to maximize the output signal-to-noise ratio of the BPSK signal demodulator. This is discussed in detail in the next chapter.

The baseband signal is sampled at twice the chipping rate (or four time the chipping rate with a two-sample preaccumulation) by a dual-channel 8-bit ADC. The samples are synchronously written to a bank of four FIFO memories, and asynchronously read from the FIFOs and written to the DSP by four FIFO/TMS320C40 communication ports. As explained more fully in the next section, for each channel of data (I or Q), the tracking algorithm requires the same channel of data delayed by one data symbol — resulting in a total of four data streams to be processed by the digital demodulator.

Figure 7 shows the high-level block diagram of the IF receiver. It was prototyped by the author and built on a full size PC AT printed circuit board as documented in [7]. Each of the modules indicated in Figure 7 is described in detail, with circuit schematics, in Appendix C.

### 3.4 The Digital Demodulator

There are two primary methods of implementing a despreader for the standard DS/SS system: the code-matched filter and the serial correlator-accumulator technique. This is also the case in the CPSK signaling scheme, wherein the receiver employs a bank of correlators or matched filters — one for each of the possible phase shifts.

In the code-matched filter technique, the entire reference PN sequence and each of its phase shifts corresponding to a data symbol are stored in separate length G registers; while the incoming signal samples are stored in another length G shift register. As the incoming signal moves chip by chip down the signal register, it will give a large positive correlation with one signal register when it contains a data symbol. In this method, no separate sequence acquisition is required, as the signal is acquired during the first complete symbol received. However, implementing this algorithm in software results in a prohibitively slow receiver because the cross-correlation between the signal sequence and each phase shifted PN sequence is computed once per chip. With a serial correlator-accumulator, one has an entire symbol period in which to compute the required cross correlations; and therefore we choose this technique, as it is appropriate for a DSP based implementation.

Figure 8 shows a block diagram of the digital receiver. The term m-correlator means a correlator which correlates against the PN sequence,  $p_m(t)$ , representing the *m*-th data symbol.

Figure 8 Digital Demodulator Block Diagram

Each correlator must process at the sampling rate (two times the chipping rate,  $R_c$ ); whereas the symbol decision device must process at the correlators output rate (the data symbol rate times the number of symbols). With a fixed amount of processing power available for correlation at a given PN sequence length, the maximum chipping rate which the system can handle is inversely proportional to the number of data symbols (the number of correlators); whereas the data rate is proportional to the symbol word length, k, times the chipping rate. Because the number of data symbols is  $2^k$ , the data rate,  $R_d$ , is given by

$$R_d = K \frac{k}{2^k}; \tag{3.1}$$

for some constant K. Thus, the maximum data rate is obtained for word lengths 1 and 2.

Based on this finite processing power performance consideration, we choose to implement the word length 1 and word length 2 versions on the DSP. By adding more processing power, one could maintain the chipping rate constant as one increases the data symbol alphabet length. This would give a data rate proportional to the word length. This could be done by adding more processors to the DSP, or by implementing the correlators in hardware, and using the DSP for processing the correlator bank output. The latter approach is taken in [8]; where a RAKE receiver for conventional DS-SS is designed.

The three processors dedicated to the digital demodulator share the tasks indicated in Figure 8 as follows: Processor A implements the symbol decision device, the timing decision device, and the symbol decoder. Processor B implements the bank of punctual correlators. Processor D implements the early and late pair of correlators required for tracking. (Processor C is dedicated to transmission). The one symbol delay required for the input sample stream to the early/late correlator pair is implemented in hardware by a FIFO on the IF receiver. Processor A is the master processor which controls the two slave processors implementing correlators. It reads from, and configures the correlators; reading and updating the configuration at the data symbol rate.

### 3.5 The Tracking and Acquisition Algorithms

The system is designed for packet transmission. After initialization, the receiver enters it's acquisition mode, to perform the initial PN code synchronization, and remains in this mode indefinitely until it successfully acquires a signal. It then enters it's tracking mode; during which it continually fine adjusts the symbol interval synchronization, and decodes and stores the incoming data. It remains in this mode until it loses lock — either because of excessive noise or because the signal transmission has ended. It then passes the data, stored in the DSP's on board memory, to the host computer. The program may then be restarted.

Each data packet must have a preamble, of sufficient length (discussed later), consisting of a string of the zeroth data symbol. This is followed by a special data sequence to flag the end of the preamble and the beginning of the original data. The data is also terminated by the special sequence. The data passed to the host by the modern will consist of the portion of the preamble remaining after the receiver achieved acquisition, the encapsulated data packet, and perhaps several bits decoded from noise before the receiver lost lock. It is left to the host to extract the encapsulated data packet.

In the acquisition mode, the data symbol correlators are precessed by a shift of two samples, (one chip) between every trial symbol read. With reference to Figure 8, the symbol decision device chooses the correlator with the largest output and passes that output to the timing device, the timing device outputs the two-sample correlator precession, and the symbol decode is not invoked. The early/late pair of correlators compute a one sample early and a one sample late (called slides) version of the correlation (with precessed correlator) corresponding to the symbol which gave the largest correlation on the trial precession. When a data symbol correlator output crosses a first threshold, the timing device compares the early and late correlator outputs with the on-time correlator output, and the maximum of the three is checked against a second higher threshold. If it is crossed, the timing device adjusts the precessed (shifted) correlators according to the one sample slide adjustment and on the next trial symbol read, checks if the largest correlation crosses a third threshold. If the acquisition is confirmed, it switches to tracking mode; if the acquisition is not confirmed, it stays in acquisition mode — increments the precession and repeats the tests. In this way, the signal can be acquired in the presence of a timing error less than or equal to the maximum timing error that the tracking module can handle. See Figure 9 for the timing decision device's algorithm for acquisition.

The CPSK signaling method is well suited to this acquisition scheme because all M data symbol correlators contribute to the search on every trial. Therefore, to precess through an entire PN sequence length G; takes only G/M trials. In other words, the acquisition time for the CPSK scheme is cut down from the standard acquisition time for conventional DS-SS by a factor of M.

Figure 9 Timing Decision Algorithm in Acquisition Mode

In tracking mode (refer to Figure 8), the symbol decision device chooses the correlator with the largest output and passes the symbol to the symbol decoder. This symbol also determines which shift of the PN sequence the early/late pair of correlators use for correlating against the one symbol delayed stream. If the early or the late correlator give a larger output than the punctual correlator, and the timing decision device has its flag raised for tracking adjustment in the corresponding direction, all the correlators are precessed by the plus one or minus one sample slide. If the flag was not up, it gets raised. If the punctual correlator gave the largest output, the flag is lowered. In other words, the correlators must indicate that the tracking must be adjusted in a particular direction twice in a row before the tracking adjustment is made. See Figure 10 for the timing device's tracking algorithm. It follows a similar algorithm to check for tracking loss.

The timing decision device checks for loss of lock by raising a flag if the maximum of the punctual, early, or late correlator output falls below a threshold. If the flag was already up, the tracking is declared to be lost. If the maximum of the punctual, early, or late correlator exceeds the threshold, the flag is lowered. That is, the maximum of the punctual, early, or late correlator outputs must fall below the threshold on two consecutive data symbols before the tracking is declared to be lost — at which point the reception is aborted, and the stored data is then passed to the host.

Figure 10 Timing Decision Algorithm for Tracking

#### 3.6 DSP On Board Results

Before inserting the IF link, the DSP software was tested on-board by having the digital transmitter communicate directly with the digital receiver. Besides providing a test of the software functionality, this allows determination of the maximum sampling rate which the receiver can handle. Also, timing error can be simulated in real time by adding or deleting samples from the transmitted data stream. The receiver acquires and decodes the otherwise noiseless transmission successfully for a timing slippage as high as 1 sample for every 4 data bits. Because there are 2G samples per data bit, this translates to a maximum timing slippage of 12.5/G percent.

Table 1 shows the maximum sampling rates in MSPS and the corresponding data rate in KBPS for spreading factors of  $G = 2^{l} - 1$ , and word lengths 1 and 2, for single channel and complex channel processing.

| shift     | PN seq | k=1, single chan. |      | k=2, single chan |      | k=1, I+Q chan. |        |

|-----------|--------|-------------------|------|------------------|------|----------------|--------|

| reg len l | len G  | MSPS              | KBPS | MSPS             | KBPS | MSPS           | KBPS . |

| 3         | 7      | 1.45              | 104  | 0.80             | 114  | 0.70           | 100    |

| 4         | 15     | 1.96              | 65.3 | 1.02             | 68.0 | 0.92           | 61.3   |

| 5         | 31     | 2.33              | 37.6 | 1.16             | 37.4 | 1.06           | 34.2   |

| 6         | 63     | 2.57              | 20.4 | 1.24             | 19.7 | 1.15           | 18.3   |

| 7         | 127    | 2.70              | 10.6 | 1.28             | 10.1 | 1.19           | 9.4    |

| 8         | 255    | 2.77              | 5.4  | 1.30             | 5.1  | 1.22           | 4.8    |

| 9         | 511    | 2.81              | 2.7  | 1.32             | 2.6  | 1.24           | 2.4    |

| 10        | 1023   | 2.83              | 1.4  | 1.32             | 1.3  | 1.24           | 1.2    |

Table 1 Maximum sampling rates and the corresponding data rates

The maximum chipping rate is determined by the speed at which the receiver DSP modules can process. For word lengths of 1 or 2, and with G larger than the threshold value of 63, the inner kernel of the code implementing a correlator is the bottleneck. For G smaller than the threshold value, the bottleneck becomes the "intelligent" process which accepts the correlator outputs. We have not determined how much this threshold value of the spreading factor increases for word lengths higher than 2.

## 3.7 Experimental Setup

Figure 11 Experimental Setup for Measuring BER in AWGN

The DSP is a full-sized PC AT card residing in a 16 bit expansion slot of the host 486 PC. It communicates with the IF transmitter and the IF receiver via the C40's 8-bit high speed parallel communication ports.

The Marconi 2022D signal generator provides the 140 MHz LO for the IF transmitter; while the Marconi 2031 signal generator provides the 140 MHz LO for the IF receiver. It should be stressed that the IF transmitter and the IF receiver are each driven by their own TTL clock oscillator as well; rendering them independent.

The IF transmitter produces a 2.9 dBm double-sideband-suppressed-carrier signal centered at 140 MHz, which is further attenuated by 30 to 50 dB, by the KAY 437A step attenuator. This signal is summed with the AWGN by Mini-Circuit's two-way, 0 degrees, ZSC-2–1 Summer/Splitter.

The AWGN is produced at baseband by the Wandel & Goltermann White Noise Generator; and is mixed up to the frequency range of the data transmission by Mini-Circuit's MCL SBL-1 frequency mixer, whose LO is provided by the Hewlett-Packard 8656B signal generator.

The total signal (data plus noise), is brought back up in strength by 28 dB at the IF receiver front-end. The signal-to-noise power measurements were made at the IF receiver front-end with the Tektronix 497P Spectrum Analyser. The BER measurements were made by having the transmitter send a simple pattern of data bits (therefore, essentially random pattern of chips) and having the receiver operate like a BER analyser. It triggers on the first non-zero symbol, and counts the times that the decoded symbol stream does not match the pattern.

## Chapter 4 Steady-State Performance of the Coherent Receiver

### 4.1 Approximating The Optimal Correlator

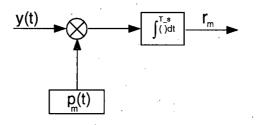

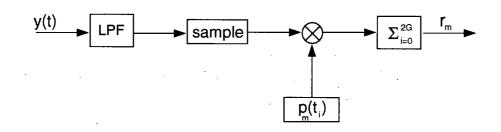

In the DSP based implementation of the CPSK receiver, the baseband signal is sampled at twice the chipping rate, and the 2G samples representing a data symbol are correlated by an add and accumulate operation. Thus the integration in Figure 3 is approximated by a summation, and the optimal correlator is roughly approximated. To improve the approximation, we low-pass filter the baseband signal, y(t), before sampling it; and therefore, approximate the ideal analog correlator of Figure 12 by the combination of analog filter and digital correlator in Figure 13.

Figure 12 Analog Correlator

Figure 13 Analog Filter with Digital Correlator

The resolution of the tracking scheme is one sampling interval, so that the position in the chipping interval of the pair of samples for one chip is a random variable. The purpose of this chapter is to show how the cut-off frequency of the low-pass filter (which filters the chips) can be chosen so as to maximize the output signal-to-noise ratio of the digital correlator for a PN sequence of chips. The output signal-to-noise ratio of a filter or correlator,  $SNR_o$ , at time T, is defined as the ratio of the instantaneous power of the output signal,  $r_o(T)$ , to the average power in output noise  $n_o(t)$ :

$$SNR_o = \frac{|r_o(T)|^2}{\mathcal{N}_o}.$$

(4.1)

A matched filter or correlator, optimizes this ratio to the value for coherent reception:

$$SNR_{o,opt} = \frac{2E_s}{N_o}.$$

(4.2)

We take the low-pass filter of Figure 13 to be first order RC; thus, with transfer function given by

$$H(f) = \frac{1}{1 + jf/f_c};$$

(4.3)

where the 3-dB bandwidth of the filter,  $f_c$ , is given by

$$f_c = \frac{1}{2\pi RC}.\tag{4.4}$$

We require the output SNR of the digital correlator for the reception of 2G samples of the LPF output correlated against the PN sequence,  $p_m(t_i)$ , which takes values  $\pm 1$ . Start by calculating the output noise power  $\mathcal{N}_o$ .

The *i*th sample of the low-pass filtered noise is

$$n_i = \int_{-\infty}^{+\infty} h(\tau) n(t_i - \tau) \, d\tau; \qquad (4.5)$$

where  $h(\tau)$  is the impulse response of the LPF. Since the noise output is  $\sum_{i=0}^{2G} p_m(t_i)n_i$ , the average output noise power, obtained by taking the expectation of the noise output squared, is

$$\mathcal{N}_{o} = \sum_{i=0}^{2G} \sum_{j=0}^{2G} p_{m}(t_{i}) p_{m}(t_{j}) E[n_{i}n_{j}].$$

(4.6)

Using (4.5), the expectation  $E[n(t_i)n(t_j)] = \frac{1}{2}N_o\delta(t_i - t_j)$ , and the fact that  $h(\tau)$  is the fourier transform of H(f); leads to

$$E[n_i n_j] = \frac{\pi}{2} N_o f_c e^{-2\pi f_c |t_j - t_i|}.$$

(4.7)

Since the cutoff frequency,  $f_c$ , is the same order of magnitude as  $T_c^{-1}$ , and for  $i \neq j$ ,  $|t_j - t_i| \geq T_c/2$ , the terms for which i = j are dominant. Furthermore, most of the terms

in the sum (4.6) cancel for  $i \neq j$ ; therefore, the sum (4.6) is approximately given by the sum of the i = j terms:

$$\mathcal{N}_o = \pi G N_o f_c. \tag{4.8}$$

To calculate the output signal power of the filter/correlator, we first need the sampled response of the LPF to a square pulse chip of duration  $T_c$  and amplitude A, as shown in Figure 14. The time origin is indicated by the circle, and the two sampling instances are indicated by the crosses. Let  $\tau$  be the time, as measured from the origin, of the first sampling instance. The second sampling instance occurs at time  $\tau + T_c/2$ . Let  $\delta t$  be the time interval from the rising edge of the square pulse to the time origin. The tracking scheme (next chapter) keeps the sampling times synchronized to the chip intervals, to within 1 sampling interval, by maintaining maximum signal power. Therefore  $\tau$  takes a random value uniformly distributed in the interval  $[0, \frac{1}{2}T_c]$ .

Figure 14 LPF Response To a Square Pulse Chip

$\delta t$  is determined by demanding that the well-known exponential solution to the first order RC circuit go from -A to 0 in time  $\delta t$ :

$$0 = -A + 2A \left( 1 - e^{-\delta t/RC} \right);$$

(4.9)

which solves, using (4.4), for  $\delta t$  to

$$\delta t = \frac{\ln 2}{2\pi f_c}.\tag{4.10}$$

The sampled response,  $s_c(\tau)$  of the LPF to the chip, is the sum of the LPF output at the two sampling times:

$$s_{c}(\tau) = \begin{cases} 2A - A(1 + e^{-b})e^{-\omega_{c}\tau}, & \text{for } \tau \in [0, \frac{1}{2}T_{c} - \delta t];\\ A(e^{b} - e^{-b} - 1)e^{-\omega_{c}\tau}, & \text{for } \tau \in [\frac{1}{2}T_{c} - \delta t, \frac{1}{2}T_{c}]; \end{cases}$$

(4.11)

where b is defined to be  $b = \pi f_c T_c$ . To obtain an approximate expression for  $r_o(T)$ , the response of the correlator to a synchronized (to within a sampling interval) PN sequence, we make use of (4.11) along with some of the general properties of maximal length PN sequences. We will assume that the LPF response to chips which are preceded by a chip of the same polarity is  $\pm A$ . In other words, that the LPF output essentially reaches the voltage of the input when the input is held constant for longer than a chip duration. Once the LPF cut-off frequency is found, it can be checked that this assumption is consistent with the solution.

One quarter of the chips of a maximal length PN sequence (of length G) are included in run lengths of 1; and there are G/4 runs of length greater than 1. Therefore, since 3G/4chips are members of a run length greater than 1, and G/4 chips begin such a run length, there are G/2 chips preceded by a chip of the same polarity; and therefore the sampled signal strength of G/2 chips is approximately  $\pm 2A$ . The G/4 chips that immediately follow a greater than length 1 run length have the signal strength magnitude depicted in Figure 15 and given exactly by (4.11). The G/4 chips that immediately follow a run length of 1 have a signal strength magnitude approximately given by (4.11). Therefore, since multiplication by the synchronized PN sequence gives all the samples positive polarity, the output of the digital correlator is approximately

$$r_o(T) = \frac{1}{2}G(s_c(\tau) + 2A).$$

(4.12)

It remains to average the output SNR of equation (4.1) over the random variable  $\tau$ .

From (4.2) it follows immediately that

$$\mathrm{SNR}_{o,opt} = \frac{2A^2T_s}{N_o}.$$

(4.13)

So that with (4.12) and (4.8) substituted into (4.1), we have the ratio of the average output signal-to-noise ratio of the digital correlator,  $\overline{\text{SNR}}_o$ , to the output signal-to-noise ratio of an ideal analog correlator,  $\overline{\text{SNR}}_{o,opt}$ :

$$\frac{\overline{\mathrm{SNR}}_o}{\mathrm{SNR}_{o,opt}} = \frac{\left(\frac{1}{2}(2+s_c(\tau))\right)^2}{2b};$$

(4.14)

where the indicated average is with respect to  $\tau$ , and  $s_c(\tau)$  is given by (4.11) with A set to unity.

The average of  $s_c(\tau)$  with respect to  $\tau$  is

$$\overline{s}_c = 2\left(1 - \frac{\ln 2}{b}\right) + \frac{e^{-2b}}{b}; \tag{4.15}$$

and the average of  $s_c^2(\tau)$  with respect to  $\tau$  is

$$\overline{s_c^2} = 4\left(1 - \frac{\ln 2}{b}\right) + \frac{1}{2b}\left(10e^{-2b} + 14e^{-3b} - e^{-4b} - 4\right).$$

(4.16)

Substitution of these last 2 equations into (4.14) yields the ratio of SNR's as a function of  $b = \pi f_c T_c$  for the received data symbol.

The optimization of (4.14) with respect to b is not well defined because the signal strength A was assigned to one half of the chips, when really these strengths should be subject to the optimization as well. Instead we optimize, with respect to b, the ratio of the average output SNR of the LPF due to the chip of Figure 14 to the output SNR of a filter matched to the chip. This ratio is given by:

$$\frac{\overline{\mathrm{SNR}}_{o,chip}}{\mathrm{SNR}_{o,mat}} = \frac{\overline{(s_c(\tau))^2}}{2b};$$

(4.17)

and is plotted in Figure 15. Optimizing the ratio (4.17) with respect to b yields an optimal value for the chip of

$$b = 2.28;$$

(4.18)

which, when substituted into (4.14) for the symbol, yields

$$\frac{\overline{\text{SNR}}_o}{\text{SNR}_{o,opt}} = 0.63 = -2.0 \text{ dB.}$$

(4.19)

The optimal value of b, as given by (4.18), corresponds to the first order RC LPF cut-off frequency  $f_c = 0.73T_c^{-1}$ .

The extremely complicated complete optimization problem has here been simplified to something tractable by the approximations made above. Thus both the optimum value of the LPF cut-off frequency, and the performance degradation of -2.0 dB incurred by approximating the matched filter by the LPF followed by the digital correlator, should only be viewed as reasonable estimates. Experimentation with the hardware of the implementation

has lead us to the approximate optimal value of  $f_c = 0.5T_c^{-1}$  for which we have found an SNR degradation of only  $0.8 \pm 0.4$  dB. By doubling the sampling rate and performing a two-sample preaccumulation, we find an SNR degradation of only  $0.45 \pm 0.4$  dB.

Figure 15 Signal-to-Noise Ratio for a Sampled Low-Pass Filtered Chip as a Function of LPF Cut-off Frequency

#### 4.2 BER Performance In The Presence of Timing Slippage

In this chapter, we evaluate the BER in AWGN performance degradation for coherent reception, due to the fact that the receiver is not always exactly on track, even to within the one sample timing resolution. Recall from chapter 3 that at every data symbol interval, the output signal strength of the correlator corresponding to the data symbol being received is compared to the output signal strength of the corresponding correlator synchronized to the signal delayed by one sampling interval, and to the output signal strength of the corresponding interval. If the delayed or advanced correlator has a higher output than the on-time correlator, the sample stream is shifted with respect to the on-time correlator appropriately.

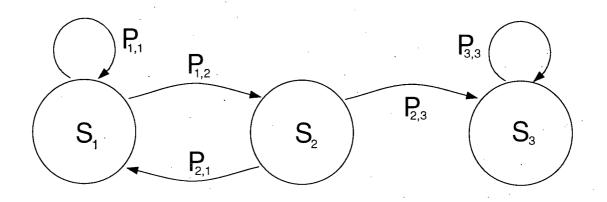

Let  $S_0$  denote the state in which the receiver is synchronized to within the one sample resolution;  $S_1$  denote the state in which the receiver synchronization is off by one sample; and  $S_2$  denote the state in which the receiver synchronization is off by more than one sample. The receiver tests for state  $S_2$  by checking if the signal strengths of the on-time, delayed, and advanced correlators all fall below a threshold. If it tests positive for state  $S_2$ , the receiver leaves its tracking and data decoding mode and returns to the state in which it is searching for a new transmission. When the receiver is in state  $S_2$ , the probability of exiting the tracking/data decoding mode is very high, so that the probability of state  $S_2$  is very low; and we approximate the problem by assuming that the probability of state  $S_2$  is zero. We have checked this approximation, in the absence of timing slippage, by including state  $S_2$  in the analysis, and have obtained the same result as that of the following calculation.