# REGISTER FILE ARCHITECTURE OPTIMZATION IN A COARSE-GRAINED RECONFIGURABLE ARRAY

by

Zion Siu-On Kwok B.A.Sc., University of British Columbia, 2003

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Applied Science

in

The Faculty of Graduate Studies

Electrical and Computer Engineering

The University of British Columbia

April 2005

© Zion Siu-On Kwok, 2005

# **ABSTRACT**

# REGISTER FILE ARCHITECTURE OPTIMIZATION IN A COARSE-GRAINED RECONFIGURABLE ARRAY

This thesis investigates the impact of the global and local register file architecture on a reconfigurable system based on the ADRES architecture. The register files consume a significant amount of area on the reconfigurable device, and their architecture has a strong impact on the performance. We found that the global registers should be tightly connected to as many functional units as possible, while the connection of the local register files to their neighbours is less critical. We found that the global register file should contain 14 registers, while each local register file should only contain two registers. We used these results to propose two new architectures that demonstrate between -33% and 383% higher instructions per cycle per unit area compared to the original 4x4 and 8x8 array architectures, with 56% and 88% average improvement over a set of benchmarks for the new 4x4 and 8x8 array architectures, respectively.

# TABLE OF CONTENTS

| ABSTRACT                                                                      | ii   |

|-------------------------------------------------------------------------------|------|

| LIST OF FIGURES                                                               | vii  |

| LIST OF TABLES                                                                | ix   |

| LIST OF ACRONYMS                                                              | xi   |

| ACKNOWLEDGEMENTS                                                              | xiii |

| CHAPTER 1 INTRODUCTION                                                        | 1    |

| 1.1 MOTIVATION                                                                | 1    |

| 1.2 RESEARCH GOALS                                                            | 3    |

| 1.3 SIGNIFICANCE                                                              | 4    |

| 1.4 Organization of this Thesis                                               | 4    |

| 1.5 CONTRIBUTIONS OF THIS THESIS                                              | 5    |

| CHAPTER 2 BACKGROUND AND PREVIOUS WORK                                        | 7    |

| 2.1 RECONFIGURABLE CUSTOM COMPUTING                                           | 7    |

| 2.1.1 Island-Style FPGAs                                                      | 9    |

| 2.1.2 Addition of Fixed IP Cores                                              | 11   |

| 2.1.3 Hard-Wired FPGAs                                                        | 12   |

| 2.1.4 System-on-a-Chip Designs with Embedded Programmable Logic Cores         | 13   |

| 2.1.5 Fine-Grained Reconfigurable Architectures Coupled with a Microprocessor | 15   |

| 2.1.6 Coarse-Grained Reconfigurable Architectures                             | 16   |

| 2.1.7 VLIW Processors                                                         | 17   |

| 2.1.8 Clustered VLIW Processor with a Reconfigurable Inter-Cluster Bus        | 18   |

| 2.2 COARSE-GRAINED RECONFIGURABLE ARCHITECTURES                               | 19   |

| 2.2.1 Applications                                                            | 19   |

| 2.2.2 Distinguishing Features                                                 | . 10 |

| 2.2.3 Examples of Coarse-Grained Reconfigurable Architectures | 21  |

|---------------------------------------------------------------|-----|

| 2.2.4 Architectural Studies                                   | 26  |

| 2.3 Focus of this Thesis                                      | 29  |

| CHAPTER 3 FRAMEWORK                                           | 30  |

| 3.1 Architecture                                              | 30  |

| 3.1.1 Computation Units                                       | 31  |

| 3.1.2 Register Files                                          | 33  |

| 3.1.3 Interconnect                                            | 35  |

| 3.1.4 Context Memory                                          | 41  |

| 3.2 COMPILERS                                                 | 41  |

| 3.2.1 IMPACT-I                                                | 42  |

| 3.2.2 DRESC                                                   | 42  |

| 3.3 DESIGN SPACE EXPLORED IN THIS THESIS                      | 45  |

| 3.3.1 Parameters                                              | 45  |

| 3.4 SUMMARY                                                   | 46  |

| CHAPTER 4 EXPERIMENTAL METHODOLOGY                            | 47  |

| 4.1 Experimental Flow                                         | 47  |

| 4.1.1 Overall Flow                                            | 47  |

| 4.1.2 SCRAP                                                   | 48  |

| 4.2 VHDL MODEL                                                | 49  |

| 4.2.1 Functional Units                                        |     |

| 4.2.2 Multiplexers                                            | 50  |

| 4.2.3 Register Files                                          | 50  |

| 4.2.4 Context Memory                                          |     |

| 4.2.5 Benchmarks                                              | 51  |

| 4.3 EVALUATION METRICS AND TECHNIQUES                         |     |

| 42 L Avag Estimation                                          | £ 1 |

| 4.3.2 Performance Measurements                                 | 53       |

|----------------------------------------------------------------|----------|

| 4.3.3 Instructions Per Cycle Per Unit Area                     | 55       |

| 4.4 SUMMARY                                                    | 56       |

| CHAPTER 5 RESULTS                                              | 57       |

| 5.1 Global Register Files                                      | 57       |

| 5.1.1 Degree of Connectivity                                   | 57       |

| 5.1.2 Number of Ports                                          | 60       |

| 5.1.3 Number of VLIW FUs                                       | 61       |

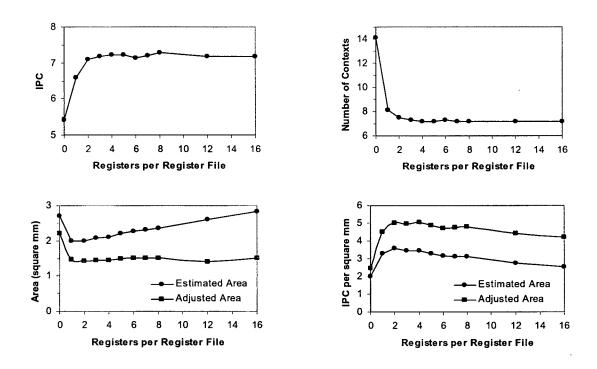

| 5.1.4 Register File Size                                       | 64       |

| 5.2 LOCAL REGISTER FILES                                       | 66       |

| 5.2.1 Degree of Connectivity                                   | 66       |

| 5.2.2 Number of Ports                                          | 70       |

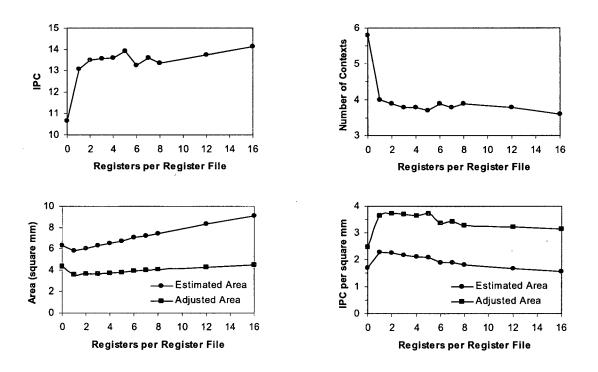

| 5.2.3 Register File Size                                       | 71       |

| 5.3 SUMMARY                                                    | 80       |

| CHAPTER 6 ENHANCED ARCHITECTURES                               | 82       |

| 6.1 New 4x4 Array Architecture                                 | 82       |

| 6.1.1 Selected Parameters                                      | 82       |

| 6.1.2 Results                                                  | 83       |

| 6.2 New 8x8 Array Architecture                                 | 85       |

| 6.2.1 Selected Parameters                                      | 85       |

| 6.2.2 Results                                                  | <i>.</i> |

| 6.3 COMPARISON BETWEEN THE NEW 4x4 AND 8x8 ARRAY ARCHITECTURES | 87       |

| 6.4 Summary                                                    | 88       |

| CHAPTER 7 CONCLUSIONS AND FUTURE WORK                          | 89       |

| 7.1 Conclusions                                                | 89       |

| 7.2 FUTURE WORK                                                | 90       |

| 7.3 CONTRIBUTIONS OF THIS WORK                                 | 91       |

| א כם כון כון כם כו | NOTEC   | · · · · · · · · · · · · · · · · · · ·   |   |

|--------------------|---------|-----------------------------------------|---|

| KEFEKE             | NC. P.S | 9                                       |   |

|                    |         | *************************************** | • |

# LIST OF FIGURES

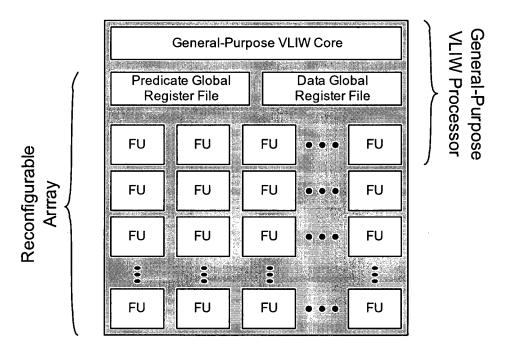

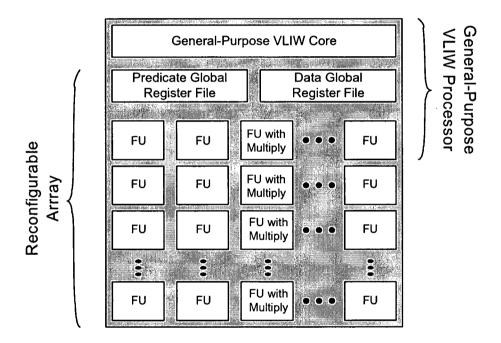

| FIGURE 1.1: BASELINE ARCHITECTURE BASED ON ADRES [3]                                             | 3  |

|--------------------------------------------------------------------------------------------------|----|

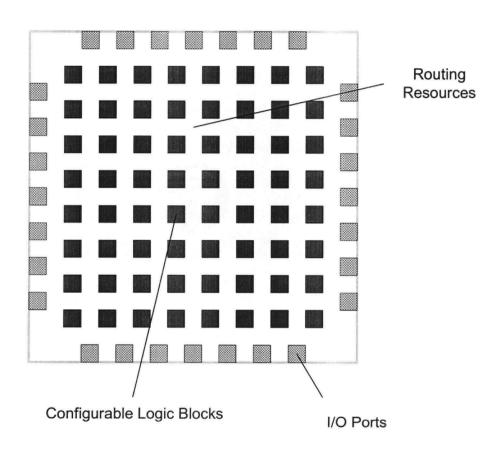

| FIGURE 2.1: LUT-BASED ISLAND-STYLE ARCHITECTURE                                                  | 10 |

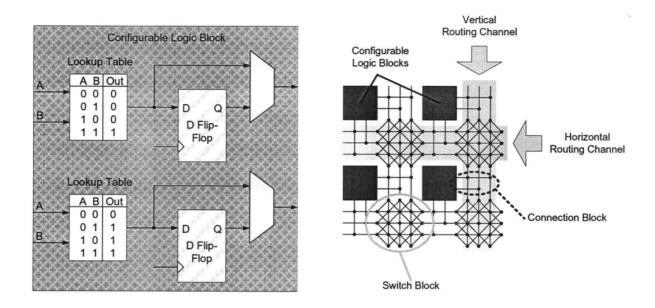

| FIGURE 2.2: DETAILS OF THE LUT-BASED ISLAND-STYLE FPGA                                           | 11 |

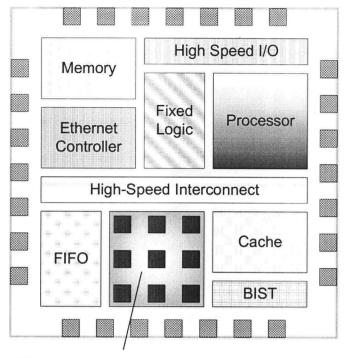

| FIGURE 2.3: FPGA WITH FIXED IP CORES                                                             | 12 |

| FIGURE 2.4: SYSTEM-ON-A-CHIP DESIGN WITH AN EMBEDDED PROGRAMMABLE LOGIC CORE                     | 14 |

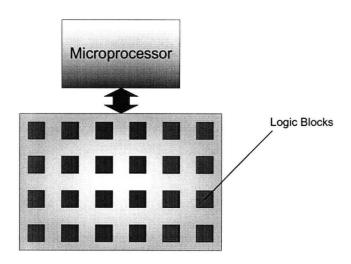

| FIGURE 2.5: FINE-GRAINED RECONFIGURABLE ARCHITECTURE                                             | 15 |

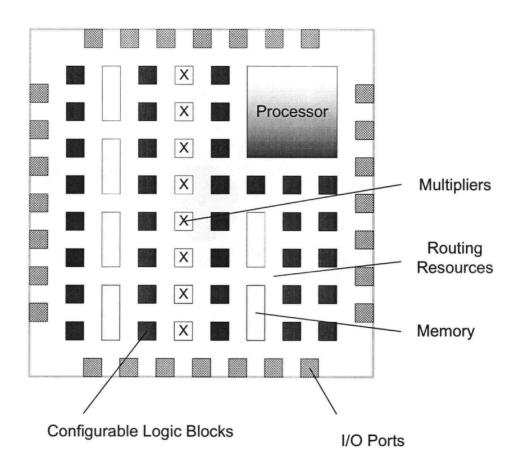

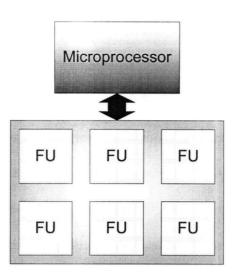

| FIGURE 2.6: COARSE-GRAINED RECONFIGURABLE ARCHITECTURE                                           | 17 |

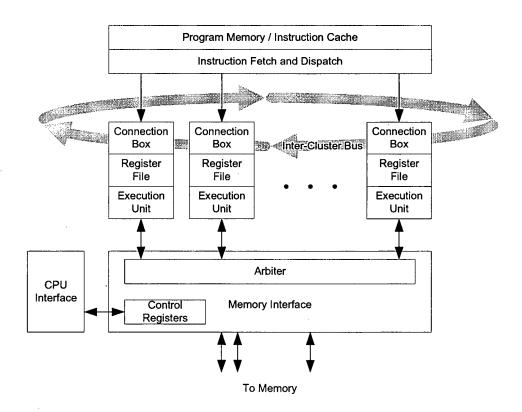

| FIGURE 2.7: CLUSTERED VLIW PROCESSOR WITH AN INTER-CLUSTER BUS (FROM [62])                       | 18 |

| FIGURE 2.8: ONE OF SIXTEEN SETS OF FUNCTIONAL UNITS IN THE RAPID-I ARCHITECTURE (FROM [70])      | 22 |

| FIGURE 2.9: BLOCK DIAGRAM OF MORPHOSYS ARCHITECTURE (FROM [1])                                   | 23 |

| FIGURE 2.10: RECONFIGURABLE CELL IN THE MORPHOSYS ARCHITECTURE (FROM [1])                        | 23 |

| FIGURE 2.11: MORPHOSYS INTERCONNECT ARCHITECTURE (FROM [1])                                      | 25 |

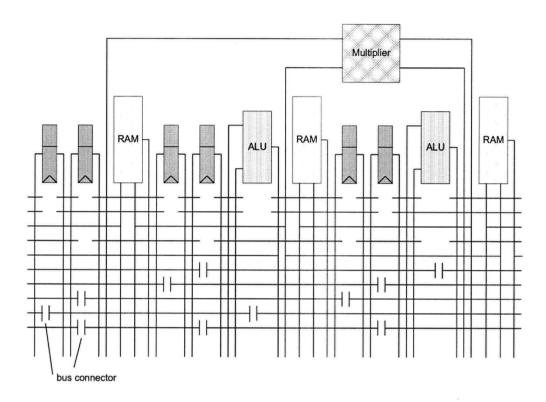

| FIGURE 3.1: COLUMNS OF FUNCTIONAL UNITS WITH MULTIPLIERS                                         | 31 |

| FIGURE 3.2: CONFIGURABLE FUNCTIONAL UNIT IN THE ADRES-BASED ARCHITECTURE                         | 32 |

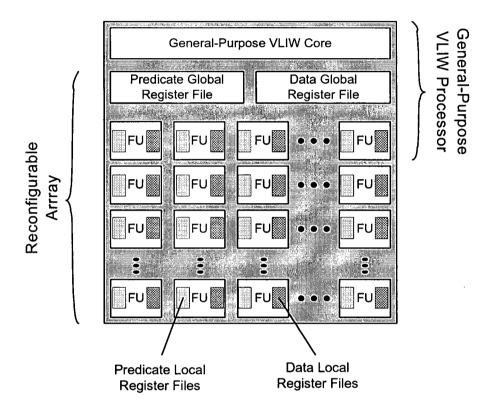

| FIGURE 3.3: GLOBAL AND LOCAL REGISTER FILES IN THE ADRES-BASED ARCHITECTURE                      | 33 |

| FIGURE 3.4: INTERCONNECT PATTERN FOR SRC1 DATA ALU INPUT IN THE BASELINE ARCHITECTURE            | 36 |

| FIGURE 3.5: INTERCONNECT PATTERN FOR SRC2 DATA ALU INPUT IN THE BASELINE ARCHITECTURE            | 36 |

| FIGURE 3.6: INTERCONNECT PATTERN FOR PRED PREDICATE ALU INPUT IN THE BASELINE ARCHITECTURE       | 37 |

| FIGURE 3.7: INTERCONNECT PATTERN FOR LOCAL REGISTER FILE READ PORTS IN THE BASELINE ARCHITECTURE | 38 |

| FIGURE 3.8: GENERATION OF LOOP STOP SIGNAL                                                       | 39 |

| FIGURE 3.9: GENERATION OF WRITE ENABLE SIGNAL FOR THE DATA GLOBAL REGISTER FILE                  | 40 |

| FIGURE 3.10: GENERATION OF WRITE ENABLE SIGNAL FOR THE PREDICATE GLOBAL REGISTER FILE            | 40 |

| FIGURE 3.11: COMPILATION FLOW                                                                    | 41 |

| FIGURE 3.12: ILLUSTRATION OF ITERATION INTERVAL WHEN MAPPING A LOOP TO AN ARCHITECTURE           | 44 |

| FIGURE 4.1: EXPERIMENTAL FLOW                                                                    | 48 |

| Proving A 2. Varying group on Anna Mongy                                                         | 50 |

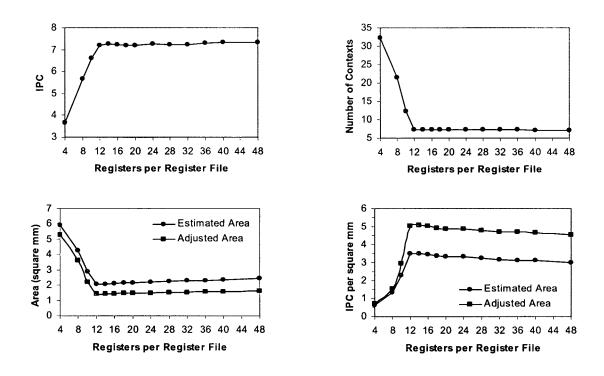

| FIGURE 5.1: IMPACT OF CHANGING THE NUMBER OF REGISTERS IN EACH GLOBAL REGISTER FILE IN THE 4X4 ARRAY | Y  |

|------------------------------------------------------------------------------------------------------|----|

|                                                                                                      | 55 |

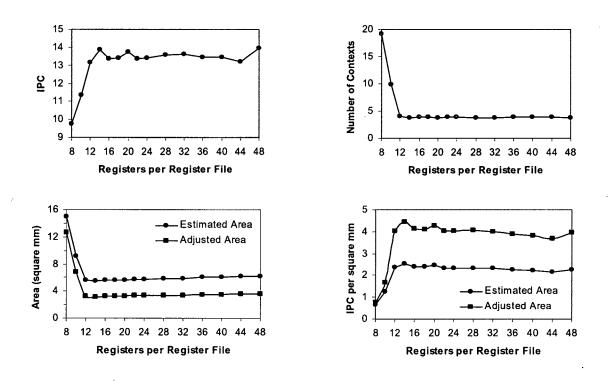

| FIGURE 5.2: IMPACT OF CHANGING THE NUMBER OF REGISTERS IN EACH GLOBAL REGISTER FILE IN THE 8X8 ARRAY | Y  |

|                                                                                                      | 55 |

| FIGURE 5.3: LOCAL REGISTER FILE CONNECTION PATTERN FOR ARCHITECTURE 1                                | 57 |

| FIGURE 5.4: LOCAL REGISTER FILE CONNECTION PATTERN FOR ARCHITECTURE 2                                | 58 |

| FIGURE 5.5: IMPACT OF CHANGING THE NUMBER OF REGISTERS IN EACH LOCAL REGISTER FILE IN THE 4X4 ARRAY  | 72 |

| FIGURE 5.6: IMPACT OF CHANGING THE NUMBER OF REGISTERS IN EACH LOCAL REGISTER FILE IN THE 8X8 ARRAY  | 72 |

| FIGURE 5.7: EFFECT OF INTERCONNECT ARCHITECTURE ON IPC AND AREA                                      | 74 |

| FIGURE 5 8: FEEE CT OF LOCAL PEGISTER FILE SIZE ON IPC AND AREA                                      | 75 |

# LIST OF TABLES

| TABLE 1.1: TYPICAL CONTRIBUTIONS OF VARIOUS MEMORY RESOURCES TO CHIP AREA                          |

|----------------------------------------------------------------------------------------------------|

| TABLE 2.1: COARSE-GRAINED RECONFIGURABLE ARCHITECTURES ORGANIZED BY GRANULARITY OF FUNCTIONAL      |

| Units                                                                                              |

| TABLE 3.1: ARCHITECTURAL PARAMETERS USED IN THIS THESIS                                            |

| TABLE 5.1: IMPACT OF CHANGING THE NUMBER OF FUS THAT CAN CONNECT TO THE GLOBAL REGISTER FILES (4X4 |

| Array)59                                                                                           |

| TABLE 5.2: IMPACT OF CHANGING THE NUMBER OF FUS THAT CAN CONNECT TO THE GLOBAL REGISTER FILES (8X8 |

| Array)59                                                                                           |

| TABLE 5.3: IMPACT OF CHANGING THE NUMBER OF PORTS ON THE GLOBAL REGISTER FILES (4X4 ARRAY)60       |

| TABLE 5.4: IMPACT OF CHANGING THE NUMBER OF PORTS ON THE GLOBAL REGISTER FILES (8X8 ARRAY)60       |

| TABLE 5.5: IMPACT OF CHANGING THE NUMBER OF FUS THAT CAN CONNECT TO THE GLOBAL REGISTER FILES AND  |

| MAIN MEMORY (4X4 ARRAY)62                                                                          |

| TABLE 5.6: IMPACT OF CHANGING THE NUMBER OF FUS THAT CAN CONNECT TO THE GLOBAL REGISTER FILES AND  |

| MAIN MEMORY (8x8 Array)62                                                                          |

| TABLE 5.7: IMPACT OF CHANGING THE LOCAL REGISTER FILE CONNECTION PATTERN (4X4 ARRAY)69             |

| TABLE 5.8: IMPACT OF CHANGING THE LOCAL REGISTER FILE CONNECTION PATTERN (8x8 Array)69             |

| TABLE 5.9: IMPACT OF CHANGING THE NUMBER OF READ PORTS ON THE LOCAL REGISTER FILES (4X4 ARRAY)70   |

| TABLE 5.10: IMPACT OF CHANGING THE NUMBER OF READ PORTS ON THE LOCAL REGISTER FILES (8x8 Array)71  |

| TABLE 5.11: NUMBER OF LOCAL REGISTERS IN EACH CONFIGURABLE FUNCTIONAL UNIT IN VARIOUS PUBLISHED    |

| Architectures                                                                                      |

| Table 5.12: Per Benchmark Register Utilization (4x4 Array)                                         |

| Table 5.13: Per Benchmark Register Utilization (8x8 Array)                                         |

| Table 5.14: Recommendations for Architectural Parameters                                           |

| Table 6.1: Per Benchmark Comparison Between Results for Enhanced and Baseline Architectures        |

| WITH A 4X4 ARRAY84                                                                                 |

| TABLE 6.2: PER BENCHMARK COMPARISON BETWEEN RESULTS FOR ENI | HANCED AND BASELINE ARCHITECTURES |

|-------------------------------------------------------------|-----------------------------------|

|                                                             | 8                                 |

. • <del>-</del>.

# LIST OF ACRONYMS

ALU Arithmetic Logic Unit

**ASIC** Application-Specific Integrated Circuit

**BIST** Built-In Self-Test

**CAD** Computer-Aided Design

**CLB** Configurable Logic Block

**DMA** Direct Memory Access

**DSP** Digital Signal Processing

FIFO First-In First-Out

**FFT** Fast Fourier Transform

**FPGA** Field-Programmable Gate Array

FU Functional Unit

**IDCT** Inverse Discrete Cosine Transform

II Iteration Interval

**ILP** Instruction-Level Parallelism

IMEC Interuniversity MicroElectronics Centre

**IP** Intellectual Property

**IPC** Instructions Per Cycle

LLP Loop-Level Parallelism

LUT Look-Up Table

MIPS Million Instructions Per Second (processor)

**MPEG** Moving Picture Experts Group

**RAM** Random-Access Memory

**RC** Reconfigurable Cell

RISC Reduced Instruction Set Computer

RTL Register-Transfer Level

SCRAP Steve's Coarse-grained Reconfigurable Architecture Program

SIMD single-instruction multiple-data

**SRAM** Static Random-Access Memory

VHDL Very high speed integrated circuits Hardware Description Language

**VLIW** Very Long Instruction Word (processor)

XML eXtensible Markup Language

#### **ACKNOWLEDGEMENTS**

First of all, I would like to thank my supervisor, Dr. Steven Wilton for the topic, his support, his counsel, and just being such an understanding advisor who gives so much time and encouragement, as well as the occasional treat to his students. I also want to thank Dr. Guy Lemieux, with whom I have been privileged to work closely in EECE 583 and EECE 259, for sharing his experience.

I would also like to thank people I have looked up to: Julien Lamoureux, Ernie Lin, Kara Poon, Andy Yan, Noha Kafafi, James Wu, Martin Ma, and Victor Aken'Ova. They have introduced me to lab life, helped me get up on my feet, and made research something to look forward to. It has been a pleasure to be a part of the FPGA research group with Marvin Tom, Eddy Lee, Anthony Yu, Brad Quinton, Natalie Chan King Choy, Cary Feldstein, Scott Chin, and David Yeager. I've had good neighbours in the lab: Dipanjan Sengupta, Samad Sheikhaei, Zahra Ebadi, Cristian Grecu. Others who have enriched my experience in the SOC Lab include: Baosheng Wang, Andy Kuo, Jess Chia, Santosh Sood, Mohammad Hekmat, Neda Nouri, Amit Kedia, Peter Hallschmid, and Rod Foist. The friendly people and staff like Sandy, Roozbeh, and Roberto, have also made the lab a good place to work.

I am also grateful for Nelson Siu, Changsong Shen, and Mike Wang for welcoming me to their own corners of the world. Prayers and concern from my friends and family have been much appreciated. Lastly, I thank the Lord Jesus Christ for His grace and getting me through this time of learning and growth.

# Chapter 1

# **INTRODUCTION**

# 1.1 Motivation

Coarse-grained reconfigurable architectures promise high computing parallelism and low power consumption. Published architectures such as MorphoSys [1], PipeRench [2], and ADRES [3] demonstrate higher computing performance than general-purpose processors and very long instruction word (VLIW) processors, especially in loop-intensive digital signal processing (DSP) applications. Coarse-grained reconfigurable architectures are more suitable for applications requiring datapaths than field-programmable gate arrays (FPGAs), which are more effective for random logic [2]. Compared to fine-grained reconfigurable architectures and FPGAs in particular, coarse-grained reconfigurable architectures have larger reconfigurable functional units which require fewer programming bits and routing resources within each block, leading to power, area and delay reductions inside each functional unit. These power savings are important, especially in mobile systems.

As in any compute engine, the memory architecture has a significant effect on the performance of coarse-grained reconfigurable architectures [4]. MorphoSys [1] uses a frame buffer to stream image data. In REMARC [5], the MIPS microprocessor loads the data into the data register for the co-processor to access. The instruction memory is also significant; instructions can be stored

in instruction registers, in context registers, or in random-access memories (RAMs) [5, 6, 7, 8, 9]. Furthermore, many coarse-grained architectures contain additional register files within the reconfigurable fabric for use as scratch-pad memory [1, 3, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15].

One such coarse-grained reconfigurable architecture is ADRES [3]. ADRES, which is being developed at the Interuniversity Microelectronics Centre (IMEC) in Leuven, Belgium, contains both a general-purpose Very Long Instruction Word (VLIW) processor and a reconfigurable fabric. Estimates obtained using two area models described in this thesis will show that 36% to 62% of the area of the device is memory. Of this, just under half is devoted to register files used as scratch-pad memory and used to communicate between the VLIW processor and the reconfigurable fabric. Table 1.1 shows a breakdown of the area devoted to memory in our baseline ADRES-based architecture with 16 functional units and five contexts. Clearly, the area devoted to the register files is significant; hence, we would expect that the register file architecture would have a significant effect on the efficiency of the reconfigurable architecture. In this thesis, we show that this statement is true, and that we can design a significantly more efficient reconfigurable architecture by optimizing the register files.

Table 1.1: Typical Contributions of Various Memory Resources to Chip Area

| Type of Memory      |                                  | Area | Adjusted Area |

|---------------------|----------------------------------|------|---------------|

| Register Files      | Data Global Register Files       | 10%  | 8%            |

|                     | Predicate Global Register Files  | 2%   | 1%            |

|                     | Data Local Register Files        | 13%  | 6%            |

|                     | Predicate Local Register Files   | 2%   | 2%            |

| FU Output Registers | FU Data Output Registers         | 3%   | 4%            |

|                     | FU Predicate Output Registers    | 1%   | 1%            |

|                     | Input Multiplexer Context Memory | 4%   | 2%            |

| Context Memory      | Operation Code Memory            | 3%   | 2%            |

|                     | Immediate Data Memory            | 23%  | 12%           |

| Total               |                                  | 62%  | 36%           |

## 1.2 Research Goals

This research consists of an experimental analysis of the register file architecture in one representative reconfigurable processor, an architecture based on the ADRES architecture from IMEC [3], as shown in Figure 1.1. This architecture contains two types of register files: global register files that can be accessed by some (or all) of the reconfigurable functional units on the fabric, and local register files, each of which is associated with a specific reconfigurable functional unit. In particular, we ask three questions for each type of register file:

- 1) How big should each register file be?

- 2) How should the register file be connected to the rest of the fabric?

- 3) How many read and write ports should each register file have?

Figure 1.1: Baseline Architecture Based on ADRES [3]

We will then use these answers to construct a modified version of the ADRES architecture which has -7% to 38% smaller area and runs code between -29% and 200% faster than the original architecture. Although the numerical results are specific to this processor, the trends that we observe may apply to other reconfigurable systems which have global or local register files.

# 1.3 Significance

The reduction in area offers several benefits. Since this reduction in area means fewer transistors are required, we can expect a higher number of chips to fit on each silicon wafer, higher yield resulting from the rarer occurrence of manufacturing chips that have a physical defect, and potentially lower power consumption. The first two make the chip more economical. The latter makes the chip more attractive for applications where power is limited or expensive, such as mobile applications that are powered by a battery.

The performance gain that comes from an optimized register file architecture allows more applications to be executed on the reconfigurable system every second or more complex processing in real-time applications, where tight deadlines are imposed on each task.

# 1.4 Organization of this Thesis

The thesis is organized as follows. Background of the related research will be presented first in Chapter 2. In Chapter 3, we will describe our baseline architecture, shown in Figure 1.1, which is very similar to the ADRES architecture [3]. Chapter 4 will describe our experimental methodology and Chapter 5 will present experimental results illustrating the impact of various architectural parameters on both the area and performance of the device. Then in Chapter 6, we

will use the results from Chapter 5 to propose two new architectures that are significantly smaller and faster than the baseline architecture. Finally, the conclusions, future work, and contributions are stated in Chapter 7.

# 1.5 Contributions of this Thesis

The contributions of this thesis are as follows:

- 1. We presented a methodology for evaluating ADRES-based reconfigurable architectures. This included the use of the IMPACT-I [73] and DRESC [74] compilers used for ADRES [3]. As well, the SCRAP tool used in [79] was enhanced to generate an XML architecture file, modularized VHDL code that included global register files, and a parameterized area model that could produce area estimates that correlate well with Synopsys post-synthesis area estimates, but runs in less than a second.

- 2. We performed experiments on the degree of connectivity of global and local register files to the functional units and found that shared connectivity of every functional unit to the global register files is vital to obtain high performance.

- 3. We verified that increasing the number of read and write ports on global and local register files improves performance, but at the cost of significant area.

- 4. We performed sweeps of the size of global and local register files and discovered in particular that only very few registers are needed in each local register file. This was attributed to the low utilization of local register files by the benchmark kernels.

- 5. We constructed enhanced 4x4 array and 8x8 array architectures that applied this new knowledge about register files to achieve on average 56% and 88% higher instructions per cycle per unit area, respectively, compared to the baseline architectures. For individual benchmarks, the enhanced 4x4 array architecture increased the instructions per

cycle per unit area by -6% to 152% and the enhanced 8x8 array architecture increased the instructions per cycle per unit area by -33% to 383%.

A portion of this work has been published in [16].

# Chapter 2

# **BACKGROUND AND PREVIOUS WORK**

In this chapter, the realm of reconfigurable custom computing is introduced with a particular emphasis on coarse-grained reconfigurable architectures.

# 2.1 Reconfigurable Custom Computing

Reconfigurable custom computers consist of programmable functional blocks that are connected by programmable routing, both of which are programmed using configuration bits [17]. They are reconfigurable because their hardware configuration can be modified and they perform custom computing because this flexible hardware configuration can be tailored to meet the needs of each specific application. This means that one such reconfigurable custom computer can give good performance, area, and power consumption for a wide variety of applications. Reconfigurable custom computing solutions possess some of the speed of dedicated hardware while also holding some of the programmability associated with software execution. According to Hartenstein [18], reconfigurable custom computing bridges the gap between the application-specific integrated circuits (ASICs) and microprocessors.

Today, general-purpose processors are very popular in desktop and laptop computers. However, based on audio, image, video, and cryptography application benchmarks, Lee et al. [19] showed that more than 90% of memory accesses on general-purpose processors can be considered

overhead, which can be avoided in ASICs and systolic arrays, where data can be forwarded directly to perform the next operation. They also report potential instruction-level parallelism (ILP) from 6 to 558, opening up the possibility of significant speedups on certain applications. As well, the need to load instructions from memory, decode them, and then execute the instructions constitutes a significant overhead in processing time [17]. Moreover, sometimes the instruction set does not have a single instruction that performs the exact function that is required [17]. Multiple instructions may be required to implement a function that could be implemented as specialized logic that is much smaller and faster.

Custom computing refers to a class of systems that contains exactly the type of logic that is required for an application. For example, some applications require more on-chip memory than others, while others require multipliers or Ethernet controllers. Custom computing is efficient because there is no wasted functionality and complex functions that may require multiple instructions on a general-purpose processor can be implemented in hardware that is more optimized in terms of speed, area, and power consumption. ASICs are an example of custom computers, where the circuit is designed specifically to perform a certain task. This circuit can therefore be well-optimized in terms of speed, density, and power. However, it is expensive and time-consuming to design and manufacture an ASIC for every different task that must be performed. To layout and fabricate such a chip typically requires two to five months [20] and can cost one million dollars for the mask set alone which is used in fabrication.

Field-programmable gate arrays (FPGAs) are important to reconfigurable custom computing because they provide the flexible hardware building blocks that can be configured to perform different functions. As an array of these blocks, FPGAs can be configured to implement digital circuits for a diverse range of applications including network routers and robotics controllers.

Devices which can be used to implement reconfigurable custom computing include island-style FPGAs, FPGAs with fixed intellectual property (IP) logic cores, system-on-a-chip designs with embedded FPGA cores, fine-grained reconfigurable architectures, and coarse-grained reconfigurable architectures. Each of these will be discussed in the following subsections. Hardwired FPGAs are also described because they fit nicely in the discussion about the tradeoffs between programmable and fixed logic. We also mention very long instruction word (VLIW) processors because of their similarity to some coarse-grained reconfigurable architectures. Coarse-grained reconfigurable architectures will be described further in Section 2.2 and form the basis of the discussions in the thesis.

# 2.1.1 Island-Style FPGAs

Field-programmable gate arrays (FPGAs) consist of an array of programmable logic blocks that are interconnected by programmable interconnect. The programmable logic blocks can be configured to perform many different digital logic functions. The programmable interconnect is controlled by routing switches that connect wires together to form paths between the logic blocks.

Designs using FPGAs enjoy short turn-around time, low non-recurring engineering cost, freedom from the complexities and risks of physical design, and flexibility to modify the functionality, making them favourable compared to ASICs in many situations. Where the turn-

around time is vital, production volume is low, or where simplicity of design effort is desired, FPGAs are an attractive option. Their applications have expanded from simple glue logic to large stand-alone designs. The price for this flexibility is that they have lower performance, lower logic density, and higher power consumption than ASICs [20].

Figure 2.1: LUT-Based Island-Style Architecture

One popular architecture that has formed the basic pattern of early commercial FPGAs [21, 22] and has been the subject of much academic research [23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 34, 35] is the *look-up table* (LUT)-based island-style FPGA architecture. The LUT-based island-style FPGA architecture consists of a matrix of configurable logic blocks (CLBs) arranged like

islands in a sea of routing resources. Each CLB contains one or more LUTs, that act as programmable gates, and D flip-flops. The routing resources are organized in wires that form horizontal and vertical channels. These channels intersect at switch blocks and connect to the CLBs in connection blocks. Surrounding the entire matrix are input and output ports that interface the logic in the FPGA with the outside world. A typical island-style architecture is shown in Figure 2.1 and Figure 2.2.

Figure 2.2: Details of the LUT-Based Island-Style FPGA

#### 2.1.2 Addition of Fixed IP Cores

In addition to general-purpose logic resources, state-of-the-art commercial FPGAs such as Altera's Stratix-II [36] and Xilinx's Virtex-4 [37] now include adders, multipliers, memories, processors, clock management circuitry, and support for many I/O standards. These fixed intellectual property (IP) cores lead to significant increases to performance, savings in area,

reductions in power, and simplifications of customer designs for applications in which these cores can be used. Figure 2.3 illustrates an FPGA with fixed logic cores.

Figure 2.3: FPGA with Fixed IP Cores

## 2.1.3 Hard-Wired FPGAs

Even with these fixed cores, FPGAs still have lower performance, density, and power efficiency than ASICs. Performance and power efficiency can be improved by hard-wiring the routing on the FPGA [38]. The routing inside the CLB can be hard-wired as well, either using vias [38, 39] or two metal layers [40]. Designs destined for hard-wired FPGAs are easy to prototype using an FPGA and then can be made into fixed logic later on. The density can also be increased because

the configuration memory can be eliminated [38]. To build on this concept, Altera's HardCopy II [41] converts the FPGA design into an ASIC made up of smaller cells, but customization is still performed using two metal layers. This further improves performance, density, and power efficiency. In essence, these two approaches allow the FPGA users to build fast and efficient, fixed logic without the cost of a full fabrication mask set or the complexities and risks of physical design. However, it requires approximately 8 weeks [40] and the FPGA is no longer reconfigurable. Though this is acceptable for custom computing, a hard-wired FPGA with fixed logic and routing cannot be used for reconfigurable custom computing.

## 2.1.4 System-on-a-Chip Designs with Embedded Programmable Logic Cores

The system-on-a-chip (SoC) design methodology involves the re-use and integration of off-the-shelf intellectual property (IP) cores into the design of a single chip in efforts to reduce design complexity. These IP cores are designed and tested by third-party vendors to provide a specific functionality. The SoC designer would assemble a number of these IP cores together to construct a larger chip. Given the popularity of FPGAs and their reconfigurability, SoC designers are starting to embed FPGA-like programmable logic cores [42, 43, 44, 45, 46, 47, 48, 49] in chips along with fixed logic IP cores. Figure 2.4 gives an example of this.

FPGA cores offer the flexibility to modify the chip's function when the specifications change, the possibility of producing a single chip that can be dynamically customized for a family of related applications, the opportunity to design a new chip by customizing only the embedded FPGA in platform-based design, and use of the programmable logic to perform on-chip tests [50]. As part of a reconfigurable computer, such a programmable fabric could possibly be configured during run-time as a custom functional unit [51, 52] or co-processor [53, 54].

**Embedded Programmable Logic Core**

Figure 2.4: System-on-a-Chip Design with an Embedded Programmable Logic Core

There are two broad categories of programmable logic cores: hard cores and soft cores. Hard cores [42, 43, 44, 45, 46, 47] are circuits of programmable logic described by a layout that is ready to be integrated with the rest of the logic on the chip. Like most FPGAs, the hard cores have customized layouts to maximize their density. Soft cores [48, 49] are circuits of programmable logic that are described using a high-level hardware description language (HDL), that can be synthesized along with the other logic on the chip using a standard computer-aided design (CAD) flow. This eliminates the need to add the programmable IP core in the physical layout stage. It also means the size of the soft core can be adjusted to what is needed. However, the soft cores are slower and consume significantly more area than the hard cores.

# 2.1.5 Fine-Grained Reconfigurable Architectures Coupled with a Microprocessor

Fine-grained reconfigurable architectures have logic blocks that operate on bits that are connected by programmable logic. Components such as logic gates, LUTs, and flip-flops, which are used to implement Boolean logic functions, usually characterize these architectures [1]. While an FPGA fits this description, we describe in this subsection fine-grained reconfigurable architectures that have an FPGA-like fabric coupled with a microprocessor.

Figure 2.5: Fine-Grained Reconfigurable Architecture

As mentioned in the previous subsection, an embedded FPGA can be combined with a microprocessor to serve as a functional unit or a co-processor as shown in Figure 2.5. This has been researched substantially, even while FPGAs were still stand-alone devices. Programmable logic used as functional units [51, 52, 55, 56, 57] and co-processors [53, 54, 58, 59, 60, 61] in fine-grained reconfigurable architectures have delivered large increases in performance compared to microprocessors. For example, the reconfigurable functional unit in PRISC [51]

increased performance by 22%, while Splash [58] demonstrated a 2700 times speedup over a Sun Workstation on a DNA sequence matching application.

Even though fine-grained reconfigurable logic is suitable for implementing functional units and co-processors, there are applications where custom processing capabilities are not needed. Rather, parallel processing on bytes or words using standard instructions are sufficient. An FPGA can do this, but its logic and routing flexibility exceed what is necessary. FPGAs are more efficient for implementing random logic than for applications with datapaths [2].

## 2.1.6 Coarse-Grained Reconfigurable Architectures

Medium and coarse-grained reconfigurable architectures represent a class of programmable logic architectures that operate on data that are 4 to 32 bits wide. There are typically functional units resembling arithmetic logic units (ALUs) that operate on this data as well as interconnect that routes data in 4- to 32-bit wide buses. Like fine-grained reconfigurable architectures, medium and coarse-grained reconfigurable architectures have blocks with programmable functionality which communicate over programmable interconnect.

Coarse-grained reconfigurable architectures are typically comprised of an array of configurable functional units (FUs) with programmable interconnect, as shown in Figure 2.6. They are similar to FPGAs except that larger functional units take the place of LUTs and the routing buses primarily carry words rather than bits. Compared to FPGAs, coarse-grained reconfigurable architectures require far fewer configuration bits, which can also be thought of as instruction memory.

Figure 2.6: Coarse-Grained Reconfigurable Architecture

#### 2.1.7 VLIW Processors

Very long instruction word (VLIW) processors, like coarse-grained reconfigurable architectures, have multiple functional units. VLIW processors also have local memory in the form of one or more register files. They differ in the fact that VLIW processors usually have functional units that only communicate via the shared global register file while the functional units in reconfigurable architectures communicate through a programmable interconnect. This requires VLIW processors to have many read and write ports on the global register file, slowing down access speed [62]. This also results in a scalability bottleneck; VLIW processors typically have four or at most eight functional units [62], far fewer than the 16 or 64 functional units found in some coarse-grained architectures [1, 3, 5, 8, 9, 10]. To scale the VLIW processor further in terms of the number of functional units, one to four functional units are typically clustered so that each cluster has a separate register file. However, the communication between clusters is complex [62].

# 2.1.8 Clustered VLIW Processor with a Reconfigurable Inter-Cluster Bus

The clustered VLIW with a reconfigurable inter-cluster bus, illustrated in Figure 2.7, is able to scale well to a greater number of functional units [62]. These clusters communicate via a bus with a ring topology, with connection boxes associated with each cluster's register file. Again, the communication between functional units is restricted to shared register file access. In fact, this clustered VLIW is very similar to CRISP [13], a coarse-grained reconfigurable architecture, which has four functional units and a register file in each slice. The functional units in CRISP can communicate directly with functional units in the same slice as well as through shared access to register files. Since the clustered VLIW architecture has programmable functional units and programmable interconnect, it too could be classified as a coarse-grained reconfigurable architecture.

Figure 2.7: Clustered VLIW Processor With an Inter-Cluster Bus (From [62])

# 2.2 Coarse-Grained Reconfigurable Architectures

This section delves deeper into the area of coarse-grained reconfigurable architectures and presents the applications, distinguishing features, example architectures, and architectural studies.

# 2.2.1 Applications

Coarse-grained reconfigurable architectures are suitable for accelerating loops by exploiting instruction-level parallelism (ILP) and loop-level parallelism (LLP). One area of interest has been digital signal processing (DSP) applications, which have many large loops in the form of fast Fourier transforms (FFTs), finite impulse response (FIR) filters, and correlations [63, 64, 65]. Similarly, MorphoSys [1] was designed for image processing and another architecture [66] for parallel particle filtering. However, when there are many loop-carried data dependencies, the large number of functional units in these architectures cannot be fully utilized because there is not enough parallelism available in the loop [67]. This observation is similar to Amdahl's Law, which indicates that data dependencies in the form of sequential code restricts the maximum speedup available from parallel execution [68].

# 2.2.2 Distinguishing Features

Some features that distinguish the coarse-grained reconfigurable architectures from one another are the nature of the functional units, the interconnect, and the register files.

As summarized in Table 2.1, functional units (FUs) have granularities of 4 bits, 8 bits, 16 bits, or 32 bits, and can perform addition, multiplication, and other operations. In the case of MorphoSys [1], functional units are wired to execute the same instruction across a row or down a column

like a single-instruction multiple-data (SIMD) processor. Another approach has been to fabricate a linear array of fixed-logic standard cells targeted for an application domain [70]. In the application domain of DSPs, specialized functional units have also been proposed [63, 64, 65, 66].

Table 2.1: Coarse-Grained Reconfigurable Architectures Organized By Granularity of Functional Units

| Granularity of Functional Units | Coarse-Grained Reconfigurable Architectures                                                  |

|---------------------------------|----------------------------------------------------------------------------------------------|

| 4 bits                          | PipeRench [2], CHESS [7], D-Fabrix [69]                                                      |

| 8 bits                          | PADDI [6], DReAM [15]                                                                        |

| 16 bits                         | MorphoSys [1], REMARC [5], PADDI [6], PADDI-II [10],<br>Montium [14], DReAM [15], RaPiD [70] |

| 32 bits                         | ADRES [3], RAW [8], MaRS [9],<br>Kress ALU Array III [12], CRISP [13], Chameleon [71]        |

The interconnect has 4- to 32-bit wide buses, which can be arranged in a mesh, where functional units communicate with their neighbours [1, 5, 7, 8, 11, 15], or like a crossbar [6, 10], in which the functional units communicate with many other functional units. There are direct FU to FU connections [1, 5, 7, 11, 12, 14, 15], buses that span several functional units [1, 2, 5, 7, 11, 14, 15, 70], and network routers [8, 9]. Some architectures have several layers of routing, possessing elements of more than one style [1, 5, 7, 11, 14, 15].

The structure and connectivity of register files varies between different architectures. REMARC [5] contains local register files that are only accessible by a single FU. Input register files are found in [6, 10, 11, 14]. The presence of register files with read and write access shared between

functional units characterizes the architectures in [1, 5, 9, 13, 72]. This shared access enables communication between functional units in addition to temporary storage [9].

## 2.2.3 Examples of Coarse-Grained Reconfigurable Architectures

In this subsection, we describe three architectures: RaPiD-I [70], MorphoSys [1], and ADRES [3].

#### 2.2.3.1 RaPiD-I

The RaPiD-I architecture [70] consists of a linear array of functional units arranged in a manner similar to standard cells. There are 16 sets of functional units, each set containing two integer 16-bit ALUs, one 16-bit x 16-bit multiplier, six 16-bit registers, and three small local memories. These functional units are connected by segmented 16-bit wide routing buses to form a linear datapath, as shown in Figure 2.8. The inputs and outputs come in the form of I/O streams at both ends of the datapath. These I/O streams are implemented as FIFOs that read and write data.

The functional units within each cell are independent of one another. Each functional unit input has an input multiplexer that selects from eight 16-bit buses; each functional unit output can be configured to be registered and can drive up to eight 16-bit buses via tri-state buffers. Local memories can be configured to have input registers as well.

There are ten 16-bit wide buses with varying segment lengths that span the length of the linear datapath. Just as there are switch blocks located at the intersections between horizontal and vertical routing channels in FPGAs, there are buffers and registers located between adjacent

segments of the same horizontal 16-bit bus. These buffers and registers allow two segments to be concatenated to form a longer segment, as well as pipeline stages to be inserted.

Figure 2.8: One of Sixteen Sets of Functional Units in the Rapid-I Architecture (From [70])

## 2.2.3.2 MorphoSys

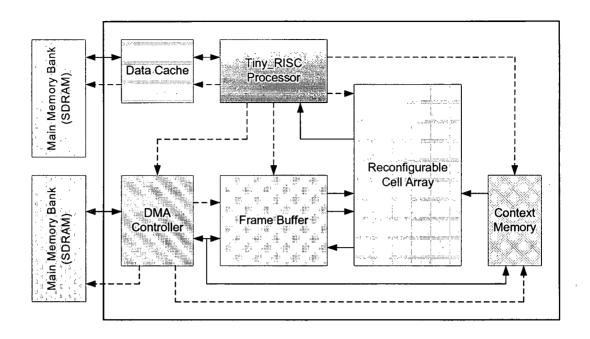

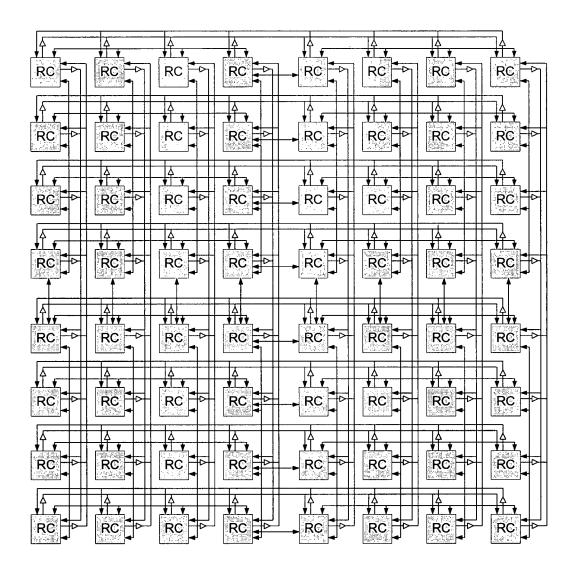

MorphoSys [1] is an image processing reconfigurable architecture. It consists of a reduced instruction set computer (RISC) processor, an array of 64 reconfigurable cells (RCs), a frame buffer, and a direct memory access (DMA) controller, as shown in Figure 2.9. With the layout specified in  $0.35~\mu m$  fabrication process technology, the 8x8 array of reconfigurable cells takes up  $96~mm^2$ , roughly half of the chip. Simulations using HSPICE show that it has a clock speed of 100~MHz.

Figure 2.9: Block Diagram of MorphoSys Architecture (From [1])

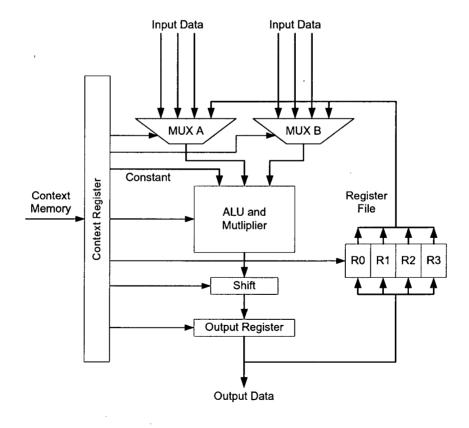

Figure 2.10: Reconfigurable Cell in the MorphoSys Architecture (From [1])

Each reconfigurable cell, illustrated in Figure 2.10, has a 28-bit fixed point ALU and a 16-bit x 12-bit multiplier. There are two multiplexers for the two 16-bit inputs to the ALU and a 12-bit constant input. As well, a register file with four 16-bit registers is available to store data from the ALU's output register for subsequent use as an ALU input.

As shown in Figure 2.11, the interconnect between the reconfigurable cells has three components: nearest neighbour, intra-quadrant, and inter-quadrant interconnect. Each reconfigurable cell is connected to its four nearest neighbours to form a two-dimensional mesh topology. Inside each quadrant of 4x4 reconfigurable cells in the 8x8 array, the reconfigurable cells are connected directly to the three other cells in the same row and the three other cells in the same column. Between quadrants, horizontal and vertical 16-bit buses called express lanes exchange data from the four reconfigurable cells in one quadrant to four reconfigurable cells in another quadrant that are in the same row or column.

Unlike most reconfigurable systems where each functional unit has its own set of configuration bits, MorphoSys shares the same set of configuration bits between eight reconfigurable cells in a row, or alternatively, eight reconfigurable cells in a column. This technique is called context broadcast. The context memory can store up to 32 row or column contexts. New contexts can be loaded into available context memory while the reconfigurable array executes instructions from another set of contexts. Moreover, entire rows or columns can be disabled, so that data transfers require only one row or column of context.

Figure 2.11: MorphoSys Interconnect Architecture (From [1])

#### 2.2.3.3 ADRES

The ADRES architecture [3] consists of a reconfigurable array coupled with a general-purpose VLIW processor. Highly pipeline-able loops are identified by a compiler [73, 74] and executed on the reconfigurable array, while sequential code is executed by the general-purpose VLIW processor. The general-purpose VLIW processor and the reconfigurable unit communicate via two global register files.

ADRES differs from MorphoSys in at least five ways. First, ADRES contains a VLIW processor that is tightly coupled to the reconfigurable array by the shared global register files, unlike MorphoSys, which has a separate RISC processor. Second, MorphoSys has a frame buffer --something not found in ADRES. Third, every functional unit in ADRES can execute a unique instruction at any given time, whereas reconfigurable cells in MorphoSys execute the same instruction across a row or column. Fourth, ADRES has multipliers in some of its functional units, while every reconfigurable cell in MorphoSys includes a multiplier. Fifth, ADRES operates using 1-bit predicates and 32-bit data, while MorphoSys operates using 16-bit data. This suggests that ADRES can execute instructions conditionally using predication while MorphoSys cannot.

A very similar architecture based on ADRES, shown in Figure 1.1, will be the framework of the experiments in this thesis. Its details will be given in Chapter 3.

#### 2.2.4 Architectural Studies

In order to develop more efficient coarse-grained reconfigurable architectures, researchers have experimentally measured the impact of the functional unit architecture, the interconnect architecture, the memory interface architecture, and the register file architecture on the performance and density of a coarse-grained reconfigurable architecture. In this subsection, we consider each of these separately.

First, the functional units in the coarse-grained reconfigurable architectures have been studied, particularly in terms of performance. Increasing the number of functional units can significantly reduce the number of instruction cycles required to execute a loop, but it was found that the

loop-carried data dependencies limit this speedup [2, 67]. Bansal et al. [67] found that dividing a functional unit into two smaller fully connected functional units, one of which performs multiplication while the other the remaining operations, results in a performance gain of 0 to 13%. The performance gain is not observed, however, when the multiplication and arithmetic units cannot be used simultaneously in certain benchmark programs. Ienne et al. [75] state that predication support, which allows the execution of conditional *if* statements, is fundamental to parallelism, and is therefore essential for obtaining the best results. Compton et al. [76] try to allocate just the appropriate amount of each type of functional unit for specific application domains. Goldstein et al. [2] have compared the computational density of functional units with granularities of 2, 4, 8, 16, and 32 bits, measured in bit-operations per unit time per unit area, and found that the computational density remained relatively constant for different granularities. While area can be optimized for functional units with larger word widths, the delay of the adder's carry chain also increases. Nevertheless, they predict that the computational density would increase linearly with increasing bit widths if logical operations were implemented rather than arithmetic operations.

Second, the functional unit interconnect has been explored. Compton et al. [77] show how track placement for a segmented routing architecture can be assigned within 1.2% of the optimal spreading of wires, where the number of routing wires accessible to each node is balanced. By fully connecting functional units in clusters of four, Bansal et al. [67] increased the performance by 0 to 41% above the performance when the functional units are neither grouped into clusters nor fully connected. In a different study, Bansal et al. [78] found that connecting a functional unit to two other functional units in the same row and two in the same column is sufficient to

achieve good performance. Compared to connecting to only two functional units, one in the same row and one in the same column, connecting to four gives significantly higher performance. Connecting to six functional units gives only slightly higher performance. These experiments assumed the presence of row and column buses. In the absence of row and column buses, Wilton et al. [79] showed that connecting a functional unit to six functional units gives performance comparable to the performance achieved by fully connecting the functional units, but with much smaller area.

The architecture of the memory interface has also been studied. Ienne et al. [75] showed that most basic blocks of dataflow, or code segments without control instructions, require very few memory accesses. Therefore, having one memory read and write port is only 15-20% slower than having an unlimited number of memory ports for the reconfigurable logic. Lee et al. [80] also showed that the inclusion of an address generator can improve performance, though its effect varies between different applications.

As for register files, Tabrizi et al. [9] have explicitly referred to them as a second layer of communication between functional units. Colavin et al. [62] allocated two read ports and two write ports on a shared register file for inter-cluster communication and two read ports and one write port for the local cluster of functional units, based on empirical data. A more general study by Ienne et al. [75] showed that it is important for performance to have at least two or three write ports on the global register file for the reconfigurable logic to access, though this may be costly in terms of area.

## 2.3 Focus of this Thesis

The goal of this research is to study the role of register files in coarse-grained reconfigurable architectures, which were introduced in Subsection 2.1.6 and explored further in Section 2.2. Chapter 3 describes the reconfigurable array of a coarse-grained reconfigurable architecture that is based on the ADRES architecture discussed in Subsection 2.2.3. Chapter 4 describes an experimental flow for conducting an architecture study on the register files similar to studies in Subsection 2.2.4. The results of the experiments are shown and discussed in Chapter 5. The knowledge gained about register files is then applied to create two new and improved architectures in Chapter 6.

# Chapter 3

# **FRAMEWORK**

In this chapter, we describe the framework upon which our study is built.

To make our results concrete, we have performed our studies in the context of a specific reconfigurable architecture, ADRES [3]. As described in Chapter 2, ADRES contains an array of coarse-grained logic blocks integrated with a very long instruction word (VLIW) processor. Application code is mapped to the architecture by first using the IMPACT-I compiler [73], developed at the Center for Reliable and High-Performance Computing in the University of Illinois at Urbana-Champaign, to perform architecture-independent optimization and parallelism extraction, followed by DRESC [74] to perform architecture-dependent mapping. Section 3.1 will describe the reconfigurable array of the ADRES-based architecture, Section 3.2 will describe the IMPACT-I and DRESC compilers, and Section 3.3 will state the architectural design space that will be explored in this thesis.

#### 3.1 Architecture

In this section, the computation units, the register files, the interconnect, and the context memory of the reconfigurable array will be described in detail.

### 3.1.1 Computation Units

The reconfigurable fabric consists of a heterogeneous array of configurable functional units (FUs). In this thesis, we will consider two array sizes: 4x4 and 8x8. Each FU can perform a subset of forty-five 32-bit operations in each clock cycle. All FUs can perform a variety of arithmetic (signed and unsigned), logic, shifting, and comparison instructions. One out of every four columns has FUs that can also perform 16-bit x 16-bit multiplication, as shown in Figure 3.1.

Figure 3.1: Columns of Functional Units With Multipliers

The FUs in the top row are different than the others. These FUs perform two tasks: they make up the functional units of the general-purpose VLIW processor when this processor is executing code, and act as additional configurable FUs when the device is executing parallel code on the

reconfigurable array. These FUs have direct connections to the two global register files through dedicated read and write ports.

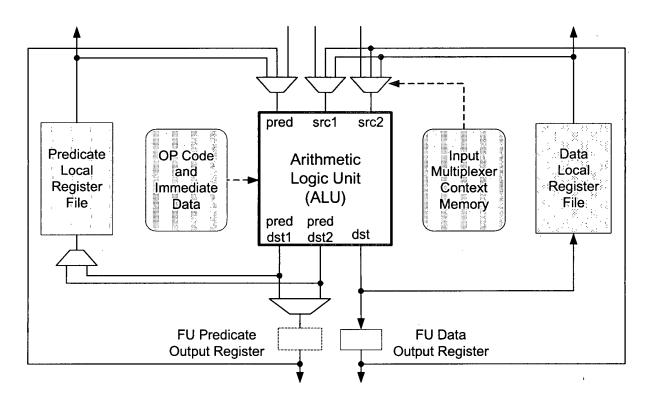

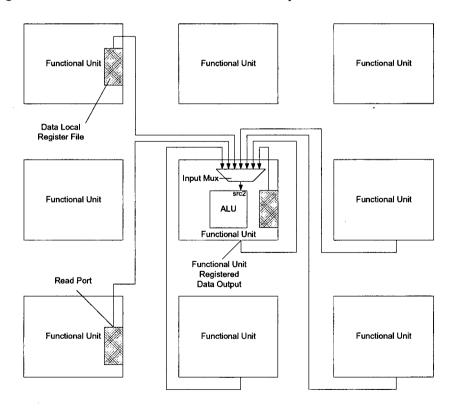

Figure 3.2 shows a single configurable functional unit (FU) in the baseline architecture. The important features of the FU are depicted in the figure, but the number of signals and read and write ports will vary between the different architectures that are discussed in this thesis. Each FU contains both a configurable ALU (the function of which can be specified using context memories, analogous to the configuration memories in an FPGA or the instruction memory in a microprocessor) and two local register files; these register files will be described in more detail below.

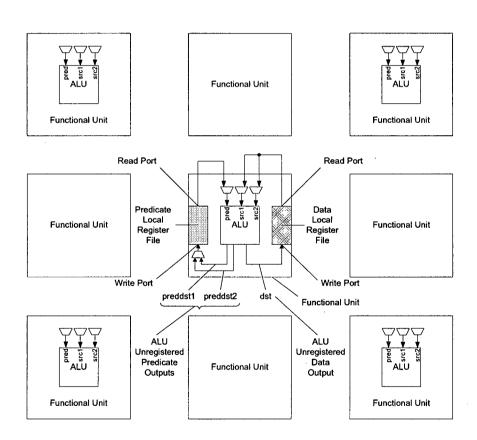

Figure 3.2: Configurable Functional Unit in the ADRES-based Architecture

### 3.1.2 Register Files

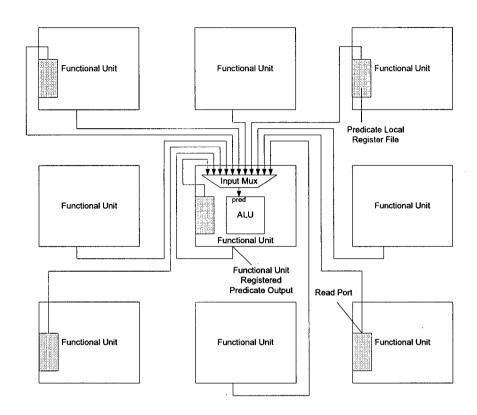

As described above, this architecture has two types of register files: two local register files within each FU, and two global register files, as shown in Figure 3.3.

Figure 3.3: Global and Local Register Files in the ADRES-based Architecture

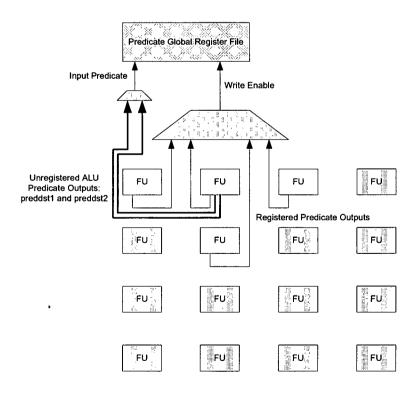

First consider the two global register files. These register files are used for two purposes: (1) to transfer data between the general-purpose VLIW processor and the reconfigurable array, and (2) as scratch-pad memory for the functional units in the top row of the reconfigurable array when they operate as the general-purpose VLIW processor. There is one global register file (32 bits wide) to store data values, and one global register file (1 bit wide) to store predicate values.

As described above, in the baseline architecture, each data global register file is connected to each FU in the top row through two dedicated read ports, one for each data ALU input, and one dedicated write port. Thus, in a 4x4 array, each data global register file has eight read ports and four write ports; in an 8x8 array, each data global register file has sixteen read ports and eight write ports.

Each predicate global register file is connected to the FUs in the top row through one dedicated read port and one dedicated write port. Thus, in a 4x4 array, each predicate global register file has four read ports and four write ports; in an 8x8 array, each predicate global register file has eight read ports and eight write ports.

There are also two local register files within each functional unit. These register files can be used as scratch-pad memory by the functional units in the reconfigurable array, and can be used to transfer data between functional units. Each functional unit contains one 32-bit wide register file to store data values, and one 1-bit wide register file to store predicate values.

The main difference between global and local register files is that global register files have multiple read and write ports to support the operation of the general-purpose VLIW processor while the local register files typically have one write port and possibly several read ports. Another difference is that the write enable signals on the global register files can be controlled by predicate signals generated by functional units, while the write enable signals of local register files are determined solely by values stored in configuration bits.

Note that the functional unit output registers can simply be viewed as local register files with one read port and one write port. There have been attempts to amalgamate the output register with the local register file, but the preliminary performance results have generally been disappointing. These results suggest that the DRESC compiler does not handle them this way. Since output registers and register files are specified differently in the architecture description, DRESC may assume different functions for them.

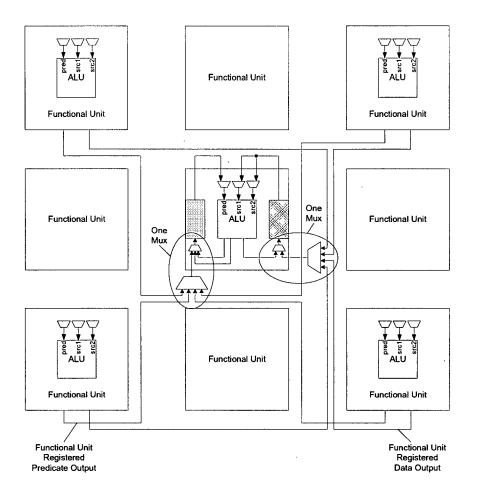

#### 3.1.3 Interconnect

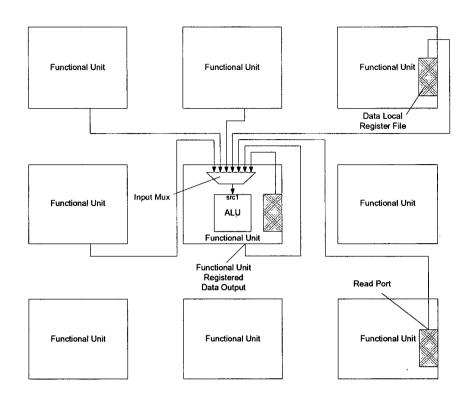

The functional units in the reconfigurable array communicate with the general-purpose VLIW processor via the two global register files. There are input multiplexers to each functional unit that receive data and predicate signals from other functional units. As well, the local register files may or may not be shared between different functional units, depending on the experiment.

The FUs are interconnected using the "closest" architecture as described in [79] and shown in Figure 3.4, Figure 3.5, and Figure 3.6. The interconnect buses that carry these signals are in the form of direct connections, and there are no shared buses or segmented routing. In this interconnect architecture, each of the two data ALU inputs is driven by registered versions of four neighbouring data FU outputs including the data output from the local FU. The single predicate ALU input is driven by registered versions of seven neighbouring predicate FU outputs including the predicate output from the local FU.

Figure 3.4: Interconnect Pattern for src1 data ALU input in the Baseline Architecture

Figure 3.5: Interconnect Pattern for src2 data ALU input in the Baseline Architecture

Figure 3.6: Interconnect Pattern for pred predicate ALU input in the Baseline Architecture

In the baseline architecture, each local register file has one read port and one write port. As shown in Figure 3.2, the write port of each local register file is driven by the unregistered output of the ALU within the local FU. The read port of each local register file, however, is connected to six sinks: the two inputs of the ALU in the local FU, and one input in each of four neighbouring FUs (the four FUs diagonally adjacent to the local FU). These connections are shown in Figure 3.7.

Figure 3.7: Interconnect Pattern for Local Register File Read Ports in the Baseline Architecture

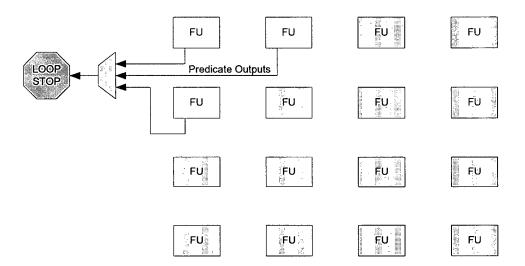

Now we describe the interconnect of control signals. The loop stop signal, which is used to inform the VLIW processor that the reconfigurable array has finished a computation, is multiplexed from the three functional unit predicate output registers in the upper left corner of the functional unit array, as shown in Figure 3.8.

Figure 3.8: Generation of Loop Stop Signal

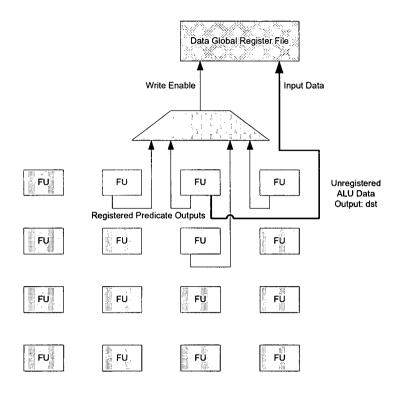

As shown in Figure 3.9, the write enable signal for a write port on the data global register files is supplied by the predicate outputs of the same functional unit that supplies the input data; additional inputs to the write enable multiplexer come from the predicate outputs of the functional units immediately to the left, to the right, and below. Similarly, as shown in Figure 3.10, the write enable signal for a write port on the predicate global register file is supplied by the predicate output register of the same functional unit that supplies the input data; additional inputs to the write enable multiplexer come from the predicate outputs of the functional units immediately to the left, to the right, and below. In Chapter 5, we will increase the number of functional units which supply potential data and predicate inputs to each write port; in these architectures, the additional functional units supply additional registered predicate outputs for the write enable multiplexer but the nearest neighbours of these additional functional units do not supply additional registered predicate outputs for the write enable multiplexer.

Figure 3.9: Generation of Write Enable Signal for the Data Global Register File

Figure 3.10: Generation of Write Enable Signal for the Predicate Global Register File

### 3.1.4 Context Memory

One set of configuration bits is required for each context. The configuration bits for a context represents the configuration during each clock cycle of a loop iteration and are selected using multiplexers. For the 4x4 array, 1 to 18 contexts are typically required for the set of benchmarks with approximately 2000 configuration bits in each context; for the 8x8 array, 1 to 8 contexts are typically required for the set of benchmarks with approximately 8000 configuration bits in each context. The number of required configuration bits remains constant throughout the lifetime of the loop, while the selected context is changed at every clock cycle.

## 3.2 Compilers

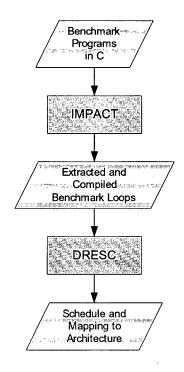

This section introduces two compilers, IMPACT-I and DRESC, that are used to schedule and map C programs onto the ADRES-based architectures. Figure 3.11 shows where they fit in the compilation flow.

Figure 3.11: Compilation Flow

#### **3.2.1 IMPACT-I**

When a C program is mapped to the ADRES-based architecture, it is first compiled using IMPACT-I. The IMPACT-I C compiler [73] was designed to perform optimizations for a parameterized processor that can execute multiple instructions at a time. This processor must be specified by its instruction set, architecture, and code scheduling model. IMPACT-I separates code into basic blocks that can be executed sequentially and applies code optimization techniques such as function inline expansion, loop unrolling, loop peeling, branch expansion, induction variable expansion, register renaming, global variable register allocation, operation combining, operation folding, memory disambiguation, inline target insertion, and speculative execution of instructions following a branch. Instructions can also be moved around in the code, and even pushed before or after branch instructions. IMPACT-I transforms the C code into an intermediate representation called "Lcode", which resembles a collection of assembly-level instructions to be mapped to the architecture.

#### **3.2.2 DRESC**

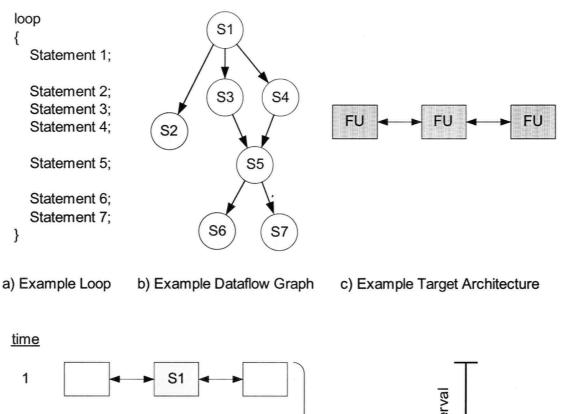

DRESC first partitions the Lcode into the loops that will be mapped to the reconfigurable array and the rest of the Lcode that will be mapped to the general-purpose VLIW processor [3]. The Lcode for the reconfigurable array is scheduled to exploit loop-level parallelism (LLP) while the Lcode for the general-purpose VLIW processor is optimized for instruction-level parallelism (ILP). DRESC identifies and allocates space in the global register files for the live-in and live-out variables. These are the input and output variables of the loop that constitute the interface between the Lcode for the reconfigurable array and the Lcode for the general-purpose VLIW processor.

Taking the particular basic blocks from IMPACT-I that constitute loops, the DRESC compiler [74] uses a modulo-scheduling algorithm to schedule each loop on the target reconfigurable array, assigning each operation in the loop to a specific FU in a specific time slice and assigning each variable to one of the register files, where temporary storage is necessary. The DRESC tool takes into account the characteristics of the target architecture, including the capabilities of each FU, the size of each register file, and the interconnect between the FUs and the register files. This ensures that the resulting schedule can be implemented on the reconfigurable device. In essence, the DRESC tool performs the tasks of scheduling, placement, and routing simultaneously. DRESC uses techniques from the simulated annealing algorithm [81] and the Pathfinder routing algorithm [82] to perform these tasks.

During mapping, DRESC attempts to minimize the iteration interval (II) of the scheduled loop. The iteration interval is the number of clock cycles between the initiation of successive iterations of the loop, as shown in Figure 3.12. As explained in [74], the II is equal to the number of contexts required in the configuration memory of the reconfigurable fabric. Therefore, the achievable II directly impacts the area of the architecture. Intuitively, if an architecture is more flexible (either because there are more registers or they are better located or connected to the computation units), the DRESC compiler will be able to find a schedule with a smaller value of II. On average, this means that if the fabric was constructed, a smaller number of contexts would be used, meaning less context memory is required, and thus smaller area is required. As explained in [74], the value of II also has a strong influence on the achievable *instructions per cycle* (IPC), which dictates the overall performance of the device.

d) Scheduling and Mapping Loop onto the Target Architecture

Figure 3.12: Illustration of Iteration Interval when Mapping a Loop to an Architecture

In this way, DRESC takes the parallelized code from IMPACT-I and maps it to the ADRES-based architecture. DRESC produces a schedule for the execution of each accelerated loop, as well as the assignment of each instruction to specific functional units. All of the information required for configuring the ADRES-based architecture, including register file accesses and multiplexer select lines, is generated by DRESC.

## 3.3 Design Space Explored in This Thesis

This section describes the design space explored in this thesis. In particular, it identifies the parameters that are varied in the experiments.

#### 3.3.1 Parameters

Table 3.1 shows a list of the architectural parameters that describe the register files in the baseline architecture for both a 4x4 array and an 8x8 array. In Chapter 5, one parameter is varied at a time, and the impact on area and performance is measured. The range investigated for each parameter is also shown in Table 3.1.

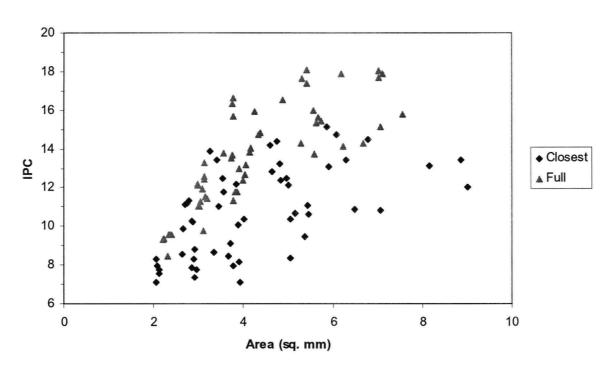

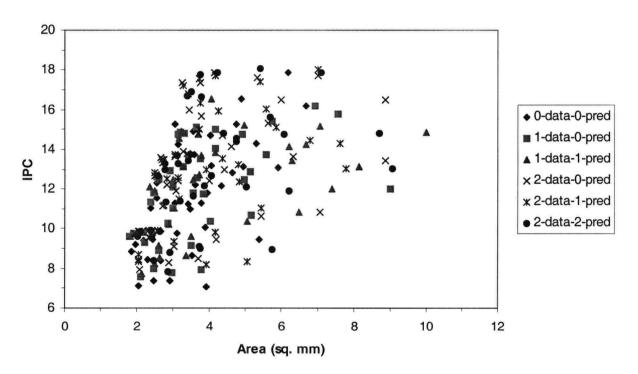

Besides the "closest" interconnect architecture, the "full" and "empty" interconnect architectures are also used in some experiments. The "full" architecture describes an array of functional units in which each functional unit is connected to every other functional unit. The "empty" architecture describes the opposite; each functional unit has no direct connection to any other functional unit, but only connections from each functional unit to the global register files, which is typical in general-purpose VLIW processors.

Table 3.1: Architectural Parameters Used in This Thesis

|                             | Parameter                                                                       | Value in Baseline<br>Architecture   | Range Considered in Chapter 5                  |  |

|-----------------------------|---------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------|--|

| Global<br>Register<br>Files | Number of FUs connected to each register file                                   | 4 (4x4 array)<br>8 (8x8 array)      | 4 to 16 (4x4 array)<br>8 to 64 (8x8 array)     |  |

|                             | Number of read and write ports per register file                                | 4* (4x4 array)<br>8* (8x8 array)    | 4* to 16* (4x4 array)<br>8* to 64* (8x8 array) |  |

|                             | Number of FUs with ports to the register file and to main memory                | 4 (4x4 array)<br>8 (8x8 array)      | 4 to 16 (4x4 array)<br>8 to 64 (8x8 array)     |  |

|                             | Number of registers per register file                                           | 16 (4x4 array)<br>64 (8x8 array)    | 4 to 48 (4x4 array)<br>8 to 48 (8x8 array)     |  |

| Local                       | Number of FUs connected to<br>the read and write ports on<br>each register file | 5 per read port<br>1 per write port | 1 or 5 per read port<br>1 or 5 per write port  |  |

| Register<br>Files           | Number of read ports per register file                                          | 1                                   | 1 to 6                                         |  |

|                             | Number of registers per register file                                           | 4                                   | 0 to 16                                        |  |

<sup>\*</sup> There are twice as many read ports on the Data Global Register File.

## 3.4 Summary

In this chapter, the ADRES-based architecture has been described in detail. Then the capabilities of the IMPACT-I and DRESC compilers were presented in relation to how they are used to map C programs on the ADRES-based architectures. The chapter concluded with a discussion of the parameter values which will be varied when we explore the design space for the ADRES-based architectures.

# Chapter 4

## EXPERIMENTAL METHODOLOGY

This chapter describes the flow used to perform experiments on the ADRES-based architectures.

The metrics chosen for evaluating the experimental results are also presented.

## 4.1 Experimental Flow

The design flow for mapping C programs to the ADRES architecture, using IMPACT-I and DRESC, have already been described in Chapter 3. This section will explain how the experimental architectures are incorporated into the overall flow. Then SCRAP, a tool useful for manipulating architectures, will be introduced along with the VHDL model that is included in SCRAP. Lastly, a description of the benchmark kernels will be given.

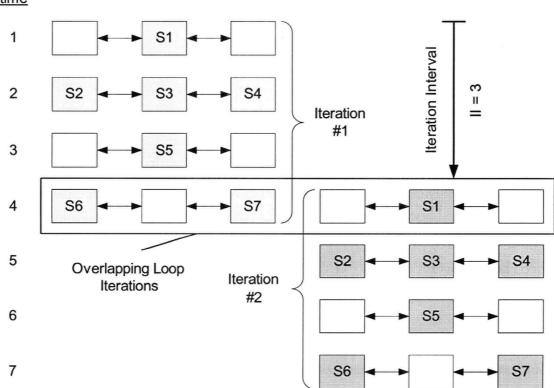

#### 4.1.1 Overall Flow

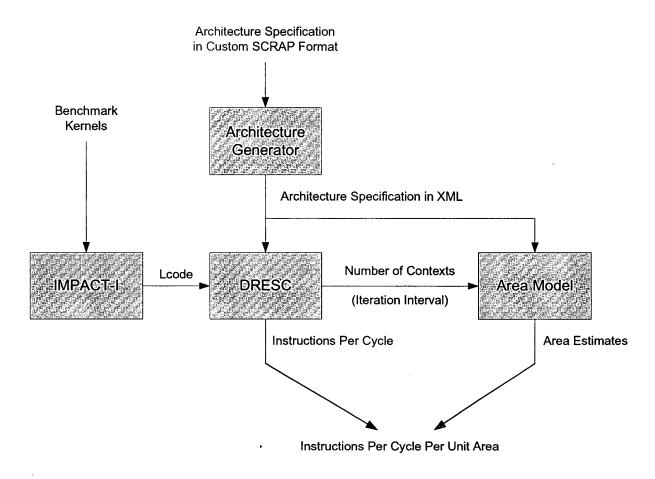

In the overall flow shown in Figure 4.1, C benchmark programs are compiled using IMPACT-I and DRESC. DRESC uses an eXtensible Markup Language (XML) architecture description file during compilation. This same architecture description is used to estimate the area using an area model. Note that the area model is affected by the number of contexts, given by the iteration interval (II) produced by DRESC. After the instructions per cycle (IPC) is extracted from DRESC's output files and the area is estimated, we divide the IPC by the area estimate to compute the *number of instructions per cycle per unit area*.

Figure 4.1: Experimental Flow

#### **4.1.2 SCRAP**

Steve's Coarse-grained Reconfigurable Architecture Program (SCRAP) is a tool that was developed to ease the specification of new architectures and to provide an area estimate. SCRAP contains an architecture generator and part of an area model. It takes as input a description in a custom SCRAP format and converts it into the standard XML architecture description that is recognizable by DRESC. Manipulating the architecture in its own internal format, SCRAP then produces a VHDL description of the architecture. Enhancements made as part of this work include the generation of the XML architecture description, the addition of global register files to the VHDL description, a transition to a modular VHDL description, and part of the area model.

With the new modular VHDL description, only the top-level entity is customized for each architecture, while the modules representing parameterized functional units, multiplexers, configuration memory, and registers are unchanged.

#### 4.2 VHDL Model

A Very High Speed Integrated Circuits Hardware Description Language (VHDL) model was developed for the ADRES-based architecture and included in SCRAP. The VHDL model was specified at the register-transfer level (RTL), and synthesized using Synopsys using generic standard-cells. This section describes how the functionality of our architectures was specified.

#### 4.2.1 Functional Units

The ALU in each functional unit was implemented using a switch-case block that performed different operations on the input data based on the operation code. While arithmetic, logical, shift, compare, predicate, and multiplication instructions were easy to specify, the division and remainder operations were left unimplemented. There are two reasons for this: (1) there is no standard synthesis of a divider available from Synopsys; and (2) the paper describing ADRES [3] does not mention the presence of dividers. For divisions by powers of two, an arithmetic shift right instruction would suffice. For other types of divisions, subroutines can use shifts, comparisons, and subtractions to perform long division one bit at a time. Note that certain commercial DSP processors do not perform long division one bit at a time [83, 84, 85].