## CHANNEL WIDTH REDUCTION TECHNIQUES FOR SYSTEM-ON-CHIP CIRCUITS IN FIELD-PROGRAMMABLE GATE ARRAYS

by

#### **MARVIN TOM**

B.A.Sc., Simon Fraser University, 2002

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

(Electrical and Computer Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

April 2006

© Marvin Tom, 2006

### **ABSTRACT**

Users of field-programmable gate arrays (FPGAs) typically measure the size of a FPGA by its logic capacity. If a design fits within the logic capacity limits of an FPGA, it is generally assumed that it must also be routable. To ensure this high routability, FPGA vendors typically over-design the routing network. Despite this over-design, there may still be circuits that remain un-routable in a given FPGA family. This thesis presents two new computer-aided design (CAD) tools, DHPack and Un/DoPack, that are able to route these un-routable circuits by trading off logic utilization for interconnect. DHPack uses the natural design hierarchy of the circuit to identify high congestion regions. For a set of benchmark circuits used in this thesis, DHPack is able to reduce channel width by 13% with a small area increase of 3%. DHPack can continue to decrease channel width by 29% with a larger area increase of 146%. Un/DoPack improves on DHPack by targeting hard channel width constraints without having to rely on the design hierarchy of the circuit to perform congestion estimation. For a set of benchmark circuits presented in this thesis, Un/DoPack can reduce channel width by 38% with an 18% penalty in critical path delay and 64% increase in area. The primary application of these tools is to make previously unroutable circuits routable by using an FPGA with more logic.

# TABLE OF CONTENTS

| Ab  | stract.  | ••••••  |                                         | ii    |

|-----|----------|---------|-----------------------------------------|-------|

| Ta  | ble of ( | Content | S                                       | iii   |

| Lis | t of Ta  | bles    | ••••••••••••••••••••••••••••••••••••••• | . vii |

| Lis | t of Fig | gures   | ······································  | viii  |

| Gle | ossary . | ••••••  | ••••••••••••••••••••••••••••••••••••••• | x     |

| Ac  | knowle   | dgemen  | ıts                                     | . xii |

| 1   | Intro    | duction |                                         | 1     |

|     | 1.1      | Motiva  | ation and Objectives                    | 2     |

|     | 1.2      | Contri  | butions                                 | 4     |

|     | 1.3      | Thesis  | Organization                            | 5     |

| 2   | Back     | ground. |                                         | 6     |

|     | 2.1      | FPGA    | Architecture                            | 6     |

|     | 2.2      | FPGA    | CAD Flow                                | 10    |

|     |          | 2.2.1   | Synthesis                               | 11    |

|     |          | 2.2.2   | Technology Mapping                      | 11    |

|     |          | 2.2.3   | Clustering                              | 13    |

|     |          | 2.2.4   | Placement                               | 15    |

|   |      | 2.2.5 Routing                                                |

|---|------|--------------------------------------------------------------|

|   | 2.3  | Previous Methods to Reduce Channel Width                     |

| 3 | Meth | ods to Reduce Minimum Routable Channel Width20               |

|   | 3.1  | Input-Limits vs. BLE-Limits                                  |

| 4 | Benc | nmark Circuits23                                             |

|   | 4.1  | Meta Benchmark Circuits                                      |

|   | 4.2  | Stdev Benchmark Circuits                                     |

| 5 | Chan | nel Width Reduction Using Design Hierarchy Packing: DHPack30 |

|   | 5.1  | DHPack - Depopulation Strategy31                             |

|   |      | 5.1.1 Steps 1,2: Channel Width Profiling and BLE-Limits33    |

|   |      | 5.1.2 Steps 3,4: Cluster IP blocks and Stitch Circuit35      |

|   | 5.2  | Experimental Results                                         |

|   | 5.3  | Experimental Conclusions                                     |

|   | 5.4  | Technique Limitations and Future Work44                      |

|   |      | 5.4.1 I/O Padframe Congestion44                              |

|   |      | 5.4.2 IP Block Granularity Too Coarse45                      |

|   |      | 5.4.3 Hard Channel Width Constraints45                       |

|   |      | 5.4.4 Congestion Profile Run Time Long                       |

| 6<br>Un |      |          | Ith Reduction Using Automated Congestion Identification:47 |  |

|---------|------|----------|------------------------------------------------------------|--|

|         | 6.1  | Un/Do    | Pack - Depopulation Strategy48                             |  |

|         |      | 6.1.1    | Step 1: Traditional SIS/VPR Flow49                         |  |

|         |      | 6.1.2    | Step 2: UnPack - Congestion Calculator49                   |  |

|         |      | 6.1.3    | Step 3: DoPack - Incremental Re-Cluster                    |  |

|         |      | 6.1.4    | Step 4: Placement and Routing53                            |  |

|         | 6.2  | Experi   | imental Results54                                          |  |

|         |      | 6.2.1    | Stdev Benchmark Circuit Results55                          |  |

|         |      | 6.2.2    | Comparison of Un/DoPack and DHPack66                       |  |

|         | 6.3  | Experi   | imental Conclusions68                                      |  |

|         | 6.4  | Techn    | ique Limitations and Future Work69                         |  |

|         |      | 6.4.1    | Fast Placement Improvements69                              |  |

|         |      | 6.4.2    | Benchmark Interconnect Variation Verification71            |  |

| 7       | Conc | lusion a | and Future Work72                                          |  |

|         | 7.1  | Future   | e Work74                                                   |  |

|         |      | 7.1.1    | DHPack Future Work74                                       |  |

|         |      | 7.1.2    | Un/DoPack Future Work75                                    |  |

|         |      | 7.1.3    | System Level Interconnect Prediction76                     |  |

|       | 7.1.4        | Improved FPGA Modeling           | 77 |

|-------|--------------|----------------------------------|----|

| 8 R   | eferences    |                                  | 79 |

| Appe  | ndix A – Sto | dev Benchmark Circuit Parameters | 84 |

| Appe  | ndix B – DI  | HPack Simulation Results         | 85 |

| Apper | ndix C – Ur  | n/DoPack Simulation Results      | 89 |

## LIST OF TABLES

| Table 1-1: Features and Costs of Two FPGA Families (from [2], [3], [19]) | 2 |

|--------------------------------------------------------------------------|---|

| Table 2-1: Altera Cyclone Size Options (from [2])                        | 8 |

| Table 5-1: Maximal BLE-Limit Sizes from T-VPack                          | 4 |

| Table 5-2: Maximal BLE-Limit Sizes from iRAC                             | 5 |

| Table 5-3: Reductions in Channel Width for DHPack4                       | 1 |

| Table 6-1: Maximum % Change in Channel Width, Critical Path and Area5    | 6 |

| Table 6-2: Results for PlaceScratch, -fast and Fine Grained6             | 3 |

| Table 7-1: Summary of Channel Width Decreases for DHPack                 | 3 |

| Table 7-2: Summary of Channel Width Decreases for Un/DoPack7             | 3 |

## LIST OF FIGURES

| Figure 1-1: Channel Width / CLB Count Tradeoff                               |

|------------------------------------------------------------------------------|

| Figure 2-1: BLE and CLB7                                                     |

| Figure 2-2: Mesh Based FPGA Architecture                                     |

| Figure 2-3: FPGA CAD Flow10                                                  |

| Figure 2-4: Directed Acyclic Graph Representation of a Circuit (from [29])11 |

| Figure 2-5: Example of Technology Mapping (from [29])12                      |

| Figure 2-6: Example of Clustering (from [29])                                |

| Figure 2-7: Example of Placement (from [29])15                               |

| Figure 3-1: Input- and BLE-Limits during Clustering for Circuit clma21       |

| Figure 4-1: Rent Linear Interpolation for GNL Benchmark Circuits28           |

| Figure 5-1: Pseudo-code for DHPack Flow                                      |

| Figure 5-2: Channel Width Profile of IP Blocks clma/tseng                    |

| Figure 5-3: DHPack CLB Count and BLE Utilization                             |

| Figure 5-4: VPR Placement of Non-Uniform Clique with T-VPack37               |

| Figure 5-5: DHPack MRCW and Average Channel Width39                          |

| Figure 5-6: DHPack Routed Area Factor40                             |

|---------------------------------------------------------------------|

| Figure 5-7: DHPack Critical-Path Delay42                            |

| Figure 6-1: Un/DoPack CAD Flow48                                    |

| Figure 6-2: Congestion Map Before and After Un/DoPack51             |

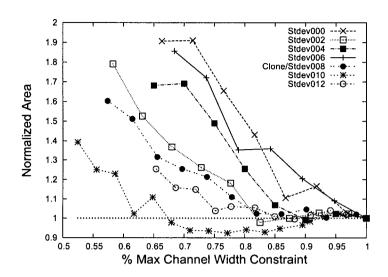

| Figure 6-3: Normalized Area vs. % Max Channel Width Constraint57    |

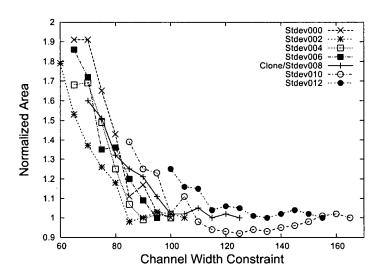

| Figure 6-4: Normalized Area vs. Absolute Channel Width Constraint59 |

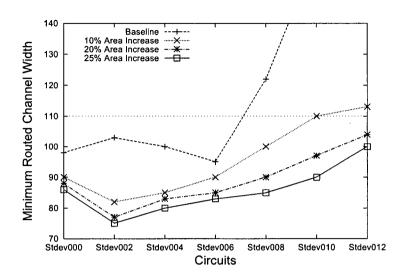

| Figure 6-5: MRCW vs. Stdev Circuit60                                |

| Figure 6-6: Critical Path Delay vs. Channel Width Constraint61      |

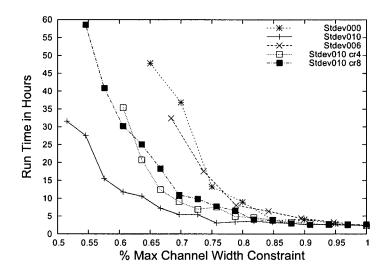

| Figure 6-7: Run Times vs. Channel Width Constraint62                |

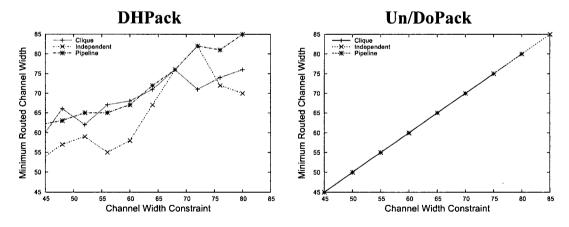

| Figure 6-8: MRCW for DHPack vs. Un/DoPack66                         |

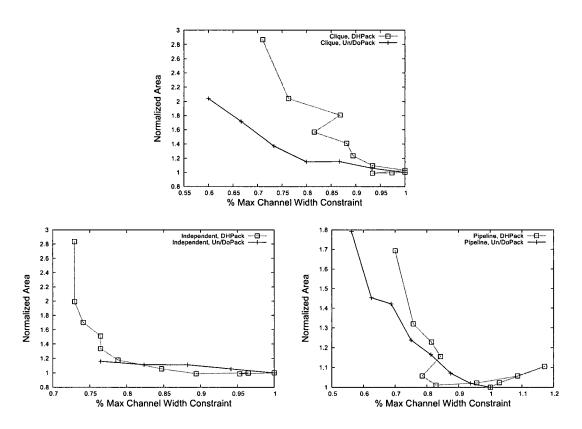

| Figure 6-9: Comparison of Area between DHPack and Un/DoPack67       |

| Figure 7-1: FPGA Architecture with Macro Blocks77                   |

## **GLOSSARY**

Application Specific Integrated Circuit (ASIC):

An integrated circuit intended for a specific use rather than general-purpose use. Once manufactured, the logical function of an ASIC cannot be changed

Basic Logic Element (BLE):

Logic element in an FPGA composed of a K-input

LUT and flip-flop.

Computer Aided Design

(CAD) Tools:

Software automation tools to aid in the design of

electrical systems.

Configurable Logic Block

(CLB):

Logic element in an FPGA composed of 'N' BLEs.

CLB Depopulation:

The process of inserting empty BLEs into a circuit

mapped to a FPGA to reduce the MRCW.

Design Hierarchy Pack

(DHPack):

An FPGA channel width reduction tool which relies on

the design hierarchy of the circuit to identify

congestion regions.

Field Programmable Gate

Array (FPGA):

An integrated circuit that can be programmed, erased and re-programmed again to implement digital logic

functions.

Generate Netlist (GNL):

A synthetic benchmark generator [51].

Interconnect Resource

Aware Clustering (iRAC):

The state of the art FPGA clustering algorithm for

channel width reduction [46].

Intellectual Property Blocks

(IP Blocks):

A reusable unit of logic, cells or layout of an integrated circuit. SoC designs are created by merging IP blocks

that have been pre-designed and pre-tested.

Look Up Table (LUT):

An FPGA element capable of implementing any logical

function of its inputs.

Meta Benchmark Circuits: A synthetic benchmark circuit suite created by stitching

together the 20 largest MCNC benchmark circuits.

Microelectronics

Corporation of North

Carolina (MCNC) Circuits:

A standard set of benchmark circuits used in the FPGA academic community [36].

Minimum Routable Channel Width (MRCW):

The minimum channel width an FPGA must have to route a given circuit.

Non-Recurring Engineering Fees (NRE):

The one time costs of product development. This often includes mask costs and costs of CAD tools in integrated circuit design.

SIS:

A logic synthesis package developed at the University of California at Berkeley which allows interactive optimization of sequential digital circuits.

System-on-Chip (SoC):

A design philosophy which integrates all the components of an electronic system into a single integrated circuit. A SoC design philosophy makes the design of complex systems simpler by merging together pre-existing and pre-tested circuit designs.

**Stdev Benchmark Circuits:**

A synthetic benchmark suite created by cloning the Meta benchmarks. Each circuit in this suite represents a circuit with a varying amount of interconnect variation.

T-VPack:

The most commonly used academic FPGA clustering algorithm.

Un/DoPack:

An FPGA channel width reduction tool that can target hard channel width constraints.

Versatile Place and Route

(VPR):

The most commonly used academic FPGA place and

route tool.

## **ACKNOWLEDGEMENTS**

I would like to thank my academic advisor, Dr. Guy Lemieux for his technical advice throughout my Master's degree. I have learned a great deal about academia and the research world from Guy and I am grateful for his guidance and support.

I would also like to thank the members of the UBC System-on-Chip research group for making my stay an enjoyable one. In particular, I'd like to thank Edmund Lee, Anthony Yu, Victor Aken'Ova, Martin Ma, James Wu, Amit Kedia, Scott Chin and Nathalie Chan for the good times in the lab.

I am grateful for the use of WestGrid<sup>1</sup> computing resources. The types of experiments that I have performed in this thesis would not have been possible without Westgrid.

Finally, I would like to thank my family for all the encouragement and support over the past few years.

<sup>&</sup>lt;sup>1</sup> Westgrid is funded in part by the Canada Foundation for Innovation, Alberta Innovation and Science, BC Advanced Education, and the participating research institutions. WestGrid equipment is provided by IBM, Hewlett Packard and SGI.

## Chapter 1

#### 1 INTRODUCTION

A field- programmable gate array (FPGA) is capable of implementing a large variety of digital logic applications. Typically, FPGAs can be programmed, erased and re-programmed again multiple times. An alternative to FPGAs are application specific integrated circuits (ASICs) which are designed to perform one specific function. ASICs provide much higher speed, density and power characteristics than FPGAs but require very large up-front costs and cannot be changed after the manufacturing process. FPGAs are generally slower, larger and consume more power than their ASIC counterparts, but offer faster time-to-market and are programmable in the field after the manufacturing process. Many digital logic applications would benefit from the high performance characteristics of an ASIC, but these applications don't have the manufacturing volume needed to justify the \$10+ million in computer-aided design (CAD) tools, design and verification costs, and non-recurring engineering (NRE) fees. Because FPGAs are not subject to most of these up-front costs, they are very attractive to low-to-medium density logic and low-to-medium volume designs.

As FPGAs increase in capacity and capability, it has become common to offer separate low-cost and resource-rich families. For a similar number of logic elements, also known as configurable logic blocks (CLBs), the low-cost families often have less

embedded memory, embedded multipliers, and routing tracks. This is demonstrated by Table 1-1, where the low-cost Altera Cyclone family offers significant savings. Unfortunately, some designs may fit within the Cyclone logic and memory capacity limits but not within the routing capacity limits. This can be solved by switching to the resource-rich family (e.g. Altera Stratix) at ~4x the cost. Instead, it is preferable to stay in the low-cost family and use the same or next-larger device (at ~2x cost). To do this, the FPGA computer-aided design (CAD) tools must meet the device routing capacity by targeting a *hard channel width constraint*. Since interconnect use of a design varies spatially with placement, this can be done by spreading out regions of peak demand to use fewer routing tracks but more CLBs.

| Altera Device | Logic Elements | Memory    | Mult. | Routing | Cost  |

|---------------|----------------|-----------|-------|---------|-------|

| Cyclone 1C12  | 12,060         | 239,616   | 0     | 80      | \$56  |

| Stratix 1S10  | 10,570         | 920,448   | 48    | 232     | \$190 |

| Cyclone 1C20  | 20,060         | 294,448   | 0     | 80      | \$100 |

| Stratix 1S20  | 18,460         | 1,669,249 | 80    | 232     | \$350 |

Table 1-1: Features and Costs of Two FPGA Families (from [2], [3], [19])

#### 1.1 Motivation and Objectives

The **minimum routable channel width (MRCW)** of a circuit is defined as the smallest possible channel width a FPGA device must have in order to route that circuit. This thesis presents an algorithmic way of reducing the minimum routable channel width (MRCW) of a logic design by inserting whitespace in the form of empty look-up tables (LUTs) into congested areas. Whitespace is inserted by identifying a congested region of CLBs, unpacking the CLBs into its constituent basic

logic elements (BLEs), and then re-packing these BLEs into more CLBs so they are "less full" than before. This process of inserting whitespace into each CLB is called depopulating.

Note that it is possible to reduce the MRCW of a circuit through clustering. Traditional clustering algorithms, such as T-VPack [6], fully pack the clusters to minimize the total number of CLBs needed. However, DeHon [17] and Tessier [48] have shown that the channel width needs of a circuit can be decreased by packing fewer BLEs into each CLB. The resulting "under-utilization" of CLBs is known as depopulation.

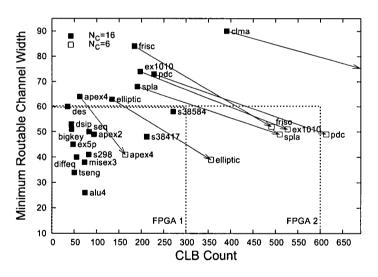

Figure 1-1: Channel Width / CLB Count Tradeoff

To see how depopulation works, consider the two large dashed boxes in Figure 1-1 representing the logic and routing capacities of two FPGA devices. These FPGAs contain 16 BLEs per CLB and 60 wiring tracks per routing channel. The MRCW of 20 MCNC benchmark circuits [36] after clustering (T-VPack [6]) and routing (VPR [6])

are shown. Notice that circuits with similar CLB counts can require vastly different channel widths (varying from 25 to 65). Similar results for industrial benchmarks are shown in [34].

In Figure 1-1, FPGA 1 contains 300 CLBs and can implement all circuits inside its box. In comparison, FPGA 2 has 600 CLBs and the same channel-width constraint of 60 because it is based on the same layout tile. Even though it is larger, FPGA 2 is incapable of realizing any circuits that require a channel width greater than 60, e.g. apex4 or elliptic. After depopulation (limiting to 6 BLEs per CLB), apex4's MRCW shrinks from 62 to 41 tracks. Although the CLB count increases, it still fits into FPGA 1. More importantly, apex4 now has a viable, routed solution. Similarly, some circuits like elliptic can be made to fit FPGA 2.

The problem with depopulation is that it quickly leads to an inflated CLB count. In the example, circuits pdc and clma are too large for FPGA 2. They must be depopulated less to meet the CLB constraint as well. What is needed is a way to depopulate only the routing-congested regions of a circuit so CLB count is inflated as little as possible. Such an approach is important for fitting large System-on-Chip designs onto modern FPGAs.

#### 1.2 Contributions

This thesis presents two FPGA CAD tools that can depopulate an FPGA design to target channel width constraints. The first tool, DHPack, relies on the design hierarchy of the design to detect areas of congestion. Results of this work have been

published at the Design Automation Conference (DAC 2005) [49]. The second tool, Un/DoPack, is an iterative tool designed to target **hard** channel width constraints. A paper based on this work has been submitted to DAC 2006 [50]. The primary application of these tools is to reduce the channel width requirements of a circuit so that it can be mapped to a channel-width constrained FPGA. Rather than depopulate the entire circuit, which would inflate area rather quickly, the tools depopulate smaller regions (possibly entire IP blocks) that are interconnect-intensive.

### 1.3 Thesis Organization

This thesis is organized as follows. Chapter 2 presents an overview of modern mesh based FPGA architectures and the state of the art CAD tools to map circuits to these FPGAs. It also includes some discussion on previous techniques to reduce MRCW. Chapter 3 compares two basic depopulation approaches for channel width reduction. Chapter 4 presents two benchmark suites (Meta and Stdev) that mimic system-on-chip (SoC) designs and discusses the benchmark circuit characteristics that are important for channel width reduction. Chapter 5 presents the FPGA CAD tool DHPack which uses the natural design hierarchy of the circuit to identify high congestion regions. Chapter 6 presents the FPGA CAD tool Un/DoPack which iteratively depopulates circuits to meet hard channel width constraints. Finally, some conclusions are provided in Chapter 7 along with some possible future work.

## Chapter 2

#### 2 BACKGROUND

This chapter begins with an overview of modern FPGA architectures. The two most typical FPGA architectures are mesh-based and hierarchical. Since industrial FPGA vendors typically use mesh-based structures, the architectures and CAD tools discussed in this thesis will only target mesh-based FPGAs. An overview of the current state-of-the-art CAD algorithms that map digital circuits into FPGAs is then provided. The FPGA CAD flow can be split into 5 steps: synthesis, technology mapping, clustering, placement and routing. A survey of the most commonly used tools for each of these 5 steps is provided. The chapter concludes with a discussion on previous methods to reduce MRCW.

#### 2.1 FPGA Architecture

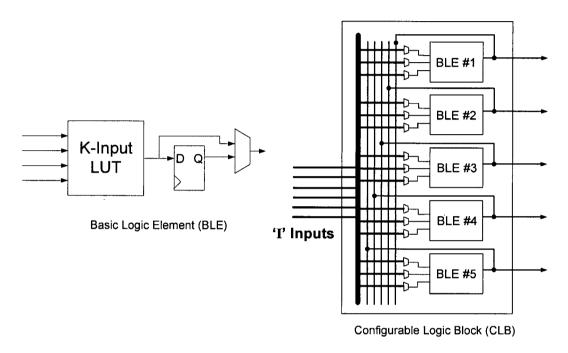

A commercial FPGA family consists of a number of devices, each with a different logic capacity. Figure 2-1 illustrates the logic resources: CLBs and BLEs. A basic logic element (BLE) is composed of a K-input look-up table (LUT) and flip-flop. A K-input LUT has one dedicated output and is capable of implementing any Boolean function of its K-inputs. Logic capacity of an FPGA is measured by the number of BLEs. Alternatively, it can be measured by the number of CLBs, or

configurable logic blocks, which are simply fixed-size clusters of BLEs. Since mesh-based FPGAs are typically laid out in a 2-dimensional structure, device logic capacity can also be expressed by the logical dimensions of the CLB array.

Figure 2-1: BLE and CLB

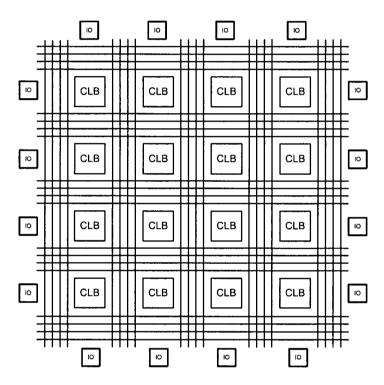

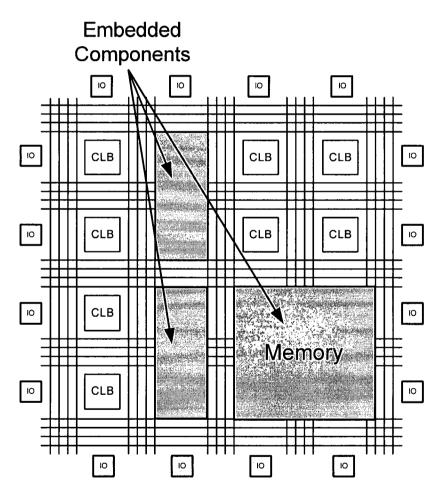

The logic elements in an FPGA are connected through a mesh based programmable interconnect network. A typical mesh based FPGA architecture similar to [2] and [53] is given in Figure 2-2.

The **channel width** of a mesh based FPGA architecture is defined by the number of routing tracks running in each horizontal and vertical channel. In Figure 2-2, the channel width is 4 since there are 4 tracks in each horizontal and vertical channel. This channel width is fixed across an entire FPGA family. The reason it is fixed is that larger sized FPGAs in the same family are created by placing more tiles

on a larger sized die. Since the channel width is a fixed feature on a tile, the inclusion of more tiles has no effect on the channel width of a family. For example, the Altera Cyclone device contains five different options in terms of logic capacity. This is demonstrated in Table 2-1. However each of these devices contains the same channel width constraint of 80 routing tracks per channel.

Figure 2-2: Mesh Based FPGA Architecture

| Altera Device            | EP1C3 | EP1C4 | EP1C6 | EP1C12 | EP1C20 |

|--------------------------|-------|-------|-------|--------|--------|

| Number of LEs            | 2,910 | 4,000 | 5,980 | 12,060 | 20,060 |

| Number of Routing Tracks | 80    | 80    | 80    | 80     | 80     |

Table 2-1: Altera Cyclone Size Options (from [2])

The LUT size, number of BLEs in each CLB and the number of inputs per cluster vary across many different vendors. For all of the experiments performed in the remainder of this thesis, an FPGA architecture based on the parameters given below is used unless otherwise specified. Note that the channel width of the FPGA is left as a variable. The CAD tools described in this thesis attempt to find the minimum possible channel width needed to route a circuit.

- LUT Size (K)= 6

- Cluster Size (N) = 16

- Number of Inputs Per Cluster (I) = 51 = k/2\*(N+1) (from [1])

- Length of Wires (L) = 4

- Switch Block Type  $(SB_{type}) = Subset$

- C-Block Input Connectivity  $(F_{cin}) = 0.366$

- C-Block Output Connectivity  $(F_{cout}) = 0.1$

- C-Block I/O Pad Connectivity  $(F_{cpad}) = 1$

- Fully Buffered Switches

- I/O Ratio = Minimum value to ensure circuit is logic limited

- Process Parameters = 0.18µm TSMC

- Channel Width = Variable

#### 2.2 FPGA CAD Flow

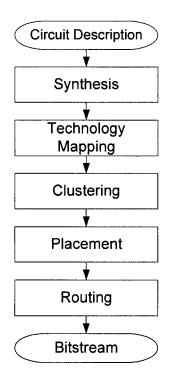

The process of converting a circuit description into a format that can be loaded into an FPGA can be roughly divided into five discrete steps, namely: synthesis, technology mapping, clustering, placement and routing. The final output of FPGA CAD tools is a bitstream that configures the state of the memory bits in an FPGA. The state of these bits determine the logical function that the FPGA implements. Figure 2-3 shows a flowchart of the FPGA CAD flow. The following sections will describe the algorithms that are typically used in each step of the CAD flow.

Figure 2-3: FPGA CAD Flow

#### 2.2.1 Synthesis

Synthesis involves translating a circuit description, traditionally in a hardware description language (HDL) (e.g. VHDL or Verilog), into a gate-level representation. The gate-level representation is a network consisting of Boolean logic gates and flip-flops. There are no FPGA-specific optimizations performed during synthesis since this is normally a technology independent step. Further details concerning synthesis are omitted because it is beyond the scope of this thesis.

#### 2.2.2 Technology Mapping

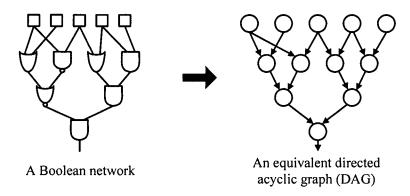

The output from synthesis tools is a circuit description of Boolean logic gates, flip-flops and the wiring connections between these elements. The circuit can also be represented by a directed acyclic graph (DAG). Each of the nodes in the graph represents a gate, flip-flop, primary input or primary output. Each of the wires in the graph represents the connections between the different circuit elements. Figure 2-4 shows an example of a DAG representation of a circuit.

Figure 2-4: Directed Acyclic Graph Representation of a Circuit (from [29])

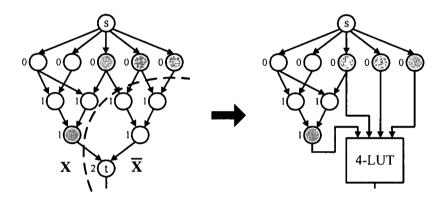

Given a library of "cells", the technology mapping problem can be expressed as finding a network of "cells" that implements the Boolean network. In the FPGA technology mapping problem, the library of "cells" is composed of K-input LUTs and flip-flops. Therefore, FPGA technology mapping involves transforming the Boolean network into K-bounded cells. Each cell can then be implemented as an independent K-LUT. Figure 2-5 shows an example of transforming a Boolean network into K-bounded cells.

Figure 2-5: Example of Technology Mapping (from [29])

Technology mapping algorithms can optimize for a variety of objectives including depth, area or power. The FlowMap algorithm [12] is the most widely used academic tool for FPGA technology mapping. FlowMap was a breakthrough in FPGA technology mapping because it is able to find a depth-optimal solution in polynomial time. FlowMap guarantees depth optimality at the expense of logic duplication. Since the introduction of FlowMap, numerous technology mappers have been designed that optimize for area and run-time while still maintaining the depth-optimality of the

circuit ([13], [14], [15]). A series of technology mapping algorithms that optimize for power ([4], [11], [29]) have recently attracted much interest as well.

For the CAD tools discussed in this thesis, all technology mapping of circuits was performed by running FlowMap [12] for depth optimality and FlowPack [13] for area reduction. The SIS scripts *scipt.rugged* and *script.algebraic* were run and the lower area solution out of the two was chosen. The result of the technology mapping step generates a network of K-bounded LUTs and flip-flops.

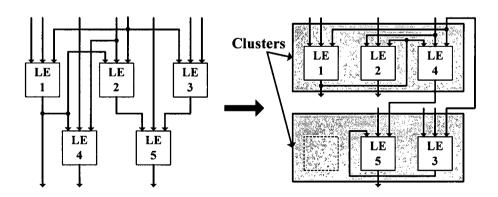

#### 2.2.3 Clustering

The logic elements in a mesh-based FPGA are typically arranged in two levels of hierarchy. The first level consists of basic logic elements (BLEs) which are K-input LUT and flip-flop pairs. The second level hierarchy groups 'N' BLEs together to form configurable logic blocks (CLBs). The clustering phase of the FPGA CAD flow is the process of forming groups of 'N' BLEs. These clusters can then be mapped directly to a logic element on an FPGA. Figure 2-6 shows an example of the clustering process.

Figure 2-6: Example of Clustering (from [29])

Clustering algorithms can be broadly categorized into three general approaches, namely top-down ([20], [22]), depth-optimal ([16], [40], [54]) and bottom-up ([6], [7], [8], [37], [46]). Top-down approaches involves recursively partitioning a circuit into fixed size clusters. Depth-optimal solutions attempt to minimize delay (similar to [12]) at the expense of logic duplication. Bottom-up approaches are generally preferred for FPGA CAD tools because of their fast run times and reasonable timing delays.

Bottom-up approaches build clusters sequentially one at a time. The process starts with choosing a BLE which acts as a cluster seed. BLEs are then greedily selected and added to the cluster based on various attraction functions. The VPack [37] attraction function is based on the number of shared nets between a candidate BLE and the BLEs that are already in the cluster. T-VPack [6] is a timing driven version of VPack which gives added weight to grouping BLEs on the critical path together. RPack [7] improves the routability of a circuit by introducing a new set of routability metrics. RPack significantly reduced the required channel widths required by circuits compared to VPack. T-RPack [8] is a timing driven version of RPack which is similar to T-VPack by giving added weight to grouping BLEs on the critical path. iRAC [46] improves the routability of circuits even further by using an attraction function that attempts to encapsulate as many low fanout nets as possible within a cluster. If a net can be completely encapsulated within a cluster, there is no need to route that net in the external routing network. By encapsulating as many nets as

possible within clusters, routability is improved because there are less external nets to route in total.

For the experimental results discussed in this thesis, a replica of the iRAC algorithm was constructed based upon the description given in [46]. The replica was used because the original tool is no longer available. The replica implements the cluster seed and attraction function of the original iRAC algorithm but omits the Rent based input limiting function. Despite this, the iRAC replica achieves results within 2% of the number of external nets given in [46].

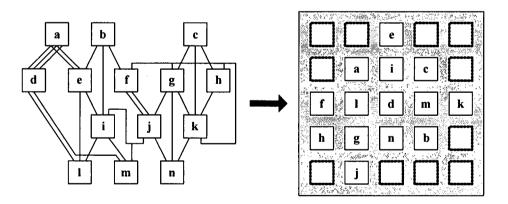

#### 2.2.4 Placement

The placement step in the CAD flow involves placing the clustered netlist on to fixed locations on the FPGA. Figure 2-7 shows an example of the placement problem.

Figure 2-7: Example of Placement (from [29])

Placement algorithms traditionally attempt to minimize routing congestion and critical-path delays. Routing congestion is minimized by arranging the highly

connected blocks close together and critical-path delay is minimized by placing blocks on the critical path close together. Placement techniques can be broadly categorized into three different approaches: min-cut ([18], [24], [43]), analytical ([26], [42], [45]), and simulated annealing ([6], [27], [38]). Although all three methods produce good results, simulated annealing provides the most flexibility for new optimization goals and architectural changes.

Simulated annealing begins with a random initial placement of all the blocks. Pairs of blocks are then randomly swapped repeatedly. After each swap, the quality of the placement solution is analyzed. In VPR [6], the placement quality is determined by the sum of the half-perimeter bounding box of all the nets in the circuit. The probability of accepting a swap is based on the temperature of the simulated annealing schedule. Initially, the temperature is high which results in almost all swaps (good and bad) being accepted. As the temperature is slowly lowered, the probability of accepting a bad swap is reduced. Once the temperature reaches 0, only good swaps are permitted. The process of initially accepting bad swaps allows the placement process to find its way out of local minima in the solution space. For the CAD tools discussed in this thesis, the T-VPlace algorithm in the VPR tool is used unless otherwise specified.

#### **2.2.5 Routing**

The final stage in the FPGA CAD flow is the routing step which connects the placed blocks though the programmable routing network. Connections between wires on an FPGA are formed by using a programmable routing switch. Traditionally, wires

were bi-directional which indicates that tri-state drivers are placed on both ends of a wire. More recently, [33] has suggested that single driver, directional wires improve area and delay. However, since the directional VPR tool was unavailable at the time of this work, a bi-directional model for wiring was used.

Routing techniques can be broadly categorized into two methods, namely two-step routers ([10], [31], [32]) and combined global-detailed ([6], [39], [52]) routers. Two-step routers perform global routing and detailed routing in two discrete steps. Global routing assigns nets to specific channels and logic block pins. After global routing is complete, detailed routing assigns the nets to specific wire segments in its assigned channel. Two-step routers are generally used for ASIC flows and are not normally used for FPGAs because the limited flexibility of the FPGA routing architecture makes detailed routing difficult under global routing constraints. FPGAs use combined global-detailed routers because of the inflexibility of the two-step routers.

The VPR router (combined global-detailed) is based on a modified version of the PathFinder [39] algorithm. Pathfinder is an iterative algorithm which allows nets to share wires in the initial iterations. Successive iterations penalize the use of wires that were shared or used in previous iterations. The penalty factor is continually increased until a routing solution is found where each wire segment has at most one net assigned to it. The VPR router is also timing-driven. This is achieved by assigning the shortest possible paths to critical nets. Other non-timing critical nets may tend to take longer

routes in the presence of congestion. For the CAD tools discussed in this thesis, the T-VRoute algorithm in the VPR tool is used unless otherwise specified.

#### 2.3 Previous Methods to Reduce Channel Width

One of the earliest attempts to balance logic and routing elements to decrease area was performed by DeHon [17]. However, this analysis was performed for an FPGA with a binary tree interconnect structure. In this work, we use a mesh based interconnect which is more representative of commercial FPGAs. Tessier [48] showed that depopulation of clusters can result in reduced MRCW of circuits. The algorithm presented in [48] depopulates each cluster equally so there is a uniform distribution of empty BLEs across the chip. Although this reduces MRCW, it also depopulates regions of the circuit that are not heavily congested. This leads to unnecessary CLB inflation in these regions. The tools presented in this thesis use a different cluster size limit for different partitions of the circuit. This cluster size limit value may vary across the chip such that routing-congested areas are depopulated more.

Singh [46] presented a clustering algorithm (iRAC) which is very effective at reducing channel width. iRAC reduces channel width by identifying low fan-out nets and completely absorbing them into a cluster. This reduces the total number of external nets, hence reducing the MRCW. iRAC also limits the number of inputs to each CLB by using the Rent parameter of the underlying architecture, resulting in solutions that have some depopulation. The tools in this thesis differ from [46] by targeting specific channel-width constraints.

Independence, a FPGA placement tool by Sharma [44], targets hard channel width and array size constraints. It works by using the router tool as an inner loop during placement and runs 10,000 times slower. In comparison, the tools presented in this thesis run much faster and can work with most clustering, placement and routing tools. Also, Independence inserts entire CLBs as whitespace, while the tools in this thesis insert individual BLEs.

## Chapter 3

## 3 METHODS TO REDUCE MINIMUM ROUTABLE CHANNEL WIDTH

This chapter compares two basic techniques for channel width reduction. These methods are input-limiting and BLE-limiting. Results will show that contrary to popular belief (such as results in [46]), input-limiting is not effective at reducing channel width. Instead, BLE-limiting is shown to be much more effective.

## 3.1 Input-Limits vs. BLE-Limits

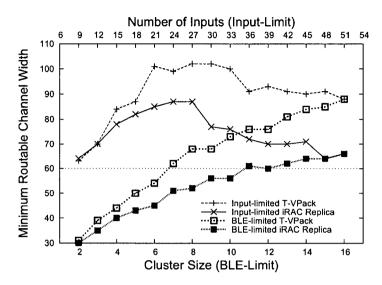

This section evaluates the effectiveness of two different CLB depopulation methods, namely input-limiting and BLE-limiting. The first method, similar to [48], is to strictly limit the number of BLEs that can be packed into a CLB (BLE-limit). The second method, similar to [46], is to strictly limit the number of inputs that can be used on a CLB (input-limit). Figure 3-1 shows the MRCW for circuit **clma** after implementing the two limits in two different clustering algorithms: (T-VPack, iRAC replica). Other circuits produce similar results. For example, a BLE-limit size of 7 would indicate that 9 of the BLEs in each cluster are empty. Alternatively, an input-limit size of 24 indicates that 27 of the inputs in every cluster are left unused.

Figure 3-1: Input- and BLE-Limits during Clustering for Circuit clma

Figure 3-1 shows that the BLE-limit method exhibits a monotonically increasing relationship between the BLE-limit size and the MRCW. Hence, BLE-limit can be effectively used to decrease routed channel widths. Surprisingly, the input-limit approach did not exhibit this same relationship. This contradicts traditional thinking that reducing inputs is an effective way to reduce channel width. This occurs because there are two competing factors that affect the MRCW. As the BLE-limit or input-limit size is decreased, the increase in array size tends to **reduce** the MRCW but the increase in the total number of routable nets tends to **increase** the MRCW. BLE-limiting ensures that the array size increases more quickly than the number of routable nets, leading to a decrease in MRCW. In contrast, for the input-limiting case of Figure 3-1, as the number of used inputs decreases from 51 to 30, the number of routable nets is increasing while the array size remains relatively constant. Effectively, the reduction in the number of inputs is causing poor clustering solutions to be generated (e.g.

increase in total number of routable nets) without any increase in the required array size. Because BLE-limiting is an effective control method for reducing channel width, it is used as the depopulation method for all the depopulation tools discussed in this thesis.

## Chapter 4

### 4 BENCHMARK CIRCUITS

Before the channel width reduction tools are presented, this chapter will discuss the importance of benchmark circuits to channel width reduction tools and present two new synthetic benchmark suites. FPGA researchers need large circuits to investigate new FPGA device architectures and CAD algorithms. However, the gap between the size of real world circuits and those available to the academic community for designing FPGAs continues to grow. Modern, multi-million gate System-on-Chip designs are highly proprietary; hence, they are not commonly available for academic research. Instead, the only designs available are small MCNC benchmark circuits [36] that have been in use since 1993. In an industry where circuit density doubles every 18-24 months, these circuits are rapidly becoming outdated.

A viable alternative to real world circuits is the use of synthetic circuits. Synthetic circuits can be generated using a variety of different methods. This chapter will present two different benchmark suites and discuss the mechanisms used to create the circuits. The first benchmark suite, Meta, was used to test the DHPack depopulation strategy described in Chapter 5. The second benchmark suite, Stdev, was used to test the Un/DoPack depopulation strategy described in Chapter 6.

#### 4.1 Meta Benchmark Circuits

The System-on-Chip (SoC) design philosophy consists of integrating multiple components from different sources into a single chip. For FPGA systems, these components are normally digital intellectual property (IP) blocks. The IP blocks can be widely varied in their function and purpose, and are often developed by different designers. During development, each IP block might be individually placed and routed on an FPGA several times. As well, these different blocks may have different interconnect demands, just like those shown in Figure 1-1.

To mimic a large SoC design, the Meta circuit benchmarks were created by treating the largest 20 MCNC circuits [36] as individual IP blocks of a common SoC and *randomly stitching* them into a single, large Meta circuit. Stitching involves connecting compatible inputs and outputs of the blocks together. Each MCNC circuit is a unique, self-contained function with an appropriate input/output (I/O) count, just like an IP block. Connections between IP blocks are made only at these I/O boundaries and not to internal nodes of the block. Also, some of these MCNC circuits (*e.g.* **bigkey**) have many inputs and outputs, making them similar to "glue logic" that may be used to connect multiple IP blocks together. To avoid creating combinational loops, the stitching process adds a flip-flop to the primary outputs of each MCNC circuit. The IP blocks were stitched together in three different ways to create three different circuits in the Meta benchmark suite:

- Independent: Each primary input and primary output of each IP block remains a primary input and primary output of the Meta circuit. There is no interaction between IP blocks.

- **Pipeline:** The IP blocks are placed in a random, sequential order, each representing stages in a pipeline. Additional (leftover) inputs/outputs between pipeline stages become primary inputs/outputs of the Meta circuit.

- Clique: The outputs of each individual IP block are uniformly distributed to the inputs of all other circuits in the Meta circuit. The connections are made to encourage as much inter-block communication as possible.

When stitching, precise output-to-input connections are randomly assigned once. From this stitching assignment, multiple versions of each benchmark circuit were created by stitching different clustering solutions of each IP block. During stitching, only connections with a fan-out of one are formed. Alternatively, synthetic circuit generating techniques ([23], [28]) could have been used. These techniques are good for cloning existing circuits: they typically work by top-down partitioning or bottom-up clustering of modules and adding nets between the modules while enforcing stochastic interconnect parameters. Unfortunately, we do not have any initial SoC designs to clone. Another synthetic benchmark generator developed by Stroobandt [51] is discussed section 4.2.

When developing the Meta benchmarks, the primary concern was to create large circuits with varying interconnect usage among the IP blocks. The names of the

3 benchmark circuits are **Clique**, **Pipeline** and **Independent**. These benchmark circuits were used to test the DHPack depopulation strategy described in Chapter 5 which requires strict IP block boundary definitions.

### 4.2 Stdev Benchmark Circuits

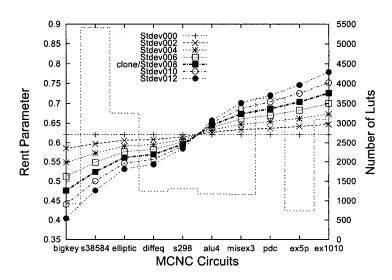

The Meta benchmark suite was created by randomly stitching together existing, smaller benchmarks (MCNC circuits) and treating the smaller circuits as IP blocks. However, the stitching was somewhat unrealistic as a flip-flop was placed at every IP block output to prevent combinational loops. Un/DoPack (the depopulation technique described in Chapter 6) does not have the requirement that the circuit be strictly partitioned into IP blocks. To mimic more realistic benchmark circuits, a synthetic benchmark generator, GNL [51] was used to generate a second benchmark suite. GNL allows benchmarks to be generated hierarchically and allows control over the Rent parameter [30] in each division. GNL is also able to prevent combinational loops and can place limits on the maximum depth of a circuit. The key parameter of GNL is that it is able to create synthetic benchmarks based on Rent's rule. Empirical evidence has shown that most circuits follow Rent's rule. Since it is not known how much interconnect variation is present in real world circuits, GNL gives provides a mechanism to generate circuits that have a controllable amount of interconnect variation.

The GNL synthetic circuits generated consist of two levels of hierarchy. The root level defines the overall structure of the circuit. This level includes the total

number of logic cells in the circuit, as well as a required input and output count. The number of primary inputs and outputs were defined as 240 and 120 respectively. The root level is defined such that it is made up of twenty leafs that mimic the 20 largest MCNC circuits [36]. Each leaf represents an IP block with a specific Rent parameter. The Rent parameter and number of logic blocks of each IP block was chosen to match the same parameter values as each corresponding MCNC circuit. These Rent numbers were extracted from [46]. The number of inputs and outputs for each sub-circuit was not defined, thus allowing GNL to randomly stitch each Rent region together to form the overall circuit. The standard deviation of the Rent parameter for the 20 MCNC circuits was calculated to be 0.08 and the average value was 0.62. Using these Rent values, we produced a *clone* of the Meta circuit and named it Stdev008. To create a family of circuits, a linear interpolation scheme was applied to keep the same overall mean, but to vary the standard deviation to produce 4 smaller values and 2 larger ones. Figure 4-1 shows a graphical representation of our linear interpolation scheme. For clarity, only 10 of the 20 MCNC circuits are shown.

Figure 4-1: Rent Linear Interpolation for GNL Benchmark Circuits

Each line in Figure 4-1 represents a benchmark circuit for a specific standard deviation of the Rent parameters. Circuit Stdev000 contains 20 IP blocks each having the identical Rent parameter of 0.62, producing a flat line. The average Rent parameter is a simple average of the sub-circuits and is not weighted by the sub-circuit size. Three other circuits with standard deviations 0.02, 0.04, 0.06 were created between the flat line and bold **clone** circuit line. Circuits Stdev010 and Stdev012 were obtained by extrapolating the Rent parameter 2 steps farther. The "bar line" in Figure 4-1 shows the size of each of the IP blocks in terms of the number of LUTs; the size does not depend on the Rent parameter.

The resulting circuits had standard deviations of 0.0, 0.02, 0.04, 0.06, 0.08, 0.10 and 0.12 in their Rent value and contained 51,900 to 52,200 6-input BLEs. The names of the circuits are **Stdev000, Stdev002, Stdev004, Stdev006, Stdev008/clone, Stdev010** and **Stdev012**. The linear interpolation scheme will

be used to show that a large amount of depopulation is necessary to reduce the MRCW in circuits with a low standard deviation. This is because the circuit is uniform, and routing resources demands should be fairly consistent across the entire circuit. In contrast, with a high standard deviation, routing resource demands should be non-uniform, thus allowing the depopulation scheme to reduce the routing demands of high Rent regions. Appendix A gives complete information on the size and Rent parameter of the IP blocks in the Stdev benchmark circuits.

It was not possible to use the Stdev circuits to test DHPack (Chapter 5) because DHPack requires that the IP block boundaries be strictly defined. Even though it is possible to specify the Rent parameter of each IP block, GNL is still random in nature. Therefore, there is no method of determining where the boundaries of these IP blocks are located. The Stdev benchmarks will be used primarily in Chapter 6 to demonstrate the significance of interconnect variation in channel width reduction strategies. Experimental results will show that Un/DoPack is effective at reducing MRCW for the Stdev circuits and the Meta circuits regardless of their interconnect variation. However, the amount of interconnect variation has a direct affect on the overall area increase and run time of this tool.

# Chapter 5

# 5 CHANNEL WIDTH REDUCTION USING DESIGN HIERARCHY PACKING: DHPACK

This chapter describes a non-uniform depopulation technique (DHPack) that uses the natural design hierarchy of the benchmark circuits to identify depopulation regions. DHPack requires that the benchmark circuits have clearly defined IP block boundaries. Since the Meta benchmarks (Section 4.1) were created from a strict design hierarchy, they were ideal for evaluating DHPack. The Meta circuits were formed by stitching together individual clustering solutions of each IP block. This allows DHPack to depopulate only the routing-intensive blocks. Clustering individually preserves each IP block in a form that more closely resembles how each was developed and tested by separate designers prior to integration.

This chapter begins with an explanation of the DHPack algorithm. An analysis of the experimental results will then show that this technique is effective at reducing the minimum routable channel width (MRCW) of the benchmark circuits. The chapter concludes with a discussion of some of the limitations of this technique. Note that this technique is described in [49].

# 5.1 DHPack - Depopulation Strategy

**Design Hierarchy Pack** (DHPack) uses the design hierarchy of the benchmark circuit to identify depopulation regions. This approach enforces BLE-limits during clustering, profiles each IP block's channel width needs for different depopulation levels, and chooses the one with the fewest CLBs that meet a given channel width constraint. Results will show that a large, flat area region exists where CLB count can be safely traded off for channel width.

For FPGA designs that contain multiple IP blocks, it was hypothesized that the channel width needed to route the entire circuit will be similar to the IP block with the highest channel width needs. That is, the other IP blocks do not temper the channel width needs of the hard-to-route IP block. Although this is just a first-order approximation that ignores the effects of inter-block communication, results show that it is a good estimate of the final routed channel width. Hence, the first step of DHPack is to develop a channel-width profile of each IP block. Then, DHPack selects the depopulation level needed by each IP block to meet the overall channel-width constraint. DHPack is described in pseudo-code in Figure 5-1. Each of the 4 different steps of DHPack is discussed in the following sections.

```

Routed Circuit DHPack ( circuit, channel width constraint,

cluster size ) {

IP Blocks[] = Decompose Circuit into IP Blocks( circuit );

// Step 1: Generate Channel Width Profile

foreach (IP Block) {

for(LimitSize=1; LimitSize<=cluster size; LimitSize++) {</pre>

cluster_ip_blk = Cluster( IP Block, LimitSize );

routed ip blk = Place&Route( cluster ip blk );

CW[IP Block][LimitSize] = get CW( routed ip blk );

}

// Step 2: Calculate Maximal Cluster Sizes

foreach (IP_Block) {

Limit = Cluster Size;

while ( CW[IP Block] [Limit] > channel width constraint &&

Limit > 0) {

Limit--;

if( Limit == 0 ) {

return( NO SOLN );

} else {

BLE_Limit[IP_Block] = Limit;

}

// Step 3: Cluster IP Blocks

foreach (IP_Block) {

Clustered Soln[IP Block] = Cluster( IP Block,

BLE Limit[IP Block]);

// Step 4: Stitch Circuit back together & P&R

Clustered_Circuit = Stitch_Circuit(circuit, Clustered_Soln[]);

Routed Circuit = Place&Route( Clustered Circuit );

return ( Routed_Circuit )

```

Figure 5-1: Pseudo-code for DHPack Flow

# 5.1.1 Steps 1,2: Channel Width Profiling and BLE-Limits

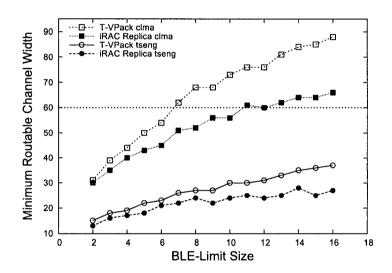

The channel width profile of each IP block in the Meta circuits were created by placing and routing each IP block independently of each other for all possible BLE-limit sizes. Figure 5-2 shows the channel width needs of two IP blocks for BLE-limits 2 to 16. A BLE-limit size of 16 indicates that the clustering tool has no restriction on the number of BLEs that can be used in a cluster. Conversely, a BLE-limit size of 2 indicates that a maximum of 2 BLEs can be used per cluster.

Figure 5-2: Channel Width Profile of IP Blocks clma/tseng

If a channel-width constraint of 60 is imposed using T-VPack, a BLE-limit size of 6 is required to route clma. We say 6 is the **maximal cluster size** for clma at the given channel-width constraint. In contrast, the maximal cluster size for tseng is 16 for the same constraint. Once a channel width profile is created for each IP block in the design, the maximal cluster size for each IP block can be calculated given a channel width constraint.

For the 3 Meta circuits, 11 different channel-width constraints were set and the maximal cluster sizes were determined for each IP block using both T-VPack and the iRAC replica. The maximal cluster sizes using T-VPack are shown in Table 5-1. Channel-width constraints below 45 were not possible because some circuits could not be depopulated enough to route with such a small channel width. Channel-width constraints greater than 95 were not interesting because all CLBs were fully populated. A table with the maximal cluster sizes using the iRAC replica is also given in Table 5-2.

|          | Channel-Width Constraint |    |    |    |    |    |    |    |      |    |    |

|----------|--------------------------|----|----|----|----|----|----|----|------|----|----|

| Circuit  | 95                       | 90 | 85 | 80 | 75 | 70 | 65 | 60 | 55   | 50 | 45 |

| alu4     | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 16 | 16 |

| apex2    | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 16 | 12 |

| apex4    | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 14 | - 10 | 9  | 8  |

| bigkey   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 14 | 9  |

| clma     | 16                       | 15 | 14 | 12 | 11 | 10 | 8  | 6  | 5    | 5  | 3  |

| des      | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 15 | 4    | 3  | 2  |

| diffeq   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 16 | 16 |

| dsip     | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 13 | 6  |

| elliptic | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 14 | 11   | 9  | 7  |

| ex1010   | 16                       | 16 | 16 | 16 | 16 | 15 | 12 | 9  | 7    | 5  | 4  |

| ex5p     | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 16 | 15 |

| frisc    | 16                       | 16 | 16 | 15 | 13 | 10 | 9  | 7  | 7    | 5  | 4  |

| misex3   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 16 | 16 |

| pdc      | 16                       | 16 | 16 | 16 | 16 | 14 | 12 | 9  | 7    | 6  | 4  |

| s298     | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 16 | 16 |

| s38417   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 16 | 14 |

| s38584   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 13   | 11 | 9  |

| seq      | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 15 | 11 |

| spla     | 16                       | 16 | 16 | 16 | 16 | 16 | 13 | 11 | 8    | 6  | 5  |

| tseng    | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16   | 16 | 16 |

Table 5-1: Maximal BLE-Limit Sizes from T-VPack

|          | Channel-Width Constraint |    |    |    |    |    |    |    |    |    |    |

|----------|--------------------------|----|----|----|----|----|----|----|----|----|----|

| Circuit  | 80                       | 76 | 72 | 68 | 64 | 60 | 56 | 52 | 48 | 44 | 40 |

| alu4     | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| apex2    | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 14 | 9  |

| apex4    | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 13 | 11 | 8  | 5  |

| bigkey   | 16                       | 16 | 16 | 16 | 16 | 16 | 15 | 15 | 15 | 15 | 12 |

| clma     | 16                       | 16 | 16 | 16 | 13 | 10 | 8  | 7  | 6  | 5  | 3  |

| des      | 16                       | 16 | 16 | 16 | 16 | 16 | 15 | 15 | 15 | 15 | 15 |

| diffeq   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 14 | 12 | 8  |

| dsip     | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 15 | 15 | 15 | 15 |

| elliptic | 16                       | 15 | 12 | 11 | 9  | 8  | 6  | 5  | 5  | 4  | 3  |

| ex1010   | 16                       | 16 | 16 | 16 | 15 | 11 | 8  | 8  | 5  | 4  | 3  |

| ex5p     | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 11 |

| frisc    | 16                       | 16 | 16 | 16 | 14 | 10 | 9  | 8  | 8  | 6  | 4  |

| misex3   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| pdc      | 16                       | 16 | 16 | 16 | 12 | 10 | 9  | 6  | 5  | 5  | 3  |

| s298     | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| s38417   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| s38584   | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 15 |

| seq      | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 12 | 8  |

| spla     | 16                       | 16 | 16 | 16 | 16 | 14 | 11 | 9  | 7  | 5  | 4  |

| tseng    | 16                       | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

Table 5-2: Maximal BLE-Limit Sizes from iRAC

# 5.1.2 Steps 3,4: Cluster IP blocks and Stitch Circuit

Once the maximal cluster sizes have been determined for a given channel width constraint, DHPack selects the individual clustering solutions for each IP block and stitches the circuit back together. When clustering the IP blocks, there are two choices for the BLE-limit size with a given channel-width constraint:

• Uniform (Minimum) Cluster Size: Depopulate all of the IP blocks to the same BLE-limit size, the minimum of the maximal cluster sizes for all IP blocks. This is similar to [48] which uses uniform depopulation of clusters.

• Non-uniform (Maximal) Cluster Size: Depopulate the IP blocks by different amounts, using the maximal cluster size for each one.

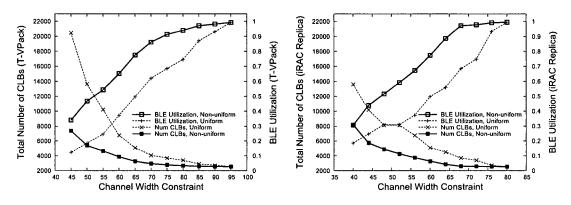

For each of the 11 channel width constraints in Table 5-1, we generated a **Uniform** and **Non-uniform** clustered version of Meta using T-VPack. This was also repeated for the iRAC replica algorithm. As discussed earlier, the **Uniform** version will contain more CLBs than necessary and results in lower BLE utilization. Figure 5-3 shows the total CLBs and BLE utilization obtained from the Meta circuits produced from T-VPack and iRAC replica clustering.

Figure 5-3: DHPack CLB Count and BLE Utilization

It is evident from Figure 5-3 that **Non-uniform** clustering of the IP blocks significantly improves both BLE utilization and reduces CLB count as the channel width constraint is decreased

# 5.2 Experimental Results

In total, 66 Meta netlists were created and placed using VPR (11 channel width constraints, 3 Meta circuits, using 2 clustering tools (T-VPack and the iRAC replica)).

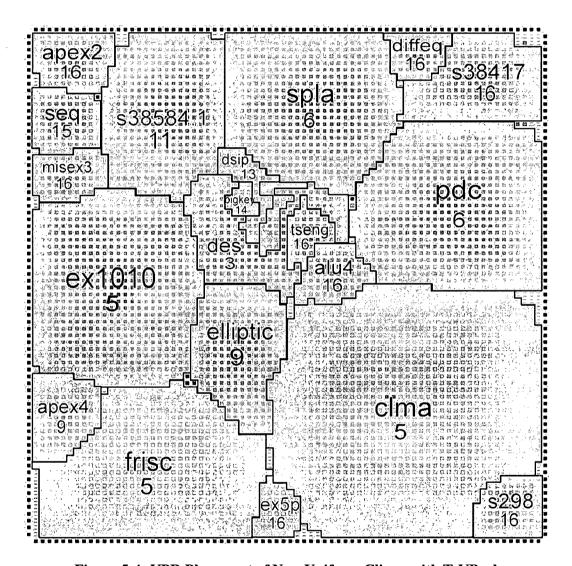

Figure 5-4 shows a post place and route screen shot from VPR of the Meta circuit Clique with a channel width constraint of 50. The screen shot has been edited to show the location of the IP blocks.

Figure 5-4: VPR Placement of Non-Uniform Clique with T-VPack

The numbers below each IP block indicate the BLE-limit size of that IP block.

Analyzing the place and route results from the Meta circuits led to two key observations.

**Observation 1:** VPR placer successfully groups IP blocks from a random initial placement

It was expected that large SoC designs will be floor planned prior to the final placement process, but VPR does not support floor planning. Instead, it starts with a random placement of all CLBs and uses simulated-annealing to find a minimum-cost placement. Interestingly, VPR was able to generate solutions that appear to be floor planned. This reduced the need to impose an artificial floor plan on the design a priori.

**Observation 2:** VPR router confirms the MRCW of a Meta circuit is dominated by a few IP blocks

Figure 5-4 illustrates that only a few IP blocks (i.e. des, clma, frisc, ex1010) needed a large amount of depopulation for the given channel width constraint. It is these IP blocks that dominate the channel width needs of the entire circuit.

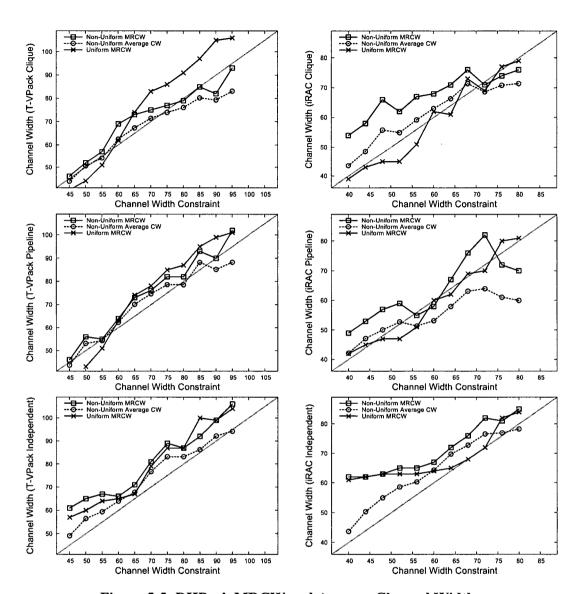

While routing, the channel width was continuously reduced until the circuit became un-routable. This produced the final minimum routable channel width (MRCW). It is a minimum because the FPGA architecture must have at least this minimum channel width in order for the circuit to be routable. Routing results for the 6 Meta circuits are shown in Figure 5-5. A comprehensive table of results is given in Appendix B.

Figure 5-5: DHPack MRCW and Average Channel Width

The results show that the non-uniform MRCW was usually higher than what was imposed by the channel-width constraint. In contrast, the uniform MRCW results track the channel width constraint more closely. However, this comes at the expense of area which is shown in Figure 5-6. The high MRCW values for some Independent and Pipeline cases involving iRAC led to further investigation. It was found that on

these occasions, the I/O intensive IP blocks were strongly attracted to the I/O padframe during placement and stretched into highly rectangular shapes. This caused severe localized congestion in the routing channels nearest to the padframe. Figure 5-5 also shows the average channel width of all routing channels. The average channel width tracks the channel-width constraint much more closely, suggesting that the approach is viable if the I/O padframe congestion can be reduced.

Figure 5-6 shows the normalized area results of the 3 Meta circuits for non-uniform and uniform depopulation cases. For the non-uniform case, the final routed area shows a substantially flat area response (small area increases) for channel widths of 70-95 for T-VPack and 65-80 for iRAC. Channel width decreases of up to 50% are possible with much larger area increases. In comparison, the uniform area curves increases much more quickly as the channel width constraint is decreased. This suggests that uniform depopulation unnecessarily depopulates in low-congestion areas.

Figure 5-6: DHPack Routed Area Factor

Table 5-3 shows a summary of the channel width decreases that were obtained for each Meta benchmark circuit. Small MRCW decreases of 23%/13% for T-

VPack/iRAC are possible with 4%/3% increase in area. Larger MRCW decreases of 39%/29% are possible with 166%/146% increase in area.

|             | Clustering | Channel Width Changes |           |      |      |           |       |  |  |

|-------------|------------|-----------------------|-----------|------|------|-----------|-------|--|--|

| Circuit     | Tool       | CW                    | Avg<br>CW | Area | CW   | Avg<br>CW | Area  |  |  |

| Clique      | T-VPack    | -19%                  | -14%      | +6%  | -50% | -47%      | +129% |  |  |

|             | iRAC Rep.  | -7%                   | -4%       | -1%  | -29% | -39%      | +187% |  |  |

| Pipeline    | T-VPack    | -25%                  | -15%      | +2%  | -55% | -51%      | +184% |  |  |

|             | iRAC Rep.  | -17%                  | -11%      | +1%  | -30% | -30%      | +69%  |  |  |

| Independent | T-VPack    | -24%                  | -19%      | +3%  | -42% | -48%      | +184% |  |  |

|             | iRAC Rep.  | -15%                  | -11%      | +6%  | -27% | -44%      | +183% |  |  |

| Arithmetic  | T-VPack    | -23%                  | -16%      | +4%  | -49% | -49%      | +166% |  |  |

| Mean        | iRAC Rep.  | -13%                  | -9%       | +3%  | -29% | -38%      | +146% |  |  |

Table 5-3: Reductions in Channel Width for DHPack

In some cases, only small decreases in MRCW were achievable. As explained earlier, this is because some IP blocks introduce heavy congestion at the periphery due to high I/O padframe needs. Table 5-3 also shows the average channel width required. In the cases where I/O congestion occurs, the average channel width tracks the channel width constraint more closely. This suggests that if the I/O congestion can be somehow eliminated the MRCW will also decrease and track the channel width constraint more closely.

Figure 5-7 shows the critical-path delay results. It was initially expected critical-path delay would increase as more depopulation is applied. Critical-path delay does seem to follow this trend, but it tends to "jump around". This delay "noise" appears to result from instability in the placement. As depopulation is applied, the VPR placement engine keeps IP blocks together, but sometimes their location in the floor plan is shifted significantly relative to other IP blocks. This caused the critical

path to sometimes relocate from within an IP block (which gradually degrades as depopulation is applied) to connections between IP blocks (which introduces large delay jumps). Imposing a pre-defined floor plan may help reduce this "noise" in large designs.

Figure 5-7: DHPack Critical-Path Delay

Figure 5-7 also shows the average wirelength per net. Average wirelength per net increased as more depopulation is applied (e.g. channel width constraint reduced). This is expected because an increase in CLB count must also increase the average distance a net must traverse. Also, depopulating will cause connections that were previously internal to a CLB (hence, ignored) to become external nets with a small measurable distance. This slightly tempers the increase in average wirelength. Note

that iRAC replica produces a higher average wirelength than T-VPack. However, the total wirelength was lower and the critical-path delay results were similar.

# 5.3 Experimental Conclusions

This chapter has proposed a system-level technique for mapping large system-on-chip (SoC) designs to channel-width constrained FPGAs. In particular, the method helps fit hard-to-route circuits into FPGAs that have narrow channel widths at the expense of using more CLBs. Since larger devices with more CLBs are usually available, this is a practical trade-off.

Results have shown that depopulating CLBs (e.g. not filling them to capacity) is a very effective way to reduce channel width needs of a circuit. It is important to apply non-uniform depopulation when clustering. Otherwise, area increases very rapidly and limits the usefulness of the approach. It was shown that channel width reduction can be achieved by selectively depopulating parts of a large circuit that would otherwise have routing congestion. The most routing-intensive IP blocks are depopulated until the routing demands of those blocks are comparable to the demands of the other blocks. On average, small MRCW decreases of 23%/13% for T-VPack/iRAC are possible with 4%/3% increases in area. Large MRCW decreases of 39%/29% are possible with 166%/146% increases in area. Although this is a high area cost, it may be the only viable solution in a real FPGA device where hard channel-width constraints are imposed. By purchasing an FPGA device with higher logic capacity, designs which are otherwise un-routable can be made routable.

# 5.4 Technique Limitations and Future Work

This section will discuss some of the limitations of DHPack and some possible directions for future work.

# 5.4.1 I/O Padframe Congestion

The main reason why DHPack was not able to track the channel width constraint for large channel width decreases is because some IP blocks stretched into highly rectangular shapes along the I/O padframe causing congestion hotspots along the channel adjacent to the I/Os. Xilinx FPGAs have added additional routing resources to the I/O channel that runs in between the I/O pads and the logic blocks so that I/O pad placement does not impact routability and speed [47]. Hallschmid [21] also investigated the impact the aspect ratio of a circuit has on the required channel width. [21] suggests that a square aspect ratio generates the lowest channel widths and that larger aspect ratios increase the required channel width because the majority of the signals run along the tracks in the longer dimension. Table 5-3 demonstrated that the *average* channel width tracked the channel width constraint more closely than the MRCW. This suggests that if the channels adjacent to the I/O padframe were larger relative to the rest of the chip, channel width reductions could be improved. Another alternative is to tune the placement algorithms to avoid creating this congestion at all. These techniques need further investigation.

### 5.4.2 IP Block Granularity Too Coarse

DHPack is dependent on the design having a well-defined IP block partitioning. Often, SoC designs have multiple levels of hierarchy which makes it difficult to choose appropriate boundaries. DHPack does not allow the exploration of other design partitions. A more efficient partitioning of the circuit that does not rely on the design hierarchy may more accurately identify high congestion regions. This issue is addressed in Chapter 6 which presents a CAD tool (Un/DoPack) that does not rely on design hierarchy information.

### **5.4.3 Hard Channel Width Constraints**

Even though a channel width constraint is an input parameter, DHPack may generate a routed solution that exceeds the constraint. In practice, industrial FPGAs have hard channel width constraints and routed solutions that exceed the constraint by even 1 track are not routable. Un/DoPack in Chapter 6 addresses this limitation by iterating to meet hard channel width constraints.

# 5.4.4 Congestion Profile Run Time Long

The run time to create the congestion profile of each IP block can be very time consuming. In our Meta circuit example, each of the 20 IP blocks needed to be placed and routed individually for BLE-limit size 2 to 16 (15\*20=300 place and route executions). It may be argued that since each IP block is assigned to a different engineer that this channel width profiling must be done before integration into the

overall system. Nonetheless, this profiling step will increase the total CAD time significantly.

# Chapter 6

# 6 CHANNEL WIDTH REDUCTION USING AUTOMATED CONGESTION IDENTIFICATION: UN/DOPACK

This chapter describes a depopulation technique (Un/DoPack) that iteratively applies non-uniform depopulation on a circuit until a given channel width constraint is met. The main difference between Un/DoPack and DHPack is that Un/DoPack is a multi-pass technique whereas DHPack is single-pass. Un/DoPack does not have the requirement that the design hierarchy be known a priori. It can be applied on any circuit irrespective of whether the design hierarchy is known or not.

This chapter begins by describing the Un/DoPack algorithm including a detailed discussion of each step of the CAD flow. The experimental results will show that Un/DoPack is effective at reducing channel width. The results will also highlight the importance of interconnect variation in benchmark circuits for determining the device channel width in FPGA architecture design. Finally, a comparison between DHPack and Un/DoPack is made followed by some of the limitations of this technique.

# 6.1 Un/DoPack - Depopulation Strategy

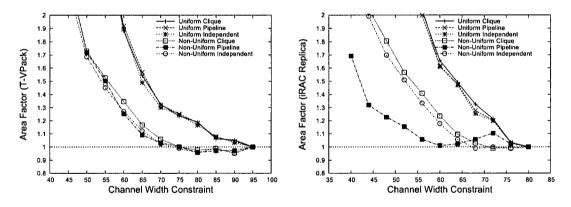

Figure 6-1 shows a flowchart of the Un/DoPack algorithm.

Figure 6-1: Un/DoPack CAD Flow

Un/DoPack can be roughly divided into 4 steps. Each of these steps are highlighted in Figure 6-1 and discussed below.

# 6.1.1 Step 1: Traditional SIS/VPR Flow

The first step is highlighted in the shaded portion of Figure 6-1. This step is the traditional academic FPGA CAD flow which uses SIS / FlowMap [12] and VPR [6] to synthesize, cluster, place and route a circuit. If the traditional CAD flow fails to produce a routed solution given a fixed channel width constraint, the iterative portion of Un/DoPack is invoked to reduce the MRCW.

There are four inputs to Un/DoPack: the circuit description, the architecture description, the channel width constraint and the maximum array size (logic capacity constraint). Traditionally, VPR performs a binary search on the device channel width until the MRCW is found. Un/DoPack does not perform this binary search but requires the user to specify a hard channel width constraint. This has many practical applications since industrial FPGAs have hard channel width constraints as well. The iterative portion of Un/DoPack is invoked only if the routed solution does not meet the given channel width constraint and the logic capacity of the FPGA will not be exceeded through depopulation.

### 6.1.2 Step 2: UnPack - Congestion Calculator

The second step (UnPack) determines which portion of the circuit to depopulate, calculates the amount of depopulation required as a new cluster size

constraint (BLE-limit size), and un-packs the BLEs. A smaller BLE-limit size constraint ensures the new CLBs will be "less full" than before.

Following a failed routing attempt, UnPack creates a congestion map based on the final routed solution. The congestion map is created by *labeling* each CLB with the maximum of the required channel width in each of the four channel segments adjacent to the CLB. Some wiring tracks may have multiple nets assigned to it from the failed routing solution. This is acceptable as the required channel width is estimated by counting the total number of nets **traveling** through the channel segment.

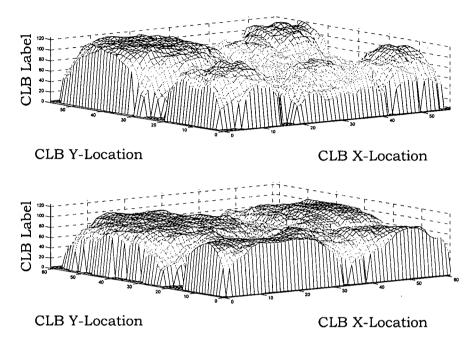

Figure 6-2 shows a sample 3-D congestion map of circuit Stdev008 before (top) and after (bottom) Un/DoPack meets a channel width constraint of 100. The x-y coordinates indicate the CLB locations and the z coordinate indicates the CLB congestion label. The peak / avg / stddev of channel utilization were 120 / 79.4 / 26.9 tracks before Un/DoPack, and 100 / 79.2 / 19.6 afterwards.

Figure 6-2: Congestion Map Before and After Un/DoPack

From Figure 6-2, it is observed that both the peak and variation of CLB labels were both decreased.

The depopulation region center is determined by finding the largest label in the congestion map. In the case of a tie, the CLB that is closest to the center of the map is chosen as the depopulation center. Two different methods were considered to determine how large the depopulation region is and how much to depopulate the region by.

1. **Coarse Grained:** A circle is drawn around the depopulation center with a radius of 1/4 the logical dimension of the array. For example, in a 19x19 CLB grid, the region radius would be floor(1/4\*19)=4. All CLBs within the drawn circle are inserted into the depopulation region. The new BLE-limit size is

determined such that the increase in the total number of CLBs will fill an entire new row/column in the *entire array*.

2. **Fine Grained:** A circle is drawn around the depopulation center with a possible radius of 1/4, 1/5, 1/6 or 1/8 the logical dimension of the array. The new cluster size is determined so that the increase in the total number of CLBs will fill an entire row/column in *just the depopulation region*.

The coarse grained approach increases the array size by one in the x and y direction in every iteration. In comparison, the fine grained approach grows the array size much more slowly as there is no guarantee that enough new CLBs will be created to fill an entire new row/column in the array after each iteration.

# 6.1.3 Step 3: DoPack - Incremental Re-Cluster

The third step (DoPack) performs incremental re-clustering of the depopulated region with the smaller BLE-limit size constraint. It re-clusters the BLEs from the depopulation region identified by UnPack and leaves all other CLBs outside of this region untouched. UnPack provides DoPack with the new BLE-limit size limit to use, which guarantees the production of more CLBs. This is crucial: by using more CLBs, the congested region can span more routing channels to obtain more total routing tracks. This tool can use any existing clustering method (e.g. T-VPack [6], T-RPack [8], iRAC [46]) as the underlying packing engine since the only changing constraint is the BLE-limit size.

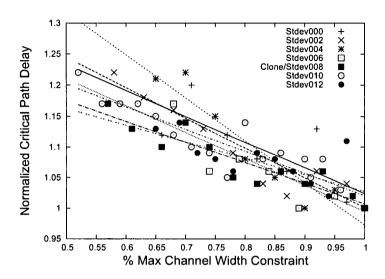

# 6.1.4 Step 4: Placement and Routing