## OVNI: (Object Virtual Network Integrator) A New Fast Algorithm for the Simulation of Very Large Electric Networks in Real Time

by

LUIS RAFAEL LINARES-ROJAS

Elec. Eng., Universidad Central de Venezuela, Caracas, Venezuela, 1981 M.A.Sc., The University of British Columbia, Vancouver, Canada, 1993

#### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

#### THE REQUIREMENTS FOR THE DEGREE OF

#### DOCTOR OF PHILOSOPHY

in

THE FACULTY OF GRADUATE STUDIES

(Department of Electrical & Computer Engineering)

We accept this thesis as conforming to the required standard

#### THE UNIVERSITY OF BRITISH COLUMBIA

August 2000

© Luis Rafael Linares-Rojas, 2000

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

#### Department of ELECTRICAL AND COMPUTER ENGINEERING

The University of British Columbia Vancouver, Canada

Date AUG. 31, 2000

#### ABSTRACT

A portable fast algorithm for solving power electric and electronic networks, and its implementation in the real-time simulator OVNI, are introduced. The implementation of OVNI, object virtual network integrator, on an off-the-shelf hardware platform, a 400 MHz Pentium-II workstation is presented. Simplified fast-models, based on those used by the EMTP<sup>1</sup>, are included for the network elements: lumped resistors, capacitors, inductors -both linear and nonlinear- and a constant parameters transmission lines model. Real-time models for HVDC rectifying and inverting bridges, and for the corresponding PIcontrollers, using node hiding, were created specially for OVNI and reported in this thesis. Core saturation and zero sequence flux in three phase core transformers are modelled. Fast non-linear models are included for current and potential transformers. A fast modelling scheme to account for switching operations is presented, and its successful implementation on an industrial product, reported. Multilayer segmentation of the network, topological segmentation followed by MATE<sup>2</sup> segmentation, the node hiding technique, and a history sources limited encapsulation scheme are introduced. Two fast asynchronous commutation modelling techniques  $-DSDI^3$  and  $BIFE^4$  to eliminate spikes and numerical oscillations are introduced. Industrial real-time test cases are included for power system protective relays, and for high-voltage DC bridges and their corresponding controllers.

<sup>&</sup>lt;sup>1</sup> Acronym for Electromagnetic Transients Program.

<sup>&</sup>lt;sup>2</sup> Multi-Area Thevenin Equivalent.

<sup>&</sup>lt;sup>3</sup> Double Step, Double Interpolation.

<sup>&</sup>lt;sup>4</sup> Backward Interpolation, Forward Extrapolation.

### CONTENTS

| Abstract  | •••••••••••••••••••••••••••••••••••••••                         | ii             |

|-----------|-----------------------------------------------------------------|----------------|

| Contents  | 3                                                               | iii            |

| List of T | ables                                                           | x              |

| List of F | igures                                                          | xi             |

| Preface   |                                                                 | . <b>x</b> xii |

| Acknow    | ledgements                                                      | xxv            |

| Dedicati  | on                                                              | xxvii          |

| Part I    | Motivation                                                      | 1              |

| 1. Intr   | oduction                                                        | 2              |

| 1.1       | Research Claim and Contributions.                               | 9              |

| Part II   | The Problem                                                     | 10             |

| 2. The    | Problem                                                         | 11             |

| 2.1       | Real-Time Simulations                                           | 11             |

| 2.2       | Digital Real-Time Simulations [1]                               | 12             |

| 2.3       | Frequency Bandwidth, Integration Rule, and Accuracy Limitations | 13             |

| 2.4       | Hard Real Time versus Soft Real Time Simulations                | 15             |

| 2.5       | Network Size. Critical Complexity Network, CCN                  | 16             |

|           |                                                                 |                |

| Part III  | I The Solution                                                  | 19             |

| 3. Inte   | gration Rules in OVNI                                           | 20             |

| 3.1       | Introduction                                                    | 20             |

| 3.2       | Accuracy and Stability                                          | 21             |

| 3.3       | Frequency Response [2]                                          | 21             |

| 3.4       | Choosing OVNI's rule                                            | 23             |

|           | 3.4.1 Calviño's second order rule                               | 25             |

Contents

|    |      | 3.4.2    | Trapezoidal versus backward Euler's          | 25 |

|----|------|----------|----------------------------------------------|----|

|    |      | 3.4.3    | Backward Euler's, a "lossy" rule             | 29 |

|    | 3.5  | Improv   | ved performance of OVNI and backward Euler's | 30 |

|    | 3.6  | A sing   | le-phase power system test case              | 30 |

| 4. | Digi | tal Solu | ntion, Element Models                        | 36 |

|    | 4.1  |          | on versus Simulation                         | 36 |

|    | 4.2  | Genera   | al purpose ODE-solvers                       | 36 |

|    | 4.3  | Discre   | tizing the Network, not the Equations        | 37 |

|    | 4.4  | Discre   | te-time model for an Element [3]             | 38 |

|    | 4.5  | Basic    | models in the prototype                      | 40 |

|    |      | 4.5.1    | On Notation                                  | 41 |

|    |      | 4.5.2    | Lumped Elements [3, 4]                       | 41 |

|    |      | 4.5.3    | Transmission Lines $[3, 5]$                  | 42 |

|    |      | 4.5.4    | Single-phase non-linear core Transformer     | 49 |

|    |      | 4.5.5    | Three-phase non-linear core Transformer      | 49 |

|    |      | 4.5.6    | Switches                                     | 49 |

|    |      | 4.5.7    | HVDC Modules                                 | 50 |

|    |      | 4.5.8    | HVDC-current-loop Controller                 | 50 |

|    |      | 4.5.9    | Metal Oxide Varistors (MOV)                  | 51 |

|    |      | 4.5.10   | Measuring Transformers, ITs                  | 52 |

| 5. | Segr | nentatio | on and OVNI                                  | 54 |

|    | 5.1  | Introd   | uction                                       | 54 |

|    | 5.2  | The Ta   | asks of the Simulator                        | 54 |

|    | 5.3  | Precal   | culation of Network Matrices                 | 57 |

|    | 5.4  | The C    | omplexity Index, a metric                    | 58 |

|    | 5.5  |          | ty and the Solution                          | 58 |

|    | 5.6  |          | et Impera. Segmentation                      | 59 |

|    | 5.7  |          | pgical Segmentation                          | 60 |

iv

Contents

|    | 5.8           | The Need for Topological Independent Segmentation, forwarding |     |

|----|---------------|---------------------------------------------------------------|-----|

|    |               | MATE [6]                                                      | 63  |

|    | 5.9           | On Notation                                                   | 67  |

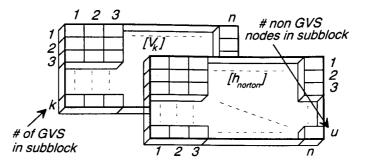

|    | 5.10          | Multi-Area Thevenin Equivalent, MATE                          | 67  |

|    | 5.11          | MATE and Diakoptics [7, 8]                                    | 73  |

|    | 5.12          | MATE and the Compensation Method                              | 74  |

|    | 5.13          | Node Hiding and Element Models                                | 74  |

|    | 5.14          | Node Hiding. A numerical example                              | 77  |

| 6. | Sour          | rces, Links and Expanded MATE                                 | 82  |

|    | 6.1           | Introduction                                                  | 82  |

|    | 6.2           | Precalculation of Source Values                               | 82  |

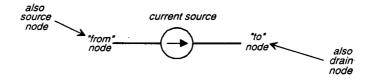

|    | 6.3           | Current Sources                                               | 85  |

|    | 6.4           | Voltage Sources                                               | 86  |

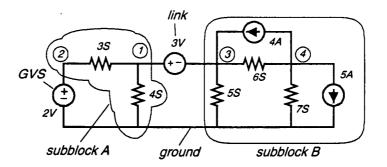

|    |               | 6.4.1 Grounded Voltage Sources — GVS                          | 86  |

|    |               | 6.4.2 An example on Grounded Sources, MATE versus Norton      | 88  |

|    |               | 6.4.3 Ungrounded Voltage Sources, UVS                         | 90  |

|    |               | 6.4.4 Voltage Sources "Ownership"                             | 91  |

|    | 6.5           | Extended MATE                                                 | 92  |

|    | -             | 6.5.1 Extended MATE: A numerical example                      | 94  |

| 7. | Swit          | tches and Asynchronous Commutation                            | 98  |

|    | $7.1^{\circ}$ | Introduction                                                  | 98  |

|    | 7.2           | Switch Closing, Collapsing Nodes                              | 99  |

|    | 7.3           | Expanding a System of Linear Equations                        | 01  |

|    | 7.4           | Closing a Switch without collapsing a Node                    | 02  |

|    |               | 7.4.1 A Numerical Example                                     | 03  |

|    | 7.5           | Switch openings                                               | .04 |

|    | 7.6           | Asynchronous Commutation in OVNI                              | 07  |

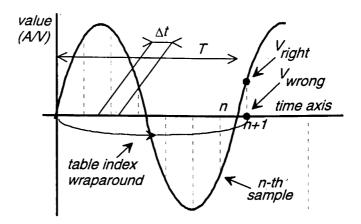

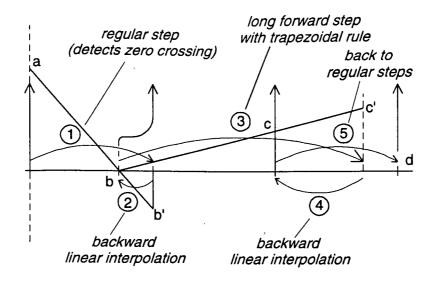

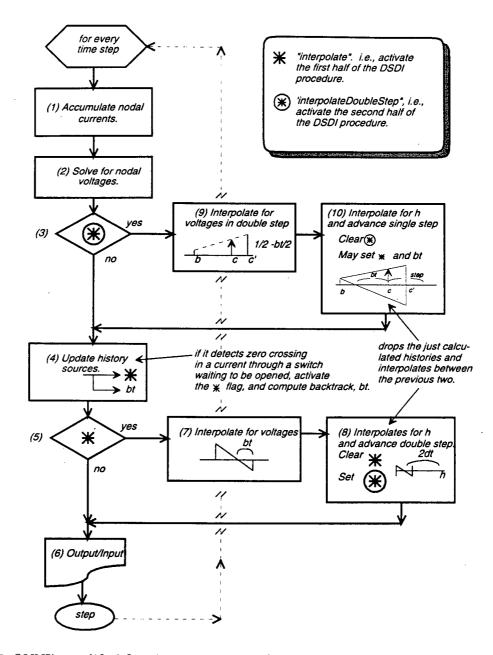

|    |               | 7.6.1 Double Step-Double Interpolation, DSDI                  | .09 |

| -  | 7.7           | DSDI's OVNI Modified Tasks Schedule                           | 10  |

Contents

|    | 7.8    | Single Step and Double Step Interpolation Details                      | 114 |

|----|--------|------------------------------------------------------------------------|-----|

| Pa | ert IV | OVNI Element Models                                                    | 117 |

| 8. | OVI    | VI Element Models                                                      | 118 |

|    | 8.1    | Introduction                                                           | 118 |

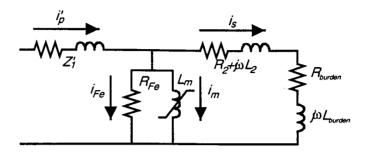

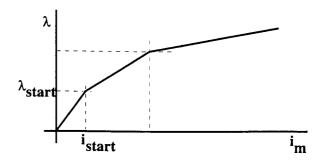

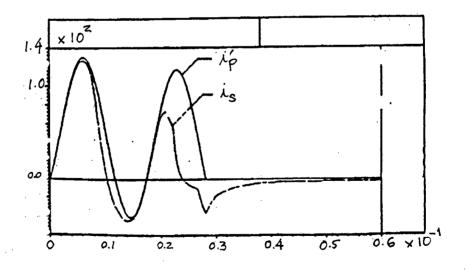

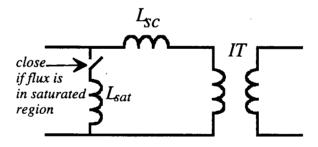

|    | 8.2    | Current Transformers                                                   | 118 |

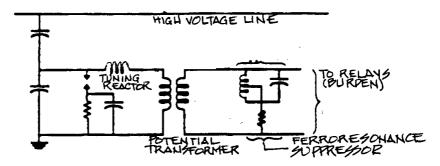

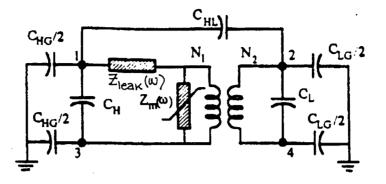

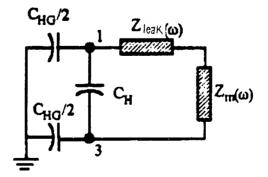

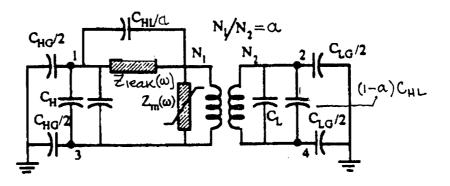

|    | 8.3    | Coupling-Capacitor Voltage Transformers                                | 124 |

|    |        | 8.3.1 Potential transformer and reactors                               | 124 |

|    |        | 8.3.2 Simplified equivalent circuit                                    | 126 |

|    |        | 8.3.3 CCVT model for real-time simulation                              | 127 |

|    |        | 8.3.4 Potential Transformer Model, PT                                  | 128 |

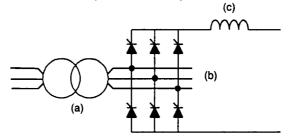

| 9. | The    | HVDC Model                                                             | 132 |

|    | 9.1    | Introduction                                                           | 132 |

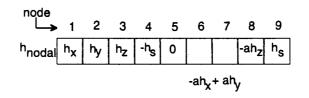

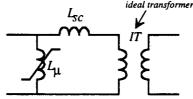

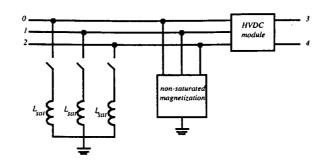

|    | 9.2    | The three-phase linear transformer model                               | 133 |

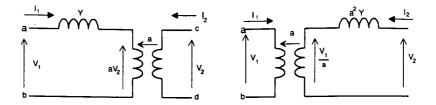

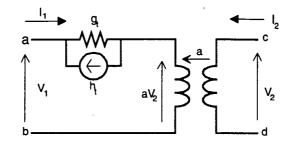

|    |        | 9.2.1 Single-phase transformer model                                   | 133 |

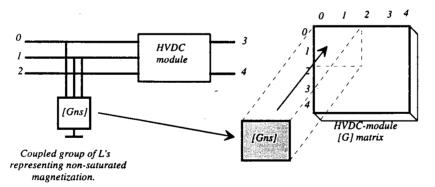

|    |        | 9.2.2 The three-phase transformer matrix/model                         | 136 |

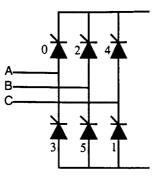

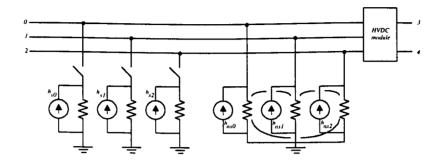

|    |        | 9.2.3 Adding the 6-valve bridge and the smoothing reactor $\therefore$ | 139 |

|    | 9.3    | History sources in the hvdc-module                                     | 141 |

|    |        | 9.3.1 Examples                                                         | 142 |

|    | 9.4    | Hvdc matrices                                                          | 142 |

|    | 9.5    | Interface of the hvdc model and OVNI                                   | 144 |

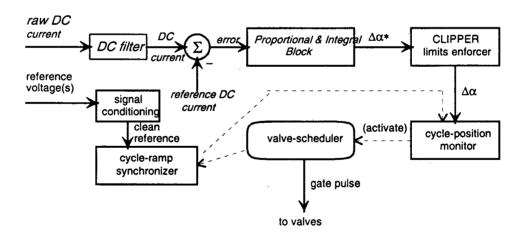

| 10 | . HVI  | OC-bridge Controller                                                   | 146 |

|    | 10.1   | Block View of the Controller                                           | 146 |

|    | 10.2   | Stage One: The DC filter                                               | 147 |

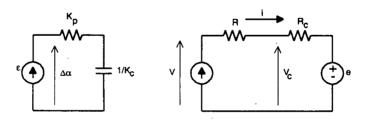

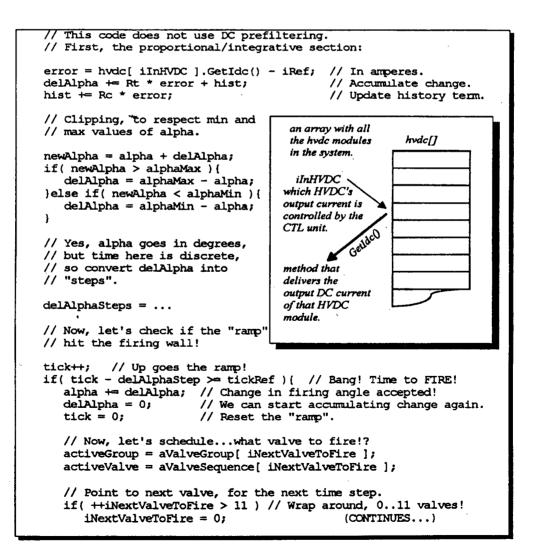

|    | 10.3   | Proportional-Integrative Block                                         | 148 |

|    | 10.4   | Cycle position monitor and the Valve Scheduler                         | 150 |

|    |        | Cycle Ramp Synchronizer                                                | 154 |

|    | 10.6   | Modulating the firing angle                                            | 156 |

| Contents                                                                     |   |     |

|------------------------------------------------------------------------------|---|-----|

| 10.7 Filtering the angle reference voltage                                   |   | 158 |

| 1. Modelling saturation in power transformers                                |   | 161 |

| 11.1 Saturation in single phase units                                        |   | 161 |

| 11.2 Saturation in three-phase units                                         |   | 162 |

| 11.3 Keeping track of a phase-leg's flux                                     |   | 164 |

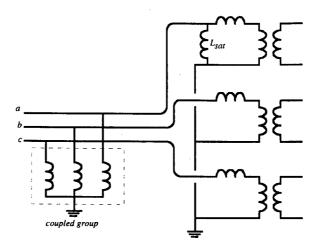

| 11.4 Modification of the HVDC-module model to include saturation             | L | 165 |

| 11.5 History sources introduced by magnetization modelling                   |   | 168 |

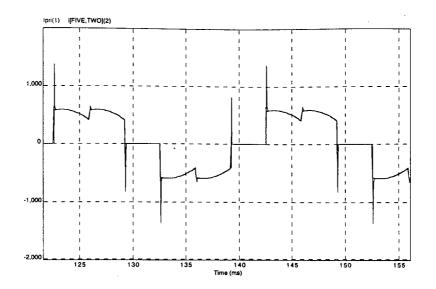

| 11.6 Effect of the saturation modelling in the primary current               | • | 169 |

|                                                                              |   |     |

| Part V Implementation                                                        |   | 171 |

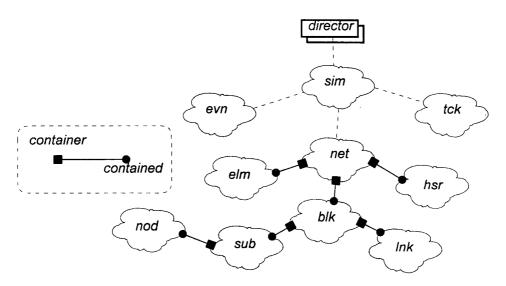

| 2. OVNI, the simulator's engine                                              |   | 172 |

| 12.1 Introduction                                                            |   | 172 |

| 12.2 Input Data File                                                         |   | 172 |

| 12.3 Names in OVNI                                                           | • | 173 |

| 12.4 From nodes to the network                                               | • | 174 |

| 12.5 Classes in OVNI                                                         |   | 178 |

| 12.5.1 The Element Class, $elm_t$                                            |   | 178 |

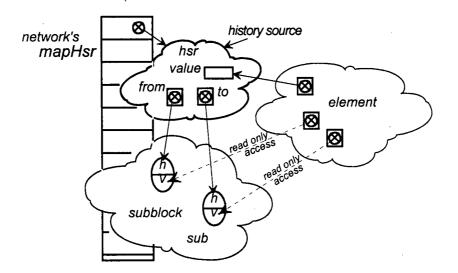

| 12.5.2 The history source class, $hsr_t$                                     | • | 180 |

| 12.5.3 The subblock class, $sub_t \ldots \ldots \ldots \ldots \ldots \ldots$ |   | 181 |

| 12.5.4 The block class, $blk_t$                                              |   | 181 |

| 12.5.5 The clock object, tck                                                 |   | 182 |

| 12.5.6 The simulation object, sim                                            |   | 183 |

| 12.5.7 The network class, net                                                |   | 183 |

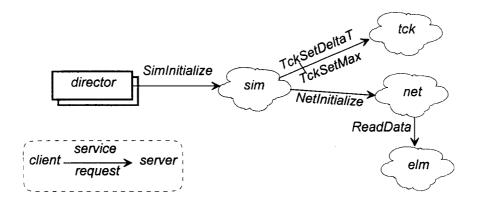

| 12.6 How classes within OVNI relate to each other                            |   | 184 |

| 12.7 Main tasks of the simulator's engine                                    |   | 184 |

| 12.7.1 Initialization                                                        |   | 185 |

| 12.7.2 Simulating the case                                                   |   | 185 |

| 13. OVPP, The Preprocessor                                                                                         | 89  |

|--------------------------------------------------------------------------------------------------------------------|-----|

| 13.1 Introduction $\ldots$        | 89  |

| 13.2 The Preprocessor Input File                                                                                   | 89  |

| 13.2.1 General Data                                                                                                | 90  |

| 13.2.2 Lumped Elements                                                                                             | 90  |

| 13.2.3 Intrablock "links" and Switches $\ldots$ $\ldots$ $\ldots$ 1                                                | 91  |

| 13.2.4 Transmission Lines $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                                                  | 93  |

| 13.2.5 Grounded Voltage Sources                                                                                    | 94  |

| 13.2.6 High Voltage DC rectifier/inverter, HVDC                                                                    | 194 |

| 13.2.7 HVDC Controllers                                                                                            | 196 |

| 13.3 Classes in the Preprocessor                                                                                   | 197 |

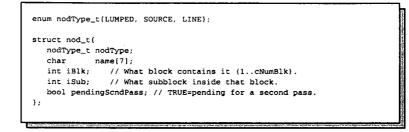

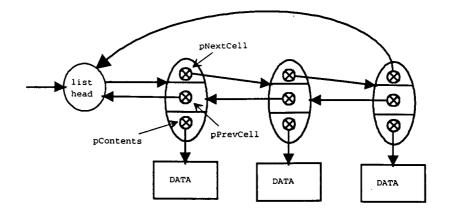

| 13.3.1 The list Class $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                 | 198 |

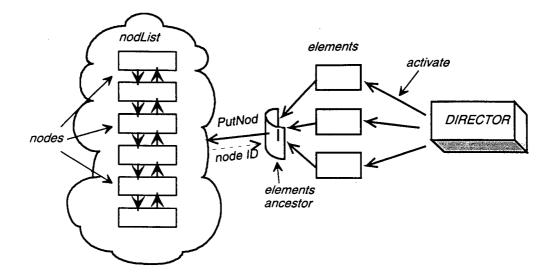

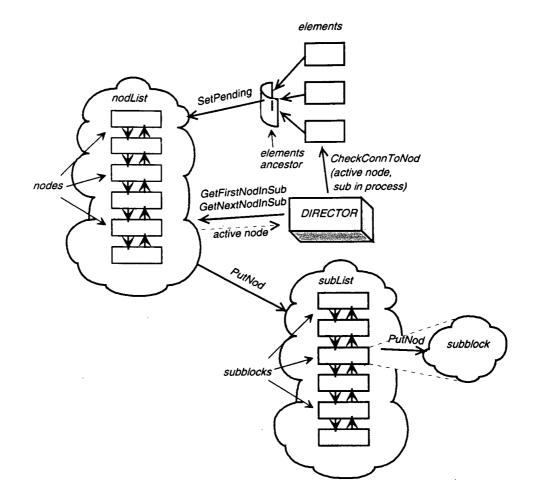

| 13.3.2 The $nodList_t$ class $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                          | 198 |

| 13.3.3 The sub_t class $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                       | 199 |

| 13.3.4 The subblock list, $subList_t$ , class $\ldots$ $\ldots$ $\ldots$ $\ldots$                                  | 199 |

| 13.3.5 The $blk_t$ class                                                                                           | 199 |

| 13.3.6 The block list, $blkList_t$ , class $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 200 |

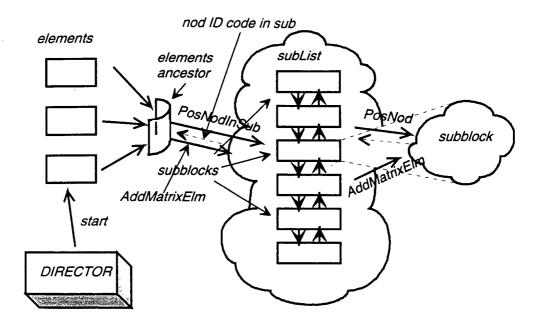

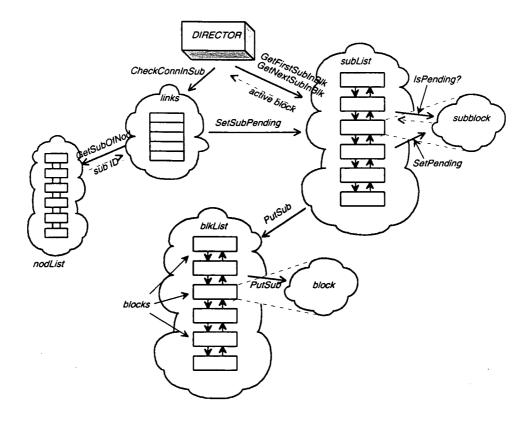

| 13.4 Main Tasks of the Preprocessor                                                                                | 201 |

| 13.4.1 Creation of a list of all the nodes $\ldots$ $\ldots$ $\ldots$ $\ldots$                                     | 202 |

| 13.4.2 Grouping Subblocks                                                                                          | 204 |

| 13.4.3 Calculate Subblock Matrices                                                                                 | 206 |

| 13.4.4 Grouping Blocks                                                                                             | 208 |

|                                                                                                                    |     |

| Part VI Validation                                                                                                 | 209 |

| 14. Validation Tests                                                                                               | 210 |

| 14.1 Introduction                                                                                                  | 210 |

| 14.2 Integration Issues                                                                                            | 211 |

| 14.3 Asynchronous Commutation                                                                                      | 212 |

| 14.4 Speed                                                                                                         | 215 |

| •                                                                                                                  |     |

-

Contents

## viii

|                   | Contents                            |     |

|-------------------|-------------------------------------|-----|

|                   |                                     |     |

| 14.4.1 R          | elay Testing                        | 215 |

| 14.4.2 H          | VDC Systems                         | 216 |

| 14.4.3 M          | ATE vs. Conventional Solution       | 217 |

| 14.4.4 C          | holesky vs. LU Decomposition        | 219 |

| 14.5 Accuracy     |                                     | 222 |

| 14.5.1 H          | VDC Module and its controller model | 222 |

| 14.5.2 R          | elay Testing                        | 237 |

|                   |                                     |     |

| Part VII Conclu   | isions                              | 242 |

| 15. Conclusions a | nd Future Work                      | 243 |

| 15.1 Future w     | ork                                 | 245 |

.

-

## LIST OF TABLES

| 9.1  | (Matrix "node") Connection nodes for transformers $x$ , $y$ , and $z$ .     |     |

|------|-----------------------------------------------------------------------------|-----|

|      | Rows are the transformers, and columns are the nodes                        | 138 |

| 14.1 | Solution time, per integration step, in microseconds                        | 216 |

| 14.2 | Solution time (in microseconds) $\dots$ with the MATE segmentation          |     |

|      | algorithm.                                                                  | 218 |

| 14.3 | Solution times $\dots$ with standard unsegmented algorithm, $\dots$ $\dots$ | 219 |

| 14.4 | Solution times of Cholesky method versus LU                                 | 221 |

| 14.5 | Solution time for a single-block network using precalculation               |     |

|      | for the link matrices.                                                      | 221 |

## LIST OF FIGURES

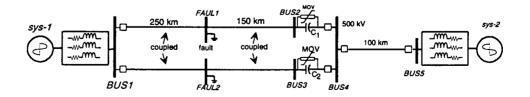

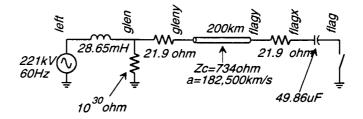

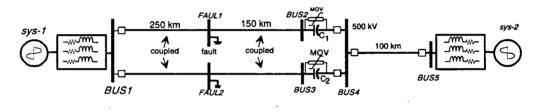

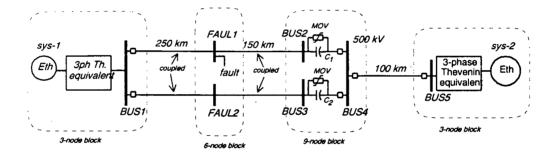

| 1  | An HVDC test case.                                                                                            | 4  |

|----|---------------------------------------------------------------------------------------------------------------|----|

| 2  | A protective relay test case.                                                                                 | 5  |

| 3  | Multilayer segmentation: Topological segmentation, followed by                                                |    |

|    | MATE-Diakoptics Segmentation.                                                                                 | 6  |

| 4  | All element models look and behave the same from the point of                                                 |    |

|    | view of the simulator's core.                                                                                 | 8  |

| 5  | Front end and back end interfaces to OVNI's core                                                              | 9  |

| 6  | An observer watching over and controlling a system                                                            | 11 |

| 7  | From discrete to continuous, through $\ensuremath{D}\xspace/\ensuremath{A}\xspace$ converters and amplifiers. | 12 |

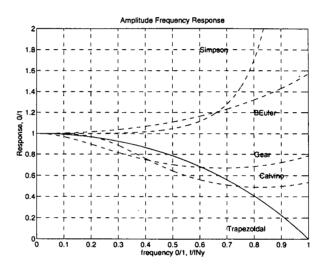

| 8  | Magnitude distortion introduced by Trapezoidal rule at frequen-                                               |    |

|    | cies up to $40\%$ the Nyquist's. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                 | 14 |

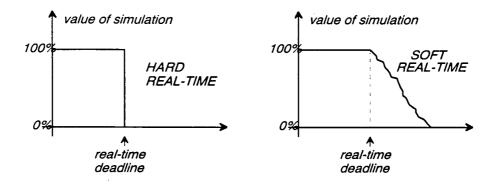

| 9  | Usefulness of the simulation results for: a) a hard real time sim-                                            |    |

|    | ulation; b) a soft real time simulation.                                                                      | 15 |

| 10 | Typical configuration of power networks used in protective relay                                              |    |

|    | testing                                                                                                       | 16 |

| 11 | Critical Complexity Network targeted for relay testing. It in-                                                |    |

|    | cludes two multicircuit transmission links, and MOV protection.                                               | 16 |

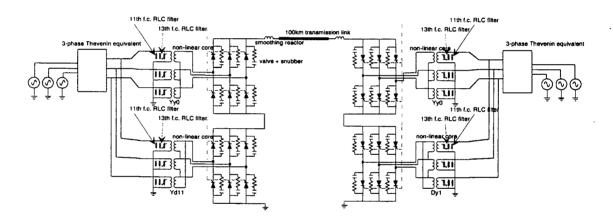

| 12 | Target Network for HVDC controllers testing. The controllers                                                  |    |

|    | triggering the gate signals, used in tuning the simulator, are not                                            |    |

|    | shown, but were included in the simulation.                                                                   | 17 |

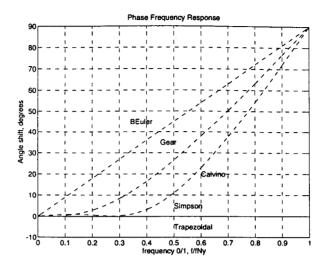

| 13 | Frequency response, magnitude, for the rules: trapezoidal, back-                                              |    |

|    | ward Euler's, Simpson's, Gear's second order, Calviño's second                                                |    |

|    | order                                                                                                         | 23 |

| 14 | Frequency response, phase shift, for the rules: trapezoidal, back-                                           |    |

|----|--------------------------------------------------------------------------------------------------------------|----|

|    | ward Euler's, Simpson's, Gear's second order, Calviño's second                                               |    |

|    | order                                                                                                        | 24 |

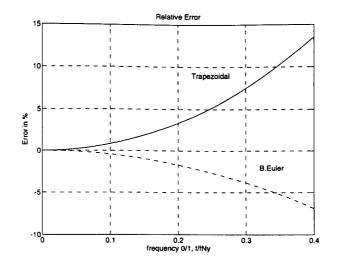

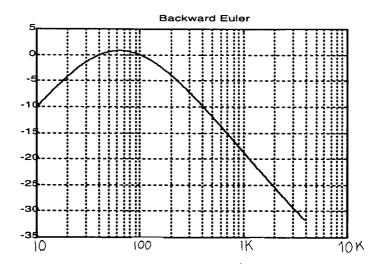

| 15 | Error in magnitude introduced by trapezoidal and Backward Eu-                                                |    |

|    | ler's rule, up to 40% of the Nyquist's frequency.                                                            | 26 |

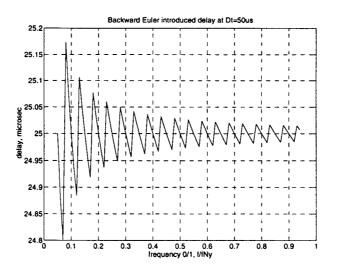

| 16 | Time delay introduced by backward Euler's rule at each frequency                                             |    |

|    | up to Nyquist's                                                                                              | 28 |

| 17 | Single phase power system with a short circuit on the receiving                                              |    |

|    | end, to test the different integration rules.                                                                | 31 |

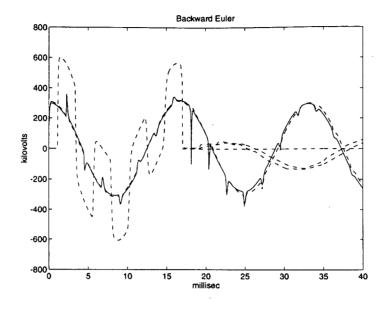

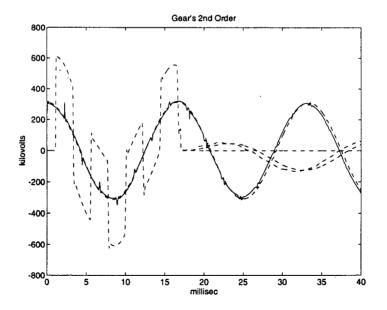

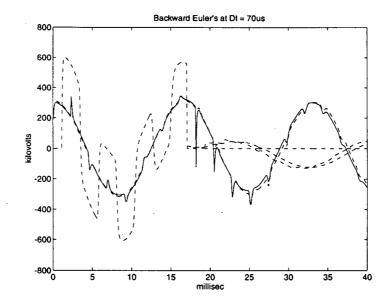

| 18 | Solution obtained by the EMTP with the CDA option activated                                                  |    |

|    | with an integration step $\Delta t = 50 \ \mu s.$                                                            | 32 |

| 19 | Solution obtained by the EMTP with the CDA option activated                                                  |    |

|    | with an integration step $\Delta t = 70 \ \mu s. \ \ldots \ \ldots \ \ldots \ \ldots$                        | 32 |

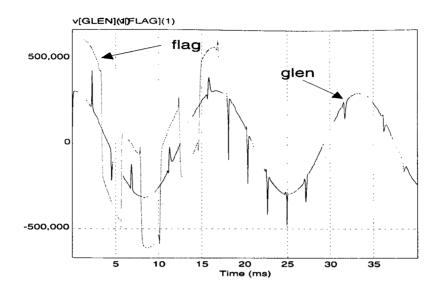

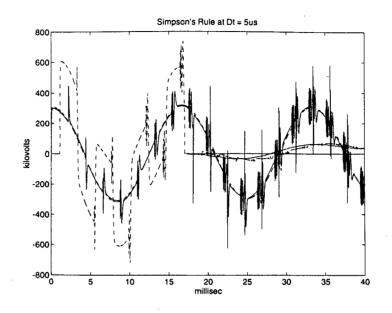

| 20 | Simpson's rule solution with $\Delta t = 5\mu s$ . Voltages at all the nodes                                 | •  |

|    | in the network in Fig. 17                                                                                    | 33 |

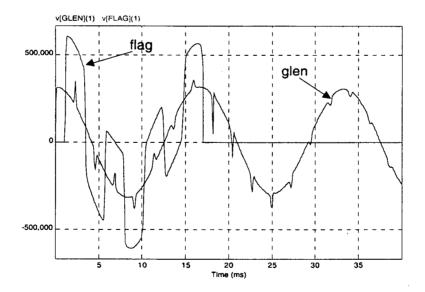

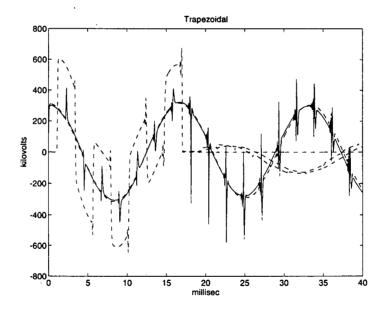

| 21 | Trapezoidal rule solution with $\Delta t = 50 \mu s$ . Voltages at all the                                   |    |

|    | nodes in the network in Fig. 17                                                                              | 33 |

| 22 | Backward Euler's rule solution with $\Delta t = 50 \mu s$ . Voltages at all                                  |    |

|    | the nodes in the network in Fig. 17                                                                          | 34 |

| 23 | Gear's second order rule solution with $\Delta t = 50 \mu s$ . Voltages at all                               |    |

|    | the nodes in the network in Fig. 17                                                                          | 34 |

| 24 | Backward Euler's rule solution at an expanded integration step.                                              |    |

|    | $\Delta t = 70 \ \mu s. \ \ldots \ $ | 35 |

| 25 | A test case for relay testing                                                                                | 37 |

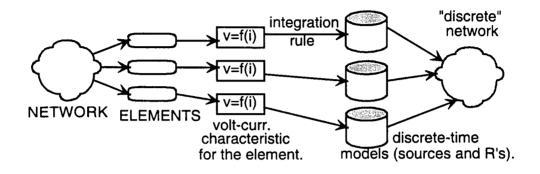

| 26 | Discretization process.                                                                                      | 38 |

| 27 | a) Lumped inductor, and b) its discrete time domain model cor-                                               |    |

|    | responding to the trapezoidal integration rule                                                               | 39 |

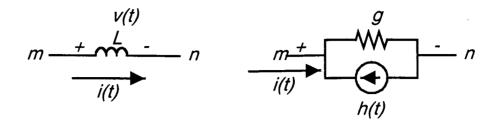

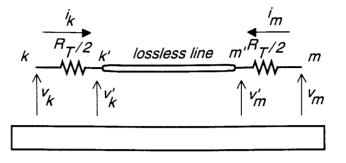

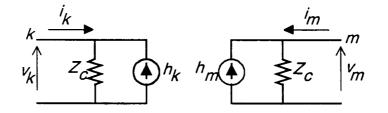

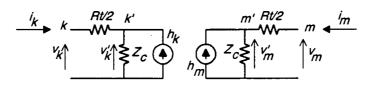

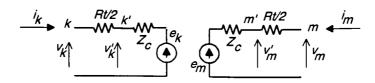

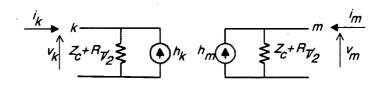

| 28 | Lumped losses in the transmission line model                                                                 | 43 |

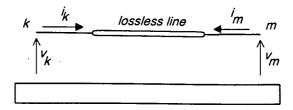

| 29 | Single phase lossless transmission line.                                                                     | 44 |

| 30 | Single phase lossless transmission line model.                                                               | 44 |

| 31 | Lossy single phase transmission line.                                                                                                       | 44   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------|------|

| 32 | History voltage source equivalent circuit.                                                                                                  | 45   |

| 33 | Lossy line equivalent circuit.                                                                                                              | 45   |

| 34 | Equivalent circuit for mode "i"                                                                                                             | 47   |

| 35 | Multiphase transmission line model in phase-domain. [g] is a                                                                                |      |

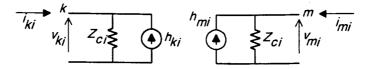

|    | matrix, all the other parameters are vectors.                                                                                               | 48   |

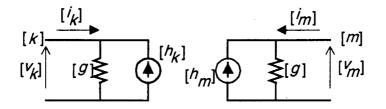

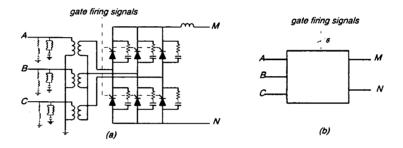

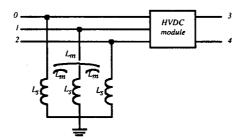

| 36 | OVNIs HVDC module: a) detailed view; b) block view                                                                                          | 50   |

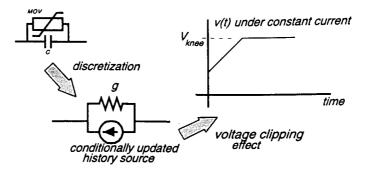

| 37 | Modelling the voltage clipping effect of the MOV.                                                                                           | 52   |

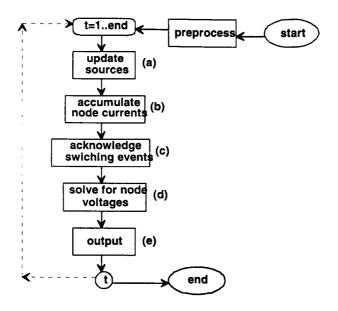

| 38 | Tasks in OVNI's simulation cycle.                                                                                                           | 55   |

| 39 | A typical power electric system.                                                                                                            | 61   |

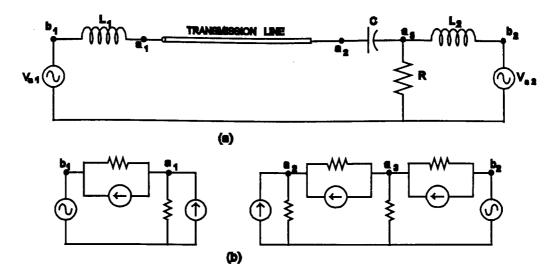

| 40 | a) Simple single-phase power system; b) Discrete-time equivalent                                                                            |      |

|    | circuit for system in (a). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                   | 62   |

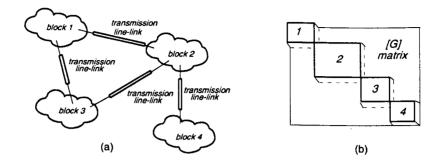

| 41 | a) Power network topology; b) Corresponding conductance ma-                                                                                 |      |

|    | $\operatorname{trix}[G].\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ | 63   |

| 42 | Relay testing case with blocks identified.                                                                                                  | 63   |

| 43 | A partial view of an HVDC-controller test case with two topolog-                                                                            |      |

|    | ical blocks                                                                                                                                 | 64   |

| 44 | Circuit with an ungrounded voltage source                                                                                                   | 65 - |

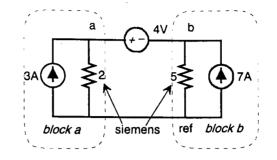

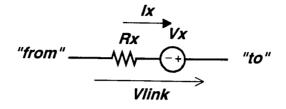

| 45 | An OVNI's link                                                                                                                              | 66   |

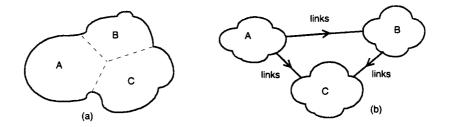

| 46 | a) Network with MATE's subblocks delineated; b) Subblocks con-                                                                              |      |

|    | nected by links, after MATE.                                                                                                                | 68   |

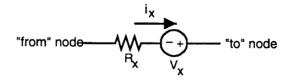

| 47 | A link's voltage source and resistance, and the directions assumed                                                                          |      |

|    | positive for current and voltages.                                                                                                          | 70   |

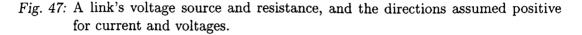

| 48 | MATE's Thevenin equivalent rendering for each of the subblocks.                                                                             |      |

|    | Nodes a b c d represent <i>docking</i> ones                                                                                                 | 72   |

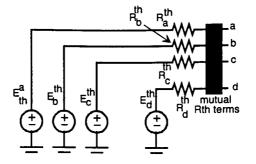

| 49 | Node Hiding: Internal nodes and external nodes                                                                                              | 75   |

| 50 | Complete network with the node hiding region delineated. Ex-                                                                                |      |

|    | ternal nodes: (1) and (2). Internal nodes: (3) and (4). $\ldots$                                                                            | 78   |

| 51 | Hiding zone: an element's model. See external nodes $(1)$ and $(2)$ ,                                                                       |      |

|    | and internal nodes $(3)$ and $(4)$ .                                                                                                        | 79   |

| 52   | "External" network, as seen by OVNI, with hidding region rep-       |     |

|------|---------------------------------------------------------------------|-----|

|      | resented as a "black-box".                                          | 79  |

| 53   | The $n$ prestored samples of a sinusoidal source. $\ldots$          | 83  |

| 54   | Wraparound of prestored source's samples.                           | 84  |

| 55   | A current source in OVNI: its nodes.                                | 85  |

| 56   | Precalculated time matrices corresponding to grounded voltage       |     |

|      | sources in a subblock                                               | 87  |

| 57   | Network with one grounded voltage source accounted for as a link.   | 88  |

| 58   | Ungrounded voltage sources in OVNI: a) a link; b) not a link. $\ .$ | 91  |

| 59   | Voltage sources "ownership", in OVNI                                | 92  |

| 60   | KCL nodal equations and KVL voltage sources equations, getting      |     |

|      | ready for standard MATE                                             | 92  |

| 61   | Extended matrices and vectors for the subblock with UVS's. Ex-      |     |

|      | tended MATE                                                         | 94  |

| 62   | Subblock with and ungrounded voltage source                         | 95  |

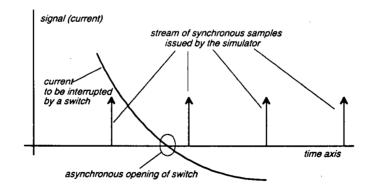

| 63   | Samples output stream, and asynchronous commutation                 | 98  |

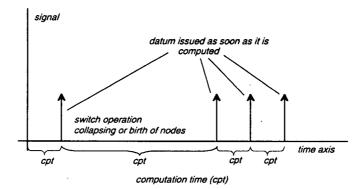

| 64   | Short and long integration steps. Non real-time simulation. Data    |     |

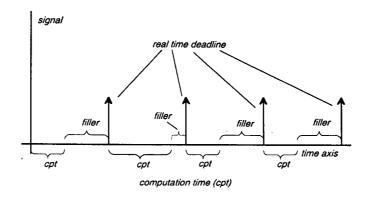

|      | are issued as soon as they are available                            | 99  |

| 65   | Short and long integration steps. Filler time slices. Data output   |     |

|      | stream in a real time simulation                                    | 100 |

| 66   | Closing a switch between nodes $i$ and $j$                          | 102 |

| 67 . | Case to illustrate how to avoid collapsing nodes                    | 103 |

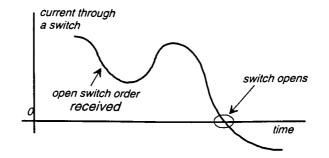

| 68   | Switch opening event: signal, and actual opening                    | 105 |

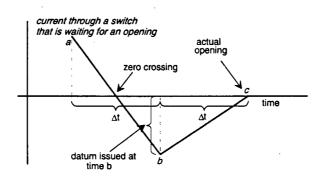

| 69   | Zero crossing and actual opening of a switch                        | 105 |

| 70   | Six valve rectifier circuit                                         | 106 |

| 71   | Voltage before smoothing reactor.                                   | 106 |

| 72   | Non real time backtracking.                                         | 107 |

| 73   | Simple non regressive backtracking                                  | 107 |

| 74   | Accurate but too expensive backtracking                             | 108 |

| 75 | BIFE: Backward interpolation, forward extrapolation                                   | 109 |

|----|---------------------------------------------------------------------------------------|-----|

| 76 | DSDI used in OVNI. The most expensive step takes one regular                          |     |

|    | integration step with precalculated matrices, plus one inexpensive                    |     |

|    | linear interpolation                                                                  | 111 |

| 77 | OVNI's modified flowchart to include DSDI. Elements handle                            |     |

|    | three instances of their histories: $h_{next}$ , $h_{now}$ , $h_{before}$ . When they |     |

|    | "decide" to backtrack, they discard $h_{next}$ , and interpolate between              |     |

|    | the other two.                                                                        | 112 |

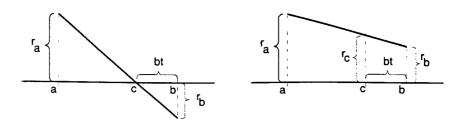

| 78 | Linear interpolation between points $(a, r_a)$ and $(b, r_b)$ . bt is the             |     |

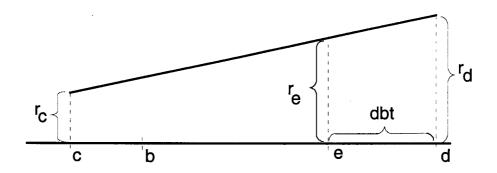

|    | per unit backtracking necessary                                                       | 115 |

| 79 | Interpolation across the double step span. $\ldots$                                   | 115 |

| 80 | Equivalent circuit of current transformer (minus the ideal trans-                     |     |

|    | former) referred to the burden side.                                                  | 119 |

| 81 | Piecewise linear representation of magnetization in flux path                         | 121 |

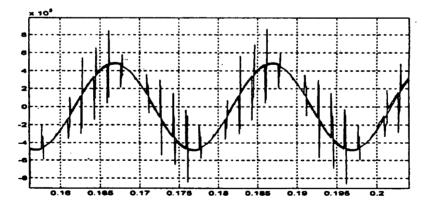

| 82 | Secondary current match between OVNI's model and EMTP's                               |     |

|    | discrete elements one. Both simulation coincide completely                            | 123 |

| 83 | Coupling Capacitor Voltage Transformer, CCVT.                                         | 124 |

| 84 | Lumped parameter high frequency equivalent circuit of a two                           |     |

|    | winding transformer.                                                                  | 125 |

| 85 | High frequency model of a reactor.                                                    | 125 |

| 86 | High frequency equivalent circuit for a two winding transformer.                      | 126 |

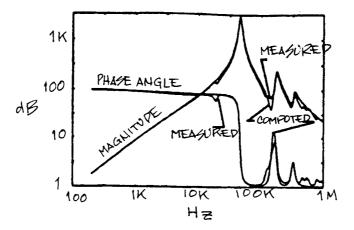

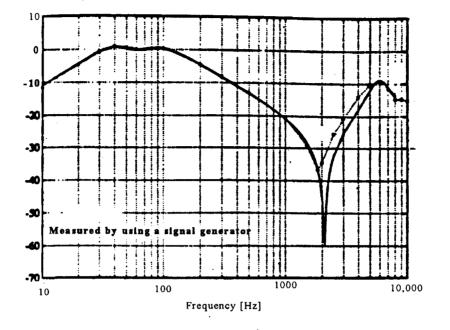

| 87 | Frequency response $(Z_{short})$ of a two winding transformer. Mea-                   |     |

|    | sured and synthesized responses                                                       | 127 |

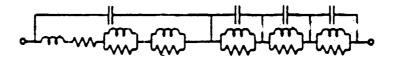

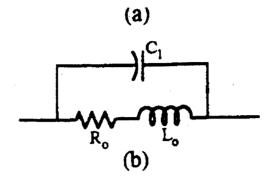

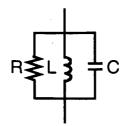

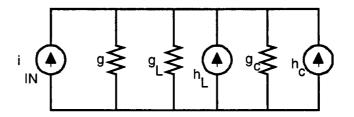

| 88 | Synthesized RLC network used to approximate $Z_{short}(\omega)$ , multiple            |     |

|    | peak high-accuracy synthesis.                                                         | 127 |

| 89 | Simplified model to represent only the main peak delivers accept-                     |     |

|    | able accuracy.                                                                        | 128 |

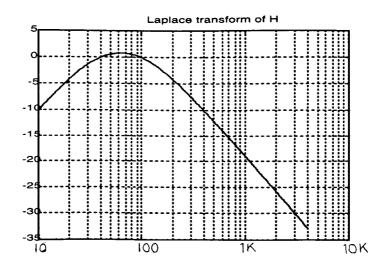

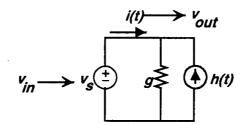

| 90 | PT's frequency response, $20 \log(V_{out}/V_{in}) dB$ versus frequency in             |     |

|    | hertz                                                                                 | 129 |

| 130<br>130<br>131 |

|-------------------|

|                   |

| 131               |

| 131               |

|                   |

|                   |

|                   |

| 132               |

| 133               |

|                   |

| 134               |

| 135               |

| 136               |

| 137               |

| 138               |

|                   |

| 139               |

| 140               |

| 140               |

| 141               |

| 142               |

| 143               |

| 143               |

| 143               |

| 146               |

| 147               |

| 148               |

| 151               |

|                   |

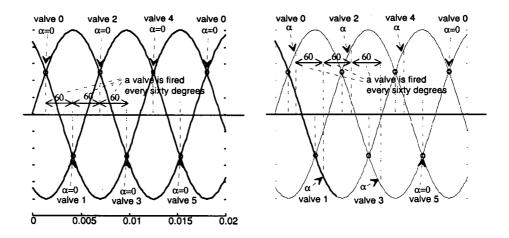

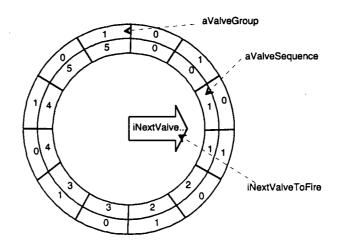

| 113 | a) Firing time points when alpha is zero; b) Firing points when         |     |

|-----|-------------------------------------------------------------------------|-----|

|     | alpha is not zero.                                                      | 151 |

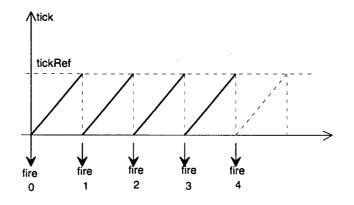

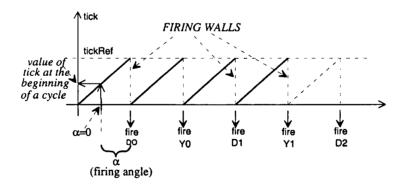

| 114 | The ramp signal and the model's variables for $a = 0$                   | 152 |

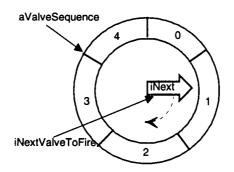

| 115 | Data structure to select next valve to be fired, when the ramp so       |     |

|     | requests                                                                | 152 |

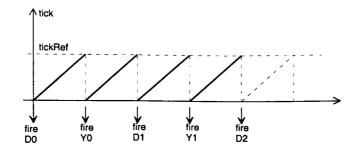

| 116 | The ramp signal and the model's variables for $\alpha = 0$ , when gate  |     |

|     | signals are issued for Yy and Yd modules                                | 153 |

| 117 | Scheduling the next valve to be fired: index, iNextValveToFire;         |     |

|     | and arrays: a Valve Group and a Valve Sequence                          | 153 |

| 118 | Firing walls and initial value of the tick ramp counter at the          |     |

|     | beginning of each reference cycle                                       | 154 |

| 119 | Filtering the angle reference voltage signal                            | 159 |

| 120 | Discretized version of the reference angle voltage filter               | 159 |

| 121 | Reference angle voltage $V_{ac}$ and its fundamentals obtained by the   |     |

|     | filter described in this section.                                       | 160 |

| 122 | Magnetization branch in a single-phase transformer (non-linear)         | 161 |

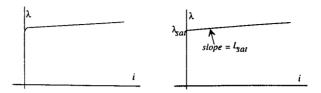

| 123 | a) Magnetization of a transformer core (typical); b) Two-segments       |     |

|     | piecewise magnetization curve used                                      | 162 |

| 124 | Saturation modelling for a single phase transformer                     | 162 |

| 125 | Non-saturated three phase core transformer.                             | 163 |

| 126 | Three phase core transformer with phase-a's leg saturated               | 164 |

| 127 | Non-saturated magnetization in three phase core transformers. $\ .$     | 165 |

| 128 | Phase voltages and non-saturated magnetization currents                 | 166 |

| 129 | Including the non-saturated magnetization matrix, $[G_{ns}]$ , into the |     |

|     | HVDC-module $[G]$ matrix                                                | 167 |

| 130 | Modelling saturation in the core.                                       | 168 |

| 131 | The six history sources introduced to model magnetization in the        |     |

|     | transformer.                                                            | 169 |

xvii

| 132 | Primary current with a linear core under steady state conditions,      |     |

|-----|------------------------------------------------------------------------|-----|

|     | OVNI's model and EMTP simulation. The large spikes belong to           |     |

|     | OVNI's before DSDI, §7.7. Microtran/EMTP avoids them using             |     |

|     | CDA [10]                                                               | 170 |

| 133 | Primary current with a saturated core under steady state con-          |     |

|     | ditions, OVNI's model and EMTP simulation. See caption to              |     |

|     | Fig. 132                                                               | 170 |

| 134 | Standard abbreviations in OVNI.                                        | 173 |

| 135 | Hungarian notation prefixes as used in OVNI                            | 173 |

| 136 | Structure that represented originally a node in OVNI                   | 174 |

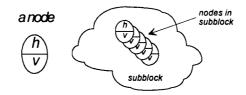

| 137 | Node array inside a subblock object.                                   | 174 |

| 138 | A node registration item, an element of the node registry array.       | 175 |

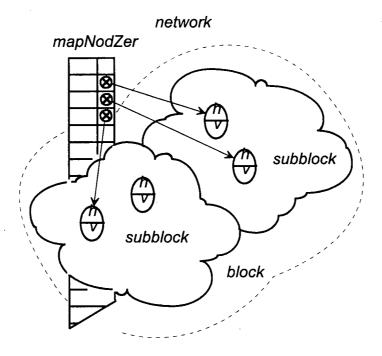

| 139 | Network registry of nodes, and their spatial relationship with the     |     |

|     | nodes, subblocks, blocks, and the network                              | 175 |

| 140 | The external history source class, hsr_t                               | 176 |

| 141 | Relationship among the elements, their history sources and the         |     |

|     | subblock's                                                             | 176 |

| 142 | The element abstract class, elm_t. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 177 |

| 143 | The subblock class, $sub_t$ .                                          | 181 |

| 144 | The blk_t class, template for every block in the network. $\ldots$     | 182 |

| 145 | Header of the clock object, the ticker, tck_t. $\ldots$                | 183 |

| 146 | Services provided by the simulation object                             | 183 |

| 147 | Container/contained relationship of classes in OVNI. $\ldots$ .        | 184 |

| 148 | Initialization Task of the Engine.                                     | 185 |

| 149 | General structure of the preprocessor input file.                      | 191 |

| 150 | Section on general data for a case with an integration step of fifty   |     |

|     | microseconds and a total simulation time of fifty miliseconds          | 192 |

| 151 | Section on lumped elements: including one resistor of $20\Omega$ con- |     |

|-----|-----------------------------------------------------------------------|-----|

|     | nected between nodes $TOPO$ and $BURRO$ ; an inductor of $20  mH$ ,   |     |

|     | and a capacitor of $20\mu F$                                          | 192 |

| 152 | This switch data section includes a single switch: the one between    |     |

|     | nodes $TOTUMA$ and $COBIJA$ , a switch open at the beginning          |     |

|     | of the simulation, with two open operations, one at seven hundres     |     |

|     | microseconds, the other at twelve hundres microseconds                | 193 |

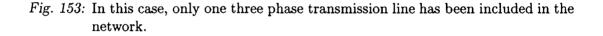

| 153 | In this case, only one three phase transmission line has been in-     |     |

|     | cluded in the network.                                                | 194 |

| 154 | HVDC controller data.                                                 | 196 |

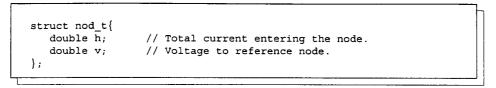

| 155 | Every node is represented by a 'nod_t' structure and registered in    |     |

|     | a cell of the list 'nodList_t'. $\ldots$                              | 197 |

| 156 | A cell in the $list_t$ class.                                         | 198 |

| 157 | The "head" cell and the circular linked list defined by $list_t$      | 199 |

| 158 | Methods and data items in the $list_t$ class                          | 200 |

| 159 | Methods and data items in the $nodList_t$ class                       | 201 |

| 160 | Each node in the network list is an instance of this structure        | 202 |

| 161 | Methods and data items in the $sub_t$ class                           | 203 |

| 162 | Methods and data items in the $subList_t$ class                       | 204 |

| 163 | Interaction of classes in OVPP during node registration               | 205 |

| 164 | Interaction of classes in OVPP during assembling of subblocks         | 206 |

| 165 | Interaction of classes in OVPP during subblock matrix calculation     | 207 |

| 166 | Interaction of classes in OVPP during block grouping                  | 209 |

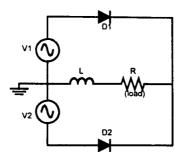

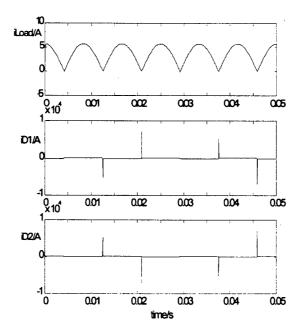

| 167 | A two-diode full wave rectifier case.                                 | 212 |

| 168 |                                                                       |     |

|     | For the two-diode retifier, current in the load                       | 212 |

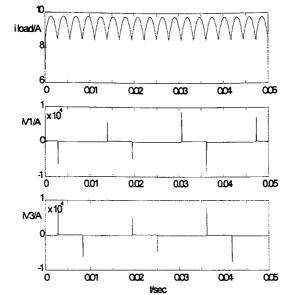

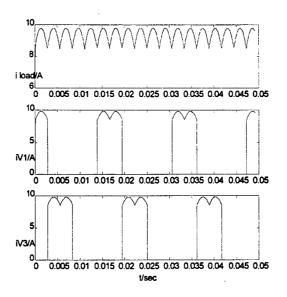

| 169 | DSDI output for two-diode rectifier case.                             | 213 |

| 170 | A six-valve three-phase rectifier group.                              | 213 |

| 171 | EMTP algorithm results for the six-valve rectifier.                   | 214 |

| 172 | DSDI results for the six-valve three-phase case.                      | 214 |

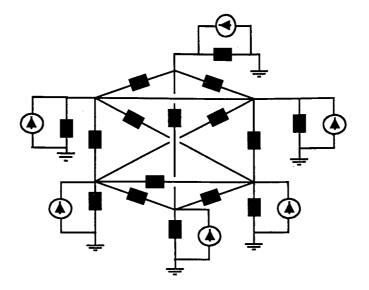

| 173 | One of the six sections in the test network used to benchmark     |           |

|-----|-------------------------------------------------------------------|-----------|

|     | MATE                                                              | 217       |

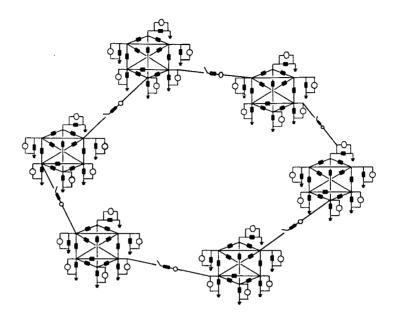

| 174 | Six node sections connected in a ring.                            | 218       |

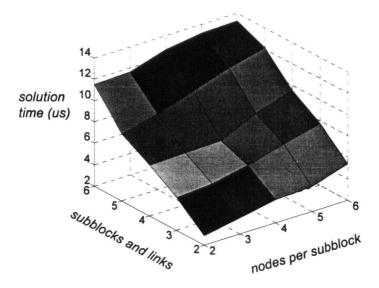

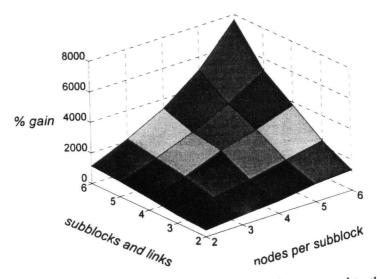

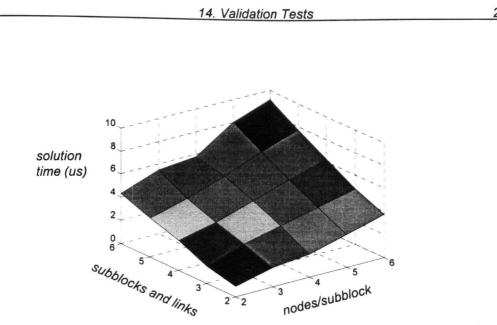

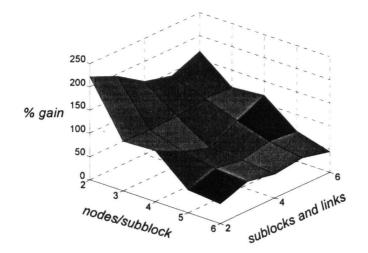

| 175 | Solution times, in microseconds, for MATE algorithm               | 219       |

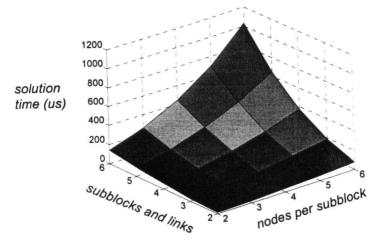

| 176 | Solution times for the standard unsegmented algorithm             | 220       |

| 177 | In percentage, how much faster MATE is compared to the stan-      |           |

|     | dard unsegmented algorithm                                        | 220       |

| 178 | Solution time for precalculated MATE link matrices                | 221       |

| 179 | Percentage grains of precalculating the link matrices vs vs. cal- |           |

|     | culating them on the run                                          | 222       |

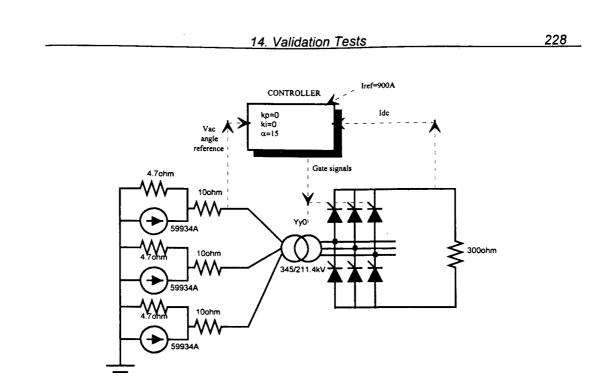

| 180 | Single module, six-valve test case used to validate the HVDC      |           |

|     | module under steady state                                         | 224       |

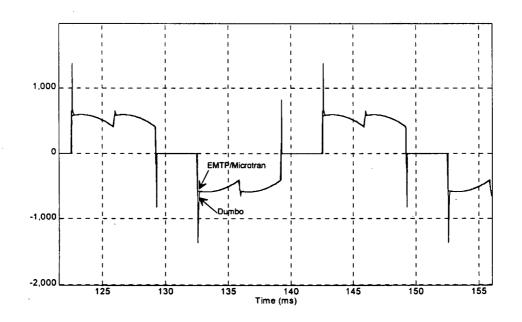

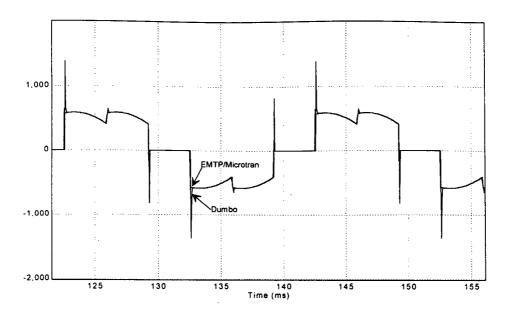

| 181 | Primary current, steady-state, linear transformer core. EMTP/MIC  | ROTRAN    |

|     | and Dumbo (DU-99)                                                 | 224       |

| 182 | Primary current, steady state, linear transformer core. EMTP/Micr | cotran    |

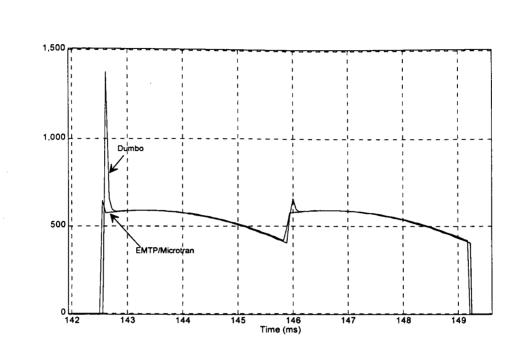

|     | and Dumbo. A detail view.                                         | 225       |

| 183 | DC voltage in steady state: EMTP/Microtran and Dumbo              | 225       |

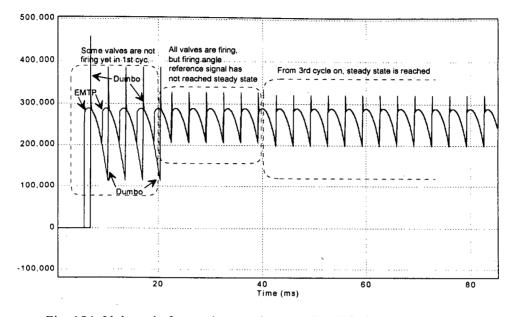

| 184 | Voltage before and at steady state: EMTP/Microtran and Dumbo.     |           |

|     | Initialization: two cycles for Dumbo.                             | 226       |

| 185 | Zoom on the primary current, steady state, linear transformer     |           |

|     | core. EMTP/Microtran and Dumbo.                                   | 227       |

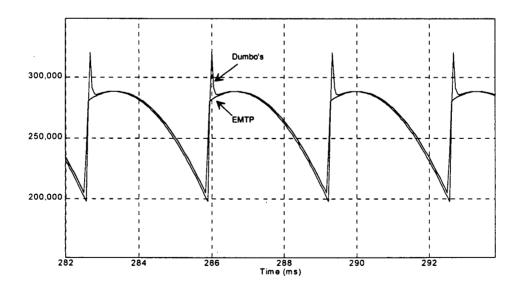

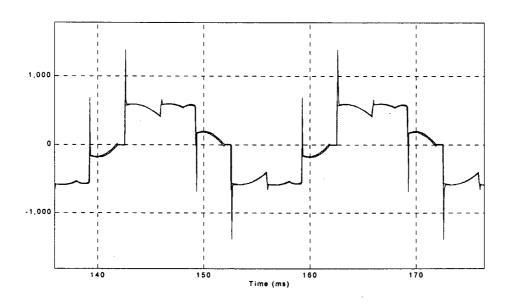

| 186 | Primary current, steady state, non-linear transformer core. EMTP/ | Microtran |

|     | and Dumbo                                                         | 227       |

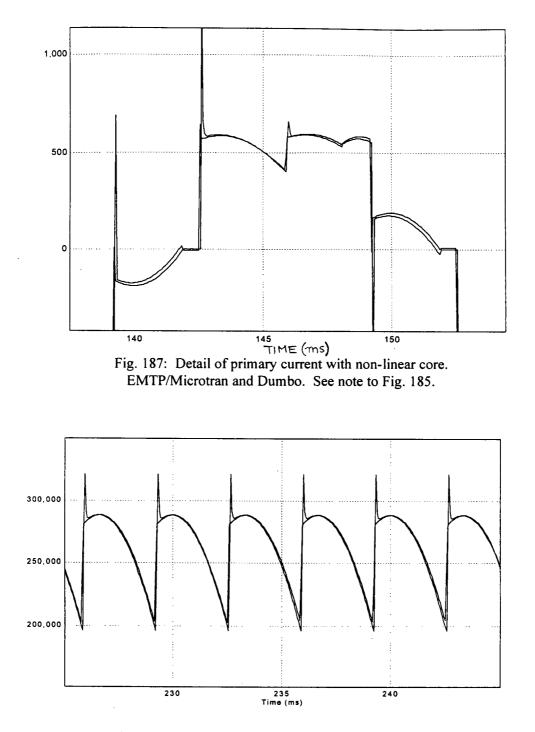

| 187 | Detail of primary current with non-linear core. EMTP/Microtran    |           |

|     | and Dumbo                                                         | 228       |

| 188 | DC voltage, with non-linear transformer core. EMTP/Microtran      |           |

|     | and Dumbo                                                         | 228       |

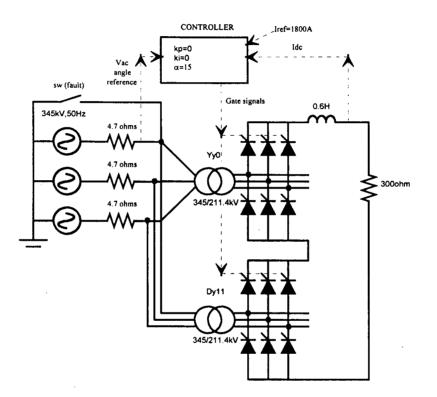

| 189 | 12-valve case to validate behaviour of HVDC model under AC        |           |

|     | faults.                                                           | 229       |

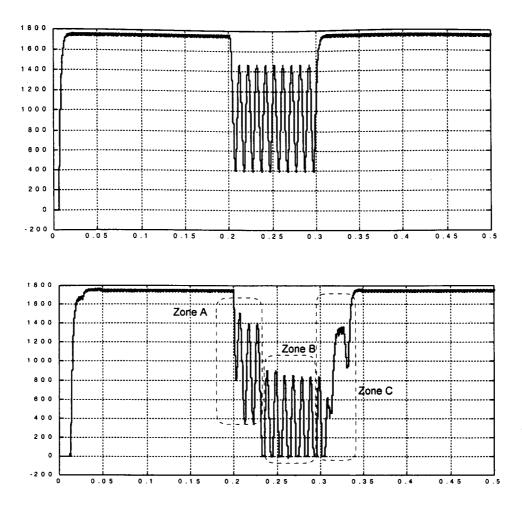

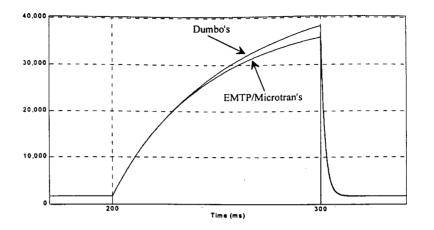

| 190 | DC current, as calculated by: a) Microtran; b) Dumbo              | 230       |

XX

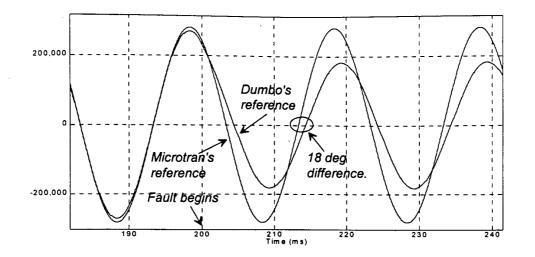

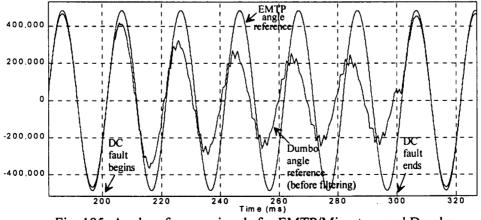

| Angle reference voltage for a) Microtran; b) Dumbo. Observe the                                |                                                                                 |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| small phase error before the fault, and the large error during the                             |                                                                                 |

| shortcircuit.                                                                                  | 231                                                                             |

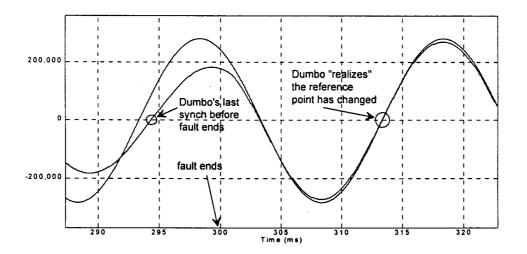

| Angle reference voltage for Microtran and Dumbo near the end                                   |                                                                                 |

| of the fault.                                                                                  | 231                                                                             |

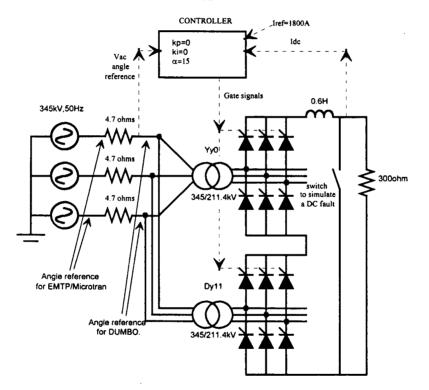

| A double bridge, twelve valve case used to explore the HVDC                                    |                                                                                 |

| module during and after a low impedance fault on the DC side.                                  | 232                                                                             |

| Fault current (DC-side): a) EMTP/Microtran; b) Dumbo                                           | 233                                                                             |

| Angle reference signals for EMTP/Microtran and Dumbo. Before,                                  |                                                                                 |

| during, and after the DC fault.                                                                | 233                                                                             |

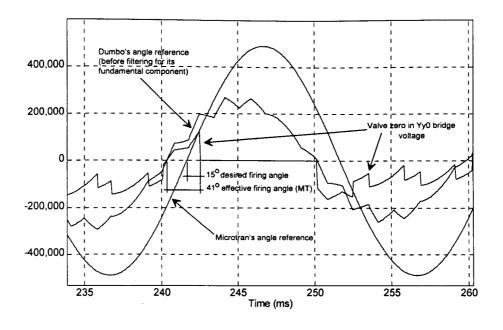

| During the DC fault period: a) Firing angle reference voltage, Vac                             |                                                                                 |

| for Microtran; b) Reference voltage Vac, for Dumbo; c) Voltage                                 |                                                                                 |

| across valve zero in the Yy0 bridge, as obtained by Microtran. $% \mathcal{A} = \mathcal{A}$ . | 234                                                                             |

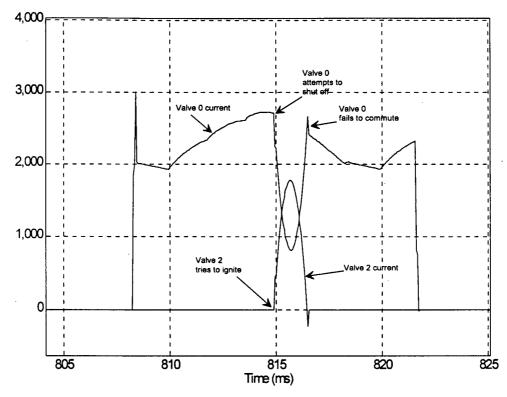

| Valves zero and two of HVDC module Yy0.                                                        | 235                                                                             |

| Twelve valve, double bridge inverter case used to investigate com-                             |                                                                                 |

| mutation failure modelling                                                                     | 236                                                                             |

| DC current before, during, and after the AC single phase fault,                                |                                                                                 |

| in the inverter.                                                                               | 236                                                                             |

| Protective relay test case, with two multi-circuit segments and                                |                                                                                 |

| MOV protection of series compensation.                                                         | 237                                                                             |

| Voltage on phase b at FAULT1                                                                   | 237                                                                             |

|                                                                                                | small phase error before the fault, and the large error during the shortcircuit |

#### PREFACE

This research began as a quest for an algorithm to solve power system networks that was fast enough as to perform real-time equipment testing.

Testing of the algorithm focused on two cases provided by industry: a protective relay test case, and an HVDC controller test case.

The work took the EMTP's algorithm as a starting point. The EMTP turned out to be more than sixty times too slow for the second case mentioned above, and fourteen times too slow for the first case.

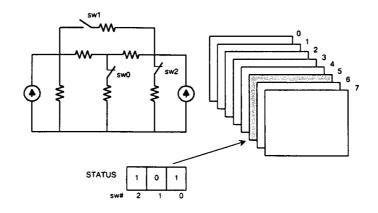

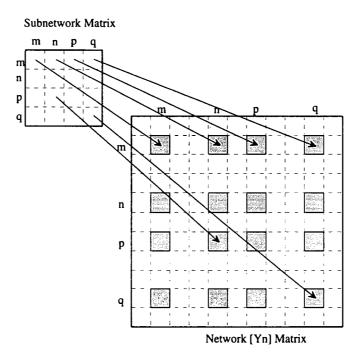

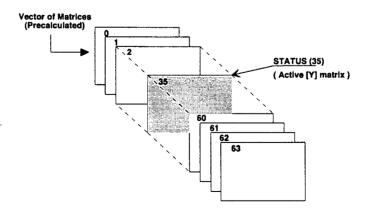

In the first of the test cases, that algorithm spent more than two-thirds of the time solving the nodal equation system,  $[G][v] = [h]^1$ . To accelerate the solution process, precalculation of all possible [G] matrices (and of their triangular decompositions) was considered. It is easier to visualize the obstacles ahead of this approach through an example (which will be detailed later in this thesis): a 1000-node network with 1000 switches would require several trillions of Earth-sized planets covered with RAM chips (continents and oceans as well) to provide for storage to such set of matrices. However, conveniently segmenting the same network, would bring down the memory requirements to less than 180 kilobytes.

Segmentation was introduced in three different forms: the one suggested by the time delay provided by transmission lines (topological segmentation), the new Multi-Area Thevenin Equivalent (expanded and presented in this thesis in its full potential for the first time), and the also new node-hiding procedure. The combination of those segmentation strategies was labelled multi-layer seg-

<sup>&</sup>lt;sup>1</sup> Where [G] is the network bus conductance matrix; [v] is the vector of nodal voltages, to be computed; and [h] is the vector of total nodal currents.

mentation. This segmentation yielded the performance looked for.

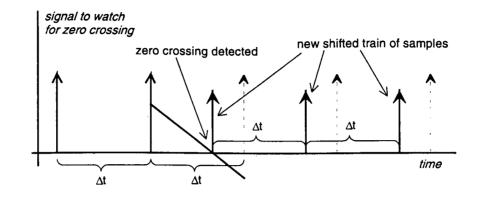

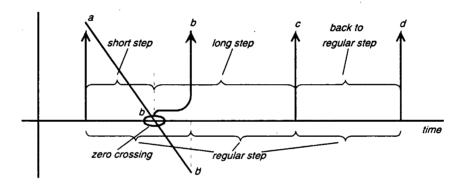

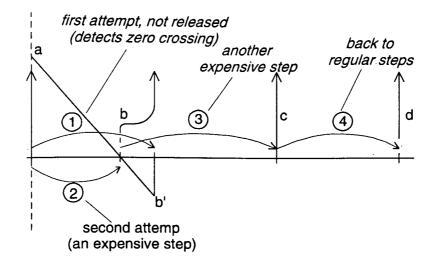

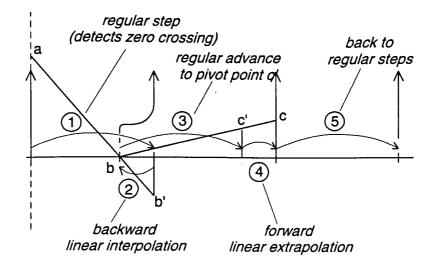

To eliminate the voltage spikes produced by switch or valve openings that occur between simulation points, a new mechanism was introduced, the new double-step and double-interpolation procedure, a technique that backtracks to the occurrence of the switching event, and then advances by a double step to fall back in synchronism with the real-time train of samples.

Buttressing the algorithm's robustness and stability, a careful integrationrule study shed new light into the effect (in the time-domain) of the phase shift that the backward Euler integration rule introduces (in the phase-domain).

The result of this work is a very fast and stable algorithm with no loss of generality. During testing, as reported in this thesis, the algorithm delivered real-time performance for the demanding test cases outlined above, and it did so on an off-the-shelf PC-Pentium 400 MHz workstation.

This thesis is divided in several *parts*, as follows:

- 1. Motivation. A brief account of the events that triggered this research;

- 2. The problem. A description of the challenge to overcome at the outset of the work;

- 3. The Solution. This is the main part of the thesis, it contains its contributions, which are scattered among several chapters: Chapter 3 presents a new look at the backward Euler integration rule; Chapter 5 introduces, in its general format, precalculation riding on top of a multi-layer form of network segmentation (topological segmentation, the new Multi-Area Thevenin Equivalent concept, and the also new node-hiding segmentation strategy); Chapter 6 describes the precalculation subtleties of periodic sources used in OVNI, and extends and generalizes the multi-area Thevenin equivalent concept to produce the very efficient tool that bring the performance needed to meet the real-time deadline targeted (less than fifty microseconds for the test case described above); Chapter 7 presents, among other things, the new double step with double interpolation back-

#### xxiii

tracking algorithm used to eliminate the voltage spikes introduced by opening of switches between the instants where the simulation solves the network, it does that with a mimimum overhead that keeps the whole simulation within the real-time deadline;

- 4. New Models. Chapters 8, 9, 10, and 11 include measuring transformer models, some non-linear element models with fast topology-change, and a minimal functionality controller, the last two as examples of the implementation of the node hiding strategy on an element model, and on the creation of two element models that interact with one another;

- 5. Implementation. Chapters 12 and 13 describe the implementation of the simulator core and of its preprocessor with some minimal detail;

- 6. Validation Tests. Chapter 14 shows several test cases where the simulator delivered results whose accuracy is compared with those of the EMTP, those results were obtained within the real-time bandwidth targeted;

- 7. Conclusions. Finally, Chapter 15 closes the thesis with a summary of conclusions.

#### ACKNOWLEDGEMENTS

"No book published is ever solely the work of the author. Assistance comes from a variety of sources in as many different ways," wrote Jean M. Auel at the introduction to her best-selling novel The Clan of the Cave Bear. This cannot be more true than in the case of a thesis. So many people have contributed in one way or another to help me reach this goal, from my mother, Rita Elena, who decided to teach her three year old son to read and write, and both my wonderful elementary school teachers, Sra. Rojas and Prof. Hernandez, to my father Rafael Jose, who insisted on integrity, curiosity, and originality as the hallmark of a true human being.

My recognition and gratitude to Prof. Marti, who put in my hands this most critical part of the OVNI project, and who always believed in my skill to somehow pull the proverbial rabbit out of the hat and produce an ever faster and faster algorithm. I want to acknowledge him for his financial support, for sharing his impressive knowledge and intuition with me, but above all I want to thank him for his trust.

To Prof. Dommel, whose prompt advice and guidance during the first years of my research widened my horizons in this his land, the land of the electromagnetic transients analysis, I want to acknowledge and thank his kindness and support, .

To Mrs. Doris Metcalf, Ms. Cathleen Holtvolg, Ms. Katy Brindamour, Mrs. Gail Schmidt, Ms. Anne Coates, Mr. Alan Prince, and Mr. Ken Madore, thanks for their friendship and patience.

To Prof. Donaldson and Prof. Davies for trusting me with the young minds of the students of ECE 263, 370, 373 and thus providing me with a necessary retreat from the intense research activity (albeit for a few hours).

XXV

For all the help in preparing and setting the slides for the final presentation, thanks to my daughter Jazmin Carolina, to my son Ivan Jose, and to my colleague and friend Richard Rivas.

My appreciation and recognition goes to my friend Mr. Jesus Calvino-Fraga, who interfaced OVNI with the real-world, and to my friend Mr. Jorge Hollman who ported OVNI to his multi-PC cluster which allowed the simulator code to perform at maximum efficiency.

I would also like to thank my friend and colleague, Dr. Salvador Acevedo, for sharing his power electronics knowledge with me, and for his patience and tolerance in having his model turned inside out and upside down to accommodate OVNI's interface and the corresponding node simplification schemes. Thanks for the many productive discussions about the *nachos*-problem.

To this wonderful land, to Canada, to her people, to her future, thanks for welcoming my family and myself, and for providing the platform on which all this has been possible.

Last but not least, I thank my wife Maria Josefina, for her almost inexhaustible patience, for her love, her support, and for kick-starting me when I needed it most.

To you all, my gratitude. May God bless you all!

Luis R. Linares-Rojas.

XXYI

I dedicate this thesis to these three wonderful women

Maria Josefina, my wife

Jazmin Carolina, my daughter

Rita Elena, my mother

# Part I

## MOTIVATION

#### 1. INTRODUCTION

This thesis describes an effort to develop a general purpose digital simulator for electric and electronic power networks, suitable for real-time closed-loop equipment tests under flexible constraints of bandwidth and network complexity.

Simulation of an electric network can be viewed as the process to determine its state at a certain number of points along the time axis. If the network is described by its circuit theory representation, its state can be obtained as the solution to a set of non-linear coupled partial differential equations [11]. Using nodal analysis, for instance, this mathematical representation includes one of such equations for each node in the network. Even for a small network, with only a few tens of nodes, the solution task is rather demanding. When the solution needs to be obtained within the constraints of a real-time simulation<sup>1</sup>, the problem becomes even more challenging.

The Engineering community has been able to reduce the complexity of the problem of determining the state of the network, at the price of reducing the scope of the solution as well, by classifying the network's behaviour into operational areas of interest, and applying suitable simplifying assumptions to each of those areas separately. The most important of those areas are: steady-state power flow [12, 13, 14], slow transients [15], fast transients [4], short-circuits [16, 14], and real-time equipment testing.

This thesis presents an attempt to a unified solution, and explores its validity on two counts, fast transients simulations, and real-time simulations for equipment testing; away from analog simulations and into the realm of digital

<sup>&</sup>lt;sup>1</sup> i.e., a few microseconds.

simulations.

For each of the areas of interest mentioned, industry counts on specialized software based on the corresponding assumptions and restrictions. In particular, for insulation coordination analysis, the standard tool, the  $EMTP^2$  [4], is built around the widest of the assumption sets, and uses a powerful discretization process for the problem that provides the seed for the work presented in this report. It is then convenient to establish the place of the EMTP in current power engineering practice.

During the last decades, the electromagnetic transients program —EMTP has been gaining ground that used to be the sole domain of the expensive and bulky analog network simulator  $TNA^3$  [17], transients computations in power systems. Today, the EMTP is the standard tool for this kind of simulations. Even if already existing TNAs remain in service, most new needs are covered by EMTP installations.

Cost and room use are two main areas where the EMTP has clear advantage when compared with the TNA. Another advantage is enhanced flexibility: very accurate models for system components can be developed and incorporated into the EMTP. Such is the case of the power transmission line, whose distributed parameters nature is not representable with the scaled-down analog models available in a TNA<sup>4</sup>. In spite of those advantages, in cases when testing some device requires real-time interaction between the device and the power system it is connected to, the analog simulator TNA is very often still the answer.

However, if a computer program is to attain real-time performance while simulating a power network, the program has to be capable of solving the system equations fast enough to encompass the bandwidth required for the equipment under test. In both, protective relay tests, and in HVDC controller tests, a bandwidth between 2,000 Hz and 4,000 Hz is considered adequate [18, 19, 9].

<sup>&</sup>lt;sup>2</sup> Electromagnetic Transients Program

<sup>&</sup>lt;sup>3</sup> Transients Network Analyser.

<sup>&</sup>lt;sup>4</sup> Hybrid simulators include the best of both worlds, digital and analog, but at very high costs.

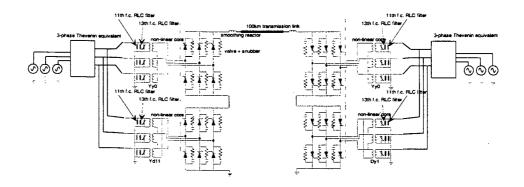

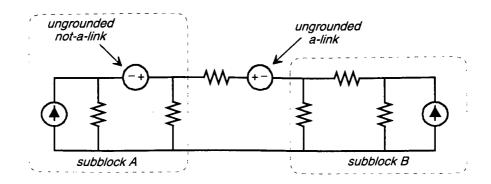

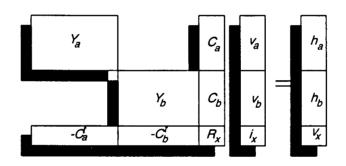

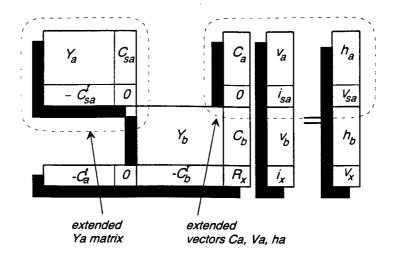

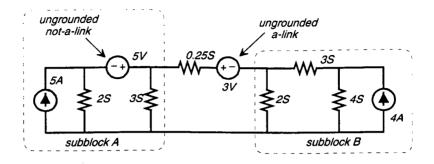

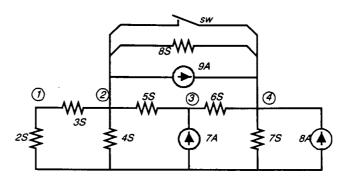

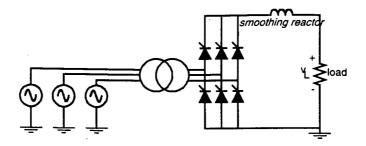

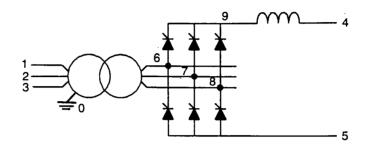

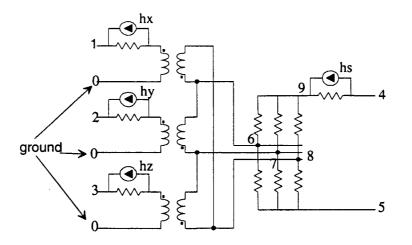

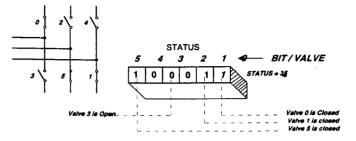

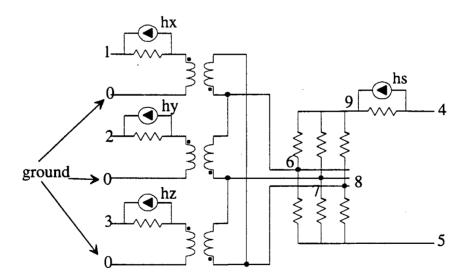

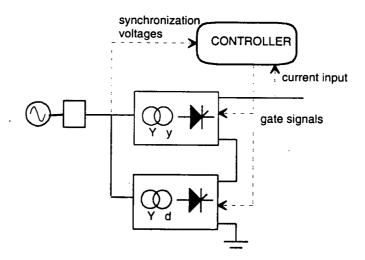

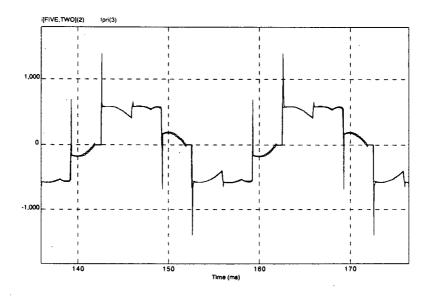

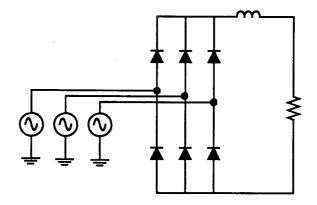

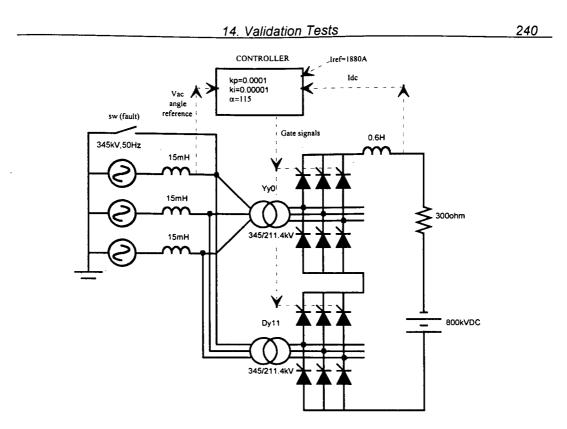

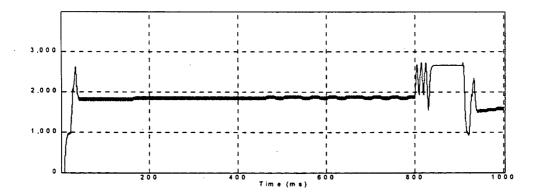

Fig. 1: An HVDC test case.

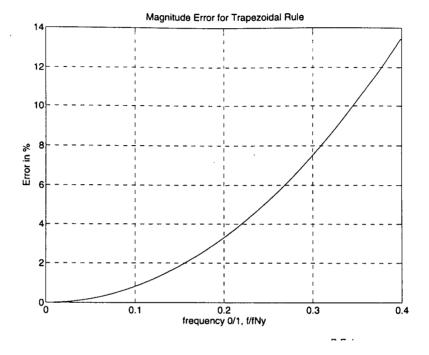

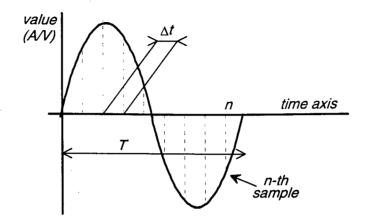

Using the trapezoidal integration rule as a reference, and keeping the maximum distortion error introduced by the rule under 10%, an integration time-step between  $50\mu s$  and  $100\mu s$  is then necessary [10].

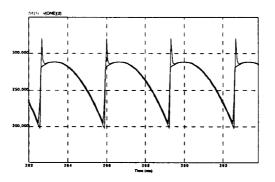

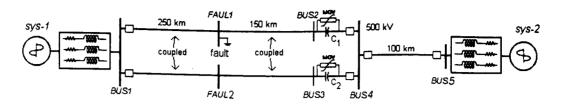

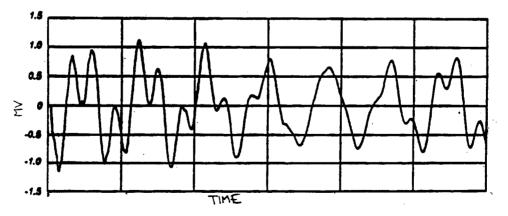

To perceive the performance improvement needed, two important test cases were simulated with Microtran's EMTP<sup>5</sup>: the HVDC test case in Fig. 1, and the protective relays test case whose one line diagram is shown in Fig. 2. Both cases were run on a 200 MHz Pentium Pro workstation. For the first case, the EMTP used an average<sup>6</sup> of  $3120\mu s^7$ , that is, an improvement in speed of thirty to sixty times is necessary for real-time performance. For the second case, an improvement factor between seven and fourteen was found needed.

In spite of the strict speed requirements, the new breed of microchips and computer architectures has been attracting researchers [18, 20, 21, 22, 23, 19, 24, 25, 26, 9, 27] into trying to produce a digital real-time simulator. Most of those researchers have chosen a hardware approach. Some mimic the topology of the power network with a convenient arrangement of DSP's [18, 27] (some tried

<sup>&</sup>lt;sup>5</sup> UBC's PC version of the EMTP.

<sup>&</sup>lt;sup>6</sup> The critical step is —most likely— much larger than this, but internal probing into the EMTP's simulation cycle was not available.

<sup>&</sup>lt;sup>7</sup> Actually, more than that, since capacitive snubbers and harmonic filters were not included in this simulation.

Fig. 2: A protective relay test case.

this approach with transputers in the past [20, 21]), others rely on expensive and sophisticated super-computer architectures [24] to meet real-time deadlines for reduced size test cases<sup>8</sup>. Some other researchers [22] have attempted a transient stability analysis of a power network by splitting the simulation loop into spawned parallel child processes, where each of these processes is assigned a node in a hypercube architecture system, according to a sophisticated mapping pattern. The results reported in [22] show a speedup of 45% when moving from one to two processors, but an additional gain in speed, for the linear part of the problem, with four processors of only 15%. If more than four processors were used, the additional overhead actually increased the total execution time. In hardware based solutions like those in [18, 20, 21], the close match between the particular network to be solved and the physical connection of boards (or transputers, in the past) may render the solution inflexible<sup>9</sup>. Besides, depending on customized hardware platforms, the upgrading cycle to new and faster hardware may be much slower than in the case of commercially available off-the-shelf computer systems.

In the work that occupies us, an algorithmic-software-based method is introduced. By going back to the original set of non-linear coupled partial differential equations, a global view is obtained. The increased level of complexity of

5

<sup>&</sup>lt;sup>8</sup> Even though they originally employed supercomputers, the Mitsubishi group, with which we performed common work in 1995, has recently switched to a PC solution for the hardware [26].

<sup>9</sup> As of this writing, [27] implemented an elegant solution around this problem.

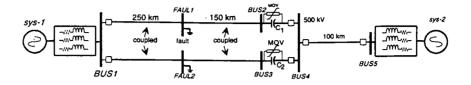

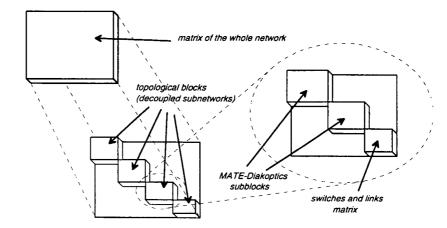

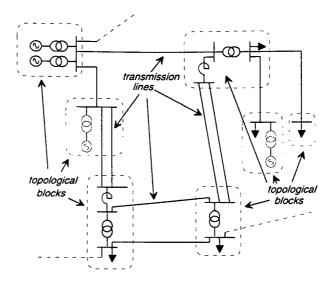

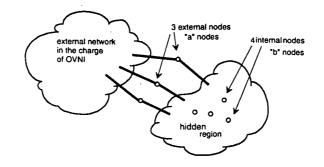

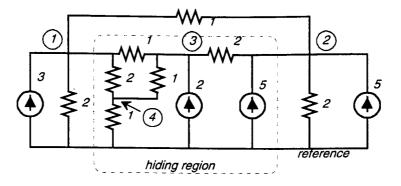

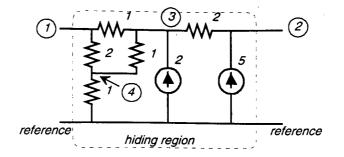

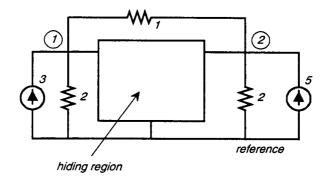

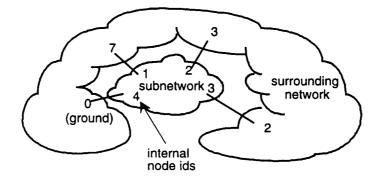

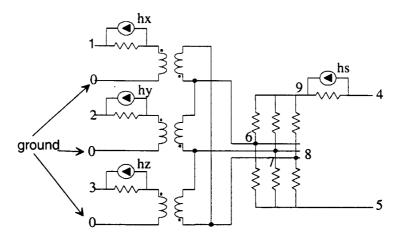

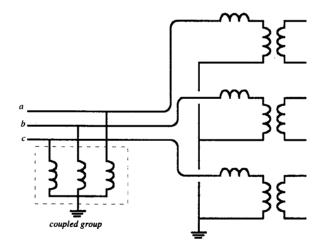

Fig. 3: Multilayer segmentation: Topological segmentation, followed by MATE-Diakoptics Segmentation.

the representation is dealt with by fragmenting the network into smaller quasidecoupled fragments. Two fragmenting techniques are combined into a two step process, topological segmentation [9], and MATE segmentation [28, 29], Fig. 3. Further simplification and efficiency are achieved by hiding, or shading away, certain nodes, and so reducing the effective size of the network fragments even more. Also, as the smaller network fragments contain a reduced number of switches, ergo a reduced number of switching states, and contain fewer nodes, after node hiding, they become suitable for some judicious precalculation without loss of generality in the solution [29].

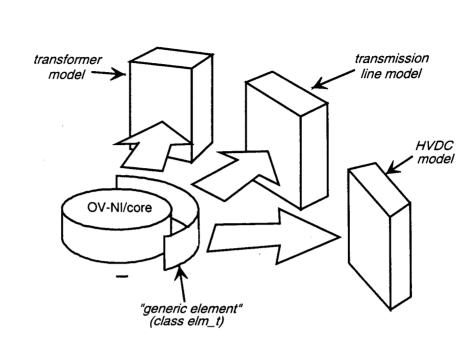

Apart from the speed-related issues of the solution algorithm, growth-security was also considered. The fast changing evolutionary process of real-time model development for network elements imposes the need to incorporate simplicity and flexibility in the interface between those element models and the integrator proper. That is, we need to plug-in and out new models as old ones become obsolete, as painlessly and reliably as possible. Some of those models may represent a centre of fast-changing topology to the integrator, as in the case of the HVDC model [30], or complex internal representations that must not perturb the core of the simulator with their details, as in the case of the time domain frequency dependent transmission line model [31, 32]. Even models that include non electrical issues, such as the synchronous generator model [33], must be incorporated seamlessly and used within a common model-integrator-interface. This goal was achieved by object-oriented design techniques [34]. All models, present and future, are to be connected to the core through a common and unique interface, Fig. 4. This means that they all look and behave the same, as far as the core is concerned. In OOP<sup>10</sup> parlance, that common interface is provided by a "defined" generic element, (an abstract class named elm\_t), that comprises all the behaviour groups<sup>11</sup> of interest to the integrator core. The result is that all models turn out to be a particular case of that abstract class, with the additions and refinements that are unique to the model in question: the models are classes that inherit the behaviour defined for the elm\_t class.

The solution presented here relies on a fast solution algorithm, and has the advantages of enhanced flexibility and upgradability: it is not hardwired to the configuration of the network to be simulated, and its core (NI) is written in C++. The algorithm is easily portable to faster hardware platforms, as they become available, with the only concern in real-time applications of the adaptation of port-cards, amplifiers, and the corresponding synchronization signals. During the research cycle of this project, the core was developed on Intel platforms, run on Sun workstations (for portability tests), moved to IBM RISC System/6000 Model 560 machines, where it delivered real-time performance for the first time, with the first version of the integrator. More recently, the integrator was ported back to Intel machines of later vintage, workstations of the Pentium series, Pentium Pro 200 MHz, and lately to a Pentium II 400 MHz. That the simulator delivered real-time performance<sup>12</sup> on these inexpensive platforms is a sign of the efficiency of the underlying algorithm. The integrator is portable.

7

<sup>&</sup>lt;sup>10</sup> Object Oriented Programming [34].

<sup>&</sup>lt;sup>11</sup> In OOP parlance, *behaviour* of an object describes one of the routines that can be applied to the object.

<sup>&</sup>lt;sup>12</sup> Within the target bandwidth and network size and configurations.

1. Introduction

Fig. 4: All element models look and behave the same from the point of view of the simulator's core.

The design allowed the exploration of avenues for improved efficiency: latency [2], dependent on the relatively different time constants of different sections of the network; and backtracking, to cope with switching not produced at one of the time points of the simulation [35].

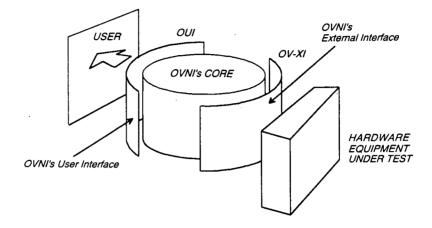

The integrator solution must respond as well to events generated at both interface ends, see Fig. 5. On the side of the user, OVNI interacts with OUI, OVNI's user interface [36, 37] (due either to configuration changes in the network, or to the connection or removal of probes, voltmeters, ammeters, oscillo-scopes, etc.). On the hardware end, OVNI interacts with OV-XI [36, 38], the back-end hardware interface with the real world (opening or closing signals, or gate signals for controlled rectifier groups).

Fig. 5: Front end and back end interfaces to OVNI's core.

#### 1.1 Research Claim and Contributions.

Our summarized claim is that "Real-time simulation of realistic power networks is possible using stock computer hardware." To demonstrate that claim, this thesis introduces as contributions: a) the use of backward Euler integration rule as a preferred method, and demonstrates its validity; b) a multi-layer segmentation scheme with: topological segmentation (introduced by lines time delay), an extended multi-area Thevenin equivalent concept segmentation, a node-hiding technique; c)a double-step double-interpolation technique to syncronize the simulation both with switching operations and with the real-time output stream with very low overhead.

Other central contribution was the implementation of the simulator around the OOP paradigm in C++, which is both efficient enough for real-time performance, and extensible to allow new models to be added without modifying the core. Also, a set of models was developed that prove the speed advantages of the proposed solution algorithm. The resulting simulator was tested on two real problems for real-time power networks simulation: a protective relay testing case, and an HVDC controller testing case.

# Part II

# THE PROBLEM

## 2. THE PROBLEM

#### 2.1 Real-Time Simulations

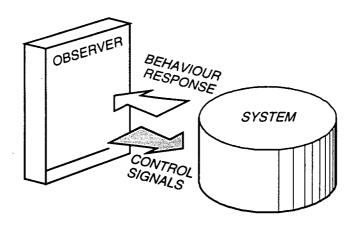

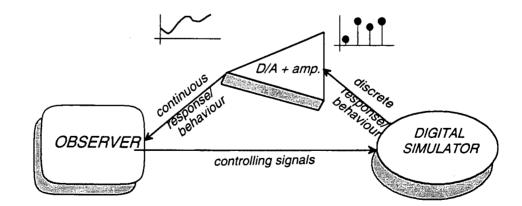

Real-time simulations stem from a situation like the one depicted in Fig. 6. An observer interacts with a system. The observer perceives the behaviour of the system, sends controlling signals to it, and watches the system's response to those signals; all this in a continuous cycle.

Fig. 6: An observer watching over and controlling a system.