# Optimum Test Strategy for SoCs Including wrapper and TAM design and optimization

bv

Zahra sadat Ebadi

B.A.Sc., Sharif University of Technology, 2000

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

The Faculty of Graduate Studies

(Department of Electrical and Computer Engineering)

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

December 4, 2002

© Zahra sadat Ebadi, 2002

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of Electrical and Computer Engineering

The University of British Columbia Vancouver, Canada

Date <u>Dec 6, 2002</u>

### Abstract

Using the large number of transistors available on a chip, designers have already managed to put an entire system on a single chip. These are referred to as System-on-a-Chip (SoC). Being able to rapidly develop, manufacture, test, debug and verify complex SoCs is crucial for the continued success of the electronics industry.

In the problem of SoC test integration three issues need to be addressed: wrapper design, TAM design and test scheduling. In this thesis, a novel wrapper design method is introduced to minimize the core test time, the number of test I/O pins and the required ATE memory. While previous methods for wrapper design only minimize the test time, the proposed method considers all of these factors in the test cost.

Also a novel TAM based on time domain multiplexing (TDM-TAM) is introduced. This TAM is P1500 compatible and uses a P1500 wrapper. Its characteristics are flexibility, scalability, and reconfigurability.

# Contents

| $\mathbf{A}^{\cdot}$ | bstra | ict                          |

|----------------------|-------|------------------------------|

| C                    | onter | nts                          |

| Li                   | st of | Tables vii                   |

| Li                   | st of | Figures ix                   |

| Ρı                   | efac  | e                            |

| $\mathbf{A}$         | ckno  | wledgements                  |

| 1                    | Intr  | oduction                     |

|                      | 1.1   | Motivation                   |

|                      | 1.2   | Research Goals               |

|                      | 1.3   | Thesis Organization          |

| 2                    | Bac   | kground and Previous Works 6 |

|                      | 2.1   | Overview of SoC Testing      |

|                      |       | 2.1.1 Wropper 7              |

| _ |     | Contents                                     | iv |

|---|-----|----------------------------------------------|----|

|   |     | 2.1.2 TAM                                    | 12 |

|   | 2.2 | Wrapper Optimization Methods                 | 16 |

|   | 2.3 | TAM Optimization Methods                     | 17 |

|   | 2.4 | Focus and Contributions                      | 20 |

| 3 | Wr  | apper Design                                 | 23 |

|   | 3.1 | Wrapper Design Issues                        | 23 |

|   | 3.2 | Wrapper Design w.r.t. Test Time              | 24 |

|   |     | 3.2.1 TAM Chain Design                       | 24 |

|   |     | 3.2.2 Ordering of TAM Chain Elements         | 29 |

|   |     | 3.2.3 Partitioning of TAM Chain Elements     | 30 |

|   | 3.3 | Wrapper Design w.r.t. Area                   | 42 |

|   | 3.4 | Wrapper Design w.r.t. the ATE Memory         | 45 |

|   |     | 3.4.1 Wrapper Design Algorithm to Reduce UMA | 55 |

|   |     | 3.4.2 ATE Deployment Procedure to Reduce UMA | 60 |

|   | 3.5 | Wrapper Design for Flexible Cores            | 61 |

|   | 3.6 | Experiments                                  | 67 |

|   | 3.7 | Conclusions                                  | 75 |

| 4 | Tin | ne Domain Multiplexed TAM                    | 76 |

|   | 4.1 | Basics                                       | 77 |

| v |

|---|

|   |

|              | 4.3   | Overhead Area Model                 |

|--------------|-------|-------------------------------------|

|              | 4.4   | Dynamic Masking                     |

|              |       | 4.4.1 Multi-Frequency SoC           |

|              | 4.5   | Optimization                        |

|              | 4.6   | Case Study                          |

|              |       | 4.6.1 Platform Description          |

|              |       | 4.6.2 Results                       |

|              | 4.7   | Conclusions                         |

| 5            | Con   | clusions                            |

|              | 5.1   | Future Work                         |

|              | 5.2   | Contributions of this Work          |

| Bi           | bliog | raphy                               |

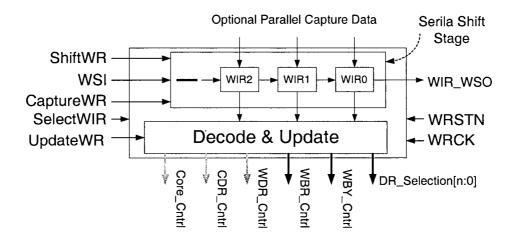

| $\mathbf{A}$ | P15   | 00 Wrapper Elements                 |

|              | A.1   | Wrapper Boundary Cells              |

|              | A.2   | Wrapper Interface Port (WIP)        |

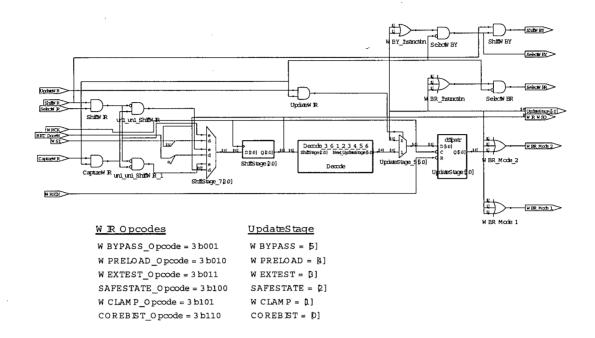

|              | A.3   | Wrapper Instruction Register (WIR)  |

|              | A.4   | Bypass Register                     |

| В            | Min   | imum Makespan Problem               |

|              | B.1   | Problem Formulation                 |

|              |       | B.1.1 Strongly NP-complete Problems |

|     |        | Contents                                          |

|-----|--------|---------------------------------------------------|

| B.2 | Heuris | stics for Solving the Problem                     |

|     | B.2.1  | An Example using the LIST Heuristic               |

|     | B.2.2  | An Improvement: The LIST DECREASING Heuristic 130 |

| B.3 | Polyno | omial Approximation Scheme to "Makespan" 135      |

# List of Tables

| 1.1 | Manufacturing test cost issues                               | 3  |

|-----|--------------------------------------------------------------|----|

| 3.1 | List Decreasing Algorithm                                    | 35 |

| 3.2 | Using Bin-packing solution to solve MPS                      | 36 |

| 3.3 | Using First Fit Decreasing to solve MPS                      | 37 |

| 3.4 | Best Fit Decreasing Algorithm (BFD)                          | 38 |

| 3.5 | The maximum scan-in/scan-out length of the assignment of     |    |

|     | core internal scan chains to TAM chains for core 6 of p93791 |    |

|     | of ITC'02 benchmarks                                         | 39 |

| 3.6 | Adding wrapper input/output cells to TAM chains              | 40 |

| 3.7 | Adding wrapper input/output cells to minimize UMA            | 57 |

| 3.8 | ATE deployment procedure                                     | 61 |

| 3.9 | The result of the wrapper design algorithm for S1196 of IS-  |    |

|     | CAS'89 Benchmarks                                            | 67 |

| 3.10 | The result of the wrapper design algorithm and comparisons |

|------|------------------------------------------------------------|

|      | with previous works for core 6 of p93791 of the ITC'02 SoC |

|      | Test Benchmarks                                            |

|      |                                                            |

| 4.1  | Area estimates for TDM-TAM controller block 86             |

| 4 2  | U226 from ITC SoC'02 benchmarks                            |

| 1.2  |                                                            |

| 4.3  | Test data for the cores in D695                            |

| 11   | Test data for the cores in D695                            |

| 7.7  | Test data for the cores in Doss                            |

| 4.5  | Overhead area comparison                                   |

| 4.6  | Scenarios for assessing TAM performance                    |

|      |                                                            |

# List of Figures

| 1.1 | Example of System-on-Chip (SoC)                         | 1  |

|-----|---------------------------------------------------------|----|

| 2.1 | SoC test integration steps                              | 7  |

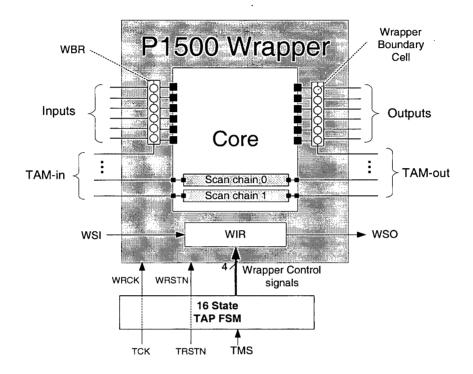

| 2.2 | Conceptual view of IEEE P1500 wrapper                   | 11 |

| 2.3 | Conceptual TAM architecture                             | 12 |

| 2.4 | TAM using bus-based connection                          | 15 |

| 2.5 | TESTRAIL architecture for TAM [41]                      | 16 |

| 2.6 | Comparison of result using ILP [14] and GA [19]         | 19 |

| 2.7 | Example of result of the system in [19]                 | 20 |

| 3.1 | Ordering of TAM chain elements                          | 29 |

| 3.2 | A conceptual view of TAM elements partitioning over TAM |    |

|     | chains                                                  | 33 |

| 3.3 | The scan-in length length vs. TAM width                 | 42 |

| 3.4 | Wrapper design for core 6 in P93791 SoC from ITC'02 for |    |

|     | TAM of width 38                                         | 45 |

| 3.5 | Useless Memory Allocation                               | 48 |

| 3.6               | Alternative wrapper design with equal test time              | 50             |

|-------------------|--------------------------------------------------------------|----------------|

| 3.7               | TAM chain design and ATE memory bitmap when $s_i < s_o \;$   | 52             |

| 3.8               | TAM chain design and ATE memory bitmap when $s_i = s_o \;$   | 53             |

| 3.9               | ATE test vector deployment                                   | 55             |

| 3.10              | Wrapper design for S1196 from ISCAS'89 benchmarks            | 66             |

| 3.11              | The final wrapper design for core 6 of p93791 from ITC'02    |                |

|                   | SoC test benchmarks for TAM width=38                         | 70             |

| 3.12              | New TAM width for core test vs. given TAM width              | 72             |

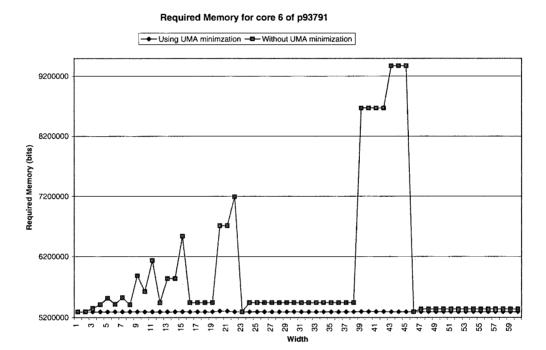

| 3.13              | Required memory for core test vs. TAM width                  | 73             |

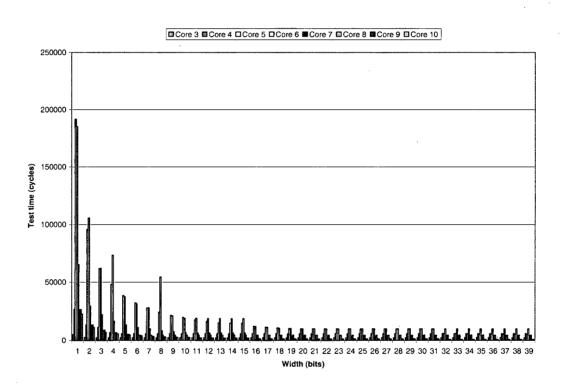

| 3.14              | Core test time vs. TAM width                                 | 74             |

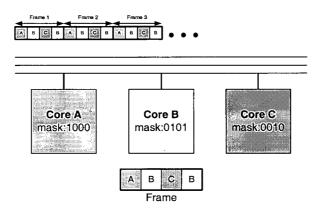

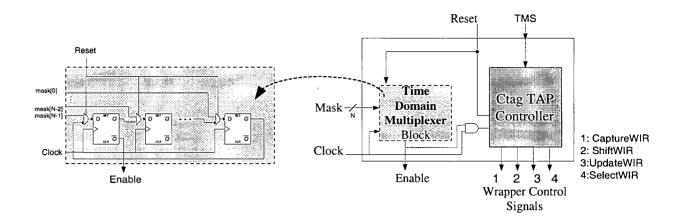

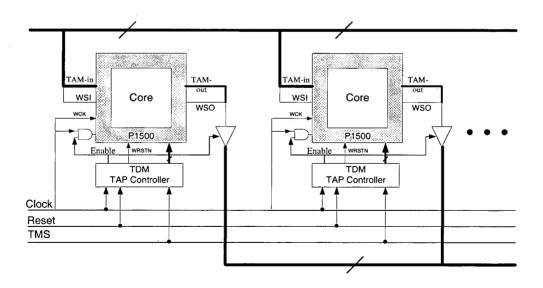

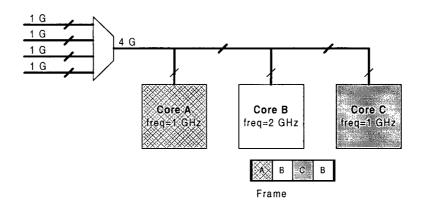

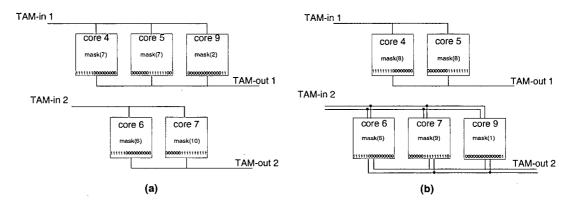

| 4.1               | Example illustrating the concept of Time Domain Multiplex-   |                |

|                   |                                                              |                |

| •                 | ing (TDM)                                                    | 77             |

| 4.2               | ing (TDM)                                                    | 77             |

| 4.2               |                                                              |                |

| 4.2               | Conceptual view of the IEEE P1500 wrapper and TAP con-       |                |

|                   | Conceptual view of the IEEE P1500 wrapper and TAP controller | 78<br>79       |

| 4.3               | Conceptual view of the IEEE P1500 wrapper and TAP controller | 78<br>79<br>80 |

| 4.3<br>4.4        | Conceptual view of the IEEE P1500 wrapper and TAP controller | 78<br>79<br>80 |

| 4.3<br>4.4<br>4.5 | Conceptual view of the IEEE P1500 wrapper and TAP controller | 78<br>79<br>80 |

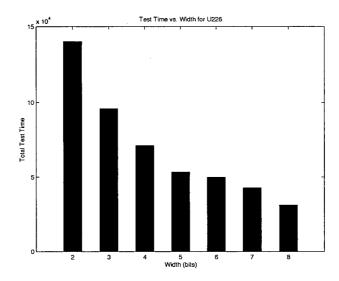

| 4.7  | Benchmark U226: Test time (cycles) vs. total effective TDM-     |

|------|-----------------------------------------------------------------|

|      | TAM width for two-branch configurations                         |

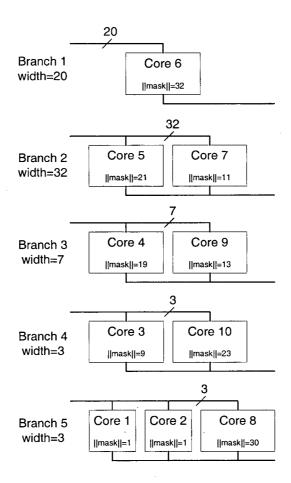

| 4.8  | Benchmark D695: Design for minimum test time, 5 branches,       |

|      | with mask 32 bits and, total width=65, total test time=9869. 97 |

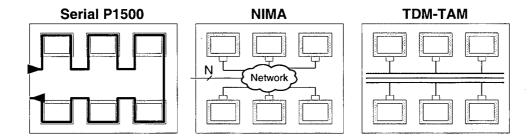

| 4.9  | TAM architectures considered in our comparison 100              |

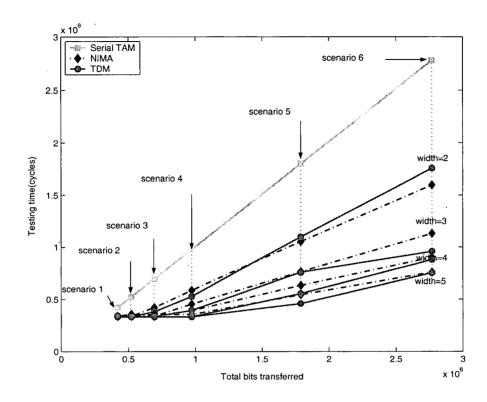

| 4.10 | Test Time for Serial P1500, NIMA, and TDM-TAM 106               |

| Δ 1  | P1500 Wrapper Boundary Cells                                    |

|      | P1500 Wrapper Boundary Cell: Cell Example Displaying all        |

|      | Events                                                          |

| A.3  | P1500 Wrapper Interface Port (WIP)                              |

| A.4  | P1500 Wrapper Instruction Register Circuitry                    |

| A.5  | P1500 Wrapper Instruction Register: Example Implementation 125  |

| A.6  | P1500 Wrapper Bypass Register                                   |

| A.7  | P1500 Wrapper Bypass Register: Example Implementation 126       |

Preface xii

# **Preface**

These papers have been published earlier:

- Z. Ebadi, A. Ivanov, "Design of an optimal test access architecture using genetic algorithm", Proc. IEEE Asian Test Symposium (ATS), pp. 205-210, 2001.

- 2. Z. Ebadi, A. Ivanov, "Design of an Optimal Test Access Architecture under Power and Place-and-Route Constraints using GA", Proc. IEEE Latin-American Test Workshop(LATW), pp. 154-159, 2002.

- 3. Z. Ebadi, A. Ivanov, "Time Domain Multiplexed TAM: Implementation and Comparison", will apear in Proc. Design Automation and Test in Europe, March 2003.

# Acknowledgements

I would like to dedicate this thesis to my parents, Seyyed Mohammad and Seyyedeh Hajar Ebadi, and my dear husband, Alireza Nasiri Avanaki, who was my mentor during my studies in UBC.

I had the pleasure of being a member of the SoC research group at UBC.

I would like to thank my fellow researchers in this group for their support and ideas.

This work is supported by Micronet, the Canadian Microelectronics Corporation, and the Natural Sciences and Engineering Research Council of Canada. Their support is greatly appreciated.

I would like to thank Dr. Andre Ivanov for his encouragement and invaluable advice. Also I would like to thank Dr. Resve Saleh for his helpful discussions.

# Chapter 1

# Introduction

#### 1.1 Motivation

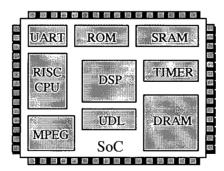

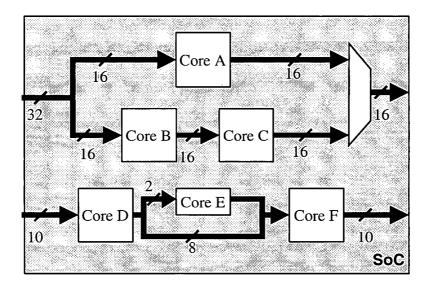

Spurred by technology which makes millions of gates per chip now available, system-level integration is evolving as a new paradigm, allowing an entire system to be built on a single chip, referred to as *System-on-a-Chip* (SoC; Figure 1.1). The advantages of an SoC over its conventional multi-chip counterpart include higher performance, lower power consumption, higher density and lower weight.

Figure 1.1: Example of System-on-Chip (SoC).

In SoC design, using complex, pre-designed and pre-verified functional

blocks (modules) allows greater on-chip functionality, and leads to shorter product development cycles. These reusable modules are called *Embedded Cores*, while the reuse design style is known as a core-based design. A few examples of reusable cores include CPUs, DSPs and embedded memories.

Being able to rapidly develop, manufacture, test, debug and verify complex SoCs is crucial for the continued success of the electronics industry. To make production practical and cost effective, however, the International Technology Roadmap for Semiconductors (ITRS) identifies a number of major hurdles to be overcome [5]. Among these problems, testing and diagnosis of SoCs is the most important. Many experts believe that testing SoC chips will be the bottleneck of future designs if issues of DFT (design for testability) for SoCs are not addressed [41, 54]).

ITRS introduces "Manufacturing Test Cost" as a difficult challenge (through 2007) to be solved in the short term. The most important issues involved in manufacturing test costs are shown in Table 1.1.

Table 1.1 makes it obvious that DFT methods that reduce test cost by minimizing test I/O pin, test time, and equipment reuse, are desired. Also, since using such DFT methods leads to longer test development time, automatic test program generators are required. The research reported in this thesis focuses on DFT methods for SoCs to reduce test costs and also develop tools to automate generating test circuitry for SoCs.

Difficult Challenge

through 2007

Test cell throughput enhancements are needed

to reduce manufacturing costs.

Device test needs must be managed through

DFT to enable low-cost manufacturing test

solutions; including reduced pin count test,

equipment reuse, and reduced test time.

Automatic test program generators are

needed to reduce test development time.

Table 1.1: Manufacturing test cost issues (from Table 19 in [5]).

#### 1.2 Research Goals

For the problem of SoC test integration three issues need to be addressed: wrapper design, test access mechanism (TAM) design and test scheduling. The wrapper forms the interface between the embedded core and its system chip environment, and provides switching capability between the normal operation mode and test mode. A TAM is used to deliver test data to the cores and also to transfer test response from the cores to the sink where it is evaluated. Test scheduling focuses on determining the start time of the various core tests, such that no resource conflict occurs with respect to the test access infrastructure from I/O pins to core terminals, and vice versa [21].

The test cost of an SoC depends on three major factors: (1) test time, (2) test input/output (I/O) pins, and (3) Automatic Test Equipment (ATE) machine resources. In an SoC integration problem, it is desirable to minimize

test cost by minimizing the test cost factors.

Therefore, the goal here is to design and develop a computer-aided-design (CAD) tool which facilitates shorter test development time. Using this tool SoC designers can design the "optimal" test circuitry (with the minimum test cost).

The first two issues concerning SoC testing and their optimization are addressed extensively in this thesis, both theoretically and experimentally. Software has also been developed for optimal SoC testing in two steps: a core wrapper design for each individual core within the SoC, and a TAM design for the entire SoC.

In the first step, the wrapper that optimizes the core's test cost (by minimizing all the important test cost factors), is designed for each core. In the second step, the optimal TAM configuration for SoC are derived to optimize test cost (by minimizing test time and test I/O pins).

#### 1.3 Thesis Organization

The remainder of this thesis is organized as follows. Chapter 2 provides an overview of basic concepts of SoC testing such as wrapper, TAM, and so forth. It also describes previous work on wrapper and TAM design and optimization. This work on TAM optimization [19, 20] is addressed in this chapter.

Chapter 3 describes wrapper design and optimization. In this chapter, a novel wrapper design method is introduced to minimize the core test time, the TAM width (translates to test I/O pins) and the required ATE memory. Superior performance of my method as compared to existing methods is proved through several experiments.

Chapter 4 proposes a novel TAM based on time domain multiplexing (TDM-TAM), which can especially handle multi-frequency SoCs. It also provides TDM-TAM characteristic details and a comparison to the two other approaches.

The thesis is concluded with a summary, possible directions for future research, and the contributions this project has made to the SoC test research community.

# Chapter 2

### Background and Previous

### Works

This chapter presents an overview of basic concepts of SoC testing, along with a background on wrapper and TAM design and optimization methods. Also, the focus and contribution of this research project are presented.

### 2.1 Overview of SoC Testing

In a core-based design, the system integrator is responsible for putting together a test strategy (for all embedded cores, and User Defined Logics (UDLs) and interconnect wiring) for the entire system chip.

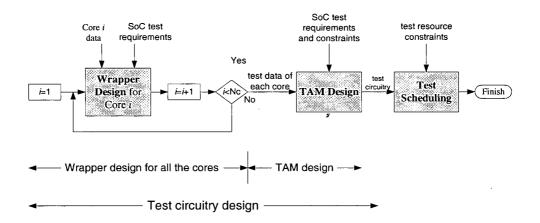

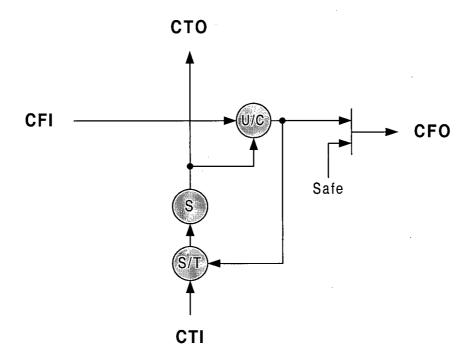

The SoC test integration steps are shown in Figure 2.1. The wrapper concept and existing wrappers in the literature are discussed in Section 2.1.1. The definition of TAM and different types of TAM design are reviewed in Section 2.1.2. For test scheduling, given a set of tests for each core in the SoC and a set of test resources (e.g., TAM), a test plan for conducting the tests

on the SoC is derived. Test scheduling is the last step of SoC test integration, however, it is not part of test circuitry design and can usually be done after tape out; thus, it is not in the scope of this research.

Figure 2.1: SoC test integration steps.

#### 2.1.1 Wrapper

A wrapper is a shell around the core that integrates it with its surroundings and provides an isolation mechanism for testing purposes. A wrapper acts like a switch between normal functional access and test access, providing a mechanism for core test data access and core test isolation; it allows the tester to control core inputs and observe core outputs via the TAM, so that the core's internal test can be re-applied at the SoC level. To avoid any damage to the SoC, a core has to be isolated when it, or one of its neighboring cores or UDLs, is tested.

Furthermore, a wrapper should have additional modes so that the isolated core can interface with available test access paths and assume internal states necessary for the core's own test execution, as well as testing external interconnects and UDLs. Therefore, a well-designed wrapper can handle both core-internal testing and core-external testing. In order to achieve these objectives, the following capabilities are potentially required at core terminals:

- Input Observation: This capability allows logic values of the core input terminals (which are supplied by external logic) to be observed by the wrapper.

- Input Control: This wrapper function allows test data to be applied to the core input terminals.

- Input Constraint: Allows forcing or limiting core input terminals to fixed logic values. Input constraint can be useful during testing to prevent damage to the core, reduce power consumption, and so forth.

- Output Observation: This capability allows for the observation of logic values of the core output terminals (which are propagated from internal logic) at the wrapper.

- Output Control: This wrapper function allows test data to be applied at the core output terminals by the wrapper, such that the test data can be propagated to the system chip logic external to the core.

- Output Disable: Allows forcing tri-sate core outputs to their inactive state. This is useful in preventing damage to other tri-state drivers on the same bus during the test application.

- Output Constraint: This allows constraining appropriate non-trisate core output to fixed logic values in order to prevent damage to the logic external to the core and reduce its power consumption.

There are several proposed core test wrappers in the literature. A core test wrapper called *TestShell* [41] has been proposed by Marinissen, and is currently being used by Philips. This wrapper supports four basic modes: (1) normal (functional), (2) core test, (3) interconnect test and, (4) bypass. In this approach, TAMs are called TestRail. In principle, a TestShell is connected to the same TestRail at both input and output. Therefore, the TAM input plug and the TAM output plug of a TestShell normally have the same width.

Varma and Bhatia of Duet Technologies described a very similar wrapper, called *Test Collar* [50]. Aside from the different naming of basically similar features, the main difference between this wrapper and TestShell is that the Test Collar does not have a bypass feature.

The IEEE P1500 Standard for an Embedded Core Test (SECT; under development) [4] consists of two components: a *Core Test Language* to facilitate the test knowledge from the core provider to the core user, and a *Core*

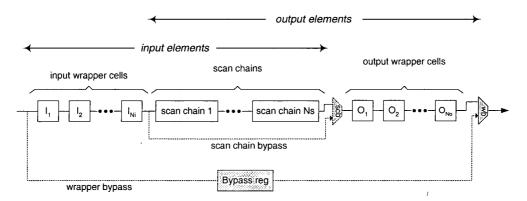

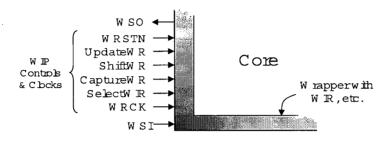

Test Wrapper [44]. The P1500 wrapper (see Figure 2.2), which satisfies all of the functional requirements mentioned above, is composed of the following:

- Wrapper Boundary Cells: These are associated with the core terminals.

They provide controllability as well as observability. Together, these cells make the Wrapper Boundary Register.

- Wrapper Instruction Register (WIR): This is used to load instructions to control the operation of the wrapper.

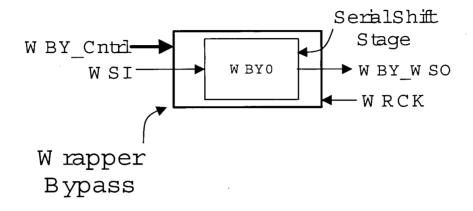

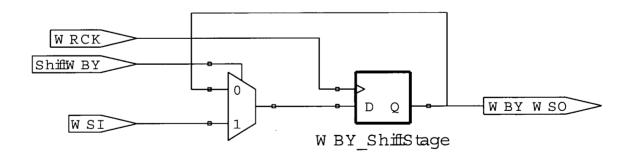

- Bypass Register: This is the bypass for the Serial Interface Layer (SIL).

- Wrapper Interface Port (WIP): This is for the control of wrapper registers via SIL. It comprises control and data signals for accessing DFT features of the target core.

A detailed description of P1500 core test wrapper elements is reported in Appendix A.

The P1500 wrapper connects to one mandatory one-bit wide TAM, Wrapper Serial Input/Output (WSI/WSO), and zero or more scalable-width TAMs (TAM-in/TAM-out). A minimal compliant implementation has only the single-bit TAM plug, through which both test control values for the WIR, as well as test stimuli and responses are transported. Envisaged typical usage has one multi-bit TAM next to the mandatory TAM. In this case, access to the bulk test data is performed along the multi-bit TAM, while the single-

Figure 2.2: Conceptual view of IEEE P1500 wrapper [44].

bit TAM is used to program the WIR, and possibly transport test data in a silicon debug scenario. TAM-in and TAM-out need not have the same width.

This research on optimal wrapper design (Chapter 3) is based on the P1500 wrapper standard. The previous works on wrapper design and optimization are reported in Section 2.2.

#### 2.1.2 TAM

Since cores in an SoC are not directly accessible via chip inputs and outputs, special access mechanisms are required to test them at the system level.

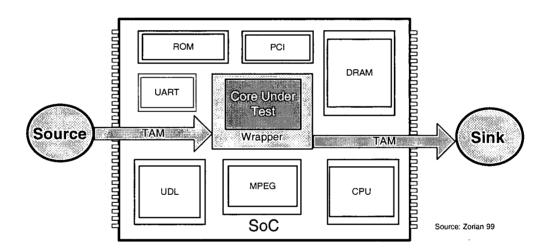

Zorian et al. [54] proposed a generic conceptual test access architecture for embedded cores, with the following components: source, sink, and TAM (Figure 2.3). A TAM is used to deliver test stimuli from the source (which generates test stimuli) to cores, and also to deliver responses from cores to the sink (which evaluates test responses).

Figure 2.3: Conceptual TAM architecture.

In this architecture (Figure 2.3), both source and sink can be either onchip or off-chip. The TAM is not only the physical mechanism that connects source and sink to the core, but also includes the control signals needed for this connection. The IEEE P1500 proponents, accepting the fact that test schemes for each core cannot be standardized, specifically decided not to standardize the design for the TAM. Hence, the TAM design is left to the SoC integrator.

Several TAM architectures are suggested. These architectures can be classified into four categories: (1) multiplexing, (2) serial connection, (3) indirect access and (4) bus-based connection.

In the first category, multiplexing is uses to access the cores. The simplest method in this category directly multiplexes the test pins to the primary inputs/outputs (I/O) [30]. Another method modifies the cores such that each core has a transparent mode for testing [22]. There are several problems with the multiplexing TAM methods, such as limited scope of use for future complex SoCs, large overhead area, long test time, and non-scalability of the architecture.

TAMs in the serial connection category [40, 49, 52] use the established IEEE 1149.1 standard. For a few cores on an SoC, it may be possible to spend time transporting the test vectors serially to the cores. However, as the number and complexity of the cores increases, a serial solution based on the IEEE 1149.1 standard, or its variants, proves too costly in terms of test time.

There are some proposed methods that implement TAM without a direct path from I/Os to each core. One of these methods is Networked Indirect

and Modular Architecture (NIMA) proposed in [45], where the emphasis is placed on modularity, generality, and configurability of the architecture. The basis of NIMA is the establishment of indirect digital communication paths among cores using packet-switching connections. It is assumed that all test-related communications destined and/or originated to or from the SoC need to be communicated by the on-chip network.

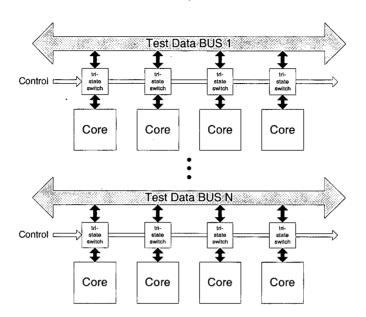

Bus-based connection schemes are the most common TAM architecture. A number of different variations of the scheme are reported in [41, 50, 53]. The idea is to have parallel access to the cores using a shared medium on which data is broadcasted. Bus access control is usually provided by tristate switches (Figure 2.4). In terms of trading-off increased overhead area to reduce test access time, bus-based architectures are the most efficient TAM schemes suggested to date.

Marinissen and others [41] suggest a topology (as a bus-based TAM) where cores are connected in a rail configuration, and buses have different widths, fan-in, and fan-out. If needed, each core can be bypassed to access the next one in line, and control is achieved by a serial connection. This architecture is conceptually illustrated in Figure 2.5 (the control signals for the bypass elements are not shown). Test data is normally passed through the bypass elements and the corresponding cores are inhibited in this mode. When the data has to be applied to a core, the bypass element is inhibited

Figure 2.4: TAM using bus-based connection.

and the corresponding core reads the data. The wrapper configuration used for each core (not shown in the diagram) closely resembles that of the first draft of IEEE P1500.

Using the bus width as the varying parameter, TAM architectures based on a bus provide some degree of adaptability and configurability for the designer: increased overhead area is traded-off for reduced test access time to design for the best case. In Section 2.3 previous work on TAM optimization are reported.

Figure 2.5: TESTRAIL architecture for TAM [41].

### 2.2 Wrapper Optimization Methods

The existing wrapper optimization methods are mostly based on the P1500 wrapper standard. The publications on P1500, however, provide only general guidelines for wrapper design, and details are left to the core user. For example, a wrapper may provide width adaption in case of a mismatch between the core I/O width and TAM width (e.g. by serial-parallel and parallel-serial conversion). Interconnection between the wrapper cells, core-internal scan chains and TAM plugs effect core test time, required TAM width, and also required ATE memory.

Marinissen [42] proved that the unbalanced TAM scan chains (i.e. the scan chains formed by internal scan chains and the core's inputs/outputs

having unequal lengths; see Section 3.2.1) of the wrapper lead to longer core test time. He suggested a method to balance the TAM scan chains of the wrapper, aimed at minimizing core test time [42].

Iyengar [32, 34, 35] not only improved Marinissen's method of reaching shorter test times, but also considered minimizing TAM width while keeping the test time at the minimum.

Gonicari [24] addressed useless memory allocation (UMA) as an issue in wrapper design. To reduce on-chip control when feeding embedded core's multiple scan chains, the test vectors are augmented with useless data to account for their unequal lengths (Section 3.4). Gonicari proposed a new test methodology which merges core wrapper design and ATE memory management problems. His core wrapper design is capable of finding the minimum number of TAM scan chain partitions, so that for each partition, useless memory is minimized.

### 2.3 TAM Optimization Methods

An efficient TAM should reduce test costs by minimizing test application time and test I/O pins. Since there is no standard for a TAM configuration, each type of TAM has its own optimization method. Usually for any proposed TAM, optimization is also addressed as part of the TAM solution. However, sometimes the problem of TAM optimization for a general bus-based

configuration is also addressed.

Chakrabarty [14, 16, 31] addressed several issues in optimal TAM design with respect to test time, for example, assignment of cores to the test buses, the distribution of the test width among multiple test buses, and the estimation of TAM width required to satisfy an upper bound on testing time. All of these problems are proved to be NP-complete, and therefore, in [14, 16] integer linear programming (ILP) is used to solve them.

As an extension of previous work, Chakrabarty [15] proposed a method of designing the optimum TAM (using ILP) considering system level constraints on power consumption and place-and-route (arising from the functional interconnections amongst the cores). All of his work [14–16] required serialization at all the cores' I/Os.

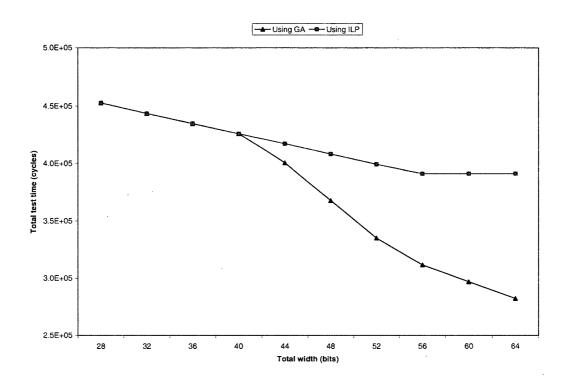

As part of this research, the TAM optimization problem was. The same issues as Chakrabarty (cores assigned to buses, width distribution and required width estimation) were investigated. However, the necessity of serialization constraint was removed, which allowed the system to handle serial or parallel loading of test data for any core; this improves the test time for up to 40%. The implementation of the proposed method was built around a genetic algorithm (GA). In Figure 2.6 this method [19] is compared to Chakrabarty's [14].

In another work, the proposed method have been improved to handle the

Figure 2.6: Comparison of result using ILP [14] and GA [19].

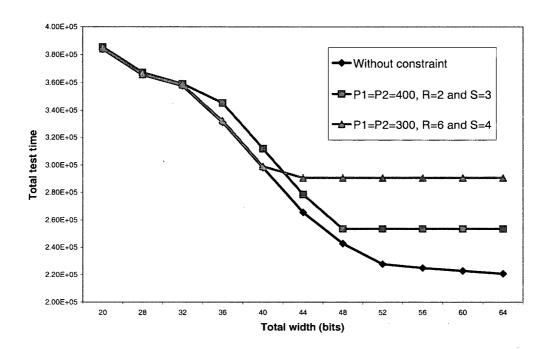

power and place-and-route constraints [20]. In this work the proposed system was able to find an optimal test architecture with four options: (1) without any constraint, (2) with a power consumption constraint, (3) with a place-and-route constraint, and (4) with power consumption and place-and-route constraints. An example of the results of the proposed system is shown in Figure 2.7.

In some works the problem of wrapper and TAM optimization are combined and solved together [33–36]. For example, in [33], the wrapper design algorithm (which minimizes test time and TAM width) calculates test time

Figure 2.7: Example of result of the system in [19].

values that are used by a mathematical model for TAM optimization.

#### 2.4 Focus and Contributions

The goal for this research project is to build a tool for designing a test circuitry for SoC test integration. As it is shown in Figure 2.1, the first step is wrapper design. In this thesis, a new method for wrapper design regarding all important test cost factors, including test time, required width, and required ATE memory is proposed. As reported in Section 2.2, all previous works consider only one or two of the major factors. The proposed approach not

only considers all the major test cost issues, but also, its performance is better than the previous methods (e.g., lower test time as compared to the methods that just minimize test time [32, 42]). Also, the proposed method is implemented as a tool for optimal wrapper design for a given core. The details of wrapper design and optimization are discussed in Chapter 3.

In Chapter 4, a novel TAM based on time domain multiplexing (TDM-TAM) is proposed. This TAM is P1500 compatible, and uses a P1500 wrapper. TDM-TAM characteristics are flexibility, scalability, and reconfigurability. Also, this TAM could be very useful for testing multi-frequency SoCs because with TDM, we can manipulate frequency. The concept of TDM-TAM is expanded theoretically and experimentally. The optimization method is tailored specifically for TDM-TAM based on my previous work in TAM optimization [19, 20]. The efficiency of TDM-TAM is proved by a comparison with two other TAMs.

The contributions of this thesis are summarized as follows:

- A novel wrapper design algorithm considering all major components of test cost.

- 2. A novel TAM based on time domain multiplexing with the following special characteristics:

- P1500 standard compatible

- Reconfigurability (even after fabrication)

- Low overhead area and acceptable test time

- Ability to handle multi-frequency SoCs without expensive ATE and complicated ATE programming

- 3. Specific optimization algorithms for TDM-TAM based on previous work on TAM optimization is reported in [19, 20].

# Chapter 3

# Wrapper Design

This chapter introduces the important issues in wrapper design. Next, the TAM chain design problem is addressed and existing methods for this problem are reviewed. A new method is introduced that improves wrapper design to minimize area and ATE (Automatic Test Equipment) resources, as well as core test time. Finally, wrapper design for flexible cores is elaborated.

# 3.1 Wrapper Design Issues

There are many important factors to consider in the design of wrappers. Anything that has an impact on the test cost can be a factor. The most important part of the test cost is known to be determined by the test time. The silicon area is also a factor of the test cost. Another factor is the number of I/O pins in the test cost, because the number of I/O pins is limited by area. That is, as the number of I/O pins increase, we need a larger area so the test cost increases. The resources of an ATE machine can also be counted as a factor of the test cost. Since we need more resources from an

ATE, such as memory, we have to employ a more expensive ATE, which has a large impact on the test cost. To summarize, the factors that should be considered are as follows:

#### • Test Time

- Core Internal Test Time: core test time

- Core External Test Time: interconnection test time

#### • Area

- Silicon Area

- I/O Pins

#### • ATE Resources

- Memory

- I/O Pins

# 3.2 Wrapper Design w.r.t. Test Time

### 3.2.1 TAM Chain Design

One of the most important tasks in wrapper design, which has a direct impact on the core test time, is to make the interconnection between the wrapper boundary cells, the core internal scan chains, and the TAM lines (plugs). We refer to this task as TAM chain design. Also, we call the elements that make up a TAM chain (wrapper input cells, core internal scan chains and wrapper output cells), TAM chain elements. Access to the core for testing is already guaranteed if all the TAM chain elements are accessible from the TAM plugs. In this section, it will be shown that the ordering and partitioning of TAM chain elements has a large impact on the size of the resulting test vectors set. Also, it is obvious that the size of the test vector set is an important cost factor in the testing of ICs. When the test vector set is large, not only the application test time is long, but also, expensive pieces of equipment with large pin memories to store those vectors are required to test the IC. Therefore, the reduction of the size of the test vector results in the reduction of test cost.

Wrappers are used for both core-internal and core-external tests. Designing the wrapper to optimize the test vector set for a core-internal test might lead to a conflict with the test vector set optimizing for a core-external test. Usually, the core-internal circuitry is much larger than the circuitry used to interconnect the cores. Therefore, the test data volume involved in core-internal testing is much larger than the test data volume for core-external testing. Also, in many cases, the wrapper is designed by the core provider to whom the circuit environment in which the core is used is unknown, and data about the core-external test is not available at the wrapper design time.

Therefore, we give priority to optimizing the core-internal test vector set, and the wrapper is designed without considering the core-external test.

The test time T (in clock cycles) of a core is determined [23] by the scan-in length  $s_i$ , the scan-out length  $s_o$ , and the number of test patterns  $N_P$ :

$$T = (1 + \max(s_i, s_o)) \cdot N_P + \min(s_i, s_o)$$

(3.1)

This equation assumes that the scan-out operation of one pattern is overlapped with the scan-in of the subsequent test pattern, and that the actual test application costs one clock cycle. In regular scan testing, typically  $s_i = s_o$ . Since in the wrapped cores, the scan chains also include wrapper cells for core terminals, and the number of core input terminals might differ from the number of core output terminals [42], then  $s_i$  and  $s_o$  might be different for these. Note that this formula is valid even for non-scan-testable cores, for which  $s_i = s_o = 0$ .

**Theorem 3.2.1** For a core with  $N_I$  inputs,  $N_O$  outputs,  $N_S$  scan chains of length  $l_1, l_2, \dots, l_{N_S}$  respectively and  $N_P$  test patterns, the lower bound on the core test time, T, is given by the following:

$$T_{lower} = N_P l_{max} + N_P + l_{max}$$

and the minimum TAM width required to achieve this test time's lower bound

is given by  $W_{min}$ , as follows:

$$W_{min} = \lceil \frac{L + \max(N_I, N_O)}{l_{max}} \rceil^*$$

where  $l_{max} = \max_{i=1,\dots,N_S} l_i$  and  $L = \sum_{i=1}^{N_S} l_i$ .

**Proof** Since in best case, each TAM chain element is on one TAM line, so  $s_i$  and  $s_o$  cannot be less than  $l_{max}$ . In the best case the longest internal scan chain is on a private TAM chain making  $s_i = s_o = l_{max}$ . Substitution of these values into Equation (3.1) gives the lower bound for the test time  $N_P l_{max} + N_P + l_{max}$ . Also, the minimum width required to achieve this lower bound is in the case where  $s_i = s_o = l_{max}$  for all the TAM chains. As well, we know that  $s_i \geq \frac{L+N_I}{W}$ , and  $s_o \geq \frac{L+N_O}{W}$ , giving us the following:

$$s_i \geq \frac{L + N_I}{W}, s_i = l_{max} \Longrightarrow l_{max} \geq \frac{L + N_I}{W} \Longrightarrow W \geq \frac{L + N_I}{l_{max}}$$

$$s_o \ge \frac{L + N_O}{W}, s_o = l_{max} \Longrightarrow l_{max} \ge \frac{L + N_O}{W} \Longrightarrow W \ge \frac{L + N_O}{l_{max}}$$

Therefore,  $W \geq \frac{L+\max(N_I,N_O)}{l_{max}}$ . However, W can only take integer values, so  $W \geq \lceil \frac{L+\max(N_I,N_O)}{l_{max}} \rceil.$

**Theorem 3.2.2** For a core with  $N_I$  inputs,  $N_O$  outputs,  $N_S$  scan chains of length  $l_1, l_2, \dots, l_{N_S}$  respectively, and  $N_P$  test patterns, the upper bound on

<sup>\*[.]</sup> denotes rounding to the closest larger integer.

the core test time, T, is given by the following:

$$T_{upper} = (1 + L + \max(N_I, N_O))N_P + L + \min(N_I, N_O)$$

where  $L = \sum_{i=1}^{N_S} l_i$ .

**Proof** The worst case for test time is when only a one-bit wide line is used for TAM. In this case all the scan chains and inputs and outputs are on one TAM line, so  $s_i = L + N_I$  and  $s_o = L + N_O$ . By substituting in Equation (3.1), the upper bound of the test time is  $(1 + L + \max(N_I, N_O))N_P + L + \min(N_I, N_O)$ .

In our test architecture design approach, we distinguish two types of cores:

- Cores with *fixed-length* scan chains: cores for which the numbers and the lengths of the internal scan chains are fixed. Examples of such cores are hard cores and firm cores after scan insertion. When designing an SoC-level test architecture, we have to cope with the fixed scan chain parameters.

- Cores with *flexible-length* scan chains: cores for which the numbers and lengths of the internal scan chains are determined during test architecture design. Examples of such cores are soft cores and firm cores before scan insertion. Such cores provide better opportunities to minimize test time, as we can tune their scan chain parameters to fit the overall SoC.

In all the sections of this chapter, except Section 3.5, we assumed all the cores have fixed-length scan chains.

### 3.2.2 Ordering of TAM Chain Elements

From the set of all TAM chain elements, two non-disjoint subsets are involved in the loading and unloading of test patterns. The wrapper input cells and the core-internal scan chains (we refer to these as the *input elements*) participate in loading of test patterns, while the wrapper output cells and core-internal scan chains (we refer to these as the *output elements*) participate in the unloading of test patterns. In order to reduce  $s_i$  and  $s_O$ , it is best to order the items in any TAM chain such that the *input elements* are at the head, and the *output elements* are at the tail of the TAM chain. However, considering that core-internal scan chains are in both sets, the elements should be ordered in the following way: (1) wrapper input cells, (2) core-internal scan chains, and (3) wrapper output cells.

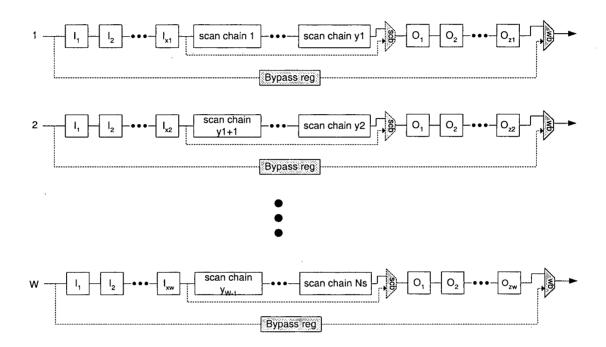

Figure 3.1: Ordering of TAM chain elements (optional items are dashed).

In Figure 3.1, the generic template for a single TAM chain is shown. As another option, we can provide a bypass for the core-internal scan chains, and at the cost of a multiplexer and an additional control wire, we can reduce the length of the access chain by bypassing them during the core-external test. We can also provide a bypass for the entire TAM chain in this wrapper. Such a bypass is practically useful when multiple cores are concatenated into a single TAM, such as the case in the Daisy-chain architecture described in [8]. Cores which are not being tested can be bypassed in order to reduce the access length to cores which are being tested. As multiple cores are daisy chained into one TAM, this might lead to long TAM wires, and hence to long propagation delays.

### 3.2.3 Partitioning of TAM Chain Elements

Usually the TAM width is limited because of limited IC pins, silicon area, and so forth. Therefore, in many cases, the total number of TAM elements is much larger than the width of the TAM (the number of TAM lines). In these cases, it is required to partition the set of TAM elements into a number of subsets equal to the number of available TAM chains.

The partitioning of TAM elements over TAM wires has a direct impact on scan-in time,  $s_i$ , and scan-out time  $s_o$ . Partitioning determines core test time; hence, we look for a partitioning of the TAM elements which yields to the minimum test time.

For cores with fixed-length scan chains, the TAM element partitioning is challenging. Suppose that we have the core and the following information:  $N_I$  functional inputs,  $N_O$  functional outputs and  $N_S$  scan chains with lengths  $l_1, l_2, \ldots, l_{N_S}$ . We want to design a wrapper for this core with TAM width (TAM plugs) W to minimize the core test time.

The partitioning problem can be formulated as finding an assignment of all TAM elements to one of the available TAM chains such that the core test time, Equation 3.1, is minimized. This problem can be formalized as follows [42]:

#### **Problem 1** Partitioning of TAM Chain Elements (PTE)

Assume a set of W identical TAM chains and a set  $\mathcal{WI} = \{I_1, I_2, \cdots, I_{N_I}\}$  of wrapper input cells, where each wrapper input cell has a length  $1, l(I_j) = 1$ . Given a set of  $S = \{s_1, s_2, \cdots, s_{N_S}\}$  of core-internal scan chains, where scan chain  $s_j$  has length  $l_j, l(s_j) = l_j$ . Given a set of  $\mathcal{WO} = \{O_1, O_2, \cdots, O_{N_O}\}$  of wrapper output cells with length of  $1, l(O_j) = 1$ . We define, the group of TAM elements as:  $\mathcal{TE} = \mathcal{WI} \cup S \cup \mathcal{WO}$ , with  $|\mathcal{TE}| = N_I + N_S + N_O$ . A TAM partition  $\mathcal{P} = \{P_1, P_2, \cdots, P_W\}$  of  $\mathcal{TE}$  is such that it divides  $\mathcal{TE}$  into W disjoint sets, one for each TAM chain. For each TAM chain  $j, 1 \leq j \leq W$  we define a set of input elements  $IN_j = P_j - \mathcal{WO}$  and a set of output elements  $OUT_j = P_j - \mathcal{WI}$ . Thus, the scan-in length of TAM chain j,

becomes  $l(s_{i_j}) = l(IN_j)$ , which is actually the length of the wrapper input cells (or the number of wrapper input cells) and the sum of the lengths of the scan chains in TAM i. Also, the scan-out length of TAM chain j becomes  $l(s_{o_j}) = l(OUT_j)$ . Hence, the scan-in and scan-out length for the whole core with this partitioning becomes  $s_i(\mathcal{P}) = \max_{j=1}^{j=W} (s_{i_j})$  and  $s_o(\mathcal{P}) = \max_{j=1}^{j=W} (s_{o_j})$ , respectively. Thus, the core test time for this partitioning would be  $\mathcal{T}(\mathcal{P}) = \{1 + \max(s_i(\mathcal{P}), s_o(\mathcal{P}))\} \cdot N_{\mathcal{P}} + \min(s_i(\mathcal{P}), s_o(\mathcal{P}))$ . From the latter definitions, the PTE problem can be stated as follows:

To solve the PTE problem, we use a three-step approach.

partitions  $\mathcal{P}$  of TE.

- 1. First, we assign the core-internal scan chains in S to W TAM chains, such that the maximum sum of scan lengths assigned to a TAM chain is minimized. The resulting partition is named  $\mathcal{P}_S$ .

- 2. Second, we assign the wrapper input cells in WI to TAM chains on top of  $P_S$ , such that the maximum scan-in time of all TAM chains is minimized.

- 3. Third, we assign the wrapper output cells in WO to TAM chains on top of  $P_S$ , such that the maximum scan-out time of all TAM chains in minimized.

Figure 3.2: A conceptual view of TAM elements partitioning over TAM chains.

Note that wrapper input and output cells have lengths of one. Therefore, Steps 2 and 3 can yield an optimal solution in linear processing time, once Step 1 is completed. The first step is to solving the problem of partitioning scan chains over TAM chains, which can be formulated as follows.

### **Problem 2** Partitioning of Scan Chains (PSC)

Assume a set of  $S = \{s_1, s_2, \dots, s_{N_S}\}$  of core-internal scan chains, where scan chain  $s_i$  has length  $l_i$ , i.e.  $l(s_i) = l_i$ , and a set of W identical TAM chains. A scan partition is a partition  $\mathcal{PS} = \{Ps_1, Ps_2, \dots, Ps_W\}$  of S into W disjoint sets, one for each TAM chain. TAM chain  $i, 1 \leq i \leq W$ ,

contains all scan chains in  $Ps_i$ . The scan length of scan partition  $\mathcal{P}$  is given  $s(\mathcal{P}) = \max_{i=1}^{i=W} (l(Ps_i))$ , where for any  $\mathcal{X} \subset \mathcal{S}$ ,  $l(\mathcal{X}) = \sum_{s \in \mathcal{X}} (l(s))$ . Find an optimal scan partition  $\mathcal{P}^*$ , which satisfies  $s(\mathcal{P}^*) \leq s(\mathcal{P})$ , for all partitions  $\mathcal{P}$  of  $\mathcal{S}$  into W subset.

#### **Theorem 3.2.3** The PSC problem is NP hard.

**Proof** The PSC problem [39] is equivalent to the well known problem of minimum makespan problem, described in Appendix B. To show that PSC is NP hard, we consider the decision problem version of PSC: given  $N_S$  scan chains with length  $\{l_1, l_2, \dots, l_{N_S}\}$  and W TAM chains, is there any partition (of  $N_S$  scan chains into W subset,  $P_i$ ) such that,  $\sum_{j \in P_i} (l_j) \leq \mathcal{K}$ ,  $\forall P_i$ ? This problem is exactly equivalent to the multiprocessor scheduling version minimum makespan problem. The multiprocessor scheduling (MPS) problem is stated as follows [47]:

Instance: There is a finite set A of "tasks", a "process time" t(a) for each  $a \in A$ , a number m > 0 of "processors", and a "deadline", D > 0.

Question: Is there a schedule of A into m disjoint subsets, i.e.  $A = A_1 \cup A_2 \cup \cdots \cup A_m$ , such that  $\max\{\sum_{a \in A} t(a); 1 \le i \le m\} \le D$ ? This problem is known to be strongly NP-complete[47].

The equivalence between a decision version of PSC and a minimum makespan problem can be easily established by noting the correspondence between processors (m) and TAM chains (W), and between tasks and scan chains. The

Table 3.1: List Decreasing Algorithm.

```

Algorithm 1 [LD]

(assume W \leq N_S)

Sort S such that l(s_1) \geq l(s_2) \geq \ldots \geq l(s_{N_S});

for i := 1 to W

P_i = s_i;

for i := W + 1 to N_S

select k \in \{j | l(P_j) = \min_{1 \leq x \leq W} l(P_x)\};

P_k := P_k \cup \{S_i\};

return \max_{1 \leq x \leq W} l(P_x);

```

deadline D corresponds to  $\mathcal{K}$ . Therefore, the decision version of PSC problem is NP-complete. Also, when a decision version of a combinatorial optimization problem is proven to belong to the class of NP-complete problems, then the optimization version is NP-hard [6]. So PSC problem is NP-hard.

In the literature, various polynomial-time algorithms have been proposed for MPS [9, 18, 28, 47] that achieve near-optimal schedules. These methods are reviewed in the following.

Graham [25] proposed the List Decreasing (LD) algorithm (See Table 3.1), that first sorts the tasks in order of decreasing processing time. Then it assigns the task at the top to the minimally loaded processor. LD has a time complexity of  $\mathcal{O}(N_S \log N_S + N_S \log W)$ , in which W is the number of the processors (the width of TAM) and  $N_S$  is the number of tasks (scan chains). In Appendix B it is proved that the worst case performance ratio is  $\frac{4}{3} - \frac{1}{3W}$ .

Bin-packing and MPS problems are dual problems[27]. In the MPS problem, the goal is to pack several objects of given sizes into a given number of bins, and to minimize the maximum necessary capacity of the bins. The original formulation of MPS was scheduling jobs of different lengths to run on a given number of machines so that the whole system finishes as early as possible (these formulations are equivalent). In the bin-packing problem, the number of bins is variable, but their capacities are constant. The two problems are the duals of each other: both are known to be strongly NP-hard. Suppose we have a super-optimal solution to the bin packing problem, an instance that is known to use at most as many bins as the optimal, but may "overhang" a bit, by a factor of  $\varepsilon$ , making it infeasible. This solution then can be used to approximate the corresponding makespan problem in Table 3.2

Table 3.2: Using Bin-packing solution to solve MPS.

Let  $L = \max\{\max_j s_j, \frac{1}{m} \sum_i s_i\}.$

Guess a median  $d \in [L, 2L]$ .

Find an  $\varepsilon$ -dual approximation for packing W bins of size d.

If less than W bins were used, search the smaller half of the interval.

If W bins proved to be too few, search the larger half of the interval.

Repeat until length of the interval is less than 1.

The algorithm shown in Table 3.2 is very general. For example there is a method (Table 3.4) in which the *First Fit Decreasing* (FFD) algorithm is used for bin-packing [11, 38, 46]. 'Also, for upper bounds of the interval, the

List Decreasing algorithm is used.

Table 3.3: Using First Fit Decreasing to solve MPS.

```

Algorithm 2 (Using First Fit Decreasing)

Sort S such that l(s_1) \ge l(s_2) \ge \ldots \ge l(s_{N_S})

MinCost := \frac{\sum_{i=1}^{N_S} l_{s_i}}{m};

C_U := LD;

C_L = \lfloor \max(\frac{LD}{\frac{4}{3} - \frac{1}{3W}}, l_1, MinCost) \rfloor;

d:=C_L;

while d \leq C_U \wedge FFD(d) > W do

d := d + 1;

return \mathcal{P};

First Fit Decreasing : FFD(d)

Assume initially P_i = \emptyset for all j

Sort S such that l(s_1) \geq l(s_2) \geq \ldots \geq l(s_{N_S})

for i := 1 to N_S

j := 1

while l(P_i) + l_i > d do

j := j + 1

P_i := P_i \cup S_i;

return \max\{j|P_i\neq\emptyset\};

```

As we mentioned above, MPS and bin-packing are equivalent, so from a standard algorithm providing a bin-packing solution we can extrapolate to solve MPS. There are some standard algorithms for bin-packing, such as FFD, Last Fit Decreasing, Worst Fit Decreasing, and Best Fit Decreasing (BFD) [11, 38, 46]. BFD is the best algorithm for our purposes because it looks for the best possible assignment (of scan chain to TAM chains) with the minimum cost (minimum makespan). Algorithm shown in Table 3.4 uses the BFD to solve PSC.

**Example** Consider core 6, the largest logic core from p93791 from the

Table 3.4: Best Fit Decreasing Algorithm (BFD).

```

Algorithm 3 (BFD)

Assume initially P_j = \emptyset for all j

Sort S such that l(s_1) \geq l(s_2) \geq \ldots \geq l(s_{N_S})

for i := 1 to N_S

find P_{max} with current maximum length

find P_{min} with current minimum length

assign s_i to TAM chain P, such that |l(P_{max}) - \{l(P) + l(s_i)\}| is minimum if there is no such TAM chain (P) then assign s_i to P_{min}

return P;

```

ITC'02 SoC Benchmarks [7]. Core 6 has 417 functional inputs, 324 functional outputs, 72 bidirectional I/Os, and 46 internal scan chains. Seven scan chains have length of 500 bits, thirty have length of 520 bits, and nine scan chains have length of 521 bits. LD, the one that used FFD to solve MPS (Table 3.3) and BFD have been used to assign core internal scan chains to the TAM chains. The result is shown in Table 3.5.

From Table 3.5, the three algorithms, LD and BFD perform the same, but Algorithm 2 performs better. Here, LD and BFD perfomance is the same baceause in both algorithm all the scan chains are sorted first, so best assignment (BFD) is the same as the assignment to the TAM chain with minimum length (LD). Algorithm 2 performance is better, for example, for W=9, both LD and BFD output has a cost of 3081, but the Algorithm 2 solution has a cost of (makespan) 3000, which means saving 81 cycles for each pattern, considerable for a large number of test patterns.

The same result (better performance of Algorithm 2) has been derived

Table 3.5: The maximum scan-in/scan-out length of the assignment of core internal scan chains to TAM chains for core 6 of p93791 of ITC'02 benchmarks.

|           | $\mathbf{makespan} \colon \max(l(P))$ |                     |             |

|-----------|---------------------------------------|---------------------|-------------|

| TAM Width | Algorithm 1                           | Algorithm 2         | Algorithm 3 |

|           | (LD)                                  | (using bin-packing) | (BFD)       |

| 1         | 23789                                 | 23789               | 23789       |

| 2         | 11904                                 | 11904               | 11904       |

| 3         | 8263                                  | 8263                | 8263        |

| 4         | 6202                                  | 6202                | 6202        |

| 5         | 5142                                  | 5142                | 5142        |

| 6         | 4141                                  | 4140                | 4141        |

| 7         | 3621                                  | 3620                | 3621        |

| 8         | 3101                                  | 3100                | 3101        |

| 9         | 3081                                  | 3000                | 3081        |

| 10        | 2581                                  | 2580                | 2581        |

| 11        | 2561                                  | 2560                | 2561        |

| 12        | 2080                                  | 2080                | 2080        |

| 13        | 2061                                  | 2060                | 2061        |

| 14        | 2060                                  | 2060                | 2060        |

| 15        | 2041                                  | 2000                | 2041        |

| 16-19     | 1560                                  | 1560                | 1560        |

| 20-21     | 1540                                  | 1540                | 1540        |

| 22        | 1521                                  | 1500                | 1521        |

| 23        | 1041                                  | 1041                | 1041        |

| 24-38     | 1040                                  | 1040                | 1040        |

| 39-42     | 1020                                  | 1020                | 1020        |

| 43-45     | 1000                                  | 1000                | 1000        |

| 46-∞      | 521                                   | 521                 | 521         |

Table 3.6: Adding wrapper input/output cells to TAM chains.

```

Algorithm 4: Adding wrapper input/output cells to TAM chains i := N_I or N_O;

While i > 0, do

find P_{max} with current maximum scan-in/scan-out length

find P_{min} with current minimum scan-in/scan-out length

if l(P_{max}) < l(P_{min}) then

Add l(P_{max}) - l(P_{min}) wrapper input/output Cells to P_{min}

i := i - (l(P_{max}) - l(P_{min}))

if l(P_{max}) = l(P_{min}) then

Add \lfloor \frac{i}{W} \rfloor to all P_S;

if i\%w \neq 0 then

Add 1 wrapper input/output cell to i\%w P_S;

return \mathcal{P} (which we call it after that \mathcal{P}_S;

```

for difference cores. Therefore, Algorithm 2, the one using a bin-packing solution, is chosen for the first step of wrapper design, the assignment of core internal scan chains to the TAM chains.

The second step is adding the wrapper input cells to the TAM chains, and the third step is to add wrapper output cells. These two steps are equal and both can be solved optimally in linear processing time. Algorithm  $4^{\dagger}$  in Table 3.6 is proposed for steps 2 and 3.

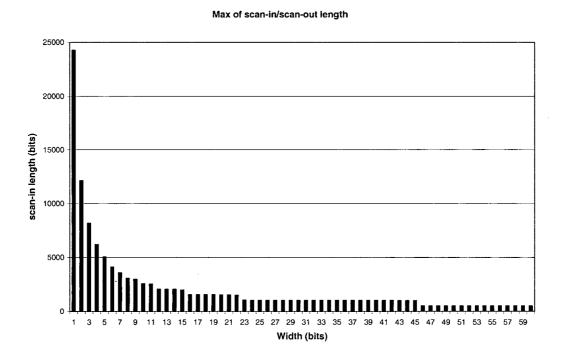

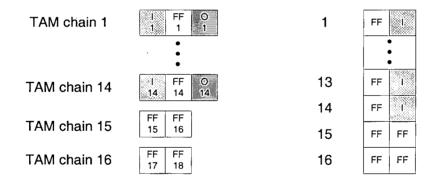

The result of wrapper design for core 6 of p93791 is shown in Figure 3.3. For this wrapper design we used Algorithm 2 to assign core internal scan chains to the TAM chains, and Algorithm 4 to add wrapper input/output cells. In Figure 3.3, the  $\max\{s_i, s_o\}$  vs. TAM width is plotted (for this core since  $N_I > N_O$ , so  $\max\{s_i, s_o\} = s_i$ ). We observe that as W increases, the

<sup>&</sup>lt;sup>†</sup>In Algorithm 4 i%w is the remainder of i divided by w.

scan-in length decreases in a series of distinct steps. This is because as W increases, the core internal scan chains are distributed among a larger number of TAM chains. Thus the scan-in length decreases only when the increases in W are sufficient to remove an internal scan chain from the longest TAM chain. For example, when the internal scan chains of core 6 are distributed among 24 TAM chains,  $s_i$  is 1040 bits long. The value of  $s_i$  remains at 1040 until W reaches 39. We will use this trend to save in test I/O pins (for example, we can reach the same test time using 24 TAM lines instead of 38 TAM lines, saving 14 TAM lines for just one core). Another observation is that beyond a TAM width of 47, the test time does not decrease. This observation corresponds to Theorem 3.2.1: the lower bound on the test time based on the theorem is this (for this example  $l_{max} = 521$  and number of test patterns  $N_P = 218$ ):

$$T \ge l_{max} \cdot N_P + l_{max} + N_P = 521 \times 218 + 521 + 218 = 114317$$

and the minimum TAM width required to achieve this test time lower bound is  $W_{min}$

$$W_{min} = \lceil \frac{L + \max(N_I, N_O)}{l_{max}} \rceil$$

$$= \lceil \frac{7 \times 500 + 30 \times 520 + 9 \times 521 + \max(417 + 72, 324 + 72)}{521} \rceil$$

$$= \lceil \frac{23789 + 489}{521} \rceil = \lceil \frac{24278}{521} \rceil$$

= 47

Therefore, any increase after 47 bits in the TAM width does not affect the test time.

Figure 3.3: The scan-in length for core 6 in P93791 SoC from SoC benchmarks ITC'02.

## 3.3 Wrapper Design w.r.t. Area

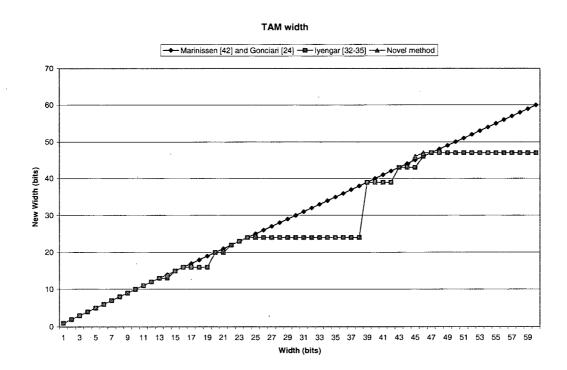

As we mentioned in the previous section, sometimes a decrease in TAM width does not affect the core test time. For example, for core 6 of SoC p93791, the test time for widths 38 and 24 are the same, so we can save 14 bits on

TAM width. Therefore, our wrapper design strategy is to first minimize test time, and second, to identify the maximum number, W', of TAM chains that actually need to be created to minimize test time, when W TAM lines are provided to the wrapper. The set of values of W' corresponding to the values of  $1 \le W < \infty$  is known as the set of pareto-optimal points [1] for the graph.

$\mathcal{P}_{\mathcal{W}}$ , the two-priority wrapper optimization problem, addressed in this section, can now be formally stated as follows:

\$\mathcal{P}\_W\$: Given a core with \$N\_I\$ functional input, \$N\_O\$ functional output and \$N\_S\$ scan chains of lengths \$l\_1, l\_2, \ldots, l\_{N\_S}\$, and TAM width \$W\$, assign the \$N\_I + N\_S + N\_O\$ TAM chain elements to \$W' \leq W\$ TAM chains, such that (i) core test time in Equation 3.1 is minimized and (ii) \$W'\$ is minimum subject to priority (i).

The second priority is based on the earlier observation that test time can be minimized even when the number of designed TAM chains is less than W. This reduces the width of a TAM required to connect to the wrapper. Therefore,  $\mathcal{P}_{\mathcal{W}}$  is analogous to the problem of MPS (minimizing the makespan of scheduling) with the secondary priority of bin-packing (minimizing the number of bins). When W' is fixed at the value of W, this problem is equal to the partitioning of TAM chain elements (PTE), which has been proved to be NP-hard (Theorem 3.2.3). Therefore, the  $\mathcal{P}_{\mathcal{W}}$  problem is also NP-hard. To solve  $\mathcal{P}_{\mathcal{W}}$  an algorithm with three steps is developed:

- 1. Calculate the possible minimum test time (T(W)) using TAM width W. For this step we can use the previous algorithm of wrapper design.

- 2. Calculate the possible minimum W', for which  $W' \leq W$  and T(W) = T(W'). For this step we can use a standard algorithm for bin-packing, such as First Fit Decreasing (FFD). Therefore, W' = FFD(T(W)).

- 3. Now, we know the minimum test time and the minimum obtainable width. The last step is wrapper design (assignment of TAM scan chain elements, i.e., internal scan chains, inputs and outputs) for a TAM width of W' using wrapper design algorithms is discussed in the Section 3.2.3.

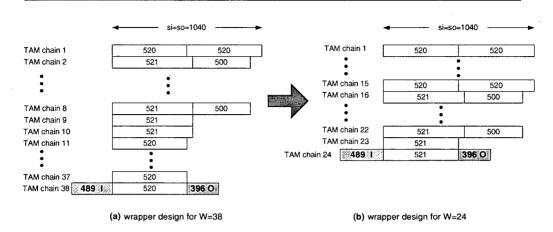

For example, for the core 6 of SoC p93791, when W = 38, our wrapper design algorithm works as follows. First, the possible minimum test time for the TAM width 38 should be calculated. Using the wrapper design algorithm (Algorithm 2), the scan-in and scan-out times are  $s_i = s_o = 1040$  and the total test time  $(N_P = 218)$  is T(38) = 227978.

In the second step, we calculate the possible minimum W'. For this step we can use the first fit decreasing procedure (mentioned in Section 3.2.3). The result becomes W' = FFD(1040) = 24.

The last step is wrapper design for W' = 24, as shown in Figure 3.4. For this step we can use Algorithm 2 (for internal scan chain assignment) and then Algorithm 4 (for adding wrapper input/output cells).

Figure 3.4: Wrapper design for core 6 in P93791 SoC from ITC'02 for TAM of width 38.

As we can see in Figure 3.4, even with a 14-bit decrease in width, the scan-in/scan-out lengths and so the core test time has not been changed.

With this algorithm we can save in the TAM width of each core, which decreases the total TAM lines required to test the whole SoC. This translates to silicon area and test I/O pins savings.

So far, the wrapper design optimizing both test time and area (silicon area and I/O pins) has been addressed. The remaining important factor in wrapper design, ATE memory, is addressed in the next section.

## 3.4 Wrapper Design w.r.t. the ATE

# Memory

In this section we discuss wrapper design optimization considering ATE resources. One of the important ATE resources which has a large impact on

ATE cost is memory. Therefore, the goal is to minimize the memory requirement for testing by eliminating useless test data memory for SoC testing. First, useless test data memory is analyzed. Next, the core wrapper design algorithm is combined with a new test vector deployment procedure stored in the ATE. To reduce memory requirements, the proposed core wrapper design finds the minimum number of TAM chain element partitions, minimizing the useless memory allocation in each partition, which facilitates efficient usage of ATE capabilities. Furthermore, the new test vector deployment procedure provides seamless integration with the ATE [24].

Since modern SoCs may consist of highly complex cores, the memory requirements to test these cores tend to increase. Therefore, careful management of memory requirements is of importance. Although tester accuracy has improved by 12% annually, IC performance increases 30% per year [12]. This forces semiconductor manufactures to step down from functional testing paths and adopt design-for-test (DFT) solutions for SoC. These new solutions, however, come with different requirements for the ATEs. Hence, the features of these new DFT-ATEs differ significantly from the conventional ATEs [10]. For example, one of the features of these new testers manages memory as a reconfigurable pool, that is, by using the right memory management, the DFT makes a larger number of transfers on some pins, while others remain unchanged [10]. Here, we show how core wrapper design and

a simple ATE deployment procedure (which also accounts for memory management) can be combined to exploit this feature of DFT-ATE, leading to reduced ATE memory requirements.

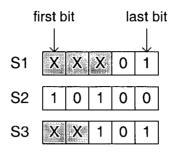

Two factors influence ATE memory requirements: TAM design and core wrapper design. The previously described approaches to designing core wrappers indirectly influence ATE memory requirements. A potential straightforward solution to the ATE memory problem is a built-in self-test (BIST). However, to make existing cores BIST-ready, considerable redesign effort is required and performance penalties are incurred. An alternative solution to the ATE memory problem is test data compression [17, 37]. While test data compression reduces useful data, our goal here is to reduce useless data (in multiple scan chain embedded cores). The useless data can be explained as follows. The test vectors should be augmented with useless data (to account for the unequal lengths of multiple scan chains) to reduce on-chip control. For example, for three scan chains of lengths 2, 5 and 3, the test tools pad the scan patterns with "don't cares" (X) to make them all of equal lengths. This is illustrated in Figure 3.5, where the padded values (shown as X) are part of the test vector. Hence, they have to be stored explicitly in the ATE memory, even though they do not represent any valuable test information. This extra memory is defined as useless memory allocation, hereafter referred to as UMA [24].

Figure 3.5: Useless Memory Allocation.

Here, the core wrapper design and the ATE memory management problems have been merged. The core wrapper design algorithm should be capable of finding the minimum number of TAM chain elements partitions such that for each partition the UMA is minimized. The ATE deployment procedure (proposed in [24]) provides memory management for the ATE, since it exploits the features of the core wrapper and deploys test data on each TAM chain partition as required. That is, the ATE deployment procedure uses the reconfigurable memory pool (RMP) feature of DFT-ATEs.

To recognize the feasibility of this method, one should note that the ATE supports sequencing-per-pin, which replicates a sequence of events in the same manner as an IC timing/logic simulator [51]. The only requirement of the ATE is to allow the memory management module to transfer test data on some ATE channels, while the remaining ATE channels remain unchanged. Recently [48], the sequencing-per-pin ATEs have been used in a similar manner where separate groups of ATE channels run at different frequencies, with

each group having different memory requirements.

From Equation 3.1 we know that core test time is a function of  $\max(s_i, s_0)$  because the last term of the equation,  $\min(s_i, s_0)$ , has a small influence on the overall test time. It should also be noted that each TAM line is assumed to be assigned to one ATE channel. Having explained the  $s_i$  and  $s_o$ , the following two examples clarify their relation to UMA.

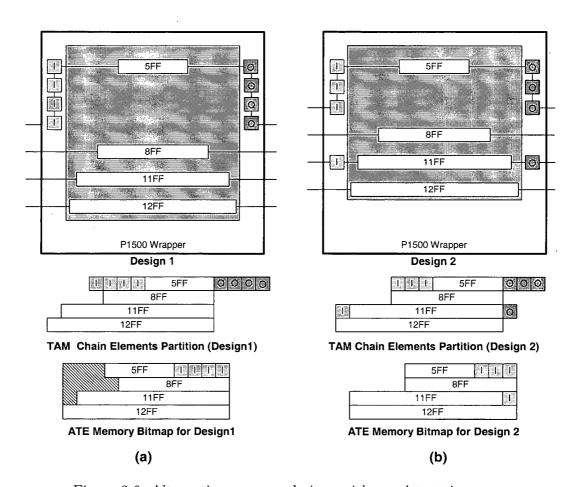

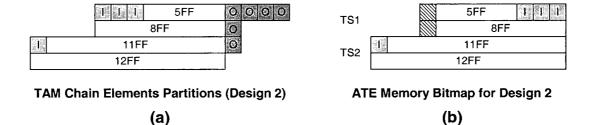

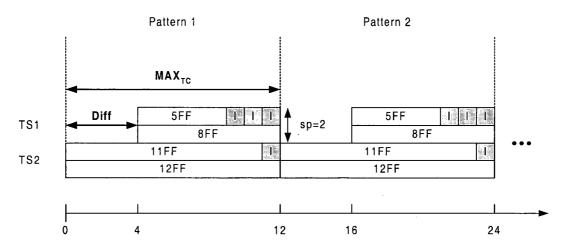

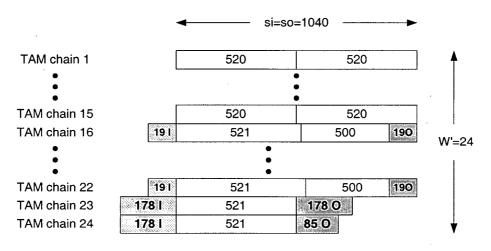

**Example** Figure 3.6 shows two core wrappers with 4 inputs, 4 outputs, 4 internal scan chains of length 5, 8, 11 and 12, and a TAM with width of 4. The two designs are equivalent from the test time point of view since the longest scan-in/out have an equal length (for both designs  $s_i = s_o = 12$ ). The TAM chains representation and the corresponding ATE memory bitmap (AMB) for both designs are shown. Because the inputs are loaded last, they are shown at the end of the memory bitmap. Considering that the ATE can control the load of each group of TAM chains of different lengths, the UMA in both cases can be reduced. However, the control overhead implied in this situation should be considered. The main difference between AMB for design 1 and design 2 is that the latter has a smaller number of ATE channels partitions (e.g. AMB1 has 4 partitions, the maximum possible number of partition in which each TAM chain is one partition, while AMB2 has just two partitions:  $p1 = \{TAM \text{ chains } 1 \& 2\}, p2 = \{TAM \text{ chains } 3 \& 2\}$ 4)). The advantage of this (having less partition) is explained as follows.

Figure 3.6: Alternative wrapper designs with equal test time.

Assuming a DFT-ATE with RMP, the control overhead implied by the first solution is larger because a larger number of partitions have to be controlled. Furthermore, as the number of TAM chains differ from core to core and the number of partitions obtained can vary for different cores, different number of parameters are required for the memory management of each core. On the contrary, AMB2 is shaped such that it can be easily split into two partitions (TS1 and TS2). This reduces the control, and having only two partitions, the memory management becomes very simple (Section 3.4.2). The same reasoning is applicable for sequencing-per-pin ATEs. It should be noted that the amount of test control for the first solution is clearly larger than for the second solution. This is why the first solution is considered to have useless memory as illustrated in Figure 3.6. Since the proposed ATE deployment procedure can handle maximum two partitions, for the case with more than two partitions, there will be UMA (this is one resource for UMA).

All the TAM chains are loaded in parallel using the same clock. Also, in the explanation of Equation 3.1, we note that the scan-out operation overlaps the scan-in. Hence, in a case where the number of inputs is larger than the number of outputs, the ATE memory has to account only for the UMA caused by the input scan chain, as in the previous example.

The second source of UMA is caused by the difference in TAM chain lengths when  $s_i < s_o$ . Since the scan-out operation of one pattern overlaps

with the scan-in of the subsequent test pattern, in a case where  $s_i < s_o$ , we need to scan-in more data, causing useless data in ATE memory. We will show that the UMA caused by a difference of  $s_i$  and  $s_o$  cannot be eliminated completely.

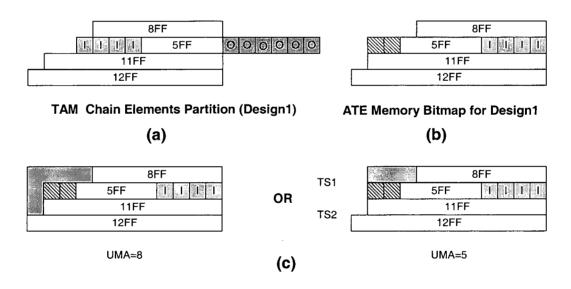

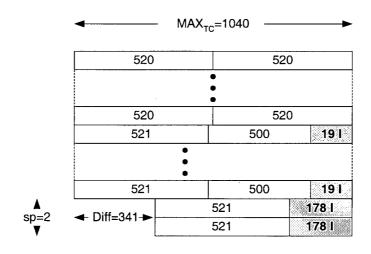

**Example** Consider the core in the Figure 3.7(a) with  $N_I = 4$ ,  $N_O = 6$  and four scan chains of lengths 12, 11, 8 and 5. An optimum TAM chain design with respect to test time leads to  $s_i = s_o = 12$ . The ATE memory bitmap (AMB) of this design is shown in Figure 3.7(b) and (c).

Figure 3.7: TAM chain design and ATE memory bitmap when  $s_i < s_o$ .

While the UMA for this design (even if we use the ATE feature) is 5, we can get a UMA of only 2 by simply rearranging the inputs and outputs in TAM chains. The design 2, shown in Figure 3.8(a), has the minimum possible UMA that we can reach for this core ,i.e., 2. The AMB for this

Figure 3.8: TAM chain design and ATE memory bitmap when  $s_i = s_o$ . design is shown in Figure 3.8(b).

**Theorem 3.4.1** For a core with  $N_I$  inputs,  $N_O$  outputs and  $N_S$  scan chains of lengths  $l_1, l_2, \dots, l_{N_S}$ , and  $N_I < N_O$ , the lower bound on UMA is given by  $N_O - N_I$ .

**Proof** In the case of  $N_I < N_O$ ,  $s_i$  is smaller than  $s_o$ . Certainly then, there is a source for the UMA in the difference between  $s_i$  and  $s_o$ , even if we could prevent other UMA sources. Therefore,

$$UMA \geq \sum_{i=1}^{i=W} (s_o - s_i) \geq \sum_{i=1}^{i=W} s_o - \sum_{i=1}^{i=W} s_i = (L + N_O) - (L + N_I)$$

$UMA \geq N_O - N_I$

where  $l_i$  is the length of scan chain i and  $L = \sum_{i=1}^{N_S} l_i$ .

There are two steps to follow in order to reduce UMA. First, a new core wrapper design algorithm is needed. Second, the ATE has to exploit the features of new wrappers. Since the test set is divided into two, the ATE

has to deploy the test vectors for the two sets at different intervals. Consider the example of Figure 3.6. The intervals at which the ATE deploys the test vectors are shown in Figure 3.9. Three parameters for ATE test vector deployment are introduced:  $MAX_{TC}$ , Diff and sp.  $MAX_{TC}$  is the length of the maximum partition, Diff is the difference between the lengths of the two partitions, and sp (split point) is the number of TAM chains that AMB fits to the first partition (their data should be sent as the first test set). So, for example in Figure 3.9,  $MAX_{TC} = 12$ , Diff = 4 and sp = 2. Since the core wrapper design is an intermediate step in a SoC test, the proposed approach does not incur any extra overhead. Hence, the ATE modifications are the only changes. For both DFT-ATEs with RMP and sequencing-per-pin ATEs, the deployment of two sets can be achieved at the expense of an external module [13] to support custom ATE behavior, employed when IEEE P1500 compliant SoCs are tested. If DFT-ATEs with RMP are employed, a test vector deployment procedure (see Section 3.4.2) can be part of the memory management. If sequencing-per-pin ATEs are considered, the methodology proposed in [48] can be used, and the control of test vector deployment can be carried out by a procedure similar to the one in Section 3.4.2.

Figure 3.9: ATE test vector deployment.

### 3.4.1 Wrapper Design Algorithm to Reduce UMA