# TRAFFIC ENGINEERING METHODS FOR A NETWORK PROCESSOR BASED MULTIMEDIA ROUTER

By

#### Amr Elramly

B.Sc. Electrical and Computer Engineering, Ein Shams University, 1982

# A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

The Faculty of Graduate Studies

Electrical and Computer Engineering

THE UNIVERSITY OF BRITISH COLUMBIA

July 2006

© Amr Elramly, 2006

#### **ABSTRACT**

The thesis proposes methods to build network processor based multimedia router that provides more services than what is offered by the most expensive network routers. The new methods provide scalability to serve hundreds of thousands of multimedia streams and serve fast enough to meet the low latency required by the multimedia application. The first method proposed is a proxy agent that turns the router into multimedia aware router by preparing the profiling and the routing information for the forwarder and the scheduler, which simplifies the processes required for the rest of the router operation. The second method is Lowest Credit Weighted Fair Queuing or LCWFQ scheduler, that achieves a fairness index of 1 (One) and a work order of O(1) which is similar to the famous Deficit Round Robin (DRR) scheduling algorithm, except that the LCWFQ avoids the DRR weakness in implementation. The third method is an Adaptive Weight Adjustment (AWA) traffic shaper that the Internet Service Provider (ISP) may use when the total ISP commitments to the subscribers are more than what the network can handle. The AWA also serves the bursty streams when conflicting with the assigned SLA while maintains fair services to non-bursty traffic. The forth method is a three level memory index that fast search a record in the forwarding table where the number of memory accesses is always three no matter how large is the forwarding table. The thesis also includes two methods to translate the Service Level Agreement (SLA) into scheduling profiles and to report any bandwidth over-usage to help redefining the subscriber SLA. The proposed methods are designed to fit the network processors abilities to implement loosely coupled profiling, traffic shaping and scheduling.

# **Table of Contents**

| ABSTRACT      | Γ                                              | . ii |

|---------------|------------------------------------------------|------|

|               | ntents                                         |      |

| List of Table | es                                             | . v  |

|               | res                                            |      |

| List of Acro  | nyms and Symbols                               | vii  |

|               | gement                                         |      |

| Dedication.   |                                                | . x  |

| 1 Introdu     | action                                         |      |

| 1.1           | Contributions                                  |      |

| 1.1.1         | Architecture Design of SMM Router              |      |

| 1.1.2         | LCWFQ Scheduler                                |      |

| 1.1.3         | Adaptive Weight Adjustment Traffic Shaper      |      |

| 1.1.4         | Other Contributions                            | . 4  |

| 1.2           | Thesis Outline                                 | . 4  |

| 2 Netwo       | rk Processors                                  | . 6  |

| 2.1           | Introduction                                   | . 6  |

| 2.2           | Micro-engines                                  | . 7  |

| 2.2.1         | Registers                                      | . 7  |

| 2.3           | Memory                                         | . 9  |

| 3 Netwo       | rk Processor Based Multimedia Router           | 10   |

| 3.1           | Introduction                                   | 10   |

| 3.2           | Proxy Agent - Proxy Server Relationship        | 13   |

| 3.3           | Architecture                                   | 14   |

| 3.4           | The Ingress                                    | 14   |

| 3.5           | The Proxy Agent                                | 15   |

| 3.6           | The SMM Forwarder                              | 18   |

| 3.7           | The Forwarder                                  | 19   |

| 3.7.1         | Three-Levels Indexing                          | 20   |

| 3.8           | The Scheduler                                  | 22   |

| 3.9           | The Egress Module                              | 22   |

| 4 Selecti     | on of a Suitable Scheduler                     | 23   |

| 4.1           | Introduction                                   | 23   |

| 4.2           | First-In-First-Out (FIFO)                      | 23   |

| 4.3           | Simple Round Robin                             | 23   |

| 4.4           | Deficit Round Robin                            | 24   |

| 4.4.1         | DRR Weakness                                   | 25   |

| 4.5           | The SFQ and SCFQ                               | 25   |

| 5 Schedu      | ıler and Traffic Shaper                        |      |

| 5.1           | Introduction                                   |      |

| 5.1.1         | Per-Flow scheduling Vs Aggregate Scheduling    |      |

| 5.1.2         | Forwarder, Profiler and Scheduler relationship |      |

| 5.1.          |                                                |      |

|    | 5.2     | The Profiler                                     | 30   |

|----|---------|--------------------------------------------------|------|

|    | 5.3     | Adaptive Weight Adjustment                       |      |

|    | 5.3.1   | Formulas and mechanism                           |      |

|    | 5.3.2   | AWA Traffic Shaper Performance                   |      |

|    | 5.4     | LCWFQ Scheduler                                  |      |

|    | 5.4.1   | Assumptions and Notations                        |      |

|    | 5.4.2   | The LCWFQ Name Origin                            |      |

|    | 5.4.3   | LCWFQ Concept                                    |      |

|    | 5.4.4   | LCWFQ Operation                                  |      |

|    |         | Performance Analysis of LCWFQ                    |      |

|    | 5.5.1   | Computational Complexity                         |      |

|    | 5.5.2   | Startup Latency                                  |      |

|    | 5.6     | Service Level Agreement (SLA)                    |      |

|    | 5.7     | FIFO-Effect                                      |      |

|    | 5.8     | FIFO-Effect Suppression                          |      |

|    | 5.8.1   | FIFO-Effect Suppression Mechanism                |      |

| 6  |         | tion and Results                                 |      |

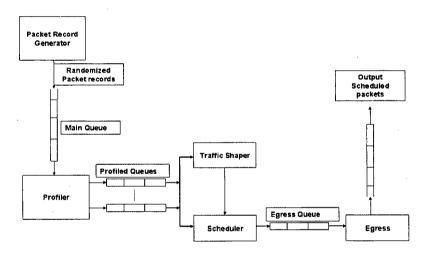

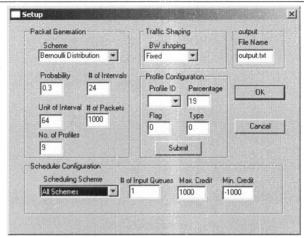

| 0  | 6.1     | Simulation Overview                              |      |

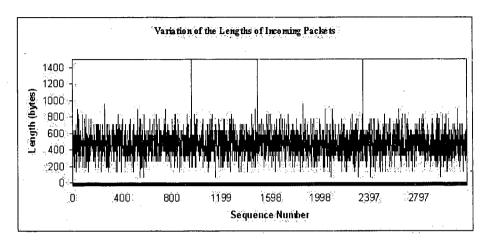

|    | 6.2     | Traffic Generation                               |      |

|    | 6.2.1   | Traffic Generation Using the Bernoulli's Process |      |

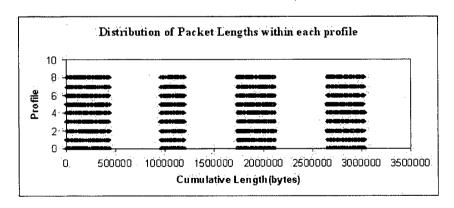

|    | 6.2.2   | Results of Traffic Generation                    |      |

|    | 6.3     | Simulation                                       |      |

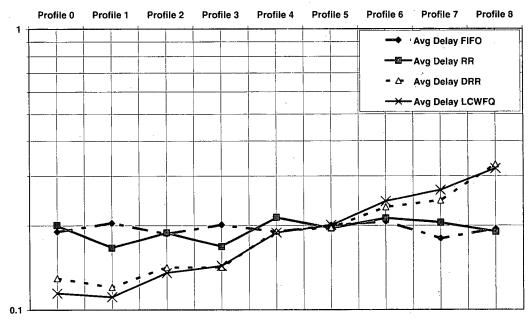

|    | 6.3.1   | Scheduling with Fixed Bandwidth                  |      |

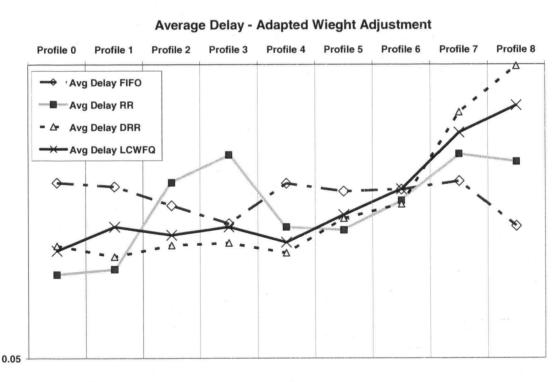

|    | 6.3.2   | Scheduling with Adapted Weight Adjustment        |      |

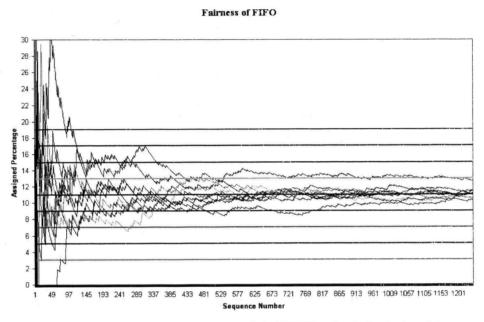

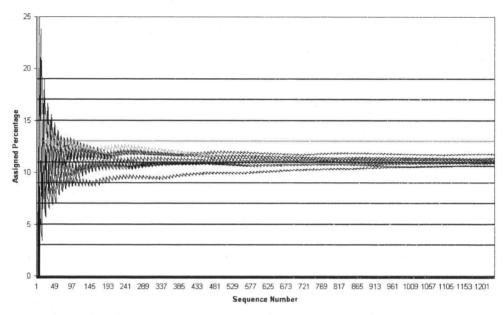

|    | 6.3.3   | Fairness Index diagrams                          |      |

|    | 6.3.4   | Simulation of the FIFO effect                    |      |

|    | 6.4     | Memory Access Overhead Estimates                 |      |

| 7  |         | ision and Future Work                            |      |

| 8  |         | graphy                                           |      |

| 9  |         | dix A: Class Description                         |      |

| י  | 9.1     | Program Execution Overview                       |      |

|    | 9.2     | Class Description                                |      |

|    | 9.2.1   | BWShape                                          |      |

|    | 9.2.1   | CSchedulerDlg                                    |      |

|    | 9.2.2   | Queue                                            |      |

|    | 9.2.3   |                                                  |      |

|    | 9.2.4   |                                                  |      |

|    | 9.2.4   |                                                  |      |

|    |         |                                                  |      |

|    | 9.2.4   |                                                  |      |

|    | 9.2.4   |                                                  |      |

|    | 9.2.4   |                                                  |      |

|    | 9.2.4   |                                                  |      |

|    | 9.2.4   |                                                  |      |

|    | 9.2.4   |                                                  |      |

|    | 9.2.4   |                                                  |      |

| 10 | ) Appen | dix B: GUI Screen Shots                          | . 84 |

# **List of Tables**

| Table 5.1: Illustration of Traffic shaping in the case of four profiles | 34 |

|-------------------------------------------------------------------------|----|

| Table 5.2: Illustration of Traffic shaping in the case of nine profiles | 36 |

| Table 5.3: Numerical example of the scheduler                           | 41 |

| Table 5.4: Illustration of Profiling based on a Service Level Agreement | 45 |

| Table 6.1: Bandwidth quota assignment assumed by the SLA Manager        | 61 |

| Table 6.2: Typical Read/Write time for the router modules               | 71 |

|                                                                         |    |

# **List of Figures**

| Figure 3.1: Simple Diagram of the proposed router architecture                     | . 10 |

|------------------------------------------------------------------------------------|------|

| Figure 3.2: Packet Classifying & Forwarding Diagram                                | . 12 |

| Figure 3.3: Proxy Agent – Proxy Server Relationship Diagram                        | . 13 |

| Figure 3.4: Detailed architecture of the SMM Router                                | . 14 |

| Figure 3.5: Operational relationship between the Core and the Proxy Agent          | . 16 |

| Figure 3.6: Relationship between Forwarding and routing tables                     | . 17 |

| Figure 3.7: Three Levels Indexing                                                  | . 20 |

| Figure 3.8: Forwarding Table Structure                                             | . 21 |

| Figure 5.1: An illustration of the profiling mechanism for three profiles          | . 28 |

| Figure 5.2: ASD Architecture                                                       | 31   |

| Figure 5.3: BW adjustment performed by the Traffic Shaper in case of four profiles | 35   |

| Figure 5.4: BW adjustment performed by the Traffic Shaper in case of nine profiles | 35   |

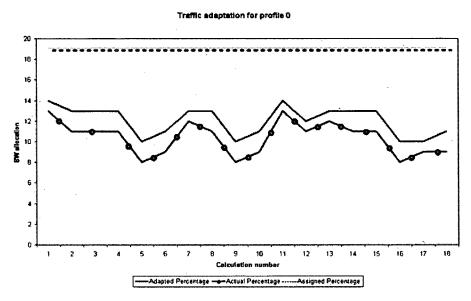

| Figure 5.5: Adaptive Weight Adjustment for profile 0                               | 37   |

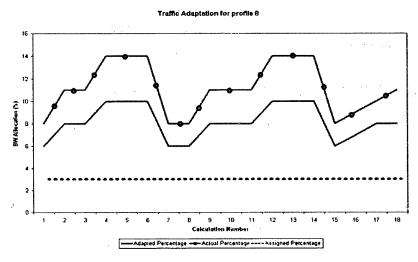

| Figure 5.6: Adaptive Weight Adjustment for profile 8                               | . 38 |

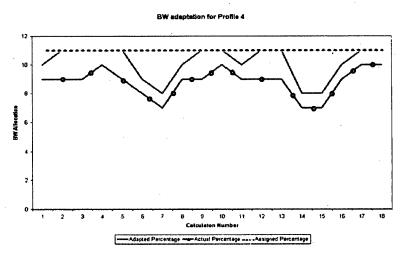

| Figure 5.7: Adaptive Weight Adjustment for profile 4                               | 38   |

| Figure 5.8 Diagram showing the FIFO Effect                                         | 50   |

| Figure 5.9 Illustration of the Scheduling and the FIFO-Effect                      | . 52 |

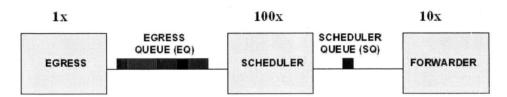

| Figure 6.1 The Simulator Schematic Diagram                                         |      |

| Figure 6.2 Sample of Generated Packets Length Variation                            | . 60 |

| Figure 6.3 Generated packets arrivals per profile for a case of four bursts        | . 60 |

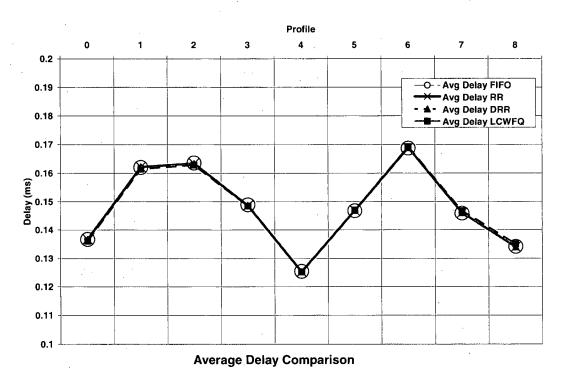

| Figure 6.4 The average delay with fixed B/W assigned                               | 62   |

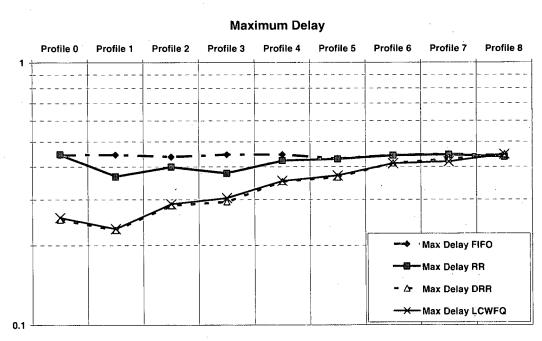

| Figure 6.5 The maximum delay with fixed B/W assigned                               | 62   |

| Figure 6.6: Average delay with adapted weight assignment                           | 63   |

| Figure 6.7 The maximum delay with adapted weight assignment                        | 64   |

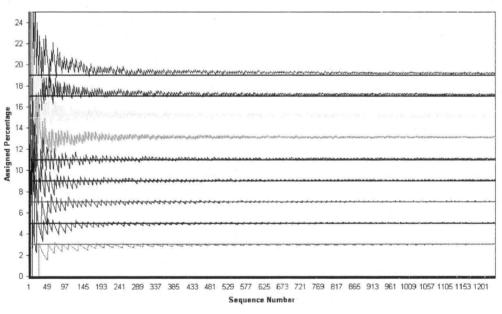

| Figure 6.8 Fairness measurement of the FIFO scheduling algorithm                   | 65   |

| Figure 6.9 Fairness measurement of the RR scheduling algorithm                     |      |

| Figure 6.10 Fairness measurement of the DRR scheduling algorithm                   | 66   |

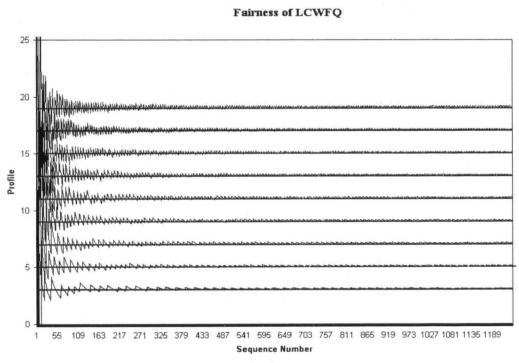

| Figure 6.11 Fairness measurement of the LCWFQ scheduling algorithm                 | 67   |

| Figure 6.12 The Average delay when the Egress queue size is 1000 packets           | 69   |

| Figure 10.1: Main Setup Screen                                                     | 84   |

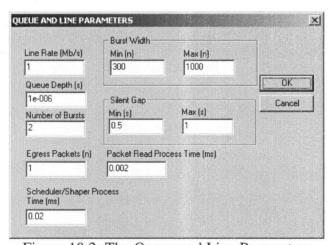

| Figure 10.2: The Queue and Line Parameters                                         | 84   |

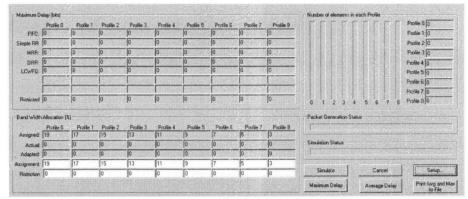

| Figure 10.3: Simulation in initial mode before setup                               | 85   |

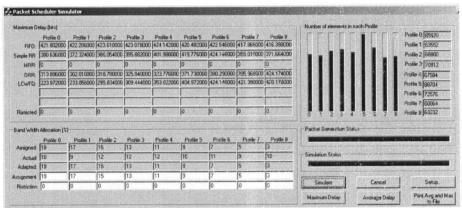

| Figure 10.4: Simulation completed shows the average delay and maximum delay        |      |

| Figure 10.5: The simulator reports on profiles that have more than their shares    |      |

### **List of Acronyms and Symbols**

ASD Adaptive Scheduling Device

AWA Adaptive Weight Adjustment

DC Deficit Counter

DRR Deficit Round Robin

ERR Elastic Round Robin

GPS Generalized Processor Sharing

IP Internet Protocol

ISP Internet Service Provider

LCWFQ Lowest Credit Weighted Fair Queuing

LR Latency Rate

LI Lawful Intercept

MRR Mini Round Robin

NP Network Processor

PDRR Pre-order Deficit Round Robin

PERR Prioritized Elastic Round Robin

QoS Quality of Service

RF Relative Fairness

RFB Relative Fairness Bound

RR Round Robin

SC Surplus Counter

SCFQ Self-Clocked Fair Queuing

SFF Smallest Finish-time First

SFQ Start-time Fair Queuing

SLA Service Level Agreement

SMM Selective MultiMedia

SRR Surplus Round Robin

SSF Smallest Start-time First

TE Traffic Engineering

UA User Agent

VoIP Voice over IP

WF2Q Worst-case Fair Weighted Fair Queuing

WFQ Weighted Fair Queuing

WRR Weighted Round Robin

### Acknowledgement

I would like to express my sincere gratitude and appreciation to my supervisor, Professor Hussein Alnuweiri for his encouragement and support at all levels. Dr. Hussein Alnuweiri has constantly guided me to remain focused on achieving my goal and exploring in depth and many thanks for his support in funding this research.

I would like to thank Dr. Steve Wilton and Dr. Rabab Kreidieh Ward for agreeing to be on my thesis committee and reviewing my thesis.

I would like to thank all the people who made this work possible. Thanks to Mollalign Assefa for providing expertise C++ and for the help in lab experiments. I would like also to thank Yasser P. Fallah and Tariq Al-Khasib for the critical comments and the helpful suggestions.

I really appreciate the wonderful Research Assistance program provided by The University of British Columbia. The program helped me to give up my previous job and get dedicated for my thesis. Thanks to UTStarcom for offering better job afterwards and funding the last part of the research. I would like to mention my mangers, Wael Menyawi and Jack Mar for their support in the last two years and Joe Perrella for the appreciation.

My gratefulness is to my wife Mosheera for the inspiration and the moral support.

Raising four kids is challenging when living on one income most of the time.

# Dedication

To Mosheera

#### 1 Introduction

The Intel IXP2400 is an example of a network processor that consists of one Intel XScale core processor and eight micro-engines. The micro-engines are organized into two clusters of four, all on the same die. Applications can be implemented using the network processor to perform pipeline processing in which the different processors exchange packet descriptor information through Next-Neighbor (NN) registers or shared memory.

The thesis is proposing new methods to implement multimedia routers using the advantages of the network processors. The proposed methods are tested heuristic methods and focus on simplifying the implementation of the multimedia router. The methods are implemented in the proxy agent module, the scheduler module, the traffic shaper module, the forwarder three-level index module and the SLA manager module. In general, the Service Level Agreement (SLA) defines the profiles and the scheduler serves the streams according to their profiles. The streams that are classified under the same SLA profile are also expected to receive the same level of network services.

It is a complex task for the Internet Service Provider (ISP) to recalculate the bandwidth share per subscriber every time a new SLA is in action and added to the service. In some cases, the total commitment for the ISP to subscribers may be more than what the network can handle.

The thesis proposes methods to help design multimedia routers that are capable of reading the SLA parameters, recalculate the bandwidth per each SLA and schedule the traffic to provide fair bandwidth allocation for each SLA in action.

#### 1.1 Contributions

The main contributions of this thesis are summarized hereinafter as follows:

- (1) High level architecture design of selective multimedia (SMM) router to show where the proposed Scheduler, Profiler and Traffic Shaper fits

- (2) Design and simulation of advanced complex scheduling algorithm referred hereinafter as the Lowest Credit Weighted Fair Queuing (LCWFQ)

- (3) Design and simulation of adaptive weight adjustment traffic shaper

- (4) Introducing methods to input the SLA parameters into the traffic shaper and recalculating the bandwidth allocated to each profile. Also introducing a method to provide feedback to the network manager when over commitment occurs

- (5) Implementing a simulator and traffic generator that mimic network traffic and configuring traffic parameters like silent gaps, bursts and streams

#### 1.1.1 Architecture Design of SMM Router

The Selective Multi-Media (SMM) router architecture includes two main contributions, a design of an SMM Proxy Agent and a Forwarder. The design of the proxy agent turns the router into multimedia aware router. The proxy agent selects the multimedia streams from the Egress modules and provides priority services to them. The proxy agent populates a proposed indexed forwarding/routing table for the active streams and adhere

the profile tag to each record in the forward table. Moreover, it provides time stamp for each record for the purpose of aging and cleanup.

On the other hand, the proposed SMM forwarder performs forwarding functions that are controlled by the proxy agent. Strictly speaking, the SMM forwarder is unaware of the type of the stream it processes, while the proxy agent is the one that determines the type of the multimedia streams. The proxy agent makes the router capable of recognizing and handling different multimedia streams, by simply configuring the proxy agent.

The thesis also proposes a memory indexing method to improve the suitability of the network processors in implementing the multimedia routers. The index method limits the search for a route record in a forwarding table to three memory accesses. Regardless of how large is the forward table; the number of memory accesses is fixed. In a worst-case scenario, more than 100,000 records in a table can be searched in only three memory accesses by using less than 16MB of memory. A 16MB of memory is affordable internally in most of the network processors.

#### 1.1.2 LCWFQ Scheduler

The Lowest Credit Weighted Fair Queuing (LCWFQ) scheduler is a new innovative algorithm and is considered as the main contribution for the thesis. LCWFQ algorithm has some similarity with the famous Deficit Round Robin (DRR) scheduler. The LCWFQ algorithm performs as good as the famous Deficit Round Robin (DRR) scheduling

algorithm. LCWFQ is relatively easier to implement on NP, and avoids the DRR weaknesses and implementation problems.

#### 1.1.3 Adaptive Weight Adjustment Traffic Shaper

The Adaptive Weight Adjustment (AWA) method is designed to control the bandwidth allocation according to the composition of the existing measured traffic, and the SLA assigned bandwidths to reshape traffic congestion. AWA is considered as an extended function to the scheduler where it feeds back the scheduler with the status of the traffic in the backlog, recalculates the bandwidth assigned to the profiles, and adjusts the priority to achieve the optimum fairness. The AWA is a traffic shaping technique and the word "Traffic Shaper" is used alternatively through the thesis for simplicity.

#### 1.1.4 Other Contributions

The thesis also proposed a mechanism to translate the Service Level Agreement SLA into profiles and assure fairness to all subscribers. More contributions added to the thesis, which is implementing a simulator and traffic generator that mimic network traffic by configuring the parameters like the silent gaps, the bursts and the packets. The simulator provides more of a deep look into the backlog traffic in the scheduler input buffer.

#### 1.2 Thesis Outline

This thesis introduces a multimedia aware router architecture that can be implemented on the IXP Network Processor (NP) platform. The thesis is organized as follows:

- Chapter 1 is this introductory chapter.

- Chapter 2 is an overview on the IXP NP platform.

- Chapter 3 describes the design of the proposed router architecture based on the IXP NP platform. In this chapter, the relevant NP modules and features, and the implementation of the respective network services are described in details.

- Chapter 4 describes three of the commonly known scheduling algorithms called the First-In-First-Out (FIFO), the Round Robin (RR) and the Deficit Round Robin (DRR) scheduling algorithms.

- Chapter 5 introduces a proposed scheduling algorithm named the Lowest Credit

Weighted Fair Queuing (LCWFQ) and describes its operation. The chapter also

describes a proposed adaptive weight adjustment method.

- Chapter 6 presents the simulation technique used to proof and justify the

suitability of the proposed methods for the network processors based multimedia

routers. The chapter demonstrates advantages of the LCWFQ proposed

scheduling algorithm and presents simulation results of the performance of the

scheduler and the adapted weight adjustment.

- Chapter 7 concludes the thesis and summarizes simulation results.

- Chapter 8 is the bibliography and references

- Appendix A describes the Class Description for the simulator

- Appendix B includes GUI screenshots

#### 2 Network Processors

#### 2.1 Introduction

Network Processors (NP) are optimized for packet processing and offer performance and flexibility for implementing network services. Network Processor also allow the addition of the new network services while maintaining high packet throughput and low packet latency. The NP meets the network performance and flexibility requirements through highly parallel, programmable architectures. The parallel nature of network processors allows processing of multiple packets simultaneously, which can greatly increase the throughput. This chapter provides a brief overview of the Intel IXP2400 Network processor that is relevant to the design of network processor based router design discussed in the next chapter [1].

The Intel IXP2400 Network processor consists of one Intel XScale core processor and eight micro-engines. The micro-engines are organized into two clusters of four, all on the same die. The Intel XScale core is an Advanced Reduced Instruction Set Computer (RISC) machine. The micro-engines are also RISC processors optimized for fast-path packet processing. IXP2400 has one scratchpad-hash-Control and status Access Proxy (CAP) unit, one Media Switch Fabric unit, one PCI controller, two SRAM controllers and one-DRAM controller.

The Intel XScale Core is compliant with the ARM V5TE architecture as defined by ARM Limited and has support for ARM's thumb instructions that allow the Intel XScale core to

switch back and forth between the standard 32-bit instruction set and a 16-bit instruction set for better performance.

#### 2.2 Micro-engines

Each micro-engine has an independent instruction store large enough for 4K of 40-bit instructions that is initialized by a code in the XScale core. The micro-engine has eight hardware-based threads of execution, which can be configured to use either eight or four threads. The threads are non-preemptive, which means that the currently active thread must explicitly release control of the processor before another thread can run. This nature of the threads simplifies synchronization within the micro-engine.

#### 2.2.1 Registers

The micro-engines have four types of registers: general purpose, SRAM transfer, DRAM transfer, and Next Neighbor (NN). Micro-engine registers do not need to be flushed to memory when the control of the micro-engine switches from one thread to another because the hardware allocates an equal portion of the total register set to each micro-engine thread.

Each micro-engine has 256, 32-bit General Purpose Registers (GPRs), allocated into two banks of 128 registers. The GPRs per-micro-engine can be accessed in thread-local or absolute mode. In thread local mode, each thread accesses a unique set of GPRs. If the micro-engine configured to execute eight threads, 32 GPRs are allocated to each thread. However, if is configured to execute four threads, 64 GPRs are allocated to each thread.

Each micro-engine has 256, 32-bit SRAM transfer registers that are used to read from and write to all functional units on the Intel IXP2400 network processor except for the DRAM unit. SRAM transfer registers are the primary mechanism for dealing with asynchronous memory operations.

Each micro-engine has 256, 32-bit DRAM transfer registers divided equally into read-only and write only. DRAM transfer registers are used for communication between the micro-engines and the DRAM unit can be used for read-only communications with the other hardware unit. Like the SRAM transfer registers, DRAM registers can be accessed in thread-local and global manners.

Each micro-engine has 128 32-bit next neighbor registers. These registers can be used in one of two modes. The first mode makes data written in these registers available in the next micro-engine. Assisted by two Control and Status Registers (CSRs) in the micro-engine, the next neighbor registers are used as a 128-entry First-In-First-Out (FIFO) queue. In the second mode, the registers are used as extra general purpose registers. Each micro-engine has 640 long words of local memory. Any thread in the micro-engine can access data in this memory with at most three-clock-cycle latency, much faster than the scratchpad, SRAM or DRAM memory.

### 2.3 Memory

The IXP2400 Processor can access three external memory types the scratchpad, the SRAM and the SDRAM. All micro-engines as well as the Intel XScale Core processor share these memory interfaces.

Scratchpad memory is a 16K on-chip memory organized as 4K 32-bit words. It provides a small low-latency interface to all of the micro-engines. It supports operations that are ideal for keeping counters across multiple micro-engine threads as well as synchronizing access to data structures across micro-engines.

Unlike scratch pad memory, SRAM is off-chip. The IXP2400 processor only provides an interface to the actual SRAM. This interface is embodies in the micro-engine's SRAM unit. Each SRAM unit provides an interface for up to 64 Mbytes of memory. In addition, each SRAM unit contains a 64-element queue array. Like the SRAM memory, SDRAM memory is external to the IXP2400 processor. The DRAM unit provides an interface for up to one Gigabyte of high throughput memory.

#### 3 Network Processor Based Multimedia Router

#### 3.1 Introduction

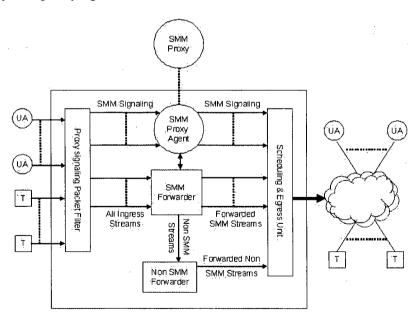

This chapter presents an architecture design that exploits the implementation of pipelined router architecture. A simple diagram of the proposed router architecture is shown in Figure 3.1 where it shows User Agents (UA) where each UA represents a multimedia client/server that may establish connection to another multimedia UA server/client. The router serves also non-multimedia Terminals (T) connected that may send, and receive non-multimedia streams like FTP, HTTP and text messaging. The first stage shown in the figure is a simple packet classifier in the ingress module that sends all received packets to an SMM forwarder while it picks the packets that should be distant to SMM proxy and sends a copy to a proxy agent.

Figure 3.1: Simple Diagram of the proposed router architecture

The purpose of the Ingress Packet Classifier is to determine the packets distant to a proxy server configured in the proxy agent, while the purpose of a proxy agent is to turn the router into multimedia aware router. The proxy agent can be programmed to serve selected multimedia streams that pass through the router and known to the agent. The router contains a Selective MultiMedia (SMM) forwarder that performs forwarding to the multimedia streams selected by the proxy agent. Strictly speaking, the SMM forwarder is unaware of the type of the stream it processes while the proxy agent is the one that determines the type of the streams, and builds the SMM forwarder lookup table.

To meet the quality of service requirements for multimedia networks and to enhance the search speed for the lookup tables in routers, the thesis proposes a fast method for searching the lookup table. The method is an indexing scheme that makes the search time for a record always constant regardless of the number of records in the lockup table. The lockup table record contains profiling information and forwarding information that is obtained from a static database and is updated by the network administrator. The forwarding information is obtained from the conventional routing table of the router.

When a new stream starts, the proxy agent is the one that updates the stream record in the SMM lookup table during the stream connection establishment.

Figure 3.2 shows the packet classification and forwarding where the Selective MultiMedia (SMM) classifier classifies the packets it receives into packets distant to a proxy servers and non-proxy packets that are not distant to a proxy server. The packet

distant to the proxy server passes through the proxy agent. Then, the proxy agent modifies the lookup table of the SMM forwarder. The forwarder knows from the updated lookup table which streams are Selected Multimedia streams and push the stream forward to the scheduler, while the non-selected multimedia streams passes through the normal routing and forwarding module.

Figure 3.2: Packet Classifying & Forwarding Diagram

Next, the streams are scheduled according to their profiles assigned by the scheduler that uses a new proposed scheduling algorithm known as the Lowest Credit Weighted Fair Queuing (LCWFQ) and the details of the algorithm are discussed in Chapter 5. the last module in the router is the egress module that transmits the packets to the external network.

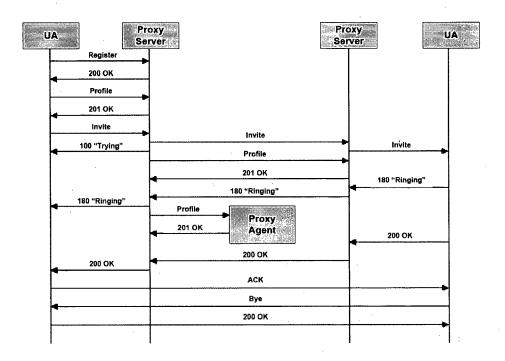

#### 3.2 Proxy Agent - Proxy Server Relationship

The User Agent (UA) sends signaling messages to the proxy Server to establish a connection to a remote UA. As explained earlier the router has a non-multimedia forwarding tables and a multimedia forwarding table. The UA signaling message uses the non-multimedia routing and forwarding module, as it does not need to have a high priority. Afterwards, the proxy server contacts the distant User Agent (UA) to establish the connection. In doing so, the normal routing module finds the routing information to the distant UA. Simultaneously, the proxy agent reads a copy of signaling message, which is distant to the proxy server that is known to the agent [2].

Figure 3.3: Proxy Agent – Proxy Server Relationship Diagram

#### 3.3 Architecture

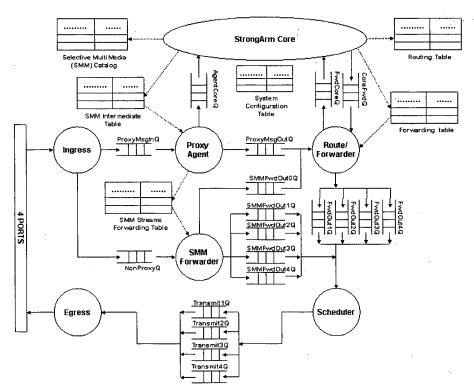

As shown in Figure 3.4 below, the proposed router has six modules, which are the Ingress, the Proxy Agent, the SMM Forwarder, the Route Forwarder, the Scheduler, and the Egress. The proposed router has a pipelined architecture taking the advantage of the of the network processor where each module is implemented in its own micro-engine and executed independent of each other (loosely coupled)

Figure 3.4: Detailed architecture of the SMM Router

#### 3.4 The Ingress

The Ingress unit receives packets at high speeds and maintains two queues, one queue to communicate with the Proxy Agent, which is known as the proxy queue, and the second is the non-proxy queue that communicates with the SMM Forwarder. The Ingress module maintains the IP address of the Proxy Server represented by the proxy agent.

#### 3.5 The Proxy Agent

When a User Agent (UA) seeks to communicate with another UA, it undergoes a sequence of steps that enables the UA to establish a communication session. The Proxy Agent handles these steps. Upon successful reception of a packet, the Ingress module retrieves the destination IP address from the DRAM where the packet is stored. It then compares the destination IP address with the IP address of the Proxy Server. If it matches, the packet is sent to the proxy queue or else to the non-proxy queue.

Assuming that the proposed router has eight ports, the Ingress will have eight hardware-assisted threads at its disposal. Each thread is associated with one port and performs similar operations on the packets received from that port. The Ingress unit design is modified to include a first level classifier to identify the multimedia signaling data with a destination address pointing to a proxy server previously configured in the proxy agent. It is assumed that the implementation of the router provides a way to set the address in the multimedia proxy server.

Part of the responsibility of the proxy agent is to identify the content of the packet to determine the proxy server of the UA. The Proxy Agent needs to know the address of each proxy server and can be as many proxy servers as needed. The addresses of the proxy servers are maintained in the *proxy agent* module. All packets sent to the proxy are kept in a single queue called *ProxyQ* queue. All other packets are sent to a single FIFO

queue called *NonProxyQ*. The Proxy Agent partially depends on the StrongArm XScale Core, hereinafter referred to as the Core.

Upon retrieving packets from *ProxyMsgInQ*, the first operation performed by the Proxy Agent is to copy the packet pointer into the output queue called *ProxyMsgOutQ*. This method enables the next module, which resides in a different micro-engine, to carry on processing the packet.

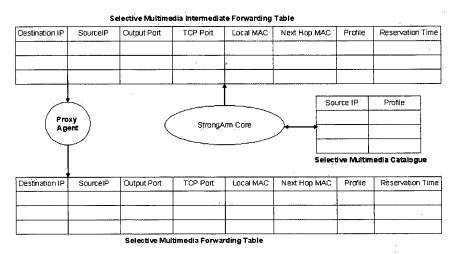

Figure 3.5: Operational relationship between the Core and the Proxy Agent

Figure 3.5 above shows a Proxy Agent makes use of three lookup tables called SMM Catalogue, SMM Forwarding Intermediate Table and SMM Forwarding Table. The SMM Catalogue is a static data table that associates the source address of the SMM UA to its assigned profile. The catalogue is initialized and then updated through the Core processor. Multiple User Agents may be assigned identical profiles. The network administrator assigns the profiles to indicate the service level for each UA. SMM Forwarding table is a data structure stored in the SRAM that is used to store records of composed information retrieved from the SMM Catalogue and the routing table.

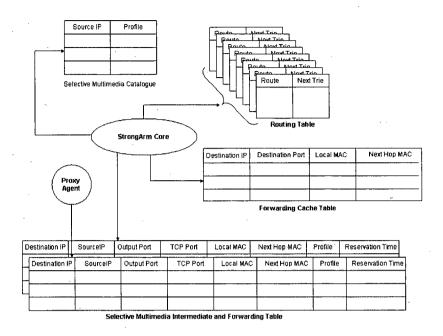

Figure 3.6: Relationship between Forwarding and routing tables

Unlike the Ingress module, the Proxy Agent needs to know the signaling protocol and has to be able to identify when a sender UA invites another UA for a communication session and when the receiver UA accepts the invitation. When the Proxy Agent detects an *INVITE* Message, the agent communicates with the Core processor so that the core loads all the necessary routing information into the SMM Forwarding Intermediate table. This is because an *INVITE* message most likely will be followed by an *OK* message and the communication begins. Retrieving the routing information before the communication begins will speed up the process. When an *OK* message is received, the stream record is marked active, and then is used later to assemble the packet to forward it to its destination. In fact, the SMM Forwarding Intermediate table and the SMM Forwarding Table are implemented as a single table with the addition of a flag field in the data

structure. Thus, the two tables are implemented as contiguous array of records interleaved with each other. The records marked active are those records for which the *INVITE* and *OK* messages have been received and the records marked inactive are those records for which only the *INVITE* message has been received [3] [4].

#### 3.6 The SMM Forwarder

SMM Forwarder is a module running in a single micro-engine that is responsible for classifying incoming packets into multimedia and non-multimedia packets. It places the classified packet record into a queue identified by the port number while the non-multimedia packets are placed in a single queue, which is a shared memory by the SMM Forwarder and the Route/Forward unit.

The SMM forwarder communicates with the Ingress module through a FIFO queue implemented in the SRAM. Each queue element contains a pointer to a DRAM unit where the packet under consideration is stored. The proposed SMM forwarder and profiler modules create a common data structure that contains the pointer to the packet, the source and destination IP addresses, and the length of the packet. It uses the source IP address to index the active catalogue maintained in the SRAM from which the profile of the source are retrieved. The profile ID and the relevant data are then added to the data structure created. These data are then placed in a different SRAM queue that serves as communication channel between the SMM Forwarder and the Scheduler. If a route record corresponding to a source is not found in the SMM forward table, the source record data is passed to the normal Router/Forwarder module [5].

The SMM Forwarder identifies whether the packet is a multimedia or not by looking up the SMM Forwarding table updated by the Proxy Agent. The packet is identified as multimedia packet if the source IP address of a packet is found in the SMM Forwarding table. Then the forwarder passes the profile information to the scheduler. If the packet is non-multimedia, then the SMM forwarder send it to the normal forwarder to find the routing information in conventional way. Non-multimedia packet gets the lowest profile then sent to the scheduler.

#### 3.7 The Forwarder

The Route/Forward module is responsible for routing and forwarding all non-multimedia in addition to the multimedia signaling packets. It initializes and maintains the routing table to determine the output port path of the packets. After determining the route for a packet, both the Proxy Agent module and the Route/Forward module transfer the records for the packets under consideration to the respective queues. The scheduler dispatches the packets to the Egress module, which performs the actual transmission of the packets to the external network. The next chapter provides more details on the scheduler.

Because of the real time requirements of multimedia streams, it is important that the search of a record corresponding to the packet under consideration is time efficient. For this purpose, the thesis introduces a three level indexing scheme discussed next.

#### 3.7.1 Three-Levels Indexing

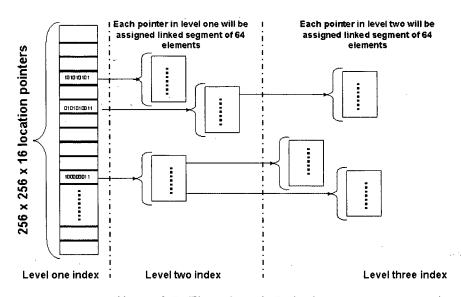

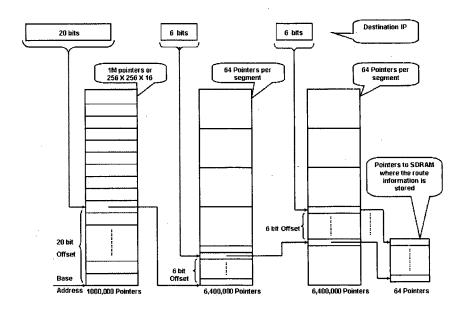

In the implementation of the proposed router, the lookup tables are designed to keep the routing information in the SDRAM. However, retrieving the information with fewer memory accesses is critical. The thesis proposes Three-Levels Indexing method for route storage scheme whereby the route of any destination IP address is determined by three memory accesses as illustrated in Figure 3.7.

Figure 3.7: Three Levels Indexing

The first level is an array of one million SRAM pointers pointing to a second level of memory segments, which uses the most significant 20 bits of the destination IP address. The second level, indexed by the next 6 bits of the IP address, points to a memory segment storing 64-DRAM memory locations represented by the last 6 bits. The third level of the memory segment is stored in the DRAM and contains the addresses where the stream information is stored.

This mechanism insures that the time required finding a record is always 3 memory accesses regardless of the number of records. The lookup table may hold hundreds of thousands of records or even millions while keeping the search time fixed. The record may include the destination port, the multimedia profile tag, the pointer to the actual packet, and any other information that may be required. The record is used in the forwarding process, scheduling process, and routing process.

Figure 3.8: Forwarding Table Structure

In an example of a worst case scenario, the maximum number of memory locations to build the three levels index is equal to the first level 20 bits (1,000,000) x second level 6 bits (64) x third level 6 bits (64) = 4 Giga locations, which practically will not happen. Typically, for 64,000 streams routes, it needs 100,000 locations out of the first 20 bits index and that reduces the total number of locations to the following:

L1 (1,000,000) + L2  $(100,000 \times 64)$  + L3  $(100,000 \times 64)$  = 13,800,000 locations.

Similarly, one million records need 129,000,000 index locations, which is still affordable by most of the available network processors. The three-levels indexing method is scalable to accommodate larger forwarding tables. In this way, one forwarding table may hold millions of records and searching time stays fixed unlike the hashing searching method and the binary searching method where the scalability costs more delay. However, if the memory cost is a concern, then more levels of indexing may be considered [6][7][8].

#### 3.8 The Scheduler

There is a complexity in implementing the per-flow scheduler in the most commonly used core routers. Routers use aggregate scheduling rather than per-flow scheduling. The proposed scheduler module provides a simple method to regroup the individual streams into aggregate flows and turn the per-flow scheduling to aggregate scheduling. The scheduler uses the time waiting the Egress to transmit one packet to turn on Adaptive Weight Adjustment (AWA) scheme. The AWA calculates the backlog traffic in the scheduler input queue and readjust the aggregate profiles accordingly. For simplicity, the AWA scheme will be referred through the thesis as the traffic shaper. The traffic shaper looks at the backlog packets and adjusts the aggregate profile weight. The scheduler uses the calculated aggregate profiles.

### 3.9 The Egress Module

The Egress module transmits the scheduled packets to the external network. The Egress is deployed on one micro-engine. Each port requires a dedicated micro-engine thread.

When it dispatches packets, the scheduler uses as many queues as the number of ports.

#### 4 Selection of a Suitable Scheduler

#### 4.1 Introduction

In this chapter, there is a consideration of three scheduling algorithms called First-In-First-Out (FIFO), Round Robin (RR), and Deficit Round Robin (DRR). The chapter discusses the merits of these algorithms to determine their suitability in the real time system. The next chapter will introduce the Lowest Credit Weighted Fair Queuing that has a predictable behavior and effective packet processing cost.

#### 4.2 First-In-First-Out (FIFO)

In FIFO scheme, the order of the packet arrival determines the allocation of packets to output buffers. This algorithm assumes that congestion control is performed by the source itself. To achieve this purpose it uses a feedback scheme. In feedback schemes for congestion control, connections are supposed to reduce their sending rate when they sense congestion. However, a rogue flow can keep increasing its share of the bandwidth and cause other well-behaved flows to reduce their share. If a rogue connection sends packets at a high rate, it can capture an arbitrary fraction of the outgoing bandwidth.

#### 4.3 Simple Round Robin

Simple Round Robin is a scheme by which every profiled queue is serviced at least once in every round. Ordinary round robin servicing of queues can be done in constant time.

The major problem, however, is the unfairness caused by possibly different packet sizes used by different profiles. For example, if, hypothetically, the low priority profile keeps

sending long packets while the high priority profiles have short packets, then the low priority profile monopolizes the use of the bandwidth. Therefore, this scheme is not suitable for scheduling multimedia streams [9] [10].

#### 4.4 Deficit Round Robin

Deficit Round Robin is a scheduling algorithm [11][12] whereby the scheduler transmits packets from different profiles based on predetermined quantum values assigned to each of these profiles. The scheduler allows each profile to send packets subject to the length of the packet. The packet length, expressed in bytes, is less than or equal to the sum of the quantum value assigned to the profile and the value contained in a state variable called the Deficit Counter, which contains the difference between the assigned quantum value and the number of bytes transmitted in the previous round. If there are no more packets in the queue, the scheduler resets Deficit Counter to zero. Otherwise, it holds the difference between the assigned quantum value and the length of the packet sent.

DRR provides an isolation mechanism that achieves nearly perfect fairness, and also takes O (1) work to process a packet. The scheme is simple to implement at a router or a gateway. The main difference between DRR and RR is that if a queue was not able to send packet in the previous round because its packet size was too large, the remainder from the previous quantum is added to the quantum for the next round. Thus, deficits are tracked and recorded, and hence, queues that were shortchanged in a round are compensated in the next round.

#### 4.4.1 DRR Weakness

The empty queue introduces errors for the DRR process. To avoid empty queues, the algorithm keeps an auxiliary list called the Active List, which is a list of indices of queues that contain at least one packet. The packet is added to the end of Active List when it arrives to a previously empty queue. Whenever the index is at the head of the Active List, the algorithm services the corresponding queue by scheduling packets whose combined length is less than or equal to the sum of the Quantum value and the Deficit Counter. If at the end of this service opportunity the queue still has packets to send, the index is moved to the end of Active List, otherwise the Deficit counter is set to zero.

The size of the various quantum variables in the DRR algorithm determines the number of packets that can be served from a queue in a round. This means that the latency for a packet and the throughput of the router are dependent upon the value of the quantum variable. The thesis introduces a new scheduling algorithm to avoid this dependency. The new scheduling algorithm called the Lowest Credit Fair Queuing that has work load of O(1) and achieves a fairness index of 1 (one), which is discussed in the next chapter.

#### 4.5 The SFQ and SCFQ

These schedulers are time-based schedulers [13]. The LCWFQ, DRR, RR, and FIFO are frame-based schedulers [14][15]. However, the proposed adaptive weight adjustment method behaves when used with the scheduler it does fall in a category between the frame scheduling and time scheduling as it depends on the time spent by the Egress to transmit the last packet to recalculate and redistribute the bandwidth shares.

### 5 Scheduler and Traffic Shaper

#### 5.1 Introduction

This chapter presents a proposed scheduling method as part of a router and called Lowest Credit Weighted Fair Queuing (LCWFQ). There is an additional module added to the scheduler, which is Service Level Agreement Manager module that allocates bandwidth to clients based on a specified Service Level Agreement (SLA).

The chapter presents also the proposed Adaptive Weight Adjustment method that may be used in some situations when the Internet Service Provider may be over committed to the subscribers. Another situation would be when there is a need to serve applications that normally are inactive unless required like the Lawful Intercept (LI) function. The LI function is intercepting with certain streams, copy the streams, and send them to a LI agent. The intercepted streams require a very small bandwidth, yet have a very high priority.

#### 5.1.1 Per-Flow scheduling Vs Aggregate Scheduling

The thesis proposes the LCWFQ, which is a weighted fair queuing scheme. LCWFQ is used to schedule flow traffic in a per-flow scheduling mode. However, the LCWFQ is designed also to schedule the aggregate flows with the help of the proposed add-on modules like the SLA manager and the proposed AWA traffic shaper.

In order to use the LCWFQ with the aggregate flows, each flow must be assigned to a profile group and then each group is assigned to an aggregate flow. Each aggregate flow must have a new profile value for the scheduler. The traffic shaper calculates these values as explained later. All flows belong to the same aggregate flow must have the same profile weight. The aggregate flow weight is calculated as the total number of streams/flows within the aggregate multiplied by the per flow weight originally assigned by the SLA. The thesis presents two schemes for the traffic shaper where one scheme is based on fixed weight assigned by the SLA while the other scheme is an adaptive weight adjustment calculated based on the backlog traffic in the scheduler input queue.

### 5.1.2 Forwarder, Profiler and Scheduler relationship

Since packet sizes are generally large to move internally between the internal modules, the router saves the packets in memory and work only with packet pointers. The payload data portion of the packet is not needed until the packet is ready to leave the router. Following this logic, the forwarding module passes one record for each packet, which contains the packet pointer, the packet length, and the packet profile. The profile of the packet represents the percentage quota of the bandwidth given to a packet stream from a specific source address. In the design of the high performance network processor based router, the Ingress module extracts information from the received packet and passes it through to the forwarder. Then, the forwarder calculates some other information to determine the route for each incoming packet and send it to the scheduler.

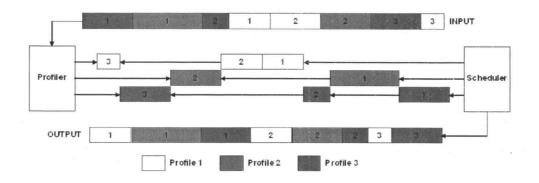

The profiler is a module that adds the profile information into a proposed forwarding table. It should be mentioned that the profiler reuses the forwarder information to classify the packets. The profiler in this case is running with a minimal processing cost since it reuses the existing information. Then the profiler passes the results into the scheduler input queue along with the packet descriptor information. The scheduler works with the classified packets that are placed in their own separate queues by the profiler. Figure 5.1 illustrates the profiling mechanism applied on three profiles, when the scheduler implements a round robin scheduling algorithm.

Figure 5.1: An illustration of the profiling mechanism for three profiles

#### **5.1.2.1** Profiler Processing Cost

In order to depict the profiler processing cost, a sample calculation is provided below to calculate the total time required to build the profiler information for one packet in the worst condition when the packet is short, or in other words, 64 bytes long. A single access to the SRAM takes approximately 4 clock cycles and the maximum clock frequency of the IXP2400 network processor is 600MHz.

The proposed Three-Level indexing needs three memory accesses to read a record then one-memory access to write. Thus, the access time, as discussed in chapter 2, takes a total memory access time of

$$t_{read} = \frac{3*2 \ Clock \ Cycles}{600MHz} = 0.01 \mu s$$

$$t_{write} = \frac{1*4 \ Clock \ Cycles}{600MHz} = 0.006 \mu s$$

However, sending the same packet (64 bytes) over a line with a rate of 100Mbps line takes a transmission time, tx, of

$$t_x = \frac{8\frac{bits}{byte} * 64bytes}{100Mbps} = 5.12\mu s.$$

Therefore, the maximum overhead delay,  $t_{overhead}$ , is approximately

$$t_{overhead} = \frac{0.016\mu s}{5.12\mu s} *100 = 0.003\%$$

This delay is considered negligible compared to delay caused by any queuing situation.

One of the conclusions is that by adding processing functions on early stages of the router, it saves processing time later. These proposed functions are the profiler, the Proxy Agent, the SLA manager, and weight adjustment traffic shaper. The proposed functions are simple and low cost processes. Moreover, these functions make the other modules like the scheduler and the forwarder processes simpler and shorter.

## 5.2 The Profiler

The purpose of the Profiler is to assign a profile tag to the incoming packet record and place the packet record in a queue designated for each profile. The profiler packet record is mainly the packet length, source IP and destination IP addresses and the profile tag.

Normally, the profiler search for the profile tag for each incoming packets in the profiling table based on the source address. It is proposed that the profiler with the use of the SLA manager extracts the profile information from each SLA and populate the profiling table. It is proposed also that the profiler with the help of the weight adjustment, construct the aggregate flows and assign them new profile values.

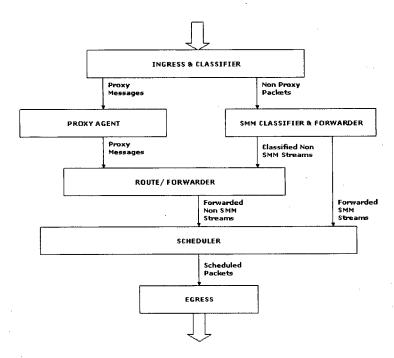

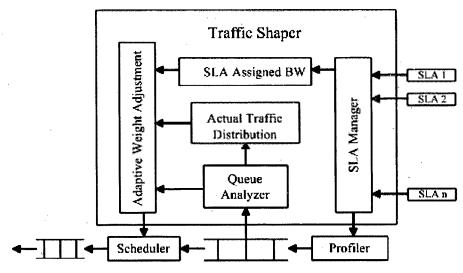

In ASD Architecture diagram shown in figure 5.2, the profiler does calculations that describe the aggregate flow profiles and sends the results along with the packet headers to the scheduler input queue.

The profiler module classifies incoming packets according to their source information like the IP address, port number, and then obtains the profile information from the SLA manager. That makes the scheduler dedicated to perform packet scheduling based on the assignments prepared by the profiler. The record for each packet in the scheduler input queue contains:

- 1. The length of the packet

- 2. The profile identification

- 3. The total length of all previously arrived packets

- 4. The total length of all previously arrived packets from the same profile

- 5. The pointer to the next packet in the same profile

- 6. The pointer to the packet data

The Scheduler creates one queue for each physical egress port. These queues are shared memory regions, or Next-Neighbor registers in the IXP2400, used by the Scheduler and the Egress module to exchange packet records.

Figure 5.2: ASD Architecture

The Profiler is responsible for assigning profiles for incoming packets according to a profiling database maintained within the profiler application. Having done the profiling, the Profiler sets up a separate queue for each profile and places every packet in its own respective queue. In the proposed Multimedia Router application, the profiling database is a static data table based on the Service Level Agreements (SLA) and can be changed by the network administrator. The profiler is accessible to both the Traffic Shaper and the Scheduler.

# 5.3 Adaptive Weight Adjustment

#### 5.3.1 Formulas and mechanism

Routers use aggregate scheduling rather than flow scheduling. The thesis proposes an Adaptive Weight Adjustment (AWA) heuristic method to provide a simple way to adjust the scheduling parameters and adapt the scheduler to serve aggregate flows. For simplicity, the adaptive weight adjustment will be expressed as the traffic shaper though the thesis. To explain the traffic shaper method, assume that the service provider signs hundreds of thousand of service level agreements with the subscribers. It is expected that the subscribers, over time, will generate distinctive flows equal to or more than the number of the signed agreements. However, these distinctive flows may be grouped into few aggregate flows based on their assigned profiles.

Similarly, the proposed traffic shaper reads the SLA parameters for each subscriber and catalogues the agreements into complete and detailed database of flow profiles. Then the traffic shaper works on the created database to link each flow profile to an aggregate flow profile. All flow profiles that belong to the same aggregate profile have the same type like VoIP, HTTP, FTP and also have the same characteristics like packet length and maximum accepted delay. This way, the number of aggregate flows will be few compared to the distinctive flows. Within the aggregate flow, all packets are treated similarly. The proposed traffic shaper puts each aggregate flow in a separate input queue to the scheduler. This way, it simplifies the scheduling process and the scheduler deals with aggregate flow as if it is a single flow.

During initialization, a proposed SLA manager module calculates the weight assigned to each aggregate flow and assigns it as initial value. Then after initialization, the adaptive weight adjustment or the traffic shaper starts. The traffic shaper measures the actual active aggregate flows, recalculates the aggregate flow weight, and then sends the new values to the scheduler. From figure 5.2 shown earlier, a queue analyzer unit determines the actual traffic distribution for all profiles. The traffic shaper receives the assigned bandwidth from the SLA manager and the actual traffic distribution from the analyzer. Then the shaper uses the assigned bandwidths and the actual traffic composition to determine the final weights for each aggregate profile, which is named within the thesis as the adaptive weight adjustment. The actual aggregate profile rate,  $R_{act,p}$  is recalculated according to the following formula:

$$R_{act,P} = \frac{l_p}{\sum_{p=1}^{N_p} l_p},$$

Where  $l_p$  is the combined length of all the packets in aggregate profile p and  $N_p$  is the number of aggregate profiles.

If,  $\forall p, R_{act,p} \leq R_{as,p} \Rightarrow R_{f,p} = R_{as,p}$ , where p is the active aggregate profile number, and  $R_{f,p}$  is the final calculated percentage of the active aggregate profile. Otherwise,

$$R_{f,p} = \frac{R_{act,p} + \min(R_{as,p}, R_{act,p})}{\sum_{p=1}^{N_p} (R_{act,p} + \min(R_{as,p}, R_{act,p}))}$$

Where  $R_{as,p}$  is the assigned percentage for profile p. It is assumed that the above formulas expressed for a single output port. For any port j and profile i the two schemes are expressed as,

$$R_{acr,Porr[j]}[i] = \frac{profileLength[i]_{Porr[j]}}{\sum_{i=0}^{n-1} profileLength[i]_{porr[j]}}$$

And

$$R_{adapted,port[j]}[i] = \frac{R_{actual,port[j]}[i] + \min(R_{assigned,port[j]}[i], R_{actual,port[j]}[i])}{\sum_{i=0}^{n-1} (R_{actual,port[j]}[i] + \min(R_{assigned,port[j]}[i], R_{actual,port[j]}[i]))}$$

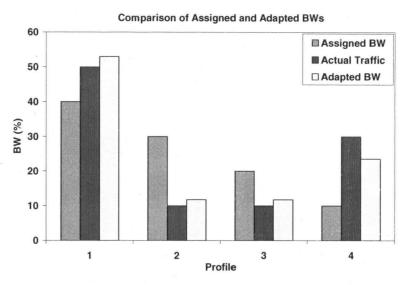

Table 5.2 and figure 5.4 are numerical examples for the above formulas and demonstrate the effectiveness of the traffic shaper, which is based on adapted weight adjustment. For example, the actual traffic of profile 1 is greater than the assigned value while profile 2 and profile 3 have a traffic level less than the assigned. In this case, the traffic shaper distributes the BW such that active aggregate profile 1 gets more than the assigned BW while profile 2 and 3 are assigned a value of BW that is just enough to accommodate their needs. In addition, even though profile 4 has the lowest priority (as determined by the initial BW assignment), it is allocated more than its assigned value.

|                                                 | P1    | P2    | P3    | P4    |

|-------------------------------------------------|-------|-------|-------|-------|

| Assigned BW (%)                                 | 40    | 30    | 20    | 10    |

| Actual Traffic (%)                              | 50    | 10    | 10    | 30    |

| Minimum of Actual and assigned R <sub>min</sub> | 40    | 10    | 10    | 10    |

| Sum of Actual and R <sub>min</sub>              | 90    | 20    | 20    | 40    |

| Adapted BW Assignment                           | 52.94 | 11.76 | 11.76 | 23.53 |

Table 5.1: Illustration of Traffic shaping in the case of four profiles

Figure 5.3: BW adjustment performed by the Traffic Shaper in case of four profiles

The traffic shaper used the unallocated bandwidth from the aggregate profiles that are not using all of their assigned bandwidth and then reassigns the unused bandwidth to active aggregate profiles that needs it. The traffic shaper may also be configured to set threshold alarms when a certain aggregate profile exceeds its usage of the allocated bandwidth.

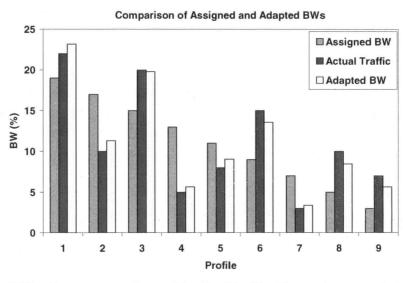

Table 5.3 and figures 5.4 show another example using nine profiles.

Figure 5.4: BW adjustment performed by the Traffic Shaper in case of nine profiles

|                                                 | P1   | P2   | Р3   | P4  | P5  | P6   | P7  | P8  | P9  |

|-------------------------------------------------|------|------|------|-----|-----|------|-----|-----|-----|

| Assigned BW (%)                                 | 19   | 17   | 15   | 13  | 11  | 9    | 7   | 5   | 3   |

| Actual Traffic (%)                              | 22   | 1.0  | 20   | 5   | 8   | 15   | 3   | 10  | 7   |

| Minimum of Actual and assigned R <sub>min</sub> | 19   | 10   | 15   | 5   | 8   | 9.   | 3   | 5   | 3   |

| Sum of Actual and R <sub>min</sub>              | 41   | 20   | 35   | 10  | 16  | 24   | 6   | 15  | 10  |

| Adapted BW Assignment                           | 23.2 | 11.3 | 19.8 | 5.7 | 9.0 | 13.6 | 3.4 | 8.5 | 5.7 |

Table 5.2: Illustration of Traffic shaping in the case of nine profiles

In the proposed network processor architecture, the Traffic Shaper and the Scheduler reside on the same micro engine. Therefore, the adapted percentage, which is calculated by the Traffic Shaper, is communicated to the Scheduler through shared registers, called absolute registers in the IXP2400 NP. If the number of profiles is too large to be contained within the registers, it is spilled to the local memory of the micro engine. The local memory has a lower latency than all the three different kinds of memory the IXP2400 supports, and hence the performance penalty has low significance.

In relation to the network processors, and in order to calculate the actual percentage composition, the Traffic Shaper makes use of the state information stored in Scratchpad. It performs a number of Scratchpad memory accesses that is equal to one more than the number of the active aggregate profiles. One memory access is required per profile to read the length of each aggregate profile. Additional memory access is required to read the combined length of all aggregate profiles. Therefore, its performance is proportional to the number of the active aggregate profiles.

### 5.3.2 AWA Traffic Shaper Performance

As described before, the traffic shaper uses the unallocated bandwidth from the profiles that are not using their assigned bandwidth and reassigns it to the profiles that need it. Figure 5.5 shows an example of the traffic shaper handling the highest priority. It can be seen that the Traffic shaper always finds middle "ground" between the actual traffic percentage and the assigned bandwidth. Because Profile 0 does not have enough traffic to use, the traffic shaper strips off the bandwidth assigned to profile 0.

Figure 5.5: Adaptive Weight Adjustment for profile 0

Figure 5.6 shows an example of the adaptive weight adjustment handling the lowest priority profile. It can be seen that the Traffic shaper always finds middle "ground" between the actual traffic percentage and the assigned bandwidth. Because profile 8 has a traffic level that is much higher than it can accommodate within its share, the traffic assigns more bandwidth to the "needy" profile 8. The extra bandwidth was taken earlier from the unused bandwidth by other profile like profile 0.

Figure 5.6: Adaptive Weight Adjustment for profile 8

Figure 5.7 shows the bandwidth allocation pattern for profile 4, which has a medium priority compared to profile 0 and profile 8. As shown in the figure, profile 4 has been provided less bandwidth than the assigned value because its actual traffic is low.

Figure 5.7: Adaptive Weight Adjustment for profile 4

However, the Traffic shaper ensures that this profile does not get more bandwidth than the assigned value when the actual traffic of the profile is less than the assigned value.

## 5.4 LCWFQ Scheduler

### **5.4.1** Assumptions and Notations

- The line rate (wire speed) is known to be a constant R bits per second.

- The total number of active aggregate profiles  $(N_p)$  is known.

- The elements (packets) of the aggregate queue are sorted according to their arrival time in the queue.

- The rate for every active aggregate profile  $(r_i)$  is specified as a percentage of the line rate, where r is the percentage bandwidth allocation of the  $i^{th}$  profile.

### 5.4.2 The LCWFQ Name Origin

The "Lowest Credit" name is driven from your bank credit card statement value when it is negative, it means the bank owes you money and when it is positive, it means you owe the bank. Assume that all cardholders are the only owners of the bank and assume simple bank operation that when you owe the bank, you owe each cardholder a percentage of your debts equal to the share of the cardholder.

## **5.4.3 LCWFQ Concept**

Similarly, the LCWFQ scheduler serves all profiles as if all the profiles own the scheduler and each profile owns a share equal to the assigned bandwidth percentage defined by the SLA for that profile. When a packet is served from a profile for a certain time t, the served profile owes each of the active non-served profiles a share of the time t

to wait. Each of the non-served profiles gets a share equal to the time *t* multiplied by the assigned bandwidth percentage for that non-served profile.

The credit value  $C_i$  for the  $i^{th}$  profile that has just been scheduled and is calculated according to the formula  $C_i = C_i - 1 + L_i * (1 - r/100)$ . This is the bandwidth that the current profile "owes" to the other profiles. The credit value for the other profiles is calculated according to the formula  $C_i = C_i - 1 - L_i * r/100$ . The right operand calculates the share of the total bandwidth that is owed to this profile by the profile of the transmitted packet. The whole expression evaluates the net credit value for the profile.

After the credit values for every profile is updated, the scheduler goes back to fetch the record for the next packet in the next profile. If there are no packets in the queue, the scheduler resets the previous credit values. If there is only one packet in the queue, the scheduler updates the previous credit to the new calculated value. If there is more than one packet in the queue and if all the packets have the same profile, the packets will be scheduled according to their order in queue. Within the same profile, the first packet encountered first is the first to be scheduled.

However, if the packets in the queue have different profiles, the scheduler will select the packet that has a profile of the lowest credit value. Again, the credit value of each profile is calculated accordingly. A sample scheduler calculation for the scheduler is shown table 5.3. For simplicity, it is assumed that all packets have the same length of 1500 bytes.

| Packet | Rate    | 10%      | 10% 20%  |          | 40%      |

|--------|---------|----------|----------|----------|----------|

| Length | Profile | Credit 1 | Credit 2 | Credit 3 | Credit 4 |

|        |         | 0        | 0        | 0        | 0        |

| 1500   | 4       | -150     | -300     | -450     | 900      |

| 1500   | 3       | -300     | :-600    | 600      | 300      |

| 1500   | 2       | 600      | 600      | 150      | -300     |

| 1500   | 1       | 750      | 300      | -300     | -900     |

| 1500   | 4       | 600      | 0        | -750     | 0        |

| 1500   | 3       | 450      | -300     | 300      | -600     |

| 1500   | 4       | 300      | -600     | -150     | 300      |

| 1500   | 2       | 150      | 600      | -600     | -300     |

| 1500   | 3       | 0        | 300      | 450      | -900     |

| 1500   | 4       | -150     | 0 .      | 0        | 0        |

Table 5.3: Numerical example of the scheduler

-300

-600

-900

1200

1050

900

750

-450

-900

150

-750

-600

300

-900

### 5.4.4 LCWFQ Operation

1500

1500

1500

1500

1500

The scheduler serves only one packet in a full round. The scheduler starts the round by checking the credit value of all active profiles and serves a packet from the profile that has the lowest credit. A credit is defined as the assigned bandwidth percentage that a served profile owes to other non-served profiles. A negative credit value for a profile indicates that the scheduler owes the profile a service. If the system owes multiple profiles a service, the system serves the profile with the lowest credit value first.

Initially a credit of zero is assigned to each profile. As packet(s) arrive in the queue, the scheduler selects a packet that has the lowest credit and places it in the corresponding egress queue then updates the credit value for all profiles. The credit value Ci for the ith profile that has just been scheduled is given by

$$C_i = C_{i-1} + L_i * (1 - \frac{r_i}{100})$$

Following the logic, for the non-served profiles, the credit value Cj for the jth is given by

$$C_{j} = C_{j-1} - L_{i} \frac{r_{j}}{100}, i \neq j$$

The right operand evaluates the share of the total bandwidth that is owed to the profile.

After the credit value for each profile is updated, the scheduler starts the next round and fetches next record for the next packet. If there are no packets in the queue, the scheduler resets the previous credit values.

If, during the scheduling process, the LCWFQ scheduler finds that any two or more aggregate profiles have identical and lowest credit values, it selects a packet that has an aggregate profile with the highest assigned percentage. However, if all of the lowest credit profiles have identical assigned percentages, it schedules the packets in a simple round robin fashion.

LCWFQ always operates with O(1) work complexity and, unlike DRR and PDRR, does not require the prior knowledge of the maximum size of a packet that eventually arrives in the system. All profiles are considered during every scheduling cycle and only one of them qualifies to have a packet scheduled. In addition, the scheduling process is independent of the status of the input queue. That is, it performs steadily whether the queue is backlogged or not. In the case when a profile is empty, it accumulates credit

only to a pre-specified level. In addition, a profile can only owe a pre-specified level of credit to the remaining active profiles.

# 5.5 Performance Analysis of LCWFQ

### 5.5.1 Computational Complexity

The input queue to the scheduler is organized such that it has as many queues as the number of profiles. The scheduler, the traffic shaper, and the profiler share a data structure that describes the queue. The description of the queue contains the location of the head of each sub-queue. The profiler adds a packet at the end of the queue and the scheduler removes a packet from the beginning of the queue. Therefore, the scheduler does not spend any time searching for a packet within the queue. That is why the per packet work complexity of the LCWFQ scheduler is O(1). The scheduler performance does not depend upon knowing the maximum packet size that possibly arrives in the system. Furthermore, there is no hashing involved to queue packets according to their profiles. Each aggregate profile is assigned its own queue and newly arriving packets are appended at the end of the queue. This renders the queuing mechanism to be simple and low processing cost.

# 5.5.2 Startup Latency

The worst-case situation is when all aggregate profiles are active at the same time.

Assume a case when the router restarts or when many packets arrive at the same time from multiple input ports and exit from one single output port. Also, assume that these packets belong to deferent profiles. In this circumstance, the LCWFQ scheduling

algorithm selects the packet that has a profile of the highest bandwidth percentage assignment. The worst-case scenario is when a profile i has the lowest assigned bandwidth. The packet that belongs to the profile in question will wait until its credit value becomes the lowest. This happens after  $(N_P - I)$  aggregate profiles are served where  $N_P$  is the number of the active profiles. Assume that m is the size (in bits) of the largest packet served during the execution of one scheduling cycle. It implies that, at most,  $(N_P - I)^*$  m bits are sent before the first bit of the profile is sent. Then the maximum latency experienced by an aggregate profile in a startup cycle is

$$D_{LCWFQ} \le \frac{(N_P - 1)m}{R}$$

## 5.6 Service Level Agreement (SLA)

The ISP may provide three types of services called Premium, Normal, and Light. Subscribers under the same type of service share the same aggregate profile. Assume the Normal service is an average type of service and the Premium service has higher priority and higher bandwidth allocation than the Normal service. Also, assume the Light service is a low speed service with a lower priority than the Normal and Premium Services.

Suppose that the premium SLA (profile 1) value is 60 (like \$60 a month), the normal SLA (profile 2) value is 30, and the light SLA (profile 3) value is 10. Assume also, there is only one common output port channel that is used to carry the traffic from all

subscribers. Then the fair percentage of the output port usage should be 60%, 30%, and 10% respectively.

However, if there are 20 subscribers that have a premium SLA of profile1-1, 10 clients with SLA of profile-2 and 10 clients with SLA of profile-3 and all of them uses the common channel simultaneously. Then profile-1 subscribers would require 1200 points value of the port assigned bandwidth percentage, while profile-2 Subscribers would require 300 points value of the bandwidth, and finally profile-3 clients would require 100 points value of the bandwidth. In this case, the bandwidth allocations can be adjusted so that it reflects the weight of the original percentage assignments. The results are summarized below.

| SLA Value                           | $ \begin{array}{c cccc} SLA \ Value & Symbolic & Profil \\ \hline & Representation & BW_1=0 \end{array} $ |                         | Profile2<br>BW <sub>2</sub> = 30% | Profile3<br>BW <sub>3</sub> = 10% |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------|-----------------------------------|--|--|

| # Of subscribers per<br>SLA         | $(N_{C_i})$                                                                                               | 20 Subscribers          | 10 Subscribers                    | 10 Subscribers                    |  |  |

| Relative BW<br>Requirement          | $(BW_i * N_{C_i})$                                                                                        | 60 x 20 = 1200          | 10 x 30 = 300                     | 10 x 10 = 100                     |  |  |

| BW Assignment Per Aggregate profile | $\left(\frac{BW_i * N_{C_i}}{\sum BW_i * N_{C_i}}\right) * 100$                                           | 75.00 %                 | 18.75 %                           | 6.25 %                            |  |  |

| BW Share per Client                 | $\left(\frac{BW_i}{\sum BW_i * N_c}\right) * 100$                                                         | 3.75%<br>per subscriber | 1.875%<br>per subscriber          | 0.625 %<br>per subscriber         |  |  |

Table 5.4: Illustration of Profiling based on a Service Level Agreement

The SLA manager accepts the SLA configurations from the administrator. Individual SLA specifies the maximum delay and minimum transmit rate then translated into assigned bandwidth BW for each aggregate profile and maximum delay aggregate profiles whenever required.

The shaper readjusts the assigned bandwidth and reports over-usage using the maximum delay. For example, for a certain profile  $P_i$ , if the line speed is 10Mb/s and the SLA for  $P_i$  is 10% guaranteed bandwidth and the maximum delay guaranteed is 250ms, there will be number of issues to consider. In order to guarantee the maximum delay for a certain SLA, the SLA should include profile rate ratio,  $r_{MaxDelay}$ , of

$$r_{MaxDelay} = \frac{LP_i}{TP_i x R}$$

Where R is the line rate, where  $TP_i$  is the Max delay for a profile i, and where  $LP_i$  is the length of profile i in the input queue.