#### DECOUPLING CAPACITOR DESIGN ISSUES IN 90NM CMOS

by

#### XIONGFEI MENG

B.A.Sc., The University of British Columbia, 2004

# A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES (ELECTRICAL AND COMPUTER ENGINEERING)

The University of British Columbia

April 2006

© Xiongfei Meng, 2006

#### **ABSTRACT**

On-chip decoupling capacitors (decaps) are widely used to reduce power supply noise. Typically, designs use NMOS decaps between standard-cell blocks and NMOS+PMOS decaps within the blocks. Starting at the 90nm CMOS technology node, the traditional decap designs may no longer be suitable due to increased concerns regarding thin-oxide gate leakage and electrostatic discharge (ESD) reliability. This thesis investigates new decap design approaches that address gate leakage and ESD. A cross-coupled design is described that has been recently introduced by cell library developers to handle ESD problems. Three modifications of the cross-coupled design are introduced here and the tradeoffs among transient response, gate leakage and ESD performance are analyzed. The modifications offer designers greater flexibility in decoupling capacitor design for 90nm and below. To improve the power-grid noise reduction capability in the areas between blocks, two versions of a switched-decap design are proposed. One provides excellent decap performance but consumes large power, whereas the other saves power but suffers from excessive delay. A novel low-power voltage regulator using switched decaps is proposed to better balance performance and power consumption.

# TABLE OF CONTENTS

| ABSTRACT                                                  | I    |

|-----------------------------------------------------------|------|

| TABLE OF CONTENTS                                         | III  |

| LIST OF TABLES                                            | V    |

| LIST OF FIGURES                                           | Vl   |

| ACKNOWLEDGMENTS                                           | VIII |

| CHAPTER 1 INTRODUCTION                                    | 1    |

| 1.1 MOTIVATION                                            | 1    |

| 1.2 DECOUPLING CAPACITORS ISSUES AT 90NM                  | 5    |

| 1.3 RESEARCH OBJECTIVES                                   | 7    |

| 1.4 Organization of the Thesis                            | 8    |

| CHAPTER 2 BACKGROUND                                      | 10   |

| 2.1 Introduction                                          | 10   |

| 2.2 DECOUPLING CAPACITOR MODELING                         | 11   |

| 2.3 GATE TUNNELING LEAKAGE                                | 12   |

| 2.4 ELECTROSTATIC DISCHARGE RELIABILITY IN DECAP DESIGN   | 15   |

| 2.5 STANDARD-CELL DECAP LAYOUT AND PLACEMENT              | 17   |

| CHAPTER 3 EXISTING DECOUPLING CAPACITOR DESIGN APPROACHES | 22   |

| 3.1 Introduction                                          | 22   |

| 3.2 Cross-Coupled Decap                                   | 22   |

| 3.3 GATED DECAP                                           | 25   |

| 3.4 THICK OXIDE DECAP                                     | 28   |

| 3.5 High-k Gate Dielectric                                | 30   |

| 3.6 METAL-INSULATOR-METAL CAPACITOR                       | 32   |

| 3.7 SUMMARY                                               | 33   |

| CHAPTER 4 PASSIVE DECOUPLING CAPACITOR DESIGNS            | 34   |

| 4.1 Introduction                                    | 34 |

|-----------------------------------------------------|----|

| 4.2 RC MODELING OF BASIC CROSS-COUPLED DECAP DESIGN | 34 |

| 4.3 Transient Response Simulation                   | 36 |

| 4.4 ESD PERFORMANCE SIMULATION                      | 42 |

| 4.5 GATE LEAKAGE SIMULATION                         | 44 |

| 4.6 MODIFIED CROSS-COUPLED DECAP DESIGNS            | 45 |

| CHAPTER 5 ACTIVE DECOUPLING CAPACITOR DESIGNS       | 51 |

| 5.1 Introduction                                    | 51 |

| 5.2 SWITCHED DECOUPLING CAPACITOR                   | 52 |

| 5.3 Sun's Voltage Regulator                         | 55 |

| 5.4 FUJITSU'S ACTIVE POWER STABILIZER               | 59 |

| 5.5 LOW-POWER VOLTAGE REGULATOR                     | 63 |

| 5.6 SIMULATION SETUP AND RESULTS                    | 67 |

| CHAPTER 6 CONCLUSIONS AND FUTURE WORK               | 74 |

| 6.1 SUMMARY                                         | 74 |

| 6.2 CONTRIBUTIONS IN THIS THESIS                    | 76 |

| 6.3 FUTURE WORK                                     | 76 |

| DEFEDENCES                                          | 70 |

# LIST OF TABLES

| Table 4.1: Comparison on ESD performance, transient response and gate leakage | . 47 |

|-------------------------------------------------------------------------------|------|

| TABLE 5.1: NODE BIASING AND SWING FOR SUN VOLTAGE REGULATOR [41]              | . 56 |

| TABLE 5.2: NODE BIASING AND SWING FOR FUJITSU ACTIVE POWER STABILIZER [42]    | . 61 |

| TABLE 5.3: NODE BIASING AND SWING FOR LOW-POWER VOLTAGE REGULATOR.            | . 64 |

# LIST OF FIGURES

| FIGURE 1.1: TWO COMPONENTS OF POWER SUPPLY NOISE [3].                           | 2  |

|---------------------------------------------------------------------------------|----|

| FIGURE 1.2: USE OF DECOUPLING CAPACITOR TO REDUCE POWER GRID NOISE [3].         | 4  |

| FIGURE 1.3: DECOUPLING CAPACITOR IMPLEMENTED USING AN NMOS DEVICE.              | 5  |

| FIGURE 2.1: DECAP MODELING AS A SERIES RC CIRCUIT                               | 11 |

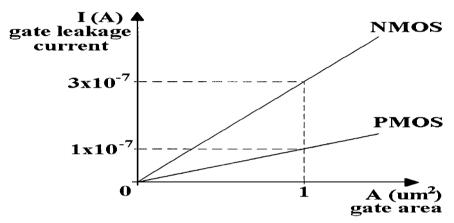

| Figure 2.2: Gate leakage current versus gate area.                              | 13 |

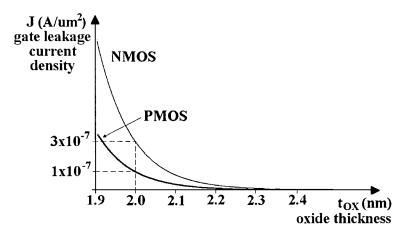

| FIGURE 2.3: GATE LEAKAGE CURRENT DENSITY VERSUS OXIDE THICKNESS.                | 14 |

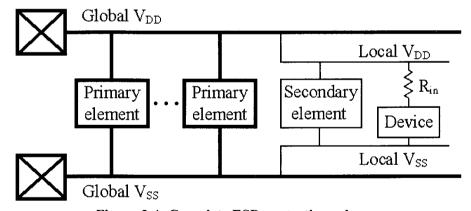

| FIGURE 2.4: COMPLETE ESD PROTECTION SCHEME.                                     | 16 |

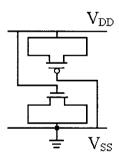

| FIGURE 2.5: STANDARD CELL N+P DECAP CONFIGURATION.                              | 17 |

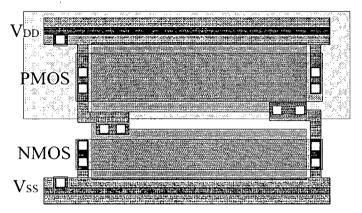

| FIGURE 2.6: SAMPLE LAYOUT OF STANDARD-CELL N+P DECAP WITH NO FINGERS.           | 18 |

| FIGURE 2.7: SAMPLE LAYOUT OF STANDARD-CELL N+P DECAP WITH TWO FINGERS           | 18 |

| FIGURE 3.1: CROSS-COUPLED DECAP SCHEMATIC [11]                                  | 23 |

| Figure 3.2: Intuitive understanding of input resistance in cross-coupled design | 24 |

| FIGURE 3.3: BASIC GATED DECAP SCHEMATIC [12] AND GATE LEAKAGE FLOW.             | 25 |

| FIGURE 3.4: SAMPLE CLOCK FOR THE CTRL SIGNAL IN GATED DECAP.                    | 27 |

| FIGURE 3.5: INSERTION OF SMALL INVERTER IN GATED DECAP [12].                    | 27 |

| FIGURE 3.6: STACK OF THIN-OXIDE DECAPS VERSUS THICK-OXIDE DECAP.                | 29 |

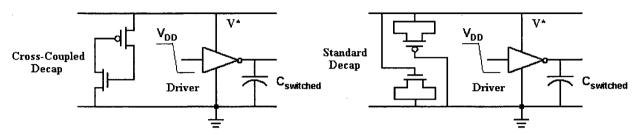

| FIGURE 4.1: CROSS-COUPLED DECAP SCHEMATIC [11] AND MODELING.                    | 35 |

| FIGURE 4.2: SCHEMATIC FOR THE FIRST TRANSIENT SETUP.                            | 37 |

| Figure 4.3: <i>RC</i> modeling of the first transient setup.                    | 37 |

| Figure 4.4: Simplification of $RC$ modeling of the first transient setup        | 38 |

| FIGURE 4.5: TRANSIENT RESPONSE FOR THE FIRST SETUP.                             | 40 |

| FIGURE 4.6: SCHEMATIC FOR THE SECOND TRANSIENT SETUP.                           | 41 |

| FIGURE 4.7: TRANSIENT RESPONSE FOR THE SECOND SETUP                          |

|------------------------------------------------------------------------------|

| FIGURE 4.8: SIMULATION SETUP FOR ESD ANALYSIS [10]                           |

| FIGURE 4.9: SAMPLE LAYOUT OF MOD1 (BASIC CIRCUIT WITHOUT FINGERING)          |

| FIGURE 4.10: SAMPLE LAYOUT OF MOD2 (REPLACE NMOS WITH PMOS)                  |

| FIGURE 4.11: SAMPLE LAYOUT OF MOD3 (REPLACE NMOS WITH PMOS, AND USE SMALLEST |

| NMOS)                                                                        |

| FIGURE 4.12: COMPLETE TRANSIENT RESPONSE FOR THE FIRST SETUP                 |

| FIGURE 4.13: COMPLETE TRANSIENT RESPONSE FOR THE SECOND SETUP                |

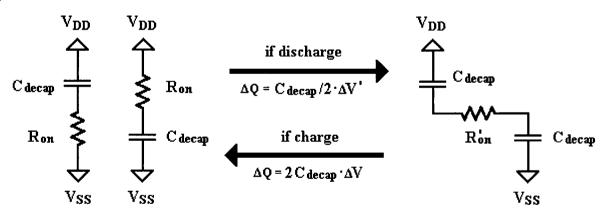

| FIGURE 5.1: PRINCIPLE OF SWITCHED DECOUPLING CAPACITOR [40]                  |

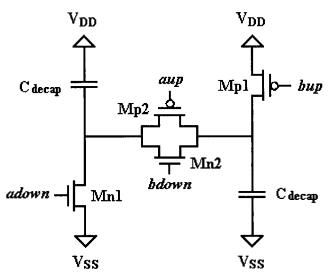

| FIGURE 5.2: MOS IMPLEMENTED SWITCHED DECOUPLING CAPACITOR [40]-[42]          |

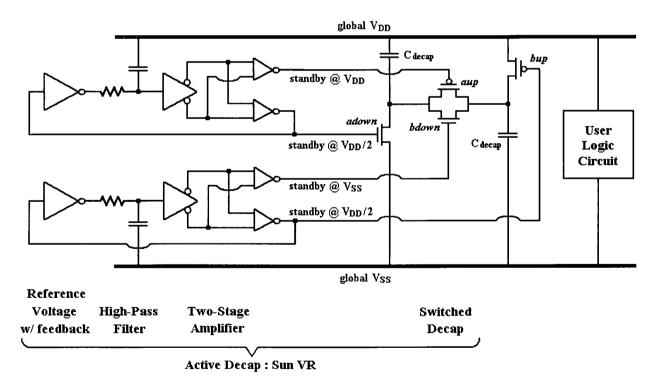

| FIGURE 5.3: BLOCK DIAGRAM OF SUN VOLTAGE REGULATOR [41]                      |

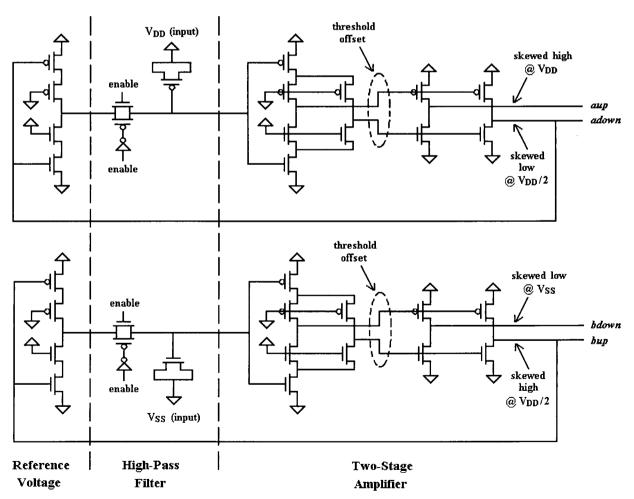

| FIGURE 5.4: CIRCUIT IMPLEMENTATION OF SUN VOLTAGE REGULATOR [40] [41]        |

| FIGURE 5.5: CIRCUIT IMPLEMENTATION OF FUJITSU ACTIVE POWER STABILIZER [42]   |

| FIGURE 5.6: CIRCUIT IMPLEMENTATION OF LOW-POWER VOLTAGE REGULATOR            |

| FIGURE 5.7: SIMULATION SETUP FOR ACTIVE DECAP CIRCUITS                       |

| FIGURE 5.8: SIMULATION RESULTS FOR NO DECAP INSERTED                         |

| FIGURE 5.9: SIMULATION RESULTS FOR STANDARD DECAPS INSERTED                  |

| FIGURE 5.10: SIMULATION RESULTS FOR SUN VR INSERTED                          |

| FIGURE 5.11: SIMULATION RESULTS FOR FUJITSU APS INSERTED                     |

| FIGURE 5.12: SIMULATION RESULTS FOR LOW-POWER VR INSERTED                    |

#### **ACKNOWLEDGMENTS**

I would like to express my gratitude to my academic supervisor, Dr. Resve Saleh, whose expertise, understanding, patience, and support, added significantly to my graduate experience. I appreciate his profound and vast knowledge in many areas, both within and outside of the scope of my research. I would like to thank my industrial supervisor, Dr. Karim Arabi, for his technical advice, encouragement, and kindness.

A very special thanks to my colleagues and friends in the SoC group, without whose assistance, I would not have accomplished this research. More specifically, I would like to thank Amit Kedia, Dipanjan Sengupta, Karim Allidina, Reza Molavi, Scott Chin, Roberto Rosales, Roozbeh Mehribadi, and Dr. Steve Wilton. I also thank Dr. Shahriar Mirabbasi who provided me with technical and personal support whenever I asked and became more of a mentor and friend, than a professor. I also acknowledge Asad Shayan and Mamta Bansal of PMC-Sierra Inc. for their suggestions and help in this study.

I recognize that this research would not have been possible without the financial support from NSERC and PMC-Sierra Inc., and express my gratitude to them. I also thank CMC Microsystems for providing the CAD tools.

Last, but not least, I would especially like to thank my family for both giving and encouraging me to seek for myself a demanding and meaningful education. In particular, I must acknowledge my fiancée, Liming, for her love, caring and patience through many years of my life. The appreciation extends beyond any words at my command.

### Chapter 1

### Introduction

#### 1.1 Motivation

As integrated circuit (IC) technology scales, more and more transistors are being placed within a single chip, while the clock frequency continues to increase into the gigahertz range. The result is that large transient currents are drawn from the power supply rails in just a few hundred picoseconds [1] in modern custom and application-specific integrated circuit (ASIC) chips. Meanwhile, the supply voltage is scaled with technology to reduce overall power consumption, and as a consequence, the circuitry becomes more prone to power-supply noise. The management and regulation of the quality of the on-chip power supply is a major challenge [1].

The power grid, which provides  $V_{DD}$  and  $V_{SS}$  (or ground) signals throughout the chip, experiences fluctuations in value due to a variety of noise sources. If the supply voltage noise or variation is excessively large, it may lead to problems such as delay variation, timing unpredictability, or even improper functionality [2]. A commonly used metric, *noise budget*, is defined as the maximum allowable noise amplitude [3]. Typically, it is required to keep the power supply noise within a certain percentage (e.g., 10%) of the nominal supply voltage  $V_{DD}$ .

Namely, 10% of  $V_{DD} - V_{SS}$  is typically the noise budget, a *rule-of-thumb* used in the industry [4]. Circuit designers must ensure that the chip operates correctly if the maximum voltage difference between  $V_{DD}$  and  $V_{SS}$  is 10% or smaller than the nominal value.

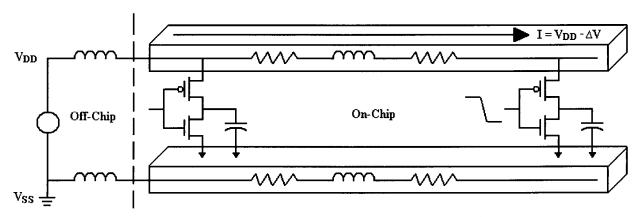

In today's advanced deep-submicron (DSM) technology, the power grid noise is due to two main issues: (1) As the power lines made of metal wires become thinner, the wire resistance R increases. When logic gates switch and a current I flow through the power lines to deliver charge to the gates, the voltage drop  $\Delta V$  at the gates is  $\Delta V_1 = I \cdot R$ . This type of power-supply noise is known as IR drop. (2) Due to package pin inductance and thin-interconnect inductance, the power lines experience inductance effect when the current flow changes with respect to time. This second source of voltage drop is given by  $\Delta V_2 = L \frac{dI}{dt}$ . The two power supply noise components are illustrated in Figure 1.1, which depicts two inverters connected to an off-chip voltage supply through the on-chip power grid.

Figure 1.1: Two components of power supply noise [3].

Considering the two components together, the overall voltage drop  $\Delta V$  at any point in the power grid is:

$$\Delta V = IR + L \frac{dI}{dt} \tag{1.1}$$

To illustrate the IR drop, all the nodes in the power grid are initially charged to  $V_{DD}$  with no activity in the circuit. As the second inverter starts to switch, the wire resistance along the  $V_{DD}$  line creates voltage drops as current flows from the external voltage source towards the second inverter [3]. Similarly, the ground grid is subject to the same type of problem when the outputs of the buffers switch low, except that the voltage level of the ground line will increase. This is sometimes referred to as *ground bounce*. In practice, IR drop can be caused by simultaneous switching of clock buffers, bus drivers, memory decoder drivers, and so on, when there is high activity in the circuit. These simultaneous switching activities can happen anywhere on the chip. Thus, all regions in the chip are susceptible to IR drop. In a wire-bond (e.g., dual-inline) package, the supply voltage level remains relatively high at the periphery of chip where the voltage supply I/O pads are located, and drops noticeably at the centre of the chip. In contrast, in a flip-chip (or ball-grid array) package, the centre of the die has rather high voltage level, whereas the periphery of the die experiences larger IR drops.

Considering the *Ldi/dt* term in Equation (1.1), the inductance *L* is another source of voltage drop in the power supply and is typically at 1 to 2 nH in a dual-inline package (DIP) or at roughly 0.1-0.2nH in a ball-grid array (BGA) package [3]. In a traditional DIP package, this inductance arises from the bonding wire used to connect the chip I/O pads to the lead pins. On the other hand, in a modern ceramic BGA package, the inductance comes from the solder bumps that can be placed anywhere in the chip area [5]. Although BGA is a more expensive solution, it provides more I/O connection capability and less inductance value [3].

In the past, compared to IR drop, the Ldi/dt term was not considered as a significant source of power supply noise, mainly because the chip clocks were not running at the gigahertz range. However, in today's chips, this inductance effect is a much more significant [6]. The value of L has not changed considerably over the years, while the value of di/dt has continued to increase due to faster and faster clock frequencies.

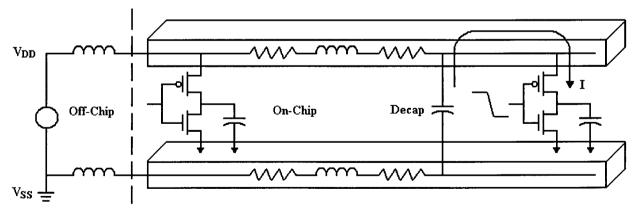

A common technique for reducing power supply noise and keeping the noise within the noise budget is through the use of on-chip decoupling capacitors (decaps). Decaps are essentially capacitors that hold a reservoir of charge and are placed close to the power pads and near any large drivers. When large drivers switch, the decaps provide instantaneous current to the drivers to reduce IR drop and Ldi/dt effects, and hence keep the supply voltage relatively constant. As shown in Figure 1.2, the on-chip decap delivers current to charge up the load capacitance of the second inverter when it switches. The supply voltage level is relatively constant at the inverter tap point since the decap is nearby, so  $\Delta V$  is minimal.

Figure 1.2: Use of decoupling capacitor to reduce power grid noise [3].

This thesis focuses on the issues of power supply noise reduction through the use of decoupling capacitors. In a typical ASIC design, decaps can be placed in the open areas of the chip between

intellectual property (IP) blocks (called white-space decaps, or global decaps) and within the IP blocks composed of standard cells [7]. The thesis discusses both types of on-chip decaps, although off-chip decaps are commonly used as well [8].

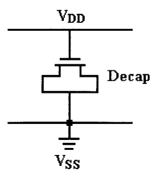

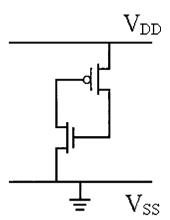

### 1.2 Decoupling Capacitors Issues at 90nm

A standard decap is usually made from NMOS transistors in a CMOS process [3]. As shown in Figure 1.3, the gate of the NMOS transistor is connected to  $V_{DD}$ , whereas source, drain and substrate of the transistor are tied to  $V_{SS}$ . This approach is considered effective because the thin-oxide capacitance of the transistor gate provides a higher capacitance than any other oxide capacitance available in a standard CMOS fabrication process [4]. For this MOS decap, the first-order calculation of the capacitance is  $WLC_{OX}$ , where W is the transistor width, L is the transistor length, and  $C_{OX}$  is the oxide capacitance per unit area. Accurate capacitance model needs to include the parasitic fringing and overlap capacitance of the transistor, and will be discussed in greater detail in Chapter 2.

Figure 1.3: Decoupling capacitor implemented using an NMOS device.

At the 90nm technology node, the oxide thickness of a transistor is reduced to roughly 2.0nm or less. The thin oxide causes two new problems: possible electrostatic discharge (ESD) induced oxide breakdown and gate tunneling leakage [9], [10]. Potential ESD oxide breakdown increases

the likelihood that an IC will be permanently damaged during an ESD event, and hence raises a reliability concern. Higher gate tunneling leakage increases the total static power consumption of the chip. As technology scales further down, with a thinner oxide, the result is an even higher ESD risk and more gate leakage. The standard decap design using NMOS transistors experiences these two problems and therefore becomes rather inappropriate for 90nm and below.

While satisfying ESD reliability and gate leakage limitations, decap designs must also meet the transient performance requirements. Since a 90nm process (or below) usually provides the capability of running at gigahertz frequencies, the decap must respond in the order of a hundred picoseconds.

A new cross-coupled standard-cell design approach [11] addresses the issue of ESD performance. The design provides a certain amount of ESD input protection to the decap, but does not offer any savings in gate leakage. Even worse, the new design experiences a much degraded transient response, making it somewhat unsuitable for high-speed chips. Modifications to the cross-coupled decap design that properly trades off ESD, transient response and gate leakage are needed.

Another new global decap design approach, called *gated decap*, has been reported [12] to control gate leakage. Based on the approach of multi-threshold CMOS circuit, the gated decap is capable of saving a significant amount of leakage current while in power-saving mode. However, the design suffers from an oscillation problem. The lack of robustness of the design makes it somewhat less attractive for industrial use.

Most fabrication processes provide high-voltage thick-oxide I/O transistors. Those transistors have properties of excellent ESD reliability and almost-zero gate leakage. These desired properties make them good candidates for global decap implementation in 90nm or below. However, the effective capacitance for such thick-oxide decaps is much less than thin-oxide ones. Certain fabrication limitations also apply for thick-oxide devices.

From a process perspective, the use of high-k gate dielectrics is an active field. Progress has been made to provide savings in gate leakage. Nevertheless, many process issues still exist and the high-k technology is far from mature enough for mass production. Metal-insulator-metal capacitors are available in many fabrication processes. It is useful to examine if those capacitors are suitable for making global decaps since it is known that the leakage current for such a capacitor is low.

For global decaps, to improve the area efficiency, the use of switched decoupling capacitors is an interesting alternative. Compared to the passive designs, the intent of the switched decaps is to boost the supply voltage to provide better power-grid noise reduction capability. Two existing designs from Sun and Fujitsu are worth investigating, and improving for low-power operation. Such a low-power voltage regulator would be suitable for general low-power applications in both ASIC and custom designs.

### 1.3 Research Objectives

The research objectives of this work are as follows:

- Understand relationship between critical decap design issues, such as electrostatic discharge reliability, gate leakage and transient response.

- Develop passive solutions to decap designs that properly trade off gate leakage, ESD and transient response, and provide designers with design flexibility for sub-90nm technologies for standard-cell decaps.

- Explore active solutions to decap designs that provide better power-grid noise reduction capability than the passive approaches. Design a novel switched-decap voltage regulator that properly balances power dissipation and decap performance in white-space decaps.

### 1.4 Organization of the Thesis

The remainder of this thesis is organized as follows. Chapter 2 provides the necessary background for decap modeling, gate tunneling leakage phenomenon, ESD reliability, and standard-cell placement of decoupling capacitors.

Chapter 3 explores various decap design approaches that may be suitable for upcoming technologies. The circuit-level designs are discussed first, followed by the process-level efforts. The pros and cons of each approach are provided.

Chapter 4 develops a set of new designs based on the cross-coupled decap. The modeling of the new designs is described to allow hand calculations and analyses to be carried out. The new designs are validated using a full set of simulations in transient, ESD and gate leakage measurements. Based on the simulation results, the proper layout of these designs is described.

Chapter 5 analyzes the advantages and disadvantages of Sun's voltage regulator and Fujitsu's active power stabilizer to improve decap area efficiency. A novel low-power switched-decap

voltage regulator is designed to achieve good power-grid noise reduction performance while maintaining a low level of dc power consumption.

Chapter 6 summarizes the results of the thesis and provides conclusions. Future research directions are provided.

# Chapter 2

# **Background**

### 2.1 Introduction

The topics in this chapter provide the necessary background for the rest of the thesis. Moreover, some fundamental and practical decap design issues are highlighted in this chapter to motivate the topics in the remainder of the thesis. This chapter begins with modeling of standard NMOS decaps. An overview of design challenges and problems associated with decoupling capacitors in 90nm and below is provided. The overview includes gate tunneling leakage, electrostatic discharge phenomenon and protection, and standard-cell decap placement. The gate leakage is introduced from a physical point of view, and useful information from recent technologies is given. ESD reliability is presented and typical phenomena during an ESD event are discussed. Primary and local ESD protection schemes are briefly illustrated. Since ASIC designs typically utilize standard cells, the decap insertion and placement procedure within standard-cell blocks is briefly introduced.

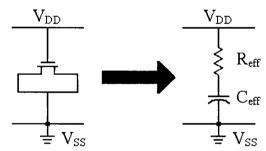

### 2.2 Decoupling Capacitor Modeling

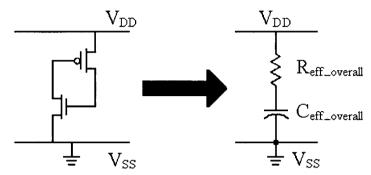

A standard decap is usually implemented using an NMOS transistor with the gate connected to  $V_{DD}$  and both source and drain connected to  $V_{SS}$ , or a PMOS device with opposite connections. When implemented using MOS transistors, decaps experience parasitic channel resistance that imposes certain delay on the transient response of the decap [4] [13]. Therefore, a decap should be modeled as a series connection of effective resistance and effective capacitance [4], as shown in Figure 2.1.

Figure 2.1: Decap modeling as a series RC circuit.

For precise calculation, the effective capacitance at low frequencies can be written as:

$$C_{eff} = C_{OX}WL + 2C_{OL}W \tag{2.1}$$

where  $C_{OX}$  is the oxide capacitance per unit area,  $C_{OL}$  is the overlap and fringing capacitance per unit width, and W and L are the width and length of the transistor, respectively.

The decap's effective resistance at low frequencies is given by [4]:

$$R_{eff} = \frac{L}{6\mu C_{OX}W(V_{GS} - V_T)}$$

(2.2)

where  $\mu$  is the channel mobility,  $V_{GS}$  (or  $V_{GD}$  since source and drain are tied) is the voltage across the oxide, and  $V_{T}$  is the threshold voltage. From Equation (2.2),  $R_{eff}$  is proportional to the

channel length L. That is, for faster transient response, a decap design should use a small L to keep  $R_{eff}$  small. Both  $R_{eff}$  and  $C_{eff}$  can be considered constant at low or moderate operating frequencies, but they are degraded a high frequencies [4] [14].

Since decaps are usually built using MOS transistors, the high-frequency behavior of MOS transistors needs to be investigated. Previous work in [4] has shown that both  $R_{eff}$  and  $C_{eff}$  will decay as operating frequency increases. That is, both  $R_{eff}$  and  $C_{eff}$  are functions of frequency, f. Although it is desired to have a small  $R_{eff}$ , the decreased  $C_{eff}$  results in reduced capability of the decap at high frequencies.

The channel length L of the decap controls its frequency response. If L is small enough, the effective capacitance remains relatively constant at high frequencies. As a consequence, a fingering technique in decap layout is commonly used to maintain its frequency response [4]. Moreover, NMOS has better frequency response than PMOS [4]. Thus, the use of PMOS decaps should be limited, from the frequency response perspective.

### 2.3 Gate Tunneling Leakage

A new design issue for decaps due to oxide thickness reduction is the gate tunneling current. The current is in the form of tunneling electrons or holes from substrate to gate or from gate to substrate through the gate oxide, depending on the voltage biasing conditions [15]. Two forms of gate tunneling exist: Fowler–Nordheim (FN) tunneling and direct tunneling. For normal operations on short-channel devices, FN tunneling is negligible, and direct tunneling is dominant [15]. In the case of direct tunneling, the gate leakage current in PMOS is much less than in

NMOS, and it has been shown experimentally that PMOS gate leakage is roughly 3 times smaller than NMOS gate leakage for same size transistors [16] [17]. The gate leakage simulations can be carried out by using BSIM4 SPICE models [18] [19]. Assuming a 90nm technology with 2.0nm oxide thickness and 1.0V power supply, the gate leakage current is shown in Figure 2.2.

Figure 2.2: Gate leakage current versus gate area.

The gate leakage current density J and the oxide thickness  $t_{OX}$  have an empirical relationship as follows, assuming the voltage across the oxide  $V_{OX}$  is fixed [16]:

$$J = 10^{(A-B \cdot t_{OX})} \tag{2.3}$$

where A and B are experimental constants and are process dependent. Equation (2.3) implies that the gate leakage current is exponentially related to the oxide thickness. A typical J and  $t_{OX}$  relationship for a fixed  $V_{OX}$  is illustrated in Figure 2.3.

Figure 2.3: Gate leakage current density versus oxide thickness.

It is evident that from 90nm technology onward, the gate leakage from decaps will be significant [17]. The gate leakage contributes to the total static power consumption, and decaps usually occupy a large on-chip area. The use of PMOS devices exclusively is not a viable solution for high-frequency circuits since they have a poor frequency response relative to the NMOS devices [4].

In addition, the amount of gate leakage is also a strong function of the applied bias [20]. If the transistor has a  $V_{OX}$  that is roughly equal to  $V_{DD}$ , the leakage current density is largest. If the transistor has a  $V_{OX}$  set to close or below  $V_T$ , it leaks significantly less. Indeed, under such a condition, the gate leakage current is typically 3-6 orders of magnitude less, depending on the values of  $V_{DD}$  and  $t_{OX}$  [20]. Thus, the gate leakage in the second condition can be roughly considered to be zero. In decaps, the gate is at  $V_{DD}$  and the source and drain of a transistor are tied together. Therefore, decaps would experience the highest levels of leakage.

### 2.4 Electrostatic Discharge Reliability in Decap Design

Another new consideration has arisen in the form of ESD protection due to the thin oxide in 90nm technology. ESD is the process of static discharge that can typically arise from human contact with any IC pin. Approximately 0.6uC of charge is carried on a body capacitance of 100pF, generating a potential of 2kV or higher to discharge from the contacted IC pin to ground for a duration of more than 100ns [10]. Under such an event, the peak discharge current is in the ampere range, leading to permanent damage on certain transistors in the chip if not properly protected. The damage can be in one of two forms, or a combination of the two: one is thermal burnout in devices or interconnects, while the other is oxide breakdown of devices due to the high voltage across the oxide [10]. When running simulations for an ESD event, the maximum current density  $J_{max}$  of devices and interconnects is measured to check for potential thermal damage. The oxide voltage also needs to be measured to compare with the oxide breakdown voltage of a device for a given fabrication process. The oxide breakdown voltage is almost linearly proportional to the oxide thickness [10]. For instance, assuming a 90nm process uses 2.0nm of oxide thickness, the corresponding oxide breakdown voltage is just below 5V. If the thickness is doubled, the oxide breakdown voltage is also doubled to around 10V [10].

An ESD event can be delivered between any two pins of an IC. To properly protect an IC from ESD damage, an ESD circuit must shunt ESD current between these two pins [10]. In the case of decaps within standard cells, the only two pins that the decaps have access to are the two local power rails, namely  $V_{DD}$  and  $V_{SS}$ . Primary and local (sometimes called *secondary*) protection elements are needed to protect the two rails by limiting the voltage difference between the two rails to a value below the oxide breakdown voltage. The primary element will shunt most of the

ESD current, whereas the local element serves to limit the voltage or current at the local circuit until the primary element is fully operational [10]. A primary element can be a thick oxide transistor, a silicon-controlled rectifier, an open-gate, grounded-gate or coupled-gate NMOS transistor, or a large diode [10]. A local protection element can be simply a diode formed by a grounded-gate NMOS transistor [10].

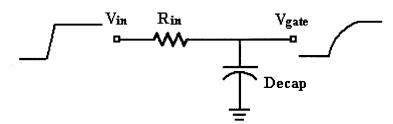

A typical ESD protection scheme is illustrated in Figure 2.4. In addition to the primary and local elements, a resistor  $R_{in}$  is required to limit the maximum current flow to the decap and to limit the voltage seen from the gate of the decap. For better ESD protection, this resistance is normally large and can be in the forms of polysilicon, diffusion, n-well, or even channel resistance [10]. The resistance is generally not implemented together with primary and local protection devices. Rather, it is usually inserted within standard cells where ESD damage is a concern.

Figure 2.4: Complete ESD protection scheme.

Previous decap designs (before 90nm technology) did not consider ESD performance mainly because: 1. The transistor's oxide thickness was large and the oxide breakdown voltage was high enough so that the transistor was likely to survive during an ESD event with adequate protection circuits. 2. Insertion of the large resistance  $R_{in}$  dramatically reduces the transient response of the

decap. However, starting from 90nm, the gate oxide is so thin that the designer cannot ignore the increased ESD risk. A large resistance is therefore recommended to be placed inside the decap cells to protect from potential ESD damage. As a consequence, this tradeoff between ESD performance and transient response becomes the main decap design challenge in 90nm.

### 2.5 Standard-Cell Decap Layout and Placement

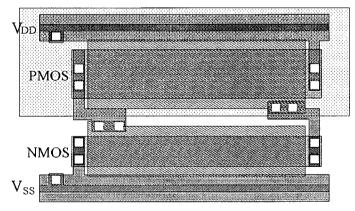

In white spaces, decaps are usually made of NMOS devices, as described in the early sections. However, within standard cells, it is more convenient to make decaps using both types of NMOS and PMOS to form a decap filler cell, as shown in Figure 2.5. This is because the n-well is already implemented and usually reserved for PMOS devices. Only the lower half-cell area is for NMOS devices [4].

Figure 2.5: Standard cell N+P decap configuration.

One sample standard-cell decap layout is illustrated in Figure 2.6. In the figure, the NMOS decap occupies roughly the bottom half of the cell area, whereas the PMOS decap is located in the n-well. The capacitor areas are the polysilicon gates placed on top of the channel regions of the MOS transistors. For standard cells, the height of the cell is always fixed, and the designers can only adjust the cell width. Once the cell width is determined, the size of the decap and the

capacitance of the decap are established. Figure 2.6 implies a large decap cell (measured in cell width) with long channel transistors.

Figure 2.6: Sample layout of standard-cell N+P decap with no fingers.

The decaps laid out in this long-channel fashion have poor performance at high frequencies, as discussed in Section 2.3. Therefore, a fingering technique is commonly used to improve the frequency response. Figure 2.7 depicts the same decap cell but with two fingers.

Figure 2.7: Sample layout of standard-cell N+P decap with two fingers.

To model this N+P decap configuration, the overall impedance of two parallel RC circuits is

determined as

$$(R_{eff_{-}n} + \frac{1}{sC_{eff_{-}p}})//(R_{eff_{-}p} + \frac{1}{sC_{eff_{-}p}})$$

, and simplified as

$$\frac{R_{eff\_n}R_{eff\_p}}{R_{eff\_n}+R_{eff\_p}} + \frac{1}{s(C_{eff\_n}+C_{eff\_p})} + higher\_order\_terms.$$

For first-order hand calculations, the higher-order terms are negligible. Thus, the overall effective capacitance is the sum of the two individual decoupling capacitances, and the overall effective resistance is the parallel combination of the two individual effective resistances. That is:

$$C_{eff \ overall} \approx C_{eff \ n} // C_{eff \ p} = C_{eff \ n} + C_{eff \ p}$$

(2.4)

$$R_{eff\_overall} \approx R_{eff\_n} // R_{eff\_p} = \frac{R_{eff\_n} R_{eff\_p}}{R_{eff\_n} + R_{eff\_p}}$$

(2.5)

During the placement procedure, computer-aided design (CAD) tools place standard cells into rows. Because the height of each cell is always the same, when cells are placed adjacent to each other, the n-well region and the  $V_{DD}$  and  $V_{SS}$  lines are automatically aligned. The cells for placement are obtained from the standard-cell library, where all the cells are predefined in width and driving strength. Since the total width of the row is fixed and the individual cell widths are fixed, some empty spaces (typically small) between the cells are left after placing cells. Those empty spaces are good candidates for the placement of decap cells due to its convenience [4]. In fact, a set of decap cells with different cell widths is also implemented in the standard-cell library. All the cells in the library must be designed for a specific process and meet all the design rules. Routing is typically carried out right after placement.

Decap insertion is considered as a part of the complete design flow. In a typical ASIC design flow, once the standard-cell blocks are synthesized, placed and routed by CAD tools, the decap cells are naturally placed into the empty spaces. Generally, since the spaces are filled using a library of decap cells with various sizes, the decap placement is done without affecting the placement of other logic cells. After placement and routing, chip-level timing is analyzed and timing violations will be fixed by replacement and/or rerouting. Then, chip-level voltage-drop analysis is carried out by some CAD tools (e.g., Apache<sup>TM</sup> Redhawk<sup>TM</sup>) such that the *hot spots* of severe voltage-drop areas are identified. If the voltage drop at the hot spots exceeds the noise budget, more decaps will be inserted into the violation regions and a modification of the placement of other logic cells may have to be done. The logic cell movement requires additional timing and routability analysis before moving on to next step. Then, the chip voltage drop is analyzed again for the remaining hot spots. These steps in the design flow are iterated until all the hot spots are eliminated and all the logic circuits pass timing analysis. Typically, it may take 1 or 2 (occasionally even more) iterations to eliminate all the hot spots [3]. In addition, the potential problem of electromigration is also checked alongside the IR drop analysis [3].

This generally used decap placement approach is not optimal simply because the empty cells may not be located near the high voltage-drop regions. After the hot spots are first identified, the remaining empty spaces near the hot spots may not be largely enough. Hence, the logic cells may have to be shifted, resulting in additional timing analysis. In order to improve the placement efficiency, researchers suggest a few approaches including: global decap placement between standard-cell blocks [21], decap placement using activity [7], standard-cell decap placement not

affecting relative placement of logic cells [2], and earlier-stage decap placement decision [4]. Since decaps are experiencing excessive gate leakage, decap placement methods considering leakage current are proposed in [9] and [22].

### Chapter 3

# **Existing Decoupling Capacitor Design Approaches**

#### 3.1 Introduction

Before 90nm technology, the use of MOS transistors as decoupling capacitors appeared to be a straightforward solution to the decap design problem. However, many factors such as excessive gate leakage, increased ESD risk, and consideration for high-performance transient response come to play important roles from 90nm technology. The consequence is that the standard MOS decap design may no longer be appropriate for the use in 90nm or below. Researchers have provided some new design approaches to address the design issues for decaps. This chapter provides an overview that sequences through all the major existing methodologies and identifies their advantages and disadvantages.

### 3.2 Cross-Coupled Decap

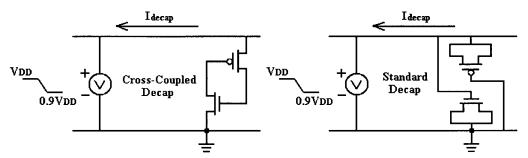

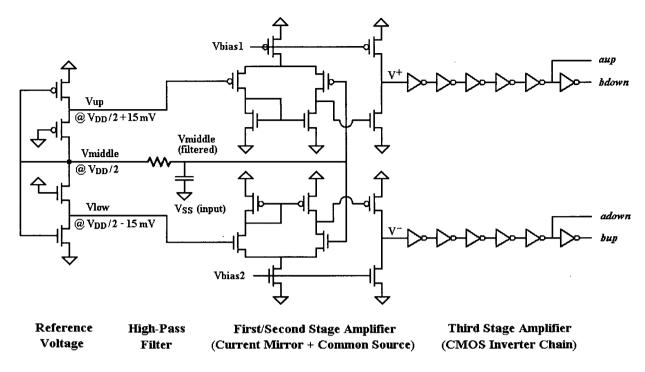

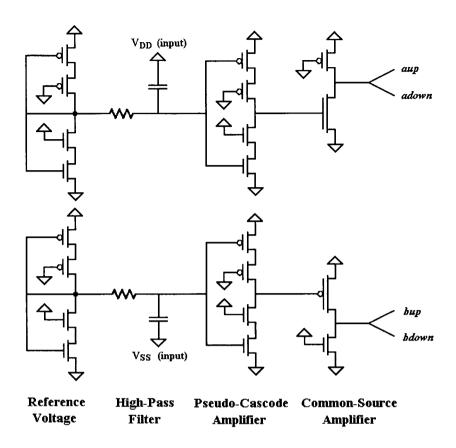

Knowing that the standard N+P decap design for standard cells may no longer be suitable for 90nm technology due to increased ESD risk, a new cross-coupled decap design has been proposed [11] to address this issue. In the new cross coupled design (Figure 3.1), the drain of the PMOS connects to the gate of the NMOS, whereas the drain of the NMOS is tied to the gate of the PMOS [11].

Figure 3.1: Cross-coupled decap schematic [11].

From the layout perspective, this cross-coupled circuit can be seen simply as a terminal-swapped version of the standard decap. In other words, the decap transistor areas need not to be modified, while only the metal wire connections are modified. Thus, this new design does not require additional area in layout, compared to the standard design.

Both transistors in this design are still in the linear region. In the standard decap design, the gates of the transistors are directly connected to either  $V_{DD}$  or  $V_{SS}$ , depending on the transistor type. In this case, the gate of the NMOS device is connected to  $V_{DD}$  through the channel resistance of the PMOS device. Similarly, the gate of the PMOS device is tied the channel resistance of the NMOS device and then connected to  $V_{SS}$ . The added channel resistance to the gate provides the input resistance  $R_{in}$  for ESD protection, as previously mentioned in Section 2.4. The input resistance can help to limit the maximum current flow to the decap so that the voltage seen from the gate of the decap is also limited.

Intuitively, the input resistance along with the decap can be thought as a low pass filter, as illustrated in Figure 3.2. When there is a sudden voltage jump at the power line  $(V_{in})$  during an

ESD event, the voltage at the gate of the decap ( $V_{gate}$ ) does not increase instantaneously with the increase of  $V_{in}$ . Instead, the increase of  $V_{gate}$  is delayed due to the low-pass RC effect. This time delay in the voltage change at the transistor gate helps to protect the gate until the primary and secondary ESD devices are fully operational and shunt the ESD current away. Hence, it is desirable to have  $R_{in}$  as large as possible from the standpoint of ESD protection.

Figure 3.2: Intuitive understanding of input resistance in cross-coupled design.

By simply swapping the terminal connections, the cross-coupled design adds a considerably large  $R_{in}$  to the gate of the decaps, without increasing the layout area. The tradeoff of this design is the reduced transient performance as a decap.

Since both transistors are in the linear region, the two transistors are on and do not limit the gate leakage current flow compared to the standard design. Hence, no savings in gate leakage are achieved in this cross-coupled approach. This design nicely illustrates the concept of tradeoffs between transient response and ESD reliability when designing a decap. This cross-coupled circuit is also considered to be fairly passive and robust. In the next chapter, this circuit will be discussed in greater detail, and modifications will be provided to address different design tradeoffs including gate leakage. Two of the modification circuits can achieve higher gate leakage savings and provide comparable or better transient response, while another is better in terms of ESD reliability.

### 3.3 Gated Decap

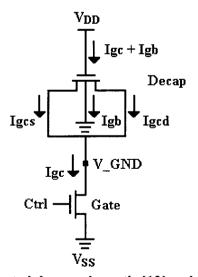

Chen et al. [12] has recently implemented a new decap structure that saves gate leakage. The structure is called *gated decap*, as shown in Figure 3.3. A control transistor is inserted between the standard NMOS-only decap and the  $V_{SS}$  line. The source and drain of the decap are connected to the source of the control transistor, making the node a virtual ground ( $V_{SN}$ ). The drain of the control transistor is tied to the real  $V_{SS}$ . As shown in Figure 3.3, the substrate of the decap is still attached to  $V_{SS}$ . There are two major components in gate leakage: leakage current from gate to channel (Igc), and from gate to substrate (Igb). The current Igc can be partitioned into two: leakage current from gate to source (Igcs) and from gate to drain (Igcd) [19]. The amount of gate leakage from gate to substrate Igb is roughly 10x smaller than the leakage from gate to channel Igc [15] [16]. Thus, the substrate of the decap does not need to be tied through the control transistor, and the leakage current Igb is neglected.

Figure 3.3: Basic gated decap schematic [12] and gate leakage flow.

There are two modes of operation of the circuit: active mode and power saving mode [12]. When in the active mode, the Ctrl signal of the control transistor is turned high. The gated decap

operates almost like the standard decap, except that there is a small channel resistance of the control transistor. The size of the control transistor needs to be large to have the channel resistance small since a large resistance will reduce the transient response of the decap. When in power saving mode, the Ctrl signal is turned low so that the control transistor operates in the subthreshold regime. The node  $V_GND$  can be considered a virtual ground (floating), where the voltage at  $V_GND$  can be determined by the series resistance of  $R_{eff}$  of the decap and the channel resistance of the control transistor. In this configuration, the gate leakage saving is projected to be 99% in a 70nm process [12].

The basic idea of the gated decap is from multi-threshold CMOS (MTCMOS). The control transistor comes from the concept of the sleep transistor in MTCMOS. As expected, the control transistor should have a high V<sub>T</sub> to keep the subthreshold leakage small. The largest challenge of this gated decap would be the proper selection of the Ctrl signal. At the top level, the Ctrl signal can be driven by the hardware/software interface. When there is no activity in the system, the operating system (software) will set up the signal to force the chip into power saving or standby mode. From the hardware architectural level, the Ctrl signal can be managed by some self-predictive architecture [12] [23]. At the circuit level, it is desired that the gated decap is self-maintained, and no external circuitry is required to control it on or off. In that case, it may need to have a special clock, as shown in Figure 3.4. Before the regular clock rises, the Ctrl signal can be set high to allow some setup time for the decap to fully setup. When the regular clock falls, the Ctrl signal can also fall simultaneously to save power. The time period when the Ctrl signal is low can be considered as the power saving period.

Figure 3.4: Sample clock for the Ctrl signal in gated decap.

Another substantial difficulty is oscillation. It was observed in [12] that the voltage levels at the local power lines oscillate when the gated decap is turned on or off. The reason is that sharp rises and falls in the Ctrl signal get passed through the decap and hence make the power lines noisy. The oscillation level is determined to be excessive: more than 10% of  $V_{DD}$  of the simulation process [12]. Such large oscillation is certainly non-acceptable and some form of modification has to be taken.

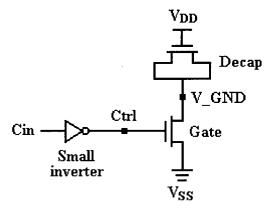

The solution of reducing excessive oscillation provided in [12] is to insert a small-size inverter, as shown in Figure 3.5. Sharp rising and falling edges in the Ctrl signal correspond to the concept of large *slew rate*. The insertion of the small inverter helps reduce the slew rate at Ctrl.

Figure 3.5: Insertion of small inverter in gated decap [12].

The gated decap is a good attempt in solving the problems of excessive gate leakage for decap designs. Nonetheless, the design style is not conservative enough so that it experiences many issues such as oscillation. In other words, the robustness of this gated decap may not be good enough to implement in industrial designs.

### 3.4 Thick Oxide Decap

Fabrication foundries usually provide high-voltage, thick-oxide MOS devices in a CMOS process. The thick-oxide devices are intended for the use in I/O interfaces and other places where a higher voltage supply is present. Typically, for a 90nm process, the nominal  $V_{DD}$  is scaled to 1.0V, while the thick devices can still hold for 3.3V voltage level [24]. Similarly, for a 130nm process, with a nominal power supply of 1.2V, the high voltage for the thick-oxide transistors is 3.3V [25].

For thick-oxide devices in a 90nm process [24], the oxide is roughly 3x thicker than the thin-oxide devices, resulting in 3x higher oxide breakdown voltage. Moreover, because of the exponential relationship between  $t_{ox}$  and  $J_{gate\_leak}$  given in Equation (2.3), the gate leakage of such thick-oxide devices in 90nm is almost zero, which is also consistent with SPICE simulations. Hence, the use of thick-oxide transistors can eliminate the concerns of ESD reliability and gate leakage completely.

The largest disadvantage of thick-oxide devices is that the effective capacitance  $C_{eff}$  is reduced by roughly 1/3. Moreover, it is difficult to place thick-oxide devices within a standard-cell block. The thick-oxide decaps must be properly placed around the periphery of the block. The use of

thick decaps is only suggested in the open areas between blocks when both ESD risk and gate leakage need to be minimized and while there is also a high demand on transient response performance. Under such scenarios, the 3x area penalty may have to be paid.

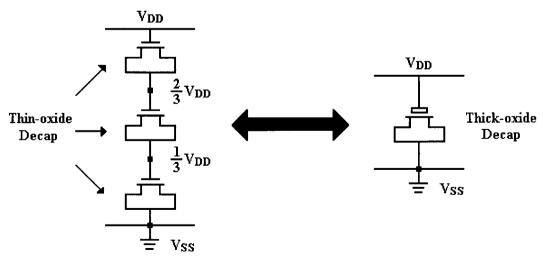

To complete the concept of thick-oxide decaps, there is a similar situation where a stack of thin-oxide decaps is used, as shown in Figure 3.6. Assuming a 90nm process has a 1.0V power supply and a threshold voltage  $V_T$  of 0.3V,  $V_T$  is roughly at  $V_{DD}/3$ . Stacking three thin-oxide decaps in series results in the gate voltage difference  $V_{OX}$  across each decap to be  $V_{DD}/3$ . As mentioned in Section 2.3, gate leakage is a function of biasing voltage. If  $V_{OX}$  is in the subthreshold region (close to  $V_T$ ), the leakage current is 3-6 orders of magnitude less than the leakage current in strong inversion. Namely, biasing the decap in the subthreshold region will have negligible gate leakage. The disadvantage of this approach is also similar to that of thick-oxide devices: it serializes 3 decaps and has therefore a resulting equivalent capacitance of 1/3 of one decap. Thus, in order to provide certain amount of decoupling capacitance, much more areas ( $\sim$ 9x) are needed in this fashion.

Figure 3.6: Stack of thin-oxide decaps versus thick-oxide decap.

Showing the idea of the stacked thin-oxide decaps is only to further illustrate the concept of using thick-oxide devices. Stacking thin-oxide decaps does not have practical applications due to its large area requirement.

### 3.5 High-k Gate Dielectric

The oxide capacitance  $C_{OX}$  is a critical factor to many physical properties of MOS transistors. The drain current  $I_{DS}$  of a transistor is proportional to  $C_{OX}$ . A larger  $C_{OX}$  results in a larger drain current and hence a faster transition or a shorter gate delay [3]. Also, the subthreshold leakage including drain-induced barrier lowering (DIBL) is related to  $C_{OX}$ . A larger  $C_{OX}$  corresponds to smaller subthreshold leakage and less DIBL effect [15]. As a consequence, each technology generation attempts to increase  $C_{OX}$  by roughly 1.4x while reducing the channel length L to 0.7x of the previous technology's channel length. The result is that the product of  $C_{OX}L$  has been maintained constant for over 25 years [3] as technology scales. The increase in  $C_{OX}$  balances the tradeoff between the drain current and the subthreshold leakage current in each technology node.

From Equation (2.3), the gate leakage density is inversely related to  $t_{OX}$ . A smaller  $t_{OX}$  leads to exponentially increasing gate leakage. From the gate leakage perspective, the oxide thickness  $t_{OX}$  should be kept large. However, the oxide capacitance per unit area,  $C_{OX}$ , is determined by [3]:

$$C_{OX} = \frac{\varepsilon_{OX}}{t_{OX}} \tag{3.1}$$

where  $\varepsilon_{OX}$  is the permittivity of the oxide and is fixed for a given oxide material. Equation (3.1) suggests that if  $\varepsilon_{OX}$  is kept unchanged, the increase in  $C_{OX}$  will lead to certain decrease in  $t_{OX}$  and hence exponential growth in gate leakage.

Knowing that the gate leakage increase may be excessive for 90nm technology and below, in order to keep  $t_{OX}$  thick while increasing  $C_{OX}$ , one can adjust the relative dielectric constant, k, where  $\varepsilon_{OX} = k \cdot \varepsilon_0$ , and  $\varepsilon_0$  is the vacuum permittivity. If a high permittivity (high-k) dielectric can be used instead of the normal SiO<sub>2</sub> oxide, the physical oxide thickness  $t_{OX}$  would no longer be limited by its electrical property  $C_{OX}$ . This concept of using high-k dielectrics was first presented in [26], and researchers and process engineers have continued to pursue better high-k materials [27]. Most experts agree that high-k gate dielectrics will help to keep the gate leakage under control [27].

Commonly suggested high-k materials include HfO<sub>2</sub>, ZrO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub> [27]-[29], whose permittivity ranges from 10 to 30, compared to 3.97 of SiO<sub>2</sub>. [30] presents the materials of barium titanate (BTO) and barium strontium titanate (BSTO) that have permittivity ranged from 100 to 400, about the highest among the up-to-date research results.

The application of high-k gate dielectrics is currently an active research area. Many challenges still remain [27]: thermal stability of the dielectrics, interfacial layer formation, effective oxide thickness control and environmental sensitivity, channel mobility degradation, high-k dielectric stability with poly-silicon gates, and possible use of metal gate instead of poly-silicon. Among all, the two most critical problems are: (1) High-k and polysilicon gates are incompatible due to Fermi level pinning at the interface between high-k and polysilicon, which causes high threshold voltages in transistors. (2) The high-k/polysilicon transistor structure exhibits a degradation of

channel mobility  $\mu$  due to Coulombic scattering since high-k MOSFETs tend to have more oxide charge and interface traps [27] [29].

Until the majority of the above mentioned issues are solved, high-k dielectrics may not be applied to industrial designs. [31] predicts the availability of high-k technology in the year 2007. At least for now, for a typical 90nm process [24], the oxide material still uses regular SiO<sub>2</sub>, which was also the case for the 130nm technology.

### 3.6 Metal-Insulator-Metal Capacitor

Many fabrication processes support the implementation of metal-insulator-metal (MIM) capacitors. MIM capacitors can be integrated into both aluminum and copper interconnect backend of the line (BEOL) processes [32]. In an Al process, a MIM capacitor is usually composed of an Al bottom plate with Ti or TiN liners, a silicon dioxide SiO<sub>2</sub> or silicon nitride Si<sub>3</sub>N<sub>4</sub> dielectric, and a titanium nitride TiN top plate [33] [34]. For Cu processes, various MIM integration schemes have been reported for the past few years by several research groups [34]. The materials of metal electrodes and dielectrics in use vary from case to case [34]. Typically, in a Cu process, a MIM capacitor is composed of a Cu (or Ta or TaN) bottom place, a plasmaetched chemical vapor deposition SiN dielectric, and a Ta top electrode [34] [35]. MIM capacitor designs typically utilize the top metal layer and the next lower metal plate as the two capacitor electrodes in order to minimize the parasitic coupling capacitance between the bottom of the MIM plate and substrate [33].

MIM capacitors are popular in analog, mixed-signal, and RF IC designs, mainly because of high linearity, low series resistance, high capacitance density, high precision, and low parasitic capacitance [33]. The depletion-free, highly-conducting metal electrodes are suitable for high speed applications at low cost [34]. In addition, MIM capacitors usually have small leakage currents, mainly because the dielectric thickness is large (>50nm) [33]. The low effective resistance and low leakage make MIM capacitors good candidates for white-space decaps. When connecting to the MIM capacitors, the interconnects need to be kept short and wide so that the total resistance is maintained low [35].

### 3.7 Summary

This chapter described a number of design approaches for decaps in recent technologies. Starting from circuit level, cross-coupled decap, gated decap, and thick-oxide decaps are discussed in details. Process level efforts are also taken into account, where the use of high-k gate dielectrics and MIM capacitors is addressed. Moreover, researchers are implementing decaps in special MOS structures [36] and claiming good results in gate leakage savings. Another circuit design approach, called *switched decap*, is more complex and will be discussed separately in Chapter 5.

As already mentioned, decap design with gate leakage consideration is still an active field because the problem of excessive gate leakage is fairly new. In order to make further improvements from the existing design approaches, the cross-coupled design is investigated in this research since it is commonly used in 90nm standard-cell libraries.

### Chapter 4

# **Passive Decoupling Capacitor Designs**

#### 4.1 Introduction

The objective of this chapter is to provide passive decoupling capacitor designs that properly tradeoff between their transient response, ESD performance, and gate leakage. The basic idea of the cross-coupled decap is to use a crossly coupled N+P decap pair to reduce ESD risk by adding series resistances to the gates. Continuing on from the discussion in Section 3.2, modeling of the cross-coupled decap is provided. Before any improvements can be made, detailed transient, ESD and gate leakage simulations have to be setup and carried out to compare against the standard decap. After the quantitative analysis of the advantages and limitations, three modifications based on the basic cross-coupled design are then proposed in [37] and [38]. One sample cell layout for each of the modified circuits is provided. From the simulation results, recommendations are made as to how to select the appropriate design for a given technology or a process.

### 4.2 RC Modeling of Basic Cross-Coupled Decap Design

Knowing that the standard N+P decap design may no longer be suitable for 90nm technology due to the increased ESD risk, a cross-coupled decap design has been proposed [11] to address

the issue of ESD reliability. It reconnects the terminals of the two transistors: the drain of the PMOS connects to the gate of the NMOS, whereas the drain of the NMOS is tied to the gate of the PMOS [11].

Figure 4.1: Cross-coupled decap schematic [11] and modeling.

The design can be modeled as a series connection of  $R_{eff}$  and  $C_{eff}$ , similar to the standard decap, as illustrated in Figure 4.1. The overall  $C_{eff}$  is roughly the same, while the overall  $R_{eff}$  increases significantly. Both transistors are still in the linear region, but the channel resistance is modified. Specifically,

$$C_{eff\_overall} \approx C_{eff\_n} // C_{eff\_p} = C_{eff\_n} + C_{eff\_p}$$

$$R_{eff\_overall} \approx (R_{eff\_p} + R_{on\_n}) // (R_{eff\_n} + R_{on\_p})$$

$$R R$$

$$(4.1)$$

$$\approx R_{on_{-n}} // R_{on_{-p}} = \frac{R_{on_{-n}} R_{on_{-p}}}{R_{on_{-n}} + R_{on_{-p}}}$$

(4.2)

where  $C_{eff\_n}$ ,  $C_{eff\_p}$ ,  $R_{eff\_n}$  and  $R_{eff\_p}$  are the intrinsic effective capacitances and resistances, respectively, and  $R_{on\_p}$  and  $R_{on\_n}$  are the channel resistances of the two transistors. Since  $R_{on\_p}$  and  $R_{on\_n}$  are at least one order of magnitude larger,  $R_{eff\_p}$  and  $R_{eff\_n}$  can be neglected in the overall  $R_{eff}$  calculation. Here,

$$R_{on} \approx R_{eq} \frac{L}{W} \tag{4.3}$$

where  $R_{eq}$  is the process-dependent square resistance ( $k\Omega/\Box$ ). It is important to realize that Equation (4.1)-(4.3) are first-order, low-frequency approximations only. The real transistor channel resistance by nature is nonlinear and depends strongly on applied voltages, operating frequency, and geometry [3]. The only reason for providing these formulae is to give designers some insight into the design tradeoffs.

This cross-coupled design improves the ESD performance of the decap by making the overall effective resistance larger without adding additional area. The tradeoff of the design is a reduced transient response. The larger  $R_{eff}$  corresponds to a longer RC delay. In addition, this design provides no savings in gate leakage as compared to the standard design.

To quantitatively measure ESD performance, transient response, and gate leakage, a number of simulations were carried out. The layouts were created in Virtuoso<sup>TM</sup> Layout Editor, verified by Calibre<sup>TM</sup> DRC checker, and then extracted by Calibre XRC parasitic extraction tool. The extracted data were simulated with HSPICE<sup>TM</sup> for different simulation setups. For fairness, the same cell area was used for all the designs.

### 4.3 Transient Response Simulation

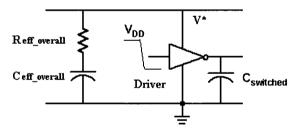

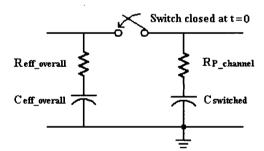

In order to carry out some simple but efficient transient simulations, the setup in Figure 4.2 was chosen to evaluate the time domain decap performance. The setup is a pessimistic situation where no power supply is present. Only the decap provides the needed current to charge up the load when the inverter switches. The node  $V^*$  is initially charged to  $V_{DD}$ , and the output is initialized to 0V while the total switched capacitance  $C_{switched}$  is set to roughly 1/10 of the

decoupling capacitance and then fixed. Note that  $C_{switched}$  includes the output parasitic capacitance of the inverter. The input of the inverter is initially set to  $V_{DD}$ . At 30ps, it starts to drop linearly from  $V_{DD}$  to 0V, reaches 0V at 60ps, and then remains constant.

Figure 4.2: Schematic for the first transient setup.

To simplify this transient setup, the decap can still be treated as series of  $R_{eff\_overall}$  and  $C_{eff\_overall}$  as shown in Figure 4.3. The values of  $R_{eff\_overall}$  and  $C_{eff\_overall}$  would be different for cross-coupled and standard decaps.

Figure 4.3: RC modeling of the first transient setup.

It is possible to gain insight into the required  $C_{eff\_overall}$  value obtained from the final V\* voltage. When the transient analysis runs for sufficient long time (>1ns), the voltage level at V\* stabilizes. Applying the charge-sharing equation, the final voltage V\* can be derived as a function of  $C_{eff\ overall}$ , as follows:

$$Q_{before} = Q_{after}$$

$$C_{eff\_overall} V_{DD} = C_{eff\_overall} V * + C_{switched} V *$$

$$V^* = \left(\frac{C_{eff\_overall}}{C_{eff\_overall} + C_{switched}}\right) V_{DD}$$

(4.4)

If the decap has a large  $C_{eff\_overall}$ , which is desired, the final V\* value will be also large and close to the initially charged value  $V_{DD}$ .

One step of further simplification of this circuit can be used to understand the significance of  $R_{eff\_overall}$  of the decap. For this purpose, the  $R_{eff\_overall}$  and  $C_{eff\_overall}$  are both assumed to be fixed. Also, the '1' to '0' ramp transition that the inverter switches is replaced by a pulse, meaning that there is no time delay from  $V_{DD}$  to 0 when the inverter switches. Since the NMOS device in the inverter can be assumed off during the transition, it can be neglected from the model. The switching of the PMOS device in the inverter is simplified as a constant channel resistance of  $R_{p\ channel}$ . Therefore, the circuit can be modeled as shown in Figure 4.4.

Figure 4.4: Simplification of RC modeling of the first transient setup.

After applying Laplace transform to the circuit in Figure 4.4, the voltage at V\* can be expressed in the s-domain as a simple voltage divider:

$$V*(s) = \frac{R_{P\_channel} + \frac{1}{sC_{switched}}}{R_{P\_channel} + \frac{1}{sC_{switched}} + R_{eff\_overall} + \frac{1}{sC_{eff\_overall}} \cdot \frac{V_{DD}}{s}$$

$$V*(s) = \frac{V_{DD}(\frac{C_{eff\_overall}}{C_{eff\_overall} + C_{switched}})}{s} + \frac{V_{DD}\frac{R_{P\_channel}C_{switched} - R_{eff\_overall}C_{eff\_overall}C_{eff\_overall}}{(C_{eff\_overall} + C_{switched})(R_{eff\_overall} + R_{P\_channel})}{s + \frac{C_{eff\_overall} + C_{switched}}{C_{eff\_overall}C_{switched}(R_{eff\_overall} + R_{P\_channel})}}{c_{eff\_overall}C_{switched}(R_{eff\_overall} + R_{P\_channel})}$$

(4.5)

Applying the inverse-Laplace transform, the time-domain voltage  $V^*$  is (for t > 0):

$$V^*(t) = V_{DD}(\frac{C_{eff\_overall}}{C_{eff\_overall} + C_{switched}}) \cdot u(t) +$$

$$V_{DD} \frac{R_{P\_channel} C_{switched} - R_{eff\_overall} C_{eff\_overall} C_{eff\_overall} + R_{P\_channel})}{(C_{eff\_overall} + C_{switched})(R_{eff\_overall} + R_{P\_channel})} \cdot e^{\frac{(R_{eff\_overall} + R_{P\_channel})(\frac{C_{eff\_overall} C_{switched}}{C_{eff\_overall} + C_{switched}})}$$

(4.6)

constant associated with V\* is  $(R_{eff\_overall} + R_{P\_channel})(\frac{C_{eff\_overall}C_{switched}}{C_{eff\_overall} + C_{switched}})$ , the serial combination of  $R_{eff\_overall}$  and  $R_{p\_channel}$  multiplied by the serial combination of  $C_{eff\_overall}$  and  $C_{switched}$ . The effective overall resistance  $R_{eff\_overall}$  of the decap should be made small so that this time constant will also be small.

Here, the final voltage V\* is consistent with the simple charge-sharing calculation. The time

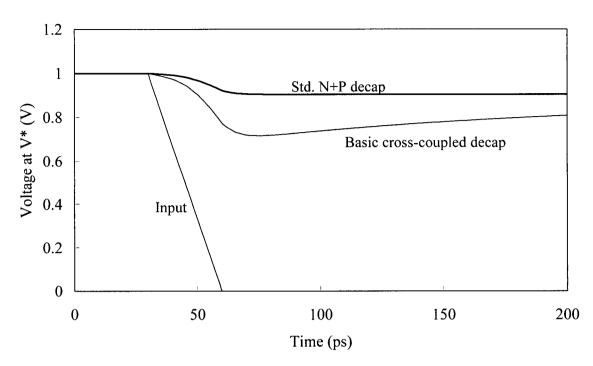

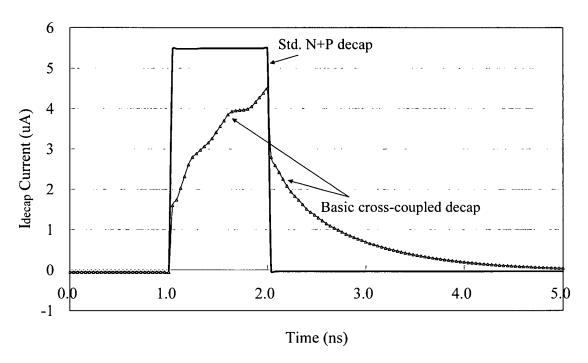

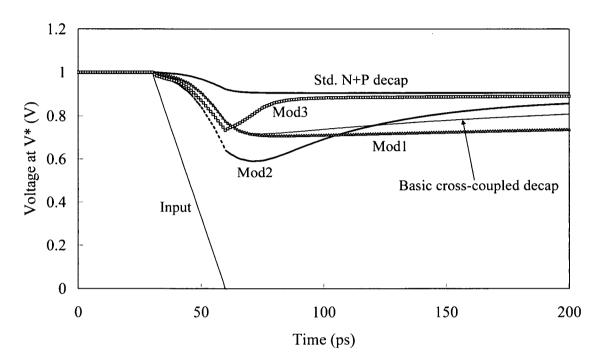

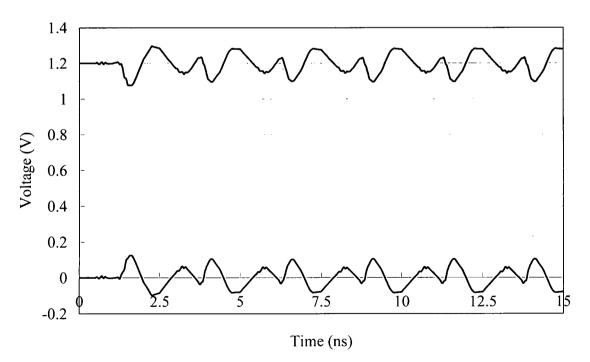

HSPICE simulation for this setup is illustrated in Figure 4.5, where the response of the two designs is plotted. Although not shown, the hand calculation can generate curves that are close to the SPICE results, as expected. From the figure, the two designs have close effective capacitance because their final voltage levels at V\* are close. On the other hand, the cross-coupled design experiences larger  $R_{eff\_overall}$ , resulting in an undershoot and faster voltage drop as input switches. Clearly, the standard decap can provide much better transient response.

Figure 4.5: Transient response for the first setup.

The simplified model indicates that the value of  $R_{eff\_overall}$  determines if there is an undershoot in the transient response. Specifically, if  $R_{P\_channel}C_{switched} \geq R_{eff\_overall}C_{eff\_overall}$ , then the voltage at V\* exponentially drops to its final value without an undershoot. Otherwise, if  $R_{P\_channel}C_{switched} < R_{eff\_overall}C_{eff\_overall}$ , the voltage at V\* will drop below its final value first and then exponentially increase back to the final level, which is an undesired case. It is evident from the transient response perspective that the decap should be designed to have large  $C_{eff\_overall}$  and small  $R_{eff\_overall}$ .

Note that the above circuit simplification is only intended for giving designers some useful guidelines. The real situation involves many nonlinear factors such as varying  $R_{p\_channel}$  when switching, and varying  $R_{eff\_overall}$  and  $C_{eff\_overall}$  at high frequencies. However, for the purpose of

first-order calculations or estimations, the simplified model gives valuable insight into the design tradeoffs.

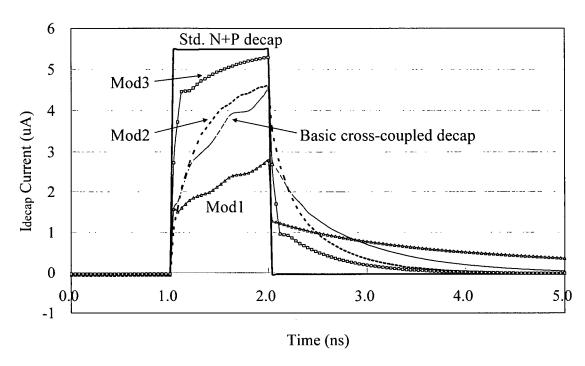

Another simple setup was also used to determine the effective capacitance value and the RC delay of the decap. The setup is shown in Figure 4.6. The  $V_{DD}$  node is connected to the nominal supply of 1V (for 90nm), and  $V_{SS}$  is tied to a common ground. When there is no activity, the current flow from  $V_{DD}$  to  $V_{SS}$  is solely due to gate leakage. At 1ns,  $V_{DD}$  starts to drop linearly from 1V to 0.9V, reaches 0.9V at 2ns, and then remains constant.

Figure 4.6: Schematic for the second transient setup.

By definition, an ideal capacitor responds to a voltage change as a current source if it is fully charged, as follows [39]:

$$I_{decap} = C_{decap} \frac{dv}{dt} \approx C_{decap} \frac{\Delta v}{\Delta t}$$

(4.7)

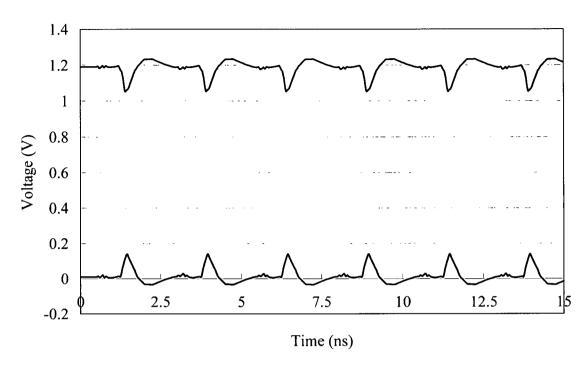

If the voltage change is a ramp, the current provided by the ideal capacitor should be a pulse. In practice, due to the presence of the effective resistance associated with the decap designs, a certain amount of RC delay exists. A good transient response should have sharp rise and fall edges (at 1ns and 2ns in this case), and also provide a large average current  $I_{avg}$  during the time period from 1ns to 2ns. The sharpness of rise and fall is measured from the rise/fall slopes with a

unit of A/s. The average capacitance  $C_{avg}$  is calculated from  $I_{avg}$  from Equation (4.7). Figure 4.7 illustrates the curves for the two designs in transient analysis, and indicates that the standard decap is better in the transient response. The result in this plot is consistent with the result obtained from Figure 4.5 previously.

Figure 4.7: Transient response for the second setup.

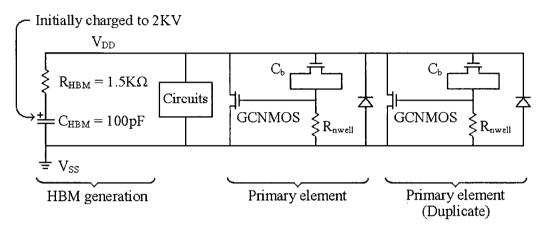

#### 4.4 ESD Performance Simulation

The ESD simulation requires an ESD generation model. Among all the existing models, the human body model (HBM) was adopted for simplicity. Following the standard MIL-STD-883x method 3015.7 [10], a human body can be simulated as a series of  $1.5k\Omega$  resistance  $R_{HBM}$  and 100pF capacitance  $C_{HBM}$ . The capacitor  $C_{HBM}$  is initially charged to 2kV that needs to be discharged through some primary elements. The primary element is arbitrarily chosen to be an

ESD diode plus a gate-coupled NMOS device (GCNMOS) with an n-well resistor  $R_{nwell}$  (~15k $\Omega$ ) and an NMOS bootstrap capacitor  $C_b$ . Two identical primary elements are used to protect the circuit placed in between the HBM generation and the elements, as shown in Figure 4.8. For simplicity, no secondary element is used.

Figure 4.8: Simulation setup for ESD analysis [10].

Since the primary elements are designed to handle large current flow, the maximum current density,  $J_{max}$ , is assumed to be within the safe range and is not measured. HBM generation raises the voltage level at node  $V_{DD}$ , and hence turns on the primary elements to discharge. For device protection from oxide breakdown, the voltage differences across gate and source ( $V_{GS}$ ) and across gate and drain ( $V_{GD}$ ) of the two transistors are simulated. The  $V_{GS}$  and  $V_{GD}$  voltages should to be kept as low as possible, given that the oxide breakdown voltage for a typical 90nm is below 5V.

From simulation measurements, it was found that:

- For standard decaps,  $V_{GD_p} = V_{GS_p} = V_{GD_n} = V_{GS_n} = 4.2V$ .

- For cross-coupled case,  $V_{GD_p} = 4.0V$ ,  $V_{GS_n} = 3.2V$ , and  $V_{GS_p} = V_{GD_n} = 3.0V$ .

The cross-coupled design provides better ESD protection by making the overall effective resistance larger without adding additional area. However, the improved ESD performance is at the expense of transient response, as described earlier.

### 4.5 Gate Leakage Simulation

The gate leakage levels can be obtained from the two transient setups in Section 4.3. In the first transient setup (Figure 4.2), before the inverter switches, the static current flow through the decaps can be treated purely as gate leakage. In the second transient analysis (Figure 4.6), before the node  $V_{DD}$  starts to drop its voltage, the current flow through the decaps is solely gate leakage.

When carrying out SPICE simulations, it is essential to use BSIM4 version to have gate leakage models built-in [14]. Earlier BSIM versions do not support gate leakage models [14]. The gate leakage in BSIM4 is partitioned into two parts: the tunneling current between gate and substrate (Igb) and the current between gate and channel (Igc) [19]. Since the current Igb is considerably smaller than Igc, Igb is set off by default [24]. To make sure both current components are set on for the best accuracy, two selectors, IGBMOD and IGCMOD, need to be set '1' [19].

As discussed in the earlier sessions, the cross-coupled decap design does not provide any savings in gate leakage. HSPICE simulations show that the two designs have almost identical gate leakage: 53.8nA for the standard decap and 53.7nA for the cross-coupled design.

### 4.6 Modified Cross-Coupled Decap Designs

Three modifications are made to address different goals of decap design: ESD performance, transient response, and gate leakage. It is difficult to simultaneously make improvements on all the three goals, but trying to balance them and to make tradeoffs is certainly feasible and indeed achievable. Each modification is compared to the basic cross-coupled design to show advantages and disadvantages. Again, the total cell area is fixed for all the designs.

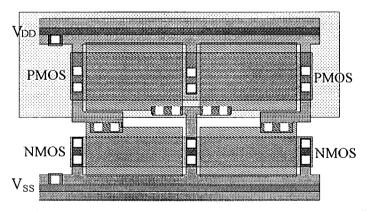

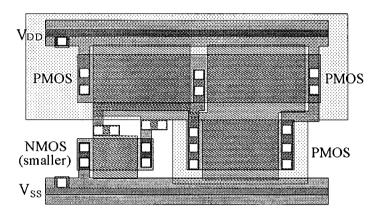

The first modification (Mod1) attempts to improve ESD performance by making the channel lengths of the two resistors longer (Figure 4.9). The two fingers are combined into one. As a result, the overall  $R_{eff}$  is almost doubled, while the overall  $C_{eff}$  remains roughly the same. The disadvantage of this design is reduced transient response and slightly larger gate leakage since the gate area increases a little.

Figure 4.9: Sample layout of Mod1 (basic circuit without fingering).

The second modification (Mod2) attempts to reduce gate leakage while maintaining ESD performance and transient response at roughly the same level (Figure 4.10). One NMOS is replaced by a PMOS with the n-well expanded to accommodate the new PMOS. The effect of

this change is then increased  $R_{on\_p}$  and  $C_{eff\_p}$ . To match ESD performance,  $R_{on\_n}$  needs to be reduced. One simple change to obtain a small  $R_{on\_n}$  is to reduce the channel length of the NMOS. By the same token,  $C_{eff\_n}$  is also reduced. The result is comparable ESD performance and transient response if carefully designed. Using the fact that the new same-area PMOS leaks 3 times less than the replaced NMOS, extra saving in gate leakage is realized.

Figure 4.10: Sample layout of Mod2 (replace NMOS with PMOS).

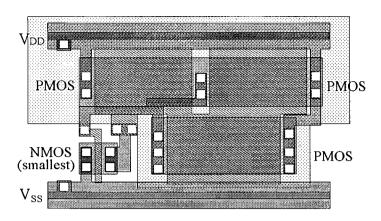

The third modification (Mod3) (Figure 4.11) follows the similar approach as of Mod2. It further increases the new PMOS area while reducing the NMOS area. Indeed, the minimum length NMOS is used to obtain the smallest possible  $R_{on_n}$  so that it dominates and makes the overall  $R_{eff}$  smaller. Since the overall  $R_{eff}$  is greatly decreased while the overall  $C_{eff}$  is somewhat higher, the transient response dramatically improves. The only downside is reduced ESD protection capability due to the reduced overall  $R_{eff}$ .

Figure 4.11: Sample layout of Mod3 (replace NMOS with PMOS, and use smallest NMOS).

Table 4.1: Comparison on ESD performance, transient response and gate leakage.

|                   | ESD performance with 2 primary elements |                                                            |                          | Transient response             |                        |          | Gate<br>leakage |

|-------------------|-----------------------------------------|------------------------------------------------------------|--------------------------|--------------------------------|------------------------|----------|-----------------|

|                   |                                         | $V_{\mathrm{GD_p}}(V) \left  V_{\mathrm{GS_n}}(V) \right $ | $V_{GS_p} = V_{GD_n}(V)$ | First<br>setup                 | Second setup           |          | Leakage         |

|                   | $V_{GD_p}(V)$                           |                                                            |                          | Voltage<br>drop rate<br>(V/ns) | Rise<br>slope<br>(A/s) | Avg. cap | current (nA)    |

| Std. Decap        | 4.2                                     | 4.2                                                        | 4.2                      | -1.8                           | 2.8e5                  | 54.3     | 53.8            |

| Cross-<br>coupled | 4.0                                     | 3.2                                                        | 3.0                      | -5.4                           | 8.2e4                  | 33.1     | 53.7            |

| Mod1              | 3.8                                     | 2.9                                                        | 2.8                      | -5.3                           | 8.7e4                  | 21.4     | 59.7            |

| Mod2              | 4.0                                     | 3.7                                                        | 3.4                      | -8.6                           | 7.0e4                  | 35.8     | 33.6            |

| Mod3              | 4.1                                     | 3.9                                                        | 3.8                      | -7.0                           | 1.1e5                  | 47.5     | 31.8            |

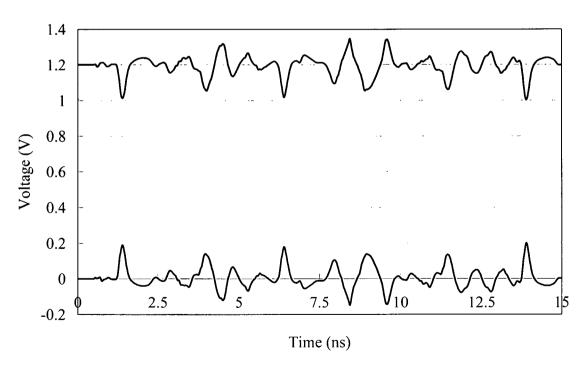

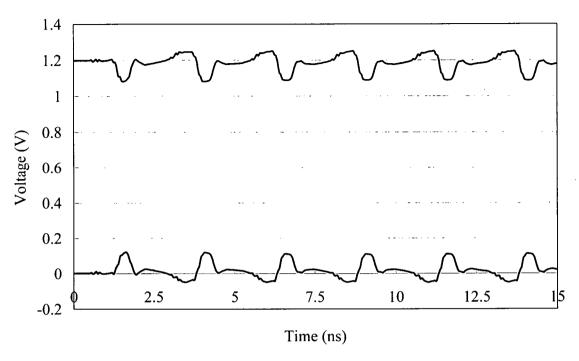

Following the same simulation procedures outlined earlier, Table 4.1 summarizes the comparisons for all the designs on ESD performance, transient slope response, and gate leakage. The **bold** numbers indicate the best results in the comparison. The standard decap provides the best transient response. Mod1 provides the best ESD protection, while Mod3 provides the lowest

gate leakage. One can view Mod2 as a compromise between Mod1 and Mod3. The complete transient simulations for the first and second setups are also depicted in Figure 4.12 and Figure 4.13, respectively.

Figure 4.12: Complete transient response for the first setup.

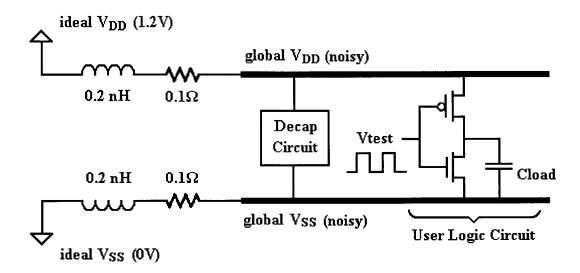

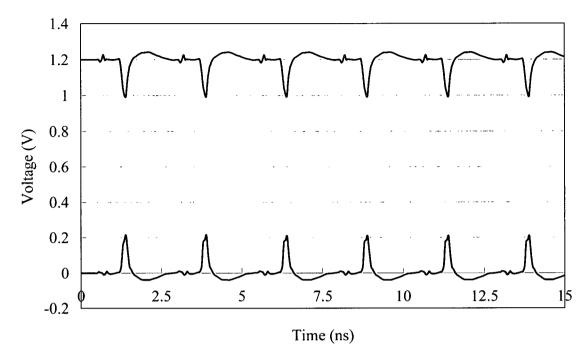

Figure 4.13: Complete transient response for the second setup.