### **TESTABILITY INFRASTRUCTURE**

#### FOR SYSTEMS-ON-CHIP

by

#### MOHSEN NAHVI

B.Sc. University of Manchester Institute of Science and Technology, 1989 M.Sc. University of Manchester Institute of Science and Technology, 1990

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### DOCTOR OF PHILOSOPHY

in

## THE FACULTY OF GRADUATE STUDIES (ELECTRICAL AND COMPUTER ENGINEERING)

We accept this thesis as conforming to the required standard

#### THE UNIVERSITY OF BRITISH COLUMBIA

June 2004

© Mohsen Nahvi, 2004

## Abstract

Relying on external *automatic test equipment* (ATE) resources is insufficient for the new paradigm of billion-transistor core-based *System-on-Chip* (SoC) designs. Embedded testers that take over some functionality of these ATEs are increasingly deemed essential. To achieve high-quality test and reduce cost, these embedded infrastructures need to perform deterministic tests and exploit the advantages of *automatic test pattern generation* (ATPG) test vector sets. This thesis proposes an embedded testing infrastructure that leverages the potentials of the classical embedded testing in the form of *Built-in Self-Test* (BIST). However, unlike BIST, the methodology of this thesis is based on the conventional scan/ATPG approach. This novel methodology partitions test resources to embed the test application and test results analysis on-chip while keeping the ATPG test vector files off-chip. The proposed infrastructure was implemented on silicon and experimental area and test time results are reported. Using the methodology of this thesis, a high-quality deterministic test, with reduced overall test time through ideal multi-site testing, can be achieved.

Modular, flexible, and systematic test architectures are also deemed essential in SoC tests. The conventional testing paradigm requires a direct connection between a tester and the *circuit under test* (CUT). This arrangement undermines the modularity in the test

architecture by tightly coupling its elements. This thesis proposes to de-couple test data processing and communication to lower test cost. To that end, a novel systematic and indirect test architecture that is based on network-oriented protocols is proposed. In this new architecture, test stimuli and expected results for digital cores are formatted into new protocols and then encapsulated into packets. These packets are augmented with control and address bits allowing them to be autonomously transmitted to their destination through a switching infrastructure. Finally, embedded autonomous blocks at each core are used for applying the test and comparing the results. In this way, the methodology of this thesis facilitates test cycle automation and eliminates the need for control lines. This results in better utilisation of available resources. A first implementation of this new architecture and its area and test time impact are presented.

## **Table of Contents**

| Abstractii                                    |

|-----------------------------------------------|

| Table of Contentsiv                           |

| List of Tables viii                           |

| List of Figuresix                             |

| Acronyms xi                                   |

| Acknowledgements xiv                          |

| Chapter 1 Introduction                        |

| 1.1 Current Test Strategies                   |

| 1.2 Research Goals                            |

| 1.2.1 Dedicated Autonomous Scan-based Testing |

| 1.2.2 Test Network-on-Chip7                   |

| 1.3 Contributions                             |

| 1.4 Thesis Organization13                     |

| Chapter 2 Background and Motivations          |

| 2.1 System-on-Chip Design Methodology14       |

| 2.2 Reuse Paradigm17                          |

| 2.3 Te | est Challenges                                 | 19 |

|--------|------------------------------------------------|----|

| 2.3    | 1 Test Challenges in DSM Technology            | 19 |

| 2.3    | 2 Test Challenges in SoC                       | 22 |

| 2.4 Sc | oC Test Trends                                 | 24 |

| 2.4    | 1 Test Reuse                                   | 25 |

| 2.4    | 2 Systematic Test Architecture                 | 25 |

| 2.4    | .3 Test Resources Partitioning                 | 27 |

| 2.4    | .4 Multi-site Testing                          | 28 |

| 2.4    | .5 Test Data Compression                       | 29 |

| 2.4    | .6 Embedded Testing                            | 29 |

| 2.5 C  | urrent Test Architectures                      | 31 |

| 2.5    | .1 Standard Wrapper                            | 31 |

| 2.5    | .2 Built-in Self Test                          | 33 |

| 2.5    | .3 ATE-based Test Architectures                |    |

| Chap   | oter 3 Dedicated Autonomous Scan-Based Testing | 42 |

| 3.1 In | troduction                                     | 42 |

| 3.2 C  | omponents of Scan-based Testing                | 43 |

| 3.3 D  | AST Concept                                    | 46 |

| 3.4 In | nplementation                                  | 50 |

| 3.4    | .1 EAS & EARA Compilers                        | 51 |

| 3.4    | .2 EAS & EARA Hardware                         | 54 |

. .

| 3.5 Expe  | rimental Procedure                                             | 59   |

|-----------|----------------------------------------------------------------|------|

| 3.6 Resu  | lts                                                            | 64   |

| 3.7 Sum   | mary and Conclusions                                           | 72   |

| Chapte    | er 4 Network-Oriented Indirect and Modular Architecture for Te | st75 |

| 4.1 Intro | duction                                                        | 75   |

| 4.2 NIM   | A Concept                                                      | 79   |

| 4.3 Phys  | ical Layer                                                     | 83   |

| 4.4 Netw  | vork Layer                                                     | 84   |

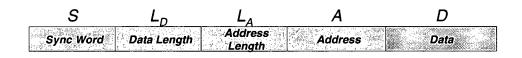

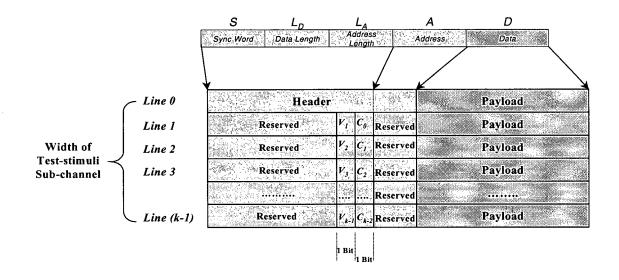

| 4.4.1     | Packet Format                                                  | 85   |

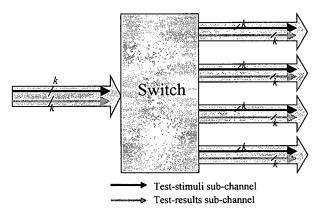

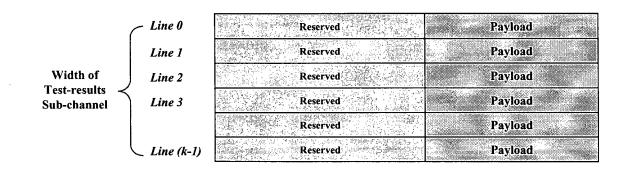

| 4.4.2     | Switches                                                       | 87   |

| 4.4.3     | Dynamic Addressing Mechanism                                   | 91   |

| 4.4.4     | Routing in the Switches                                        | 94   |

| 4.5 Appl  | ication Layer                                                  | 95   |

| 4.6 Imple | ementation                                                     |      |

| 4.6.1     | Physical Layer                                                 | 98   |

| 4.6.2     | Network Layer                                                  |      |

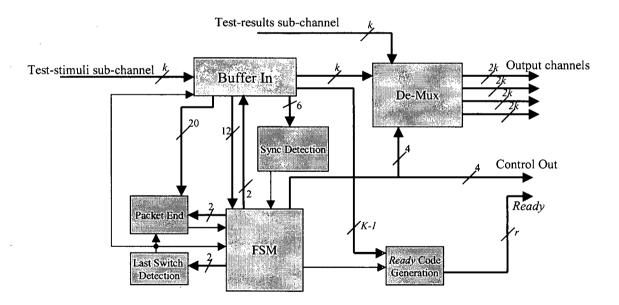

| 4.6.3     | Application Layer                                              |      |

| 4.7 Expe  | erimental Results                                              |      |

| 4.7.1     | Area and Power Overhead                                        | 103  |

| 4.7.2     | NIMA's Test Time                                               |      |

| 4.8 Sum   | mary and Conclusions                                           | 107  |

)

| Chapter 5 Conclusions                                                 | 110 |

|-----------------------------------------------------------------------|-----|

| 5.1 Summary                                                           | 110 |

| 5.2 Future Work                                                       |     |

| Bibliography                                                          |     |

| Appendix A: DAST Test Time Models                                     |     |

| Appendix B: Theoretical Test Time Models for Serial ATE-based Testing |     |

## **List of Tables**

•

| Table 2-1: ITRS Prediction for Number of Transistors on a Chip [4]         15      |

|------------------------------------------------------------------------------------|

| Table 3-1: EAS Area and Power for the UBC_SoC Benchmark Cores                      |

| Table 3-2: EARA Area and Power for the UBC_SoC Benchmark Cores                     |

| Table 3-3: EAS Area and Power for ITC'02 SoC Benchmark Modules                     |

| Table 3-4: EARA Area and Power for ITC'02 SoC Benchmark Modules67                  |

| Table 3-5: Simulated DAST Test Time (clock cycles) and its Test Time Models        |

| Prediction Values for Cores of UBC_SoC70                                           |

| Table 3-6: Predicted Test Time (clock cycles) for ITC'02 SoC Benchmarks Modules in |

| DAST Methodology71                                                                 |

| Table 4-1: NIMA Simulated Test Time and its Test Time Model Prediction Values for  |

| Cores of UBC_SoC (in clock cycles)105                                              |

| Table 4-2: Predicted NIMA Test Time for ITC'02 SoC Benchmarks Modules (in clock    |

| cycles)106                                                                         |

|                                                                                    |

•

# **List of Figures**

| Figure 1-1: An example of a simplified SoC test architecture                          |

|---------------------------------------------------------------------------------------|

| Figure 1-2: DAST concept                                                              |

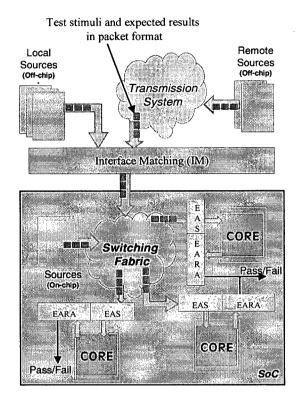

| Figure 1-3: NIMA concept                                                              |

| Figure 2-1: Example of a System-on-Chip [5]16                                         |

| Figure 2-2: Potential design complexity and designer productivity [9]17               |

| Figure 2-3: Design development and test flow for (a) System-on-Board, and (b) System- |

| on-Chip [15]23                                                                        |

| Figure 2-4: A generic conceptual test architecture [15]26                             |

| Figure 2-5: Block level overview of a P1500 wrapper [45]32                            |

| Figure 2-6: Conceptual view of the required P1500 wrapper architecture [45]33         |

| Figure 2-7: Block diagram of a typical BIST arrangement                               |

| Figure 3-1: Block diagrams of (a) D-type flip-flop, and (b) Scan D-type flip-flop44   |

| Figure 3-2: Generic scan test waveforms                                               |

| Figure 3-3: Concept of DAST                                                           |

| Figure 3-4: DAST design flow                                                          |

| Figure 3-5: EAS compiler algorithm                                                    |

| Figure 3-6: EARA compiler algorithm                                                   |

| Figure 3-7: Hardware implementation of DAST components                                    |

|-------------------------------------------------------------------------------------------|

| Figure 3-8: EAS block Algorithmic State Machine                                           |

| Figure 3-9: EARA block Algorithmic State Machine                                          |

| Figure 3-10: UBC_SoC Benchmark61                                                          |

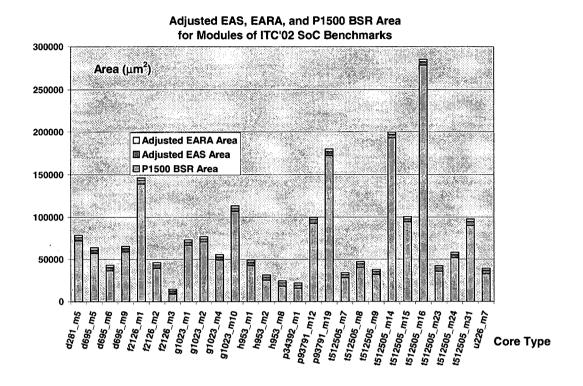

| Figure 3-11: P1500 BSR and adjusted EAS and EARA areas for modules of ITC'02              |

| Benchmarks69                                                                              |

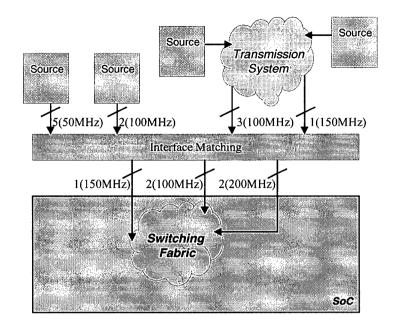

| Figure 4-1: Conceptual representation of NIMA80                                           |

| Figure 4-2: An example showing function of the IM block                                   |

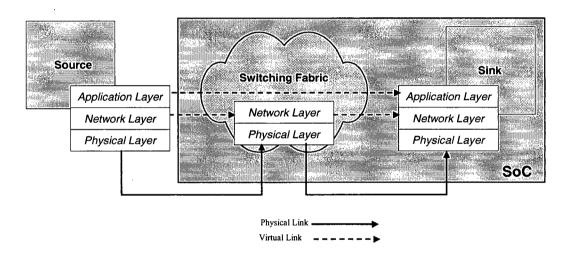

| Figure 4-3: The conceptual 3-layer model in NIMA83                                        |

| Figure 4-4: NIMA packet format85                                                          |

| Figure 4-5: Black box diagram of a switch in NIMA with four output channels               |

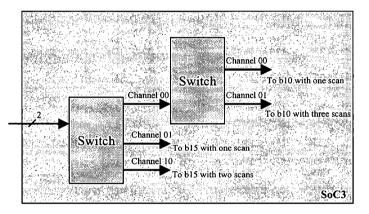

| Figure 4-6: Occupancy of test-stimuli sub-channels in NIMA switches                       |

| Figure 4-7: Occupancy of test-results sub-channels in NIMA switches                       |

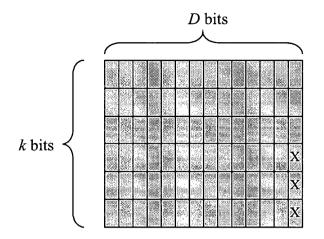

| Figure 4-8: A typical payload array in sub-channels with invalid last bits marked by "X". |

|                                                                                           |

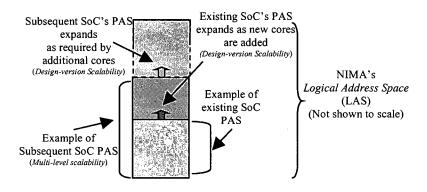

| Figure 4-9: Address spaces for NIMA's Network Layer                                       |

| Figure 4-10: Interconnect architecture for the switch fabric in UBC_SoC                   |

| Figure 4-11: Block diagram of a switch in the NIMA implementation                         |

## Acronyms

| ASIC | Application-Specific Integrated Circuit       |

|------|-----------------------------------------------|

| ASM  | Algorithmic State Machine                     |

| ATE  | Automatic Test Equipment                      |

| ATPG | Automatic Test Pattern Generation             |

| BIST | Built-in Self-Test                            |

| BSR  | Boundary Scan Register                        |

| CAS  | Core Access Switch                            |

| CTL  | Core Test Language                            |

| CUT  | Circuit under Test                            |

| DAST | Dedicated Autonomous Scan-based Testing       |

| DFT  | Design for Testability                        |

| DSM  | Deep Sub-Micron                               |

| EARA | Embedded Autonomous Results Analyzer          |

| EAS  | Embedded Autonomous Sequencer                 |

| EDA  | Electronic Design Automation                  |

| FSM  | Finite State Machine                          |

| GALS | Globally Asynchronous and Locally Synchronous |

| IC   | Integrated Circuit                                  |

|------|-----------------------------------------------------|

| I-IP | Infrastructure IP                                   |

| ILP  | Integer Linear Programming                          |

| IM   | Interface Matching                                  |

| I/O  | Input/Output                                        |

| IP   | Intellectual Property                               |

| ITRS | International Technology Roadmap for Semiconductors |

| LAN  | Local Area Network                                  |

| LAS  | Logical Address Space                               |

| LFSR | Linear Feedback Shift Register                      |

| LSB  | Least Significant Bit                               |

| NIMA | Network-oriented Indirect and Modular Architecture  |

| NoC  | Network on Chip                                     |

| PAS  | Physical Address Space                              |

| PI   | Primary Input                                       |

| PLL  | Phase Locked Loop                                   |

| PO   | Primary Output                                      |

| SC   | Scan Chain                                          |

| SE   | Scan-cell Element                                   |

| SECT | Standard for Embedded Core Test                     |

| . SI | Scan Input                                          |

Þ

| SO   | Scan Output                         |

|------|-------------------------------------|

| SoC  | System-on-Chip                      |

| TAM  | Test Access Mechanism               |

| ТАР  | Test Access Port                    |

| TLM  | TAP Link Module                     |

| TP   | Test Pattern                        |

| TS   | Test Select                         |

| UDL  | User-Defined Logic                  |

| VLSI | Very Large Scale Integrated Circuit |

| WAN  | Wide Area Network                   |

| WBR  | Wrapper Boundary Register           |

| WIR  | Wrapper Instruction Register        |

| WPC  | Wrapper Parallel Control            |

| WPI  | Wrapper Parallel Input              |

| WPO  | Wrapper Parallel Output             |

| WSC  | Wrapper Serial Control              |

| WSI  | Wrapper Serial Input                |

| WSO  | Wrapper Serial Output               |

.

## Acknowledgements

I am very grateful to my supervisor, Professor André Ivanov, for his friendship, support, guidance, and encouragement in the course of my graduate studies. I have been truly fortunate to have the pleasure of working with him for the past few years while conducting the research of this thesis. André has contributed a great deal to the manner in which I have conducted the work of this thesis, and to the development of my ability to write technical papers and be articulate when presenting my work. I thank him most sincerely for all his contributions to my professional life.

My sincere thanks go to my dear wife, Elham. Her love and support have always been unconditional and heart warming. She never ceases to amaze me with her ability to be so loving and caring. She has contributed so much to the successful completion of my graduate studies through her constant support, kindness, and love. Thank you Elham.

I am also grateful to Professor Resve Saleh and Dr. Steve Wilton who have helped and encouraged me as my supervisory committee. My thanks are also extended to the many great people working in the System-on-Chip (SoC) lab, and, in particular, to Roozbeh Mehrabadi and Victor Aken'Ova for their readiness to help in any way. I am also grateful to Doris Metcalf, and Shahab and Ameneh Ghoreishi. Finally, I would like to thank Canadian Microelectronics Corporation (CMC), Micronet, PMC-Sierra, Genum Corporation, and the University of British Columbia for their financial support.

.

To Elham, for her love and kindness.

•

# Chapter 1 Introduction

The semiconductor industry has witnessed an astonishing rate of growth in the past 40 years. The fundamental element contributing to this growth has been the continuous reduction in the size of the transistors on a chip. This trend has been doubling the number of transistors on an *integrated circuit* (IC) every eighteen months or so, a well-known trend referred to as Moore's law. According to the 2003 edition of International Technology Roadmap for Semiconductors (ITRS), this rate of growth could be sustained for at least fifteen more years, resulting in even more complex *very large scale integrated* (VLSI) circuits [1].

However, random failures in the process of fabricating an IC cannot be avoided and these failures result in defective chip circuitry. Hence, it is essential to test semiconductor ICs after fabrication. This post fabrication test is intended to guarantee, with a high probability, the absence of possible defects in the chips. In this way, the post fabrication test verifies a chip's reliability before it is used in a system [2][3]. ICs are tested in different stages (sometimes referred to as *test insertions*). Based on the intended goals, test insertions can target the parametric, temperature stressing, logical, functional, and timing integrity of the integrated *circuit under test* (CUT). Testing VLSI circuits can be a very expensive and difficult process and will grow in its cost and complexity as ICs follow Moore's law [4]. *Design for testability* (DFT) techniques are, hence, essential to facilitate the testing of VLSI chips and reduce test cost [2][4]. In addition to certain design guidelines, which enhance the testability of a CUT, DFT techniques generally consist of added hardware or circuitry that improves *observability* and *controllability* of internal nodes of the CUT.

The focus of this thesis is on DFT techniques for digital circuits. In particular, this thesis proposes two effective and novel testability infrastructures for testing embedded digital blocks of *system-on-chip* (SoC) designs. These unique infrastructures combine the advantages of the current SoC test solutions in innovative ways in order to accommodate different trends and requirements in addressing the SoC test challenges. The solutions developed in this thesis lower test cost by partitioning of the test resources, performing embedded deterministic test, and enabling ideal multi-site parallel testing. Moreover, when compared to existing solutions, the proposed techniques described in this thesis exhibit modular, systematic, and flexible architectures that result in improved quality, productivity, and diagnostic capability of SoC post fabrication test. Since the focus of

this thesis is on DFT techniques for digital blocks of SoC designs, unless explicitly mentioned otherwise, this thesis uses the terms *test* and *DFT* as applied to digital components of an SoC design.

Section 1.1 of this chapter outlines the current test strategies. Section 1.2 motivates and presents the research goals of this thesis. Section 1.3 outlines the contribution of this thesis in terms of its original and novel work. Finally, Section 1.4 provides the organization of the rest of this thesis.

#### **1.1 Current Test Strategies**

There are two distinctive testing strategies for digital circuits: external testing of a chip using *automatic test equipment* (ATE); and embedded self-testing in the form of logic *Built-in Self-Test* (BIST).

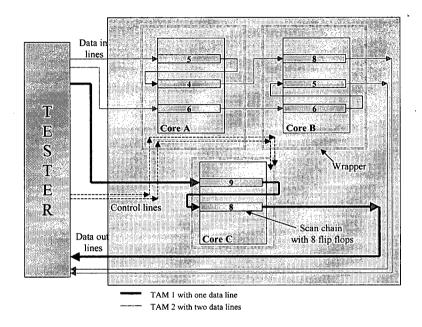

In ATE-based testing, *automatic test pattern generation* (ATPG) tools are used to create deterministic test vector sets. Using the ATPG test vector sets, the ATE applies the test stimuli to the CUT and collects the test results to compare them with the expected values. Effectively, in the ATE-based testing strategy, the communication and the application of test data are closely coupled. In other words, the ATE acts as both a test source and a sink and it is assumed that the tester establishes a data path between itself and a core such that the tester has direct control of features of the core's DFT. Using this data path, the tester applies the test data to the core before it collects and observes the results. Figure 1-1 shows an example of a simplified test arrangement with six data lines

-also referred to as *test access mechanism* (TAM)- and two control lines. In Figure 1-1, the data lines are grouped into two TAMs such that the tester can have direct control of the scan chains of each core, while minimising test time.

Figure 1-1: An example of a simplified SoC test architecture.

In contrast to ATE-based testing strategy, typical logic BIST techniques rely on pseudo-random test patterns. In a typical BIST arrangement, embedded blocks generate the test stimuli and apply them to the CUT. Test results are compacted into signatures and these signatures are compared to the expected ones. In effect, the BIST strategy can be considered as the opposite of the ATE-based strategy, as both the source and the sink of the test architecture are on-chip.

#### **1.2 Research Goals**

#### 1.2.1 Embedded Deterministic Scan-based Testing

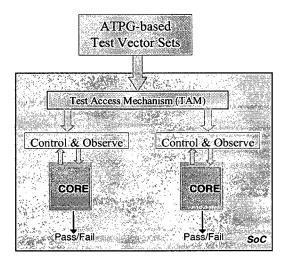

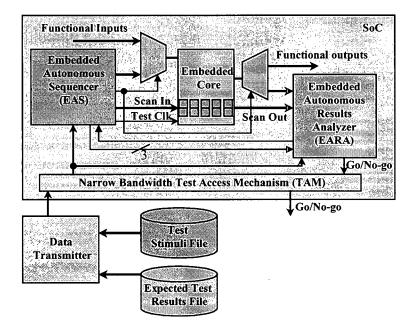

One goal of this thesis is the development of a new methodology for embedded deterministic testing of digital cores in SoC designs. In this thesis, this novel method is referred to as *dedicated autonomous scan-based testing* (DAST). With DAST, the goal is to leverage the potentials of logic BIST in SoC test, without paying the potential penalties of BIST. To that end, the DAST methodology uses embedded test resources that use ATPG test stimuli and expected results, as illustrated in Figure 1-2. Effectively, in the DAST methodology, DFT-tester resources are partitioned, keeping the ATPG test vector sets off-chip while embedding the control and the observation functions at the cores. As such, DAST is a novel embedded deterministic testing infrastructure, where both the test stimuli and the expected test results of the ATPG test vectors are used for on-chip ATPG-grade testing. In the unique methodology of DAST, the embedded resources require the communication of ATPG-based test stimuli and expected results through global interconnects that act as a communication link. This communication link can be any generic TAM or the novel on-chip network-oriented switching fabric developed in this thesis as outlined in Section 1.2.2.

Figure 1-2: DAST concept.

The partitioning of the test resources in DAST lowers DFT-testers cost. This, in turn, reduces total production costs. However, unlike conventional BIST, the partitioning of the test resources in DAST does not require any changes to embedded cores and only requires minimal modification of the ATPG test flow. In this way, DAST results in flexible and modular test architectures that facilitate the reuse of test resources and achieving a highly productive test scheme.

DAST benefits from the advantages of both the BIST and the ATPG-based testing as, with DAST, ATPG test vector sets are used alongside embedded blocks. Hence, DAST enables testing to be performed at-speed and deterministically, ensuring high test quality with minimal test time. Moreover, contrary to the BIST methodology, the diagnostic information in DAST is not lost, as no compaction is implemented in the form of a signature. Owing to the fact that both the test stimuli and the test results are sent to the cores, DAST, theoretically, achieves an ideal multi-site testing strategy for ATPG-based testing. Hence, given unlimited power for the external test resources, a tester, with a limited number of test channels that are equal to the number of the test pins of one chip, can test an unlimited number of chips in parallel. This ideal case is achieved as the same data set is sent to all chips, enabling sharing of test channels between all the chips.

#### 1.2.2 Test Network-on-Chip

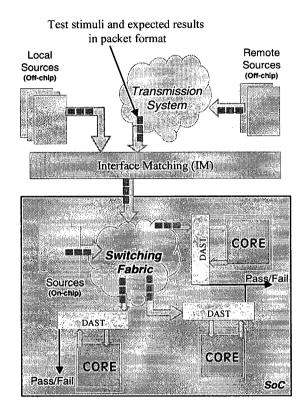

As a second objective, this thesis proposes and develops the architecture of a novel onchip test network. In this thesis, this architecture is referred to as a *Network-oriented*, *Indirect and Modular test Architecture* (NIMA). In NIMA, the tester is assumed to lack direct control over a core's DFT and is de-coupled from the TAM, and the core and its wrapper. This de-coupling facilitates partitioning of an external tester into its external and embedded components, and enhances the modularity and scalability of the test architecture. In addition, NIMA presents the concept of a highly hierarchical, modular, and flexible test architecture that can address high-productivity requirements of testing SoC designs and, ultimately, help in lowering test cost. Figure 1-3 illustrates combined NIMA and DAST concepts as a block diagram.

In NIMA, test data, comprised of test stimuli and test results, is formatted into a new protocol and augmented with control bits. In this way, control lines are eliminated in NIMA and the TAM is only comprised of test signal lines that communicate both the test

data and the control bits. Hence, using NIMA, the effective test time is reduced, as the TAM lines are used more efficiently.

Figure 1-3: Combined NIMA and DAST concepts.

The reformatted test data and the control bits in NIMA are then encapsulated into packets such that the test data can be forwarded to its core autonomously. This autonomous behaviour of the NIMA architecture serves well in automating test cycles, a requirement of high-productive test. Moreover, as no interaction from the tester is required in this step, a low-cost test template is achieved.

Finally, at a core, embedded autonomous blocks decode NIMA's packets and retrieve the test data. These embedded blocks apply the test stimuli to the core and compare the responses with expected results, identifying any error. This process can be handled using the DAST approach. In using autonomous embedded blocks, NIMA achieves the main requirements of SoC testing. More specifically, NIMA serves as a methodology that enables high quality at-speed testing.

Moreover, an important system-level design challenge identified in [4] is due to *system complexity*. It is predicted that this challenge will lead to forcing a focus on communication rather than computation in the next ten years. It is stated in [4] that:

"At 65 nm and below, communication architectures and protocols for on-chip functional processing units will require significant change from today's approaches. As it becomes impossible to move signals across a large die within one clock cycle or in a power-effective manner, or to run control and dataflow processes at the same clock rate, the likely result is a shift to asynchronous (or, globally asynchronous and locally synchronous (GALS)) design style. In such a regime, islands of self-timed functionality communicate via network-oriented protocols." Therefore, an underlying assumption of this thesis is that future SoC designs will include a switching fabric coupled with network-oriented protocols, for core interconnect. Hence, this thesis proposes the first methodology and test architecture that enables the reuse of such a fabric for testing cores.

Evidently, the concept of having a *network-on-chip* (NoC) that uses network-centric protocols and a switching fabric for data communication on a chip is very new. Most relevant works are geared towards the problem of core interconnection [5][6][7][8]. The motivations for many of these works are the non-scalability of global wire delays and their effect on global synchronization, the degradation of bus electrical performance with every attached unit, and the need for special error control mechanisms because of the unreliable transmission medium. Based on the open literature, no work on the subject of test architectures that use network-oriented approaches has been reported to date, with the possible exception of [9] and [10]. Reference [9] studies the impact of reusing an NoC for testing core-based systems, and reports the results of such reuse on test time based on two proposed scheduling mechanisms. When reusing an NoC, the work in [10] studies the effect of power consumption on the test time and test scheduling. Hence, the studies in [9] and [10] focus on the general concept of test data packetization and its impact on test time, and they do not address the methodology and the implementation of the test architecture required for NoC reuse. Therefore, this thesis is the first to propose, develop, and empirically validate the methodology and implementation of a test network on-chip that can use its unique switching fabric or reuse other networks on-chip as they become available.

#### **1.3 Contributions**

In short, the principal contributions of this thesis are listed here.

- The DAST methodology of Chapter 3 is developed as a novel on-chip deterministic tester. In addition, DAST is developed such that it partitions the functionality of external testers into two distinctive operations of *data delivery* and *control/observation*. This partitioning enables embedding of the latter functionality at cores of an SoC design.

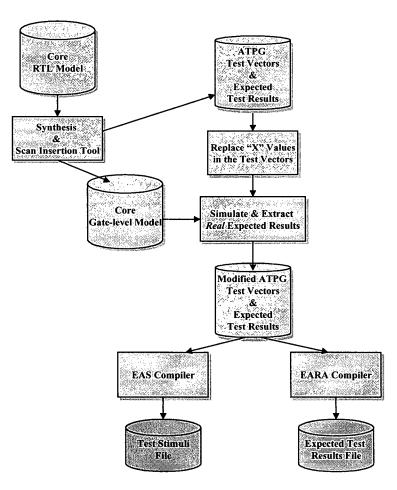

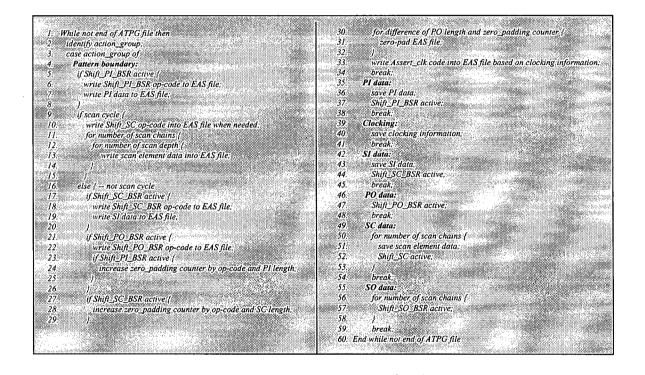

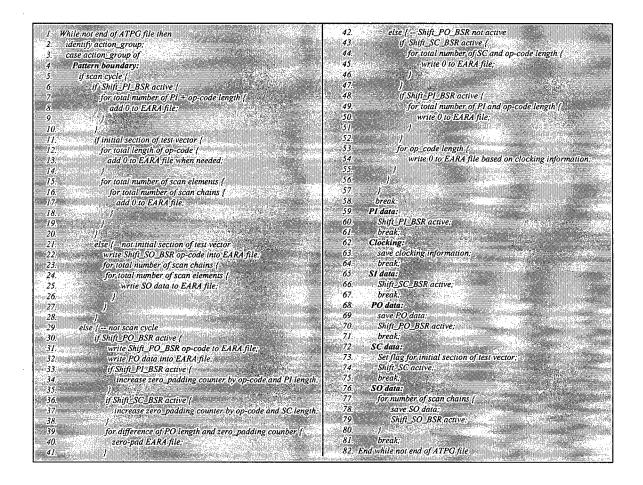

- The algorithms of Section 3.4.1 are developed to enable the full use of ATPG in the embedded testing methodology of DAST. The use of ATPG results in deterministic high-quality embedded testing in DAST, and the algorithms of Section 3.4.1 can be integrated into the design flow of a core to enhance its productivity.

- An efficient and simple implementation of DAST hardware is presented in Section 3.4.2. This implementation enables automatic and flexible DAST hardware development, as it uses hardware description language with generic parameters that can be set for any cores. Moreover, the implementation avoids design iterations, as it only requires the interface information of cores and does not alter cores or their functionality.

- DAST is characterized in terms of its test time models and these models are presented in Section 3.5.

- A novel on-chip test network is proposed and developed in Chapter 4. NIMA methodology of Chapter 4 is developed to enable a hierarchical systematic test architecture that can reuse an on-chip switching fabric with network-oriented protocols.

- NIMA is developed as a 3-layer communication network to enable modularity and scalability of test architectures. In this way, the design of NIMA facilitates test resource partitioning.

- A novel dynamic addressing mechanism to simplify the design of NIMA's network layer is presented in Section 4.4.3.

- A simple and efficient implementation of NIMA network layer is presented in Section 4.6.2, while DAST implementation is altered to work as the application layer of NIMA. To facilitate NIMA flexibility and the automation of the integration of NIMA in an SoC design flow, this implementation uses a hardware description language and generic values for different parameters of NIMA's design.

- NIMA is characterized in terms of its test time models of Section 4.7.2.

- The methodologies of NIMA and DAST are empirically validated to fit into a typical ASIC design flow, and NIMA and DAST are implemented on silicon. This

validation supports the fact that these methodologies can easily be integrated in a design flow.

#### **1.4 Thesis Organization**

Chapter 2 of this thesis, after the introduction of the SoC design methodology, reviews the test challenges in SoC designs. It then discusses the test trends and solutions in addressing these test challenges. Finally, Chapter 2 reviews the current test architectures in detail.

Chapter 3 reviews the concept of scan-based testing and identifies the components of scan-based testing, i.e., *data delivery* and *control/observation*. Chapter 3 then presents the concept of DAST in detail, provides the design flow, and presents an implementation for DAST. It also presents the experimental results when applying the DAST methodology to a number of benchmark circuits.

In Chapter 4, further motivation for NIMA is presented. Chapter 4 also provides NIMA's concept and architecture, and suggests an implementation of NIMA where DAST is integrated into the architecture. It also presents the experimental results of using the NIMA methodology in a number of benchmark circuits.

Finally, Chapter 5 concludes the thesis by summarizing the results and thesis contributions and provides direction for future work.

# Chapter 2 Background and Motivations

This Chapter reviews the background and outlines the test challenges in SoC designs. The required test trends to address SoC test challenges are then discussed. Finally, current test architectures are reviewed and the research work of this thesis is motivated.

#### 2.1 System-on-Chip Design Methodology

Table 2-1, an extract from [4], compares the number of transistors on a chip in the year 2001 to that predicted for the year 2016.

| Year                                                                                              | 2001 | 2016   |

|---------------------------------------------------------------------------------------------------|------|--------|

| High-volume Microprocessors<br>Functions per chip at introduction (Million Transistors)           | 193  | 6,184  |

| Application Specific ICs (ASIC)<br>Maximum functions per chip at production (Million Transistors) |      | 16,326 |

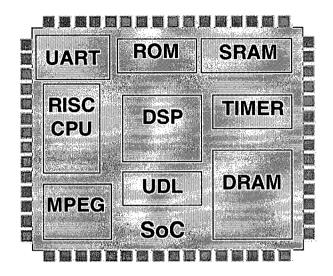

Using the large number of transistors available on a chip, designers have already managed to place an entire electronic system on a single chip. These are referred to as *systems-on-chip* or *system chips* for short. An example of an SoC is illustrated in Figure 2-1, where different embedded functional blocks (or embedded cores) of the system are conceptually shown [11]. As the number of the transistors increases, more complex systems, utilising hundreds of embedded cores, will be placed on a single chip. Apart from the availability of large transistor counts, there are other reasons behind this trend. One important reason is the market demand for portable products with increasing functionality [11][12], and another important reason is the need for a lower product cost [11][13].

Figure 2-1: Example of a System-on-Chip [11].

The justification behind the first reason is that SoC designs are faster, more reliable, and require less power per function compared to systems on a board. This holds true as most of the communication is on-chip and, hence, there is no need for large and power-hungry drivers at the chip terminals [14]. In addition, the smaller footprint is more suitable for portable, low-weight, and low-cost products.

The rationale behind the comparatively lower cost of products using SoC chips is the fact that smaller and more compact products require fewer packages. Products with fewer packages, when compared to those with more packages, amount to comparatively simpler design process and integration. Hence, the overall product cost can be reduced significantly. In addition, simpler design process result in faster introduction of the product into the market and, hence, will generate more profit.

#### 2.2 Reuse Paradigm

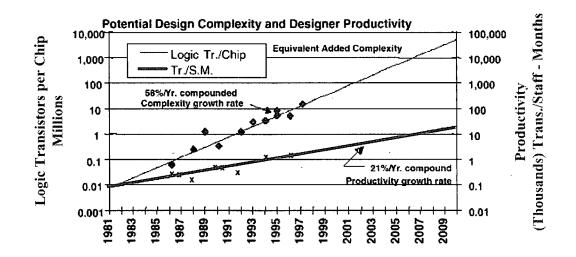

Figure 2-2, adopted from [15], illustrates potential design complexity and designer productivity. In Figure 2-2, the horizontal axis represents the year and the left hand side vertical axis shows the number of logic transistors per chip in million units. In addition, in Figure 2-2, the vertical axis on the right hand side represent a measure of designer productivity in the form of the number of thousand transistors each designer can design and verify per month in his/her designs. According to Figure 2-2, designers' productivity growth rate is equal to 21% each year. However, the number of logic transistors per chip follows Moore's law and increases at a rate of 58%. Owing to these different rates of growth, the gap between the productivity of designers and the number of available transistors is widening very rapidly.

Figure 2-2: Potential design complexity and designer productivity [15].

It is becoming increasingly difficult to utilise all the transistors available on the chip effectively and still meet the time-to-market constraints. Nowadays, the very short life cycle of products compounds the problem further, as demand for a product might diminish before designers have a chance to introduce their version of the product [15][16][17][18].

To overcome the productivity gap and meet the stringent time-to-market constraints, it is not enough to put more manpower on the job. In fact, by virtue of the law of diminishing return, it is not economical. Hence, the only viable solution put forward so far is for designers to *reuse* in-house or externally acquired pre-designed/verified *intellectual properties* (IP) as embedded *cores* in SoC designs [4][12][13][17][18][19][20]. Effectively, SoC designs need to be *application-specific integrated circuits* (ASIC) that maximize reuse of IPs to improve design productivity.

The concept of reuse is not new to the semiconductor industry. In the typical design flow of systems-on-board, pre-fabricated ICs are reused. However, the difference in the case of SoC design methodology is the fact that cores to be used in SoC designs are not fabricated before they are used. Instead, cores in SoC design methodology come in some form of hardware description. Based on the method of their hardware description, there are three main categories for cores, i.e., *soft, firm*, and *hard* cores [18]. *Soft* cores are those functional blocks that are described in any synthesizable hardware description language such as VHDL or Verilog. *Firm* cores are typically gate-level descriptions that are targeted for a specific fabrication technology and can be optimized for speed, area, power, etc. Finally, *hard* cores use the least flexible description method, and are the layout description –usually in a standard industry format such as GDSII– of optimized *firm* cores.

#### 2.3 Test Challenges

In order to satisfy the reliability requirements of fabricated ICs, it is imperative to test these chips before they are shipped out to potential customers. However, there are many challenges in testing SoC chips, and many experts believe that testing SoC chips will be the bottleneck of future designs, if issues of DFT for SoCs are not addressed [4][21][22][23]. These challenges are the result of both the SoC design methodology itself [4][20][21][24][25][26], and the *deep sub-micron* (DSM) technology used to fabricate SoC chips [24][27][28][29]. This section summarizes these challenges.

#### 2.3.1 Test Challenges in DSM Technology

The DSM fabrication process, shrinking chip geometries, the continuity of Moore's law, aggressive time-to-market and time-to-volume requirements, and finally, the need for lower total cost are all contributing to the test challenges in the DSM era. Based on different test requirements, some of the important test issues due to the DSM technology can be categorized into the following five groups [4][27][28][29][30].

#### High-quality Test

Very high-quality test, which achieves high fault coverage, is essential in manufacturing highly reliable chips. To guarantee high fault coverage, in addition to the stuck-at-fault

models, new fault models are needed to facilitate the detection of static and dynamic defects in the DSM fabrication processes [4][29][30]. Therefore, at-speed testing, using transition and path delay fault models in conjunction with scan chain(s), is becoming a requirement of chip testing [31]. However, in many cases, the performance of external testers lags behind the performance of chips they intend to test. In particular, external testers cannot operate at the high frequency required for at-speed testing of many CUTs and have insufficient accuracy for pin-to-pin timing requirements [31]. Hence, these testers lack the necessary accuracy and resources to handle at-speed testing and other new fault models. Therefore, new DFT methodologies and testing techniques are needed to facilitate at-speed testing. In addition, these new DFT methodologies and testing techniques and testing techniques should maintain the high quality of test and be able to use a variety of fault models.

#### Low-cost Test

With almost exponential reduction trend in ICs fabrication cost, chips test cost will soon equal that of their fabrication, if new test and DFT methods are not devised [4]. Today's monolithic testers are not designed to take advantage of the DFT used within a chip. Moreover, the design of these testers is such that they are able to perform a variety of different tests and support a broad range of ICs [27]. However, this amounts to very expensive testers with features that may not be needed or used for many CUTs or test insertions. It also results in the requirement of a large capital investment by companies for purchasing these multi-purpose testers. In addition, owing to the rapid advancement of ICs, this large capital investment will be outdated within a few years, adding to the test cost. Thus, an important challenge facing the test community is finding solutions to reduce test cost through new DFT techniques, redesign of testers towards low-cost, reduced-functionality testers, and design of DFT-aware testers that take advantage of CUT DFT infrastructure.

#### Low-volume Test Data

To maintain high fault coverage, for complex designs, a larger test data volume is inevitable. In turn, larger test data sets require more memory in testers. In addition, with larger test data sets and limited number of tester channels, test time will increase. These problems are exacerbated by the slower rate of increase in the number of a chip's primary input/output (I/O) pins when compared to that of the number of transistors on a chip. Therefore, reduction in the test data volume to lower test time by either reducing the test data set or increasing the effective bandwidth is a problem in need of solution. Note that, using low-cost testers can mitigate the problems associated with test data volume as, in these cases, test time contribution to the overall cost is reduced.

## High-productivity Test

To lower the cost and keep the time-to-market and the time-to-volume of products to their minimum, the DFT insertion, the test program development, and the test process should be hierarchical and automated as much as possible [29]. Hence, DFT techniques and test resources need to be modular and flexible to facilitate hierarchical and automated

test flow. Moreover, DFT circuitry should be seamless with the normal design flow and, thus, the DFT insertion process must avoid design iteration.

#### Test for Diagnosis

Yield improvements of new chips are essential in lowering production costs and achieving the time-to-volume [32]. Diagnostic information helps in the rapid yield ramp up. Thus, the test flow needs to include fault diagnosis as one of its objectives in order to avoid expensive off-line and special diagnosis testing processes. To this end, test resources and DFT techniques are needed to facilitate real-time yield analysis [28].

## 2.3.2 Test Challenges in SoC

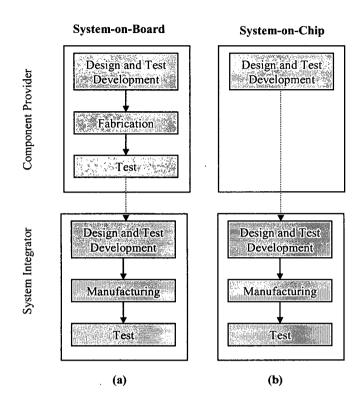

The *IP*- or *core-based* design methodology is creating a new style of design with its own characteristics, requirements, benefits, and challenges. One particular challenge is how to test these core-based systems. Testing of SoC designs differs from system-on-board testing. Figure 2-3, adopted from [21], illustrates the differences in the design development and the test flow between systems-on-chip and systems-on-board. In a system-on-board, each component is designed, verified, fabricated, and finally tested. The system integrator uses these tested components, and performs testing of the board and the system with the assumption that the components are fault-free. However, as illustrated in Figure 2-3, in the SoC design methodology, cores are designed and verified, but are not pre-fabricated. Hence, these cores cannot be tested before their integration into the SoC. Therefore, the system integrator is responsible for all post-manufacturing tests of both the cores and the system that uses these cores.

.

Figure 2-3: Design development and test flow for (a) System-on-Board, and (b) System-on-Chip [21].

The different test flows as explained above and illustrated in Figure 2-3, as well as having embedded cores with limited accessibility, result in unique challenges in SoC test. Moreover, stringent time-to-market and time-to-volume requirements, and the need for lower total cost also contribute to SoC test challenges. These challenges can be summarised as follows:

- Effective communication mechanisms for the test flow between different parties in the design of the SoC (note that the design of an SoC can span multiple groups in different companies which can be located in many different geographical locations);

- Accessibility of embedded cores from the primary input/output (I/O) of the chip;

- Testing different types of cores with compatible methodologies;

- Testing the user-defined logic (UDL) and the interconnects;

- Seamless integration of cores' DFT into the system DFT (modularity of the system test architecture);

- Having a test architecture allowing new cores to be integrated into the chip without incurring core design changes (scalability of the system test architecture);

- Designing the system DFT such that the chip will be reusable hierarchically (scalability of the system architecture).

## 2.4 SoC Test Trends

Test challenges as discussed in Section 2.3 call for new and advanced test methodologies for core-based SoCs. A few of the most important test trends that, according to the literature, help in addressing some or all of the challenges described in Section 2.3, are outlined in this section.

#### 2.4.1 Test Reuse

The integration of IP blocks into an SoC results in a non-linear complexity growth for DFT and manufacturing test [4]. Hence, it is costly and inefficient to assign the design of embedded core DFTs and generation of test vectors to the system designer. It, however, is more practical to reuse pre-designed DFT schemes of the cores and their test vectors [4][18][21][24][25][33][34]. Core-based design with reuse methodology requires a new business model. In this new model, *core-providers* design and develop the IPs and *core-users* integrate them in an SoC environment. Hence, *core-providers* are responsible for the DFT techniques used in the core as well as being responsible for providing all the information to *core-users*. In this modular model, *core-users* treat individual core test programs as distinct components and integrate/schedule these components into a system test program with limited knowledge of the core's internal detail [21]. Separation of the tasks between *core-providers* and *core-users* introduces new challenges in the entire design flow. Hence, modularity and scalability of the test architecture are deemed essential to enhance the rapid development of designs and to avoid costly iterations between core-providers and core-users.

#### 2.4.2 Systematic Test Architecture

To address core-based SoC testing challenges and enable test access to embedded cores, a more structured, systematic, and hierarchical approach than the traditional DFT is required [4]. Zorian *et al.* [21] proposed a generic test architecture consisting of three

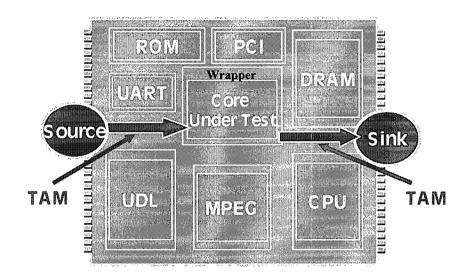

components: *Source/Sink*; *Wrapper*; and *Test Access Mechanism* (TAM). Figure 2-4 illustrates this generic conceptual test architecture.

Figure 2-4: A generic conceptual test architecture [21].

In the model of Figure 2-4, the *source* applies the test stimuli to the core under test and the *sink* collects and performs an analysis of the test results with expected responses. In other words, the source *stores* and *controls* whereas the sink *stores* and *observes* in the process of testing a core. Independently, the source and the sink can either be on- or off-chip.

In addition, in the model of Figure 2-4, the TAM is the physical mechanism that connects the source and the sink with the core for communicating test data and control signals. TAM design determines how efficiently information is received and transmitted from and to the outside world, and thus it affects, in part, the total test time, the complexity of test flow, and the test cost in general. Finally, the test wrapper is a shell around a core, which provides an interface between the core and its surroundings, isolates the core for test purposes, and helps in testing the interconnects. The wrapper is intended to enable "plug-and-play" cores such that cores, acquired from different providers, can be integrated into an SoC without any modifications.

As part of a wide variety of methods in addressing SoC test challenges, new *control* and *observation* mechanisms are required in SoC test [4]. Moreover, to facilitate a hierarchical test architecture, it is proposed that the test architecture needs to be separated from its behaviour [4]. In other words, it is proposed that the separation of the computation from the communication components of a test architecture is essential to address SoC test challenges. Finally, unification of the design and the test architecture flow is believed to be inevitable in SoC designs.

## 2.4.3 Test Resources Partitioning

With the growing complexity of ICs, more features have historically been added to external testers. This trend has transformed *automatic test equipment* (ATE) into expensive monolithic testers that conform to the idea of *one-solution-fits-all* [28][30]. In addition, many existing ATE are not designed to leverage the DFT features of the chips they test. DFT-aware testers are considered an important cost reduction factor in SoC test. In addition, the partitioning of ATE resources is emerging as an important solution to address test challenges in SoC. In this new model, the functionality of testers is broken

into different segments and distributed between different resources. For example, testing digital components, memory, and analog blocks of an SoC are performed in different ways and with different resources.

Trade-offs of test resource partitioning and features of low-cost testers are still the subject of debate and extensive research. However, it has been argued and shown that this division helps in creating much needed hierarchy, modularity, flexibility, and scalability in the test flow and the test resources, and ultimately, it helps to achieve higher test quality and reduce test cost [27][28][30][35][36]. As an example, it is known that almost every chip has *phase locked loop* (PLL) circuits for its clocking circuitry. Migrating clocking circuitry of ATE to chips and reusing on-chip PLL not only reduces ATE cost but also enables at-speed testing. As another example, reference [28] presents an economic study of using testers with reduced features in the test flow. In this study, the benefits of using lower cost testers in the early stages of the test flow is compared with the penalties of escaping certain defects due to the lower capabilities of these low-cost and reduced-feature testers. It is shown in [28] that, even in extreme cases, using low-cost testers results in a lower overall chip cost.

#### 2.4.4 Multi-site Testing

Multi-site testing, or parallel testing, refers to concurrent testing of multiple similar chips on a single tester. Multi-site testing reduces overall test time and test cost. However, with the current ATE architecture, pin densities on the testers cannot easily increase to enable multi-site testing. One solution is to reduce tester pin functionality, enabling more pins per tester [28][35]. This solution is the direct outcome of the test resource partitioning as described in Section 2.4.3. Therefore, multi-site testing is one of the main driving forces behind low-cost, low-feature, and DFT-aware testers [28].

In addition, new DFT methodologies are required to achieve higher degrees of parallelism in testing. These methodologies should significantly reduce the number of required test pins per IC, and, hence, increase the number of ICs that can be tested on a tester.

Another way to achieve testing parallelism in SoC designs is to simultaneously test multiple cores using new DFT techniques [37]. However, one limiting factor in such a solution is the power rating of the IC under test. This rating may limit the number of cores that can be tested concurrently and, hence, limit the effectiveness of the solution.

#### 2.4.5 Test Data Compression

Compressing the test data is a clear way to address some of the challenges detailed in Section 2.3. There are many techniques in this domain [38][39][40][41][42][43]. The majority of them target *Built-in Self-Test* (BIST) as the primary method of the IC test. However, there are newer published techniques that use *automatic test pattern generation* (ATPG) test data sets alongside embedded blocks [44][45][46].

## 2.4.6 Embedded Testing

One important challenge for testing core-based SoC designs is accessing embedded cores from the system's primary inputs/outputs (I/O). This accessing proves challenging owing

to the limited number of primary I/O pins. According to the ITRS prediction, the maximum number of pins on the chips is to increase from about 3,070 in the year 2001 to 4,420 by the year 2016 [4]. However, the ratio of power/ground pins to the total pins on the chip can typically vary between 2:3 and 1:2 [4]. Moreover, with more complex IPs, there will be more test pins on each core. Hence, the combined effect is a shortage of available pins for testing in future chips. Multiplexing signal and test pins can mitigate this problem. However, increasingly there are high-speed signal pins on a chip that cannot be shared and, hence, the shortage of test pins to access embedded cores will still be a problem needing to be addressed.

In addition, testing core-based SoCs requires a level of complexity that makes relying on external *automatic test equipment* (ATE) insufficient [4]. As previously mentioned, the cost of ATE rises as the complexity of ICs increase. Moreover, ATEs can quickly become outdated compared to the chips that they test, and, for example, often lack the necessary resolution and accuracy to test new devices effectively and perform at-speed testing of these devices [4][23].

The limited number of chip I/Os, high tester cost, the need for at-speed testing, and the typically lagging technology of external testers call for specialized embedded support infrastructure blocks, suited for embedded testing [4][23]. Test resources, hence, need to be partitioned into their internal and external components such that embedded test components take over some functionality of the external ATE resources [4][47]. These embedded solutions are referred to as *infrastructure IPs* (I-IP) [32][48]. I-IP blocks do

not add to the main functionality of the chip. Rather, they facilitate post fabrication test, and can enhance chip's lifetime reliability [49]. It is imperative that such embedded solutions perform deterministic tests, use the benefits of the *automatic test pattern generation* (ATPG), and work in harmony with their specialized off-chip counterparts [4][29][44][50].

#### **2.5 Current Test Architectures**

This section overviews current test architectures. Section 2.5.1 reviews the standard wrapper being developed by the IEEE P1500 Working Group. Section 2.5.2 describes the general concept of *Built-in Self-Test* (BIST) architectures. Finally, Section 2.5.3 provides a comprehensive survey of other test architectures where external test equipment is used as the test *source* and the test *sink*.

## 2.5.1 Standard Wrapper

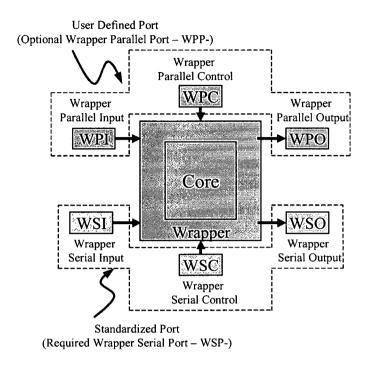

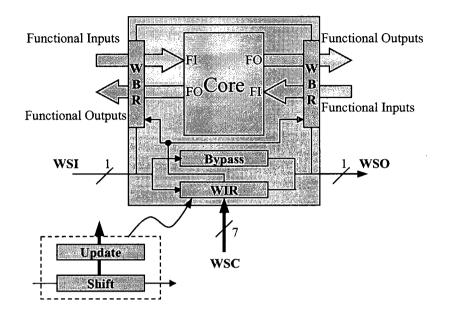

The IEEE P1500 Working Group is working towards a *Standard for Embedded Core Test* (SECT), to allow the automatic identification and configuration of testability features in integrated circuits containing embedded cores [51]. Towards that end, the P1500 aims at standardising a scalable architecture in the form of a wrapper around a core and defines a *Core Test Language* (CTL). However, other components of the test architecture, i.e., source, sink, and TAM will not be standardized. The scalable architecture, as illustrated in Figure 2-5, will provide a mandatory serial port and an optional parallel interface for testing a core.

Figure 2-5: Block level overview of a P1500 wrapper [51].

In addition, the standard will provide a set of instructions enabling different modes, mandatory and optional, for the wrapper architecture. These instructions will be loaded into a *wrapper instruction register* (WIR) and control *wrapper boundary registers* (WBR) in front of the core's functional input/outputs. Figure 2-6 illustrates a conceptual view of the required P1500 wrapper architecture [51]. A *core-provider* will use the standard language to communicate to the *core-user* the internal, external, and pattern information for every test mode of a core. A *core-user*, however, is responsible for designing the source, sink, TAM, and the overall system DFT.

Figure 2-6: Conceptual view of the required P1500 wrapper architecture [51].

## 2.5.2 Built-in Self Test

Embedded testing architectures in the form of Built-in Self-Test (BIST) have been used to reduce test cost [2][52][53][54][55]. BIST facilitates in-field and at-speed testing and, hence, improves the quality of test. Moreover, BIST lowers the test cost by partitioning the test resources as outlined in Section 2.4.3. Memory BIST is now widely used to test the memory components of ICs. Moreover, using analog BIST results in reducedfunction and low-cost external testers, and can potentially achieve better test quality. Finally, logic BIST is gaining more interest as a solution that can address many of the test challenges explained in Section 2.3. This thesis uses BIST to refer to logic BIST, as the focus of this thesis's work is the development of new and novel DFT techniques for digital cores of SoC designs.

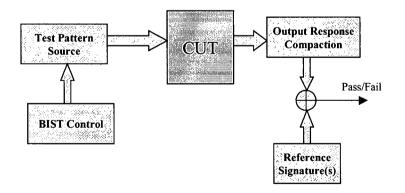

A block diagram of a typical BIST arrangement is illustrated in Figure 2-7. In a typical BIST arrangement, test patterns are either stored or generated on chip and are local to the CUT. These patterns are applied to the CUT under the control of a BIST controller. The outputs of the CUT are compacted during the entire process of test data application. Finally, the compacted output response is compared to reference signatures at the end of the test process, and a *pass/fail* signal is generated. The dominant technique in logic BIST is based on the STUMPS architecture [38][56], which uses multiple scan chains as the underlying DFT technique in the CUT (for an introduction to scan chains, see Section 3.2). Hence, this thesis assumes the use of scan chains in BIST.

Figure 2-7: Block diagram of a typical BIST arrangement.

BIST can simplify the integration of a core's DFT into a system DFT in SoC designs and, hence, enable near-seamless reuse of test resources. In these techniques, both the test source and the sink are local to the CUT and, thus, the TAM amounts to local wires between BIST circuitry and the core. This local communication model simplifies the problem of test data transmission. However, on-chip storage of the entire deterministic test vectors, for each core, is not cost-effective or even practical in many cases.

To eliminate the need for on-chip storage of test data, typically, *linear feedback shift registers* (LFSR) are used to generate pseudo random patterns as the stimuli in the BIST arrangement. These test vectors are then applied to the CUT, and, in the simplest configuration of BIST, the test results are compacted and the final signature is compared to the signature of expected results. One problem with such pseudo-random pattern BIST is the potentially lower fault coverage, compared to that resulting from deterministic patterns obtained via *automatic test pattern generation* (ATPG). This lower fault coverage is mainly due to the linear dependency of the generated random patterns and the fact that some faults, such as path delay faults, are resistant to random patterns.

The potentially lower fault coverage associated with a BIST methodology can be mitigated, although not solved, in different ways. One method for smaller circuits is the introduction of a *phase shifter* between the LFSR and the CUT's scan chains[56]. This phase shifter reduces the dependency of the bits applied to the scan chains. Another method consists of inserting additional test points in the design [2][57][58]. However, test point insertion requires modification of the design and is therefore not desirable.

In BIST, phase shifters and test points cannot typically guarantee the same high fault coverage achievable using ATPG-based vectors. Other techniques have been proposed that target the pseudo-random pattern generator to mitigate the problem of low coverage [38]. These techniques include: weighted pseudo-random sequences [59] and multiple-polynomial LFSR with reseeding [60]. However, the complexity and cost factor of these solutions can be high and not desirable in many cases.

Another strategy to address the potential low fault coverage in BIST is known as mixed-mode BIST. Mixed-mode BIST uses deterministic test vectors as well as pseudo-random vectors [61]. As one example, the fault coverage can be increased by applying top-up test vectors from an external tester. However, it has been shown that for large industrial designs, the ATPG top-up pattern volume is 25-65% of a full ATPG test approach [62]. In another study, this ratio is reported as high as 70% [63]. This large ratio defeats many reasons for using BIST, and is not acceptable in many cases. Other techniques in mixed-mode BIST include: bit-flipping [64], bit-fixing [65], weighted random pattern generation [66], and *Sequence Generating Logic* [67]. In this latter work, no external deterministic pattern is applied. Rather, a block is placed between the LFSR and the CUT that changes the output of the LFSR into deterministic patterns. The potential problem with these techniques is the large area required for the BIST circuit. Reference [67] reports BIST hardware equal to about 5-15% of the total CUT area, for circuits of up to 100K gates that use 10,000 test patterns. It is, however, possible to

trade-off test quality, test time, and BIST area overhead [67], if lower test quality or longer test time is acceptable.

Compacting test responses and using a signature analyzer at the output of the CUT, result in additional challenges of BIST techniques. Diagnostics in BIST is more difficult than ATE-based testing as, in BIST, most of the information needed for diagnosis is lost during compaction of the test results into signatures. Therefore, diagnosis is only possible with multiple test runs that add to the test time and the complexity of the test process. Moreover, using signature analyzer compaction schemes. Another problem with signature analyzers, and consequently in BIST, is the "zero-ing out", where the history of the circuit response is lost [2].

Another drawback with logic BIST techniques is in their very long test time requirement. In ATPG-based testing, the test vectors are generated and then compacted to be as few as possible. Moreover, the CUT's output response is compared with the expected response for each test vector, resulting in shorter test time for faulty chips. However, in BIST, owing to the random nature of the entire test vector set –or at least the initial set of test vectors in the more elaborate versions of BIST–, a large number of test vectors is needed for achieving an equivalent level of fault coverage. In addition, the comparison with the expected reference signatures is only possible at the end of the test process or, at best, at the end of intermediate sections of the test process [68][69]. Hence, the result of the test is only available after application of multiple test vectors in addition

to the vector that can identify a fault, resulting in even longer test time for faulty chips. The study in [62] shows that, typically, the test time is two to three times longer than the test time using ATPG.

Using pseudo-random patterns in BIST, results in additional challenges. These patterns can cause parts of the CUT to generate responses that are unpredictable ("X") in the BIST simulation, and no signature can be defined for these cases. It is imperative to prevent the propagation of these unknown ("X") values to the compaction circuit, as the signature will be corrupted otherwise. Moreover, it is necessary to prevent bus conflicts during the application of the pseudo-random patterns. Finally, BIST using pseudo-random patterns can cause a large power dissipation, as these patterns may result in large circuit switching [70][71].

As was presented in this section, logic BIST is a powerful test methodology that can address many problems facing the test community for testing core-bases SoCs. However, there are many challenges in the path of making logic BIST a viable test solution. These challenges were summarized in this section and some of the proposed improvements presented. Additional problems and challenges in BIST include: making the design BIST-ready; automating BIST insertion; and integrating BIST into the overall design flow with minimal impact [62]. This thesis, as explained in Section 1.2.1 and detailed in Chapter 3, builds on the strengths of BIST methodology, solves some of its potential shortcomings, and, hence, presents an alternative solution in addressing some of the different SoC test challenges described in Section 2.3.

## 2.5.3 ATE-based Test Architectures

ATE-based test architectures differ from BIST in the fact that both the source and the sink are an integral part of an external tester in the form of an ATE. This thesis uses the TAM arrangement in these architectures as a classifier. In SoC test architectures, test stimuli and test results are transported through the TAM. Hence, the TAM can be viewed as the communication link in the architecture. In addition to the TAM, extra control lines are used to properly set-up the TAM and core wrappers. Hence, there are two categories of lines in generic SoC test architectures: 1) data lines (referred to as TAM in this work) and 2) control lines.

Dedicated wires or existing functional interconnects can be used for the data lines [72][73][74][75]. While in [72], [73], and [74] the cores are modified such that each core has a *transparent* mode for testing, [75] uses the processor bus for test data transport. There are many proposed ATE-based test architectures in the literature. Based on the connection method between the chip pins and the core terminals, these can all be grouped into three main categories: multiplexer-, serial-, and bus-based connections. Most of these architectures suggest the use of a serial control mechanism to properly set-up the TAM and core wrappers.

In the first category, multiplexers are used to allow test access to the cores. The simplest method in this category is to multiplex the test pins to the primary I/Os such that a direct path is established during test [76]. A second method modifies the cores such that each core has a *transparent* mode for testing [72][73]. A recent third method

provides a transparent path based on modelling the TAM design as an *Integer Linear Programming* (ILP) problem, to minimise the overall test time and overhead area [74].

A number of test architectures in the serial-based category use the established IEEE 1149.1 standard [26][77][78]. Whetsel, in [79], uses a hierarchical structure by introducing a *Tap Link Module* (TLM). An improvement on the TLM is presented in [80], where the *Test Access Port* (TAP) of the 1149.1 standard is kept unchanged from its original form, and hence, simpler TLM controls are designed.

A number of different variations of the bus-based connection schemes have been reported. Varma *et al.* [33] suggest a structured architecture based on separate data and control buses. In their work, provision has also been made for using several such buses with different widths. To simplify the control mechanism in the TAM architecture and provide scalability of the architecture through hierarchy, a multilevel bus structure connected in a tree topology has been suggested [81]. Marinissen *et al.* suggested the TestRail architecture [22], where cores are connected in a daisy chain configuration and buses (or Rails) can have different widths, fan-in, and fan-out. In TestRail, each core can be bypassed if needed to access the next one in line and control is achieved via a serial connection.

In the busebased category, different methods are suggested for accessing the cores from the buses. *Core Access Switches* (CAS) select P signals out of N bits of a bus and use the TestRail topology for the buses [82]. Whetsel has suggested an addressable architecture in [83]. In this latter architecture, each core is given an addressable *Test Port*, which can

serially be assigned with its appropriate address to provide an intelligent distributed control mechanism for connecting cores to buses. Finally, a time division multiplexing technique has been suggested in [84]. In the latter, using configurable and dedicated arbiters, cores autonomously assume the control of the bus. Additional issues in the busbased connection scheme are the test architecture optimization and test scheduling. In order to minimize the test time and the number of required test pins for a given set of constraints, many studies have been reported that suggest different heuristics to optimally design test wrappers and assign the cores to the TAMs [85][86][87][88][89][90].

ATE-based test architectures benefit from a high test quality, as ATPG test vector sets are used. However, in the above test architectures, there is no distinction made between the communication and the application of test data. The close coupling between the communication and the application of test data works against many of the test trends detailed in Section 2.4. Therefore, novel test architectures are needed that, while utilising the quality of ATPG-based testing, conform to the test trends of Section 2.4 to a high degree. This thesis, as outlined in Section 1.2.2 and explained in Chapter 4, presents a methodology that helps in achieving systematic test architectures that benefit from test reuse, resources partitioning, and multi-site and embedded testing.

# Chapter 3 Dedicated Autonomous Scan-Based Testing

## **3.1 Introduction**

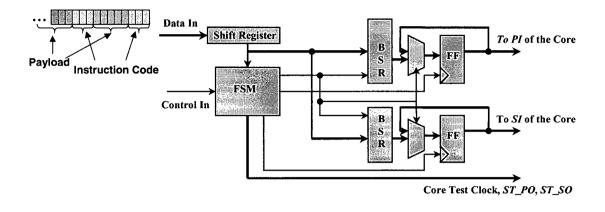

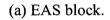

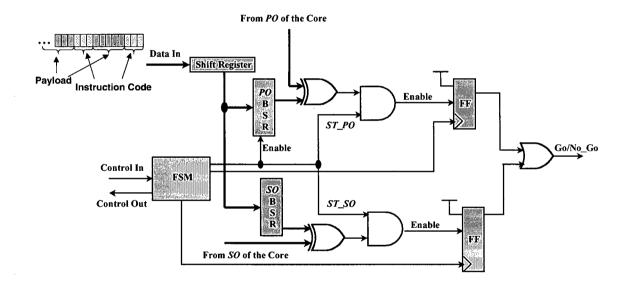

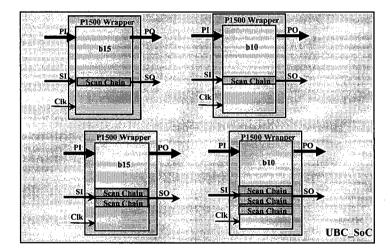

As discussed in Section 2.4.6, embedded testing is one of the most important trends in dealing with challenges of testing core-based SoC designs. Test resources need to be partitioned to move part of the tester's functionality onto a chip. This chapter presents the concept, and provides the implementation and experimental results of a *Dedicated Autonomous Scan-based Testing* (DAST) methodology [91][92], for testing embedded digital cores. The novelty in DAST is in the fact that core test stimuli and expected results, generated by ATPG, are pre-processed into a new test-data protocol. In doing so, all the control sequence of testing is transferred from the external ATE to a dedicated *Embedded Autonomous Sequencer* (EAS) block, associated with single or multiple cores

on an SoC. Moreover, *Embedded Autonomous Results Analyzer* (EARA) blocks [92] are used in synchronism with EAS blocks to deterministically analyze the test results and to compare them with expected results. Thus, using DAST, a simple data transmitter can be used in place of an external ATE. Hence, the complexity of the test flow can be significantly reduced and rendered much more scalable and portable between technology generations.

In essence, DAST divides the ATE functionality into its test data *communication* and test data *control/observation* components, and migrates the latter away from the ATE to place it on-chip at the periphery of the core in the EAS and EARA. Therefore, the former can be reduced to an inexpensive unintelligent block. Since DAST is based on the conventional scan/ATPG approach, it does not imply any compromise in terms of test-quality (coverage and fault models), ease of use, and broad applicability. Moreover, as the EAS and EARA blocks are external to a core, the impact on the design and the design flow is also minimal. Finally, as the test is performed on chip, at-speed test is feasible with minimal cost.

#### **3.2 Components of Scan-based Testing**

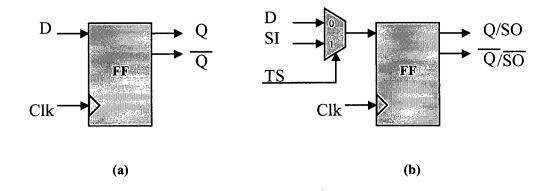

One of the most popular structural DFT techniques is scan design. Scan design increases internal circuit node controllability and observability of sequential circuits. In essence, scan design transforms the difficult task of sequential circuit test into the easier task of combinational circuit test. To achieve this transformation, regular D-type flip-flops in a sequential circuit, as shown in Figure 3-1a, are replaced with the scan flip-flops as shown

in Figure 3-1b. When the sequential circuit is in test mode, *Test Select* (*TS*) signals of the multiplexers are asserted to select the *Scan In* (*SI*) as the input of the scan flip-flops (*scan cells*). In this way, flip-flops are connected in long chains to form shift registers. Using the created shift registers, all the scan cells can be set to desired states in the test mode. Similarly, the state of the internal flip-flops and nodes can be captured by the scan registers and shifted out serially, thereby providing increased observability [2][3].

Figure 3-1: Block diagrams of (a) D-type flip-flop, and (b) Scan D-type flip-flop.

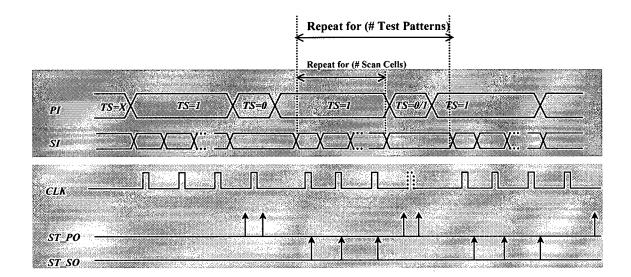

By nature, scan-based testing is a repetitive procedure. The steps in scan testing a core can be summarised by the generic waveforms in Figure 3-2. In Figure 3-2, the signal labels *PI*, *SI*, *CLK*, *ST\_PO*, and *ST\_SO* denote primary input values, scan input values, test clock, strobe primary outputs, and strobe scan outputs, respectively. In addition, *TS* represents the value of the test select signal.

Figure 3-2: Generic scan test waveforms.

From Figure 3-2, a scan test procedure can be conceptually divided into two functions: a) *data delivery*, and b) *control/observation*. For a given test pattern, *data delivery* refers to the following steps:

- Load the test vector into the scan chain flip-flops through the scan inputs (SI);

- Apply and maintain non-scan portions of the test vector at the primary inputs (*PI*) of a core;

- Set TS to logic 1 and apply new values to PI.

For the same given test pattern, *control/observation* refers to the following steps/actions:

• Assert *CLK* to load-in test vector in the scan chain;

- Assert *ST\_SO* to test for values at scan outputs (*SO*);

- Assert *ST\_PO* on two different occasions to check consistency at the primary outputs (*PO*).

In the traditional methodology, the ATE is responsible for transforming raw test vector data into scan sequence waveforms of Figure 3-2. This thesis, however, introduces a simple hierarchy whereby the complex ATE scan functionality is replaced by a simple off-chip test-data compiler. As described in Section 3.3, the compiler only needs to marginally transform (into a new protocol) the raw test data from ATPG, embedding the capability to generate the complex scan sequences in the dedicated EAS and EARA blocks associated with specific cores.

#### **3.3 DAST Concept**

External ATEs need to perform both functions of data delivery and control/observation. This is one of the reasons for increasingly expensive and complex test flows and equipment. Given today's ample resources in terms of silicon, this thesis takes advantage of the repetitive nature of scan testing by incorporating EAS and EARA blocks dedicated to each core on an SoC. The EAS's function is to accept simple binary test data and to transform it to produce the specific waveforms required for applying the scan pattern to the specific target core. The EARA's function is to work in synchrony with the EAS block and compare the incoming expected test results to the test results at the output of the core. This essentially amounts to separating the two functions of the off-chip ATE, as

described in Section 3.2, and moving the control and observation onto the chip. That is, DAST replaces a hierarchically flat system by one with a simple hierarchy.