# Cache and Branch Prediction Improvements for Advanced Computer Architecture

by

#### YUL CHU :

B.Sc., KwangWoon University, Korea, 1984. M.S.E.E., Washington State University, USA, 1995.

# A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### DOCTOR OF PHILOSOPHY

in

# THE FACULTY OF GRADUATE STUDIES

(Department of Electrical and Computer Engineering)

# We accept this thesis as conforming to the required standard

## THE UNIVERSITY OF BRITISH COLUMBIA

May 2001

© Yul Chu, 2001

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of <u>Electrical</u> and <u>Computer</u> Engineering

The University of British Columbia Vancouver, Canada

Date May 30, 200/

DE-6 (2/88)

# ABSTRACT

As the gap between memory and processor performance continues to grow, more and more programs will be limited in performance: by the memory latency of the system and by the branch instructions (control flow of the programs). Meanwhile, due to the increase in complexity of application programs over the last decade, object-oriented languages are replacing traditional languages because of convenient code reusability and maintainability. However, it has also been observed that the run-time performance of object-oriented programs can be improved by reducing the impact caused by the memory latency, branch misprediction, and several other factors. In this thesis, two new schemes are introduced for reducing the memory latency and branch mispredictions for High Performance Computing (HPC).

For the first scheme, in order to reduce the memory latency, this thesis presents a new cache scheme called TAC (Thrashing-Avoidance Cache), which can effectively reduce instruction cache misses caused by procedure call/returns. The TAC scheme employs N-way banks and XOR mapping functions. The main function of the TAC is to place a group of instructions separated by a call instruction into a bank according to the initial and final bank selection mechanisms. After the initial bank selection mechanism selects a bank on an instruction cache miss, the final bank selection mechanism will determine the final bank for updating a cache line as a correction mechanism. These two mechanisms can guarantee that recent groups of instructions exist in each bank safely. A simulation program, TACSim, has been developed by using Shade and Spixtools, provided by SUN Microsystems, on an ultra SPARC/10 processor. Our experimental results show that TAC schemes reduce conflict misses more effectively than skewed-associative caches in both C (9.29% improvement) and C++ (44.44% improvement)

programs on L1 caches. In addition, TAC schemes also allow for a significant miss reduction on Branch Target Buffers (BTB).

For the second scheme to reduce branch mispredictions, this thesis also presents a new hybrid branch predictor called the GoStay2 that can effectively reduce misprediction rates for indirect branches. The GoStay2 has two different mechanisms compared to other 2-stage hybrid predictors that use a Branch Target Buffer (BTB) as the first stage predictor: First, to reduce conflict misses in the first stage, an effective 2-way cache scheme is used instead of a 4-way set-associative scheme. Second, to reduce mispredictions caused by an inefficient predict and update rule, a new selection mechanism and update rule are proposed. A simulation program, GoS-Sim, has been developed by using Shade and Spixtools, provided by SUN Microsystems, on an Ultra SPARC/10 processor. Our results show significant improvement with these mechanisms compared to other hybrid predictors. For example, the GoStay2 improves indirect misprediction rates of a 64-entry to 4K-entry BTB (with a 512- or 1K-entry PHT) by 14.9% to 21.53% compared to the Cascaded predictor (with leaky filter).

# TABLE OF CONTENTS

| Abstract                                                     | ·ii  |

|--------------------------------------------------------------|------|

| Table of Contents                                            | iv   |

| List of Tables                                               | vii  |

| List of Figures                                              | viii |

| Acknowledgements                                             | xi   |

| CHAPTER I Overview and summary                               | 1    |

| 1.1 Introduction                                             | 1    |

| 1.2 Problem definitions and resolutions                      | 9    |

| 1.3 General background                                       | . 14 |

| 1.3.1 Cache Misses                                           | 14   |

| 1.3.2 Branch Mispredictions                                  | 19   |

| 1.4 Contributions and summary                                | .24  |

| CHAPTER II Reduction of Instruction Cache Misses             | 27   |

| 2.1 Introduction                                             | 28   |

| 2.2 Cache Misses                                             | 30   |

| 2.2.1 Total miss ratios vs. conflict miss ratios             | 30   |

| 2.2.2 Skewed-associative caches                              | 34   |

| 2.3 Thrashing-Avoidance Cache (TAC)                          | 37   |

| 2.3.1 An overview of a TAC scheme                            | 38   |

| 2.3.2 Bank Selection Logic (BSL) – Initial Bank Selection    | 40   |

| 2.3.3 Bank-originated Pseudo LRU Replacement Policy (BoPLRU) |      |

| – Final Bank Selection                                       | . 44 |

| 2.3.4 Benefit of the TAC scheme                              | 47   |

iv

|             | 2.3.5    | Examples of cache misses: a 2-way TAC scheme vs. a 2-way    |     |

|-------------|----------|-------------------------------------------------------------|-----|

|             |          | skewed-associative                                          | 49  |

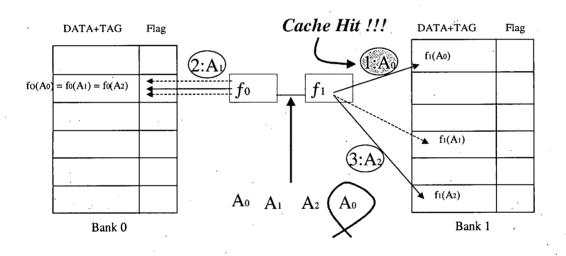

| 2.4 Ex      | perime   | ntal Environment                                            | 52  |

|             | 2.4.1    | Simulation methodology                                      | 52  |

|             | 2.4.2    | Benchmarks                                                  | 54  |

| 2.5 Ex      | perime   | ntal results                                                | 55  |

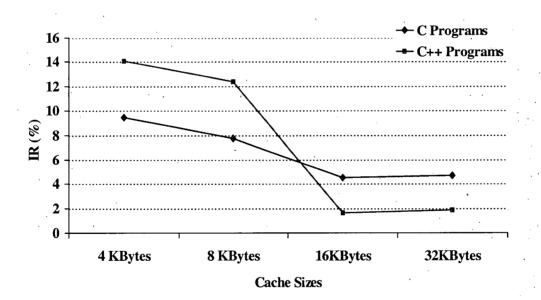

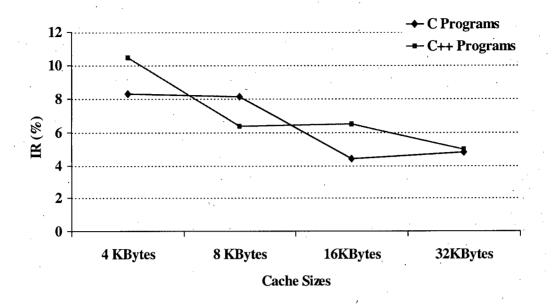

|             | 2.5.1    | Cache Misses vs. Cache Sizes                                | 56  |

|             | 2.5.2    | Bank Switching vs. Procedure Calls                          | 60  |

|             | 2.5.3    | Instruction Cache Misses for various cache schemes          | 66  |

|             | 2.5.4    | Skewed-associative caches vs. TAC schemes                   | 68  |

|             | 2.5.5    | Various cache schemes for the Branch Target Buffer          | 76  |

|             | 2.5.6    | Comparison for all 2-way schemes                            | 81  |

| 2.6 Ch      | apter co | onclusions                                                  | 83  |

| CHAPTER III | Reduc    | tion of Indirect Branch Mispredictions                      | 85  |

| 3.1 Intr    | oductio  | on                                                          | 85  |

| 3.2 Rel     | ated wo  | ork                                                         | 88  |

|             | 3.2.1    | Indexing functions for indirect branch predictors           | 89  |

|             | 3.2.2    | Selection mechanisms and update rules for hybrid predictors | 92  |

| 3.3 Go      | Stay2 E  | Branch Predictor                                            | 94  |

|             | 3.3.1    | An overview of a GoStay2 predictor                          | 95  |

|             | 3.3.2    | The 2-way TAC scheme for the BTB – The first mechanism      | 99  |

|             | 3.3.3    | The GoStay predict and update rule – The second mechanism   | 101 |

|             |          | 3.3.3.1 GoStay predict rule                                 | 101 |

|             |          |                                                             |     |

v

t .

|              |          | 3.3.3.2 Update rule                                              | 103 |

|--------------|----------|------------------------------------------------------------------|-----|

|              | 3.3.4    | Benefits of the GoStay2 branch predictor                         | 104 |

| 3.4 Exp      | perimen  | tal environment                                                  | 108 |

|              | 3.4.1    | Benchmarks                                                       | 109 |

| 3.5 Exp      | perimen  | tal results                                                      | 111 |

|              | 3.5.1    | Implemented branch predictors                                    | 111 |

|              | 3.5.2    | Indirect Branch Instructions                                     | 114 |

| •            | 3.5.3    | Conventional indirect branch predictors                          | 116 |

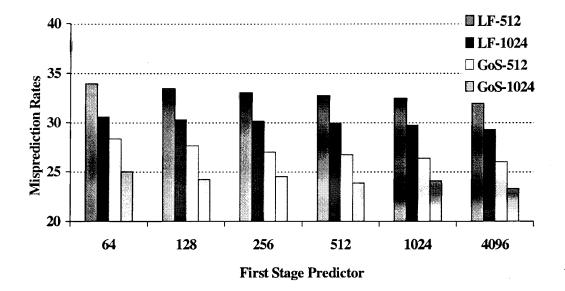

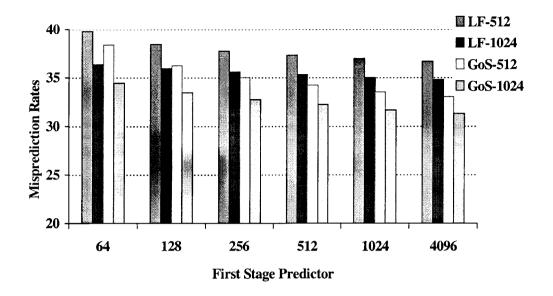

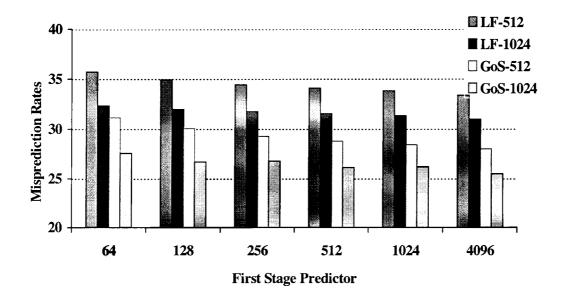

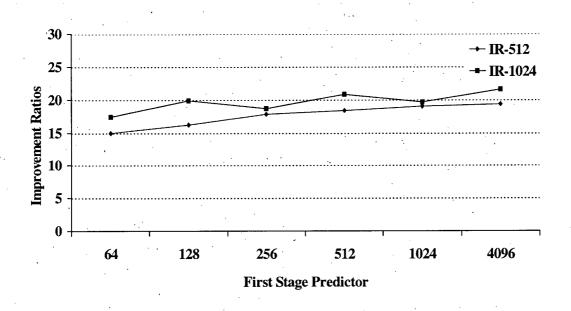

|              | 3.5.4    | Misprediction rates for indirect branches between the LF and GoS | 122 |

|              |          | ·                                                                | 122 |

|              | 3.5.5    | Analyses of the update rule                                      | 129 |

| 3.6 Cha      | apter co | nclusions                                                        | 134 |

| CHAPTER IV   | Concl    | lusions and Future Research                                      | 137 |

| 4.1 Cor      | nclusior | ns                                                               | 137 |

|              | 4.1.1    | Reduction of cache misses                                        | 138 |

| ·            | 4.1.2    | Reduction of indirect branch mispredictions                      | 139 |

| 4.2 Fut      | ure Res  | earch                                                            | 140 |

| BIBLIOGRAP   | HY       |                                                                  | 145 |

| Appendix A E | xperime  | ent results for TAC schemes                                      | 152 |

vi

# LIST OF TABLES

| Table 1 Actual miss rate versus block size for five different-sized caches.               | 16          |

|-------------------------------------------------------------------------------------------|-------------|

| Table 2. Behavioral differences between C and C++ Programs [Calder et al '94]             | 28          |

| Table 3. Benchmark descriptions                                                           | 54          |

| Table 4. Benchmark characteristics                                                        | 55          |

| Table 5. Instruction cache miss rates in percentages (cache size: 8 KB, a line size: 16 b | ytes)<br>66 |

| Table 6. Comparison of hardware complexity and access time among three representat        | ive         |

| 2-way schemes: 2-way set-associative, 2-way skewed-associative, and 2-way TAC sch         | iemes       |

|                                                                                           | 82          |

| Table 7. Update rules for the Target Cache and Cascaded predictors                        | 93          |

| Table 8. Benchmark descriptions                                                           | 110         |

| Table 9. Benchmark characteristics                                                        | 111         |

| Table 10. Comparisons for the percentages of conditional and indirect branches            | 114         |

| Table 11. The relevance of indirect branches by comparing lines of code, inst./ind.       |             |

| (instructions/indirect branch), and cond./ind. (conditional branches/indirect branch)     | 115         |

| Table 12. Indirect branch misprediction rates according to the BTB entries.               | 136         |

vii

# LIST OF FIGURES

| Figure 1. An overview of High Performance Computing (HPC)                                 | 2          |

|-------------------------------------------------------------------------------------------|------------|

| Figure 2. The technical trend for supercomputers and microprocessors [Buyya '00]          | 3          |

| Figure 3. Comparison of the performance between microprocessor and DRAM accordin          | g to       |

| Moore's Law [Patterson and Keeton '00] [Alexander & Kedem '95]                            | 7          |

| Figure 4. Problem definitions                                                             | <b>9</b> · |

| Figure 5. Relative CPU execution time by cache miss rates.                                | 11         |

| Figure 6. Relative CPU execution time by branch misprediction rates.                      | 13         |

| Figure 7. Reduction of cache misses (overview)                                            | 14         |

| Figure 8. This cache example has eight block frames and memory has 32 blocks              |            |

| [Patterson & Hennessy '96]                                                                | 17         |

| Figure 9. Reduction of branch mispredictions (overview)                                   | 19         |

| Figure 10. Components of Total CPI (Cycles Per Instructions) [Bondi et al. '96]           | 23         |

| Figure 11. Miss ratios (%) of the various cache schemes [Gonzales et al '97]              | 31         |

| Figure 12. An example of instructions with two procedure calls                            | 32         |

| Figure 13. Execution of the code shown in Figure 12 in a direct-mapped cache              | 32         |

| Figure 14. Execution of the code shown in Figure 12 in a fully-associative cache          | 33         |

| Figure 15. a, b, and c compete for the same location in bank 0, but can be present at the | same       |

| time, as they do not map to the same location in bank 1 [Seznec '97]                      | 35         |

| Figure 16. One of replacement polices, PLRU, for a 2-way skewed-associative cache         | 36         |

| Figure 17. The basic operations of a conventional cache scheme and a TAC scheme           | 38         |

| Figure 18. The operation of the BSL (2-bit counter, 2-way) according to a flow of instru  | ctions.    |

| Conflicts in (B, H) and (I, X)                                                            | 41         |

| Figure 19. An example for the grouping instructions in a 2-way TAC scheme                 | 42         |

viii

| Figure 20. Initial bank selection of BSL for a 2-way TAC scheme                          | 43  |

|------------------------------------------------------------------------------------------|-----|

| Figure 21. Pseudo code for the BoPLRU replacement policy                                 | 45  |

| Figure 22. Final bank selection of BoPLRU replacement policy for a 2-way TAC scheme      | 46  |

| Figure 23. Placement of instructions in a 2-way TAC scheme                               | 47  |

| Figure 24. An example for a 2-way skewed-associative scheme                              | 50  |

| Figure 25. An example for a 2-way TAC scheme                                             | 51  |

| Figure 26. Simulation methodology with benchmark programs and various tools              | 52  |

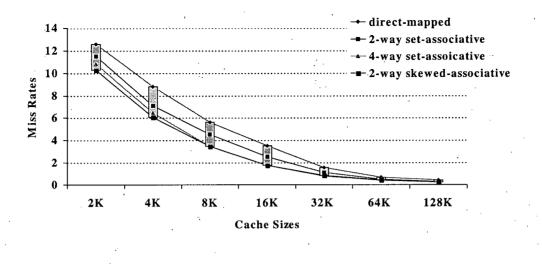

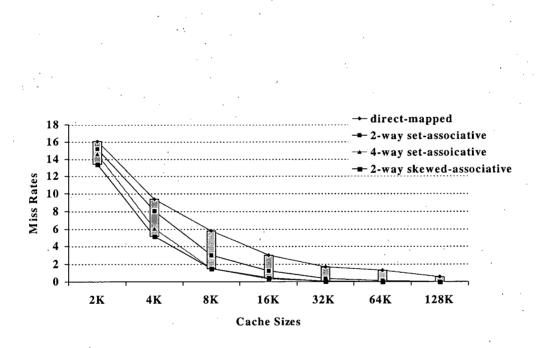

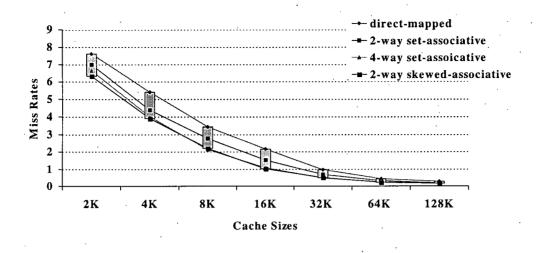

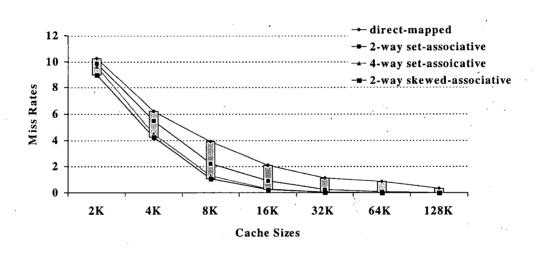

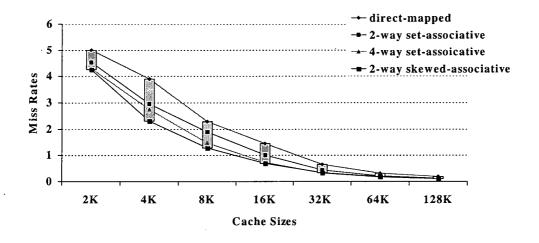

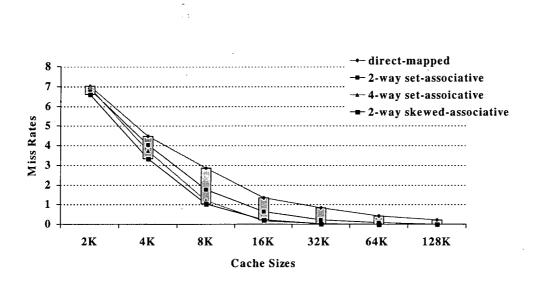

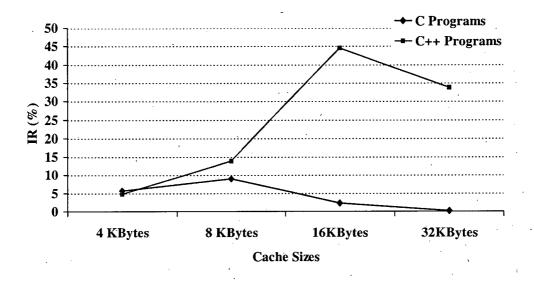

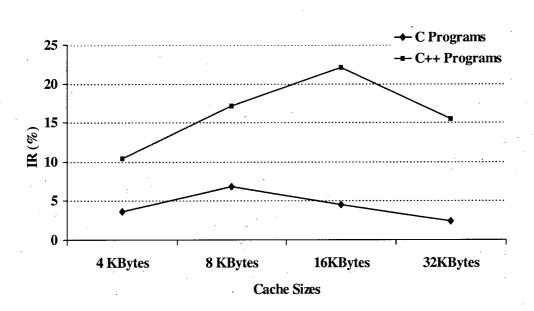

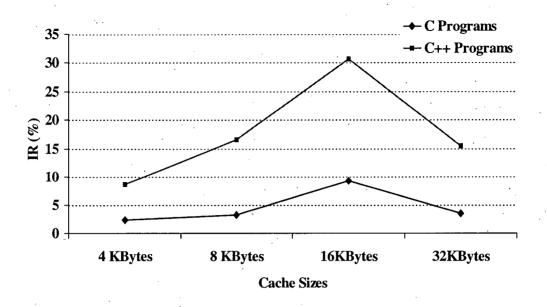

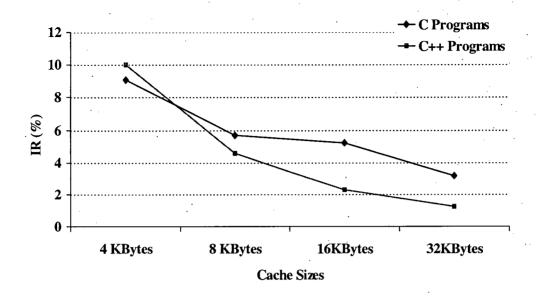

| Figure 27. Comparisons for cache misses according to the cache sizes (4 cache schemes)   | 57  |

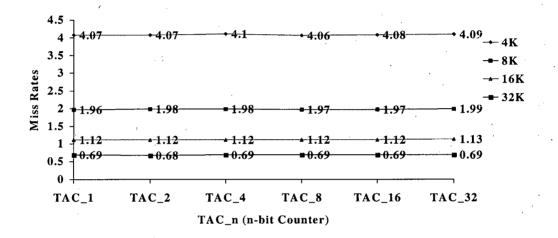

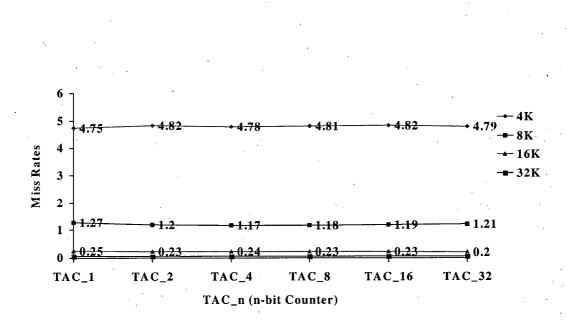

| Figure 28. Cache miss rates according to the sizes of the n-bit counter (C programs)     | 61  |

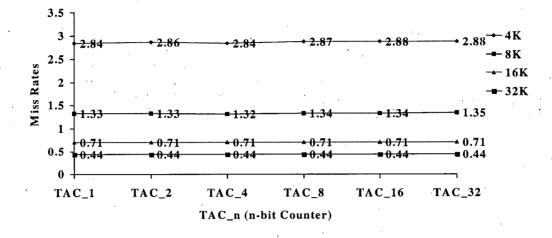

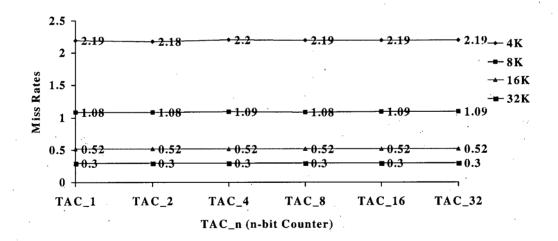

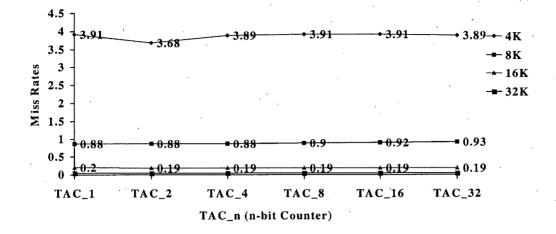

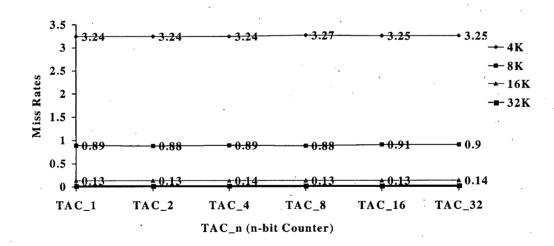

| Figure 29. Cache miss rates according to the sizes of the n-bit counter (C++ programs)   | 63  |

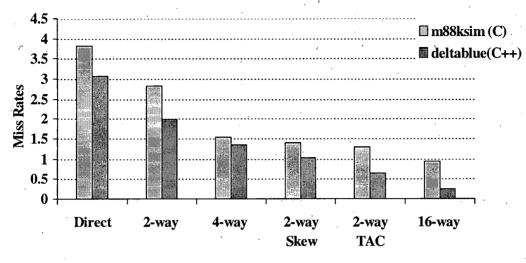

| Figure 30. Comparison for instruction cache miss rates between C (m88ksim) and C++       | -   |

| (deltablue) programs (8Kbytes, 16bytes)                                                  | 67  |

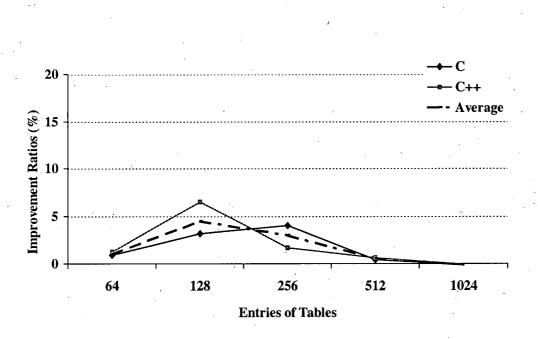

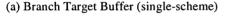

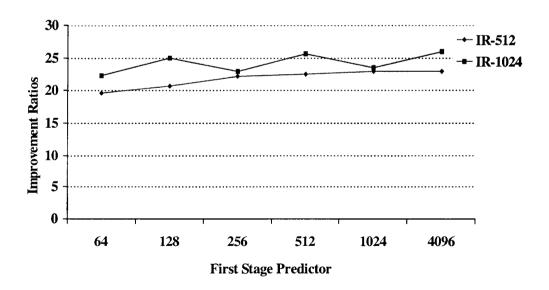

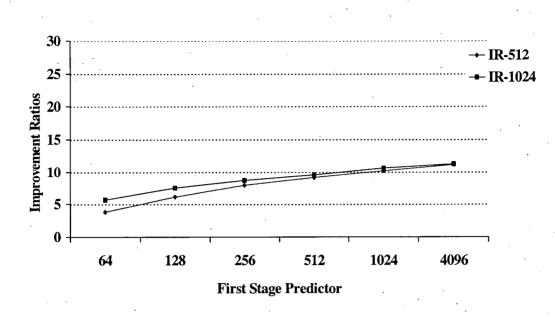

| Figure 31. Comparisons for Improvement Ratios between 2-way skewed-associative           | .'  |

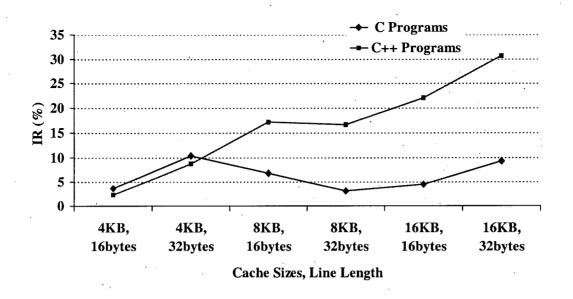

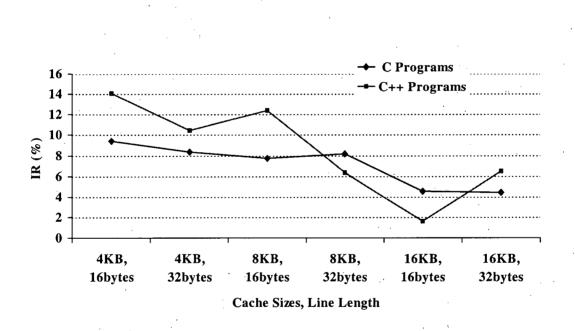

| and 2-way TAC caches                                                                     | 69  |

| Figure 32. Comparisons for Improvement Ratios between 4-way skewed-associative           |     |

| and 4-way TAC caches                                                                     | 72  |

| Figure 33. Comparisons for Improvement Ratios between skewed-associative and TAC         |     |

| caches from 4Kbytes to 8 Kbytes                                                          | 75  |

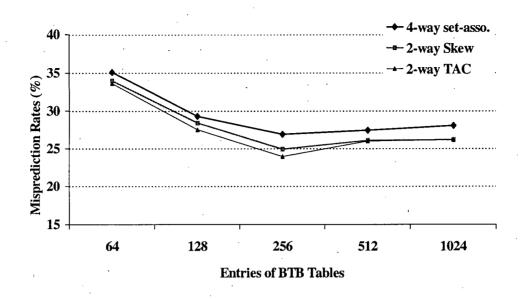

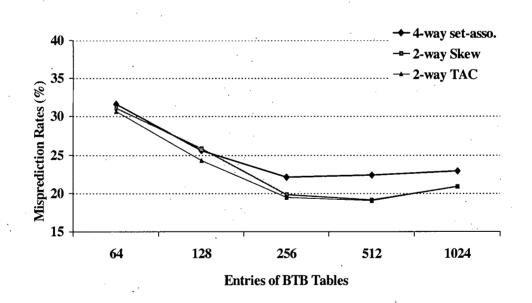

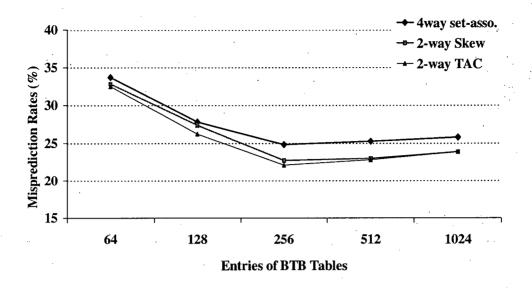

| Figure 34. Comparisons of branch misprediction rates of BTB with a 4-way set-associative | ve, |

| 2-way skewed-associative and 2-way TAC caches.                                           | 77  |

| Figure 35. Comparisons for Improvement Ratios among 4-way set-associative, 2-way         |     |

| skewed-associative and 2-way TAC schemes                                                 | 79  |

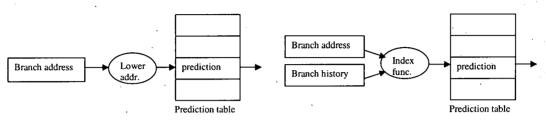

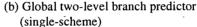

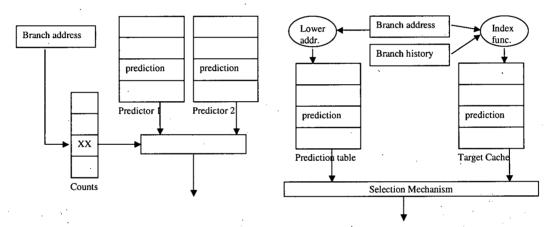

| Figure 36. Various indirect branch predictors                                            | 89  |

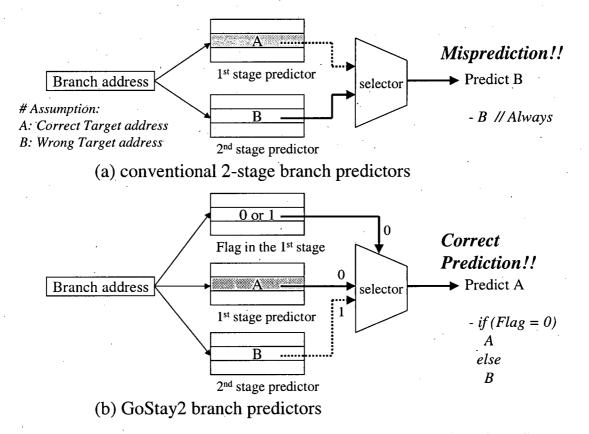

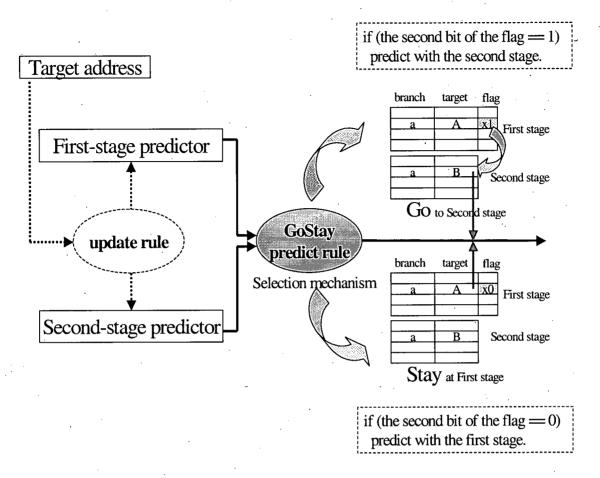

| Figure 37. The basic operations of conventional 2-stage and GoStay2 branch predictors.   | 96  |

∝ ix

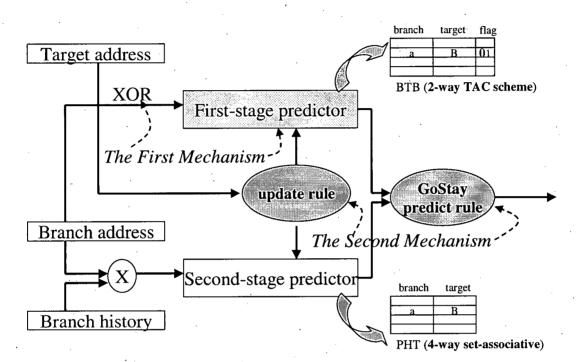

| Figure 38. The overview of the GoStay2 branch predictor                                 | 97  |

|-----------------------------------------------------------------------------------------|-----|

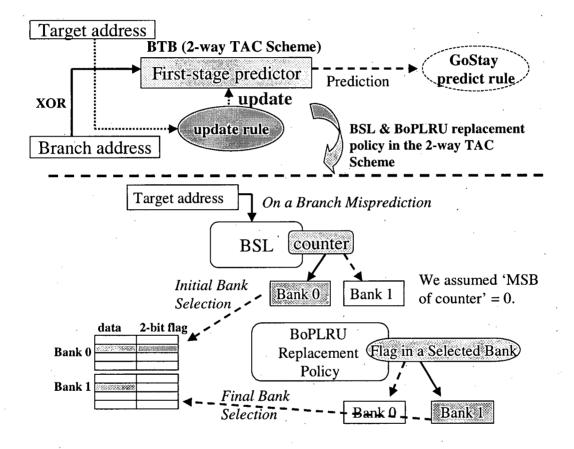

| Figure 39. The operation of the first mechanism. data = branch address + target address | 99  |

| Figure 40. The GoStay predict rule of the second mechanism                              | 102 |

| Figure 41. Update rule of the second mechanism                                          | 103 |

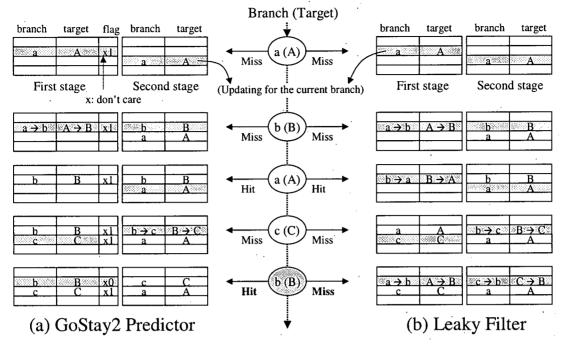

| Figure 42. A comparison of the update processing between the GoStay2 and the leaky      |     |

| filter                                                                                  | 106 |

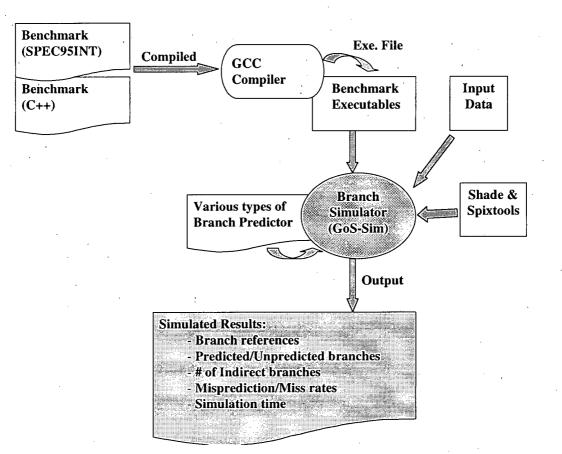

| Figure 43. Experimental methodology                                                     | 108 |

| Figure 44. The comparison of misprediction rates according to BTB sizes for indirect    |     |

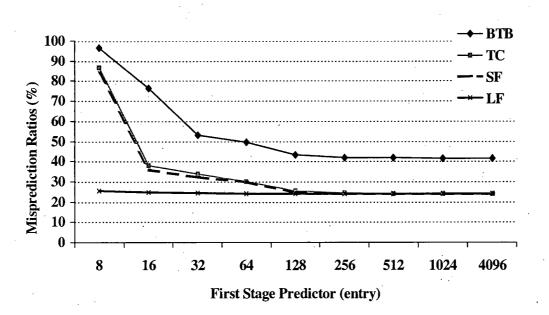

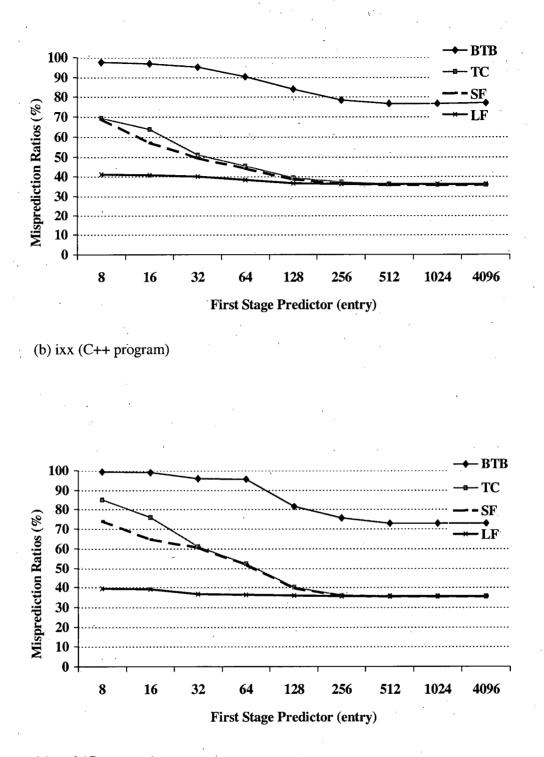

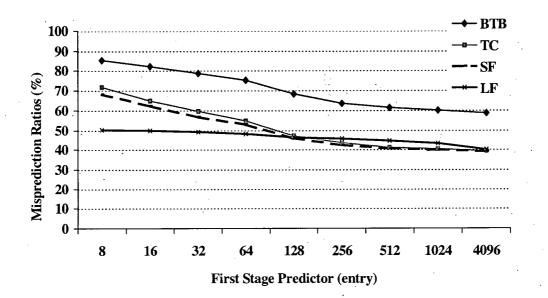

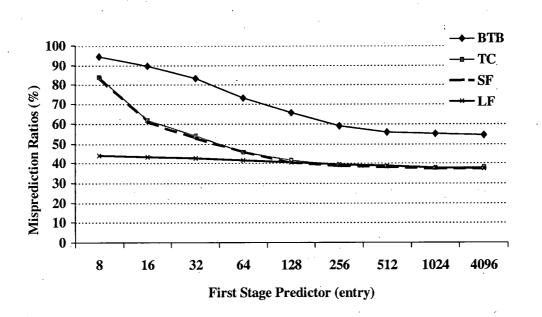

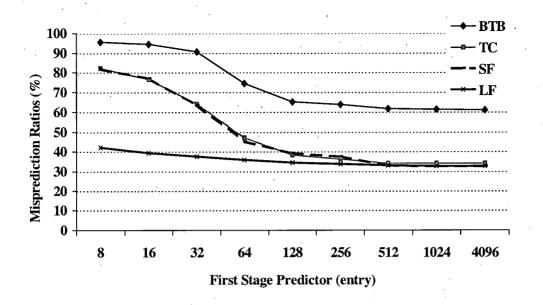

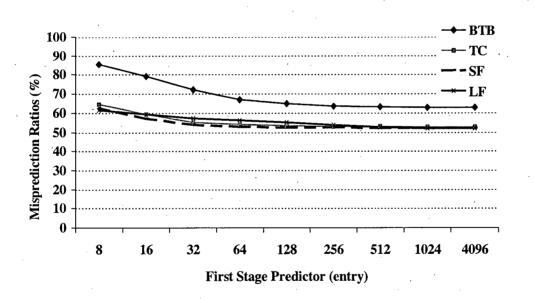

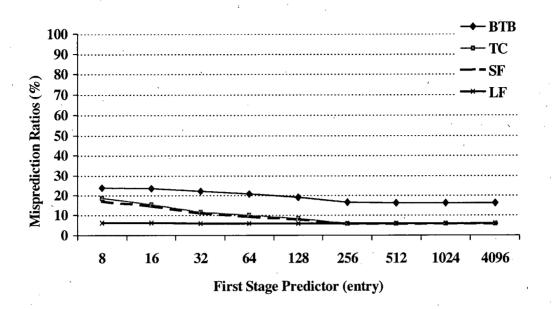

| branch predictors. The second stage is a table with 512 entries (4-way)                 | 116 |

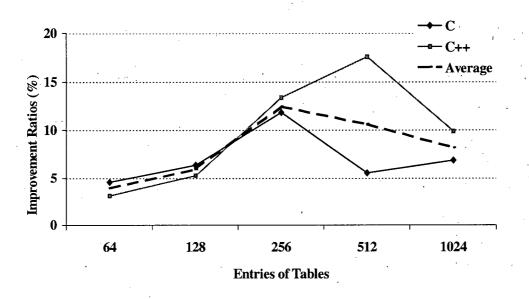

| Figure 45. Comparison Misprediction Rates and Improvement Ratios between C and          |     |

| C++ Benchmark programs                                                                  | 124 |

| Figure 46. Comparison misprediction rates and Improvement Ratios between the LF and     | d   |

| GoS for all Benchmark programs(C and C++ programs, harmonic mean)                       | 127 |

| Figure 47. Analysis of prediction rates according to cases whether both predictors have |     |

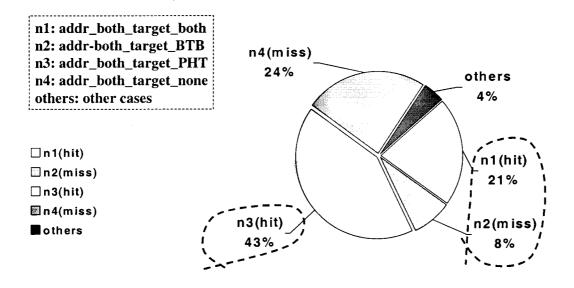

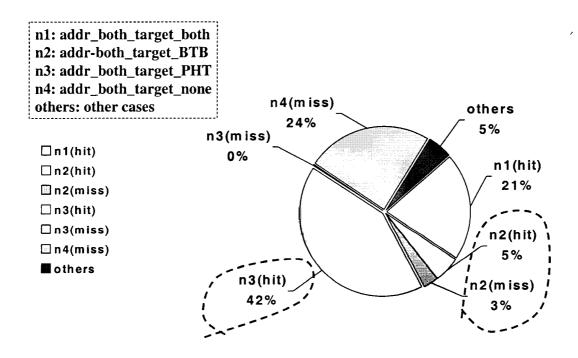

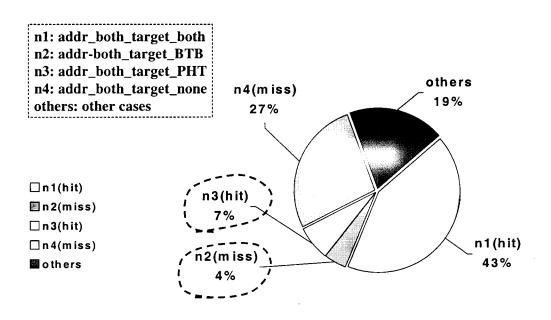

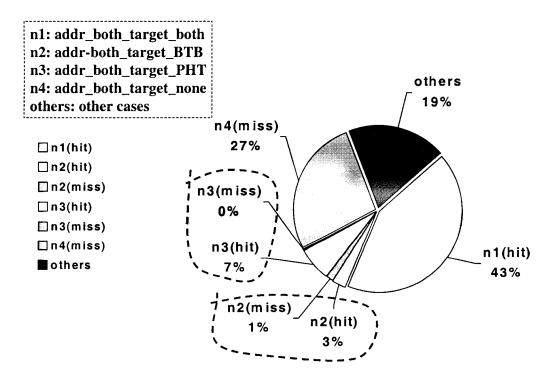

| a correct target address or not. 'Others' means all other cases except the n1 to n4     | 130 |

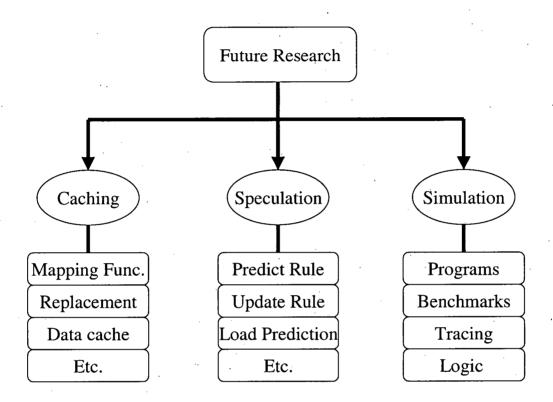

| Figure 48. Future Research for caching, speculation, and simulation                     | 141 |

х

#### ACKNOWLEDGEMENTS

I sincerely wish to express my gratitude to my supervisor, Dr. M. R. Ito, for his inspiring and encouraging guidance in leading me to a deeper understanding of this work. His invaluable oral and written comments were always extremely perceptive, helpful, and appropriate.

I would also like to thank my committee members, Dr. Steve Wilton and Dr. Alan Hu, for their help, advice, and valuable suggestions throughout my work. Thanks to Dr. Hu, I was able to use SPEC95 benchmark program for my simulation without any trouble. Thanks to Dr. Wilton, I was able to expand one of my future research programs to include the field of FPGA.

Special thanks should go to my friends Robert Ross and Susan Ritchie who provided valuable proofreading comments on this work.

I am also very grateful to Dr. Norm Hutchinson, Dr. Babak Hamidzadeh and Dr. Mark R. Greenstreet for their kindness in participating in my examining committee. I am also very grateful to Dr. Nikitas Dimopoulos for his valuable editorial comments and for passing me as an external examiner.

It is my great pleasure to dedicate this small achievement to my mother Sunghye Hwang, my father Kwangho Chu, my wife Myunghee Chu, our children, Sangjun, Jinna and Yuna for their love, support, and patience over the past several years.

xi

I want to express my deep gratitude to my brother Dr. Hong Chu, my cousin Ronald Choo, and their families for their love and encouragement.

Last, but certainly not least, I would like to extend my deepest thanks to Kyungwoo club members in Korea and many friends for their support and understanding throughout my time at UBC.

This dissertation could not have been completed without the support of the many people who are gratefully acknowledged here.

This research has been funded by the Natural Sciences and Engineering Research Council of Canada.

### **Chapter 1 Overview and summary**

#### **1.1 Introduction**

Through the mid-1980s, supercomputers such as Cray were used to achieve high performance for advanced scientific and engineering applications. However, since the late 1980s, supercomputers have not been able to significantly improve performance. They have been restricted by high cost (about \$3 million) compared to a personal computer (about \$3000) and limited by the number of customers [Dowd & Severance '98].

Meanwhile, the performance of microprocessor architectures has doubled every two to three years. This has occurred for two reasons. First, microprocessor architectures are borrowing and innovating with techniques formerly unique to supercomputers and large mainframes. The second reason has been the emergence of a personal and business computer market which demands high performance for computer usage such as 3D graphics, graphical user interface, and games [Dowd & Severance '98]. However, supercomputers are still used for the most demanding applications such as weather forecasting.

#### What is High Performance Computing (HPC)?

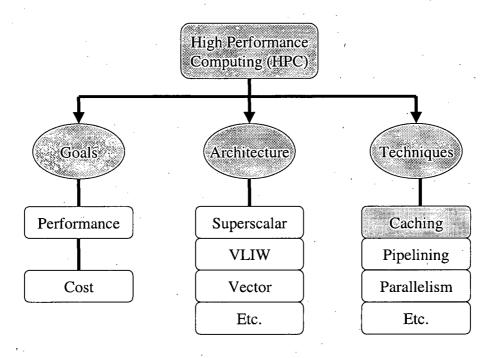

In general, High Performance Computing (HPC) refers to computing systems that are used to provide solutions to problems that require the significant computational power needed to process very large amounts of data quickly, and are also needed to operate interactively across a geographically-distributed network. Figure 1 shows an overview of HPC with respect to three different areas: goals, architectures, and techniques.

Figure 1. An overview of High Performance Computing (HPC)

In Figure 1, the goals for HPC could be achieved through maximum performance and minimum cost. How to maximize performance depends on reducing the time to execute a program (*T*), which is a function of the number of instructions to execute  $(n_i)$ , the average number of clock cycles per instruction (*CPI*), and the clock cycle time  $(t_c)$ . From (1), there are two distinct approaches for increasing system performance:

####

By lowering the clock cycle time  $(t_c)$  – Much of this performance gain comes as a consequence of circuit and layout improvement. However, this is becoming increasingly

difficult and will eventually reach physical constraints. Since this topic is beyond the scope of this thesis, it will not be covered in detail.

• By improving two other factors (*CPI*,  $n_i$ ) – The major performance optimization is pipelining, in which a stream of instructions progress from pipeline stage to pipeline stage with overlapping of instruction fetch, decode, and execution. This technique will be discussed in detail with other techniques such as cache memory, parallelism and superscalar throughout this section.

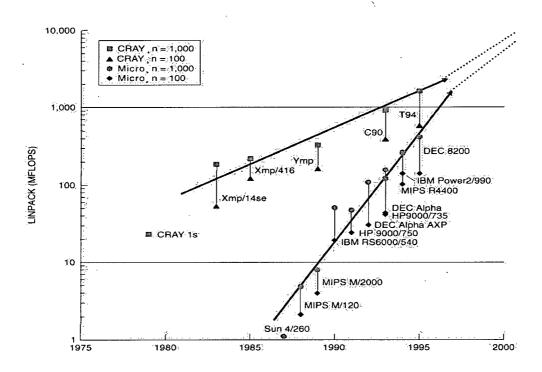

Figure 2. The technical trend for supercomputers and microprocessors [Buyya '00].

Figure 2 compares the performance since 1980 between supercomputers such as CRAY and microcomputers by using the LINPACK benchmark program. The LINPACK is one of the more famous floating-point benchmarks of recent years, created by Jack Dongarra, and gets its name from a linear algebra package that it uses to solve a dense

system of linear equations with Gaussian elimination. The LINPACK keeps track of execution time and then divides this into the number of floating-point operations that are performed to get a MegaFLOPS rating. 'n = 100 and n = 1000' in Figure 2 describes the results based on a 100 x 100 and 1000 x 1000 matrix using a double-precision floating point. Figure 2 shows that the performance of a supercomputer in 1990 is similar to a microcomputer in 1995. Moreover, the performance gap between supercomputers and microprocessors has been decreasing since 1995 because of the rapid technical development of microprocessors.

In 1988, an article appeared in the Wall Street Journal titled 'Attack of the Killer Micro' that described how computing systems made up of many small (\$3,000 to \$20,000) machines would soon make large supercomputers (\$3 million) obsolete. These inexpensive processors have been developed toward high performance computing systems. HPC, which is broader than supercomputing with supercomputers, is a moving target because of the steady and rapid gains in the performance/cost ratio. Yesterday's supercomputer is today's personal computer; today's leading-edge techniques for supercomputers will be among tomorrow's mainstream capabilities for HPC.

In Figure 1, the architectures for HPC have a tendency to be designed in such a way as to do additional parallelism proportional to increased machine resources [Lipasti & Shen '97]. According to Lipasti & Shen ('97), these architectures are:

Superscalar machines schedule instructions dynamically at runtime. These machines can reduce the average number of cycles per instruction, but they need extra hardware. Therefore, performance depends on the amount of resources in the machine;

- VLIW machines schedule instructions statically at compile time. These machines contain numerous functional units, which accommodate multiple streams of data input, such as audio and video. In general, VLIW machines heavily rely on powerful compilers to detect and resolve inter-instruction dependencies in software. This keeps the hardware design simple and fast. But their static nature makes them incompatible with dynamic variations in parallelism, which are caused by an aggressive memory subsystem and speculative-execution techniques;

- Multithreaded processors support multiple machine contexts and execute multiple instruction streams simultaneously. The performance depends on finding enough thread parallelism by software. The disadvantages of these machines are that debugging multithread programs is difficult, and that there is a lack of automatic thread-partitioning compilers;

- Single chip multiprocessors are used for improving throughput under multiprogrammed workloads. However, these machines are restricted to numerical applications that contain easily parallelized loops. Limited processor interconnects and synchronization overhead will degrade system performance.

- Vector processors are machines built primarily to handle large scientific and engineering calculations. Their performance derives from a heavily pipelined architecture which operations on vectors and matrices can efficiently exploit. As an example, the NEC SX5/3C is reported at 8 Gflops per second per processor peak.

The techniques for HPC in Figure 1 can be categorized into four different fields. Those fields include:

- *Pipelining* allows increased utilization of hardware resources by the partial execution of more than one instruction at the same time. One of the most common uses of pipelining is to fetch the next instructions from lower level memory while executing a current one.

- Cache memory is to improve the throughput of memory data and instruction flow. Memory data flow is relevant to the load/store instructions. The data values are stored and retrieved from data memory. To reduce average memory latency, the prediction of load values and addresses are incorporated into the execution core. Meanwhile, there are two main logical stages in the instruction flow: Fetch – the processor retrieves instructions from cache or main memory; and Decode – the processor decodes instructions, renames their operands, and detects inter-instruction dependencies. For each stage, there is a need to reduce cache misses by using an efficient cache scheme and increase the speculation for the control-flow instructions with an accurate branch predictor.

- For the technique of *parallelism*, multiple execution units are popular for improving performance. The execution core must strive for two fundamental goals to increase instruction throughput. It must:

- efficiently detect and resolve inter-instruction dependencies; and

- eliminate or bypass as many dependencies as possible to explore more parallelism between instructions.

- Other techniques such as *prefetching*, *buffering*, etc. are also popular for improving system performance for the HPC.

### What do future architectures look like?

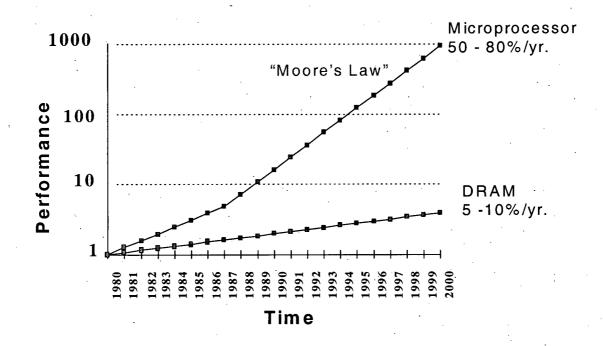

Figure 3 shows Moore's Law (the observation made in 1965 by Gordon Moore, cofounder of Intel): The number of transistors on a microprocessor would double approximately every 18 months. Meanwhile, memory densities (DRAM) and disk densities will continue to quadruple every three years. The gap between microprocessor and memory will be discussed in detail in section 1.2.

To date, Moore's Law has proven remarkably accurate even if the end of Moore's Law has been predicted so many times that rumors of its demise have become an industry joke. In reality, microprocessors have achieved a performance growth of 10,000 times during the last two decades. Transistor count increased from 10,000 to 100,000 in the 1970s, and then increased up to 1 million in the 1980s; while clock frequency increased from 200KHz to 2MHz in the 1970s and up to 20MHz in the 1980s. In the 1990s, both transistor count and clock frequency achieved an increase of 20 to 30 times. Future billion-transistor chips in the 2000s will create machines that are much wider (issue more than four instructions at once) and deeper (have longer pipelines) [Lipasti & Shen '97].

According to Burger & Goodman ('97) and Patt et al. ('97), microprocessors will have more than one billion transistors on a single chip by 2010. As we discussed before, most of the current techniques for microprocessors have come from supercomputers. Moreover, some future techniques will be based on current ones such as instruction level parallelism. The future architectures surveyed by Burger & Goodman ('97) are:

- Advanced Superscalar processors that issue 16 to 32 instructions per cycle and Superspeculative processors that have wide-issue speculation;

- *Vector IRAM processors* couple vector processor execution with large, highbandwidth, on-chip DRAM banks, which provide the vector units with sufficient bandwidth at a reasonable cost;

- Chip multiprocessors that place a number of processors (four to 16) on a single chip;

- *Raw processors* that implement parallel architectures with 128 tiles, very simple processors with reconfigurable functional logic.

Beyond the previous potential architectures, *Simultaneous multithreaded processors* and *Trace processors* are also included in the surveyed future architectures [Burger & Goodman '97].

### **1.2 Problem definitions and resolutions**

The previous section provided an overview of high performance computing. This section will discuss two problem definitions intended to improve system performance for current and future microprocessors.

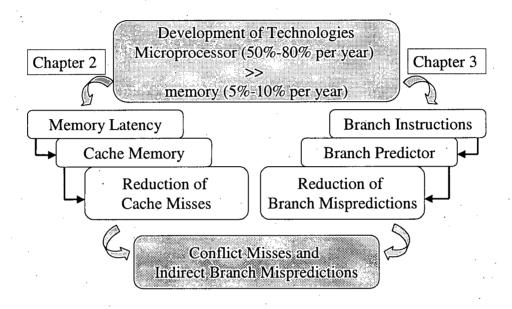

Figure 4. Problem definitions

In Figure 4, rapidly changing technologies are improving microprocessor execution speeds at a rate of 50% - 80% per year. In contrast, DRAM access time has developed at the much lower rate of 5% - 10% per year [Alexander & Kedem '95]. As the performance gap between microprocessor and memory increases dramatically, more and more programs will be limited in performance:

- by the memory latency and bandwidth of the system;

- by the branch instructions (control flow of the programs).

Latency is described as the total time memory requires to satisfy a request from the processor, and bandwidth as the rate of information transfer between the processor and memory that supports the required processing rate.

1) First Problem Definition (Left side of Figure 4): Cache Misses

Since the processor is much faster than the main memory, latency often causes the processor to go into one or more wait states. In order to solve the latency problem, a cache memory has been introduced as part of a memory hierarchy. The memory hierarchy combines a fast, small memory matched to the processor speed with slower and larger memories (level-two or main memory).

When a CPU does not find data it needs in a cache memory, a cache miss occurs. If a cache miss occurs, the CPU must wait until the needed data is retrieved from a lower level memory.

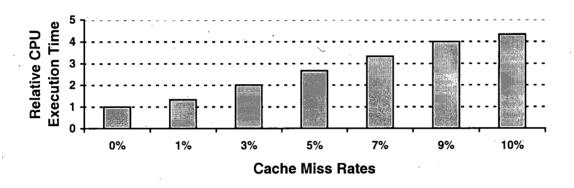

The impact on CPU performance caused by cache miss rates is:

CPU Execution time = IC \* (CPI + (Memory stall clock cycle/Instruction))\*

Clock cycle time

= IC \* (CPI + (memory accesses per instruction) \* MR \* MP) \*

Clock cycle time

Where, IC (Instruction Count), CPI (Cycles per Instruction), MR (Miss Rate), and

MP (Miss Penalty).

Relative CPU Execution time = CPU Execution time / (IC \* Clock cycle time\* CPI) If there are no memory stalls (perfect cache), then Relative CPU Execution time is 1. Assume that CPI = 2, memory references per instruction = 1.33, Cache Miss Rate = 10%, and Miss Penalty = 50 cycles.

Then, Relative CPU Execution time = (2 + 1.33 \* 0.1 \* 50) / 2 = 4.33.

This Relative CPU Execution time shows that a CPU Execution time of 10% cache miss rate is 4.33 times longer than a CPU Execution time with a perfect cache (0% cache miss rate).

Figure 5 shows Relative CPU Execution time when the behavior of the cache (from 0% cache miss rate, perfect cache, to 10% cache miss rate) is included.

Without any memory hierarchy at all, the CPI would increase to 2.0 + 50\*1.33 or 66.5 – a factor of over 33 times longer.

As the above example illustrates, cache behavior can have enormous impact on performance. Therefore, the efficiency of a cache memory depends on reducing cache misses and will be discussed in detail in chapter 2. This thesis defines reduction of cache misses as the first problem to be solved and in chapter 2 introduces a new cache scheme to reduce cache misses, focused on conflict misses due to the cache set overfilling, even though the cache as a whole may not be full.

### 2) Second Problem Definition (Right side of Figure 4): Branch Mispredictions

For current microprocessors, multi-instruction issues are a popular method of increasing system performance. Therefore, instruction cache misses can severely limit the performance of high-speed microprocessors. It has been observed that many instruction cache misses are caused by the control flow of programs.

Control flow is related to the branch instructions, which can be generally categorized into conditional or unconditional, and direct or indirect [Chang et al '97]. Since these branch instructions do not tend to fetch the next instruction in sequence, it is not possible to know the next instruction until a current instruction is executed. To overcome this obstacle, branch prediction schemes have been used for predicting and fetching the outcome of branches before they are executed. Therefore, if the prediction is wrong (branch misprediction), the processor needs to be stalled because as a result of flushing all the instructions incorrectly fetched, issued, and executed. This is referred to as branch penalty. Thus, without an appropriate branch predictor, the branch penalty can have a critical impact on overall system performance.

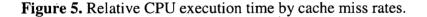

If branches are the only thing that cause stalls in a pipeline, the impact of CPU performance caused by branch penalty is:

CPU Execution time = IC \* (CPIbase + branch frequency \* branch penalty)\*

#### Clock cycle time

Where, IC (Instruction Count), CPI<sub>base</sub> (an ideal CPI without branch stalls in the pipeline), branch penalty (branch misprediction rate \* misprediction penalty).

Relative CPU Execution time = CPU Execution time / (IC \* Clock Cycle time \* CPIbase) If there are no branch stalls (perfect branch predictor), Relative CPU Execution time is 1.

Assume that  $CPI_{base} = 1$ , branch frequency = 25%, branch misprediction rate = 20%, and misprediction penalty = 5 cycles.

Then, Relative CPU Execution time = (1 + 0.25 \* 0.2 \* 5) / 1 = 1.25.

This Relative CPU Execution time shows that a CPU Execution time of 20% branch misprediction rate is 1.25 times longer than a CPU Execution time with a perfect branch predictor (0% branch misprediction rate).

Figure 6 shows Relative CPU Execution time when the behavior of the branch predictor (from 0% branch misprediction rate, perfect branch predictor, to 40% branch misprediction rate) is included.

Figure 6. Relative CPU execution time by branch misprediction rates.

To reduce the branch penalty, there is a need to reduce branch mispredictions: direct mispredictions and indirect branch mispredictions. As object-oriented languages such as C++ and JAVA are widely used, more accurate branch predictors for multi-targets, which are called indirect branch predictors, are needed. This thesis also defines the reduction of branch mispredictions as the second problem to be solved, and introduces in chapter 3 a new branch predictor to reduce branch mispredictions focused on indirect branch mispredictions due to multi-targets.

# **1.3 General background**

The previous section briefly describes the problems defined in this thesis. In this section, we discuss the general background of cache misses and branch mispredictions in more detail.

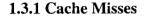

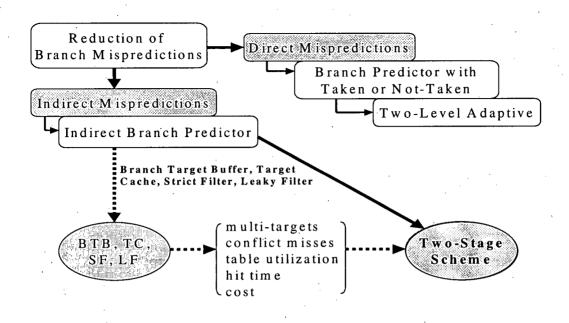

Figure 7. Reduction of Cache Misses (overview).

Figure 7 shows the problem of reduction of cache misses. There are three cache-miss types: compulsory, capacity, and conflict. Compulsory and capacity cache misses can be reduced by larger cache and block sizes. However, conflict misses are more complex than other cache misses and are critical to system performance. Figure 7 also suggests the problems which the conventional cache schemes have in regard to conflict misses, memory utilization, etc. In Chapter 2, we will discuss the conflict miss ratios of several

cache schemes (direct-mapped, 2-way skewed associative, etc.) compared to the fullyassociative scheme which has no conflict misses, and also introduces a new cache scheme called the TAC (Thrashing-Avoidance Cache) scheme, which can reduce conflict misses effectively.

# Cache Miss Types

Despite tremendous research efforts, current cache schemes make poor use of cache capacity. One of the drawbacks of conventional cache schemes is that they perform a myopic management of all memory references: if the reference misses, a new block is brought into the cache at the expense of replacing another [Sanches et al '97].

There are three cache-miss types - compulsory, capacity, and conflict [Patterson & Hennessy '96]:

- Compulsory misses: these are the first reference misses since a block must be brought into the cache the first time it is accessed;

- Capacity misses: if the number of active blocks is more than the cache can contain, capacity misses take place;

- Conflict misses: these misses take place because of limited or zero associativity, when blocks must be discarded in order to accommodate new blocks which are mapped to the same line in the cache. A conflict miss occurs when the replaced block needs to be accessed.

In case of compulsory misses, it is not possible to avoid these misses since the first access is to a block that is not in the cache. Fortunately, the frequency of these misses tends to be quite small compared to other cache misses.

| Block Size | Cache Size |        |        |        |        |

|------------|------------|--------|--------|--------|--------|

|            | 1K         | 4K     | 16K    | 64K    | 256K   |

| 16         | 15.05 %    | 8.57 % | 3.94 % | 2.04 % | 1.09 % |

| 32         | 13.34 %    | 7.24 % | 2.87 % | 1.35 % | 0.70 % |

| 64         | 13.76 %    | 7.00 % | 2.64 % | 1.06 % | 0.51 % |

| 128        | 16.64 %    | 7.78 % | 2.77 % | 1.02 % | 0.49 % |

| 256        | 22.01 %    | 9.51 % | 3.29 % | 1.15 % | 0.49 % |

**Table 1**. Actual miss rate versus block size for five different-sized caches. Note that for a 1-KB cache, 64-byte, 128-byte, and 256-byte blocks have a higher miss rate than 32-byte blocks. In this example, the cache would have to be 256 KB in order for a 256-byte block to decrease misses [Patterson & Hennessy '96].

Table 1 shows the trade-off of block size versus miss rate for a set of programs and cache sizes. Larger cache and block sizes reduce compulsory misses since larger blocks take advantage of spatial locality. At the same time, the larger blocks increase any miss penalty. Since they reduce the number of blocks in the cache, larger blocks may increase conflict misses and even capacity misses if the cache size is small.

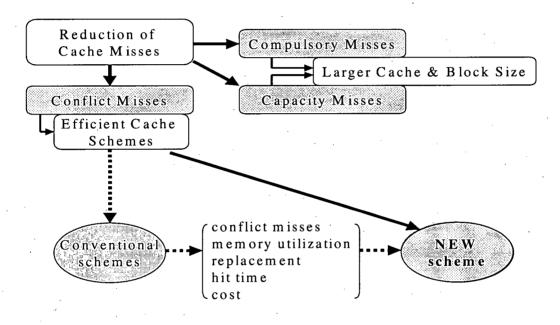

Figure 8. This cache example has eight block frames and memory has 32 blocks [Patterson & Hennessy '96].

The basic mapping functions can be categorized into the following types:

- If a block can be placed anywhere in the cache, the cache is said to be *fully-associative*;

- If each block has only one place it can appear in the cache, the cache is said to be *direct-mapped*. The mapping is usually (Block address) MOD (Number of blocks in cache);

• If a block can be placed in a restricted set of places in the cache, the cache is said to be *set associative*. A set is a group of blocks in the cache. A block is first mapped onto a set, and then the block can be placed anywhere within that set. The set is usually chosen by bit selection; that is, (Block address) MOD (Number of sets in cache). If there are n blocks in a set, the cache replacement is called n-way set associative.

Figure 8 shows that the restrictions on where a block is placed create three categories of cache organization. The set-associative organization shown has four sets with two blocks per set, and is called two-way set associative. Assume that there is nothing in the cache and that the block address needed identifies lower-level block 28. The three options for caches are shown left to right. In fully-associative, block 28 from the lower level can go into any of the eight block frames of the cache. With direct-mapped, block 28 can only be placed into block frame 4 (28 modulo 8). In two-way set associative, the block is to be placed anywhere in set 0 (28 modulo 4). With two blocks per set, this means block 28 can be placed either in block 0 or block 1 of the cache. The vast majority of processor caches today are direct-mapped, two-way set associative, or four-way set associative.

#### **1.3.2 Branch Mispredictions**

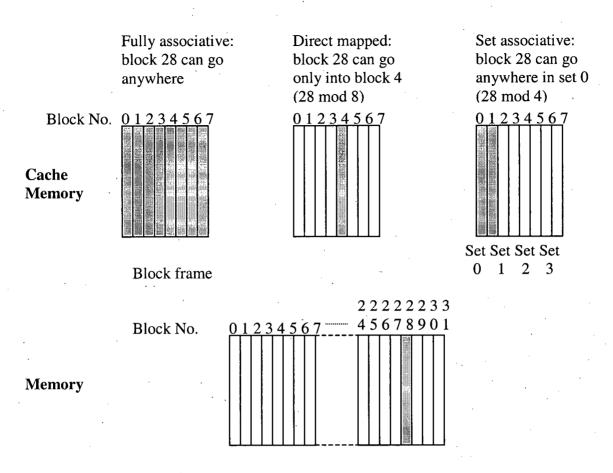

#### Figure 9. Reduction of Branch Mispredictions (overview).

Figure 9 shows methods for the reduction of branch mispredictions, which are categorized into direct and indirect branch mispredictions. Direct branches can be predicted with two-level branch predict schemes with hit ratios of up to 97%. However, it cannot be used for indirect branches which have more than one target. Chapter 3 explains indirect branch mispredictions in detail and discusses current indirect hybrid branch predictors such as Target Cache and Cascaded Predictor. These predictors work better than BTB-based predictors, which are used to predict for a single target such as direct branches, but they suffer from conflict misses in the first stage predictor and have inefficient update rules. Chapter 3 introduces a new indirect hybrid branch predictor called the GoStay2 predictor to improve the update rules and reduce conflict misses in the first stages.

Branch prediction is a key mechanism used to achieve high performance on multiple issue, deeply-pipelined processors. By predicting the branch outcome at the instruction fetch stage of the pipeline, ILP (Instruction Level Parallelism) can be exploited by providing a larger window of instructions [Kalamatianos & Kaeli '98].

#### **Branch** Classification

Branches can be categorized as conditional or unconditional and direct or indirect, resulting in four classes: conditional direct, conditional indirect, unconditional direct, and unconditional indirect. Of the four classes, prediction of conditional indirect branches are typically not implemented [Kalamatianos & Kaeli '98].

*Conditional direct* branches, which involve a condition, have two types: loop-closing conditional branches and other conditional branches. The loop-closing branches are backward branches that are taken for all but the last iteration of a loop. Other conditional branches are either taken or not taken, depending on whether the specified condition is true of false [Sima et al '97].

*Unconditional direct* branches, which are always taken, have three types: simple unconditional branches, branches to subroutines, and returns from subroutines. Simple unconditional branches do not save the return address, whereas branches to subroutines do. Returns from subroutines are dedicated unconditional branches performing a control transfer to the saved return address. In case of nested subroutines, while branching to and returning from the individual subroutines, the return addresses are saved and used in a last-in first-out (LIFO) manner.

A conditional/unconditional direct branch has a statically specified target that points to a single location in the program, whereas an unconditional indirect branch has a dynamically specified (i.e. computed) target that may point to any number of locations, multi-targets, in the program. Indirect branches with multi-targets are harder to predict accurately than single-target direct branches.

Driesen & Holzle ('98) also classified branches according to the number of different targets encountered in a program run (SPECint95 and object oriented languages): one target, two targets, and more than two targets. Branches with only one target constitute 67% of all branches; 18% of all branches jump to two targets and branches with three or more targets constitute 15% of all branches.

#### **Branch Predictors**

There are several types of branch predictors such as one-level, two-level, hybrid, etc. For the one-level predictor, a BTB (branch target buffer) is commonly used. BTB is a cache that contains the address of the branch instructions and their target addresses. The BTB is accessed in the fetch stage to predict the state of a branch instruction. If a hit occurs, then the current instruction is a taken branch. The PC (program counter) is loaded with the target address from BTB, and fetching starts from the new PC. For indirect branch, the taken address is the last computed target for the indirect jump. Unfortunately, BTB-based prediction schemes perform poorly for indirect jumps [Chang et al '97].

The two-level branch predictor uses two levels of history to make branch predictions [Yeh and Patt '92]. The first-level of history records the outcomes of the most recently

executed branches and the second-level history keeps track of the more likely direction of a branch when a particular pattern is encountered in the first level history. The 2-level branch predictor uses one or more k-bit shift registers, called branch history registers, to record branch outcomes of the most recent k branches. It uses one or more arrays of 2-bit saturating up-down counters, called a Pattern History Table (PHT), to keep track of the more-likely direction for branches. The lower bits of the branch address select the appropriate PHT and the value in the Branch History Register (BHR) selects the appropriate 2-bit counter to use within that PHT. There are many variations of two-level predictor. In Chapter 3, we will discuss various branch predictors in detail.

According to Sima et al ('97), the prediction accuracy of BTB is less than 70% in the processor MC88110. In order to improve the prediction accuracy of simple BTB, more complex hardware such as a two-level adaptive BTB, which can detect more varied branch execution sequences and treat them individually, has been proposed to take advantage of the relationship between nearby branches to improve its branch prediction accuracy. Even if the misprediction rate is less than 10%, the residual misprediction penalty that these programs incur still deteriorates processor performance significantly.

#### **Branch Misprediction Penalty**

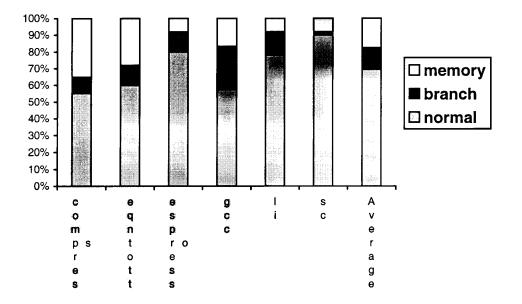

In Figure 10, Bondi et al ('96) show the total CPI (Cycles Per Instruction) for the model classified as normal processing, branch misprediction penalty, and memory access wait cycles (imperfect cache). They evaluated x86 traces with the performance model of a microprocessor design comprising a moderate-depth pipeline, 2-bit branch predictor, 4

integer execution resources, and on-chip instruction and data caches. The SPECint92 traces were generated by running the subject program on a PC under DOS after compilation with the gcc compiler from DJGPP (one of SPECint92 benchmark programs).

.

Figure 10. Components of Total CPI (Cycles Per Instruction) [Bondi et al. '96]

Of the total processing expended, normal processing consumes about 70%, branch consumes about 13% and memory access consumes about 17%. Together, branch penalties and memory waits waste about 30% of the overall processing effort. So if the branch misprediction penalty and memory access wait cycles can be reduced further, the system performance can be improved substantially. For example, if the branch accuracy

rate is increased from 95.2% to 96.0%, then the misprediction rate can be reduced up to 17.6%. If the recovery time from misprediction is reduced, it also improves the overall CPI.

According to Bondi et al ('96), mispredicted branch instructions are categorized into two types: branches that are repeatedly mispredicted over program life, and branches that are mispredicted just once over program life. They showed that branches that have been previously mispredicted cause most mispredictions. This behavior suggests that there is a need to hold the flushed branch instructions caused by conflict misses in a specific cache memory in the processor.

#### **1.4 Contributions and summary**

As object-oriented languages are widely used, procedure calls are increasing frequently in application programs, causing a significantly increased number of conflict misses in the instruction flow. Basically, the instruction flow has several problems to solve: conflict misses in the instruction cache memory, conditional or unconditional branch throughput, direct or indirect branch prediction, and misprediction penalty. Current high performance architectures such as superscalar processors use branch prediction to speculatively execute instructions beyond an unresolved branch. If the branch is mispredicted, this work is lost, and execution must restart right after the branch instruction.

As we discussed in section 1.2, there is a need to reduce cache misses and branch mispredictions for improving system performance. The contributions of this thesis lie in the fact that:

- 1. By developing a new cache scheme called the TAC (Thrashing-Avoidance Cache)

- Cache miss rates can be reduced significantly compare to other conventional cache memory schemes.

- Since the TAC has almost the same hardware complexity as n-way setassociative, it is possible to increase system performance with the same hardware cost as n-way set-associative.

- As small on-chip cache memory is popular, there is a need to have more efficient memory storage management than n-way set-associative. The TAC provides this by using sophisticated mapping functions.

- The TAC scheme can be applied to the techniques for HPC in regard to instruction flows.

- 2. By developing a new indirect branch predictor called the GoStay2

- Indirect branch mispredictions can be reduced significantly compared to other conventional indirect branch predictors.

- Since the GoStay has almost the same hardware complexity as the other branch predictors, it is possible to increase system performance with the same hardware cost as the others.

- The GoStay2 can increase instruction level parallelism by improving update rules for the indirect branch predictions.

There are four chapters and one appendix in this thesis. They include:

Chapter 1, Overview and summary, describes high performance computing, which is divided into three parts including goals, architectures, and techniques. Moore's Law is

discussed in order to understand the future trend of processors. From Moore's Law, we outlined problem definitions such as cache misses and branch mispredictions, which degrade system performance because of the gap between processors and memory. General background for cache misses and branch mispredictions are discussed, and a new cache scheme and branch predictor are suggested;

Chapter 2, Cache misses, gives an overview and problems of conventional cache schemes and introduces a new cache scheme called the TAC (Thrashing-Avoidance Cache). Through the experimental results, it is shown that the TAC schemes reduce conflict misses better than conventional cache schemes;

Chapter 3, Branch Mispredictions, explains branch mispredictions caused by direct and indirect conditional branches and discusses current branch predictors that were recently proposed to reduce indirect branch predictors. Since those branch predictors have an inefficient update rule, a new branch predictor called the GoStay2 predictor is introduced for improving branch prediction rates. Through experiments, it is shown that the GoStay2 works better than other indirect branch predictors such as Cascaded predictors or Target Cache;

Chapter 4, Conclusion and Future Research, summarizes the experimental results for the TAC scheme and GoStay2 predictor compared to conventional schemes and suggests future research in regard to reducing memory latencies and speculative work;

Appendix A, Experimental results for TAC schemes, gives detailed tables of the experimental results for TAC schemes.

# **Chapter 2 Reduction of instruction cache misses**

Due to the increased complexity of application programs over the past decade, objectoriented languages are replacing traditional languages as a result of convenient code reusability and maintainability. However, it has also been observed that the run-time performance of object-oriented programs can be improved by reducing the impact caused by instruction cache misses. This thesis presents a new cache scheme called TAC (Thrashing-Avoidance Cache), which can effectively reduce instruction cache misses caused by procedure call/returns. The TAC scheme employs N-way banks and XOR mapping functions. The main function of the TAC is to place a group of instructions separated by a call instruction into a bank according to the Bank Selection Logic (BSL) and Bank-originated Pseudo-LRU replacement policy (BoPLRU). After the BSL selects a bank initially on an instruction cache miss, the BoPLRU will determine the final bank for updating a cache line as a correction mechanism. These two mechanisms can guarantee that recent groups of instructions exist in each bank safely. A simulation program, TACSim, has been developed by using Shade and Spixtools, provided by SUN Microsystems, on an ultra SPARC/10 processor. Our experimental results show that TAC schemes reduce conflict misses more effectively than skewed-associative caches for both C (9.29% improvement) and C++ (44.44% improvement) programs on L1 caches. In addition, TAC schemes also allow for a significant miss reduction on Branch Target Buffers (BTB).

# 2.1 Introduction

For current microprocessors, multi-instruction issues are a popular method of increasing system performance. Therefore, instruction cache misses can severely limit the performance of high-speed microprocessors.

Several researchers have shown that many instruction cache misses are caused by the frequent procedure call/returns in object-oriented languages.

|                                                                |         |                               | +                     |                  | · · · · · · · · · · · · · · · · · · ·                                                                |

|----------------------------------------------------------------|---------|-------------------------------|-----------------------|------------------|------------------------------------------------------------------------------------------------------|

|                                                                |         | C++ mean (12<br>C++ programs) | C mean<br>(SPECint92) | Ratio<br>(C++/C) | Description                                                                                          |

| Туре                                                           |         | Object Oriented               | Traditional           |                  |                                                                                                      |

| Call/Return Frequency                                          |         | 4.6%                          | 0.7%                  | 6.7              | Procedure calls and returns                                                                          |

| Basic block                                                    |         | 4.8                           | 5.9                   | 0.8              | Instructions per block size                                                                          |

| Function size                                                  | Dynamic | 48.7                          | 152.8                 | 0.3              | During program run-time                                                                              |

|                                                                | Static  | 27.3                          | 44.3                  | 0.6              | Property of program itself                                                                           |

| Inst. Cache<br>miss rate<br>(Direct<br>mapped,<br>32byte line) | 4 K     | 5.83                          | 3.49                  | 1.67             | C++ programs tend to                                                                                 |

|                                                                | 8 K     | 3.98                          | 2.32                  | 1.72             | perform many calls to small functions and benefit less                                               |

|                                                                | 16 K    | 2.47                          | 1.18                  | 2.09             | from the spatial locality of<br>larger cache blocks.<br>Average Ratio (C++/C):1.95                   |

|                                                                | 32 K    | 1.37                          | 0.59                  | 2.32             |                                                                                                      |

| Data cache<br>miss rate<br>(Direct<br>mapped,<br>32byte line)  | 4 K     | 13.98                         | 13.09                 | 1.06             | Since the miss rates are quit<br>similar, there is little room<br>to improve data cache<br>features. |

|                                                                | 8 K     | 9.20                          | 9.08                  | 1.01             |                                                                                                      |

|                                                                | 16 K    | 6.35                          | 6.43                  | 0.98             |                                                                                                      |

|                                                                | 32 K    | 4.42                          | 4.31                  | 1.03             | Average Ratio (C++/C):1.0                                                                            |

Table 2. Behavioral differences between C and C++ Programs [Calder et al '94]

In Table 2, Calder et al ('94) showed that object-oriented programs (C++) execute almost seven times more calls (4.6 % versus 0.7 %) and have smaller function sizes (48.7 versus 152.8 instructions/function) than traditional programs (C). While C programs execute large monolithic functions to perform a task, C++ programs tend to perform

many calls to small functions. Thus, C++ programs benefit less from the spatial locality, and suffer more from function call overhead.

The smaller function size of C++ programs is another cause of poor instruction cache misses. According to Calder et al ('94), programs executing a small number of instructions in each function, such as C++, may suffer from instruction cache conflicts. For example, two mutually recursive functions may be aligned to the same cache memory addresses and constantly displace each other from the cache. C programs execute more instructions per function invocation, meaning that more work is done within a particular function.

Holzle & Ungar ('94) also showed that for instruction cache behavior the miss ratios of object-oriented programs are significantly higher for most cache sizes and that the median miss ratio is 2 – 3 times higher than traditional programs. Meanwhile, Calder et al ('94) and Holzle & Ungar ('94) observed that the data cache misses for both programs were seen to be similar. So this thesis has focused on developing an effective cache scheme to reduce the instruction cache misses of object-oriented programs, which can be much higher than traditional programs because of the frequent call/returns.

In general, if a cache size is less than 32KB, conflict misses can degrade system performance significantly. For example, for a direct-mapped cache, conflict misses are about 60% of the total cache misses of a small-sized cache of 8KB [Gonzalez et al '97]. If we do not want to increase the cache size, we need to design a small-sized, low-cost cache scheme to improve the cache miss ratio by reducing only the conflict misses which are mainly caused by call/returns. This thesis presents a new cache scheme called TAC

(Thrashing-Avoidance Cache), which can effectively reduce instruction cache misses caused by call/returns.

This chapter is organized as follows: Section 2.2 explains cache misses and skewedassociative caches; section 2.3 presents a new instruction cache scheme called TAC (Thrashing-Avoidance Cache); section 2.4 describes simulation methodology and benchmark programs; section 2.5 presents our simulation results; and section 2.6 provides our chapter conclusions.

### **2.2 Cache Misses**

As we discussed in chapter 1, there are three types of cache misses namely: compulsory, capacity, and conflict misses. In this section, several conventional cache schemes are compared for determining the most effective conventional cache scheme for reducing conflict misses.

#### **2.2.1** Total miss ratios vs. conflict miss ratios

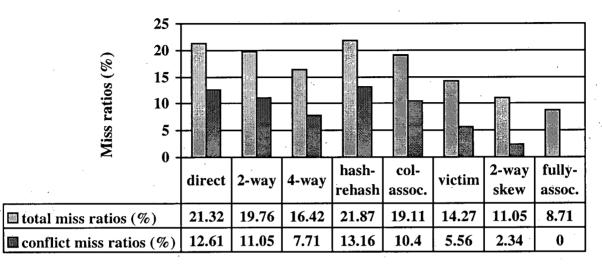

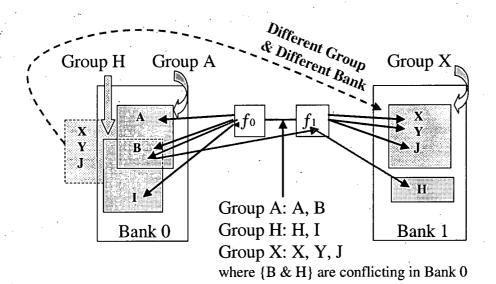

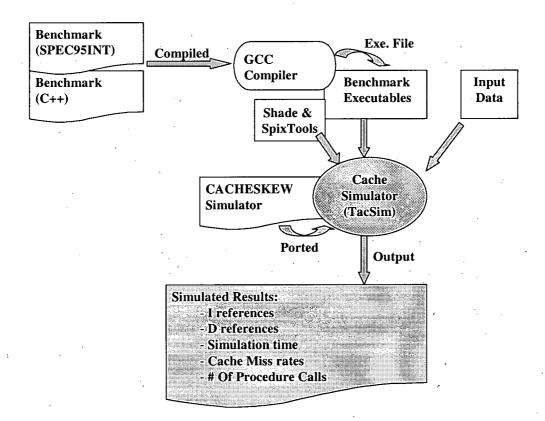

Gonzalez et al ('97) generated the miss ratios for several cache schemes as shown in Figure 11: direct-mapped, 2-way set-associative, 4-way set-associative, hash-rehash, column-associative, victim, and 2-way skewed-associative. They obtained the results in Figure 11 by using the SPEC95 benchmark suite and by implementing a cache memory (8 kilobytes capacity and 32 bytes per line).

For comparison, the miss ratio of a fully-associative cache is shown in the last column. For each organization, the difference between its miss ratio and that of a fully-associative cache represents the conflict miss ratio. For example, the 'direct-mapped' cache has a miss ratio of '21.32' in Figure 11. Here, '21.32' means the total miss ratio (compulsory + capacity + conflict) while '12.61' is the conflict miss ratio which is computed as (total miss ratio for a scheme – total miss ratio for the fully-associative scheme).

Various cache schemes

Figure 11. Miss ratios (%) of the various cache schemes [Gonzales et al '97].

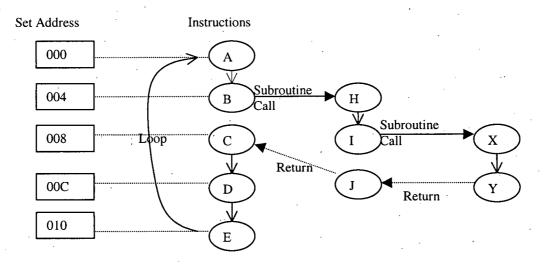

From the results in Figure 11, the hash-rehash scheme has a miss ratio similar to that of a direct-mapped cache. Although both have similar access times, the hash-rehash scheme requires two cache probes for some hits. Hence, the direct-mapped cache will be more effective. The victim cache scheme removes many conflict misses and it outperforms a 4way set-associative cache. The 2-way skewed-associative cache offers the lowest miss ratio of the existing schemes and is significantly lower than a 4-way set-associative cache [Gonzalez et al '97].

Figure 12 shows how conflict misses can happen in a cache memory. It is assumed that there are 10 instructions (A, B... X, and Y) as an assembly code program in Figure 12, which include two procedure calls (B to H and I to X) and two returns (Y to J and J to C). It is also assumed that (B, H), (C, I, X), and (D, J, Y) have the same set address (cache

memory index), namely 004, 008, and 00C, and that there is a stack register for the two return addresses. The arrows in Figure 12 show instruction flows for executing this program.

Figure 12. An example of instructions with two procedure calls.

Figure 13 shows the contents of a direct-mapped cache during execution of the two loops of code shown in Figure 12. In the case of the set address '008', there are two conflict misses with three memory accesses (to main memory) in the first loop and three conflict misses with three memory accesses in the second loop.

Set address

000

004

008

00C

010

...

Tag Cache Instructions

Α

₿Н

hk c

K D

Ε

Set address

Tag Cache Instructions

|      | _ |     |              |

|------|---|-----|--------------|

| ·000 |   | xxx | Α            |

| 004  |   | xxx | ивн          |

| 008  |   | xxx | dhxc         |

| 00C  |   | xxx | <b>d</b> k d |

| 010  |   | xxx | E            |

|      |   |     |              |

|      | - |     |              |

First Loop

XXX

XXX

XXX

xxx

xxx

. . .

Second Loop

Figure 13. Execution of the code shown in Figure 12 in a direct-mapped cache.

For the direct-mapped cache in Figure 13, problems occur when alternating memory references point to the same set-address. Each reference causes a cache miss (conflict) and replaces the entry just replaced, causing a lot of overhead. The popular word for this is thrashing. When there is a great deal of thrashing, a cache can be more of a liability than an asset because each cache miss requires that a cache line be refilled - an operation that moves more data than merely satisfying the reference directly from main memory [Handy '93]. However, the direct-mapped cache has advantages of simplicity of memory access and hit time.

Figure 14 shows the contents of a fully-associative cache which has no conflict misses.

| Tag   | Cache Instructions |       | Tag   | Cache Instructions |

|-------|--------------------|-------|-------|--------------------|

| xxxxx | A                  |       | xxxxx | A                  |

| xxxxx | В                  | ].    | xxxxx | В                  |

| xxxxx | Н                  | ] →   | xxxxx | H, _               |

| xxxxx | Ι                  | ] · . | xxxxx | I                  |

| xxxxx | x                  |       | XXXXX | X                  |

| xxxxx | Y                  |       | xxxxx | Y                  |

| xxxxx | J                  |       | xxxxx | J                  |

| xxxxx | C C                |       | XXXXX | С                  |

| xxxxx | D                  |       | xxxxx | D                  |

| xxxxx | E                  |       | xxxxx | E                  |

| •••   |                    | ]     | •••   |                    |

First Loop

Second Loop

(b) Fully-associative cache.

For the fully-associative cache in Figure 14, any block (i.e., instruction) from the main memory can be placed anywhere in the cache. After being placed in the cache, a given block is identified uniquely by its main memory block number and referred to as the tag, which is stored inside a separate tag memory in the cache. The fully-associative cache makes the most flexible and complete use of its capacity, storing the blocks where it needs to, but there is a penalty to be paid for this flexibility: the tag memory must be searched in its entirety for each memory reference. Moreover, it is more expensive in terms of gates than other access-by-address memories, because of the need to do simultaneous bit-by-bit comparisons of all bits in the memory [Heuring & Jordan '97].

To reduce memory stalls effectively, there is a need to have a sophisticated form of cache memory, which has:

- less conflict misses;

- simplicity (access-by-address);

- faster hit time;

- efficient cache memory storage management; and

- low hardware costs.

### 2.2.2 Skewed-associative caches

In the previous section, Gonzalez et al ('97) showed that a 2-way skewed-associative cache offers the lowest miss ratio, and is significantly lower than that of a 4-way set-associative cache. Therefore, this scheme is discussed in detail in this section.

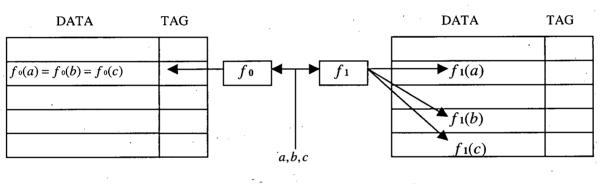

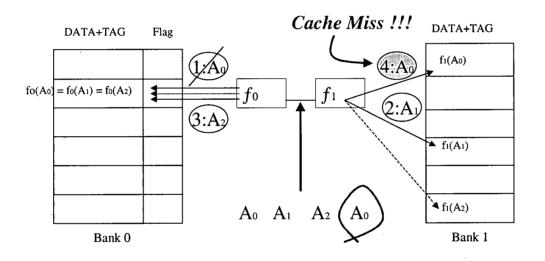

Skewed associative caches have been previously proposed by Seznec ('93). An N-way skewed-associative cache consists of N distinct banks that are accessed simultaneously with different mapping functions. For example, Figure 15 shows that a 2-way skewed-associative cache consists of two banks of the same size that are simultaneously accessed with two different mapping functions. That means a memory block at address 'd' may be mapped onto physical line  $f_0$  (d) in bank 0 or onto  $f_1$  (d) in bank 1, where  $f_0$  and  $f_1$  are different mapping functions.

bank 1

**Figure 15**. a, b, and c compete for the same location in bank 0, but can be present at the same time, as they do not map to the same location in bank 1 [Seznec '97].

#### Mapping functions

Bodin & Seznec ('95) presented skewing functions that are obtained by XORing a few bits in the address of a memory block. Let a skewed associative cache be built with 2 or 4 cache banks, each one consisting of  $2^n$  cache lines of  $2^c$  bytes, and let  $\sigma$  be the perfectshuffle on n bits, so that the data block at memory address  $A_3 2^{c+2n} + A_2 2^{n+c} + A_1 2^c$  may be mapped:

- on a cache line  $A_1 \oplus A_2$  in cache bank 0

- 2. or on a cache line  $\sigma(A_1) \oplus A_2$  in cache bank 1

- 3. or on cache line  $\sigma^2(A_1) \oplus A_2$  in cache bank 2 (on a 4-way)

- 4. or on cache line  $\sigma^3(A_1) \oplus A_2$  in cache bank 3 (on a 4-way)

## **Replacement policies**

1.

Figure 16. One of replacement polices, PLRU, for a 2-way skewed-associative cache.

Figure 16 shows that a 2-way skewed-associative cache uses a Pseudo-LRU (Least Recently Used) replacement policy by associating a one-bit flag to each line in bank 0 when a miss occurs on a cache [Seznec '97]:

- A flag bit is associated with each line in bank 0: when the line is indexed, the flag bit is set when the data is in bank 0 and reset when the data is in bank 1;

- On a miss, the flag of the line selected in bank 0 is read: when this flag is 1, the missing line is written in bank 1, otherwise the missing line is written in bank 0.

# 2.3 Thrashing-Avoidance Cache (TAC)

In the previous section, several cache memory schemes were investigated in detail: a direct-mapped scheme was shown to have the advantages of fast cache hit time and simplicity, but it has the problem of conflict misses that can adversely affect system performance. Using a fully-associative scheme can solve the conflict misses, but it is too expensive for implementation and inefficient for accessing to memory references. Even though a 2-way skewed-associative scheme partially resolves these problems, it still has an inefficient replacement policy for frequent procedure call/returns, which can increase conflicts for certain locations in a cache memory.

There are two main reasons for designing a new instruction cache memory:

- As technology changes, smaller on-chip L1 caches (less than 32 Kbytes) have replaced large external caches (greater than 256 Kbytes);

- As object-oriented languages become more widely used, procedure calls tend to increase in application programs, causing an increasing number of conflict misses.

Thus, there is a need to have a new cache memory scheme to reduce instruction cache misses focused on reducing thrashing conflict misses (i.e., a commonly used location is displaced by another commonly used location in a cycle).

# 2.3.1 An overview of a TAC scheme

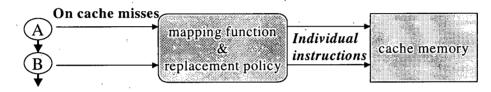

If the cache size is relatively small, conflict misses can degrade system performance significantly [Gonzales et al '97]. Figure 17(a) shows that, in a conventional cache scheme, individual instructions (A or B) are placed or replaced into cache memory according to a mapping function and replacement policy on a cache miss. A conventional cache scheme works well for reducing conflict misses for traditional programs but not for object-oriented programs since traditional programs have fewer calls and larger function sizes than object-oriented programs (refer to section 2.1).

A: an instruction except 'call' B: 'call' instruction

(a) A conventional cache scheme

(b) A TAC scheme

Figure 17. The basic operations of a conventional cache scheme and a TAC scheme.

Figure 17(b) shows the basic operations of a TAC scheme, which can reduce conflict misses effectively for object-oriented programs by grouping instructions. In Figure 17(b), a group of instructions (A and B) separated by call instruction (B) are placed and replaced into cache memory according to a mapping function or replacement policy on a cache

miss. Our measurements shows that grouping instructions benefits more from localities than individual instructions in both traditional and object-oriented programs.

A TAC scheme is built with N distinct banks. Since Gonzales et al ('97) showed that XOR mapping functions work well for reducing conflict misses, TAC employs XOR mapping functions (refer to section 2.2.2) for accessing the instruction cache memory.

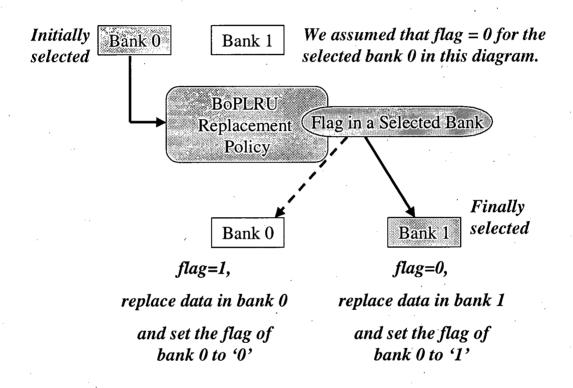

On a cache miss, data must be fetched from a lower level memory according to the XOR mapping functions and replacement policies, the Bank Selection Logic (BSL, refer to section 2.3.2) and Bank-originated Pseudo LRU replacement policy (BoPLRU, refer to section 2.3.3). The BSL selects a bank initially according to the number of call instructions and the BoPLRU determines a final bank according to the replacement policy by using a flag.

The BSL and BoPLRU can guarantee that recent groups of instructions exist in each bank safely. So if the frequency of call/returns is increased, the TAC scheme works well since the manageable size of an instruction group is smaller. For example, if the average number of instructions per call of an object-oriented program is 40 and that of a traditional program is 100, then the TAC scheme of an object-oriented program will work better than a traditional one for limited cache sizes.

In a TAC scheme, each cache line consists of tag, data, and flag. The tag word consists of an address tag and some other status tags. The bit length of the flag is determined by the N distinct banks; that is, an n-bit flag represents  $2^n$  banks or an N-Way (N =  $2^n$ ) cache scheme. For convenience, this thesis represents the cache line of a TAC scheme as just a flag and data throughout this paper and omits the tag part.

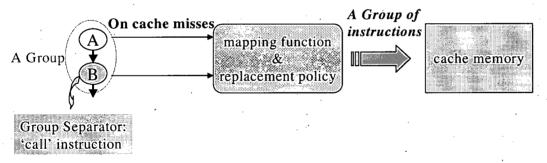

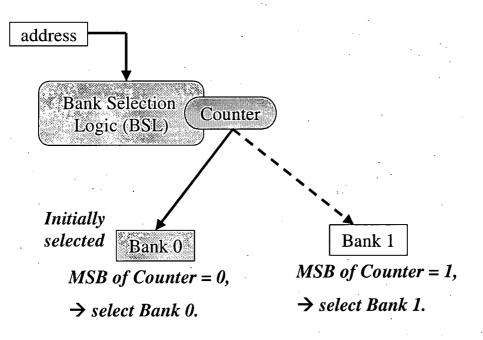

#### 2.3.2 Bank Selection Logic (BSL) – Initial Bank Selection

The function of the Bank Selection Logic (BSL) is to select a bank initially on a cache miss according to a fixed frequency of the procedure call instructions. The BSL employs an x-bit counter for counting the frequency of call instructions. The x-bit counter will be increased by one whenever a fetched instruction proves to be a call instruction. An n-MSBs (n-Most Significant Bits) of the x-bit counter represents a selected bank for each instruction. Each bank can be selected for every  $2^{r-n}$  procedural calls. For example, if x = 2 and n = 1, then there are two banks ( $2^n = 2$ ) and a bank is switched to the other bank for every two procedure calls ( $2^{r-n} = 2$ ). A group of instructions terminated by a procedure call can be placed into the same bank through the BSL (Bank Selection Logic) and XOR mapping functions. The goal of the BSL is to help each bank to share instructions equally according to the occurrence of procedure call instructions.

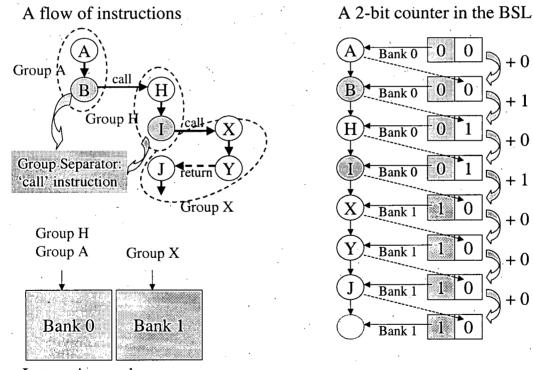

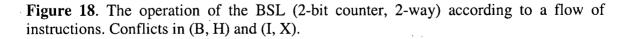

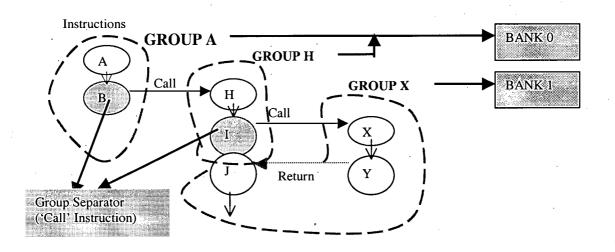

As an example, Figure 18 shows how a 2-bit counter (x = 2 and n = 1) in the BSL works with the flow of example instructions in Figure 18. The left side of Figure 18 shows the flow of instructions. Each call instruction works as a separator for grouping instructions. For a group of instructions, the next call instruction becomes the last one in the group. In Figure 18, it is assumed that there are cache conflicts in (B, H) and (I, X). The detailed operations of the 2-bit counter in the BSL on the right side of Figure 18 are:

- Instruction A is fetched. On a cache miss, the flag of the selected line in bank 0 is read. A is not a call instruction, so there is no change in the 2-bit counter (+ 0);