# DESIGN AND EVALUATION OF A HIGH PERFORMANCE MULTI-PRIORITY MULTICAST ATM AND IP SWITCH

1

by

## JOSEPH CHU

## B.A.Sc., Queen's University, Canada, 1996

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE DEGREE OF MASTER OF APPLIED SCIENCE

IN

# THE FACULTY OF GRADUATE STUDIES

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

We accept this thesis as conforming

to the required standard

#### THE UNIVERSITY OF BRITISH COLUMBIA

June, 2002

© Joseph Chu, 2002

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of <u>Electrice</u> and <u>Computer</u> Engineering.

The University of British Columbia Vancouver, Canada

Date June 3/2002

## **Abstract**

Asynchronous Transfer Mode (ATM) and Internal Protocol (IP) are two commonly used protocols for the demands of high speed networking technology. The switching technologies employed in ATM cell and IP packet switches have seen extensively researched and studied in recent years. However, most of the switches developed have room for improvement in performance and cost-efficiency. Furthermore, most switching research is based on uniform incoming cell/packet traffic, which is very different from real time traffic. Real time traffic is not only bursty, but also involves multiple classes of prioritized traffic, as well as multicast traffic.

In this thesis, a high performance ATM and IP switch architecture is introduced. The switching architecture is based on two existing technologies namely Random Early Detection (RED), and the internal buffer. Simulation results show that with a little modification of these schemes, a switch can perform extremely well under many kinds of real time traffic patterns, including multi-priority and multicast. In addition, the proposed switching architecture shows that cell loss ratio can be arbitrarily reduced using a finite internal buffer size.

# **Table of Contents**

,

| Abstract          |                                 | ••••••       | ii                                       |

|-------------------|---------------------------------|--------------|------------------------------------------|

| Table of Contents |                                 | ••••         | iii                                      |

| List of Figures   | •••••                           | •••••        | vi                                       |

| List of Tables    |                                 | •••••        | ix                                       |

| Acknowledgment    |                                 |              | x                                        |

| Chapter 1         | Introduct                       | ion          |                                          |

| 1.1               | Features                        | of Next-Ge   | neration Switching Fabrics 2             |

| 1.2               | Motivation and Scope of Thesis4 |              |                                          |

| 1.3               | Thesis C                        | ontributions | 5 6                                      |

| 1.4               | Organiza                        | tion of the  | Thesis                                   |

| Chapter 2         | Switch A                        | rchitecture  |                                          |

| 2.1               | Switch E                        | lement       |                                          |

|                   | 2.1.1                           | Knockout     | Switching Element                        |

|                   | 2.1.2                           | Roxanne S    | Switching Element 16                     |

|                   | 2.1.3                           | Coprin Sv    | vitching Element 19                      |

|                   | 2.1.4                           | Athena Sv    | vitching Element 25                      |

|                   | 2.1.5                           | Summary      | of Different Switching Elements 29       |

| 2.2               | Switch F                        | abric        |                                          |

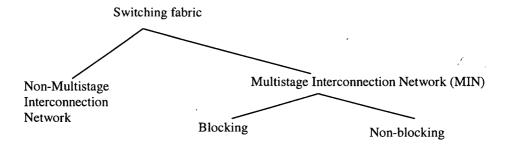

|                   | 2.2.1                           | Non-Mult     | istage Interconnection Networks (MIN) 31 |

|                   | 2.2.2                           | Multistage   | e Interconnection Networks (MIN) 32      |

|                   |                                 | 2.2.2.1      | Delta Networks                           |

|                   |                                 | 2.2.2.2      | MIN with Internal Blocking 35            |

|                   |                                 | 2.2.2.3      | MIN without Internal Blocking 41         |

| Chapter 3 | Bandwidth Optimization in Banyan Switches |                                            |    |

|-----------|-------------------------------------------|--------------------------------------------|----|

| 3.1       | Introduction                              |                                            |    |

| 3.2       | The Buffered-Dilated Banyan (BDB) Switch  |                                            |    |

| 3.3       | BDB Architectural Features                |                                            |    |

|           | 3.3.1                                     | Enqueuing in the DSE                       | 51 |

|           | 3.3.2                                     | Cell Forwarding in the DSE                 | 51 |

|           | 3.3.3                                     | Backpressure (BP) Controlling              | 53 |

|           | 3.3.4                                     | Multicasting Capabilities                  | 55 |

| Chapter 4 | Buffer N                                  | Ianagement                                 | 57 |

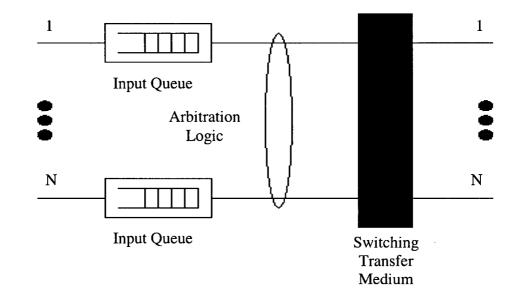

| 4.1       | Queuing                                   | g Technique                                | 57 |

|           | 4.1.1                                     | Introduction                               | 57 |

|           | 4.1.2                                     | Input Queuing                              | 57 |

|           | 4.1.3                                     | Output Queuing                             | 58 |

|           | 4.1.4                                     | Central Queuing                            | 59 |

|           | 4.1.5                                     | Recirculation Buffering                    | 60 |

|           | 4.1.6                                     | Comparison of Different Queuing Approaches | 60 |

| 4.2       | Buferrin                                  | g Management                               | 63 |

|           | 4.2.1                                     | Introduction                               | 63 |

|           | 4.2.2                                     | Random Early Detection (RED) Technique     | 64 |

| Chapter 5 | Perform                                   | ance of the Packet Switches                | 67 |

| 5.1       | Introduction                              |                                            | 67 |

| 5.2       | Input Tr                                  | affic Model                                | 67 |

|           | 5.2.1                                     | Uniform Traffic Pattern                    | 67 |

|           | 5.2.2                                     | Bursty Traffic Pattern                     | 67 |

|           | 5.2.3                                     | Load Varies under Poisson Distribution     | 68 |

| 5.3          | Performance Analysis under Independent Uniform Traffic 69 |  |

|--------------|-----------------------------------------------------------|--|

| 5.4          | Cell Loss and Stage Dilation                              |  |

| 5.5          | With Sliding Window and Back-Pressure                     |  |

| 5.6          | With Backpressure Control but no Sliding Window           |  |

| 5.7          | Without Sliding Window and Back-Pressure                  |  |

| 5.8          | Results for ATM Pattern 83                                |  |

| 5.9          | Results for IP Pattern                                    |  |

| Chapter 6    | Conclusions and Future Research Plan                      |  |

| 6.1          | Conclusion                                                |  |

| 6.2          | Future Research Plan                                      |  |

| Appendix A   | List of Standard Acronyms                                 |  |

| Bibliography |                                                           |  |

.

,

v

# **List of Figures**

r

.

| Figure 1 : Knockout Switching Element                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 9                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 : Knockout Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                                                                 |

| Figure 3 : Contention Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11                                                                                                                                 |

| Figure 4 : An 8 input/4 Output Concentrator                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                                                                                                 |

| Figure 5 : Shifter Function for 8 Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                                                                                                 |

| Figure 6 : Knockout Switch with a Multicase Module                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15                                                                                                                                 |

| Figure 7 : Multicast Module with a Cell Duplicator                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16                                                                                                                                 |

| Figure 8 : ISE Function Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                                                                                 |

| Figure 9 : Coprin Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                                                                                                 |

| Figure 10 : Extracting Packets in Buffer Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20                                                                                                                                 |

| Figure 11 : Four States of the Space Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21                                                                                                                                 |

| Figure 12 : Extracing Packets in Buffer Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                                                                                 |

| Figure 13 : Control of the Coprin Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                                                 |

| Figure 14 : The Athena Basic Switching Block                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26                                                                                                                                 |

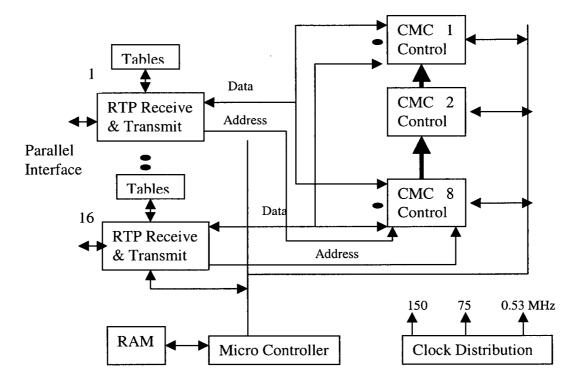

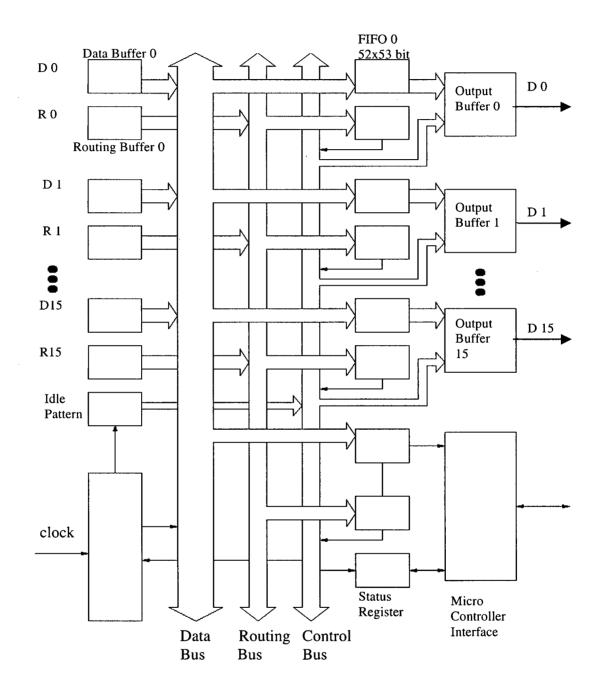

| Figure 15 : The CMC of the Anthena Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27                                                                                                                                 |

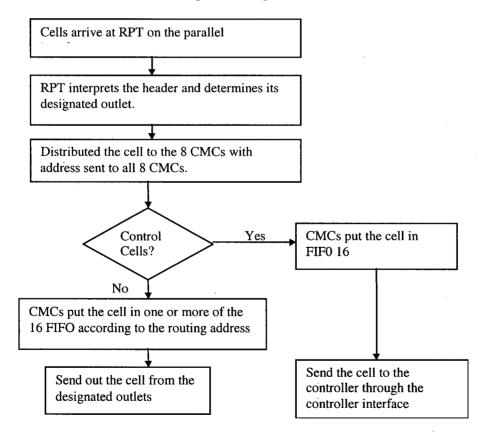

| Figure 16 : Sequency Diagram Showing how Athena Switch Handles Incoming Cell                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                                                                                                                                 |

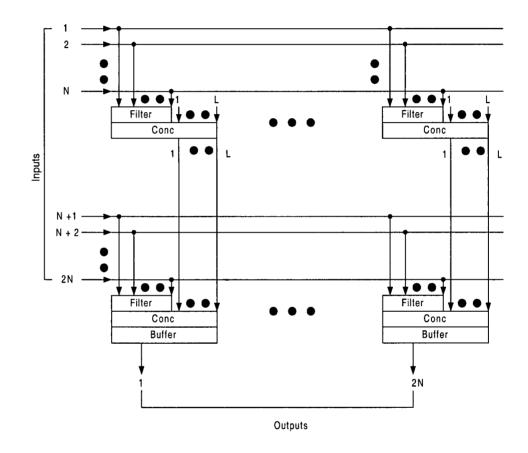

| Figure 17 : 2N x 2N Switch Built with N x N Knockout Switches                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                                                                                                                                 |

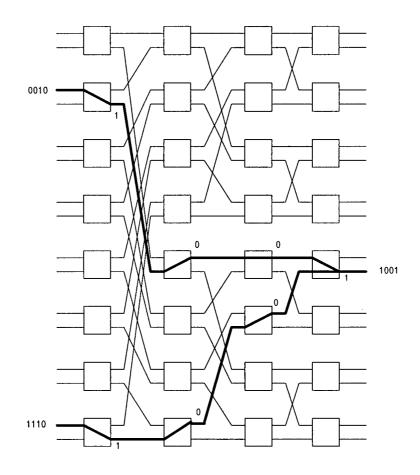

| Figure 18 : Self-Routing Properties of a Delta Network                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33                                                                                                                                 |

| Figure 18 : Self-Routing Properties of a Delta Network                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33<br>34                                                                                                                           |

| Figure 18 : Self-Routing Properties of a Delta Network<br>Figure 19 : Contention in a Delta Network                                                                                                                                                                                                                                                                                                                                                                                              | 33<br>34<br>39                                                                                                                     |

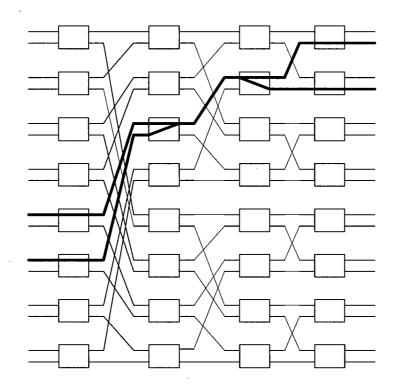

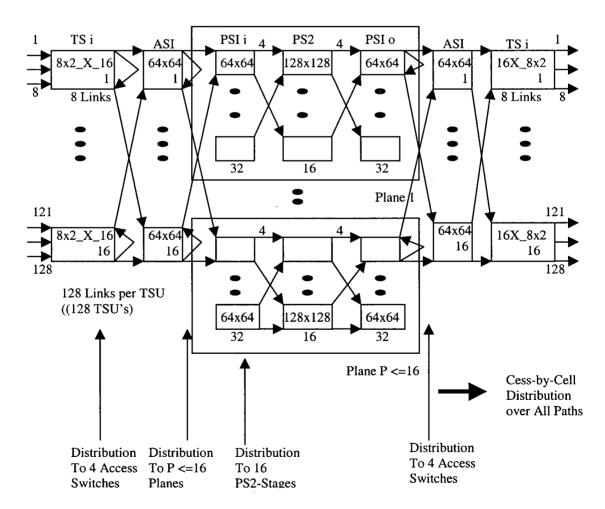

| Figure 18 : Self-Routing Properties of a Delta Network<br>Figure 19 : Contention in a Delta Network<br>Figure 20 : Roxanne Switching Fabric [22]                                                                                                                                                                                                                                                                                                                                                 | 33<br>34<br>39<br>42                                                                                                               |

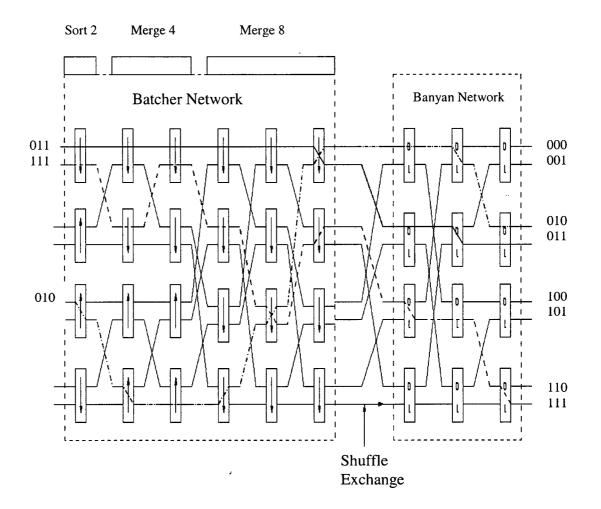

| <ul> <li>Figure 18 : Self-Routing Properties of a Delta Network</li> <li>Figure 19 : Contention in a Delta Network</li> <li>Figure 20 : Roxanne Switching Fabric [22]</li> <li>Figure 21 : Batcher-Banyan Network Topology</li> </ul>                                                                                                                                                                                                                                                            | <ol> <li>33</li> <li>34</li> <li>39</li> <li>42</li> <li>44</li> </ol>                                                             |

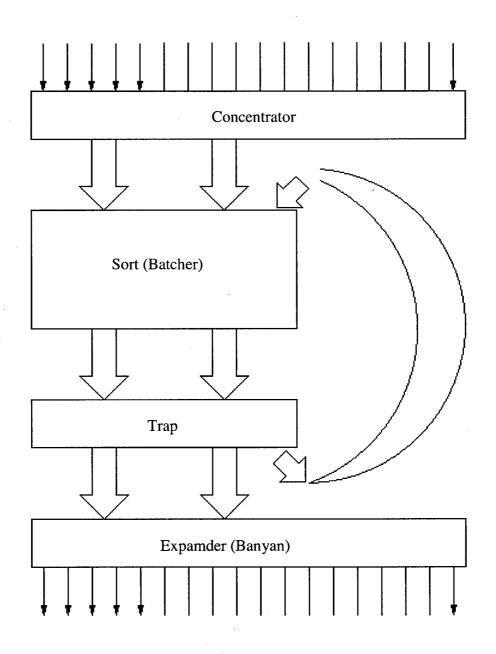

| Figure 18 : Self-Routing Properties of a Delta Network         Figure 19 : Contention in a Delta Network         Figure 20 : Roxanne Switching Fabric [22]         Figure 21 : Batcher-Banyan Network Topology         Figure 22 : Starlite Switch Architecture                                                                                                                                                                                                                                  | <ol> <li>33</li> <li>34</li> <li>39</li> <li>42</li> <li>44</li> <li>46</li> </ol>                                                 |

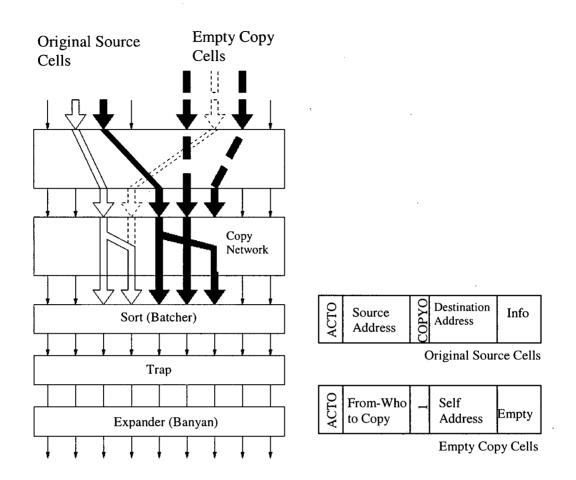

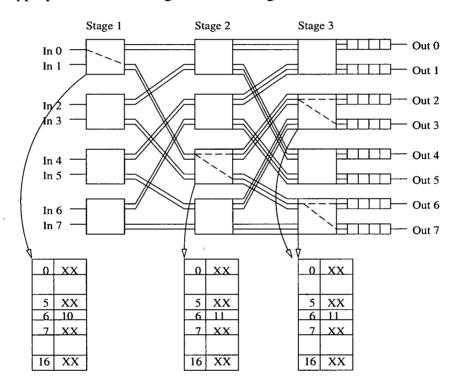

| Figure 18 : Self-Routing Properties of a Delta Network         Figure 19 : Contention in a Delta Network         Figure 20 : Roxanne Switching Fabric [22]         Figure 21 : Batcher-Banyan Network Topology         Figure 22 : Starlite Switch Architecture         Figure 23 : Multicast in Starlite                                                                                                                                                                                        | <ol> <li>33</li> <li>34</li> <li>39</li> <li>42</li> <li>44</li> <li>46</li> <li>49</li> </ol>                                     |

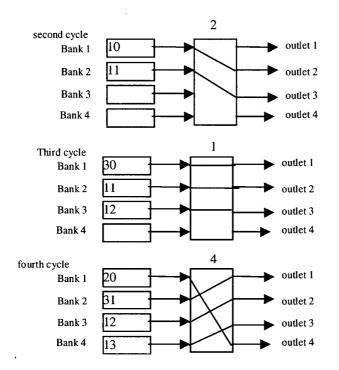

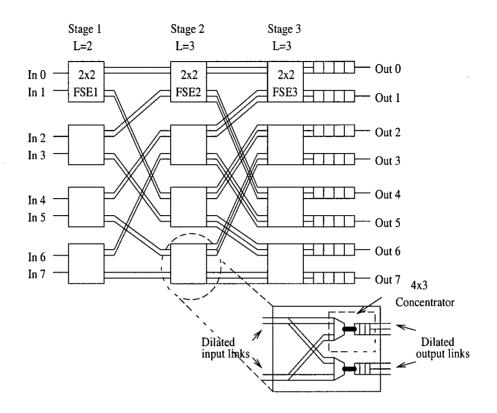

| <ul> <li>Figure 18 : Self-Routing Properties of a Delta Network</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>33</li> <li>34</li> <li>39</li> <li>42</li> <li>44</li> <li>46</li> <li>49</li> <li>al</li> </ul>                         |

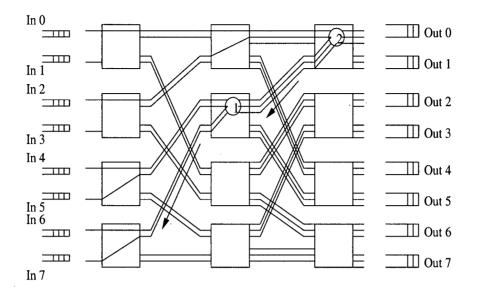

| <ul> <li>Figure 18 : Self-Routing Properties of a Delta Network.</li> <li>Figure 19 : Contention in a Delta Network</li> <li>Figure 20 : Roxanne Switching Fabric [22]</li> <li>Figure 21 : Batcher-Banyan Network Topology</li> <li>Figure 22 : Starlite Switch Architecture</li> <li>Figure 23 : Multicast in Starlite.</li> <li>Figure 24 : 8x8 Banyan Switch Architecture</li> <li>Figure 25 : Concept of LC Backpressure in Input-Ouput Queued BDDB with International starlite.</li> </ul> | <ul> <li>33</li> <li>34</li> <li>39</li> <li>42</li> <li>44</li> <li>46</li> <li>49</li> <li>al</li> <li>54</li> </ul>             |

| <ul> <li>Figure 18 : Self-Routing Properties of a Delta Network</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>33</li> <li>34</li> <li>39</li> <li>42</li> <li>44</li> <li>46</li> <li>49</li> <li>al</li> <li>54</li> <li>56</li> </ul> |

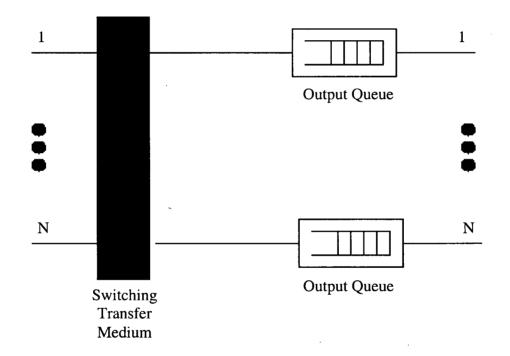

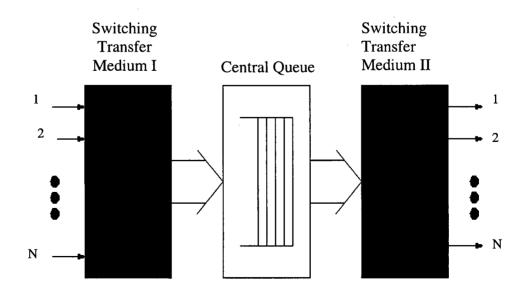

| Figure 29 : Switching Element with Central Queuing 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

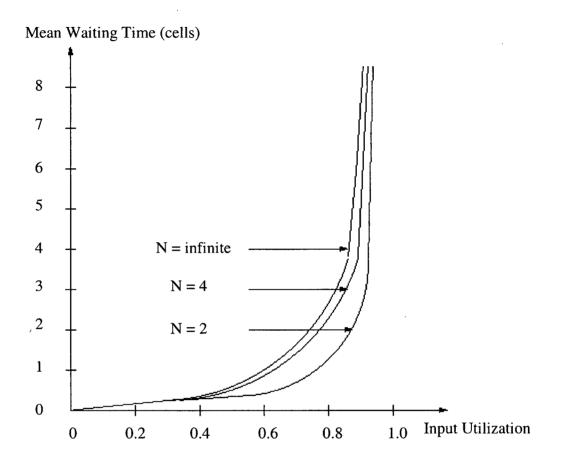

| Figure 30 : Mean Waiting Time for Output Queues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

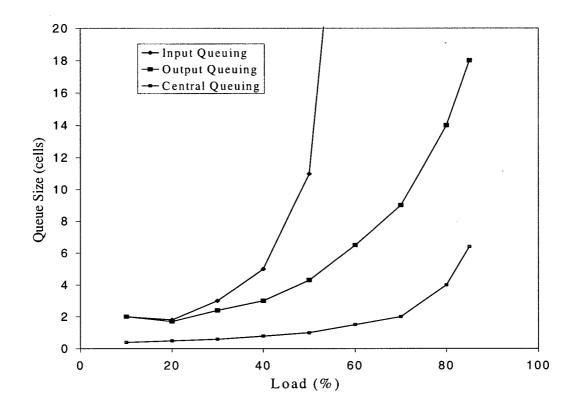

| Figure 31 : Queue Size as a Function of the Load (Cell lost rate = $10^{-3}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

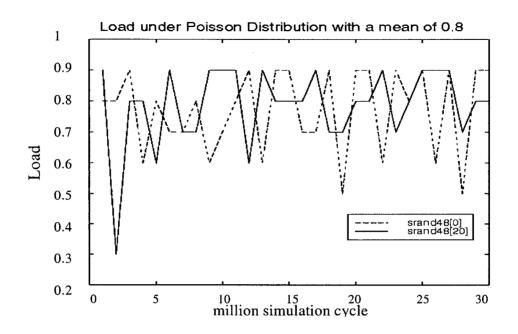

| Figure 32 : Load under Poisson Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 33 : 16x16 Banyan Switch under Uniform Traffic with 0.95 Load 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 34 : 16x16 Banyan Switch under Uniform Traffic with IBT =0, OBT=60 and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BS =0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 35 : 16x16 Banyan Switch Cell Loss vs 300 Total Buffer Size Per Port 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 36 : 16x16 Banyan Switch Cell Loss vs 500 Total Buffer Size Per Port 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 37 : 16x16 Banyan Switch Cell Loss vs 1000 Total Buffer Size Per Port 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

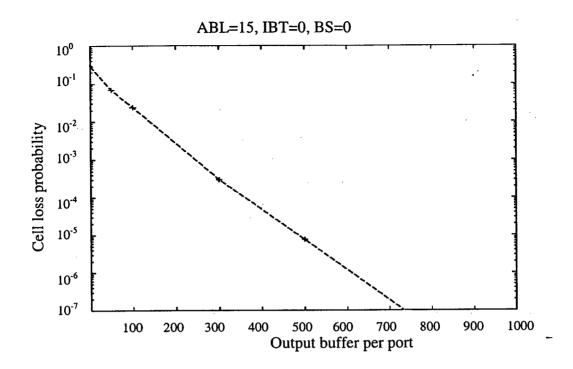

| Figure 38 : 16x16 Banyan Switch with no Input and Internal Switch Buffer under                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Unicast Bursty Traffic Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 39 : 16x16 Banyan Switch Cell Loss vs Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

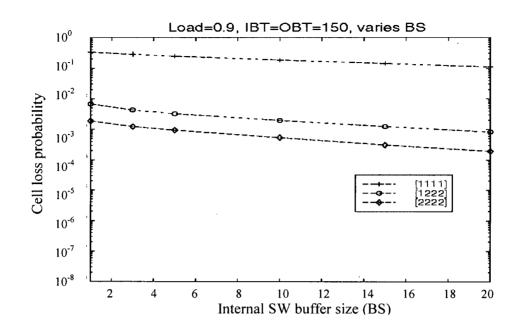

| Figure 40 : 16x16 Banyan Switch Cell Loss vs Internal Switch Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Rigure 41 + 64+64 Deriver Switch Coll Logg ve Total Duffer Size Der Dert under                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 41 : 64x64 Banyan Switch Cell Loss vs Total Buffer Size Per Port under                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Multicast Bursty Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Multicast Bursty Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

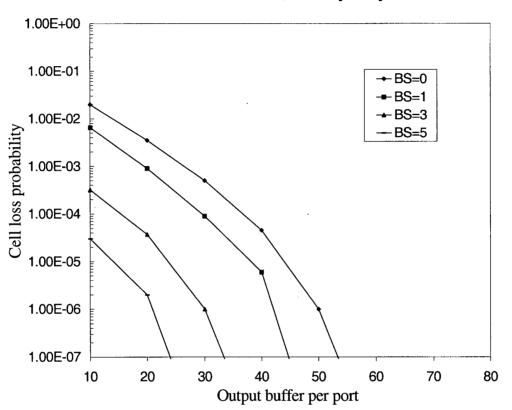

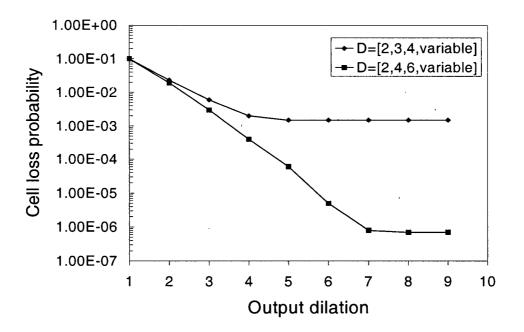

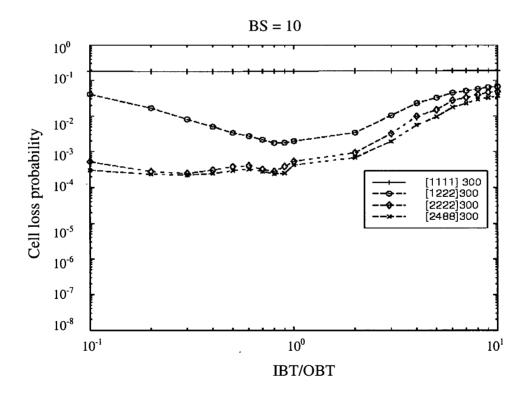

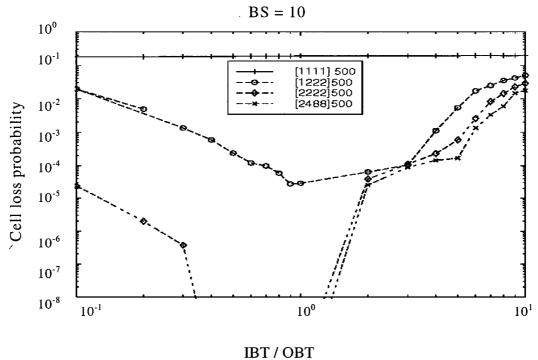

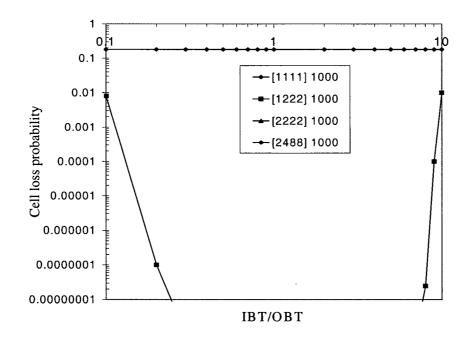

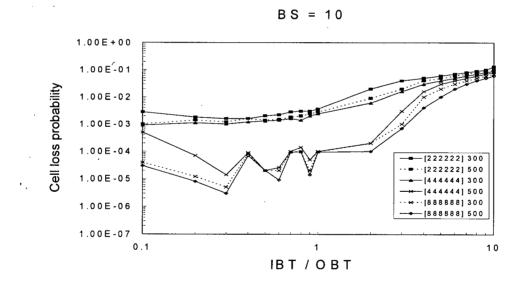

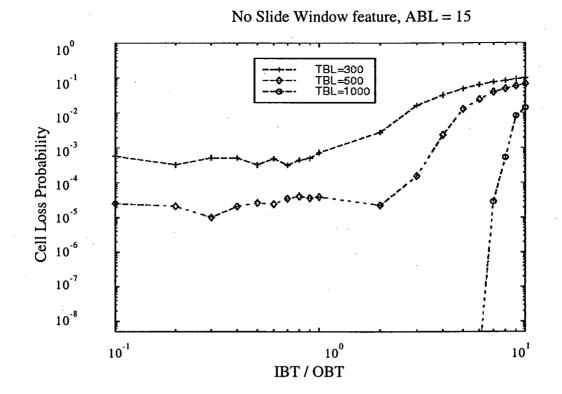

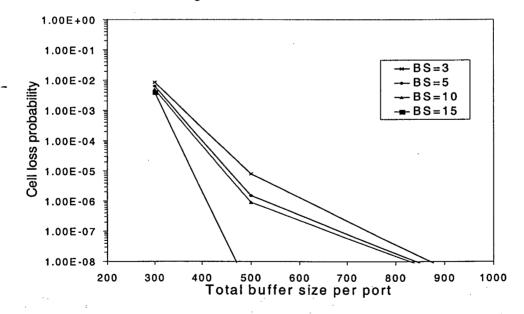

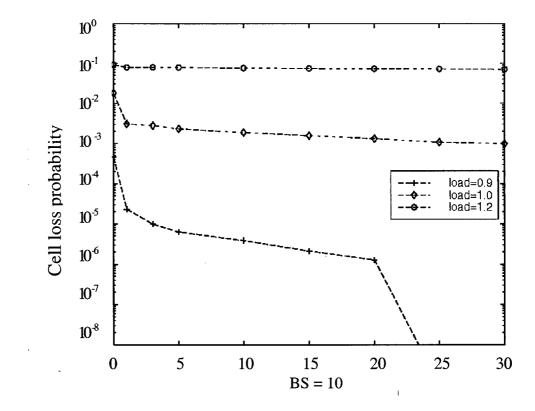

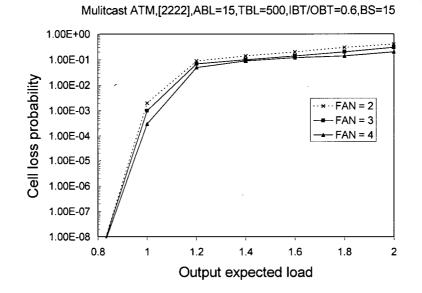

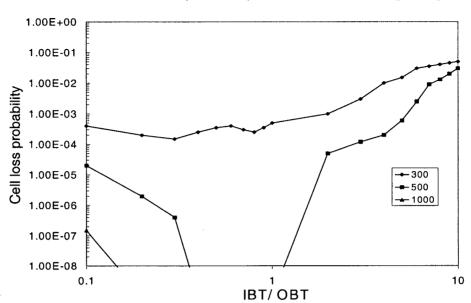

| Multicast Bursty Traffic       79         Figure 42 : 16x16 Banyan Switch Cell Loss vs IBT/OBT Ratio without Sliding       81         Window Feature       81         Figure 43 : 16x16 Banyan Switch Cell Loss vs Total Buffer Size Per Port on Different       81         Figure 44 : 16x16 Banyan Switch Cell Loss vs Internal Switch Buffer (BS)       83                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

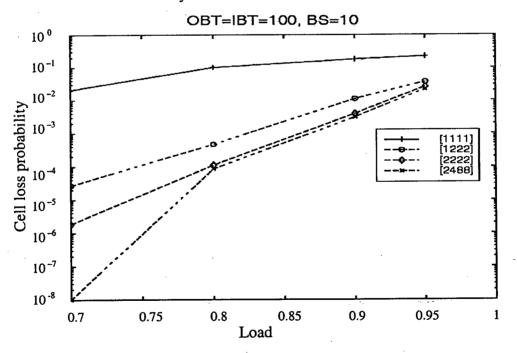

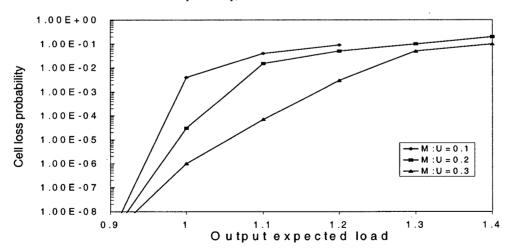

| Multicast Bursty Traffic79Figure 42 : 16x16 Banyan Switch Cell Loss vs IBT/OBT Ratio without Sliding<br>Window Feature81Figure 43 : 16x16 Banyan Switch Cell Loss vs Total Buffer Size Per Port on Different<br>BS without Sliding Window Feature81Figure 44 : 16x16 Banyan Switch Cell Loss vs Internal Switch Buffer (BS)83Figure 45 : 16x16 Banyan Switch Cell Loss vs Output Expected Load with84                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Multicast Bursty Traffic79Figure 42 : 16x16 Banyan Switch Cell Loss vs IBT/OBT Ratio without Sliding<br>Window Feature81Figure 43 : 16x16 Banyan Switch Cell Loss vs Total Buffer Size Per Port on Different<br>BS without Sliding Window Feature81Figure 44 : 16x16 Banyan Switch Cell Loss vs Internal Switch Buffer (BS)83Figure 45 : 16x16 Banyan Switch Cell Loss vs Output Expected Load with84Figure 46 : Cell Loss vs Ratio of IBT/OBT under Bursty ATM Traffic85                                                                                                                                                                                                                                                                                                                                                          |

| Multicast Bursty Traffic79Figure 42 : 16x 16 Banyan Switch Cell Loss vs IBT/OBT Ratio without Sliding<br>Window Feature81Figure 43 : 16x 16 Banyan Switch Cell Loss vs Total Buffer Size Per Port on Different<br>BS without Sliding Window Feature81Figure 44 : 16x 16 Banyan Switch Cell Loss vs Internal Switch Buffer (BS)83Figure 45 : 16x 16 Banyan Switch Cell Loss vs Output Expected Load with84Figure 45 : 16x 16 Banyan Switch Cell Loss vs Output Expected Load with84Figure 46 : Cell Loss vs Ratio of IBT/OBT under Bursty ATM Traffic85Figure 47 : Cell Loss vs Output Expected Load under Multicast and Unicast ATM                                                                                                                                                                                                |

| Multicast Bursty Traffic79Figure 42 : 16x 16 Banyan Switch Cell Loss vs IBT/OBT Ratio without Sliding<br>Window Feature81Figure 43 : 16x 16 Banyan Switch Cell Loss vs Total Buffer Size Per Port on Different<br>BS without Sliding Window Feature81Figure 44 : 16x 16 Banyan Switch Cell Loss vs Internal Switch Buffer (BS)83Figure 45 : 16x 16 Banyan Switch Cell Loss vs Output Expected Load with84Figure 45 : 16x 16 Banyan Switch Cell Loss vs Output Expected Load with84Figure 46 : Cell Loss vs Ratio of IBT/OBT under Bursty ATM Traffic85Figure 47 : Cell Loss vs Output Expected Load under Multicast and Unicast ATM<br>Bursty Traffic without RED Meachanism85                                                                                                                                                     |

| Multicast Bursty Traffic79Figure 42 : 16x16 Banyan Switch Cell Loss vs IBT/OBT Ratio without Sliding<br>Window Feature.81Figure 43 : 16x16 Banyan Switch Cell Loss vs Total Buffer Size Per Port on Different<br>BS without Sliding Window Feature81Figure 44 : 16x16 Banyan Switch Cell Loss vs Internal Switch Buffer (BS).83Figure 44 : 16x16 Banyan Switch Cell Loss vs Output Expected Load with84Figure 45 : 16x16 Banyan Switch Cell Loss vs Output Expected Load with84Figure 46 : Cell Loss vs Ratio of IBT/OBT under Bursty ATM Traffic85Figure 47 : Cell Loss vs Output Expected Load under Multicast and Unicast ATM<br>Bursty Traffic without RED Meachanism85Figure 48 : ATM, ABL=15, Fanout=3, BS=15, IBT/OBT=0.6, IBT+OBT = 1000 86                                                                                |

| Multicast Bursty Traffic79Figure 42 : 16x 16 Banyan Switch Cell Loss vs IBT/OBT Ratio without Sliding<br>Window Feature81Figure 43 : 16x 16 Banyan Switch Cell Loss vs Total Buffer Size Per Port on Different<br>BS without Sliding Window Feature81Figure 44 : 16x 16 Banyan Switch Cell Loss vs Internal Switch Buffer (BS)83Figure 44 : 16x 16 Banyan Switch Cell Loss vs Internal Switch Buffer (BS)83Figure 45 : 16x 16 Banyan Switch Cell Loss vs Output Expected Load with84Figure 46 : Cell Loss vs Ratio of IBT/OBT under Bursty ATM Traffic85Figure 47 : Cell Loss vs Output Expected Load under Multicast and Unicast ATM<br>Bursty Traffic without RED Meachanism85Figure 48 : ATM, ABL=15, Fanout=3, BS=15, IBT/OBT=0.6, IBT+OBT = 1000 8686Figure 49 : ATM[2222], ABL=15, Fanout=3, BS=15, IBT/OBT=0.6, IBT+OBT =87 |

.

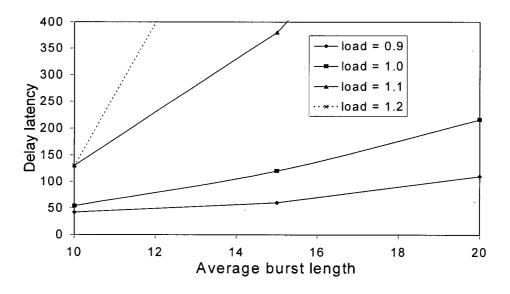

| Figure 51 : Banyan Switch Latency on High Priority Class vs Average Burst Length |

|----------------------------------------------------------------------------------|

| under IP Multicast Bursty Traffic with FANOUT=3 and RED Mechanism                |

|                                                                                  |

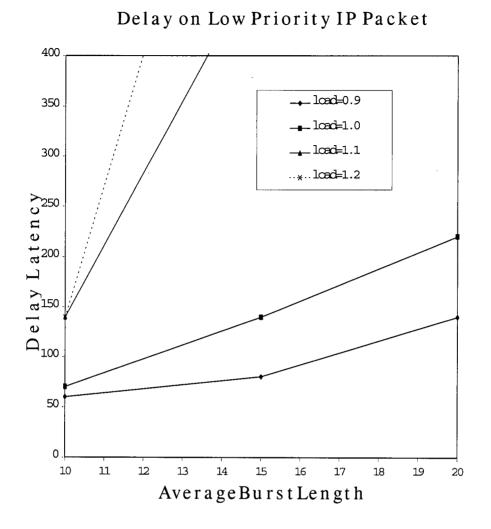

| Figure 52 : 16x16 Banyan Switch Latency on Low Priority Class vs Average Burst   |

| Length with FANOUT=3, IP Multicast Burst Traffic and RED                         |

| Mechanism                                                                        |

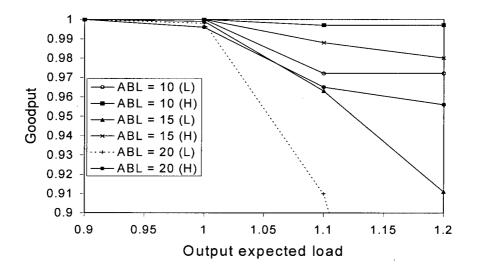

| Figure 53 : Normalized Goodput vs Output Expected Load with Different Burst      |

| Length (10,15 and 20), FANOUT=3 and RED Mechanism                                |

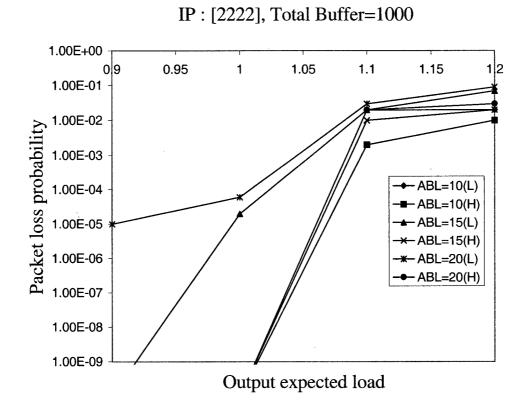

| Figure 54 : IP traffic [2222], NO RED, BS = 15                                   |

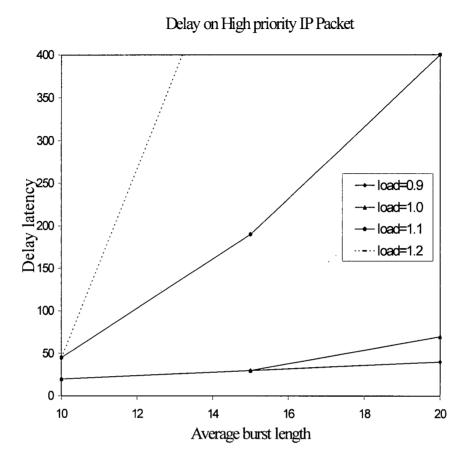

| Figure 55 : Delay on a High Priority IP Packet, [2222], NO RED BS=1593           |

| Figure 56 : Delay on a Low Priority IP Packet, [2222], NO RED, BS=15             |

4

,

.

# List of Tables

| Table 1: Summary of Different Switching Element    | 30 |

|----------------------------------------------------|----|

| Table 2 - Four Types of MIN with Internal Blocking | 35 |

| Table 3 - Roxanne Switch Expandability             | 39 |

| Table 4 – Requrired Memory Access Time             | 63 |

# **Acknowledgment**

I would like to thank my supervisor, Dr. H. M. Alnuweiri, for his constant guidance and advice in supervising my master's research work. His patience and support throughout this project are very much appreciated.

# **Chapter 1 Introduction**

One of the most outstanding features of ATM switching is its ability to provide perflow quality-of-service (QoS), guaranteed under a multi-rate, multi-service, variable bandwidth environment, in a scalable and manageable manner. ATM networks have the potential of subsuming the Internet and telephone network to provide a unified infrastructure for supporting guaranteed traffic (e.g. voice and video), as well as besteffort traffic (mainly data). No other technology can provide the type and versatility of QoS that ATM can provide in a scalable manner and at a high-bandwidth. Not only is ATM switching well established for the wide-area-network (WAN), it is also becoming the tool of choice for implementing the emerging technology of IP switching in the local-area-network (LAN). The underlying concept is to combine ATM as the level 2 (data-link layer) switching protocol with level 3 (network layer) IP routing in a single "IP" switch.

This new vision of the expanding role of ATM switching to provide QoS routing in LANs and WANs, requires taking a second look at what functionalities and guaranteed performance can be delivered by next-generation switches. Few vendors supply per-flow queuing chips that enable accurate QoS control at a switch port. However, these chips are planned for use in small switch configurations. For large switch configurations, many challenging problems remain to be solved, including how to route cells with minimum delay and cell loss ratio to the output ports where perflow queuing can be exercised, and how to manage and coordinate multicasting operations in the switch fabric. The efficiency of per-flow queuing at the output ports will be greatly reduced if delay-sensitive cells are delayed considerably by the routing

1

fabric or at the input ports. Similarly, per-flow scheduling and fair-share bandwidth allocation will be ineffective if cells experience excessive QoS coupling in the routing fabric.

## **1.1 Features of Next-Generation Switching Fabrics**

First generation ATM switch designs were mainly focused on single QoS-class traffic. However, the integration of LAN with other broadband traffic, including voice and video, requires switches to be able to handle multi-class traffic and multicast efficiently without violating the QoS guarantees for the wide range of services. The addition of the available bit-rate (ABR) component introduces substantial complexity to the switch buffering and internal signaling structure because switches must monitor internal congestion, QoS guarantees fairness to the individual virtual channel (VC), and it cooperates with end-to-end feedback congestion control mechanisms. The following are some important qualities of next-generation switching fabric:

- 1.QoS Preservation: This requires switching fabrics to provide low cell delay, low cell loss and low cell delay-variation (jitter).

- 2.Flow Isolation (or QoS Decoupling): QoS handling is normally relegated to the buffer controllers at the output and input ports of the switch. Therefore, the core fabric should minimize the QoS interaction or coupling among flows from different input ports. Fairness is another important quality related to flow isolation. On a coarse level it means that all input and output ports should receive equal service and equal internal bandwidth. On a finer level, it implies that cells from each VC must be serviced according to some weighted fairness measure.

- 3.**Multicasting:** This capability is essential for next-generation switches. Multicasting is a challenging problem for large-scale switches because early replication of multicast cells can potentially congest the switch fabric.

- 4.**Scalability:** This is a measure of the normalized (or average) growth in hardware and buffering resources to maintain a uniform performance as the switch size or the external link rate is increased.

- 5.Implementation Feasibility: For switch architectures with multi Gb/s link rates, the feasibility of implementation is limited mainly by input and output (I/O) requirements, off-chip communication speeds, and inter-board wiring and cabling. The switch should be modular so that it can be easily partitioned among multiple chips and boards.

### **1.2 Motivation and Scope of Thesis**

This thesis focuses on the issues pertaining to the design and implementation of next-generation large-scale ATM switches that support QoS routing and buffering, and efficient multicasting with an external link-rate reaching up to 10 Gb/s per port (i.e. OC-192 rate) or higher. At this junction, it is worth stressing that the switch core fabric and the switch ports are viewed as two distinct entities. The switch ports normally reside in the line cards and they contain the major buffering and QoS control resources of the switch, while the switch core is responsible for routing and/or multicasting cells to the output ports. Delivering high QoS performance on a per-flow basis is a challenging task especially in large-scale switches. The problem for largescale switches is to deliver cells to the output buffers with minimum delay, and preferably, with no cell loss. Another source of difficulty is the potential occurrence of unbalanced or hot-spot traffic, such as when several workstations simultaneously burst data to a server, or when several subnets send data to an inter-switch trunk. Such traffic can easily exhaust even the most generous buffering resources at the hot-spot output port(s), and therefore, must be handled by efficient distributed buffering or by back-pressure signaling. The presence of unspecified bit rate (UBR) and ABR traffic further complicates matters. These two kinds of traffic are designed to occupy any leftover bandwidth after servicing guaranteed traffic. The presence of this "background" traffic will tend to saturate switching fabrics most of the time, especially if ABR / UBR multicasting is supported. This problem can be more serious than it may appear at first, because ABR / UBR traffic is not subjected to connection admission and control (CAC). In surveying present architectures for ATM switches, two very important qualities of switching fabrics have hardly been addressed, which

are the issues of *QoS coupling* and *fairness*. QoS coupling occurs when multiple flows (e.g. traffic from different input ports) interact through the routing fabric and subsequently affect each other's performance (delay and loss). Severe QoS coupling can lead to serious performance degradation especially for delay-sensitive traffic. The issue of fairness is related to the fabric ability to provide equal service to traffic flows independent of their input or output port number.

The switch architecture proposed in this thesis is based on the approach of internal bandwidth expansion, which increases the internal bandwidth of the switching fabric either by paralleling or by speeding up the switching resources (switching elements and internal links) at each stage of the fabric. Either method implies that the output buffers must operate at a higher speed than the input link rate. The required level of speedup depends on the degree of internal bandwidth expansion. However, output buffer speedup can be controlled by using a small amount of internal buffering. Bandwidth expansion can be achieved by several methods including *fabric replication, fabric dilation,* or by using *tree-type* networks for cell distribution from input ports, and for cell concentration at the output ports. The proposed switch architecture is based on the fabric dilation method.

5

### **1.3 Thesis Contributions**

This thesis proposes several techniques for the designing and implementation of next-generation large-scale switch fabric and the support of QoS routing and buffering. The following elaborates on several specific contributions of this thesis:

- 1. This thesis proposes a Buffered-Dilated Banyan (BDB) switch architecture, which provides high utilization of two main resources of the switch: interconnect and buffers. Interconnect and wiring complexity become a major bottleneck for large-scale implementations, where the switch fabric spans several boards and shelves. Thus, minimizing interconnect complexity is an important design issue. Buffer is a significant component in determining the cost and delay performance. Switch with QoS and multicast support may require large buffers in order to guarantee all the QoS requirements and multicast packet streams passing through the fabric completely. Hence, the optimization of buffering in switches is another important design issue.

- 2. Analyses of the performance of the proposed fabrics with computer simulations under independent and bursty traffic conditions are provided. The effects of various parameters which affect cell loss, such as internal link dilation, depth of the fabric, and share memory size, are considered in the performance analysis.

- 3. Different buffering strategies on the proposed architectures are studied. This is based on the use of a truly self-routing interconnect. Input, output and inputoutput buffering are considered. The notion of the link-capacity back-pressure mode of operation for all different buffering strategies is also introduced. This

mechanism eliminates cell loss from the internal stages of the switch and limits cells to the BDB switch inputs only. In the switch core, a small amount of strategically placed buffers can be used to control cell loss and enhance switch robustness to changing traffic characteristics.

4. Multicast traffic is a significant portion of all of the existing traffic. A multicast mechanism is introduced into the switch as a copy network. Its performance under multicast traffic on both the uniform and bursty traffic pattern is analyzed by simulation. The proposed copy network achieves very low cell loss even at very high output offered loads.

# **1.4 Organization of the Thesis**

Chapter 2 presents a comprehensive survey of the existing switch architectures. It takes an in-depth look into the existing switch fabrics and highlights their drawbacks and the required improvements for large-scale switching.

Chapter 3 looks at the architecture of the Buffered-Dilated Banyan switch in terms of the interconnection complexity. It also addresses the features of the BDB switch.

Chapter 4 looks at the buffer management of the switches. The ideas of Random Early Detection (RED) and Drop Tail Mechanism are introduced. The overall system performance is analyzed by computer simulations.

Chapter 5 introduces the input-output buffered BDB banyan. The performance under uniform traffic conditions is analyzed. The performance of the input-output buffered banyan is further enhanced by placing a small amount of internal buffers into the switch element and introducing a backpressure mechanism. Simulation results under independent uniform and bursty traffic conditions with multicast cells are presented.

Chapter 6 concludes the thesis and outlines future research areas.

# **Chapter 2 Switch Architecture**

## **2.1 Switch Element**

Switching elements are building blocks of switching fabric which is the core of an ATM switch. In this section, four ATM switching elements will be presented. They are Knockout, Roxanne, Coprin and Arena [7] [22]. Although they do not represent all of the ATM switching elements, their architectures are very different.

2.1.1 Knockout Switching Element

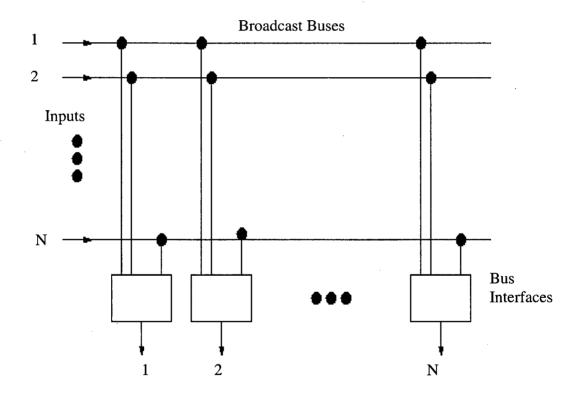

Figure 1 : Knockout Switching Element

The Knockout Switch belongs to the crossbar network family used to describe any single path non-blocking network that has a complexity, and which grows as a function of  $N^2$ . Figure 1 shows a simple block diagram of the Knockout Switch with N inlets and N outlets (NxN). One of the advantages of the Knockout Switch

architecture is that each bus is driven by only one inlet instead of sharing multiple inlets. This makes implementation simpler, and makes a higher transmission rate possible.

Since N inputs are connected to one outlet via a bus interface, N cells may contend for the same output. Therefore, the bus interface provides a queue. This is the reason why the Knockout Switch is based on an output queuing solution. Figure 2 shows a closer look at the bus interface, which contains the cell filters, the concentrator, and the shifter.

Figure 2 : Knockout Bus Interface

Due to the connections on the bus interface, N cells may arrive at one bus interface and try to reach one particular output. Without the cell filters, concentrator and shifter, the buffer must operate at N times the speed of one inlet in order to send out all the cells at one cell time. However, this may put too much constraint on the memory. Instead, the Knockout Switch uses a smarter bus interface, which lowers the required memory. By scanning the addresses of incoming cells, the cell filters select ones that are destined for specific outlets and let them pass, otherwise the cell is discarded. Then, the concentrator concentrates N inputs to L outputs. If the number of incoming cells is greater than L, some of the cells are dropped; however, the probability of this is very small.

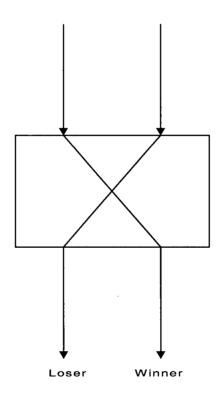

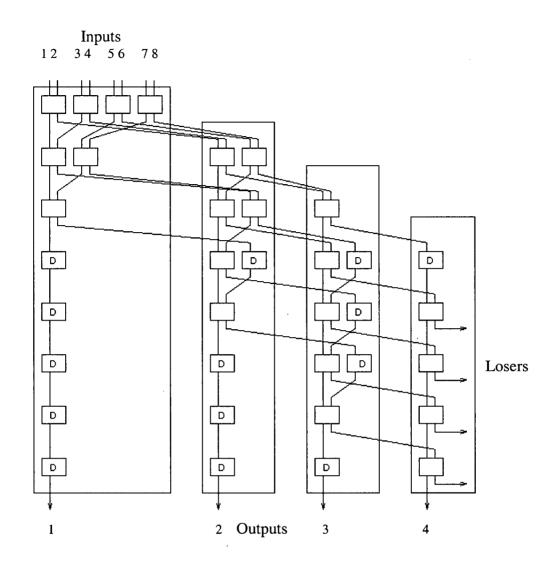

The purpose of the concentrator is to reduce the number of memory writes to the buffer in one cell time to L instead of N. In addition, the concentrator reduces the number of buffers required. The concentrator is divided into several stages composed of many contention switches. Figure 3 shows one block of a 2x2-contention switch, and Figure 4 shows the architecture of a concentrator.

Figure 3 : Contention Switch

Figure 4 : An 8 input/4 Output Concentrator

The contention switch operates in the following ways:

- 1. If only one cell is present in one of the inputs, it is selected as the winner (pass).

- 2. If two cells are present in both of the inputs, then the left cell is selected as the winner and the right cell is dropped.

In order to implement an 8-input, 4-output concentrator, the 2x2 contention switches are organized in a Knockout game architecture. The Knockout game can be broken down into different stages (a tournament). In each tournament, players (incoming cells) are knocked out of the tournament as soon as they lose one match, and one

winner is selected. The losers in the first tournament again compete in the second tournament, and the winner becomes the second in rank. Finally, in the last tournament, the losers are discarded.

When there is an odd number of players in one round, the odd player must wait for a competitor. This requirement can be achieved by adding a 1 bit delay element indicated by a letter D as shown in Figure 4.

An interesting property of the concentrator is that if the number of input cells is less than L, the concentrator always concentrates the cells in the left most outputs.

The cell buffers are separated into L queues. This allows for a simpler implementation of the buffer because now each queue only needs to handle one write and one read in one cell time, instead of L writes and one read in a combined queue implementation. Less memory access means that the memory does not require fast access time.

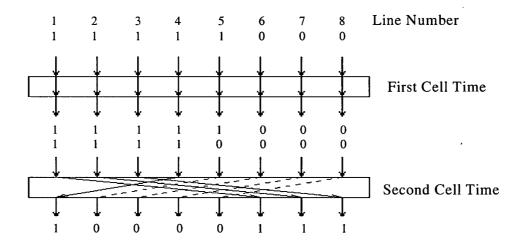

The shifter in front of the cell buffer guarantees that all the L buffers are equally loaded and optimally used. Moreover, the cell sequence at the output is guaranteed in this way. The shifter is a circular shift register. Figure 5 shows two instances of its operation.

Figure 5 : Shifter Function for 8 Lines

13

In this figure, "1" indicates that there are cells on the inputs. In the first cell time, input one is mapped to output one, and so on. In the second cell time, input one is mapped to output 6, since output 5 was the last output filled the time before. In a more mathematical notation, if  $S_i$  denotes the position that the shifter must shift to on the right during cell time i, then the following is true:

$S_{i+1} = (S_i + k_i) \mod L$

where  $k_i$  represents the number of filled cells arriving during cell time i. It is assumed that  $S_1 = 0$ . For example, using the situation shown in the figure, let  $k_0 = 5$ . Thus, the position of the shifter at the next cell time (1) is  $S_1 = (0 + 5) \mod 8 = 5$ . Therefore, the shifter is now at line 6 (position 5, starting from 0).

#### Multicast/broadcast Capability

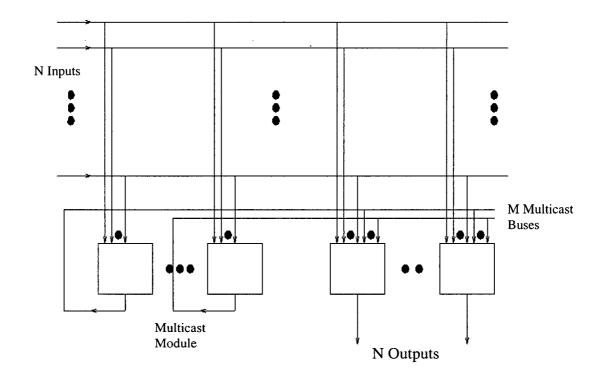

Since each bus interface has already connected to N inlets, and the multicast/broadcast information gets distributed over all of the bus interface due to this configuration, it is quite easy for the Knockout Switch to perform a multicast or broadcast function. The only requirement is that the cell filters must be able to distinguish the multicast/broadcast cell and know if the incoming cell belongs to its outlet. In order to avoid this complex functionality, which is built on all of the cell filters in every bus interface, multicast modules are added to the bus interface network, as shown in Figure 6 [22].

Figure 6 : Knockout Switch with a Multicase Module

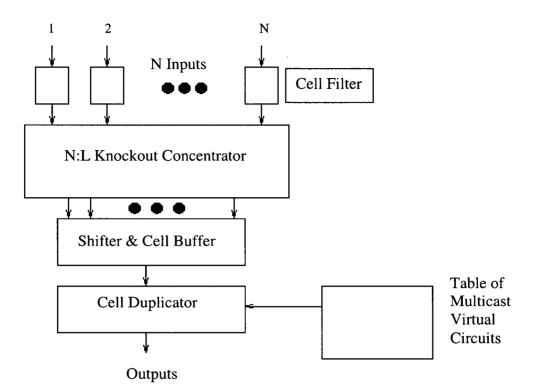

The multicast modules have very similar structures to the bus interfaces. Moreover, the multicast module has a cell duplicator and a table of multicast virtual circuits. The architecture of a multicast module is shown in Figure 7.

Figure 7 : Multicast Module with a Cell Duplicator

In the multicast module, the cell filters, concentrator, shifter, and cell buffer are all the same as the one in the bus interface described previously. The table of multicast virtual circuits provides the number of copies required for a particular multicast/broadcast cell and the destination address of each copy. The information in the table is updated at connection time. Having received that information, the cell duplicator makes the correct number of copies and sends them out to the bus interface via the multicast buses. If there are M multicast modules, the bus interface requires N + M inputs. The number M depends on the demand of multicast functionality.

#### 2.1.2 Roxanne Switching Element

Invented by Alcatel researchers in 1990, the design of the Roxanne Switching Element is based on the central queuing principle [22]. The switching element is called the Integrated Switching Element (ISE), and it supports a multicast/broadcast

16

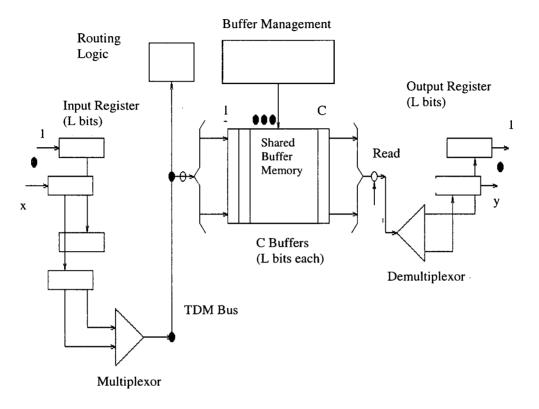

function. One possible dimension of the ISE is a 32 x 32 basic switching block with inlets and outlets operating at 150 Mbit/s. Figure 8 is a block diagram of an ISE.

Figure 8 : ISE Function Block Diagram

After L bits of data have been shifted into the input register (serially), the L bit data is latched. Then the data (parallel) is sent to the Shared Buffer Memory (SBM) via the TDM bus (L bit wide). The conversion from serial input to parallel input lowers the requirement for the internal operating speed. If the inlets and outlets transfer at 150Mbit/s and the TDM bus is 8 byte wide, the frame period is 64bit/150 Mbit/s = 0.43 $\mu$ s. If the ISE has 32 inlets, 32 write operations have to be performed by the SBM within one frame period, which is the time taken to fill up the input register. Therefore, the internal bus speed becomes1/0.43 $\mu$ s x 32 = 74.4Mwords/s (word size is 8 bytes).

In order to use the memory space more efficiently and reduce memory size, queues in the SBM represent groups of 4, 8, 16 or 32 outlets. A queue such as this that is called a "logical queue" and is treated like a single queue. The idea is to distribute the load as equally as possible on all outlets. Before a cell is written into the ISE, the routing logic performs tag processing which mainly consist of routing information interpretation. Implemented as a pipeline machine, it analyzes the self-routing tag on the cell and routes the cell to a logical queue, depending on the specified ISE routing mode. Possible routing modes include direct routing modes, where a particular outlet is specified, and distributed routing mode where a cell may be routed freely to a group of different outlets. The use of a distributed routing mode illustrated in the Roxanne Switching fabric section.

The buffer management keeps track of the free and occupied cells by using a linked list. In addition, it is responsible for handling the multicast/broadcast function.

#### Multicast/Broadcast

For multicast cells, all routing tags contain an internal reference number. The reference number is used to access a special memory (not shown in Figure 8) in the ISE, where the number of copies and the destinations of the copies are stored. The destinations are represented as a mask. This mask comprises one bit per logical queue, indicating whether or not a copy has to be placed in that logical queue. The buffer management allocates one copy count per cell. When a copy is sent, the count decreases until the count is zero. Then, the address of the cell can be released.

#### **Multislot Cells**

An interesting point about the Roxanne Switch is that it will convert incoming cells into several fixed length slots before they are stored. Within each slot, 2 bits are used to indicate the slot sequence (start of cell, end of cell). As a result of this data structure, the Roxanne Switch is compatible with variable cell lengths. This may extend the application of the Roxanne Switch to other types of networks. Another advantage of this structure is that a new cell can start to move into the slot of a previous cell location even though not all of the slots of the old cell have become available. Consequently, memory space can be used more efficiently. However, if there are n slots in a cell, the size of the linked list management in the buffer management will be n times larger.

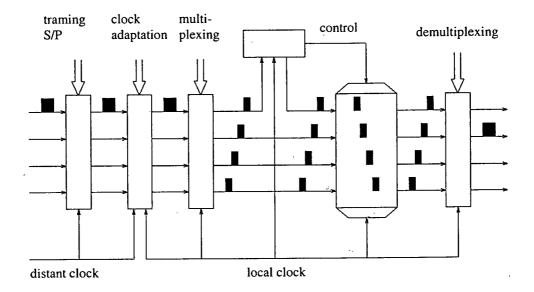

#### 2.1.3 Coprin Switching Element

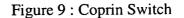

The Coprin Switch was discovered and designed by the French CNET in order to transfer data, voice, and video signals. It was originally intended to operate with links at 280 Mbit/s and cells of 15-byte information, and a 1-byte header that contains routing information. It has a reference number that is known internally to the switch and is determined at the time of connection. The Coprin Switch uses the reference number to determine the physical outlets of a cell. The design of the Coprin Switch is based on the central queuing system. The block diagram of the Coprin switch is show in Figure 9.

A major characteristic of the switch is that a cell coming into the Coprin Switch will be converted to a parallel stream of information inside the switch. The Super Multiplexing block is responsible for this task. Figure 10 shows an example of a 4 by 4 super multiplexing function, assuming that each cell has one header byte and 3 data bytes.

Figure 10 : Extracting Packets in Buffer Memory

In order for the Super-Multiplexing block to function correctly, the headers on different inlets have to arrive in consecutive time slots, as shown in Figure 10. This alignment of the incoming cells is an important precondition. In order to satisfy this requirement, the phase alignment block is put before the Super-Multiplexing block, as shown in Figure 10.

### **Super-Multiplexing**

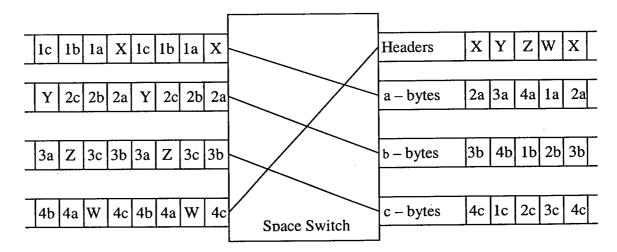

The function of the Super Multiplexing Switch is to place bytes of information of different meaning into different channels. Through this way, different parts from different cells are loaded into the memory at the same time. Therefor, the cell loading operation is "pipelined". As shown in the example, headers are put on the first outlet, the second byte is put on the second outlet in the next clock cycle, and so on. Therefore, consecutive slots in the outlets actually contain information from different inlets. In order to achieve this function, the Space Switch is implemented in four states as shown in Figure 11.

Figure 11 : Four States of the Space Switch

The four states will be rotated on each clock signal (in the order 1, 2, 3, 4, 1...).

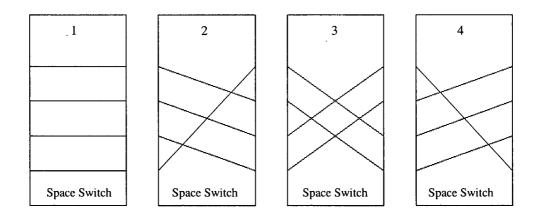

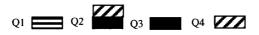

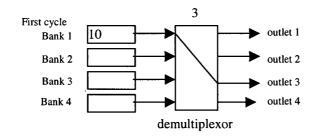

### **Buffer Memory**

The buffer memory stores the ATM cells in parallel form. The central queue is divided into banks that are dedicated to a byte of the cell. For example, if the header address of a cell is A and it is stored in bank 1, then the first data byte will be located

at A +1 which is in bank 2. Figure 12 below, shows how packets are extracted in the buffer memory.

Figure 12 : Extracing Packets in Buffer Memory

First the header address (A) will be provided by the control and sent to bank 1. Thus, the header stored in A will be retrieved. In the next cycle, the address A + 1 will be sent to bank 2 and the data in address (A + 1) will be retrieved. The header address will continue to ripple down into the next bank with the correct index on each clock cycle until it has reached bank 4.

Before the data is put on the outlets, the ATM cells are demultiplexed. In order to reconstruct the cells, the demultiplexor performs the opposite task of the Super-Multiplexing module. It has a Space Switch of the four states described in the Super-Multiplexing. However, for the demultiplexor, the four states are rotated in the opposite direction, that is, 4, 3, 2, 1, 4 and so forth.

•

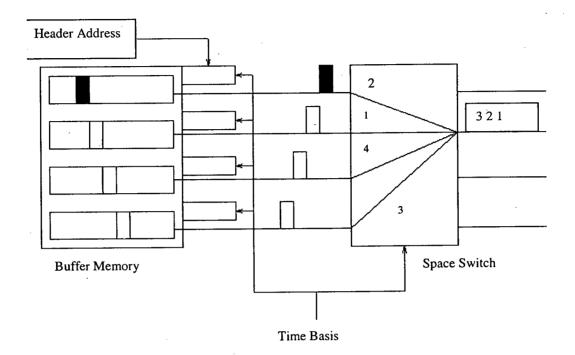

#### **Routing operation**

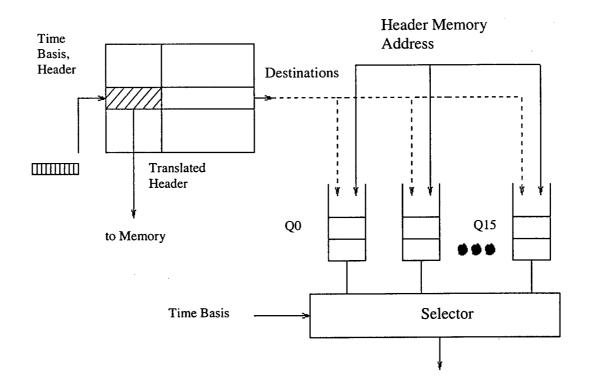

The routing operation is done in the control block. It consists of a translation table, where each item has 3 bytes of data, 1 byte of translated header, and 2 bytes of destination locations. When a cell arrives, the control will determine the translated header of the cell and replace the cell's incoming reference number with the translated header. This is accomplished according to the time basis (which tell from which inlets . the cell arrives) and the value of the incoming header. The new header will write into memory to where the header should be stored. The other two bytes of data in the table are used to indicate whether a cell has to be copied to any of the 16 outlets by allocating a '1' to the specific location represented by an outlet. Figure 13 shows the basic structure of the control.

Figure 13 : Control of the Coprin Switch

The header address in the memory is stored in the queues  $(Q_0 \text{ to } Q_{15})$  if the cell has to be copied to those specific outlets. The advantage of using the queues to hold the header addresses is that the output contention problem can be avoided.

#### An Example of a Routing Operation

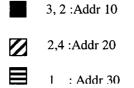

Please refer to Figure 13 as an example of the arriving cell patterns.

Suppose those headers have the following destinations and addresses in the memory:

After all of the three headers have been scanned by the control, the queues will look like this:

Below shows the addresses on each bank in the memory after the headers are ready to be retrieved from the memory. The selector shown in Figure 13 will select the header address value in the queue whose number is the state number in the demultiplexor. For instance, if the demultiplexor is in state 3, the selector will pick the address in queue 3. Suppose the selector starts with queue 3, then after the selector has picked up the header address, the address will be removed from the queue.

As shown in the example, the broadcasting or multicasting operation is quite simple in the Coprin Switch.

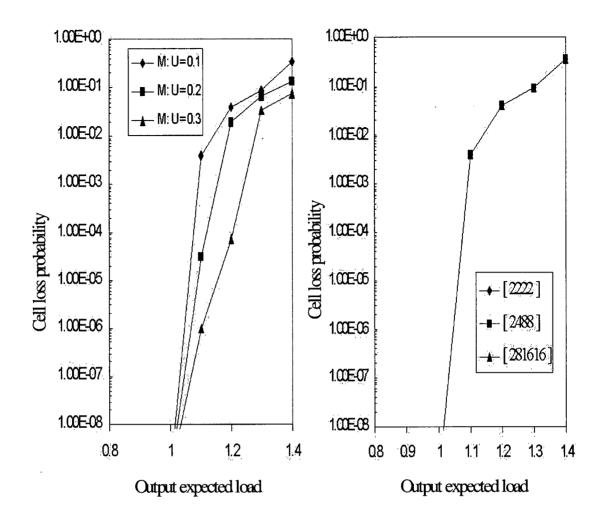

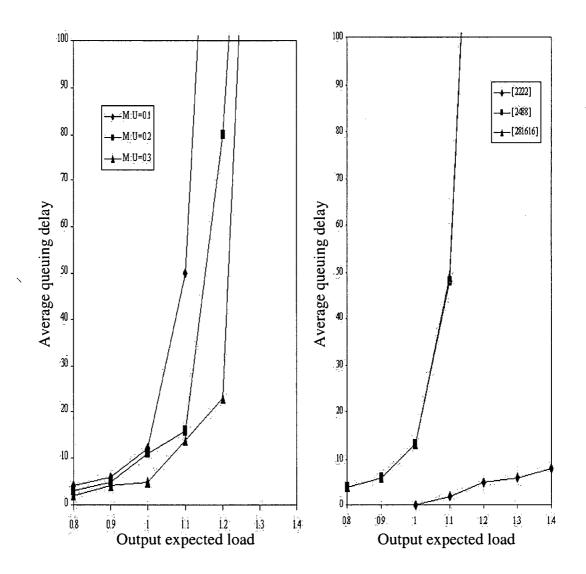

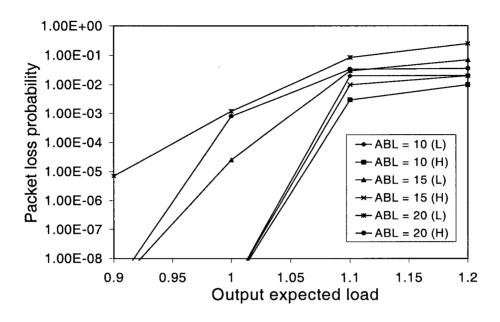

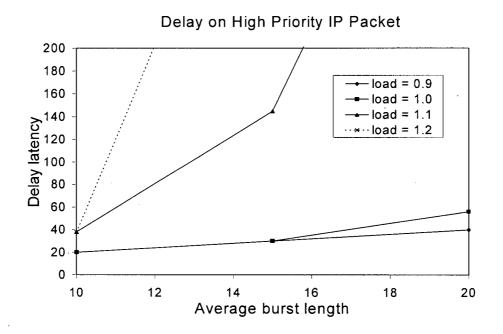

#### 2.1.4 Athena Switching Element