# Embedded Test Circuits and Methodologies for Mixed-Signal ICs

by

Sassan Tabatabaei-Zavareh

M. Sc. (Electrical & Computer Engineering), The University of Calgary, 1994

B. Sc. (Electrical & Computer Engineering), Isfahan University of Technology, 1991

#### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

#### THE REQUIREMENTS FOR THE DEGREE OF

## **Doctor of Philosophy**

in

#### THE FACULTY OF GRADUATE STUDIES

(Department of Electrical and Computer Engineering) We accept this thesis as conforming to the required standard

## The University of British Columbia

February 2000

© Sassan Tabatabaei-Zavareh, 2000

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of <u>Electrical & Computer</u> Engineering

The University of British Columbia Vancouver, Canada

20, 2000 Date

# Abstract

The rapid pace of the integrated circuit industry towards more miniaturization is making system-on-chip (SOC) a reality. For practical implementations of SOC, however, the test issues of such devices must be addressed through the integration of design-for-testability (DFT), built-in self-test (BIST), and embedded test for embedded blocks, such as digital, memory, and mixed-signal circuits.

This thesis presents two novel embedded test solutions for mixed-signal circuits. The first one is a built-in current monitor (BICM) suitable for power supply current ( $I_{DD}$ ) testing. The BICM includes a built-in current sensor (BICS) which provides high measurement sensitivity without introducing a large impedance in the  $I_{DD}$  path. Although the BICS structure has been proposed before, the new circuit analysis and chip measurement results provide important insights into the BICS characteristics and design trade-offs. The BICM also includes a mixed-signal built-in current integrator (BICI) which generates a digital signature proportional to the average  $I_{DD}$  ( $\overline{I_{DD}}$ ). Two different circuits have been developed for BICI: a single-phase and a double-phase BICI; the first is less accurate but requires less silicon area. These new BICI architectures offer an advantage over previously proposed circuits because they can perform integration over large time windows (T > 1 ms) while occupying a chip area equivalent to a only few hundred NAND gates. The BICM is compact, accurate (error < 2%), and insensitive to process and temperature variations.

The second embedded test circuit is designed for non-intrusive functional testing of high-speed clock-recovery units (CRU) and clock-synthesis units (CSU). To the author's knowledge, this new structure is the first circuit which can perform on-chip, single-shot jitter measurement with high resolution and precision without requiring element matching. The simulation and analysis predict a jitter measurement resolution of 10ps and a precision of 11ps in a 0.35  $\mu m$  CMOS technology under typical power supply and thermal noise conditions. Combined with a jitter generator block, it can test intrinsic jitter, and jitter transfer characteristics of CRUs and CSUs. The circuit is digital, partially synthesizable, and automatically placeable and routable. Novel gate delay model and analysis techniques, supported by simulation, are also introduced to evaluate the accuracy of the circuit.

# Contents

| Abstra    | ct       |                           |          |   |   | ii    |  |

|-----------|----------|---------------------------|----------|---|---|-------|--|

| Conten    | ts       |                           |          |   |   | iv    |  |

| List of ' | Tables   |                           |          |   |   | ix    |  |

| List of ] | Figures  |                           |          |   |   | x     |  |

| Claims    | of Orig  | inality                   |          |   |   | xiv   |  |

| Acknow    | vledgem  | ents                      |          |   |   | xvi   |  |

| Dedicat   | tion     |                           |          |   |   | xviii |  |

| 1 Mo      | tivation | s and Overview            |          |   |   | 1     |  |

| 1.1       | Built-i  | n current monitoring      | • •      | • | • | . 2   |  |

|           | 1.1.1    | On-chip current sensing   |          | • |   | . 3   |  |

|           | 1.1.2    | On-chip current averaging |          | • |   | . 5   |  |

| 1.2       | PLL te   | sting                     | 、<br>• • | • |   | . 7   |  |

|           | 1.2.1    | Jitter testing            |          |   | • | . 8   |  |

|   | 1.3 | Motivations and Contributions                                             | 9          |

|---|-----|---------------------------------------------------------------------------|------------|

| 2 | Bac | ckground And Survey 1                                                     | 13         |

|   | 2.1 | IC Testing                                                                | 4          |

|   |     | 2.1.1 Why test integrated circuits?                                       | 6          |

|   |     | 2.1.2 Test and diagnosis                                                  |            |

|   |     | 2.1.3 Functional versus structural testing                                | 1 <b>8</b> |

|   |     | 2.1.4 Defects and faults                                                  | 9          |

|   |     | 2.1.5 Test generation                                                     | 21         |

|   |     | 2.1.6 Design for testability (DFT), built-in-self-test (BIST), and embed- |            |

|   |     | ded test                                                                  | 22         |

|   |     | 2.1.7 Digital circuit testing                                             | 24         |

|   | 2.2 | Analog and Mixed-Signal Testing                                           | 26         |

|   |     | 2.2.1 History                                                             | 27         |

|   |     | 2.2.2 Testing analog circuits                                             | 29         |

|   |     | 2.2.3 Analog and mixed-signal DFT                                         | \$4        |

|   |     | 2.2.4 Mixed-signal BIST                                                   | 5          |

|   | 2.3 | Conclusions                                                               | 7          |

| 3 | Bui | ilt-In Current Monitor for Testing Analog Circuit Blocks 3                | 38         |

|   | 3.1 | Built-In Current Sensor (BICS)                                            | ŀ0         |

|   |     | 3.1.1 BICS circuit                                                        | 0          |

|   |     | 3.1.2 BICS accuracy                                                       | 2          |

|   |     | 3.1.3 Calculating $Z_{BIC}$                                               |            |

|   |     |                                                                           |            |

|   |     | v                                                                         |            |

|   |     |                                                                           |            |

.

|   | 3.2               | Single                                                                           | -phase BICI                    | 47                                                                                                                     |

|---|-------------------|----------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   |                   | 3.2.1                                                                            | Basis                          | 47                                                                                                                     |

|   |                   | 3.2.2                                                                            | Notation and definitions       | 49                                                                                                                     |

|   |                   | 3.2.3                                                                            | Circuit operation              | 50                                                                                                                     |

|   |                   | 3.2.4                                                                            | BICI two-point calibration     | 55                                                                                                                     |

|   |                   | 3.2.5                                                                            | Single-phase BICI accuracy     | 57                                                                                                                     |

|   |                   | 3.2.6                                                                            | Circuit implementation         | 58                                                                                                                     |

|   | 3.3               | Simula                                                                           | ation and Experimental Results | 61                                                                                                                     |

|   |                   | 3.3.1                                                                            | BICS                           | 61                                                                                                                     |

|   |                   | 3.3.2                                                                            | Single-phase BICI              | 65                                                                                                                     |

|   | 3.4               | Conclu                                                                           | usions                         | 68                                                                                                                     |

|   |                   |                                                                                  |                                |                                                                                                                        |

| 4 | Dou               | ible-Ph                                                                          | ase Built-In Integrator        | 70                                                                                                                     |

| 4 |                   |                                                                                  | ase Built-In Integrator        | 70                                                                                                                     |

| 4 | <b>Dou</b><br>4.1 |                                                                                  | ase Built-In Integrator        |                                                                                                                        |

| 4 |                   | Introdu                                                                          |                                | 70                                                                                                                     |

| 4 | 4.1               | Introdu                                                                          | uction                         | 70<br>71                                                                                                               |

| 4 | 4.1               | Introdu<br>Double                                                                | uction                         | 70<br>71<br>71                                                                                                         |

| 4 | 4.1               | Introdu<br>Double<br>4.2.1                                                       | uction                         | 70<br>71<br>71<br>73                                                                                                   |

| 4 | 4.1               | Introdu<br>Double<br>4.2.1<br>4.2.2                                              | uction                         | <ul> <li>70</li> <li>71</li> <li>71</li> <li>73</li> <li>75</li> </ul>                                                 |

| 4 | 4.1               | Introdu<br>Double<br>4.2.1<br>4.2.2<br>4.2.3                                     | uction                         | <ul> <li>70</li> <li>71</li> <li>71</li> <li>73</li> <li>75</li> <li>76</li> </ul>                                     |

| 4 | 4.1               | Introdu<br>Double<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                            | uction                         | <ul> <li>70</li> <li>71</li> <li>71</li> <li>73</li> <li>75</li> <li>76</li> <li>81</li> </ul>                         |

| 4 | 4.1               | Introdu<br>Double<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                   | uction                         | <ul> <li>70</li> <li>71</li> <li>71</li> <li>73</li> <li>75</li> <li>76</li> <li>81</li> <li>82</li> </ul>             |

| 4 | 4.1               | Introdu<br>Double<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7 | uction                         | <ul> <li>70</li> <li>71</li> <li>71</li> <li>73</li> <li>75</li> <li>76</li> <li>81</li> <li>82</li> <li>82</li> </ul> |

| 5 | On- | Chip Ji  | tter Specification Testing of High-Performance PLLs | 89  |

|---|-----|----------|-----------------------------------------------------|-----|

|   | 5.1 | Jitter D | Definitions                                         | 90  |

|   |     | 5.1.1    | PLL jitter specifications                           | 92  |

|   | 5.2 | Jitter M | fleasurement Circuit (JMC)                          | 92  |

|   |     | 5.2.1    | State of the art in TDC design                      | .93 |

|   |     | 5.2.2    | High-resolution TDC                                 | 98  |

|   |     | 5.2.3    | Notation and definitions                            | 99  |

|   |     | 5.2.4    | Time quantizer                                      | 100 |

|   |     | 5.2.5    | Measurement range extension                         | 105 |

|   |     | 5.2.6    | Calibration                                         | 108 |

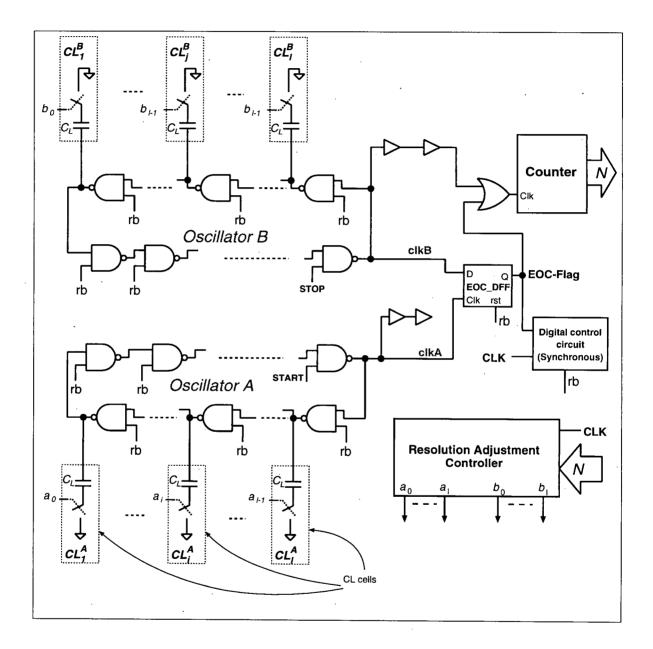

|   |     | 5.2.7    | Automatic resolution adjustment                     | 110 |

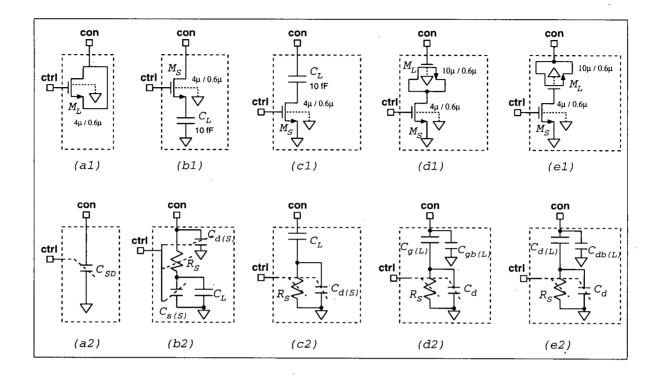

|   |     | 5.2.8    | Controlled load (CL) cell design                    | 116 |

|   |     | 5.2.9    | Resolution adjustment control block                 | 119 |

|   |     | 5.2.10   | TDC error sources                                   | 132 |

|   |     | 5.2.11   | Accuracy, Precision, and Resolution                 | 136 |

|   | 5.3 | Jitter G | enerator                                            | 141 |

|   | 5.4 | Schem    | es for On-Chip Jitter Specification Testing         | 142 |

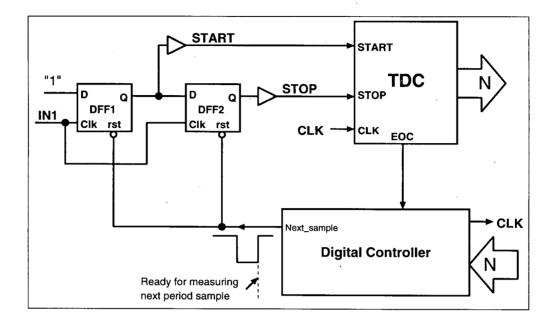

|   |     | 5.4.1    | Cycle-to-cycle jitter measurement                   | 142 |

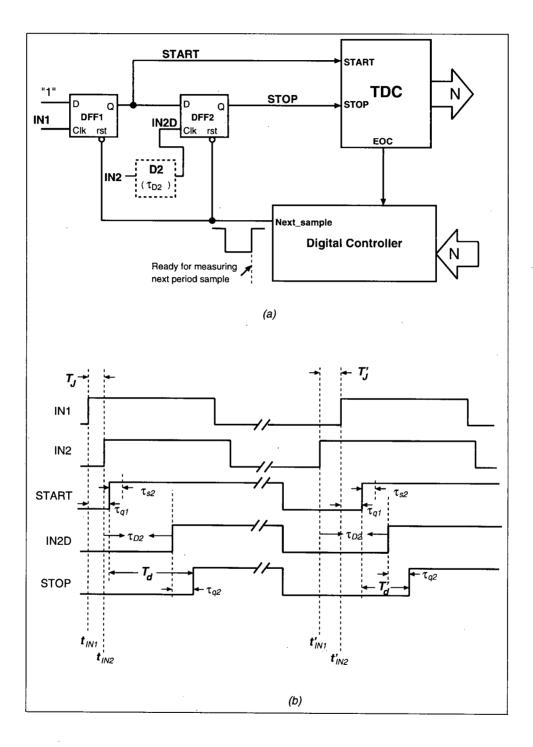

|   |     | 5.4.2    | Relative jitter measurement                         | 142 |

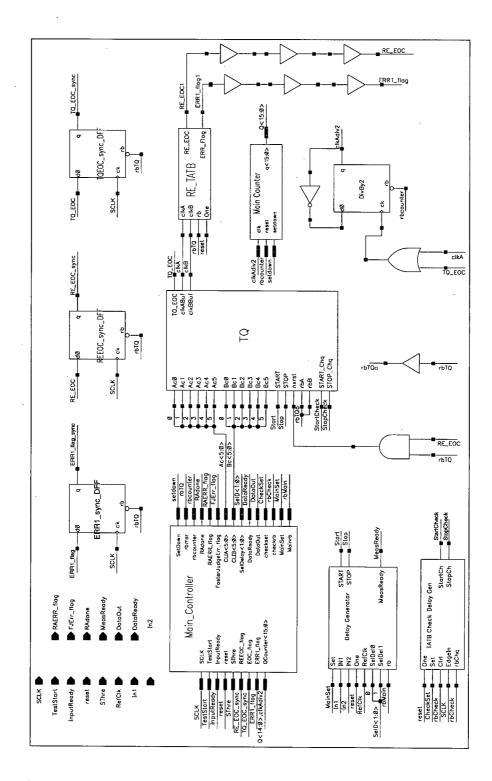

|   | 5.5 | Implen   | nentation                                           | 146 |

|   | 5.6 | Simula   | tion Results                                        | 150 |

|   |     | 5.6.1    | Jitter measurement circuit                          | 150 |

|   |     | 5.6.2    | Accuracy estimation                                 | 151 |

.

.

| 5.7 Conclusions                                                              | . 153 |

|------------------------------------------------------------------------------|-------|

| 6 Summary and Conclusions                                                    | 159   |

| 6.1 Future Research                                                          | . 163 |

| Bibliography                                                                 | 165   |

| Appendix A BICS Frequency Response Analysis                                  | 178   |

| <b>Appendix B</b> N and $\overline{I}$ Relationship in the Single-Phase BICI | 181   |

| <b>Appendix C</b> N and $\overline{I}$ Relationship in the Double-Phase BICI | 185   |

| Appendix D TDC Calibration                                                   | 187   |

| D.1 Two-point Calibration                                                    | . 187 |

| D.2 <i>n</i> -point Calibration Technique                                    | . 190 |

| Appendix E Metastability window of a D flip-flop                             | 194   |

| Appendix F Range Extender Block Analysis                                     | 197   |

| Appendix G Two-Parameter Model for $V_{dd}$ -induced Gate Delay Variations   | 199   |

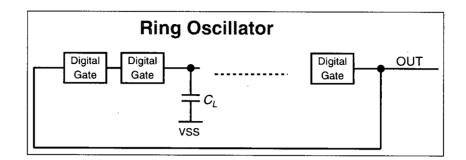

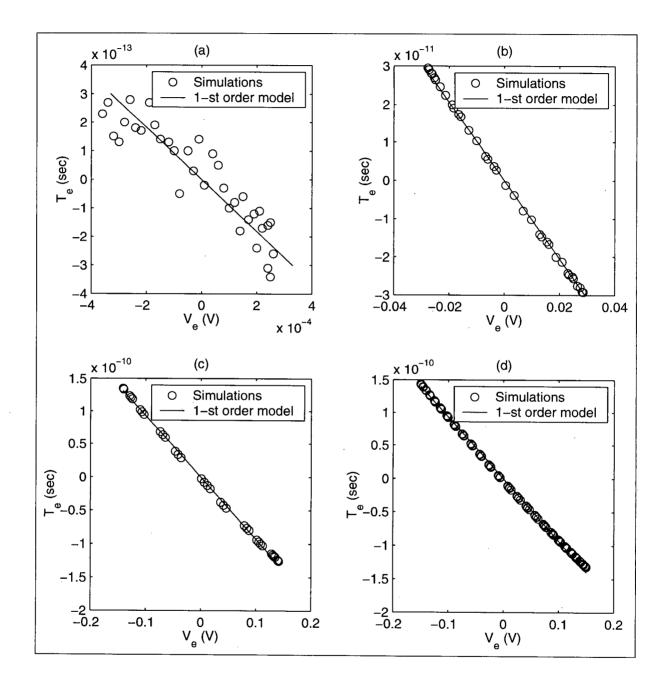

| G.1 Test 1: Single Gate Delay Simulations                                    | . 199 |

| G.2 Test 2: Ring Oscillator Test                                             | . 201 |

| Appendix H TDC Power Supply Noise Analysis                                   | 205   |

# **List of Tables**

| 3.1 | Area overhead comparison of two current mirror matching techniques                                  | 43  |

|-----|-----------------------------------------------------------------------------------------------------|-----|

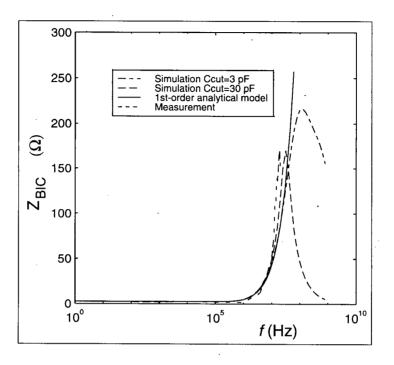

| 3.2 | Low frequency impedance and bandwidth of $Z_{BIC}$                                                  | 61  |

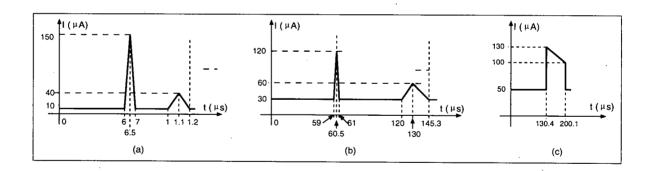

| 3.3 | Single-phase BICI test signals                                                                      | 66  |

| 3.4 | Simulation results for the average current measurements by single-phase                             |     |

|     | BICI circuit                                                                                        | 68  |

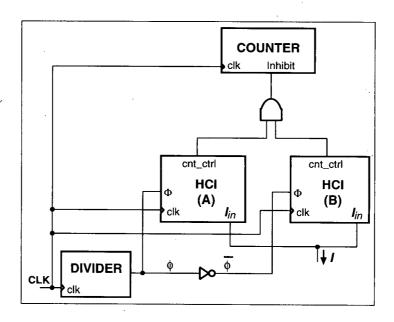

| 4.1 | Double-phase BICI test signals                                                                      | 86  |

| 4.2 | Simulations of average current measurements by double-phase BICI                                    | 88  |

| 5.1 | $T_{dif}$ and $S_{V_{ctrl}}^{T_{dif}}$ for different styles of CL cells. Numbers 1 through 6 in the |     |

|     | first column refer to the states $\vec{a} = 000001, 000011, 000111, 001111, 011111,$                |     |

|     | 111111 in test bench circuit shown in Fig. 5.10, respectively.                                      | 120 |

| 5.2 | Specifications of the implemented CL cells                                                          | 147 |

| . 1 | Number of product terms in the coefficients of $N_{BIC}(s)$ and $D_{BIC}(s)$ 1                      | 180 |

| A.1 |                                                                                                     |     |

# **List of Figures**

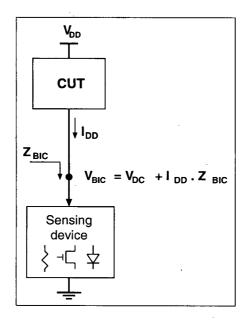

| 1.1  | CUT and the current sensor.                                                          | 3  |

|------|--------------------------------------------------------------------------------------|----|

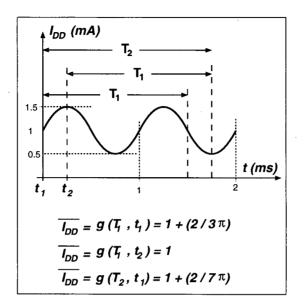

| 1.2  | $\overline{I_{DD}}$ dependence on the duration and beginning of the averaging window | 6  |

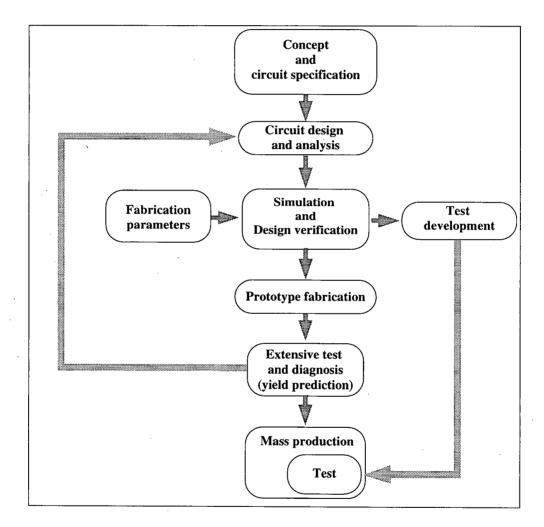

| 2.1  | Integrated circuit design and test flow                                              | 15 |

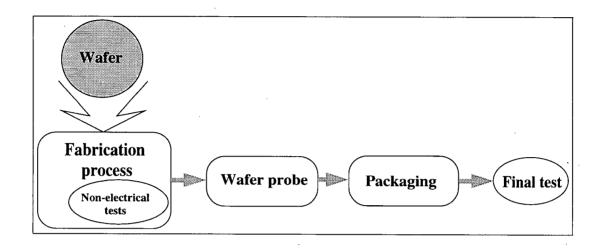

| 2.2  | Integrated circuit test stages.                                                      | 18 |

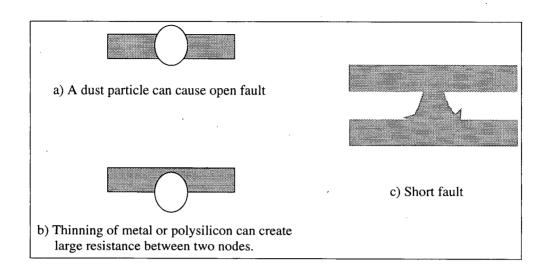

| 2.3  | Examples of faults due to local defects                                              | 20 |

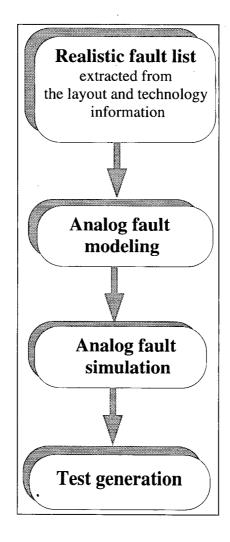

| 2.4  | Inductive fault analysis flow diagram.                                               | 33 |

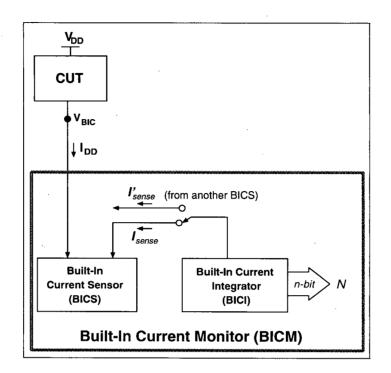

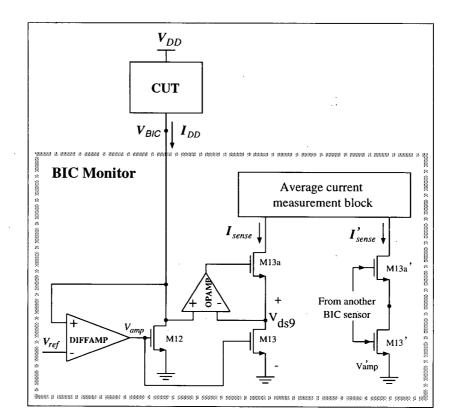

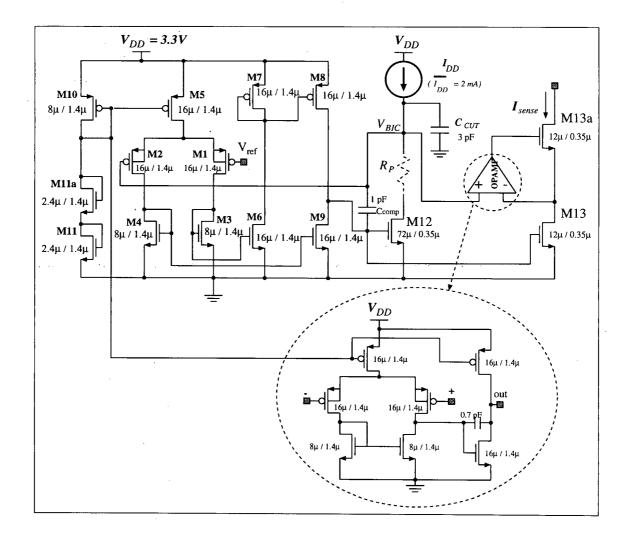

| 3.1  | The proposed current monitor.                                                        | 39 |

| 3.2  | The block diagram of the current sensor.                                             | 41 |

| 3.3  | Current sensor circuit                                                               | 44 |

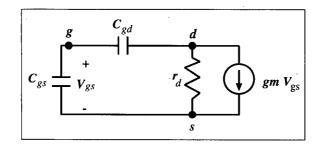

| 3.4  | AC model of a MOS transistor.                                                        | 45 |

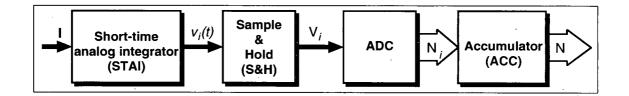

| 3.5  | Single-phase BICI functional block diagram                                           | 48 |

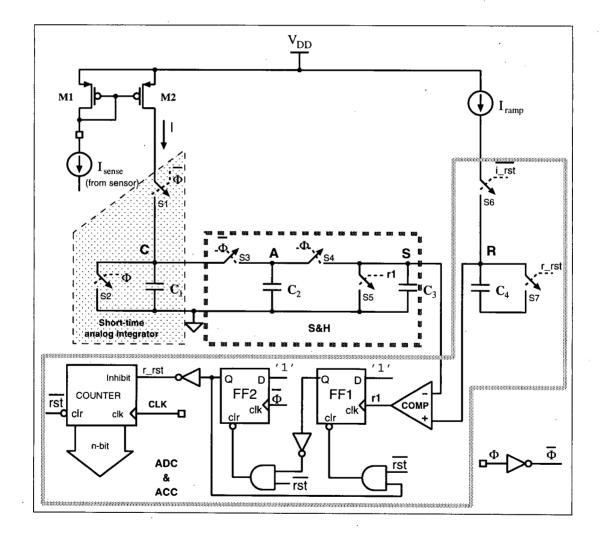

| 3.6  | Single-phase BICI circuit schematic                                                  | 50 |

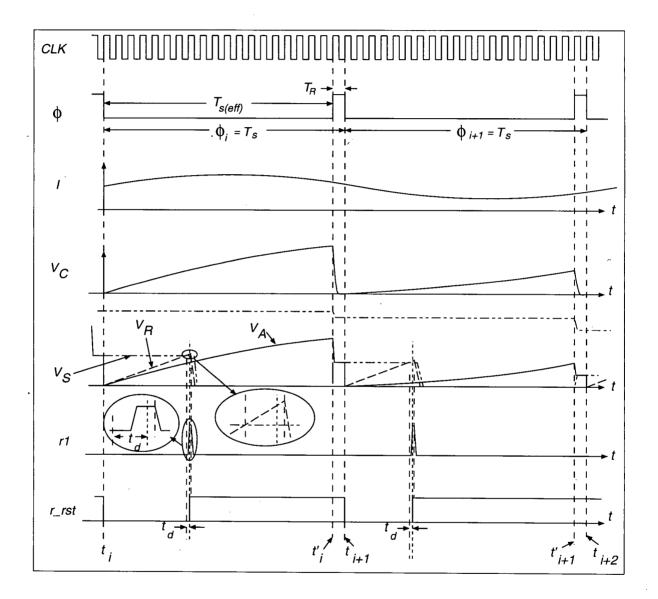

| 3.7  | Timing diagram and different waveforms in the BICI circuit of Fig. 3.6 .             | 52 |

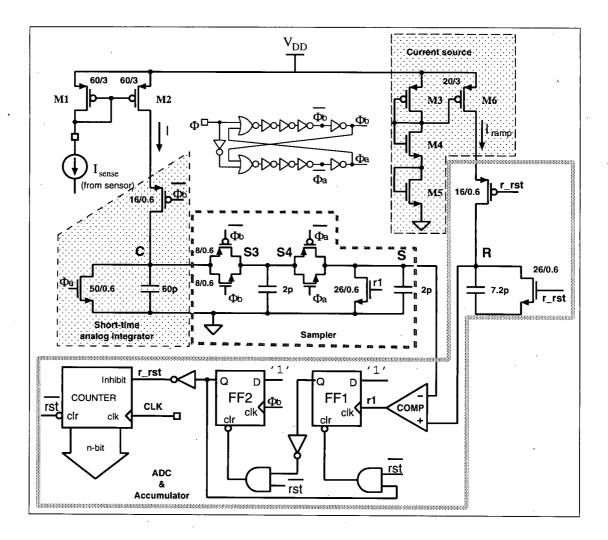

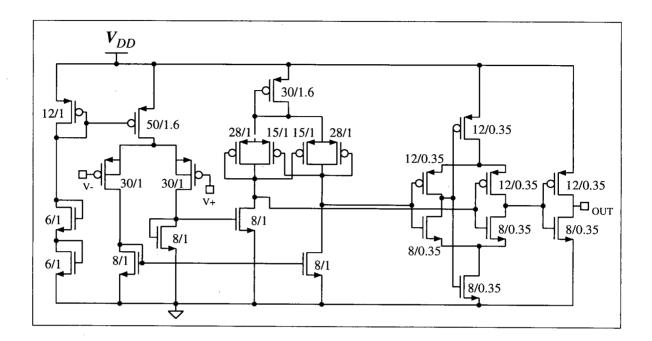

| 3.8  | The transistor-level schematic of the integrator circuit                             | 59 |

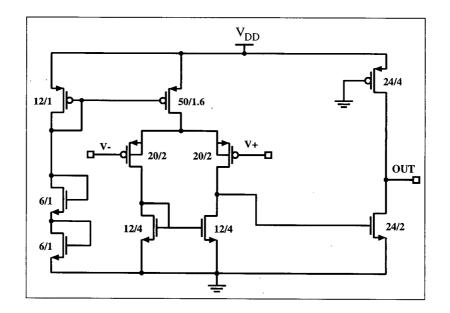

| 3.9  | Schematic of the comparator                                                          | 60 |

| 3.10 | $Z_{BIC}$ versus frequency                                                           | 62 |

Х

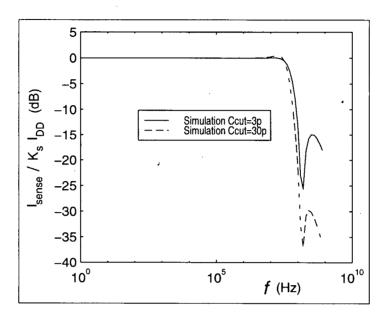

| 3.11 | $I_{sense}/K_s I_{DD}$ transfer function for $I_{DD} = 1 mA$ at the operating point ( $K_s =$ |                 |

|------|-----------------------------------------------------------------------------------------------|-----------------|

|      | 1/6)                                                                                          | 63              |

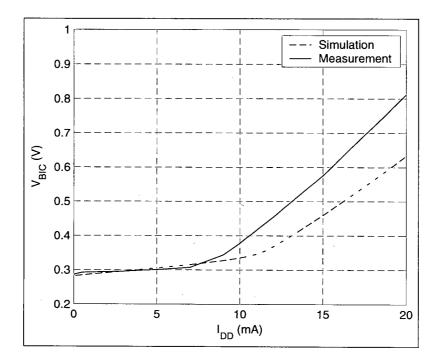

| 3.12 | $V_{BIC}$ versus $I_{DD}$ DC characteristics                                                  | 64              |

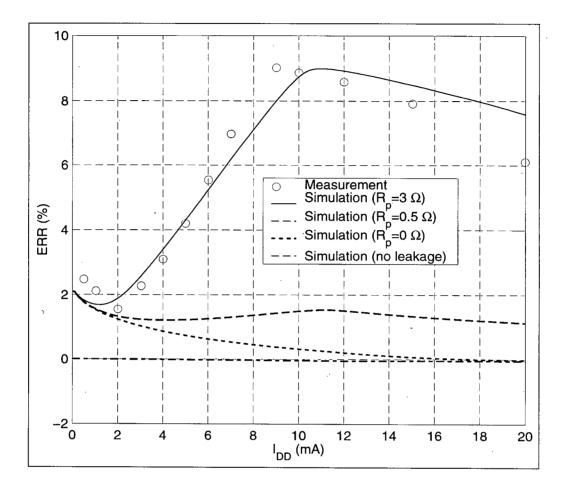

| 3.13 | Measurement and simulation results for $ERR$ versus $I_{DD}$ considering the                  |                 |

|      | parasitic resistances in the circuit.                                                         | 65              |

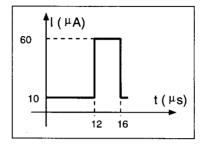

| 3.14 | Current waveforms SPK1, SPK2, and SQ for validating the operation of the                      |                 |

|      | single-phase BICI circuit                                                                     | 67              |

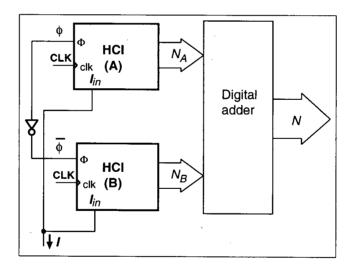

| 4.1  | Double-phase BICI functional block diagram                                                    | 71 <sup>-</sup> |

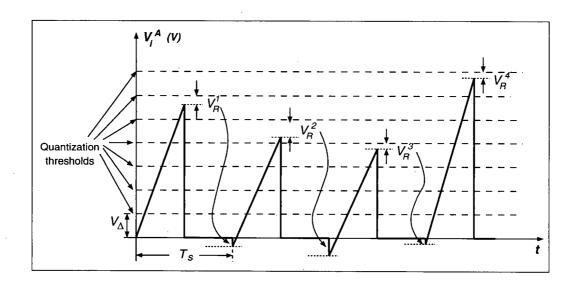

| 4.2  | Quantization residue feed forward technique used in the ADC of double-                        |                 |

|      | phase BICI                                                                                    | 74              |

| 4.3  | Current integrating circuit schematic                                                         | 75              |

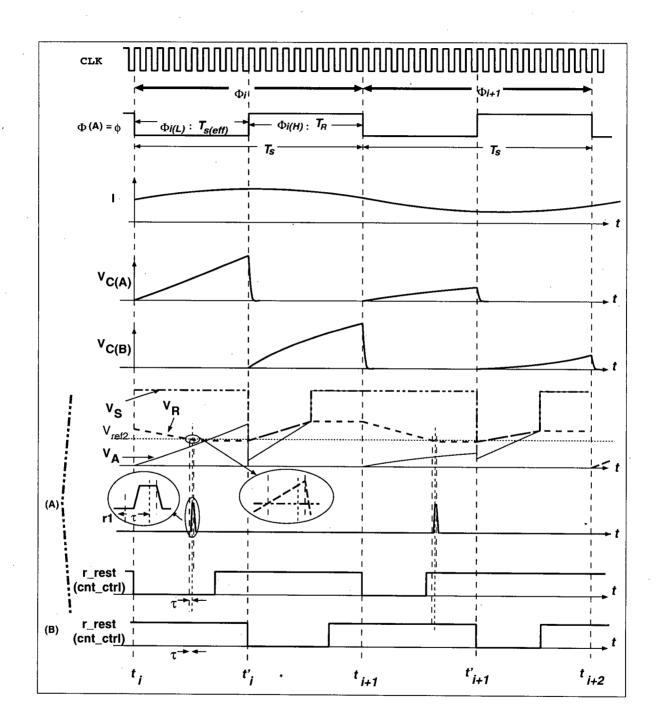

| 4.4  | Timing diagram and different waveforms in the integrator circuit of Fig. 4.3                  | 77              |

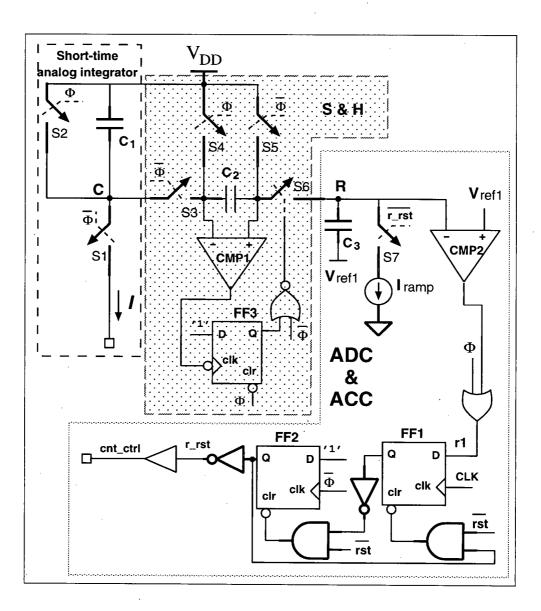

| 4.5  | Half-wave current integrating circuit schematic                                               | 79              |

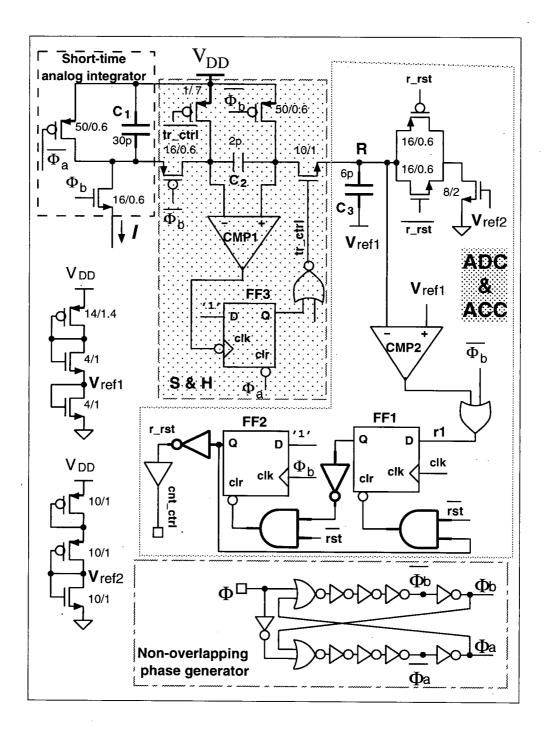

| 4.6  | The transistor-level schematic of the half-wave integrator circuit (HCI)                      | 84              |

| 4.7  | Schematic of the comparator                                                                   | 85              |

| 4.8  | Current waveforms for validating the operation of the integrator circuit                      | 87              |

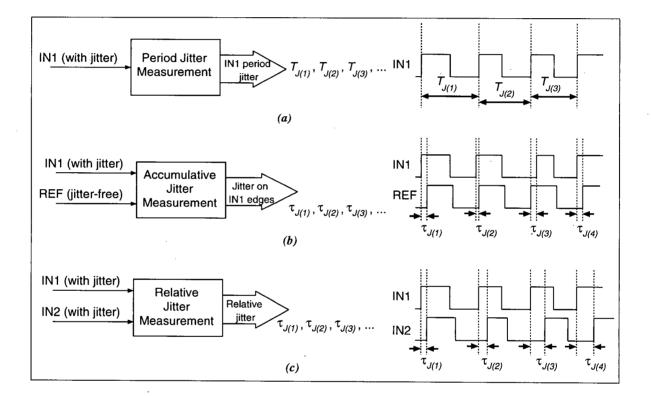

| 5.1  | (a) Measuring cycle-to-cycle or period jitter, (b) Measuring accumulative                     |                 |

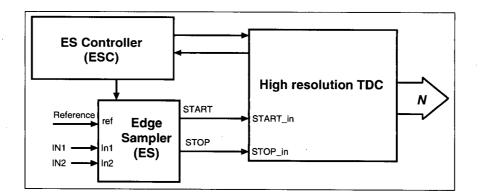

|      | jitter using a reference clock, (c) Measuring relative jitter                                 | 91              |

| 5.2  | Block diagram of the proposed jitter measurement circuit                                      | 93              |

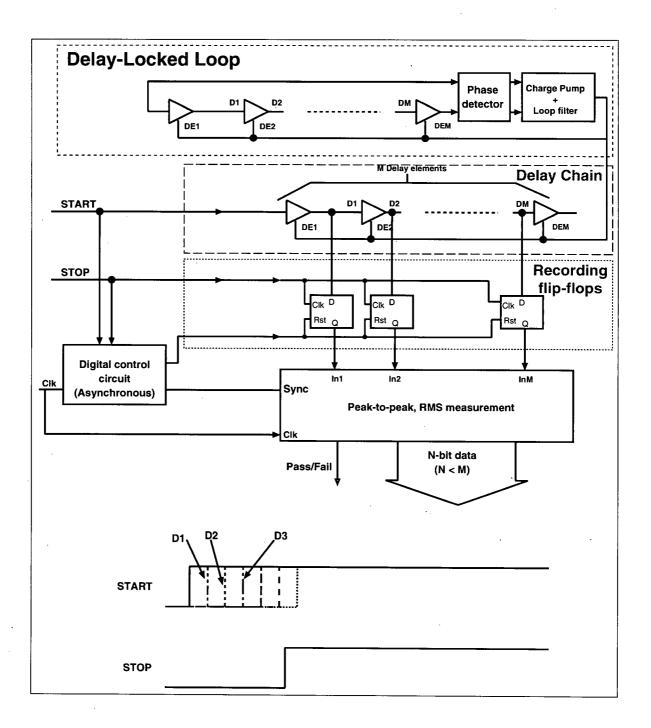

| 5.3  | Time digitization using a delay chain                                                         | 95              |

| 5.4  | Time digitization using differential delay technique                                          | 97              |

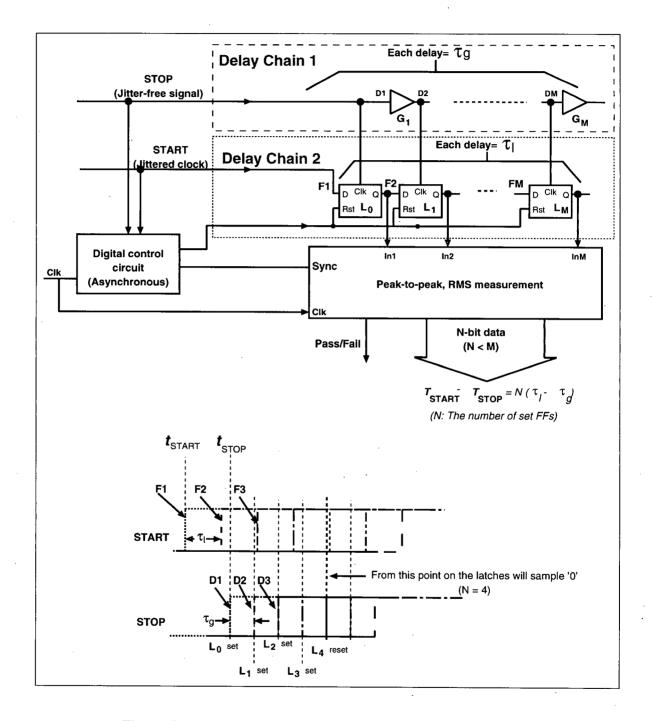

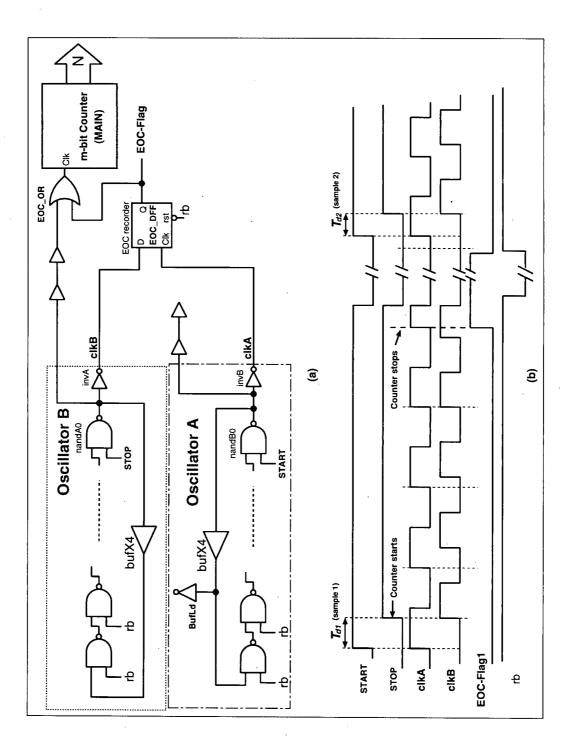

| 5.5  | Block diagram of the proposed TDC circuit                                                     | 99              |

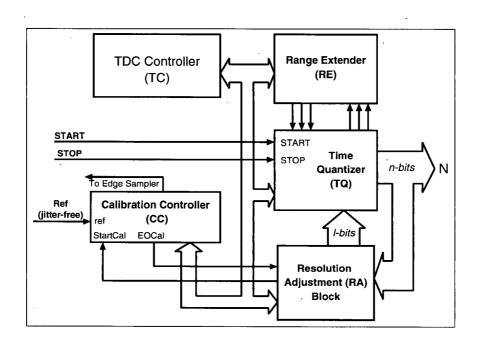

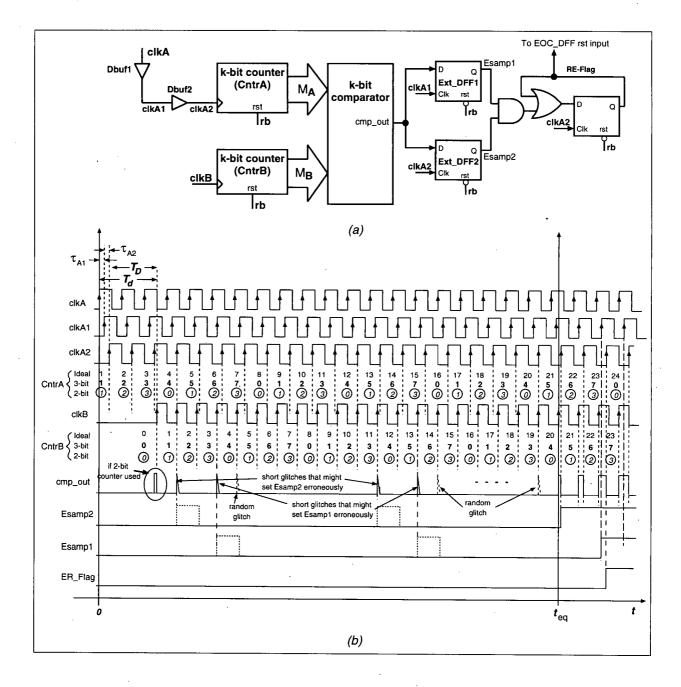

| 5.6  | Time digitization using two oscillator period difference method 1                             | .02             |

| 5.7  | Measurement range extension to $(2^k - 1)T_A \dots \dots$ |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

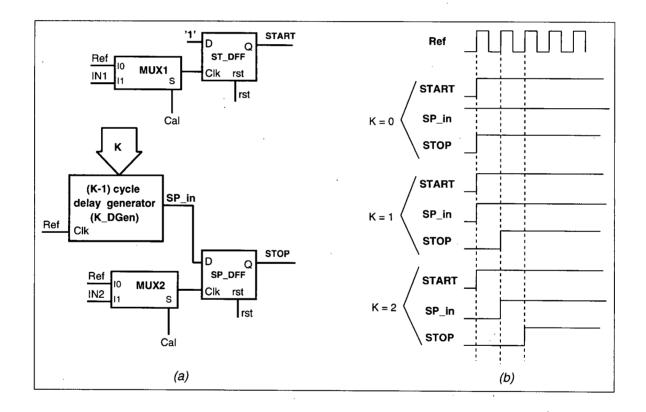

| 5.8  | $KT_{ref}$ interval selection circuit                                                                                                                           |

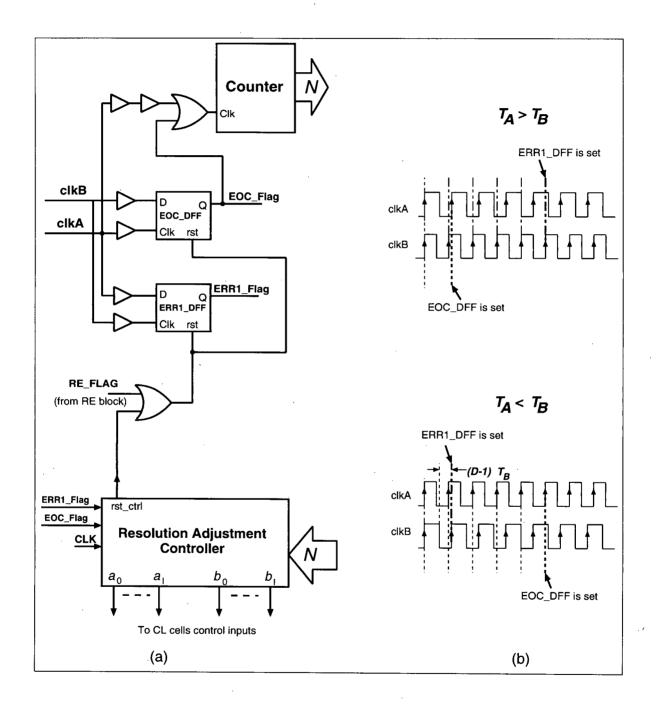

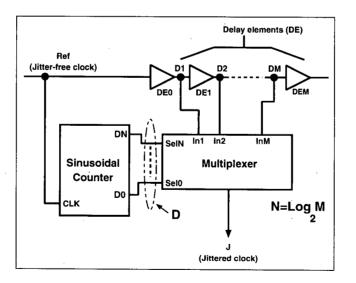

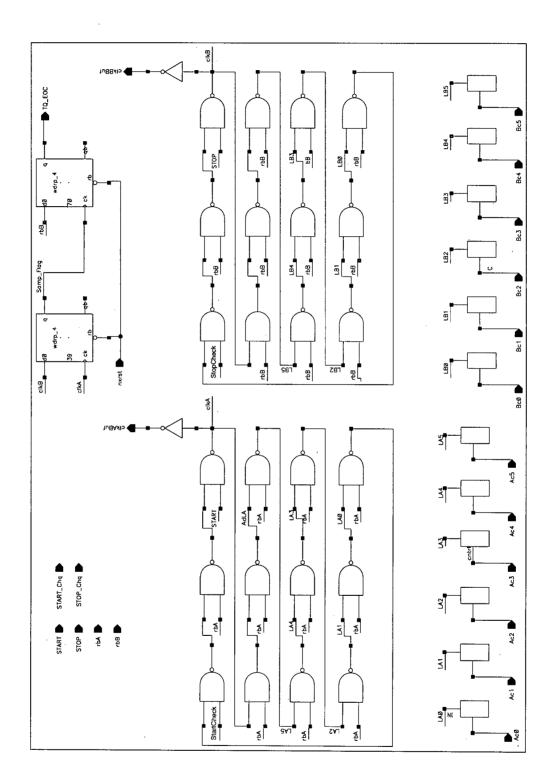

| 5.9  | Automatic resolution adjustment circuit                                                                                                                         |

| 5.10 | CL cell evaluation test bench                                                                                                                                   |

| 5.11 | Different CL cell styles: (a1, b1, c1, d1, e1) Circuits; (a2, b2, c2, d2, e2)                                                                                   |

|      | simplified models                                                                                                                                               |

| 5.12 | Circuit for checking the necessary condition that $T_A > T_B$                                                                                                   |

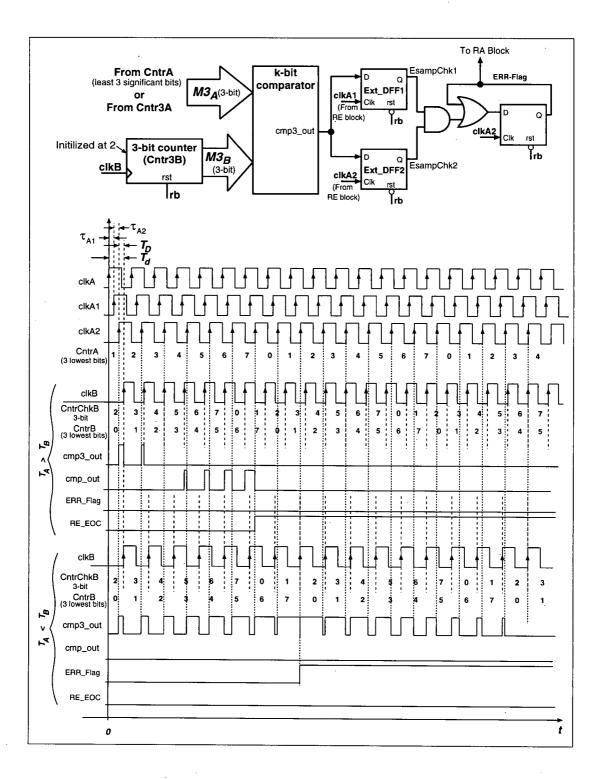

| 5.13 | Alternative circuit for checking the condition $T_A > T_B$                                                                                                      |

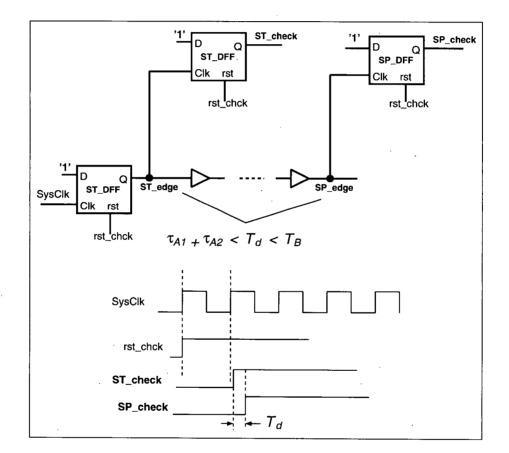

| 5.14 | Circuit to generate $\tau_{A1} + \tau_{A2} < T_d < T_B$ for TATB checker circuit 125                                                                            |

| 5.15 | Algorithms for selecting $\vec{a}$ and $\vec{b}$ in uniform load CL method, (a) exhaustive                                                                      |

|      | search, (b) directed search                                                                                                                                     |

| 5.16 | Exhaustive search algorithms for selecting $\vec{a}$ and $\vec{b}$ in the 'incremental step'                                                                    |

|      | CL cell method                                                                                                                                                  |

| 5.17 | Semi-exhaustive search algorithm for selecting $\vec{a}$ and $\vec{b}$ in the 'incremental                                                                      |

|      | step' CL cell method                                                                                                                                            |

| 5.18 | Fast search algorithm for selecting $\vec{a}$ and $\vec{b}$ in the 'incremental step' CL cell                                                                   |

|      | method                                                                                                                                                          |

| 5.19 | Jitter generator circuit                                                                                                                                        |

| 5.20 | Cycle-to-cycle jitter measurement                                                                                                                               |

| 5.21 | Relative jitter measurement                                                                                                                                     |

| 5.22 | Top block-level schematic of the jitter measurement circuit                                                                                                     |

| 5.23 | Implemented TQ circuit                                                                                                                                          |

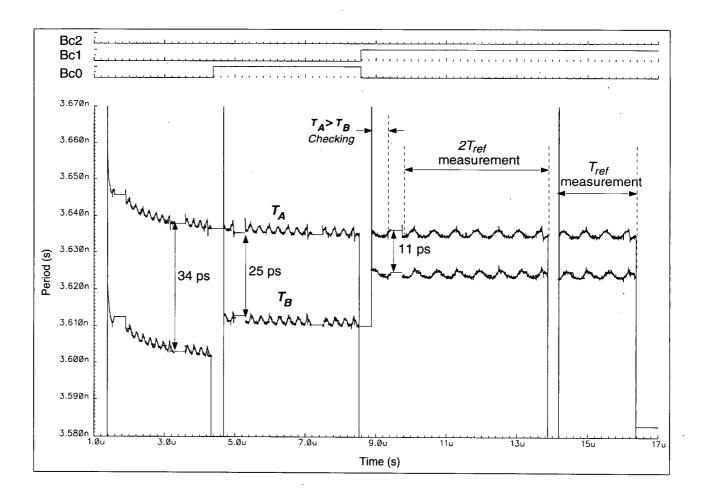

| 5.24 | TDC resolution adjustment simulation waveforms                                                                                                                  |

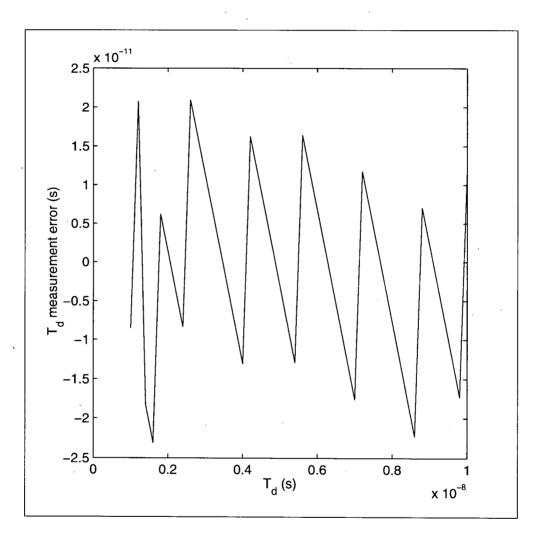

| 5.25        | TDC measurement error for resolution of 34.1 ps                                        |

|-------------|----------------------------------------------------------------------------------------|

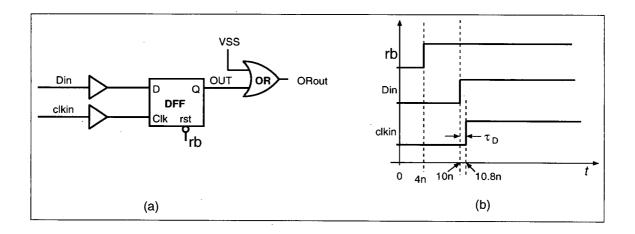

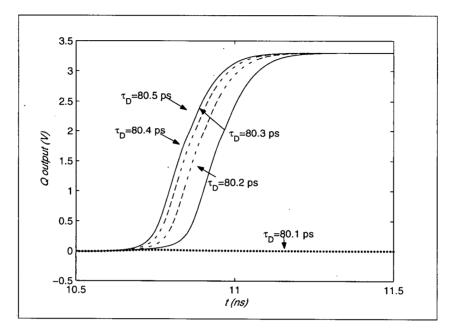

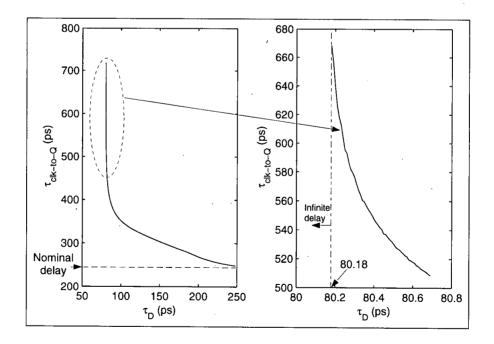

| <b>E</b> .1 | The test bench for estimating the metastability window of a D flip-flop 195            |

| E.2         | Simulation results of the flip-flop output for five different values of $\tau_D$ 196   |

| E.3         | Simulated clk-to-Q delay versus $\tau_D$                                               |

| 0.1         |                                                                                        |

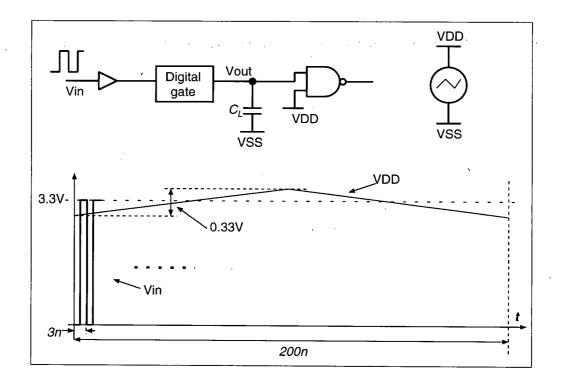

| G.1         | The test bench for validating the two parameter model for $V_{dd}$ -induced gate       |

|             | delay variations                                                                       |

| G.2         | The ring oscillator test bench to validate the two-parameter model for $V_{dd}$ -      |

|             | induced gate delay variations                                                          |

| G.3         | Ring oscillator period jitter from simulation and the two-parameter model              |

|             | for $V_{dd}$ -induced gate delay variations, a) $f=1.1$ GHz, b) $f=350$ MHz, c) $f=50$ |

| · •         | MHz, d) $f=5$ MHz                                                                      |

## Claims of Originality

#### Chapter 3:

- A novel analytical method for obtaining the frequency response of a built-in current sensor (BICS). This analysis leads to closed-form equations for the frequency domain characteristics of the BICS.

- IC Prototype measurement results for the BICS. Such results leads to conclusions about the critical importance of the routing resistances in BICS layout design.

- A novel single-phase built-in current integrator (BICI). Both the current integration technique and the circuit implementation are new. This design is small enough to reside on-chip, provides a digital signature, and is robust against process variations.

#### Chapter 4:

• A novel *quantization residue feed forward* technique. This technique prevents accumulation of ADC quantization noise which significantly enhances the accuracy of the BICI. Using this technique leads to a new, double-phase BICI which provides high accuracy for any power supply current waveform.

#### Chapter 5:

- A novel time quantizer (TQ) structure. This TQ structure achieves high resolution and high accuracy simultaneously.

- New resolution adjustment (RA) techniques for time interval measurement. These techniques guarantee high resolution under process variations.

- A high-resolution time to digital converter (TDC). The TDC uses the designed TQ and resolution adjustment circuits to measure time interval with high-resolution and accuracy. The design of this circuit is compatible with a conventional digital design flow.

- A jitter measurement circuit (JMC). The JMC uses the designed TDC to perform highresolution and accuracy single-shot jitter measurement with resolution and accuracy of approximately 10 ps.

- A jitter generator circuit. This circuit performs digital phase modulation using only digital gates. It can be used for jitter tolerance testing of phase locked loops.

- A novel power supply noise-induced gate delay variation model. This model has only two fitting parameters and is used to show the immunity of the TQ to power supply noise.

# Acknowledgements

My special thanks goes to Dr. André Ivanov, my supervisor, whose invaluable support and constant help, encouragement and guidance made this contribution possible. He has been a great source of inspiration and a role model to me not only in technical and educational sense but also in many aspects of life as a person.

Many thanks also to my supervisory committee, specially Dr. Mike Jackson, for reading my thesis carefully and giving me precious feedback which resulted in great amount of improvement in both style and content of this thesis.

I also thank Mr. Yong Luo, Mr. Zhurang Zhao for their help in testing the fabricated chips, writing 'vhdl' codes and also for their feedback and interesting discussions about different circuits. My thanks also to Mr. Farinam Farahmand and Mr. Alireza Moshtaghi for writing the CAD tools which were used from time to time in the course of this research.

I'd like also to thank Micronet, PMC-Sierra for their financial support and CMC for providing design tools and access to fabrication facilities.

Throughout the years of my Ph.D., so many family and friends have been great sources of motivation and inspiration to me which enabled me to complete this work. Thousands of thanks to all of them specially my loving parents and my wonderful sisters, Nasrin and Nooshin. And, so many thanks to my fiancée, Mojgan, who understood, helped, and encouraged me during the intense and sometimes difficult months that I was busy writing this thesis.

## Sassan Tabatabaei-Zavareh

The University of British Columbia February 2000 To my loving parents

# Chapter 1

# **Motivations and Overview**

Testing is an integral part of the integrated circuit (IC) production which ensures the correct functionality of the final product shipped to the customer. Smaller geometry technologies, higher density [1], increased performance and implementation of different sub-systems (analog, digital, memory, micro-electro-mechanical systems (MEMS), ...) on the same chip require new test methodologies. Without such methodologies, testing cost can become the major hurdle in the way of the future progress of IC production industries [2].

This work is an effort to provide effective test solutions for testing widely used mixedsignal circuits, more specifically phase-locked loop (PLL) circuits. Two different strategies have been developed for testing embedded mixed-signal circuits: power supply current testing and jitter testing. The first scheme can be used to test any analog and mixed-signal circuit, whereas the second one is more appropriate for timing circuits such as clock recovery, clock synthesis, and clock skew compensation circuitry, which are often PLL based.

This chapter outlines the state of the art and motivations of the research reported in the rest of this thesis. Sec. 1.1 and 1.2 review the literature and the incentive for designing

1

the on-chip current monitor and jitter test circuits, respectively. A background of IC testing, and analog and mixed-signal test methodologies, including the definitions of the major concepts, is given in Chapter 2 for readers who are interested or do not have sufficient background in mixed-signal IC testing.

## **1.1** Built-in current monitoring

The success of supply current monitoring in digital CMOS integrated circuits (IDDQ testing) [3, 4, 5] has prompted researchers to investigate the feasibility of monitoring supply current ( $I_{DD}$ ) in analog circuits as a testing methodology [6, 7, 8, 9]. The results of these investigations suggest that  $I_{DD}$  testing, although not sufficient by itself, can offer additional fault coverage for analog circuits.

Often,  $I_{DD}$  testing in analog circuits is based on measuring the average, rms, or the value of the current at specific times, and comparing these against a pre-defined tolerance range. If the measured value falls outside the associated fault-free tolerance range, the circuit is declared faulty [6, 7, 8]. Average  $I_{DD}$  is a convenient and attractive test signature because it is a compact indicator of the current value over time. It also serves as a means of power monitoring when the supply voltage is constant [10].

Due to the lack of resolution of off-chip current sensors, parasitic currents of pads, and also fault masking effects (*e.g.*, the  $I_{DD}$  of one block masking the faulty  $I_{DD}$  of another one), it is necessary to isolate the analog blocks in small groups, sense the supply current of each group using built-in current sensors (BICS), and average the associated  $I_{DD}$ 's on the chip [6].

## 1.1.1 On-chip current sensing

A number of different BICS's have been proposed for current monitoring. All these sensors insert a current sensing device [11, 12, 13, 14] or rely on the circuit intrinsic impedance in the  $I_{DD}$  path [15], as shown in Fig. 1.1. A voltage drop across the sensing device ( $V_{BIC}$ )

Figure 1.1: CUT and the current sensor.

results as  $I_{DD}$  passes through it. Therefore, the circuit under test (CUT) supply voltage,  $V_{CUT}$ , is:

$$V_{CUT} = V_{DD} - V_{BIC} \tag{1.1}$$

Drawbacks of the  $V_{BIC}$  voltage drop include performance degradation of the CUT, *i.e.*, additional delay and noise in the circuit [16].

$V_{BIC}$  can usually be expressed as:

$$V_{BIC} = V_{DC} + V_I = V_{DC} + f(I_{DD})$$

(1.2)

where  $V_{DC}$  and  $V_I$  are the  $I_{DD}$ -independent and  $I_{DD}$ -dependent components of  $V_{BIC}$ , respectively, and f is the function relating  $V_I$  to  $I_{DD}$ .  $V_{DC}$  is often a DC voltage whose effect is the reduction of the CUT supply voltage. The  $V_I$  component of  $V_{BIC}$ , to a first order, can be modeled by an impedance ( $Z_{BIC}$ ) in the supply current path (as illustrated in Fig. 1.1). The impact of  $V_{DC}$  on the operation of the CUT can be minimized by choosing small values of  $V_{DC}$  and designing the CUT to operate with reduced supply voltage.  $Z_{BIC}$ , however, can cause an unacceptable degradation in the CUT performance due to the induced noise, *i.e.*,  $V_{BIC} = Z_{BIC}I_{DD}$ , resulting from  $I_{DD}$  variations.

Most current sensors proposed in the literature use a resistor or a MOS transistor biased in the triode region as the current sensing device. The voltage drop across the sensing device is used as the current value indicator. Such sensing devices trade sensitivity for impact on CUT performance. Designing for small values of  $Z_{BIC}$  reduces the impact of the sensor on the CUT performance by reducing  $V_{BIC}$  variations [17], which in turn reduces the sensitivity of the sensor. In digital circuit IDDQ testing, high current sensor sensitivity is not required because the sensor only needs to distinguish two values of current which are typically at least one or more orders of magnitude apart [4]. In analog circuits, however, both a high sensitivity and a low  $Z_{BIC}$  value are required for acceptable performance.

The current sensor from [6] uses an NMOS transistor operating in the triode region for sensing  $I_{DD}$  of embedded analog blocks. This sensor cannot provide a high sensitivity and a low  $Z_{BIC}$  simultaneously. Even if the sensitivity requirement is relaxed, the sensor needs a very large NMOS transistor (width ~ 1mm - 10mm) to obtain an acceptably small  $Z_{BIC}$  (e.g.,  $10\Omega$  to  $1\Omega$ ). In [18], a low voltage current mirror based on a NMOS device and a buffer is used as the sensor. Although this design reduces  $V_{DC}$ , it has two problems: (i)  $V_{DC}$  is process dependent and *(ii)* it does not reduce  $Z_{BIC}$ . The circuit proposed in [10] provides both a small  $Z_{BIC}$  and a low process-insensitive  $V_{DC}$ . However, in [10] the  $Z_{BIC}$  characteristics have not been analyzed. Such an analysis is essential to optimize the sensor's characteristics to achieve a low  $Z_{BIC}$  in a wide frequency range while minimizing the sensor area.

#### **1.1.2 On-chip current averaging**

The current sensed by a BIC sensor has to be integrated over a time window to obtain the average  $I_{DD}$  current,  $\overline{I_{DD}}$  as shown below:

$$\overline{I_{DD}}(T,t_b) = \frac{1}{T} \int_{t_b}^{t_b+T} I_{DD}(t) dt$$

(1.3)

where T and  $t_b$  are the duration and the starting time of the averaging time window. Eqn. 1.3 indicates that by choosing a fixed averaging period T, averaging can be replaced with integration. In general,  $\overline{I_{DD}}$  depends on T and  $t_b$ ; for example, Fig. 1.2 shows how  $\overline{I_{DD}}$  varies for three different selections of T and  $t_b$  when  $I_{DD}$  is a sinusoid with offset. This requires timing circuitry to synchronize the averaging operation with  $I_{DD}$ . However, if T is chosen such that  $T \gg 1/BW_I$  where  $BW_I$  is the bandwidth of  $I_{DD}$  AC component, then  $\overline{I_{DD}} \sim I_{DD(DC)}$  where  $I_{DD(DC)}$  is the  $I_{DD}$  DC component which is independent of T or  $t_b$ .

Therefore, to avoid the need for synchronizing circuitry, averaging should be performed over a long period of time, e.g.,  $T = 100/BW_I$ . This condition results in long averaging windows in the range of a few tens of milliseconds for circuits such as audio frequency filters in which  $BW_I \sim 4 \, kHz$ .

Figure 1.2:  $\overline{I_{DD}}$  dependence on the duration and beginning of the averaging window

A simple method of integrating  $I_{DD}$  is to pass it through a capacitor; the voltage stored across the capacitor at the end of the integration window will be proportional to  $\overline{I_{DD}}$  [10],

$$V_C = \frac{1}{C} \int_0^T I_{DD} dt = \frac{T}{C} \overline{I_{DD}}$$

(1.4)

Using this method may require a large capacitor. For example, assuming a supply voltage of 3.3V, an  $\overline{I_{DD}} = 100 \ \mu A$  and  $T = 1 \ msec$ , a 30 nF capacitor would be required to ensure that  $V_C < V_{DD}$  during integration, and therefore the electronics providing the current to the capacitor do not saturate. Such a large capacitor would obviously not be able to reside on-chip. In [19] a capacitor connected between  $V_{SS}$  and  $V_{DD}$  terminals of the CUT, and the power supply is switched periodically to estimate the CUT power consumption. This estimate also provides an indirect estimate of  $\overline{I_{DD}}$ . This method, however, does not measure  $\overline{I_{DD}}$  directly and also requires a large capacitor. Therefore, an on-chip bus or multiplexer is needed to direct the  $I_{DD}$  from different analog blocks on the chip to an output pin. In addition to requiring an extra pin, the bus and pad parasitics reduce  $\overline{I_{DD}}$  measurement accuracy.

## **1.2 PLL testing**

An example of a widely used class of circuits requiring functional testing is phase-locked loops (PLL), since most structural test methods are either too intrusive (affect the performance) or provide poor correlation to important PLL specifications such as jitter.

PLL testing has gained significant interest recently due to the widespread integration of PLLs in mixed-signal communications and data processing ICs. PLLs are used in timing applications such as clock synthesis, clock recovery, and clock skew compensation. In such applications, the single most important set of specifications for a PLL is its jitter characteristics, such as intrinsic jitter, jitter transfer function, and jitter tolerance[20]. In fact, jitter specifications are critical in most high-speed interfaces because of a limited available timing budget. Jitter testing, however, is an expensive test because it requires costly equipment and long test time[21].

A number of authors have tried to find cost-effective test methods for PLLs [22, 23, 8, 24, 25, 26, 27, 28, 29, 30, 31, 32]. Works in [22] suggests partial specification testing such as lock range, lock time, and power supply current for PLL testing. Dalmia et al. [8, 29] also show the viability of power supply current monitoring for PLL testing. The authors of [24, 25] propose methods for efficient fault simulation of PLLs and suggest lock frequency range measurement for PLL testing. Although a combination of these techniques seems to provide a good fault coverage, it is difficult to correlate the test results to important jitter specifications, partly because simulating jitter for fault-free and faulty circuits is extremely

difficult due to a lack of tools capable of simulating noise in non-linear dynamic circuits. Azias et al. [26] proposes a reconfiguration technique for testing ring oscillator-based PLLs. This technique has the advantage of being compatible with digital test methods, but it requires reconfiguring sensitive parts of a PLL. Also, it exhibits the problem of unknown correlation of test results and functional specifications.

A practical solution to PLL testing is to directly measure the jitter characteristics of the PLLs on the chip. The following section reports major methods for on-chip jitter testing.

### **1.2.1** Jitter testing

Jitter testing often requires jitter measurement. Jitter measurement techniques are divided into two categories: frequency domain and time domain. Historically, spectrum-based techniques have been used more often because of the availability of high-frequency spectrum analyzers [33, 21]. The drawback of this method is that the amplitude distortion and noise degrade the measurement accuracy. Also, this method is not suitable for on-chip measurement because performing high-resolution spectrum analysis on the chip requires a significant amount of design time and silicon area.

In the time domain, jitter measurement can be performed using modulation domain analysis [34], histogram-based [21] or undersampling [21] techniques. In [30], a BIST circuit is proposed which is capable of measuring lock range and loop gain of a PLL in addition to performing a jitter test. Because of its statistical nature and dependence on bit error rate (BER), the application of the jitter testing approach in [30] is limited primarily to clock recovery PLLs. Also, high-resolution measurement requires generation of precise, high-resolution and stable delays. Two US patents in [27] and [28] outline on-chip jitter

8

measurement techniques for PLL testing. The BIST circuits proposed in these patents are mixed-signal and their resolution is limited to one gate delay, which is inadequate for testing high-speed PLLs. In [31], a jitter transfer function measurement circuit is proposed for PLL testing; however the jitter measurement circuit proposed does not have sufficient resolution for intrinsic jitter testing. Veillette et al. [32] proposes an interesting method for generating jitter at the input of the PLL for jitter transfer testing. This method, however, requires reconfiguration of the feedback in the PLL loop, which could affect the performance of the loop.

Since most of the time domain techniques require some sort of time interval measurement, on-chip accurate jitter measurement necessitates high resolution on-chip time measurement circuitry. For on-chip time interval measurement, a number of time-to-digital converters (TDC) circuits, used in physics experiments, have been proposed in the literature [35, 36, 37, 38, 39]. Such circuits, however, are mixed-signal, require custom design and layout, occupy a large area, do not provide high resolution, or rely heavily on matching of the elements. The idea of a controlled delay line used in TDCs is also used as an on-chip jitter measurement method in [27]. This circuit, however, is mixed-signal and suffers from the same limitations as most TDCs.

# **1.3** Motivations and Contributions

Although power supply current testing is proposed as an attractive structural testing method for mixed-signal circuits, it has limited applicability due to the lack of a practical BICM scheme. Two issues have to be addressed in an effective BICM:

9

- 1. The current has to be sensed with high resolution without introducing large impedance in the  $I_{DD}$  path

- 2. The  $I_{DD}$  signature has to be digital and accurate. In addition, it has to be generated without requiring large chip area

These requirements led to the design of a BICM reported in Chapter 3. This BICM is capable of sensing  $I_{DD}$  without introducing significant impedance in the power supply current path. It averages the current and generates a digital signature. Since the circuits are compact and easy to design, they are suitable for BIST and DFT applications. The circuits can provide an rms error less than 2% if the  $I_{DD}$  contains significant AC components which are uncorrelated with the system clock.

As another contribution of this thesis, a double-phase built-in current integrator is reported in Chapter 4. This integrator occupies slightly larger area than the single-phase integrator introduced in Chapter 3, but it can measure the average current with an rms accuracy of 1% for any current waveform.

The design of on-chip jitter test circuit was undertaken because the effectiveness of structural tests or non-jitter based partial specification tests can not be proven, and also existing external jitter testing methods are costly, if possible at all. At the start of this effort, there was no solution for high-precision on-chip jitter testing. Even today, the new high-precision on-chip jitter testing technique by Logic Vision, Inc. [30] is based on bit-error-rate whose application is limited to clock-recovery PLLs. Another recent technique has been announced by Fluence Technology, Inc.<sup>1</sup>, but no information is available in the public domain about the specifics of the technique. For a practical and widely applicable jitter BIST solution, we set

<sup>&</sup>lt;sup>1</sup>See the VCOBIST data sheets at http://www.opmaxx.com/products/products.htm

the following objectives for the jitter measurement circuit:

- Single-shot jitter measurements (similar to those performed by an external equipment).

This is to make the test solution independent of the circuit under test

- 2. Compatibility with digital design flow

- 3. Ability to generate digital signatures

- 4. High-resolution and precision (better than 10 ps in a  $0.35\mu m$  technology)

The search for on-chip jitter test solutions resulted in the novel jitter measurement and generation circuit for BIST of PLLs which is presented in Chapter 5. The circuit satisfies all the conditions for a practical BIST circuit mentioned in Sec. 2.2.4 as well as the objectives mentioned above. The measurement circuit is fully digital and automatically synthesizable, occupies an area equivalent to 1200 2-input NAND gate, provides a resolution of approximately 10 ps (~1/5 of a gate delay in a standard 0.35  $\mu m$  technology) and a precision of 11 ps, and generates a digital signature which can be read out by an inexpensive tester. The digital signature can be further analyzed by the tester to obtain the jitter characteristics.

In addition to the circuit structures, a number of design and analysis techniques have been employed in these designs which have wider applications. These techniques are:

- 1. The approximation technique used in Appendix A to obtain a closed form for the frequency response of the BICS

- 2. The noise feed-forward technique presented in Chapter 4, which is an effective method for quantization noise reduction in averaging analog to digital converters

- 3. The differential method used for jitter measurement which provides power supply noise rejection. This property proved in Appendix H makes such architecture a strong candidate for a multitude of high-precision timing circuits

- 4. The  $V_{DD}$ -induced modeling of gate delay variation presented in Appendix G. This model can be used for estimating the effect of power supply noise on digital circuits

# Chapter 2

# **Background And Survey**

Today's electronic integrated circuits are extremely complex and dense. New technologies allow multi-million transistors [1] and mixed-signal circuitry on the same chip. This progress has led to the design of integrated circuits possessing an unprecedented functionality with the expectation that this trend will continue. As the complexity of integrated circuits increases, IC manufacturers face many new challenges, one of which is developing effective test solutions for ICs.

This chapter provides the background, terminology, and principles often used in the field of IC testing. Sec. 2.1 reviews major concepts and the terminology used in IC testing. Sec. 2.2 reports the major issues encountered and techniques developed for testing mixed-signal circuits in more detail. Sec. 2.3 concludes this chapter by summarizing the important concepts and describing some active research areas in the field of mixed-signal testing.

# 2.1 IC Testing

The typical IC design flow starts with a concept which leads to a set of functionalities and specifications. After that, an appropriate technology is selected which is believed to yield the required performance. Using the appropriate technology models, the specifications are mapped to an implementable design, which is analyzed and simulated to ensure that the design satisfies all the requirements. Subsequently, some prototype ICs are fabricated, characterized and diagnosed thoroughly to determine if the device meets all its specifications under the given process variations. The design and/or fabrication process is corrected according to the results before the IC is sent for production (Fig. 2.1) [40]. In the last stage of production flow, each fabricated device undergoes a series of tests before it is shipped to the customers.

Some tests are performed on the wafer before cutting the dies (wafer test), and more extensive tests are run on the packaged devices (final test). Since time-to-market is a critical factor in the success of an electronic product, the test procedures are often devised parallel to design verification and prototype characterization, and automatic test equipment (ATE) programs are developed before the first batch of devices is fabricated.

This section reviews the major concepts in the field of IC testing. First, in Sec.2.1.1, the fundamental question as to why ICs must be tested is addressed. Then, a definition of test and the difference between test and its close relative, diagnosis, is presented in Sec. 2.1.2. The major test disciplines, functional and structural testing, are defined and compared in Sec. 2.1.3. Often, regardless of the test discipline selected, the concepts of *defect* and *fault* are used to generate or evaluate different test methodologies. These concepts are reviewed in Sec. 2.1.4. They are also used in Sec. 2.1.5 to briefly describe the two general test gen-

Figure 2.1: Integrated circuit design and test flow

eration methodologies, automatic and ad-hoc. Next, in Sec. 2.1.6, Design-for-testability (DFT), built-in self-test (BIST) and the embedded test concepts are defined. These techniques are used when it is difficult to generate or apply the test to the circuit under test. Finally, a very brief review of major test methodologies for digital circuit testing is presented in Sec. 2.1.7 since many of the basic ideas have also found their way into the mixed-signal test domain.

## 2.1.1 Why test integrated circuits?

If a device functions properly under the nominal variations of a fabrication line, why is there a need to test each device at the end of the line? The answer lies in the imperfections of the fabrication line. These imperfections result in some random failures at various stages of the line; *e.g.*, mask misalignments, missing or extra metal, polysilicon or oxide due to spot defects and cracks [40]. Some experts believe that these failures can be avoided by improving the fabrication line, and subsequently increasing the yield to about 100%. Assuming this opinion to be theoretically correct, the need for testing is still unavoidable because

- fabrication line improvement would require resources that may not be justified by the resulting increase in yield. This becomes especially true for the devices with short product life times;

- as fabrication line technology improves, industry demands smaller device geometries and more masking stages which drive the yield down; therefore, the need for testing.

In reality, almost all IC manufacturers test (in-house or outsource to test houses) their final products to bridge the gap between the fabrication imperfections and their customer's expected quality [2].

In some applications such as aviation systems, military equipment, and deep space systems, where correct functionality can be life-critical, the test quality is the important factor and the cost is a secondary concern. However, in commercial and consumer applications, the test choice depends on the trade-off between test quality and test cost. For today's complex chips the test cost can account for 30% of the total cost of the product [41], and may even surpass the cost of manufacturing in near future [2]. As a result, industry has focused on finding efficient ways of testing circuits and systems to increase the quality to cost ratio.

In addition to quality assurance, testing is sometimes used as a critical tool to locate and diagnose failures and to take corrective measures where possible. However, there are distinctions between test and diagnosis which are described next.

#### 2.1.2 Test and diagnosis

In general, testing is the process of identifying a faulty device, while diagnosis is the procedure of locating the source of the malfunction. As shown in Fig. 2.1, during early production stages of a design, extensive diagnosis procedures are run on the samples of the device in order to locate the most frequent faults in the circuit and improve the design or the production line in order to achieve an acceptable yield. When the device is approved for mass production, each device undergoes two stages of electrical testing. The first one is called *wafer probe* and is performed prior to packaging (Fig. 2.2). At this stage thin probes are used to apply and monitor signals at various nodes of the circuit. Devices declared faulty at this stage are discarded in order to save the high cost associated with packaging a faulty device. Furthermore, there are a number of non-electrical test and quality control procedures that can be used at this stage such as optical, infrared, scanning microscopy, and thermal imaging analysis [42].

Figure 2.2: Integrated circuit test stages.

Since packaging can introduce some faults [40, Chapter 16], and also because of the difficulty in applying high-performance tests on the wafer, a second test, called *final test*, is run on the device. Since there is no direct access to the internal nodes of the device during the final test, the test must determine the status of the chip using only package pins.

In each electrical testing step (wafer probe and final test), different approaches to test development can be chosen. These are generally divided into two groups: functional and structural. These two approaches are described in the next section.

## 2.1.3 Functional versus structural testing

Functional testing is defined as testing the conformance of the functionality of a circuit to its specifications. Historically, this type of testing has been the method most commonly used, but as the functionality of chips increased, such testing became costly and in many cases impossible. For example, for a combinational logic circuit with 64 inputs with a testing

speed of  $10^8$  patterns per second, it can take 5849 years to test the complete functionality of the chip! In other circuits such as complex analog or mixed-signal circuits, the functional testing would require a large amount of time and resources, translating into higher cost per device.

Another approach is to assume that a well-designed and analyzed circuit which has been thoroughly debugged, *i.e.*, all systematic or design errors have been eliminated prior to sending it for fabrication, will meet its specifications except when there is a fault in the circuit due to physical defects. Therefore, after identifying and modeling the possible faults in the circuit, the test procedure tries to determine their existence or absence. Should a fault be detected, the device is declared faulty and is discarded. This approach, called structural testing, is expected to achieve a more efficient outcome. But is this expectation reasonable? A supportive argument is that different functional specifications of a system are correlated, *i.e.*, if a defect exists in the circuit, it will most likely affect several circuit specifications. This notion implies that functional testing might be overkill, and detecting faults in the system would require less effort. This can be compared to data compression in which the key to compression is to transform highly correlated data to a set of uncorrelated data which carries the same information.

The next section provides the definition of defect and fault which are used to generate tests and also measure the quality of a test.

#### **2.1.4 Defects and faults**

A defect usually refers to physical failures in a circuit, while a fault is the dysfunctional electrical effect of the defect on the operation of the circuit. In a defect-oriented test method-

Figure 2.3: Examples of faults due to local defects

ology, to devise or evaluate a test strategy for a circuit, fault models based on the possible defects are first chosen, and then a test methodology is selected to detect the modeled faults. The faulty circuit is simulated to ascertain whether the selected test can detect the fault. The percentage of faults detected by a test is one measure of the test quality.

The effects of different defects are technology-dependent. Much research has focused on identifying and modeling defects in different technologies. For example, a missing oxide could cause a gate-substrate short in a CMOS transistor. Some of the common defects in most technologies include missing or extra oxide, metal, or polysilicon, and inaccuracy in the etching or doping processes. The electrical consequences of these defects include opens, shorts, as well as significant stray elements and large deviations in component values. Examples of shorts and opens due to spot defects are shown in Fig. 2.3. Hnatek [40] reviews possible physical defects and their sources at each stage of the fabrication process in detail. Faults are not always mapped directly to defects. In fact, sometimes faults are defined at higher levels of abstraction because of advantages such as the ease of test generation (*e.g.*, stuck-at fault model [43, Sec. 4.5]) and tight connection to performance parameters (*e.g.*, performance-dependent faults [44]).

### **2.1.5** Test generation

Fault models are often used to generate test strategies. To detect a fault, the fault should be activated by a set of inputs that cause a significant deviation in a circuit output parameter from its nominal value in the presence of the fault. To activate the fault, it should be both controllable, *i.e.*, the fault-free and faulty status of the area affected by the fault are significantly different, and observable, *i.e.*, the outputs reflect the change in the expected behavior of the faulty area. There are two methods used in test pattern generation:

1. Automatic test pattern generation (ATPG) algorithms. Examples are ATPG algorithms for combinational digital circuits [43, Chapter 6][45]

2. Ad hoc methods. This methods are applicable to specific circuits

The ATPG methods cannot be used easily for generating test patterns for some circuits, e.g., analog circuits, because the interaction of the signals at different nodes is too complex. An ad hoc approach used in these cases is to consider an input pattern and simulate the faulty circuit to determine whether the selected pattern can activate the fault. Fault simulation requires simulating the circuit under different faulty conditions and input signals. Simulations in low levels of abstraction (circuit level) for large circuits are computationally prohibitive. This problem is alleviated by modeling the circuit at higher levels of abstraction. Sensitivity analysis [46] has been also proposed as a test generation method. This method is regarded as a fast substitute for fault simulation because it can help to identify appropriate test stimulus in the possible space of stimulus. Functional testing is also an ad hoc method as it is circuit specific.

Once the test input stimulus has been identified, the test is exercised on each chip by applying the stimulus to the circuit and observing the outputs with a tester. However, in some cases, applying a test to a circuit with an external tester does not suffice or is not possible; in such cases, other methods are used such as design for testability (DFT), builtin-self-test (BIST), and Embedded Test, which are explained next.

# 2.1.6 Design for testability (DFT), built-in-self-test (BIST), and embedded test

In many high-density devices it may be extremely difficult to generate the test pattern for a fault using only primary inputs and observing outputs. In such cases, additional circuitry or techniques can increase the testability of the circuit significantly. Many manufacturers, realizing the importance of testing and the cost involved, include these test circuits on their devices as a means of decreasing test expenses, and, as a result, cost per device.

There are two main categories of DFT methods: general purpose, and ad hoc methods. DFT can mean adding some additional circuitry or modifying the CUT to increase the accessibility of internal nodes of a device, or can be as complete as a built-in-self-test (BIST) scheme. Perhaps, the best example of a standard DFT method is scan chain in sequential digital circuits [43, Sec. 9.4]. In a BIST scheme, the device under test (DUT) is switched to test mode, in which after a specified time required for completion of the test operation in the chip, a flag indicates whether the DUT is faulty or not. BIST for digital technology has been well investigated and is widely used in cases such as memory testing. Some of the advantages of BIST are as follows:

- 1. It eliminates the need for expensive test equipment. As technology improves and circuits with higher speeds and increased functionality are designed, the test equipment has to be upgraded correspondingly, adding to the testing cost

- 2. A large number of chips can be tested simultaneously, resulting in cost reduction

- 3. Tests can be performed on-site repeatedly. Therefore, if the customer needs, he/she can run a field test on the chip under his/her required conditions

- 4. It provides automatic and fast diagnosis which reduces time-to-market considerably [47]

BIST can be viewed as moving the tester into the chip. Inclusion of a full BIST in present day mixed chips (containing analog macros, memory, MEMS and digital circuit) may not be practical due to the area overhead. An alternative approach is to move part of the tester to the chip and leave the rest to external equipment. Such an approach is called Embedded Test. Usually embedded test circuits are designed to perform very high speed tests which are difficult to perform because of the gap between external and internal bandwidth [2]. As the chip complexity and performance increases and access to internal circuits and embedded blocks is reduced, embedded test becomes more and more necessary.

#### 2.1.7 Digital circuit testing

Digital circuit testing is a relatively mature field, and today, ATPG tools are able to generate efficient test patterns for digital circuits. The key to the success of these tools is the existence of efficient fault models, fault simulators for digital circuits and ATPG algorithms.

In a combinational digital circuit, any logic node can have one of two logical values. The status of a logic node depends on the inputs to the circuit. It can be assumed there is a fault in the circuit if a logic node does not change according to the design, or changes too late or too quickly. Consequently, stuck-at and delay faults models have been proposed for digital circuits [43, Chapter 4].

In a stuck-at fault model, it is assumed that a faulty logic node is stuck at one of the logic values (stuck-at-1 and stuck-at-0) and does not change when it is supposed to. By applying proper patterns to the inputs, a stuck-at-v (v = 0, 1) fault can be activated to  $\overline{v}$  (controllability) and observed as a discrepancy between obtained and expected outputs (observability). To detect a delay fault, at least two patterns are needed.

Sequential circuits contain memory elements. Therefore, the outputs depend not only on the circuit inputs, but also on the current state of the system, which is a function of previous inputs and states. Forcing the circuit to a known state and then applying a specific input is a challenging problem. Two alternate methods which are sometimes used to test sequential circuits are Scan Path and CrossCheck [48]. The idea of the scan path method is to divide the circuit into two parts in test mode; a combinational block and a serial shift register containing all the flip-flops in the circuit. Test patterns for the combinational part can be generated using ATPG. Entering a sequence of 1's and 0's from one end of the test shift register and reading it from the other end can determine whether any of the flip-flops in the chain are faulty. In the CrossCheck method some circuitry is added to each logic block of the device so that those blocks are accessible through external pins. Therefore, each logic block including flip flops can be accessed, initialized, and probed directly.

Test strategies based on these models have proven sufficient for most applications, although there are defects which the voltage-based test strategies do not cover. Additional test such as IDDQ testing is needed [49, 50] for these defects.

#### **IDDQ** testing

Using the quiescent supply current  $(I_{DDQ})$  as a testing parameter for CMOS circuits has become increasingly popular, mostly because it is simple and effective [3] [4]. Research shows that for some faults, the DUT draws significantly more (or less) current from its power supply than the nominal value. Therefore, many faults can be detected by monitoring  $I_{DD}$  for specific inputs. IDDQ testing is an example of massive observability because for each input pattern, a large number of faults can be detected by monitoring  $I_{DDQ}$ . In fact, some researchers claim that there are some types of defects that only IDDQ testing detects because they do not alter the functionality of the DUT, but the chip is still faulty because it draws an excessive amount of current [49]. This may lead to reliability problems.

In order to detect a defect by IDDQ testing, it should be activated by an input pattern. Currently, ATPG tools are able to generate IDDQ testing patterns for digital circuits. Although there is a conjecture that these techniques could also be used to test analog circuits, not much research has been done in this area.

25

# 2.2 Analog and Mixed-Signal Testing

The art of testing of analog circuits, unlike its digital counterparts is far from maturity. Most test engineers use ad hoc approaches that do not represent a unified test generation methodology applicable to all analog circuits. Functional testing is still widely used to test these circuits, but as the technology of mixed-signal and analog VLSI circuits progress, the cost of thorough functional testing becomes increasingly prohibitive. Currently, industry is facing serious issues with respect to testing analog and mixed-signal circuits, and it is calling for solutions to this matter, which in some cases has become a bottleneck for manufacturers. This section reviews the major developments in analog and mixed-signal testing to date.

Analog circuits are different from digital circuits in their operation. The input and output signals of an analog circuit are continuous waveforms, and since internal components do not work as switches, their values and characteristics become more important in the operation of the circuit. Digital DFT methods based on partitioning the circuit are often not applicable in the case of analog circuits due to negative impact of DFT circuitry on the performance of the circuit. Also, for many circuits expressing the outputs in an analog circuit in terms of inputs and element values cannot be formulated in a generic form applicable in faulty conditions.

The lack of effective fault models in higher levels of abstraction is one of the most important problems in analog testing. Simulating or analyzing an analog circuit at the circuit level is lengthy and computationally expensive.

Proposed fault models in analog circuits are basically of two types:

1. hard or catastrophic faults, including shorts and opens. Shorts can be capacitive or resistive. These faults can change the topology of the circuit, posing a problem in

using topology methods for analog testing and diagnosis.

2. Soft or parametric faults including some variations in element values for which some functional parameters of the circuit are affected significantly.

Catastrophic faults generally degrade the performance of the system significantly and can be detected by simple tests. For soft faults a decision has to be made regarding the amount of element value variation which is considered faulty. This is a difficult problem, especially when multiple fault models are included.

#### 2.2.1 History

Research on test and diagnosis of analog circuit testing started in the 1970's, almost one decade after digital testing had attracted attention. A number of reasons have been given for this late start [51]. Analog circuits were still largely discrete and relatively small, there-fore, functional testing was possible. Consequently, there was no industrial motive to pursue research in this area. The other reason was the lack of any major breakthrough in the academic research [51].

Since the 1970's, there have been some important results achieved largely in the area of diagnosis of linear circuits. Today's modern analog circuits are mostly non-linear, or become non-linear under faulty conditions. Some researchers have attempted to extend the linear methods to non-linear problems with some degree of success. Some of the efforts in the area of analog fault diagnosis are as follows:

**Post measurement simulations or simulation after test (SAT):** Assuming a certain circuit connectivity, this method tries to solve for the element values using the voltage and currents of accessible nodes and branches, and therefore, determine which component in the circuit is faulty. Berkowitz [52] initiated the subject of solvability of a network based on knowing the currents and voltages in a circuit. Trick et al. [53], and Navid et al. [54], provide some necessary and sufficient conditions for the solvability of a network and introduce algorithms for efficient element value computation. They investigate linear circuits using a single-frequency measurement. Navid et al. suggest their scheme could be used for non-linear circuits by linearizing them around the operating points. Since then, a number of papers on different linear and non-linear methods suggested for fault diagnosis have followed using methods such as multi-frequency measurements [55], element modulation [56], neural networks [57], and artificial intelligence-based techniques [51, Chapter 7]. Piecewise linear (PWL) modeling of non-linear elements is one of the approaches suggested for nonlinear analog fault diagnosis[51].

Estimation methods is also a SAT category. These schemes, using some estimation algorithms such as least square criteria, try to estimate circuit element values by minimizing the error between nominal and measured values. Statistical methods have also been used to select test parameters[58].

**Simulation before test:** In this method, a fault dictionary (FD) is formed through determining the response of the circuit to a set of stimuli in the presence of some specified faults. The faults can be isolated by matching the measured values to the closest set of responses in the dictionary. Schreiber [59] proposes an algorithm based on state space analysis to design an efficient stimulus for the fault dictionary. The accuracy of this method depends on the accuracy of the fault dictionary. Depending on how the FD is formed, some processing of measured values may be necessary; for example, the transient response of the circuit may have to be estimated.

Some research has focused on efficient stimulus design, by which a fault can be located with minimal measurement points and computation. Multi-frequency measurements [55] and element modulation techniques [56] provide examples of such efforts.

## 2.2.2 Testing analog circuits

With the advent of analog VLSI circuits and mixed-signal technology, the field of test development for analog circuits gained significant momentum. In recent years much research has been devoted to exploring and solving the analog testing problems. This section reviews some of these efforts.

#### **Test optimization**

Every second of test on the tester adds to the cost of the device. Testing cost for some dense and complex ICs is estimated to account for up to 30% of the total manufacturing cost. Therefore it is imperative to minimize the testing time by optimizing the test strategy. Milor et al. [41] introduce an algorithm for this optimization. Using the statistics of defects and faults, and the time associated with each test, their algorithm tries to minimize the test time by selecting and ordering the best set of tests. Using this algorithm, only the specifications of the device that provide maximum fault coverage in minimal time are tested.

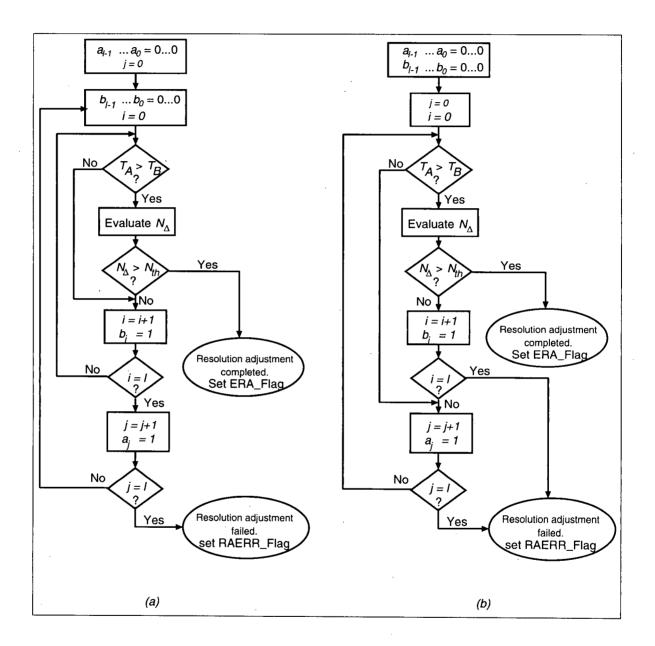

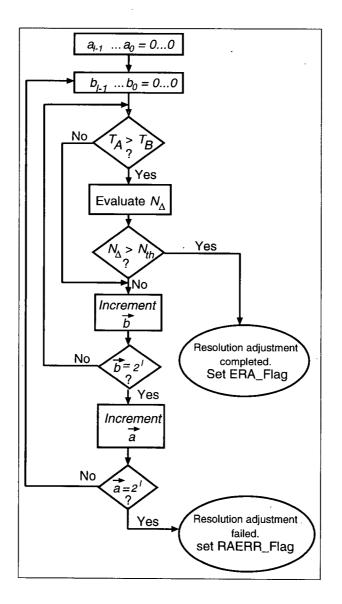

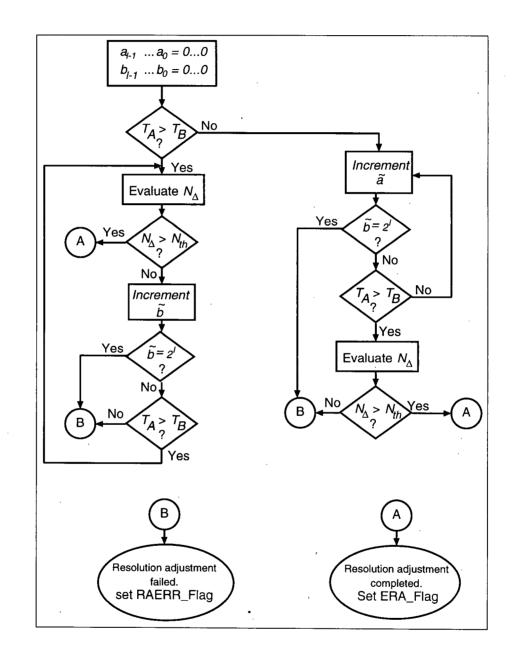

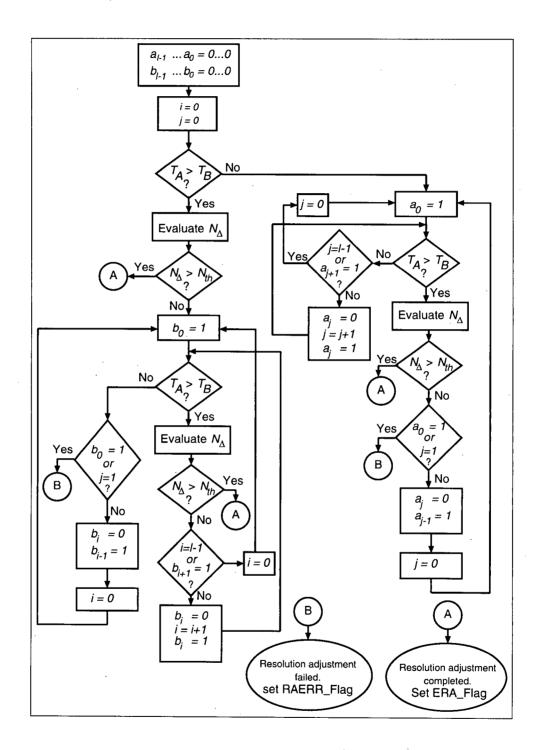

#### **Fault simulation**