# VLSI Support for Scheduling and Buffer Management in High Speed Packet-Switched Networks

by

#### **MEHDI KAZEMI-NIA**

**B.Sc.** in Elec. Eng., Sharif University of Technology, Tehran, 1988 **M.A.Sc.** in Elec. Eng., The University of Windsor, Windsor, 1994

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### **DOCTOR OF PHILOSOPHY**

in

THE FACULTY OF GRADUATE STUDIES

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

January 2000

© Mehdi Kazemi-Nia, 2000

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of <u>ELec & Comp. Fng.</u>

The University of British Columbia Vancouver, Canada

Date Jan 31 / 2000

#### **ABSTRACT**

This thesis presents a number of new approaches for designing fast, scalable queuing structures in VLSI for very high speed packet-switched networks. Such queuing structures are necessary for implementing packet buffers in switches and routers that have multi Gigabit-per-second (Gb/s) ports. The thesis addresses the design of two specific queue architectures: balanced parallel multi-input multi-output (MIMO) buffers, and systolic parallel priority queues (PPQ).

A methodology for the systematic design of order-preserving parallel MIMO buffers is presented. The MIMO buffer employs an arithmetic-free systolic routing network and bank of parallel FIFO buffers to yield a load-balanced realization with increased bandwidth. Using this methodology we derived scalable parallel buffer structures that can be designed to match the rate of ultra high-speed links using current memory technology that uses moderate clock rates. A small prototype of the MIMO buffer attains a rate of 10.6 Gb/s which is more than adequate to support a Sonet OC-192 link. The combined use of pipelined architecture and dynamic CMOS circuits resulted in significant reduction in design complexity and substantial performance gains in speed and area.

The thesis also addresses a generalization of the priority queue concept to a systolic parallel priority queue (PPQ) which can be scaled to meet the requirements of ultra high-speed links using standard CMOS technology. The PPQ has several applications in implementing real-time fair schedulers or buffer management algorithms in packet routers. The PPQ maintains prioritized access to the data it contains at all times, and the access time to the data is fixed and independent of the PPQ size, i.e. O(1)-time access. The proposed systolic PPQ is rate-adaptive in the sense that the PPQ operates correctly even when the queue input rate and output rate are different. This

decoupling of the input and output packet flow rates is a distinguishing feature of the PPQ concept because in practice the output rate of the queue is controlled by the available link bandwidth which may vary (or even become zero) independent of the packet arrival rate.

# TABLE OF CONTENTS

| ABSTRACT .    |         |                | •     | •     | •    | •           | •    | •    | •   | •    | •    | •     | • |   |   |   | • |   | ii       |

|---------------|---------|----------------|-------|-------|------|-------------|------|------|-----|------|------|-------|---|---|---|---|---|---|----------|

| LIST OF TABLE | S.      |                |       | •     |      | •           | •    | •    | •   |      | •    |       |   |   | • |   | • | • | vii      |

| LIST OF FIGUR | ES .    |                |       |       |      | •           |      |      |     |      |      |       |   |   |   |   |   |   | viii     |

| DEDICATION    |         |                |       |       |      | •           | •    | •    |     |      |      |       |   |   | • |   | • |   | xi       |

| ACKNOWLEDG    | EMEN    | TS .           |       |       | •    | •           | •    | •    |     |      | •    |       |   |   |   |   | • | • | xii      |

| CHAPTER 1     | Overv   | iew and        | l Mo  | tivat | tion |             | •    | •    |     |      |      |       |   | • | • | • |   |   | 1        |

|               | 1.1     | Buffer         | · Ma  | nage  | eme  | nt fo       | r Hi | igh  | Spe | ed ] | Lin  | KS    |   | • |   |   |   |   | 4        |

|               | 1.2     | Packet         | t-Scl | nedu  | ling | ;           | •    | •    |     |      |      |       |   |   |   |   |   |   | 5        |

|               | 1.3     | Main           | Cont  | ribu  | tion | s an        | d Tl | nesi | s O | rgaı | niza | tion  | 1 |   |   |   |   |   | 7        |

| CHAPTER 2     | Survey  | y and B        | ackg  | roui  | nd   | •           | •    |      |     |      |      |       |   |   | • |   | • | ٠ | 11       |

|               | 2.1     | Paralle        | el FI | FO :  | Bufi | ers         |      | •    |     |      |      |       |   |   |   |   |   |   | 12       |

|               | 2.2     | Priorit        |       |       |      |             |      |      |     |      |      |       |   |   |   |   |   |   | 20       |

| CHAPTER 3     | Paralle | el FIFO        | Buf   | fers  | for  | Giga        | abit | Pac  | ket | Ne   | two  | rks   |   |   |   |   |   |   | 26       |

|               | 3.1     | Introd         | uctio | n     | . /  |             |      |      |     |      |      |       |   |   |   |   |   |   | 26       |

|               | 3.2     | MIMO           | ) Bu  | ffer  | Des  | ign ]       | Prin | cip  | als |      |      |       |   |   |   |   |   |   | 29       |

|               |         | 3.2.1<br>3.2.2 | Bas   | sic C | Oper | ation<br>Bu | n of | the  | MI  | MC   | ) Bı | ıffeı | • |   |   |   |   |   | 29<br>30 |

|               | 3.3     | The B          |       |       |      |             |      |      |     |      |      |       |   |   |   |   |   |   | 33       |

|               | 3.4     | Dynar          |       |       |      |             |      |      |     |      |      |       |   |   |   |   |   |   | 38       |

|               | 3.5     | Some           |       |       |      |             |      |      |     |      |      |       |   |   |   |   |   |   | 46       |

|               | 3.6     | Summ           |       |       |      |             |      |      |     |      |      |       |   |   |   |   |   |   | 54       |

|               |         |                |       |       |      |             |      |      |     |      |      |       |   |   |   |   |   |   |          |

| CHAPTER 4 | VLSI  | Implementation of the Parallel MIMO Buffer                         |  |

|-----------|-------|--------------------------------------------------------------------|--|

|           | 4.1   | Overview                                                           |  |

|           | 4.2   | VLSI Design Strategy                                               |  |

|           | 4.3   | Circuit Diagram of a Switch Element                                |  |

|           | 4.4   | Design Simulation Results                                          |  |

| ·         | 4.5   | Summary                                                            |  |

| CHAPTER 5 | A Sys | stolic Parallel Priority Queue for High Speed Packet Networks . 69 |  |

|           | 5.1   | Overview                                                           |  |

|           | 5.2   | Scheduling Networks and Priority Queues                            |  |

|           | 5.3   | Systolic Parallel Priority Queue                                   |  |

|           |       | 5.3.1 VLSI Word-Model of a Parallel Sorter                         |  |

|           | 5.4   | Retimed Design                                                     |  |

|           | 5.5   | Summary                                                            |  |

| CHAPTER 6 | Scala | ble PPQs with Output Rate-Control                                  |  |

|           | 6.1   | Introduction                                                       |  |

|           | 6.2   | A PPQ Design with Output Rate-Control 86                           |  |

|           | 6.3   | The PPQ Retimed Design with Output Rate-Control 91                 |  |

|           | 6.4   | Systolic PPQs with an Unequal Number of Inputs and Outputs . 96    |  |

|           | 6.5   | Bit-Serial Realization of the Systolic PPQ 98                      |  |

|           | 6.6   | Structure of Parallel Sorters                                      |  |

|           |       | 6.6.1 Recursive Construction of Parallel Sorter                    |  |

|           | 6.7   | Primitive Sorter Timing                                            |  |

|           | 6.8   | VLSI Design Strategy and Implementation Issues 112                 |  |

|           | 6.9   | Summary                                                            |  |

|           |       |                                                                    |  |

| CHAPIER /    | Concit      | ision and Future Directi | ons    | •   | • | • | • | • | • | • | • | • | • | 116 |

|--------------|-------------|--------------------------|--------|-----|---|---|---|---|---|---|---|---|---|-----|

| BIBLIOGRAPHY |             |                          |        |     |   | • | • |   | • |   |   |   | • | 121 |

| APPENDIX A   | АТМ Т       | Cechnology               |        | •   |   | • |   | • | • | • |   |   | • | 131 |

|              | <b>A.</b> 1 | ATM Networking and       | Switch | ing |   |   |   |   |   |   |   |   |   | 133 |

|              |             | ATM Switch Architect     |        |     |   |   |   |   |   |   |   |   |   |     |

|              | A.3         | ATM Buffer Managem       | ent    | •   |   | • | • |   |   | • | • |   |   | 140 |

|              | i           |                          |        |     |   |   |   |   |   |   |   |   |   |     |

| APPENDIX B   | Asyncl      | ronous System Design     | •      |     |   |   |   |   |   |   |   |   | • | 142 |

## LIST OF TABLES

| Table 4.1: Transistors' sizes in the nMOS chain                           | • | • | • | • | 64  |

|---------------------------------------------------------------------------|---|---|---|---|-----|

| Table 6.1: Comparing two methods of implementation of a $2m$ -cell sorter |   |   |   |   | 109 |

|                                                                           |   |   |   |   |     |

|                                                                           |   | • |   |   |     |

|                                                                           |   |   |   |   |     |

|                                                                           |   |   |   |   |     |

|                                                                           |   |   |   |   |     |

|                                                                           |   |   |   |   |     |

## LIST OF FIGURES

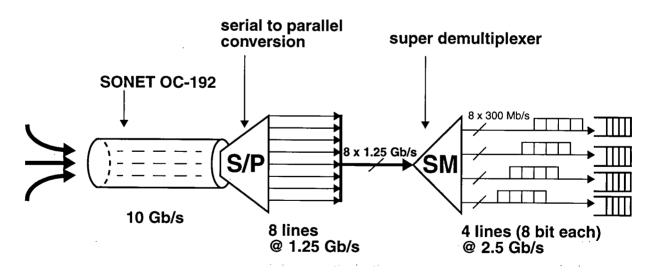

| Fig. 1.1:  | Serial-to-parallel conversion and byte staggering at the opto-electronic interface                                                                                  | 4  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

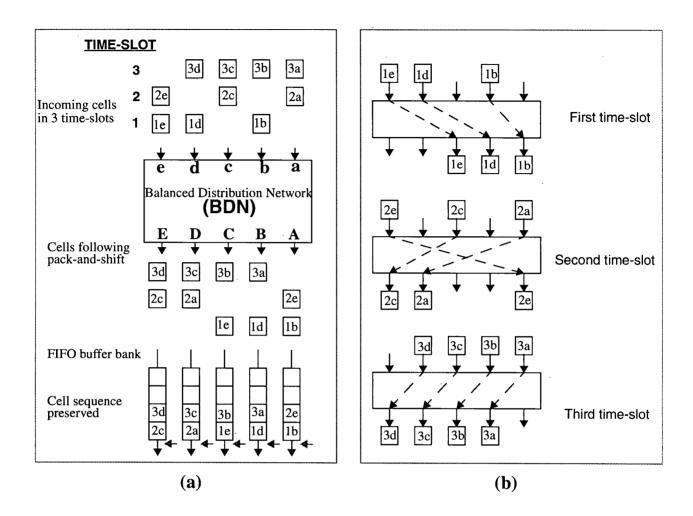

| Fig. 2.1:  | <ul><li>(a) Operation of a shared-buffer that preserves the cell arrival sequence</li><li>(b) Illustration of pack-and-shift approach in three time-slots</li></ul> | 13 |

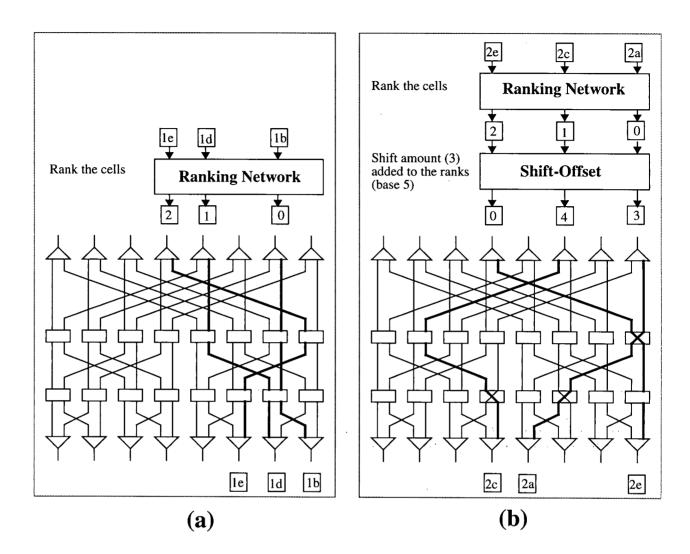

| Fig. 2.2:  | <ul><li>(a) Packing ranked cells on a butterfly network</li></ul>                                                                                                   | 15 |

| Fig. 2.3:  | Structure of shared buffers in the Knockout switch                                                                                                                  | 17 |

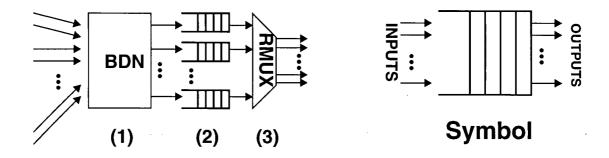

| Fig. 2.4:  | MIMO buffer and its symbol                                                                                                                                          | 19 |

| Fig. 2.5:  | (a) Parallel buffer                                                                                                                                                 | 20 |

| Fig. 2.6:  | Inserting a new arrival into a non-systolic PQ                                                                                                                      | 22 |

| Fig. 2.7:  | Buffer manager structure                                                                                                                                            | 23 |

| Fig. 3.1:  | MIMO buffer in a multi-stage switch and its symbol                                                                                                                  | 28 |

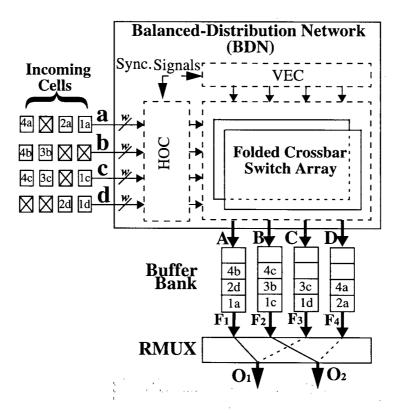

| Fig. 3.2:  | Internal structure of the buffer                                                                                                                                    | 31 |

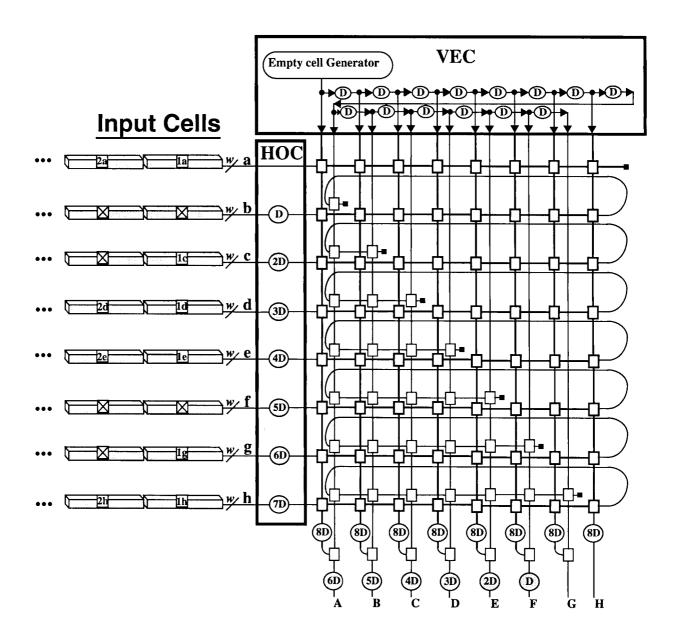

| Fig. 3.3:  | Internal Structure of an 8x8 BDN                                                                                                                                    | 33 |

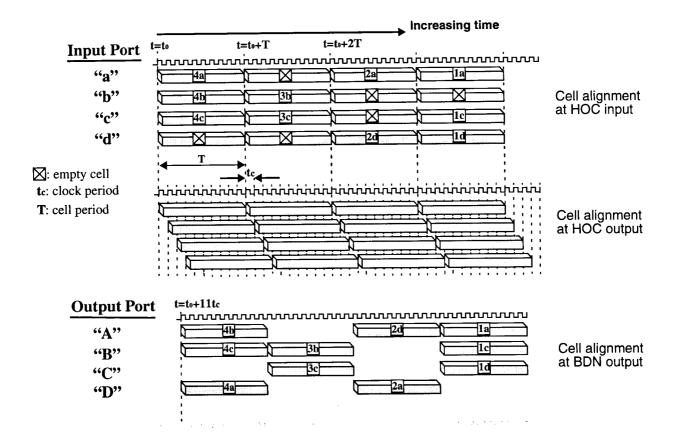

| Fig. 3.4:  | Input/Output port alignment of the BDN                                                                                                                              | 34 |

| Fig. 3.5:  | Two states of the switch element                                                                                                                                    | 36 |

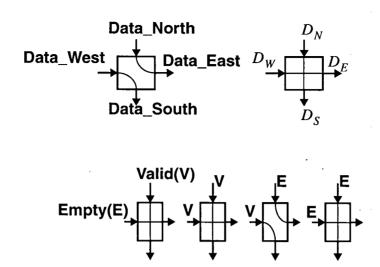

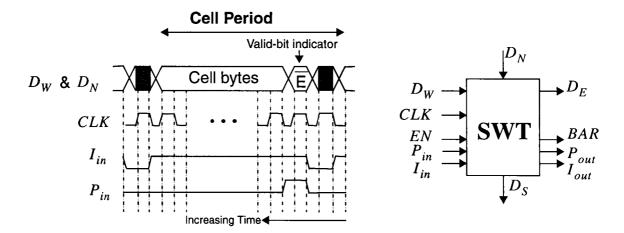

| Fig. 3.6:  | I/O diagram of the SWT and cell format                                                                                                                              | 37 |

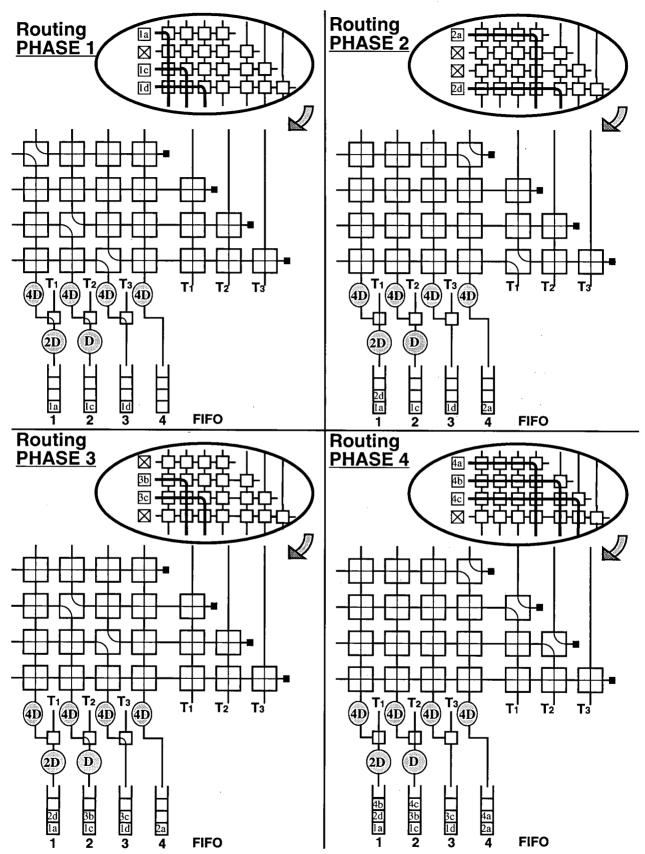

| Fig. 3.7:  | Four routing phases of the buffer                                                                                                                                   | 39 |

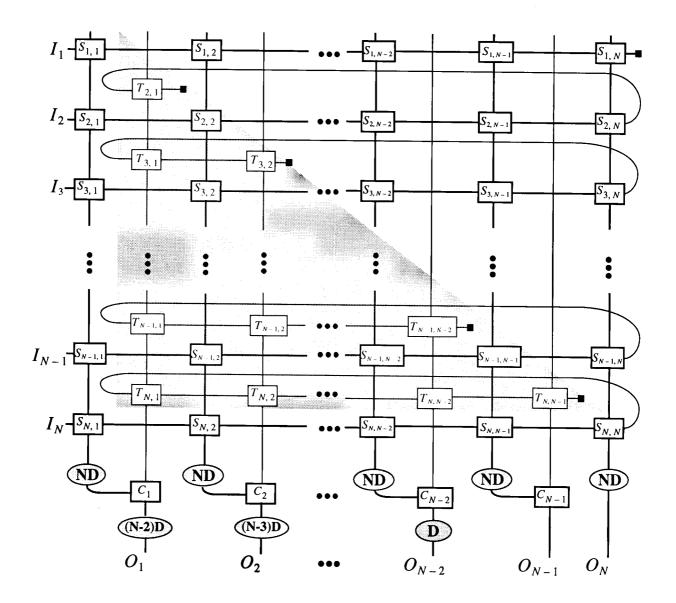

| Fig. 3.8:  | Folded crossbar array of the BDN                                                                                                                                    | 42 |

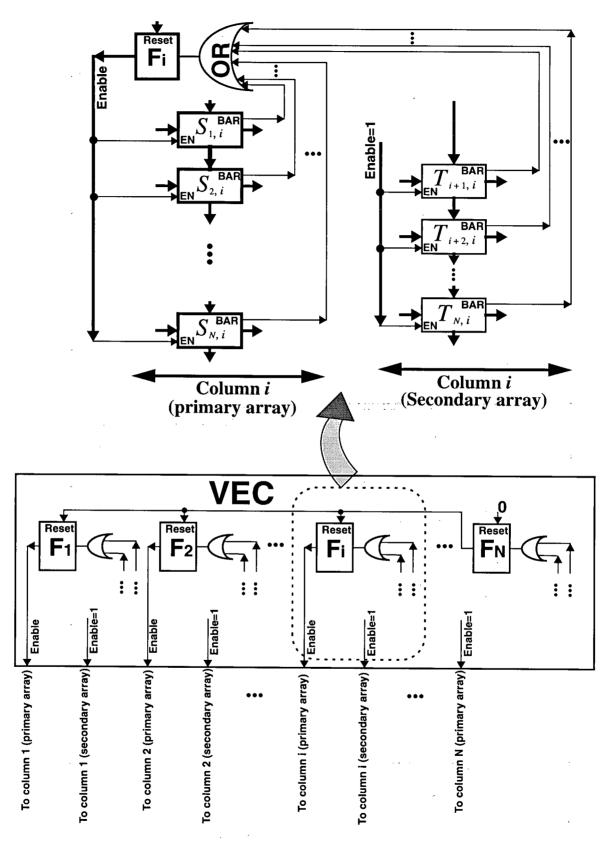

| Fig. 3.9:  | Distributed control in the VEC                                                                                                                                      | 43 |

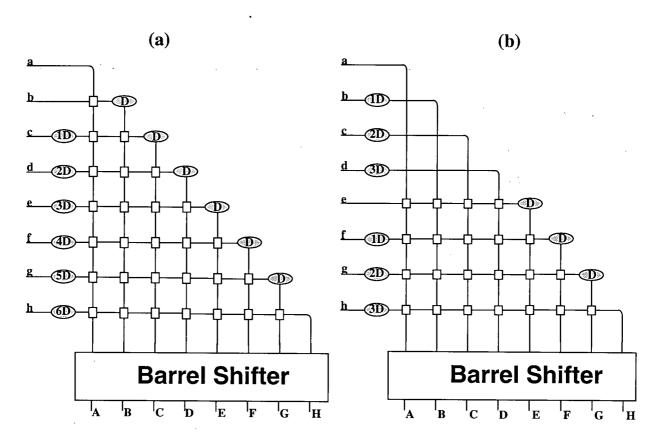

| Fig. 3.10: | Two configurations for packing the incoming cells                                                                                                                   | 45 |

| Fig. 3.11: | Self routing property of banyan networks                                                                                                                            | 46 |

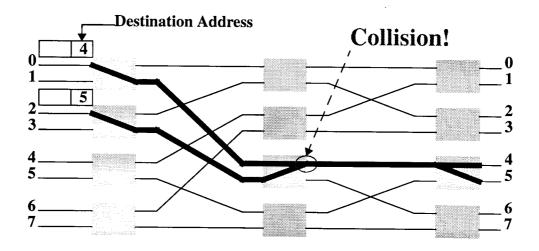

| Fig. 3.12: | Internal blocking in banyan networks                                                | 49 |

|------------|-------------------------------------------------------------------------------------|----|

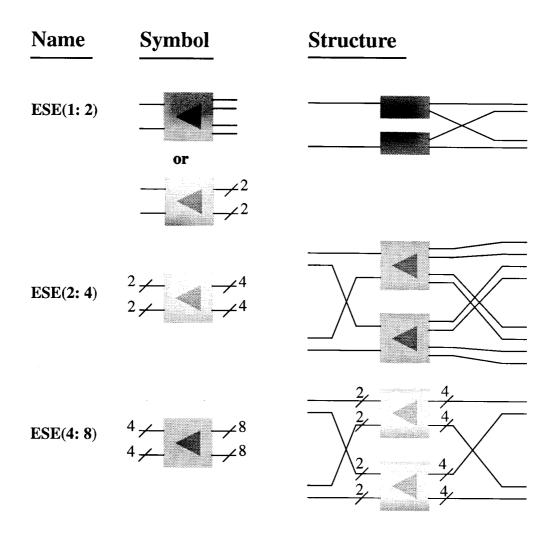

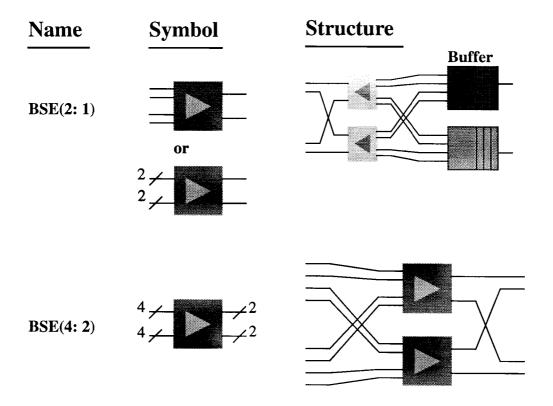

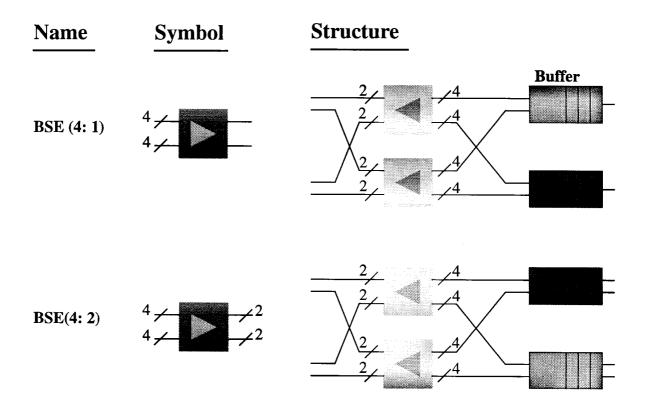

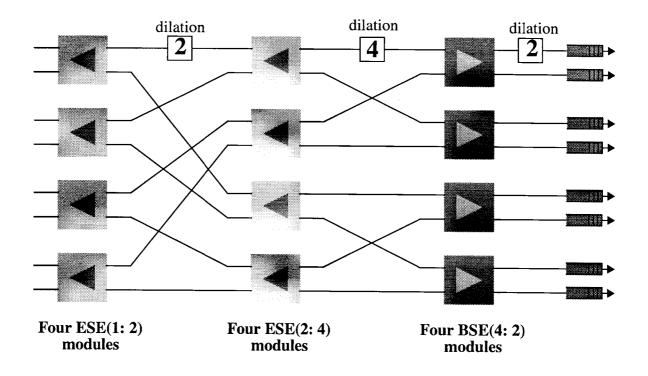

| Fig. 3.13: | Expansion modules (ESEs)                                                            | 51 |

| Fig. 3.14: | Buffered-concentration modules (BSEs)                                               | 52 |

| Fig. 3.15: | Alternative buffered core modules                                                   | 53 |

| Fig. 3.16: | Dilated banyan network with internal buffers                                        | 54 |

| Fig. 4.1:  | Part of the VHDL code                                                               | 57 |

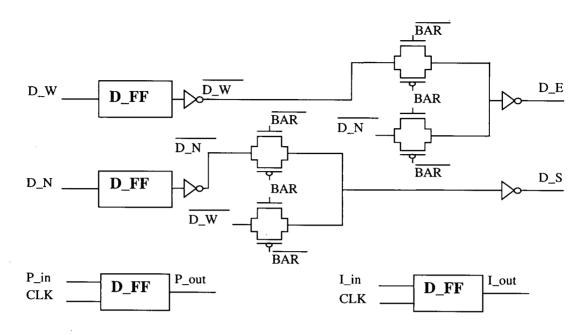

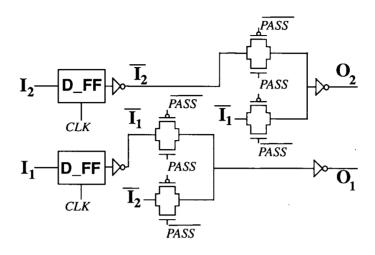

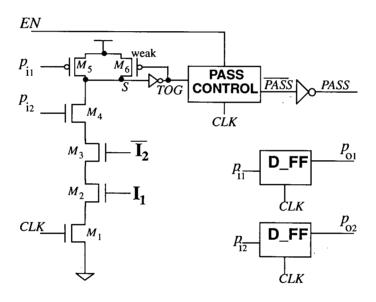

| Fig. 4.2:  | Circuit diagram of the crossbar control of SWT                                      | 58 |

| Fig. 4.3:  | Signal and data-path of a SWT                                                       | 60 |

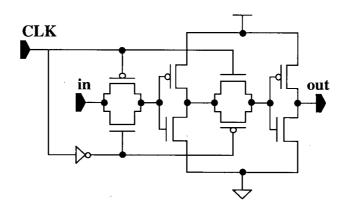

| Fig. 4.4:  | Dynamic D-type flip-flop circuit                                                    | 61 |

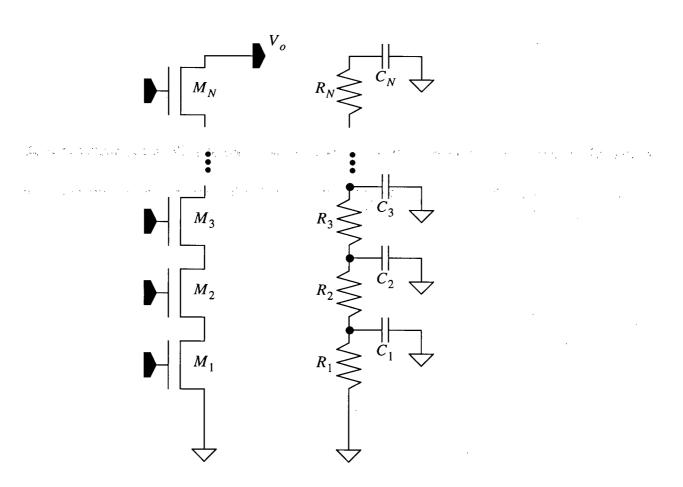

| Fig. 4.5:  | nMOS transistors chain and the RC model                                             | 62 |

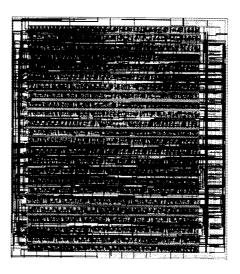

| Fig. 4.6:  | Layout diagram of a 4x4 BDN                                                         | 65 |

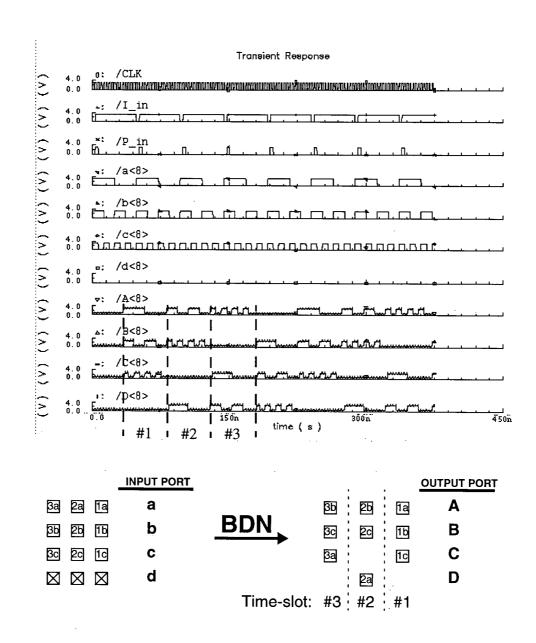

| Fig. 4.7:  | Simulation result of the 4 x 4 BDN during three time-slots                          | 66 |

| Fig. 5.1:  | A typical scheduling network                                                        | 71 |

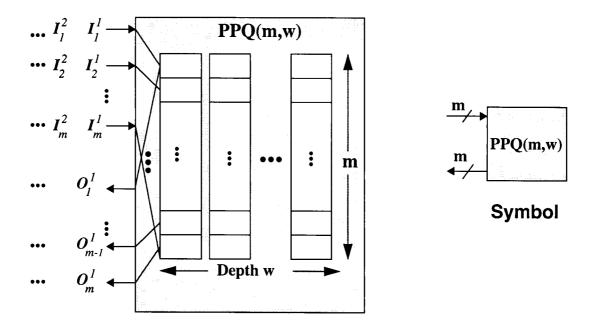

| Fig. 5.2:  | A PPQ contains $m \times w$ cells                                                   | 73 |

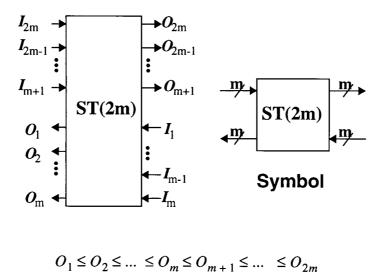

| Fig. 5.3:  | The I/O configuration of a $2m$ -cell sorter                                        | 75 |

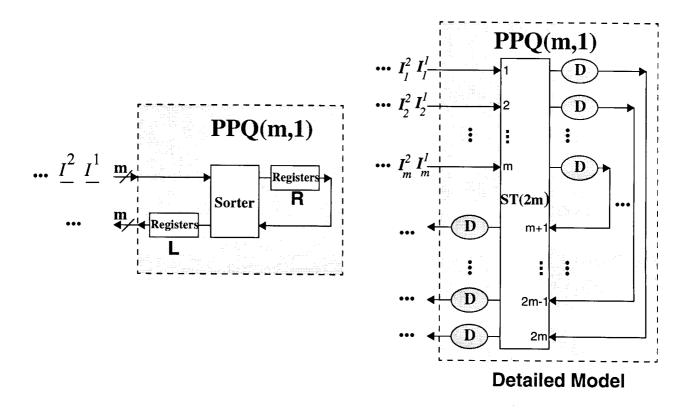

| Fig. 5.4:  | A priority queue with $m$ inputs, $m$ outputs, and depth 1                          | 76 |

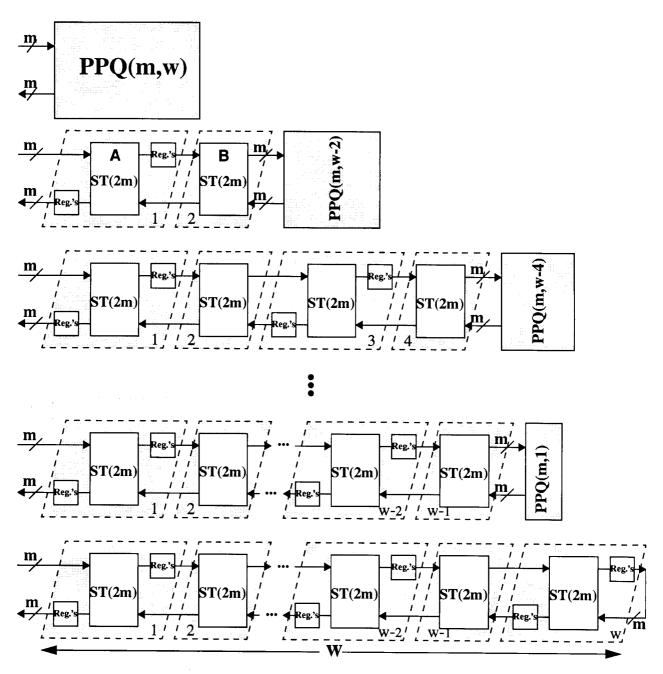

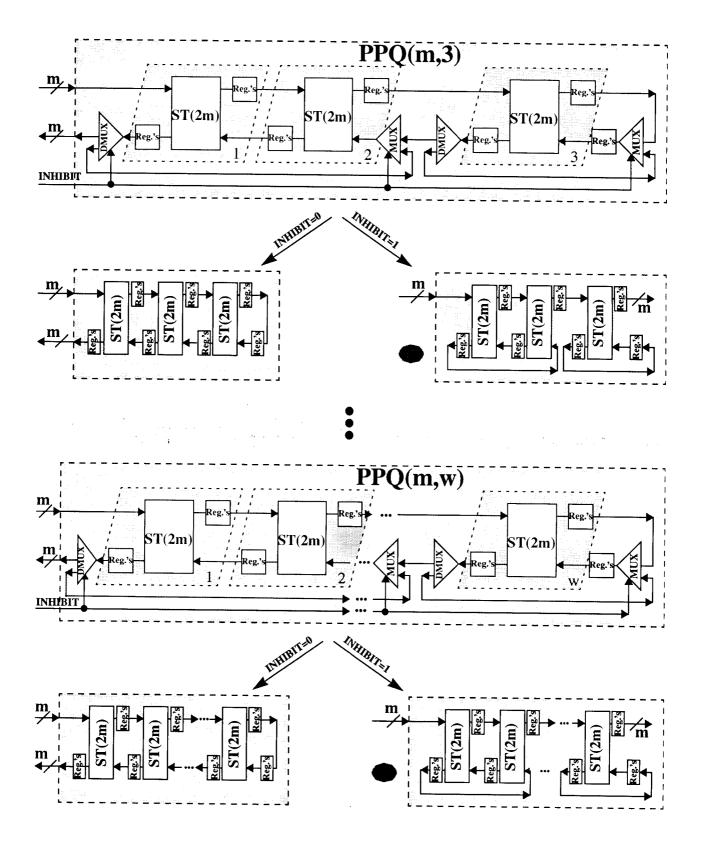

| Fig. 5.5:  | Recursive construction of the parallel priority queue $PPQ(m, w)$                   | 77 |

| Fig. 5.6:  | Retimed design of $PPQ(m, 1)$                                                       | 80 |

|            | Recursive construction of the systolic parallel priority queue $PPQ(m, w)$ .        | 82 |

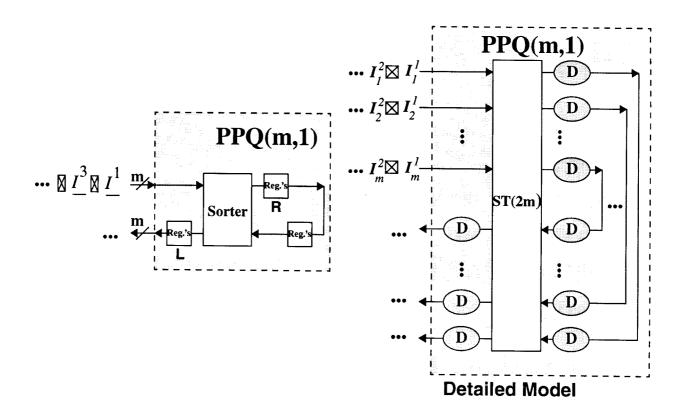

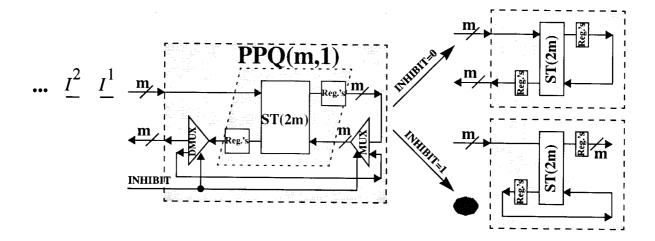

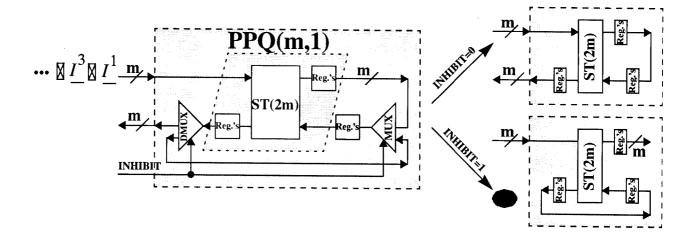

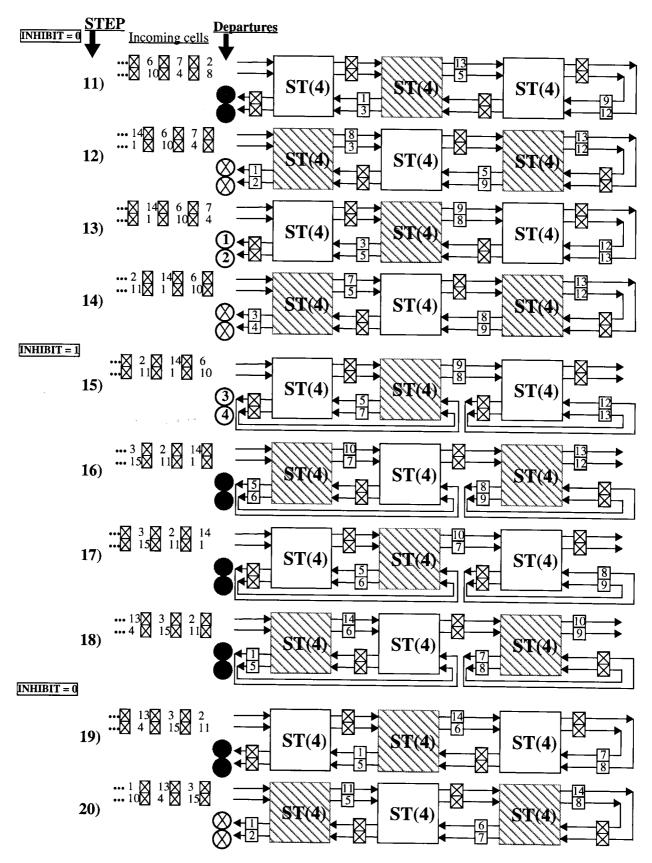

| Fig. 6.1:  | PPQ(m, 1) with inhibit feature                                                      | 86 |

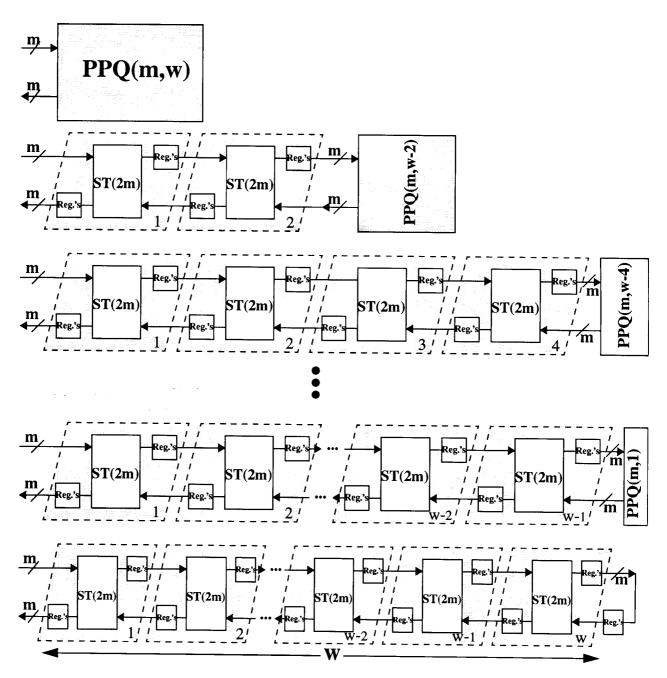

| Fig. 6.2:  | Building recursively priority queues with different depth sizes and inhibit feature | 88 |

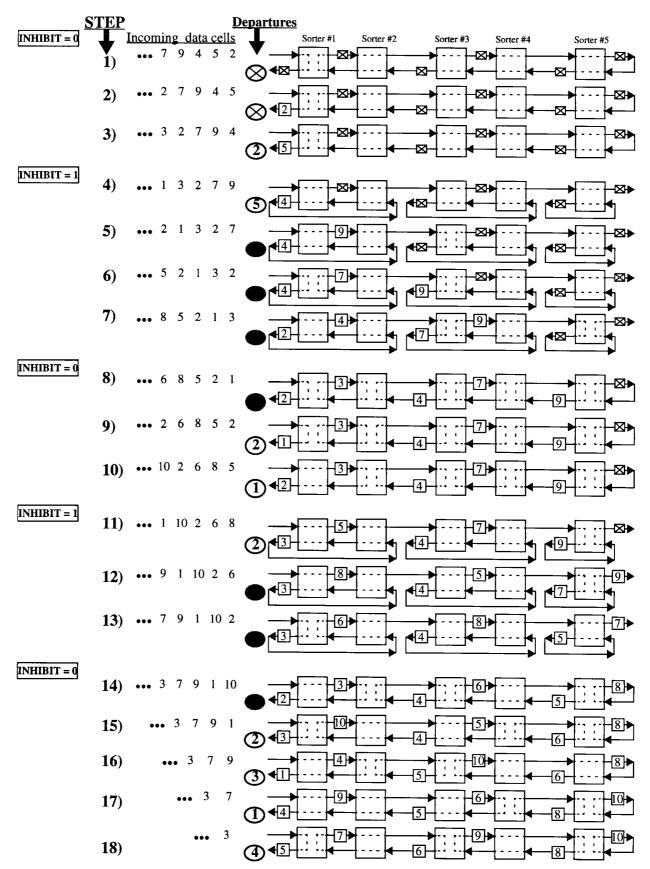

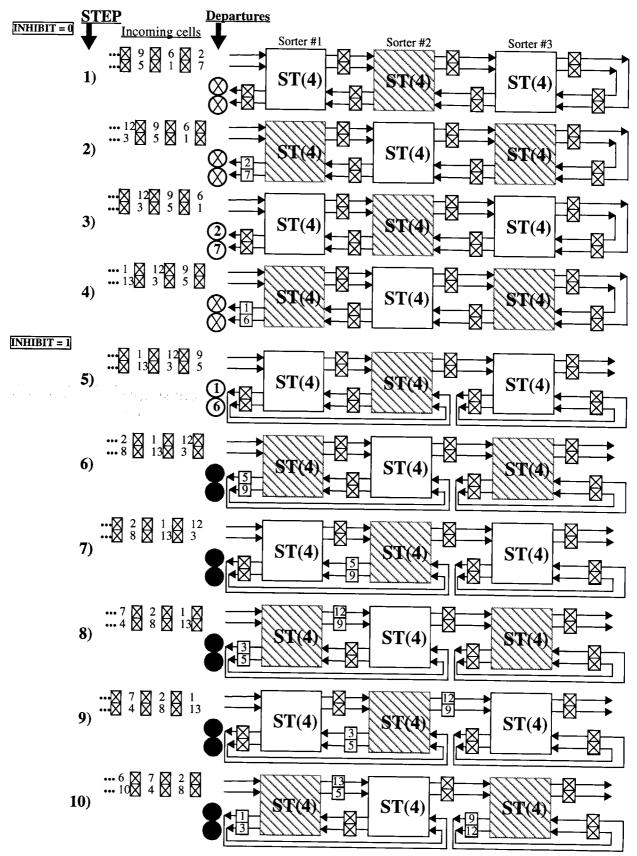

| Fig. 6.3:  | Several steps of the operation of a $PPQ(1, 5)$                      | • | • | • | • | 89  |

|------------|----------------------------------------------------------------------|---|---|---|---|-----|

| Fig. 6.4:  | Retimed design of $PPQ(m, 1)$ with inhibit feature                   | • |   |   |   | 91  |

| Fig. 6.5:  | PPQs with different depth sizes and inhibit feature                  |   |   | • |   | 92  |

| Fig. 6.6:  | Several steps of the operation of a systolic $PPQ(2,3)$              |   | • |   |   | 94  |

| Fig. 6.7:  | PPQs with an unequal number of inputs and outputs                    | • | ٠ |   |   | 97  |

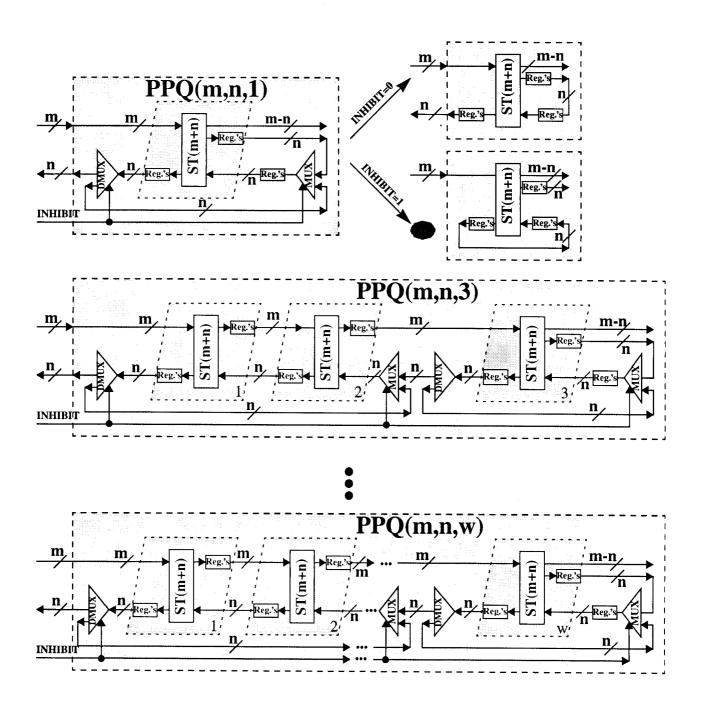

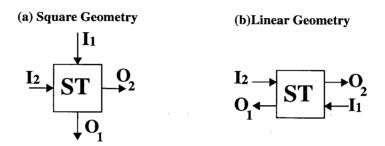

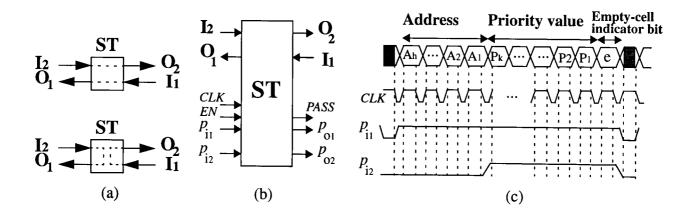

| Fig. 6.8:  | Two pictorial representations of a primitive sorter                  | • | • |   |   | 99  |

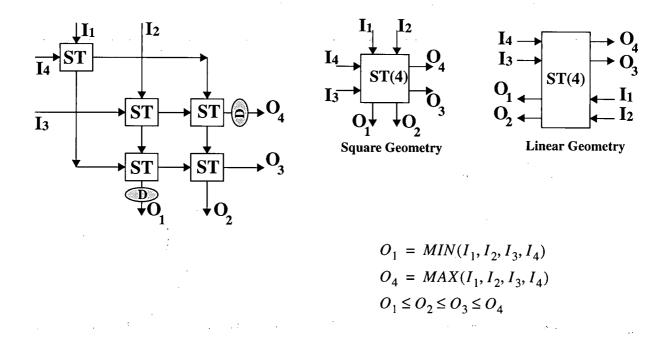

| Fig. 6.9:  | Configuration of $ST(4)$ and its two pictorial representations .     |   | • |   | • | 101 |

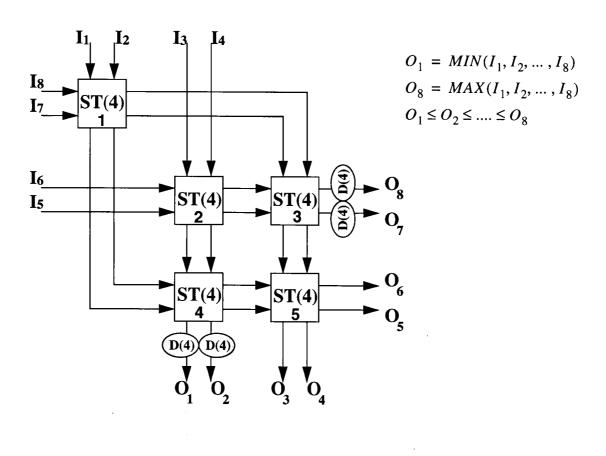

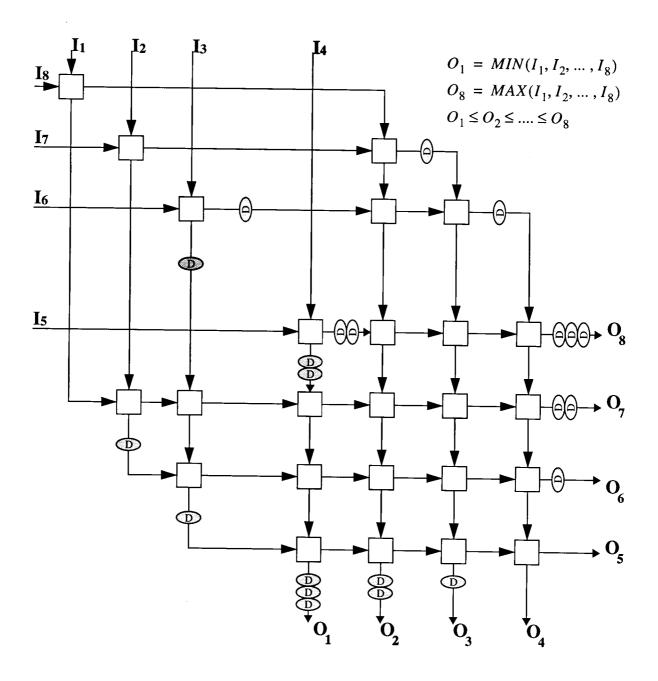

| Fig. 6.10: | Realization of an 8-cell sorter                                      |   | • | • |   | 103 |

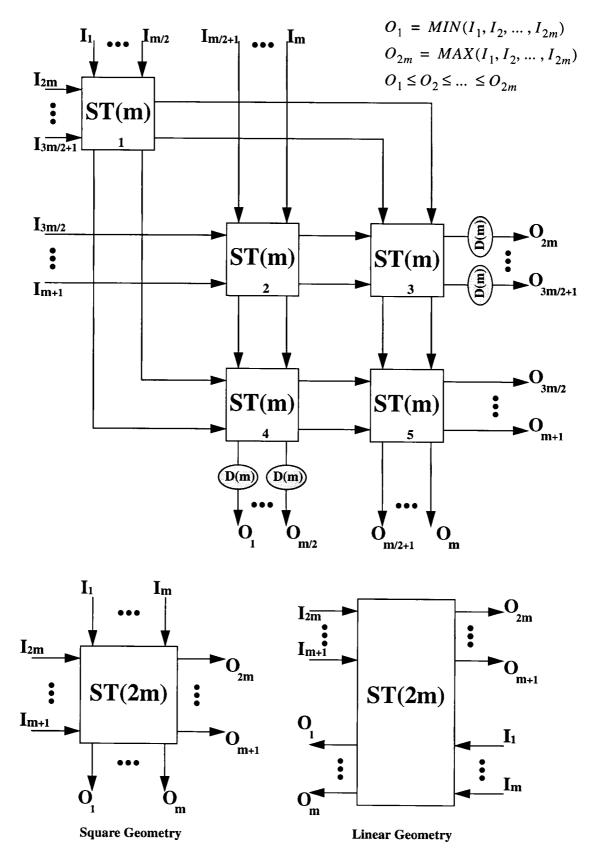

| Fig. 6.11: | Recursive construction of a $2m$ -cell sorter and its two geometries |   |   | • |   | 104 |

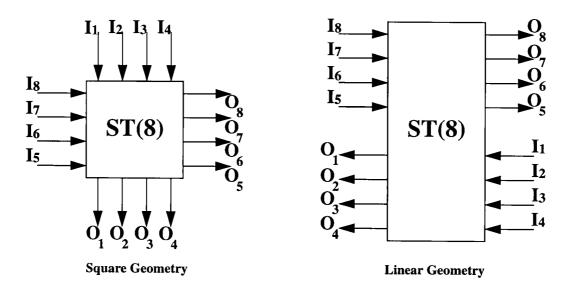

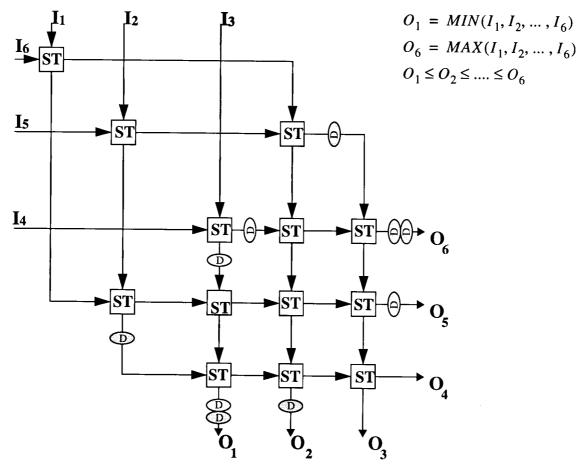

| Fig. 6.12: | Configuration of a 6-cell sorter using primitive elements            |   | • | • |   | 106 |

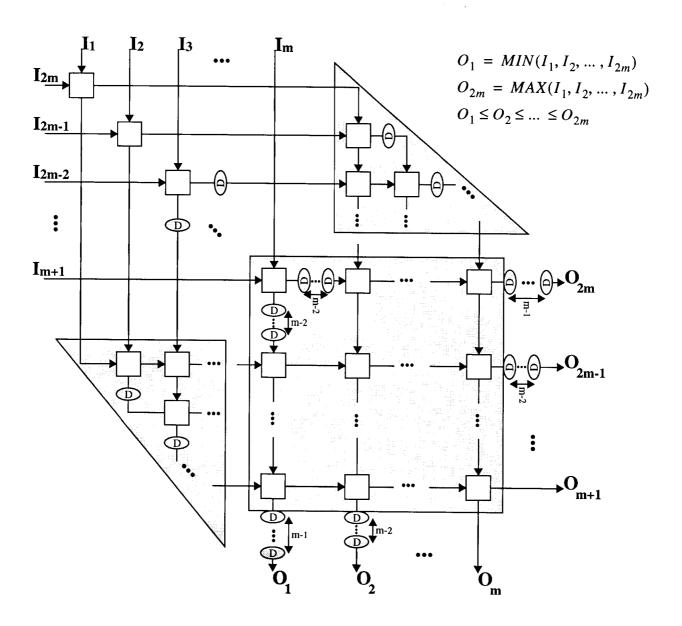

| Fig. 6.13: | Construction of an 8-cell sorter $ST(8)$ using primitive elements    |   |   |   |   | 107 |

| Fig. 6.14: | Realization of a $2m$ -cell sorter $ST(2m)$ using primitive elements |   |   | • | • | 108 |

| Fig. 6.15: | Primitive sorter                                                     |   |   |   |   | 110 |

| Fig. 6.16: | Circuit diagram of the ST                                            |   |   |   |   | 113 |

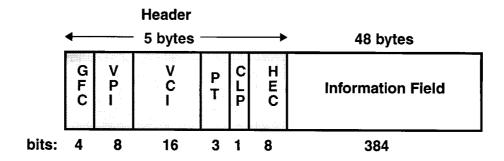

| Fig A 1.   | ATM cell format and header components                                |   |   |   |   | 122 |

|            | -                                                                    |   |   |   |   |     |

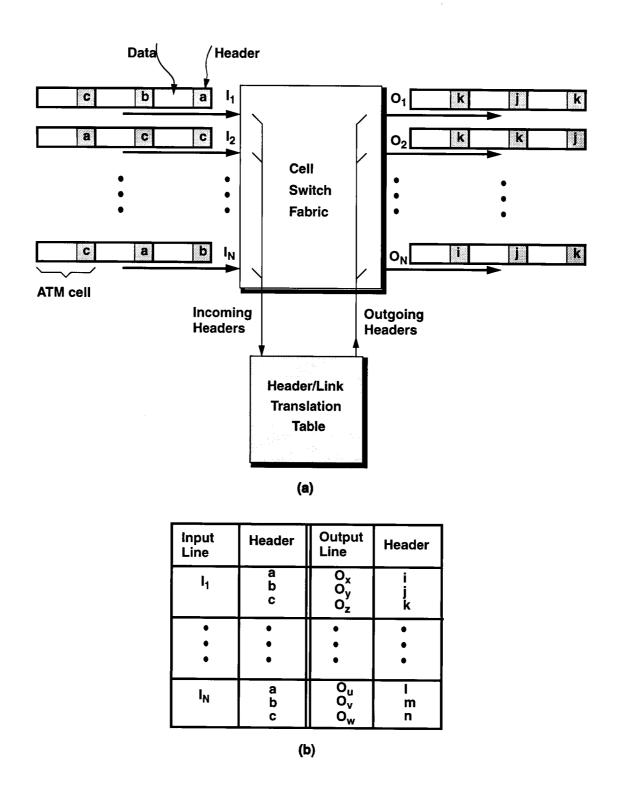

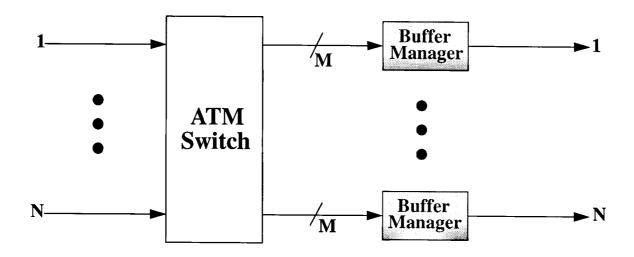

|            | An ATM switch                                                        | • | • | • | • |     |

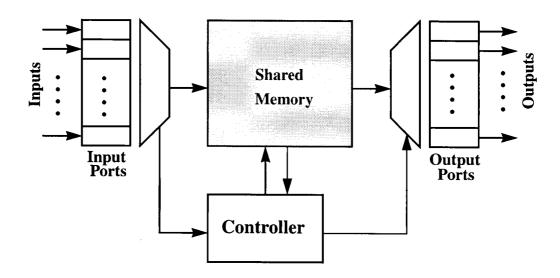

|            | Shared buffer switch architecture                                    | • | • | • | • | 137 |

| Fig. A.4:  | The buffer manager at each output port of an ATM switch              | • | • | • | ٠ | 141 |

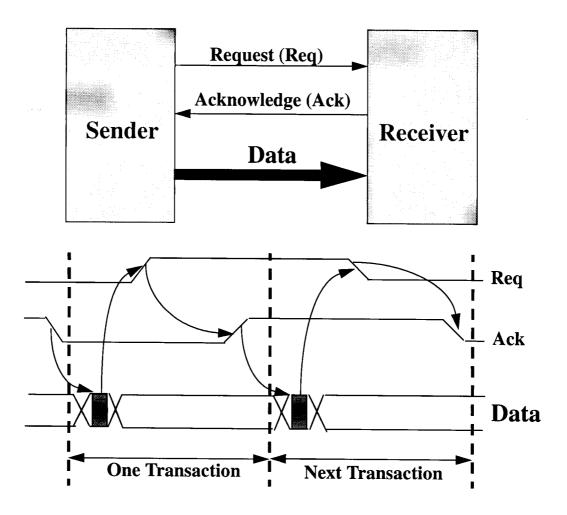

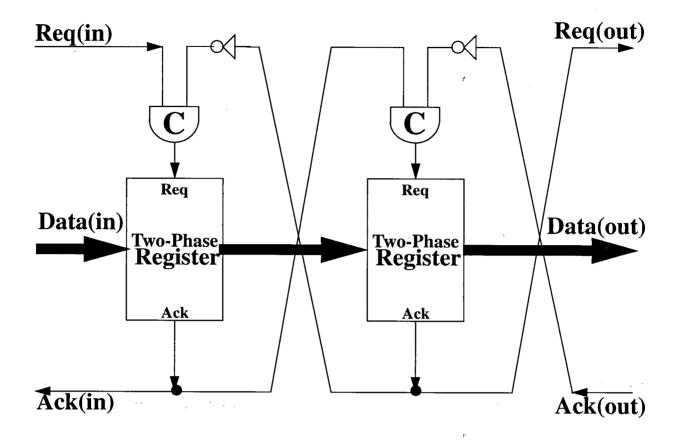

| Fig. B.1:  | Two-phase signalling scheme                                          |   | • |   |   | 145 |

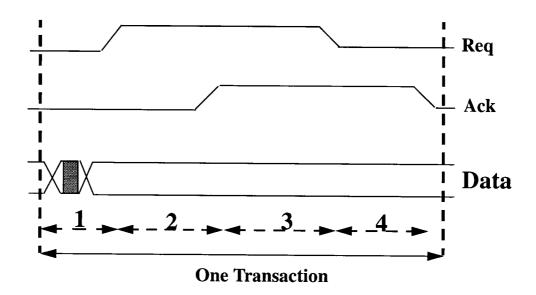

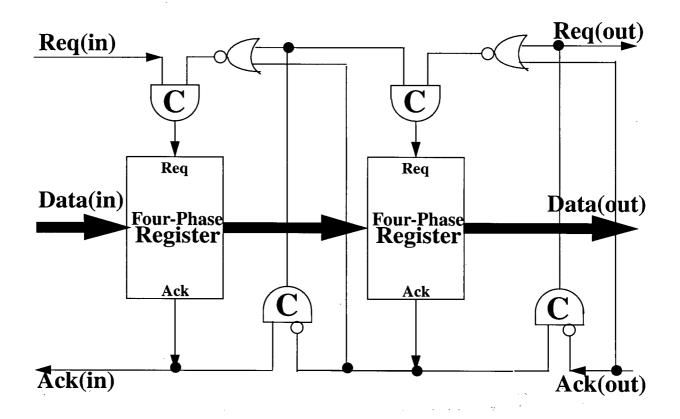

| Fig. B.2:  | Four-phase signalling scheme                                         |   |   |   |   | 146 |

| Fig. B.3:  | Two-phase FIFO structure                                             |   |   |   |   | 150 |

| Fig. B.4:  | Four-phase FIFO structure                                            |   |   |   |   | 151 |

To the memory of my father

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my supervisor, Dr. Hussein Alnuweiri, for his friendly guidance and support throughout the progress of this thesis. My deepest appreciations go to Drs. Mike Jackson, and Steve Wilton for their valuable and enlightening discussions. I am also grateful to Drs. William Dunford and Alan Wagner for their helpful suggestions. My special thanks to Dr. Fayez El-Guibaly from University of Victoria for his helpful comments to bring this thesis to fruition.

Finally, I am indebted to my mother who has always encouraged me in following my dreams.

Last but not least, my foremost appreciations go to my wife Elham, without whose love, inspiration, and support this path would likely not have been traversed.

# **CHAPTER 1**

Overview & Motivation

The advances in data communications over optical-fibre serial links has paved the way for the development of high-speed packet switching technologies such as ATM (Asynchronous Transfer Mode) and wire-speed IP (Internet Protocol) packet forwarding. Until a few years ago, the performance of the Internet was limited by the speed of the long-haul links, not by capacity of switches and routers. However, the advancements in switch/router technologies have not kept pace with advances in optics, and with the rapid provisioning of higher speed links (such as the 10 Gigabit per second Sonet OC-192), and the introduction of wavelength division multiplexing (WDM), the bottleneck has moved from the links to the switches and routers. Carriers are

currently deploying very high-density OC-192 dense wavelength division multiplexing (DWDM) systems, and leading DWDM vendors have already announced availability of 40 Gigabit per second (Gb/s) OC-768 systems in the near future<sup>1</sup>.

The demand for bandwidth is soaring and today's networks lack the ability to scale network backbone capacities at aggressive rates to accommodate this increased demand for bandwidth. The explosive growth of Internet users, the increased user demand for bandwidth, and the declining cost of technology have all resulted in the emergence of new classes high-speed distributed IP-router architectures with packet-forwarding rates on the order of Terabits per second (Tb/s)<sup>2</sup>.

This recent and unprecedented growth in bandwidth availability, poses a heavy load on the underlying infrastructure, and there is an immediate need for backbone switch/routers that can scale to support these demands. There are a broad range of architectures and techniques being proposed, and several enhanced router architectures<sup>3</sup> have been introduced to meet the demand of the evergrowing bandwidth requirements of the Internet. Vendors have been able to introduce routers that offer a range of Tb/s of non-blocking switching capacity<sup>4</sup>. Similarly, current commercial ATM switches support link speeds reaching up to 10 Gb/s (over Sonet OC-192), and experimental switches are supporting link speeds of 40 Gb/s<sup>5</sup> [1], [2]. Implementations of these networks require the development of new hardware architectures using advanced VLSI technology that are capable of handling large amounts of traffic with throughputs on the order of Gb/s. Moreover, supporting quality-of-service (QoS) in packet networks requires deploying more sophisticated

<sup>1.</sup> See http://www.eetimes.com/news/98/1026news/40-gbit.html

<sup>2.</sup> See http://www.pluris.com/html/product.html.

<sup>3.</sup> Such routers are known as switched routers or routing switches because they normally employ a switching fabric and distributed architecture for forwarding packets across the router ports. These routers are also called layer-3 switches, wire-speed routers, or hardware-based routers.

<sup>4.</sup> See http://www.pluris.com/html/product.html and http://www.alliancedatacom.com/lucent-nx64000.htm.

<sup>5.</sup> See http://www.cisco.com/univercd/cc/td/doc/product/atm/index.htm.

queuing policies in the switching or routing nodes. The first-come first-serve (or FIFO) discipline is no longer adequate in networks that provide service differentiation. Providing QoS guarantees in both cell- and packet-based networks requires the use of a scheduling algorithm in the switches and network interfaces. These algorithms need to be implemented in hardware in a high-speed network. At minimum, some level of priority scheduling must be supported. In more advanced applications, buffers with rate adaptation features must be deployed between the switch and external links.

The main challenge is maintaining the correct operation at very high speeds. As the combined forces of increasing traffic levels and escalating performance demands continue to push network infrastructures to their limits, new buffering structures are required which can be scaled to match the ever-increasing link speeds. Such queuing structures are necessary for implementing packet buffers in switches and routers that have multi Gb/s ports.

Satisfying the QoS requirements for high-speed modern packet switching networks such as ATM requires a combination of high-level architectural synthesis methods (system design level), the use of state-of-the-art circuit design techniques, and the efficient realization of distributed control policies. However, advances in device technology cannot alone meet these demands or it would be cost prohibitive. Even though, the use of deep submicron CMOS technology as the industry standard for IC manufacturing will eventually enable designers to integrate a variety of components into a system-on-a-single chip solutions, limitations of deep submicron technologies can still limit the clock speed.

Therefore, there is an immediate need to achieve speedups using other techniques such as parallel processing. Employing parallel processing approaches to solve the scalability problem, this thesis

develops effective VLSI design methodologies for implementing scalable buffering schemes for high-speed networking applications, and presents a number of novel approaches. Our approaches combine the concepts of parallelism, pipelining, dynamic reconfiguration, and interconnection structures in a unified framework of system design and VLSI implementation.

#### 1.1 Buffer Management for High Speed Links

The ultra high data rates of optical fibre links can not be matched directly by the microelectronic interfaces and components deployed in today's packet switches. Techniques such as serial-to-parallel conversion and byte staggering (or multiplexing) are normally employed at the opto-electronic interface to bring the "parallel" data rate down so that it can be handled by VLSI circuits running at a typical clock rate of up to few hundred MHz. The process is depicted in Fig. 1.1 for

Fig. 1.1: Serial-to-parallel conversion and byte staggering at the opto-electronic interface

an OC-192 link that supplies data at a rate of about 10 Gb/s to a switch line-card with high-speed input buffers (and byte-wide inputs) which are triggered by 300 MHz clocks, i.e. each buffer has an input rate of 2.5 Gb/s. Because low-cost memories are still limited in speed, a 2.5 Gb/s buffer will likely be constructed from an interleaved, or a wide data-word, memory structure. Although faster memory technologies can be employed, such as RDRAM [3], this would normally increase the buffer cost significantly and would not be the ideal solution for the large capacity buffers normally associated with high-speed links.

The demand on the internal and/or the output buffers of a switch will be even higher because of the possible instantaneous traffic aggregation from multiple links over an outgoing link. To maintain low packet loss, it is not uncommon to have the output buffers supporting an input packet rate several times that of the input link rate, even for well-behaved input traffic [1]. For example, with 10 Gb/s input link rate, an output buffer that receives packets from up to four input links, simultaneously, must have an aggregate input rate of 40 Gb/s. Supporting this rate require using a parallel arrangement of at least sixteen 300-MHz FIFO buffers with an 8-bit data-path and the associated demultiplexing and multiplexing circuitry. Implementation problems do not stop there. A very undesirable effect of using a parallel FIFO buffer arrangement is the possible out-of-order delivery of packets to the outgoing links. In ATM, preserving the order of cells is mandatory. In this case, costly cell reordering must take place before the cells leave the switch.

#### 1.2 Packet-Scheduling

Providing QoS guarantees over packet-switched networks, such as the Internet, relies crucially on the scheduling and buffer management capabilities of the network switches and routers. Packetswitched networks with efficient packet-scheduling mechanisms can support the diverse QoS requirements of various real-time applications.

Multimedia sessions may have QoS specifications that include bounded end-to-end delay, bounded delay-jitter, bounded cell-loss rates, and guaranteed minimum link bandwidth. Scheduling is required to order packets, for example, to satisfy delay bounds of real-time sessions or to enforce fair bandwidth allocation for sessions sharing a link.

Packet-switched networks exploit a variety of scheduling schemes to provide the QoS guarantees for each connection. Priority-based scheduling is one of the most widely used techniques in packet switches and routers. In this scheme, packets are organized in different priority levels and served according to their priorities. Normally a packet is assigned an attribute which becomes its priority number and it is appended to the packet as an additional field. Packets in a buffer are then ordered and delivered according to their priority value by the scheduler. For example, the priority number may be a finish-time computed by a weighted fair queuing (WFQ) algorithm [4], [5], or a class index assigned by a class-based queuing (CBQ) algorithm [6], [7], etc. In any case, accessing the highest-priority packet requires the use of a *priority queue* structure. By definition a priority queue is a queuing structure for which the dequeue operation always removes the highest (or lowest) priority element in the queue. Arbitrating between a large number of packets on a high-speed link requires an efficient hardware implementation of a priority queue. In high-speed networks, the main challenge is maintaining the correct operation of the priority queue at very high link speeds, e.g. 2.4 to 40 Gb/s [1].

#### 1.3 Main Contributions & Thesis Organization

This thesis presents a number of new approaches for designing fast, scalable queuing structures in VLSI for very high speed packet-switched networks. Such queuing structures are necessary for implementing packet buffers in switches and routers that have multi Gb/s ports. Chapter 2 will draw some comparisons between systolic and non-systolic processing techniques, and survey shared buffer and priority queue hardware implementations. It will also point out how these issues have been addressed by various investigators.

The main objective of the thesis is to develop effective VLSI design methodologies for implementing scalable buffering schemes for high-speed networking applications. The thesis addresses the design of two specific architectures: balanced parallel multi-input multi-output (MIMO) buffer, and systolic parallel priority queue (PPQ). In the following, we elaborate on these two contributions and compare them to previous related research.

Balanced Parallel MIMO Buffer: The thesis presents a methodology for the systematic design of order-preserving MIMO buffers. Using this methodology we derive scalable parallel FIFO buffer structures that can be designed to match the rate of ultra high-speed links using current memory technology that uses moderate clock rates. Chapters 3 and 4 develop the design concept and VLSI implementation for a parallel MIMO buffer structure which can be used in ultra high-speed network interfaces and similar applications. The buffer is capable of inputting and/or outputting multiple packets while maintaining their FIFO (first-in first-out) order. These two chapters focus on buffer design for fixed-size packets, such as ATM cells (see Appendix A), but the design strategy can be extended to variable-length packets. Some applications of the MIMO buffers are outlined in Chapter 3 too.

Our approach employs a systolic routing network and bank of parallel FIFO buffers to yield a load-balanced multi-input multi-output FIFO realization with increased bandwidth [8], [9]. The MIMO buffer adaptively manages the available buffer space for statistically multiplexed input traffic. Our systolic routing network provides significant advantages over previously proposed banyan/butterfly networks since the systolic network eliminates the need for parallel-prefix adders that compute packet ranks before concentrating them on the output ports. The combined use of pipelined architecture and dynamic CMOS circuits resulted in significant reduction in design complexity and substantial performance gains in speed and area. A small 4-input 4-output prototype buffer has been designed using a triple-metal/single-poly 0.5- $\mu$  m CMOS technology to demonstrate our concepts. The buffer can attain a rate of 10.6 Gb/s which is more than adequate to support a Sonet OC-192 link.

Although the idea of using a parallel arrangement of FIFO buffers to realize a faster shared FIFO buffer has been around since the inception of the Knockout ATM switch [10], our realization and use of such buffer structures differ significantly from previous approaches, as will be pointed out in the next chapters. Our design approach is truly scalable and has real advantages from VLSI perspective. Also, in our designs, load-balancing is done using arithmetic-free circuits. As it will be explained in more details in Chapter 2, typically load-balancing is done using a multistage network of adders to do packet-ranking, and routing is done by a second pass through another multistage network as was done in the Knockout switch [10], and Multinet switch [11], [12].

and the contract of the contra

Systolic Parallel Priority Queue: The thesis also generalizes the priority queue concept to a *parallel priority queue* (PPQ) which can be scaled to meet the requirements of ultra high-speed links using standard CMOS technology. Chapters 5 and 6 present an area-efficient, systolic design of the PPQ for VLSI implementation. The proposed PPQ is rate-adaptive in the sense that the PPQ operates correctly even when the queue input rate and output rate are different [21]. This is an important feature because in practice the output rate of the queue is controlled by the available link bandwidth which may vary (or even become zero) independent of the packet arrival rate. This decoupling of the input and output packet flow rates is a distinguishing feature of our PPQ concept and has not been addressed in previous literature [22].

In many real applications, it is desirable to decouple the input process to the PPQ from the output process. Specifically, the PPQ outputs may be intermittently blocked from sending cells due to a link congestion. This process is usually called output rate-adaptation, and it requires significant modifications to the conventional architectures. To provide rate-adaptation capability to our PPQ, we strategically employ data steering blocks, between pipeline stages of PPQ, which are controlled by a global "go/stop" signal.

In non-systolic architectures, data insertion is normally performed over a global bus connected to the inputs of all the modules in the queue [23], as it will be explained in Chapter 2. This creates a bus loading problem, which adds to the hardware costs (buffers), and decreases the maximum operating speed of the queue clock [24]. In a systolic PQ implementation, the clock can be faster, but technology limitations can limit the clock speed. This problem is more serious when dealing with ultra-fast data links operating at 10 Gb/s (e.g. Sonet OC-192) to 40 Gb/s (e.g. Sonet OC-768) rate. In this thesis we employ a parallel processing approach to solve this scalability problem for

systolic PQs. Our approach embodies a combination of hardware design with more theoretical parallel processing concepts. The combined use of a systolic structure, and dynamic CMOS circuits facilitated the balancing of design complexity and performance gain, as will be shown in Chapters 5 and 6.

respondente de la companya de la co La companya de la co

10

# **CHAPTER 2**

Background & Survey

Buffering structures are integral components of packet networks. With the rapid proliferation of high speed packet-switching systems, the demand for high speed data buffers and scheduling networks has increased. Special requirements for such applications, suggest the use of customized memory-based architectures such as parallel buffers and priority queues. Before proposing efficient scalable queuing architectures to implement buffering and scheduling schemes using current VLSI technology, this chapter reviews previously proposed techniques for designing these buffers and queuing structures.

#### 2.1 Parallel FIFO Buffers

We start this section by considering previously proposed techniques for designing parallel multi-input multi-output (MIMO) buffers that preserve the FIFO ordering of cells. It is worth mentioning that such buffers have been also called "shared" FIFO buffers in previous literature and have been used before in several switch designs, for example, see [10]-[20].

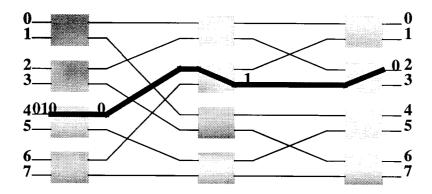

As shown in Fig. 2.1, if a high-speed buffer is constructed from multiple FIFO buffers (as discussed in Chapter 1), then a dynamic balanced distribution network (BDN) stage is needed to pack and shift the incoming cells so as to balance the load on all FIFO modules while preserving the arrival order of the cells at the same time. The buffer shown in the figure has 5 input ports and 5 output ports. The five ports are labeled a, b, c, d, and e. The labeled squares in the figure represent cells arriving in three different time-slots (1, 2, and 3), and the label of each cell indicates its arrival time-slot and arrival port. For example, the square label (2c) represents a cell arriving on port c in time-slot 2.

Typically load-balancing is done using a multistage network of adders to do packet-ranking, and routing is done in a second pass through another multistage network as was done in the Knockout switch [10], and Multinet switch [11], [12]. Note that the BDN packs incoming cells in adjacent output locations and shifts them appropriately to achieve a balanced loading of the FIFO buffers. Note also the order of cell arrivals is preserved. Fig. 2.1(b) shows the dynamic configuration of the BDN in each time-slot. In short, the BDN distributes cells arriving in the same time-slot among the FIFO buffers in a cyclic (or round robin) fashion so that the difference between the contents of any two buffers does not exceed one cell. Note, that load balancing eliminates the need for combinational concentrators and restricts the causes of cell loss to buffer overflow only.

Fig. 2.1: (a) Operation of a shared-buffer that preserves the cell arrival sequence (b) Illustration of pack-and-shift approach in three time-slots

Several schemes have been proposed to achieve the BDN function using multistage interconnection networks (cf. [25], and the references therein). To perform the pack-and-shift function, cells are first packed using either a concentrator or a routing network then shifted cyclically to distribute the packed cells evenly among the FIFO buffers at the output. Both the pack and shift func-

tions can be implemented by the well known butterfly (which is a banyan type) network [25]. The butterfly network nodes must have an arithmetic addition capability to perform parallel prefix addition for ranking the cells arriving at the same time in a given order. Ranking the cells can also be done by a low-latency adder network, such as the one described in [25].

Fig. 2.2 shows how cells can be packed and shifted (after they have been ranked) on a butterfly network for a  $5 \times 5$  (5-input/5-output or 5 I/O) buffer architecture. Referring to the example in Fig. 2.2(a), the three cells labeled 1b, 1d, and 1e, are first assigned the ranks 0, 1, and 2, respectively, then packed by a butterfly network. These ranks will be used as local routing headers to route these cells to output ports 0, 1, and 2 using a greedy self-routing strategy. At the output of the ranking network of Fig. 2.2(a) the cells appear labeled by their computed ranks. Fig. 2.2(b) illustrates a situation where the cells are ranked first, then packed and shifted cyclically by 3 positions. The shift-offset function modifies the ranks of the cells, so that they can be packed and shifted by the same butterfly network as the one used in Fig. 2.2(a). The routing procedure utilizes the monotonic routing property of the butterfly to pack-and-shift input cells with no path contention.

It is clear that the above realization of a BDN adds a high degree of complexity and latency to the buffer design. This approach has been employed in the Multinet switch [11], [12]. The internal buffers in the Multinet switch implement a partial buffer (PS) sharing discipline that maintains cells in the correct order [11]. Each PS buffer in the switch is constructed using a reverse banyan network (similar to the butterfly network illustrated in Fig. 2.2), of appropriate size, that feeds cells to a bank of FIFO buffers. The reverse banyan network is equipped with a Fetch-and-Add capability that contributes to balancing the load in the bank of FIFO buffers constituting the PS

- 0 cell with rank 000

- 1 cell with rank 001

- 2 cell with rank 010

- 3 cell with rank 011

- 4 cell with rank 100

Fig. 2.2: (a) Packing ranked cells on a butterfly network (5 I/O - first time-slot)

(b) Packing and shifting ranked cells on a butterfly network (5 I/O - second time-slot)

buffer space. Despite claims of simplicity, the Multinet switch is actually complex and cells can experience significant delays, mainly because of the structure of the PS buffers. The Fetch-and-Add reverse banyan network employed in each PS buffer performs arithmetic as well as routing operations. Three passes of computing and routing through the reverse banyan are required before cells are finally fed to the bank of FIFO buffers of PS buffer [12]. In current deep submicron CMOS technologies, the delay in signal propagation over longer wires becomes a significant design limitation, particularly for a shared buffer architecture with large number of I/O ports. This limitation is particularly applicable to high wire organizations such as the butterfly network (or reverse banyan network) typically used in interconnection networks [25].

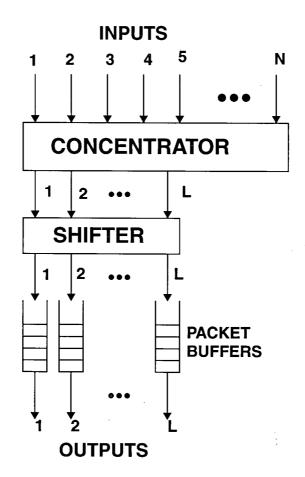

A somewhat different approach has been employed by the Knockout switch [10] and many of its realizations (such as the growable packet switch [13], [14], and the MOBAS switch [16]) to achieve load balancing. The knockout approach employs a lossy deep multi-stage concentration network followed by a shifter network, as shown in Fig. 2.3. The concentration is performed by N-to-L combinational tournament circuit, in which packets losing contention are knocked-out [10]. The parameter L (for the N-to-L concentrator) is selected in the Knockout switch to achieve a particular cell loss, and cell loss can be reduced by increasing L. The original Knockout concentrators have depth proportional to N, and their complexity as well as delay can be substantial for large N.

The PINIUM switch [18] is basically another Knockout switch with the concentrators modified to perform priority routing of cells. Each such concentrator is constructed from modified bitonic sorters and mergers [18], [25]. An N-to-L concentrator is constructed iteratively from L-input bitonic sorters and 2L-to-L bitonic mergers. As in the Knockout switch, the value parameter L determines the cell loss ratio in the memoryless routing and concentrating part of the switch. The

Fig. 2.3: Structure of a shared buffer in the Knockout switch

main weakness of the switch is the use of sorters in the priority concentrator blocks. The sorters can incur significant routing delays in large scale versions of the switch. The delay caused by the use of sorting in the priority concentrators becomes unacceptable at high link speeds. It is also not clear whether the use of priority concentration can lead to unfairness.

In the Helical switch [19], which is a self-routing multistage banyan network with output as well as internal buffers, each internal buffer consists of a non-blocking concentrator feeding a bank of FIFO buffers. Each non-blocking concentrator is constructed using a running adder and a two-

dilated reverse banyan network of appropriate size. Correct cell sequence is maintained by the concentrators. A concentrator routes the incoming cells to the next available concentrator output in round-robin order. At the concentrator output dummy cells are generated and inserted into the proper FIFO to maintain the integrity of cell ordering. The dummy cells generated by one stage of concentrators are not routed by the next stage of concentrators, rather they are used to create idle cycles that keep later cells from advancing past earlier cells. The concentrators employed in each stage of the switch can cause significant cell delays. This is caused by the insertion of dummy cells in internal FIFOs as well as the delays caused by the running adder. In other words, the delays will grow as the number of stages increase in large switches and the insertion of dummy cells in internal buffers will aggravate this problem. Additional hidden delays are caused by the running-adder operations in the reverse banyan networks employed in every stage.

One of the main contributions of this thesis is a very efficient implementation of the pack-and-shift function using a dynamically reconfigurable systolic interconnection array which is managed by two simple distributed controllers. The systolic architecture essentially realizes a pipelined switch array with embedded load-balancing and order-preserving capabilities (see Section 2.2 for definition of systolic architectures). To our knowledge, the work on parallel FIFO implementation has been done mainly under the concept of shared output buffer design in high speed packet switches as reported in [10]-[20]. Our work improves on these techniques by proposing an arithmetic-free, pipelined, load balancing network that forwards cells to a parallel MIMO FIFO bank [8]. Our design approach is based on a three-stage VLSI architecture as shown in Fig. 2.4 [9]. The first stage (BDN) is a systolic array of simple switches which performs load-balancing and ensures proper cell ordering. The second stage is a bank of single-input single-output FIFO buffers which operate in parallel. We enhance the flexibility of the design by adding a rotating multi-

Fig. 2.4: MIMO buffer and its symbol

plexer (or RMUX) at the output to adapt the buffer rate to that of the output link.

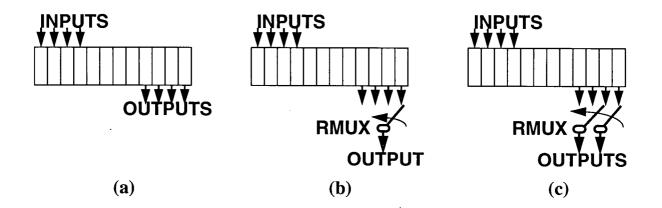

In the system design of the MIMO buffer the following objectives have been pursued: 1) maximum buffer space, 2) minimal routing delay, and 3) packet arrival in the correct order [26]. In Chapters 3 and 4, the detailed structure of the above realization is reported. Here, it is worth mentioning that because of the uniform structure of the proposed MIMO buffer, it has the advantages of simple synchronization and expansion due to the modular structure of the systolic switch array. It is a truly scalable architecture, and amenable to simple VLSI implementation. As shown in Fig. 2.5, if a rotating multiplexer (RMUX) is applied in the last stage of the parallel buffer, the buffer can also be employed as an ATM access point or as a buffer concentrator [26]. In addition to their use in high speed interfaces, these buffers can be utilized in a number of switch architectures [27]. Some of these applications are addressed in Section 3.5.

Fig. 2.5: (a) Parallel buffer, (b) ATM access point, and (c) Buffer concentrator

#### 2.2 Priority Queues

As mentioned in Chapter 1, priority queues are essential in implementing link-scheduling algorithms. Priority queues can be implemented in software or hardware. Due to the high speed at which the networks operate, a hardware priority queue is needed to transmit packets at link rates. For example, in a 10 Gb/s ATM network, an ATM cell can be transmitted every about 42 ns. In a worst-case scenario the priority queue must determine the next highest priority cell (dequeue operation) every 42 ns, while being able to accept new cells (enqueue operation) from all incoming links within the same time unit. Software solutions are typically not fast enough to keep up with this packet transmission rate [24]. On the other hand, a scalable hardware solution can operate close to the operating speeds of the link. Also, a hardware solution can overlap enqueue and dequeue operations with packet transmission to avoid wasting link bandwidth. In hardware implementations, a sequencer determines the departure sequence for the packets that are stored in a buffer bank. In general, hardware solutions can be categorized in two families: systolic and non-systolic.

Systolic Arrays: The term systolic array, which became popular in the early 80's, refers to certain processing structures with regular cellular organization and a large number of neighbouring processing elements with same function [28], [29]. They communicate via direct physical interconnections only with a limited number of adjacent processing elements to exchange data. Therefore, interconnections are local and in a regular pattern. VLSI technology has made one thing quite clear: simple and regular interconnections have substantial advantages over complicated interconnections. The original motivation for proposing the systolic array concept was their high efficiency for implementing VLSI systems [28]. Being highly regular and modular structures, they do not suffer from the VLSI design problems which are typical of other systems. Fitting the principal constraints imposed by VLSI design and technology, the systolic systems should, in principle, be able to profit from VLSI as a potential implementation means [29].

A systolic priority queue architecture typically consists of a large number of similar processing elements which are interconnected to exchange data. In fact, many processors work in parallel and the data is processed and transferred by pipelining (as will be described in Chapter 5). The first systolic priority queue was proposed by Leiserson [30]. In recent years, systolic [31], and non-systolic [33], priority queues were proposed for high-speed network buffers.

美国特殊 医多种性 医多种性 医皮肤

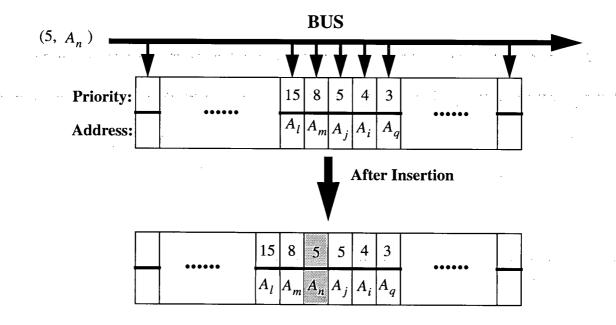

In non-systolic architectures [34], data cell insertion is normally performed over a global bus connected to the inputs of all the modules in the queue. A priority queue always serves the packet that has the highest priority. It determines the departure sequence for the packets that are stored in a buffer bank in such a way that higher priority values are always at the right of lower priority values so they will be accessed sooner. Each entry in the priority queue contains the pair (P,A), where P is a priority field and A is an address pointer to a packet in a packet memory. In a non-systolic hardware structure, as shown in the example in Fig. 2.6, these pairs are stored in the sequencer in

a descending order. Now, let us consider an example of a newly arrived data cell with P=5 and  $A=A_n$ . This pair is broadcast to all modules. All pairs on the right of  $A_j$ , including the  $A_j$  itself, remain at their positions while others shifted to the left, and the vacant position is replaced with the new pair  $(5,A_n)$ . When the PQ is full, the priority field at the leftmost position of the sequencer is compared to that of the newly arrived data cell. If the new's one is smaller than it, the pair (P,A) at the leftmost position is pushed away from the sequencer as the new pair is inserted in the sequencer.

Fig. 2.6: Inserting a new arrival into a non-systolic PQ

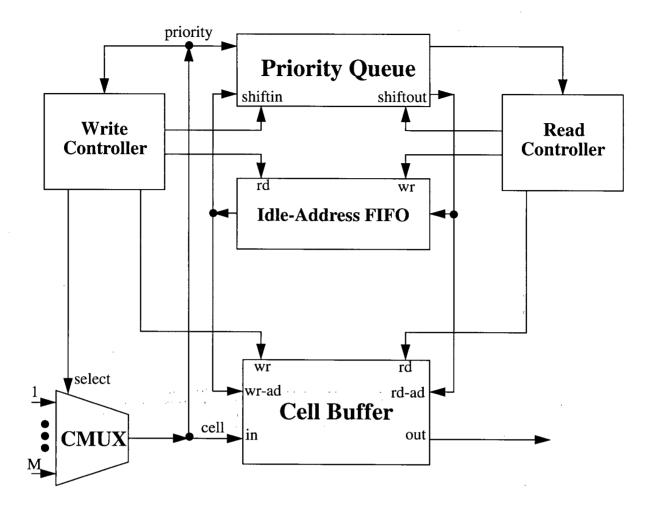

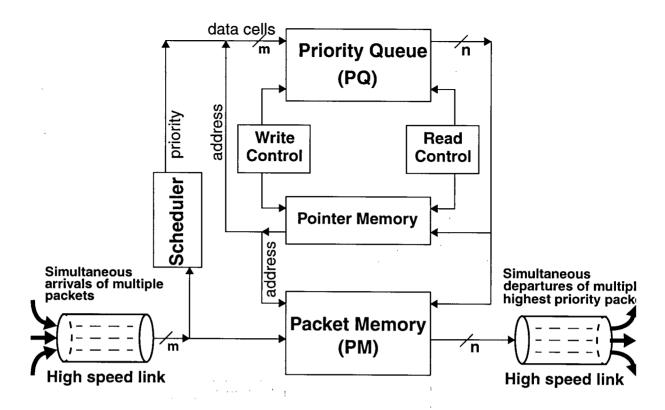

Fig. 2.7: Buffer manager structure

Fig. 2.7 shows a typical buffer manager structure for an ATM switch (see Appendix A) that uses a priority queue or sequencer [32]. The buffer manager consists of a cell multiplexer (M inputs and one output), a cell buffer, an idle-address FIFO, read and write controllers, and a priority queue. The cell multiplexer (CMUX) located after a switch fabric receives and multiplexes up to M cells from the switch fabric, where M is the number of cells that are routed through an ATM switch network and arrived at an output port. Cells from the inputs are multiplexed onto the cell buffer at idle-addresses retrieved from a FIFO (only valid cells are stored in the cell buffer). The read/write

controllers generate proper control signals for all other functional blocks. The buffer manger always serves the cell that has the smallest priority value of the P first and they will be accessed earlier by the read controller. In the buffer manager structure, the sequencer determines the departure sequence for the cells that are stored in the cell buffer.

In the non-systolic architecture presented in [34], which is one of the only few dedicated priority queue designs to be implemented in silicon, a bus structure has been used to access all of the buffering modules. At each module the data cell on the common bus is compared to the data cell in the module. However, because data insertion is performed over a global bus, the queue cannot operate at very high speed. As seen in Fig. 2.6, before any decision can be made by each module during an enqueue operation, the new entry must be present at the inputs of all modules. At the VLSI level, the bus must be routed all over the queue. This creates a bus loading problem, which adds to the hardware costs (buffers), and decreases the maximum operating speed of the queue clock [24].

The design presented in [36] is also a priority queue controller designed for use in ATM switches. The chip provides no data storage, but rather maintains a separate logical FIFO queue in external RAM (random access memory) for each of its four supported priority levels. Although this simplifies comparator logic, maintaining separate FIFO's is impractical in the presence of a larger number of priority levels. Moreover, since ATM switches have equal input and output data rates, this chip was not designed to accommodate different read and write clock speeds.

A binary tree comparator architecture was presented in [37] whose output is the highest-priority entry among those in a storage. The architecture consists of a storage block and a comparator tree. A feedback mechanism is also applied in the design to remove the output of the tree from storage. Problems with this design include bus loading problem for distributing the new entry to each stor-

age element in the storage block, and increased dequeue time resulting from an increase in depth of the comparator tree. A possible solution to the increased dequeue time is to pipeline the comparator tree operation to reduce the clock period and increase performance [24].

Chapters 5 and 6 present an alternative design technique using systolic design concept, which can achieve higher speed, to meet the requirements of ultra high-speed links using standard CMOS technology [22]. The proposed PPQ has several applications in implementing real-time fair schedulers or buffer management algorithms in packet routers.

the second of the contract of

And the second second second

25

# **CHAPTER 3**

Parallel FIFO Buffers for Gigabit Packet Networks

### 3.1 Introduction

This chapter presents a methodology for the systematic design of order-preserving multi-input multi-output (MIMO) buffers for large scale or ultra fast packet switches. It focuses on buffer design for fixed-size packets, such as ATM cells, but the design strategy can be extended to variable-length packets. These buffers are capable of inputting and/or outputting multiple packets while maintaining their FIFO (first-in first-out) order, and can be used in ultra high-speed network interfaces and similar applications. Our approach employs a systolic routing network and bank of

parallel FIFO buffers to yield a load-balanced MIMO FIFO realization with increased bandwidth [8]. The MIMO buffer adaptively manages the available buffer space for statistically multiplexed input traffic. Our systolic routing network provides significant advantages over previously proposed banyan/butterfly networks since the systolic network eliminates the need for parallel-prefix adders that compute packet ranks before concentrating them on the output ports [9]. Also, in our designs, load-balancing is done using arithmetic-free circuits.

Using this methodology we derive scalable parallel FIFO buffer structures that can be designed to match the rate of ultra high-speed links using current memory technology that uses moderate clock rates. Our design approach is truly scalable and has real advantages from a VLSI perspective. As it was described in Chapter 2, if a high-speed buffer is constructed from multiple FIFO buffers then a balanced distribution network (BDN) stage is needed to *pack* and *shift* the incoming cells so as to balance the load on all FIFO modules while preserving the arrival order of the cells at the same time. Our design approach is based on a three-part VLSI architecture as shown in Fig. 3.1. The first part is a systolic two-dimensional array (folded crossbar) of simple switches which performs load-balancing and ensures proper cell ordering. The second part is a bank of single-input single-output FIFO buffers which operate in parallel. The last part is a rotating multiplexer (RMUX) which adapts the buffer output rate to the output link rate. Note that the folded crossbar is used for load balancing in a single MIMO buffer and not for general routing of packets.

An example of how MIMO buffers can be used in a multistage switch is shown in Fig. 3.1. Note that a MIMO buffer spreads its cells equally among its output links thus achieving load balancing on the links as well. Each bundle of links connected to the output of a MIMO buffer can be viewed as a "super link" with aggregate bandwidth equal to the total bandwidth of its individual links. The proper operation of multiple stages of MIMO buffers is possible because of their order

# Stage i BDN Balanced Distribution Network MIMO Buffer NPUTS NPUTS NOTPUTS

Fig. 3.1: MIMO buffer in a multi-stage switch and its symbol

### preserving capability.

The rest of the chapter is organized as follows. The next section outlines the basic operation of the MIMO buffer. The buffer architecture and its main components are presented in Section 3.3. Section 3.4 describes the operation of a balanced distribution network (BDN) and illustrates its pipelined operation and dynamic reconfiguration for load balancing. In Section 3.5 some applications of the MIMO buffer are discussed, followed by a summary in Section 3.6.

# 3.2 MIMO Buffer Design Principals

This section outlines the main principles underlying the VLSI design and performance of MIMO buffers with the aforementioned properties. Our design approach exploits pipelining, parallelism, distributed control, and dynamic reconfiguration, as key techniques for achieving scalability and optimal buffer utilization. Pipelining increases switch utilization, and is used as the main tool for maximizing hardware utilization. Both data and control paths are pipelined yielding a true systolic design with short nearest-neighbor interconnections which is ideal from VLSI design perspective. Parallelization of the data or packet path is employed as the main tool for achieving significant speed gains in a scalable manner. However, parallelizing the buffer structure may lead to underutilization of memory and wire resources and may also cause out-of-sequence packet delivery as was pointed out earlier, hence the need for load-balancing and order-preserving control in the MIMO buffer.

## 3.2.1 Basic Operation of the MIMO Buffer

The main contribution of this chapter is a very efficient implementation of the pack-and-shift function using a dynamically reconfigurable systolic interconnection array which is managed by two simple distributed controllers. The systolic architecture essentially realizes a pipelined cross-bar switch array with embedded load-balancing and order-preserving capabilities. Systolic cross-bar interconnection networks have better composite VLSI performance than other interconnection networks that use higher wire area such as the butterfly and omega networks [25], especially in submicron CMOS technologies. Crossbars have the advantage of employing short wire segments only which allows the use of faster clock rates and achieves higher utilization of silicon area.

The proposed folded crossbar network is dynamically reconfigurable in the sense that the reconfiguration is achieved by locally adjusting the switch position within each switching element based on single-bit information in the cell headers. Each switch element has a set of locally controllable switches which enable its I/O ports to be connected internally in various configurations. Switch control provides for connection autonomy in the sense that different switch elements can select different configurations based on local decisions made within the element. In the following section, the structure of this realization is described.

### 3.2.2 The MIMO Buffer Structure

The proposed MIMO buffer consists of a balanced-distribution network (BDN) feeding a bank of FIFO buffers, as illustrated in Fig. 3.2. A rotator multiplexer (RMUX) can be attached to the outputs of the buffer bank to decouple their rate from the output link rate, as will be explained below. Before proceeding to architectural details, it is useful to identify the main design parameters that can be used to specify the MIMO buffer architecture based on aggregate bandwidth requirements and the clock rate of the implementation technology. The main design parameters are:

- k: the number of FIFO buffers used and also the number of input links to the MIMO buffer assuming a constant data-path width of w bits (wires) per link,

- m: the number of output links of the MIMO buffer assuming a constant width of w bits (wires) per link, and

- r: the rate of each input (or output) link.

Proper values for the above parameters are determined based on two key restrictions:

- R: the aggregate link-rate (in bits-per-second) at the input of the MIMO buffer, and

- c: the clock-rate of the MIMO buffer circuit.

Fig. 3.2: Internal structure of the buffer

Note that c is a parameter that depends mainly on the technology used. Because of the high-degree of pipelining used in our design, c will be determined mainly by the access-time of the FIFO buffers, since all other components have delays much shorter than that.

Given a FIFO buffer whose bit rate is r and clock rate is c, then  $r = c \cdot w$ . To match an aggregate input link rate of R, k input links and k FIFO buffers must be used, where  $k = \lceil R/r \rceil$ . The RMUX allows further design scalability by decoupling the FIFO rate from the output link rate. This is an important property of the design since it is normally the case that the aggregate input rate is higher than the aggregate output rate in the buffers of a packet switch. For example, if the number of input links is an integer multiple of the output links, i.e.  $k = n \cdot m$  form some integer

n, then an RMUX with k inputs and m outputs can be used to forward packets from the FIFO buffers onto the output link. The RMUX samples the FIFO outputs m at a time, and visits all FIFO outputs in n cycles. Essentially, the RMUX enables the MIMO buffer to operate as a buffered concentrator which does not incur any packet loss unless the FIFO buffers are full.

As an example, consider the design of a MIMO buffer with an aggregate input rate of 10 Gb/s and an output rate of 5 Gb/s, when the data-path width is w=8, and the clock rate that can be supported by the CMOS technology at hand is 320 MHz. In this case, the input link-rate is 2.5 Gb/s, and so k=4, i.e. the MIMO can be designed using a  $4\times4$  folded crossbar switching array, 4 FIFO buffers, and a 4-to-2 RMUX.

The scalability feature of BDN can be used to construct very high bandwidth packet memories from standard FIFO memory units of moderate speed. Specifically, the BDN allows a packet memory of bandwidth  $2(k \cdot r)$  to be realized from k memory units of bandwidth 2r each [9]. The BDN also ensures equal utilization of the memory units under all traffic patterns. In the following section we explain the BDN structure in more detail.

# 3.3 The Balanced Distribution Network (BDN)

The BDN is the primary routing engine in the MIMO buffer, performing both pack and shift operations. Additionally, the BDN maintains the state of the last shift operation, which indicates the position of the last FIFO buffer to which a cell has been forwarded. Maintaining this state is essential for the load balancing operation. The 8×8 BDN shown in Fig. 3.3, is comprised of a folded crossbar simple switching elements (SWTs), a horizontal controller (HOC), and a vertical controller (VEC). For FIFO operation, the HOC and VEC are constructed from simple networks

Fig. 3.3: Internal Structure of an 8x8 BDN

of delay elements for the purpose of synchronizing the arrivals of cells and control signals at the appropriate switching elements. In Fig. 3.3, SWTs are represented by squares while delay chains are represented by circles labeled by the amount of delay, e.g. a circle labeled 5D represents a delay chain of length 5, where a unit of delay corresponds to one clock period.

Fig. 3.4: Input/Output port alignment of the BDN (crossed squares indicate empty cells)

The BDN operates in a synchronous time-slotted manner, with each time-slot equivalent to one cell (fixed-size packet) time over a *w*-bit link. Cell arrivals are always aligned with the beginning of time-slot for all BDN inputs. Within a time-slot, a BDN receives either a valid or an invalid (or empty) cell. We assume that a special bit in the cell header is used to indicate whether the cell is valid or not. Such empty cells will be removed of the cell stream during the packing operation in the BDN. Note that before entering the BDN, the cells are passed through the HOC which routes incoming cells through proper delay stages before they enter the BDN.

Fig. 3.4 explains the timing alignments of the cells at the input of the HOC for the 4×4 BDN

example of Fig. 3.2, also at the input of the folded crossbar (i.e. the output of the HOC), and at the output of the crossbar before being written into the FIFO buffers. Note the difference between a clock period which defines one *time-unit* versus a cell period which defines one *time-slot*. Basically, the incoming cells (whether valid or empty) are always aligned at the HOC inputs. The HOC then "staggers" the cells before entering the crossbar. This is a necessary step because cells in the crossbar can turn-around and rendezvous with one another at a SWT as will be explained later. However, before leaving the crossbar, the cells are aligned back again.

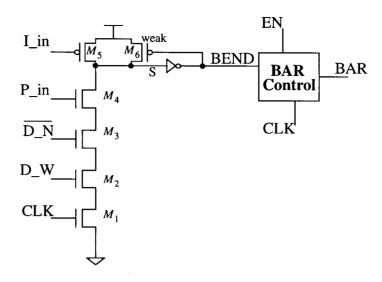

As mentioned above, the folded crossbar network consists of simple 2-input 2-output switching elements. Cells enter a SWT from its north port (i.e. port  $D_N$ ) and/or from its west port (i.e. port  $D_W$ ). Based on its local state and the information available at its input ports, a SWT will steer the incoming cells to the proper output ports. A SWT has a set of locally controllable transmission circuits which enable its four I/O ports to be connected internally in various configurations.

As shown in Fig. 3.5, each SWT can be in one of two modes representing its local state: a *cross* (or *unswitched*) mode and a *toggle* (or *bar*) mode. Normally, the SWT is in the cross mode, i.e. cells from its north (west) port are routed to its south (east) port. Fig. 3.5 also shows the four possible configurations of a SWT based on the type of simultaneous cell arrivals on its two inputs. Note that empty cells are always routed eastwards where eventually they will be discarded (the small solid black squares in Fig. 3.3 and other figures in this chapter indicate a cell-discard port). On the other hand, valid cells are always routed southwards, except when both cell arrivals at a SWT are valid cells. In this case priority is given to the valid cell from the north port, and the cell from the west port is propagated eastwards until it is eventually switched to a south port. Other possible states of the SWT will be discussed under dynamic load balancing on the BDN in the

Fig. 3.5: Two states of the switch element

next section.

The horizontal controller (HOC) synchronizes the entry of data cells, valid bit indicator and cell length signals into the folded crossbar switch array. It ensures that cells are properly aligned when they arrive at each switch element as shown in Fig. 3.4. The HOC function is realized by instantiating some *delay elements* as illustrated in Fig. 3.3. In Fig. 3.3, and other figures in this chapter, we use the symbol D to denote a basic clocked delay element. Delay chains in the BDN are represented by circles labeled by a multiple of D (e.g. 5D) indicating the length of the delay chain. The basic delay elements ensure the integrity of the wavefront at any switch element. A delay element D is basically a clocked register of width w bits (w= 8 is assumed throughout this chapter). For proper operation of the BDN, we require such registers to be of the master-slave type. All SWTs and delay elements are triggered by the same clock. *Delay element nD* can be defined as a register with a delay equal to n clock periods [8].

Fig. 3.6: I/O diagram of the SWT and cell format

Timing Details for a SWT: Before moving on to further discussion of the BDN operation, it is important to clarify the timing details for a SWT during normal operation. A more detailed diagram of the SWT and its data input signals format are shown in Fig. 3.6. In addition to its 4 ports  $(D_W, D_N, D_E, \text{ and } D_S)$ , a SWT has a clock signal (CLK), an enable signal (EN), and 5 additional control signals: two input signals  $I_{in}$ , and  $P_{in}$ , and three output signals  $I_{out}$ ,  $P_{out}$ , and BAR. The  $I_{in}$  signal is used to indicate the beginning of a cell time-slot, while the  $P_{in}$  signal is employed to determine whether two cells arrive at the  $D_W$  and  $D_N$  ports are valid or empty cells. BAR is a special signal which is propagated among SWTs in the same column to maintain certain state information, as will be explained in the next section. The correct operation of a SWT assumes that two byte-aligned cells arrive simultaneously at the  $D_W$  and  $D_N$  ports and also synchronize with the  $I_{in}$  and  $P_{in}$  signals.

$P_{out}$  and  $I_{out}$  are two delayed versions of  $I_{in}$  and  $P_{in}$ . As demonstrated in the last section, ATM

cells are propagated in the SWT array similar to a wave propagating along the diagonal direction toward the bottom right corner. The control signals which communicate between adjacent SWTs ease the synchronization problem. This requires the same phase to the signal arriving at each SWT. For this reason, the  $P_{in}$  and  $I_{in}$  signals are applied from the top left of the SWT array, and each SWT distributes these signals through the  $P_{out}$  and  $I_{out}$  output signals to its east neighbor with the exception of the SWTs in the first column of the square array which disperse these two signals to both their east and south neighbors. These signals have to pass through delay elements in each SWT of the architecture as will be shown later. In order to increase speed and minimize the silicon area of the switch elements, a modified version of domino circuits [38] has been employed (as will be explained in Chapter 4). The operation of the BDN will be discussed in the next section.

# 3.4 Dynamic Load Balancing on the BDN

This section provides additional details on the folded crossbar array architecture and how it performs load balancing on the FIFO buffers. We will start by illustrating the operation of an "unfolded" version of the folded crossbar array, then provide a more formal description of the folded crossbar architecture and control signals.

Consider the simplified  $4 \times 4$  BDN architecture shown in Fig. 3.7. The crossbar switching array consists of a primary (square) array and a secondary (triangular) array of SWTs, and both arrays are arranged in an unfolded configuration. In the topologically equivalent folded crossbar version, the secondary array is overlaid on the primary array so that the SWTs in column i of the primary and column i of the secondary array are adjacent.

Fig. 3.7: Four routing phases of the buffer (configuration of the SWTs in the example of Fig. 3.2)

Fig. 3.7 illustrates the load-balancing action of the BDN under four waves of input cells according to the arrival pattern of example of Fig. 3.2. For simplicity, we suppress unnecessary details of the pipelined operation and explain the operation in terms of routing phases. In a *routing phase* all the cells arriving in the same time-slot will be routed completely through the crossbar array, packed, shifted, and stored in their destination FIFO buffers. A new routing phase is always started in the primary array. In cases where the shift operation results in cells being pushed out of the rightmost column of the primary array, the secondary array will complete the routing for such cells.

As shown in Fig. 3.7, the first routing phase will use the first three columns of the primary array. We say a column has been "used" in a routing phase if one of its SWTs has been set to the toggle mode. When a SWT is in the toggle mode, it will broadcast its status to all SWTs in the same column (and to the VEC unit) over a special control line. This status is maintained by a special "used" flag in each SWT. Therefore, in our example, the "used" SWTs can easily identify their status through the "used" flag (i.e. output signal *BAR* in the actual SWT circuit). At the end of the first routing phase, the three incoming cells will end up in FIFO buffers 1, 2, and 3.

In the second routing phase, all SWTs in the first three columns (i.e. columns used in the previous phase) will be set to the cross configuration. Therefore, any incoming packets in the second phase will bypass the first three columns of SWTs of the primary array and routing towards the FIFO buffers will start at column 4 of the primary array as desired. The two incoming packets in the second phase will be routed through column 4 of the primary array and column 1 of the secondary array, and will end up in FIFO buffers 4 and 1 respectively. Once the last column of the primary array has been used (column 4 in this example), the next phase always involves transferring the state of the columns used in the secondary to the corresponding columns in the primary array, and routing starts from the next available column in the primary array. In other words, we never start a

new routing phase at a column in the secondary array.

The state transfer is carried out by the VEC unit in a straight forward manner. Basically once a SWT in some column j (j = 1 at the third routing phase of our example) of the secondary array has been set to toggle mode, its column will be marked as "used" as was explained before. In the next routing phase the status of columns 1 through j of the primary array is set to "disable" to mirror the state of the corresponding columns in the secondary array. In the example of Fig. 3.7, we have j = 1, and the third routing phase will start at column 2 of the primary array as shown. Then, the fourth routing phase will begin at column 4 of the primary array as shown, i.e. j = 3 at the fourth routing phase of the example. Note that last column (i.e. column N) of the primary array is always set to "enable" (in all routing phases). Also, it is important to emphasize that a balanced load on the FIFO buffers is always maintained at the end of each routing phase.

The details of the structure of a folded crossbar array are shown in Fig. 3.8. Note that the primary array consists of  $N^2$  SWTs arranged in N columns and N rows, with each switch element  $S_{i,j}$  (where i, j = 1, 2, ..., N) connected to each of four nearest-neighbor SWTs through its four ports. The secondary array consists of N((N-1)/2) switch elements  $T_{i,j}$  (where i = 2, 3, ..., N and j = 1, 2, ..., N-1) arranged in a triangular plane with N-1 columns and N-1 rows. Each switch element (SWT)  $C_i$  (where i = 1, 2, ..., N-1) acts as a multiplexer, selecting inputs from either the triangular array or the square array and switching them to the output ports. The appropriate number of clock delays are added to ensure that output cells in each cell cycle appear at the output at the same time. Therefore, the total delay of the BDN is equal to  $(3N-1) \times t_c$ , where  $t_c$  is the clock period.

Fig. 3.8: Folded crossbar array of the BDN

The control of data flow through the folded crossbar is done in a distributed fashion using the VEC and the status bits of the SWTs (i.e. BAR signals). As shown in Fig. 3.9, in the VEC unit there are N, 1-bit register flags, such that register  $F_i$  is associated with column i of the primary array as well as column i of the secondary array. The connectivity between the SWTs and a regis-

Fig. 3.9: Distributed control in the VEC