# TANTALUM PENTOXIDE, A NON CONVENTIONAL GATE INSULATOR FOR MOS DEVICES

by

ANTONIO L. EGUIZABAL-RIVAS

Ingeniero Civil-Electrico, Universidad Tecnica del Estado

(Santiago, Chile, 1970)

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

THE FACULTY OF GRADUATE

STUDIES

Department of Electrical Engineering

We accept this Thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

November 1984

© Antonio L. Equizabal Rivas, 1984

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of <u>Electrical Engineering</u>

The University of British Columbia 2075 Wesbrook Place Vancouver, Canada V6T 1W5

Date November 6th, 1984

#### ABSTRACT

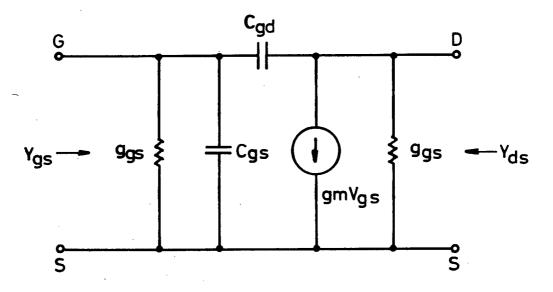

Non conventional gate insulators for MOS devices generally dielectrics that depart considerably from the classic SiO<sub>2</sub> used extensively in this technology. The presented here reflects the research and development of an existing compound, Ta<sub>2</sub>O<sub>5</sub>, and its application as a insulator for both MOS capacitors and transistors. The oxide grown both thermally and anodically from pure sputtered tantalum metal over silicon wafers. Successful dielectrics for gate insulators were obtained using both suitable High relative permittivity (~26-28) characteristic of tantalum pentoxide, offers considerable advantage over classic silicon dioxide gate insulators, however higher leakage currents (100 to 1000 times greater) were encountered in MOS Capacitor samples at temperature. A method for processing the tantalum metal was developed using the liftoff technique, and successfully applied to both MOS capacitors and field effect transistors. Furthermore, devices were fabricated in the form of MOS Transistors, which exhibited good Id vs. characteristics, with Vgs as a parameter. Gate leakage currents were low, as a double dielectric Ta<sub>2</sub>O<sub>5</sub> over SiO<sub>2</sub> structure was used as gate insulator. A small signal model of this class of devices is presented, that takes account the non zero gate leakage current. Another successful technique, interfacial oxidation of Ta 205 Si, was used in fabricating MOS Capacitors that yielded also low leakage currents and high specific capacitances.

The purpose of this Thesis is to report the development at the University of British Columbia of the double gate insulator MOSFET technology based on the Tantalum Pentoxide-Silicon Dioxide  $(Ta_2O_5/SiO_2)$  heteromorphic structure.

# TABLE OF CONTENTS

| ABSTRACTii                                                             |

|------------------------------------------------------------------------|

| TABLE OF CONTENTSiv                                                    |

| LIST OF TABLESviii                                                     |

| LIST OF FIGURESx                                                       |

| ACKOWLEDGEMENTSxiii                                                    |

| CHAPTER 1                                                              |

| INTRODUCTION1                                                          |

| CHAPTER 2                                                              |

| AN OVERVIEW OF NON CONVENTIONAL INSULATORS6                            |

| CHAPTER 3                                                              |

| THE THEORY OF THE Ta2O5-SiO2 DOUBLE DIELECTRIC                         |

| STRUCTURE29                                                            |

| 3.1 STEADY STATE ANALYSIS                                              |

| 3.2 TRANSIENT ANALYSIS                                                 |

| 3.3 EFFECT OF THE DOUBLE DIELECTRIC GATE INSULATOR                     |

| ON THE MOSFET PERFORMANCE41                                            |

| 3.4 EFFECT OF A HIGH PERMITTIVITY GATE INSULATOR ON                    |

| THE MOSFET PERFORMANCE46                                               |

| 3.5 ENERGY BANDS OF THE TANTALUM PENTOXIDE INSULATOR                   |

| 50                                                                     |

| 3.6 DOUBLE DIELECTRIC MOSFET STRUCTURE52                               |

| CHAPTER 4                                                              |

| FABRICATION AND PROCESSING OF MOS CAPACITOR DEVICES 54                 |

| 4.1 MOS CAPACITORS WITH THERMAL ${\rm Ta}_2{\rm O}_5$ AS INSULATOR .54 |

| 4.1.1 THICKNESS AND SHEET RESISTIVITY                                  |

| MEASUREMENTS55                                                         |

| 4.1.2 SCRIBING AND MARKING55                                           |

| 4.1.3 PEROXIDE ACID CLEANING                                                 |

|------------------------------------------------------------------------------|

| 4.1.4 RF SPUTTERING                                                          |

| 4.1.5 THERMAL OXIDATION57                                                    |

| 4.1.6 ALUMINIUM DEPOSITION59                                                 |

| 4.1.7 PHOTOLITHOGRAPHY59                                                     |

| 4.1.8 CONTACT METALLIZATION60                                                |

| 4.2 MOS CAPACITORS WITH DOUBLE DIELECTRIC STRUCTURE 60                       |

| 4.3 PROCESS AND FABRICATION COMMENTS61                                       |

| 4.4 THE LIFTOFF TECHNIQUE ON TANTALUM FILMS64                                |

| 4.5 MOS CAPACITORS WITH ANODIC Ta <sub>2</sub> O <sub>5</sub> AS INSULATOR65 |

| 4.5.1 ANODIZATION IN CITRIC ACID ELECTROLYTE                                 |

| SOLUTION69                                                                   |

| 4.5.2 ANODIZATION IN H <sub>3</sub> PO <sub>4</sub> ELECTROLYTE SOLUTION72   |

| 4.6 INTERFACIAL OXIDATION MOS CAPACITORS73                                   |

| CHAPTER 5                                                                    |

| RESULTS AND MEASUREMENTS ON MOS CAPACITORS76                                 |

| 5.1 ELLIPSOMETRY76                                                           |

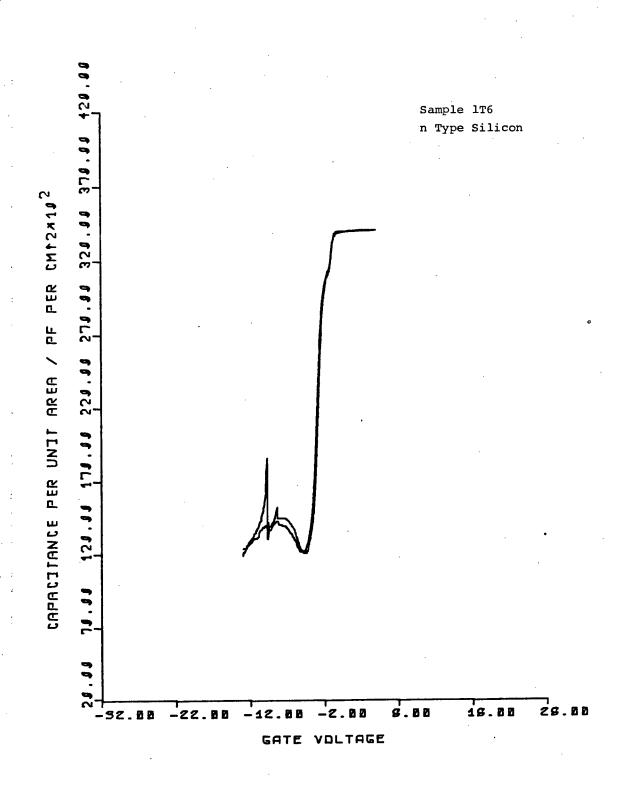

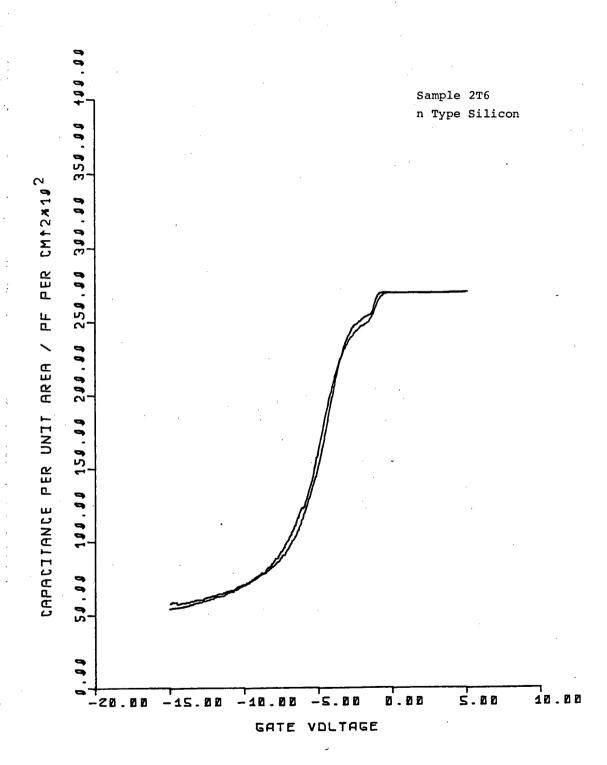

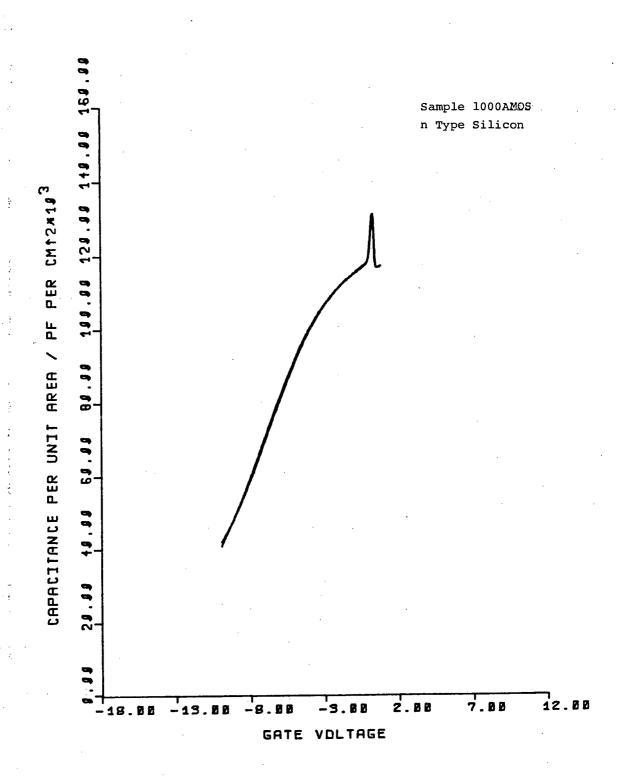

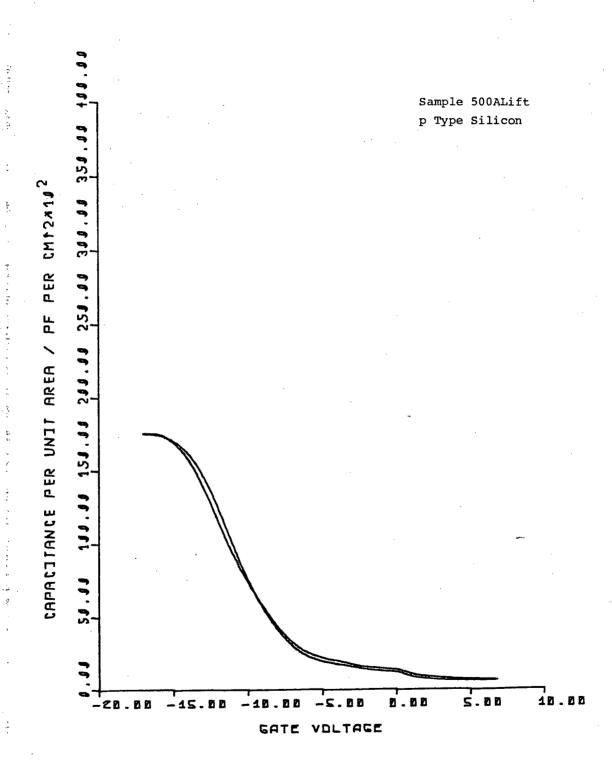

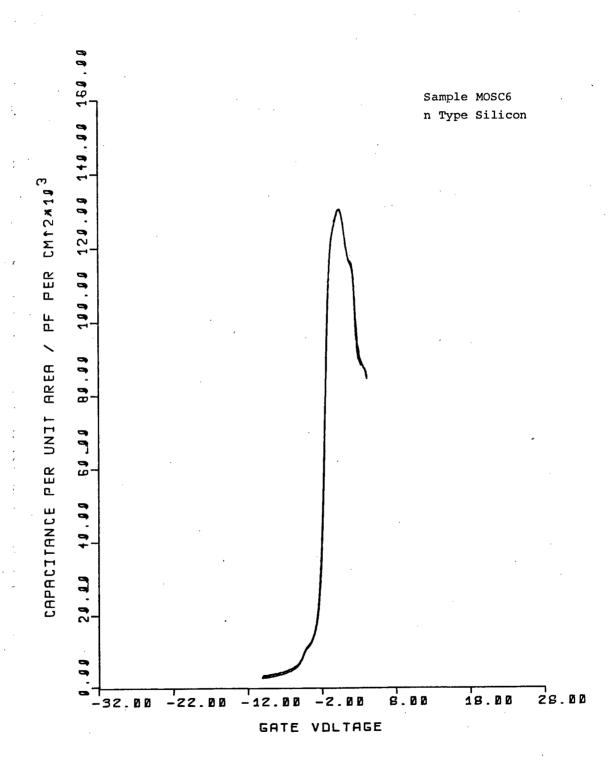

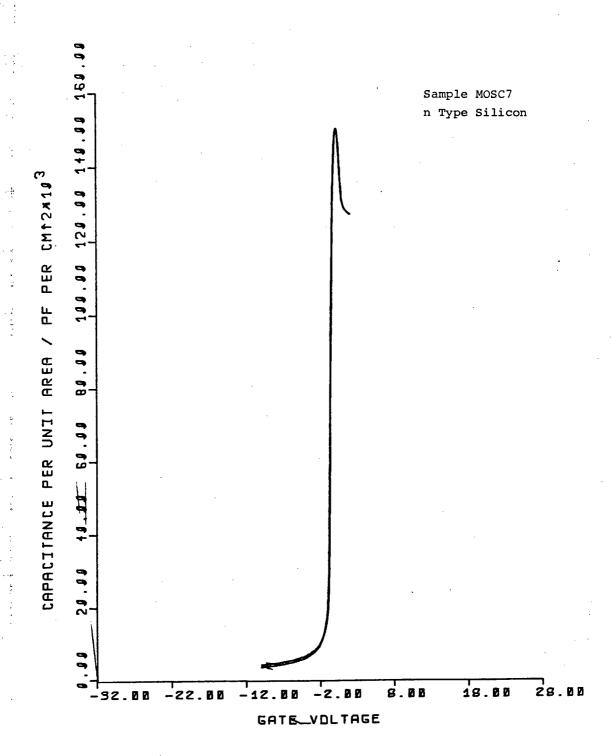

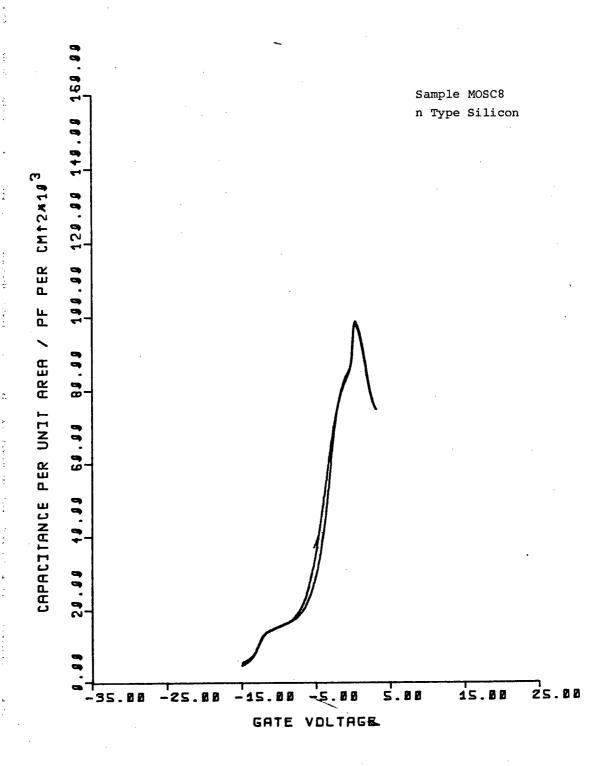

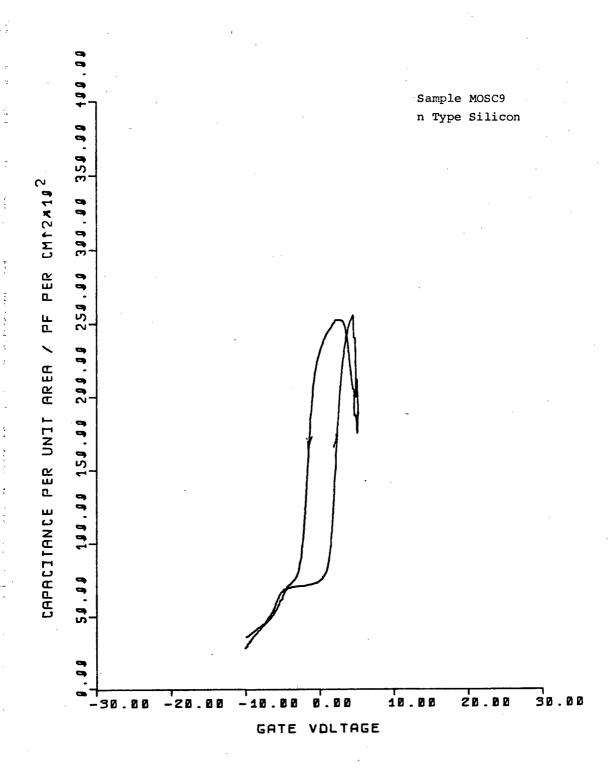

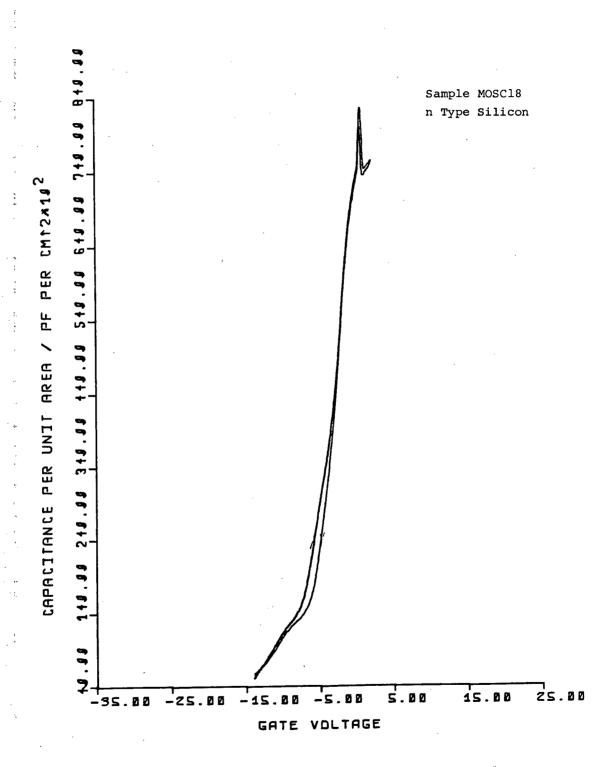

| 5.2 C-V MEASUREMENTS77                                                       |

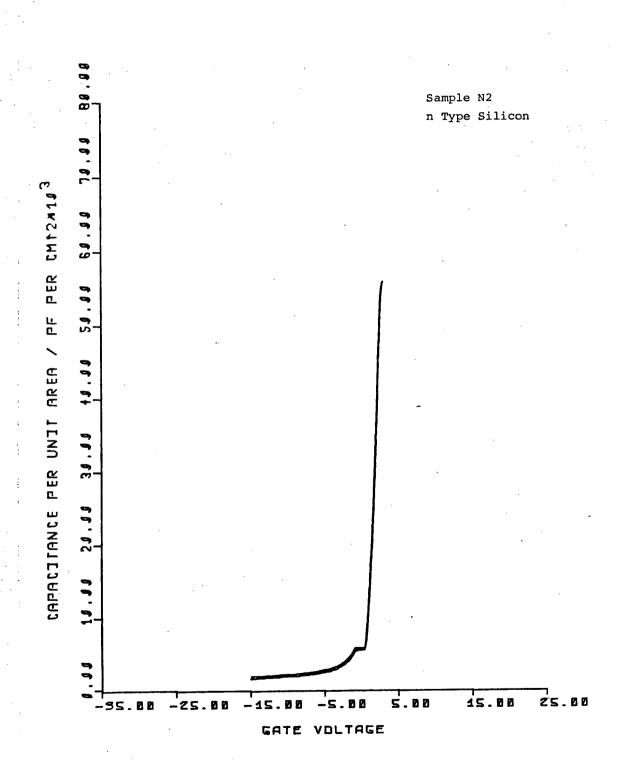

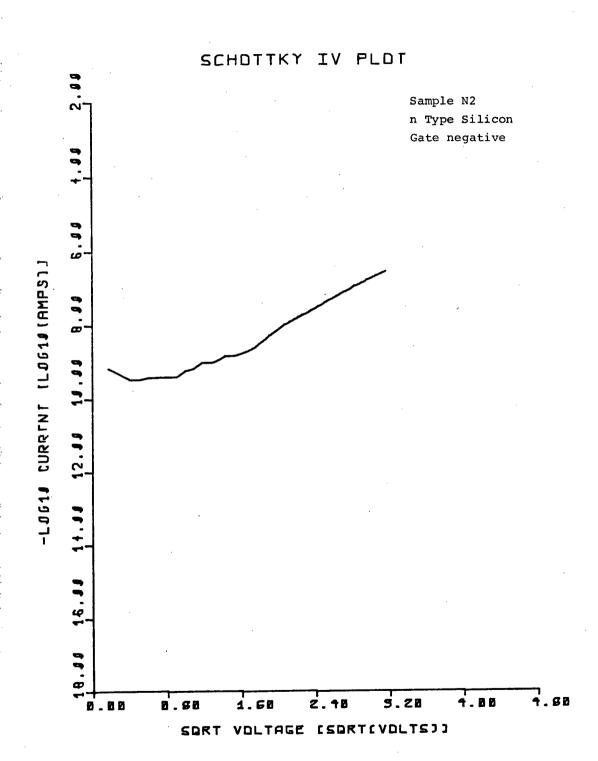

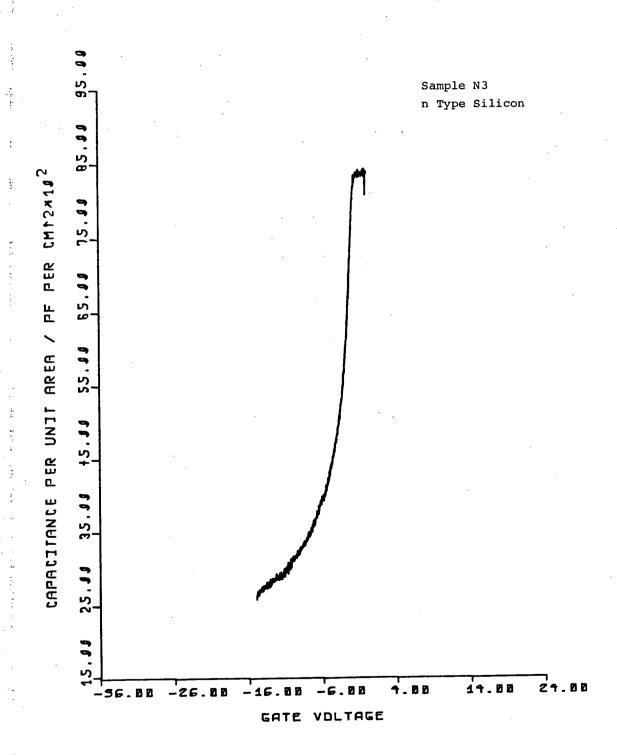

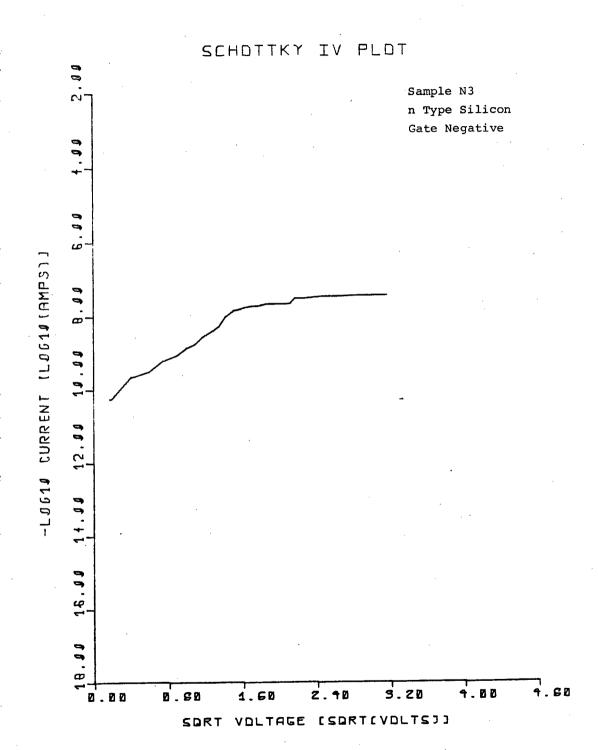

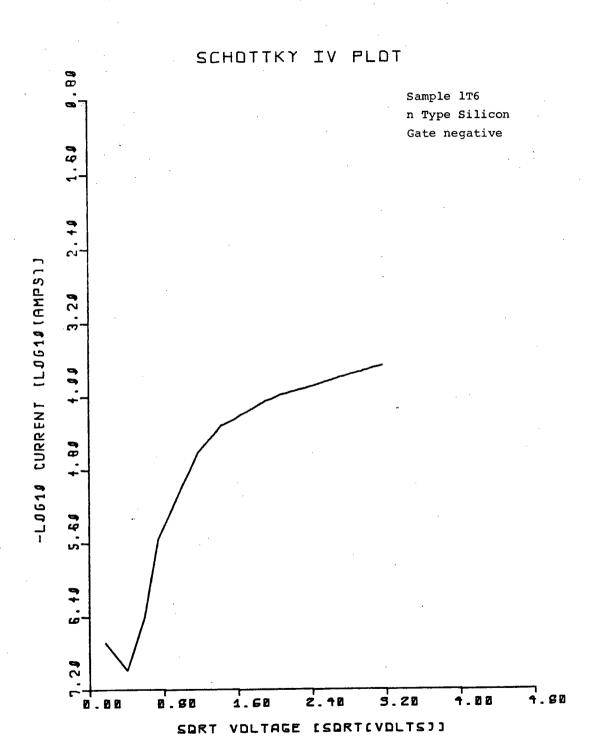

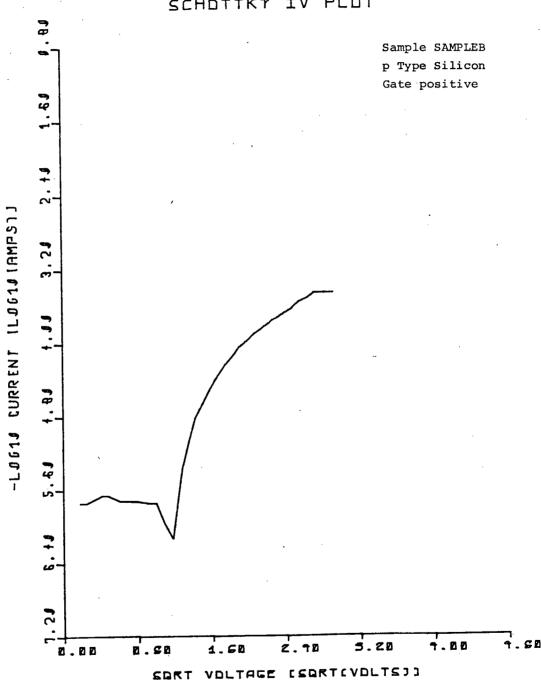

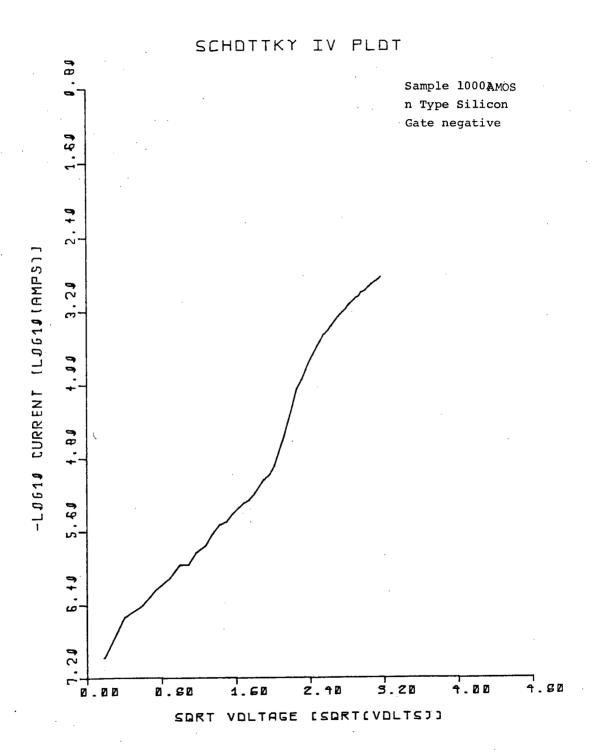

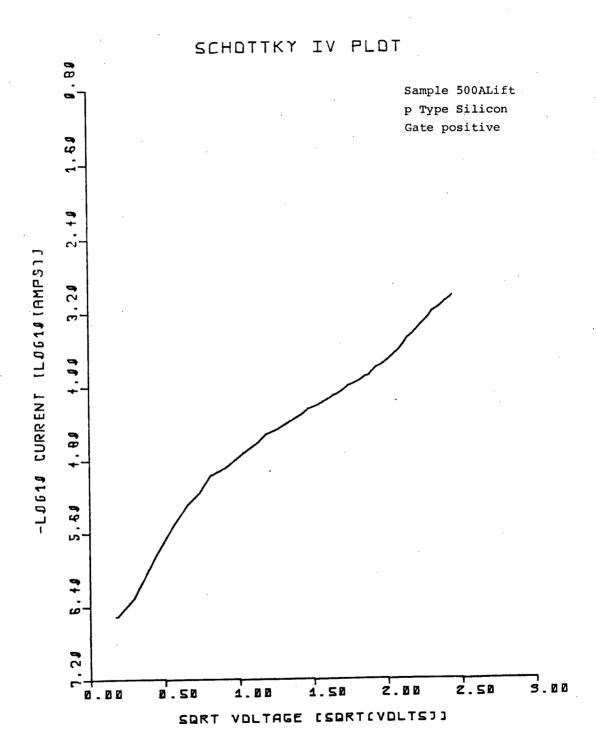

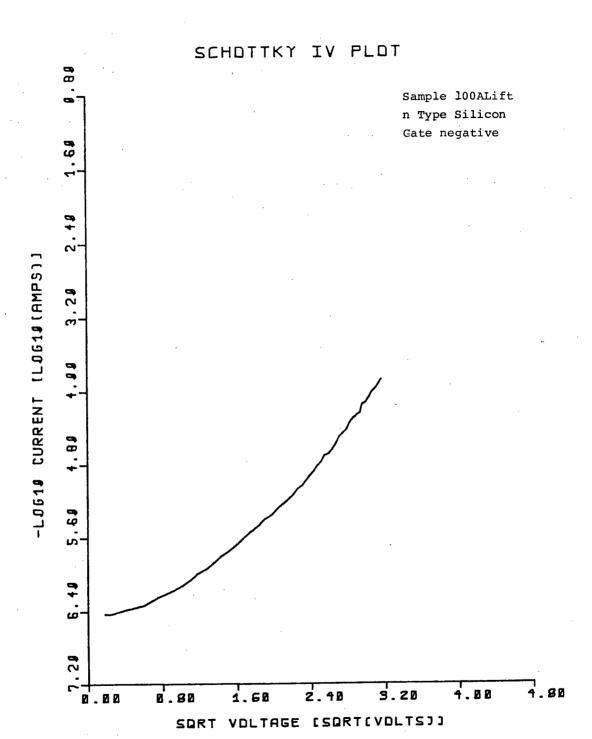

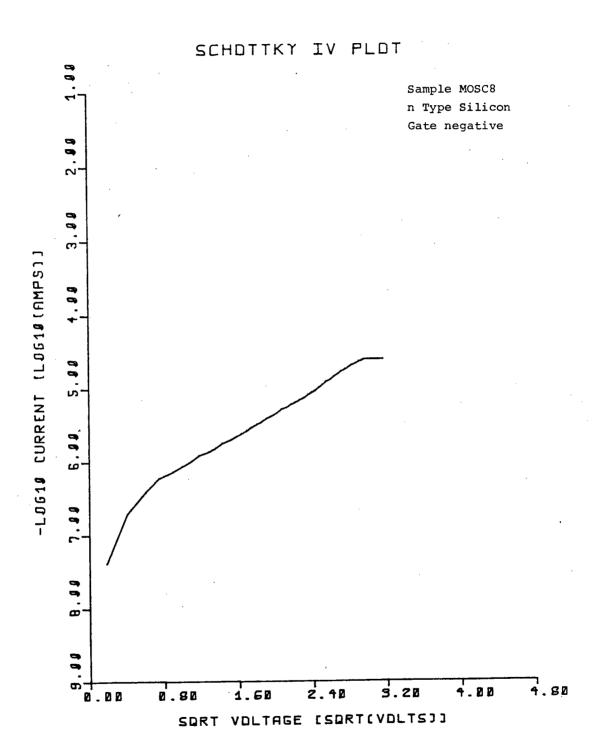

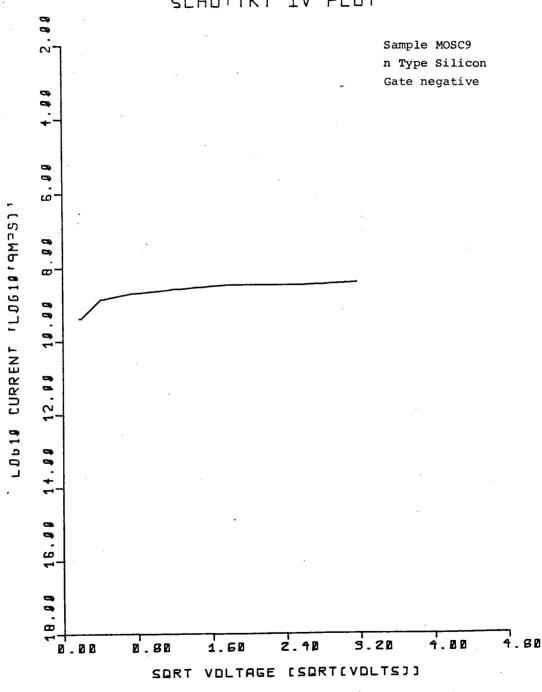

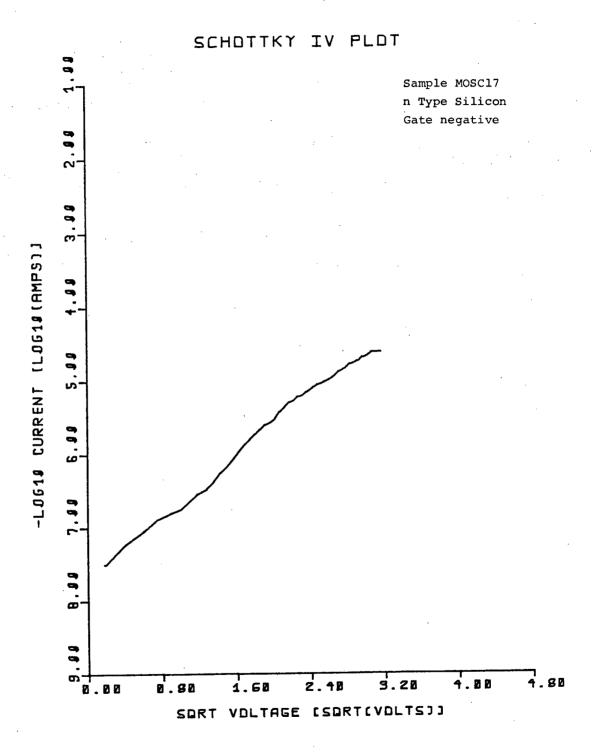

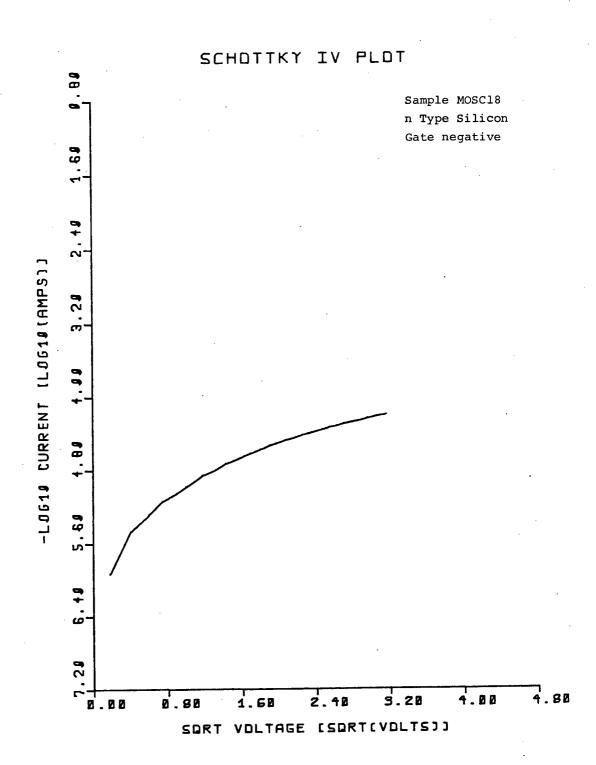

| 5.3 I-V MEASUREMENTS81                                                       |

| 5.4 HILLOCK FORMATION INVESTIGATION85                                        |

| 5.5 DISCUSSION OF RESULTS93                                                  |

| 5.5.1 ELLIPSOMETRY93                                                         |

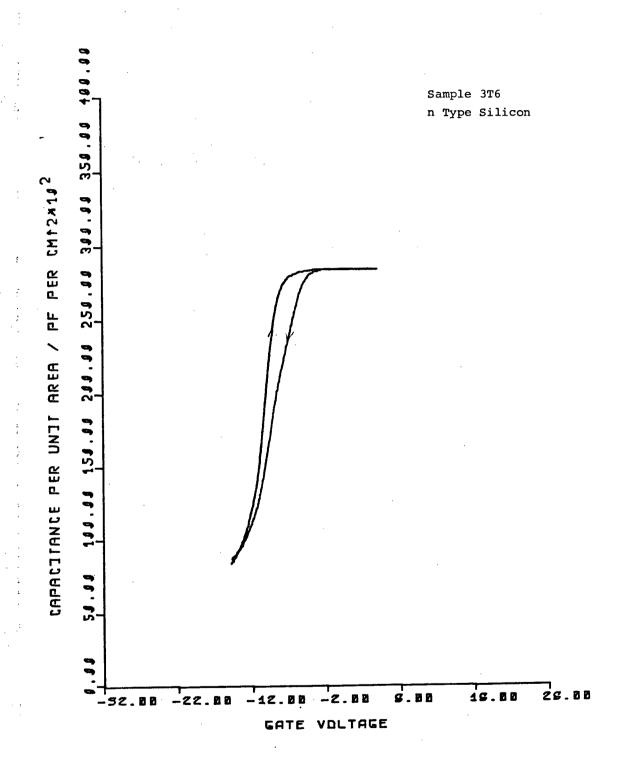

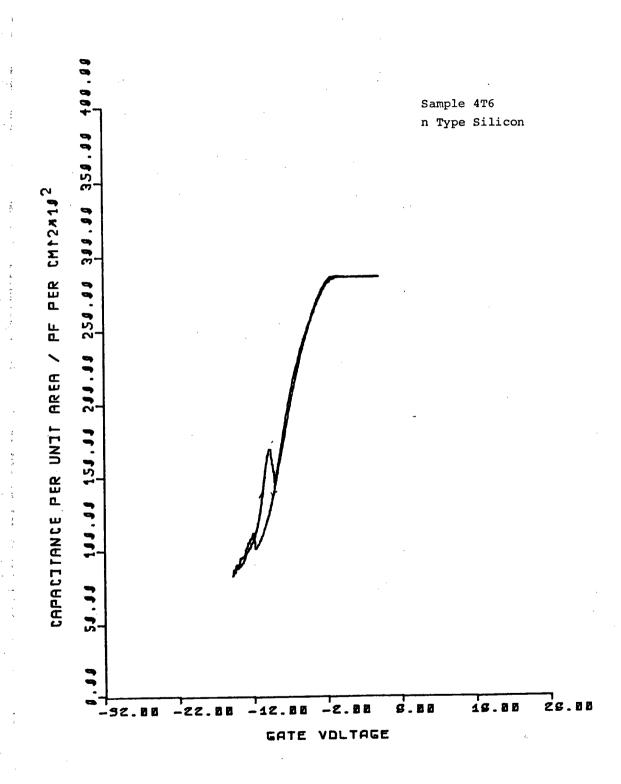

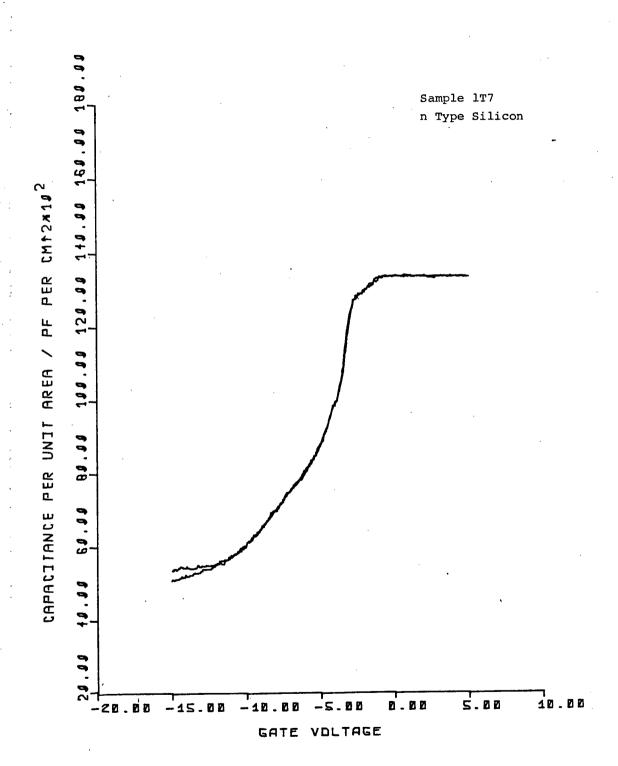

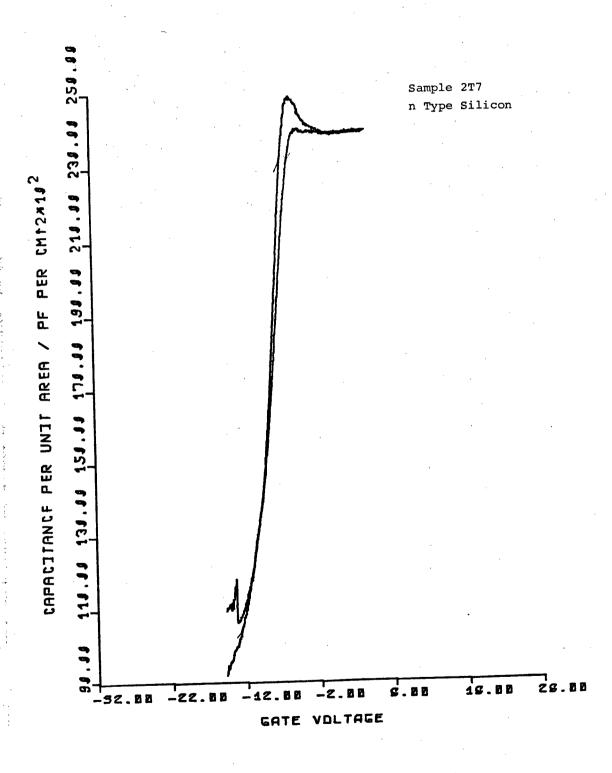

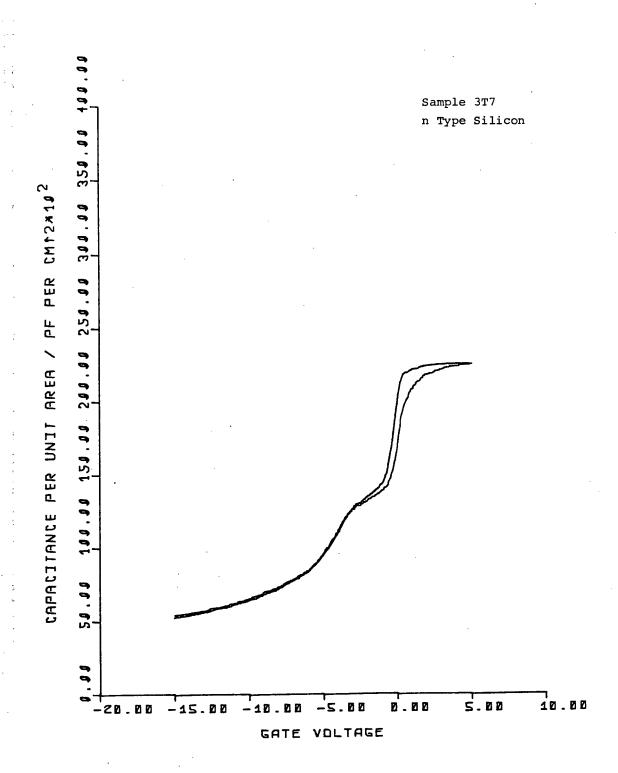

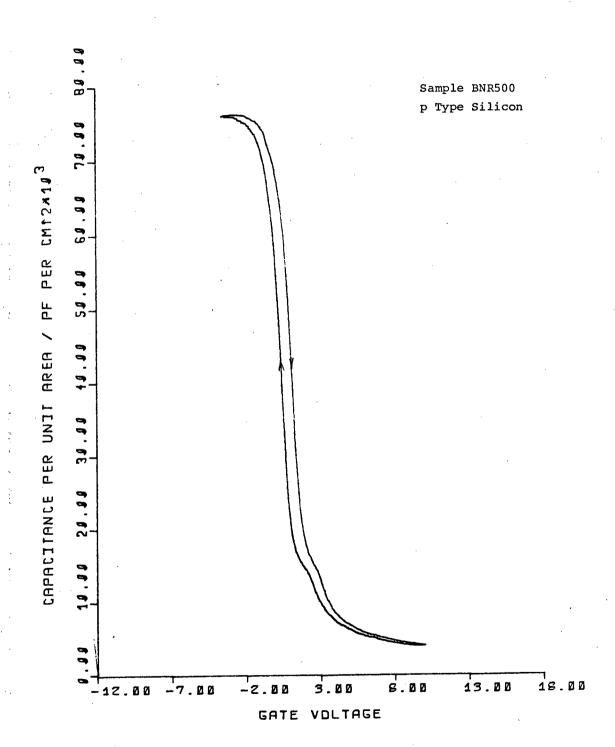

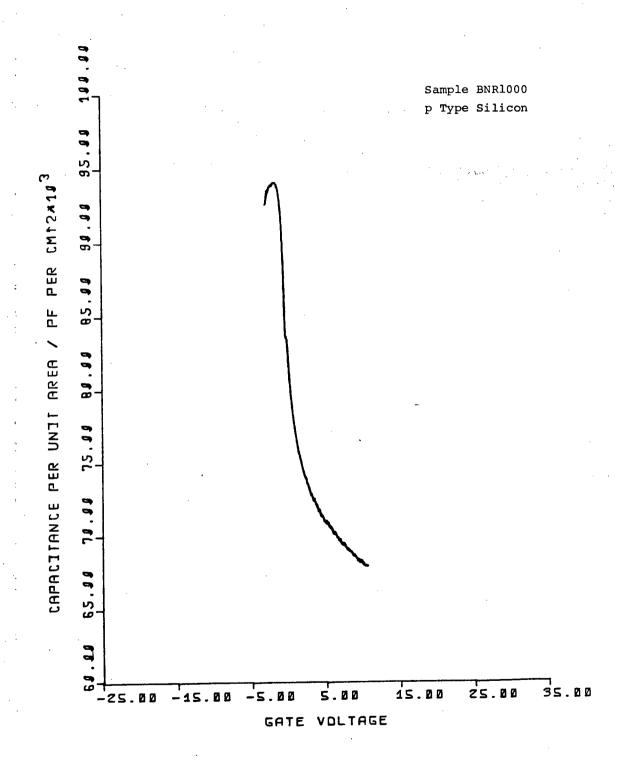

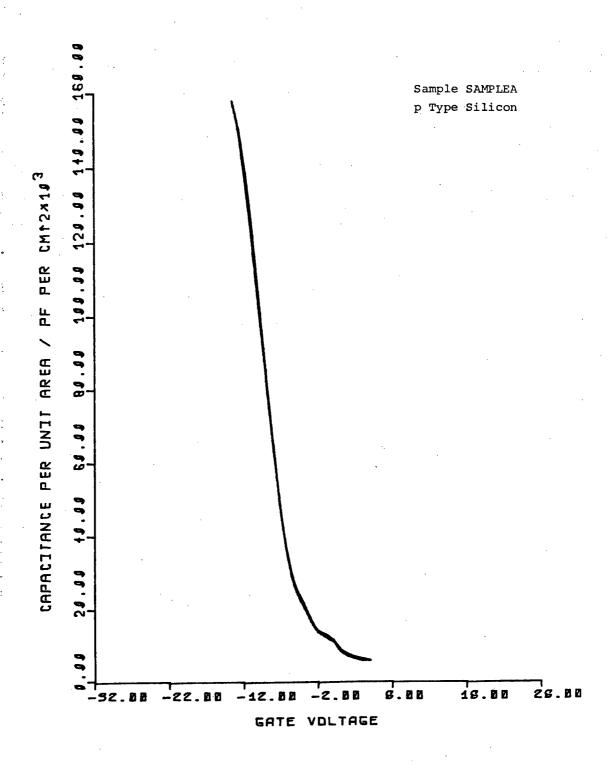

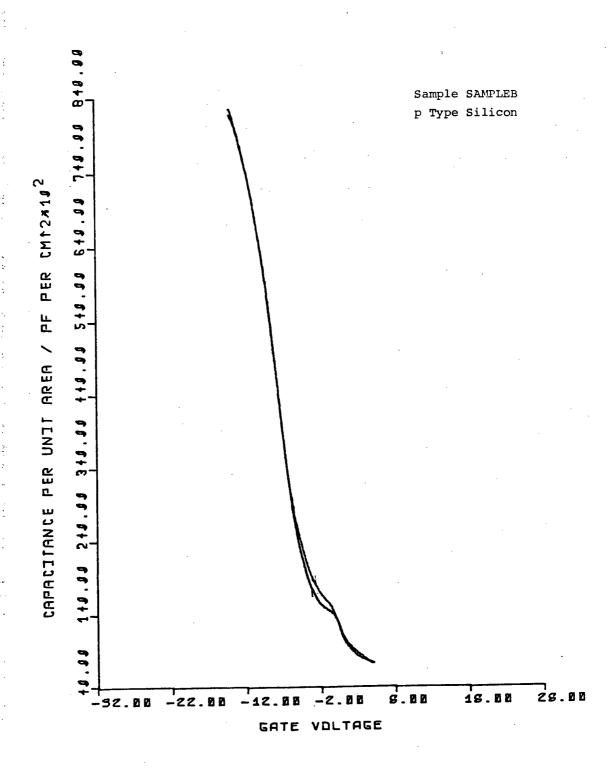

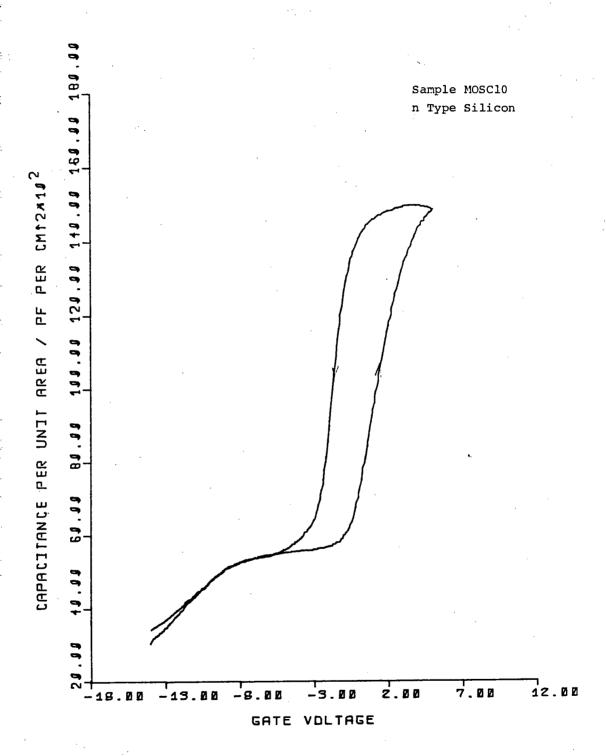

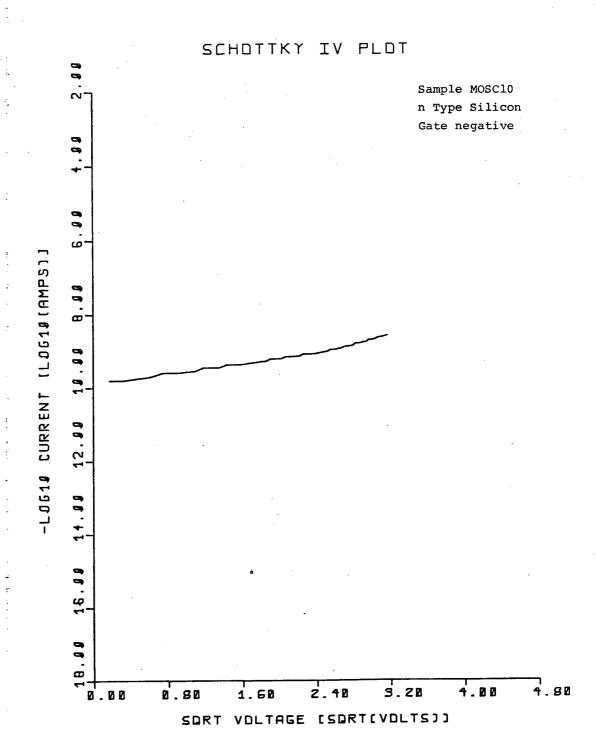

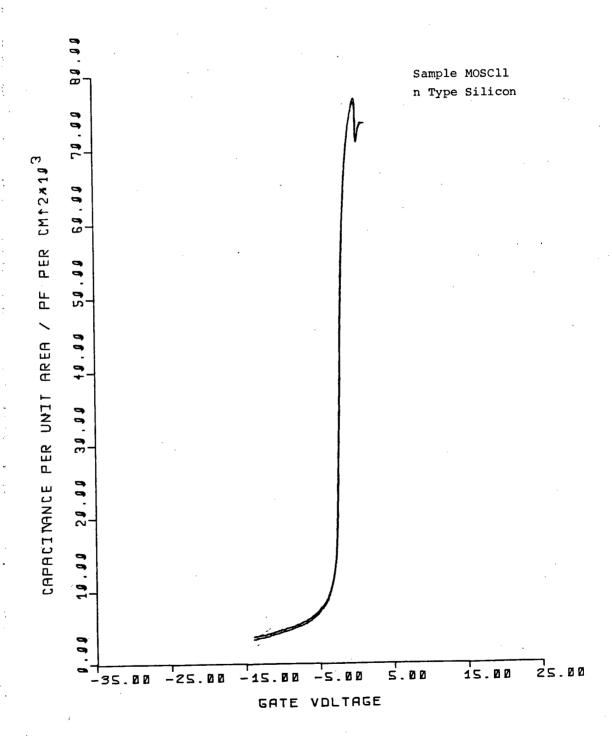

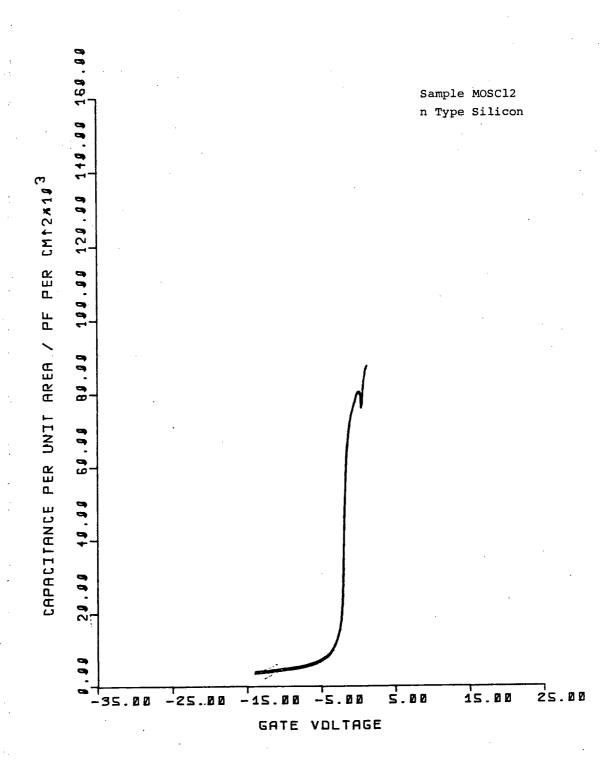

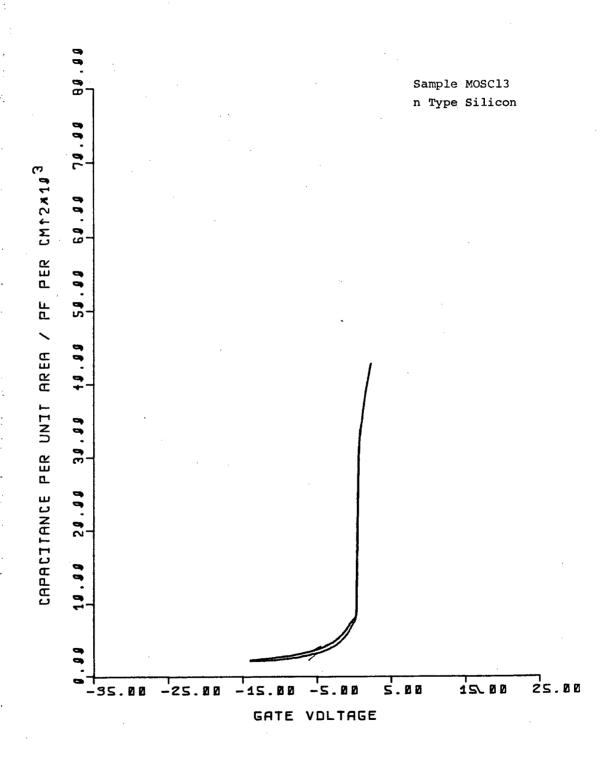

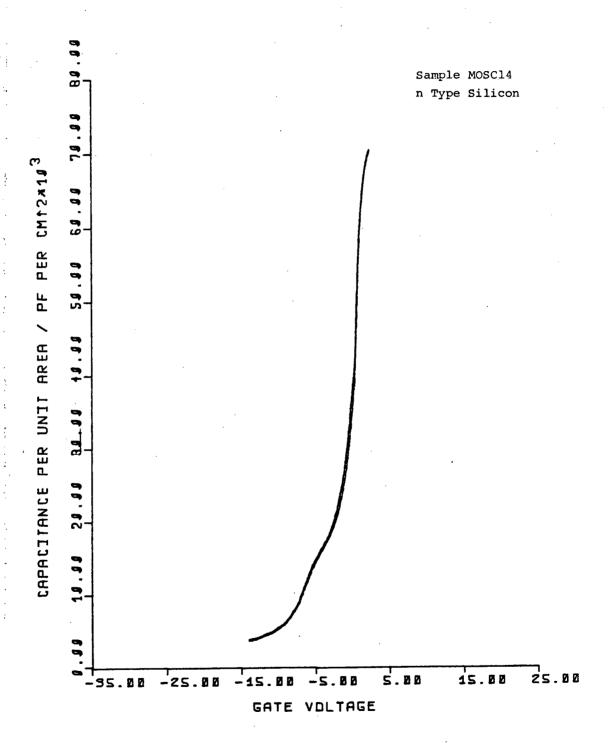

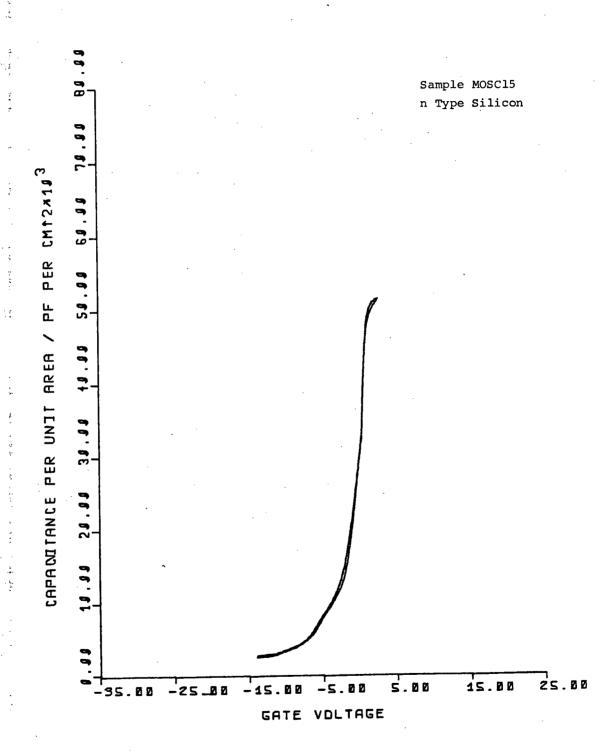

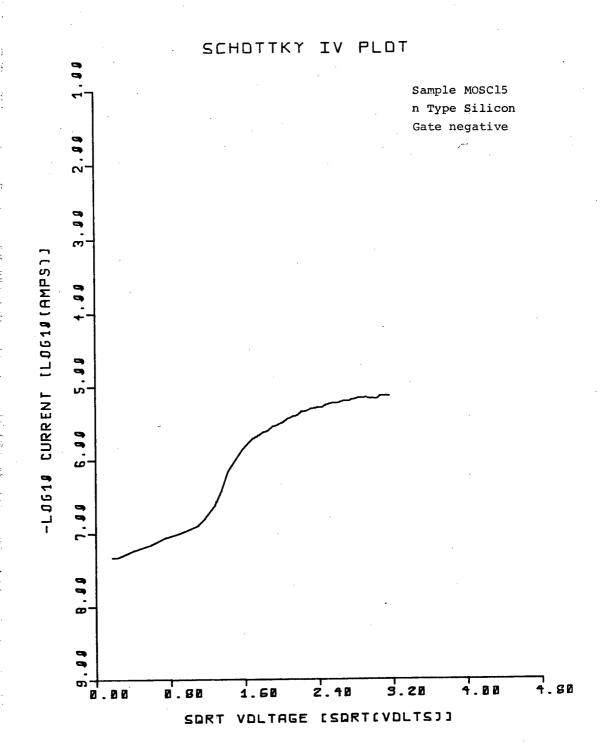

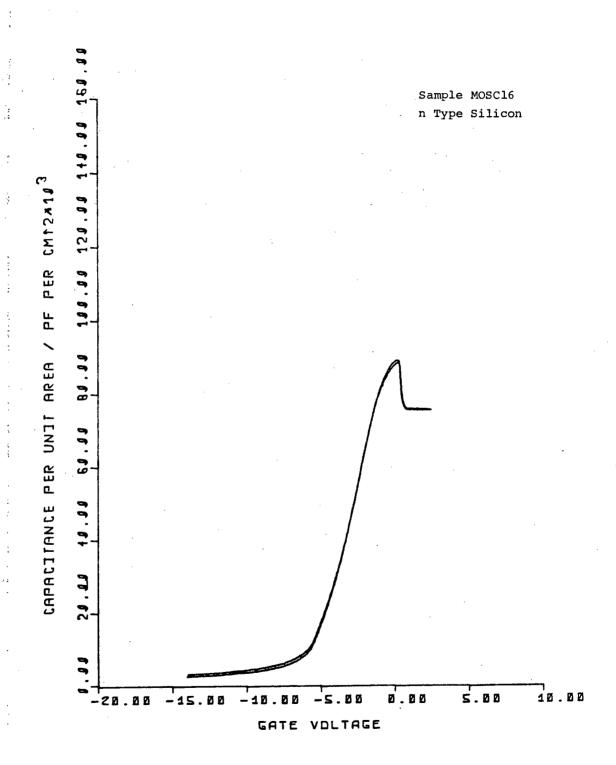

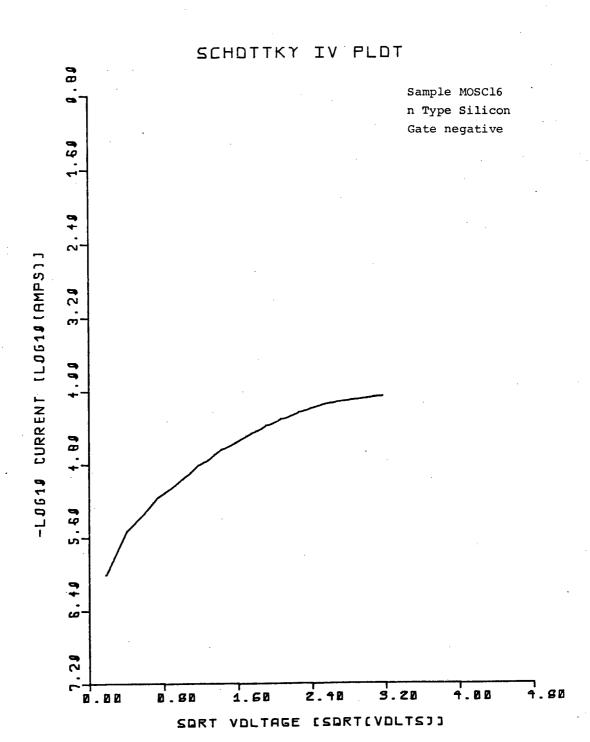

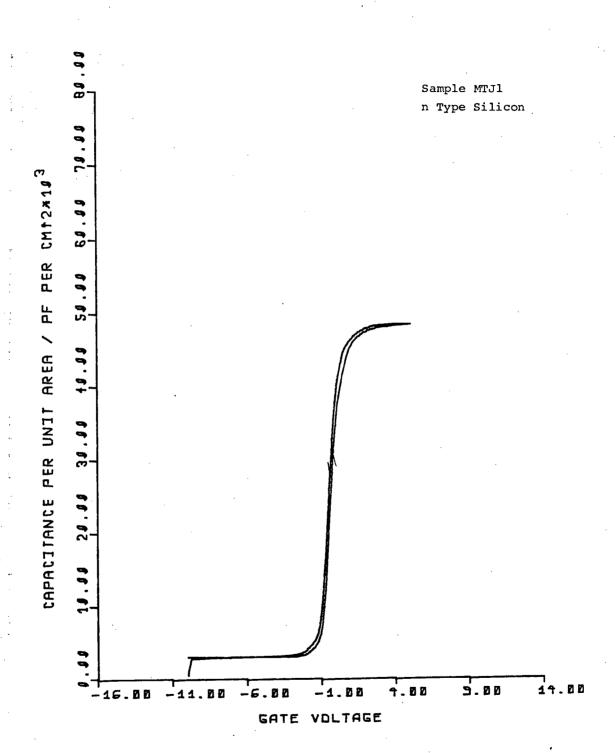

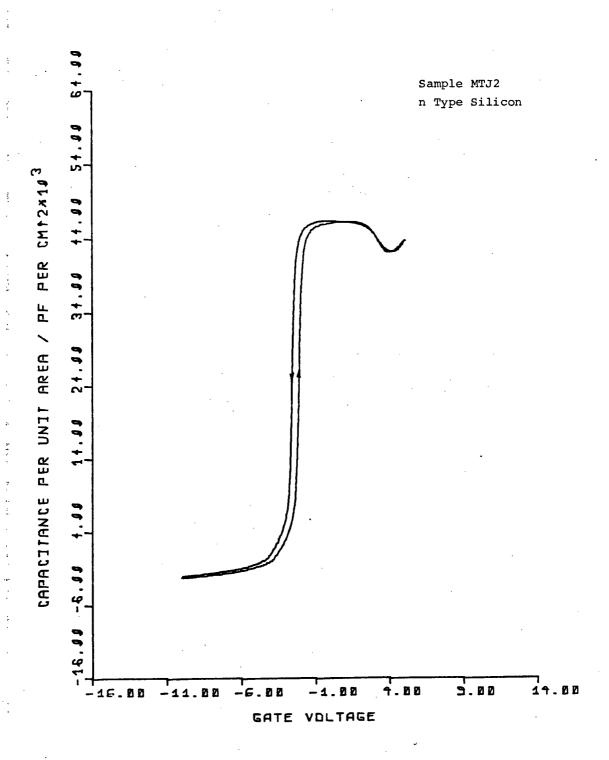

| 5.5.2 C-V CURVES99                                                           |

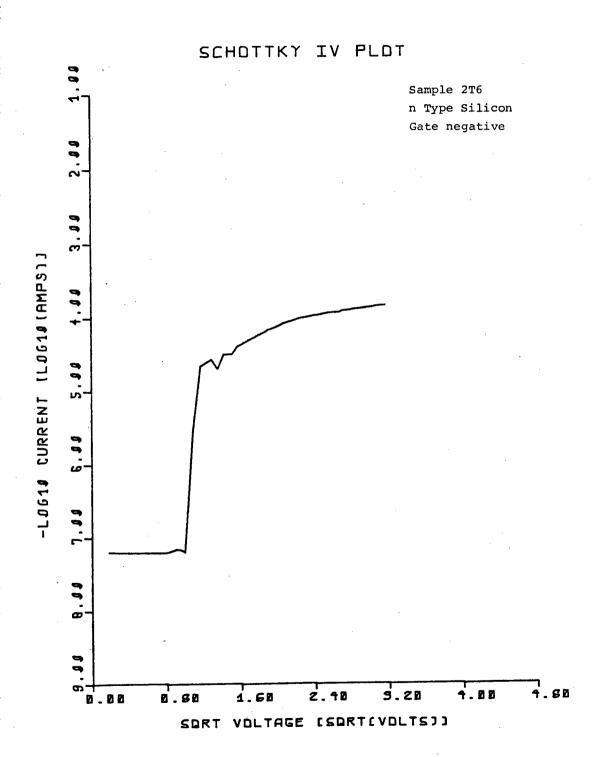

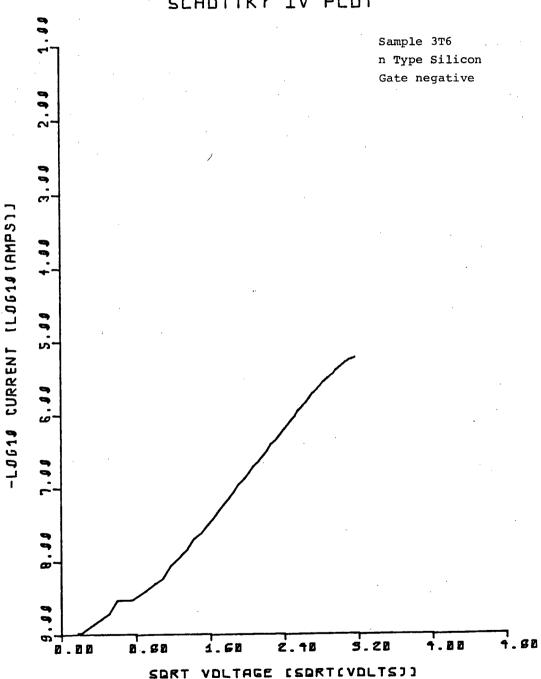

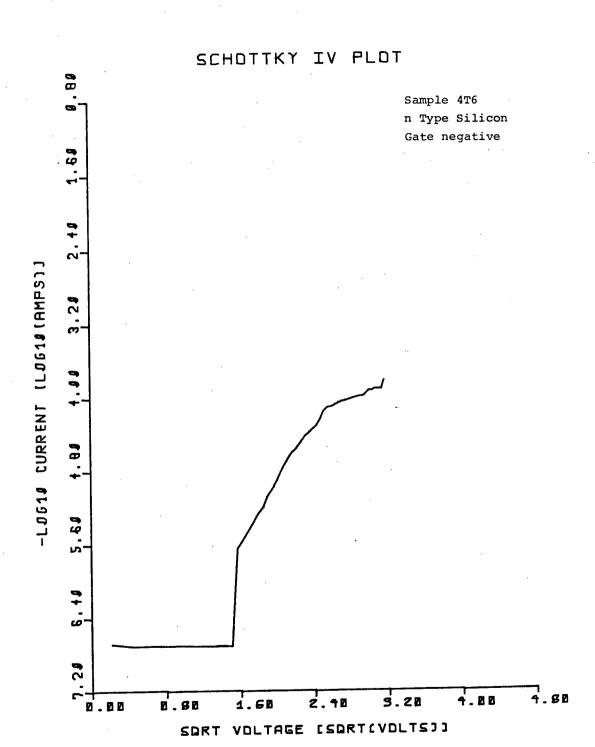

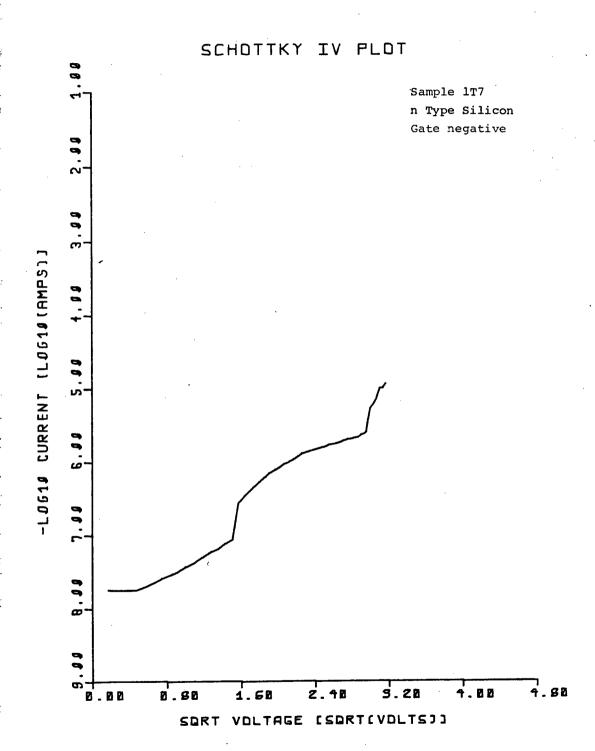

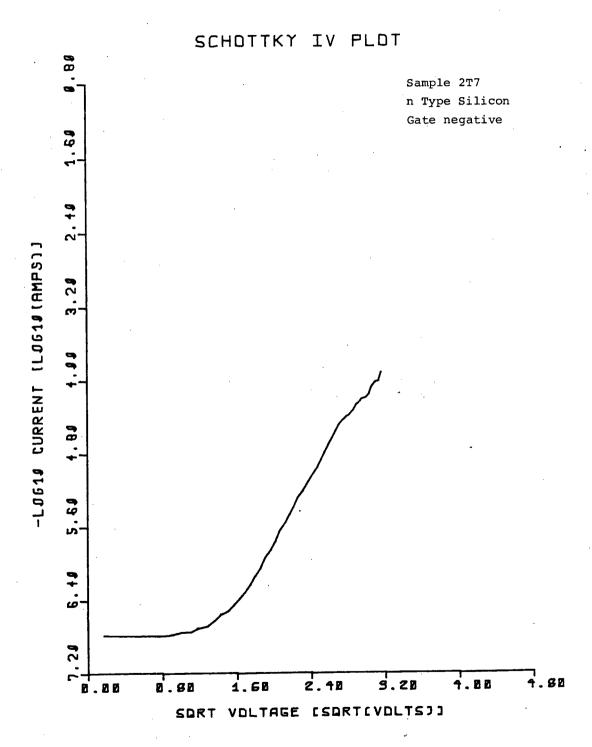

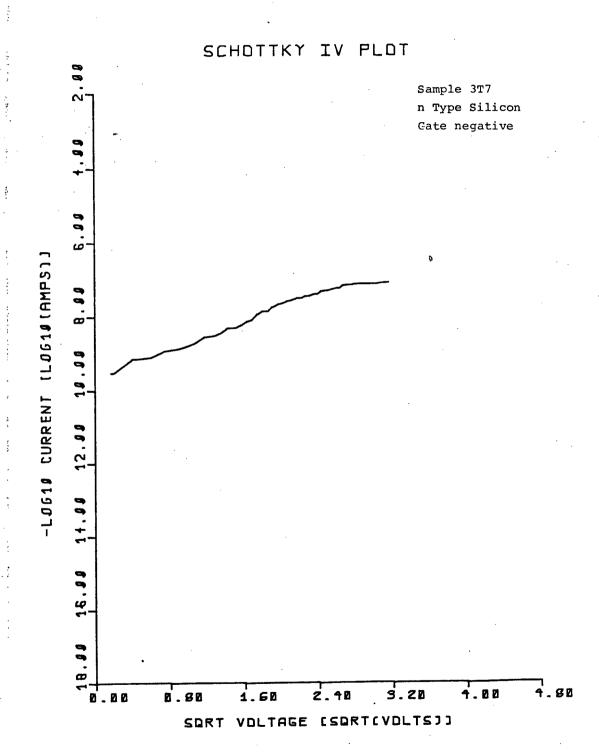

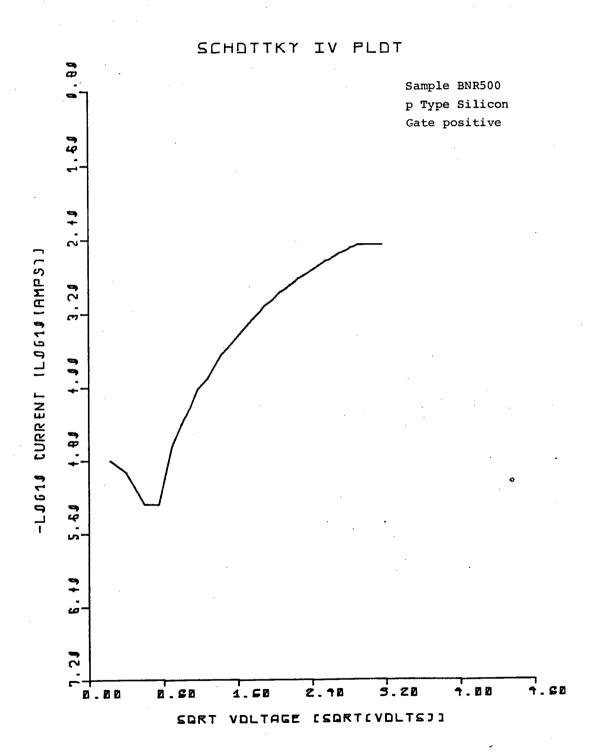

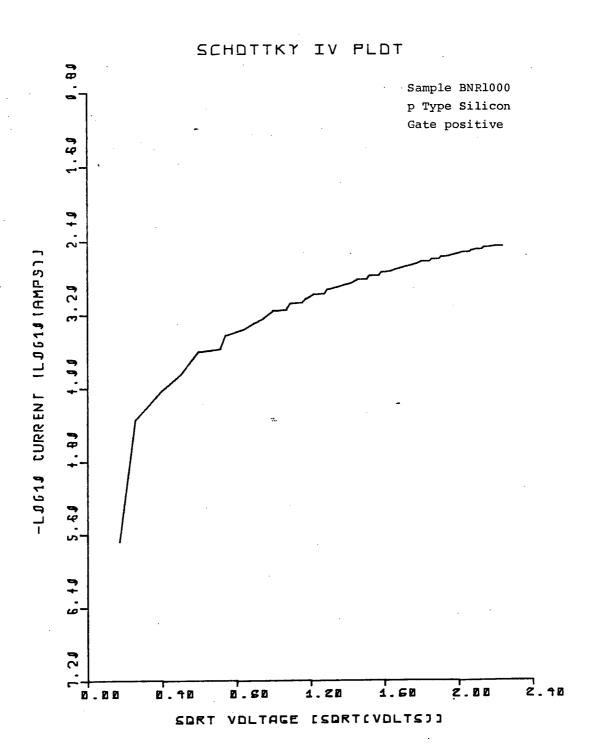

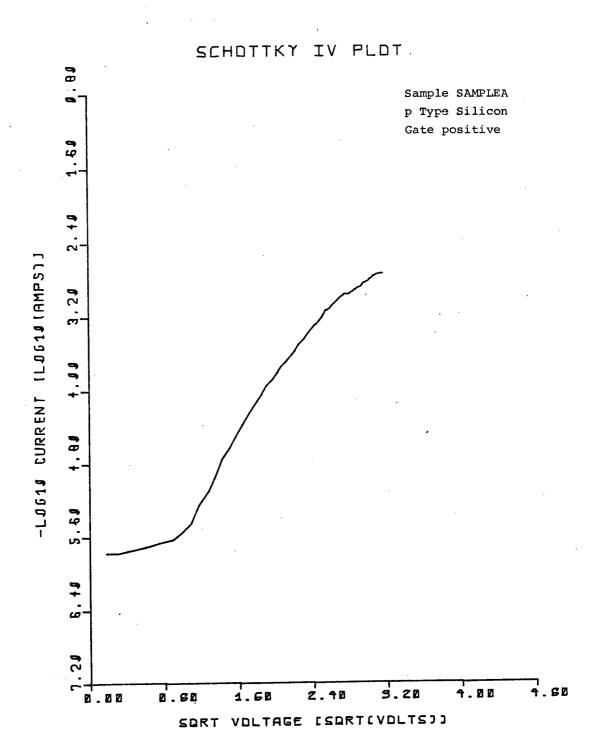

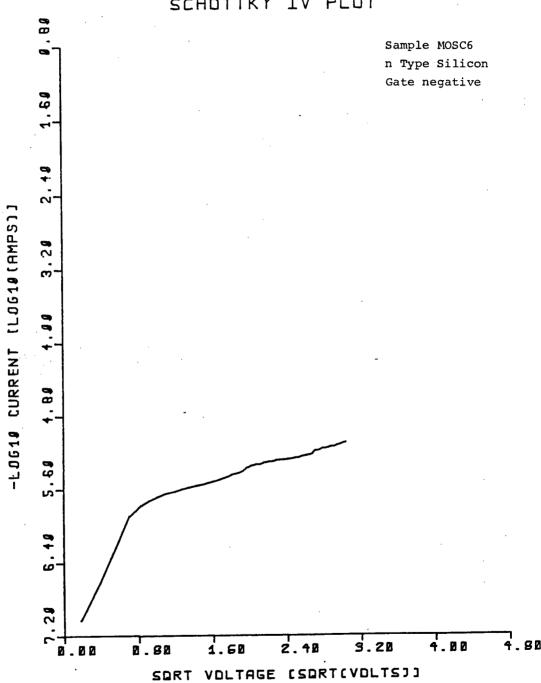

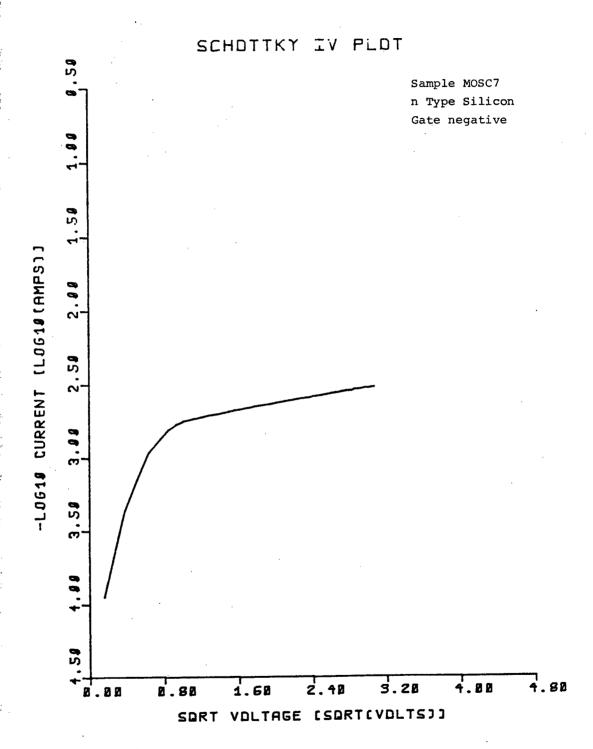

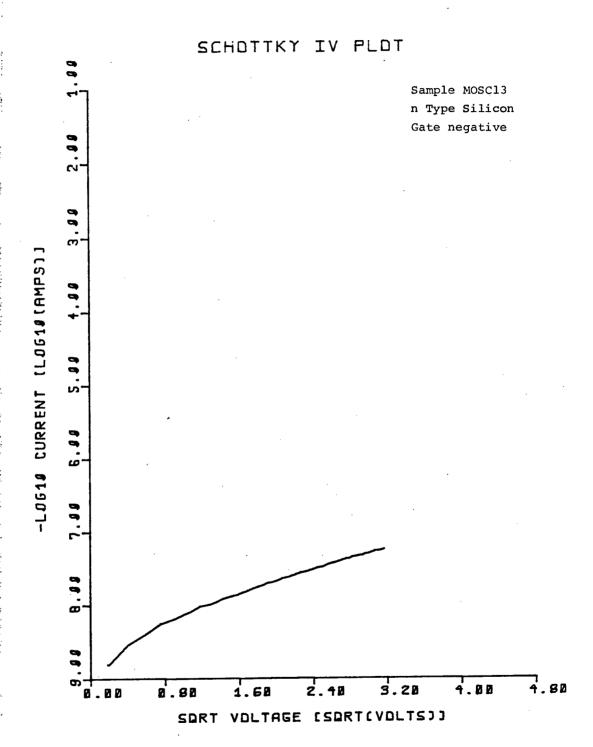

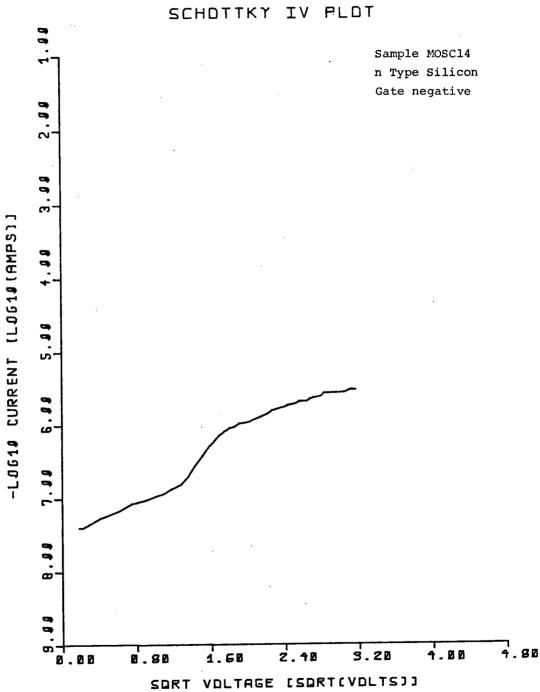

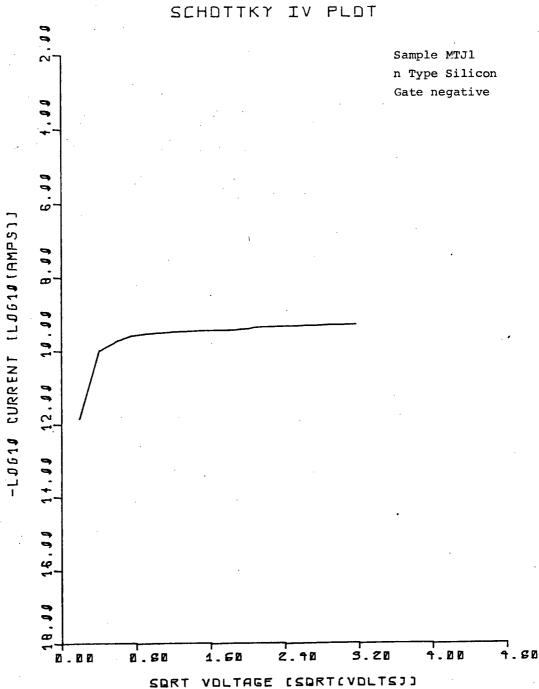

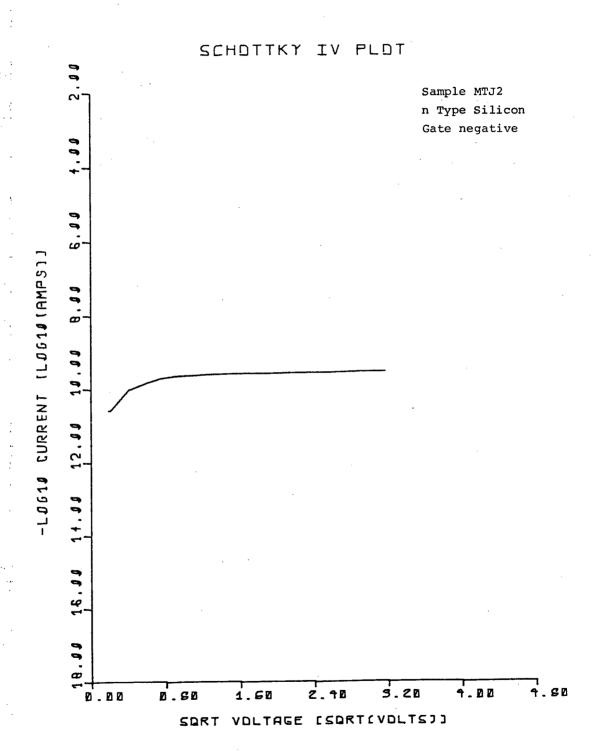

| 5.5.3 I-V CURVES114                                                          |

| 5.6 INTERFACIAL OXIDATION MOS CAPACITORS121                                  |

| CHAPTER 6                                                                    |

| FABRICATION AND PROCESSING OF MTAOS FIELD EFFECT                             |

| TRANSISTORS123                                                               |

| 6.1 SHEET RESISTIVITY DETERMINATION125              |

|-----------------------------------------------------|

| 6.2 SILICON THERMAL OXIDATION126                    |

| 6.3 THICK OXIDE PHOTOLITHOGRAPHY127                 |

| 6.4 BORON PREDEPOSITION128                          |

| 6.5 BORON DRIVE-IN128                               |

| 6.6 GATE PHOTOLITHOGRAPHY129                        |

| 6.7 THIN OXIDE PROCESS SIMULATION USING SUPREM129   |

| 6.8 PREPARATION OF DEVIĆE WAFERS FOR ANODIZATION132 |

| 6.9 PEROXIDE-ACID CLEANING OF ALL WAFERS133         |

| 6.10 ALUMINIUM EVAPORATION133                       |

| 6.11 PHOTOLITHOGRAPHY FOR LIFTOFF                   |

| 6.12 MICROSCOPE EXAMINATION AFTER LIFTOFF134        |

| 6.13 DETERMINATION OF THE SWELLING FACTOR S134      |

| 6.14 PRELIMINARY RF SPUTTERING OF TANTALUM136       |

| 6.15 PRELIMINARY THERMAL OXIDATION                  |

| 6.16 PRELIMINARY ANODIC OXIDATION138                |

| 6.17 RF SPUTTERING OF TANTALUM139                   |

| 6.18 THERMAL OXIDATION OF TANTALUM139               |

| 6.19 ANODIC OXIDATION OF TANTALUM140                |

| 6.20 PRELIMINARY MICROSCOPE EXAMINATION143          |

| 6.21 LIFTOFF PATTERNING143                          |

| 6.22 MICROSCOPE EXAMINATION AFTER LIFTOFF144        |

| 6.23 PEROXIDE-ACID CLEANING145                      |

| 6.24 SOURCE AND DRAIN THIN GATE OXIDE REMOVAL145    |

| 6.25 MICROSCOPE PHOTOGRAPHY145                      |

| 6.26 ALUMINIUM DEPOSITION FOR CONTACTS146           |

| 6.27 DRAIN AND SOURCE CONTACT PHOTOLITHOGRAPHY147   |

| 6.28 ETCHING ON BACK OF WAFER AND Au DEPOSITION147  |

| 6.29 FINAL MICROSCOPE EXAMINATION148                                  |

|-----------------------------------------------------------------------|

| CHAPTER 7                                                             |

| RESULTS AND MEASUREMENTS ON MTAOS FIELD EFFECT                        |

| TRANSISTORS154                                                        |

| 7.1 TESTING AND MEASUREMENT PROCEDURE154                              |

| 7.2 DISCUSSION OF RESULTS163                                          |

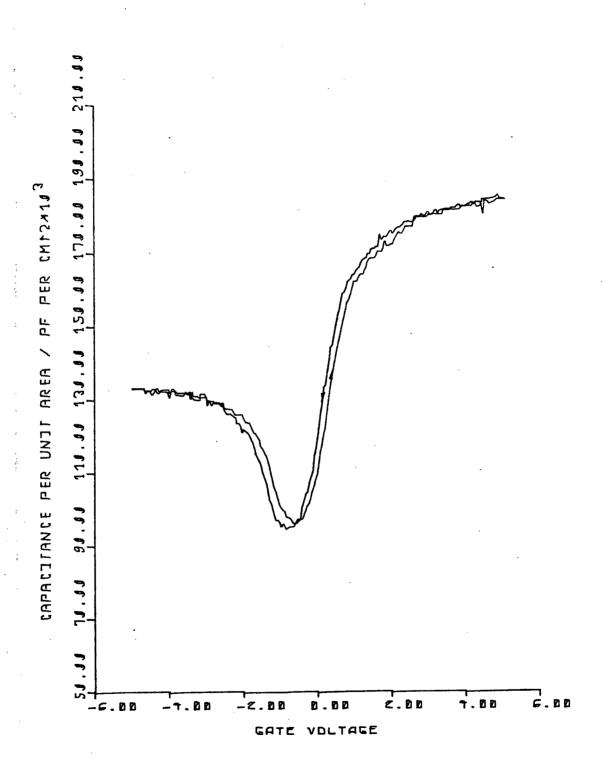

| 7.2.1 C-V CURVES ON DOUBLE DIELECTRIC INSULATOR .163                  |

| 7.2.2 I-V CURVES ON THE DOUBLE DIELECTRIC GATE                        |

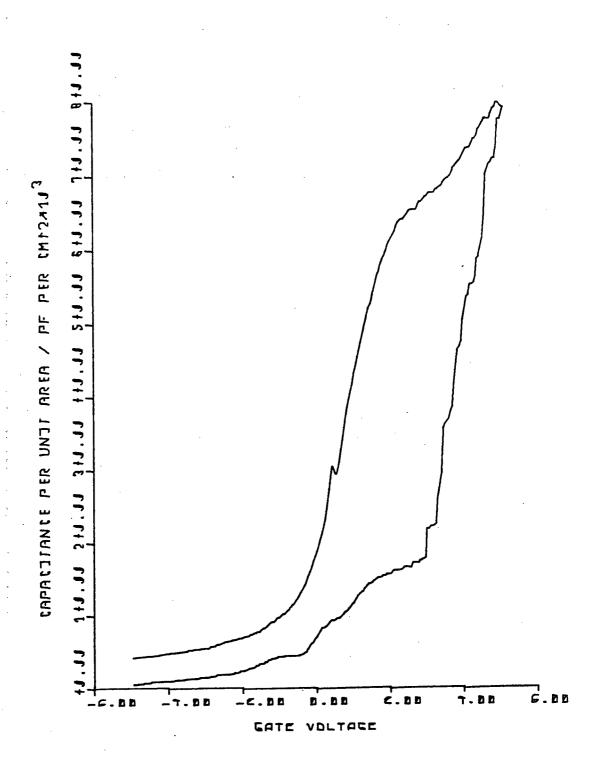

| INSULATOR169                                                          |

| 7.2.3 GATE THRESHOLD VOLTAGE169                                       |

| 7.2.4 THE OUTPUT CURVES170                                            |

| 7.2.5 THE TRANSFER CURVES173                                          |

| 7.2.6 PULSE RESPONSE OF THE DD MOSFETs174                             |

| 7.2.7 SPICE SIMULATION OF MOSFET CHARACTERISTICS 175                  |

| 7.3 DOUBLE DIELECTRIC MOSFET EQUIVALENT CIRCUIT181                    |

| CHAPTER 8                                                             |

| SUMMARY AND CONCLUSIONS183                                            |

| REFERENCES187                                                         |

| APPENDIX I                                                            |

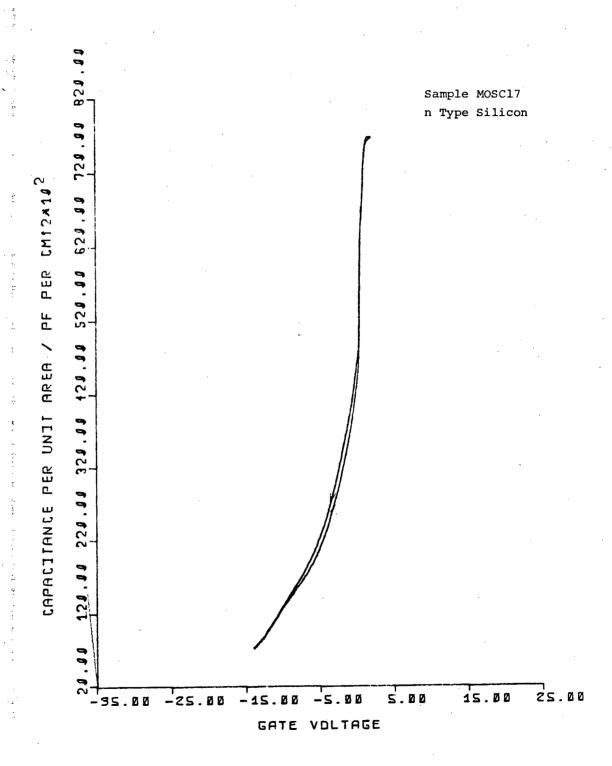

| C-V AND I-V CURVES OF MOS CAPACITORSSee Addendum under separate cover |

| APPENDIX II                                                           |

| COMPUTER SOURCE PROGRAMS195                                           |

| APPENDIX III                                                          |

| LABORATORY PROCESSING DETAILS212                                      |

| APPENDIX IV                                                           |

| SPICE AND SUPPEM SIMULATION RESULTS                                   |

# LIST OF TABLES

| 3.1 Double Dielectric MOSFET Parameters45                          |

|--------------------------------------------------------------------|

| 3.2 Single Dielectric MOSFET Parameters47                          |

| 3.3 MOS Capacitor Insulator Figure Of Merit49                      |

| 4.1 Single Dielectric Thermal MOS Capacitors56                     |

| 4.2 Thermal Oxidation Of Tantalum On Silicon58                     |

| 4.3 Double Dielectric MOS Capacitors61                             |

| 4.4 Single Dielectric Anodic MOS Capacitors73                      |

| 4.5 Interfacial Oxidation Of Tantalum On Silicon75                 |

| 5.1 Sputtering Of Ta On Glass Samples88                            |

| 5.2 Oxide Thickness Determination By Ellipsometry99                |

| 5.3 Resume Of Thermal Oxide MOS-SD Capacitors C-V                  |

| Curves105                                                          |

| 5.4 Resume Of Thermal Oxide MOS-DD Capacitors C-V                  |

| Curves106                                                          |

| 5.5 Resume Of Anodic Oxide MOS-SD Capacitors C-V Curves            |

|                                                                    |

| 5.6 Calculated Relative Dielectric Constant Of Thermal             |

| Ta <sub>2</sub> O <sub>5</sub> 108                                 |

| 5.7 Calculated Relative Dielectric Constant Of Anodic              |

| Ta <sub>2</sub> O <sub>5</sub> 109                                 |

| 5.8 Flatband Voltage, Capacitance And Fixed Charge Of              |

| Single Dielectric Ta <sub>2</sub> O <sub>5</sub> MOS Capacitors110 |

| 5.9 Flatband Voltage, Capacitance And Fixed Charge Of              |

| Double Dielectric MOS Capacitors111                                |

| 5.10 Flatband Voltage, Capacitance And Fixed Charge Of             |

| Anodic Ta <sub>2</sub> O <sub>5</sub> MOS Capacitors112            |

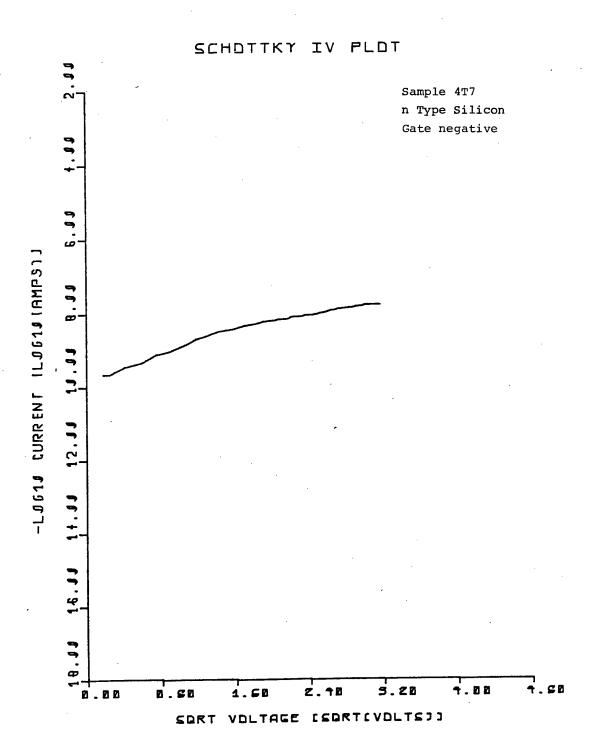

| 5.11 Resume Of Schottky I-V Curves And Calculated                  |

| Optical Value Of The Relative Dielectric Constant          |

|------------------------------------------------------------|

| For Thermal Ta <sub>2</sub> O <sub>5</sub> 116             |

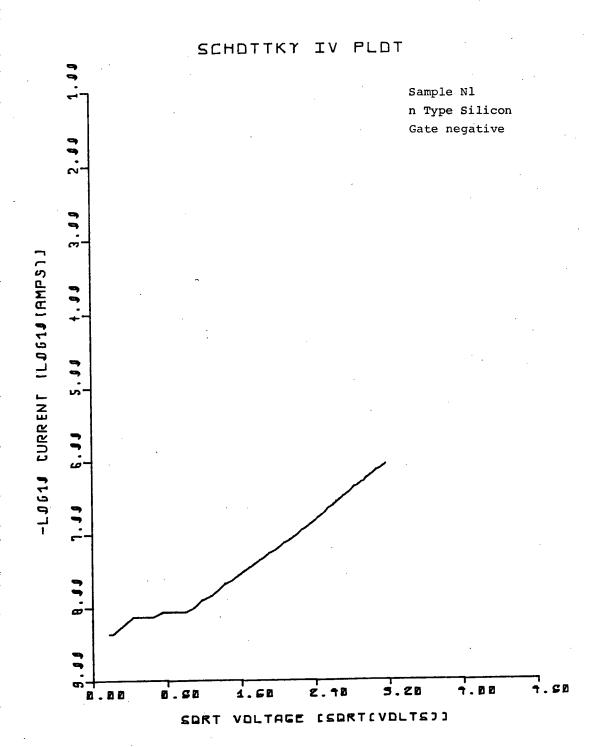

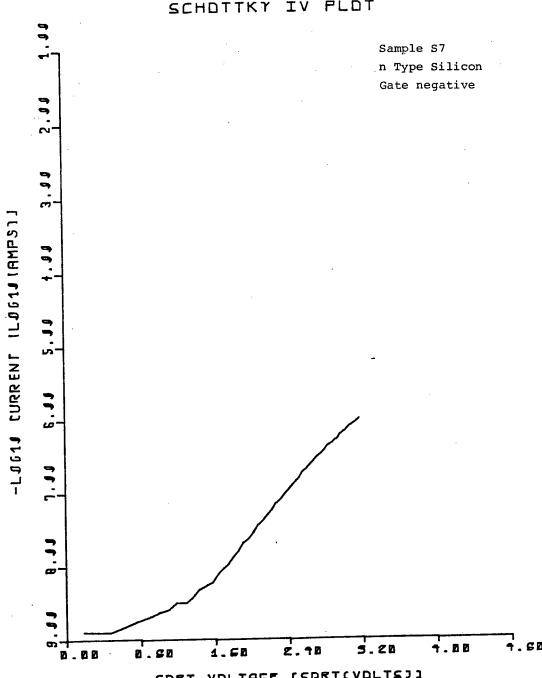

| 5.12 Resume Of Schottky I-V Curves And Calculated          |

| Optical Value Of The Relative Dielectric Constant          |

| For Anodic Ta <sub>2</sub> O <sub>5</sub> 117              |

| 5.13 Photoconduction In Tantalum Oxide MOS Capacitors .120 |

| 5.14 Interfacial Oxidation MOS Capacitors, C-V Results 122 |

| 5.15 Interfacial Oxidation MOS Capacitors, I-V Results 122 |

| 6.1 Device Substrate Marking And Measured Resistivity .126 |

| 6.2 SUPREM Simulation Results130                           |

| 6.3 Dry Thermal Oxidation Of SiO <sub>2</sub> 131          |

| 7.1 Summary Of Double Dielectric MOSFET Characteristics    |

|                                                            |

# LIST OF FIGURES

| 3.1 The General Double Dielectric Structure31                                       |

|-------------------------------------------------------------------------------------|

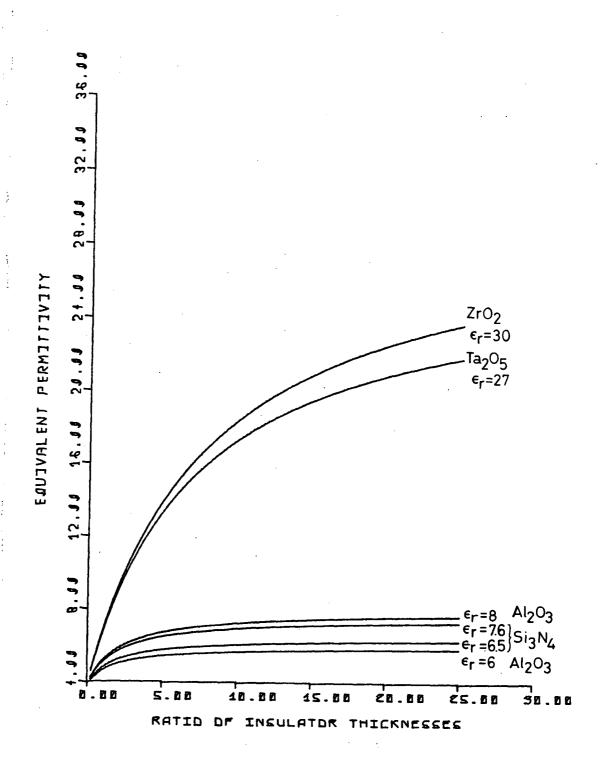

| 3.2 Equivalent Permittivity Of A Double Insulator44                                 |

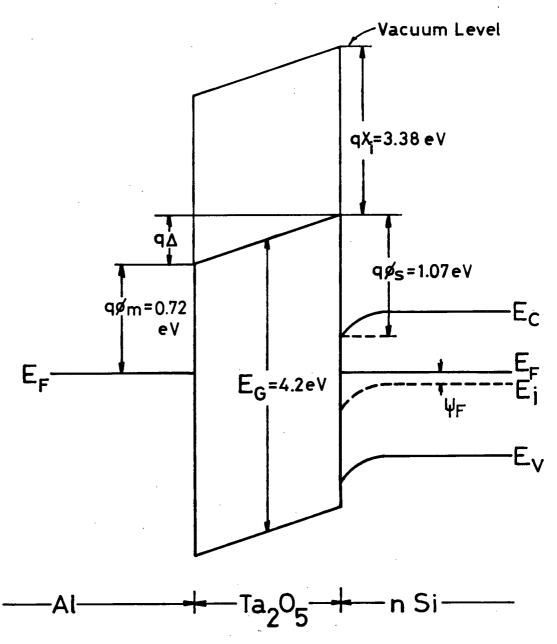

| 3.3 Energy Band Diagram Of The Al-Ta <sub>2</sub> O <sub>5</sub> -nSi Structure .50 |

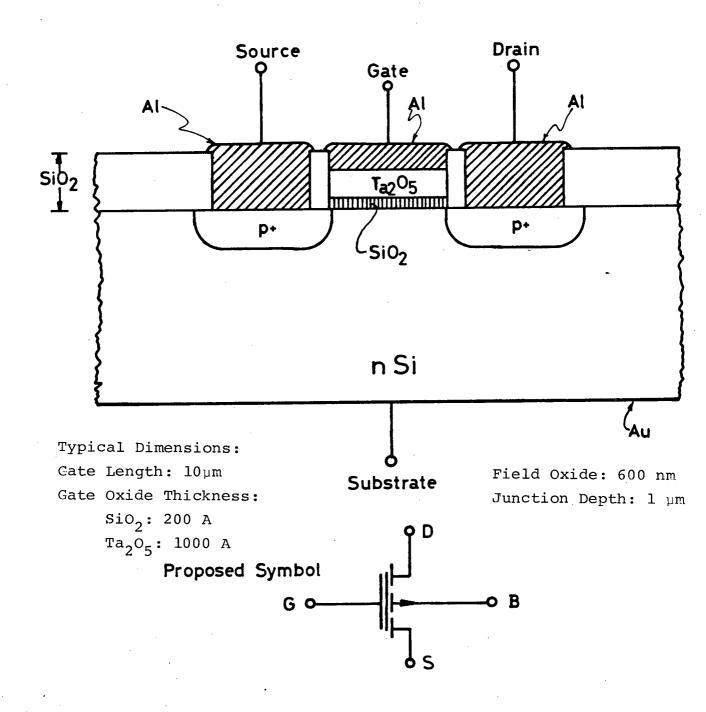

| 3.4 Double Dielectric MOSFET Structure53                                            |

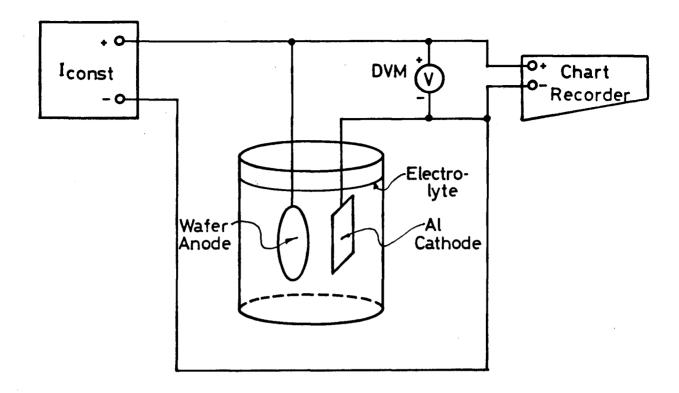

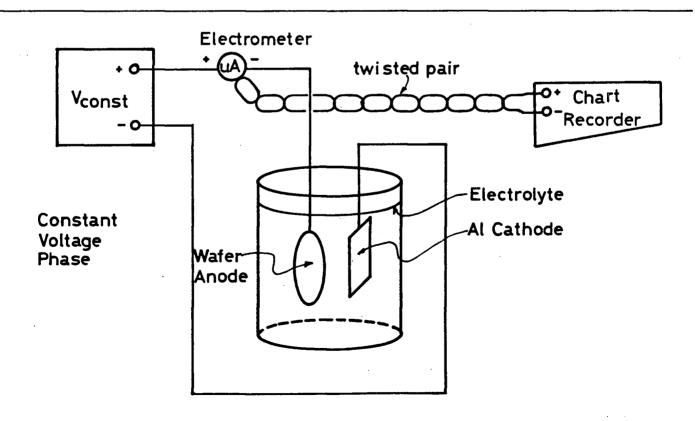

| 4.1 Anodization Cell And Equipment                                                  |

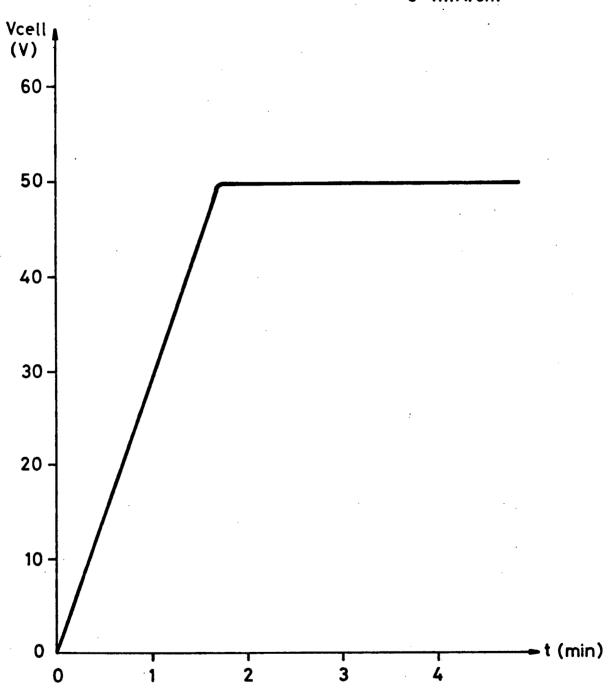

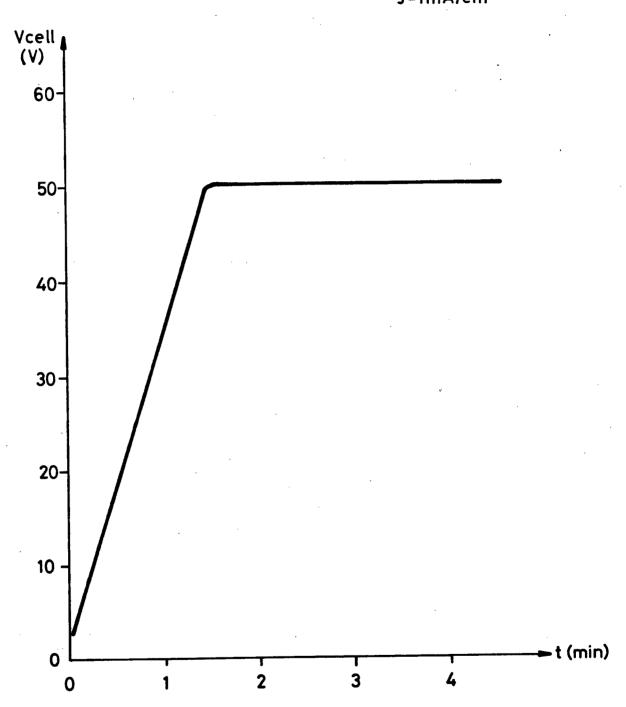

| 4.2 Anodization Cell Voltage Under Constant Current70                               |

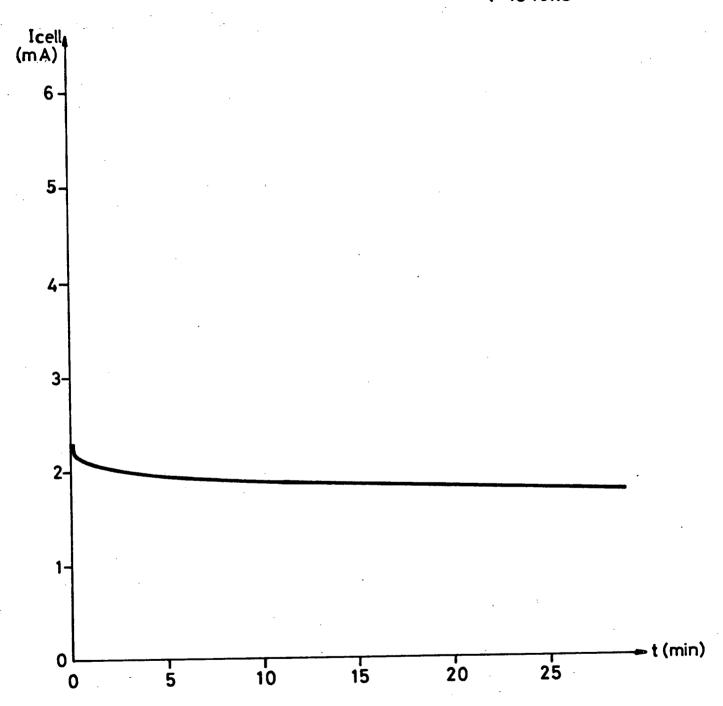

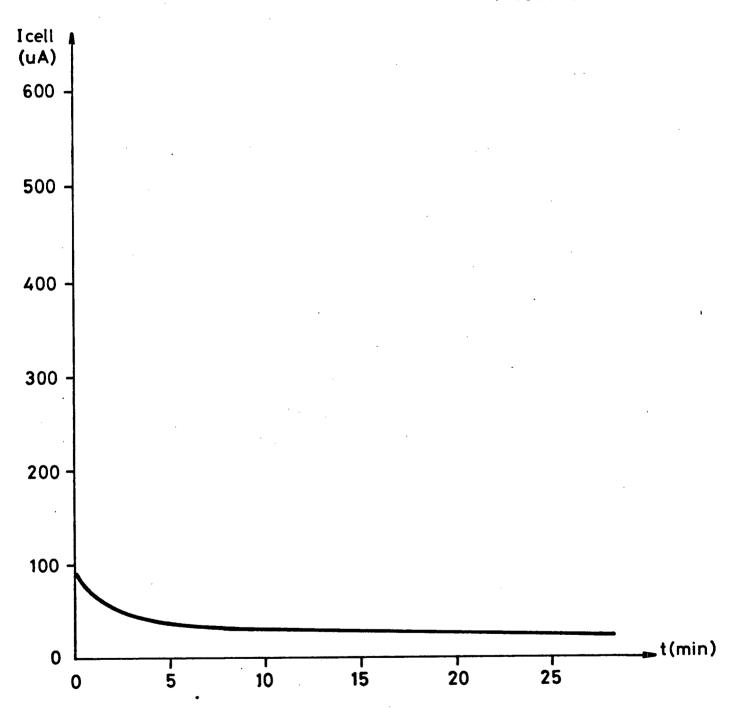

| 4.3 Anodization Cell Current Under Constant Voltage71                               |

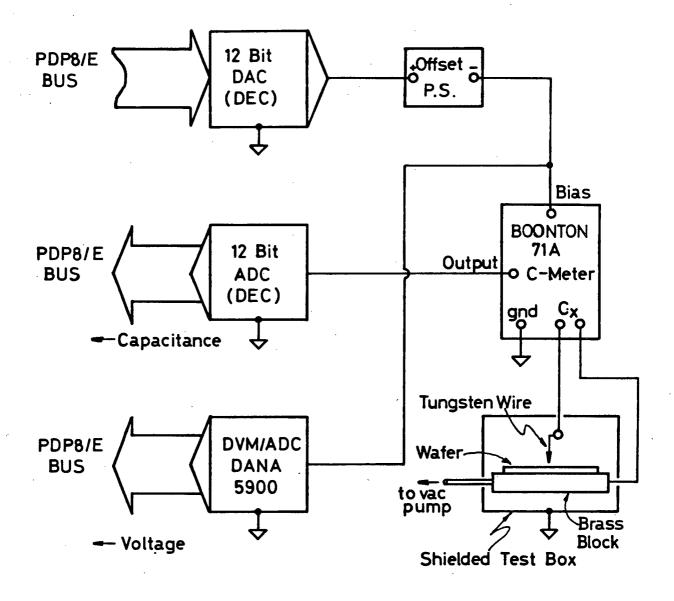

| 5.1 C-V Measuring System For MOS Capacitors79                                       |

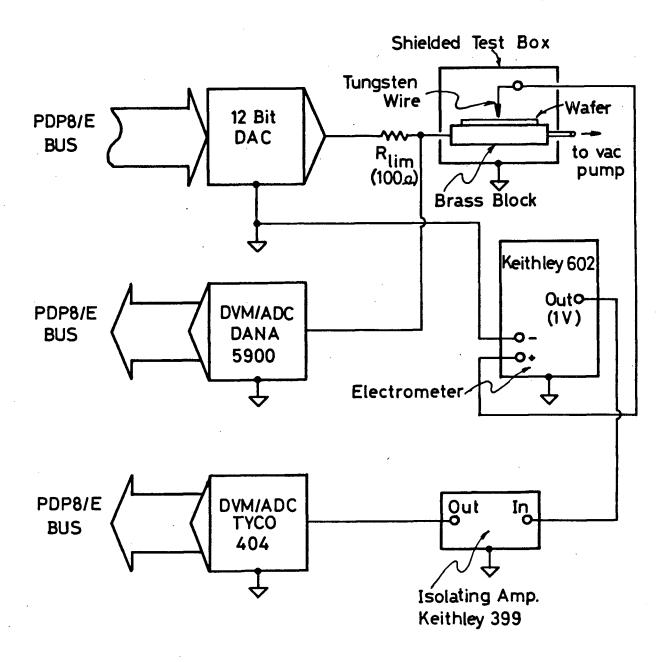

| 5.2 I-V Measuring System For MOS Capacitors83                                       |

| 5.3 Dark Field Photograph (560%), 500 A Ta RFS On                                   |

| Glass(sample G500)90                                                                |

| 5.4 Dark Field Photograph (560X), 500 A Ta MES On                                   |

| Silicon (sample BNR500)90                                                           |

| 5.5 Dark Field Photograph (140X), 200 A Ta RFS On Thin                              |

| SiO <sub>2</sub> On Silicon (sample 4T6)91                                          |

| 5.6 Dark Field Photograph (140X), 50 A Ta RFS On Thin                               |

| SiO <sub>2</sub> On Silicon (sample 2T6)91                                          |

| 5.7 Dark Field Photograph (140%), 500 A Ta RFS On Thin                              |

| SiO <sub>2</sub> On Silicon (sample 3T7)92                                          |

| 5.8 Dark Field Photograph (140%), 1000 A Ta RFS On Thin                             |

| SiO <sub>2</sub> On Silicon (sample 4T7)92                                          |

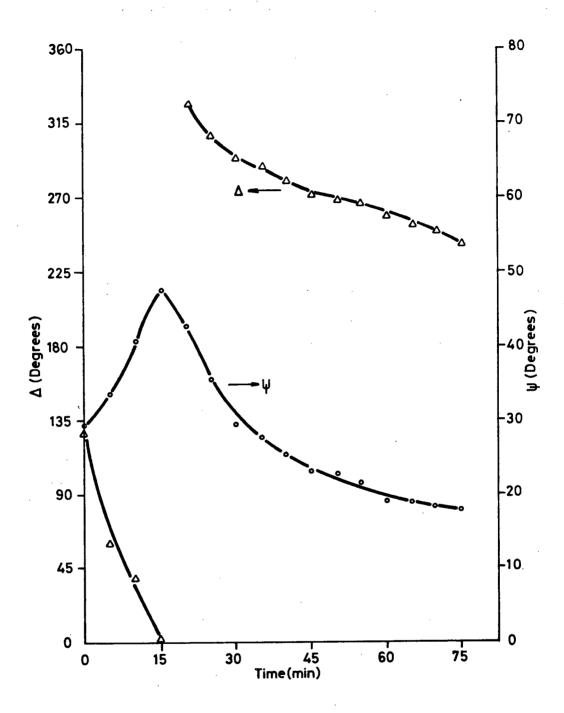

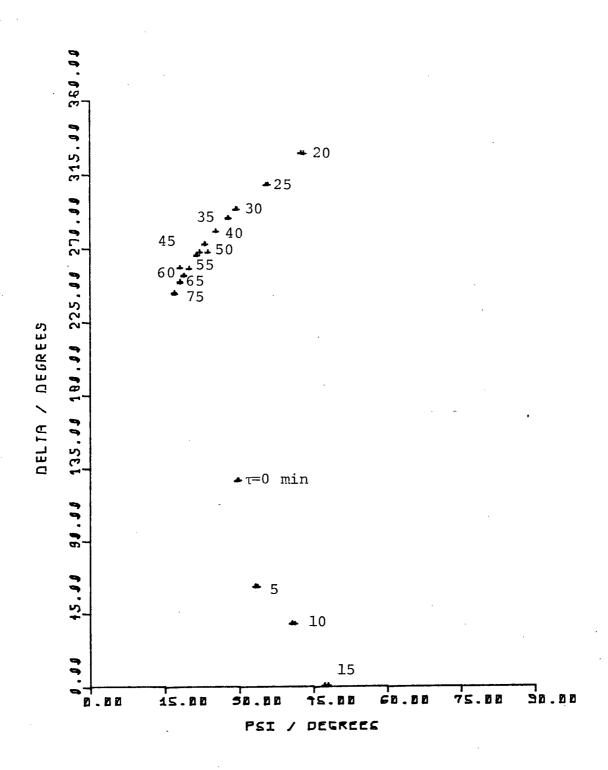

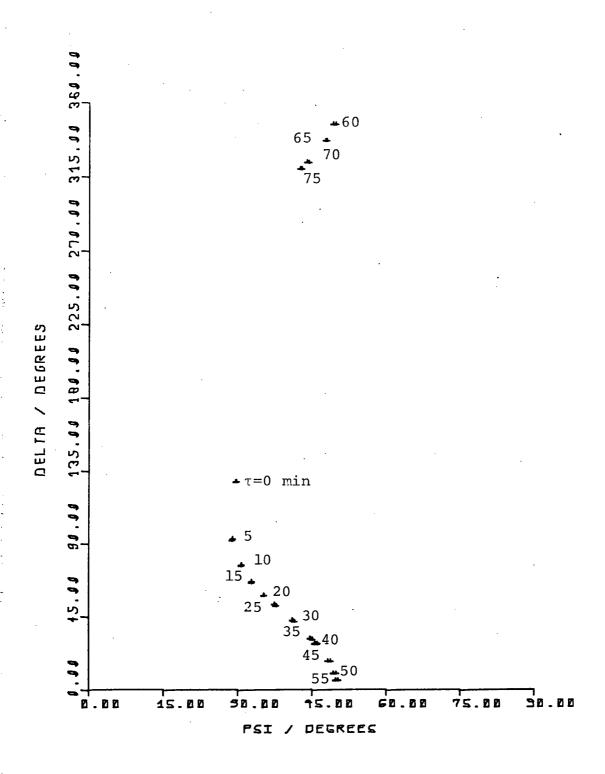

| 5.9 Ellipsometric Data Vs. Time, Sample BNR50094                                    |

| 5.10 Ellipsometric Data Vs. Time, Sample BNR100095                                  |

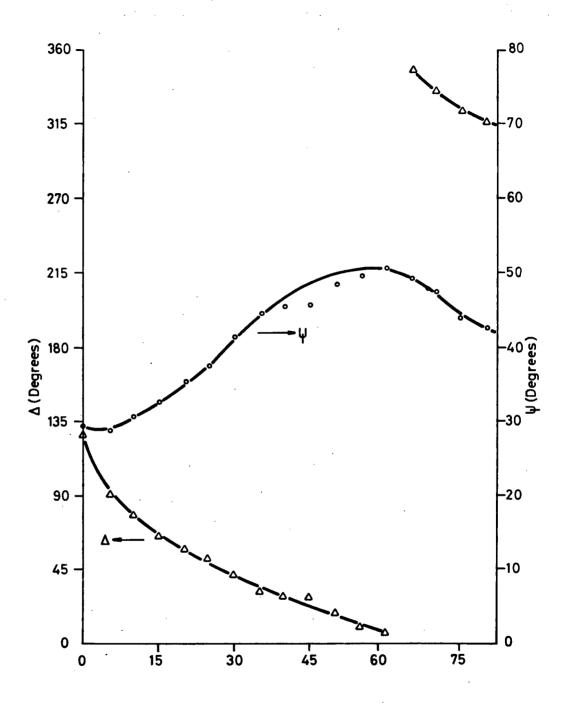

| 5.11 Transient Ellipsometry, Sample BNR50097                                        |

| 5.12 Transient Ellipsometry, Sample BNR100098                                       |

| 6.1 MTAOS Anodic Oxidation Under Constant Current14                                 |

| 6.2 MTAOS Anodic Oxidation Under Constant Voltage142                                |

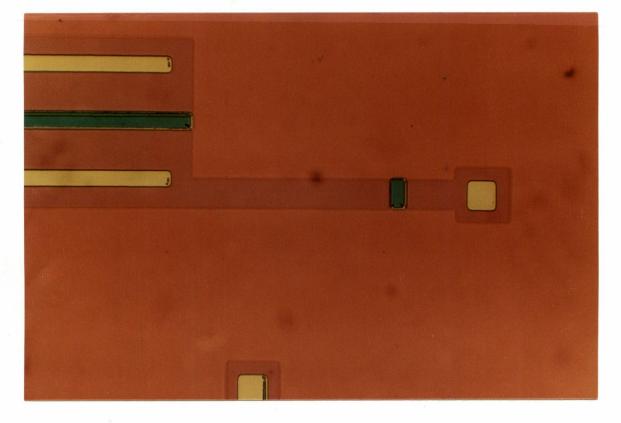

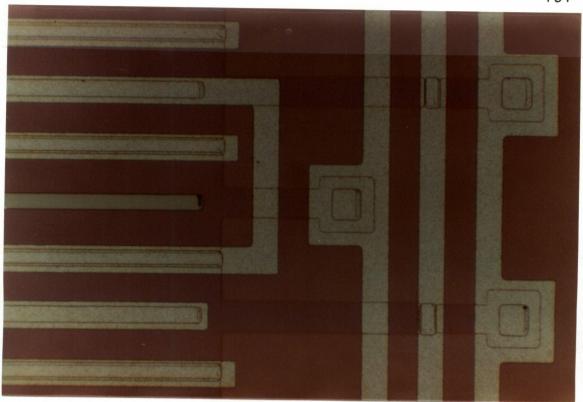

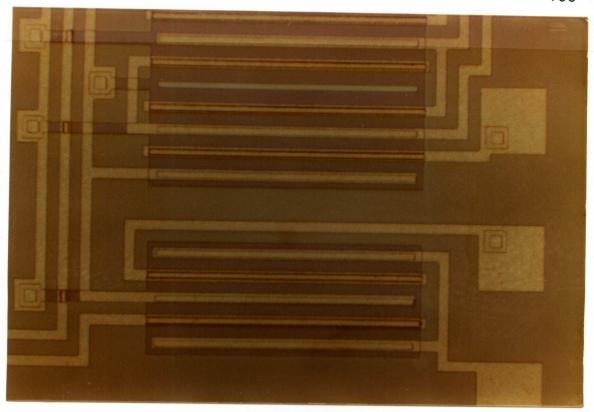

| 6.3 MTAOS Transistor; Drain, Source And Gate Details149    |

|------------------------------------------------------------|

| 6.4 MTAOS Transistor, Contact Window Area Detail149        |

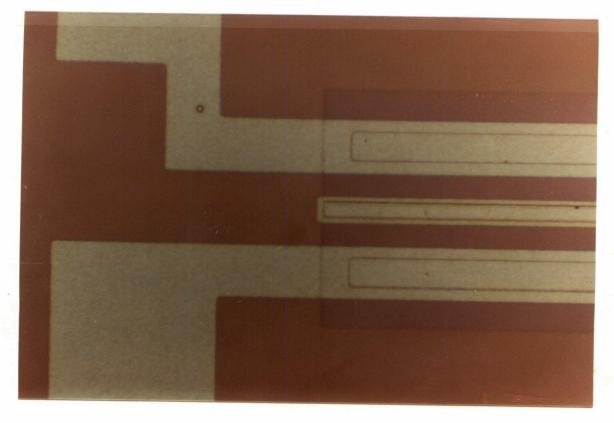

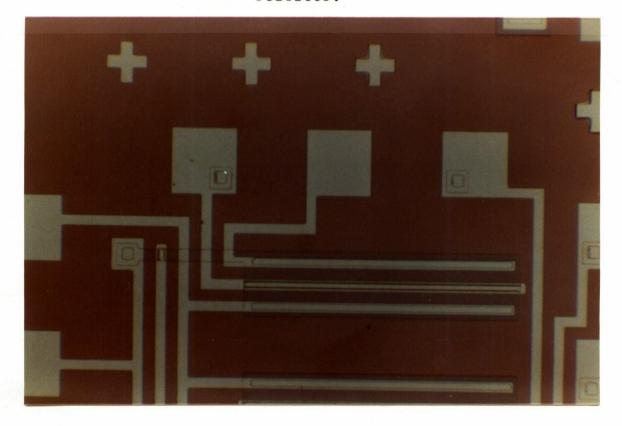

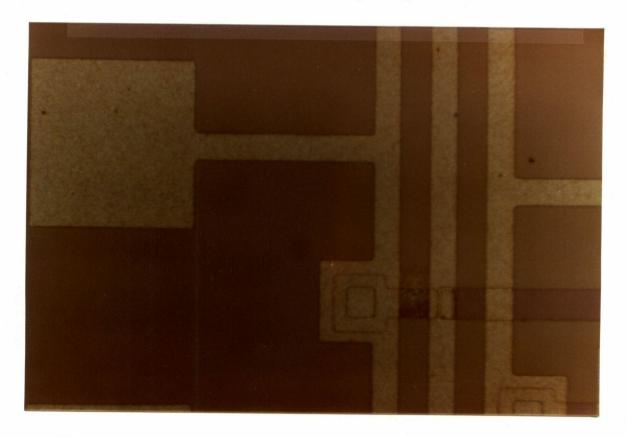

| 6.5 Overall View Showing MOSFET And R-S Flip Flop150       |

| 6.6 MTAOS Transistor Contact Metallization Details150      |

| 6.7 R-S Flip Flop Contact Metallization Windows151         |

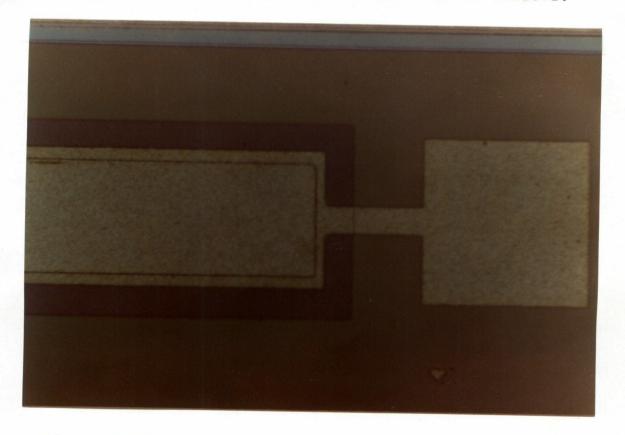

| 6.8 MOS Capacitor Area, Contact Metallization151           |

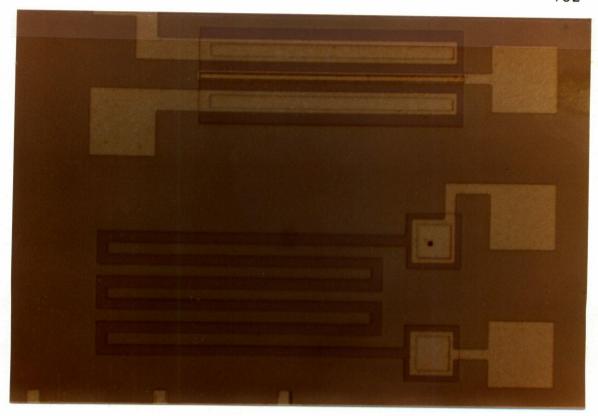

| 6.9 Overall View Showing MOSFET And Diffused Resistor .152 |

| 6.10 Contact Pads And Alignment Markers152                 |

| 6.11 NOR Gate And R-S Flip Flop Overall View153            |

| 6.12 Interconnection And Contact Pad Detail153             |

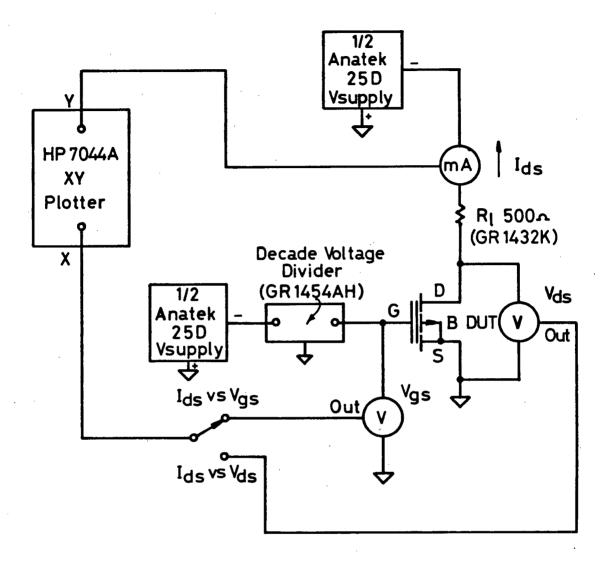

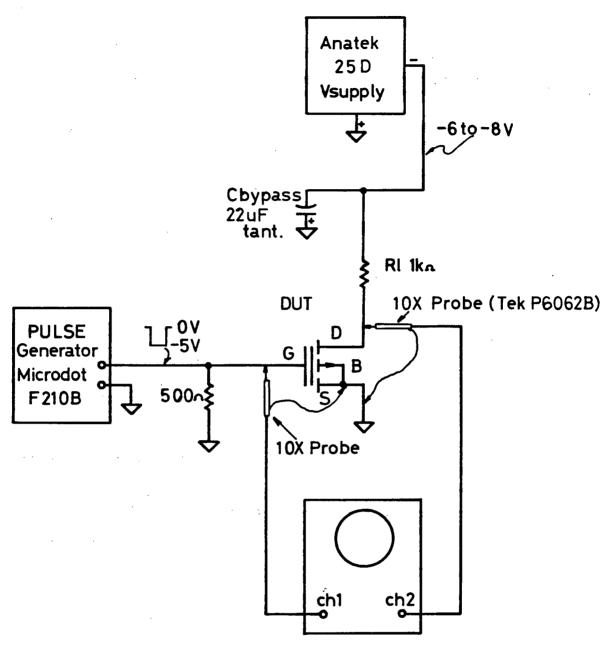

| 7.1 System For Plotting MOSFET Static Curves156            |

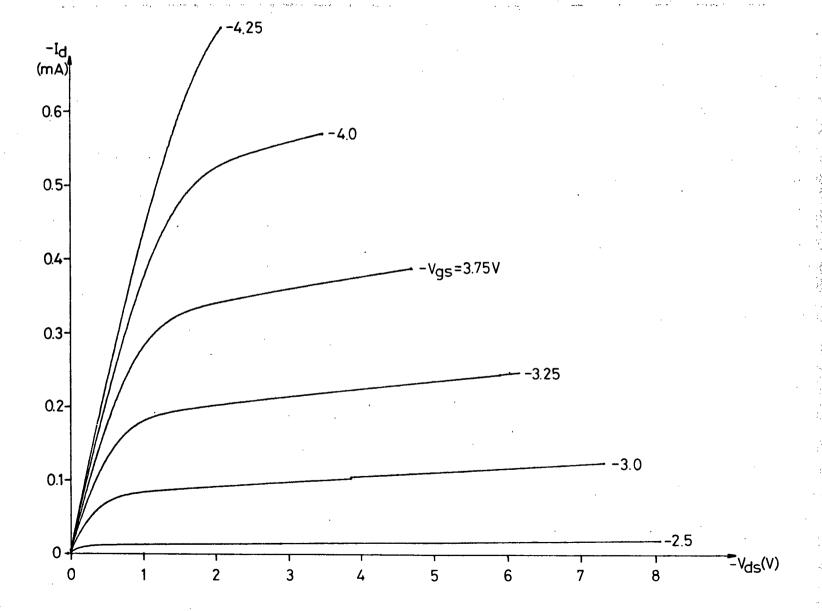

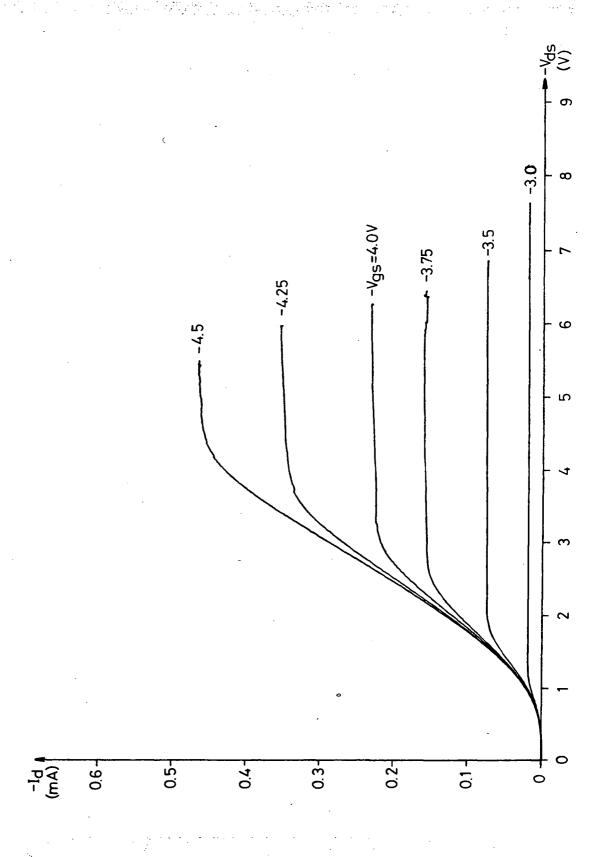

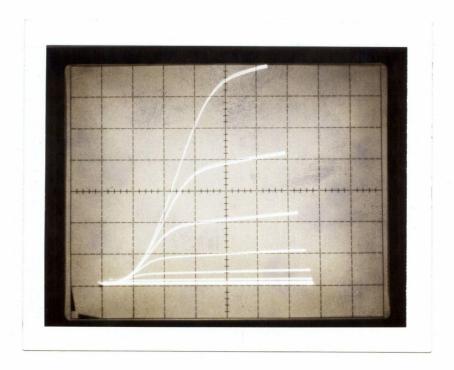

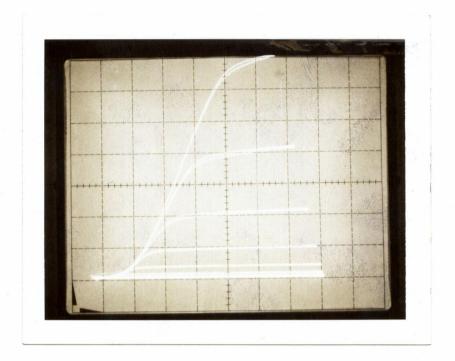

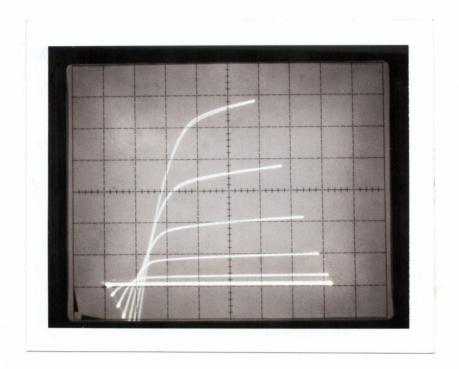

| 7.2 Static Output Curve, Sample MTAOS3 Thermal157          |

| 7.3 Static Output Curve, Sample MTAOS4 Anodic158           |

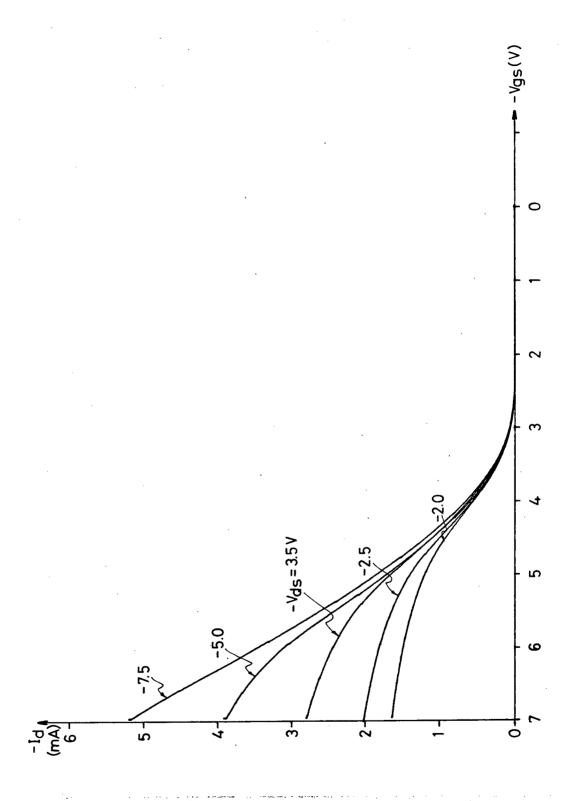

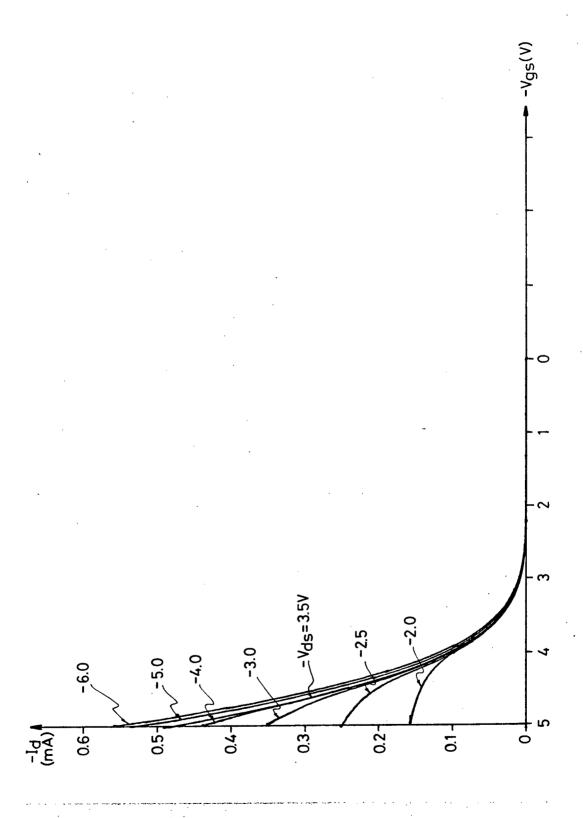

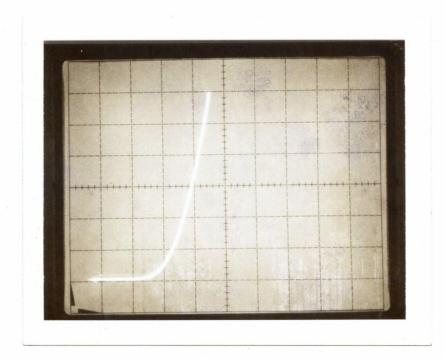

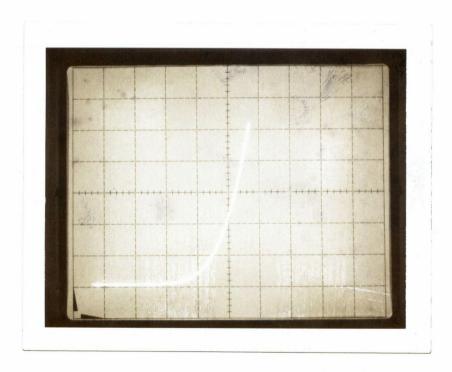

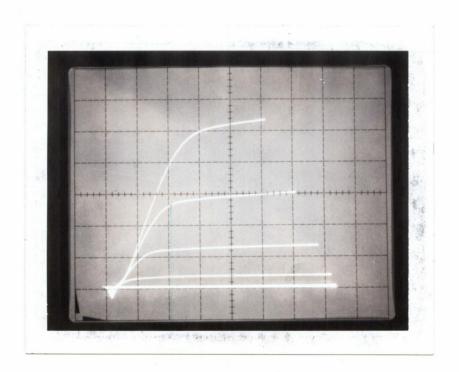

| 7.4 Static Transfer Curve, Sample MTAOS3 Thermal159        |

| 7.5 Static Transfer Curve, Sample MTAOS4 Anodic160         |

| 7.6 System For Measuring The MOSFET Pulse Response162      |

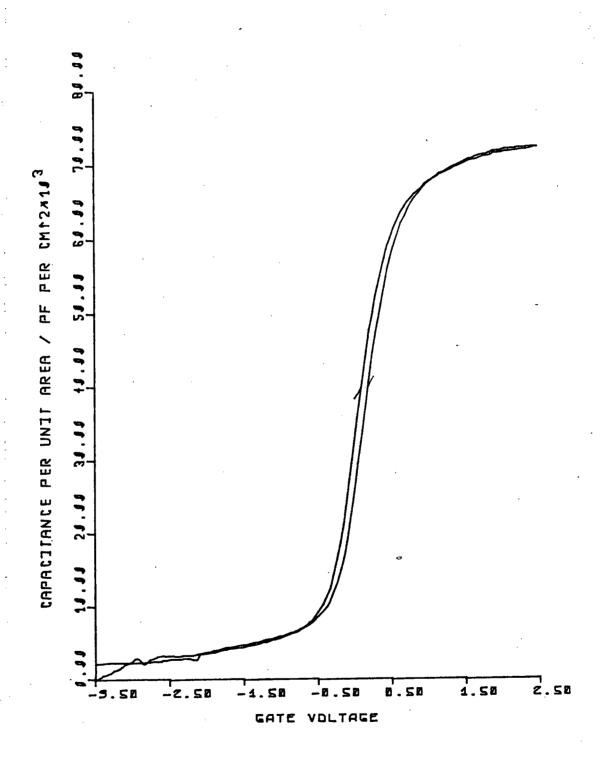

| 7.7 C-V Curve On Double Dielectric Test Wafer (sample      |

| MOSCTest 200A Thermal165                                   |

| 7.8 C-V Curve On Double Dielectric Test Wafer (sample      |

| MOSCTest 200A Anodic166                                    |

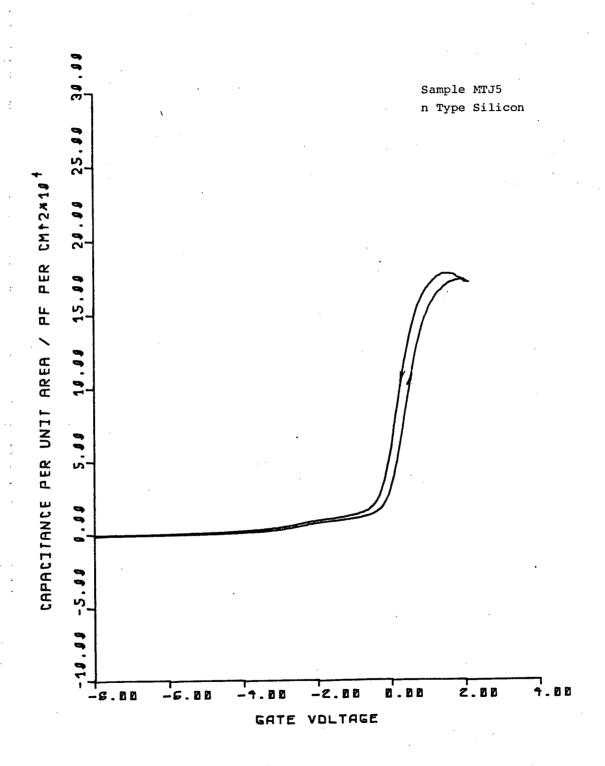

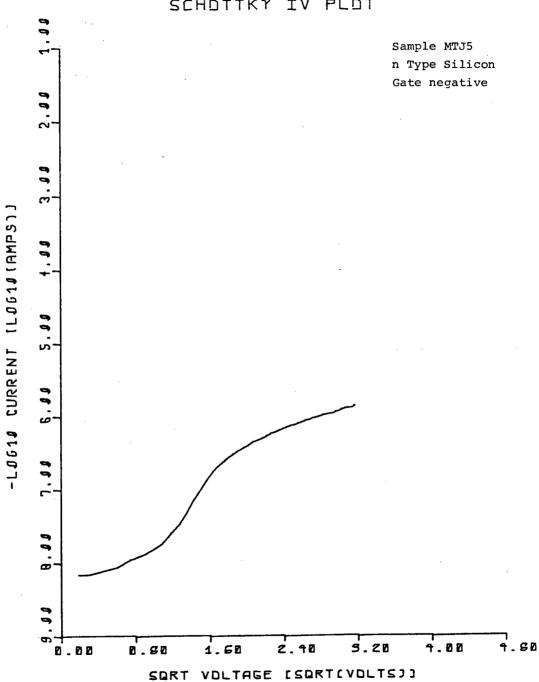

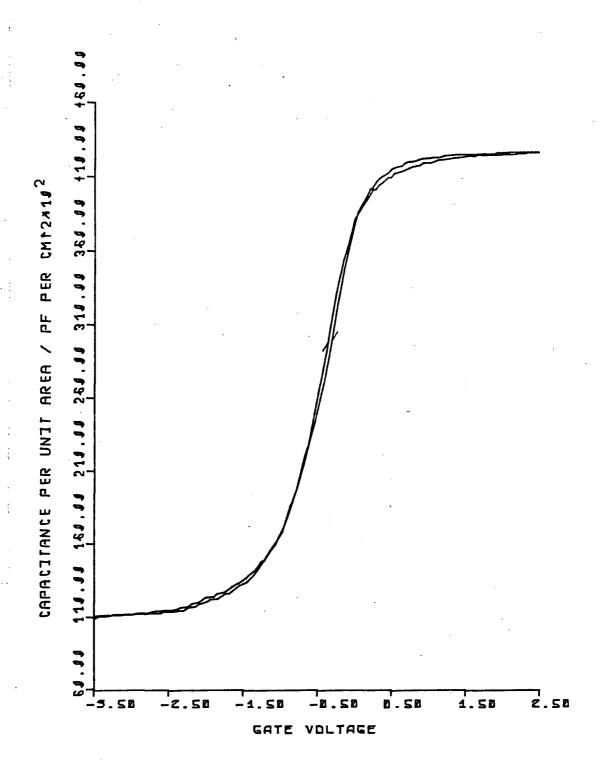

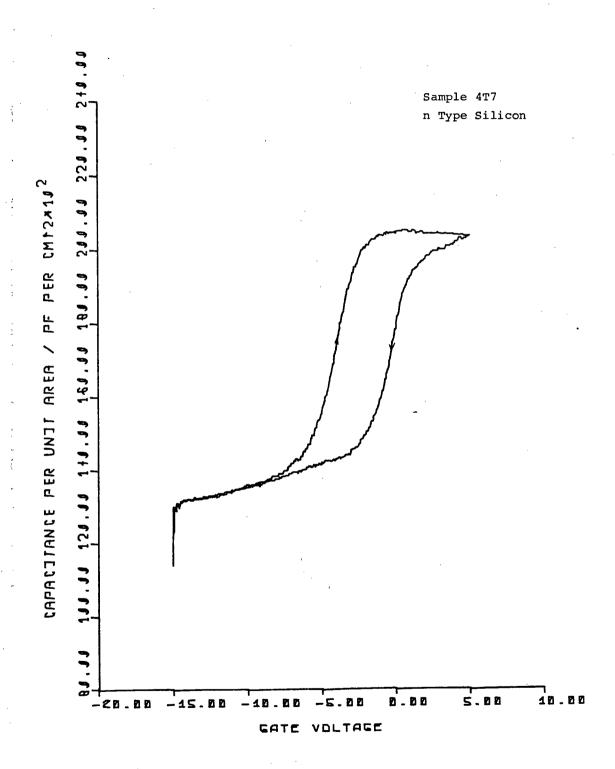

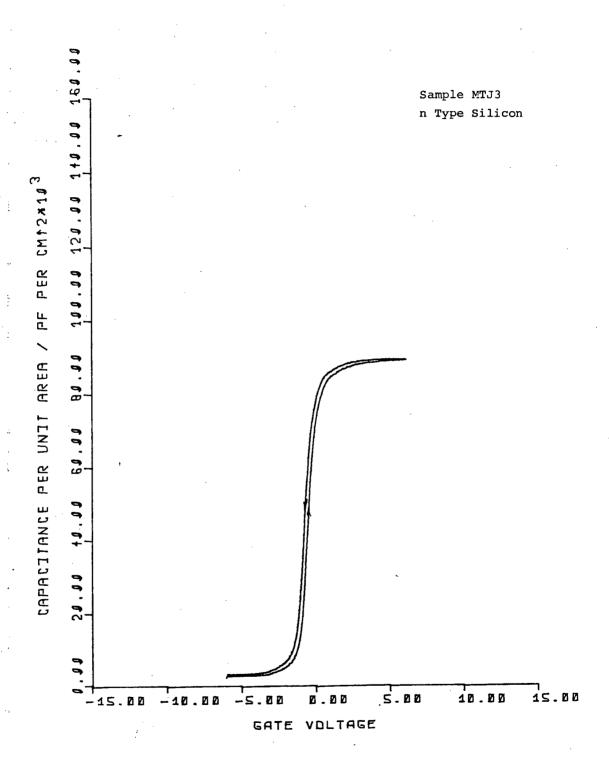

| 7.9 C-V Curve Of MOSFET Gate, Thermal Sample MTAOS3167     |

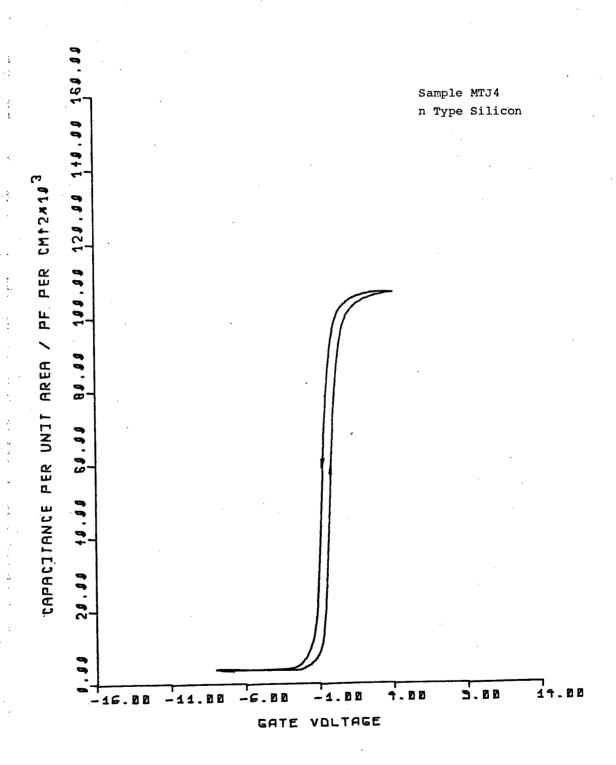

| 7.10 C-V Curve Of MOSFET Gate, Anodic Sample MTAOS5168     |

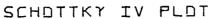

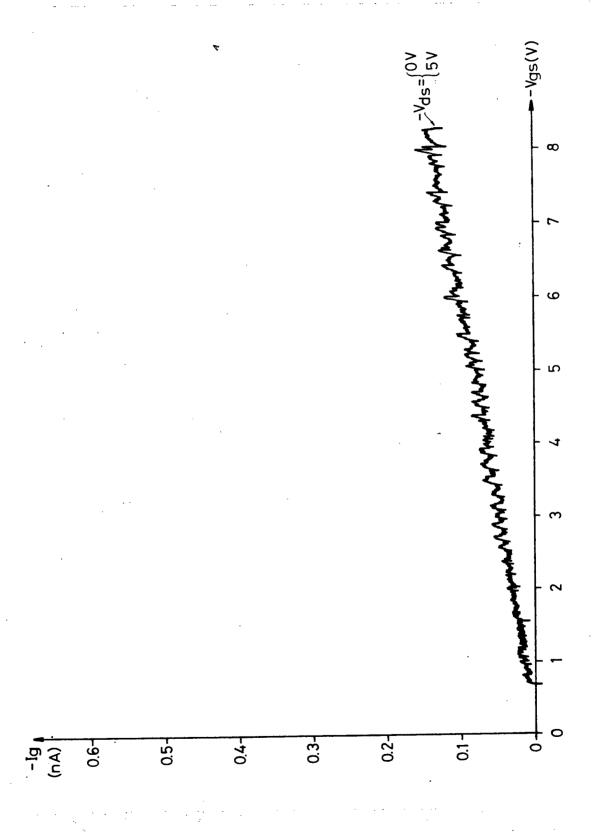

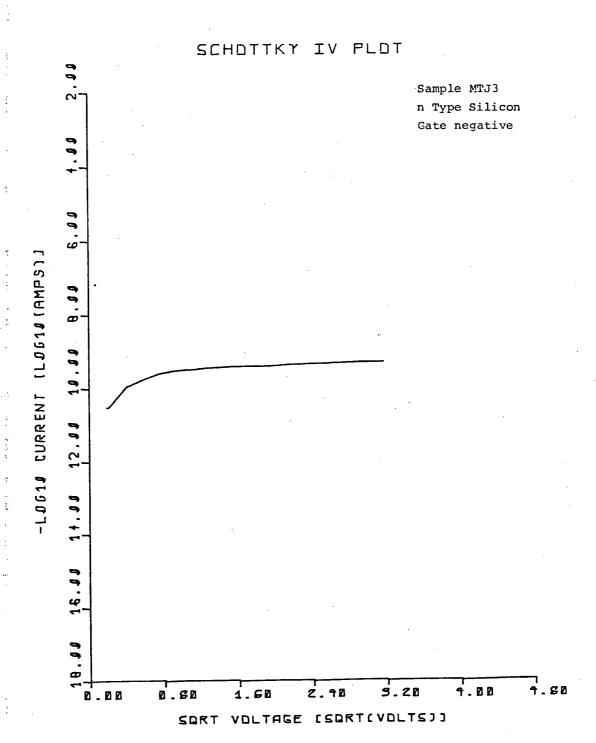

| 7.11 I-V Curve On MOSFET Gate, Thermal Sample MTAOS3171    |

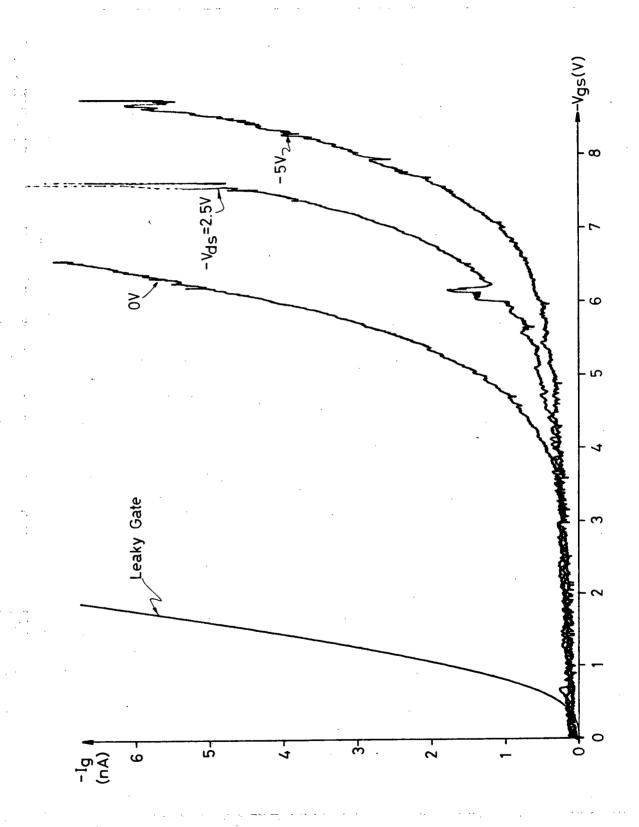

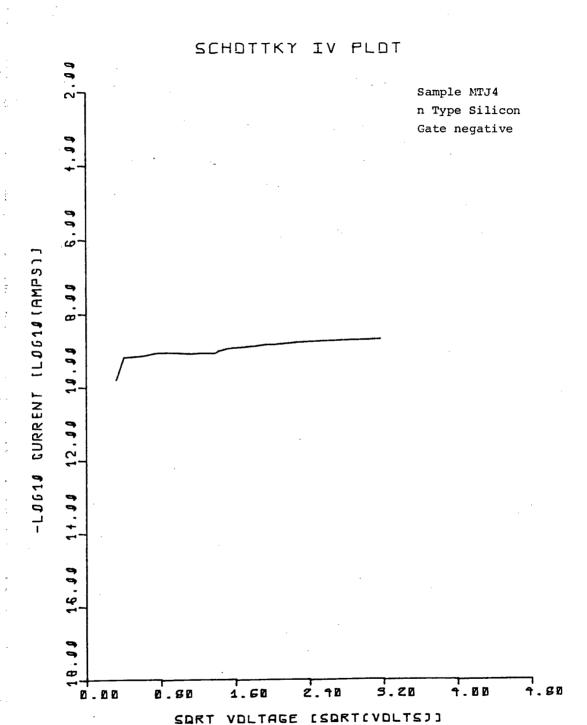

| 7.12 I-V Curve On MOSFET Gate, Anodic Sample MTAOS4172     |

| 7.13 Double Dielectric MOSFET Output Curves, Sample        |

| MTAOS3176                                                  |

| 7.14 Double Dielectric MOSFET Saturated Test, Sample       |

| MTAOS3176                                                  |

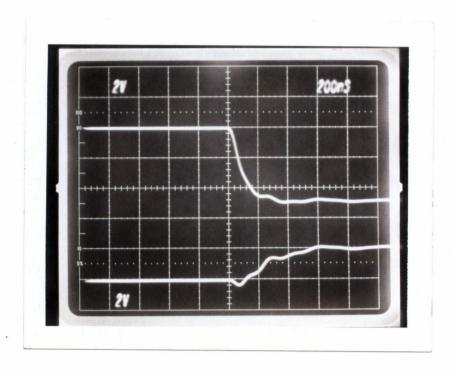

| 7.15 Double Dielectric MOSFET Pulse Test (Turn On),                               |

|-----------------------------------------------------------------------------------|

| Sample MTAOS3177                                                                  |

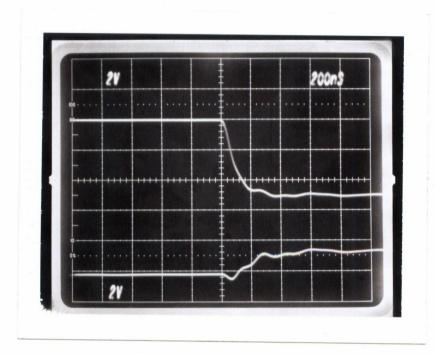

| 7.16 Double Dielectric MOSFET Pulse Test (Turn Off),                              |

| Sample MTAOS3177                                                                  |

| 7.17 Double Dielectric MOSFET Output Curves, Sample                               |

| MTAOS4178                                                                         |

| 7.18 Double Dielectric MOSFET Saturated Test, Sample                              |

| MTAOS4178                                                                         |

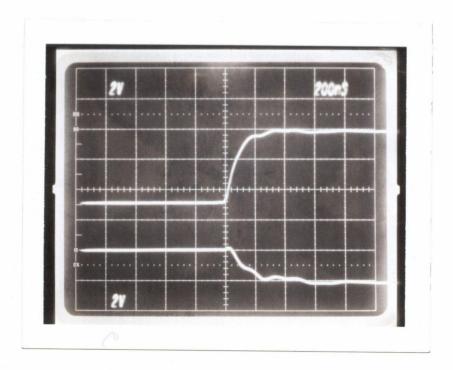

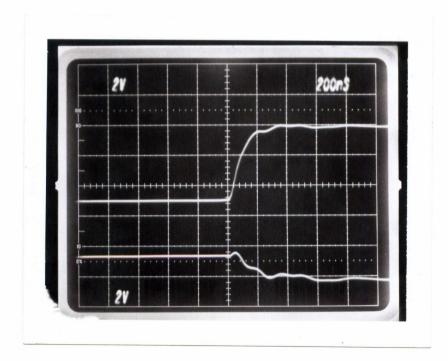

| 7.19 Double Dielectric MOSFET Pulse Test (Turn On),                               |

| Sample MTAOS4179                                                                  |

| 7.20 Double Dielectric MOSFET Pulse Test (Turn Off),                              |

| Sample MTAOS4179                                                                  |

| 7.21 Leaky Gate In MOSFET, Anodic $Ta_2O_5$ , Sample MTAOS4 180                   |

| 7.22 Leaky Gate In MOSFET, Thermal Ta <sub>2</sub> O <sub>5</sub> , Sample MTAOS3 |

| 180                                                                               |

| 7.23 Double Dielectric MOSFET Equivalent Circuit182                               |

#### **ACKNOWLEDGEMENTS**

I wish to thank my Supervisor, Dr. Lawrence Young for his guidance and encouragement on the work presented in this Thesis. My thanks to Dr. David Pulfrey for his interest and enlightning conversations on the subject. Also I am indebted to Dr. Peter Janega (Solid State Laboratory at UBC) for his most valued assistance in many processing details, and in preparing the interfacial oxidation samples; to Dr. Jamil Ahmed (now with Microtel Pacific Research) for suggesting the possible use of the Liftoff Technique on tantalum metal; to Dr. David Smith (now with Ballard Research) for his initial assistance and help on the subject, and for allowing me the use of some of his computer interfacing software.

My expression of gratitude to Ms. Carla Miner of Bell Northern Research in Ottawa, for supplying the Magnetron Enhanced Sputtering samples for MOS capacitors.

My thanks to Mr. James Henderson of the Science Division, Main Library, for his assistance in the Computer Assisted Library Search for obtaining the reference material. The assistance of Ms. Angela Runnals, Ms. Victoria Lyons-Lamb and Mr. Jon Nightingale of the Computer Centre is also acknowledged, as they made possible to compose this Thesis using the FMT editor under the MTS operating system.

I also wish to acknowledge the infinite patience that my wife Brenda and our children have demonstrated during all these years of hard work and study. Without the encouragement of other members of my family, in particular my mother and brother, this work would have not been

possible. To all them, I express my deep indebtedness. I dedicate this work to a man that fought many battles in life, but heroically lost the last one: my father.

#### CHAPTER 1

## INTRODUCTION

The term non-conventional dielectrics is used to describe those which depart considerably from the classic  $SiO_2$  used in MOS technology as gate insulators, device isolation, diffusion masking, implant resist and general surface passivation. Notwithstanding the natural advantages of the silicon dioxide, numerous authors have followed research in alternate dielectrics suitable for use in MOS devices. In the present work, one of such non-conventional insulators is used, namely Tantalum Pentoxide  $(Ta_2O_5)$ , either obtained by thermal or anodic oxidation of tantalum metal to form MOS capacitors and field effect devices on silicon substrates.

Large Scale, Very Large Scale Integrated and future Ultra Large Scale Integrated Circuits will require technologies and devices capable of performing when scaled down to 1 micron features and beyond, in order to achieve large number of devices per dice (>300,000) if this microtechnology is to be successful. At this present time (early 1984), major problem areas seem to have not been resolved yet, namely the solution to electromigration induced failures, in which the ions that form the interconnecting metal lines (usually Aluminium) transported by the extremely high current densities, i.e., "electron wind", of typically 10,000 A/cm<sup>2</sup> [Black, 1969]; and the subthreshold conduction in MOS transistors, in which the device does not turn off, i.e., a small, but non-zero drain current still flows despite of the efforts of the applied gate voltage to do so [Troutman, 1974]. The latter is particularly critical to the operation of circuits where low leakage (the device is in the cutoff or OFF condition) currents are required. The subthreshold currents do not scale properly and this presents a problem for very small devices [Dennard et al., 1974]. As a consequence, the reduction of the subthreshold effect is of great importance in attaining successful devices for VLSI and ULSI.

The high permittivity dielectrics presently used gate insulators for Metal Oxide Semiconductor Field Effect Transistors (MOSFET's) have definitive advantages. A close examination of the equations [Sze, 1969] that relate the drain current with its geometry, threshold voltage and drain voltage, reveals that the former is in direct relation with insulator relative dielectric constant. A similar effect, and perhaps the most important, is on the device transconductance gm: it is also directly proportional to the qate insulator dielectric constant. Another important parameter, the threshold voltage, is reduced by about factor, which is crucial in the design of transistors for analog (linear) applications. The channel conductance, suffers a more complicated change, as depends on both insulator capacitance (which increases with the dielectric constant) and on the threshold voltage (which decreases). It can be said then, that a general improvement

on the MOSFET device performance can be accomplished by the use of high permittivity gate insulators. Tantalum pentoxide  $(Ta_2O_5)$  has a relative dielectric constant of 27, about seven times larger than silicon dioxide  $(SiO_2)$ . Therefore, in theory, a sevenfold increase in performance should be expected. Because of its negative interface charge density,  $Ta_2O_5$  can help in further reducing the gate threshold voltage [Seki et al., 1984]

Another promising application is in avoiding the gate insulator breakdown by either the internal fixed charge generated field, or the one caused by the application of a gate voltage to the classic gate oxide. As the device is scaled down in its three dimensions, the gate insulator thickness is reduced by the same factor K, hence limiting the maximum applied gate voltage by oxide breakdown. The applied gate voltage has then a lower bound, the turn-on and a higher bound, the insulator breakdown voltage, voltage. This situation can be avoided, if a dielectric structure is used instead of the single layer, silicon dioxide gate insulator [Angle and Talley, 1978]. thick layer of high dielectric constant material (i.e., tantalum pentoxide) is deposited over a thin layer of dielectric constant material (i.e., silicon dioxide), the latter is protected from breakdown fields, as most of voltage drop across the compound dielectric will appear in the higher permittivity material, the thicker tantalum pentoxide.

the double insulator structure, the probability of Ιn pinholes coinciding in the same location is vanishingly small, thus producing a much better quality insulator. Amorphous silicon dioxide is structurally porous and has high permeability to water vapour and migration of alkali ions. By applying a second outer dielectric onto the inner one, these effects can be reduced. Tantalum pentoxide has a much denser structure, and possibly retards the migration. The double dielectric insulating structure is used in the present work as the gate insulator for both MOSFET and MOS capacitor devices. The successful devices functional proved to be transistors, with moderate transconductance and fast switching pulse response. The MOS capacitors have good C-V curves and low leakage currents.

It is quite possible that the single dielectric high permittivity insulator and the double dielectric structure have direct application in future VLSI and ULSI technologies. Already, the high dielectric constant tantalum pentoxide has found use in a VLSI 256/512 kbit dynamic Random Access Memory (RAM), which aims towards the 1 Mbit memory Integrated Circuit [Ohta et al., 1980].

The purpose of this Thesis is to present the measurements and results obtained from experimental MOS Capacitors fabricated with anodic and thermal tantalum pentoxide; and from the experimental MOSFET's utilizing a double dielectric ( $Ta_2O_5$ ) gate insulator structure, in which the tantalum oxide was obtained by thermal and anodic

processes.

This Thesis is divided into eight chapters and four appendices. The second chapter contains an overview of the previous work done by several authors in this field. In the third chapter, the theory of the double dielectric insulator is presented, as later on a device will be developed around this technology. The fourth and sixth chapters contain all the information related to the processing of the MOS capacitor and double dielectric device. In the fifth chapter, the measurements performed on the MOS capacitors and results are presented. The seventh chapter contains the measurements made on the double dielectric MOSFET's (MTAOS devices) and the results obtained. In chapter eight, the summary and conclusions of this work are presented.

### CHAPTER 2

## AN OVERVIEW OF NON CONVENTIONAL INSULATORS

A large number of authors have reported many different properties of non conventional dielectrics. In this chapter, I have attempted to present a summary of published works on the subject. These cover thin and thick films of several compounds used as dielectrics in a non conventional way.

Despite early difficulties in obtaining good counter electrode contacts, successful tantalum pentoxide thin films were first obtained by anodic oxidation of sputtered tantalum metal [Berry and Sloan, 1959], to be used in low value capacitors for printed circuits. Typical capacitance densities of 10 nF/mm² and capacitances of 30 nF with leakage currents of 10-100 nA were obtained for samples made on ceramic substrates. Thin films of anodically oxidized aluminium were also produced for the same application and a certain degree of simplicity over the tantalum version was claimed, since Al metal was evaporated instead sputtered and the same was used as contact and for anodic dielectric formation [Huber and Haas, 1960].

A detailed study of the anodic oxides of the so called "valve metals", i.e., the electrolytically formed oxides of Ta, Nb, Al, Zr, Hf, W, Bi, Sb and others, was given concisely in book form by Young in 1961, with great attention devoted to tantalum and the properties of its thin film oxides.

Anodically grown thin films of silicon oxide (SiO), aluminium oxide  $(Al_2O_3)$ , tantalum pentoxide  $(Ta_2O_5)$ , zirconium oxide  $(ZrO_2)$  and titanium oxide  $(TiO_2)$  were fabricated, using evaporation techniques for evaluating their conduction and negative resistance at low frequencies (60 Hz); although the application was not intended for MOS devices, but rather in switching and rectifying [Hickmott, 1962].

A study done on a Metal-Insulator-Metal (MIM) structure of the form Ta-Ta<sub>2</sub>O<sub>5</sub>-Au revealed that the electronic transport mechanism obeys an Ohmic characteristic at low fields and that at high fields it follows a Poole-Frenkel type emission at room temperatures. At high fields and low temperatures (i.e. 77K), the electronic conduction is governed by a Fowler-Nordheim type emission. Measurements gave an activation energy of 0.1 eV. A discontinuity in the oxide properties was noted around 50 nm [Mead, 1962].

A rather unusual current-voltage characteristics was observed for niobium, titanium and tantalum oxides, when prepared as thin films and their oxides obtained by the thermal process. Regions of negative resistance are found to be current controlled, as opposed to the voltage controlled negative resistance of the Tunnel (Esaki) diode [Chopra, 1963].

Thin film circuits using resistors made of tantalum nitride (TaN) and capacitors made of anodic tantalum oxide were successfully applied in creating the first hybrid circuits, i.e., incorporating discrete bipolar transistors

to a common ceramic substrate, in making both analog and digital circuits [Berry, 1963]. Later a method for producing high value resistors was developed, by sputtering tantalum in a partial atmosphere of argon and oxygen [Pendergast, 1963]. Furthermore, a production style open ended vacuum system for deposition of tantalum films for manufacturing resistors was reported to make 4 million square inches of metal film per year-shift [Balde, Charschan and Dineen, 1964].

Reactive sputtering of tantalum metal with subatmospheric partial pressure gas pressures was used to deposit films of tantalum nitride (TaN), tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>), tantalum carbide (TaC and Ta<sub>2</sub>C) titanium nitride (TiN) and oxides (TiO2), Niobium Nitrides (NbN and Nb2N); for the fabrication of two dimensional hybrid thin film circuits. It was noted that the introduction of Oxygen as a reactive component, had a drastic effect in the electrical properties of the sputtered films. By controlling its partial pressure, reproducible values of sheet resistivity were obtained. It was found that most nitrides and carbides have superconducting properties and that niobium nitride, has one of the highest transition temperatures [Gerstenberg, 1964].

The discovery of beta tantalum [Read and Altmann, 1965] sparked more interest in the research of thin films made of this material, as it offered improved electrical properties over its predecessors. It has higher resistivity, a smaller temperature coefficient of resistance and its

superconducting transition temperature is much less. Beta tantalum is formed in a sputtering system when an atmosphere of argon is introduced at a partial pressure of 10 to 30 mTorr and the total pressure (i.e., vacuum quality) of the other gases is 10  $\mu$ Torr. It was found that a conversion to normal tantalum (body centered cubic structure) takes place, when beta tantalum (tetragonal) is heated in vacuum to about 750 C.

Evidence of photoelectric properties has been found for made of Nb<sub>2</sub>O<sub>5</sub> over metal substrates, as knowledge of the conduction mechanism through the oxide film can obtained by photoresponse studies [Hickmott, 1966]. Electronic photoconduction is also found in thin films Ta<sub>2</sub>O<sub>5</sub>, with sharp increases of conduction current when irradiated with ultraviolet light, in which the increase current was found to be approximately proportional to the intensity of the light [Young, 1961]. A thin film photocell, using thermally oxidized niobium metal, has been fabricated, and it was found that a linear relation exists between the photocurrent light intensity, experimental and as measurements indicated. However, the transient response very slow (50-100 sec) and the conversion efficiency is two orders of magnitude below the conventional junction type silicon cells. For Ta and Ti anodic oxides a linear relation exists between photocurrent and photovoltage, although such a characteristic is not desirable in a practical photocell [Chopra and Bobb, 1963].

Chemical vapour deposition techniques (CVD) have been

applied to the fabrication of MOS capacitors, in which films of  $TiO_2$ ,  $Ta_2O_5$  and  $Nb_2O_5$  were obtained by pyrolysis of the appropriate organo-metal compound. Lead oxide (PbO) films were also deposited, using the same CVD techniques, for use in Vidicons. A wide range of substrates, from silicon to platinum was used [Wang, Zaininger and Duffy, 1970].

Bismuth titanate films ( $\mathrm{Bi_4Ti_3O_{12}}$ ) with a very high relative permittivity ( $\simeq 160$ ) have been reported for use in Metal-Insulator-Metal capacitors, in spite of the stoichiometry control problems in the sputtering of this compound. High dissipation factors which depend strongly on frequency and heavy conduction currents were found [Szedon and Takei, 1971].

Tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>) thin films have been considered for application as dielectrics for Microwave Integrated Circuits (MIC's), due to its high relative constant and moderately high Q (≈100) dielectric microwave frequencies. The so called Tantalum dielectrics for MIC's based on metal sputtering and are later anodic oxidation on an alumina substrate technologies. The guide wavelength \( \lambda \) can be reduced, and the degree of size reduction as well as integration can be increased, if the relative dielectric constant of the substrate is made larger. This is determined by the effective dielectric constant  $\epsilon$ eff, which is a direct function of the relative dielectric constant  $\epsilon r$  of the substrate. Hence, by using substrates with large  $\epsilon r$  (i.e.  $Ta_2O_5$ ), a larger degree of integration and size reduction can be achieved [Caulton,

1971].

A rather unorthodox approach to a non-conventional gate insulator was applied to a MOSFET voltage divider, in which the gate electrode is made to slide over silicone oil (later glycerine), with the gate oxide being underneath. This formed a capacitive voltage divider, with the MOSFET drain current being a function of the movable gate electrode position [Okamoto and Ugai, 1971].

Thermal oxidation of sputtered tantalum metal over silicon was made feasible in the form of a Si-Ta and Si-Ta-Al structures, placed under heat treatment in different atmospheres of  $N_2/O_2$  and  $N_2/H_2O$  mixtures. The kinetics of oxygen incorporation show an approximate square root dependence with time. It was reported that the interface exhibited negligible interdiffusion when annealed. Because of the relatively low temperature process used (525 is said that the tantalum thin films are technologically compatible with the Silicon System. This due to the stability shown by silicon, the Si-SiO2 interface and aluminium metal at this temperature [Croset and Velasco, 1971].

A thin film capacitor of silicon dioxide over tantalum pentoxide has been successfully fabricated, in which  $SiO_2$  was sputtered over anodized  $Ta_2O_5$  over a ceramic substrate. The capacitance density is dominated by the silicon dioxide film, because of its smaller dielectric constant as compared with anodic tantalum oxide. This gave a high degree of reproducibility, as the desired capacitance density of the

SiO<sub>2</sub>/Ta<sub>2</sub>O<sub>5</sub> thin film capacitor is controlled by the thickness of the silicon dioxide film. The temperature coefficient of capacitance (TCC) can be adjusted to compensate the negative temperature coefficient of resistance (TCR) of tantalum nitride resistors (used in RC networks based on the Tantalum System), by proper selection of the silicon dioxide thickness [Sato, Sato and Okamoto, 1973].

oxidation of tantalum films deposited electron beam evaporation on silicon, have been prepared order to study the Si-Ta-{Ta oxide} structure. The criteria of a maxima in the oxide's apparent refractive index used in deciding the complete oxidation of the tantalum metal. The elapsed time for this maximum value oxidation time of the film. It was concluded that some interaction with the Si substrate ocurred during the Ta film, namely the co-oxidation of a oxidation of the small, but non-zero amount of silicon. This interaction at the Si-Ta interface has actually moved into the Si crystal, in a similar fashion as the Si-SiO<sub>2</sub> interface when oxidation takes place. It was claimed that the properties of the oxide film and the Si-{Ta oxide} interface can be controlled by the Si/Ta ratio in the oxide film [Revesz, Allison, Kirkendall and Reynolds, 1974].

An interesting insulator structure is made using evaporated oxide films of tungsten  $(WO_3)$  and molybdenum  $(MoO_3)$  oxides, sandwiched between orthogonally evaporated Al electrodes. It was established that a Schottky type barrier

exists between the contacts and oxide by verifying the linearity of the  $1/C^2$  versus applied voltage plot and it was concluded that a compound barrier, i.e., an insulating layer adjacent to a space charge layer exists between the oxide film and the electrode [Padmanabhan and Sathianandan, 1975].

Another use of tantalum pentoxide is in the field of antireflection coatings for silicon solar cells, since its refractive index (2.23) is very close to the optimum value of 2.3 required in this application. The thermal oxidation of tantalum is a low temperature process that results in a noncrystalline oxide with a Silicon-{Ta oxide} structure of high perfection. This is of great importance if a high quantum yield is desired at short wavelengths, as with a good interface, the carriers generated in its surroundings reach the n-p junction without recombination. Niobium pentoxide has also similar properties with a refractive index of 2.37, close to the optimum [Revesz, Allison and Reynolds, 1976].

MOS capacitance measurements using the C-V plot techniques are helpful in determining the characteristics of the semiconductor- oxide interface, as the density of interface states can be obtained in various ways, in particular by the Terman method [Sze, 1969]. Thermally oxidized samples of sputtered tantalum have been prepared for this purpose, and observing the final oxide thickness, it gave twice that of the original film. It was noted that annealing in forming gas  $(N_2/H_2\ mixture)$ , reduced the density of interface states by a factor of 4, while the

oxide charge remained fixed and negative [Revesz and Allison, 1976].

Ellipsometric observations of the optical properties of thermally oxidized Ta<sub>2</sub>O<sub>5</sub> on silicon have shown gradient in the optical refractive index exists at the substrate-oxide interface and that the index actually increases slightly from its Si-Ta<sub>2</sub>O<sub>5</sub> boundary towards the outer end of the oxide. The existence of this refractive index gradient is somewhat controversial, as in its actual measurement, a thin (≃10 nm) layer of oxide was etched at time, and its index measured by ellipsometry using multilayer model. Measurements performed on a GaAs substrate show that a gradient with opposite slope exists, as compared with the silicon substrate case. Hence, the gradient in the refractive index (and its slope) of the Ta oxide depends largely on the substrate were they are grown [Revesz, Reynolds and Allison, 1976].

Chemical Vapour Deposition (CVD) is a technique by which an organo-metallic compound is deposited by pyrolysis with the assistance of a carrier gas, usually a mixture which contains oxygen among others. Tantalum pentoxide films have been deposited using this method, with the advantage of being a low temperature (300-500 C) process, that results in oxides with amorphous structures, similar to the thermally grown tantalum oxides. The disadvantages of this approach are mainly in the vast complexity of the deposition equipment and the availability of a suitable tantalum organic compound. Films deposited by CVD show smooth

surfaces and good adhesion, with an index of refraction close to 2.3 and an optical bandgap of 4.4 eV. Capacitance measurements gave a relative dielectric constant of and C-V plots indicated that there was no difference among different crystal orientations ٥f p-silicon substrates, all showing no hysteresis. Some distortion of the C-V curves was attributed to fast surface states. conduction mechanism at DC was established to limited, with a Poole-Frenkel emission at low current densities and space charge limited at higher densities. A Schottky plot (log Current vs. Square Root Voltage) revealed a two-slope curve, and from the linear portion (first slope) a dielectric constant of 5.3 was obtained, which fits the constant value, but not the one obtained by optical capacitance measurements. Interestingly, the CVD SiO<sub>2</sub> films show current saturation, but at much lower currents (six orders of magnitude) than Ta<sub>2</sub>O<sub>5</sub> films [Kaplan, Baloq and Frohman-Bentchkowsky, 1976].

Further research work on the  $Si-Ta_2O_5$  interface has revealed that a significant interaction occurs well below the temperature required to form tantalum silicide ( $TaSi_2$ ) or silicon dioxide ( $SiO_2$ ). This phenomenon occurs in the deposition of the tantalum metal film, to which silicon incorporates in the process. It is claimed that this interaction is the cause for the refractive index gradient of the Ta oxide film. Gravimetric analysis show that thermally oxidized  $Ta_2O_5$  films contain a significant amount of silicon and the results give a ratio of 0.85 Si-Atom/Ta-

atom in the oxide film. Secondary Ion Mass Spectroscopy (SIMS) analysis seem to strengthen this hypothesis at least a qualitative sense. The interface interaction explained by assuming that oxygen facilitates the incorporation of silicon by grain boundary diffusion due the formation of strong Si-O bonds [Revesz and Kirkendall, 1976].

The Rutherford Backscattering (RBS) analysis technique been applied to study the Ta{oxide}-Si boundary and the characteristics of the oxide layer itself. Ιn analysis, light and high energy ions (typical are helium positive ions with an energy of 1-5 MeV) are used to bombard the surface to be studied, and by collecting data from the elastic scattered (i.e. bounced back) energy spectrum, knowledge of the surface and near surface composition can be obtained. A depth concentration profile from the energy spectra is then obtained from the He ions rate of inelastic energy loss. Results from this technique on Ta films show significant impurity effects due to gettering during the electron beam deposition from а high purity source. partial thermal tantalum oxides, they exhibit substantial oxygen incorporation, and in contrast with anodic sharp boundary between the Ta metal and the there is tantalum pentoxide layer. It was found that the refractive index varies with the oxide thickness, decreasing slightly with thinner oxides, as reported previously by Revesz et (1974 and 1976). The formation of Si-O-Ta bonds has been pointed to be responsible for this effect, and the

incorporation of silicon to the  $Ta_2O_5$  is noted for this interaction [Hirvonen, Revesz and Kirkendall, 1976].

Anodic titanium-tantalum films have been prepared in capacitor TM (tantalum-tantalum-oxide/metal) structures, by the standard sputtering and anodization The films had varying atom fractions of tantalum to titanium and the results gave an increased reliability (lower failure rate) under reverse bias, as compared with the tantalum oxide capacitors. Furthermore, it has proposed that alloying agents into tantalum have the effect increasing the symmetry οf the DC conductance characteristic at room temperature [Peters and Schwartz, 1977].

A conduction mechanism study of another potential insulator film, vanadium pentoxide (V2O5) indicated that for both forward and reverse bias (i.e., the gate is positive under forward bias) the I-V characteristic exhibited combination of different conduction and emission effects and that no single one could account for the carrier transport in the MOS structure. For example, under reverse bias conditions, the experimental I-V measurements showed that at low voltages (0.4 V) an Ohmic region exists; a Schottky type relation (log I is proportional to the square root of V) between 0.4-0.7 V; and a Square Law area for voltages above 1.25 V and then for higher voltages, a transition region in which the current passes from a Schottky type relation, to a linear one and then to a Square Law one. A similar situation exists under forward bias, with differences in the region

extensions and slopes of the I-V characteristic. Capacitance measurements, C-V plots, also indicate complex relationships with voltage and frequency. It was found that above a certain critical frequency, the capacitance became frequency independent, under both forward and reverse bias conditions. An inverse square law characteristic dominates the C-V relationship, with different slopes under forward or reverse bias, i.e., with forward bias the capacitance decreases with voltage, whereas with reverse bias, it increases voltage. A certain degree οf deviation from this relationship was found at voltages close to zero. A plot of the inverse square of the Capacitance vs. Voltage gave a curve which has a slope, such that when intersected at the ordinate (voltage) axis, gives a value Vb (the barrier height), independent of frequency [Mackus, Suli, Torok and Hevesi, 1977].

Thin film capacitors, fabricated by sputtering tantalum metal over glass substrates and then producing tantalum oxide by the anodization method, which gave a finished capacitor area of 0.1 mm², were used in the experimental determination of the AC properties of these. The effect of annealing the capacitors in nitrogen at temperatures between 250-350 C was studied, and the authors established that an improved capacitance stability, lower losses and better temperature coefficient of capacitance (TCC) was obtained after the nitrogen annealing. The metal deposition process, Magnetron Enhanced Sputtering (MES), proved to give better quality films, of lower DC leakage, than those prepared by

the conventional DC Diode sputter equipment [Rottersman, Bill and Gerstenberg, 1978].

Capacitors made of anodically oxidized tantalum nitride (TaN), using thin film technology have also successfully been fabricated on glazed ceramic substrates. Reactive sputtering of TaN is followed by anodic oxidation, with counterelectrodes deposited by evaporation. These capacitors showed superior performance as compared with the previous {Ta-oxide} metal capacitors. Lower TCC and dissipation factors were obtained, with high endurance at to heat treatment and improved reliabilty [Doken, Ohwada, Okamoto and Kamei, 1978].

Tantalum pentoxide also exhibits acousto-optic properties, and Bragg cells using a surface acoustic wave (SAW) have been fabricated for use in integrated optical RF spectrum analyzers. This oxide is representative of a group of materials (namely silicon nitride, zinc oxide and glass) which have low optical loss, refractive indices greater than SiO<sub>2</sub> and can be deposited by conventional techniques. For example, Ta<sub>2</sub>O<sub>5</sub> had an optical refractive index of 2.15, an optical loss of 1.5-2.0 dB/cm, a surface acoustic wave velocity of 3500-3700 m/s, and an acoustic loss of 7.0-7.5 dB/cm, when used in a thin film waveguide made on silicon substrates [Hickernell, Davis and Richard, 1978].

Double dielectric structures, which incorporate both  ${\rm Ta}_2{\rm O}_5$  and  ${\rm SiO}_2$  have been analyzed for potential use in nonvolatile memory devices. Anodic and thermal  ${\rm Ta}_2{\rm O}_5$  is formed over glass or silicon substrates, and then aluminium

electrodes are deposited for determining the characteristics of the insulator film. Theory predicts that by applying a voltage between the gate electrode and substrate, a charge can be stored at the interface between both insulators. this structure is used as the gate insulator in a MOS device, the presence of this charge affects the threshold voltage of the transistor. Hence, a memory cell can be constructed, as the presence or absence of the interface charge can define the logical state of the device. The Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> double conduction mechanism through the dielectric is, under high field conditions (i.e., the "write" cycle), Poole-Frenkel. At moderate fields, it is the temperature dependent ohmic component that predominates. Only MOS capacitors of Metal-Ta{oxide}-Si{oxide}-Silicon (MTOS) structure were used in the experimental work [Angle and Talley, 1978].

Thin film transistors, fabricated with anodized  $Ta_2O_5$  as gate insulator have been developed, which replaced the usual  $Al_2O_3$  and eliminated the frequent cleaning of masks during manufacturing. The gate insulator was developed from the anodization of tantalum oxynitride, which was used as the gate electrode. This combination produced matched temperature coefficients between gate insulator and electrode. The resultant anodic tantalum pentoxide had a high relative dielectric constant of 22, which produced devices with high transconductance, thus eliminating the necessity for double gate transistors [Kalfass and Lueder, 1979].

Experimental work of tantalum pentoxide films grown on GaAs substrates showed that good insulating films were obtained for both thermal and anodic oxides. The optical properties of these films indicate that a pronounced interaction takes place during the thermal growth of  ${\rm Ta}_2{\rm O}_5$ , similar to the interaction on silicon substrates. Better insulating properties were obtained with anodic processing of  ${\rm Ta}_2$  as a reduced film-substrate interaction was claimed, due to less incorporation of  ${\rm Ga}_2$  and/or  ${\rm As}_2$  into the tantalum pentoxide film. However, it was not possible to obtain MOS capacitance-voltage curves [Nishi and Revesz, 1979].

A microelectrode array, using Ta<sub>2</sub>O<sub>5</sub> on sapphire, was developed for production of localized electrical excitation of the fibre bundles in the auditory nerve. The array serves as the interface between the nervous system and the implanted electronics of an auditory cochlear prosthesis. The electrodes are made of tantalum metal, insulated from the conducting medium and from each other by anodically formed tantalum pentoxide, with an overall passivation of silicon nitride. This provided a structure with significant advance in the mechanical and electrical stability required to survive the continous electrical stimulation in the nervous system fluids without metal dissolution due to the inertness of tantalum and its oxides [May, Shamma and White, 1979].

Capacitors made with thin film anodic tantalum oxide were used for studying the efects of humidity on the failure rate of these. Two distinct failure modes were established:

point breakdown caused by randomly distributed weak spots resulting from material processing defects, and edge failures which are localized at the exposed edge of the counterelectrode when only subjected to reverse bias [Adolt and Melroy, 1980].

Α Dynamic Random Access Memory (DRAM) using the Quadruply Self Aligned (QSA) MOSFET and a stacked high storage capacitor was developed in the construction of a 256 kbit memory using 1.5  $\mu$ m double-polysilicon-Si process. The word line is polySi and the bit line is Al. The anodic capacitor uses Ta<sub>2</sub>O<sub>5</sub> as a high permittivity insulator, which is crucial in realizing the capacitance on the required small area of 7.4  $\mu m^2$ . The leakage current through the insulator was small enough that it did not affect the operation of memory cell, nor its hold time. Experimental 512 kbits and 1 Mbit integrated circuits have also been designed using the same technology [Ohta, Yamada, Saitoh, Shiraki, Nakamura, Shimizu and Tarui, 1980].

The conduction phenomena in tantalum pentoxide films shows that they obey the Schottky theory at low fields, and at higher fields, the Poole-Frenkel model prevails. However there is experimental evidence that an anomalous Poole-Frenkel conduction takes place at high fields in anodic  $Ta_2O_5$ . Heat treatment of samples using anodic tantalum films, reveals that an increase in conductivity takes place after 10 minutes in oxygen or vacuum, and if this time is exceeded in a second heat treatment in oxygen, the conductivity is decreased again. A shift from the anomalous

Poole-Frenkel into the normal one is then observed. These changes were attributed to variations in the donor density to trap density ratio and in the donor level energy [Matsumuto, Susuki and Yabumoto, 1980].

A new kind of thin film transistor (TFT) that uses a rather novel gate insulator, a thin polymer film of polytetrafluoroethylene (i.e., teflon) was fabricated to study the MIS structure using organic insulators. The insulator was applied by electron gun evaporation on a Te semiconductor substrate. However, the device showed instability after a few weeks of been fabricated, caused by slow drift in the insulator- semiconductor interface. This is an improvement over the previous TFT fabricated with the same polymer over a CdSe film, which was quite instable and deteriorated the device in a few days [De Vos and Hindryckx, 1980].

The optical and electrical properties of Ta thermal oxides have been determined by analyzing the films on silicon substrates by ellipsometric, C-V and I-V methods. The oxidation time for the tantalum films in dry oxygen was obtained by examination of the ellipsometric parameters Psi and Delta as a function of time. After a certain amount, they had a very slow rate of change, indicating that a complete conversion from metal to oxide had taken place. Any further change in these parameters could be attributed to annealing effects and slow changes in stoichiometry. In contrast with a previous work by Revesz et al., a tapered refractive index transition layer, represented by five

layers of 1.5 nm thick was found, instead of the graded refractive index through the oxide thickness. The C-V curves indicated the presence of a negative oxide charge at flatband, hysteresis and a relative dielectric constant of 26. The I-V curves revealed a two slope Schottky plot, which is typical of tantalum pentoxide films [Smith and Young, 1981].

Metal-Insulator-Metal (MIM) devices have been developed for use as non-linear devices in multiplexing Liquid Crystal Displays (LCDs). A MIM device, using Ta<sub>2</sub>O<sub>5</sub> as the insulator, was optimized for this application, by partially anodizing a sputtered metal film on a glass substrate. A computer program was used to determine the parameters in the Poole-Frenkel conduction model to optimize the performance of the MIM switch. Furthermore, nitrogen doping enhanced the conductivity parameter for better multiplexing [Baraff, Long, MacLaurin, Miner and Streater, 1981].

Waveguide films prepared with tantalum pentoxide over  $SiO_2$  are important, since this class of thin films has a wide range of refractive index with low propagation loss (less than 1 dB/cm at 633 nm wavelength). Irradiation using a  $CO_2$  laser produces a decrease in the refractive index, up to 2%. This decrease is considered to be related to the  $Ta_2O_5$  crystallization process from its amorphous state, when exposed to intense laser radiation. This in turn affects the permittivity of the tantalum oxide [Terui and Kobayashi, 1981].

Bismuth oxide is another insulator material that has

been used in the fabrication of Metal-Insulator-Semiconductor (MIS) capacitors. The film was deposited by reactive ion sputtering and later annealed in air. The  $Bi_2O_3$  capacitor yielded a relative dielectric constant of 25, and a  $\tan\delta$  (loss factor) of 0.002 at 35 kHz, making it useful for production of low frequency capacitors. The C-V curves show a shift in the negative direction with relatively small hysteresis [Raju and Talwai, 1981].

films are tantalum deposited over substrates by sputtering, a stress field is induced, which produces a curvature of the substrate. A MIS device was used as a photovoltaic cell in order to study the stress in its performance. Ιt was found that the induced stress produced large changes in the minority carrier diffusion length and recombination time, as well as the recombination time and capture cross section. Moreover, the short circuit current, open circuit voltage and fill factor were reduced [Lalevic and Murty, 1981].

Indium phosphide, InP, was anodically oxidized to form an gate insulator in a MOSFET accumulation mode device. The oxide had low enough interface state density to be used as gate insulator. No C-V or I-V data was reported, and the oxide required annealing in order to reduce the C-V hysteresis loop. The device had a gate length of 500  $\mu$ m and a gate width of 2 mm. The measured estimated electron mobility,  $\mu$ eff, was 1500 cm²/Vs [Yamamoto and Uemura, 1981].

GaAs technology for Microwave Integrated Circuits (MICs) makes use of high quality tantalum oxide capacitors

in interstage coupling of microwave amplifiers. The capacitor has a Metal-Insulator-Metal (MIM) structure and they were integrally sputtered (reactively) on the semi-insulating GaAs substrate. A staircase shape is then formed by lift-off and patterning. Typical capacitances in the range of 50-200 pF were obtained, with an oxide thickness of 150 nm, a relative dielectric constant of 20-25 and a loss factor ( $\tan \delta$ ) of 0.03 at 1 MHz. The leakage current had an exponential relation with applied voltage [Elta, Chu, Mahoney, Cerretani and Courtney, 1982].

Anodization of aluminium has also produced dielectrics for MIC capacitors, in the form of  $Al_2O_3$ , with a typical value of 30 pF, and a relative dielectric constant of 8. The figure of merit  $\epsilon$ rE, the product of the relative permittivity and the dielectric strength, indicates the quality in terms of bandwidth and area for a given material [Binet,1982].

Further work in the Ta<sub>2</sub>O<sub>5</sub> MIC capacitors indicates that a two stage monolithic IF amplifier, operating in the 1.2 to 2.8 GHz range and using these as coupling elements, is quite feasible. The reactive MIM process produced a capacitance density of 1500 pF/mm<sup>2</sup>, and a very good quality dielectric was obtained with an insertion loss of 1 dB at 16 GHz for a 29 pF capacitor [Chu, Mahoney, Elta Courtney, Finn, Piacentini and Donnelley, 1983].

Ion Sensitive Field Effect Transistors (ISFET's), fabricated with SOS (silicon on sapphire) technology and tantalum pentoxide as gate insulator produced the highest pH

sensitivity among three other dielectrics. ISFETs do not have a metal gate electrode, and it is the electrolyte in which they are immersed which acts as the gate electrode, making them very useful as pH detectors. The  $Ta_2O_5$  gate ISFET exhibits a linear relation between output voltage and the solution pH, with a 90% response time of a few seconds. It was concluded that the  $Ta_2O_5$  film was the most suitable as sensing material for hydrogen activity measurements [Akiyama, Ujihira, Okabe Sugano and Niki, 1982].

Langmuir-Blodgett films are single molecular layers, formed by the removal of a amphiphilic molecule from an aqueous solution with a polar substrate (i.e., aluminium amphiphilic molecule is a simple fatty acid, oxide). The which has a hydrophilic termination immersed in the aqueous solution and a hydrophobic end in the air. The relative permittivity of such a molecule can be selected by choosing suitable CH2 chain length and by substituting a divalent ion bond for for the hydrophilic termination. A thin film using amorphous silicon and L-B film techniques as gate insulator was developed. The L-B layer not only is pinhole free but also has a high dielectric breakdown strength and exhibits many of the characteristics of an ideal gate insulator. [Pitt, 1983; Lloyd, Petty and Roberts, 1983]

Further analysis of thermal  ${\rm Ta}_2{\rm O}_5$  films on silicon substrates show that the amount of silicon incorporated to the oxide depends on the residual pressure during the tantalum metal evaporation. As the vacuum quality is reduced, less amount of silicon is incorporated to the

oxide. Also, it was found that the the relative dielectric constant and the leakage current decrease as the amount of Si increases in the oxide film. [Hasegawa, Ogawa, Wada and Nakano, 1983].

An interesting technique for growing a heteromorphic dielectric layer,  $Ta_2O_5$  over  $SiO_2$ , was developed for producing high quality storage capacitors for a VLSI dynamic RAM. The technique is based in the oxidation of a silicon substrate covered with a thin  $Ta_2O_5$  layer. The interfacial oxidation of Si takes place by wet oxidation, and a high quality double dielectric is then produced, thus avoiding separate oxidations of Ta and Si. A memory cell was fabricated using this technique [Kato, Ito, Taguchi, Nakamura and Ishikawa, 1983].

A thin film transistor (TFT) with tantalum pentoxide as gate insulator and deposited by Magnetron Enhanced Sputtering has recently being developed. The device has a p-channel structure, with a fused quartz substrate and Al doped source and drain regions. Reactive Ion Etching (RIE) was used to pattern the  $Ta_2O_5$ . The device exhibits a threshold voltage of -2.5 V and a transconductance of  $70\mu S$ . The fabrication of the device allowed a maximum temperature of 625C, which is compatible with glass substrates and tantalum pentoxide [Seki, Unagami and Tsujiyama, 1984].

#### CHAPTER 3

# THE THEORY OF THE Ta<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub> DOUBLE DIELECTRIC STRUCTURE

Considerable amount of work was done in double dielectric insulators, which were based on the Nitride-Oxide-Silicon (MNOS) system -used in memory devicessuch as non-volatile dynamic and static cells in Electrically Programmable Read Only Memories (EPROMs). The MNOS Memory Transistor was studied by Wallmark and Scott (1969), Ross (1969) and Frohman-Bentchkowsky (1970). The theoretical aspects of this device have great importance, as the MNOS and MTAOS behaviour is quite similar, although not identical. They also have in common a thin layer of SiO2, immediately above the substrate. The electrical performances similar, and Angle (1976) established that devices could also be fabricated using MTAOS technology, which had superior characteristics over the MNOS device.

The double heteromorphic Ta{ox}/Si{ox} dielectric structure has been developed as a result of investigations on large permittivity insulating thin films for applications in MOS Capacitors [Angle, 1976], memory devices [Angle and Talley, 1978] and more recently storage MOS capacitors for dynamic Random Access Memories of VLSI proportions [Ohta et al.,1982].

Generally speaking, the Metal-Double Insulator-Semiconductor (MDIS) structures have similar properties, namely a

dissimilar field distribution in each insulator, different electronic conduction (emission) mechanisms and under certain conditions, a charge retention or memory effect.

Several areas of common interest to microelectronics and the research in double insulating structures are identifiable:

- 1) The LSI and VLSI densities require increase device scaling.

- 2) Further scaling in MOS devices requires thinner oxides and insulators.

- 3) Device scaling decreases the maximum gate voltage due to insulator breakdown.

- 4) Insulators of large dielectric constant produce the required capacitance in proportionally less area, but in most cases an increase in leakage current is observed.

- 5) Breakdown of a thin scaled down oxide can be avoided if a larger permittivity insulator is placed between itself and the gate electrode.

- 6) The large dielectric constant of Tantalum Pentoxide can be combined with the excellent insulating properties of Silicon Dioxide, thus producing a double dielectric with a breakdown voltage governed by the high permittivity oxide thickness, while maintaining a low level of leakage current.

- 7) In the double insulator structure, the probability of pinholes coinciding in the same location is negligible, thus producing a better quality insulator.

- 8) Amorphous Silicon Dioxide is structurally porous and it has high permeability to water vapour and migration of alkali ions. The application of a second outer dielectric reduces these effects. Tantalum Pentoxide has a much denser structure, possibly retarding the ion migration through it.

- 9) Double dielectric stuctures exhibit memory effects, hence they can be used as memory cells if properly designed.

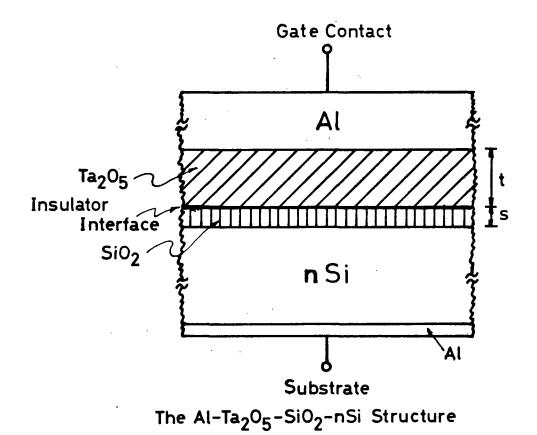

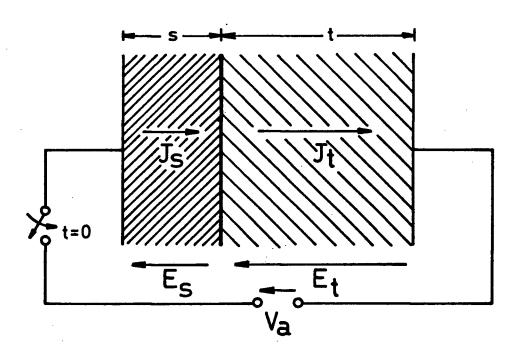

this work, our main effort is concentrated in the Ιn a Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> insulator for development of applications as opposed to a memory cell for either RAMs or DRAMs. The MOSFET device that incorporates the tantalum pentoxide-silicon dioxide gate insulator is termed a Metal-Tantalum{Oxide}- Silicon{Oxide}-Silicon device, or MTAOS structure. The inner insulator is immediately above the substrate, and the outer insulator is below the gate contact electrode. Figure 3.1 gives a cross section of such a double dielectric, with the main features and dimensions shown. The critical areas are the interfaces between the Ta<sub>2</sub>O<sub>5</sub> and SiO<sub>2</sub> insulators and to a lesser degree, the interface between the top (gate) electrode and the Ta<sub>2</sub>O<sub>5</sub>. The interface between SiO<sub>2</sub> and the silicon substrate is well known [Grove et al., 1964; Grove et al., 1965; Gray, 1969] and it is not analyzed here.

Of great importance is the physical model for carrier transport under steady state and transient conditions. The

Figure 3.1 The General Double Dielectric Structure.

differences in the composition of each dielectric makes the exact analysis quite complicated, particularly for transient case. When a voltage is applied to the double insulator structure, conduction currents flow, however, mechanism that governs these are quite different for the tantalum pentoxide and silicon dioxide. The dominant current transport mechanism for SiO<sub>2</sub> has been established to limited due to electrode Fowler-Nordheim emission [Lenzlinger and Snow, 1969]. This type of conduction mechanism is caused by tunneling through the barrier into the insulator conduction band. In the case of Ta<sub>2</sub>O<sub>5</sub>, carrier transport is bulk limited by Poole-Frenkel type emission [Mead, 1962; Angle, 1976; Angle and Talley, 1978], although it is greatly influenced by the existence of trapping centres. For example, if the trapping density low, normal Poole-Frenkel conduction takes place, but if it is high (as compared with the donor density), compensated or anomalous Poole-Frenkel emission dominates. Anodic tantalum oxide follow these considerations, however the thermal tantalum oxide exhibits a more complex behaviour, depending on the sign of the applied bias. Angle (1976) explained this complex behaviour by observing that positive gate bias, normal P-F conduction takes place, but under negative bias space charge limited conduction determines the current flow, attributed to surface states formed at the Al{qate}-Ta<sub>2</sub>O<sub>5</sub> interface. The Poole-Frenkel effect represents the increase in electrical conductivity by lowering the Coulombic potential barrier, when it interacts

with an electric field. Space charge conduction results from carriers injected into the insulator where there is no compensation charge present.

Considering the displacement and conduction current density contributions by virtue of the Ramo-Shockley theorem, the terminal currents for the  ${\rm Ta}_2{\rm O}_5$  and  ${\rm SiO}_2$  insulators can be expressed as:

$$I_{t} = A_{t} \left( \frac{\varepsilon_{t}}{t} \frac{dV_{t}}{d\tau} + \frac{1}{t} \int_{0}^{t} j_{t}(z) dz \right)$$

(3.1a)

$$I_s = A_s \left( \frac{\varepsilon_s}{s} \frac{dV_s}{d\tau_t} + \frac{1}{s} \int_0^s j_s(z) dz \right)$$

(3.1b)

Where At and As are the cross section areas;  $\epsilon t$  and  $\epsilon s$  are the  $Ta_2O_5$  and  $SiO_2$  dielectric constants; t and s are the insulator thicknesses; Vt and Vs are the resulting voltages in each insulator and the variable  $\tau$  represents time. The term jt(z) is the conduction current density in the tantalum pentoxide, given by the Poole-Frenkel effect, and js(z) is the conduction current density in the silicon dioxide and determined by Fowler-Nordheim tunneling. The dependency on the variable z indicates that a current density distribution exists along that axis.

In the Poole-Frenkel emission, the current density usually can be expressed as:

$$J_{t} = C_{pf} E_{t} \exp \left(-\frac{q}{kT} \left(\psi_{B} - \sqrt{qE_{t}} / \pi \varepsilon_{i}\right)\right) \quad (3.2)$$

Where Et is the electric field in the tantalum pentoxide and the quantity  $\psi_{_{\mathbf{R}}}$  represents the barrier height.

For the Fowler-Nordheim emission, the current density is expressed as:

$$J_s = C_{fn}E_s^2 \exp(-E_o/E_s)$$

(3.3)

Where Es is the field in the silicon dioxide. The characteristic constants Cfn and Eo depend on the effective mass and barrier height. Notice that in both cases, the current densities are strong functions of the applied field. Furthermore, upon the application of a gate voltage Va to the double insulator structure, an electric field is created in each individual insulator. Gauss' Law prescribes that the continuity of the displacement D at the interface between insulators shall be maintained:

$$\varepsilon_{t}^{E}_{t} - \varepsilon_{s}^{E}_{s} = \frac{Q_{i}}{\varepsilon_{0}}$$

(3.4)

Qi is the charge per unit area at the interface. The sum of the voltage drops across each dielectric has to be equal to the total applied voltage. Then, considering the metal semiconductor work function  $\phi$ ms, we have:

$$V_a = -tE_t - sE_s + \psi_s + \phi_{ms}$$

(3.5)

The silicon surface potential is represented by  $\psi s$  and the conventional definition of potential difference (drop) is used.

Finally, the electric charge has to be conserved at all times:

$$J_{t} - J_{s} = \frac{\partial Q_{i}}{\partial T}$$

(3.6)

In general, an interface charge Qi will appear between both dielectrics, at the interface. The dependence of this interface charge upon time and geometry of the insulating structure, can be obtained by simultaneous solution of Equations 3.4, 3.5, 3.6, and considering the P-F Ta<sub>2</sub>O<sub>5</sub> emission and the F-N mechanism in the SiO<sub>2</sub>; not an easy task!

### {3.1} STEADY STATE ANALYSIS:

The different conduction mechanisms responsible for the current transport in the  $SiO_2$  and  $Ta_2O_5$  are also the cause for creating an accumulation of carriers at the interface between dielectrics. Upon the application of an external field, caused by the gate voltage, electronic conduction following the Fowler-Nordheim emission takes place in the silicon dioxide and conduction following Poole-Frenkel takes place in the tantalum pentoxide. These being quite different, create a current discontinuity, which leads to a charge accumulation at the interface. This charge

accumulation, in turn, adjusts the electric field distribution, until current continuity is established.

The solution obtained by steady state analysis gives the electric field in each dielectric Et and Es, as well as the charge at the interface Qi. Under steady state conditions, both currents Js and Jt are equal, and therefore, the charge at the interface is negligible. By substituting these conditions in Equations 3.4 and 3.5 above, we obtain the field Es in the SiO<sub>2</sub>:

$$E_{s} = -\frac{(V_{a} - \psi_{s} - \phi_{ms})/s}{1 + \frac{t}{s} - \frac{\varepsilon_{s}}{\varepsilon_{t}}}$$

(3.7)

$$r = \frac{1}{1 + \frac{t}{s} - \frac{\varepsilon_{s}}{\varepsilon_{+}}}$$

(3.8)

This last equation represents the reduction in the  $SiO_2$  electric field due to the addition of a second dielectric of thickness t and relative permittivity  $\epsilon$ t. Using values of  $\epsilon$ s=3.8,  $\epsilon$ t=27, s=200 A, and t=1000 A, a reduction factor of 0.587 is obtained.

By similar reasoning we obtain the field Et in the Ta<sub>2</sub>O<sub>5</sub>:

$$E_{t} = \frac{(V_{a} - \psi_{s} - \phi_{ms})/t}{1 + \frac{s}{t} - \frac{\varepsilon_{t}}{\varepsilon_{s}}}$$

(3.9)

On the other hand, if the interface charge Qi is non-zero,

the internal electric fields due to this charge, can be calculated in each individual dielectric:

For the Ta<sub>2</sub>O<sub>5</sub> insulator:

$$E_{t} = -\frac{Q_{i}/\varepsilon_{o} + \frac{\varepsilon_{s}}{s}(\psi_{s} + \phi_{ms})}{\varepsilon_{t} + \frac{t}{s}\varepsilon_{s}}$$

(3.10)

For the SiO<sub>2</sub> insulator:

$$E_{s} = + \frac{\varepsilon_{t}}{\varepsilon_{s}} + \frac{\varepsilon_{t}}{\varepsilon_{t}} + \frac{\varepsilon_{t}}{\varepsilon_{s}}$$

$$(3.11)$$

## {3.2} TRANSIENT ANALYSIS:

Upon the application of a sudden voltage at the gate, both insulators will have certain fields applied and conduction currents will flow as prescribed before. The Law of Conservation of Charge requires that:

$$\frac{dQ_{i}(V_{a},\tau)}{d\tau} \stackrel{\neq}{=} J_{t}(V_{a},\tau) - J_{s}(V_{a},\tau)$$

(3.12)

The rate of change in the interface charge will be directly proportional to the difference in current density for both dielectrics, at a given applied gate voltage and time. The solution to this partial differential equation of two independent variables can be obtained if more information of the detailed conduction mechanisms is available. For example

Ross and Wallmark (1969) studied the transient behaviour of a MNOS structure, and explained the conduction mechanism at the interface between dielectrics, as a function of trapping centres of the donor type which communicate with the silicon, when a field is applied to the structure. In their mathematical derivation, they assumed a monoenergetic trap level, and the charge transfer was assumed to be through direct tunneling between trap states in the composite insulator. These authors obtained a relation for the transferred charge, that depended logarithmically on the applied gate pulse duration and exponentially on the amplitude of the applied gate pulse.

Considering the fact that the interface charge is a function of applied voltage and time, if Equation 3.4 is substituted in Equation 3.5, the general time varying solution is found for both insulator electric fields:

$$E_{t} = -\frac{(V_{a} - \psi_{s} - \phi_{ms})}{t + s - \frac{\varepsilon_{t}}{\varepsilon_{s}}} + \frac{Q_{i}/\varepsilon_{o}}{\varepsilon_{t} + \frac{t}{s} \varepsilon_{s}}$$

(3.13)

$$E_{s} = -\frac{(V_{a} - \psi_{s} - \phi_{ms})}{t - \frac{\varepsilon_{s}}{\varepsilon_{t}} + s} - \frac{Q_{i}/\varepsilon_{o}}{-\frac{s}{t} \varepsilon_{t} + \varepsilon_{s}}$$

(3.14)

Where the relation Qi=Qi(Va,t) is valid for t>to, the instant of gate voltage application.

Then the corresponding voltages across each dielectric are given by:

$$V_{t} = \frac{(V_{a} - \psi_{s} - \phi_{ms})}{\{1 + \frac{s}{t} - \frac{\varepsilon_{t}}{\varepsilon_{s}}\}} = \frac{Q_{i}/\varepsilon_{o}}{\{\varepsilon_{s}/s + \varepsilon_{t}/t\}}$$

(3.15)

$$V_{s} = \frac{(V_{a} - \psi_{s} - \phi_{ms})}{\{1 + \frac{t}{s} \frac{\varepsilon_{s}}{\varepsilon_{t}}\}} = \frac{Qi/\varepsilon_{o}}{\{\varepsilon_{s}/s + \varepsilon_{t}/t\}}$$

(3.16)