# A FAMILY OF PROTOCOL TESTING TECHNIQUES

by

WENDY YUEN-LING CHAN

B.A.Sc., The University of British Columbia, 1987

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES (DEPARTMENT OF ELECTRICAL ENGINEERING)

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

August 1989

© Wendy Yuen-Ling Chan, 1989

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of ELECTRICAL ENGINEERING

The University of British Columbia Vancouver, Canada

Date 1989 AUGUST 10

#### ABSTRACT

This thesis developed three testing techniques that are applicable to the conformance testing of protocols: the UIOv-method, the eUIOv-method and the hybrid technique.

The UIOv-method is for testing simple modelled by finite state machines (FSMs). Any protocol that passes its tests possesses an FSM skeleton that is identical The UIOv-method is extended to the to the specified FSM. eUIOv-method to test more complex protocols that can be modelled by extended FSMs (EFSMs). A data flow testing procedure (DFTP) based on static data flow analysis and FSM testing is developed in this thesis to test the flow of parameters and variables in a protocol. This procedure is augmented with the eUIOv-method to form the hybrid technique which is directly applicable to the testing of complex protocols implemented according their to Estelle The technique captures specifications. protocols with erroneous EFSM control structures that cannot be detected by existing testing methods developed by Sarikaya and Ural.

KEYWORDS: conformance testing, protocols, Estelle, finite state machines, unique input/outputs, extended finite state machines, data flow, fault coverage, protocol specification.

# TABLE OF CONTENTS

| Abstractii                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Table of Contentsiii                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| List of Figuresvi                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| List of Tablesvii                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Acknowledgementviii                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 2 The UIOv-Method.       .8         2.1 The Finite State Machine Model       .9         2.2 FSM Testing Techniques       .11         2.2.1 The T-Method.       .11         2.2.2 The W-Method.       .11         2.2.3 The D-Method.       .12         2.2.4 The U-Method.       .13         2.2.5 Comments on the Four Methods       .14         2.2.5.1 Applicability       .14         2.2.5.2 Fault Coverage       .15               |  |  |  |  |

| 2.3 The Shortcoming of the U-Method       18         2.3.1 Assumptions       18         2.3.2 The UIOS Problem       19         2.3.3 The State Signature Problem       23         2.4 The UIOv-Method       25         2.4.1 Uniqueness Problem Analysis       26         2.4.2 Uv       27         2.4.3 IO(S,K)s       28         2.4.4 Comparing the UIOv-Method with the Others       31         2.5 Unique Test Sequences       33 |  |  |  |  |

| 2.6 FSM Testing                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 3 Testing Extended Finite State Machines                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

# Table of Contents

| 4 Data Flow Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 3.3.2 Verification of TSS Variables       48         3.3.2.1 Verification of N.TSSs       49         3.3.2.2 Verification of C.TSSs       51         3.3.2.3 UIOSs for TSSs       53         3.3.4 An Evample       57         3.3.5 Summary of the eUIOv-Method       61         3.4 Fault Coverage       62                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 Background       82         5.1.1 Estelle       82         5.1.2 Normal Form Estelle Specifications       84         5.1.2.1 Example of an NFS       85         5.2 Refining the NFS       87         5.2.1 Canonical Transitions       87         5.2.2 Reformatting the NFS       89         5.2.2.1 Executability Problems       89         5.2.2.2 The Reformatted NFS       90         5.2.2.3 The Enabling Conditions       91         5.2.2.4 The Def Statements       91         5.2.2.5 Format of the rNFS       92         5.3 Estelle EFSM Testing       94         5.3.1 Spontaneous Transitions       96         5.3.2 Testing the EFSM in the COTP       97         5.4 Estelle Data flow Testing       105         5.4.1 Data Flow Testing for the COTP       107         5.5 Chapter Summary       119         6 Evaluation and Comparison of the Hybrid Technique       120         6.1 Evaluation       120         6.1.2 Executability       121         6.1.3 Applicability       122         6.1.4 Test Data Selection       123         6.1.5 Testability       124 | 4 | 4.1 Static Data Flow Analysis       65         4.2 Data Flow Paths       66         4.3 Data Flow Testing       67         4.4 The Data Flow Testing Procedure       70         4.5 An Example       72         4.6 Chapter Summary       75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 | 5.1 Background       82         5.1.1 Estelle       82         5.1.2 Normal Form Estelle Specifications       84         5.1.2.1 Example of an NFS       85         5.2 Refining the NFS       87         5.2.1 Canonical Transitions       87         5.2.2 Reformatting the NFS       89         5.2.2.1 Executability Problems       89         5.2.2.2 The Reformatted NFS       90         5.2.2.3 The Enabling Conditions       91         5.2.2.4 The Def Statements       91         5.2.2.5 Format of the rNFS       92         5.3 Estelle EFSM Testing       94         5.3.1 Spontaneous Transitions       96         5.3.2 Testing the EFSM in the COTP       97         5.4 Estelle Data flow Testing       105         5.5 Chapter Summary       119 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6 | 6.1 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | Table of Concents                     |

|------------------------|---------------------------------------|

| 7.1 Thesi<br>7.2 Futur | s Summary                             |

| Bibliography           | 7                                     |

| Appendix A             | NFS OF CLASS 0 TRANSPORT PROTOCOL141  |

| Appendix B             | rNFS OF CLASS 0 TRANSPORT PROTOCOL147 |

# LIST OF FIGURES

| 2.1 | An FSM specification20                             |

|-----|----------------------------------------------------|

| 2.2 | A faulty IUT of the FSM in Figure 2.121            |

| 2.3 | An FSM with no UIOS for state C24                  |

| 2.4 | A faulty implementation of the FSM in Figure 2.325 |

| 2.5 | A simple FSM with an inherent UTS35                |

# LIST OF TABLES

| 2.1 | U-method test sequence for the FSM in Figure 2.121     |

|-----|--------------------------------------------------------|

| 2.2 | D-method test sequence for Figure 2.122                |

| 2.3 | U-method test sequence for FSM in Figure 2.324         |

| 2.4 | UIOv-method test sequence for the FSM in Figure 2.128  |

| 2.5 | UIOv-method test sequence for the FSM in Figure 2.330  |

| 3.1 | An EFSM table44                                        |

| 5.1 | EFSM table for the Class 0 Transport Protocol95        |

| 5.2 | Augmented EFSM table for Class 0 Transport Protocol109 |

## ACKNOWLEDGEMENT

I would like to thank Dr. Son Vuong for his guidance and for his constant encouragements that I publish my work. I would like to thank Dr. Mabo Ito for his careful reading of this thesis and for his help in improving my writing tremendously. I would like to thank Dr. Sam Chanson and Jianping Wu for many helpful discussions and for their moral support during difficult times. Also, a very special thank you to Dr. Gunther Schrack, without him, I would not have been able to become a graduate student.

I would like to thank the Natural Sciences and Engineering Council of Canada and Idacom Electronics Limited for their support in the form of an University and Industry Cooperative Research Grant.

Lastly, many heartfelt thanks to my parents for their immeasurable love and understanding; and especially to my brother, Ramsey, and my fiance, Dawson, for their continuous moral support and their immense faith in me; without them, this work would not have been possible.

During conformance testing, the protocol implementation under test (IUT) is typically considered as a "black box" since its source code is generally not accessible. Testing is carried out using test sequences. A test sequence is a sequence of input/output (I/O) pairs derived from the protocol specification. Test inputs are applied to the IUT via its input port. The outputs generated by the IUT are received via its output port and compared with the corresponding outputs in the test sequence. If they match, the IUT is said to conform to the specification.

The ability of a test to detect non-conforming or erroneous IUTs during testing depends solely on the test sequence used. Recently, test sequence generation has received much attention from the research community; in particular, sequences generated from the formal specification of protocols. The formal specification language of interest in this thesis is Estelle. In Estelle, the control structure of the protocol is modelled as an extended finite state machine (EFSM) while the data flow aspect of the protocol is described by a set of Pascal statements.

#### 1.1 PAST TEST GENERATION EFFORT

Recent work on test sequence generation based Estelle protocol specifications include those of Sarikaya [Sari87] and Ural [Ural88], both of whom emphasize the data flow aspect of protocols and both of whom work from normal form Estelle specifications [Sari86]. Other notable test sequence generation techniques that are applicable Estelle protocol specifications include those developed for testing finite state machines (FSMs) [Kou87, Sari82, These include the T-method [Nait81]; the W-method [Chow78, Sidh89], the D-method [Gone70], and the U-method [Sabn88, Aho88]. Their applications to protocol conformance testing were extensively studied in [Sidh89]. These methods examine only the control structure of protocols; they ignore interaction primitive parameters and may face executability problems when applied to Estelle specifications. However, these methods are directly applicable to the testing of simple protocols that can be modelled by FSMs.

#### 1.2 THESIS GOAL

The goal of this thesis is to develop testing techniques for the conformance testing of protocols such that maximum fault coverage can be achieved. Fault coverage is defined in this thesis according to the specifications of

the protocols used. The following two issues are not of primary concern in here: test sequence optimization and test architecture.

Problems in the generation of conformance sequences generally fall into two categories: coverage and optimization. While coverage deals with how to generate test sequences to achieve a particular fault coverage, optimization deals with how to optimize a given test sequence. Although optimization is necessary to reduce the cost of a test, it is secondary to coverage. Only when a desirable fault coverage is achieved should optimization This thesis thus focuses on the more important follow. coverage issue in test sequence generation. Some sample test sequences generated in this thesis are not optimized so that their intents may be easily followed.

In testing the IUT of a protocol that belongs to the Open System Interconnection (OSI) Reference Model [Zimm80], an upper tester and a lower tester are assumed to be available in this thesis to provide control and observation at the upper and lower interfaces of the IUT.

## 1.3 THESIS CONTRIBUTIONS

This thesis contributes to solving the problem of generating conformance test sequences for protocols from their specifications in the following ways.

This thesis found the original U-method to be inadequate and modified it so that it is now capable of detecting all I/O errors as well as state errors [Chan89b]. Its fault detection capability is now equivalent to those of the W- and D-method. The D-method and W-method are actually special cases of the modified U-method (UIOv-method) developed in this thesis where the UIOv-method enjoys the applicability advantage of the W-method and the length advantage of the D-method while providing full fault coverage.

This thesis introduced the concept of unique test sequences (UTSs). These are test sequences unique to the specified FSM from which they are generated. Any FSM that passes a test using an UTS possesses a FSM skeleton identical to the specified FSM.

This thesis extended the UIOv-method to produce the eUIOv-method for testing protocols that can be modelled by EFSMs.

This thesis developed a data flow testing procedure based on static data flow analysis where each definition and

usage of a variable are exercised during testing and, whenever possible, they are verified as well.

This thesis created a hybrid test sequence generation technique by augmenting the eUIOv-method with the data flow testing procedure. This hybrid technique is applicable to testing the EFSM control structure of a protocol as well as its data flow; hence, it is directly applicable to IUTs that are implemented according to their Estelle specifications. During testing, the IUT is checked for each transition in its Estelle specification. Each statement in the transition is exercised as well as verified whenever possible.

This thesis refined and reformatted the normal form of Estelle so that its transitions are in canonical form and its format explicitly brings out the underlying EFSM and data flow in an Estelle specification.

The hybrid technique was tailored for protocols with underlying EFSM control structures, this technique is thus capable of detecting faulty IUTs with erroneous EFSMs that would otherwise be missed by the techniques developed by Ural and Sarikaya. Since the hybrid technique also includes data flow testing, it is capable of detecting certain types of data flow errors in an IUT that would otherwise be missed by FSM testing techniques.

Test sequences generated by the hybrid technique are also applicable to IUTs not implemented according to their Estelle specifications. The fault coverage achieved would be limited to faults in the flow of data; sequencing faults may or may not be captured.

#### 1.4 THESIS ORGANIZATION

The remainder of this thesis is organized as follows. Chapter 2 discusses FSM test sequence generation techniques and presents the UIOv-method as well as the UTS concept. chapter 3, a brief introduction to EFSMs is followed by a discussion of extending the UIOv-method to the eUIOv-method for the testing of protocols modelled by EFSMs. Chapter 4 provides a brief review of static data flow analysis and shows how the data flow testing procedure is developed from it. In chapter 5, the hybrid technique is discussed and applied to Estelle using the Class O Transport Protocol as an example. An evaluation and a comparison of the hybrid technique with existing test sequence generation techniques applicable to Estelle protocol specifications are presented Chapter 7 concludes this thesis with a in Chapter 6. summary of its contributions and a discussion of possible future work in the area of conformance testing.

## 2 THE UIOV-METHOD

generation techniques developed sequence state machines (FSMs) may be used to generate conformance test sequences for those protocols that can be modelled as FSMs. This chapter looks at a recent study done by Sidhu [Sidh89] on this approach to conformance generation. Four notable test generation methods compared in that paper: the T-method, the D-method, the Wmethod and the U-method. In general, the D-method hampered by its limited applicability while the W-method is undesirable because of the lengthy test sequences generates. The T-method, on the other hand, has neither one of the above problems; however, it generally cannot achieve full fault coverage. The most recent method, the U-method, is more widely applicable than the D-method and it generates shorter test sequences than those generated by the W-method. Fault coverage produced by the U-method was found to be full in [Sidh89]. The U-method thus seemed to be the best of the four methods.

This chapter shows that the U-method does not always achieve full fault coverage; it points out a shortcoming with the U-method [Chan89b] that sometimes hampers its fault detection capability. The U-method is then revised with the addition of a verification procedure in here to form the

UIOv-method [Chan89b] which corrects the problem and produces full fault coverage each time. The resulting UIOv-method is still more widely applicable than the D-method and it generally produces shorter test sequences than the W-method does.

All test sequences generated by the D-method, W-method and UIOv-method possess a property that is responsible for their full fault coverages. This property distinguishes these sequences to be unique test sequences (UTSs) [Chan89b], and it guarantees the detection of any erroneous IUT provided that the number of states in the IUT does not exceed that which is in the FSM specification. This concept of UTSs is also reviewed in this chapter.

# 2.1 THE FINITE STATE MACHINE MODEL

A finite state machine (FSM) can be represented as  $F=\{S,I,O,T,A\}$  where S denotes the set of states, I denotes the set of inputs, O denotes the set of outputs, T denotes the state transition function which produces a new state based on the current state and the current input, and A denotes the action function which produces an output based again on the current state and the current input.

An FSM can also be represented by a collection of transitions each of which performs an output operation and a

state transition provided that an input event is correctly received at the appropriate starting state. This representation can be presented in a tabular or graphical In the tabular format, each column is labelled by a state to denote the starting state of a transition. row is labelled by an input operation. Each transition is denoted by a table entry identified by its output operation and the next state. The graphical format is denoted by G=(N,E), where N is a set of nodes representing the states of the machine and E is a set of arcs representing the set of transitions. Each arc starts at the starting state of the transition and ends at its final state. Each arc is identified by the input event that triggered the transition and the output event produced.

The FSM models considered in this thesis are assumed to be minimal and strongly connected Mealy machines that may or may not be completely specified. A Mealy machine, M, is an FSM whose set of outputs is dependent on the set of states as well as the set of inputs. The Mealy machine is minimal, or reduced, implies it does not have equivalent states; that is, it has the smallest number of states possible. Machine M is completely specified if an output is specified for each input in I for each of the states in S. A strongly

connected machine possesses an input sequence which traverses between any two states in the machine.

## 2.2 FSM TESTING TECHNIQUES

There are four notable test sequence generation techniques for FSMs: the T-method, the W-method, the D-method and the most recent method, the U-method.

# 2.2.1 The T-Method

The T-method [Nait81] is the simplest of the four methods. This method is applicable to any strongly connected FSM. It generates a test sequence, called a transition tour, by applying random inputs to an FSM until every transition is traversed at least once.

There are two disadvantages to using the T-method. One is the test sequences generated may contain redundant inputs. The other being the test only checks for the existence of transitions; it does not verify that the states in each transition are correct. As a result, the T-method may not detect state errors; it detects only output errors.

## 2.2.2 The W-Method

The original PW-method [Chow78] was slightly modified in [Sidh89] to form the W-method, which is a checking

experiment that uses the W-set for state identification. A checking experiment is a test procedure which verifies that each input specified for a state produces the expected output and takes the FSM to the correct next state. In the first part of a checking experiment, each state in the FSM is identified using a chosen characterizing I/O sequence. In the second part of the experiment, each I/O operation and the final state in each transition in the FSM are verified.

The W-set is also known as the characterization set. It is a set of input sequences which is composed of, for every pair of states in the FSM, at least one input sequence that can distinguish them. Every minimal, strongly connected and completely specified FSM possesses a W-set. Of the four methods, the W-method produces the longest test sequences. It is capable of detecting all faults in an FSM with a number of states not exceeding that which is in the specified FSM.

#### 2.2.3 The D-Method

The D-method [Gone 70] is a checking experiment which uses a set of distinguishing sequences (DSs) for state identification.

An DS can be thought of as a special case of a W-set where there exists only one sequence of inputs. This

sequence produces a different sequence of outputs for every different starting state. Not every completely specified, minimal and strongly connected FSM possesses an DS. This method, when applicable, is also capable of detecting all faults in an FSM with a number of states smaller than or equal to that in the specified FSM.

#### 2.2.4 The U-Method

The U-method [Sabn88] is also a checking experiment with the exception that it uses a sequence of unique input/outputs (UIOs) to identify the states in each transition.

An UIO sequence (UIOS) for a state is an I/O behavior not exhibited by any other state in the FSM. Not every state in an FSM possesses an UIOS. In the absence of an UIOS, a state signature is used which is formed by concatenating a set of input sequences, each of which distinguishes the state from one other state in the FSM.

An FSM does not have to be completely specified in order to possess a set of UIOSs. In [Sidh89], it was found that the U-method possesses a fault detection capability equivalent to those produced by the W- and D-method for minimal, completely specified and strongly connected FSMs. The U-method generates test sequences whose lengths are

comparable to those generated by the D-method. Their lengths are generally shorter than those produced by the W-method.

Both the U-method and the W-method are generally applicable to completely specified, strongly connected and minimal FSMs, but being completely specified is a necessary condition for the W-method while it is sufficient, but not necessary, for the U-method [Sidh89].

## 2.2.5 Comments On The Four Methods

# 2.2.5.1 Applicability

In deciding on which test method to use, the first factor to be considered is applicability, then comes the achievable fault coverage, and finally, the length of the test sequence produced. If all T-, W-, D- and U-methods were applicable to test a particular FSM, then any one of the latter three methods is preferred over the T-method because of their better fault coverages. Among the three methods, the W-method is the most undesirable because of its lengthy test sequences. Since UIOSs generally occur more frequently than DSs do, the U-method seems to stand out from among the three.

In fact, DSs are special cases of UIOSs where the input sequences for all the UIOSs are identical. In the search algorithm presented in [Sabn88] for finding minimum UIOSs, if the resulting UIOSs have identical input sequences, then they would also be referred to as DSs.

The W-set is to DSs as the signatures are to UIOSs. The W-set possesses the same input constraint as that in the DSs. While signatures are used when UIOSs are absent, the W-set should be used only when the DSs are absent because of the lengthy test sequences that can result from using the W-method. From this viewpoint, the UIOSs or the signatures, having the least restrictive constraints, occur more frequently than the DSs or the W-set does in FSMs.

## 2.2.5.2 Fault Coverage

The four FSM test methods are directly applicable to the conformance testing of those protocols that can be modelled as FSMs. The ability of a test sequence to decide whether a protocol implementation under test (IUT) conforms to its specification solely relies upon the range of faults that it can detect.

The four methods work by checking for the existence of transitions and, with the exception of the T-method, by verifying that the states in each transition are correct.

In this sense, missing and erroneous states and I/Os in an IUT can be detected, but extra states and I/Os cannot. However, conformance merely requires that an IUT behaves as according to its specification. This implies as long as an IUT possesses a skeleton FSM that is identical to its specification FSM, it would be a conforming IUT independent of whether other states or transitions exist. As a result, the W-, D- and U-method suffice as conformance test methods for protocols. Their only limitation is that the IUT must not possess a number of states that exceeds that which is in the specified FSM since extra states no longer guarantee "what you see is what you get" during testing.

FSMs that model protocols may not be completely specified. Those edges that are specified are referred to as core edges [Sabn88]. For the unspecified state-input pairs, a Completeness Assumption can be used where the protocol machine is either assumed to produce a null output and remain in its current state or it is assumed to enter an error state following the generation of an error message. The Completeness Assumption allows an incompletely specified FSM to become completely specified. Conformance can thus be defined at two levels: strong and weak. An IUT has strong conformance to its specification if, for all test inputs, it generates the same outputs as those specified in its

specification. An IUT has weak conformance to its specification if the IUT has the same I/O behavior as its incompletely specified FSM specification. For the non-core edges, the IUT has unspecified behavior. This implies strong conformance testing can be carried out only for those IUTs whose specification FSMs are completely specified; otherwise, only weak conformance testing is possible.

The following summarizes the fault coverages that were reported in [Sidh89] of the four test methods. The fault coverage of the weak conformance test sequence for the Umethod is better than that of the T-method since the Tmethod only checks the I/O operations at each transition while the U-method verifies the states of each transition as The fault coverages of the strong conformance test well. sequences for the W-, D- and U-method are identical and are better than that of the T-method. The latter is again based on the fact that the T-method does not verify the states during testing while the other three methods do. The former is based on all three methods are checking experiments except different characterizing I/O sequences are used for state identification. Sidhu claims that each of the three methods can detect all I/O errors well as as state This, however, is not the case as the transition errors. following section will show.

In general, a test sequence generated by any one of the four methods is not unique. The reason being an FSM has more than one transition tour, and it may have more than one set of UIOSs or DSs, or it may have more than one W-set. The choice of which characterizing sequence to use depends on the tester.

#### 2.3 THE SHORTCOMING OF THE U-METHOD

The U-method appeared to be the ultimate test sequence generation method for FSMs where the applicability advantage of the W-method is combined with the length advantage of the D-method, and, at the same time, it possesses full fault detection capability. Unfortunately, this is not the case. Ιt was found in [Chan89b] that the fault detection capability of the U-method in fact depends on the set of UIOSs chosen. This section is extracted from [Chan89b]. compares the U-method with the D-method and it shows why the U-method does not have as strong fault coverage as the Dmethod does.

## 2.3.1 Assumptions

In the following discussion, each state in an IUT is assumed to have a reset input, r, which takes the IUT back to the initial idle state; no output is generated by the IUT

in response to r. An arc to denote this feature would be labelled as r/-; it would begin at a starting state and end at the initial idle state. Each r/- arc should be treated as a transition and exercised as well as verified during testing, but for simplicity, each arc will be assumed to be correct in the following discussion.

Sample test sequences generated in this section are not optimized to better illustrate the role of each subsequence. These sequences can be optimized by eliminating those test subsequences that are completely contained in other test subsequences.

## 2.3.2 The UIOS Problem

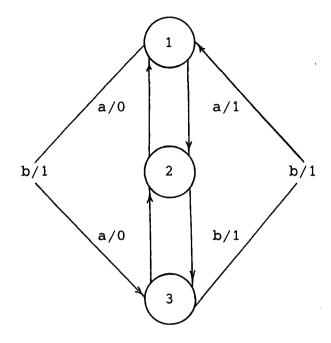

Testing of the simple FSM extracted from [Chan89b] and shown in Figure 2.1 shows the fault coverage for the U-method is not always identical to that of the D-method.

Figure 2.1: An FSM specification.

The test sequence generated by the U-method, shown in Table 2.1, cannot detect the faulty implementation, shown in Figure 2.2, of the FSM in Figure 2.1. The UIOSs chosen for states 1, 2 and 3 in that test sequence are a/1, a/0.a/1 and b/1.a/1 respectively. The resulting test sequence could not detect the erroneous tail state for the b/1 edge.

```

r/- a/1

r/- a/1.a/0.a/1

r/- a/1.b/1.b/1.a/1

r/- a/1.a/0.a/1

r/- a/1.b/1.a/1

r/- a/1.a/0.a/1

r/- a/1.b/1.b/1.a/1

r/- a/1.b/1.b/1.a/1

r/- a/1.b/1.a/0.a/0.a/1

r/- a/1.b/1.b/1.a/1

```

Table 2.1: U-method test sequence for the FSM in Figure 2.1.

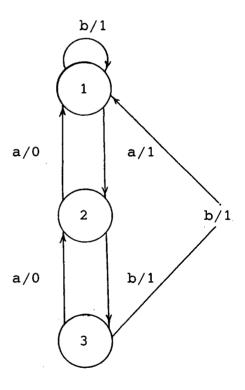

Figure 2.2: A faulty IUT of the FSM in Figure 2.1.

However, the test sequence generated by the D-method shown in Table 2.2 is capable of detecting this faulty IUT. The DSs chosen for states 1, 2 and 3 are respectively a/1.a/0, a/0.a/1 and a/0.a/0.

```

r/- a/1.a/0

r/- a/1.a/0.a/1

r/- a/1.b/1.a/0.a/0

r/- a/1.b/1.a/0.a/0

r/- a/1.a/0.a/0

r/- a/1.a/0.a/1.a/0

r/- a/1.b/1.a/0.a/0

r/- a/1.b/1.a/0.a/0.a/1

r/- a/1.b/1.b/1.a/1.a/0

```

Table 2.2: D-method test sequence for Figure 2.1.

The reason why the U-method test sequence could not detect the erroneous tail state for the b/1 edge is because the chosen set of UIOSs is unique in the specification FSM, but it is not unique in the faulty IUT in Figure 2.2. Both states 1 and 3 in the faulty IUT could generate the UIOS, b/1.a/1, chosen for state 3 in the test. This nonuniqueness is not detected during the testing of the IUT. As a result, the IUT could be in either state 1 or state 3 when b/1.a/1 is observed during testing. If, however. another set of UIOSs were chosen, for instance, a/1 for state 1, a/0.a/1 for state 2 and a/0.a/0 for state 3, then the faulty IUT would be detected as these UIOSs are also unique I/O behaviors in the faulty IUT.

The problem with the U-method is thus UIOSs are used based on the assumption that they are also UIOSs in the IUT when in fact they may not be. UIOSs are chosen based on the FSM specification. They are capable of identifying the states in the specification, but they cannot identify states in the IUT unless they are also UIOSs in the IUT. faulty IUT, UIOSs may not be unique. Hence, the U-method incorrectly assumes that if UIOSs are unique in the specification, then they must also be unique in the IUT. a result, an erroneous state could escape detection if it is capable of producing exactly the same UIOS that belongs to another state.

# 2.3.3 The State Signature Problem

uniqueness problem may also exist for signatures. It may even be inherent since signatures are not required to be unique [Chan89b]. Figure 2.3 is a duplicate of Figure 4 in [Chan89b]. It shows an FSM whose state C has no UIOSs. A signature, 0/0.0/1.1/0, generated for it. Note that the signature is not unique to state C; state B is also capable of generating this I/O sequence.

Figure 2.3: An FSM with no UIOS for state C.

A test sequence for this FSM generated by the U-method is shown in Table 2.3. The UIOSs chosen for states A and B are 0/1 and 1/1 respectively.

```

r/- 0/1

r/- 1/0.1/1

r/- 0/1.0/0.0/1.1/0

r/- 1/0.1/1

r/- 0/1.0/0.0/1.1/0

r/- 1/0.0/0.0/1

r/- 1/0.1/1.0/0.0/1.1/0

r/- 0/1.0/0.0/1

r/- 0/1.1/0.1/1

```

Table 2.3: U-method test sequence for FSM in Figure 2.3.

This test sequence cannot detect the faulty IUT shown in Figure 2.4. The edge 1/1 from state B incorrectly ended at state B in the faulty IUT, but this is not detected by the test sequence in Table 2.3. The reason is because the

state signature used to verify state C is not unique. As a result, when the state signature is observed, the state that generated it could have been either C or B. This problem, unlike the UIOSs, could be inherent in state signatures; that is, this non-uniqueness could also exist in the specification FSM. As a result, the erroneous final state also escapes detection during testing.

Figure 2.4: A faulty implementation of the FSM in Figure 2.3.

# 2.4 THE UIOV-METHOD

This section revises the U-method with the addition of a verification procedure to eliminate its uniqueness problems.

# 2.4.1 Uniqueness Problem Analysis

The uniqueness problem with the U-method concerning its UIOSs is not evident in the D-method or the W-method. The reason is because the input sequences for the DSs and the W-set are identical for all the states in a given FSM. During the first state identification procedure in a checking experiment generated by the D- or W-method, a state that responds with the correct output sequence implies two things: the state possesses the correct DS or W-set as according to the specification; as well, the state does not generate an DS or W-set that belongs to another state. This eliminates the possibility that more than one state in the IUT may produce the same characterizing I/O sequence.

In a checking experiment generated by the U-method, the first state identification procedure may have different input sequences for different states. As a result, a state which responds with the expected output sequence implies it possesses the expected UIOS as according to its specification, but it certainly does not imply that it cannot produce an UIOS that belongs to another state whose input sequence differs from that of its own UIOS.

#### 2.4.2 ~Uv

The way to eliminate the uniqueness problem concerning the UIOSs is thus to ensure that the chosen set of UIOSs for a specified FSM is also a set of UIOSs in the IUT; that is, the uniqueness of the UIOSs also holds in the IUT. This can be achieved by verifying the uniqueness of the UIOSs prior to their uses during testing [Chan89b]. This verification procedure will be referred to as "Uv while the usual state identification procedure in the U-method will be referred to as Uv from now on. The U-method with the addition of "Uv will henceforth be referred to as the UIOv-method.

"Uv is required only for those states whose UIOSs have different input sequences; for the other states, "Uv is implied in Uv [Chan89b]. During "Uv, a partial input sequence may be sufficient. For instance, given two states A and B in an FSM, if the UIOS for A is a/1.b/1.a/0 and the response of B to the input sequence a.b.a is 1.0.0, then B can be tested for the absence of a/1.b/1.a/0 by merely observing that B generates the subsequence a/1.b/0 since this is enough to show that B cannot generate a/1.b/1.a/0. This partiality reduces the cost of the final test sequence.

In "Uv, the emphasis is on states not generating UIOSs that belong to other states, hence, identical outputs generated by different states in response to the same inputs

are acceptable; whereas in Uv, this would not be allowed as it implies one UIOS is generated by more than one state. An example test sequence using the UIOv-method is produced in Table 2.4 for the FSM in Figure 2.1. This test sequence is equivalent to that shown in Table 2.1 with the exception that "Uv is added. Note that at subsequence r/- b/1.a/0 the faulty IUT in Figure 2.2 fails since state 1 displays r/-b/1.a/1 instead; that is, state 1 generates the UIOS that belongs to state 3.

```

r/- a/1

r/- a/1.a/0.a/1

r/- a/1.b/1.b/1.a/1

r/- a/1.b/1.a/0

r/- a/1.b/1.a/0.a/0

r/- b/1.a/0

r/- a/1.b/1.a/0

r/- a/1.b/1.a/0

r/- a/1.b/1.a/1

r/- a/1.a/0.a/1

r/- a/1.b/1.b/1.a/1

r/- a/1.b/1.a/1

r/- a/1.b/1.a/1.a/1

r/- a/1.b/1.a/1.a/1

```

Table 2.4: UIOv-method test sequence for the FSM in Figure 2.1.

## 2.4.3 IO(S,K)s

To correct the inherent uniqueness problem in state signatures, [Chan89b] proposed the use of a set of IO(S,K)s in place of a state signature. Each member in the set of IO(S,K)s is a sequence of I/Os that distinguishes the state,

S, to which the IO(S,K)s belongs, from at least one other state, K, in the FSM. This is somewhat similar to the W-set with the exception that the input sequences in the IO(S,K)s for different S states may be different and the number of sequences in each set of IO(S,K)s may also vary depending on state S. The size of the set of IO(S,K)s for a state S is the minimum required to distinguish S from all other states in the FSM.

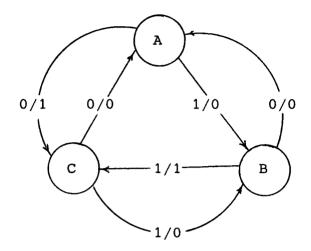

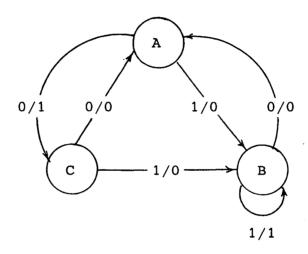

Each set of IO(S,K)s must be unique to state S. Each set is treated as though it is an UIOS during testing; that is, each is verified in the same way UIOSs are verified in the "Uv and Uv procedures prior to their uses during testing. During the transition testing, Tt, portion of the checking experiment, each I/O operation with tail state S will be tested a number of times equals to the number of I/O sequences in its set of IO(S,K)s. An example is shown in Table 2.5 for the FSM in Figure 2.3.

```

r/- 0/1

r/-1/0.1/1

r/- 0/1.0/0

r/- 0/1.1/0

r/-1/0

r/-1/0

r/- 0/1

r/- 0/1.0/0

r/- 0/1.1/0

r/-1/0.1/1

r/-1/0.0/0

r/-1/0.0/0

r/-1/0.1/1

r/-1/0.0/0.0/1

r/- 0/1.0/0.0/1

r/- 0/1.1/0.1/1

r/-.0/1.0/0

r/- 0/1.1/0

r/-1/0.1/1.0/0

r/-1/0.1/1.1/0

```

Table 2.5: UIOv-method test sequence for the FSM in Figure 2.3.

For state C, IO(C,A) is 0/0 and IO(C,B) is 1/0. These two sequences are checked for their absences in states A and B during "Uv. In state A, although 1/0 is present, 0/0 is absent. In state B, 0/0 is present but 1/0 is absent. Hence, IO(C,A) and IO(C,B) together can be used to uniquely identify state C. Each edge that ends at C, 1/0 from A and 1/1 from B, is checked twice using 1/0 first then 0/0 the second time. Note that the faulty IUT in Figure 2.3 possesses the same set of UIOSs and IO(C,K)s as that in the specified FSM. As a result, the erroneous final state for edge 1/1 is detected by IO(C,B).

While the DSs are special cases of the UIOSs, the W-sets can be viewed as special cases of the IO(S,K)s where the former has the additional constraints that the input sequences must be identical for all the states and the number of sequences in each W-set for each state must be identical. As well, the W-set must exist for every state in the FSM.

In the remainder of this thesis, when UIOSs or IO(S,K)s are referred to, it is assumed that these are verifiable UIOSs and verifiable IO(S,K)s.

## 2.4.4 Comparing The UIOv-Method With The Others

The same of the control of the same of the control of the control

The fault coverage produced by the UIOv-method is better than that produced by the U-method. Erroneous tail states such as those illustrated in the previous sections are now detectable. The fault coverage of the UIOv-method is now identical to those of the W- and D-method. The proof is as follows.

First of all, the W-, D- and UIOv-method are all checking experiments with the exception that they use different characterizing I/O sequences for state verification. Secondly, the DSs and the W-set are special cases of the UIOSs and the IO(S,K)s respectively. Recall how the "Uv procedure for a particular state is implied in

its Uv procedure when the input sequences for the UIOSs belonging to other states are identical to that of its own UIOS. In this sense, the state identification procedures of the checking experiments generated by the W- and D-method accomplish what both Uv and "Uv accomplish in the UIOv-method. As a result, the fault coverages of the W-, D- and UIOv-method are identical.

The length of the test sequences produced by the UIOvmethod are obviously longer than those produced by the Umethod; however, they are generally shorter than the sequences derived by the W-method since the latter requires that each transition be tested a number of times equals to fixed number of I/O sequences in the comparison to the D-method, it is more difficult as the sequence lengths may differ according to different FSMs. The test subsequence corresponding to Uv and "Uv is likely longer than that corresponding to the state identification procedure for the D-method. However, the subsequence for the Tt portion of the test is likely shorter in the UIOvmethod because of less restrictive conditions in forming the UIOSs, which produce UIOSs that are generally shorter than If the UIOv- and D-method were both applicable to an FSM and the DSs are shorter than the UIOSs, then the D-

method should be used; otherwise, both methods need to be examined.

In terms of applicability, the UIOv-method is more widely applicable than both D- and W-methods. obvious due to the added constraints in the formation of the DSs and W-set. The likelihood that a set of DSs exists in a given FSM is generally lower than that for a set of UIOSs or W-set. In general, a minimal and strongly connected Mealy machine being completely specified is a sufficient but not necessary condition for the application of the D-, W- and UIOv-method. The necessary condition is that the FSM possesses an DSs set, a W-set or an UIOSs set. The same condition applies to incompletely specified machines: long as such a machine possesses a completely specified FSM skeleton from which a set of DSs or a W-set can be produced, or from which stems a set of UIOSs, the respective D-, Wand UIOv-method would be applicable. Hence, all three methods are applicable to any FSM independent of whether it is completely or incompletely specified as long as the required characterizing I/O sequences exist in the FSM.

## 2.5 UNIQUE TEST SEQUENCES

All test sequences generated by the D-, W- and UIOv-methods achieve full fault coverage in the testing of FSMs.

A property that is common among these test sequences is captured in the concept of unique test sequences (UTSs) proposed in [Chan89b]. Full fault coverage in FSM testing in this thesis implies the detection of all erroneous and An UTS is defined to be a test missing states and I/Os. sequence that is unique to a specified FSM, M, if there does not exist any other FSM with the same number of states and transitions as that in M capable of producing an sequence that is identical to the UTS of M. An IUT thus passes a test that uses an UTS if and only if the IUT possesses a FSM skeleton identical to the specified FSM. This implies UTSs are capable of detecting any faulty IUT provided that the number of states in the IUT is no greater than that which is in the FSM specification. This also implies an IUT that passes such a test may possess extra transitions in addition to those specified in the specification, provided that the IUT has a number of states greater than or equal to that which is in the specification.

An UTS can be formed by using a sequence of I/Os to accurately describe each transition in the FSM specification; that is, each I/O operation is described as is, their starting and final states are described by their characterizing I/O sequences. This implies that if there

exists a program which generates FSM graphs according to a given I/O sequence and a given number of states, then if the given I/O sequence were an UTS, then there would be one and only one graph that can be generated from the given sequence. An FSM may have more than one UTS depending on which characterizing I/O sequence is selected.

It was found in [Chan89b] that test sequences produced by the D-method and the UIOv-method were sequences of I/Os that accurately described each transition specified in the given FSM; that is, both methods produced UTSs. Since the W-method is a special case of the D-method and the UIOvmethod, it is also capable of generating UTSs. Since the Tdescribes only the I/O operations method inside transition without any reference to its states, this method generally does not produce UTSs in FSMs with the exception of the following type of simple FSMs.

Figure 2.5: A simple FSM with an inherent UTS.

In the simple FSM, assuming that the test sequence must begin at the initial state, state 1, the shortest transition tour possible is a/1.a/2.a/3. This is not an UTS because there exists two other completely specified FSMs, each having three states and an input set I = {a}, that I/O capable of generating an sequence identical a/1.a/2.a/3. These two FSMs differ from that in Figure 2.5 by the tail state of the a/3 arc. One FSM has its a/3 arc end at state 2; the other has its a/3 arc end at state 3. However, the transition tour a/1.a/2.a/3.a/1 is an UTS since it bounds the tail state of a/3 to state 1, the only state that generates a/1.

UTSs apply to both completely and incompletely specified FSM specifications since the D-, W- and UIOv-method are applicable to any FSM that possesses a set of DSs, a W-set or a set of UIOSs respectively. This implies any IUT that possesses an FSM skeleton identical to the specification FSM, whether it be completely or incompletely specified, will pass a test using an UTS based on the specification.

One question that is often brought up is whether a generated test sequence is correct; that is, whether the test correctly represents the specification so that any IUT that passes that test must conform to the specification.

One way to verify that a given test is correct is to generate all possible FSMs that correspond to the given test. If the test uses an UTS, then there would exist only one FSM, with the same number of states and transitions as that in the specification, that can be generated.

### 2.6 FSM TESTING

Much can be learnt from FSM testing. In the T-method, transitions are only exercised during testing. This method generally achieves partial fault coverage that is а comparable to that produced by the branch coverage criterion in software testing, where each branch is exercised at least From the T-method, it becomes clear that merely exercising statements, or branches, do not constitute a sufficient test; that is, some errors may escape detection. These errors are those found in elements that are not directly observable in the I/O operations; for instance, the states in an FSM. The checking experiments for FSMs solve this problem by verifying each state with its characterizing I/O sequence. This is possible because the variable STATE takes on a finite set of possible values. As well, each different value can be characterized by a different I/O This, however, may not be possible in software testing where a set of possible values for a given variable

may be infinite. As well, there may not be a sequence of externally observable events that can differentiate among different values of a variable. Nevertheless, FSM testing does show that exercise along with verification gives improved fault coverage over that produced by exercise alone.

### 2.7 CHAPTER SUMMARY

In summary, checking experiments for testing FSMs are capable of detecting all states and I/O errors as according to an FSM specification. Before the advent of the UIOv-method, checking experiments based on DSs were hampered by their limited applicabilities while those based on W-sets were handicapped by their lengthy test sequences. With the advent of the UIOv-method, checking experiments became more applicable without the disadvantage of a lengthy test sequence.

The UIOv-method solves the uniqueness problem in the UIO-method with the use of a verification procedure. This solution is independent of which UIOS is non-unique in the IUT [Chan89c]; it solves the problem by attacking its cause. This solution permits any minimum length UIOS to be used provided that it is verifiable; hence, it does not

considerably add to the complexity of the search algorithm for UIOSs given in [Sabn88].

Checking experiments generate test sequences that are unique to the specified FSM. As a result, any IUT that passes such a test possesses an FSM skeleton identical to the specified FSM; however, it may have additional transitions that do not belong to the specification.

In terms of applicability, checking experiments are generally applicable to Mealy machines that are minimal and strongly connected. Whether a Mealy machine is completely or incompletely specified is not important, so long as it has a completely specified skeleton for which a W-set or a set of DSs can be generated, or from which stems a set of UIOSs, a checking experiment would be applicable.

One result from FSM testing is that mere exercising of transitions alone generally cannot uncover all faults. Exercise of transitions along with verification, whenever possible, produce a better fault coverage.

In the remainder of this thesis, the "UIOv-method" will be used to refer to the UIOv-method, the W-method, as well as the D-method for simplicity. This implies the term "UIOSs" will refer to UIOSs as well as DSs. This is possible since DSs are merely UIOSs whose input sequences

must be identical for all the states in an FSM. Similarly, the term "IO(S,K)s" will also refer to the W-sets since the latter are really IO(S,K)s whose input sequences are identical for all the states and whose members must be consistently numbered among the states in an FSM.

## 3 TESTING EXTENDED FINITE STATE MACHINES

Techniques for testing FSMs are applicable to testing simple protocols that can be modelled by FSMs. These models, however, are impractical for complex protocols which may require a very large number of states. For instance, the use of sequence numbers in a protocol introduces a different state for each possible value. This is known as the state space explosion problem.

A remedy to the state space explosion problem is by using an extended finite state machine (EFSM) model for the specification of more complex protocols. When FSM testing techniques are applied to such models, executabilities of the resulting test sequences are no longer guaranteed. This chapter discusses how the UIOv-method can be extended to the testing of protocols modelled by EFSMs so that executability of the final test sequence is guaranteed and maximum fault coverage is achieved within the limitations of testing.

#### 3.1 BACKGROUND

An EFSM is an FSM with the addition of minor state variables. These variables form additional enabling conditions in the transitions to reduce the number of states required in the underlying FSM. As a result, different transitions may occur in response to the same combination of

Testing Extended Finite State Machines input event and starting state in an EFSM. A transition in triggered by three types of enabling EFSM may be conditions: the input event, the current state and a boolean expression involving minor state variables. transition now consists of three operations: the output operation, the state transition and operations that alter values of the minor state variables. The "state" of an EFSM longer refers to the value belonging to the STATE variable alone but it refers to the values belonging to the minor state variables as well. The "state" of an EFSM will be referred to as its total system state (TSS) from now on.

### 3.2 THE EFSM TABLE

Test sequences generated from FSMs are generally done according to their directed graphs. A similar graph can be constructed for EFSMs; however, since minor state variables need to be considered as well in EFSMs to ensure the final test sequences are executable, when these variables are included in an EFSM directed graph, the graph can become very cluttered and difficult to use. The tabular format is thus better suited for representing EFSMs for testing purposes and is used in here as a tool for the test sequence generation procedure.

Testing Extended Finite State Machines

Columns in the EFSM table are labelled by the starting TSSs of the EFSM transitions. Rows in the EFSM table are labelled by the final TSSs of the EFSM transitions. Each table entry records a transition and can be labelled by either the transition identifier, t\*, or the input and output operations within the transition. The EFSM table thus contains information on the semantics and syntax of an EFSM. By considering both, instead of syntax alone, executability is taken into consideration during the test sequence generation process.

Table 3.1 shows a simple example of an EFSM table. There is only one minor state variable, c, in the example. When c is absent at the current TSS, C.TSS, or at the next TSS, N.TSS, it indicates c can assume any value.

| C.TSS<br>N.TSS | s1<br>c<2 | s1    | s1<br>c=2 | s2  | s2<br>c<2 | s2<br>c=2 |

|----------------|-----------|-------|-----------|-----|-----------|-----------|

| s1<br>c:=c+1   | a/0       |       |           |     |           |           |

| s1             |           | b/-   |           |     |           |           |

| s2<br>c:=0     |           |       | a/3       |     |           |           |

| s2             |           |       | . 7       | a/- |           |           |

| s2<br>c:=c+1   | ·         |       |           |     | b/0       |           |

| s1<br>c:=0     |           | ÷ · . |           |     |           | b/3       |

Table 3.1 An EFSM table.

## 3.3 EXTENSION OF THE UIOV-METHOD

The UIOv-method is extended in this section to be applied to EFSM testing. An EFSM is an FSM with additional minor state variables, hence, the UIOv-method is directly applicable to testing its FSM portion. The UIOSs and preambles, however, must be carefully selected to prevent executability problems in the final test sequence. In addition, since minor state variables contribute to the TSS, they must also be verified the same way STATE variables are in FSM testing.

### 3.3.1 UIOSs Selection In An EFSM

For simplicity, those transitions in an EFSM whose starting TSSs involve p-uses of minor state variables will be referred to as "e.transitions" in the subsequent discussion. Those transitions that do not will simply be referred to as "transitions." For example, referring to Table 3.1, those transitions with the following I/Os are e.transitions: a/O, a/3, b/O and b/3.

Executability problems may exist in the chosen UIOSs if they contain e.transitions and their enabling conditions are not part of the UIOSs. An uncomplicated way to prevent executability problems in the UIOSs chosen is to "remove" all the e.transitions in the EFSM table to form a table representing a pure FSM. The search algorithm in [Sabn88] now directly applicable to for UIOSs is the E.transitions are all the transitions found under columns labelled with TSS variables consisting of minor state variables. In practice, the e.transitions are not physically removed but are simply ignored during the search. Although this method may not produce minimum UIOSs, its advantage is that executability is guaranteed within the This implies no special preamble is required to enable any UIOS. As will be seen later on, special preambles can considerably increase the final length of the Testing Extended Finite State Machines test sequence and may be problematic in the testing of e.transitions.

If the resulting FSM table produces only non-verifiable which are UIOSs whose input sequences are applicable to other states for verification, then "Uv must involve e.transitions. This may require special preambles to permit executability during "Uv. The tail states of these preambles must be verified using their respective UIOSs to ensure "Uv is performed for the correct state. These preambles are formed only for the purpose of executable "Uv procedure. The Uv and "Uv procedures during testing will use these special preambles.

If a state in the FSM table does not have an UIOS, then the EFSM table has to be used to find an UIOS for that The e.transitions in the resulting UIOS require the state. following attention. If within the UIOS the p-use of the minor state variable in an e.transition is enabled by a transition that is also within the UIOS, then the UIOS is executable by itself and does not require a special preamble. If, however, the enabling transition, et, is not within the UIOS, then the preamble for the state, s, to which the UIOS belongs must include et. Two possibilities The et may have s as its ending state. can occur. a problem if there exists more than one incoming arc to s.

This implies the UIOS cannot be used to verify the tail states of the other incoming arcs because the UIOS would not have been enabled. Another UIOS or a set of IO(s,k)s would have to be used for state s. If, however, there is only one incoming arc to s and it enables the UIOS, then the UIOS may be used for s. The other possibility is that the et ends at a state other than s, in which case a partial preamble can be formed from the initial state of the EFSM to the et, and def-free paths joining this partial preamble to each of the starting states for the incoming arcs to s complete the preambles. The UIOS for s can be used provided these preambles exist for all the incoming arcs to s. Each of the preambles must have its tail state checked to ensure it arrives at the correct state before it is used in the Tt procedure.

Testing Extended Finite State Machines

Using special preambles and having to verify their penalty to ending states is а pay when UIOSs have executability problems.... The resulting test sequence, as well, may not be minimal. In addition, if the transition to be tested is an e.transition which requires an et to be included in the preamble, then the preamble needs to enable both the e.transition and the UIOS. Such a preamble may not exist, in which case another UIOS has to be found. may perhaps be an executable set of IO(s,k)s for state s

Testing Extended Finite State Machines that would reduce the number of special preambles required and produce a shorter test sequence. An optimization technique such as that used in [Shen89] would find the best alternative.

For the example in Table 3.1, transitions a/- and b/constitute UIOSs for the states s2 and s1 respectively.

Since they are not e.transitions, they do not require

special preambles to enable them.

## 3.3.2 Verification Of TSS Variables

The UIOv-method verifies a state in an FSM with its UIOS. Similarly, in an EFSM, values of minor state variables that contribute to the TSS should also be verified so that the TSS is verified, not just the STATE variable in the EFSM.

In the same way that a state is verified by the UIOS that is unique to it, an TSS can also be verified by the I/O sequence that is unique to it. However, it may not be possible to verify the whole TSS as a unit. For instance, there may not exist a transition whose C.TSS is identical to the N.TSS to be verified so that an I/O sequence that begins at that C.TSS transition can perform the verification. The reason is as follows. The C.TSS for a particular transition may not involve all the minor state variables that appear in

Testing Extended Finite State Machines all the C.TSSs in the EFSM. Unspecified variables are allowed to assume any value. As a result, an N.TSS for a transition may not be verifiable as a whole if there does not exist a transition with an C.TSS which contains p-uses of all the variables that contributed to the N.TSS. example would be the transition a/- in Table 3.1. transition cannot be used to verify the N.TSS for the transition a/3 which has the variable c reset to 0. The C.TSS for a/- merely requires that the STATE variable be at s2, it says nothing about the variable c. Hence, exercising a/- after a/3 cannot verify c although it can verify that the final STATE is at s2. The c variable thus has to be verified separately. For C.TSSs, each variable involved may also have to be verified separately.

# 3.3.2.1 Verification of N.TSSs

Verification of final TSSs, or N.TSSs, may be achieved using I/O sequences. Each definition of a minor state variable that contributes to the N.TSS as well as the definition of the STATE variable has to be verified. The STATE variables can be verified the same way they are verified in the UIOv-method. For the minor state variables, an I/O path is used to lead the defined variable to a transition whose C.TSS contains a predicate which uses that

Testing Extended Finite State Machines variable definition. The definition of the minor state variable can then be verified using an I/O sequence that begins at that C.TSS.

Referring back to the final TSS for the a/3 transition where the STATE variable is set to s2 and c is reset to 0. None of the C.TSSs is identical to it; however, the C.TSS s2 AND c<2 can verify that c is not at 2 and STATE is at s2; as well, the sequence b/0.b/0.b/3 beginning from that C.TSS can verify that c was indeed reset to 0. Each execution of b/0 increments c by 1 and transition b/3 is not possible unless c has reached 2 after two increments. As a result, the subsequence b/0.b/0 would have incremented c to 2 if it were at 0 to begin with, and the I/O b/3 would verify that c had been incremented to 2 correctly. Hence, the sequence can verify that c was reset to 0 correctly. Similarly for the N.TSS s2 and c=c+1. The variable c can be verified that it is incremented correctly by initially setting it to 0, then When it is at 0 and STATE is at s2, the situation is identical to that mentioned above and the b/0.b/0.b/3 verifies that STATE is at s2 and that c has been both set to 0 correctly and incremented correctly. When c is at 1 and STATE is at s2, the sequence b/0.b/3 verifies that STATE is at s2 and c is incremented correctly. The b/0 transition increments c to 2, and the b/3 transition checks Testing Extended Finite State Machines that c is correctly at 2. Hence, c must have been at 1 to begin with.

### 3.3.2.2 Verification of C.TSSs

Verification of the starting TSS, or C.TSS, for a transition requires verifying that the STATE variable correct and any predicate involving a minor state variable is also correct. Verification of the STATE variable is again identical to the Uv and "Uv procedures in the UIOvmethod. Verification of the predicate is Two things have to be checked in the verification of a predicate: effect and correctness. The effect of the predicate has to be checked, whenever possible, to distinguish it from other predicates involving the same minor state variables. This is similar to the STATE variables being distinguished from one another. The distinguishing procedure is also an identification process that identifies the STATE or the predicate by means of an I/O sequence that characterizes the value of the STATE variable or the presence of the predicate. For instance, referring to the example in Table 3.1, the predicate for transition a/O can be distinguished from that for transition a/3 by setting c to 0 or 1 and inputting the sequence a.a.a or a.a respectively. The predicate for transition a/O would Testing Extended Finite State Machines prompt the response 0.0.3 or 0.3 respectively. The predicate for transition a/3 can be distinguished from that for a/0 by setting c to 2 and then inputting a.a.a or a.a to the IUT. The response of the IUT would be 3.-.- or 3.- if the predicate were correct. Note that both predicates have to be verified separately the same way that all STATE values have to be checked separately. Simply checking one does not imply the other is correct. Checking the predicate for transition a/3 can also employ only the I/O sequence a/3. The I/O sequences used are thus UIOSs for the predicates.

The other item a predicate has to be checked for is its For instance, if s1 AND c<4 constitute an correctness. C.TSS that enables transition x, then this implies s1 AND c=0, s1 AND c=1, s1 AND c=2 and s1 AND c=3 are all capable of enabling x. To check that the predicate has been implemented correctly, one way is to check all these possibilities. However, this could result in an extremely lengthy test sequence if the predicate were c<100 instead of 4. Instead, the boundary-interior value criterion can be used here and the predicate c<4 can be checked by setting c to 0, 1, then 3 so that the domain of the predicate can be established. The I/O sequence which characterizes C.TSS s1 AND c<4 can then be applied to verify the response of the IUT in each case. Checking for the correctness of the

Testing Extended Finite State Machines predicate has to be considered here in the test sequence generation procedure because setting the TSS variables to particular values may require certain sequences of I/Os to be implemented or certain values be used at the time of input. Leaving the verification procedure until the test data selection process may be too late since the I/O sequences have already been determined by then.

### 3.3.2.3 UIOSs for TSSs

In the same way UIOSs are used to verify states, I/O sequences are used to verify minor state variables. are "completely specified," then variables these I/O sequences must be unique, as discussed above, so that one predicate can be distinguished from another involving the same minor state variables. For instance, referring to Table 3.1, since starting TSSs s1 AND c<2, s1 AND c=2 and s1 are all specified, if s1 AND c=2 were used to verify a final TSS, then the I/O sequence that begins at that TSS must not be also producible at the TSSs s1 AND c<2 and s1; otherwise, when the I/O sequence is observed, the c variable at the IUT could have been at 2, less than 2 or any value. The I/O sequence used must thus be unique to the starting TSS. Table 3.1, this uniqueness exists for all TSSs; that is, at TSS s1 and c<2, a/0 is produced and it is not generated by

Testing Extended Finite State Machines any other TSS. This implies the uniqueness of a/O should be checked, prior to its use, the same way "Uv checks the UIOSs for the STATE variables, to ensure its uniqueness also exists in the IUT. If TSSs s1 AND c=2 and s1 did not exist, then a/O would not have to be checked since it does not have to distinguish TSS s1 AND c<2 from s1 AND s1 AND c=2.

# 3.3.3 The eUIOv-Method

The extended UIOv-method, or eUIOv-method, is the UIOv-method taking executability and the TSS into consideration. It consists of the following procedures.

Uv = preamble(si)@UIOS(si)

~Uv = preamble(si)@~UIOSs(si)

where preamble(si) denotes the preamble that takes the EFSM from its initial "@" state state si; denotes to concatenation; UIOS(si) is the UIOS belonging to si and ~UIOSs(si) are UIOSs that belong to other states in the FSM which should not be producible by si. Uv and "Uv are done for each STATE in the EFSM. Both procedures together determine the minimum number of STATEs in the EFSM. The choice of preamble(si) for each si must ensure that the subsequent UIOS(si) and ~UIOSs(si) are all executable. no such preamble(si) exists, then either another set of UIOSs should be used or a set of IO(si,k)s should be used.

Testing Extended Finite State Machines

Uv and "Uv must both be done because of the uncertainty of

UIOSs without their verifications as discussed in Chapter 2.

If UIOSs are used for verifying TSS variables, then their

uniquenesses must also be verified in these procedures.