# A DC-DC CONVERTER SÙITABLE FOR CONTROLLING A PHOTOVOLTAIC POWERED PUMPING SYSTEM

William A. Passmore

B.A.Sc. (Electrical Engineering) University of British Columbia

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES DEPARTMENT OF ELECTRICAL ENGINEERING

> We accept this thesis as conforming to the required standard

# THE UNIVERSITY OF BRITISH COLUMBIA

March 1989

© William A. Passmore, 1989

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of <u>Electrical Engineering</u>

The University of British Columbia Vancouver, Canada

Date March 7, 1989

# Abstract

A photovoltaic powered pumping system offers an attractive means of supplying fresh water in remote areas not serviced by a utility grid. In order to extract the maximum amount of energy from the solar panels, it is necessary to match the characteristics of the photovoltaic array to the DC motor which drives a pump. A one quadrant DC-DC converter is capable of adjusting the effective load impedance for maximum power transfer under most lighting conditions.

Three styles of DC-DC converters used to control the pumping system are described and compared. The voltage tracking style of converter fixes the array voltage at a level considered optimum. The power tracking converter measures, and attempts to maximize, the output power of the photovoltaic array. The microprocessor based power tracking, voltage tracking converter toggles between the two methods of control. Experimental results are included.

# **Table of Contents**

| AI            | Abstract |                          |    |  |  |  |

|---------------|----------|--------------------------|----|--|--|--|

| $\mathbf{Li}$ | st of    | Tables                   | iv |  |  |  |

| $\mathbf{Li}$ | st of    | Figures                  | v  |  |  |  |

| A             | knov     | wledgement               | vi |  |  |  |

| 1             | Intr     | oduction                 | 1  |  |  |  |

|               | 1.1      | System components        | 2  |  |  |  |

|               |          | 1.1.1 Photovoltaic Array | 2  |  |  |  |

|               | 1.2      | Thesis                   | 6  |  |  |  |

| 2             | Pow      | ver Converter            | 7  |  |  |  |

|               | 2.1      | Component Matching       | 7  |  |  |  |

|               | 2.2      | Component Ratings        | 8  |  |  |  |

|               |          | 2.2.1 Filter Capacitor   | 9  |  |  |  |

|               |          | 2.2.2 Power Mosfets      | 11 |  |  |  |

|               |          | 2.2.3 Diode              | 14 |  |  |  |

|               |          | 2.2.4 Power Supply       | 15 |  |  |  |

|               |          | 2.2.5 Heatsink           | 16 |  |  |  |

| 3             | Vol      | tage Tracking Converter  | 18 |  |  |  |

|               | 3.1      | Specifications           | 18 |  |  |  |

|   | 3.2 | 3.2 Circuit Description                                               |                                        |                                        |  |

|---|-----|-----------------------------------------------------------------------|----------------------------------------|----------------------------------------|--|

|   |     | 3.2.1                                                                 | Basic Operation                        | 20                                     |  |

|   |     | 3.2.2                                                                 | Gate Drive                             | 21                                     |  |

|   |     | 3.2.3                                                                 | Overcurrent Protection                 | 21                                     |  |

|   |     | 3.2.4                                                                 | Thermal Protection                     | 21                                     |  |

|   |     | 3.2.5                                                                 | Protection                             | 22                                     |  |

|   | 3.3 | Testin                                                                | g and Results                          | 23                                     |  |

|   |     | 3.3.1                                                                 | Waveforms                              | 23                                     |  |

|   |     | 3.3.2                                                                 | Efficiency                             | 29                                     |  |

|   |     | •                                                                     | Derver The ching Convertor             | 31                                     |  |

| 4 | Max |                                                                       |                                        |                                        |  |

|   | 4.1 | The L                                                                 | ogic Circuit                           | 31                                     |  |

|   | 4.2 | S                                                                     | 34                                     |                                        |  |

|   | 4.3 | Consta                                                                | ant Voltage vs. Maximum Power Tracking | 38                                     |  |

| 5 | Mic | essor Based Hybrid Control                                            | <b>4</b> 0                             |                                        |  |

| v |     | 1                                                                     | -                                      |                                        |  |

| v | 5.1 | -                                                                     | Circuit                                | 41                                     |  |

| Ŭ | 5.1 | -                                                                     |                                        | 41<br>41                               |  |

| Ū | 5.1 | Logic                                                                 | MC68HC11 Single Chip Microprocessor    |                                        |  |

| Ū | 5.1 | Logic<br>5.1.1                                                        | MC68HC11 Single Chip Microprocessor    | 41                                     |  |

| • | 5.1 | Logic<br>5.1.1<br>5.1.2<br>5.1.3                                      | MC68HC11 Single Chip Microprocessor    | 41<br>44                               |  |

| Ū | 5.1 | Logic<br>5.1.1<br>5.1.2<br>5.1.3                                      | MC68HC11 Single Chip Microprocessor    | 41<br>44<br>45                         |  |

| Ū | 5.1 | Logic<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                             | MC68HC11 Single Chip Microprocessor    | 41<br>44<br>45<br>46                   |  |

| Ū | 5.1 | Logic<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6           | MC68HC11 Single Chip Microprocessor    | 41<br>44<br>45<br>46<br>46             |  |

| Ū |     | Logic<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6           | MC68HC11 Single Chip Microprocessor    | 41<br>44<br>45<br>46<br>46<br>50       |  |

|   |     | Logic<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>Progra | MC68HC11 Single Chip Microprocessor    | 41<br>44<br>45<br>46<br>46<br>50<br>50 |  |

|   |             | 5.2.4   | Changing the Duty Cycle          | 57  |

|---|-------------|---------|----------------------------------|-----|

|   | 5.3         | Result  | S                                | 57  |

|   |             | 5.3.1   | Voltage Waveform                 | 58  |

|   |             | 5.3.2   | Current and Voltage Measurements | 58  |

|   |             | 5.3.3   | Maximum Power Point              | 65  |

| 6 | Con         | clusior | 15                               | 72  |

| A | Asse        | embly   | Language Program                 | 74  |

|   | A.1         | Main l  | Program                          | 76  |

|   | A.2         | A/D C   | Converter Set-Up                 | 78  |

|   | A.3         | Timer   | Set-Up                           | 79  |

|   | A.4         | Overce  | rrent Initialization             | 81  |

|   | <b>A</b> .5 | Read 1  | Input Data                       | 82  |

|   | A.6         | Adjust  | the Pulse Width                  | 84  |

|   | A.7         | Real I  | Time Timer                       | 90  |

|   |             | A.7.1   | Time of Day Interrupt Service    | 91  |

|   |             | A.7.2   | Increment The Time of Day        | 92  |

|   |             | A.7.3   | Add Time                         | 93  |

|   |             | A.7.4   | Compare Time                     | 94  |

|   | <b>A.</b> 8 | Clear   | Timer Node                       | 96  |

|   | A.9         | Maxin   | num Power Tracking               | 97  |

|   |             | A.9.1   | Change Search Direction          | 104 |

|   | A.10        | Curren  | nt Adjustment                    | 105 |

|   | A.11        | Voltag  | ge Tracking Routine              | 105 |

|   |             | A.11.1  | Adjustment to the Duty Cycle     | 107 |

|   | A.12        | Read    | Open Circuit Voltage and Current | 109 |

|   |             |         |                                  |     |

| A.13 Calculate Load Voltage and Current        |

|------------------------------------------------|

| A.14 Change the Duty Cycle in Small Increments |

| A.15 Overcurrent                               |

| A.15.1 Overcurrent Interrupt                   |

| A.16 Output Compare One Interrupt              |

| A.17 Output Compare Two Interrupt              |

|                                                |

# Bibliography

.

121

# List of Tables

| 2.1 | IRF730 Device Specifications:             | 13 |

|-----|-------------------------------------------|----|

| 3.2 | Voltage Tracking Converter Specifications | 20 |

| 3.3 | Converter Efficiency                      | 30 |

| 5.4 | Power Tracking Results                    | 71 |

|     |                                           |    |

.

# List of Figures

| 1.1  | Voltage vs Current Curves of a Photovoltaic Array       | · 4 |

|------|---------------------------------------------------------|-----|

| 1.2  | Current and Voltage vs Power at a Set Insolation Level  | 5   |

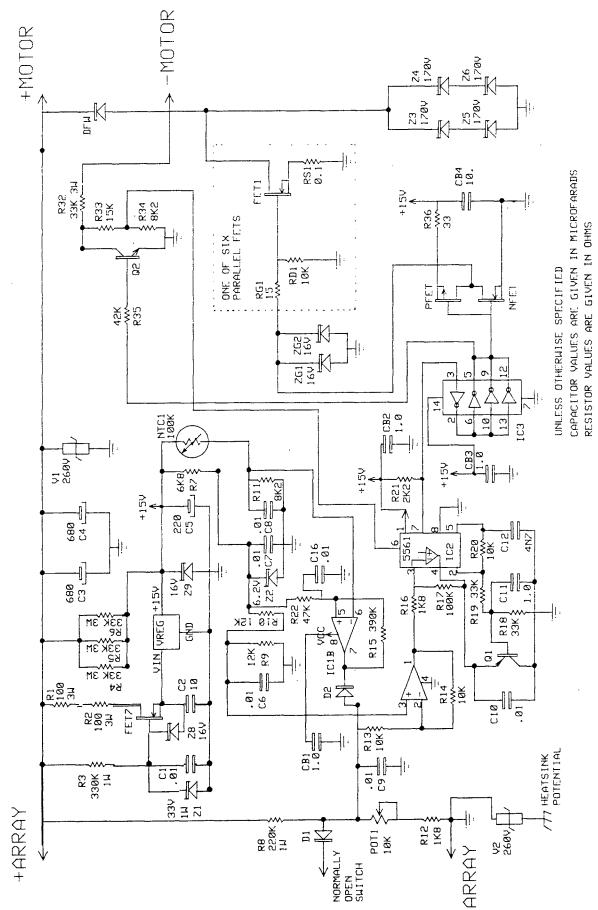

| 2.3  | DC to DC Converter                                      | 9   |

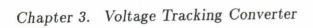

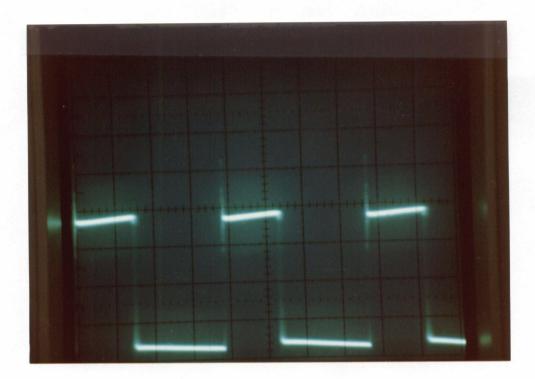

| 2.4  | Converter Voltage and Current Waveforms                 | 10  |

| 3.5  | Circuit Diagram of the Voltage Tracking Converter       | 19  |

| 3.6  | Drain-to-Source Voltage                                 | 24  |

| 3.7  | Drain-to-Source Voltage at Turn-off                     | 25  |

| 3.8  | Gate-to-Source Voltage with the Drain-to-Source Voltage | 26  |

| 3.9  | Current Signal                                          | 28  |

| 3.10 | Experimental Set-up                                     | 29  |

| 4.11 | Block Diagram of Maximum Power Point Tracking Circuit   | 32  |

| 4.12 | Array Power vs. Solar Radiation Level                   | 35  |

| 4.13 | Converter Efficiency                                    | 36  |

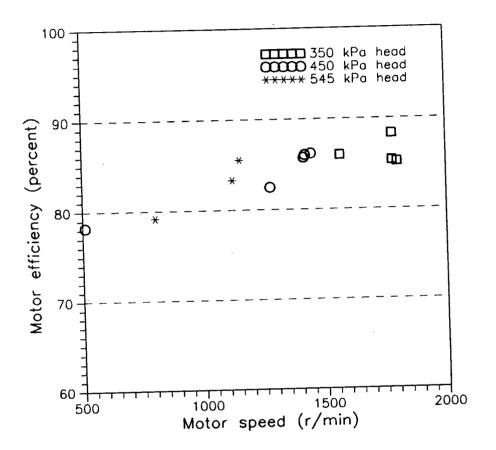

| 4.14 | Motor Efficiency                                        | 37  |

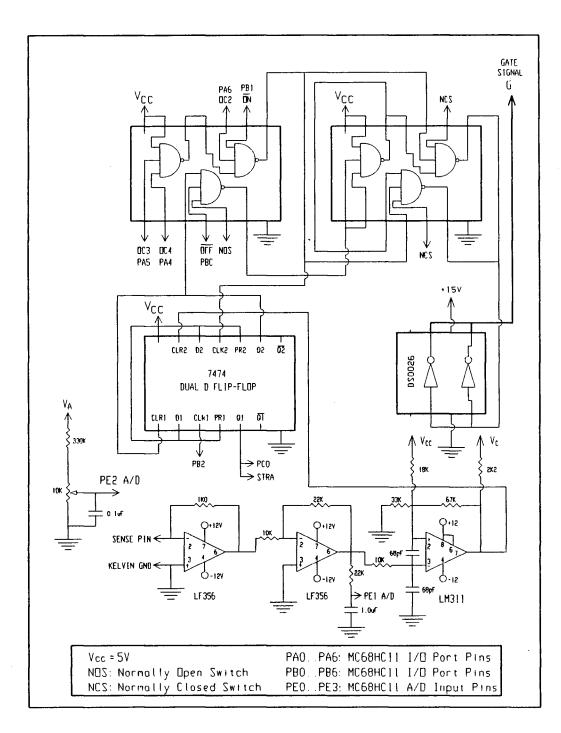

| 5.15 | External Logic Circuit                                  | 42  |

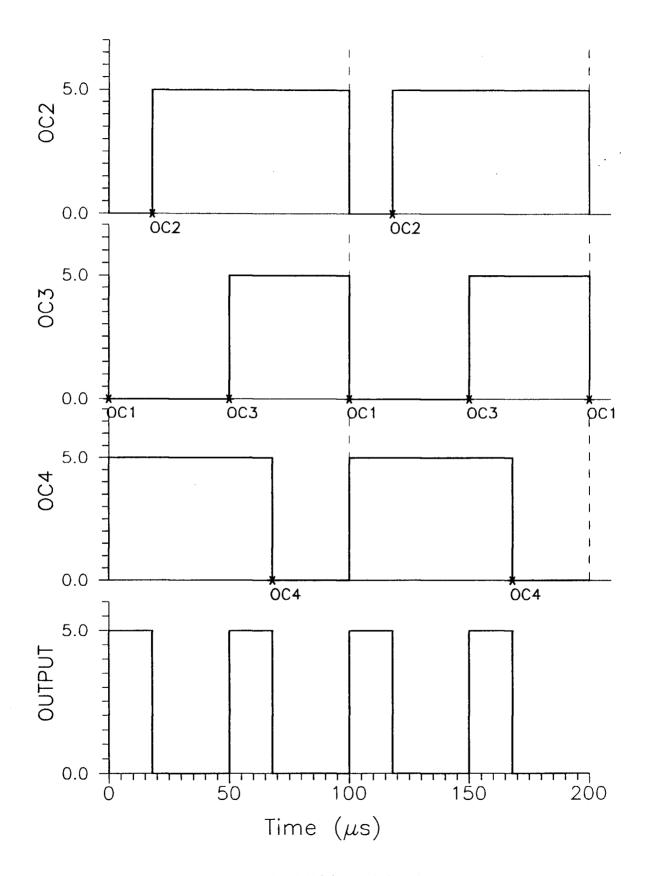

| 5.16 | Pulse Width Modulated Waveforms                         | 49  |

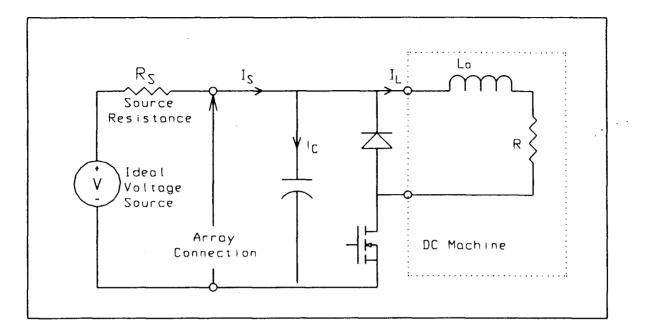

| 5.17 | Simplified Power Circuit                                | 53  |

| 5.18 | Equivalent Power Circuit                                | 53  |

| 5.19 | Drain-to-Source Voltage Waveform                        | 59  |

| 5.20 | Drain-to-Source Voltage Waveform at Turn-off            | 60  |

| 5.21 | Drain-to-Source Voltage Waveform at Turn-on                         | 61 |

|------|---------------------------------------------------------------------|----|

| 5.22 | HEXSense Current Waveform                                           | 62 |

| 5.23 | Filtered HEXSense Current Waveform                                  | 63 |

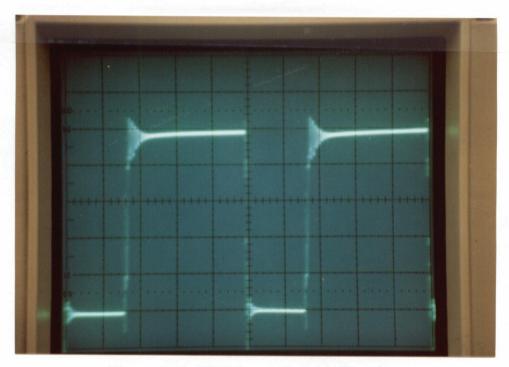

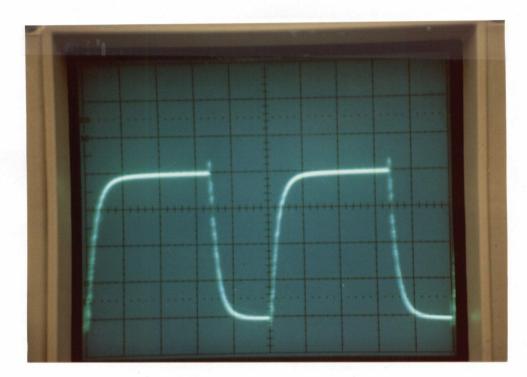

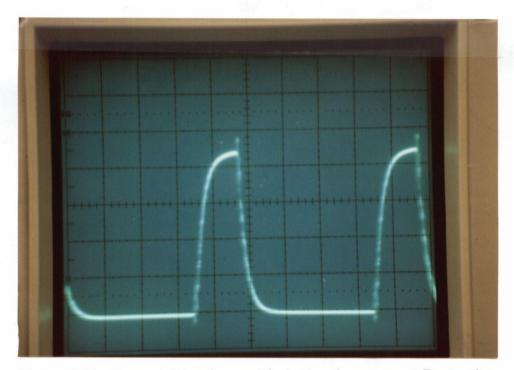

| 5.24 | Current Waveform with Active Overcurrent Protection                 | 64 |

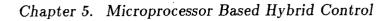

| 5.25 | Microprocessor Current Measurements vs Metered Current Measure-     |    |

|      | ments                                                               | 66 |

| 5.26 | Microprocessor Voltage Measurements vs Metered Voltage Measurements |    |

|      | 67                                                                  |    |

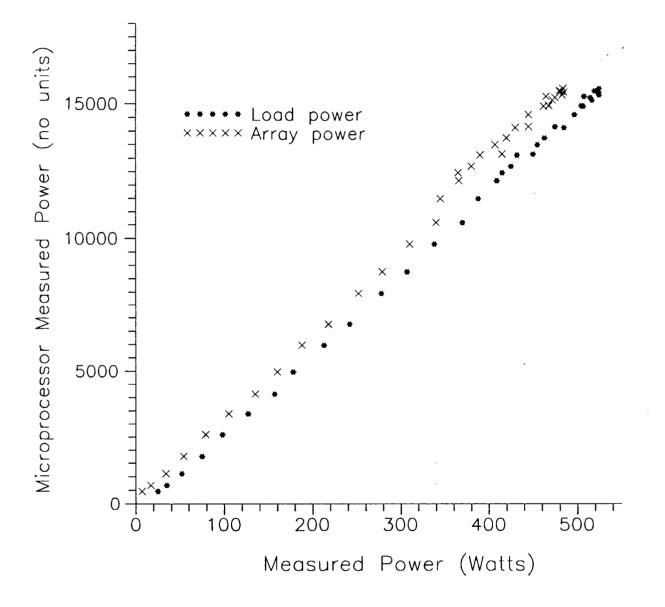

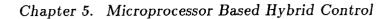

| 5.27 | Calculated Power vs Metered Power                                   | 68 |

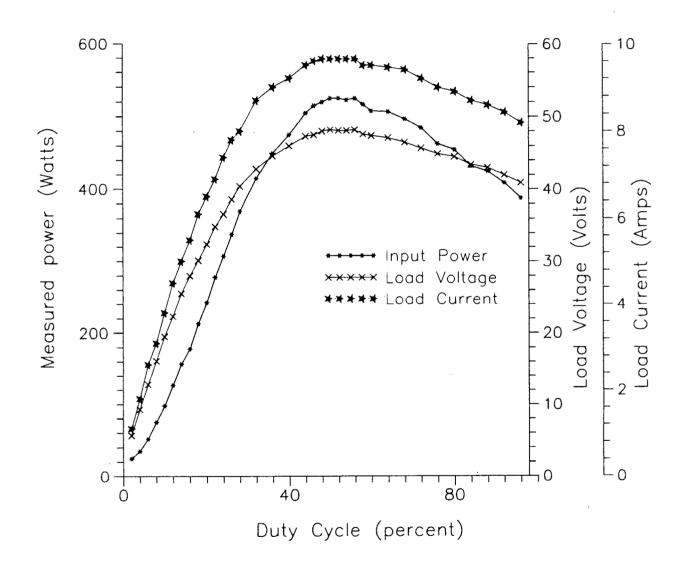

5.28 Power, Load Current, and Load Voltage vs Duty Cycle . . . . . . . . . . . . . . . . 69

### Acknowledgement

The author would like to express his appreciation to his supervisor, Dr. W. G. Dunford, for guidance and assistance during this project, and to Dr. M. D. Wvong, for assuming the role of acting supervisor during the final stages of this project.

The author also wishes to express his gratitude to his father, Mr. C. E. Passmore, for his help and assistance, and to his wife, Carol, for her understanding and support. Gratitude is also expressed to colleagues Nick Jaeger, Ben Giudici, and C.E. Sudhakar for their help.

Appreciation is also expressed to the staff of Electrical Engineering, UBC, for their helpful assistance, particularly to Alan Prince and Lloyd Welder. Appreciation is also expressed to Guang Liu for making available data on the photovoltaic array.

#### Chapter 1

#### Introduction

A photovoltaic-powered pumping system offers an attractive means of supplying water from medium head wells in locations not serviced by a utility grid. The capital cost of a system is higher than a diesel-powered pumping station but the photovoltaic system utilizes a free and inexhaustible energy source, requires very little maintenance, and can be completely automated. Therefore the long term cost and reliability of the system compares favorably with that of a diesel powered station [1].

The regions that could benefit most from such a pumping system can generally least afford it. However, industrialized countries such as Canada are willing to fund such projects. They recognize the benefits that quantities of clean drinking water would allow in the areas serviced by these pumping stations. The Canadian International Development Agency, CIDA, is currently installing test pumping stations in Morroco and is considering many more sites in various locations throughout the world. Dry tropical countries offer particularly attractive sites because of their great need of water, consistently long hours of sunshine, and lack of alternate energy sources. However, there are areas within Canada, such as the prairies or the interior of B.C. which could benefit from such a pumping system. During dry spells, water is urgently needed to feed livestock. Where ground water is present and mains power is not, a photovoltaicpowered pumping system could supply the needed water.

1

#### **1.1** System components

The photovoltaic-powered pumping system consists of an array of solar panels, a power converter, a motor, and a pump. The photovoltaic array produces a DC voltage and current, therefore, a DC motor and a DC to DC converter are the logical component choices. Some systems do employ an AC motor requiring a DC to AC converter, but for a small or medium sized system the inherent extra complexity and reduced efficiency rule it out.

A permanent-magnet DC motor is preferable to a separately-excited or compoundwound machine. The increased efficiency and reduced heating of the permanent magnet machine will justify the higher cost. A 1.1kW permanent-magnet BROT motor equipped with samarium cobalt magnets and interpole windings is used for many of the tests described in this report. This motor achieved measured efficiencies as high as 87% and has a long brush life to minimize maintenance.

The Mono progressive cavity pump is the pump of choice for this application. It is efficient over a large range of speeds and well depths [2] and is well known at many of the target sites. The pump itself is submersed at the bottom of the well and driven by a shaft running up the length of the well and connected to a motor at the top. This gives the dual advantage of having a dry, easily accessible electric motor and a submersed pump, capable of efficiently delivering water from depths of up to 150m.

#### 1.1.1 Photovoltaic Array

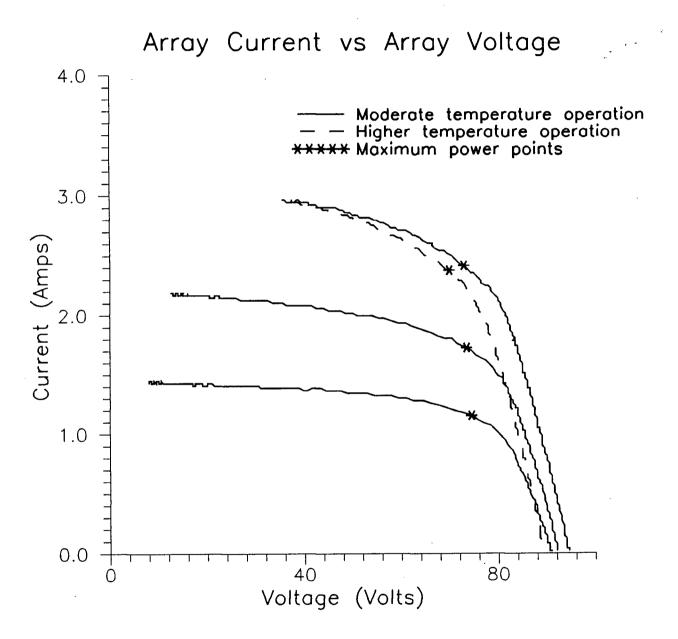

The photovoltaic array is the most expensive system component. It is therefore wise to maximize its effectiveness by extracting the maximum amount of energy from its' panels. The voltage-current curves displayed in Figure 1.1 were obtained from measurements performed on the photovoltaic array located on the roof of the Hector MacLeod building at UBC. This array is made up of two parallel strings of five series panels rated at 16V and 35w each. The curves show that the current delivered by the panels increases significantly with the insolation level as compared to the open circuit voltage which increases only a small amount. Consistent with theory [3], the open circuit voltage decreases as the temperature increases, creating intersecting curves.

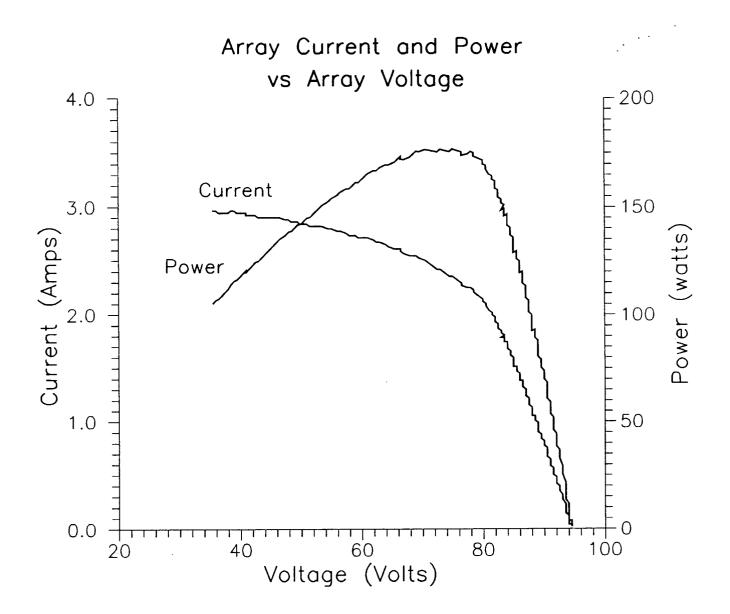

A curve displaying how the power output of the array varies with the array voltage at a particular insolation level is shown in Figure 1.2. Its jagged appearance is due to the limited eight-bit resolution of the measurement equipment. Nevertheless the general shape of the curve is clear. The peak of the power curve occurs on the knee of the corresponding voltage-current curve. The locus of maximum power points for different insolation levels is shown in Figure 1.1 and is approximately a constant voltage, variable current curve. It is apparent that a reasonable approximation to a maximum power tracking converter would be a voltage tracking converter. Such a converter would fix the array voltage at a level considered to be optimum.

The voltage-current curve tends to flatten out as the panels age, shifting the optimum operating voltage. Add to this effect the shift in the open circuit voltage with temperature and a case could be made for using a converter which can adapt to changing conditions. More practically, an adaptive converter would be able to automatically locate the best operating point regardless of the array configuration. The need for careful on-site measurements and adjustments would then be eliminated.

Figure 1.1: Voltage vs Current Curves of a Photovoltaic Array

Figure 1.2: Current and Voltage vs Power at a Set Insolation Level

#### 1.2 Thesis

This thesis covers the design and testing of three different styles of converters. The basic design of the power circuit is common to all three converters and is described in Chapter 2. The device specifications, thermal and RMS ripple current calculations, and heatsink sizing are presented in this chapter.

The voltage tracking style of converter is described in Chapter 3. It was built as a prototype for Optima Design Ltd. to be considered for use in Morroco. The control is simple, yet it is a rugged reliable device. The array voltage is set on site by means of a potentiometer which is accessible through the front of the converter.

Chapter 4 discusses an analogue maximum power tracking style of converter. It continuously searches for the maximum power point of the array and it does not require any field adjustments, however, the logic circuit is more complicated.

A hybrid maximum power tracking, voltage tracking style of converter is presented in Chapter 5. In the maximum power tracking mode it searches for the optimum operating point. Once this point has been found the array voltage is maintained at its optimum level in the voltage tracking mode. Periodically the power tracking mode is reentered to make minor adjustments to the operating voltage. The MC68HC11 makes it possible to use this more sophisticated algorithm without increasing the circuit complexity. It is able to perform the A/D conversions, execute the control algorithms, keep track of timing, and output a series of pulse width modulated output waveforms. Only a few external chips are required to assist the MC68HC11 in controlling the converter.

## Chapter 2

### **Power Converter**

#### 2.1 Component Matching

It is necessary to match the motor, pump, and photovoltaic array characteristics. Matching the D.C. motor to the Mono progressive cavity pump is relatively straightforward. Their torque-speed characteristics must be matched with possibly the aid of a mechanical gearing system. Matching the photovoltaic array to the DC motor-pump combination is more challenging. A large starting current of at least twice the rated value of the machine may be necessary to overcome the static friction of the Mono pump. Once rotating, the motor will draw an almost constant current over most of its speed range for a fixed head.

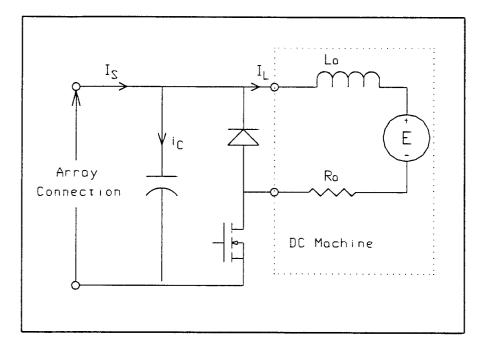

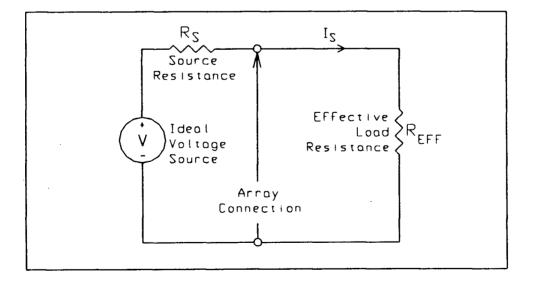

The DC-DC converter illustrated in Figure 2.3, is well suited to matching the photovoltaic and motor characteristics. It is capable of increasing the impedance of the load as seen by the source so that it is possible to extract the maximum power from the source for most lighting conditions.

This power conditioning is achieved by adjusting the ratio of the on-time to off-time, i.e. the duty cycle, of the power mosfets. During their on state the full source voltage,  $V_S$ , appears across the load while the load current,  $I_L$ , is supplied by the source and the filter capacitor. During the off state the load voltage,  $v_L$ , drops to zero while the current, maintained by the load inductance, flows through the freewheeling diode. The average load voltage,  $V_L$ , is therefore:

$$V_L = \frac{t_{ON}}{T} \cdot V_S = d \cdot V_S \tag{2.1}$$

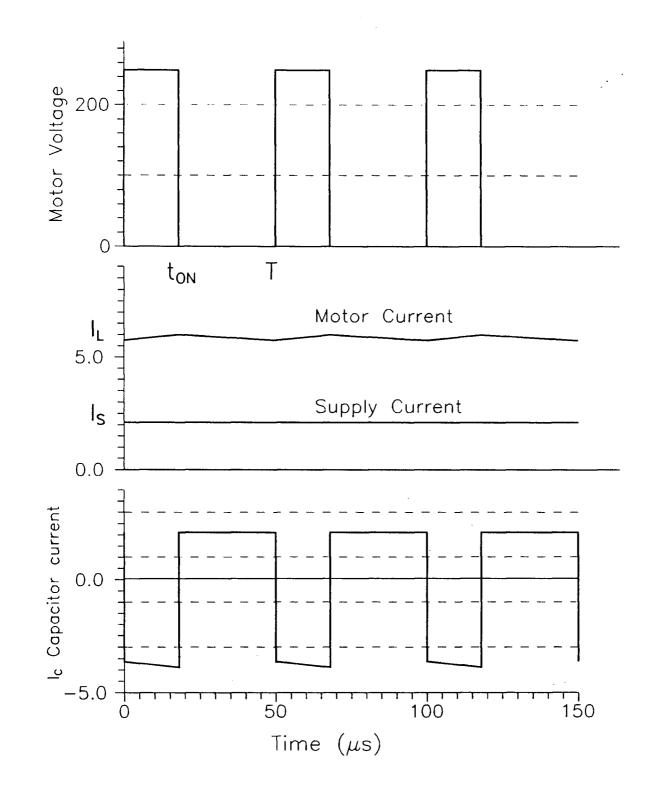

where  $t_{ON}$  is the on time, T is the period and d is the duty cycle. If the chopping frequency and load inductance are high enough the load current remains almost constant with a small ripple component. Figure 2.4 displays the voltage and current waveforms of the load, source, and filter capacitor. In the steady state the average capacitor current is zero, which implies:

$$I_S = I_L \cdot \frac{t_{ON}}{T} = I_L \cdot d \qquad (2.2)$$

The resistance of the load as seen by the source is:

$$R_{IN} = \frac{V_S}{I_S} = \frac{V_S}{I_L \cdot d}$$

$$= \frac{V_L}{I_L \cdot d^2} = R_L \cdot \frac{1}{d^2}$$

(2.3)

The chopper is in effect a transformer with turns ratio equal to the duty cycle for the purpose of transforming the voltage, current and effective resistance from one side to another. The chopper can therefore increase the load resistance by the factor of  $d^{-2}$  to capture all maximum power points lying above the base load line.

#### 2.2 Component Ratings

The reliability and efficiency of the system will depend to a large degree upon the choice of suitable components. Reliability is essential, as in most practical applications the system will be located in remote areas. Efficiency is important, as the photovoltaic panels are expensive. An increase in converter efficiency will usually result in an even greater increase in overall efficiency, as the pump and motor are generally more efficient at higher speeds.

Figure 2.3: DC to DC Converter

#### 2.2.1 Filter Capacitor

The DC-DC input capacitor is essential to fix the array voltage. It accepts current from the array during the *off* state of the mosfets and delivers current to the load while the mosfets are switched on. The value of capacitance will be determined by the allowable input voltage ripple.

Consider an example where a 0.5V ripple is acceptable with the array delivering 5A of current. The worst case will occur when the switch is either open or closed for almost all of the switching period. If the switching frequency is 20kHz, then a capacitor of at least

$$C = \frac{q}{V} = \frac{50\mu s \times 5A}{0.5V} = 500\mu F , \qquad (2.4)$$

would be required. The capacitor chosen must satisfy the RMS current requirements and withstand the peak open-circuit array voltage. From the current waveforms of Figure 2.4 and assuming a constant load current  $I_L$  the capacitor RMS current can be

calculated:

$$I_{rms} = \sqrt{\frac{1}{T} \left[ \int_{0}^{t_{ON}} (I_{S} - I_{L})^{2} dt + \int_{t_{ON}}^{T} I_{S}^{2} dt \right]} \\ = \sqrt{\frac{1}{T} \left[ I_{L}^{2} \cdot t_{ON} + I_{S}^{2} \cdot T - 2I_{S} I_{L} \cdot t_{ON} \right]}.$$

(2.5)

Substituting equation 2.2 for the source current yields:

$$I_{rms} = \sqrt{I_L^2 \frac{t_{ON}}{T} \left[1 - \frac{t_{ON}}{T}\right]} .$$

$$(2.6)$$

Which has a maximum when:

$$t_{ON} = \frac{T}{2} \tag{2.7}$$

Therefore:

$$I_{rms}(max) = \frac{I_L}{2} \tag{2.8}$$

The maximum continuous load current is usually a known quantity, so that the maximum continuous RMS capacitor current rating can be easily calculated.

### 2.2.2 Power Mosfets

The logical choice of a switching device for the converter is the power mosfet. They are easily driven by either CMOS or TTL logic chips, switch rapidly, and do not require a commutation circuit. They are robust and are readily available at the current and voltage levels typically encountered in this application. They also can easily be driven at a high enough frequency to ensure a continuous motor current.

Although the power mosfet is rugged, the designer must ensure that it is operated within its specified ratings. The ratings of concern are the maximum gate-to-source and drain-to-source voltage levels and the maximum junction operating temperature.

In this application it is not difficult to adhere to the maximum voltage ratings. A zener diode inserted between the gate and source prevents the gate voltage from rising

beyond its limit. The drain-to-source voltage rating is maintained by choosing a device rated high enough to withstand the open-circuit voltage together with the voltage spike generated as the device is switched off. This spike is minimized by paying careful attention to circuit layout and by the use of a free-wheeling diode. For further protection a zener diode may be inserted between the drain and source, or third generation devices used that have a built-in zener diode.

The current ratings listed in the device specifications are misleading as they assume a junction operating temperature of  $25^{\circ}C$  which is impractical. Realistically current ratings of the device are derived from the maximum operating junction temperature of the mosfet. It is safe to force current through the device as long as the junction temperature remains below  $150^{\circ}C$ . If the device is operated above  $150^{\circ}C$  premature failure can occur.

To arrive at an operating junction temperature for a specified current the *on* resistance must be known together with the junction to case, case to heatsink, and heatsink to ambient thermal resistances.

As an example consider the IRF730 mosfet chosen for the voltage tracking converter described in Chapter 3. Six parallel devices are used and must be capable of supplying a continuous load current of 12A and a peak current of 22A. The maximum ambient temperature is assumed to be  $55^{\circ}C$  and a heatsink will be chosen to operate at a maximum of  $30^{\circ}C$  above ambient, under rated conditions. Table 2.1 summarizes the operating conditions and device ratings.

Consider the mosfets turned fully on and delivering 12A of load current. Assume the heatsink temperature is 85°C and the junction temperature is 115°C. The calculated junction operating temperature is:

$$T_j = T_H + d * (\frac{I_L}{n})^2 * R_{ON(t)} * (T_{JC} + T_{CH})$$

| Description                                                                    | Symbol               | Value            |

|--------------------------------------------------------------------------------|----------------------|------------------|

| Ambient temperature                                                            | $T_A$                | $55^{\circ}C$    |

| Heatsink temperature                                                           | T <sub>H</sub>       | $85^{\circ}C$    |

| Junction to case thermal resistance                                            | $T_{JC}$             | $1.5^{\circ}C/W$ |

| Case to heatsink thermal resistance with an electrically insulating silica pad |                      | $1.7^{\circ}C/W$ |

| On resistance at a junction temperature. of $25^{\circ}C$                      | $R_{ON}(25^{\circ})$ | 1.0Ω             |

| On resistance at a junction temperature of $115^{\circ}C$                      | $R_{ON}(115^\circ)$  | 1.9Ω             |

$$= 85^{\circ}C + (2.0A)^{2} * 1.9\Omega * (1.5^{\circ}C/W + 1.7^{\circ}C/W)$$

$$= 109.3^{\circ}C$$

(2.9)

where n is the number of parallel mosfets.

This temperature is below the assumed value of  $115^{\circ}$ C used to determine the on resistance of the mosfets. It is also well within the safe operating temperature of  $150^{\circ}$ C. The power that must be dissipated by the heatsink due to losses within the mosfets for the above operating conditions is:

$$P_{loss} = 6 * (2.0A)^2 * 1.9\Omega = 45.6W$$

(2.10)

Consider now the converter providing peak load current, 24A, at a duty cycle of 25%. The same assumptions are made as above. The junction operating temperature would then be:

$$T_{j} = 85^{\circ}C + 0.25 * (4.0A)^{2} * 1.9\Omega * (1.5^{\circ}C/W + 1.7^{\circ}C/W)$$

= 109.3°C (2.11)

#### Chapter 2. Power Converter

with a loss of:

$$P_{loss} = 0.25 * 6 * (4.0A)^2 * 1.9\Omega = 45.6W$$

(2.12)

The mosfets are operating at a safe temperature. The array current would be 6A for these conditions and it is unlikely the duty cycle would exceed 25% as most array configurations would not be able to deliver such a large current. The load current is prevented from exceeding 24A by the current limit. Note that for these conditions there are also losses in the diode to consider.

#### 2.2.3 Diode

A freewheeling diode is essential when switching inductive loads such as a DC motor. Even a resistive load will usually contain enough stray inductance to produce an excessive voltage spike as the mosfets are switched off if the freewheeling diode is removed from the circuit.

A fast or ultra fast recovery diode is necessary to cope with the fast switching speed of the mosfets. If a slow diode is used a large reverse recovery current spike will be generated as the converter is switched on, which may damage the mosfets. This current spike also creates noise which may interfere with the operation of the logic circuits. Even when a fast recovery diode is used, it is often wise to slow down the mosfets turn-on time in order to reduce noise levels.

The converter will need to supply maximum current at a low duty cycle when the DC machine is being turned on to overcome starting torque. The diode, therefore, must be able to handle the maximum current on a continuous basis. For example, for the converter described in Chapter 3, a current rating of 30A should be adequate. The diode should also be rated at 400V to be compatible with the mosfets. The MUR3040PT ultra fast recovery diode in a T0-218AC package is the device of choice. This device is

made up of two parallel 15A, 400V diodes in the same package, with a recovery time of 50ns. The diodes are matched and thermally coupled, enabling parallel operation of the two diodes.

If the diode is operated under the same conditions used in equation (2.11) the power loss and operating junction temperature would be:

$$P_{loss} = (1-d) * I_L * V_{ON}$$

= 0.75 \* 24A \* 0.75V = 13.5W (2.13)

$$T_J = T_H + \frac{Ploss}{n} * (T_{CH} + T_{JC})$$

= 85°C +  $\frac{13.5W}{2}$  \* (1.7°C/W + 1.5°C/W)

= 106.6°C (2.14)

#### 2.2.4 Power Supply

The logic circuit requires its own power supply. The most practical way to derive this supply is directly from the photovoltaic array. The array voltage will vary at different installations and under different operating conditions while the logic voltage must remain constant.

The current requirements of the logic supply are modest, approximately 100mA, so that a simple supply is adequate. The simplest supply would consist of a resistor charging an output filter capacitor whose voltage is set by a reference zener diode. At higher input voltages excess current would be drained through the zener diode. The power supply loss increases with the square of the input voltage over its operating range. This loss is high but may be acceptable for certain applications.

The supply can be made more efficient by replacing the dropping resistor with a mosfet. The effective resistance of the mosfet is automatically adjusted to maintain a constant output voltage as the input voltage varies. The output voltage level is

maintained by the mosfet three volts below the value set by a reference zener diode attached to the gate. Only as much current as is necessary to maintain the source voltage is supplied resulting in a net loss which is directly proportional to the input voltage. This form of supply is used by the converter described in Chapter 3 and is shown in detail in Figure 3.5. The power loss in the logic supply when the array is operating at 250V is:

$$P_{loss} = 250V \times 100mA = 25W \tag{2.15}$$

A more sophisticated and efficient switched mode power supply could be used. However the extra circuit complexity would not justify the power savings achieved as only a small logic current is required. The added complexity would reduce the overall circuit reliability as well as increase costs.

Once a steady output voltage is established a single, dual or triple supply can be derived. For example the analogue maximum power tracking circuit of Chapter 4 requires a 15V, 5V and -7V supply. A linear voltage regulator is used to provide the 15V and 5V supplies from the 18V supply. The negative supply is derived with the aid of a switching regulator and a few external components.

#### 2.2.5 Heatsink

Proper sizing of the heatsink is essential for reliable operation. The heatsink must be able to maintain the temperature of the active devices within their safe operating region over a large range of ambient temperatures. To calculate the heatsink size the power being dissipated must be known along with the temperature rise above ambient which can be tolerated. It is assumed the device is operated in the shade and with its fins positioned vertically.

From the power losses calculated in equations (2.10) and (2.15) it is determined the

heatsink used in the sample converter may have to dissipate up to 70W under normal circumstances. From equations (2.11), (2.12) and (2.15) it can be seen that the losses under peak current conditions can reach as high as 84W. However, this is abnormal and peak current should only be delivered on a temporary basis. If peak current is supplied for a prolonged period, it could be expected the heatsink would warm up causing a thermal cutout to shut down the converter.

It was decided while making thermal calculations that a  $30^{\circ}$ C temperature rise between the heatsink and the environment could be tolerated. This implies a heatsink with a thermal coefficient of  $0.43^{\circ}$ C/W is required. There are many shapes and sizes of heatsinks available. A suitable heatsink for this application is heatsink #2001 from AHAM TOR INC., California.

### Chapter 3

#### Voltage Tracking Converter

### 3.1 Specifications

A DC-DC converter is to be designed for use with photovoltaic arrays of up to two kilowatts. The converter attempts to maximize the power output of the array by optimizing the operating voltage.

The converter is built to be both efficient and reliable. The power mosfets are derated to ensure a long life and reduce overall losses. A high chopping frequency minimizes the ripple voltage, ripple current and harmonic motor losses. An overtemperature cut out is built into the converter to turn it off if the motor remains stalled for a prolonged period of time. Table 3.1 summarizes the device specifications.

#### **3.2** Circuit Description

The voltage tracking converter approximates a maximum power tracking converter by fixing the array voltage at a point considered optimum. This design is based on a circuit developed and tested by Dr. W.G. Dunford and Dr. P. Ward. The logic adjusts the duty cycle of the power mosfets according to the value of the array voltage. If the voltage is too high the duty cycle is increased to bring the voltage down and vice versa. The circuit diagram is detailed in Figure 3.5. CONSTANT VOLTAGE TRACKING DC-DC CONVERTER

Figure 3.5: Circuit Diagram of the Voltage Tracking Converter

## Table 3.2: Voltage Tracking Converter Specifications.

#### **Electrical Specifications:**

| Power Rating                                             | <b>2</b> .0kW                      |  |  |  |

|----------------------------------------------------------|------------------------------------|--|--|--|

| Efficiency @ 2kW                                         | 0.90                               |  |  |  |

| Input Operating Voltage                                  | 75V - 250V                         |  |  |  |

| Input Current                                            | up to 12A                          |  |  |  |

| Output Voltage                                           | 30V - 240V                         |  |  |  |

| Continuous Output Current                                | 14A                                |  |  |  |

| Peak Output Current                                      | 24A                                |  |  |  |

| Chopping Frequency                                       | 20kHz                              |  |  |  |

| Operating ambient temperature                            | $-10^{\circ}$ C to $+55^{\circ}$ C |  |  |  |

| Relative humidity                                        | 0 to 100%                          |  |  |  |

| Automatic thermal shutdown                               |                                    |  |  |  |

| External shutdown through a normally open switch contact |                                    |  |  |  |

#### **3.2.1** Basic Operation

The logic senses the array voltage via an adjustable resistive voltage divider. This signal is inverted via an LM358 inverting operational amplifier which pivots around a 3.1V reference with a gain of minus one. The resultant signal is amplified by the internal opamp of the NE5561 PWM with a gain of minus 100 to form the reference voltage which determines the duty cycle. One volt corresponds to a 0% duty cycle while 5V corresponds to a 98% duty cycle.

The chopping frequency is set by the RC oscillator of the NE5561 to approximately 20kHz. The chopped output of the NE5561 PWM is buffered and then used as the gate drive signal.

# 3.2.2 Gate Drive

A 4041 buffer is placed between the 5561 PWM chip and the gate drive. The complementary NFET-PFET pair which forms the gate drive requires a little more switching current than the PWM can provide. Also the extra buffer helps to isolate the PWM from the power supply.

A resistor is placed in series with the positive supply of the complementary NFET-PFET pair to limit the amount of gate current which can be supplied. This slows down the switching speed of the mosfets and limits the reverse recovery current through the devices. The series resistor should be between  $29\Omega$  and  $47\Omega$  to be effective. There is no problem switching the mosfets off as fast as possible, so it is not necessary to place resistance in the ground line of the complementary FET pair.

# **3.2.3** Overcurrent Protection

Cycle by cycle overcurrent protection is provided by feeding a voltage signal proportional to the current through the mosfets to pin 6 of the NE5561. If this voltage rises above 0.6V the NE5561 output is forced high and turns off the mosfets for the remainder of the cycle. This current signal is derived from the voltage across the mosfets. A resistive voltage divider feeds a portion of the mosfets on-state voltage to the NE5561. The high off-state voltage is ignored by switching on an NPN transistor, effectively shorting the segment of the voltage divider that provides the current signal.

#### **3.2.4** Thermal Protection

The internal temperature of the converter is monitored with the aid of a thermistor. If the temperature rises beyond the limit as indicated by the 6.2V reference zener diode the converter will be shut down. Hysteresis is built around the operational amplifier, acting as a comparator, to give the converter time to cool down before the converter is restarted. Resistance values for the NTC1, R11, R15, and R22 are chosen such that the converter is shut down at 85°C and restarted at 65°C.

The sealed box which encloses the converter forms part of the heatsink so that in the steady state the internal temperature will approximately equal the temperature of the heatsinks. Also resistors and integrated circuits mounted on the printed circuit board itself produce heat that should raise the operating temperature slightly above the heatsink temperature.

All electronic components must be rated to operate in an ambient temperature of up to 85°C. The mosfets, diode and capacitor are rated to operate at this high temperature. However, all the integrated circuits used in the prototype were not. The LM358 operational amplifier should be replaced with an LM258 opamp and the NE5561 PWM should be replaced with the SE5561 PWM. These devices are rated for use over a wider temperature range and are only moderately more expensive.

# 3.2.5 Protection

Some extra components have been added to the circuit to protect the power devices:

- Two pairs of two zener diodes in series have been placed in parallel with the power mosfets to protect against overvoltages caused by any stray circuit inductance. Two pairs are used instead of one to maintain circuit symmetry. Two zeners are placed in series in each branch to form a high enough voltage rating.

- A 0.1Ω resistor is placed between source and ground of each power mosfet. This small resistance enhances the current sharing capabilities of the mosfets during switching thereby minimizing the effects of varying device current gains.

• A 16V zener diode is placed across the power supply. If the resistors provide more logic current than required, then the excess current is is bled off by the zener diode.

### 3.3 Testing and Results

To simulate a solar array source a variable DC source was used in series with a variable resistance. This would produce a linear voltage, current curve rather than the humped curve of Figure 1.1. This setup is however adequate to demonstrate the operation of the converter.

### 3.3.1 Waveforms

The converter was first tested with a load made up of a 11.5mH inductor in series with a variable resistance. The converter was run at various input voltages ranging between 50V and 250V and with input currents between 0A and 12A. Output voltages ranged between 0V to 200V and output currents between 0A to 24A.

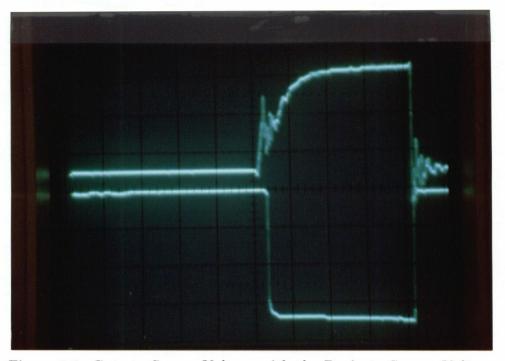

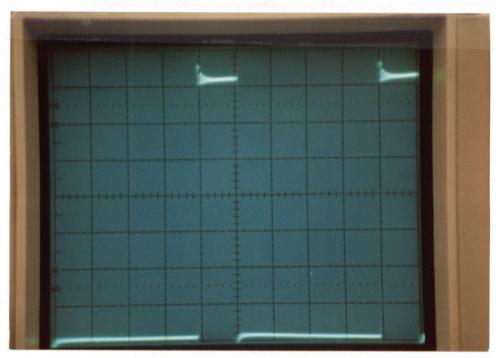

The drain to source voltage waveform is displayed in Figure 3.6. A voltage spike is evident during turn off. This is due to stray circuit inductance which is impossible to completely eliminate. The magnitude of the spike is approximately 70V and can easily be tolerated as the mosfets are rated 150V higher than the maximum input voltage. A magnified view of this spike is shown in Figure 3.7. It is seen here as a damped sinusoid with a natural frequency of 40MHz. The mosfets are protected with zener diodes which should clamp the voltage appearing across them at 350V. Even at conditions of maximum input voltage and peak output current the voltage spike across the mosfets did not approach the 350V limit.

The voltage across the mosfets drops very rapidly, even though the rise of the gate

Figure 3.6: Drain-to-Source Voltage

| $V_{IN}$ : | 200V | $V_{OUT}$ : | 123V  | 50V/div.                    |

|------------|------|-------------|-------|-----------------------------|

| $I_{IN}$ : | 7.7A | $I_{OUT}$ : | 12.1A | $10.0 \mu { m s}/{ m div}.$ |

# Chapter 3. Voltage Tracking Converter

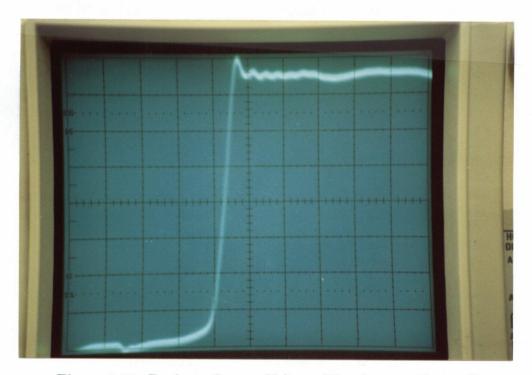

Figure 3.7: Drain-to-Source Voltage at Turn-off

| $V_{IN}$ : | 202V  | $V_{OUT}$ : | $125\mathrm{V}$ | 50V/div.          |

|------------|-------|-------------|-----------------|-------------------|

| $I_{IN}$ : | 7.52A | $I_{OUT}$ : | 11.95A          | $0.05 \mu s/div.$ |

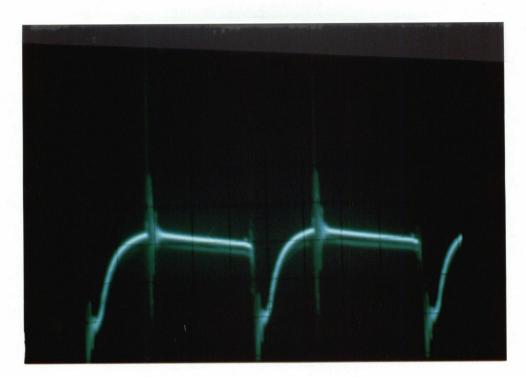

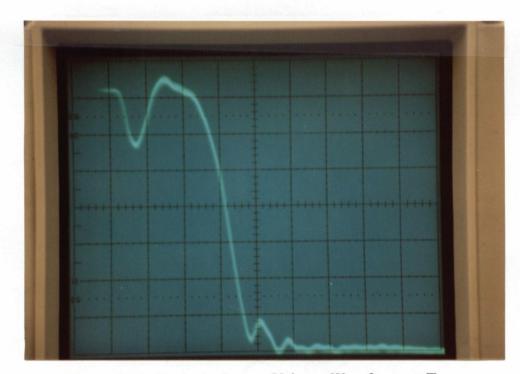

Figure 3.8: Gate-to-Source Voltage with the Drain-to-Source Voltage

| Top trace    | Gate to source | e voltage:  | $5 \mathrm{V/div}$ | $2.0 \mu \mathrm{s/div}.$ |

|--------------|----------------|-------------|--------------------|---------------------------|

| Bottom trace | Drain to sour  | ce voltage  | : 50V/div          | $2.0 \mu s/div.$          |

| $V_{IN}$ :   | 200V           | $V_{OUT}$ : | 35V                |                           |

| $I_{IN}$ :   | 1.7A           | $I_{OUT}$ : | 9.3A               |                           |

voltage is limited by a series resistor. The drain to source voltage together with the gate voltage is shown in Figure 3.8. The gate voltage takes approximately  $0.5\mu$ s to rise to near its' peak value, however the drain to source voltage falls so rapidly that it appears instantaneous. There is a delay of about  $0.15\mu$ s from the instant that the gate voltage starts to rise and the drain to source voltage falls. This is because the drain to source voltage is constrained to remain high until the mosfets are conducting the full load current. The rate at which current through the FET can rise is limited by the current gain of the device during switching. Limiting the gate current therefore limits the rate of rise of the current through the mosfet. This slows down the switching process and limits the peak recovery current through the device.

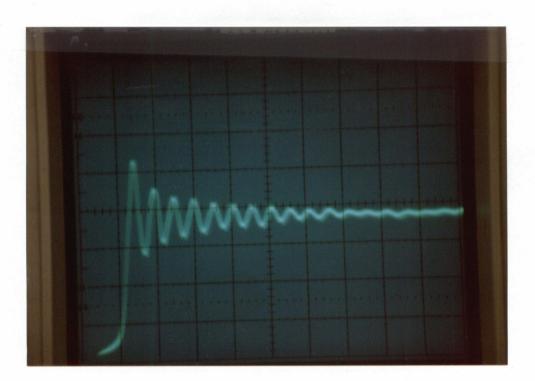

The signal used by the PWM to measure the current through the mosfets is shown in Figure 3.9. The displayed signal is turning off the mosfets on a cycle by cycle basis as the voltage exceeds the threshold level. The level at which the overcurrent protection engages is determined by the relative resistance values of R32, R33, and R34 in the voltage divider of Figure 3.5.

The PWM only samples the current signal when the mosfets are turned on. The signal voltage during the mosfets off-state is ignored even though it may be higher than the cutoff threshold value. Also during the switching intervals a considerable amount of noise is present in the current signal. However, the operation of the overcurrent detector is not adversely effected.

Figure 3.9 shows the current signal dipping down when the mosfets are first turned on. The signal grows as stray circuit capacitance is charged up through the resistive divider network. When the voltage builds up to the internal reference level of the NE5561, the mosfets are shut off creating the noise spikes visible on the waveform. The shorting transistor, Q2, is turned on when the mosfets are turned off preventing the current signal from going excessively high.

The over-temperature protection was tested by operating the device with a peak load current for a prolonged period of time. The converter shut itself off when the internal temperature reached approximately 85°C and automatically restarted when the temperature cooled to 65°C. The slow-start circuitry on the NE5561 and the overcurrent protection prevented excessive current from flowing through the converter as it was restarted.

Figure 3.9: Current Signal

| $V_{IN}$ : | 223V | $V_{OUT}$ : | 84V   | $20 \mathrm{mV/div}$ . |

|------------|------|-------------|-------|------------------------|

| $I_{IN}$ : |      | $I_{OUT}$ : | 18.5A | $10\mu s/div.$         |

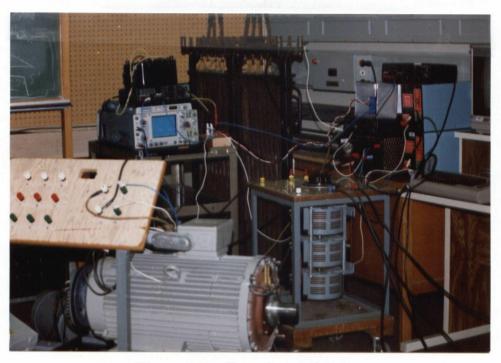

Figure 3.10: Experimental Set-up

## 3.3.2 Efficiency

The converter was also tested by driving a 2.5hp DC motor which in turn drove an induction machine operating as a generator. The generator supplied power to a resistive three-phase load. The generator load could be adjusted in order to vary the loading of the DC machine. Figure 3.10 shows the experimental set up.

No problems were experienced by the converter driving the DC machine. The overcurrent protection operated successfully during machine start up and the starting torque was easily overcome. Measurements made to determine the converter efficiency are displayed in Table 3.3. The peak efficiency of the converter is about 96% which exceeds the design specifications.

| Duty                                                                  | Input                                                                                                  | Input                                                                                | Input                                                                           | Output                                                                      | Output                                                                              | Output                                                                                    | Efficiency.                                                                            |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Cycle                                                                 | Voltage                                                                                                | Current                                                                              | Power                                                                           | Voltage                                                                     | Current                                                                             | Power                                                                                     | $\eta$                                                                                 |

|                                                                       |                                                                                                        | ductive loa                                                                          |                                                                                 | vonuge                                                                      | Current                                                                             | 10000                                                                                     | · <u> </u>                                                                             |

| 0%                                                                    | $\frac{15 \text{mA}}{15 \text{mA}}$                                                                    | 180V                                                                                 | 2.7W                                                                            | 0A                                                                          | 0V                                                                                  | 0W                                                                                        | 0                                                                                      |

| $\frac{0\%}{14\%}$                                                    | $\frac{1000}{198.5V}$                                                                                  | 1.4A                                                                                 | 278W                                                                            | 30.0V                                                                       | 6.8A                                                                                | 204W                                                                                      | 0.734                                                                                  |

| $\frac{14}{0}$ 28%                                                    | 198.3 V<br>199.8V                                                                                      | 1.4A<br>3.55A                                                                        | 218 W                                                                           | 55V                                                                         | 12.2A                                                                               | 204 W                                                                                     | 0.734                                                                                  |

| 40%                                                                   | 199.8 V<br>201.5 V                                                                                     | 3.55A<br>7.3A                                                                        | 1471W                                                                           | 80V                                                                         | 12.2A<br>18A                                                                        |                                                                                           |                                                                                        |

|                                                                       |                                                                                                        |                                                                                      |                                                                                 |                                                                             |                                                                                     | 1440W                                                                                     | 0.978                                                                                  |

| 9.3%                                                                  | 200.2V                                                                                                 | 0.22A                                                                                | 44W                                                                             | 18.3V                                                                       | 1.9A                                                                                | 34.8W                                                                                     | 0.789                                                                                  |

| 25%                                                                   | 200.5V                                                                                                 | 1.3A                                                                                 | 261 W                                                                           | 49V                                                                         | 5.1A                                                                                | 250W                                                                                      | 0.958                                                                                  |

| 47%                                                                   | 201.5V                                                                                                 | 4.57A                                                                                | 921W                                                                            | 93.5V                                                                       | 9.5A                                                                                | 888W                                                                                      | 0.964                                                                                  |

| 66%                                                                   | 204V                                                                                                   | 8.95A                                                                                | 1826W                                                                           | 133V                                                                        | 13.25A                                                                              | 1762W                                                                                     | 0.965                                                                                  |

| 71%                                                                   | 205V                                                                                                   | 10.0A                                                                                | 2050W                                                                           | 141V                                                                        | 14.0A                                                                               | 1974W                                                                                     | 0.963                                                                                  |

| 76%                                                                   | 206.5V                                                                                                 | 4.44A                                                                                | 917W                                                                            | 155V                                                                        | 5.7A                                                                                | 883W                                                                                      | 0.963                                                                                  |

| 90%                                                                   | 208V                                                                                                   | 6.4A                                                                                 | 1331W                                                                           | 187V                                                                        | 6.97A                                                                               | 1303W                                                                                     | 0.979                                                                                  |

| 95%                                                                   | 209V                                                                                                   | 7.4A                                                                                 | 1547W                                                                           | 202V                                                                        | 7.53A                                                                               | 1521W                                                                                     | 0.983                                                                                  |

| Speed                                                                 | Input                                                                                                  | Input                                                                                | Input                                                                           | Output                                                                      | Output                                                                              | Output                                                                                    | Efficiency                                                                             |

| r/min                                                                 | Voltage                                                                                                | Current                                                                              | PoWer                                                                           | Voltage                                                                     | Current                                                                             | PoWer                                                                                     | η                                                                                      |

|                                                                       | vonage                                                                                                 | Current                                                                              | rower                                                                           | , on a b c                                                                  |                                                                                     |                                                                                           | 1 1                                                                                    |

|                                                                       | otor load:                                                                                             | Current                                                                              | rower                                                                           | · onuge                                                                     |                                                                                     |                                                                                           | <u> </u>                                                                               |

|                                                                       |                                                                                                        | 4.45A                                                                                | 627W                                                                            | 98.5V                                                                       | 6.1A                                                                                | 601W                                                                                      | 0.958                                                                                  |

| DC Me                                                                 | otor load:                                                                                             | <b></b>                                                                              | ·····                                                                           |                                                                             |                                                                                     |                                                                                           |                                                                                        |

| DC Me<br>1000                                                         | otor load:<br>141V                                                                                     | 4.45A                                                                                | 627W                                                                            | 98.5V                                                                       | 6.1A                                                                                | 601W                                                                                      | 0.958                                                                                  |

| DC Mo<br>1000<br>1000                                                 | otor load:<br>141V<br>141V                                                                             | 4.45A<br>5.18A                                                                       | 627W<br>730W                                                                    | 98.5V<br>99V                                                                | 6.1A<br>7.1A                                                                        | 601W<br>703W                                                                              | 0.958<br>0.962                                                                         |

| DC Me<br>1000<br>1000<br>1000                                         | otor load:<br>141V<br>141V<br>141.5V                                                                   | 4.45A<br>5.18A<br>7.59A                                                              | 627W<br>730W<br>1074W                                                           | 98.5V<br>99V<br>98V                                                         | 6.1A<br>7.1A<br>10.5A                                                               | 601W<br>703W<br>1029W                                                                     | 0.958<br>0.962<br>0.958                                                                |

| DC Me<br>1000<br>1000<br>1000<br>1500                                 | otor load:<br>141V<br>141V<br>141.5V<br>190.8V                                                         | 4.45A<br>5.18A<br>7.59A<br>2.14A                                                     | 627W<br>730W<br>1074W<br>408W                                                   | 98.5V<br>99V<br>98V<br>137V                                                 | 6.1A<br>7.1A<br>10.5A<br>2.74A                                                      | 601W<br>703W<br>1029W<br>375W                                                             | 0.958<br>0.962<br>0.958<br>0.920                                                       |

| DC Me<br>1000<br>1000<br>1000<br>1500<br>1500                         | otor load:<br>141V<br>141V<br>141.5V<br>190.8V<br>191.2V                                               | 4.45A<br>5.18A<br>7.59A<br>2.14A<br>3.60A                                            | 627W<br>730W<br>1074W<br>408W<br>688W                                           | 98.5V<br>99V<br>98V<br>137V<br>138V                                         | 6.1A<br>7.1A<br>10.5A<br>2.74A<br>4.75A                                             | 601W<br>703W<br>1029W<br>375W<br>655W                                                     | 0.958<br>0.962<br>0.958<br>0.920<br>0.952                                              |

| DC Mo<br>1000<br>1000<br>1500<br>1500<br>1500                         | otor load:<br>141V<br>141V<br>141.5V<br>190.8V<br>191.2V<br>192.1V                                     | 4.45A<br>5.18A<br>7.59A<br>2.14A<br>3.60A<br>5.89A                                   | 627W<br>730W<br>1074W<br>408W<br>688W<br>1131W                                  | 98.5V<br>99V<br>98V<br>137V<br>138V<br>142V                                 | 6.1A<br>7.1A<br>10.5A<br>2.74A<br>4.75A<br>7.68A                                    | 601W<br>703W<br>1029W<br>375W<br>655W<br>1090W                                            | 0.958<br>0.962<br>0.958<br>0.920<br>0.952<br>0.964                                     |

| DC Me<br>1000<br>1000<br>1500<br>1500<br>1500<br>1500                 | btor load:<br>141V<br>141V<br>141.5V<br>190.8V<br>191.2V<br>192.1V<br>200V                             | 4.45A<br>5.18A<br>7.59A<br>2.14A<br>3.60A<br>5.89A<br>9.1A                           | 627W<br>730W<br>1074W<br>408W<br>688W<br>1131W<br>1820W                         | 98.5V<br>99V<br>98V<br>137V<br>138V<br>142V<br>145V                         | 6.1A<br>7.1A<br>10.5A<br>2.74A<br>4.75A<br>7.68A<br>11.86A                          | 601W<br>703W<br>1029W<br>375W<br>655W<br>1090W<br>1720W                                   | 0.958<br>0.962<br>0.958<br>0.920<br>0.952<br>0.964<br>0.945                            |

| DC Me<br>1000<br>1000<br>1500<br>1500<br>1500<br>1500<br>2000         | otor load:<br>141V<br>141V<br>141.5V<br>190.8V<br>191.2V<br>192.1V<br>200V<br>215.6V                   | 4.45A<br>5.18A<br>7.59A<br>2.14A<br>3.60A<br>5.89A<br>9.1A<br>2.45A                  | 627W<br>730W<br>1074W<br>408W<br>688W<br>1131W<br>1820W<br>528W                 | 98.5V<br>99V<br>98V<br>137V<br>138V<br>142V<br>145V<br>188V                 | 6.1A<br>7.1A<br>10.5A<br>2.74A<br>4.75A<br>7.68A<br>11.86A<br>2.18A                 | 601 W<br>703 W<br>1029 W<br>375 W<br>655 W<br>1090 W<br>1720 W<br>410 W                   | 0.958<br>0.962<br>0.958<br>0.920<br>0.952<br>0.964<br>0.945<br>0.776                   |

| DC Me<br>1000<br>1000<br>1500<br>1500<br>1500<br>1500<br>2000<br>2000 | btor load:<br>141V<br>141V<br>141.5V<br>190.8V<br>191.2V<br>192.1V<br>200V<br>215.6V<br>216V           | 4.45A<br>5.18A<br>7.59A<br>2.14A<br>3.60A<br>5.89A<br>9.1A<br>2.45A<br>3.21A         | 627W<br>730W<br>1074W<br>408W<br>688W<br>1131W<br>1820W<br>528W<br>693W         | 98.5V<br>99V<br>98V<br>137V<br>138V<br>142V<br>145V<br>188V<br>187V         | 6.1A<br>7.1A<br>10.5A<br>2.74A<br>4.75A<br>7.68A<br>11.86A<br>2.18A<br>3.6A         | 601W<br>703W<br>1029W<br>375W<br>655W<br>1090W<br>1720W<br>410W<br>673W                   | 0.958<br>0.962<br>0.958<br>0.920<br>0.952<br>0.964<br>0.945<br>0.776<br>0.971          |

| DC Me<br>1000<br>1000<br>1500<br>1500<br>1500<br>1500<br>2000<br>2000 | btor load:<br>141V<br>141V<br>141.5V<br>190.8V<br>191.2V<br>192.1V<br>200V<br>215.6V<br>216V<br>242.8V | 4.45A<br>5.18A<br>7.59A<br>2.14A<br>3.60A<br>5.89A<br>9.1A<br>2.45A<br>3.21A<br>4.1A | 627W<br>730W<br>1074W<br>408W<br>688W<br>1131W<br>1820W<br>528W<br>693W<br>995W | 98.5V<br>99V<br>98V<br>137V<br>138V<br>142V<br>145V<br>188V<br>187V<br>185V | 6.1A<br>7.1A<br>10.5A<br>2.74A<br>4.75A<br>7.68A<br>11.86A<br>2.18A<br>3.6A<br>5.0A | 601 W<br>703 W<br>1029 W<br>375 W<br>655 W<br>1090 W<br>1720 W<br>410 W<br>673 W<br>925 W | 0.958<br>0.962<br>0.958<br>0.920<br>0.952<br>0.964<br>0.945<br>0.776<br>0.971<br>0.929 |

| Table 3.3: Converter Efficiency | Table | 3.3: | Converter | Efficiency |

|---------------------------------|-------|------|-----------|------------|

|---------------------------------|-------|------|-----------|------------|

J

### Chapter 4

## **Maximum Power Tracking Converter**

A true maximum power point controller that will automatically adjust to different input conditions is described in this chapter. This converter is designed to operate at power levels of up to one kilowatt and was tested using the facilities at B.C. Hydro-Research, Surrey, B.C.

#### 4.1 The Logic Circuit

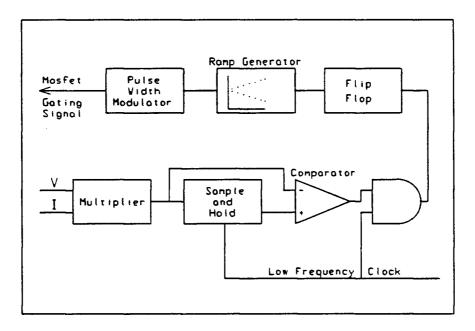

The control circuit illustrated in the block diagram of Figure 4.11 provides true maximum power point tracking. The controller adjusts the conversion ratio to maximize the array voltage and current product.

The array voltage is sampled directly using a resistive voltage divider. The array current, however, is derived from the voltage across the mosfet. During its on state, the mosfet appears as a resistive element. The average on state voltage is proportional to the current through the device which is in turn proportional to the steady state array current. Changes in the mosfet resistance with temperature are unimportant as only relative changes in the current signal are of interest and not its absolute value.

The average array current and voltage signals are multiplied using an analog multiplier to produce an output power signal. A low frequency (3 Hz.) clock latches the power level into the sample and hold unit. The controller then changes the conversion ratio of the DC to DC converter. At the end of the cycle the instantaneous power level is compared with the sampled power level.

31

If the power level has increased, another change is made to the conversion ratio in the same direction. If the power level has decreased, the change in the conversion ratio is made in the opposite direction.

When the converter is first switched on, the conversion ratio is set to its minimum value and *climbs the hill* to the value corresponding to the maximum power point. In the steady state, the duty cycle toggles around this optimum value.

Two sets of low frequency timing pulses are required to synchronize the controller. Both pulses are very short, approximately  $10\mu s$ , with the second pulse immediately following the first.

The first pulse is logically *anded* with the power level comparator output and then used as the clock input to a JK flip-flop. When the power level is decreasing, the comparator output goes high, allowing the timing pulse to propagate through to the flip-flop, causing its outputs to toggle.

The complementary flip-flop outputs are each logically *anded* with the second timing pulse. One of the resulting signals has its polarity reversed. Once every cycle, there is either a positive or negative pulse generated, depending on the state of the flip flop outputs.

These positive and negative pulses are then integrated and scaled to form the input of a pulse width modulator. As the pulses are narrow, the duty cycle is changed quickly at the beginning of each cycle. For the rest of the cycle the duty cycle is held constant while the motor and control circuit transients decay. The instantaneous power signal then represents a steady state value and a true comparison can be made with the last sampled power level.

Some additional features include over-current protection which is provided on a cycle by cycle basis. If the measured current signal rises above a threshold level, a flip flop is set, turning off the power mosfet. The next gating signal resets the flip flop

allowing the power mosfet to be turned on again.

The converter is also capable of being shut down if the motor overheats. The temperature signal provided by the DC motor can disable the gating signal as it switches from an open to a short circuit, or vice versa.

# 4.2 Results

The hydraulic test equipment consisted of a 200-litre storage tank in which various Mono progressive cavity pumps could be inserted. The pump is discharged into a pressure tank regulated by a back pressure sustaining valve. By adjusting the pressure, well depths ranging between 10 to 65 meters can be simulated. Water from the pressure tank is discharged back into the storage tank. The power output of the pump is calculated by multiplying the water flow rate with the back pressure.

The electrical system consisted of the panels, converter and motor. The photovoltaic array consisted of two parallel strings of 11 panels, producing a maximum power of 770 watts and nominal voltage of 165 V. The array was kindly supplied by British Columbia Hydro and Power Authority, Research and Development Division, which also provided laboratory space. Power from the array was routed through the DC - DC converter to a Brot 1.1 kW permanent magnet DC motor which directly coupled to the Mono pump.

The system was tested at various insolation levels and well depths. The greatest system losses occur during the conversion of sunlight to electricity, which proceeds at an efficiency of 0.083. A large loss is inevitable due to the physics of the conversion process.

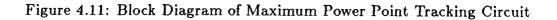

The converter successfully altered the conversion ratio to track the maximum power point of the array for most light conditions. Figure 4.12 displays the power developed

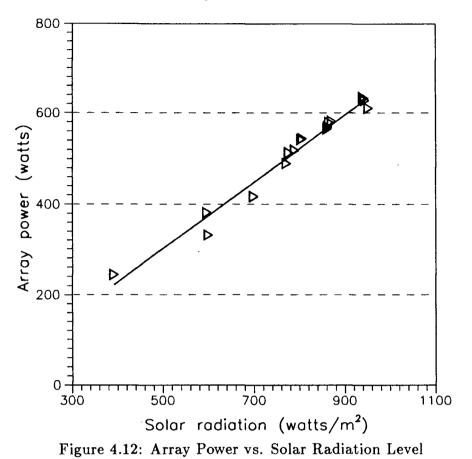

by the array for various levels of solar radiation. The converter was also able to deliver enough current to develop the required starting torque at all simulated well depths. The efficiency of the converter, as calculated by the output converter power divided by input array power (as shown in Figure 4.13), ranged from 0.75 to 0.91 with an average of 0.84. Losses were incurred in the power mosfets, the freewheeling diode and the logic power supply. The voltage tracking converter of Chapter 3 turned out to be slightly more efficient because it used six parallel power mosfets of a similar rating to the two used here. Also the voltage tracking converter used a more efficient power supply.