## ON MULTIPLE INTERMEDIATE SIGNATURE ANALYSIS FOR BUILT-IN SELF-TEST

By

#### Yuejian Wu

B. A. Sc. Beijing University of Aeronautics & Astronautics, P.R. China, 1982

M. A. Sc. Beijing University of Aeronautics & Astronautics, P.R. China, 1985

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

in

THE FACULTY OF GRADUATE STUDIES

DEPARTMENT OF ELECTRICAL ENGINEERING

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

1993

© Yuejian Wu, 1993

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

(Signature)

Department of Electrical Engineering

The University of British Columbia Vancouver, Canada

Date Nov. 4, 1993

#### Abstract

Built-In Self-Test (BIST) is becoming a widely accepted means for testing VLSI circuits. BIST usually consists of two major functions known as on chip test pattern generation and test response evaluation. There are two major difficulties regarding test response evaluation. The first is reducing the error escape rate or aliasing while still maintaining reasonably small hardware requirements. The other is accurately assessing the impact of aliasing on the overall test quality of a BIST scheme. This dissertation addresses these two difficulties by developing a group of techniques known as multiple intermediate signature analysis. Compared to the conventional single signature analysis, multiple intermediate signature analysis has many advantages, e.g., smaller aliasing, easier exact fault coverage computation, shorter average test time, and increased fault diagnosability.

Based on the investigation of an aliasing model, this dissertation develops a comprehensive fault coverage model for predicting the fault coverage performance with multiple intermediate signature analysis. In addition to the parameters used in the aliasing model, such as the number of intermediate signatures and the length of each signature, the proposed model also includes information on the scheduling of intermediate signatures.

In addition to the studies on the conventional multiple intermediate signature analysis, referred to as CMS schemes, this dissertation also describes two novel multiple intermediate signature analysis techniques. The first is a fuzzy multiple intermediate signature analysis, or simply called the FMS scheme. Unlike the CMS schemes, where each checked signature must correspond to a specific reference on a one-to-one basis for a circuit under test (CUT) to be declared good, the FMS scheme declares a CUT good if each checked signature maps to any element of the same set of references. In comparison, the FMS scheme is very simple and easy to implement. A complete theory for the aliasing performance and

hardware requirement prediction with the FMS scheme is derived.

The second novel multiple intermediate signature analysis proposed in this dissertation is single reference multiple intermediate signature analysis, simply referred to as the SMS scheme. Conventionally, checking n signatures requires n references. With the SMS scheme, however, regardless of the number of checked signatures, only one single reference is needed. The SMS scheme requires minimal hardware for multiple intermediate signature analysis, i.e., essentially the same amount of hardware as for conventional single signature analysis. To efficiently implement the SMS scheme, a systematic approach is developed based on the discovery of some identical signature properties. This implementation approach of the SMS scheme does not require any circuit modification of the CUTs. The cost for implementing the SMS scheme is a non-recurring CPU time overhead in the design phase. In return, the SMS scheme yields significantly recurring silicon area savings as well as reduced aliasing. With the algorithms provided in this dissertation, The CPU time overhead for implementing the SMS scheme is very small. For example, if the SMS scheme is used to check two 16-bit signatures, which yields 65,536 times smaller aliasing at no extra hardware cost compared to conventional single signature schemes, the total CPU time overhead required for implementing the SMS scheme is less than 4 seconds on a Sun Sparc 2 workstation for a test length of 2<sup>20</sup>, independently of the size of CUTs.

#### Table of Contents

| A                | bstra             | ct                                             | ii   |  |  |

|------------------|-------------------|------------------------------------------------|------|--|--|

| $\mathbf{T}_{i}$ | Table of Contents |                                                |      |  |  |

| Li               | st of             | Tables                                         | viii |  |  |

| Li               | st of             | Figures                                        | ix   |  |  |

| A                | cknov             | wledgement                                     | хi   |  |  |

| C.               | laims             | of Originality                                 | xii  |  |  |

| 1                | Intr              | oduction                                       | 1    |  |  |

|                  | 1.1               | Dissertation Objective and Outline             | 1    |  |  |

|                  | 1.2               | Fault Models                                   | 3    |  |  |

|                  | 1.3               | Test Quality Measures                          | 5    |  |  |

|                  | 1.4               | Conventional Approach to IC Testing            | 6    |  |  |

|                  | 1.5               | Design for Testability                         | 7    |  |  |

|                  | 1.6               | Built-In Self-Test                             | 9    |  |  |

|                  | 1.7               | Test Quality Problems of BIST                  | 10   |  |  |

| 2                | Buil              | t-in Self-Testing                              | 12   |  |  |

|                  | 2.1               | Hardware Models of BIST                        | 12   |  |  |

|                  | 2.2               | An Important BIST Component — LFSR             | 15   |  |  |

|                  | 2.3               | Test Pattern Generation                        | 18   |  |  |

|                  |                   | 2.3.1 Exhaustive and Pseudo-exhaustive Testing | 18   |  |  |

|   |      | 2.3.2    | Pseudorandom Testing                                    | 20 |

|---|------|----------|---------------------------------------------------------|----|

|   | 2.4  | Test I   | Response Evaluation                                     | 22 |

|   |      | 2.4.1    | LFSR-based Data Compaction                              | 23 |

|   |      | 2.4.2    | Counter-based Data Compaction                           | 25 |

| 3 | Alia | asing a  | and Aliasing Reduction Techniques                       | 27 |

|   | 3.1  | Aliasi   | ng Measures and Error Models                            | 27 |

|   |      | 3.1.1    | Aliasing Measures                                       | 27 |

|   |      | 3.1.2    | Error Models                                            | 29 |

|   | 3.2  | Advar    | nced Compaction Techniques                              | 32 |

|   |      | 3.2.1    | Multiple Signature Analysis                             | 32 |

|   |      | 3.2.2    | Output Data Modification (ODM)                          | 35 |

|   |      | 3.2.3    | Zero Aliasing Techniques                                | 36 |

|   |      | 3.2.4    | Modified LFSR                                           | 40 |

| 4 | Mu   | ltiple ] | Intermediate Signature Analysis — I                     | 42 |

|   | 4.1  | An Al    | iasing Model                                            | 43 |

|   | 4.2  | Fault    | Coverage Models                                         | 44 |

|   |      | 4.2.1    | Preliminaries                                           | 44 |

|   |      | 4.2.2    | A Comprehensive Fault Coverage Model                    | 46 |

|   |      | 4.2.3    | A Simplified Fault Coverage Model                       | 49 |

| 5 | Mu   | ltiple l | Intermediate Signature Analysis — II                    | 52 |

|   | 5.1  | Possib   | ole Implementations                                     | 52 |

|   |      | 5.1.1    | Conceptual Understanding of Multiple Signature Analysis | 52 |

|   |      | 5.1.2    | Straightforward Implementations                         | 53 |

|   |      | 5.1.3    | An Implementation by Resource Sharing                   | 55 |

|   | 5.2  | Test F   | Result Observation                                      | 57 |

| 5.3  | Control of Multiple Signature Analysis           | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4  | Applications                                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 5.4.1 Exact BIST Fault Coverage Calculation      | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 5.4.2 Test Time Reduction                        | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 5.4.3 BIST Failure Diagnosis                     | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fuz  | zy Multiple Signature Analysis                   | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.1  | Basis and Implementations                        | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 6.1.1 Basis                                      | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 6.1.2 Implementation                             | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.2  | FMS Aliasing Performance Analysis                | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.3  | FMS Hardware Requirement Analysis                | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.4  | Comparative Evaluation of the FMS Scheme         | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 6.4.1 FMS vs. SS                                 | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 6.4.2 FMS vs. M-LFSR                             | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 6.4.3 FMS vs. CMS                                | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.5  | Experimental Results                             | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.6  | Conclusions                                      | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sing | gle Reference Multiple Signature Analysis        | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.1  | Basis                                            | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.2  | Preliminaries                                    | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |                                                  | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 7.2.2 Non-singular LFSRs                         | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.3  | Identical Signature Properties                   | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.4  | Fast Realization of the SMS Scheme               | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |                                                  | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 7.4.2 IPG and SA Seeds Selection                 | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 5.4  Fuz 6.1  6.2 6.3 6.4  6.5 6.6  Sing 7.1 7.2 | 5.4 Applications  5.4.1 Exact BIST Fault Coverage Calculation  5.4.2 Test Time Reduction  5.4.3 BIST Failure Diagnosis  Fuzzy Multiple Signature Analysis  6.1 Basis and Implementations  6.1.1 Basis  6.1.2 Implementation  6.2 FMS Aliasing Performance Analysis  6.3 FMS Hardware Requirement Analysis  6.4 Comparative Evaluation of the FMS Scheme  6.4.1 FMS vs. SS  6.4.2 FMS vs. M-LFSR  6.4.3 FMS vs. CMS  6.5 Experimental Results  6.6 Conclusions  Single Reference Multiple Signature Analysis  7.1 Basis  7.2 Preliminaries  7.2.1 Signature Analysis  7.2.2 Non-singular LFSRs  7.3 Identical Signature Properties  7.4 Fast Realization of the SMS Scheme  7.4.1 Efficient Sample Sequences Generation |

|                  | 7.5        | Cost a | and Performance                                   | 95  |

|------------------|------------|--------|---------------------------------------------------|-----|

|                  |            | 7.5.1  | L vs. Aliasing Performance                        | 96  |

|                  |            | 7.5.2  | CPU Time Overhead for Implementing the SMS Scheme | 97  |

|                  |            | 7.5.3  | A Special Case: $k=1$                             | 100 |

|                  | 7.6        | Exper  | imental Results                                   | 101 |

|                  | 7.7        | Discus | ssions                                            | 104 |

|                  | 7.8        | Extens | sions                                             | 106 |

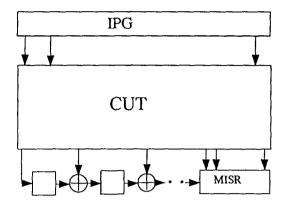

|                  |            | 7.8.1  | Applications to MISR                              | 106 |

|                  |            | 7.8.2  | Extensions to the FMS                             | 107 |

|                  |            | 7.8.3  | Applications to Weighted Random Testing           | 108 |

|                  | 7.9        | Conclu | isions                                            | 108 |

| 8                | Con        | clusio | ns                                                | 110 |

|                  | 8.1        | Summ   | ary                                               | 110 |

|                  | 8.2        | Future | e Work                                            | 112 |

| Bi               | bliog      | graphy |                                                   | 114 |

| $\mathbf{A}_{1}$ | Appendix A |        |                                                   | 126 |

| $\mathbf{A}_{1}$ | ppen       | dix B  |                                                   | 128 |

#### List of Tables

| 6.1  | The FMS scheme vs. the M-LFSR scheme when a LFSR is used              | 76  |

|------|-----------------------------------------------------------------------|-----|

| 6.2  | The FMS scheme vs. the M-LFSR scheme when a MISR is used              | 76  |

| 6.3  | Fault coverage enhancements                                           | 78  |

| 6.4  | Fault simulation time reductions                                      | 79  |

|      |                                                                       |     |

| 7.5  | Example RIS probabilities                                             | 88  |

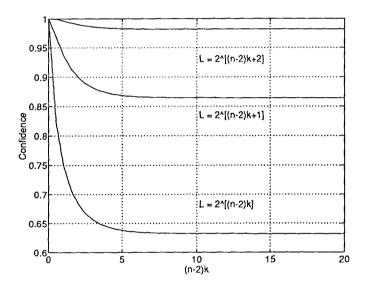

| 7.6  | $L$ vs. lower bounds on confidence, given $P_{al} \approx 2^{-nk}$    | 97  |

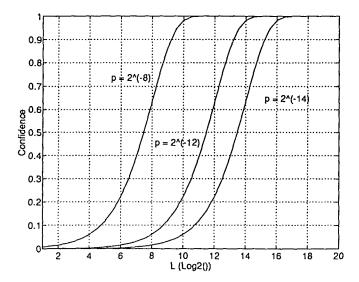

| 7.7  | Examples of $n$ , $k$ , confidence and required $L$                   | 98  |

| 7.8  | Example CPU time overheads for the SMS scheme                         | 99  |

| 7.9  | Example average CPU time overheads of the SMS scheme                  | 100 |

| 7.10 | $L$ vs. lower bounds on confidence for $p=2^{-(n-1)k}$                | 101 |

| 7.11 | Experimental results for $l=2^{16}$                                   | 102 |

| 7.12 | Experimental results for $l=2^{20}$                                   | 103 |

| 7.13 | Experimental results for $n = 16$ and $k = 1 \dots \dots \dots \dots$ | 103 |

### List of Figures

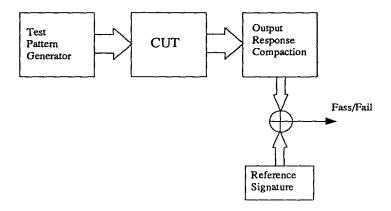

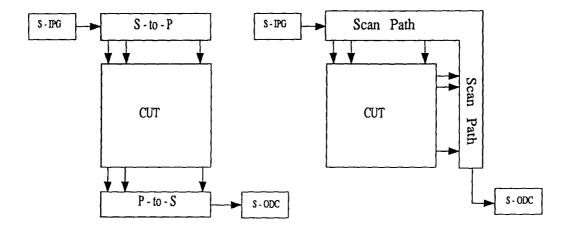

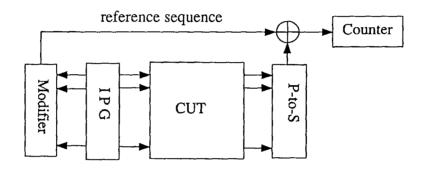

| 2.1  | General BIST scheme                                     | 13 |

|------|---------------------------------------------------------|----|

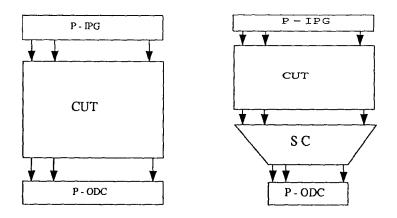

| 2.2  | The parallel-parallel BIST model                        | 13 |

| 2.3  | The parallel-serial BIST model                          | 14 |

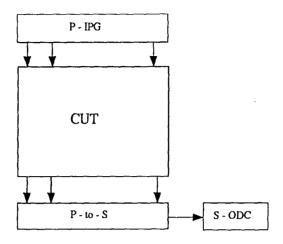

| 2.4  | The serial-parallel BIST model                          | 15 |

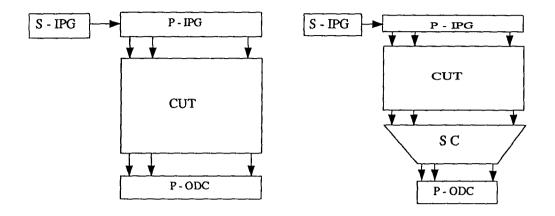

| 2.5  | The serial-serial BIST model                            | 16 |

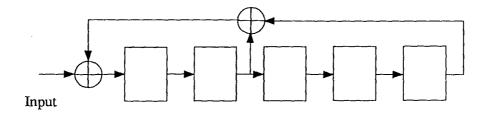

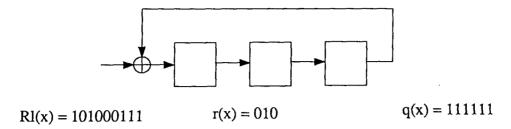

| 2.6  | An example LFSR                                         | 16 |

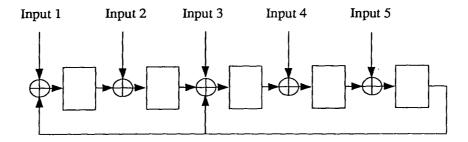

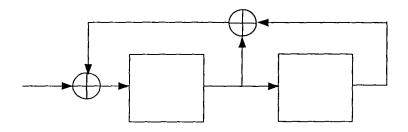

| 2.7  | An example MISR                                         | 18 |

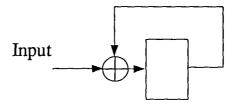

| 2.8  | A parity checker                                        | 25 |

| 2.9  | General counter-based compaction process                | 26 |

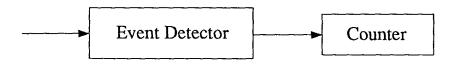

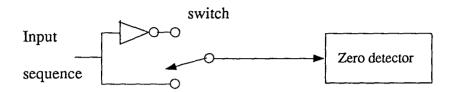

| 2.10 | Example event detectors                                 | 26 |

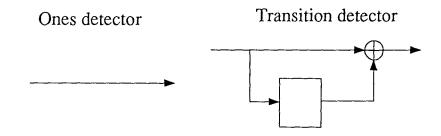

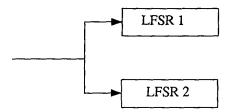

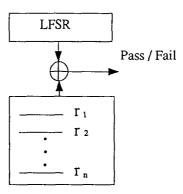

| 3.11 | Multiple LFSRs signature analysis                       | 33 |

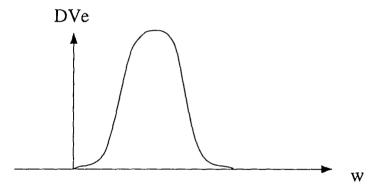

| 3.12 | Non-uniform deception volume of counter-based schemes   | 35 |

| 3.13 | An ODM scheme                                           | 36 |

| 3.14 | An example of zero aliasing compaction                  | 38 |

| 3.15 | Zero aliasing transition counting                       | 39 |

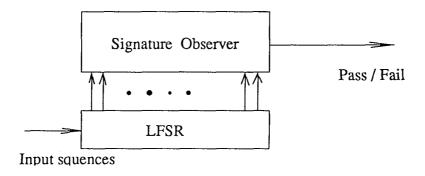

| 5.16 | Conceptual representation of the CMS scheme             | 53 |

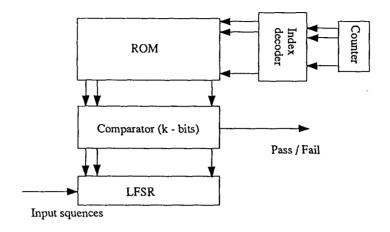

| 5.17 | A straightforward CMS implementation with ROM           | 54 |

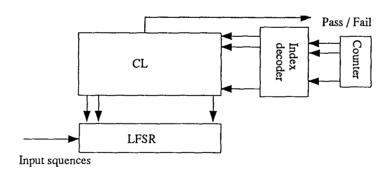

| 5.18 | A straightforward CMS implementation with CL            | 54 |

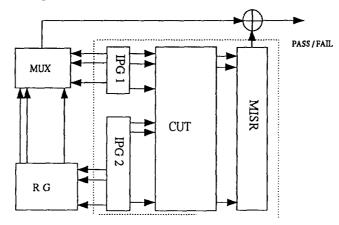

| 5.19 | A CMS implementation with resource sharing              | 55 |

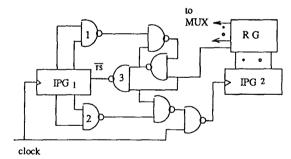

| 5.20 | An example local control circuit.                       | 56 |

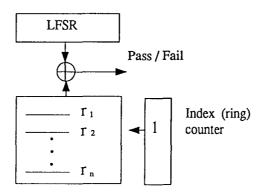

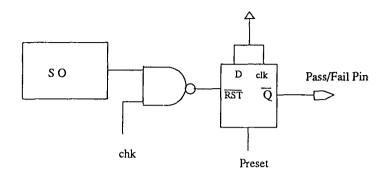

| 5.21 | Test result observation for multiple signature analysis | 58 |

| 5.22 Example controllers for signature analysis.605.23 Fault simulation time to determine fault coverage before data compaction<br>using fault dropping.615.24 Fault simulation time to determine fault coverage after data compaction.625.25 Fault simulation time with multiple signature analysis636.26 Conceptual representation of the FMS scheme.676.27 The FMS Data Compactor.686.28 An Example of the FMS Scheme696.29 Aliasing performance of the FMS scheme.726.30 The FMS scheme vs. the SS scheme.757.31 Example state transition diagrams.837.32 LFSR for the example.937.33 Confidence vs. (n-2)k.967.34 Confidence vs. L.977.35 Output compaction using a partial-length MISR.107 |      |                                                                          |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------|-----|

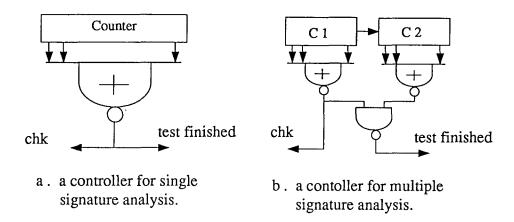

| using fault dropping.       61         5.24 Fault simulation time to determine fault coverage after data compaction.       62         5.25 Fault simulation time with multiple signature analysis.       63         6.26 Conceptual representation of the FMS scheme.       67         6.27 The FMS Data Compactor.       68         6.28 An Example of the FMS Scheme.       69         6.29 Aliasing performance of the FMS scheme.       72         6.30 The FMS scheme vs. the SS scheme.       75         7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97 | 5.22 | Example controllers for signature analysis                               | 60  |

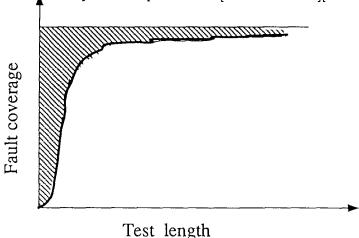

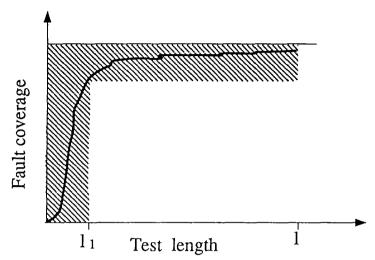

| 5.24 Fault simulation time to determine fault coverage after data compaction.       62         5.25 Fault simulation time with multiple signature analysis       63         6.26 Conceptual representation of the FMS scheme.       67         6.27 The FMS Data Compactor.       68         6.28 An Example of the FMS Scheme       69         6.29 Aliasing performance of the FMS scheme.       72         6.30 The FMS scheme vs. the SS scheme.       75         7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                          | 5.23 | Fault simulation time to determine fault coverage before data compaction |     |

| 5.25 Fault simulation time with multiple signature analysis       63         6.26 Conceptual representation of the FMS scheme.       67         6.27 The FMS Data Compactor.       68         6.28 An Example of the FMS Scheme       69         6.29 Aliasing performance of the FMS scheme.       72         6.30 The FMS scheme vs. the SS scheme.       75         7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                         |      | using fault dropping                                                     | 61  |

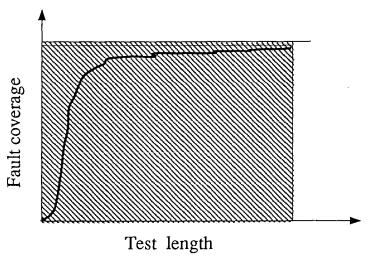

| 6.26 Conceptual representation of the FMS scheme.       67         6.27 The FMS Data Compactor.       68         6.28 An Example of the FMS Scheme       69         6.29 Aliasing performance of the FMS scheme.       72         6.30 The FMS scheme vs. the SS scheme.       75         7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                      | 5.24 | Fault simulation time to determine fault coverage after data compaction  | 62  |

| 6.27 The FMS Data Compactor.       68         6.28 An Example of the FMS Scheme       69         6.29 Aliasing performance of the FMS scheme.       72         6.30 The FMS scheme vs. the SS scheme.       75         7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                                                                                         | 5.25 | Fault simulation time with multiple signature analysis                   | 63  |

| 6.27 The FMS Data Compactor.       68         6.28 An Example of the FMS Scheme       69         6.29 Aliasing performance of the FMS scheme.       72         6.30 The FMS scheme vs. the SS scheme.       75         7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                                                                                         |      |                                                                          |     |

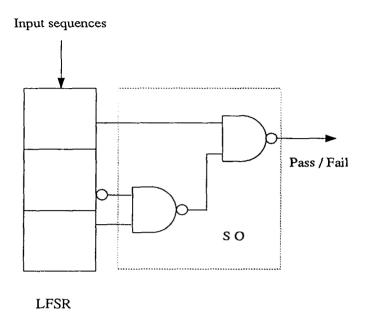

| 6.28 An Example of the FMS Scheme       69         6.29 Aliasing performance of the FMS scheme       72         6.30 The FMS scheme vs. the SS scheme       75         7.31 Example state transition diagrams       83         7.32 LFSR for the example       93         7.33 Confidence vs. (n-2)k       96         7.34 Confidence vs. L       97                                                                                                                                                                                                                                                                                                                                             | 6.26 | Conceptual representation of the FMS scheme                              | 67  |

| 6.29 Aliasing performance of the FMS scheme.       72         6.30 The FMS scheme vs. the SS scheme.       75         7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                                                                                                                                                                                          | 6.27 | The FMS Data Compactor                                                   | 68  |

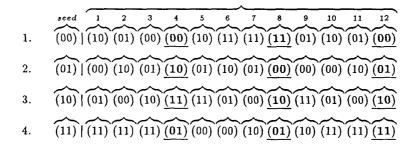

| 6.30 The FMS scheme vs. the SS scheme.       75         7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.28 | An Example of the FMS Scheme                                             | 69  |

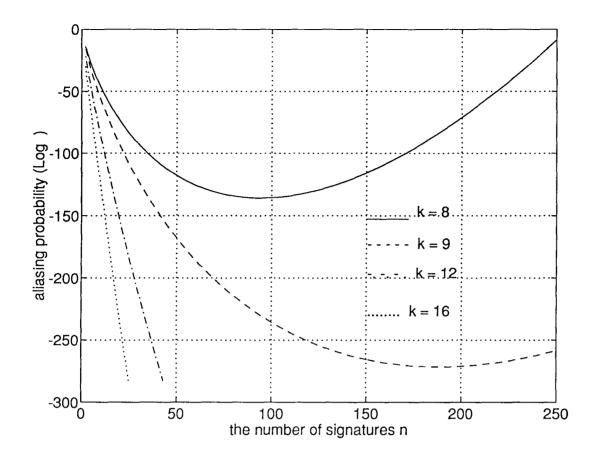

| 7.31 Example state transition diagrams.       83         7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.29 | Aliasing performance of the FMS scheme                                   | 72  |

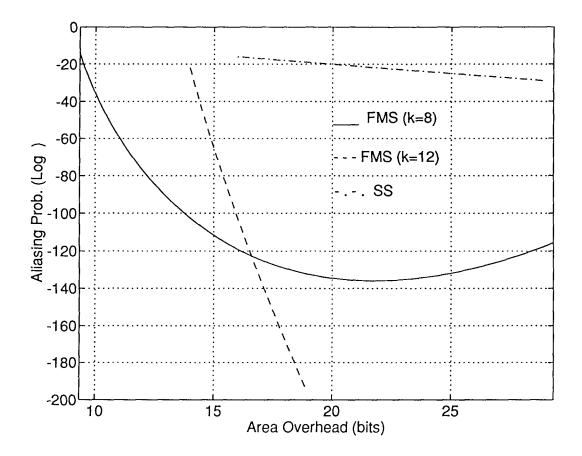

| 7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.30 | The FMS scheme vs. the SS scheme                                         | 75  |

| 7.32 LFSR for the example.       93         7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                                                          |     |

| 7.33 Confidence vs. (n-2)k.       96         7.34 Confidence vs. L.       97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.31 | Example state transition diagrams                                        | 83  |

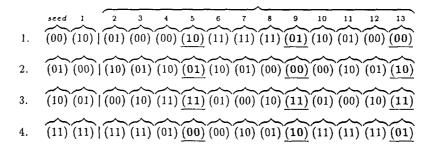

| 7.34 Confidence vs. L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7.32 | LFSR for the example                                                     | 93  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7.33 | Confidence vs. (n-2)k                                                    | 96  |

| 7.35 Output compaction using a partial-length MISR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.34 | Confidence vs. L                                                         | 97  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7.35 | Output compaction using a partial-length MISR                            | 107 |

#### Acknowledgement

I would like to take this opportunity to thank my supervisor, Dr. André Ivanov, whose friendship, constant encouragement, support and valuable guidance I was fortunate to receive all these years. I would also like to thank my colleague Chun Zhang for providing access to her fault simulator which initiated the work reported here. My appreciation goes to Victor Wong, Carly Wong, Kaiping Li and Gang Li for the helpful discussions on various topics. I would like to thank Peter Bonek, who included my work in his VLSI design, for being my first customer even though he has not paid me a penny yet. I am indebted to many other people who helped me these past few years, e.g., Jeff Chow, William Low and Barry Tsuji, who were always there when I had English problems; Andrew Bishop, who helped me put his nice frames on my slides. I would also like to thank my examination committee, especially Dr. N. Saxena, for helping me correct the errors that used to be in Chapter 4. The work reported here would have been impossible without the financial support of the University of British Columbia's Center for Integrated Computer Systems Research, the British Columbia Advanced Systems Institute, and the Natural Sciences and Engineering Research Council of Canada. Finally, I would like to express my sincere thanks to my family. I am very grateful to my dear wife, Yan Sa, who paved the way to the successful completion of this dissertation with her love and support. I do not know if she fully realizes just how much she has contributed to this work. I am extremely grateful to my parents, Yilee Wang and Zude Wu, who always encourage and support whatever I do. Without them, nothing would have been possible. Many thanks also go to my sister, Yueyan Wu, and brother-in-law, Tong Zhou, who gave me their great support by providing the extra care for my parents that I would have provided. I would like to mention my son, Eric Fenghua Wu, who brought special joys to my life even though he was time-consuming.

#### Claims of Originality

The author claims originality for the following contributions of this dissertation.

- In Chapter 4, the comprehensive fault coverage model is developed. This model is based on a fault detection probability density function of a circuit under test (CUT). In addition to the possible fault coverage loss due to aliasing, this model also takes into account the impact of the test vectors applied to the CUT.

- In Chapter 5, an efficient implementation of conventional multiple intermediate signature analysis is presented. This scheme shares some hardware existing in a conventional signature analysis BIST scheme. The detailed discussions on test control and test result observation are also not published previously.

- In Chapter 6, the proposed concept of fuzzy multiple intermediate signature analysis is novel. Unlike conventional multiple intermediate signature analysis, the fuzzy signature analysis does not contain the strict one-to-one signature-reference correspondence. The complete theory for aliasing performance prediction with the fuzzy multiple intermediate signature analysis is given. Considerations for practical implementations of fuzzy signature analysis as well as analysis on the hardware requirements are presented.

- In Chapter 7, a novel concept referred to as single reference multiple intermediate signature analysis is proposed. The proposed single reference signature analysis checks multiple signatures against a single reference, thus reducing the hardware requirements for implementation to a minimum. Therefore, this scheme is also referred to as minimal hardware multiple intermediate signature analysis.

- In Chapter 7, the discovery of the identical signature properties is a contribution to knowledge. Based on the identical signature properties, a systematic method for implementing single reference multiple intermediate signature analysis is developed. Two algorithms are given, one for the efficient generation of large number of fault-free sequences and the other for the fast identification of the fault-free sequence that possesses the identical signature properties.

- In Chapter 7, the classification of LFSRs according to their *singularity* (a useful property for implementing single reference multiple intermediate signature scheme) is also a contribution to knowledge.

#### Chapter 1

#### Introduction

For Very Large Scale Integrated (VLSI) circuits, testing is a difficult and expensive process. With improving semiconductor technology and computer-aided design (CAD) techniques, circuits with a very large number of devices can now be fabricated on a single chip, e.g., the Intel Pentium microprocessor has 3.1 million transistors on a single chip [Barr93]. The increasing package density of VLSI chips not only makes the chips more powerful, but also causes dramatic reductions in chip production cost. On the other hand, the percentage of the chip production expenditure consumed by testing has greatly increased. The increasing package density of VLSI chips has made the problem of testing extremely difficult.

#### 1.1 Dissertation Objective and Outline

When testing VLSI circuits, conventional test strategies have encountered a number of problems, such as the requirement for prohibitive CPU efforts for test pattern generation, low test quality due to limited accessibility to the internal circuit nodes, and the requirement of expensive Automatic Test Equipments (ATE). Built-In Self-Test (BIST) is one of the most promising solutions to these problems. BIST is the capability of a circuit to test itself without requiring external ATEs. In BIST, both the test pattern generation and test response evaluation are performed on the same chip as the circuit under test (CUT). However, when implementing a BIST, there exist several technical difficulties. Among these, two major difficulties are the so-called *error escape* or *aliasing*, and the inability to compute the exact *fault coverage* with reasonable CPU time efforts. The error escape problem is that some faults detected by the test patterns escape detection during the test response

evaluation process, thus causing some faulty circuits to be mistakenly declared good. Due to aliasing, some BIST schemes may result in poor test quality [Saxena85][Zorian86][Argwal83]. This dissertation addresses these two problems by developing a group of techniques known as multiple intermediate signature analysis.

The dissertation is organized as follows. The first three chapters are basically introductory chapters. Thus, readers familiar with VLSI testing may skip these chapters. The remainder of this chapter provides a general review of the art of VLSI testing. Chapter 2 is an introduction to BIST which introduces typical BIST hardware models, important BIST components, and commonly used test pattern generation and response evaluation techniques. Since this dissertation concentrates on BIST test response evaluation, a more detailed discussion on this issue and its current status is provided in Chapter 3.

The contribution to knowledge of this dissertation starts from Chapter 4. Chapters 4 and 5 discuss the basis of multiple intermediate signature analysis. Chapter 4 studies the aliasing and fault coverage performance of multiple intermediate signature analysis. More specifically, several models for aliasing and fault coverage predictions are developed. In Chapter 5, other issues associated with multiple intermediate signature analysis are discussed. The chapter begins with a discussion of the possible implementations of multiple signature analysis, in which a new scheme that shares the hardware resources of conventional BIST schemes is developed. This is followed by the discussions of test control, test result observation, and the advantages and drawbacks of multiple intermediate signature analysis compared to other data compaction techniques.

Chapter 6 is devoted to the development of a fuzzy multiple intermediate signature analysis technique for BIST. It discusses the basic concept of introducing fuzziness into signature analysis so as to simplify the conventional way of checking multiple intermediate signatures. It also discusses possible implementations, their hardware requirements, models for aliasing performance prediction, and comparisons with some other techniques. Experimental results obtained while using the fuzzy multiple intermediate signature scheme are

also reported in Chapter 6.

Chapter 7 presents a single reference multiple intermediate signature scheme that requires a minimal amount of hardware for multiple signature analysis. In addition to showing how the minimal hardware requirement is achieved, Chapter 7 also develops several techniques that help to efficiently implement the proposed scheme. Feasibility studies as well as experiments on benchmark circuits are reported. Finally, Chapter 8 summarizes this dissertation and discusses possible future work in these areas.

#### 1.2 Fault Models

Being physical devices, VLSI circuits are subject to failures. A failure is defined to occur when the delivered service by a circuit deviates from its specified service [Abraham86]. The cause of a failure is an error, which is defined to be any discrepancy between the actual circuit output sequence and the specified or expected output sequence [Breuer76]. The cause of an error is said to be a fault [Abraham86].

The causes of a fault can be numerous. First, incorrect design or design specification of a circuit can lead to a fault in the final fabricated circuit. Secondly, a fault can occur due to manufacturing defects, such as open and poor interconnections, shorts between conductors, excess leakage current, etc. [Bardell87]. Thirdly, even if a circuit is "perfectly" manufactured, it could subsequently wear out in the field due to electromigration, hot-electron injection, spreading charge loss, electrical overload, etc. [Abraham86]. Even during storage, faults may occur in a circuit due to factors such as temperature, humidity, leakage of sealed elements, and aging [Breuer76]. Lastly, even for a perfectly "good" circuit, a fault may occur temporarily in the field due to physical or environmental causes, such as lightening, radiation, stress, vibration, heat dissipation, etc. [Breuer76][Savaria86][Johnson89].

Regardless of the causes of a fault, in order for a fault's effect to be assessed, it must be modeled in a manner that is consistent with the representation of the circuit. In general, a fault described at a lower level can more accurately represent failure mechanisms, but involves a much greater degree of complexity [Abraham86]. For example, a fault described at the transistor level may become intractable because of the extremely large number of transistors in a VLSI chip, though it can very accurately describe the physical phenomena causing the fault. On the other hand, a fault described at a higher level, such as the gate level or functional level, can significantly reduce the complexity of treatment but, due to the loss of information, may result in some lower level failures not being considered [Abraham86]. For different requirements, many fault models have been developed. Some of them are simple while others are sophisticated. Among them, the *stuck-at* fault model [Breuer76][Bardell87] is one of the simplest and most commonly-used.

A stuck-at-0 (stuck-at-1) fault is defined to be any fault condition that causes a signal line to behave as if it were stuck at logical 0 (1). This model is a logical fault model, and is thus technology independent. Faults can occur singly or in multiples. A special class of these stuck-at faults is the *single stuck-at* fault model that assumes the existence of at most one such fault in a circuit. The single stuck-at fault model is the most commonly used model in practice. The popularity of this model is mainly due to its simplicity and ability to cover many common defects in ICs, e.g., bridging faults [Bardell87] and multiple stuck-at faults [Kubiak91]. However, there exist some defects that the stuck-at fault cannot model very well, e.g., delay faults and CMOS stuck-open faults. Nevertheless, the single stuck-at fault model is still the most popularly used, and still the model against which all other more complex fault models are compared [Bardell87].

As many other researches in this field, this dissertation assumes the single stuckat fault model. But, as will be noted, the methodology and techniques developed in this dissertation are also applicable to other fault models.

#### 1.3 Test Quality Measures

Testing of digital circuits consists of applying a sequence of input vectors to a circuit, observing the output sequence, and comparing it with a precomputed or expected output sequence. The presence of a given fault is said to be detected when an appropriate input vector or vectors, applied to the CUT, causes an incorrect logic output at one or more of the CUT's output lines. The input vectors are called test patterns or test vectors. Although a test procedure can be generic, its quality measures are usually associated with a specific fault model. In VLSI testing, the quality is usually measured by the ratio of the detected faults to the total number of possible faults under the assumption of a specific fault model. This ratio is termed fault coverage. Due to its dependence on fault models, for a same CUT and a same set of test patterns applied in the same order, the fault coverages obtained for different fault models can be significantly different.

The fault coverage that a given set of test vectors can achieve is usually computed by a process called fault simulation. Fault simulation consists of simulating the application of every pattern in the test set to the fault-free as well as a set of faulty circuits (each corresponding to a circuit to which a fault is injected), and comparing the simulated test response of the fault-free circuit with that from each of the faulty circuits. Fault simulation is the only way to determine the exact fault coverage [Wagner87]. In the past few years, gate-level stuck-at fault simulation for combinational circuits has been made extremely fast [Blank84][Waicukauski85][Mamari90][Keller90][Lee91]. A report from industry even declares that further speed up may not be necessary [Atken90]. For other fault models, such as delay faults, fast fault simulation techniques have also be developed [Waicukauski87b][Schulz87][Fink90][Wu92a]. For fault coverage computation, an alternative to fault simulation is the use of analytical techniques for fault coverage estimation [Wagner87][Savir84][Savir84b]. These techniques are based on the knowledge of the detectabilities

<sup>1</sup> of the faults in the CUT. Two major difficulties for using these techniques are the obstacle of obtaining the detectability profile of the CUT, and the inadequate accuracy.

#### 1.4 Conventional Approach to IC Testing

Testing a digital circuit requires three major steps, namely the generation of a set of test vectors, the application of these vectors to a CUT, and the analysis of the collected test response from the CUT. In conventional IC testing, an external tester is employed to apply test vectors and to collect and analyze the test response.

When dealing with large circuits, the conventional approach encounters a number of difficulties. First, the computational time requirements for the test pattern generation may be prohibitive. Due to the fact that signals at internal circuit nodes are easier to control in combinational circuits than in sequential circuits, test pattern generation for combinational circuits is much easier. Many test pattern generation algorithms have been developed, e.g., [Goel81][Fujiwara83][Rajski87] [Schulz88]. To speed up the test pattern generation process, fault simulation is usually employed to determine whether a test pattern generated for one fault is also able to detect other faults. If so, these detected faults are dropped from further consideration. Unfortunately, even with the best algorithm, to generate a complete test set (the set of test vectors that covers all detectable faults in a CUT) is still prohibitively expensive for today's large circuits [Sedmak85]. Secondly, the generated test set usually cannot achieve adequate fault coverage. This is because the controllability and observability of the internal circuit nodes through I/O pins have been significantly reduced as a result of the increased complexity and density of VLSI circuits. The reduced accessibility to the internal nodes not only makes test pattern generation more difficult, but results in large number of undetectable faults, and hence poor test quality. Thirdly, external testers or so-called ATEs are not only expensive, but impose a limitation on the speed at which the

<sup>&</sup>lt;sup>1</sup>The detectability of a fault is defined to be the probability that the fault is detected by a randomly chosen test vector.

CUTs can be tested. Conventionally, IC chips are tested at low speed to verify their static state functionality. However, a CUT that passed the low speed test may not be able to work properly at its operational speed due to the existence of AC faults<sup>1</sup> [Schulz87] [Maxwell91]. The speed at which a circuit can run at test is limited by the speed of the ATE. High speed ATEs are extremely expensive (easily millions of dollars). Moreover, all ATEs are made with existing IC technology. Thus, their speed is likely to be slower than the latest technology. Besides, the amount of test data is becoming too large to be handled efficiently by ATEs. To ease these problems, a group of new techniques known as design-for-testability have been proposed [William83][McCluskey85].

#### 1.5 Design for Testability

In general, design-for-testability (DFT) is any design technique that helps make a circuit more testable. For example, one can either enhance the controllability of internal circuit nodes, or enhance their observability, or both. Many DFT techniques are now available. Some are structured or generic design techniques. Some are ad hoc. A group of well-known structured DFT techniques is scan path design.

As discussed earlier, testing a sequential circuit can be much more difficult than testing a combinational circuit. Scan design defines two operational modes of a circuit: normal mode and test mode. In the normal mode, the circuit performs its normal function as a sequential circuit. In the test mode, the circuit is reconfigured into a combinational circuit and a scan register. The problem of testing a sequential circuit is thus reduced to that of testing a combinational circuit and a scan register. The conversion is accomplished by connecting all the circuit's internal state memory elements into a shift register, and connecting one end of the register to an input pin while connecting the other to an output pin. With the scan register, any internal state memory element can be fully controlled by

<sup>&</sup>lt;sup>1</sup>AC faults are the faults that cause timing failure of a system but may not affect the system's steady state functionality.

shifting a bit into that specific element from the shift register's input pin. The state of the memory element can easily be observed by shifting out its content to the shift register's output pin. In this way, the circuit nodes or lines that are connected to the internal memory elements can be treated as primary inputs and outputs in the test mode.

Although scan design significantly simplifies the problem of IC testing, it has several drawbacks. A possible drawback is that some faults may not be detected since the testing is performed in the test mode instead of the circuit's normal mode. In addition, in exchange for the reduced complexity in testing, scan design implies extra hardware requirements. For example, as estimated in [Nagle89], full scan design usually entails 10% - 20% additional hardware requirements. Furthermore, scan register cells sometimes require a more complex clocking system. Take the Level Sensitive Scan Design (LSSD) [Eichelberger78] technique for instance, which is now a compulsory requirement for all IBM's designs, two clock signals are required. In addition to extra hardware requirements and possible performance degradation, scan design also requires substantially longer test time because the test vectors must be serially shifted into the scan path bit by bit. However, experience has shown that the price paid by scan design is well compensated for by the significantly reduced effort in testing [McCluskey85].

It is worth mentioning another type of scan design for testing multichip assemblies even though this dissertation focuses on chip level testing. This type of scan design is known as boundary scan, which assigns a memory element to each I/O pin of a chip, and connects these elements into a shift register called the boundary scan register. When testing a multichip assembly, a long shift register is formed by connecting each chip's boundary scan register together. Through the long shift register, the I/O pins of each chip can be easily accessed. Boundary scan design successfully solves the problem of assembly interconnection testing [Hassan88][Jarwala89] without requiring the use of bed-of-nails equipments. Boundary scan design has now become an IEEE standard [IEEE90]

#### 1.6 Built-In Self-Test

DFT techniques such as scan design may ease the difficulty of test pattern generation and application. However, the core problems of limited internal circuit node accessibility and the requirements of expensive test pattern generation and ATEs still remain [Sedmak85].

Another DFT design approach which can well be coupled with scan design is built-in self-test (BIST) [Sedmak85][McCluskey85]. BIST is the capability of a product (wafer, chip, multichip assembly, system) to test itself without requiring external ATEs [Sedmak85]. This simple but very promising idea attacks not only the limited accessibility problem, but also the costly test pattern generation and ATE problems. A BIST must consist of a strategy for generating test vectors, a strategy for evaluating test response, and the implementation mechanisms [McCluskey85]. In chip level BISTs, both test pattern generation and test response evaluation are performed by some simple hardware in the same chip that is under test [Gelsinger86] [Katoozi92] [Zorian91] [Hagihara92] [Kuban84]. The conventional test approach's expensive requirements for test pattern generation and ATEs are no longer necessary with BIST. Furthermore, the on-chip test pattern generation and output evaluation significantly enhance the accessibility of internal circuit nodes, thus possibly yielding better test quality. Another strength of BIST is the ability to test circuits at their operational speed, which enables the detection of many AC defects in addition to the detection of static state failures. BIST can also be used for in-field test, and for multichip assembly fault diagnosis, which requires faulty chip localization.

As pointed out in [McCluskey85], all BIST methods have some associated cost. Since BIST circuitry uses chip area, there is a decrease both in the *yield*<sup>1</sup> and in the reliability [McCluskey85], and there is an increase in the power consumption [Levy91]. These costs are compensated for, however, by the significant savings in testing and especially system maintenance in the product life-cycle [Agrawal93]. The extra silicon area consumed by

<sup>&</sup>lt;sup>1</sup>Yield is usually defined to be the ratio of the number of good chips over that of all the chips produced.

BIST used to be considered as an overhead. Recently, however, with increasing demands for higher test quality, more and more people in the VLSI community tend to consider BIST as a necessary function of a chip. Thus, the silicon area associated with BIST is considered as a natural requirement, and not as an overhead. Of course, it is still desirable to keep the hardware requirements of BIST as low as possible for the sake of cost, yield, reliability, and power-consumption.

#### 1.7 Test Quality Problems of BIST

BIST is a simple and powerful idea to solve the problems of VLSI testing. However, it has a distinctive technical difficulty. In BIST, due to the on-chip test response evaluation, the bit-by-bit comparison technique that is usually adopted in the conventional approaches is not normally practical any more. To evaluate the test response efficiently while consuming reasonable amount of silicon area, the test response sequence is usually compacted into a small sequence of bits, called a *signature*. At the end of a test, the signature collected from the CUT is compared with an expected signature or *reference* to determine whether the CUT is fault-free.

A major drawback of the compaction is the loss of information, which may result in some erroneous sequences being compacted into a same signature as the fault-free one, thus causing an incorrect diagnosis whereby a faulty circuit declares itself as good. This problem is well-known as aliasing or error masking [McCluskey85][Bardell87]. Due to the aliasing problem, the overall test quality of a BIST scheme depends not only on the quality of the test vectors generated, but also on the quality of the adopted data compaction technique. Many recent research efforts have been aimed at reducing the aliasing problem while still maintaining reasonably small hardware requirements, e.g., [Zorian86], [Agarwal87], [Li87], [Robinson87], [Robinson88], [Gupta90] and [Raina91]. But, as will be discussed in the subsequent chapters, most compaction techniques have the deficiency of either excessively

large aliasing or substantially high hardware requirements.

Another difficulty associated with output data compaction is the assessment of the test quality of a BIST scheme. As discussed in Section 1.3, fault coverage is an accepted quality measure of VLSI testing. Fault coverage is usually computed by fault simulation. An important technique that makes fault simulation fast is dropping a fault from further consideration once it is detected by a test vector. This technique is known as fault dropping. In BIST, however, fault dropping is not usually possible. This is because, due to possible aliasing, once a fault is detected there is no guarantee that it will be detected at the end of the test. Without fault dropping, fault simulation is not generally computationally feasible for large circuits. Due to the inability to accurately quantify the test quality of a BIST scheme, the test quality issue of BIST has traditionally been split into two parts. The first part is to use fault coverage before compaction to measure the quality of the test vectors generated. The second part is to characterize the possible loss of the coverage due to aliasing. Unlike fault coverage measures, which are deterministic, measures for aliasing are usually probabilistic. Although many advanced probabilistic techniques have been developed, such techniques are difficult to use confidently when dealing with a specific CUT because of the statistical uncertainty. Evidence of the uncertainty can be found in experimental reports, e.g., [Aitken89], [Xavier92], [Rajski91b] and [Debany92].

#### Chapter 2

#### Built-in Self-Testing

BIST is becoming a widely-used means for VLSI testing. Many commercial products [Kuban84][Daniels85][Gelsinger86][Gelsigner89][Hagihara92] illustrates how far the BIST concept has become a reality. Testing different types of circuits usually requires different types of BIST [Zorian91], e.g., BIST for random logic, BIST for RAMs, BIST for ROMs, etc. This dissertation focuses on the BIST schemes designed for testing random logic. However, the schemes developed in this dissertation still apply to the BIST for other types of circuits. As discussed in Chapter 1, the two major functions of BIST are the on-chip test pattern generation and output data evaluation. This chapter provides a general review of both these BIST functions. The subsequent chapter will provide a more detailed discussion on BIST output data evaluation since it is the major topic of this dissertation.

#### 2.1 Hardware Models of BIST