# **NoCSim: A Versatile Network on Chip Simulator**

By

#### **Michael Jones**

**B.ASc Queen's University, Kingston 2002**

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Applied Science

In

The Faculty of Graduate Studies

**Electrical and Computer Engineering**

The University of British Columbia

**April 2005**

© Michael Jones, 2005

## **NoCSim: A Versatile Network on Chip Simulator**

#### **ABSTRACT**

The new network on chip paradigm that has been proposed involves radical changes to SoC design methodology. In this paradigm large numbers of heterogeneous IP blocks will by integrated together using a standard template. Each IP block is capable of sending and receiving data packets through an interconnect. The non-scalability of buses as on-chip interconnects forces us to select a more scalable alternative for communication.

Many different network-centric interconnects have been proposed for the large scale SoC domain such as *k-ary n-cubes*, *butterfly fat-trees*, *k-ary n-trees*, and *octagons*. With this network-on-chip (NoC) paradigm many new design challenges arise such as physical switch design, and network topology selection. Without any other means of predicting system performance, a network simulation tool is required to evaluate and compare networks.

Several network simulation tools exist, but fail to contain all functionality desired for NoC simulation (e.g. wormhole switching support). To fill this void we have developed NoCSim, an iterative flit-level network on-chip simulator capable of simulating networks under a wide variety of parameters and topologies. The tool was developed, tested, and verified against an established network simulator.

# **TABLE OF CONTENTS**

| ABSTRACT                                                          | ii   |

|-------------------------------------------------------------------|------|

| TABLE OF CONTENTS                                                 | iii  |

| TABLE OF FIGURES                                                  | V    |

| LIST OF TABLES                                                    | vii  |

| ACKNOWLEDGEMENTS                                                  | viii |

| 1.0 Introduction                                                  |      |

| 2.0 Background and Related Work                                   | 6    |

| 2.1 Background Information                                        | 6    |

| 2.2 Related Work                                                  |      |

| 2.2.1 FlexSim                                                     | 11   |

| 2.2.2 IRFlexsim0.5                                                | 13   |

| 2.2.3 NS version 2.0                                              | 14   |

| 2.2.4 <i>OPNET</i>                                                | 15   |

| 2.2.5 Stuttgart Neural Network Simulator                          | 16   |

| 2.2.6 The cnet Network Simulator (v2.0.9)                         | 17   |

| 2.2.7 QualNet Version 3.8                                         | 17   |

| 2.2.8 REAL 5.0 Network Simulator                                  |      |

| 2.2.9 MaRS Maryland Routing Simulator                             | 18   |

| 2.2.10 Boppana, Chalasani, and Siegel: Wormhole Network Simulator | 19   |

| 2.2.11 Simured Multicomputer Network Simulator                    | 19   |

| 3.0 NoCSim                                                        | 20   |

| 3.1 Network Topologies                                            | 21   |

| 3.1.1 Shared-Medium Networks                                      | 22   |

| 3.1.1.1 Bus                                                       | 23   |

| 3.1.2 Direct Networks                                             |      |

| 3.1.2.1 <i>K-ary N-cubes</i>                                      | 25   |

| 3.1.2.2 Octagon                                                   | 29   |

| 3.1.3 Indirect Networks                                           | 31   |

| 3.1.3.1 K-ary n-trees                                             | 31   |

| 3.1.3.2 Butterfly Fat-Tree                                        | 34   |

| 3.2 Switching                                                     | 35   |

| 3.3 Virtual Channels                                              | 37   |

| 3.4 Routing Options                                               | 37   |

| 3.4.1 K-ary N-cube Routing                                        | 37   |

| 3.4.2 Octagon Routing                                             | 39   |

| 3.4.3 K-ary N-tree Routing                                        |      |

| 3.4.4 Butterfly Fat Tree Routing                                  | 41   |

| 3.5 Deadlock, Livelock, and Starvation                            |      |

| 3.6 Switch Model                                                  | 47   |

| 3.7 Collision Handling                                            |      |

| 3.7.1 Port Ordered Collision Handling                             |      |

| 3.7.2 Round Robin Collision Handling                              |      |

| 3.7.3 Oldest Goes First Collision Handling                        |      |

| 3.7.4 Priority Based Collision Handling          | 51  |

|--------------------------------------------------|-----|

| 3.8 Traffic Generation                           |     |

| 3.9 Source Queue Length                          |     |

| 3.10 Simulation Duration                         |     |

| 3.11 Periodic Statistic Updates                  |     |

| 3.12 Other Settings                              |     |

| 4.0 Simulator Engine                             |     |

| 4.1 The Simulation Cycle                         |     |

| 4.2 Time Complexity Analysis                     |     |

| 4.3 Limitations                                  |     |

| 5.0 Simulation Results                           | 70  |

| 5.1 Throughput                                   | 70  |

| 5.2 Transport Latency                            | 71  |

| 5.3 Energy Consumption                           | 72  |

| 5.4 Validation                                   | 73  |

| 5.5 Sample Results                               | 75  |

| 5.5.1 Throughput vs. Load                        | 76  |

| 5.5.2 Throughput vs. Virtual Channels            | 78  |

| 5.5.3 Localization vs. Throughput                | 81  |

| 5.5.4 Latency vs. Load                           | 85  |

| 5.5.5 Energy vs. Load                            | 87  |

| 5.5.6 Latency Histograms                         |     |

| 6.0 Conclusions and Future Work                  | 93  |

| 6.1 Conclusions                                  |     |

| 6.2 Future Work                                  |     |

| Appendix A: The <i>NoCSim</i> Source Code in C++ |     |

| Appendix B: NoCSim Data Structures               |     |

| B.1 Ports Data Structure                         |     |

| B.2 Msgs Data Structure                          |     |

| B.3 IPs Data Structure                           |     |

| B.4 Headers Data Structure                       |     |

| B.5 Flit Transfer Arrays                         | 106 |

| Deferences                                       | 100 |

## **TABLE OF FIGURES**

| Figure 1: Example switch using two virtual channels                                                 | 11   |

|-----------------------------------------------------------------------------------------------------|------|

| Figure 2: NoCSim Options Menu with Default Settings                                                 | 21   |

| Figure 3: Simple Bus Structure                                                                      |      |

| Figure 4: A 8-ary 2-cube without wraparound links, also called a mesh topology                      | 26   |

| Figure 5: A 8-ary 2-cube with wraparound links, also called a torus topology                        | 27   |

| Figure 6: A <i>3-ary 3-cube</i>                                                                     |      |

| Figure 7: A conventional 8 IP, 8-ary 1-cube with wraparound link, also called a ring,               | or   |

| torus.                                                                                              | 28   |

| Figure 8: A 'folded' torus of 8 IPs. It is still an 8-ary 1-cube with wraparound link.              |      |

| node keeps the same neighbouring nodes, but the node order is changed to remo                       | ve   |

| the long wraparound link.                                                                           | 28   |

| Figure 9: An 8 node octagon.                                                                        | 29   |

| Figure 10: A 2-dimensional 64 IP octagon topology                                                   | 30   |

| Figure 11: A 16 IP 4-ary 2-tree                                                                     | 33   |

| Figure 12: A 64 IP 4-ary 3-tree                                                                     |      |

| Figure 13: A 2 level, 16 IP Butterfly Fat Tree                                                      | 35   |

| Figure 14: A 3 level, 64 IP Butterfly Fat Tree                                                      | 35   |

| Figure 15: Dimension Ordered Routing in a 64 IP mesh                                                | 38   |

| Figure 16: Shortest Path Routing in octagon                                                         | 40   |

| Figure 17: A possible path for a source/destination pair using turnaround routing in a              | ւ 16 |

| IP fat-tree topology.                                                                               | 41   |

| Figure 18: Deadlock in a 4 node <i>ring</i> .                                                       |      |

| Figure 19: A 4 node unidirectional <i>ring</i> .                                                    |      |

| Figure 20: Corresponding dependency graph.                                                          |      |

| Figure 21: A 4 node <i>ring</i> with virtual channels.                                              |      |

| Figure 22: Corresponding dependency graph.                                                          | 46   |

| Figure 23: Example Generalized Switch Block Diagram                                                 | 48   |

| Figure 24: A 64 IP 8-ary 2-cube with wraparound links. The highlighted IP's local g                 | roup |

| of 4 is circled                                                                                     |      |

| Figure 25: A 64 IP 4-ary 3-Tree. The highlighted IP's local group of 4 is circled                   | 53   |

| Figure 26: A 64 IP 3 level BFT. The highlighted IP's local group of 4 is circled                    | 54   |

| Figure 27: A 2-dimensional 64 IP octagon. The highlighted IP's local group of 8 is                  |      |

| circled                                                                                             | 54   |

| Figure 28: Example NoCSim output screen.                                                            |      |

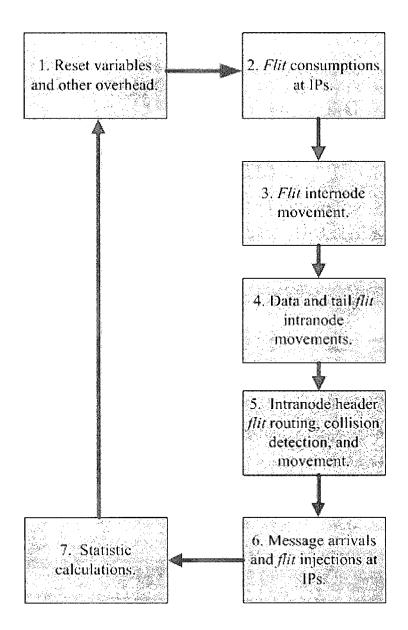

| Figure 29: NoCSim Cycle Flowchart                                                                   | 61   |

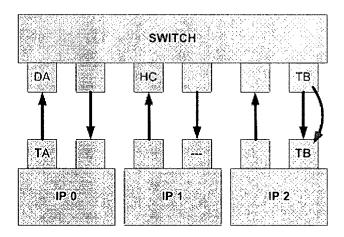

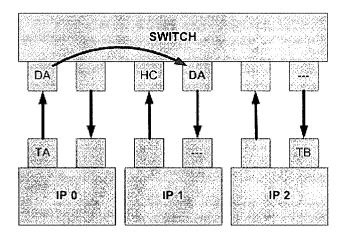

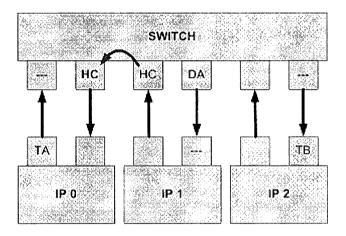

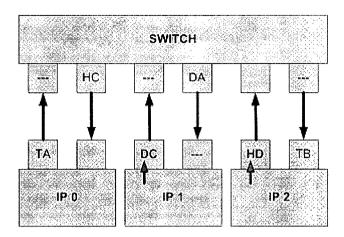

| Figure 30: Flit marked HA is consumed by IP 1.                                                      | 62   |

| Figure 31: Flit TB moves from the switch output port, to IP 2's input port                          | 63   |

| Figure 32: Flit DA moves through the switch by following the path established by                    |      |

| message A's header.                                                                                 | 63   |

| Figure 33: Header <i>flit HC</i> is routed to the switch's <i>IP 0</i> output port. No collision is |      |

| detected, so the <i>flit</i> is advanced                                                            | 64   |

| Figure 34: IP 1 injects DC to its output port. A new message D is injected from IP 2.               | 65   |

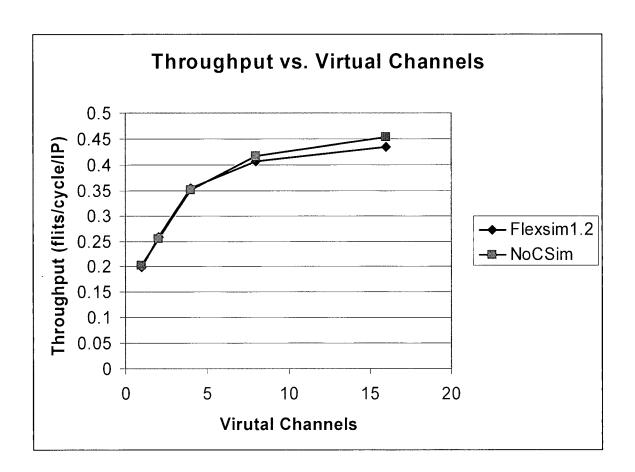

| Figure 35: 64 IP mesh FlexSim1.2 and NoCSim                                                         |      |

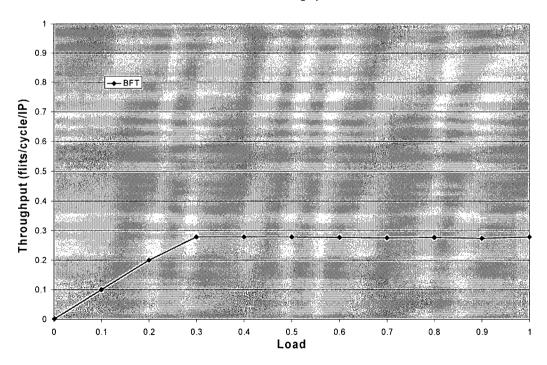

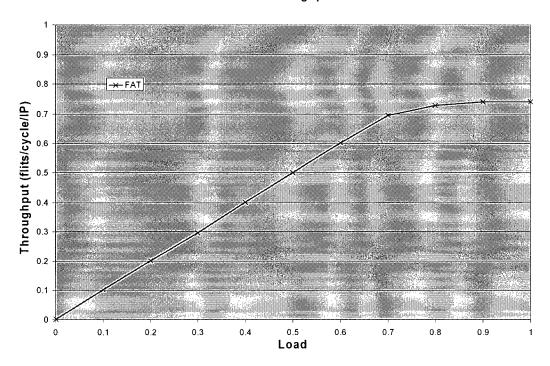

| Figure 36: 64 IP <i>BFT</i> throughput vs. load                   | 76 |

|-------------------------------------------------------------------|----|

| Figure 37: 64 IP Fat-Tree throughput vs. Load                     | 77 |

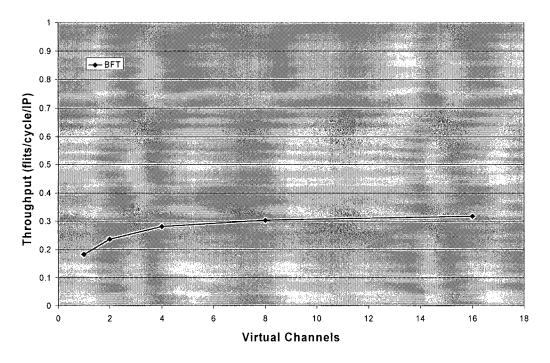

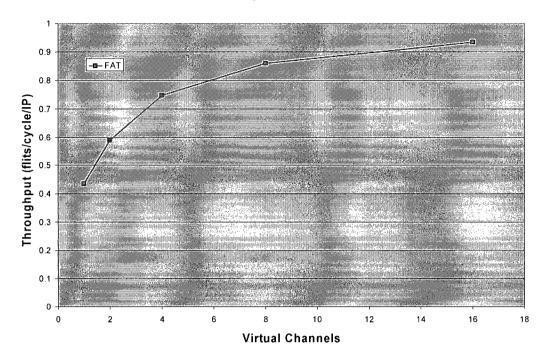

| Figure 38: 64 IP BFT Throughput vs. Virtual Channels              | 79 |

| Figure 39: 64 IP Fat-tree Throughput vs. Virtual Channels         | 80 |

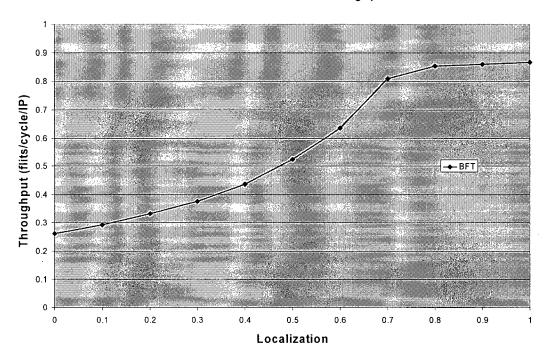

| Figure 40: 64 IP BFT Throughput vs. Localization                  | 82 |

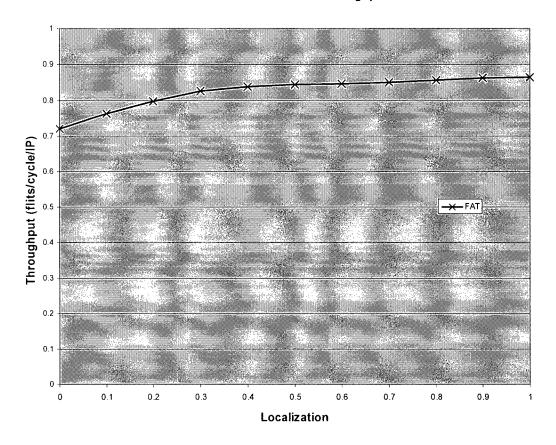

| Figure 41: 64 IP Fat-tree Throughput vs. Localization             | 83 |

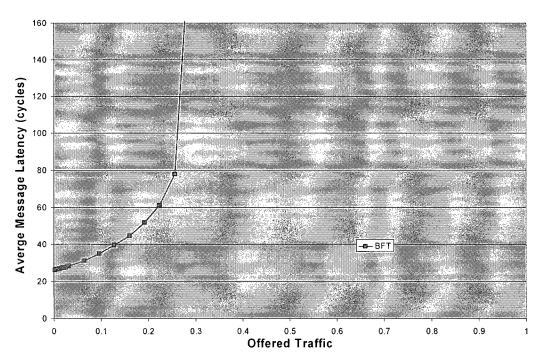

| Figure 42: 64 IP BFT Latency vs. Load                             | 85 |

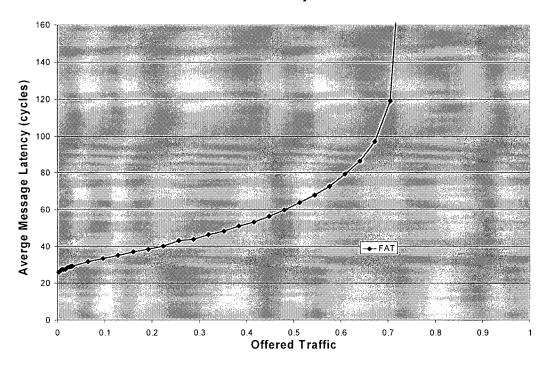

| Figure 43: 64 IP Fat-tree Latency vs. Load                        | 86 |

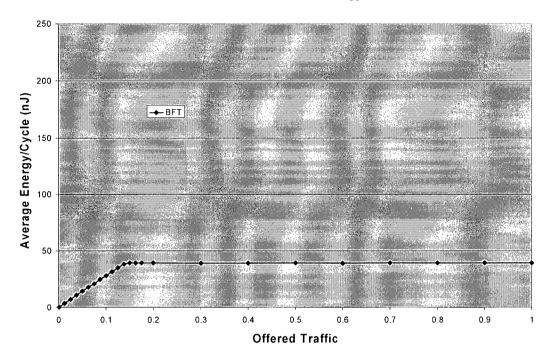

| Figure 44: 256 IP BFT Energy vs. Load                             | 88 |

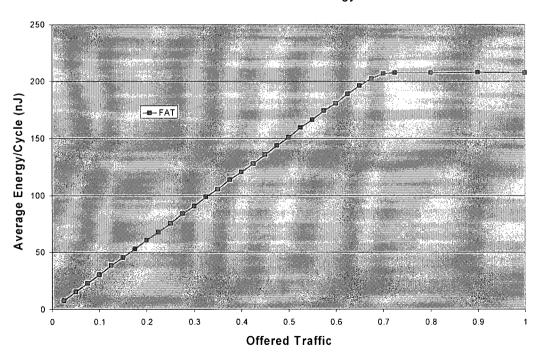

| Figure 45: 256 IP Fat-tree Energy vs. Load                        | 88 |

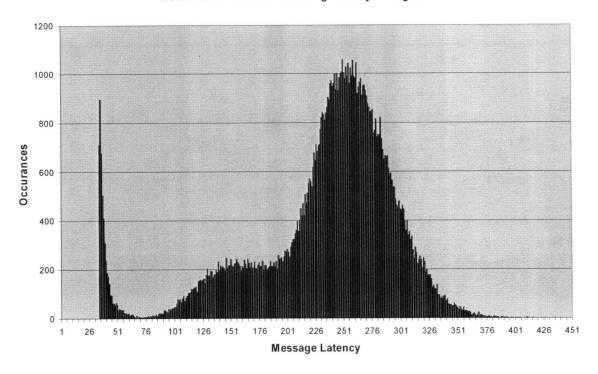

| Figure 46: Port Ordered Collision Handling Latency Histogram      | 90 |

| Figure 47: Oldest Goes First Collision Handling Latency Histogram | 91 |

|                                                                   |    |

# **LIST OF TABLES**

| Table 1: Simple shortest path octagon routing | 39  |

|-----------------------------------------------|-----|

| Table 2: Time Analysis Parameters             |     |

| Table 3: Validation Parameters                |     |

| Table 4: Default Parameter Values             |     |

| Table 5: Parameters for Figures 36-37         | 76  |

| Table 6: Parameters for Figures 37-38         |     |

| Table 7: Parameters for Figures 39-40         |     |

| Table 8: Parameters for Figures 41-42         |     |

| Table 9: Parameters for Figures 43-44         |     |

| Table 10: Parameters for Figures 45-46        |     |

| Table 11: Ports Data Structure                |     |

| Table 12: Token Representations               |     |

| Table 13: msgs Data Structure                 |     |

| Table 14: <i>IPs</i> Data Structure           |     |

| Table 15: Headers Data Structure              | 106 |

| Table 16: Flit Transfer Arrays                |     |

## **ACKNOWLEDGEMENTS**

First of all, I'd like to thank my academic advisor, Dr. André Ivanov for his advice, motivation, and guidance throughput my time here at UBC. There were many times where the direction of my work was in question and it was then that he helped me the most.

I'd also like to thank Dr. Res Saleh for his feedback and support on technical matters as well.

I need to send a huge thank you to fellow members of Dr. Ivanov's research group,

Partha Pande, and Cristian Grecu. Whenever I needed help they were there and willing

to drop whatever they were doing to help me. I can't say enough about the appreciation I

have for them, and without them this work would never have been done.

I'd also like to thank USC PhD student and member of the *SMART* Interconnects group, Wai Hong Ho, for his continued support on technical issues.

## 1.0 Introduction

The years to come will bring revolutionary changes to System on Chip (SoC) design methodology [28]. Complex SoCs consisting of billions of transistors fabricated in technologies characterized by 65 nm feature sizes and smaller will soon be a reality. At this physical size the number of semiconductor intellectual property (SIP) blocks could be in the hundreds. Each of these blocks is capable of performing its own unique function and is free to operate at its own clock frequency. However, in such a large system, integration of these heterogeneous blocks gives rise to new challenges. These problems include non-scalable wire delays, failure to achieve global synchronization, signal integrity issues and difficulties with non-scalable bus-based interconnects. It has since been established that the key to success for these large scale SoCs is the interconnection system [4].

The most frequently used on-chip interconnection architecture thus far is the shared medium bus where all communicating devices share the same transmission medium. While this topology has advantages for small networks, as the bus line increases in length to accommodate additional IPs the performance drastically declines. Intrinsic parasitic resistance and capacitance from the line and added IPs increase to extremely high levels causing propagation delay to be unacceptably high. A bottleneck also occurs as the large number of IPs must wait for their turn to use the only transmission medium [31].

It is for these reasons that several research groups have turned to the direction of a network-centric approach to integrate IPs in large scale SoCs [2,4,14,20]. In this approach the IPs are decoupled from the communication fabric removing the need for global synchronization. Independent IPs can then run on their own local clock frequency allowing IP specific clock trees to replace a system global tree.

Thus far, the suggested interconnects for large scale SoCs closely resemble interconnect architectures of high-performance parallel computing systems. The possible interconnect topologies come in many varieties, such as mesh or tree. There are also many configurable physical interconnect parameters such as switch buffer depth and size.

Routing, collision handling, and deadlock are also issues that like the physical parameters, can greatly impact the overall interconnection system's performance [21].

As large scale SoCs are pushed into development, hardware designers will need to face the challenge of designing a complex interconnects. With so many interconnect options and configurable parameter permutations available, designers require a means of educating themselves of the impact the different interconnects have on overall system metrics, performance, power consumption, and die area. The ability to weight different networks against others on a unified platform is vital as only then will designers be able to make informed decisions regarding NoC design [21].

The above problem could be solved through one of a number of solutions. One is to create mathematical analytical models possible of describe all network options and retrieving performance measurements [17]. If it were possible to create completely accurate models of every interconnect topology and parameter configuration this would be the ideal solution. Once established, models could be used with very little time or effort to predict accurate system performance. Unfortunately mathematical models for large scale complex topologies have not been successfully developed when wormhole switching is the switching technique. *Wormhole switching* is the obvious choice for on chip network switching since it allows switches to have buffer sizes that are fractions of the size of *packet switched* buffers [31]. Thus, the added complications that wormhole switching bring to the mathematical analysis problem make this solution unrealistic, and unobtainable.

Another solution would be to gather the required performance statistics by measuring fabricated large scale SoCs. This of course cannot be done since no SoC with the scale discussed above has been developed. Even if one were to be fabricated, that could provide performance measurements for only one of many possible interconnect configurations. Therefore, educating large scale SoC designers through hardware testing is not an option.

The only remaining realistic solution is to emulate the behaviour of the on chip interconnect to produce performance statistics using a network simulator. With standard network performance defining statistics such as average message latency, and throughput,

designers can clearly weight interconnects against each other and make informed decisions [22]. These statistics would be as accurate as the models used in the simulator and the emulated traffic pattern used. A simulator tool would also be advantageous as it could allow designers to evaluate a large number of parameter permutations in their aim to design the optimal interconnect for a given NoC.

A simulation tool should be able to evaluate different NoCs in terms of different parameters and conditions. Desirable features for an NoC simulator include:

- The ability to simulate different topologies structures and sizes.

- The ability to simulate under different traffic patterns and loads.

- The ability to vary switch parameters such as buffer depth, and number of virtual channels.

- The ability to implement different routing and collision handling schemes.

- The ability to implement wormhole switching

Several network simulators such as *OPNET* [36], *Flexsim1.2* [27], and *NS version 2.0* [25] have been developed both in academia and industry. While these tools are functional in their own domain, none provide all the required features for evaluating on-chip networks in a convenient and unified platform.

Without a simulator tool containing this compete feature set, the problem of uniformed interconnect design remains unsolved. It is for that reason that we have developed a flit-level network simulator called *NoCSim* to fill the void. *NoCSim* has all the above stated

features which are described in detail in Chapter 3.0. The development of *NoCSim* is the main contribution, and topic of this thesis.

The main goal of the thesis is to educate about the need for the simulator in the NoC domain, and then to describe the simulator's feature scope, describe its functionality and to then validate it where possible with results.

The thesis is organized in chapters with this general introduction to the problem and possible solutions being the first. Chapter two describes some of the background information and related work. Chapter three describes the feature set of *NoCSim*, and how those features can be used. The fourth chapter details the functional behaviour of *NoCSim* and discusses simulator performance and limitations. In chapter five possible simulator outputs will be discussed. Results validation will be done by comparing *NoCSim* results to results of Flexsim1.2. Finally in chapter six conclusions will be drawn and future work will be touched upon. The appendices contain the *NoCSim* source code and some documentation regarding how the code is organized.

## 2.0 Background and Related Work

## 2.1 Background Information

One of the most major problems that arise from the technology advancement is the non-scalability of global wire delays. Global wires carry signals across a chip, but these wires do not scale in length with the ITRS roadmap for technology scaling. While gate delays scale down with technology, global wire delays typically increase or remain constant by inserting repeaters. However, repeaters also have their inherent problems such as their need for the use of an even number of inverters, he many via cuts, and, above all, the additional silicon area and power consumed. It is estimated that non-repeated wires with practical constraints result in delays of about 120-130 clock cycles across the chip in the 50 nm technology node [40]. In ultra deep-sub micron processes, 80% or more of the delay of critical paths will be due to interconnect.

Another important problem associated with global wires is that such wires are typically implemented in top-level metal layers, with routing performed automatically in later stages of the design cycle. These wires end up having parametric capacitance and inductance that is difficult to predict before hand.

The goal of global synchronization of all IPs is therefore left unrealized due to impossibility in sending signals from one end of the chip to another within a single clock cycle. Instead of aiming for that unobtainable goal, an attractive option is to allow self-

synchronous IPs to communicate with one another through a network-centric architecture [40].

Existing on-chip interconnect architectures will give rise to other problems with scaling. The most commonly used on-chip interconnect architecture is the shared medium arbitrated bus. In such an interconnect, all communicating devices share the same transmission medium, usually a group of wires. The achievable operating frequency of the bus depends on the propagation delay in the interconnection wires. This propagation delay depends on the number of IP cores connected to the wires. Each core attached to the shared bus adds a parasitic capacitance, thus degrading performance with system growth [39]. For SoCs consisting of hundreds of IP blocks, this bus-based interconnect architectures will lead to propagation delays that exceed one clock cycle, therefore making it impossible for IPs to reliably communicate with each other.

To overcome these stated problems, it has been proposed the use of a network-centric approach to integrate IPs in complex SoCs [40]. Research groups have proposed interconnect solutions that use mesh, torus, fat-tree, and octagon network topologies [2,4,14,20,40]. In these models, IPs are connected to closely neighboured switches which are connected to neighbouring switches. Global signals which would span significant portions of a die in a more traditional bus-based architecture, now only have to span the distance separating switches. In this scenario, global wires will only consist of top level interconnects between switches. The specifics about such interconnect can be known at

early stages of the design process, enabling a better prediction of the electrical parameters of the interconnect, and overall system performance [40].

Several on-chip network proposals for SoC integration can be found in literature. One is *Sonic's Silicon Backplane* is a bus-bases architecture in which the IP blocks are connected to a shared bus through specialized interfaces called *agents* [49]. Each core communicates with an agent using the *Open Core Protocol (OCP)* [10]. Agents communicate with each other using *TDMA (Time Division-Multiplexed Access)* bus access schemes effectively decoupling the IP cores from the communication network. The basic interconnect architecture is still bus based and will hence suffer from performance degradation trends common for buses [40].

*MIPS* technologies has introduced an on-chip switch integrating IP blocks in a SoC[50]. The switch called *SoC-it* is intended to provide a high-performance link between a *MIPS* processor and multiple third party IP cores.

Kumar [28] and Dally [30] have proposed mesh-based interconnect architectures. These architectures consist of an m x n mesh of switches interconnecting IPs placed one at each switches. Each switch is thereby connected to four neighbouring switches and one IP block. The mesh topology is described in detail in Chapter 3.

In [2,3,4,39,40] the SoC group at UBC has described and interconnect architecture for a networked SoC, as well as the associated design of required switches, addressing mechanisms, and dealing with inter switch wire delay problems.

In SoC environment where die area is an issue, switches need to consume as little area as possible. In *wormhole switching* the packets are divided into fixed length flow control units (*flits*) and the input and output buffers need only to be able to store a few flits only. This feature ensures the buffer space requirement in the switches will be small relative to packet switching [31].

The performance of large scale SoCs will depend on the throughput of the network which depends on the *flow control mechanism* [31]. Flow control determines the allocation of channel and buffer resources to packets as it traverses its routed path. In switch based interconnect architectures, buffers are associated with physical channels and messages are buffered at the input and output of each physical channel and are commonly operated as *FIFO (First-In, First-Out)* queues. Therefore once a message occupies a buffer for a particular channel, no other message can access the physical channel, even if the message is blocked [9].

It is possible that the channel remains idle, while there are packets in the network waiting for it. This problem is a unique problem associated with an interconnection network using wormhole switching technique and impacts the SoCs overall performance substantially [9].

To solve this throughput degradation problem it has been propose to use the concept of virtual channels in the SoC environment [9,40].

The concept of virtual channels was introduced by Dally [9] and serves to decouple buffer resources from link transmission resources. This decoupling allows unblocked messages to pass blocked messages using transmission resources that would have otherwise been left idle. It has been shown that this increased utilization opportunity can lead to substantially higher throughput. The exact amount of performance increase depends on topology and many other network parameters.

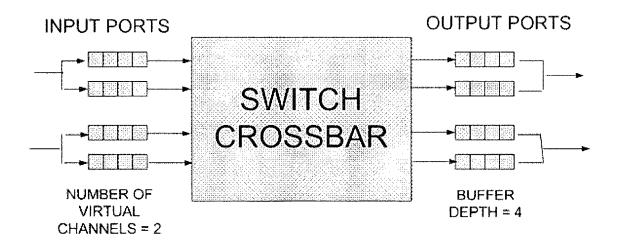

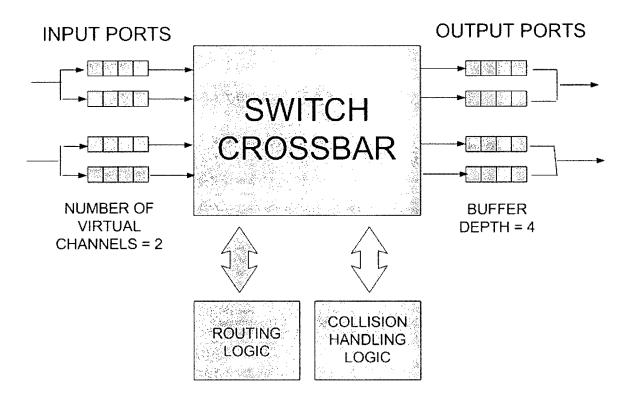

The decoupling of buffer and link resources involves adding extra buffers on the input and output end of a link (see Figure 1). Flits stored in an output buffer do not own the link as well; rather they must compete with other flits being stored in the other output buffer of this link. This competition is done in the form of round robin so that each virtual channel receives an equal share of the link bandwidth. Once a flit is granted access to the link, it can traverse and must be stored in an available buffer at the input end. If an input buffer is not available, the flit would not have been granted use of the link.

Figure 1: Example switch using two virtual channels

No message can occupy more than one virtual channel at a port's input or output port at a given time. Once a free virtual channel is populated by a header flit, the virtual channel is reserved for the use of only that message until the reservation is cleared by that message's tail flit.

#### 2.2 Related Work

Other network simulation tools have been developed, both commercially and academically. As described below, their feature capabilities fall short of what is required for NoC simulation and analysis.

#### 2.2.1 FlexSim

FlexSim1.2 is a simulator for flit-level simulation k-ary n-cube networks developed by the SMART Interconnects group at University of Southern California (USC) [27]. The

tool was developed with the purpose of studying the performance impact of various routing algorithms.

FlexSim has the ability to vary a number of network parameters such as virtual channels, traffic pattern, load, switch delays, message lengths, and buffer depths. A deadlock detection module is included that builds a dependency graph and located cycles. It also has the functionality to characterize the deadlocks in terms of frequency and size.

Various routing adaptive routing algorithms are available as well as standard dimension ordered routing.

The tool collects statistics throughout on latency and throughput and produces standard outputs (throughput, average message latency).

The main restriction of *FlexSim* is its inability to simulate networks other than the mesh or torus. Another limitation is the size of each dimension along the cube is restricted to be a power of two, preventing irregular sizes such as a 50 x 50 network. While *FlexSim* can give users a good idea of the performance of adaptive routing algorithms in these two topologies, there are many more topologies for NoC designers to consider. This drawback is the main reason *FlexSim* by itself is not enough to give designers the information they require to make a completely informed decision about on-chip network interconnection.

#### 2.2.2 *IRFlexsim0.5*

IRFlexSim0.5 is another flit-level simulator developed by the SMART Interconnects

Groups at USC [26]. The tool is based on FlexSim1.2 and shares most of its

functionality. The main purpose of IRFlexSim0.5 is to study the performance of various routing algorithms over networks with arbitrary topologies.

The parameters that could be varied with *FlexSim* (virtual channels, traffic pattern, delays, etc.) are still there. Static and adaptive routing algorithms can be chosen and routing tables can be input through external files. Deadlock detection is also present in this version.

The ability to create a regular k-ary n-cube topology is lost in this version, as are the topology specific routing algorithms. In its place, *IRFlexSim0.5* has the ability to create irregular topologies arbitrarily when given a specified number of switches and links.

Other guidelines like the minimum and maximum degree of each switch and whether or not multiple links are allowed between links can also be set.

Topologies can also be taken from a user created input file. The input file contains the number of nodes and links in the network followed by a list of links in the form <node>-<node>. This manual process is limited to use only bi-directional links, but with enough manual effort, any topology can be input into the simulator. The major drawback of this functionality is that no matter what topology is manually input, the network is still treated as an arbitrary graph of nodes. This means that if a

multidimensional octagon was manually input, it would not be routed as one, but rather as an arbitrary group of nodes.

Another limitation of the topology creation is that the process is limited to direct networks. Intermediate switches in topologies such as trees cannot be created as each node in the network contains a traffic source and sink.

#### 2.2.3 NS version 2.0

NS version 2.0 is an object-oriented discrete-event simulator for packet switched local and wide area networks [25]. The Network Research Group at the Lawrence Berkeley National Laboratory first developed NS version 1.0. Version 2 is now part of the Virtual Inter Network Testbed (VINT) project at USC.

NS version 2.0 is suitable for small scale simulations of queuing algorithms, congestion control protocols, and multicast analysis. It has the capabilities to implement network protocols such as TCP and UDP, produce application based traffic source behaviour, and use various queue management mechanisms and routing algorithms. It provides standard outputs that the USC tools also provided such as throughput, and latency.

NS version 2.0 does not inherently support wormhole switching however. Although some insight to NoC behaviour could be taken from using this tool's packet switching functionality, it is not sufficient to simulate wormhole networks under packet switching

conditions. Many added complexities and dependencies arise when wormhole switching is introduced, and to get accurate simulated results [32][33], a tool with wormhole switching capabilities is required. *NS version 2.0* would require a significant amount of modification to support wormhole switching and so falls short of fulfilling all requirements for a NoC simulator.

#### 2.2.4 **OPNET**

OPNET (Optimized Network Simulation Tool) is a very powerful piece of commercially developed simulation software [36]. It provides a development environment for simulation and analysis of communication networks. The tool has capabilities for creating topologies of static or dynamic nodes to include satellites and wireless devices. Nodes are connected together by either packet streams of statistic wires to transfer packets or numerical signals. Logic control and behaviour are modeled using process models which are written in a language called *Proto-C*.

OPNET Modeler is an environment for network modelling and simulation. It provides the ability to create hierarchies of network objects such as nodes and links. This feature makes the engine scalable to large networks. Fully parallel discrete event simulation is possible. Graphical environments model the simulated networks if specified by the user. Standard output statistics are available, as are more specialized measurements.

Although *OPNET* is a very powerful and encompassing tool, its focus is on communication networks at a higher level than on-chip. Wormhole switched simulations may be possible after some degree of customization. Comparing network topologies would involve creating each network from scratch as no automatic network creation is provided. These drawbacks cause developers to be well versed in *OPNET's* modelling language in order to evaluate newly proposed topologies.

A tool specialized for NoC simulation would be more beneficial for designers since the ability to quickly and easily compare topologies of different regular types and sizes is absent with *OPNET*.

### 2.2.5 Stuttgart Neural Network Simulator

SNNS (Stuttgart Neural Network Simulator) is a software simulator for neural networks developed at *The Institute for Parallel and Distributed High Performance Systems* (IPVR) at the University of Stuttgart [41]. The goal of the SNNS project is to create an efficient and flexible simulation environment for research on and application of neural nets.

Since network on-chip interconnects borrow ideals from large scale parallel processing and neural networks are closely linked to parallel processing it is possible that a neural network simulator can shed some light on a network on chip interconnect performance.

Neural networks do have the fundamental difference that wormhole switching is not

supported. It is for that reason that neural network simulators cannot be used for our purpose.

## 2.2.6 The cnet Network Simulator (v2.0.9)

The cnet Network Simulator (v2.0.9) was developed at The University of Western Australia [42]. cnet enables users to vary data-link later, network later, routing and transport layer networking protocols in networks consisting of point-to-point links and IEEE 802.3 Ethernet segments. This simulator is used mostly as an educational tool, rather than a design aid. As its focus is centered on protocol use at higher than physical layers of the network model, it fails to provide the requirements needed for an NoC simulator.

#### 2.2.7 QualNet Version 3.8

QualNet is a software tool used to design and test communication networks, including adhoc wireless networks as well as other wireless and wired networks [43]. It supports real-time simulation of a large number of nodes (10-10000). QualNet also has a feature that enables users to view 3D graphical models of their networks. The tool is widely used in industry and academia. While many different protocols and routing schemes are available at many layers of the network model, the simulator fails to support wormhole switching at the physical layer. Since the use wormhole switching surfaces many unique communication problems, a tool that does not allow one to investigate wormhole switching performance is less than satisfactory.

#### 2.2.8 REAL 5.0 Network Simulator

*REAL* is a network simulator originally intended for studying the dynamic behaviour of flow and congestion control schemes in packet-switched data networks [44]. The simulator takes as input a description of network topology, protocols, workload, and control parameters. It produces as output statistics such as the number of packets sent by each source of data, the queuing delay at each queuing point, and the number of dropped and retransmitted packets. Unfortunately, *REAL 5.0* does not support wormhole switching or physical switch parameters and so cannot be considered as a NoC design tool.

### 2.2.9 MaRS Maryland Routing Simulator

MaRS (Maryland Routing Simulator) is a discrete event simulation test bed for evaluating routing systems [45]. The physical network is somewhat limiting and it consists of link components and node components. A node component models the "physical" aspects of a store-and-forward entity and is characterized by parameters such as buffer space, processing speed, packet queuing discipline, and failure and repair distributions. A link component models a transmission channel between two nodes. A link component connecting node A and node B represents two one-way channels. Each one-way channel is modeled by a queue of packets. A link component is characterized by parameters such as bandwidth, propagation delay, and failure and repair distributions. By connecting link

components and node components, the user can specify a network of arbitrary topology.

However communication is limited to packet switching and virtual channels are not supported.

#### 2.2.10 Boppana, Chalasani, and Siegel: Wormhole Network Simulator

R.V. Boppana, S. Chalasani, and J. Siegel developed a network simulator which supports wormhole switching. The code is provided as is with no technical support [46]. The simulator allows for the selection of physical network parameters such as virtual channels, flit size and buffers per lane. Routing and traffic load can also be configured. The main limitation of this software is its failure to support topologies other than mesh and torus. This fact would prohibit designers from fully investigating all options and as a result this software falls short of the requirements.

## 2.2.11 Simured Multicomputer Network Simulator

Simured is a multi-computer network simulator that was developed at the University of Valencia [47]. This simulator supports only k-ary n-cube tori and meshes. Flow control is limited to wormhole switching. It has several routing functions: deterministic, adaptive, with dead-locks support. Simured also allows the user modify the number of virtual channels of the network. Notably, Simured has been referenced in the text "Interconnection Networks" of José Duato [31]. However, due to topology restrictions, this simulator does not meet the requirements.

#### 3.0 NoCSim

*NoCSim* is a flit-level network-on-chip simulator developed in C++. The main purpose of the tool is to provide a common platform to study the performances of various network topologies. The tool allows for the simulation of wormhole switched direct and indirect networks of several NoC proposed topologies. All parameters that characterize a network have default values, but can also be user-defined.

The simulator was developed using Microsoft Visual Studio, and coded in C++. C++ was chosen because the popularity of the language makes expanding or changing the program easier for future developers. The code is modular so that new topologies and routing or collision handling algorithms can be added without complications.

This chapter details the features and options available in *NoCSim*. All options are chosen in the main menu shown in Figure 2. Topology characterization is discussed first below, followed by switching and routing concepts. Descriptions of the parameters and options available with *NoCSim* follow. Finally, output options and statistics are discussed. Chapter 4 describes the simulation engine and Chapter 5 goes into more detail about output, illustrating results obtained from running simulations.

```

CURRENT NETWORK/TRAPFIC PARAMETERS

1 - Butterfly Fat Tree

2 - Number of IPs: 256

3 - Buffer Depth (flits): 1

4 - Uirtual Channels: 4

5 - Source Queue Length (messages): 100

6 - Simulation Duration (cycles): 1000000

7 - Reset stats at time: 2500

8 - Traffic Type: Uniform

9 - Load: 1

a - Message Length (flits): 16

b - Packets dropped when source queue overloads

c - Control flits not used

d - Message info not dumped

e - Port info not dumped

f - Adjacentcy list not dumped

g - Average Queue Length calculation is ON

h - Stat update interval: 2500

i - Average Active Messages calculation is OFF

j - Header Collisions handled by: Port Order

k - 1 interation per cycle

1 - Not using trace file

Derived Parameters:

Switches: 120

Nodes: 376

Levels: 4

COMMANDS: Run - r Setup Sweep - s Quit - q

Enter number to change parameter, or choose a command to run simulation:

```

Figure 2: NoCSim Options Menu with Default Settings

## 3.1 Network Topologies

Networks topologies have been previously classified as they have been widely studied in parallel processing [31]. Since so many varieties of topology exist, these classifications instantly give a better understanding of topology characteristics when considering a new topology. *NoCSim* offers simulation of a wide variety of topologies; some of the classifications of said topologies are described below:

- Shared-Medium Networks

- Direct Networks

- Indirect Networks

Available topologies in *NoCSim* are k-ary n-trees (fat trees), k-ary n-cubes, butterfly fat trees (BFT), and octagon. For k-ary n-cubes, the number of dimensions, and then number of IPs along each dimension are accepted thus making it possible to simulate a  $2 \times 5 \times 7$  network if so desired. Also, whether or not wraparound links are used is also to be specified. For k-ary n-trees, k and k must be input creating a network of k switches at k levels. Details and formal definitions of k-ary k-trees and k-ary k-cubes follow in the subsections below.

All networks require the appropriate number of IPs to be set as well. This value can be arbitrary as the simulator will create the smallest topology possible that will incorporate this number of IPs. E.g., if a 100 IP BFT is selected, a 256 IP BFT will be created with 156 dormant IPs. Dormant IPs do not impact network statistics such as throughput.

#### 3.1.1 Shared-Medium Networks

Shared-medium networks are the least complex interconnect structure. They are made up of one transmission medium which is shared between all communicating devices [31]. A major drawback of these networks is that only one device is permitted to use the medium at any given time. As the number of devices sharing the medium increases, the medium becomes a bottleneck as many collisions arise and devices are forced to wait for their turn to use the medium. To handle these collisions, a hardware arbiter is required to deal with requests.

An inherent benefit of shared-medium networks is their ability to support broadcasting. Since all devices connected to the medium can monitor the network activities one device can reach all other devices with one effect by simply including the addresses of all destination devices in the message header, or using a broadcast flag.

#### 3.1.1.1 Bus

Bus systems fall under this category and are the first suggested topology for SoC environments. Buses are shared medium networks where the medium is one or more wires that stretch across a series of communication devices. Examples of on-chip bus networks are *AMBA* [5], *CORECONNECT* [6], and *WISHBONE* [7].

As stated above, buses have been used for smaller SoCs, but as we advance to the deep sub-micron era, buses fail to provide adequate performance for any application. One of the major drawbacks of bus systems is the transmission medium (bus line) becomes a bottleneck as IPs requesting its use become backed-up with unsent packets. The problem only gets worse when additional IPs are added.

Buses also have drawbacks in the form of propagation delay and parasitic capacitance. Intrinsic parasitic resistance and capacitance from the line and added IPs increase to extremely high levels causing propagation delay to be unacceptably high. High propagation delays lead to longer clock cycles, higher latency, and lower throughput. A theoretical example of a bus topology is shown in Figure 3.

Figure 3: Simple Bus Structure

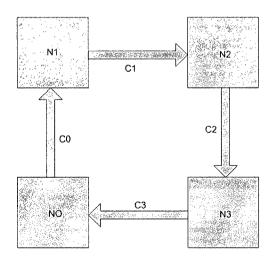

#### 3.1.2 Direct Networks

Direct networks topologies consist of a set of nodes which are connected to each other by channels. Each node contains an independent functional unit, or IP in the NoC domain, as well as a router component that is common amongst all nodes. Because of these characteristics, direct networks are also called router based networks, or point-to-point networks. The routers are connected to neighbouring routers via bi or unidirectional links. Each router also has internal channels proving paths to connect a node's external channels together. Direct networks have been generally described using graphs containing nodes N, and channels C, G(N,C) [31].

An ideal direct network would have all nodes connected to all other nodes directly without intermediate nodes in the way. A network like this is called fully connected where each router must contain N external links where N is the number of nodes. For any substantial N, the cost of such a network is prohibitive due to the overwhelming wiring complexity. Therefore even though performance may suffer when less links are

used, such sacrifices are necessary to create a scalable and cost efficient network. Many different topologies have been suggested that attempt to balance this trade-off of cost and performance.

Direct networks have the inherent feature that they scale well to large number of IPs.

Each new IP added brings with it a new router component, thus the overall bandwidth of the network increases with the number of IP blocks. This is a key advantage when designing a network which is to contain a large number of IP blocks.

As messages traverse nodes to reach their destinations, the routing algorithm used by each node determines the path it will take. Efficient routing is a critical factor of the performance of the interconnection network. Routing schemes can be specific to topologies but share the same fundamentals such as keeping travel paths short, and deadlock avoidance. Routing and deadlock issues are discussed in depth in Sections 3.4 and 3.5, respectfully.

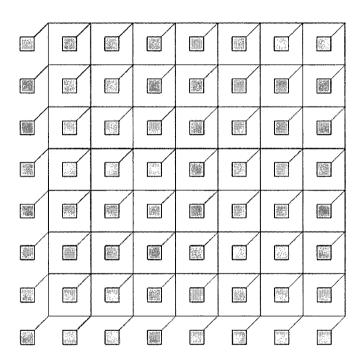

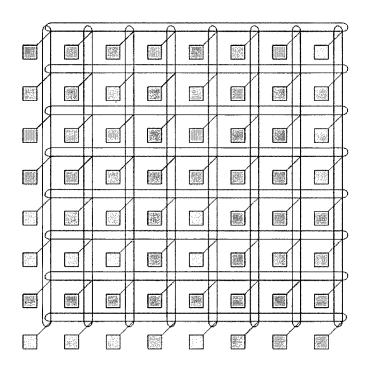

## 3.1.2.1 *K-ary N-cubes*

K-ary n-cube topologies fall under the direct network category. Each IP in the topology contains a router component that connects it to neighbouring routers their IPs [20][28]. These networks contain K nodes along N dimensions for a total of  $K^N$  nodes. Below is the formal definition of a k-ary n-cube:

A *k-ary N-cube* has *k* nodes along each dimension *n*. Each node *X* is identified by n coordinates  $(x_{n-1}, x_{n-2}, ..., x_1, x_0)$ . Two nodes *X* and *Y* are neighbours if and only if  $y_i = x_i$  for all  $i, 0 \le i \le n-1$  except one, j, where  $y_j = (x_j \pm 1) \mod k$ .

Rings fall under the *k-ary n-cube* definition with n=1. Other examples are shown in Figures 4-6.

Figure 4: A 8-ary 2-cube without wraparound links, also called a mesh topology.

Figure 5: A 8-ary 2-cube with wraparound links, also called a torus topology.

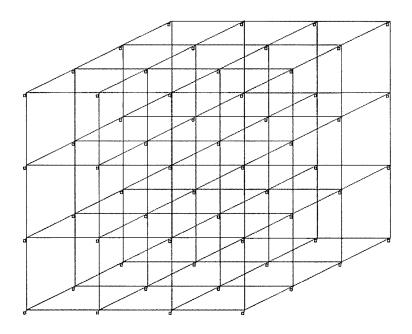

Figure 6: A 3-ary 3-cube.

A two dimensional cube as defined above is also referred to as a *torus*. A *torus* is a conventional mesh with the addition of wraparound links for each dimension. The formal

definition of a mesh is the same as the *k-ary n-cube* with the simplification that two nodes X and Y are neighbours if and only if  $y_i = x_i$  for all i,  $0 \le i \le n-1$ , except one, j, where  $y_j = x_j \pm 1$ . Leaving out the modulus k removes the wraparound links making the mesh irregular and without symmetry.

The folded torus topology is graphically equivalent to a torus topology, the only difference being the way in which the IPs are laid out [14]. IPs are 'folded' over and interleaved on a row by row basis to dispose of a long and power inefficient wrap-around link. As a result, short wire lengths increase, but the need for a long 'wrap-around' link is alleviated reducing the overall energy consumption for flit transmissions. The difference is illustrated below in Figures 7 and 8.

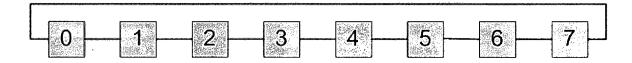

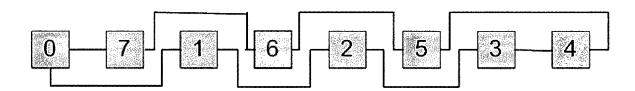

**Figure 7:** A conventional 8 IP, 8-ary 1-cube with wraparound link, also called a *ring*, or *torus*.

**Figure 8**: A 'folded' torus of 8 IPs. It is still an 8-ary 1-cube with wraparound link. Each node keeps the same neighbouring nodes, but the node order is changed to remove the long wraparound link.

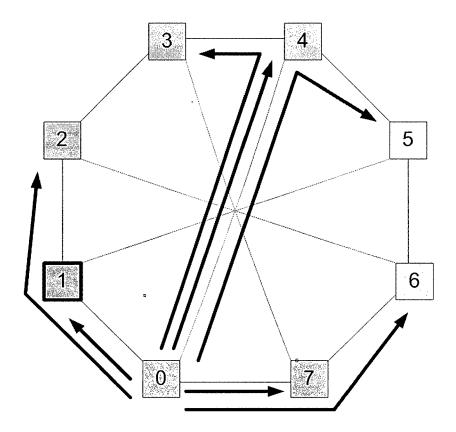

#### 3.1.2.2 Octagon

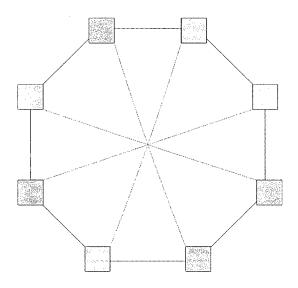

Another direct network topology that has been proposed for NoC purposes is octagon [19]. At the lowest level, the topology consists of 8 nodes and 12 bi-directional links connecting each node. Each node is connected with the node directly across from it, its clockwise neighbour, and its counter clockwise neighbour as shown in Figure 9.

Figure 9: An 8 node octagon.

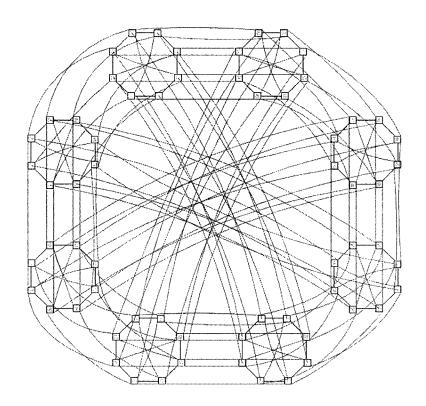

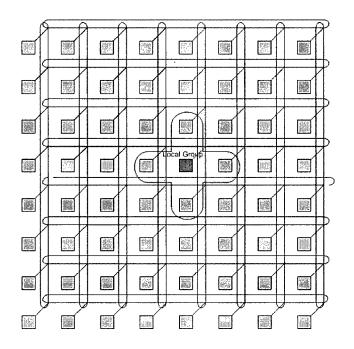

For networks with greater than 8 IPs, the octagon scales by extending into multidimensional space. A 64 IP example is shown in Figure 10. If each node is indexed with the ordered pair  $(i, j)i, j \in [0,7]$ . For each  $i = I \in [0,7]$ , an *octagon* is constructed using nodes  $\{(I, j), j \in [0,7]\}$ . These *octagons* are then connected together by linking corresponding I nodes according to the octagon configuration. Thus, each node could be thought to be in two different octagons. The first consisting of nodes  $\{(I, j), j \in [0,7]\}$ , and the second consisting of nodes  $\{(i, J), i \in [0,7]\}$ . This pattern can be continued any

number of dimensions, giving a maximum number of IPs of  $N = 8^d$ , where d is the number of dimensions.

Figure 10: A 2-dimensional 64 IP octagon topology

This strategy maintains a low worst case hop count between IPs, but comes at the cost of high wiring complexity. At the lowest level, packets have to travel at most two hops to reach their destination. That number only increases by two for each added dimension keeping the connectivity close to full even as N increases to thousands. This connectivity is extremely costly as the wiring demands increase exponentially. For example, for a 512 IP three dimensional octagon, 2304 links are required, while for a 64 IP two-dimensional octagon, only 192 are required.

#### 3.1.3 Indirect Networks

Indirect networks are similar to direct networks but differ in that instead of IPs being connected directly, they are connected though intermediate switches. These switches act like the router components of direct networks. Each contains a number of ports which contain input and output links. Because of this distinction, indirect networks have been called switch-based networks, while direct networks are called router-based networks.

The topology of an indirect network is determined by how the switches are connected together through links. Like direct networks, indirect network topologies can also be modelled by a graph G(N,C), where N is the set of switches and C is the set of links between the switches [31].

In regular indirect networks, the switches are usually identical and are organized as a set of stages. Each stage is only connected to the previous and next stage using regular connection patterns. Input/output stages are connected to functional nodes as well as to another stage in the network. These networks are referred to as *multistage interconnection networks* (*MIN*) and have different properties depending on the number of stages and how those stages are arranged.

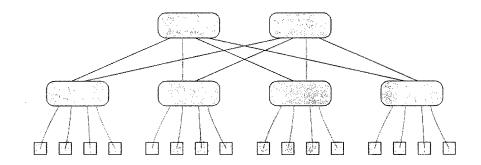

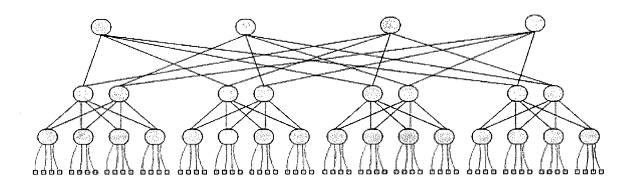

# 3.1.3.1 K-ary n-trees

*K-ary n-trees*, or *fat-trees* have been proposed for on chip network architectures [15][18]. *Fat trees* are in the indirect network category because they have IPs connected to

switches at the leaves of a tree. Those leaves are connected to other switches further up the tree. The formal definition is shown below:

Definition 1: A fat-tree is a collection of vertices connected by edges and is defined recursively as follows:

- A single vertex by itself is a fat-tree. This vertex is also the root of the fat-tree.

- If  $v_1, v_2, ..., v_i$  are vertices and  $T_1, T_2, ... T_j$  are fat-trees, with  $r_1, r_2, ... r_k$  as roots (j and k need not be equal), a new fat-tree is built by connecting with edges, in any manner, the vertices  $v_1, v_2, ..., v_i$  to the roots  $r_1, r_2, ..., r_k$ . The roots of the new fat-tree are  $v_1, v_2, ..., v_i$ .

The above definition is very general and covers regular trees, and fat-trees with variable sized switches and multiple connections between vertices and irregular constructions.

*K-ary n-trees* are a specific class of *fat-trees* where all switches are identical, and construction is regular. The formal definition is shown below:

Definition 2: A k-ary n-tree is composed of two types of vertices:  $N = k^n$  processing nodes and  $nk^{n-1}$ ,  $k \times k$  communication switches. Each nodes is an n-tuple  $\{0,1,...,k-1\}^n$ , while each switch is defined as an ordered pair (w,l), where  $w \in \{0,1,...,k-1\}^{n-1}$  and  $l \in \{0,1,...,n-1\}$ .

- Two Switches  $(w_0, w_1, ..., w_{n-2}, l)$  and  $(w'_0, w'_1, ..., w'_{n-2}, l')$  are connected by an edge if an only if l' = l + 1 and  $w_i = w'_l$  for all  $i \neq l$ . The edge is labelled with  $w'_l$  on the level l vertex and with  $w_l$  on the level l vertex.

- There is an edge between the switch  $(w_0, w_1, ..., w_{n-2}, n-1)$  and the processing node  $p_0, p_1, ..., p_{n-1}$  if and only if  $w_i = p_i$  for all i  $E\{0, 1, ..., n-2\}$ . This edge is labelled with  $p_{n-1}$  on the level n-1 switch.

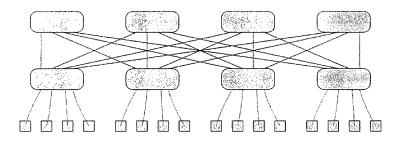

Examples of *k-ary n-trees* are shown below in Figures 11 and 12.

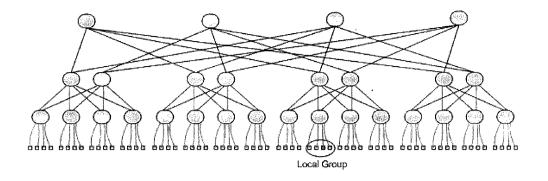

**Figure 11:** A 16 IP *4-ary 2-tree*

**Figure 12:** A 64 IP *4-ary 3-tree*

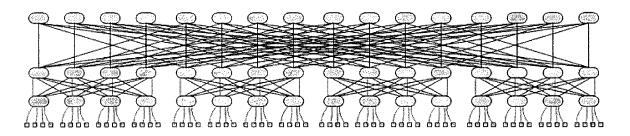

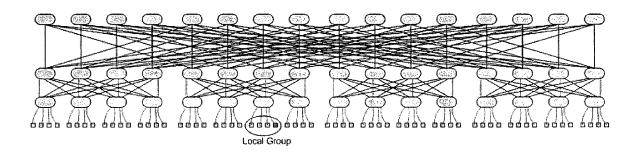

### 3.1.3.2 Butterfly Fat-Tree

The *butterfly fat-tree* (*BFT*) is another indirect network topology that has been proposed for NoC applications [3][16][17]. The *BFT* is a variation of *fat-tree* where each switch is imbalanced in that is has four child ports which send and accept traffic from further down the tree, and two parent ports that send and accept traffic towards the root of the tree. These ports are indexed as:  $partent_0$ ,  $parent_1$ ,  $child_0$ ,  $child_1$ ,  $child_2$ , and  $child_3$ . For referencing, these switches are addressed S(l,a), where l is the level, and a is the index along that level. The N IPs at the lowest level are connected to N/4 switches at the first level such that processor P(0,a) is connected to  $child_{a \bmod 4}$  of switch  $S(1,\lfloor a/4 \rfloor)$ . The number of levels in a BFT is  $\log_4 N$ , and each level contains  $N/2^{l+1}$  switches. These switches are connected according to the switch's address.  $Parent_0$  of S(l,a) is connected to  $child_l$  of  $S(l+1,\lfloor a/2^{l+1}\rfloor \cdot a \bmod 2^l$  and  $parent_1$  of S(l,a) is connected to  $child_l$  of  $S(l+1,\lfloor a/2^{l+1}\rfloor \cdot a \bmod 2^l)$ , where  $i=\lfloor a \bmod 2^{l+1}/2^{l-1}\rfloor$ . The number of switches per level is reduced by a factor of 2 as the level increases. From this the total number of switches  $S_T$  can be calculated as:

$$S_T = N/4 + (1/2)N/4 + (1/2)^2 N/4 + \dots + (1/2)^L N/4$$

$$= N/4 \frac{(1 - (1/2)^L}{(1 - 1/2)}$$

$$\lim_{L \to \infty} N/4 \frac{(1 - (1/2)^L}{(1 - 1/2)} = N/2$$

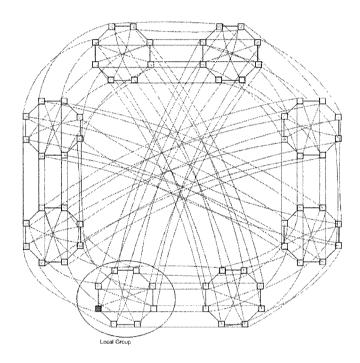

Examples of *BFTs* are shown below in Figures 13 and 14.

Figure 13: A 2 level, 16 IP Butterfly Fat Tree

Figure 14: A 3 level, 64 IP Butterfly Fat Tree

# 3.2 Switching

A switching mechanism determines how and when router input channels are connected to output channels that have been selected by the routing algorithm. It determines how network resources are allocated for message transmission. Popular switching mechanisms are *circuit switching*, *packet switching*, and *wormhole switching* [31].

In *circuit switching*, all channels required by a message are requested and reserved prior to the message being transmitted. Thus, a dedicated path is established and the transmission encounters no contention once the path is established. The establishment of the path can be delayed by other messages reserving resources beforehand.

In *packet switching*, also called store-and-forward switching, messages are divided into packets before being sent though the network. Packets advance into resources as soon as they become available. Buffer space at each switch is required for packet switching as packets are held in a buffer until the next channel becomes available.

Wormhole switching also involves breaking a message into packets at the source like packet switching [32][33]. The packets are then further divided into flow control units called flits. The first flit, or header, contains routing and status information and advances into free resources like packet switching. Flits trailing the header flit follow in a pipeline fashion. If at anytime the header flit cannot advance because its desired input or output channel is occupied, the header becomes blocked and the trailing flits are forced to wait as well until advancing is again possible. Buffer space at each switch, but each buffer only needs to be large enough to hold one flit. Packets become spread out over many switches, so the buffer demands at each switch are a fraction of what they are in packet switching where each buffer must be large enough to hold an entire packet. Because of this actuality, wormhole switching is popular in the SoC domain where there is an aim to minimize switch hardware overhead.

Since only wormhole switched networks have been proposed for large scale on-chip networks, *NoCSim* only supports *wormhole switching*.

#### 3.3 Virtual Channels

The use of virtual channels is generally accepted to be beneficial for NoCs, so *NoCSim* supports the use of virtual channels by allowing the user to select the number of virtual channels per input/output channel. All channels must have the same number of virtual channels.

## 3.4 Routing Options

How incoming packets are forwarded to outgoing channels depending on the active routing algorithm. Since routing depending greatly on the network topology [31], routing algorithms for each available topology are discussed in turn below.

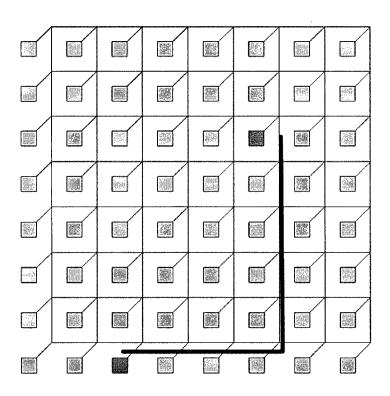

# 3.4.1 K-ary N-cube Routing

NoCSim supports the most common simply routing algorithm used for k-ary n-cubes,

Dimension Ordered Routing (DOR). It is a distributed scheme meaning routing decisions

are made locally at each node by reading header tags. It is also a non-adaptive or

oblivious algorithm, meaning messages cannot be dynamically rerouted to avoid

congestion. Each source-destination pair will have the same path each time.

*DOR* first indexes the dimensions in the network so that a set order is established. When a header arrives at router, it compares the destination address  $D(d_{n-1}, d_{n-2}, ..., d_1, d_0)$ , with the node's address  $(x_{n-1}, x_{n-2}, ..., x_1, x_0)$ , where n is number of dimensions and  $x_i$  is the coordinate in dimension i. If the coordinates in the first dimension, i = 0, do not match the header is routed in the direction of the destination in that dimension. Once the header's destination and current node address match in the first dimension, the routers then compare the coordinates of the next dimension, i=1. This process is continued until the destination node is reached. An illustration showing a possible source-destination pair for a 64 IP *mesh* is shown in Figure 15.

Figure 15: Dimension Ordered Routing in a 64 IP mesh

Many adaptive routing algorithms have been suggested for *k-ary n-cubes*. These may involve throttling, or avoiding congestion by changing dimensions additional times [35]. While these algorithms have some performance improvement in sub-saturation conditions, they also introduce added routing complexity and overhead due to added logic. For this reason, only non-adaptive algorithms are currently supported by *NoCSim*, however the modular nature of *NoCSim* allows for new routing algorithms, adaptive or non-, with relative ease.

# 3.4.2 Octagon Routing

*NoCSim* supports a simple, oblivious routing scheme for the *octagon*. It is a simple shortest-path algorithm where nodes determine the appropriate output port by checking the relative address of the destination, see Figure 16. A break down of the possible cases is shown below in Table 1:

| Relative Address | Destination Port        |

|------------------|-------------------------|

| 0                | Route to local IP port  |

| 1 or 2           | Route clockwise         |

| 6 or 7           | Route counter-clockwise |

| 3, 4, or 5       | Route across            |

| 3, 4, or 5       | Route across            |

**Table 1:** Simple shortest path *octagon* routing

Figure 16: Shortest Path Routing in octagon

When dealing with multidimensional *octagons*, this routing scheme can be applied to each dimension in order starting with the highest [19].

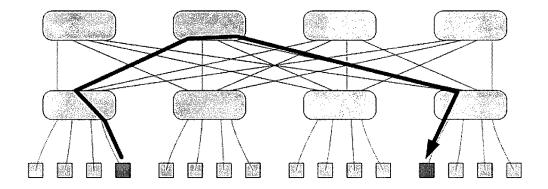

# 3.4.3 K-ary N-tree Routing

Routing in trees almost always comes in the form of turnaround routing. In this form of routing, packets ascend the tree until they find their least common ancestor shared by the source and destination nodes. Once reached, the package is 'turned around' and begins its descent to the destination as shown in Figure 17. *NoCSim* supports turnaround routing.

**Figure 17:** A possible path for a source/destination pair using *turnaround routing* in a 16 IP *fat-tree* topology.

When a header arrives at a switch child port that is not its least common ancestor, that header is routed out through one of the k parent ports. The choice of port is arbitrary as long as the port has an empty channel available; therefore redundancy exists during the ascent of the tree. After the turnaround however, there is only one unique path the header must be routed through to reach its destination, and the redundancy is no more [31].

# 3.4.4 Butterfly Fat Tree Routing

BFTs use the same turnaround routing scheme that is described above in the k-ary n-tree section.

## 3.5 Deadlock, Livelock, and Starvation

Deadlock, livelock and starvation are critical issues that need to be addressed in any network due to their catastrophic consequences [31].

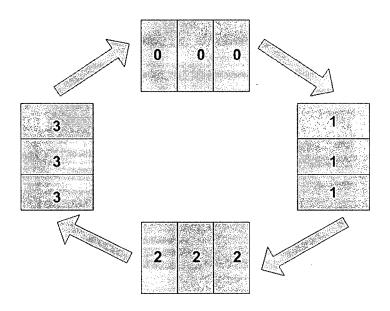

A deadlock is a situation where all packets in the network cannot advance to their destination because the resources requested by them are full. All packets involved in the deadlock are blocked indefinitely. An example of a deadlock in a 4 node *ring* is shown in Figure 18. The buffers of each node are completely full with flits waiting for resources at the next node to become free.

Figure 18: Deadlock in a 4 node *ring*.

Livelock is a similar situation where packets can never reach there destinations, the difference being packages may be moving around the network unblocked in a livelock situation. It can only occur if packets are allowed to follow non-minimal paths however, so since all networks in *NoCSim* are minimal path routed, livelock is not an issue [31]. If adaptive routing schemes are implemented, livelock avoidance strategies must be implemented as well.

Starvation occurs when a packet stops permanently when the resources it is requesting are consistently being granted to other contending packets. It can be avoided by using a fair contention resolution scheme when allocating resources. *NoCSim* allows the user to choose between several fair contention resolution schemes that prevent starvation.

Contention resolution is described in detail in Section 3.7.

Methods of handling deadlock include deadlock avoidance, and deadlock detection / recovery. The later technique is only effective when deadlocks are rare because they carry the assumption that the networks can recovery from deadlocks faster than they arise. These techniques also require added hardware and logic at the switches. *DISHA* [13] is a recovery technique that requires each node to have a central "floating" buffer. Since hardware at the switches is to be minimized and deadlocks may occur at rapid rate, only deadlock avoidance schemes were implemented in *NoCSim*.

A necessary and sufficient condition for deadlock-free non-adaptive routing is the absence of cycles in a resource dependency graph [12]. Therefore, topologies that do not have cycles will never experience deadlock. Tree-based topologies like *k-ary n-trees* and *butterfly fat trees* have no cycles when turnaround routing is used. The same is true for *k-ary n-cube* topologies when wraparound links are not used (*mesh*) and *DOR* is used.

For topologies that do contain cycles, further effort is required to break the cycles to avoid deadlock situations. The *k-ary n-cube* with wraparound links (*torus*) and *octagon* topologies do contain cycles even when *DOR* is used.

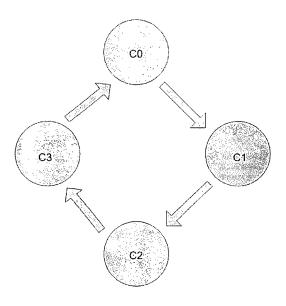

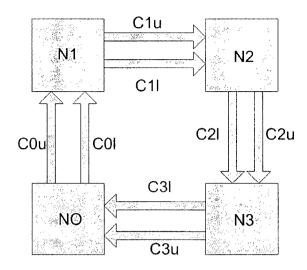

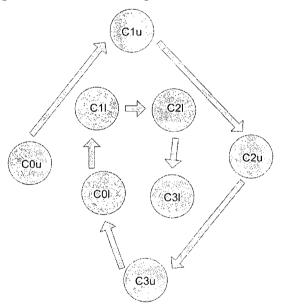

Dally and Seitz [11] proposed a way to break the cycles in *k-ary n-cube* networks with the use of virtual channels and restrictive routing. To remove the cycles, the virtual channels are first split into two groups, upper and lower. When packets are injected into the network, they restricted to upper virtual channels only. If at any time a packet traverses a predetermined link in each cycle (e.g. the wraparound link) the packet's restriction changes from upper to lower. Each time the packet changes dimension it must be restricted to the upper virtual channels. This restriction changes the cycle nature of the dependency graph into a more spiral-like shape.

To illustrate this process, consider a four node (N0-N3) ring example in which the nodes are connected with unidirectional links. This simple topology and its resource dependency graph are shown in Figures 19 and 20.

Figure 19: A 4 node unidirectional ring.

Figure 20: Corresponding dependency graph.

While the channels (C0-C3) remain undivided and routing is not restricted, the dependency graph contains a cycle. This cycle can be the source of deadlocks. However, if virtual channels are used to divide each channel into and upper channel  $(Ciu\ i=0..3)$  and a lower channel  $(Cil\ i=0..3)$  and routing is restricted as described above. Specifically, packets injected are restricted to using upper channels. If packets reach N0 and are not at their destination however, they are then restricted to using lower channels. The divided ring and its dependency graph are shown below in Figures 21 and 22.

Figure 21: A 4 node *ring* with virtual channels.

Figure 22: Corresponding dependency graph.

This restrictive routing and virtual channel use can be implemented to remove cycles from any network. It comes with the down side that the resources of the lower virtual channels remain idle when the wraparound link is not used. It is for that reason that mesh networks outperform *torus* networks under certain conditions such as highly localized

traffic loads [14]. Another notable characteristic of networks using this technique is packets must now keep track of which virtual channel they have come from when being routed. Without the restriction, packets are memoryless.

The cycles in the *octagon* could also be removed using this fashion. Since the *octagon* is so connected however, simply restricting routing to prohibit the use of a predetermined link in each level of *octagon* to physically remove the cycle gives the same effect without a very noticeable drop in performance. By doing this, the performance degradation under highly localized traffic is not an issue as virtual channels are not restricted.

#### 3.6 Switch Model

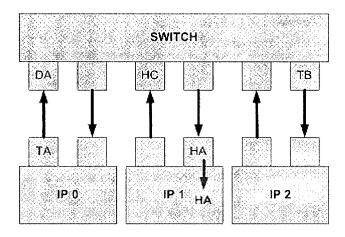

The switch model used by *NoCSim* is shown below in block diagram form, Figure 23. Several parameters are available to customize network switches.

Figure 23: Example Generalized Switch Block Diagram.

The number of input/output ports is predetermined by the topology, although different topologies have different numbers of ports per switch.

For all topologies but torus, the number of virtual channels can be set to any positive number. *Torus* has the additional restriction that it must have at least two virtual channels because of the restrictive routing involved in preventing deadlock in that topology. The number of virtual channels describes how many buffers are available per link at both the input and output end. The number of buffers must be the same at both ends.

The depth of each buffer can be specified as well. This value determines how many flits can fit into each buffer.

The crossbar of each switch is assumed to be fully connected. In other words, every combination of input port to output port is valid.

How flits pass through the crossbar to output ports is determined by the routing and collision handling logic. Data and tail flits simply follow the path of their respective headers, but header flits require routing. As previously mentioned, routing is topology specific and determines the destination output port for each header. Once all headers have been routed, collision handling logic detects and resolves and contention for output ports. Finally, header movements are processed and the appropriate headers move to the determined output buffers. Details of these processes are described below in Section 4.1.

# 3.7 Collision Handling

To deal with the collisions that arise between contending headers, a collision handling scheme, or select function, is required to select the order of which resources will be granted. *NoCSim* has several options in this respect and they are discussed in next subsection:

### 3.7.1 Port Ordered Collision Handling

In this scheme, the indexes given to ports in the network creation process are used to determine which header's requests are recognized first. In other words, the mechanism will first check all headers in *port* 0, followed by *port* 1, 2, etc. This order does not change throughout the simulation. This scheme is the easiest to implement, however it is prone to starvation, since in saturated traffic a header at a higher numbered port could be forced to wait indefinitely.

# 3.7.2 Round Robin Collision Handling

The *round robin scheme* is similar to the *port order scheme* in that a mechanism checks headers in order of their port index. The difference is that from cycle to cycle, the starting point of said mechanism changes to the next port. When the last port of a switch is reached, the mechanism returns to *port* 0, thus providing wraparound.

# 3.7.3 Oldest Goes First Collision Handling

This scheme involves the collision handler checking the network injection times of contending headers and resolving their requests in the order of oldest goes first. Doing this ensures that starvation will not occur as headers will at some time become the oldest at a particular switch. Generally, this scheme will reduce a network's worst-case latency but to be physically realized would involve headers carrying injection time information.

## 3.7.4 Priority Based Collision Handling

NoCSim has the capabilities of implementing a priority based collision handling scheme. In the supported scheme, four different levels of priority of message are possible (0-3). Messages are given this priority upon injection and the ratio of a given priority level to another can be specified as well (e.g. 10% priority 0, 50% priority 1, 20% priority 2, 20% priority 3). When collisions occur using this scheme, headers with higher priority are given the first available resources, then the next highest, etc. Collisions of headers with the same priority are handled according to round robin.

High priority messages blocked by lower level messages temporally transfer their priority to the lower priority message to encourage it to get out of the way. This priority inheritance was proposed by R. Rajkumar in [37] and is shown to further improve the average latency values of high-priority messages.

#### 3.8 Traffic Generation

NoCSim has many options for traffic generation, the default being Poisson distributed uniform random traffic. In this class, messages arrive at sources according to Poisson distribution are given randomly generated destinations that are all equally as likely. The only restriction being the source and destination cannot be equal. Uniform traffic is a long used benchmark for network analysis, but has been proven to be inaccurate when modelling real life networks [31].

Destinations can also be selected by a *bit-complement traffic pattern*. In this pattern, sources will only send messages to the destination IP whose address is the bit complement of the sources address. This pattern is even less accurate than *uniform*, but is used to evaluate networks as it provides insight to the worst-case of traffic since the destinations are usually on the opposite side of the network.

Hotspot traffic is another commonly used traffic pattern that attempts to provide a more accurate model [31]. In hotspot traffic, a number of hotspot IPs are selected by the user with the fraction of the load that is direct to only the hotspots. This attempts to mimic a network involving some popular IPs such as a memory block with data common, or a busy processor.

Localized traffic is another traffic pattern that tries to provide a more accurate look at network performance [40]. The user is asked to input the fraction of load that is destined for IPs within a local group of IPs. How the local groups are defined depends on the topology. For *k-ary n-cubes*, the local group is determined as the nodes immediately neighbouring the source on each side (see Figure 24). Thus for a 2D, 64 IP *mesh*, a central IP will have four IPs in its local group, and 59 in the non-local group. For *k-ary n-trees* and *butterfly fat trees*, the local group is defined as the group of IPs that share the same level 1 switch (see Figures 25 and 26). So for a *BFT*, the local group consists of three other IPs. *Octagon's* local group is defined by the lowest level of octagon in the hierarchy, meaning the seven other IPs in a sources bottom level *octagon* (see Figure 27).

**Figure 24:** A 64 IP *8-ary 2-cube* with wraparound links. The highlighted IP's local group of 4 is circled.

Figure 25: A 64 IP 4-ary 3-Tree. The highlighted IP's local group of 4 is circled.

**Figure 26:** A 64 IP 3 level *BFT*. The highlighted IP's local group of 4 is circled.

**Figure 27:** A 2-dimensional 64 IP *octagon*. The highlighted IP's local group of 8 is circled.

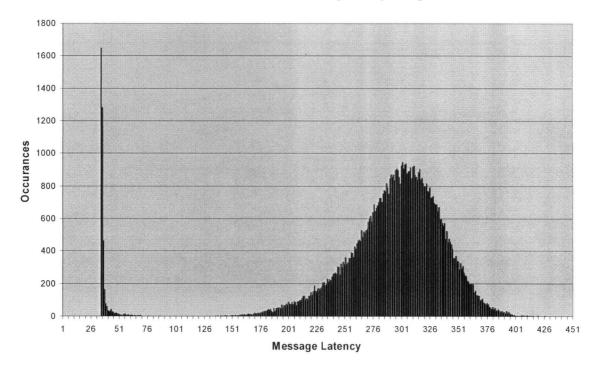

It should be noted that these local group definitions vary slightly from topology to topology, but these variations are inevitable as each topology's inherent structure are the biggest determining factor. For that reason, it is fair to compare under these conditions.