# PARASITIC SUBSTRATE EFFECTS IN GALLIUM ARSENIDE MONOLITHIC MESFETS

#### DAVID DIMA SHULMAN

B.Sc., Technion — Israel Institute of Technology, 1983

M.Sc., Technion — Israel Institute of Technology, 1986

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

in

THE FACULTY OF GRADUATE STUDIES

(The Department of Electrical Engineering)

We accept this thesis as conforming to the required standard

| ,       | •••••• |

|---------|--------|

| ••••••• | •••••  |

|         |        |

THE UNIVERSITY OF BRITISH COLUMBIA

June 1992

©David Dima Shulman

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

|             | Signature(s) removed to protect privacy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Signature) | Marine Processing Control of Cont |

|             | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Department of _ | Electrical         | Engineering |

|-----------------|--------------------|-------------|

|                 | f British Columbia |             |

| Date O          | t. 7 / 1992.       |             |

#### **Abstract**

The present large scale GaAs integrated circuit industry is based on the fabrication of metal-semiconductor field-effect-transistors (MESFETs) on semi-insulating GaAs substrates which provide the device isolation. High-resistivity in semi-insulating GaAs is achieved by the delicate balance between shallow donors and acceptors, and deep levels. The semi-insulating substrates, however, do not provide perfect isolation and do allow crosstalk between neighboring MESFETs. One source of the crosstalk is sidegating, usually defined as the change in drain current of one MESFET as a result of applying a negative potential to a nearby contact of another MESFET. In addition, the interaction of each MESFET with the semi-insulating substrate is strong enough to affect the electrical properties of the device, the most important being the change of the output conductance with frequency. This work is concerned with the above two parasitic effects with the main focus on sidegating, which is the major obstacle for developing large scale GaAs integrated circuits.

Electron injection into the vicinity of a MESFET from a nearby contact via a semi-insulating substrate is known to produce the sidegating effect. This process is known as *single* injection, because the injection is due to a single carrier type. In this work we present a novel study of sidegating in the frequency domain (AC sidegating) and a new mechanism of DC sidegating in which holes are injected into a semi-insulating substrate from the gate of a MESFET and electrons are injected into a semi-insulating substrate from a nearby contact. This process is known as *double* injection.

We distinguish between high- and low-level double injection where the low-level injection is referred to a condition in which the excess carrier concentration is much smaller than the majority carrier concentration in semi-insulating GaAs, while the low-level injection is referred to a condition in which the concentration of injected excess carriers exceeds the majority carrier concentration in semi-insulating GaAs.

High-level double injection results in a drastic variation of a MESFET drain current at voltages lower that those predicted by the single-carrier injection model. It also results in hysteresis in current-

voltage characteristics as observed in experiments.

It is shown that sidegating may occur under conditions of low-level double injection, because of the resultant excess trapped charge distribution which produces non-linear potential profiles across the semi-insulating substrate. The contribution of hole injection and recombination processes to the non-linear potential profile is discussed.

We found that AC sidegating at least up to and including the kHz range is related to DC sidegating, in a way that upon increasing a negative sidegate voltage the AC drain current is decreasing. Upon applying small negative or positive sidegate voltages, thus preserving the conditions of low-level injection, this work predicts a strong sidegating effect in the kHz-MHz range due to the decrease by a few orders of magnitude of the resistance of semi-insulating substrates. This is because semi-insulating GaAs transforms in this frequency range from what is called a "lifetime semiconductor", in which quasi-neutrality of free carriers is preserved, to a "relaxation semiconductor", in which separation of electrons and holes in space exists through zero local recombination. The present treatment predicts that this form of AC sidegating will be only weakly sensitive to hole injection, and will increase and start at lower frequencies on decreasing the distance between the MESFETs.

The peculiar electrical properties of the semi-insulating GaAs in the frequency-domain are used to explain the frequency dependence of the output conductance of GaAs MESFETs on semi-insulating substrates. One result of the model developed in this thesis for the output admittance of GaAs MESFETs is that while the magnitude of the admittance can change by a factor of two or three, the variation of its phase is negligible.

The results of this work indicate that device performance is strongly influenced by the properties of the semi-insulating substrate. One result is that device characteristics are not determined solely by the most dominant trap in the undoped SI substrate EL2, but also by recombination centers (which are not EL2) and shallower traps.

### Table of Contents

|   | Abstract ii List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Introduction 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2 | AC Sidegating       5         2.1 Introduction       5         2.2 AC Sidegating in GaAs n-i-n structures       6         2.2.1 Experimental Procedure       2.6         2.2.2 Results       7         2.2.3 Discussion       8         2.3 AC Sidegating in GaAs MESFETs       17         2.3.1 Modeling       17         2.3.2 Determination of model parameters       22                                                                                                                                                                                                                                                              |

|   | 2.3.3 Comparison with experimental results       23         2.3.4 Discussion       24         2.4 Summary       30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3 | The role of minority carriers in the sidegating effect       32         3.1 Introduction       32         3.2 Sidegating effect under conditions of low-level injection       32         3.2.1 Introduction       32         3.2.2 Sidegating model       33         3.2.3 Detailed analysis       36         3.2.4 Discussion       43         3.3 Evaluation of hole injection       48         3.4 High-level double carrier injection in the sidegating effect       58         3.4.1 Introduction and Model       58         3.4.2 Experiments       59         3.4.3 Analysis and Discussion       62         3.5 Summary       70 |

| 4 | Low-frequency transport in semi-insulating GaAs       71         4.1 Introduction       71         4.2 Analysis and results       71         4.3 Discussion       76         4.4 Applications to AC sidegating       83         4.5 Summary       84                                                                                                                                                                                                                                                                                                                                                                                     |

| 5 | Modeling frequency dependence of the output conductance of GaAs MESFETs 85 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6 Conclusions                                                 | 95  |

|---------------------------------------------------------------|-----|

| References                                                    | 99  |

| A Potential distribution in the uniform channel               | 106 |

| B Potential distribution in the exponentially tapered channel | 107 |

## List of Figures

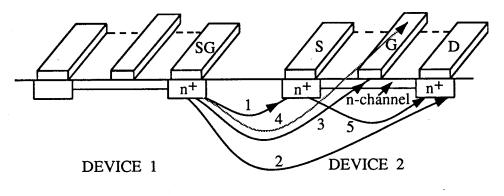

|      | Sources of parasitic effects in GaAs MESFETs on a SI substrate. Lines 1–4 visualize interaction mechanisms between two MESFETs on a SI substrate, which can be sources of sidegating: 1–2 interaction between the source/drain to the sidegate, 3 interaction between the sidegate to the gate on a doped channel, 4 interaction between the sidegate to the portion of the gate on a SI substrate (the dashed line shows the edge of the active channel area). Line 5 shows |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | drain-to-source leakage current, which contributes to the increase of an output conductance of a MESFET                                                                                                                                                                                                                                                                                                                                                                      |

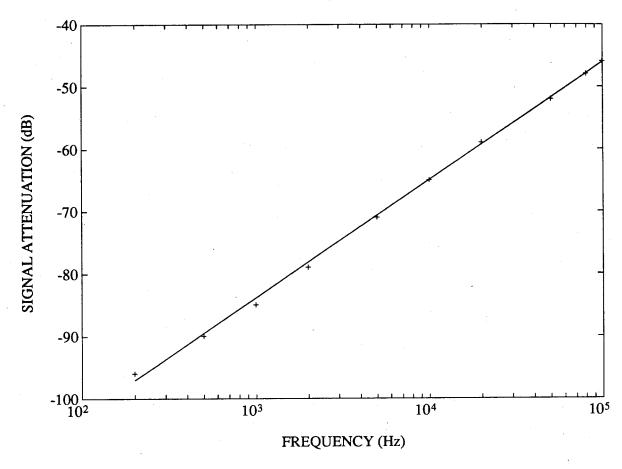

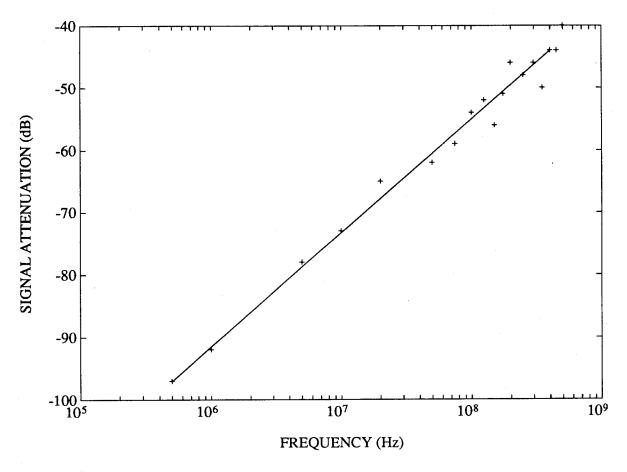

| 2.2  | Signal attenuation at low frequencies for the $20\mu m$ long structure (for sidegate voltage $V_{SG}=-6V$ ) measured using the low-frequency measurement setup 7                                                                                                                                                                                                                                                                                                             |

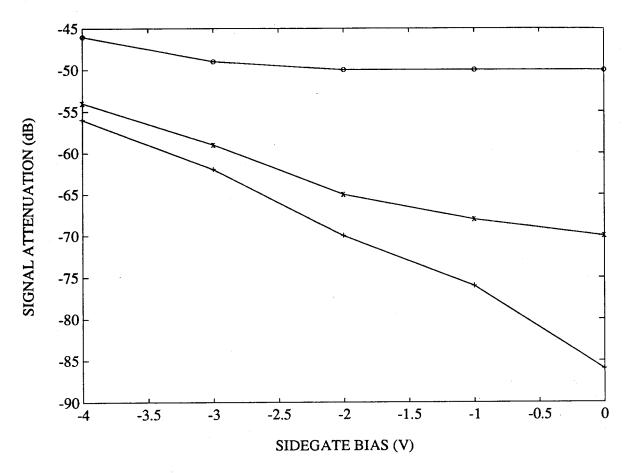

| 2.3  | Signal attenuation vs. negative sidegate voltage at 1kHz(pluses), $10kHz(x-marks)$ , and $100kHz(circles)$ measured using the low-frequency measurement setup for $3\mu m$ long structure                                                                                                                                                                                                                                                                                    |

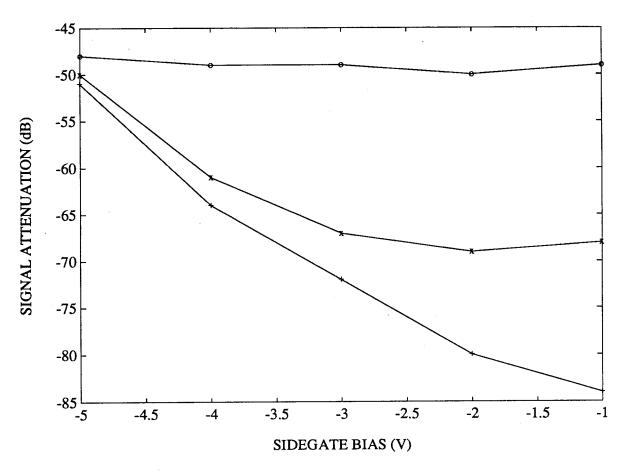

| 2.4  | Signal attenuation vs. negative sidegate voltage at 1kHz(pluses), 10kHz(x-marks), and 100kHz(circles) measured using the low-frequency measurement setup for 14μm long structure9                                                                                                                                                                                                                                                                                            |

| 2.5  | Signal attenuation at radio frequencies for the $20\mu m$ long structure (for sidegate voltage $V_{SG}=-6V$ ) measured using the high-frequency measurement setup 10                                                                                                                                                                                                                                                                                                         |

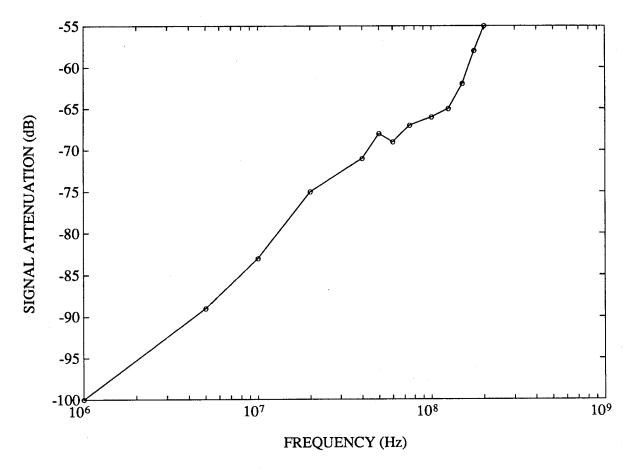

| 2.6  | Signal attenuation at radio frequencies for the $450\mu m$ long structure (for sidegate voltage $V_{SG}=-6V$ ) measured using the high-frequency measurement setup 11                                                                                                                                                                                                                                                                                                        |

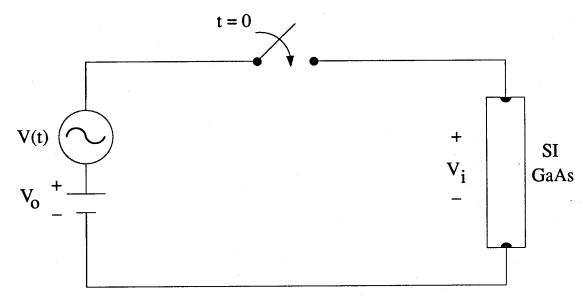

| 2.7  | Physical system corresponding to the differential equation 2.4 which is used for investigating frequency-dependent transients in SI GaAs. At $t=0$ the switch is closed and the DC biasing voltage $V_0$ and the sinusoidal input $V(t)$ are applied to a bar of SI GaAs, which is initially biased at $V_1$                                                                                                                                                                 |

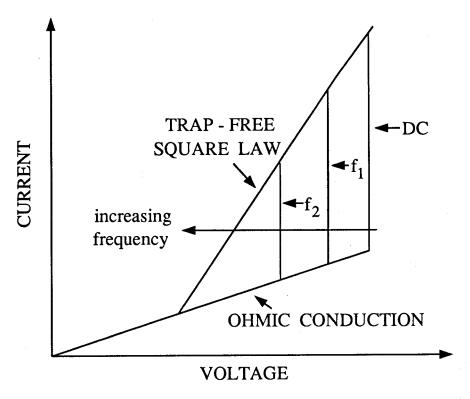

| 2.8  | Schematic AC current-voltage characteristics for space-charge-limited conduction in SI GaAs at two frequencies $f_2 > f_1$ . The current will be confined in the triangle bounded by the lines formed by the DC traps-filled-limit voltage, the trap-free square law and the ohmic conduction                                                                                                                                                                                |

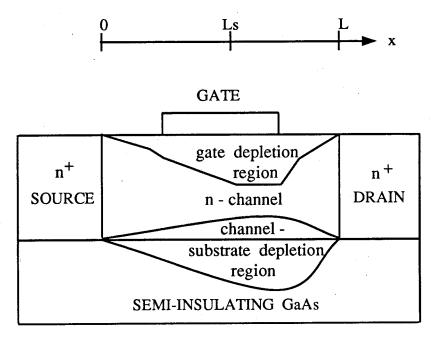

| 2.9  | Schematic space charge distribution in a GaAs MESFET operating in the saturation region with a negative gate bias                                                                                                                                                                                                                                                                                                                                                            |

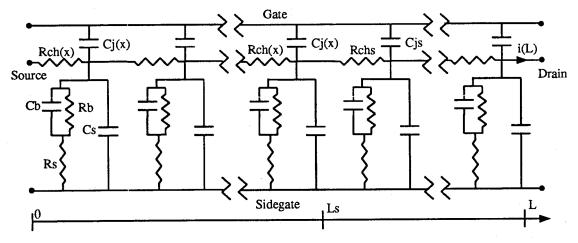

| 2.10 | Distributed network for a GaAs MESFET in the saturation region 20                                                                                                                                                                                                                                                                                                                                                                                                            |

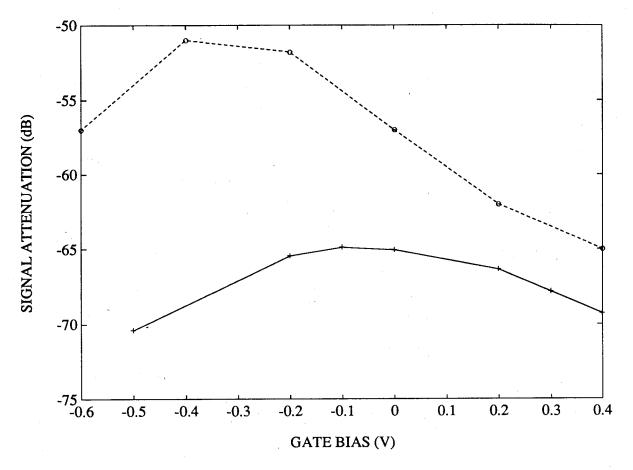

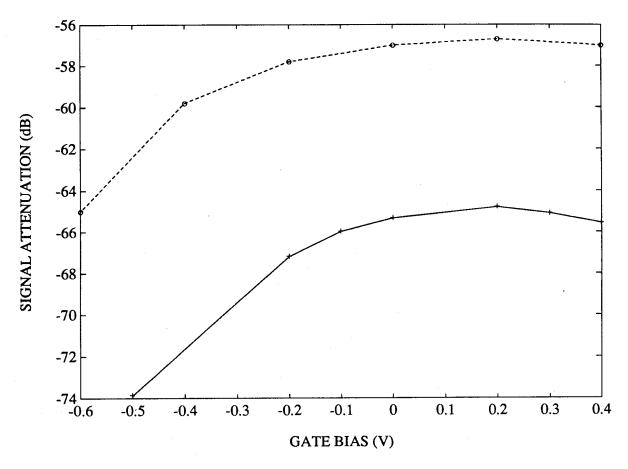

| 2.11 | Experimental (dashed line) and calculated (solid line) dependences of AC sidegating on the gate bias for a depletion-mode GaAs MESFET operating at $V_{DD}=0.5V,V_{SG}=-3V,100\mathrm{kHz}.$ Parameters: $c_b=15.4\mathrm{fF},r_b=1.1\mathrm{G}\Omega,r_s=0.06\mathrm{G}\Omega,c_s=15\mathrm{fF}.$ Zero bias gate capacitance is 90fF                                                                                                                                        |

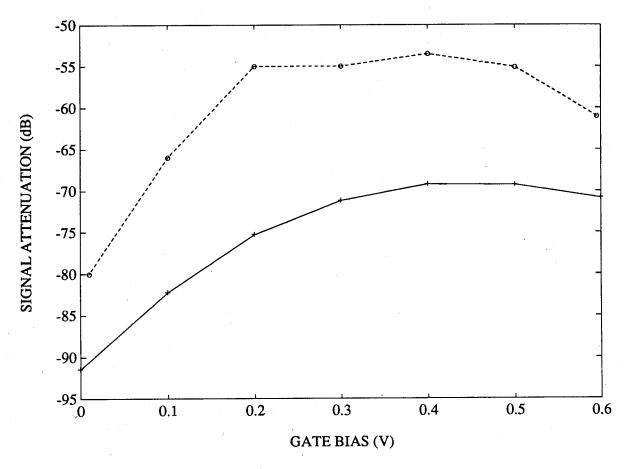

| 2.12 | Experimental (dashed line) and calculated (solid line) dependences of AC sidegating on the gate bias for a enhancement-mode GaAs MESFET operating at $V_{DD}=0.5V,V_{SG}=-1V,100\rm kHz$ . Parameters: $c_b=17\rm fF,r_b=2.8G\Omega,r_s=0.15G\Omega,c_s=15\rm fF$ . Zero bias gate capacitance is 10fF                                                                                                                                                                       |

| 2.13 | 3 Experimental (dashed line) and calculated (solid line) dependences of AC sidegating on the gate bias for a depletion-mode GaAs MESFET at $V_{DD}=3V,V_{SG}=-1V,100{\rm kHz}$ . Parameters: $c_b=17{\rm fF},r_b=2.8{\rm G}\Omega,r_s=0.15{\rm G}\Omega,c_s=15{\rm fF}\dots\dots\dots\dots\dots$ 26                                                                                                                                                                          |

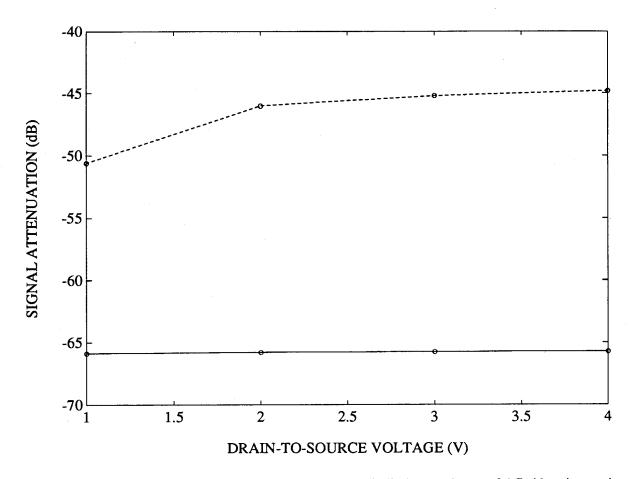

| 2.14 | Experimental (dashed line) and calculated (solid line) dependences of AC sidegating on the drain-to-source voltage for a depletion-mode GaAs MESFET operating at $V_G = 0V$ , $V_{SG} = -2V$ , $100 \mathrm{kHz}$ . Parameters: $c_b = 16.3 \mathrm{fF}$ , $r_b = 3.2 \mathrm{G}\Omega$ , $r_s = 0.17 \mathrm{G}\Omega$ , $c_s = 15 \mathrm{fF}$ , $r_{chs} \approx 210 \Omega$ , $c_{js} \approx 84 \mathrm{fF} \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

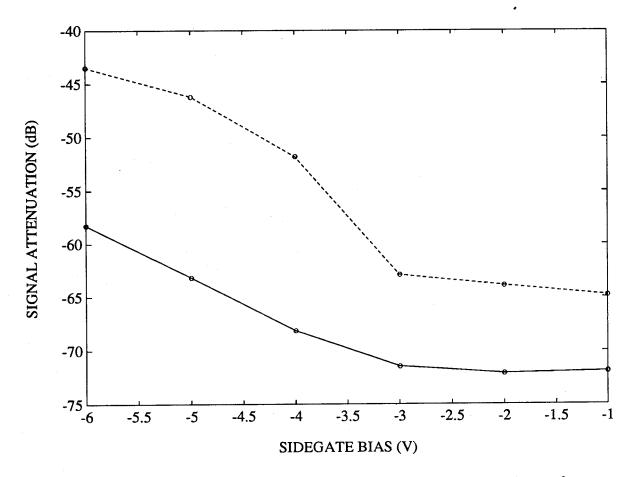

|      | Experimental (dashed line) and calculated (solid line) dependences of AC sidegating on the sidegate bias for a depletion-mode GaAs MESFET operating at $V_G=0V,V_{DD}=0.5V,10\mathrm{kHz}$ . Parameters: $r_{chs}=175\Omega,c_{js}=90\mathrm{fF},c_s=15\mathrm{fF}\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28 |

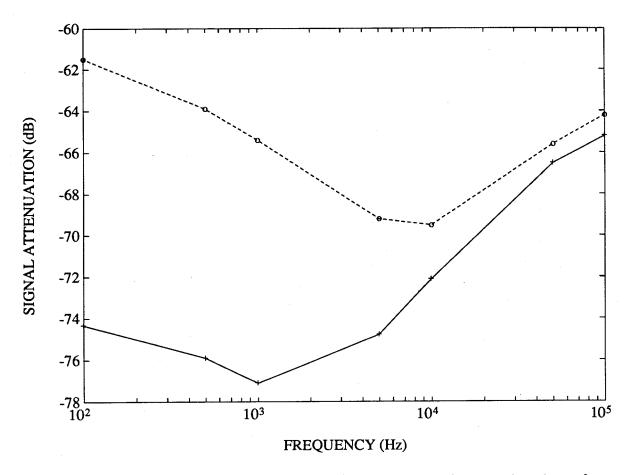

|      | Experimental (dashed line) and calculated (solid line) frequency dependence of sidegating for depletion-mode GaAs MESFET operating at $V_G=0V,V_{DD}=0.5V,V_{SG}=-1V$ . Parameters: $r_{chs}=175\Omega,c_{js}=90 {\rm fF},c_b=17 {\rm fF},r_b=2.8 {\rm G}\Omega,r_s=0.15 {\rm G}\Omega,c_s=15 {\rm fF}\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29 |

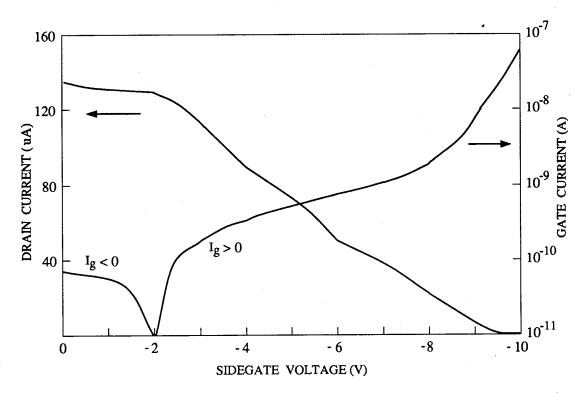

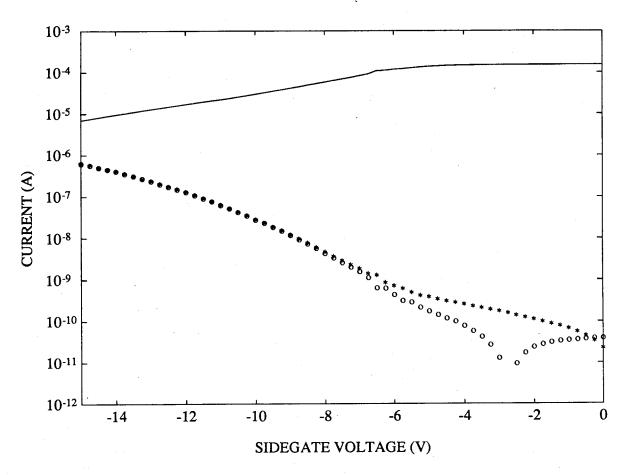

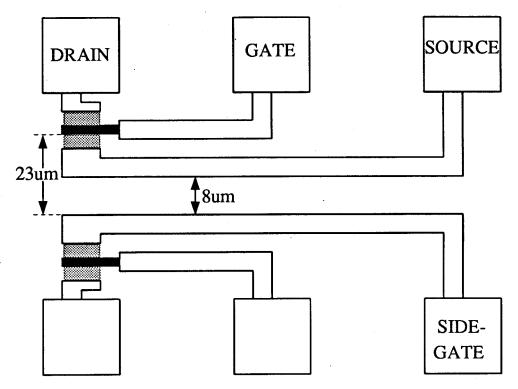

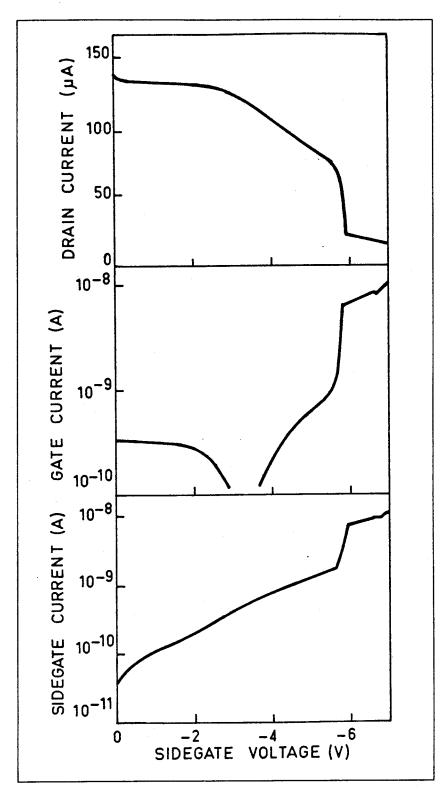

| 3.17 | Typical drain and gate currents as a function of sidegate voltage $(V_D=2V,V_G=0V)$ . The measurements were performed in the dark on depletion-mode MESFETs fabricated by ion implantation into a SI substrate. The typical threshold voltage was $-0.6V$ . The gate length was $1\mu m$ and width $4\mu m$ . The gate-source and gate-drain distances were $2\mu m$ . The ohmic contact of the adjacent MESFET, which served as a sidegate in our measurements, was placed parallel to the source at a distance of $8\mu m$ and was $23\mu m$ from the gate                                                                                                                                                                                                                                                                                                                                                                                                           | 34 |

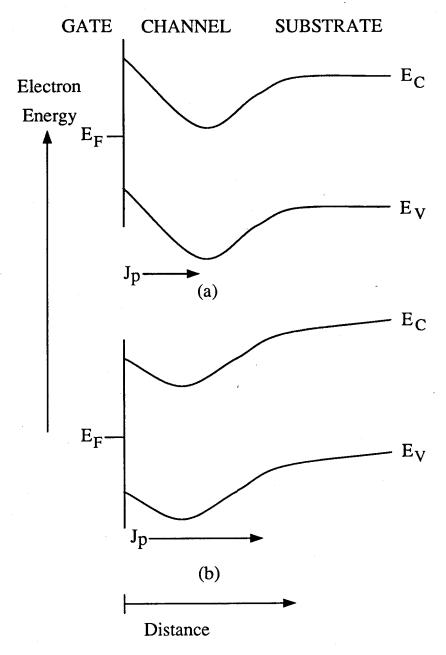

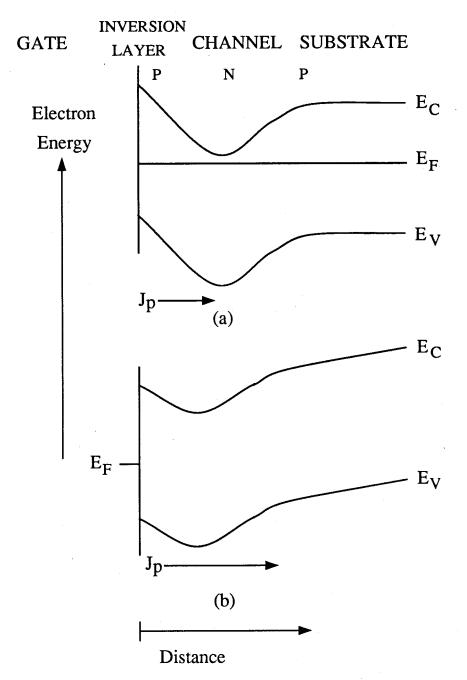

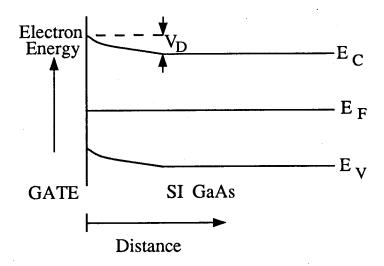

| 3.18 | Hole injection from Schottky gate. (a) For a small sidegate voltage. (b) For a large sidegate voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35 |

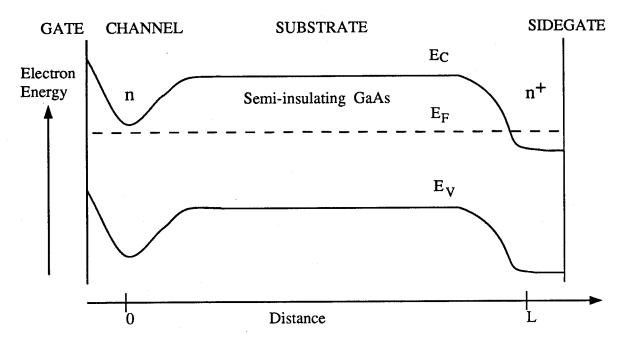

| 3.19 | Schematic band diagram of the gate-sidegate structure in equilibrium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37 |

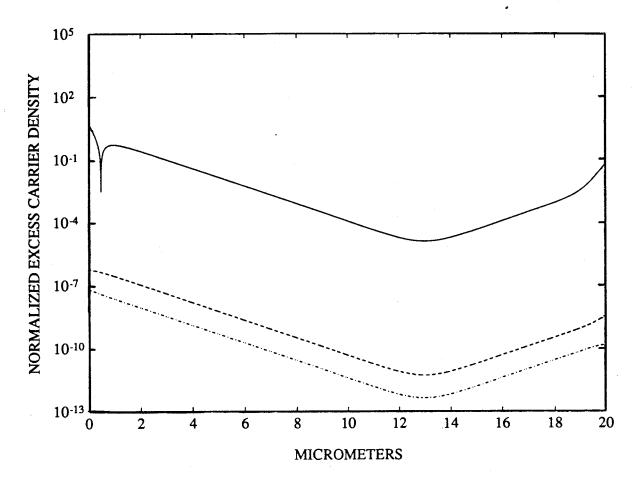

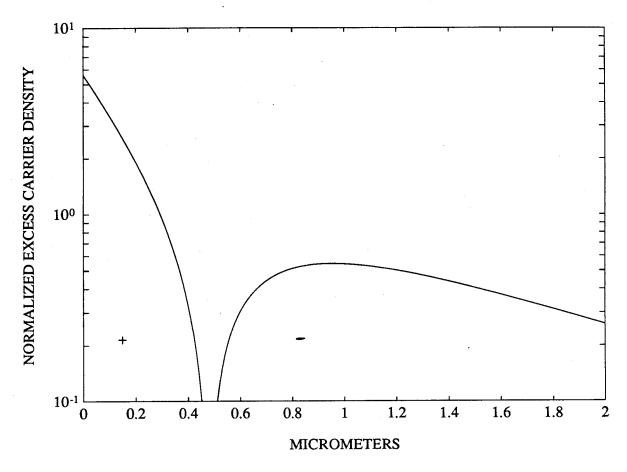

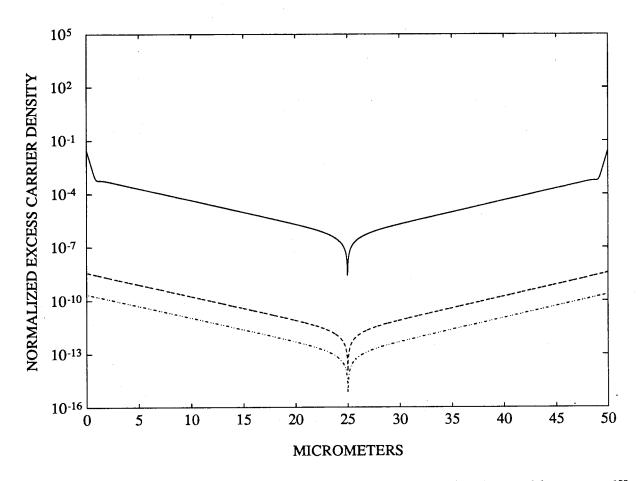

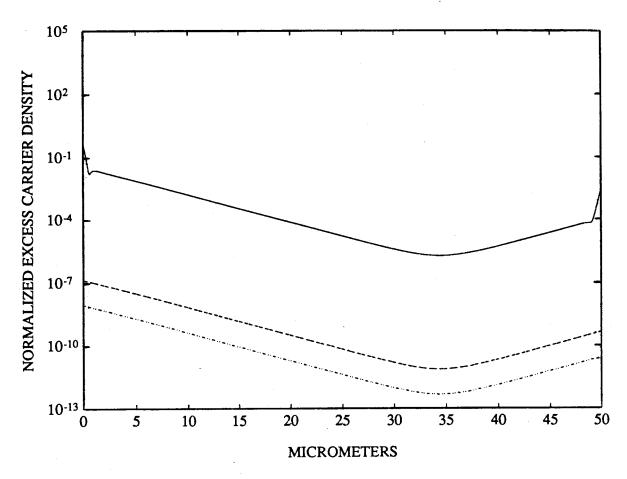

| 3.20 | Concentration profile of trapped and free excess carriers in the $20\mu m$ long model structure. The solid line corresponds to trapped carriers, dashed line to electrons, and dashdots to holes. The carrier densities are normalized to the equilibrium electron concentration The sidegate voltage is $-5V$ , the equilibrium electron concentration is $\approx 7 \times 10^6 \ cm^{-3}$ , the equilibrium hole concentration is $\approx 2 \times 10^5 \ cm^{-3}$ , the electron mobility is $4 \times 10^3 \ cm^2/V \ sec$ , the hole mobility is $400 \ cm^2/V \ sec$ , and the lifetime is $1 \ nsec$ . EL2 is assumed to be $0.75 \ eV$ from the conduction band, its density $10^{16} \ cm^{-3}$ , and the ratio of its capture cross sections for holes and electrons $10^{-3}$ . The recombination center is assumed to be $0.65 \ eV$ from the conduction band, with density $10^{15} \ cm^{-3}$ , and the ratio of its capture cross sections $100 \ eV$ | 40 |

| 3.21 | Concentration profile of trapped excess carriers as in Fig. 3.20, but only in the vicinity of hole injecting edge (x=0). The charge profile changes polarity at around $0.4\mu m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41 |

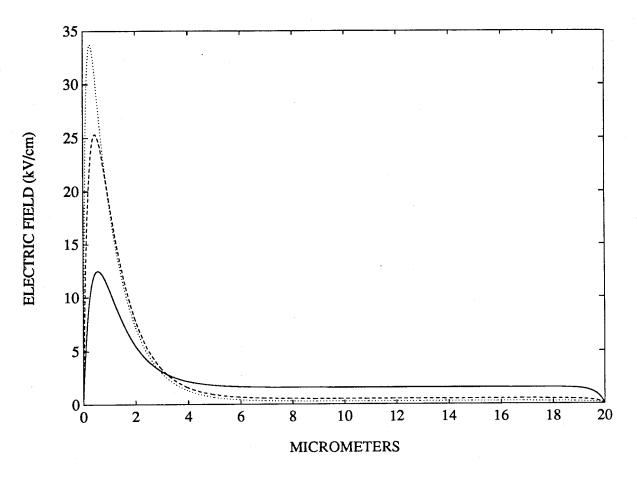

| 3.22 | Electric field profile in the investigated structure with the same parameters as in Fig. 3.20, but for different densities of recombination centers: dots correspond to $10^{16}$ cm <sup>-3</sup> , dashed line to $10^{15}$ cm <sup>-3</sup> , and solid line to $10^{14}$ cm <sup>-3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42 |

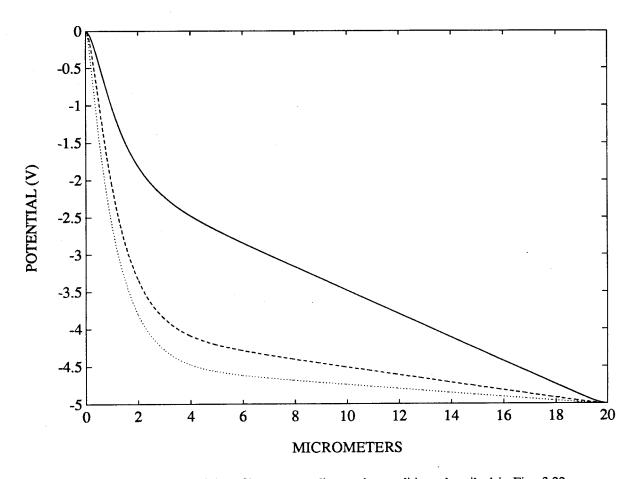

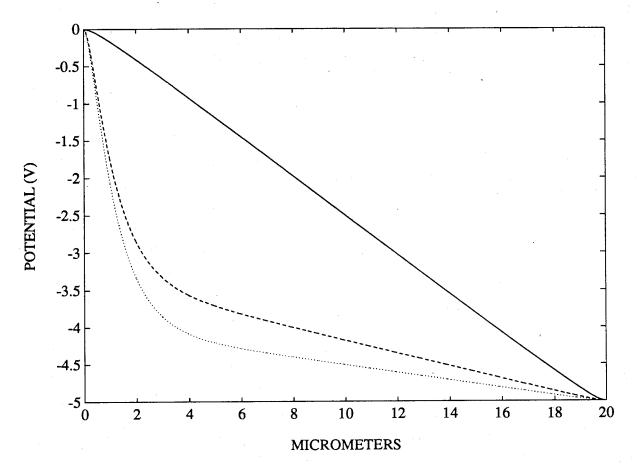

| 3.23 | Potential profile corresponding to the conditions described in Fig. 3.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |

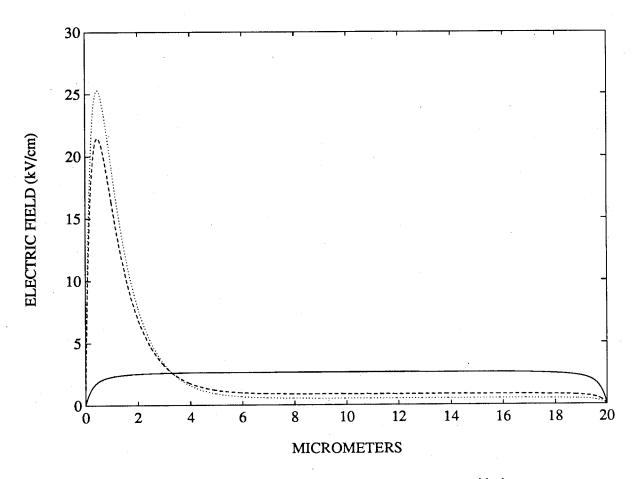

|      | Electric field profile in the investigated structure with the same parameters as in Fig. 3.20, but for different values of the minority carrier injection $(\eta)$ : dots correspond to $\eta=1$ , dashed line to 0.5, and solid line to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 3.25 | Potential profile corresponding to the conditions described in Fig. 3.24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45 |

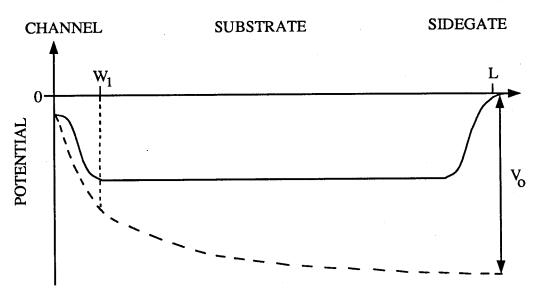

| 3.26 | Schematic superimposition of the potential profile across the investigated structure in the presence of a sidegate voltage $V_0$ (dashed line), and for zero applied voltage (solid line). $W_1$ designates the width of the substrate-channel depletion layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46 |

| 3.27 | Drain (solid line), gate (circles), and sidegate (asterisks) currents vs. sidegate voltage $(V_D = 2V, V_G = 0V)$ . The gate current changes its polarity at about $-3V$ . The gate and sidegate currents coincide at the voltages more negative than $\approx -8V$                                                                                                                                                                                                                             | 51 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

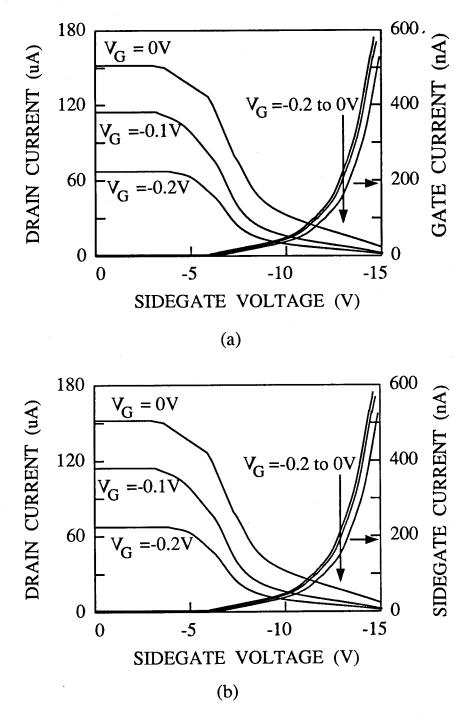

| 3.28 | Channel punch-through in low pinch-off GaAs MESFETs $(V_D = 2V, V_G: 0V \text{ to } -0.2V)$ : (a) gate current increases rapidly when a MESFET is nearly pinched off as a result of applying a negative sidegate voltage. (b) the corresponding sidegate current                                                                                                                                                                                                                                | 52 |

|      | Hole injection and a corresponding energy-band diagram for a (a) quasi-neutral MESFET, (b) MESFET with a large negative sidegate voltage applied. The combination of the inversion layer, n-channel and semi-insulating substrate creates a P-N-P looks like structure.                                                                                                                                                                                                                         | 54 |

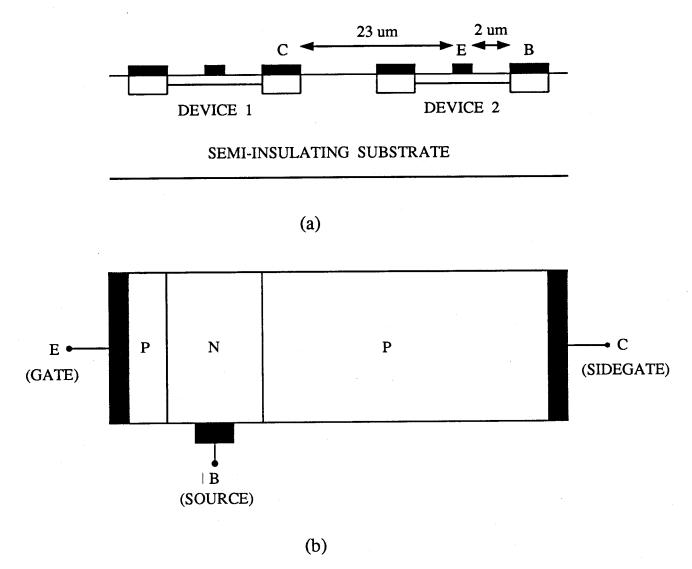

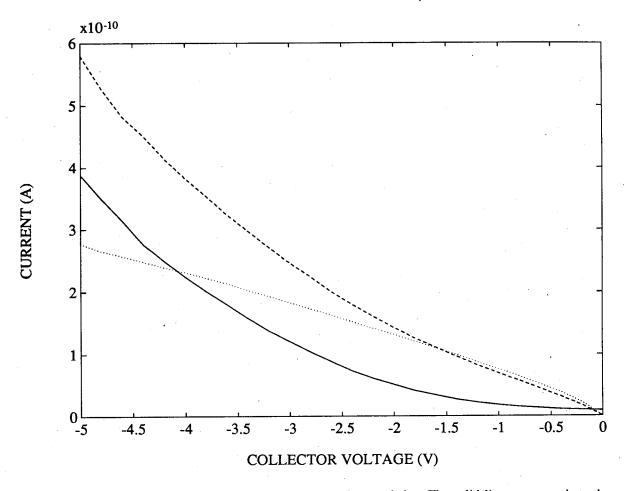

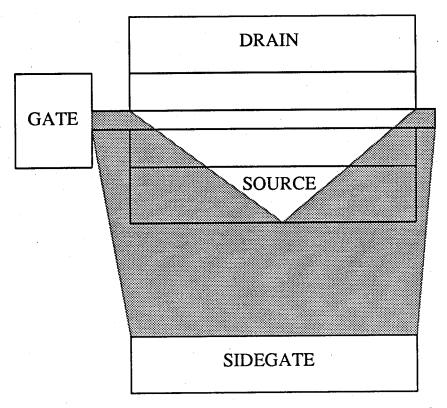

| 3.30 | (a) Cross section of the investigated three-terminal structure consisting of two MESFETs. Using a Schottky (gate) and an ohmic contact (source/drain) of one MESFET together with an ohmic contact of the other MESFET, the structure acts as a surface-barrier transistor with a gate operating as an emitter. (b) An equivalent bipolar transistor structure with a long collector region                                                                                                     | 55 |

| 3.31 | Measured currents vs. collector voltage characteristics. The solid line corresponds to the emitter (gate) current $I_E$ and the dashed line to the collector (sidegate) current $I_C$ . The leakage current $I_L$ (designated by dots) is the current between base and collector when the emitter is floating                                                                                                                                                                                   | 56 |

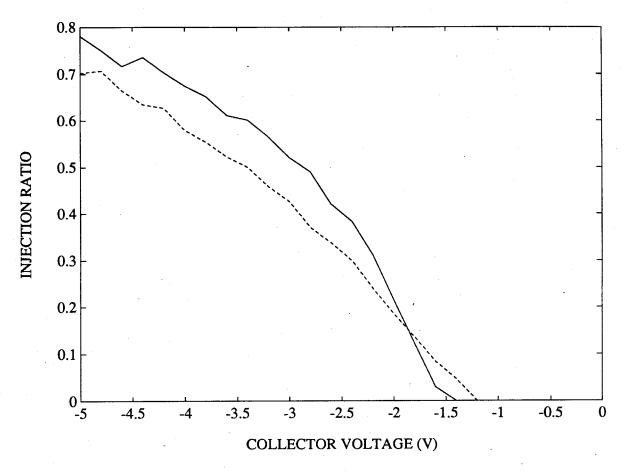

| 3.32 | Calculated hole injection ratio, defined as $(I_C - I_L)/I_E$ , for the emitter-base bias of 0.1 V (solid line) and 0.2 V (dashed line). $I_E, I_C$ and $I_L$ are defined in caption of Fig. 3.31                                                                                                                                                                                                                                                                                               | 57 |

| 3.33 | Schematic layout of the mirror-image structure of two MESFETs that were used in the sidegating measurements. The channel width, gate length, gate-source and gate-drain spacings were 4 $\mu$ m, 1 $\mu$ m, 2 $\mu$ m and 2 $\mu$ m respectively. The dotted area is the active layer area of the MESFETs. When one of the MESFETs was biased, the other's ohmic contact served as a sidegate. The sidegate was 8 $\mu$ m from the source and 23 $\mu$ m from the gate                          | 60 |

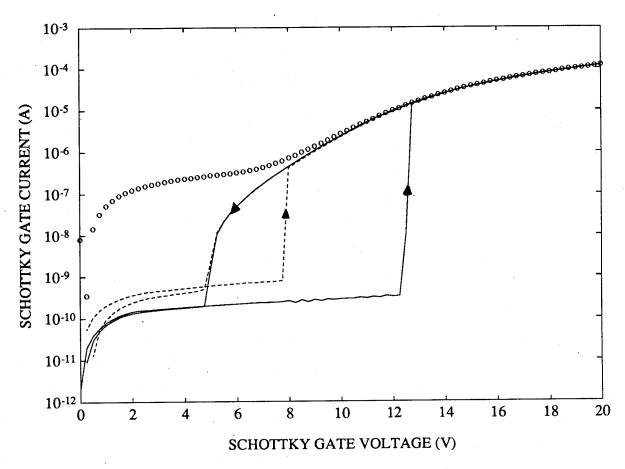

| 3.34 | Drain, gate and sidegate currents as a function of sidegate voltage $(V_D = 2V, V_G = 0V)$                                                                                                                                                                                                                                                                                                                                                                                                      | 61 |

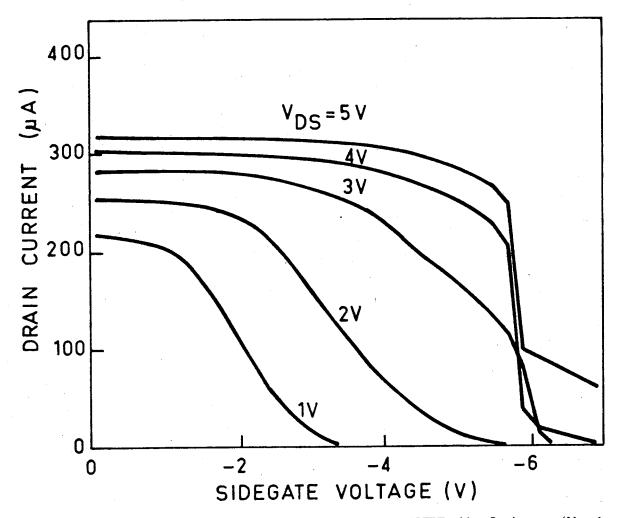

| 3.35 | Drain current versus sidegate voltage for a MESFET with a floating gate $(V_D: 1-5V)$                                                                                                                                                                                                                                                                                                                                                                                                           | 62 |

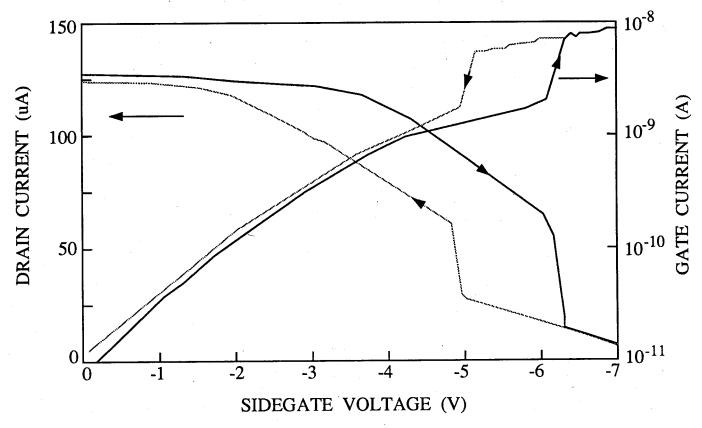

| 3.36 | Hysteresis in the drain current $(V_D = 2V, V_G = 0V)$ , and in the gate-sidegate current (source and drain are floating). The solid line represents a decreasing (more negative) sidegate voltage, while the dotted line represents the opposite direction                                                                                                                                                                                                                                     | 63 |

| 3.37 | Schematic energy-band diagram of a MESFET gate on a SI substrate                                                                                                                                                                                                                                                                                                                                                                                                                                | 65 |

| 3.38 | Hysteresis in the gate-sidegate structures under increasing illumination $(V_{SG}=0V, \text{drain} \text{ and source are floating})$ . The solid line corresponds to the data obtained in the dark, dashed line corresponds to the data obtained with room lights, and the open circles correspond to the data obtained under microscope lamp illumination. Results obtained in the dark or with room lights show hysteresis, while those obtained under direct illumination show no hysteresis | 68 |

| 3.39 | Schematic top view of the area (designated by gray pattern) that is affected by hole injection from the gate on a SI substrate                                                                                                                                                                                                                                                                                                                                                                  | 69 |

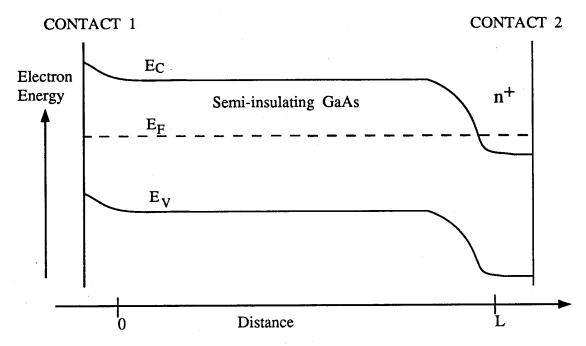

| 4.40 | Schematic equilibrium band diagram of the semi-insulating structure of a length L between zero-field points in the vicinity of $N^+$ and Schottky contacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

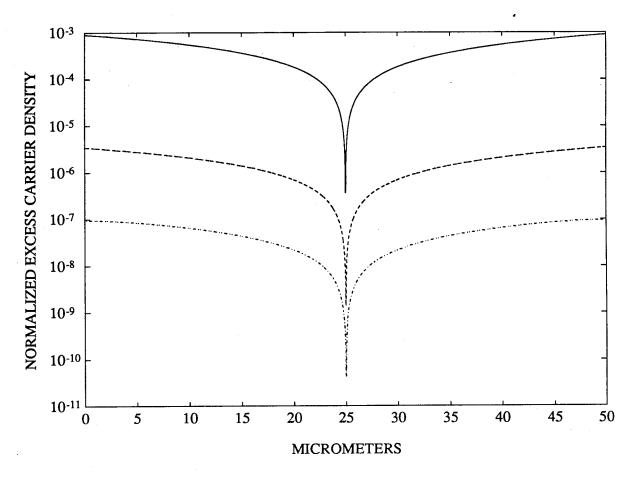

| 4.41 | Concentration profile of excess trapped and free carriers in the $50\mu m$ long model structure at 1Hz with no hole injection ( $\eta$ =0). The solid line corresponds to trapped carriers, dashed line to electrons, and dots to holes. The amplitude of AC applied voltage is $50 mV$ , the equilibrium electron concentration is $\approx 7 \times 10^6 \ cm^{-3}$ , the equilibrium hole concentration is $\approx 2 \times 10^5 \ cm^{-3}$ , the electron mobility is $4 \times 10^3 \ cm^2/V \ sec$ , the hole mobility is $400 \ cm^2/V \ sec$ , and the lifetime is $10 \ nsec$ . The deep donor is assumed to be $0.75 eV$ from the conduction band, its density $2 \times 10^{16} \ cm^{-3}$ , and with the capture cross section of $1 \times 10^{-13} \ cm^2$ for electrons and $1 \times 10^{-16} \ cm^2$ for holes. The deep acceptor is assumed to be $0.65 eV$ from the conduction band, with density $5 \times 10^{15} \ cm^{-3}$ , and with the capture cross section of $1 \times 10^{-13} \ cm^2$ for holes and $1 \times 10^{-16} \ cm^2$ for electrons | 75 |

| 4.42 | Concentration profile of trapped and free excess carriers at 1MHz with no hole injection. The rest of the parameters are given in Fig. 4.41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76 |

| 4.43 | Concentration profile of trapped and free excess carriers at 1Hz in the presence of hole injection $(\eta=1)$ . The rest of the parameters are given in Fig. 4.41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77 |

| 4.44 | Concentration profile of trapped and free excess carriers at 1MHz in the presence of hole injection $(\eta=1)$ . The rest of the parameters are given in Fig. 4.41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 78 |

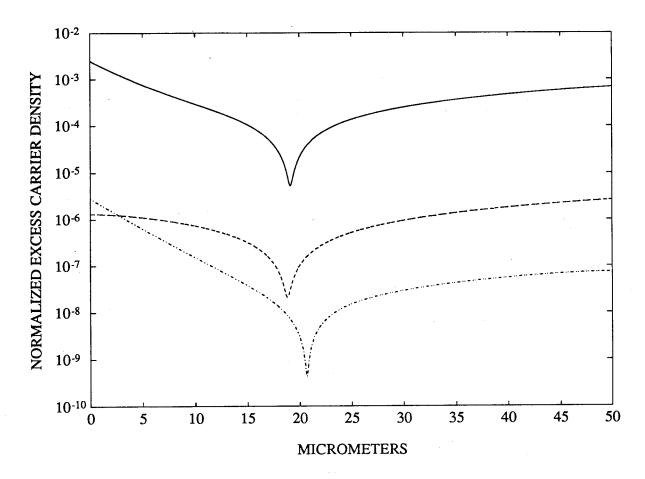

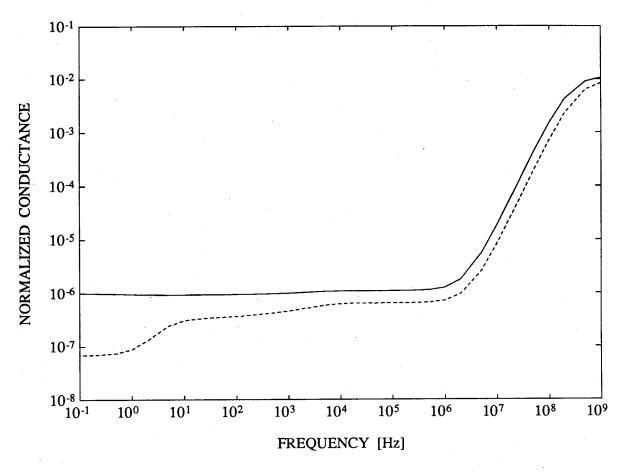

| 4.45 | Frequency dependence of the conductance of the SI structure calculated using eq. (4.64). The dashed line corresponds to the conductance in the presence of hole injection ( $\eta$ =1) and the solid line to the conductance when no hole injection occurs ( $\eta$ =0). The rest of the parameters are given in Fig. 4.41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79 |

| 4.46 | Frequency dependence of the capacitance of the SI structure calculated using eq. (4.64). The dashed line corresponds to the capacitance in the presence of hole injection ( $\eta$ =1) and the solid line to the capacitance when no hole injection occurs ( $\eta$ =0). The rest of the parameters are given in Fig. 4.41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80 |

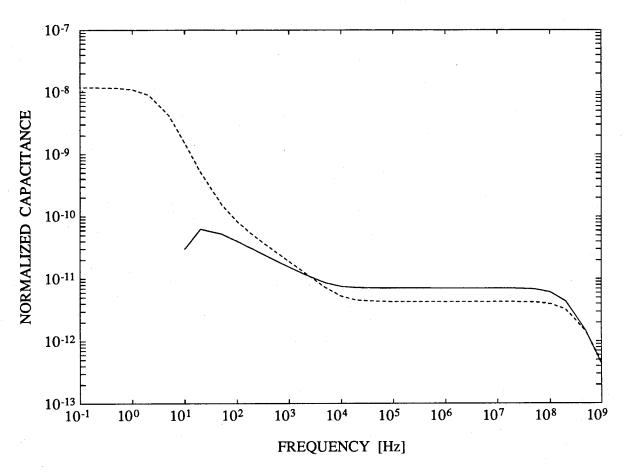

| 5.47 | Schematic cross section of a MESFET and an AC potential profile across the drain-substrate-source region. LF corresponds to the profile at low frequencies, HF at high frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 86 |

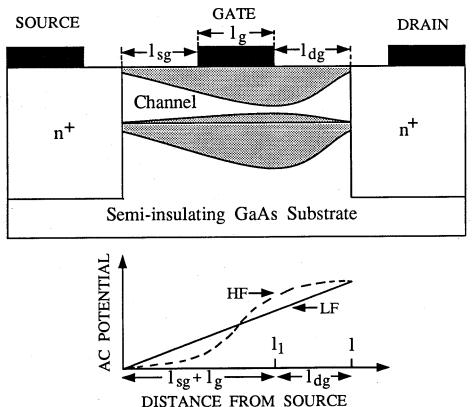

| 5.48 | Small-signal equivalent circuit of a GaAs MESFET at low frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89 |

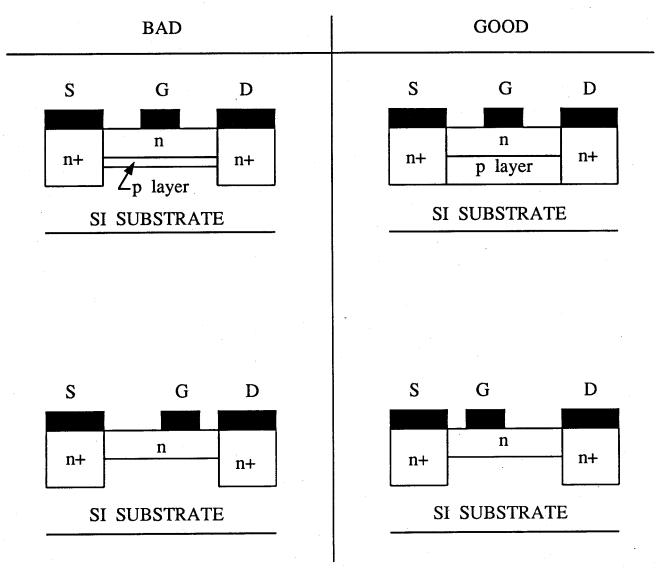

| 5.49 | The impact of the device structure on the frequency dependence of the output admittance. The first row shows MESFETs with a p-type buried layer. A deep p layer reduces the frequency dependence, while a shallow p layer may increase it. The second row shows the effect of the gate location on the frequency-dependent output admittance: placing gate closer to the source enhances the frequency dependence, while placing it closer to the source may reduce the effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91 |

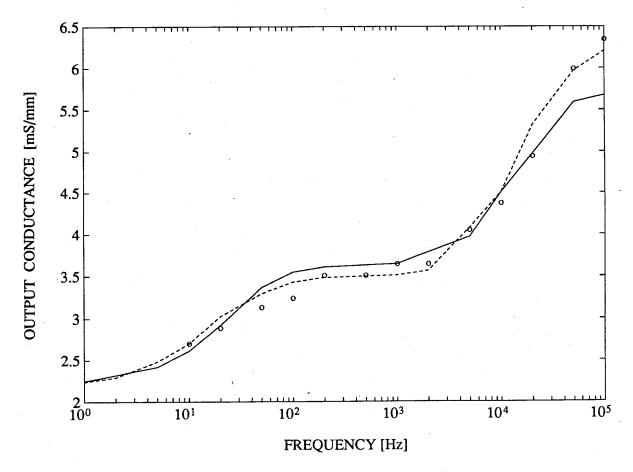

| 5.50 | Drain conductance vs. frequency. Results of the present model (solid line) are superimposed on numerical results (dashed line) [7], and experimental data (circles) [20]. Parameters used: T = 300 K, $N_D = 10^{17} cm^{-3}$ , $N_A = 6 \times 10^{15} cm^{-3}$ , $V_{DS} = 2.5V$ , $V_{DST} = 1.45V$ , $l_{sg} = l_{dg} = 1 \mu m$ , $l = 1.2 \mu m$ , $n_e \approx 7 \times 10^7 cm^{-3}$ , $p_e \approx 10^5 cm^{-3}$ , for trap at 0.69 eV; $N_1 = 5 \times 10^{16} cm^{-3}$ , $\sigma_{n1} = 2 \times 10^{-14} cm^2$ , $\sigma_{p1} = 2 \times 10^{-18} cm^2$ , for trap at 0.5 eV; $N_2 = 5 \times 10^{15} cm^{-3}$ , $\sigma_{n2} = 5 \times 10^{-13} cm^2$ , $\sigma_{p2} = 5 \times 10^{-17} cm^2$                                                                                                                                                                                                                                                                                                                                                                 | 92 |

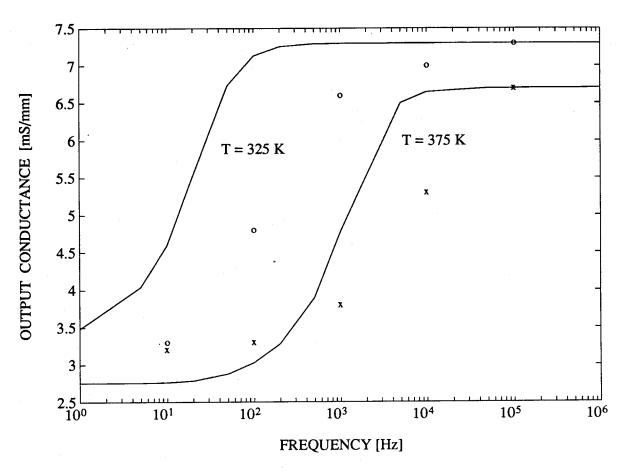

| 5.51 | Drain conductance vs. frequency at 325 K and 375 K. Results of the present                        |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | model (solid line) are superimposed on experimental data (circles and asterisks)                  |    |

|      | after Canfield et. al [4]. Parameters used: $N_{EL2} = 5 \times 10^{16} cm^{-3}, N_A =$           |    |

|      | $5 \times 10^{15} cm^{-3}$ , $l_{sg} = l_{dg} = l_g = 1 \mu m$ , $V_{DS} = 3V$ , $V_{DST} = 1.6V$ | 93 |

#### Glossary

MESFET — metal-semiconductor field-effect-transistor

SI — semi-insulating

VLSI - very-large-scale integration

LSI — large-scale integration

IC — integrated circuit

TFL — trap-filled-limit

SCL — space-charge-limited

MMIC — monolithic microwave integrated circuit

J — electric current density

I-V — current-voltage

DC — direct current

AC — alternate current

$\eta$  — minority carrier injection ratio

au — carrier lifetime

q — magnitude of the electronic charge

$\mu_n$  — electron mobility

$\mu_p$  — hole mobility

$n_e$  — equilibrium electron concentration

$\delta n$  — excess electron density

$p_e$  — equilibrium hole concentration

$\delta p$  — excess hole density

#### Acknowledgements

I would like to thank my supervisor Professor Lawrence Young for his help and support during the course of this work.

Kerry Lowe from BNR (Ottawa) is thanked for providing the test devices used in this research.

This work is dedicated to my parents.

#### Chapter 1

#### Introduction

In present GaAs technology, MESFETs are the only devices which have approached the VLSI level of integration. This is due to the simplicity of their fabrication: all we need is two ohmic contacts (source and drain) and a Schottky contact (gate) on a conductive layer (channel). However, with all its simplicity a MESFET exhibits numerous parasitic effects. This work is concerned with parasitic effects in GaAs MESFET integrated circuits, which hinder high-level integration.

The VLSI level of integration requires the fabrication of MESFETs on semi-insulating (SI) substrates, which makes the GaAs technology especially attractive because they reduce the interconnect capacitances and make device isolation simple. The MBE-grown buffer layers are currently too costly for use in the VLSI technology [1]. But the SI GaAs does not act as a mere mechanical support with high resistivity, and does allow leakage currents through the SI substrate between neighboring devices, as well as the leakage current between source and drain of each device. These currents originate effects which affect device performance. Rather than review these effects here, the reader is referred to the recently published text book on GaAs integrated circuits by Long and Butner [2]. In addition, there are review articles on the parasitic effects in GaAs integrated circuits by Rocchi [3] and more recently by Koyama et al. [4] and Salmon [5]. Many effects in GaAs MESFETs were investigated using the techniques that had already been developed for Si devices. But it is important to stress that there is a significant difference in the treatment of substrate effects in GaAs and Si devices. Probably the most fundamental difference is associated with the relaxation time in Si and SI GaAs substrates. While the relaxation time of a typical Si substrate is in the range of picoseconds, the relaxation time of a SI GaAs substrate is typically in the range of milliseconds-microseconds. This means that the charge injected into the bulk SI GaAs will not disappear as fast as in Si substrates. Consequently, the parasitic substrate effects will occur beyond the conventional silicon transistor bandwidth, but inside the bandwidth of GaAs MESFETs.

Additional parasitic effects are associated with a Schottky MESFET gate. It is interesting to note that Schottky junctions have never been used in the VLSI Si technology, and their most popular

usage found place in the earlier digital LSI technology (TTL). In comparison to p-n junctions many properties of Schottky junctions are much less understood. A Schottky gate is, however, an essential part of the GaAs MESFET technology, and, therefore, its contribution to the parasitic effects in GaAs MESFETs should be considered.

The major parasitic effect in GaAs integrated circuits is sidegating, the change in drain current as a result of applying a negative potential to a nearby contact (sidegate). The earlier attempts to explain this effect suggested electron injection into the device channel-substrate interface as the main source of sidegating [6]. This explanation was based on the one-dimensional Lampert's model of high-level carrier injection into the insulator with traps, according to which the current increases sharply at a certain threshold voltage [7]. Considering high trap densities in SI GaAs and typical distances between a MESFET and a sidegate, this model has difficulty in explaining the low voltages at which sidegating is often observed. To overcome this difficulty conduction through surface states was suggested [8, 9]. While some of the reported experimental results regarding sidegating could be explained in terms of surface conduction, there are many reports of sidegating in large-geometry devices and in layout arrangements in which the sidegating should have been greatly reduced if the surface had played a major role, but instead a strong effect was observed. According to the the recent review paper by Salmon, circuit manufacturers have developed processes, which control the surface properties, so that, "the surface component of backgating is negligible compared with the bulk backgating" [5].

Sidegating is a complicated phenomenon, in which several mechanisms of transferring charge into the vicinity of the MESFET channel may occur. In certain structures, and, depending on substrate properties, one of the mechanisms can prevail, but on the other hand some mechanisms can occur simultaneously. Fig. 1.1 visualizes some of the sources of parasitic effects in GaAs MESFETs on a SI substrate, that are discussed in this work.

Although the present work has focused on GaAs MESFETs, many of the results are applicable for other devices that incorporate SI material. MESFETs are used here as a probe of parasitic phenomena occurring in SI substrates. Being simpler than other GaAs-based transistors, they provide a tool for

#### SEMI-INSULATING SUBSTRATE

Figure 1.1: Sources of parasitic effects in GaAs MESFETs on a SI substrate. Lines 1-4 visualize interaction mechanisms between two MESFETs on a SI substrate, which can be sources of sidegating: 1-2 interaction between the source/drain to the sidegate, 3 interaction between the sidegate to the gate on a doped channel, 4 interaction between the sidegate to the portion of the gate on a SI substrate (the dashed line shows the edge of the active channel area). Line 5 shows drain-to-source leakage current, which contributes to the increase of an output conductance of a MESFET.

understanding of the interaction with the SI GaAs of more complicated devices such as HEMTs [10] and HBTs [11].

Although measurements by the author are reported throughout this work, the emphasis is not on the measurement techniques, but on the analysis and modeling of the experimental results. The reason for this is that many of the results in this work are similar to those reported by other research laboratories during the last decade. Since the general behavior of the device is known, the major task for researchers is the understanding and interpretation of this behavior. The emphasis was put on an analytical treatment, since it usually provides more insight into device physics than do numerical methods. The present state of the GaAs MESFET technology still requires understanding of the basic phenomena occurring in the integrated circuits, and, therefore, in my opinion, such analysis should precede, or at least be in parallel to, numerical analyses. For example, in order to simplify computation many numerical analyses of sidegating do not consider the continuity equation for holes, and thus eliminate from the discussion many effects predicted by the analytical analysis, which takes the participation of holes into account. An additional reason for analytical modeling is to make results useful for circuit designers by providing closed-form expressions through which a clear relationship is established between design goals and physical device parameters.

In Chapter 2 the experimental investigation and R-C network modeling of AC sidegating are reported. In Chapter 3 the sidegating under conditions of low-level injection into the SI substrate and the role of double injection in the sidegating effect are discussed. In Chapter 4 the extension of the low-level analysis to the frequency domain is presented. This frequency-domain analysis confirms and provides a new interpretation for the experimental results shown in Chapter 2. Chapter 5 shows how the frequency-domain analysis is applied to modeling of the frequency-dependent output conductance of GaAs MESFETs. Finally, conclusions are presented in Chapter 6.

#### Chapter 2

#### **AC** Sidegating

#### 2.1 Introduction

Crosstalk between GaAs MESFETs on SI GaAs substrates can severely affect device isolation and is a major obstacle to the miniaturization of GaAs integrated circuits. An important source of crosstalk is sidegating. Most reports of sidegating have been for DC conditions [12–14]. The results have been subject to different interpretations [12, 15, 8]. AC measurements and their analysis may provide a tool to decide which of various postulated mechanisms is currently occurring. Recently Chen et al. [16] addressed AC sidegating (at 40MHz and 2GHz). They concluded that it must be considered in designing GaAs monolithic microwave integrated circuits. Thus modeling of sidegating, which will predict at least the trends in device behavior, is needed in designing GaAs integrated circuits. The need to extend the investigation of sidegating to the frequency domain is further shown by the following.

As with silicon CMOS technology, in which the development of digital circuits was followed by the development of analog circuits, to provide an interface between the digital circuitry and the external world, the implementation of complex digital-analog systems on a GaAs single chip may soon be at issue. An understanding of the interaction between the analog and digital portions of the system will then be required. The investigation of this interaction is expected to be particularly troublesome at low frequencies, at which anomalies in GaAs monolithic MESFETs are observed. At high frequencies understanding crosstalk is important because of the tendency to combine microwave or RF circuits with their digital control circuits, e.g. RF switches with a driver circuit. Sidegating in GaAs digital integrated circuits has been investigated by applying a pulse train to the sidegate, but only the DC component of the pulse waveform has been considered [16, 17]. The effect, for example, of the pulse train repetition rate on sidegating has not been examined.

#### 2.2 AC Sidegating in GaAs n-i-n structures

MESFET interaction has usually been simulated by applying a negative potential to a sidegate contact on the semi-insulating GaAs substrate and examining its effect on a nearby device located on the same substrate, rather than having two MESFETs. According to the TFL model [12] sidegating is caused by electron injection into the channel-substrate interface of a MESFET and this process occurs due to the space-charge-limited conduction between the sidegate and the drain. Therefore, the sidegate-SI-drain interaction dominates sidegating, and, consequently, in the present section a simpler structure (n-SI-n) has been investigated, which avoids the complex electrical field distribution under the MESFET that otherwise complicates the analysis and the interpretation of the experimental results.

#### 2.2.1 Experimental Procedure

The measurements were performed on planar structures of ohmic contacts on semi-insulating GaAs substrates. Both the input contact, which represent the sidegate, and the output contact, which represent the drain, were  $n^+$  Si implanted directly into SI substrate. The two electrodes were separated by distances of 3  $\mu$ m to 450  $\mu$ m of semi-insulating material.

For measurement between 100Hz and 100kHz, the input of the sample was connected to a signal generator, while the output was connected to a Princeton Applied Research(PAR) 5204 lock-in analyzer via a PAR 113 low-noise amplifier, which was used in order to bring the signal to the level detectable by the lock-in analyzer.

A different experimental arrangement was used for measuring the sidegating between 500kHz and 500MHz: the sidegate was connected through a high frequency probe to the HP 8656 signal generator, while the output was connected through another high frequency probe to a HP 8558 spectrum analyzer.

Note that amplification of the signal in these two experimental set-ups is different. In the low-frequency set-up the voltage gain of the low-noise amplifier is set to  $2\times10^3$  and its input is shunted by a 150  $\Omega$  resistor. The output resistance of the amplifier is 600  $\Omega$  and it is connected to the PAR lock-in analyzer with an input impedance equivalent to a 1 M $\Omega$  resistor in parallel with a 30 pF capacitor. In the high-frequency set-up the output is connected to a 50  $\Omega$  input of the spectrum analyzer.

Figure 2.2: Signal attenuation at low frequencies for the  $20\mu m$  long structure (for sidegate voltage  $V_{SG}=-6V$ ) measured using the low-frequency measurement setup.

#### 2.2.2 Results

The measured signal attenuation through the semi-insulating substrate is plotted as a function of frequency for the range 100Hz - 100kHz in Fig. 2.2. The linear fit exhibits 20dB per decade change of the output signal level with frequency. The signal attenuation at low frequencies for structures with distances of  $3\mu\text{m}$  and  $14\mu\text{m}$  between the  $n^+$  contacts is plotted as function of a sidegate voltage in Figs. 2.3 and 2.4. The  $3\mu\text{m}$  long structure shows stronger sidegate voltage dependence than the  $10\mu\text{m}$  long structure at the same range of applied voltages. This effect becomes more pronounced for lower frequencies.

The measured RF signal attenuation is plotted vs. frequency for the range of 500kHz - 500MHz in Fig. 2.5. The output signal level increased 20dB per decade with frequency. Another set

Figure 2.3: Signal attenuation vs. negative sidegate voltage at 1kHz(pluses), 10kHz(x-marks), and 100kHz(circles) measured using the low-frequency measurement setup for  $3\mu$ m long structure.

of measurements (Fig. 2.6) at radio frequencies was performed on the structure with two contacts separated by 450  $\mu$ m.

#### 2.2.3 Discussion

Several mechanisms contribute to the crosstalk phenomena. For a given arrangement of conductors if the spacing is small, the electric and magnetic fields of the conductors will overlap sufficiently, so that a wave propagating in one of them will induce a wave in the others. Thus part of the AC sidegating is caused by the coupling between two metal pads through an air and a dielectric material [18, 19]. Capacitive coupling is of course directly proportional to the frequency and will increase 20dB per decade with it (see Figs 2.2 and 2.5).

Figure 2.4: Signal attenuation vs. negative sidegate voltage at 1kHz(pluses), 10kHz(x-marks), and 100kHz(circles) measured using the low-frequency measurement setup for  $14\mu m$  long structure.

Another mechanism contributing to the sidegating involves the conduction current through the insulating substrate with traps. At low voltages an ohmic current will be observed. With increasing applied voltage the injected carriers fill up the traps in the substrate and as the voltage reaches a certain threshold (trap-filled-limit voltage), at which all the traps are full, a steep rise in the current will occur [20]. According to Lee et al. [12] a trap-filled space-charge-limited current is observed in semi-insulating GaAs samples. The more detailed models of this phenomenon proposed by Lehovec et al. [21] and Horio et al. [22] suggest that the space-charge-limited current through the semi-insulating GaAs increases abruptly when the sidegate voltage exceeds a certain threshold and causes the substrate resistance to be reduced over a certain range of voltages. Avalanche breakdown [8] can also produce a threshold effect.

Figure 2.5: Signal attenuation at radio frequencies for the  $20\mu$ m long structure (for sidegate voltage  $V_{SG}=-6V$ ) measured using the high-frequency measurement setup.

However, the models proposed to explain the sidegating in semi-insulating GaAs concentrate on the investigation of DC current-voltage characteristics only. Semi-insulating GaAs is known to contain both electron and hole traps [23]. The dependence of the space-charge-limited conduction upon frequency is expected to be influenced by the effects of trapping [24, 25]. The frequency dependence arises from the finite time constant associated with the charging and discharging of the traps in semi-insulating GaAs. We will consider only one electron trap, commonly referred to as EL2, which is the most important trap in determining the properties of semi-insulating GaAs [26]. The trap filling can be analyzed using the Shockley-Read-Hall model for recombination through a single level, which, of course, neglects hot electron and field enhanced detrapping effects, which conceivably may be important in the present situation. The rate equation of the full traps on a single

Figure 2.6: Signal attenuation at radio frequencies for the  $450\mu m$  long structure (for sidegate voltage  $V_{SG}=-6V$ ) measured using the high-frequency measurement setup.

level is given by [27]:

$$N_T \frac{\mathrm{d}f}{\mathrm{d}t} = N_T[(c_n n + e_p)(1 - f) - (c_p p + e_n)f]; \tag{2.1}$$

where  $N_T$  = density of traps, f = fraction of traps occupied by electrons, n, p = electron and hole densities,  $e_n, e_p$  = emission rates for electrons and holes,  $c_n, c_p$  = capture probabilities for electron and holes

This equation can be simplified when the concentration of one carrier largely exceeds the concentration of the other. This is true for the single carrier high injection into the substrate. Furthermore, for EL2 the emission rates for electrons are much greater than that of the holes [28]. Next, we express the electron concentration around its steady state value:  $n(t) = n_0 + \Delta n(t)$ . Under

these conditions the trap filling equation reduces to:

$$\frac{\mathrm{d}n_T}{\mathrm{d}t} = -(n+n_1)c_n n_T + nc_n N_T

= -[n_0 + \Delta n(t) + n_1]c_n n_T + [n_0 + \Delta n(t)]c_n N_T;$$

(2.2)

where  $n_T = N_T f$ ,  $n_1$  = electron density if the Fermi level were at the trap energy level.

For small variations in electron concentration around its steady state value  $[n_0 \gg \Delta n(t)]$  the time constant associated with the traps is given by [29]:

$$\tau_s = 1/c_n(n_0 + n_1). (2.3)$$

Since the steady state electron concentration can be much greater than its equilibrium value the time constant associated with the small variations in electron density also can be much larger than the emission time constant in equilibrium. Under these conditions the time constant does not vary with time. However, it is important to stress that the electron density and consequently the time constant vary across the region between two electrodes. If the electron concentration is  $1 \times 10^{13}$ , using the equilibrium EL2 emission time constant given by [28], the time constant can be estimated to be about 20  $\mu$ s.

For large transient variations in electron concentration the exact solution of 2.2 is complicated. However, assuming  $n_0 \gg n_1$ , so that we can write  $n_0 \approx n_0 + n_1$ , which is true for high applied voltages or for traps lying below the Fermi level, the solution of equation 2.2 for  $\Delta n(t) = \Delta n_{max} \cos(wt)$  is given by:

$$n_T(t) = N_T + [n_T(0) - N_T] exp\{-c_n[(n_0 + n_1)t + \Delta n_{max} sin(wt)/w]\};$$

(2.4)

where  $n_T(0)$  = initial density of the full traps. The physical system corresponding to the eq. 2.4 is shown in Fig. 2.7.

Equation 2.4 allows an examination of the trap filling time and shows that it is frequency-dependent. At high frequencies the transient response of the traps is not affected by the variations in free electron density because  $\Delta n_{max}/w$  is small, but at low frequencies the variations in the free

Figure 2.7: Physical system corresponding to the differential equation 2.4 which is used for investigating frequency-dependent transients in SI GaAs. At t=0 the switch is closed and the DC biasing voltage  $V_0$  and the sinusoidal input V(t) are applied to a bar of SI GaAs, which is initially biased at  $V_i$ .

electron density are important in determining the transient response. For a very short period of time  $sin(wt) \approx wt$  and the time constant is given by:

$$\tau_0 = 1/c_n(n_0 + n_1 + \Delta n_{max}). \tag{2.5}$$