# MAPPING AND OPTIMIZING A SOFTWARE-ONLY REAL-TIME MPGE-2 VIDEO ENCODER ON VLIW ARCHITECTURES

by

#### **HENRY LEE**

B.A.Sc (Electrical and Computer Engineering)

University of British Columbia, 1997

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQURIEMENT FOR THE DEGREE OF MASTER OF APPLIED SCIENCE

in

## THE FACULTY OF GRADUATE STUDIES DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

We accept this thesis as conforming

to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

April 2000

© Henry Lee, 2000

In presenting this thesis in partial fulfillment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of Electrical and Computer Engineering

The University of British Columbia

Vancouver, Canada

Date:

#### **Abstract**

Due to its high computational demand, MPEG-2 video coding solutions have been based mainly on custom hardware (ASIC) systems. Such systems lack the flexibility and adaptability of software-based solutions. Achieving real-time MPEG-2 video encoding in software remains to be a major challenge. A typical MPEG-2 encoder performs 20 to 30 GOPS (giga operations per second), which exceeds the capabilities of the most advanced contemporary processors.

In this thesis, we have developed and tested a highly optimized, low complexity, highquality MPEG-2 video encoder software based on Texas Instruments' fixed-point TMS320C6201 VLIW (Very Long Instruction Word) processor. First, we developed MPEG-2 video encoder software written in C for the C62x processor platform, however, due to the difference in the processor architecture, optimization and modification are done on the software to ensure the MPEG-2 video encoder runs efficiently in the VLIW architecture. The optimization are done at the assembly language level to maximize the attainable instruction-level parallelism (ILP) of the C62x VLIW architecture. In our experience, optimizations done alone by the optimizing Ccompiler of the C62x could not meet the real-time requirements of MPEG-2. After code remapping and optimization, the resulting MPEG-2 video encoder implementation runs approximately 32 times faster than the original unoptimized MPEG-2 video encoder. Moreover, the current version of the encoder can handle SIF(320x240) video format at 16 frames per second with both I and P pictures, and CCIR-601 (720x480) at 15 frames per second for the I pictures only. Our real-time MPEG-2 encoder has been implemented and tested on the C62x Evaluation Model (EVM) board from TI.

### **Table of Contents**

| Abstract                                                                        | ii   |

|---------------------------------------------------------------------------------|------|

| Table of Contents                                                               | iii  |

| List of Tables                                                                  | vii  |

| List of Figures                                                                 | viii |

| Acknowledgments                                                                 | x    |

| Chapter 1 Introduction                                                          | 1    |

| Chapter 2 An Overview of VLIW Technology and Different Archite Video Processing |      |

| 2.1 Introduction                                                                | 5    |

| 2.2 Instruction-Level Parallelism (ILP) issues                                  | 7    |

| 2.2.1 ILP Hardware                                                              | 8    |

| 2.2.1.1 Superscalar Processors                                                  | 10   |

| 2.2.1.2 VLIW Processors                                                         | 11   |

| 2.2.2 The Use of VLIW in DSP Applications                                       | 14   |

| 2.3 Compiler-Architecture Technologies for VLIW                                 | 14   |

| 2.3.1 Trace Scheduling                                                          | 15   |

| 2.3.2 Loop Unrolling                                                            | 16   |

| 2.3.3 Software Pipelining                                                       | 18   |

| 2.4 Architectural Approaches for Programmable Processors                        | 20   |

| 2.4.1 SIMD                                                                      | 20   |

| 2.4.2 Split-ALU                                                                 | 22   |

| 2.4.3 VLIW                                                                      | 23   |

| 2.4.4 MIMD                                                                      | 24   |

| 2.4.5 Associative Controlling                                                   | 26   |

| 2.4.6 Specialized Instructions                                                  | 27   |

| 2.4.7 Coprocessor/Heterogeneous Multiprocessor                                  | 28   |

| 2.4.8 Memory System                                                      | 29 |

|--------------------------------------------------------------------------|----|

| Chapter 3 A Real-Time MPEG-2 Video Encoder                               | 31 |

| 3.1 Introduction                                                         | 31 |

| 3.2 Basics of Video Coding                                               | 31 |

| 3.2.1 Motion Estimation and Motion Compensation                          | 33 |

| 3.2.2 Transform Coding, Quantization and Variable Length Coding          | 37 |

| 3.3 The MPEG-2 Video Coding Standard                                     | 38 |

| 3.3.1 Bit Stream and Macroblock Layer                                    | 41 |

| 3.3.2 Baseline MPEG-2 Video Encoder                                      | 44 |

| 3.3.3 MPGE-2 Video Decoder                                               | 47 |

| 3.3.4 Forward and Inverse Quantization                                   | 48 |

| 3.3.5 VLC Coding of Transform Coefficients                               | 48 |

| 3.4 Proposed Software Solution for Real-Time MPEG-2 Video Encoder at UBC | 50 |

| 3.4.1 Motion Estimation (ME)                                             | 51 |

| 3.4.1.1 Optimum Fast Block Matching Strategy                             | 52 |

| 3.4.1.2 Hierarchical Block Matching Strategy                             | 53 |

| 3.4.1.3 Additional Stopping Criterion                                    | 54 |

| 3.4.1.4 The Optimum Block Matching Function                              | 54 |

| 3.4.1.5 Robust Motion Vector Prediction                                  | 56 |

| 3.4.2 Rate-Distortion Optimized Mode Selection                           | 57 |

| 3.4.3 Combination of Discrete Cosine Transform (DCT) and Quantization    | 58 |

| 3.5 Analysis of the proposed MPEG-2 video encoder                        | 58 |

| Chapter 4 Mapping the MPEG-2 Software Encoder on the Texas Instrument's  |    |

| TMS3206201 DSP Platform                                                  | 60 |

| 4.1 Introduction                                                         | 60 |

| 4.2 Texas Instrument's TMS320C6201 CPU Architecture                      | 61 |

| 4.2.1 VelociTI Principles                                                | 61 |

| 4.2.1.1 Parallelism                                                      | 61 |

| 4.2.1.2 Pipelining of Critical Speedpaths                                | 62 |

| 4.2.1.3 Reduced Instruction Set Computer (RISC)                         | 62 |

|-------------------------------------------------------------------------|----|

| 4.2.1.4 Load-Store Architecture                                         | 62 |

| 4.2.1.5 Orthogonality                                                   | 63 |

| 4.2.1.6 Determinism                                                     | 63 |

| 4.2.1.7 Conditional Instructions                                        | 63 |

| 4.2.1.8 Instruction Packing                                             | 63 |

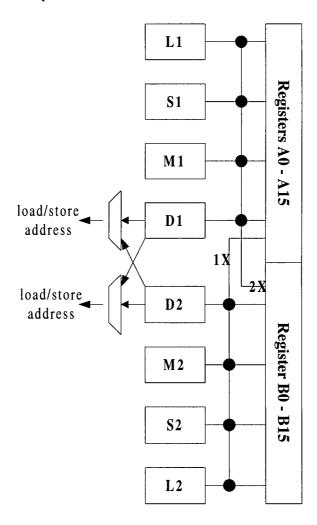

| 4.2.2 Data Paths                                                        | 63 |

| 4.2.2.1 Functional Units                                                | 65 |

| 4.2.2.2 Data Types                                                      | 65 |

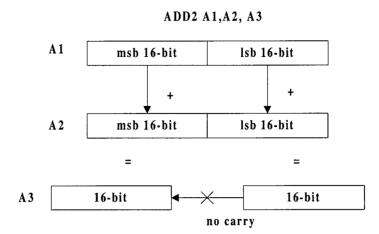

| 4.2.3 C62x Features and Instruction Set                                 | 66 |

| 4.2.3.1 Saturation Arithmetic                                           | 66 |

| 4.2.3.2 C62x Instruction Set                                            | 67 |

| 4.2.3.3 Instruction Packing                                             | 68 |

| 4.2.3.4 Conditional Instructions                                        | 69 |

| 4.2.4 Memory Architecture                                               | 69 |

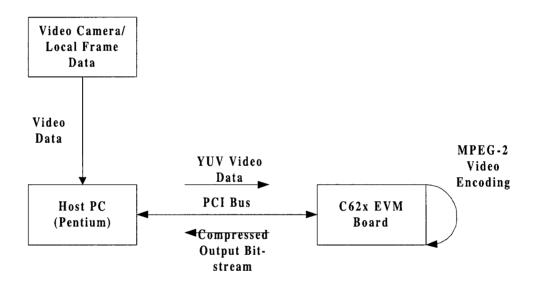

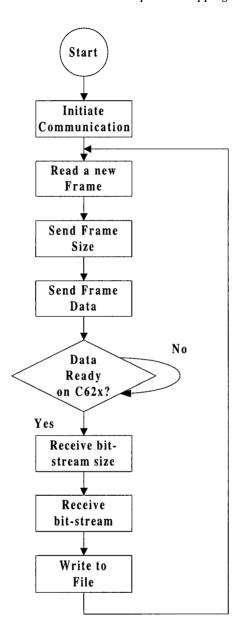

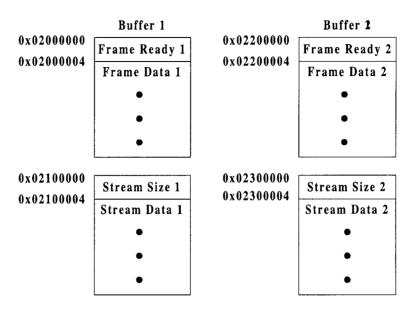

| 4.3 Memory Configuration and Host Interface of the MPEG-2 Video Encoder | 70 |

| 4.3.1 Video Encoder on the Host PC                                      | 72 |

| 4.3.2 MPEG-2 video encoder on C62x EVM board                            | 76 |

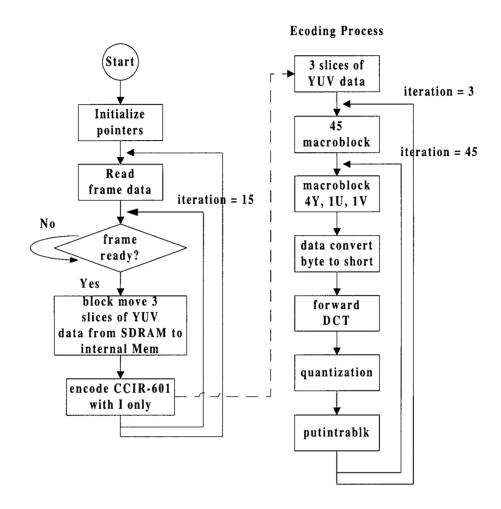

| 4.3.2.1 CCIR-601 resolution on C62x                                     | 77 |

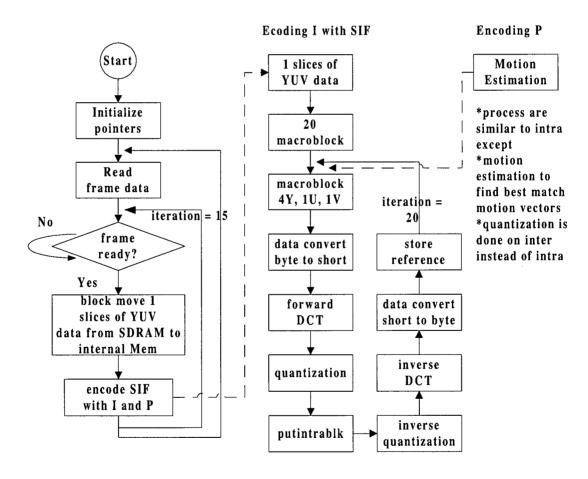

| 4.3.2.2 SIF resolution on C62x                                          | 79 |

| 4.4 Implementation Bottlenecks                                          | 84 |

| 4.4.1 Memory Issues                                                     | 85 |

| 4.4.2 Compiler Optimization Issues                                      |    |

| 4.4.3 Instruction Latency                                               | 86 |

| 4.4.4 Memory Bank Conflict                                              | 87 |

| Chapter 5 Optimized VLIW Algorithm for MPEG-2 Video Encoding            | 88 |

| 5.1 Introduction                                                        | 88 |

| 5.2 Optimizing SAD Computations for Motion Estimation                   | 89 |

| 5.2.1 First Approach of SAD Optimization                                | 89 |

| 5.2.2 Second Approach of SAD optimization              | 94  |

|--------------------------------------------------------|-----|

| 5.3 Quantization                                       | 95  |

| 5.4 Quantized Discrete Cosine Transform (QDCT)         | 98  |

| 5.5 Variable Length Coding (VLC)                       | 101 |

| 5.6 Mean Square Error (MSE)                            | 102 |

| 5.7 Putbit                                             | 102 |

| 5.8 Overall Performance Improvement of the Application | 103 |

| Chapter 6 Conclusion and Future Research               | 105 |

| Bibliography                                           | 107 |

| List of Acronyms                                       | 110 |

### **List of Tables**

| Table 1: | Constraint parameters at each level of a profile                                   | 40  |

|----------|------------------------------------------------------------------------------------|-----|

| Table 2: | Algorithms and functionalities supported with each profile                         | 41  |

| Table 3: | Relative computational costs of the most compute intensive tasks of the MPEG-2 vio | leo |

|          | encoder                                                                            | 59  |

| Table 4: | C62x functional units and subunits.                                                | 65  |

| Table 5: | Summaries the overall performance of video encoding components on different        |     |

|          | platforms with and without optimization                                            | 104 |

### **List of Figures**

| Figure 1: Example of finest-grained level of operations assigned to all functional units | 8  |

|------------------------------------------------------------------------------------------|----|

| Figure 2: Hardware enhancement for ILP.                                                  | 9  |

| Figure 3: Fundamental structure of a superscalar pipeline with degree of three           | 11 |

| Figure 4: Execution of VLIW processor instructions in a pipelined fashion                | 13 |

| Figure 5: An example of loop unrolling compiler technique.                               | 17 |

| Figure 6: Software pipelined loop execution.                                             | 19 |

| Figure 7: SIMD multiprocessor architecture                                               | 21 |

| Figure 8: Split-ALU implementation.                                                      | 22 |

| Figure 9: MIMD multiprocessor architecture.                                              | 25 |

| Figure 10: Associatively controlled multiprocessor.                                      | 26 |

| Figure 11: An example of coprocessor architecture.                                       | 28 |

| Figure 12: Generic hybrid video coder and decoder.                                       | 33 |

| Figure 13: Forward motion compensation.                                                  | 34 |

| Figure 14: Full search motion estimation process.                                        | 35 |

| Figure 15: Video sequences layer.                                                        | 42 |

| Figure 16: GOP of 12 frames.                                                             | 43 |

| Figure 17: MPEG-2 picture structure at CCIR 601 resolution                               | 44 |

| Figure 18: Block diagram of the MPEG-2 encoder.                                          | 45 |

| Figure 19: The half pixel motion estimation.                                             | 46 |

| Figure 20: Block diagram for the MPEG-2 decoder                                          | 47 |

| Figure 21: Zig-zag scan order of a 8x8 block.                                            | 49 |

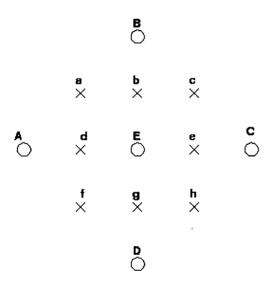

| Figure 22: (a) Fixed-center, (b) floating-center diamond shape motion vector search area | 52 |

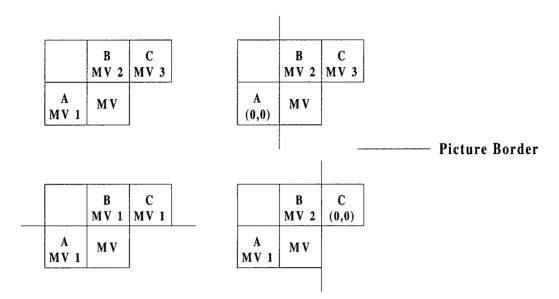

| Figure 23: Three predictor of motion vector prediction from surrounding macroblock       | 57 |

| Figure 24: C62x CPU data paths                                                           | 64 |

| Figure 25: ADD2 dual 16-bit pair arithmetic                                              | 68 |

| Figure 26: Software MPEG-2 video encoder over the C62x platform                          | 71 |

| Figure 27: Flow diagram of MPEG-2 video encoder on the Host PC                           | 73 |

| Figure 28: Dual buffer memory structure for the video encoder on the C62x EVM               | 76      |

|---------------------------------------------------------------------------------------------|---------|

| Figure 29: Flow diagram for the CCIR-601 resolution video encoder on C62x                   | 78      |

| Figure 30: Flow diagram of the MPEG-2 IP video encoder on C62x                              | 80      |

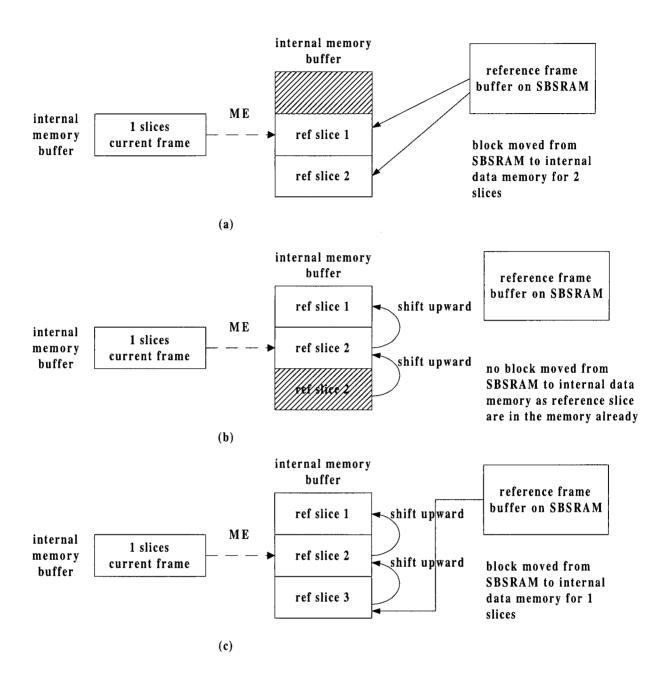

| Figure 31: Three different condition of the reference slices in the internal data memory: a | ) first |

| reference slice, b) last reference slice, c) all other slices                               | 82      |

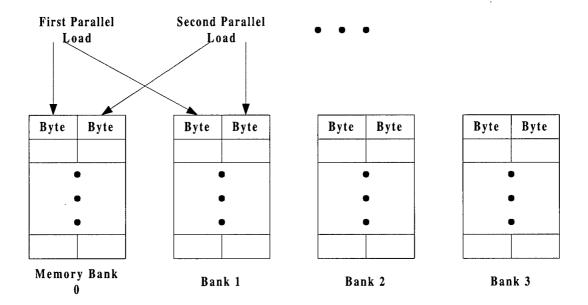

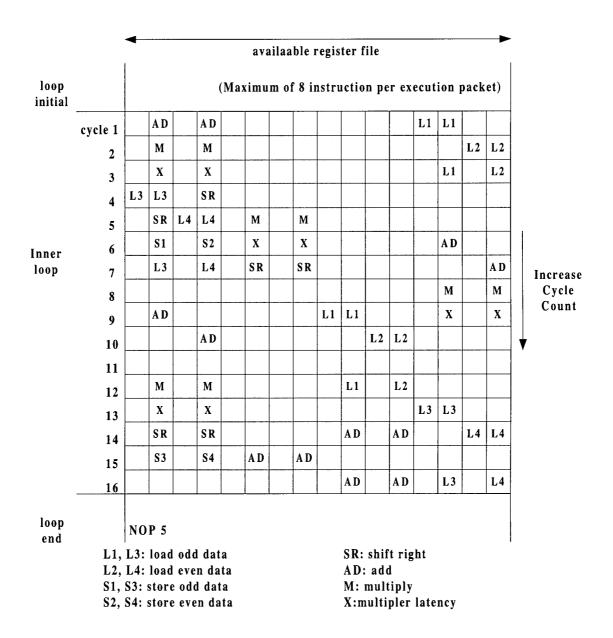

| Figure 32: Instruction scheduling of the first 16 SAD computation.                          | 91      |

| Figure 33: Avoiding memory bank conflicts by loading every second data from different       | memory  |

| banks                                                                                       | 93      |

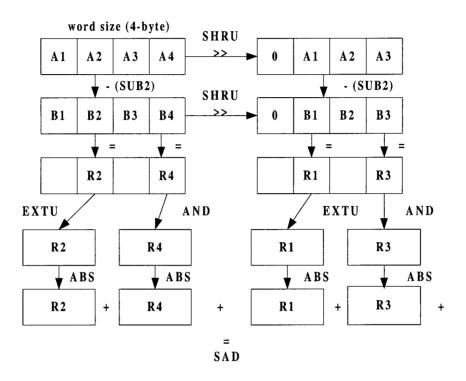

| Figure 34: Flowgraph of the SAD computation in VLIW implementation                          | 95      |

| Figure 35: Instruction scheduling for optimizing the quantization step computation          | 97      |

| Figure 36: Parallel execution of loads at the beginning and stores at the end.              | 100     |

| Figure 37: Sequential execution of load/store pairs.                                        | 100     |

#### Acknowledgments

First of all, I would like to thank my parents and my three elder brothers, for their great love and confidence in me, and for making my life easier during my heavy courses load and research work.

My research would not have become a reality without the very valuable supervision of Dr. Hussein Alnuweiri. The guidance and support are greatly appreciated.

I would like to thank my colleagues Don Hoi Ng and Joseph Chu for sharing their valuable technical knowledge with me. I also wish to express my gratitude to Dr. Faouzi Kossentini and Dr. Khanh Nguyen for the useful reference materials they has provided me and our research engineer Dr. Alen Docef for making our lives easier with his great technical support. Last but certainly not the least, I thank all my colleagues and friends for their invaluable friendship. This research was supported by a grant from the National Sciences and Engineering Research Council (NSERC) of Canada and by a grant Rogers Communications.

#### Chapter 1

#### Introduction

With the growing deployment and commercialization of the multimedia applications, comes the demand for higher performance to be offered to such applications at the lowest possible cost. Additionally, multimedia processing platforms must become more flexible and easily re-programmable to keep up with changing standards and application domains. Currently, video signal processing is the dominating task in terms of computational demands as well as amount of information bandwidth, unless compression technology is used. The wide demand for video coding applications have led to the development of video coding standards for video compression such as ISO/IEC MPEG-1 and MPEG-2. The required processing rate for video compression ranges from 100 mega operations per second (MOPS) to more than one tera operations per second (TOPS). For instances, the real-time MPEG-2 video decoding for National Television Systems Committee (NTSC) resolution requires more than 400 MOPS, while MPEG-2 video encoding can require up to 30 giga operations per second (GOPS) [1]. Such requirements are beyond the capabilities of contemporary microprocessors and have been satisfied mainly through the use of Application Specific Integrated Circuits (ASICs) technology only. However, this trend is changing with the advent of new fundamental algorithmic enhancements to video

encoding, and with the development of media-enhanced processors from various vendors such as the Visual Instruction Set (VIS) extension of Sun Microsystem's UltraSPARC [2], the MMX extension of Intel's Pentium processors, the MAX-2 extension of Hewlett-Packard's PA-RISC [3], and the Multimedia Instruction Set extensions of Silicon Graphics' microprocessor [4]. These enhancements have helped real-time video applications in software become reality.

Current solutions for real-time MPEG-2 video encoding and decoding are based principally on VLSI implementations such as the custom hardware (ASIC) systems. However, in order to make the implementations flexible and cost effective, migrating functionality from application specific hardware into software running on a programmable general-purpose processor or DSP start to gain great deal of interest. Recently developed microprocessors and programmable DSP chips offer powerful processing capabilities to do real-time video compression/decompression. These processors were designed with the target of realizing a software-implemented MPEG-2 encoder/decoder in real-time.

In this thesis, we have developed and tested a highly optimized, low complexity, high-quality MPEG-2 video encoder software that runs in real-time or near real-time on Texas Instruments' fixed-point TMS320C6201 VLIW (very long instruction word) processor. The high performance TMS320C6201 VLIW DSP processor was chosen among all the microprocessors and programmable DSP because it employs the VelociTI VLIW architecture [5]. Our encoder software is based on the encoder design by Dr.

Kossentini and others of the SPMG group at UBC. However, because of the distinctive features of the VLIW architecture, the original MPEG-2 video encoder software had to be remapped and modified substantially according to the memory and processor architecture of the targeted VLIW processor. The modifications and optimization have been applied mainly to the time consuming functions of the software, which include the DCT, IDCT, block matching (SAD), quantization, and variable length coding. Given the inefficiency of the optimizing C-compiler of the C62x, the optimization of most coder functions is mainly done at the assembly language level to maximize the attainable ILP (instruction level parallelism) of the C62x VLIW architecture. As a result of the assembly level optimization and the memory re-mapping the MPEG-2 video encoder runs approximately 32 times faster on the C62x than the unoptimized video encoder implementation. Moreover, the resulting MPEG-2 video encoder implementation can encode SIF video format at 16 frames per second with both I and P pictures, and I pictures only in CCIR-601 video format at 15 frames per second on the Texas Instrument's C62x Evaluation Model board. We believe that this is a big leap forward towards achieving real-time video encoding in software-only on a VLIW DSP processor.

This thesis is organized as the follows. Chapter 2 provides an overview of VLIW technology with the Instruction Level Parallelism (ILP) architecture and the related issues of the compiler technology of VLIW. Following the discussing of VLIW technology, the MPEG-2 video coding standard and the software solution for real-time MPEG-2 video encoder proposed by the SPMG group of UBC is discussed in chapter 3. Chapter 4 introduces the Texas Instrument's C62x VLIW architecture and provides some brief

information on its instruction set and memory structure. This chapter also describes the mapping issues of the MPEG-2 video encoder on the EVM and the memory configuration and host interface of the algorithms. In Chapter 5, the methodology of optimization of the software MPEG-2 video encoder is discussed along with some result comparison. Finally, conclusions for the real-time software MPEG-2 video encoder and suggestions for the future work towards the full feature real-time MPEG-2 video encoder are given in Chapter 6.

#### Chapter 2

# An Overview of VLIW Technology and Different Architecture Approaches for Video Processing

#### 2.1 Introduction

As stated earlier, the main objective of this thesis is to develop an efficient implementation of the MPEG-2 video encoder on the VLIW architecture. Therefore, a mutual understanding of the VLIW architecture and realizing the main differences among programmable multimedia processor architectures are needed. In this chapter, we first present the basic concepts of ILP. This is followed by a discussion of ILP architectures. A presentation of the compiler-architecture technology for the VLIW processors is given. The chapter then concludes with a discussion of the different architectural approaches to programmable processors, which are desirable for the implementation of video processing.

Traditional DSP-oriented chips were mainly built for inner-loop-oriented engines that acted as slave processors to a CPU, and let the CPU run the rest of the application and the operating system [6]. However, over the past two decades research on VLIW architectures has led to the development of stand alone DSP-oriented microprocessor

chips based on this concept. Additional advancements in the field of compiling and architecture technology has made it possible to write the actual compute-intensive loops as part of the whole application. As many of the emerging multimedia applications continuously change, programmable architectures that provide higher degree of flexibility and greater processing power became desirable. Recently, VLIW is one of the fastest growing architecture designs that fulfill high performance needs. The VLIW architecture has its concept aims at exploiting the instruction-level parallelism inherent in many multimedia algorithms to improve the performance. Multiple operations are specified within a single long instruction word for concurrent execution in every clock cycle. Hence, multiple parallel functional units are implemented in such a way that they can concurrently execute instructions. However, full utilization of the parallelism of the functional units is difficult to achieve and sustain, often resulting in the occurrence of idle resources at run time. Furthermore, compilers for DSPs have generally been unable to exploit the features of ILP architecture efficiently. As a result, a significant part of DSP applications has to be optimized manually at the assembly language level. Therefore, VLIW architectures have two major issues that must be addressed: one is the ILP issues and its architectures; and the other is the compiler-architecture interaction for VLIW.

On the other hand, the differences between architectural approaches for programmable processors must also be addressed, as the different architectural techniques applied would be able to increase the multimedia performance. By exploiting the differences of the architectural approaches, we would further understand the adequate/inadequate features of the current processor for handling multimedia

applications. The techniques can be divided mainly into parallelization strategies and adaptation strategies. For the parallelization strategy, it's done primarily on the data, instruction, and task levels, which can result in a considerable increase of computational power by achieving high level of concurrency of operations. The adaptation strategy increases the efficiency of an architecture by economical use of hardware resources.

#### 2.2 Instruction-Level Parallelism (ILP) issues

VLIW is a processor with a design philosophy similar to that of the reduced instruction set computer (RISC). A VLIW processor is basically a logical extension of the RISC processor, except it has more advanced features by adding ILP to a processor. As mentioned before, ILP is the key architectural technique employed by today's high-performance DSPs. ILP is a set of design techniques that speed up the programs by executing several RISC-style operations in parallel, such as memory loads and stores, integer additions, or multiplications. These operations execute single-cycle operations on hardware functional units, rather than performing parallel tasks. Only at the finest-grain level are these operations assigned to every possible function units such as adders and memory units at the same time as shown in Figure 1. Parallel execution occurs in every functional unit during a single-cycle of operation [7]. This parallelism is largely transparent to the user. However, advanced users may be well aware of its operation and may restructure the code or carry out other actions to enhance ILP. Distinguishing between the latent or available ILP inherent in a segment of code and the realizable or

achievable ILP provided by the hardware would be a key to maximizing the efficiency of the ILP architecture.

| ALU 1      | ALU 2      | MUL        | Data1       | Data2         | ALU 3        |

|------------|------------|------------|-------------|---------------|--------------|

| add r1, r2 | sub r3, r4 | mul r5, r6 | load r7, r8 | store r9, r10 | and r11, r12 |

\*all six functional units are assigned with operations

Figure 1: Example of finest-grained level of operations assigned to all functional units.

#### 2.2.1 ILP Hardware

Several different ways of hardware support are offered in ILP. For instances:

- more than one functional unit in a processor can execute concurrently,

- functional units with latency longer than one cycle can be pipelined,

- multiple functional units can access different register files to add register bandwidth for the purpose of parallel execution.

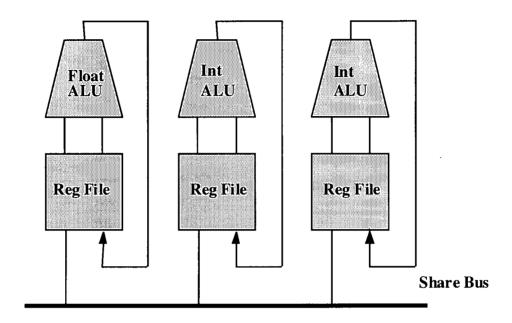

This hardware support enables the parallelization of the same RISC operations that are executed sequentially in the view of the programmer [8]. An example of the execution hardware enhanced to exploit potential ILP is depicted in Figure 2, assuming that the long instruction word execution takes place during a single-cycle. Having separate register banks for the integer and floating-point data can help reducing potential hardware resource conflicts. Also including extra integer units enables access to more than one integer operation per cycle.

Figure 2: Hardware enhancement for ILP.

Besides the execution hardware of an ILP processor, microprocessors have control hardware as well, which controls the flow of operations instead of carrying out the operations that contribute to the desired computation. There are mainly two types of architectures embodying the ILP methodology in modern microprocessor control units, and both can increase code performance by statically or dynamically scheduling parallel streams of single-cycle operations. The two types are: superscalar processors which employs dynamic instruction scheduling, and VLIW processors which employ static instruction scheduling. It should be noted that the pipelining structure of the two processor types is different.

#### 2.2.1.1 Superscalar Processors

In general, most general-purpose microprocessors embody a form of ILP called superscalar execution. However, the main difference between scalar and superscalar general-purpose processor is that the control hardware is much more complex for the latter processor type. Superscalar processors are designed to exploit more ILP in user programs. Only independent instructions can be executed in parallel without causing wait states. The amount of ILP varies widely depending on the type of code being executed. A superscalar processor fetches several RISC-level instructions from a scalar instruction stream and processes these instructions in parallel, all these decisions are made at the runtime. The control hardware of the processor checks the dependencies among the operations, reorders the instructions to take advantage of free function units or other resources, performs register renaming, then executes operations in parallel if possible; thus speeding up the computation [9]. This more complex hardware is often referred to as scheduling hardware. A superscalar processor is handed ordinary code, compiled for a sequential model of computation, and the scheduling hardware produces the ILP. For the superscalar type of architecture, a specific compiler is not required.

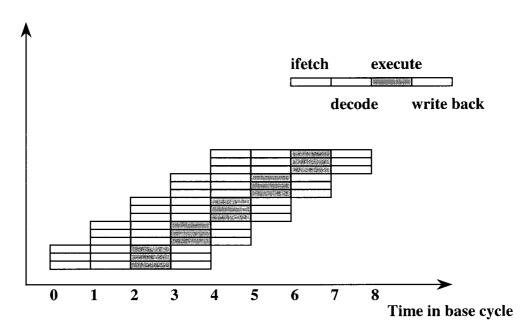

• Pipelining in Superscalar Processors: The fundamental structure of a superscalar pipeline is illustrated in Figure 3. The diagram shows the use of three instruction pipelines operating in parallel for a triple-issue superscalar processor. The superscalar processor shown below, of degree three, can issue up to three instructions per cycle, where the base scalar processor implemented either in RISC or CISC can only have a degree of one. To fully utilize a superscalar processor of degree three, three

instructions must be executable in parallel. However, this situation may not happen in all clock cycles. In that case, some of the pipelines may be stalling in a wait state. For most of the superscalar processors, the simple operation latency should require only one cycle. To achieve a higher degree of instruction-level parallelism in programs, the superscalar processor depends on an optimizing compiler to exploit ILP.

Figure 3: Fundamental structure of a superscalar pipeline with degree of three.

#### 2.2.1.2 VLIW Processors

The VLIW processors are in general very similar to superscalar processors in the sense that both processors use the same or similar execution hardware to achieve the ILP, except that the VLIW processors have extremely simple control units. A typical VLIW processor has instruction words hundreds of bits in length such as Texas Instruments' fixed-point TMS320C6201 VLIW processor is 256-bit long [10]. In a VLIW, it is the task of the compiler to determine the ILP and to schedule operations to run on multiple

functional units concurrently. All the functional units share the use of a common large register file and the operations to be simultaneously executed by the functional units are synchronized in a VLIW instruction. The compiler communicates the information about where, how, and when things are done via the program itself, by specifying directly in each cycle exactly what each function unit is to do, where it gets its data from, etc. Since this design philosophy mandates the simplest possible control hardware, it is common to put no-ops in each instruction corresponding to those functional units, making their task in that cycle explicit. However, inserting no-ops to all the unused functional unit leads to the problem of code size expansion. Coding size is especially critical issue for DSP applications. Furthermore, the static nature of scheduling has also led to a more complex compiler toolkit.

The immediate advantage of VLIW methodology is that both power consumption and silicon area are significantly reduced compared to an equivalent superscalar architecture. One drawback of traditional VLIW architectures is code expansion resulting from inserting the no-op operation into the unused functional units during a VLIW execution packet instruction cycle. Depending on the number of functional units, N, VLIW code expansion could theoretically increase the code size by as much as N times.

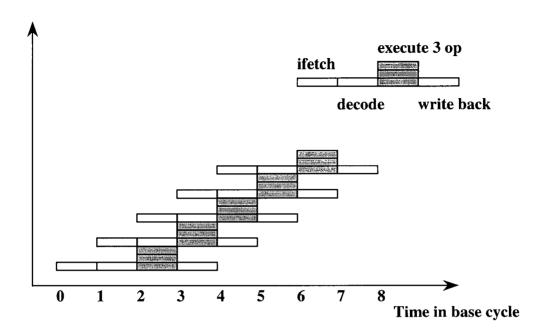

Pipelining in VLIW Processors: The execution of instructions by an ideal VLIW processor is shown in Figure 4, where each instruction specifies multiple operations.

Figure 4: Execution of VLIW processor instructions in a pipelined fashion.

VLIW processors behave much like superscalar processors except for the following three main differences:

- 1. VLIW instructions are much easier to decode than the superscalar instructions.

- 2. In terms of code density, the superscalar processor is better when the available ILP is less than that exploitable by the VLIW processor. This is due to the fixed VLIW format that includes bits for non-executable operations such as the no-ops described previously, while the superscalar processor issue only executable instructions.

- 3. A superscalar processor can be object-code-compatible with a large family of nonparallel processors. In contrast, a VLIW processor exploiting different amounts of parallelism would require different instruction sets.

#### 2.2.2 The Use of VLIW in DSP Applications

The extreme popularity of the use of VLIW architecture in the DSP world comes for several reasons. One of the most important reasons is the ability to take advantage of the abundant ILP that's available in typical DSP codes. However, the control hardware can become enormous when it must control large numbers of functional units. However, the major disadvantage of VLIW architecture as general-purpose microprocessor is the issue of object code compatibility. Programs for different VLIW are likely to be different, and thus the code must be recompiled for each processor architecture. The object code compatibility tends not to be an impediment in the DSP applications, since recompilation and unique hardware have been the norms. The relatively static flow of control in DSP and multimedia applications has made VLIW a good choice.

#### 2.3 Compiler-Architecture Technologies for VLIW

Compiling for VLIW DSP processors was done poorly for the past decade, and the only way to obtain an efficient coding was though the hand coding assembly. Clearly, a high-level language approach was much more desirable. Unfortunately, until 1980s, there were no approaches that matched, or even came close to, the performance that hand code could provide. The major barrier faced, even by experienced compiler writers, was that available practical compiler technology only enabled the scheduling of operations that come from single straight-line segments of code, called "basic blocks" by compiler writers. Whenever the compiler encountered a jump of any form, or even a branch target, the compiler would stop any further scheduling, declare that section done, and starts all

over with the next section. Unfortunately, there was little performance to be gained that way. If operations could somehow be moved globally between blocks rather then locally, far higher degrees of ILP would be available. Therefore, performance gains achieved with VLIW architectures will critically depend on the degree of exploitable instruction-level parallelism in the target algorithm as described previously. To maximize the pool of operations that can be scheduled into a single instruction word, sophisticated compiler techniques such as loop unrolling, software pipelining, trace scheduling, and guarded execution may be applied [11].

#### 2.3.1 Trace Scheduling

As the name of the scheduling algorithm states, trace scheduling is centered on traces [12]. The compiler mainly focuses on loop-free sequences of basic blocks embedded in the control flow graph rather than a single basic block. Traces are selected and scheduled in order of their frequency of execution. The selected trace is then scheduled as if it were a single basic block as giving no special consideration to branches. By scheduling the trace all at once, the compiler implicitly moves operations between blocks. After a given trace has been scheduled, the next most frequently executed trace is selected from among the remaining unscheduled operations, including those added in the process of scheduling earlier traces. This continues until the entire program has been scheduled.

The basic concept initiated by trace scheduling is to do the code motions implicitly as part of scheduling region, which is much larger than a basic block. Frequently in DSP and multimedia applications, the compiler is presented with a single

small loop. Hence, trace scheduling does not proceed beyond a back edge, there would be little opportunity for the compiler to do the global code motions that allow trace scheduling to be truly efficient. Trace scheduling compilers typically do a sophisticated job of turning a small piece of code into a long chain of blocks without back edges and without the artificial data dependencies that a naïve job of unrolling would introduce. Unrolling the loops can be very effective as will be discussed further in the following section. However, it also bring the problem of generating much extra code and sometimes loses performance because there is always a start up and close down delay at the beginning and the end of each series of unrolled iterations.

#### 2.3.2 Loop Unrolling

Loop unrolling can be a very effective compiler technique, as it replicates the original loop body multiple times, and adjusts the loop termination code and eliminates redundant branch instructions. The overhead of branching is significantly reduced with loop unrolling, especially when the latency of branching is large which is usually the case in most of the DSP architectures. This technique usually incorporates reduction of data dependencies to fully utilize the efficiency of loop unrolling. The resulting larger basic block increases the probability that the instruction scheduler can reorder instructions to exploit ILP [13]. Figure 5 shows an example of the compiler performing the loop unrolling technique. The initial iteration of the loop is 16 and the loop body is performed once every iteration. After performing loop unrolling, the compiler transform the loop iteration to four, and the loop body is executed four times every iteration. Given that

Chapter 2: An Overview of the VLIW technolog and Different Architecture Approaches unrolling the loop not only reduces the redundancy of branch instructions with long

latency, but also increases the probability of efficient pipeline scheduling.

```

int \ size = 16;

Before loop

byte out[size], in1[size], in2[size];

unrolling

for (i = 0; i < 16; i++)

out[i] = in1[i] + in2[i];

Code section for the loop

Cycle 0:

load\ t1\_0 = [in1 + i0]

body after unrolling the

load t1\_1 = [in1 + i1]

loop in the compiler

load t1_2 = [in1 + i2]

load t1 3 = [in1 + i3]

load \ t1\_0 = [in2 + i0]

cycle 1:

load \ t1\_1 = [in2 + i1]

load t1\_2 = [in2 + i2]

load t1_3 = [in2 + i3]

cycle 2:

add\ t3\_0 = t1\_0,\ t2\_0

add\ t3\_1 = t1\_1,\ t2\_1

add\ t3\_2 = t1\_2,\ t2\_2

add\ t3\ 3 = t1\ 3,\ t2\ 3

cycle 3:

store [out + i0] = t3\_0

store [out + i1] = t3\_1

store [out + i2] = t3_2

store [out + i3] = t3 3

```

Figure 5: An example of loop unrolling compiler technique.

However, loop unrolling generates extra code and sometimes loses performance because the scheduler's effectiveness is limited by artificial dependencies created by loop unrolling's naïve reuse of registers and other data dependencies between instructions. Code size expansion tends to be a problem in most DSP processors, because the program memory size is very limited. Therefore, the level of loop unrolling must be compensated with the limited code size expansion.

#### 2.3.3 Software Pipelining

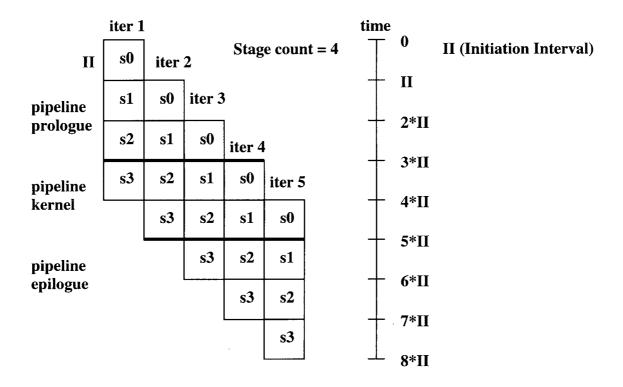

Software pipelining parallelize loops by starting new iterations before previous iterations complete. Successive iterations start at every initiation interval cycles. A single iteration's schedule can be divided into count stages, each consisting of initiation interval cycles. Figure 6 shows the execution of five iterations of a four-stage software pipelined loop. The three phases during execution of the loop are ramp up, steady state, and ramp down. The first stage count minus one cycle constitutes the ramp-up phase when not all stages of the software pipeline are executed. The steady-state portion begins with the last stage of the first iteration. During the steady-state phase, one iteration completes for every one that starts. The steady-state phase ends when the first stage of the last iteration has completed. For the final stage count minus one cycle is known as the ramp-down phase, one iteration completes every initiation interval cycle. The code generated for the three phases of the software pipelined loop are prologue, kernel, and epilogue [14].

Chapter 2: An Overview of the VLIW technolog and Different Architecture Approaches

Figure 6: Software pipelined loop execution.

Assume that without software pipelining every iteration takes N cycles to complete. With software pipelining, after the prologue, every new iteration takes one initiation interval cycle to complete. The speed up is a factor of N divided by initiation interval, when ignoring the overhead of the prologue. Scheduling the prologue and epilogue code in parallel with the code outside the loop would minimize this overhead. The overhead is insignificant for loops with large trip counts. Software pipelining works very efficiently for very simple loops and continuing research has broadened its applicability considerably.

#### 2.4 Architectural Approaches for Programmable Processors

In this section, various approaches are discussed that are widely employed to enhance the processing capability of programmable architectures for multimedia. Parallelization strategies are examined separately on data level (SIMD, split-ALU), instruction level (VLIW), and task level (MIMD, associative controlling). Adaptation strategies are divided into instruction set design modifications (specialized instructions) and the incorporation of dedicated hardware modules (coprocessors). Additionally, some remarks are given on the memory system design for programmable multimedia processors.

#### **2.4.1 SIMD**

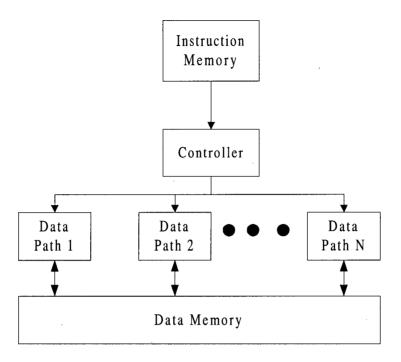

Data parallelism in image and video processing algorithms can efficiently be exploited by SIMD (single instruction stream, multiple data streams) architectures. In SIMD processors, a number of parallel data paths is centrally controlled by a global control unit. All data paths execute the same stream of instructions, but operate on different data items. To enable conditional operations, individual data paths can be excluded from the execution of single instructions by binary masking [9]. Figure 7 shows the basic structure of the SIMD architecture.

Chapter 2: An Overview of the VLIW technolog and Different Architecture Approaches

Figure 7: SIMD multiprocessor architecture.

As SIMD processors feature just a single control unit, the largest portion of available silicon area can actually be spent for the implementation of multiple data paths, leading to high degree of parallelism. However, the reduced control overhead is paid for by a lack of flexibility in case of more diverse computation requirements. While SIMD processors are highly efficient for algorithms with highly regular computation patterns, i.e., low-level tasks, utilization rapidly decreases for more irregular algorithms involving a higher portion of data-dependent processing. In consequence, pure SIMD architectures are not well suited for the implementation of complex processing schemes of heterogeneous nature as frequently encountered in multimedia applications.

#### 2.4.2 Split-ALU

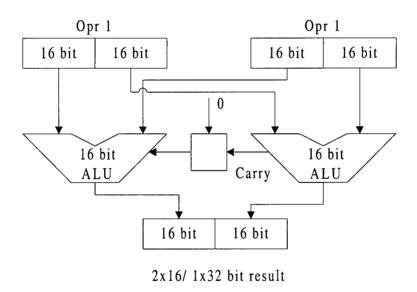

Based on a principle similar to SIMD, the split-ALU concept also targets data-level parallelism in multimedia applications. The concept, also referred to as subword parallelism, involves parallel processing of several lower-precision data item on a single ALU of higher word length: a 64-bit ALU, for example, can execute a single operation on eight 8-bit data items simultaneously [15]. The implementation of a split-ALU requires only minor hardware extensions — basically, the carry signals arising in arithmetic operations have to be prevented from being propagated across the boundaries of separate data items. A possible split-ALU implementation is shown in Figure 8.

Figure 8: Split-ALU implementation.

Similar to SIMD architecture, the main benefit from a split-ALU is obtained for highly regular low-level algorithms involving identical operations executed on large data volumes. In addition, the degree of exploitable data parallelism depends on the precision

required for an operation: with increasing word-length demands, fewer data items can be processed in parallel. Since image and video processing tasks mainly involve operations on low-precision (8-bit) pixel data, subword parallelism can effectively be exploited to enhance the performance for these computation types. By providing different split-ALU instructions for various data formats, the achievable parallelism can gradually scale with the precision requirements.

The small incremental hardware cost for a split-ALU makes this concept well suited for the extension of existing general-purpose processors with respect to multimedia processing. Typical operations to be executed in a split-ALU may include parallel addition/subtraction, multiplication, or compare. Furthermore, packing and unpacking operations have to be supported to enable a transition between conventional data words and packed subwords. As a drawback, split-ALU instructions are generally not supported by current compilers due to the lack of adequate high-level language constructs to express the desired operations. Moreover, complex code transformations usually become necessary before the packing of low-precision items into single long data words is enabled. Therefore, split-ALU instructions typically have to be inserted into the high-level language code manually by the programmer in form of intrinsic functions.

#### 2.4.3 VLIW

The VLIW processor architecture concept aims at exploiting the instruction-level parallelism. There are two types of VLIW processors. One is the VLIW processor with static mapping of the operations slots which relies on static operation scheduling at

instruction-level parallelism at runtime.

Performance gains achieved with VLIW architecture critically depend on the degree of exploitable instruction-level parallelism in the target algorithm. However, the performance limitations of VLIW processors may arise from the growing hardware expense for multiported register files and crossbar switches when the number of functional units increases. Moreover, compiler techniques like loop unrolling and trace scheduling lead to a heavy increase in code size. The already high bandwidth requirements for instruction supply are likely to worsen due to the growing gap between processor and I/O speed. This problem is addressed by compressing the instruction words in memory and expanding them for execution. Details were given in the previous sections.

#### 2.4.4 MIMD

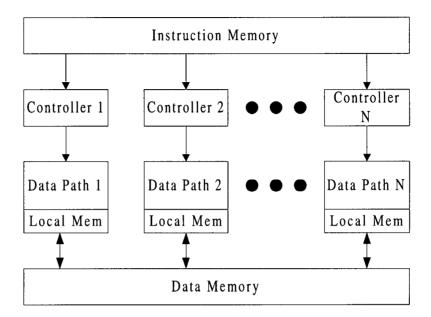

An approach exploiting parallelism on both data level and tasks level is given by the MIMD (multiple instruction streams, multiple data streams) architecture concept. In contrast to SIMD architectures, MIMD processors feature a private control unit for each single data path. Consequently, each data path is provided with its individual instruction stream, enabling concurrent execution of different programs or tasks. Likewise, by supplying several data paths with identical instruction streams, data parallelism can be targeted as well [16]. The MIMD multiprocessor concept is depicted in Figure 9.

Chapter 2: An Overview of the VLIW technolog and Different Architecture Approaches

Figure 9: MIMD multiprocessor architecture.

The major advantage of MIMD architectures is their high flexibility as each data path can be controlled individually. Therefore, MIMD architectures are typically better suited than SIMD architectures for the execution of compound multimedia processing schemes comprising low-, medium-, and high-level tasks. However, the duplication of control units and high-bandwidth requirements for a continuous supply of several instruction streams dramatically increase the hardware expense, thus limiting the number of data paths that can be economically implemented on a single chip. Furthermore, MIMD processors include poor programmability and lack of synchronization support. Typically, scalar programs have to be developed separately for individual data paths, and synchronization among processing elements has to be achieved manually by the programmer. The highly complex and time-consuming application development may be one reason for the non-popularity of the MIMD processors in multimedia processing.

#### 2.4.5 Associative Controlling

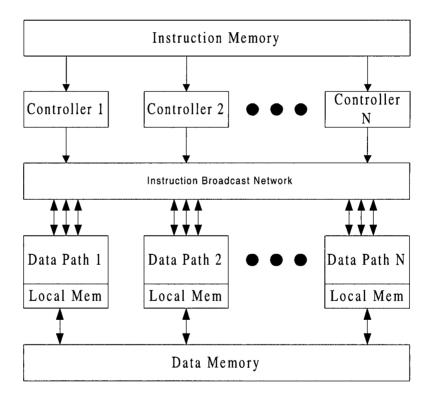

Associative controlling denotes a new concept for multiprocessor architectures aiming to prevent the typical drawbacks of both SIMD and MIMD processors in multimedia processing. The outstanding feature from the hardware point of view is a lower number of control units than parallel data paths. Therefore, in terms of hardware expense, an associatively controlled multiprocessor can be classified between SIMD and MIMD architectures [17]. Figure 10 gives a structural overview of an associatively controlled processor.

Figure 10: Associatively controlled multiprocessor.

The control units concurrently issue their individual instruction streams via an instruction broadcast network to all parallel data paths. Among the multiple instruction

streams offered, each data path autonomously selects an appropriate instruction stream for execution. In order to enable unambiguous identification, special signatures are assigned to the instruction streams and supplied to the data paths. Individual data paths can dynamically switch between different instruction streams offered by the control units. This enables, for example, an efficient execution of data-dependent control flow by simultaneously supplying the instructions of alternative branches following a decision to all data paths and letting each data path select the proper branch according to its local status. Moreover, an associatively controlled processor is able to adapt to varying parallelization degrees during computation by supporting a dynamic clustering of data paths. Issues to be further investigated include the possible area and power overhead for the distribution and selection of concurrent instruction streams and the necessary compiler support to assist software development for associatively controlled processors.

#### 2.4.6 Specialized Instructions

Programmable processors can be adapted to specific algorithms by introducing specialized instructions for frequently occurring operations of higher complexity. The use of specialized instructions reduces the instruction count and accelerates program execution [18]. For example, the use of a specialized MAC (multiply-accumulation) with saturation replacing a longer sequence of standard instructions including branches is very common in multimedia processing. Other examples of specialized instructions for multimedia include extended shift, minimum/maximum, average, and add-sign operations.

The incorporation of specialized instructions necessitates incremental hardware cost for additional function units such as a multiply\_add. However, the design complexity of additional units can usually be kept modest due to high specialization and optimization toward the targeted operations. The decision on which specialized instructions to implement involves a tradeoff between additionally required hardware effort and probability of their use. The benefit from specialized instructions is not universal, since only a subset of algorithms will experience an acceleration.

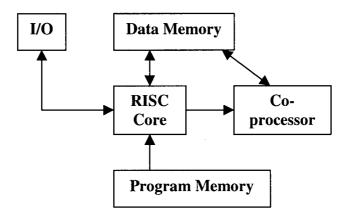

#### 2.4.7 Coprocessor/Heterogeneous Multiprocessor

Both parallelization and adaptation principles are combined within coprocessor/heterogeneous multiprocessor architectures. Coprocessor architectures for multimedia typically comprise a flexible general-purpose processing module, for instance, a standard RISC code performs high-level tasks of lower computational requirements as well as control and I/O functions, whereas the adapted module executes the computation-intensive but regular low-level tasks [19]. Figure 11 shows an example of a coprocessor architecture organization.

Figure 11: An example of coprocessor architecture.

Alternatively, specialized modules may also be employed for tasks of lower computational requirements, but with other special algorithm characteristics that make them difficult to implement on standard processors. The mixture of several programmable and dedicated modules results in a heterogeneous multiprocessor architecture, which can be seen as a generalization of the coprocessor concept. While heterogeneous multiprocessors allow us to reach higher performance levels by emphasizing parallel execution of several tasks, they are still more tied to a specific processing scheme than homogeneous multiprocessors due to the adaptation of individual modules.

#### 2.4.8 Memory System

As multimedia processing schemes operate on high data volumes, memory system design has a significant impact on the overall system performance. The streaming nature of multimedia data deviates radically from conventional data access patterns in general-purpose computing. Typical cache strategies employed in general-purpose processors rely on frequent accesses to the same data items, and thus offer little benefit for multimedia processing. However, particularly in the low-level parts of multimedia algorithms, memory access patterns are very predictable. Therefore, special stream caches have been proposed that employ prefetching techniques in order to access shortly needed data in advance [20].

In addition to the streaming multimedia data types, data structures of nonvolatile nature may also be involved in multimedia processing such as coefficient lookup tables.

When placed in cache, those data structures would be exposed to frequent replacement by the streaming data types. Therefore, the additional integration of software-controlled on-chip SRAM is advantageous where data are safe from being replaced and can always be accessed within the shortest time [21].

The performance of multimedia processing is also influenced by the instruction memory behavior. As typical for most signal processing applications, multimedia processing involves a limited set of tasks periodically executed on incoming data streams: the same set of instructions is repetitively fetched and executed. Therefore, conventional cache strategies may prove useful for speeding up instruction access, provided the cache is large enough and mutual code replacement can effectively be prevented. Code positioning schemes have been proposed that help to increase instruction cache performance in multimedia applications [22]. Instruction memory performance can further be enhanced by the integration of on-chip SRAM for the most heavily executed code parts, thus always guaranteeing fastest access without stall cycles due to cache misses.

# Chapter 3

### A Real-Time MPEG-2 Video Encoder

#### 3.1 Introduction

After realizing the basic architecture of VLIW processors and understanding the different approaches of programmable multimedia processors, the next crucial step is to obtain an efficient implementation of a real-time MPEG-2 video encoder. In this chapter, we first present the basic concepts of video coding. This is followed by a discussion of the MPEG-2 standards and the real-time implementation of the MPEG-2 video encoder proposed by our Signal Processing and Multimedia Group of UBC. This chapter concludes with an analysis of the proposed software solution for the real-time MPEG-2 video encoder.

# 3.2 Basics of Video Coding

In general, video sequences contain a significant amount of statistical and subjective redundancy within and between frames, i.e. video sequences usually contain statistical redundancies in both the temporal and spatial domains. Thus, the goal of video coding is to remove statistical and psychovisual redundancies in a video sequence while keeping intact as much perceptually important information as possible. Temporal redundancies normally exist due to structured motion and camera movement, while the spatial

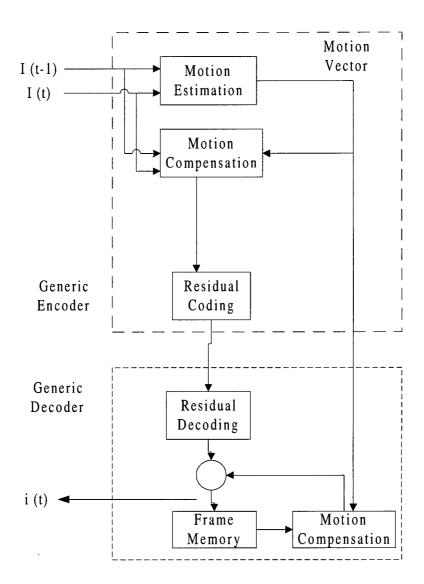

redundancies are normally due to the smoothness and edge continuity. Consequently, these two types of redundancies are efficiently reduced through employing the two well known compression schemes: inter-frame coding and intra-frame coding. Intra-frame compression reduces spatial redundancies within a video frame by employing transform coding as in still image coding, therefore, the frames can be encoded independently. This type of compression is ideal when the difference between two consecutive video frames is very large. Intra-coded pictures are also referred to as I-pictures in MPEG-2. Inter-frame compression takes advantage of temporal redundancies by coding the difference between a predicted frame and the current video frame instead of encoding the current frame itself. A forward predicted inter-frame is also referred to as a P-picture while a bi-directionally predicted inter-frame is referred to as a B-picture. The combination of intra and inter-frame coding is called hybrid coding [23]. The generic hybrid video coder is shown in Figure 12.

Figure 12: Generic hybrid video coder and decoder.

#### 3.2.1 Motion Estimation and Motion Compensation

In general, in order to achieve a good prediction of the picture currently being encoded, the motion of the objects in the video sequence must be considered. Since if the objects in present picture are well predicted from the previous picture, then the amount of information needed to be encoded is relatively small given that the difference between

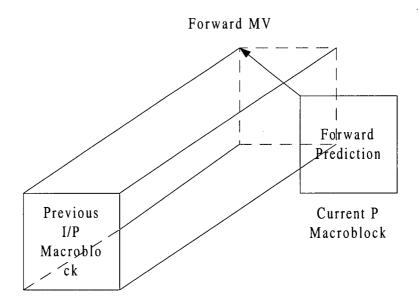

pictures is small. Therefore, the introduction of motion compensation (MC) is needed. Motion compensation is used to exploit the temporal redundancy inherent in moving pictures. It is used for the compression of P-pictures and B-pictures. The idea behind this is to reduce the information needed for the storage of the difference between the predicted block and the current block along with the motion vector associated with the current block, than would be required for storage of the current pixel data. Motion vector is the relative distance between the best-matched block in the previous picture and the current block. There are two distinct types of motion compensation. The first is called forward motion compensation, which is the result of coding a frame based on a previous frame in the actual temporal sequence. Figure 13 illustrates forward motion compensation. The other form is symmetric, using a subsequent frame in the sequence to act as a basis frame for prediction.

Figure 13: Forward motion compensation.

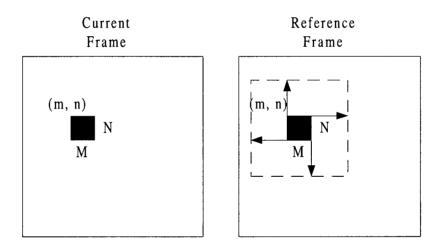

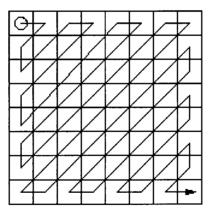

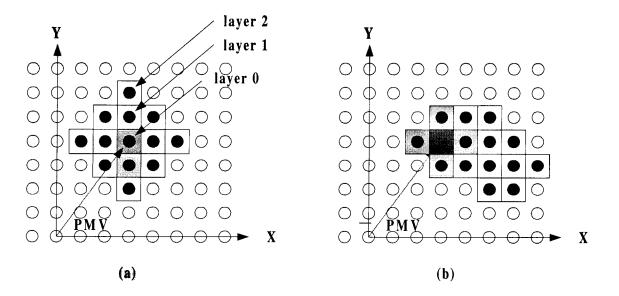

Block-base motion compensation is considered as one of the best approaches for eliminating temporal redundancies. Since in this method, the picture is divided into blocks with size M x M pixels each. For every individual block, the previous picture is searched for the best match block of the current picture. This searching process is called Motion Estimation (ME) as shown in figure 11 also. As we can see, the computation that searches for the best match block of the entire picture can be very expensive, therefore, ME is usually performed using a limited window size called search window for the search process. Figure 14 shows the full search method with search window size that is  $\pm p$  pels in the x-direction and  $\pm q$  pels in the y-direction with block size (M, N).

Figure 14: Full search motion estimation process.

The best-block matching algorithm uses a very simple cost function to evaluate the displacement vectors that describe motion in image sequences. In most cases, a simple pel-based absolute difference is used to determine the similarity between blocks. Two of the most popular cost functions used to measure the similarity between blocks are

the mean square error (MSE) and the mean absolute error (MAE). For a block at location  $(x_m, y_n)$  with block size M x N, the MSE and MAE for motion displace  $\mathbf{d} = (d_x, d_y)$  are,

$$MSE(d_x, d_y) = \frac{1}{MN} \sum_{x=xm}^{xm+M} \sum_{y=yn}^{yn+N} (I(x, y) - I_{ref}(x + d_x, y + d_y))^2, \qquad M = N,$$

(1)

$$MAE(d_x, d_y) = \frac{1}{MN} \sum_{x=xm}^{xm+M} \sum_{y=yn}^{yn+N} |I(x, y) - I_{ref}(x + d_x, y + d_y)|, \qquad M = N,$$

(2)

where I and  $I_{ref}$  are the pixels of the present frame and the reference frame, respectively. The M and N are the dimensions of the block and  $I_{ref}(x + d_x, y + d_y)$  is the value of the block element that is located in row  $x + d_x$  and column  $y + d_y$  in the reference frame. The difference in subjective performance between using the MSE and MAE is quite small for most video sequences. Hence, the number of operations necessary for calculating MAE is much smaller than that of MSE, therefore, in general, the MAE error measure is more commonly used. However, even using the MAE, the computational complexity is still quite high for most video sequences, simply because hundreds of reference blocks must be considered for each candidate block. For example, for CCIR-601 video (30 frames/sec, 720x480 pixels/frame) with a ( $\pm$ 16,  $\pm$ 16) search window size, a 30 GOPS (giga-operations per second)) capable processor is required for performing full search block matching algorithm in real-time.

As we have already suggested, motion estimation and motion compensation are the cornerstone of most video coding systems presently in vogue and are the basic mechanisms by which temporal redundancies are captured in the current H.261, H.263,

MPEG-1, and MPEG-2 standards. Therefore, the importance of exploiting an efficient algorithm for the two tasks is essential. There are many existing efficient algorithms such as logarithmic search and hierarchical search have been suggested in order to reduce the number of operations required to find the best matching block. Later in this chapter, we present a fast ME search algorithm developed in our laboratory at UBC.

#### 3.2.2 Transform Coding, Quantization and Variable Length Coding

After performing the motion estimation, the difference block between the best matching block and the current block is computed. Then a transform operation is applied to the different blocks to reduce the spatial redundancies. Transform coding does a reasonably good job of exploiting statistical redundancy in images by de-correlating the pel data and by compacting information into the lower order coefficients. The most commonly used coding algorithm is the Discrete Cosine Transform (DCT), an algorithm that greatly decorrelates signals and has a smaller complexity compared to that of other transforms with similar performance. The definition of the 2-D DCT transform for an 8x8 block is given by

$$y_{kl} = \frac{c_k c_l}{4} \sum_{i=0}^{7} \sum_{j=0}^{7} x_{ij} \cos\left(\frac{(2i+1)k\pi}{16}\right) \cos\left(\frac{(2j+1)l\pi}{16}\right)$$

(3)

where k, l = 0, ..., 7 and

$$c_k = \begin{cases} \frac{1}{\sqrt{2}} & : & k = 0\\ 1 & : & k \neq 0 \end{cases}$$

Following the transform coding, resulting coefficients are quantized and the quantized DCT coefficients, motion vectors, and side information, such as the picture coding type and the quantizer step are entropy coded using the Variable Length Codes (VLCs). For the quantization, the coding method is lossy coding while VLC coding is lossless. After the quantization, the coefficient block is reconstructed by dequantization and application of Inverse Discrete Cosine Transform (IDCT) and feed back to the coding loop to be used for prediction of temporally future blocks. The original 8x8 block of pixels can be recovered using an 8x8 inverse DCT (IDCT) as follows:

$$x_{kl} = \sum_{i=0}^{7} \sum_{j=0}^{7} y_{ij} c_k \cos\left(\frac{\pi (2i+1)k}{16}\right) c_l \cos\left(\frac{\pi (2j+1)l}{16}\right)$$

(4)

where k, l = 0, ..., 7 and

$$ck, l = \begin{cases} \sqrt{\frac{1}{8}} & : \quad k = 0\\ \sqrt{\frac{1}{4}} & : \quad k \neq 0 \end{cases}$$

Although exact reconstruction can be theoretically achieved, it is often not possible using finite-precision arithmetic. While forward DCT errors can be tolerated, inverse DCT errors must meet the MPEG-2 standard if compliance is to be achieved.

# 3.3 The MPEG-2 Video Coding Standard

The objective of MPEG-2 video coding is to provide high quality and multi-channel compressed video signals transmission over limited-capacity broadcasting infrastructure such as Cable/HFC and ATM networks. Specifically, MPEG-2 was given the mandate of

providing a video quality no less than NTSC/PAL and up to CCIR 601 quality with a target bit rates in the range 2 to 10 Mbit/s [24]. The MPEG-2 coding standard only specifies the syntax for encoded bit-stream, and many of the complex encoding decisions are to provide maximum flexibility for implementing compliant video codecs. This flexibility has posed quite a challenge for video coding engineers to design and determine the trade-offs between coding performance (high compression with acceptable quality) and implementation complexity of various MPEG-2 video coding schemes.

Like H.261 [25], H.263 [26], and MPEG-1 [27], the MPEG-2 video standard is based on motion compensated prediction and DCT residual coding. However, MPEG-2 offers a more efficient means to code interlaced video signals and supports scalable video coding. The readers should be aware that MPEG-2 is a very complex standard. The description we provide here is only an overview of its video part. The MPEG specification is intended to be generic in the sense that it serves a wide range of applications. For example, coded MPEG-2 bit rates of up to 400 Gigabits/s and picture sizes up to 16,000 by 16,000 pixels can be defined. In order to cope with the great variety of video applications within one coding standard, MPEG-2 adopts a "toolkit-like" approach; that is, MPEG-2 is a collection of tools which satisfies the requirements of specific major applications. The range of coding support provided by MPEG-2 is divided into profiles and levels. For each profile/level, MPEG-2 provides the syntax for the coded bit stream and the decoding requirements.

A profile is a defined subset of the entire bit stream syntax specified by MPEG-2. The MPEG-2 profiles can be divided into two categories: non-scalable and scalable. The two non-scalable profiles are the Simple and Main profiles. The three scalable profiles are the SNR scalable, Spatially scalable, and High profiles. Within a profile, a level is defined as a set of constraints imposed on the parameters of the bit stream. For each profile, the four levels are the Low, Main, High-1440, and High levels. The constraints of the coding parameters for each level of a profile and the various profiles are shown in table 1 and table 2, respectively. Among its profile and level combinations, the most widely used combination in the MPEG-2 industry is the main profile/main level.

| Level     | Parameters  |

|-----------|-------------|

| HIGH      | 1920 x 1152 |

|           | 60 frames/s |

|           | 80 Mbit/s   |

| HIGH-1440 | 1440 x 1152 |

|           | 60 frames/s |

|           | 60 Mbit/s   |

| MAIN      | 720 x 576   |

|           | 30 frames/s |

|           | 15 Mbit/s   |

| LOW       | 352 x 288   |

|           | 30 frames/s |

|           | 4 Mbit/s    |

Table 1: Constraint parameters at each level of a profile.

| Profile          | Algorithms  |

|------------------|-------------|

| HIGH             | 4:2:2 – YUV |

|                  | I, P, B     |

| SPATIAL Scalable | 4:0:0 - YUV |

|                  | I, P, B     |

| SNR Scalable     | 4:2:0 – YUV |

|                  | I, P, B     |

| MAIN             | 4:2:0 – YUV |

|                  | I, P, B     |

| SIMPLE           | 4:2:0 – YUV |

| ·                | I, P        |

Table 2: Algorithms and functionalities supported with each profile.

#### 3.3.1 Bit Stream and Macroblock Layer

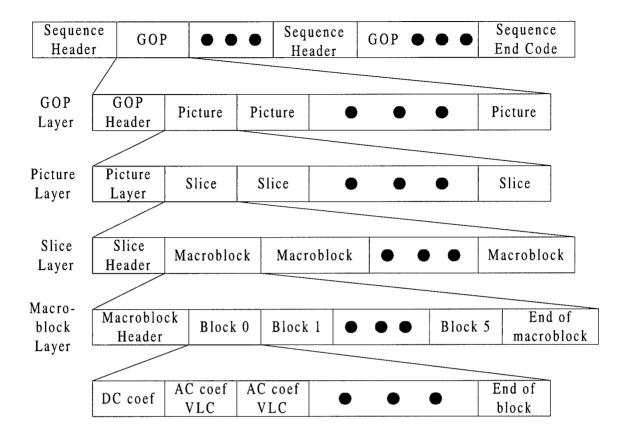

In MPEG-2, the structure of the bit stream syntax depends on the profile adapted by the application. As we will concentrate on only the main profile/main level part of the standard, we will only describe the bit stream syntax for the main profile. The MPEG-2 video bit stream consists of six hierarchical layers starting at the block layer (composed of 8x8 pels) followed by the macroblock, slice, picture, group of pictures (GOP), and the sequence layers as shown in Figure 15.

Figure 15: Video sequences layer.

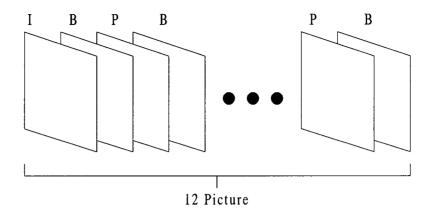

The GOP level is where the video sequence determines the ratio of I, P and B frames, and where the most relevant work on temporal picture structure is carried out. In a typical GOP size of 12 interlaced video frames, the first frame (I-picture) is intra coded, and the following 11 frames are inter coded using alternatively the forward motion compensation (P-pictures) and bi-directional motion compensation (B-pictures) as shown in Figure 16.

Figure 16: GOP of 12 frames.

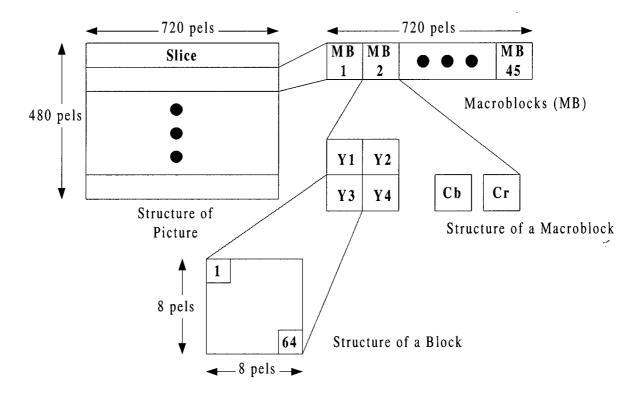

MPEG-2 video supports different standardized picture formats such as CCIR-601 (720x480 resolution) and SIF (320x240 resolution), etc. Each input picture from the video sequence is divided into macroblocks, and every macroblock (MB) consists of a 16x16 block (or four 8x8 blocks) of luminance (Y) component and two 8x8 blocks of chrominance (Cb and Cr) components. Figure 17 shows the MPEG-2 picture structure at CCIR-601 resolution.

Figure 17: MPEG-2 picture structure at CCIR 601 resolution.

#### 3.3.2 Baseline MPEG-2 Video Encoder

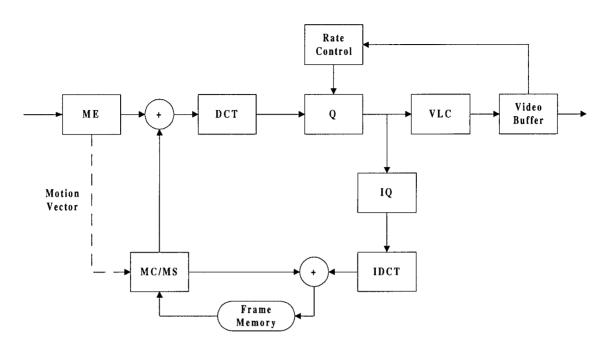

As shown previously, each picture in the input video sequence is divided into macroblocks, and the motion compensated prediction operation is performed at the macroblock level, and most of the operation is perform at that level. In MPEG-2 encoding, a high percentage of the pictures are *inter* coded to obtain a higher compression ratio, except for the first picture of each GOP, which is *intra* coded. Therefore, the *inter* coding operations dominated most of the encoding computations time. Figure 18 shows the encoding diagram for the MPEG-2 baseline encoder.

Figure 18: Block diagram of the MPEG-2 encoder.

For the basic video coding algorithm, the MPEG-2 algorithm has features similar to the ITU-T H.261 and the MPEG-1 algorithm. There are six key video coding components on the MPEG-2 video encoder, which includes motion estimation and motion compensation (ME/MC), mode selection (MS), transform coding (DCT/IDCT), quantization (Q/IQ), variable length coding (VLC), and rate control (RC). For intra coding mode, motion estimation is not required to be performed on the picture, i.e., the 8x8 luminance and chrominance blocks are transform coded with two dimensional DCT and then the transform coefficients are quantized and VLC coded. For the *inter* coding operation, motion estimation searches for the best motion vector with reference to the pervious frame and performs motion-compensation prediction to reduce the temporal redundancies. Then transform coding (using discrete cosine transform (DCT) algorithm) encodes the motion-compensated prediction of the difference frame to reduce the spatial

redundancies. Following transform coding, the resulting coefficients are quantized and then the quantized DCT coefficients, the macroblock (MB) coding mode, the quantization step, the frame/field motion vectors, and the residuals are finally variable-length encoded.

For the motion estimation, full integer pixel motion estimation is preformed first, and then the motion search continues with a half-pixel search around the current motion vector position. Half-pixel values are found using the eight neighbors of the best full-pixel motion vector as shown in Figure 19.

Figure 19: The half pixel motion estimation.

Similar to a Differential Pulse Code Modulator (DPCM), MPEG-2 decodes and reconstructs the image in the encoder. Then the reconstructed picture is added to the current predicted picture in order to obtain the decoded picture, which is then stored in frame memory.

#### 3.3.3 MPGE-2 Video Decoder

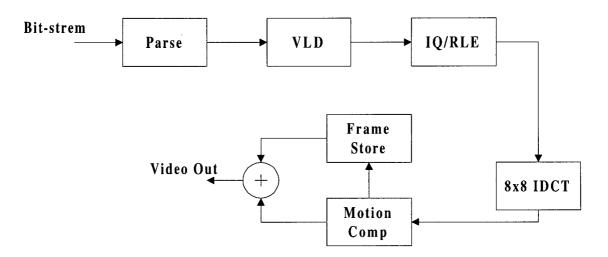

Figure 20: Block diagram for the MPEG-2 decoder.

Figure 20 shows a block diagram of the MPEG-2 video decoder. The main functions involved in the decoder are bit stream parsing, variable length decoding (VLD), inverse quantization (IQ) and run length expansion (RLE), inverse discrete cosine transform (IDCT), and motion compensation. First, the bit stream is parsed and variable-length decoded to obtain the coefficients, the motion vectors and other side information. After the VLD outputs are run-level pairs in a zigzag scan order. The next step is to expand the zero runs, quantize the level values and write the result in a row major scan order. After the coefficients are decoded by inverse quantization, IDCT is applied to the coefficient blocks. If the block is *intra* coded, the reconstructed block is equal to the result of the inverse transformation. For *inter* coded blocks, the reconstruction is formed by motion compensation, i.e. summing the predicted block and the inverse transformed block.

#### 3.3.4 Forward and Inverse Quantization

Depending on the prediction method selected at the encoder, coefficients that are going to be quantized can have a wide variation of statistics. In the case of intra prediction, the first elements of the coefficient block, called the DC coefficient, takes much larger value than the rest of the coefficients, called the AC coefficients. If the block is inter (non-intra) coded, then all the coefficients take smaller AC coefficients. In order to efficiently quantize intra coded blocks, one quantizer is used for the intra DC coefficient and one of 31 predefined quantizers is used for the AC coefficients.

Although the decision levels of the quantizers are not defined within the standard, it is suggested that the quantizer for the DC coefficients be a uniform quantizer with a step size equal to 8. Each of the other 31 quantizers use different spaced reconstruction levels with a non-uniform step size. For the blocks that are inter coded, the AC coefficients have a uniform step size. The sign of the quantized transform coefficients is signaled at the end of the VLC code word. After inverse quantization, the reconstruction levels of all coefficients other than the DC coefficient are clipped to the range -2048 to 2047.

#### 3.3.5 VLC Coding of Transform Coefficients

After quantization, the lowest DCT coefficient (DC coefficient) is treated differently from the remaining AC coefficients when performing the VLC coding of transform coefficients. Since the human visual system is more sensitive to blocking artifacts, which are mainly due to the DC coefficients, the DC coefficient is treated separately from the

other 63 coefficients. The DC coefficient corresponds to the average intensity of the component block and is encoded using a differential DC prediction method. The coding employs a first order predictor which is given by

$$DIFF = DC_i - DC_{i-1}, (5)$$

where DC<sub>i</sub> is the DC coefficient of the current block and DC<sub>i-1</sub> is the DC coefficient of the previous block in row scan order. Most of the remaining AC values that represent higher frequencies become zero. In order to exploit this before VLC coding, the 63 nonzero quantizer values of the remaining DCT coefficients and their locations are the scanned in a zig-zag scan order as illustrated in Figure 21. Then, they are run-length entropy coded using variable length code (VLC) tables.

Figure 21: Zig-zag scan order of a 8x8 block.

The scanning of the quantized DCT domain 2-dimensional signal followed by variable-length code-word assignment for the coefficients serves as a mapping of the 2-dimensional image signal into a 1-dimensional bit stream. The rearrangement places the