# IMPLEMENTATION AND EVALUATION OF VARIOUS STOP AND WAIT TYPE II HYBRID ARQ SCHEMES FOR MOBILE RADIO

by

#### REMO L. AGOSTINO

B. A. Sc., University of British Columbia, 1990.

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF APPLIED SCIENCE

in

#### THE FACULTY OF GRADUATE STUDIES

**Department of Electrical Engineering**

We accept this thesis as conforming to the required standard

#### THE UNIVERSITY OF BRITISH COLUMBIA

September 1993

© Remo L. Agostino, 1993

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

(Signature)

Department of <u>Electrical</u> Eng.

The University of British Columbia Vancouver, Canada

Date Oct 13/03

### **ABSTRACT**

This thesis investigates the design and implementation issues involved in the development of various Stop-and-Wait (SW) Type II Hybrid Automatic Repeat reQuest (ARQ) strategies. The modulation scheme utilized is the North American digital cellular standard known as  $\pi/4$ -shift DQPSK. The general Complementary Punctured Convolutional (CPC) SW Type II ARQ scheme is presented and numerically analyzed in both an AWGN channel and a combined AWGN and Rayleigh fading channel. The three variations of the general scheme implemented are: Rate 3/4 CPC SW Type II ARQ, Rate 3/4 CPC SW Type II ARQ with Code Combining, and an Adaptive CPC SW Type II ARQ scheme. The prototypes are implemented with two Spectrum TMS320C30 Digital Signal Processing (DSP) cards and a host IBM PC. The experimental data for the prototypes were verified and were in good agreement with the numerical results. This validated the prototypes' correct and proper operation along with the DSP software modules used by the prototypes. It is shown that the upgrade of the CPC SW Type II ARQ scheme to a Code Combining and an Adaptive scheme requires small software modifications. It is the versatility and flexibility of the DSP cards which allow these upgrades to be easily accomplished and extremely cost effective. The Code Combining upgrade increased the throughput performance of the general rate 3/4 scheme at low SNR levels. The Adaptive scheme resulted in an increase at both low and high SNR levels with a slight degradation at medium SNR levels with respect to the throughput curve of the general rate 3/4 scheme.

# **Contents**

| ABSTRACT          |                                                   |

|-------------------|---------------------------------------------------|

| List of Tables    |                                                   |

| List of Figures . |                                                   |

| Acknowledgmen     | tsix                                              |

| Chapter 1         | Introduction                                      |

| 1.1               | ARQ Schemes                                       |

| 1.1.1             | Stop-and-Wait ARQ                                 |

| 1.1.2             | Type I Hybrid ARQ 3                               |

| 1.1.3             | Type II Hybrid ARQ 4                              |

| 1.2               | Thesis Goals                                      |

| 1.3               | Thesis Organization 6                             |

| Chapter 2         | $\pi$ /4–Shift DQPSK Modulation Scheme 8          |

| 2.1               | Introduction                                      |

| 2.2               | Transmitter Model                                 |

| 2.3               | DSP Implementation of the Phase Shift Encoder and |

|                   | Baseband Generator                                |

| 2.4               | RF Modulator/Demodulator and Channel              |

| 2.5               | DSP Implemented Baseband Differential Detector 16 |

| 2.6               | Theoretical Analysis and Prototype Performance 18 |

| 2.7               | Conclusions                                       |

| Chapter 3 | Application of Complementary Punctured Convolutional   |

|-----------|--------------------------------------------------------|

|           | Codes to a SW Type II ARQ Scheme                       |

| 3.1       | Introduction                                           |

| 3.2       | Review of Complementary Punctured Convolutional        |

|           | Codes (CPC)                                            |

| 3.2.1     | CPC Codes                                              |

| 3.3       | Generalized CPC SW Type II Hybrid ARQ Algorithm 24     |

| 3.4       | DSP Implementation of a CPC SW Type II ARQ Scheme . 25 |

| 3.4.1     | Frame Structure                                        |

| 3.4.2     | Frame Synchronization                                  |

| 3.4.3     | Encoder/Transmitter DSP Card                           |

| 3.4.4     | Receiver/Decoder DSP Card                              |

| 3.4.4.1   | Viterbi Decoder                                        |

| 3.4.4.1.1 | Numerical Analysis                                     |

| 3.4.4.1.2 | Computer Simulation                                    |

| 3.4.4.1.3 | Viterbi Decoder Performance                            |

| 3.5       | Prototype Performance                                  |

| 3.5.1     | Throughput Analysis                                    |

| 3.5.1.1   | Numerical Results                                      |

| 3.5.2     | Experimental Throughput                                |

| 3.5.3     | Rayleigh Fading Channel                                |

| 3.6            | CPC SW Type II ARQ Scheme with Code Combining 50 |

|----------------|--------------------------------------------------|

| 3.7            | Conclusions                                      |

| Chapter 4      | An Adaptive SW Type II ARQ Scheme                |

| 4.1            | Introduction                                     |

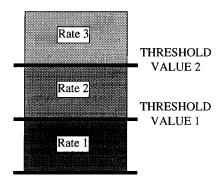

| 4.2            | The Adaptive Coding Rate Algorithm 54            |

| 4.3            | DSP Implementation of the Adaptive Scheme 56     |

| 4.4            | Performance Evaluation                           |

| 4.5            | SW ARQ Scheme Comparisons 63                     |

| 4.6            | Conclusions                                      |

| Chapter 5      | Conclusions and Future Research 66               |

| 5.1            | Conclusions                                      |

| 5.2            | Future Research                                  |

| 5.2.1          | Symbol Synchronization                           |

| 5.2.2          | Selective Repeat Upgrade                         |

| 5.2.3          | Adaptive Header                                  |

| 5.2.4          | FEC Schemes70                                    |

| Bibliography . |                                                  |

| Annendix A     | Software Listings 74                             |

# **List of Tables**

| Table 1 | Phase Shift as a function of Information Symbol 11   |

|---------|------------------------------------------------------|

| Table 2 | $\pi$ /4 Shift DQPSK State Encoder Look Up Table 13  |

| Table 3 | Distance Spectrum of Code with Rate 1/242            |

| Table 4 | Distance Spectra of Rate 3/4 Punctured Convolutional |

|         | Code of Memory m=4                                   |

# **List of Figures**

| Figure 1.1 | Stop-and-Wait ARQ Scheme                                 |

|------------|----------------------------------------------------------|

| Figure 1.2 | Typical Type I Hybrid ARQ System 3                       |

| Figure 2.1 | Block Diagram of the $\pi/4$ shift DQPSK Transmitter 9   |

| Figure 2.2 | State-space diagram of the $\pi/4$ shift DQPSK modulated |

|            | carrier at sampling points                               |

| Figure 2.3 | Flow chart representing baseband transmission            |

|            | algorithm                                                |

| Figure 2.4 | Modulator, Demodulator, and Channel simulator 15         |

| Figure 2.5 | DSP Baseband Differential Detector Block Diagram 16      |

| Figure 2.6 | BER Performance in AWGN                                  |

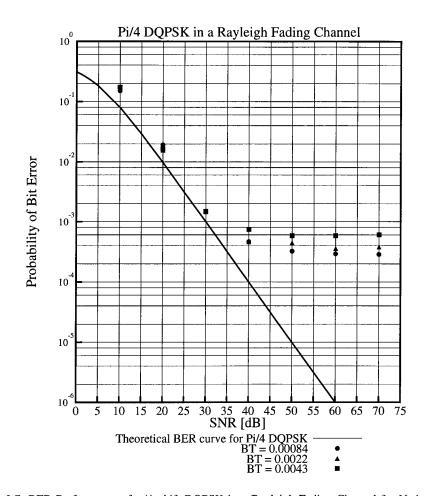

| Figure 2.7 | BER Performance of $\pi/4$ -shift DQPSK in a Rayleigh    |

|            | Fading Channel for Various B <sub>D</sub> T 21           |

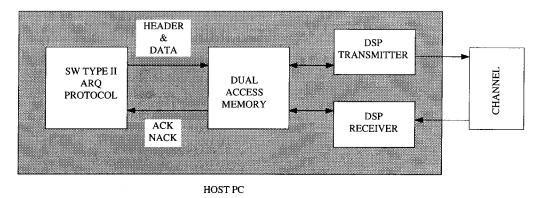

| Figure 3.1 | Block Diagram of Prototype SW Type II ARQ Scheme 26      |

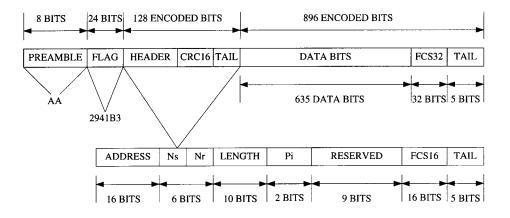

| Figure 3.2 | Detailed Structure of Frame                              |

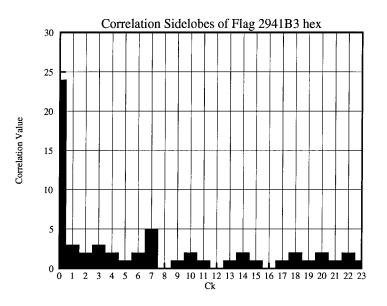

| Figure 3.3 | Correlation Sidelobes of Flag used in Prototype 30       |

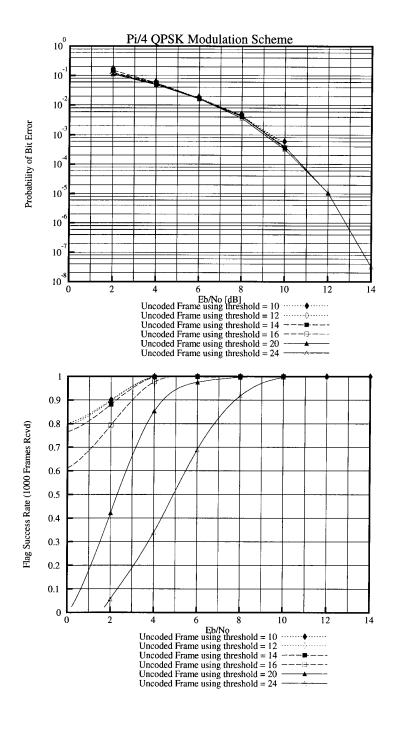

| Figure 3.4 | (a) and (b) Effects of Changing Threshold value used for |

|            | Flag Correlation                                         |

| Figure 3.5 | Frame Encoding and Construction Algorithm of DSP         |

|            | Transmitter Card                                         |

| Figure 3.6 | Frame Decoding Algorithm of DSP Receiver Card38          |

| Figure 3.7 | Choosing a Path Survivor                                 |

| Figure 3.8 | Rate 1/2 Soft Decision Viterbi Decoder Performance 43    |

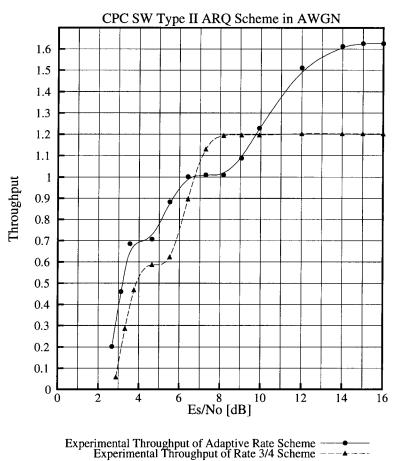

| Figure 3.9  | Numerical and Experimental Throughputs46                |

|-------------|---------------------------------------------------------|

| Figure 3.10 | Throughput of Prototype in a Rayleigh Fading Channel 49 |

| Figure 3.11 | Throughput of CPC SW Type II ARQ Scheme with and        |

|             | without Code Combining                                  |

| Figure 3.12 | Histograms for Rate 3/4 CPC SW Type II ARQ with and     |

|             | without Code Combining                                  |

| Figure 4.1  | Threshold Regions Defining Coding Rates 55              |

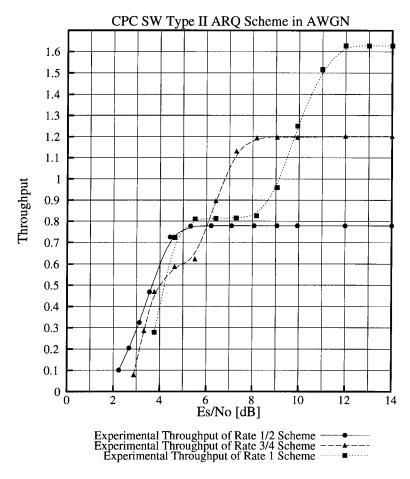

| Figure 4.2  | Experimental Throughputs of rate 1/2, 3/4, and 1 57     |

| Figure 4.3  | Adaptive CPC SW Type II ARQ Throughput 58               |

| Figure 4.4  | Affect of varying N for the Adaptive Scheme's           |

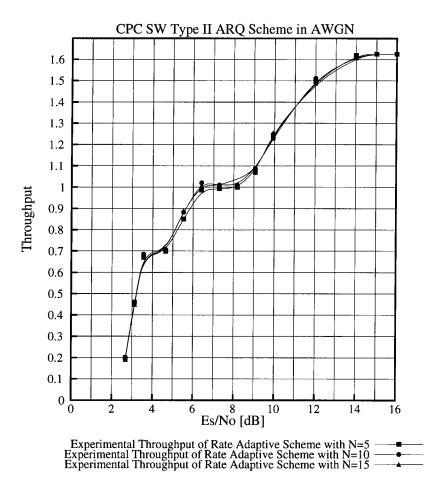

|             | Throughput                                              |

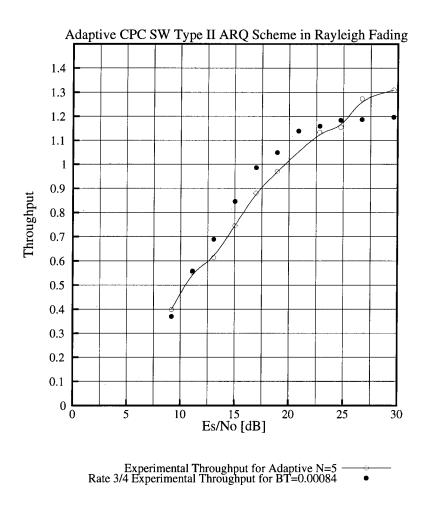

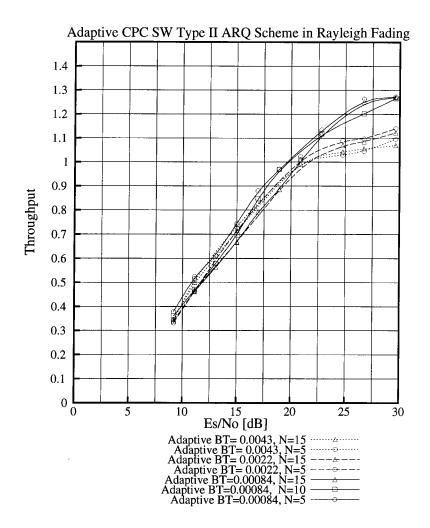

| Figure 4.5  | Adaptive CPC SW Type II ARQ in Rayleigh Channel 60      |

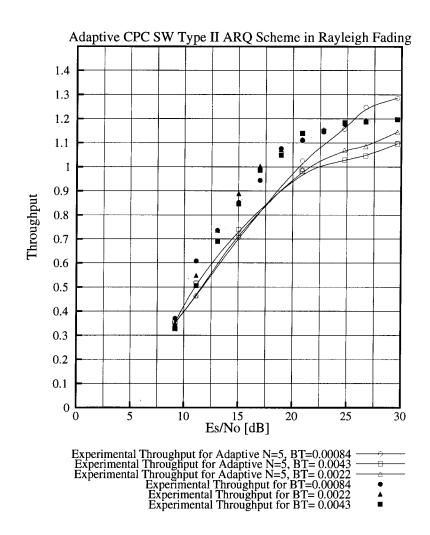

| Figure 4.6  | Adaptive CPC SW Type II ARQ in a Rayleigh Channel for   |

|             | Various B <sub>D</sub> T Products                       |

| Figure 4.7  | Effect of varying N for the Adaptive Scheme in a Fading |

|             | channel 63                                              |

## **Acknowledgments**

I would like to thank my mother and aunt, Maddalena and Maria Taddei, for their continuous moral support and constant encouragement throughout my academic career. I would also like to issue a special thanks to my uncle, Tony Bolognese, for having played a major role in my decision to enter the exciting field of communications. I am enormously grateful to my supervisors, Dr. Samir Kallel and Dr. V. C. M. Leung, for their constant guidance, moral support, and invaluable experience which allowed me to complete this thesis. I would also like to thank my fellow students and especially Dimitrios P. Bouras and William Cheung for their insightful and stimulating discussions. Finally, I would like to acknowledge the assistance provided by the B.C. Science Council.

## Chapter 1 Introduction

#### Section 1.1 ARQ Schemes

The problem of providing an efficient reliable data communications link in a land mobile radio channel is of great practical importance. Automatic Repeat reQuest (ARQ) protocols or similar custom tailored Radio Data Link Protocols are commonly used to provide a virtually error free data link for the radio channel. The ARQ protocol ensures a consistent data quality under varying channel conditions. The functions the ARQ protocol must accomplish can be divided into two different classes: low level functions involved with encoding and decoding of protocol information in the data packets and high level functions concerned with the request retransmission algorithm to support frame transmission services. The message itself is contained in the data packet of the frame, whereas the destination address and other pertinent information is contained in the header which precedes the data packet. A code with good error detecting capability is used to encode the header and data packet separately. Typically, a Cyclic Redundancy Code (CRC) is used [1]. The header is independently encoded to allow all mobile radio users to decode it in order to distinguish if the frame is addressed to them and decide whether to process the data packet.

#### 1.1.1 Stop-and-Wait ARQ

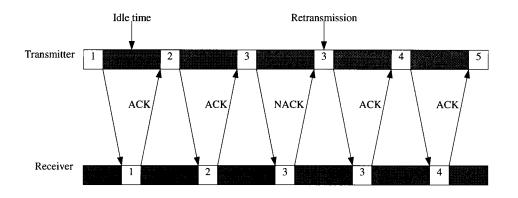

In a Stop-and-Wait ARQ (SW ARQ) scheme, the transmitter sends a single frame and stops to await the reply of the receiver. No other frame can be sent until the receiver's reply arrives at the transmitter. Three possible events may arise once a transmission has taken place. The receiver may send an acknowledgment (ACK) to indicate that the

Section 1

frame was received error free; or a negative acknowledgment (NACK) if it was received in error; or no reply if the frame was so corrupted by noise as not to be received. To account for this last event, the transmitter is equipped with a timer. Once a frame has been sent, the transmitter awaits for a recognizable reply (ACK or NACK). If no such reply is received during the time-out period, the frame is retransmitted. Therefore, any reply other than an ACK will result in the transmitter retransmitting the same frame again. Figure 1.1 illustrates the SW ARQ scheme.

It is inefficient to utilize a SW ARQ protocol in a single frequency system because the time required for the transmitter to await the receiver's reply is wasted air time. The typical mobile radio system uses a number of frequencies to communicate between the base stations and the mobile users. This configuration allows the SW ARQ protocol to make efficient use of its air time. For example, after the base transmits a message to mobile A, it can send another message to any other mobile while awaiting the reply of mobile A on the return channel. In this respect the SW ARQ protocol can be well suited for mobile radio systems.

Figure 1.1 Stop-and-Wait ARO Scheme

Section 1 2

#### 1.1.2 Type I Hybrid ARQ

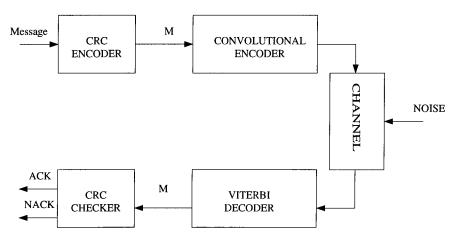

A hybrid ARQ system utilizes both Forward Error Correction (FEC) coding and error detection coding (incorporated in the ARQ scheme). The FEC code is used to reduce the number of retransmissions. In a Type I Hybrid ARQ scheme the message and its error detecting parity bits (typically CRC), are further encoded with a FEC code. At the receiver, the FEC parity bits are used to correct channel errors. The FEC decoder (typically a Viterbi Decoder) outputs an estimate of the received message and its error detecting parity bits. This estimate is tested by the error detection decoder (CRC checker) to determine if the message is error free. Figure 1.2 depicts a Type I Hybrid ARQ communication system.

Figure 1.2 Typical Type I Hybrid ARQ System

The efficiency of a Type I ARQ system in comparison to a plain ARQ system depends on the level of noise corrupting the channel. If the Signal-to-Noise Ratio (SNR) is high, the Type I ARQ scheme does not result in any improvement. The FEC parity bits are wasted, as a result of the signal strength being strong enough to deliver error free messages. On the other hand, the Type I system does show an increase in efficiency

Section 1 3

at low SNR levels, and since the signal strength is so poor, error free reception is very unlikely and the FEC parity bits are utilized to correct channel errors.

#### 1.1.3 Type II Hybrid ARQ

In a Type II ARQ scheme, the FEC parity bits are only sent if the received message contains errors. The transmitter would alternate between sending the message with its error detection parity bits on one transmission, and the FEC parity bits on the next. Note that the FEC parity bits are only sent if the received message contains errors. With this scheme, any error free reception of the message with its error detection parity bits delivers the message. If the FEC parity bits are invertible, any error free reception of the FEC parity bits also delivers the message. Finally, if both the message with its error detection parity bits and the FEC parity bits are in error, combining these two frames for error correction may successfully deliver the message. The Type II system offers the benefit of performing as a plain ARQ scheme at high SNR and performing as a Type I system at low SNR.

#### **Section 1.2 Thesis Goals**

The disadvantage of Type I and Type II hybrid ARQ schemes is the failure to provide a useful throughput at high channel error rates. Application of code combining to hybrid ARQ schemes to achieve a useful throughput has been investigated [2, 3]. Code combining involves taking frames received in error and optimally combining them with their repeated copies. Therefore, the receiver would process a combination of all received sequences for that frame, rather than only the two most recently received ones as in the conventional Type II system.

Section 1 4

An adaptive hybrid ARQ system utilizing code combining would be optimal. Adaptive refers to the FEC coding scheme being able to adjust to the channel conditions and data protection needs. Typically, a fixed code with a certain error rate and correction capability matched to the protection requirement of the data and the worst channel conditions is used. Unfortunately, different data (voice, FAX, computer data files, all using the same channel) have different error protection needs and what may be appropriate for one type may be inappropriate for another. Another problem, is the mobile radio channel conditions are constantly changing due to its multipath and time varying characteristics. Therefore, an adaptive code combining hybrid ARQ scheme would generally yield a higher throughput than a non-adaptive scheme in a radio channel [4].

Motivated by the above, this thesis investigates the design, implementation issues, and performance evaluation of various adaptive and non-adaptive FEC coding schemes of a Type II SW ARQ system. The research contributions can be summarized as follows:

- The Software design, implementation, and test of a Digital Signal Processing (DSP)

Module Library for the Spectrum TMS32C30 DSP card housed in an IBM PC

platform. The library consists of the following modules:

- CRC Encoder/Decoder

- Rate 1/2 Convolutional Encoder

- Puncturing Module

- Rate 1/2 Soft Decision Viterbi Decoder

- Block Interleaver

- Soft Data Deinterleaver

- Queueing Module

Section 2 5

#### • $\pi/4$ -shift DQPSK Baseband Transmitter/Receiver

- 2. The Software implementation and evaluation of a Complementary Punctured Convolutional (CPC) coding scheme for the SW Type II ARQ system with and without code combining utilizing the DSP library in an AWGN channel and a combined AWGN and Rayleigh Fading channel.

- 3. Software upgrade and performance evaluation of an Adaptive CPC SW Type II ARQ scheme utilizing the DSP library in an AWGN channel and a combined AWGN and Rayleigh fading channel.

#### **Section 1.3 Thesis Organization**

The thesis consists of five chapters and one appendix. It is organized as follows:

- Chapter 2 discusses the  $\pi/4$ -shift DQPSK modulation system implemented and its theoretical and practical performance.

- Chapter 3 explains the generalized Complementary Punctured Convolutional (CPC)

coding scheme for a SW Type II ARQ protocol with and without code combining. It also discusses in detail the DSP prototype CPC SW Type II ARQ scheme implemented. Finally, the prototype's performance is analyzed and evaluated.

- Chapter 4 presents the Adaptive CPC SW Type II ARQ scheme implemented and its performance evaluation. This chapter will also compare the three ARQ schemes implemented and discuss their performances.

- The thesis' conclusions and suggestions for future work are cited in Chapter 5.

- Appendix A contains the software listings for the DSP Module Library, the Adaptive SW Type II ARQ Protocol, the Transmitter DSP card, and the Receiver DSP card.

Section 2 6

The CPC scheme's software is a subset of the Adaptive scheme and is therefore not listed.

## Chapter 2 $\pi$ /4–Shift DQPSK Modulation Scheme

#### **Section 2.1 Introduction**

The  $\pi/4$  shift Differential Quadrature Phase Shift Keying (DQPSK) modulation scheme has become the modulation standard for the North American and Japanese digital cellular communications system [5]. This modulation scheme is used in the implementation of the SW Type II ARQ scheme for mobile radio communications in order to get practical results which are of interest to the cellular industry. The organization of this chapter is as follows. Section 2 will review the  $\pi/4$  shift DQPSK modulation technique. Sections 3 to 5 will describe the DSP software and the RF hardware required to construct the system. A performance comparison between the theoretical and implemented modulation scheme is presented in Section 6.

#### **Section 2.2 Transmitter Model**

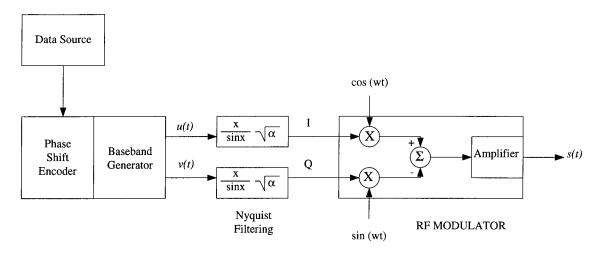

Figure 2.1 illustrates the transmitter model of the  $\pi/4$  shift DQPSK system. The Phase Shift Encoder and Baseband Generator Block produce the unfiltered rectangular pulse waveforms which are denoted as u(t) and v(t) in the Inphase (I) and Quadrature (Q) channels respectively. The waveforms u(t) and v(t) are Nyquist filtered and passed to the RF modulator which mixes the I and Q components to form the RF modulated signal.

Figure 2.1 Block Diagram of the  $\pi/4$  shift DQPSK Transmitter.

Equations 2.1 and 2.2 represent the RF modulated signal.

$$s_i(t) = \sqrt{\frac{2E}{T_s}} \cos\left(w_c t + \frac{2\pi}{8}\right) i = 0, 1, \dots, 7$$

(2.1)

$$s_i(t) = \sqrt{\frac{2E}{T_s}} \left\{ \cos w_c t \cos \frac{\pi}{4} i - \sin w_c t \sin \frac{\pi}{4} i \right\} \quad i = 0, 1, \dots, 7.$$

(2.2)

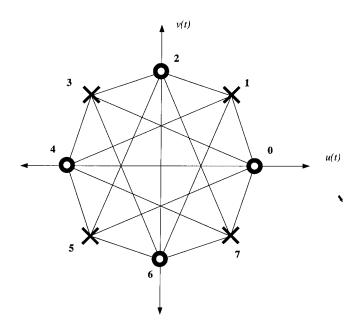

In Equation 2.2, E repesents the energy per symbol,  $T_s$  is the symbol duration, and  $w_c$  is the carrier frequency. Figure 2.2 is the state-space signal diagram which illustrates the possible 8 modulated carrier signals at their sampling instants. The state-space diagram shows that the transmitted signals are chosen from two signal groups, the circles (even numbered points  $\{0, 2, 4, 6\}$ ) and the crosses (odd numbered points  $\{1, 3, 5, 7\}$ ). If the current signal is at one of the four phase states designated by a circle, it shifts to one of the four phase states designated by a cross at the next symbol transition and vice versa. The current signal is not allowed to shift to a fellow member of its phase state at the next symbol transition (i.e., circle to circle or cross to cross). As a result of this constraint, the differential phase shift between two consecutive symbols can only be  $k\pi/4$ , where

Section 2 9

$k=\pm 1$  or  $\pm 3$ . Consecutive phase shifts of  $\pm \pi/2$  and  $\pi$  are inhibited. The connections in the state-space diagram indicate the possible phase transitions.

Figure 2.2 State-space diagram of the  $\pi/4$  shift DQPSK modulated carrier at sampling points [5].

The differential phase shift encoding operation can be mathematically represented by Equations 2.3, 2.4(a), 2.4(b), and Table 1 [6].

$$s_i(t) = \sqrt{\frac{2E}{T_s}} \{ u_k \cos w_c t - v_k \sin w_c t \}$$

(2.3)

$$u_k = u_{k-1}\cos\theta_k - v_{k-1}\sin\theta_k \tag{2.4a}$$

$$v_k = u_{k-1}\sin\theta_k + v_{k-1}\cos\theta_k. \tag{2.4b}$$

In Equations 2.4(a) and 2.4(b),  $u_k$  and  $v_k$  are the signal levels of the pulse amplitudes of

Section 2 10

| Information Symbol | $	heta_{\mathbf{k}}$ |

|--------------------|----------------------|

| 11                 | $\pi/4$              |

| 01                 | $3\pi/4$             |

| 00                 | $-3\pi/4$            |

| 10                 | $-\pi/4$             |

Table 1 Phase Shift as a function of Information Symbol.

u(t) and v(t) for a period equal to the symbol duration. The signal levels  $u_k$  and  $v_k$  are determined from the previous signal levels,  $u_{k-1}$  and  $v_{k-1}$  and the phase shift,  $\theta_k$  resulting from the current information symbol. The relationship between the phase shift and the current information symbol is given in Table 1. From Equations 2.4(a) and 2.4(b), it can be seen that the amplitudes of u(t) and v(t) can take the values of  $0, \pm \frac{\sqrt{2}}{2}$ , or  $\pm 1$ . For example, assume the current signal is  $s_0(t)$  (i.e.,  $\theta_0 = 0$ ,  $u_0 = 1$ , and  $v_0 = 0$  during  $0 \le t \le T_s$ ). At time  $t = T_s$ , the information symbol 11 is sent. Therefore,  $\theta_1 = \pi/4$  and from Equations 2.4(a) and 2.4(b),  $u_1 = \frac{\sqrt{2}}{2}$  and  $v_1 = \frac{\sqrt{2}}{2}$  denoting signal  $s_1(t)$ .

From the state-space diagram and the mathematical model it follows that the information symbol is contained in the phase difference between two consecutive sampling instants. The receiver only requires the phase difference between two consecutive sampling intervals in order to retrieve the transmitted information symbol. As a result, the receiver does not need to phase synchronize with the transmitter.

# Section 2.3 DSP Implementation of the Phase Shift Encoder and Baseband Generator

The transmitter and receiver is implemented utilizing the Texas Instruments TMS320C30 DSP chip. The DSP platform consists of a Spectrum TMS320C30 card and software development tools for an IBM PC. The TMS320C30 DSP cards were cho-

Section 3

sen due to their availability and excellent software support. A software based DSP design is more versatile, flexible, and modular than an all hardware design. The DSP system allows the user to make changes and updates to their software algorithms in a fraction of the time required for a hardware update.

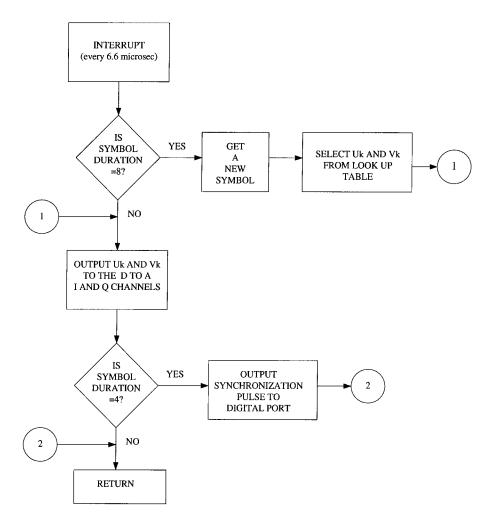

The flowchart shown in Figure 2.3 describes the baseband transmission algorithm.

Figure 2.3 Flow chart representing baseband transmission algorithm.

The algorithm is interrupt driven by one of the two timers that the TMS320C30 chip features. The timer is set to 6.6  $\mu$ s, which is the upper limit available on the Spectrum card

housing the TMS320C30. The timer value has a direct result on the rate of transmission. The smaller the timer value, the higher the transmission rate. The baseband transmission routine is interrupt driven to allow the DSP chip to encode and construct other frames for transmission while the current frame is being transmitted. Therefore, even though a SW ARQ scheme is being used, the scheme may be upgraded to a Selective Repeat (SR) ARQ with little or no change to the transmission algorithm.

The Baud rate, which is the number of symbols transmitted per second, is determined by the number of times the routine is executed per symbol or dibit. The variable <code>symbol\_duration\_count</code> keeps track of this value, which is compared to a user set limit. In the algorithm shown in Figure 2.3, the limit is set to a value of 8 and gives rise to a baud rate of 18.939kHz according to equation 2.5.

Baud rate =

$$\{(symbol\_duration\_count \ \text{Limit}) * 6.6\mu s\}^{-1}$$

. (2.5)

Every time the interrupt routine is executed, the  $symbol\_duration\_count$  is checked. If a new symbol or dibit is required, it is fetched from memory and the amplitudes  $u_k$  and  $v_k$ , of the baseband signals u(t) and v(t), are chosen from the  $\pi/4$  shift DQPSK encoder look up table displayed as Table 2. Table 2 shows all possible state transitions given the

|                | Previous Signal $s_i(t)$ |   |   |   |   |   |   |   |

|----------------|--------------------------|---|---|---|---|---|---|---|

| Current Symbol | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 00             | 5                        | 6 | 7 | 0 | 1 | 2 | 3 | 4 |

| 01             | 3                        | 4 | 5 | 6 | 7 | 0 | 1 | 2 |

| 10             | 7                        | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

| 11             | 1                        | 2 | 3 | 4 | 5 | 6 | 7 | 0 |

Table 2  $\pi/4$  Shift DQPSK State Encoder Look Up Table.

previous signal  $s_i(t)$  and the current symbol or dibit to be transmitted. This table is a direct

result of equations 2.4(a), 2.4(b), and Table 1. Once the values for  $u_k$  and  $v_k$  are chosen, they are written to the Digital to Analog registers, which in turn outputs an analog voltage on the I and Q channels. Note the transmitter outputs a +5 volt synchronization pulse on the TMS320C30 digital channel at approximately the middle of the symbol duration.

The baseband waveforms u(t) and v(t) are filtered before being sent to the RF modulator. In the transmitter model discussed in Section 2.2, Nyquist filters were used in order to eliminate Intersymbol Interference (ISI) and maximize the Signal-to-Noise Ratio (SNR). Butterworth filters, which are contained on the Spectrum DSP cards, were used in the prototype implementation. As a consequence of not using Nyquist filters, the received noise power will be greater in the Butterworth filter case.

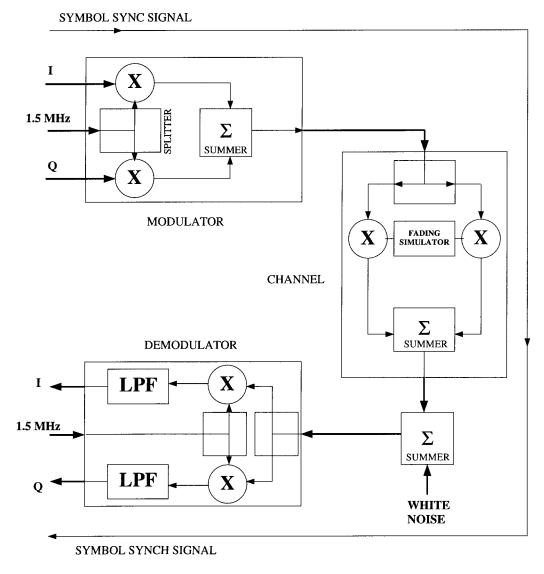

#### Section 2.4 RF Modulator/Demodulator and Channel

A detailed block diagram of the hardware implemented RF modulator/demodulator is shown in Figure 2.4 and presented in [7]. The modulator and demodulator are designed to operate at the relatively low carrier frequency of 1.5 MHz. The carrier frequency enters the modulator to be divided into its I and Q components by a 90° splitter. The carrier's I and Q components are then mixed with the I and Q baseband signals and summed by a signal combiner. The resulting RF modulated carrier is amplified and passed to the channel module, which allows fading to be simulated by the use of the Digital Fading Simulator presented in [8]. White Gaussain noise is also added to the channel from a White Noise Generator whose band coverage is 6 kHz to 25 MHz. The modulated carrier and white noise is filtered by a Band Pass Filter (BPF), which has a 3 dB bandwidth of 200 kHz centered at the carrier frequency of 1.5 MHz. The bandwidth of the BPF

is much greater than that of the Low Pass Filters (LPF) at the demodulator and is used to minimize noise.

The demodulator takes the received RF modulated carrier and splits it into its I and Q components, which are then coherently mixed down to the baseband signals. The baseband I and Q signals are passed through Low Pass Filters (LPF) and fed to the DSP card for Differential Baseband Detection.

Figure 2.4 Modulator, Demodulator, and Channel simulator.

Note the symbol synchronization pulse is directly connected from the transmitter DSP card to the receiver DSP card. In practice a local oscillator, closely tuned to the symbol rate of the I and Q channels, would trigger the receiver. This procedure was investigated, but it resulted in a synchronization problem. It was observed that approximately 150–200 symbols were correctly received, immediately followed by 50–100 incorrect symbols and then the cycle begins again. The local oscillator drifted in and out of synchronization with the I and Q channels' symbol rate. In order to obtain optimum synchronization, a Phase Locked Loop (PLL) circuit was employed. The PLL worked and the results were encouraging but required further research. Since the investigation of symbol synchronization effects is beyond the scope of this thesis, we opted to use the transmitter DSP card to trigger the receiver.

#### Section 2.5 DSP Implemented Baseband Differential Detector

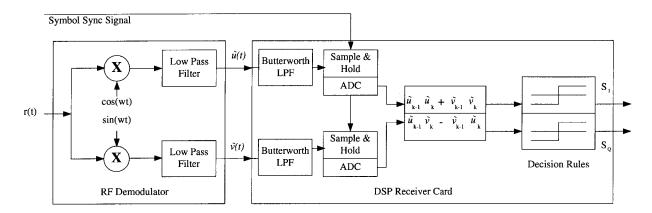

The block diagram of the Differential Detector is shown in Figure 2.5 [6]. Once

Figure 2.5 DSP Baseband Differential Detector Block Diagram

the RF modulated carrier is converted into its I and Q baseband signals  $\dot{u}(t)$  and  $\dot{v}(t)$ , it is ready to be processed by the DSP Differential Detector. The DSP card drives each baseband signal through a Butterworth filter, a Sample and Hold circuit, and an Analog

Section 4 16

to Digital Converter (ADC). It is the digital output of the ADC that the TMS320C30 addresses in order to obtain a real floating point representation of the amplitudes  $u_k$  and  $v_k$  of the received baseband signals. The DSP detector samples each symbol and uses equations 2.6(a) and 2.6(b) in order to transform the DQPSK real data  $u_k$  and  $v_k$  to QPSK real data  $v_k$  and  $v_k$  [6].

$$w_k = \dot{u}_{k-1}\dot{u}_k + \dot{v}_{k-1}\dot{v}_k = \cos(\theta_k - \theta_{k-1})$$

(2.6a)

$$z_k = \dot{u}_{k-1}\dot{v}_k - \dot{v}_{k-1}\dot{u}_k = \sin(\theta_k - \theta_{k-1}). \tag{2.6b}$$

This transformation of  $\pi/4$ -shift DQPSK data to QPSK data makes each symbol no longer dependent on the previous symbol for decoding purposes. Note that  $w_k$  and  $z_k$  are equivalent to  $\sin{(\theta_k - \theta_{k-1})}$  and  $\cos{(\theta_k - \theta_{k-1})}$ , where  $\theta_k - \theta_{k-1}$  is the phase shift. It follows that, since the phase shift can only be  $k\pi/4$ , where  $k = \pm 1$  or  $\pm 3$ ,  $w_k$  and  $z_k$  will be approximately  $\pm \frac{\sqrt{2}}{2}$ . The real floating point values obtained for  $w_k$  and  $z_k$  may be fed into a soft decision Viterbi decoder or can be hard decoded according to the following decision rules:

$$S_I=1$$

if  $w_k>0$   $S_I=0$  if  $w_k<0$

$$S_Q=1 \text{ if } z_k>0 \qquad S_Q=0 \text{ if } z_k<0 , \qquad (2.7)$$

where  $S_I$  and  $S_Q$  are the least and most significant bit of the symbol respectively. Note the prototype system utilizes the same carrier frequency for both the modulator and demodulator. In practice a local oscillator tuned to the same frequency as the transmitter is used to demodulate the received carrier. This local oscillator will have a constant phase difference but it has been shown that the phase error is cancelled through differential detection [6].

Section 5 17

#### Section 2.6 Theoretical Analysis and Prototype Performance

The probability of a binary digit error for four-phase DPSK with Gray coding in an AWGN channel is given by [9] as

$$P_{4b}(e) = e^{\frac{-2E_b}{N_o}} \left\{ \sum_{k=0}^{\infty} \left( \sqrt{2} - 1 \right)^k I_k \left( \frac{\sqrt{2}E_b}{N_o} \right) - \frac{1}{2} I_0 \left( \frac{\sqrt{2}E_b}{N_o} \right) \right\}, \tag{2.8}$$

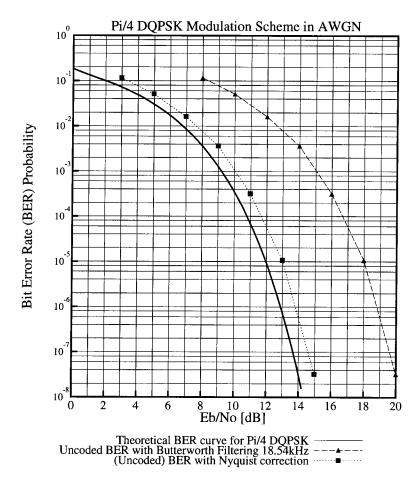

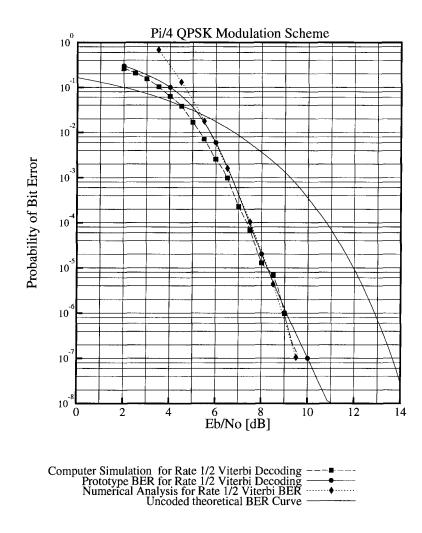

where  $I_k$  is the kth order modified Bessel function of the first kind. The Bit Error Rate (BER) curve based on Equation 2.8 is plotted in Figure 2.6.

Figure 2.6 also shows two experimentally measured curves of the prototype modulation scheme in an Additive White Gaussian Noise (AWGN) channel. The curve labelled as "Uncoded BER with Butterworth Filtering" is the actual performance of the prototype implemented. There is a considerable degradation of 6 dB as compared to the theoretical ideal curve. This degradation is primarily due to the substitution of the required Nyquist filters with 4th order Butterworth filters. The required Nyquist filters were unavailable and the Butterworth filters are contained on the DSP cards. The effect of the Butterworth filter is to allow more noise to pass through to the receiver and cause ISI in comparison to the Nyquist case. As a result, the prototype will have worse performance since the SNR after the receiver filter will be less than the  $E_s/N_0$  which would exist when employing a square root Nyquist filter. Through the use of a computer simulation, which used the Butterworth and Nyquist filters' bandwidths as parameters, it was found that the difference between the Butterworth and Nyquist case is approximately 5 dB. The curve labelled as "Uncoded BER with Nyquist correction" is a result of this correction factor. Note that this is an approximation, the true Nyquist correction factor must also account for the added ISI caused by the Butterworth filter. The prototype's corrected performance

Section 6 18

is relatively close to the theoretically expected performance with a maximum degradation of 1 dB. This deviation is attributed to the following factors.

- The non-ideal signal space at the demodulator output, due to the imperfect RF components.

- The imperfect timing of the software controlled symbol synchronization signal.

- The ISI caused by the Butterworth filters.

Figure 2.6 BER Performance in AWGN.

For convenience, all subsequent performance curves of the implemented system will be adjusted by this "Nyquist correction factor". This also holds for the coded case, since

Section 6 19

the performance is plotted against the SNR level. The SNR level that would exist with the Nyquist case is just a simple adjustment as above.

Figure 2.7 presents the measured BER performance of the modulation system in a combined AWGN and Rayleigh fading environment with  $B_DT$  equal to 0.0043, 0.0022, and 0.00084. The  $B_DT$  products correspond to a  $\pi/4$  shift DQPSK system operating with a carrier frequency of 900MHz, a baud rate of 19.2kBaud/s, and vehicle velocities of 100, 50, and 20km/hr respectively. Also shown in the graph, is the theoretical BER results for a static multipath fading channel. Static refers to the channel having a constant phase modulation (i.e., the receiver or vehicle is at rest). The experimental results are for vehicles in motion and therefore, are expected to be worse than the theoretical curve for a vehicle at rest. It is evident that the theoretical and experimental results are in close agreement until a residual error floor is established by the experimental curves. This error floor is a result of the random phase modulation caused by the doppler spread obtained from the vehicle being in motion. An increase in the doppler spread results in an increase in the level of the error floor. The experimental results are less than an order of magnitude higher than the computer simulated results of Feher [10] and Bouras [7]. This deviation is due to the imperfections in the modulation scheme and the hardware Rayleigh simulator, as well as the Receiver DSP Card clipping the input voltage waveforms of the I and Q channels to ±3 volts even though the amplitude periodically fluctuates beyond these limits.

Section 6 20

Figure 2.7 BER Performance of  $\pi/4$ -shift DQPSK in a Rayleigh Fading Channel for Various  $B_DT$ .

#### **Section 2.7 Conclusions**

The operation of the prototype  $\pi/4$  shift DQPSK system was verified through experimental measurements. The BER performance data obtained for the AWGN channel and the combined AWGN and Rayleigh Fading Channel were in very good agreement with the expected theoretical results illustrating the proper operation of the prototype modulation scheme.

Section 7 21

## Chapter 3 Application of Complementary Punctured Convolutional Codes to a SW Type II ARQ Scheme

#### **Section 3.1 Introduction**

Recently, Kallel has introduced a new class of punctured convolutional codes which are complementary [11]. In this Chapter we will briefly review Complementary Punctured Convolutional (CPC) Codes and their structure. Section 3 will present the generalized CPC SW Type II Hybrid ARQ algorithm, and Section 4 will discuss its specific implementation using DSP cards housed in an IBM PC. The performance of the implemented prototype will be compared to numerical and computer simulated models in Section 5.

# Section 3.2 Review of Complementary Punctured Convolutional Codes (CPC)

In general, a high rate (b/N) punctured convolutional code can be constructed from a rate  $1/N_0$  mother code by periodically and selectively deleting ( $bN_0-N$ ) code bits according to a specific perforation pattern [12]. The function of deleting code bits is usually performed by the use of a perforation matrix which consists of b columns and  $N_0$  rows for a rate of b/N punctured code. Each column is associated with one encoding cycle, and each row is associated with each coded bit stream from the  $N_0$  modulo-2 adders of the  $1/N_0$  encoder. The perforation matrix consists of ones and zeros which corresponds to transmitting and not transmitting code bits. An example, of a rate 3/4 punctured convolutional code of period 3 obtained from a rate 1/2 code is given by

$$P_1 = \begin{bmatrix} 1 & 0 & 1 \\ 1 & 1 & 0 \end{bmatrix}. \tag{3.1}$$

An equivalent punctured code can be obtained by likewise cyclically shifting the  $N_0$  rows. At the most, this will yield b distinct codes which have the same distance properties and error performance capabilities [13]. As a result,  $P_2$ , which is given by

$$P_2 = \begin{bmatrix} 0 & 1 & 1 \\ 1 & 0 & 1 \end{bmatrix}, \tag{3.2}$$

and  $P_1$  are equivalent perforation matrices.

#### 3.2.1 CPC Codes

Allow  $P_i$ , i=1,2,...,p, to denote the perforation matrices of p equivalent CPC codes of rate b/N obtained from a rate  $1/N_0$  mother code, where  $p=\left\lceil \frac{bN_o}{N}\right\rceil$ . The result of perforation matrix  $P_i$  is code CPC<sub>i</sub>. Define the matrix  $P_{TOTAL}$  as

$$P_{TOTAL} = \sum_{i=1}^{p} P_i . (3.3)$$

The p equivalent codes  $CPC_i$ , i=1,2,...,p, are said to be *Complementary* if every element of  $P_{TOTAL}$  is greater than or equal to one. Note that for convenience the p equivalent codes were denoted as  $CPC_i$ , but if they do not met the above restriction associated with  $P_{TOTAL}$ , they should not be referred to as  $CPC_i$ . The rate of  $P_{TOTAL}$  is given by b/(pN) which results in two possible cases. If  $N = N_0$ , we have p = b and the rate of  $P_{TOTAL}$  will be  $b/(bN) = 1/N_0$ , which is the original mother code. On the other hand, if  $N > N_0$  and p < b matrices are chosen to satisfy Equation 3.3, then some elements of  $P_{TOTAL}$  will be greater than one and the combined rate is b/(pN). As an example, the two previous matrices  $P_1$  and  $P_2$  of rate 3/4 are combined to form  $P_{TOTAL}$  and yield a resulting code rate of 3/8.

$$P_{TOTAL} = \begin{bmatrix} 1 & 1 & 2 \\ 2 & 1 & 1 \end{bmatrix}. {3.4}$$

Section 2 23

#### Section 3.3 Generalized CPC SW Type II Hybrid ARQ Algorithm

Allow  $P_i$ , i=1, 2, ..., p, to denote the perforation matrices of p CPC codes of rate b/N obtained from a rate  $1/N_0$  mother code, as discussed above. The result of perforation matrix  $P_i$  is code CPC<sub>i</sub>.

The scheme begins by appending  $n_{dp}$  detection parity bits and m tail bits, corresponding to the encoder's memory, to each k-bit data packet. The resulting sequence is encoded by the rate  $I/N_0$  mother code and then punctured and transmitted according to the following algorithm [11].

- 1. Level 1: Puncture the sequence with  $P_I$ , resulting in packet A of code  $CPC_I$  which is transmitted. The receiver decodes packet A using a rate  $I/N_0$  Viterbi decoder and perforation matrix  $P_I$ . The error detection decoder checks the decoded sequence consisting of data bits and parity bits. If the sequence is declared error free, transmission of A is complete. Otherwise, the received sequence is stored for future decoding attempts and the algorithm moves up to the next level.

- 2. Level i, 1 < i < p: Transmit packet **A** of code CPC<sub>i</sub> resulting from P<sub>i</sub>. Initially, use Viterbi decoding with perforation matrix P<sub>i</sub>. If the decoded sequence is declared error free, transmission of A is complete. Otherwise, reapply Viterbi decoding but on the combination of all i sequences, previously stored up to this level, and using perforation matrix  $P_{TOTAL}=P_1+P_2+...+P_i$ . If the resulting sequence is declared error free, transmission of **A** is complete. Otherwise, the current sequence is stored and the algorithm moves to the next level.

- 3. Level p: Send packet A of code  $CPC_p$ . As above, initially decode using only the received sequence. If unsuccessful, decode using all p sequences. If the resulting

sequence is still in error, discard the received sequence of code  $CPC_I$  and the algorithm moves to the next level.

4. Level (p+j), j=1,2,...: Send Packet A of code  $CPC_i$ . Decode using the received sequence in conjunction with perforation matrix  $P_i$ . If unsuccessful, decode using all p sequences. In the event that decoding is still unsuccessful, discard received sequence at level j+1 and the algorithm moves to the next level.

It should be pointed out, that the above encoding and transmitting strategy did not discuss the implications of appending a flag and a header to packet A. In the event that a flag is not found in the implemented prototype, the receiver will time out, and the algorithm will reinitialize at the current level. In practice it is the transmitter which times out if it receives no response from the receiver. If a header failure is detected, the current packet is discarded and the algorithm also reinitializes at the current level. Since the transmitter and receiver DSP cards are contained in the same PC they are initialized and synchronized by the Host ARQ protocol.

# Section 3.4 DSP Implementation of a CPC SW Type II ARQ Scheme

The Stop and Wait Type II Hybrid ARQ Protocol is written in Borland C++ and resident on the host PC. The protocol behaves as discussed above with p=2 CPC codes of rate 3/4 from a rate 1/2 mother code. The two perforation matrices used by the DSP transmitter card for encoding the data packet are given by

$$P_1 = \begin{bmatrix} 1 & 0 & 1 \\ 1 & 1 & 0 \end{bmatrix} \qquad P_2 = \begin{bmatrix} 0 & 1 & 1 \\ 1 & 0 & 1 \end{bmatrix} . \tag{3.5}$$

Figure 3.1 shows the physical block diagram of the prototype communication system. The protocol constructs the header and random data packet, places them in the Dual Access

Section 4 25

Memory (DAM), and strobes the DSP transmitter card to send and the DSP receiver card to listen. The DSP transmitter card retrieves the header and data packets and encodes them according to the information placed in the header. Once the frame is constructed, it is transmitted through the channel to the DSP receiver card, which is contained in the same PC. The DSP receiver card processes the received frame and either places an acknowledgment (ACK) or negative acknowledgment (NACK) in the DAM and strobes the protocol. Once the protocol fetches the DSP receiver's reply, two events may occur. If an ACK was sent, the protocol will construct a new header and a new random data packet to place in the DAM. If a NACK was sent, the protocol will keep the data packet but construct a new header which indicates the new  $P_i$  to be used for encoding the data packet. Note that if a frame is lost, the DSP receiver is equipped with a time-out feature which will result in a NACK.

Figure 3.1 Block Diagram of Prototype SW Type II ARQ Scheme.

It is during the construction of the header, that the protocol decides which perforation matrix  $P_1$  or  $P_2$  to use for encoding the data packet based on the receiver's reply. Along with the NACK, the receiver sends the motive which may be either a *Header CRC Failure* or a *Data CRC Failure*. In the event of a header failure or lost frame (time-out), the protocol will not switch perforation matrices. In the event of a data failure, the protocol

Section 4 26

alternates between  $P_1$  or  $P_2$ . The result of this algorithm is to maximize throughput. This algorithm ensures that if a corrupted data sequence of code  $CPC_1$  is received, the next data sequence received can only be encoded by  $P_2$  and be of code  $CPC_2$ . If the data sequence of code  $CPC_2$  is unsuccessfully decoded, it may be combined with the data sequence of code  $CPC_1$  for subsequent decoding. The modulation scheme used by the SW Type II ARQ Protocol for transmission, is the  $\pi/4$  Shift DQPSK discussed in detail in Chapter 2.

The following assumptions or simplifications are incorporated in the implemented prototype which consists of the DSP transmitter and receiver cards in the same Host PC under the control of the SW ARQ protocol.

- As a consequence of the transmitter and receiver DSP cards being in the same Host PC, they are initialized and synchronized by the ARQ Protocol running on the Host PC. In practice, there is an initialization and synchronization process to be executed by the independent transmitter and receiver.

- In practice a noisy return channel is used to send the receiver's reply. In the prototype, the receiver's reply is passed internally through the PC via the DAM. This is a noise free return channel.

- As a result of the ARQ protocol controlling both the transmitter and receiver, it is the receiver which times out if a flag is not found. Again, in practice it is the transmitter that times out if it does not get a response from the receiver.

- Symbol Synchronization is accomplished by hard wiring the transmitter and receiver.

The actual symbol timing signal is software generated and is not ideal. A practical system would have the receiver utilize a Phase Locked Loop or some other synchro-

nization circuit to obtain symbol synchronization with no link to the transmitter.

These simplifications do not compromise the accuracy of the experimental results. The prototype is used to evaluate various FEC strategies which are unaffected by the above simplifications.

## 3.4.1 Frame Structure

The detailed structure of the frame used for transmission in the prototype system is illustrated in Figure 3.2. Excluding the preamble and flag, the maximum length the encoded frame may attain is 1024 bits. The frame begins with an 8 bit Symbol Sync Preamble. Since a Stop and Wait scheme is implemented, the channel will always be idle before a transmission and the preamble allows the receiver to realize symbol synchronization and stabilize before the remaining portion of the frame arrives. Immediately following the preamble is the Flag or Frame Sync, whose purpose is to present the receiver with a unique bit pattern so that the receiver may synchronize itself with the data stream's frame structure. The receiver is continuously hunting for the flag pattern and the actual procedure and choice of flag is investigated in the next section.

Figure 3.2 Detailed Structure of Frame.

Control information is contained in the 64 bit header, which includes a 16 bit Frame Check Sequence (FCS) and a 5 bit tail for decoding. The header's address field is used to identify the station that is to receive the frame. The next two fields,  $N_s$  and  $N_r$  are sequence numbers used to number the frames. The sequence numbers are not required for the operation of the prototype but has been included for future upgrading to a Selective Repeat scheme. The next field contains the length of the data packet following the header. The following field consists of two bits which indicate the perforation matrix  $P_i$  used in the puncturing operation during the encoding of the data. Reserved is the next field which consists of 9 bits and is not used by the current version of the protocol. The remaining 16 bits represent the FCS which is a result of the generator polynomial CRC-CITT defined as  $G_{16}(x) = x^{16} + x^{12} + x^5 + 1$ .

The information or data bits are contained in the data packet of the frame. This consists of a maximum of 896 CPC encoded bits. As a result of using a perforation matrix which yields a rate of 3/4, the maximum number of information bits which the data packet can contain is  $\frac{3}{4}(896) - 32 - 5 = 635$  bits. The length of the entire frame consisting of preamble, flag, header, and data packet is 1056 bits. The generator polynomial used for the FCS is the CRC32 given as  $G_{32}(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x^{11} + 1$ .

# 3.4.2 Frame Synchronization

The 24 bit flag, denoted in hexadecimal as 2941B3, is used by the receiver to synchronize itself with the data stream's frame structure. A good flag sequence has the property that the absolute value of its *correlation sidelobes* is small. A correlation sidelobe is the value obtained by correlating a flag sequence with a time-shifted version

of itself. Therefore, a correlation sidelobe value,  $C_k$ , for a k-symbol shift of a N bit flag sequence  $\{F_i\}$ , is given by

$$C_k = \sum_{j=1}^{N-k} F_j F_{j+k} , \qquad (3.6)$$

where  $F_i$  ( $1 \le i \le N$ ) is an individual bit taking values of  $\pm 1$ , and the adjacent bits (associated with index values i > N) are assumed to be 0 [14]. The actual flag was found through the use of computer simulations.

Figure 3.3 shows the correlation sidelobes of the flag used in the prototype. The sidelobes are very low when compared to the main lobe of  $C_0$ , which yields a value of 24. This sidelobe profile ensures a very high probability that the receiver will find the exact starting point of the flag rather than a bit shifted version of it.

Figure 3.3 Correlation Sidelobes of Flag used in Prototype.

The following procedure is followed to allow the receiver to locate the flag. The receiver correlates the known flag pattern to the incoming data. If the incoming data does not contain a flag, the correlation value will be low. On the other hand, when a flag is

encountered the correlation value will be very high. The correlation value, C, for a 24 bit flag pattern  $\{F_j\}$  and a 24 bit data sequence  $\{D_j\}$  is given by

$$C = \sum_{j=1}^{24} F_j D_j \quad , \tag{3.7}$$

where  $F_j$  and  $D_j$  take on values of +1 or -1 representing bits 1 and 0 respectively. The maximum value of C is 24 which indicates a flag with 0 bit errors has been located. The prototype compares C to a user set *threshold* value which limits the number of bit errors which will be accepted in the flag and still ensure frame synchronization (i.e., a *threshold* value of 16 indicates that 20 bits of the data sequence match the flag pattern).

The optimum *threshold* value was found through experimentation. For each SNR tested, a 1000 uncoded frames were sent to the receiver whose correlation *threshold* value was altered over the range of 10 to 24. Referring to Figure 3.3, it is seen that the highest sidelobe has a value of 5. A starting point for the *threshold* value is to take twice the highest sidelobe value which is 10. Figure 3.4(a) illustrates that the probability of a bit error is relatively equal for *threshold* values of 24 to 10. However, lowering the *threshold* value below 10 results in the prototype operating very slowly because it must process a large number of false flags. The lower the *threshold* value, the larger the amount of false flags that the prototype must process. Figure 3.4(b) shows the percentage of flags successfully found given the different *threshold* values. It is seen that the lower the *threshold* value, the greater the success of finding the flags. Another observation is that decreasing the *threshold* value below 12 has a marginal affect on the flag success rate. A balance must be found in which a threshold value that gives a good flag success rate does not burden the prototype with false flags. The two curves representing *threshold* values of 10 and 12 give the best success rates and are relatively equal. It is obvious from

the two graphs that a *threshold* value of 10 or 12 is optimum. These values yield the best flag success rate with the least amount of false flags to be processed by the prototype.

Figure 3.4 (a) and (b) Effects of Changing Threshold value used for Flag Correlation

By comparing the correlation value, *C*, to a *threshold* value, a certain number of false flags will be located. The prototype receiver implemented is "smart" enough to eliminate the majority of false flags. When a flag is located, the header is immediately decoded and two events may occur.

- If the header fails the CRC check, the next subsequent flag is located and the new header is decoded. If the CRC check fails again, the process repeats itself until the header CRC is passed.

- 2. If the header passes the CRC check, the length of the frame is obtained and all the false flag occurrences falling within the range of the frame are ignored.

By using this simple procedure a very large majority of the false flags are ignored.

## 3.4.3 Encoder/Transmitter DSP Card

The Encoder/Transmitter DSP Card contains the following C software modules:

- **CRC Encoder** is responsible for calculating the Frame Check Sequence (FCS) bits and is able to use generator polynomials up to 32 bits.

- Rate 1/2 Convolutional Encoder outputs two data streams representing the two modulo-2 adders of the encoder. A simple module named Combine is required to interleave the two outputs of the adders. The two generator polynomials are  $G_1(x) = x^4 + x^3 + 1$  and  $G_2(x) = x^4 + x^2 + x^1 + 1$  and are user configurable.

- **Puncture Module** individually punctures the two data stream outputs of the rate 1/2 convolutional encoder. The module punctures according to the perforation matrix  $P_i$  which is chosen by the host SW ARQ protocol. **Combine** is required in order to interleave the two punctured outputs of the encoder adders.

- **Block Interleaver** accepts the coded symbols in 128, 256, or 512 bit blocks. The interleaver may be visualized as a rectangular array of *I* rows and *n* columns. The encoded symbols are read into the array by rows and read out by columns. The vertical dimension of the array, *I*, is called the interleaving degree and is user configurable by selecting values of 4, 8, and 16. The prototypes tested used an interleaving degree of 16.

- Queueing Module manages an 8 slot queue and is responsible for beginning and terminating the operations of the  $\pi/4$  shift DQPSK baseband generator.

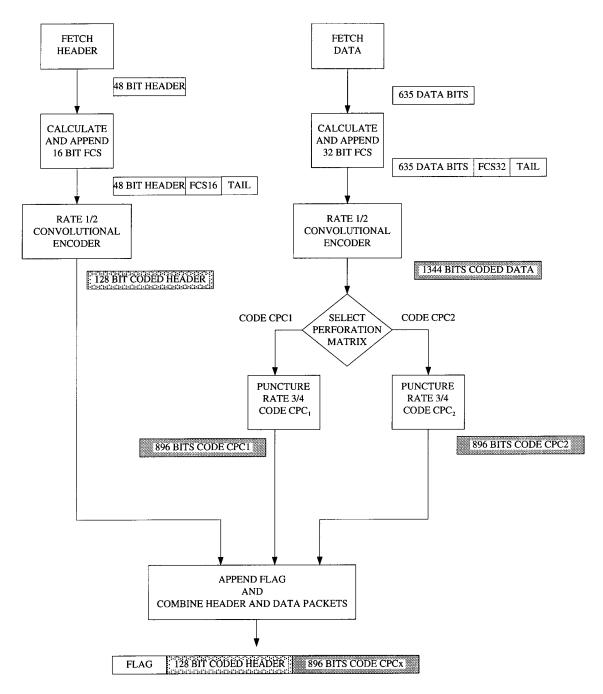

It is the main program written in DSP Assembly language which utilizes the above software modules and provides the encoding and transmitting services required by the host protocol. Figure 3.5 is a detailed description of the self explanatory procedure followed by the main program to encode and construct a frame. The two final operations not shown would be to interleave the frame and place it in the queue for transmission. The header and data are fetched from the Dual Access Memory.

Figure 3.5 Frame Encoding and Construction Algorithm of DSP Transmitter Card.

## 3.4.4 Receiver/Decoder DSP Card

The Receiver/Decoder DSP card contains the following DSP Assembly software modules:

- **Flag Correlator** is used to locate the occurrence of a flag in a data stream according to a user set threshold value. Section 3.4.2 gives a detailed explanation of this software module.

- Transform is responsible for transforming the soft  $\pi/4$  shift DQPSK data to soft QPSK data and as a result eliminate the dependency between neighboring symbols. Section 2.5 discusses this transformation and its results.

- Soft Data Deinterleaver is required to deinterleave the soft QPSK data. This module

operates on soft data as compared to its inverse module Block Interleaver which

operates on hard data.

- **CRC Encoder** is the same module used by the transmitter DSP card. The difference is that the calculated Frame Check Sequence (FCS) is compared to the received FCS in the decoding mode.

- Data Sequence Combiner is responsible for combining soft data sequences of different codes, such as CPC<sub>1</sub> or CPC<sub>2</sub>, to form a more powerful code for error correction purposes.

- Rate 1/2 Soft Decision Viterbi Decoder is utilized to decode the header and data according to the perforation matrix used in the encoding process.

- In the CPC SW Type II ARQ scheme with *code combining*, an additional module called **Code Combining**, which optimally combines data sequences of equal codes such as CPC<sub>1</sub>, is required.

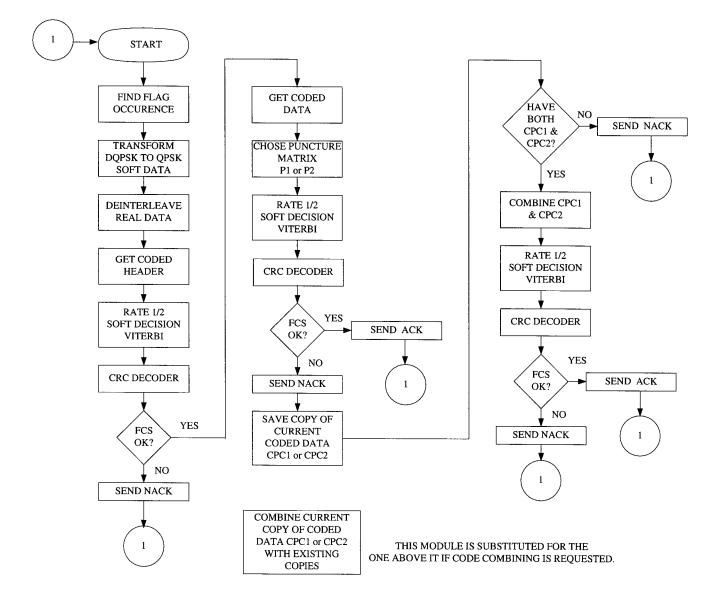

Figure 3.6 is a detailed flow chart of the Receiver/Decoder DSP algorithm. The algorithm is a direct result of the general scheme presented in Section 3.3 with p=2 CPC codes of CPC<sub>1</sub> and CPC<sub>2</sub>. As shown in Figure 3.6, the replacement of a module is necessary in order to incorporate *code combining*. Rather than simply save the most current corrupted data sequence of code CPC<sub>1</sub> or CPC<sub>2</sub>, the module combines the current sequence with all previous corrupted sequences of the same code for further subsequent decoding.

Viterbi Decoder A 16 state rate 1/2 soft decision maximum likelihood Viterbi Decoder is the heart of the receiver. It is entirely written in DSP Assembly Language for speed and efficiency. The soft decision decoding scheme makes use of past information bit history and a metric function to decode the incoming data. It follows, that the performance of the Viterbi decoder is primarily influenced by the choice of path history length and the metric function. It is common practice to select a path history length equivalent to four or five times the constraint length of the encoder which results in negligible degradation from the optimum decoder performance [14]. In the case of the prototype, the constraint length is 5 and the path history length utilized is 32 information bits. The Viterbi decoder operates on soft QPSK data which is the product of the transformation of soft  $\pi/4$  shift DQPSK data. The metric chosen is the Euclidean distance based on the signal constellation of the QPSK signals. The Euclidean distance is defined as

$$D = \sqrt{(X_C - X_R)^2 + (Y_C - Y_R)^2},$$

(3.8)

where  $X_C$  and  $Y_C$  are the coordinates of the signal on the constellation for QPSK and  $X_R$  and  $Y_R$  are the coordinates of the received data. Calculating the metric as defined in equation 3.8 is a very tedious and time consuming operation. The square root operation is not performed, and although it is not a linear function, distance values without the square root operation work well because the relationship between x and  $\sqrt{x}$  is one-to-one and monotonic. To further simplify 3.8, one may expand the brackets and discard the squared terms to yield

$$D = X_C X_R + Y_C Y_R. (3.9)$$

There is a considerable amount of time saved in calculating 3.9 as opposed to 3.8.

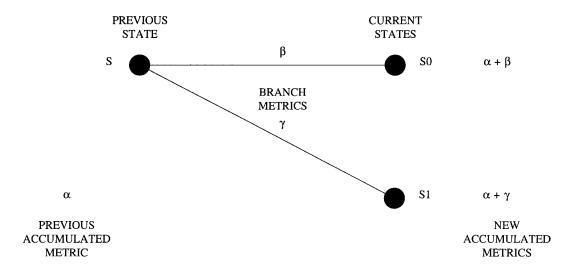

Once the Viterbi decoder is initialized, it will keep track of 16 surviving paths through the trellis. As depicted in Figure 3.7, at each new decoding instant, each survivor leads to two new states or paths, thereby yielding a total of 32 new paths. The decoder calculates the branch metrics  $\beta$  and  $\gamma$ , related to the two new states, and then adds them to the accumulated metric  $\alpha$  resulting in new accumulated metrics of  $\alpha+\beta$  and  $\alpha+\gamma$ . The smallest new accumulated metric will be chosen as the new surviving path.

Figure 3.7 Choosing a Path Survivor.

In practice, it is not possible to continue to accumulate the metric distances without encountering an overflow problem. Therefore, a weighted accumulation method is used to determine the accumulated metric and is given as

$$D_{new} = \beta D_{old} + (1 - \beta) D_{branch}, \tag{3.10}$$

where  $0 << \beta <1$  denotes the weighting factor,  $D_{branch}$  is the branch metric, and  $D_{new}$  and  $D_{old}$  are the new and old accumulated distances respectively. This ensures that the new accumulated metric is bound. The value of  $\beta$  is a performance parameter which is chosen to be 0.98 in the implemented Viterbi decoder.

**Numerical Analysis** Given the free distance  $d_{free}$  and the distance spectra  $a_d$  and  $c_d$ , where  $a_d$  is the number of incorrect paths of Hamming weight d that diverge from the correct path and remerge with it sometime later, and  $c_d$  denotes the total number of bit errors in all the paths having Hamming weight d, the probability of a bit error for Viterbi decoding is upper bounded [15] by

$$P(B) \le \sum_{d=d_{free}}^{\infty} c_d P_d. \tag{3.11}$$

$P_d$  is the probability that a wrong path at distance d is selected and depends only on the channel and modulation scheme used [9].

For an AWGN channel and  $\pi/4$  shift DQPSK,  $P_d$  may be obtained as follows. The probability of a binary digit error for four-phase signalling over L statistically independent AWGN channels is given by [16] as

$$P_{4b}(e) = e^{\frac{-2E_{b}L}{N_{o}}} \left\{ \sum_{k=0}^{\infty} \left(\sqrt{2} - 1\right)^{k} I_{k}\left(\frac{\sqrt{2}E_{b}L}{N_{o}}\right) - \frac{1}{2}I_{0}\left(\frac{\sqrt{2}E_{b}L}{N_{o}}\right) + \sum_{n=1}^{L-1} C_{n}\left[\left(\sqrt{2} + 1\right)^{n} - \left(\sqrt{2} - 1\right)^{n}\right] I_{n}\left(\frac{\sqrt{2}E_{b}L}{N_{o}}\right) \right\}$$

(3.12)

where

$$C_n = \frac{1}{2^{2L-1}} \sum_{k=0}^{\infty} {2L-1 \choose k}$$

.

$P_d$  is the probability that a wrong path at distance d is selected and may be obtained from Equation 3.12 by substituting d for L. Using 3.11 and 3.12 with the substitution, an upper bound for the performance of the rate 1/2 Viterbi decoder was calculated. Figure

3.8 depicts the resulting upper bound using a rate 1/2 code with weight spectrum given by Table 3.

| Rate | Generator Polynomials | $d_{free}$ | $(a_{dfree+j}, j=0, 1,4)$<br>$\{c_{dfree+j}, j=0, 1,4\}$ |

|------|-----------------------|------------|----------------------------------------------------------|

| 1/2  | 23, 35                | 7          | (2, 3, 4, 16, 37)<br>{4, 12, 20, 72, 225}                |

Table 3 Distance Spectrum of Code with Rate 1/2.

Computer Simulation A C computer simulation was used to verify the prototype Viterbi decoder's performance. The computer model simulates the prototype which uses a  $\pi/4$  shift DQPSK modulation system with the receiver transforming the soft DQPSK data to soft QPSK data for decoding purposes. Figure 3.8 shows the BER curve resulting from the computer simulation. As a result of transmitting  $10^6$  bits for each SNR level tested, the BER curve is accurate for points above  $10^{-5}$ . The simulation BER curve is below the upper bound curve for all accurate SNR levels tested.

Viterbi Decoder Performance Figure 3.8 illustrates the probability of a bit error for the Viterbi decoder implemented. For each SNR level tested, the Viterbi decoder processed 10<sup>7</sup> bits. As is evident, the prototype curve is slightly worse than the simulation curve but close to the upper bound curve. This is expected since the simulation cannot take into account implementation losses. The small deviation between the simulated and prototype curves is due to the imperfect modulation system and synchronization timing. The rate

Figure 3.8 Rate 1/2 Soft Decision Viterbi Decoder Performance.

1/2 soft decision Viterbi decoder implemented operates as expected and its performance is verified by the computer simulation and upper bound curves.

# **Section 3.5 Prototype Performance**

In this section the throughput performance of the prototype CPC SW Type II ARQ system in AWGN is compared to the ideal numerical results. The prototype's throughput performance in a Rayleigh fading channel is also presented and discussed.

## 3.5.1 Throughput Analysis

The throughput  $\eta$  is defined as the average number of accepted information bits per transmitted channel symbol and has a maximum possible value of 2 for DQPSK modulation. In general,  $\eta$  may be defined as  $R/\bar{N}$ , where R is the code rate and  $\bar{N}$  is the average number of packets transmitted per correctly decoded packet. If the error detection parity bits along with the overhead of the header and flag are taken into account, the resulting throughput is

$$\eta = \frac{R}{\bar{N}} L_{ED} L_{OH} , \qquad (3.13)$$

where

$$L_{ED} = \frac{k}{k + n_{dp} + m}$$

,

and

$$L_{OH} = \frac{(k + n_{dp} + m)\frac{1}{R}}{\frac{1}{R}(k + n_{dp} + m) + h + f}.$$

The factor  $L_{ED}$  is the loss in throughput due to the addition of parity bits  $n_{dp}$  and the tail of m known bits. The factor  $L_{OH}$  is the loss in throughput as a result of the overhead incurred by the frame for appending a rate 1/2 header, h, and a flag, f, to each block of k information bits. The average number of packets transmitted per correctly decoded packet,  $\bar{N}$ , for a CPC SW Type II ARQ scheme is given in [11] as

$$\bar{N} \le \left(1 + \sum_{i=1}^{p-1} Pr\{D_d(i)\}\right) \frac{1}{1 - Pr\{D_d(p)\}} , \qquad (3.14)$$

where  $D_d(j)$  is the event {decoded sequence obtained by combining j equivalent codes, is detected in error}. As in [11],  $Pr\{D_d(j)\}$ , assuming the undetected error probability is negligeable, is bounded as

$$Pr\{D_d(j)\} \le 1 - (1 - P(E))^l$$

, (3.15)

where P(E) is the error event probability of Viterbi decoding with a code obtained by combining j equivalent CPC codes (i.e.,  $CPC_1+CPC_2+...+CPC_j$ ) and where l is the number of trellis level  $(l=(k+n_{dp})/b)$ .

P(E) is bounded as [15],

$$P(E) \le \sum_{d=d_{t_{ree}}}^{\infty} a_d^j P_d \quad , \tag{3.16}$$

where  $P_d$  is the probability that a wrong path at distance d is selected, and where  $d_{free}^j$  and  $a_d^j$  are the free distance and weight spectra of the code obtained by combining j equivalent CPC codes.  $P_d$  is dependent on the channel and modulation scheme employed [9].

**Numerical Results** Table 4 contains the distance spectra for the rate 3/4 punctured convolutional code used in the CPC SW Type II Scheme.  $P_d$  is given in Equation 3.12,

| Code                                | Perforation Matrix                                     | $d_{free}$ | $(a_{dfree+j}, j=0,15)$    |

|-------------------------------------|--------------------------------------------------------|------------|----------------------------|

| CPC <sub>1</sub>                    | $\begin{bmatrix} 1 & 0 & 1 \\ 1 & 1 & 0 \end{bmatrix}$ | 3          | (1, 2, 23, 124, 576, 2852) |

| CPC <sub>2</sub>                    | $\begin{bmatrix} 1 & 1 & 0 \\ 0 & 1 & 1 \end{bmatrix}$ | 3          | (1, 2, 23, 124, 576, 2852) |

| CPC <sub>1</sub> + CPC <sub>2</sub> | $\begin{bmatrix} 2 & 1 & 1 \\ 1 & 2 & 1 \end{bmatrix}$ | 8          | (1, 4, 3, 11, 18, 38)      |

Table 4 Distance Spectra of Rate 3/4 Punctured Convolutional Code of Memory m=4.

where d is substituted for L. Using the values in Table 4 and Equations 3.13, 3.14, 3.15,

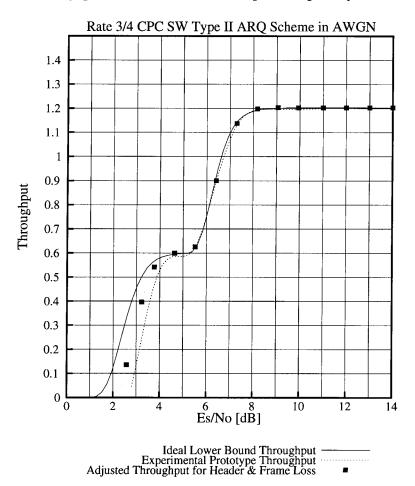

and 3.16 a lower bound on the throughput for an AWGN channel with  $\pi/4$  shift DQPSK modulation can be calculated. The resulting lower bound is plotted in Figure 3.9.

# 3.5.2 Experimental Throughput

The rate 3/4 CPC SW Type II ARQ scheme is tested over several SNR levels by executing the scheme until 1000 frames are successfully delivered. The resulting throughput is plotted in Figure 3.9 along with the previously calculated lower bound. Note that the throughput, which is the average number of information bits accepted per symbol, can be greater than one. This is a consequence of using  $\pi/4$  shift DQPSK which has a maximum throughput of 2 information bits per accepted symbol. For medium to

Figure 3.9 Numerical and Experimental Throughputs.

high SNR levels, the experimental curve and the lower bound are in good agreement. This is expected, since the Viterbi BER curve plotted against its upper bound is also in good agreement. At low SNR levels, the prototype throughput has a maximum degradation of 1dB. The calculated lower bound does not take into account header failures or lost frames. Whereas when the prototype encounters a lost frame or header failure, the entire data packet is discarded and taken into consideration for the throughput calculation. If header failures and lost frames are accounted for, the throughput of the system in question will suffer a decrease. To further prove this point, Figure 3.9 also plots a curve labelled as "Adjusted Throughput for Header & Frame Loss". This curve is obtained by ignoring lost and header damaged frames in the prototype system. Recall, that the receiver is capable of transmitting a NACK which indicates whether the frame had a header failure or data failure. The transmitter keeps track of the type of NACKs, as well as the lost frames (time-outs). It is this information which is used to adjust the throughput for header failure and frame loss. It is clear that this adjusted curve is in good agreement with the lower bound with slight degradation at low SNR levels resulting from implementation losses which are critical at lower SNR levels. The scheme is able to correct a certain number of errors. At medium to high SNR levels, the scheme easily corrects the channel errors as well as the errors associated with the implementation losses. At low SNR levels, the number of channel errors in addition to the implementation loss errors places a load on the scheme and results in a negligeable degradation of 0.5dB (maximum) from the lower bound curve. The implementation losses are factors such as:

- imperfect symbol synchronization,

- non-ideal modulator and demodulator, and

ISI from the Butterworth filtering.

It is clearly evident that since the prototype rate 3/4 CPC SW Type II ARQ scheme is in very good agreement with the lower bound, it is correctly operating and behaves as expected.

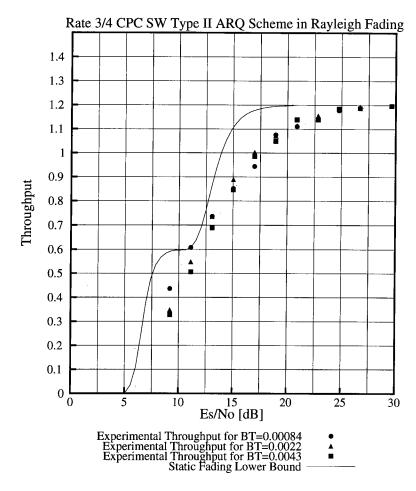

## 3.5.3 Rayleigh Fading Channel

The throughput of the prototype rate 3/4 scheme was also investigated in the combined AWGN and Rayleigh fading channel environment. The measurements were obtained for three  $B_DT$  products of 0.0043, 0.0022, and 0.00084. These  $B_DT$  products correspond to a  $\pi/4$  shift DQPSK system operating with a carrier frequency of 900MHz, a baud rate of 19.2kHz, and vehicle velocities of 100, 50, and 20km/hr respectively. The throughput curves are plotted in Figure 3.10.

For comparison purposes, a lower bound on the throughput for a combined AWGN and a static multipath fading channel is also plotted. The lower bound is calculated in the same fashion as before, by using Equations 3.13, 3.14, 3.15, and 3.16. The probability of a binary digit error for four-phase signalling over L statistically independent AWGN with static multipath fading is given by [16] as

$$P_{4b}(e) = \frac{1}{2} \left[ 1 - \frac{\mu}{\sqrt{2 - \mu^2}} \sum_{k=0}^{L-1} {2k \choose k} \left( \frac{1 - \mu^2}{4 - 2\mu^2} \right)^k \right],$$

where  $\mu = \frac{\bar{\gamma_c}}{1 + \bar{\gamma_c}}$ , (3.20)

and  $\bar{\gamma_c}$  is the average received SNR.

Figure 3.10 Throughput of Prototype in a Rayleigh Fading Channel.

As before,  $P_d$  is obtained from equating 3.20 by substituting d for L. The resulting lower bound is for a static multipath fading channel. The term static refers to the phase modulation of the multipath channel being constant (i.e., the receiver or vehicle being at rest). It is obvious that the three throughput curves obtained for the various vehicle speeds should be worse than the lower bound since the vehicle is not at rest. When the vehicle is in movement, the Doppler spread causes random phase modulations which in turn is responsible for the existence of residual error floors in the bit error rate as discussed in Section 2.6. In effect, the lower bound may actually be viewed as an *upper bound* when it is being compared to the prototype throughput at various vehicle speeds.

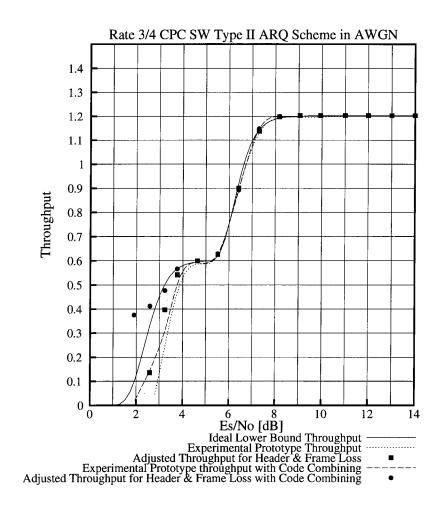

# Section 3.6 CPC SW Type II ARQ Scheme with Code Combining

The upgrading of the CPC SW Type II ARQ scheme to accommodate code combining is very simple. Only the receiver must be modified by the replacement of ten lines of DSP Assembly Language code. The new code or module ensures that the most currently received corrupted data sequence of code CPC<sub>1</sub> or CPC<sub>2</sub> will be combined with all previous corrupted copies of the same code (if the copies exist). The non-code combining scheme simply discards the previous copy of the corrupted data sequence once a new data sequence is received. It has been shown that code combining will increase the throughput of the scheme at low SNR levels [3].

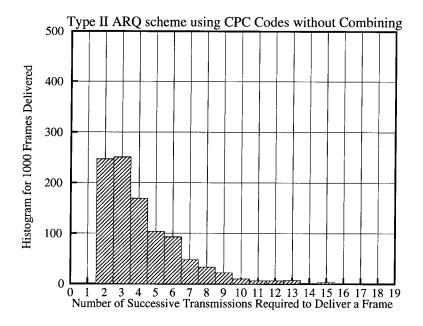

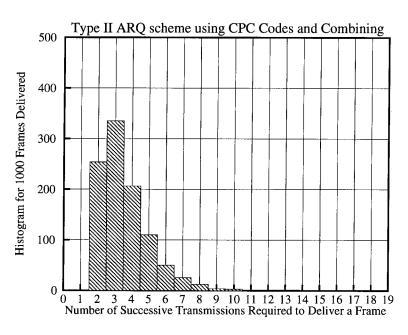

Figure 3.11 illustrates the experimental results for the rate 3/4 CPC SW Type II ARQ scheme with and without code combining. As expected, the code combining case resulted in an increase in throughput to a maximum of 1dB. If the code combining curve is adjusted for header failure and lost frames, it is expected to perform better than the ideal Type II lower bound curve. Recall, that the Type II lower bound curve does not take into account lost or header damaged frames. Figure 3.11 also displays the "Adjusted Throughput for Header & Frame Loss with Code Combining", which as expected has a substantial performance gain in throughput in comparison to the ideal Type II lower bound. To further verify the code combining scheme, measurements counting the number of frames transmitted to successfully deliver each of the 1000 frames at a certain SNR level were accumulated. Figures 3.12(a) and 3.12(b) are histograms representing the accumulated data for the non–code combining and code combining cases at a SNR level of 3.32dB. In comparing the two histograms, it is evident that the code combining case requires fewer transmitted frames to successfully deliver a frame since it is constantly combining data

Section 6 50

sequences. This results in the number of transmitted frames being concentrated toward the lower end of the histogram, as opposed to the non-code combining case where the number of transmitted frames are spread out. These experimental results verify the correct operation of the code combining scheme.

Figure 3.11 Throughput of CPC SW Type II ARQ Scheme with and without Code Combining

Section 6 51

SNR = 3.32dB with No Code Combining

SNR = 3.32dB with Code Combining

Figure 3.12 Histograms for Rate 3/4 CPC SW Type II ARQ with and without Code Combining

Section 6 52

## **Section 3.7 Conclusions**