# ELECTRONIC SYSTEMS

# A COURSE BASED ON ADULT EDUCATION PRACTICES

by

#### MIRO ANGELES

Diploma (B.Sc.), National Polytechnic Institute, Mexico, 1958 B. A. Sc., University of British Columbia, 1966 Diploma in Adult Education, University of British Columbia, 1972

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

## THE REQUIREMENTS FOR THE DEGREE OF

## MASTER OF EDUCATION

in

THE FACULTY OF GRADUATE STUDIES

(Department of Adult Education)

We accept this thesis as conforming to the required standard

THE UNIVERSITY OF BRITISH COLUMBIA

# August 1981

(C) Teodomiro Angeles-Salgado, 1981

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of ADULT EDUCATION

The University of British Columbia 2075 Wesbrook Place Vancouver, Canada V6T 1W5

Date SEPTEMBER 28, 1981

DE-6 (2/79)

## ABSTRACT

The causes of low student attendance for continuing education courses in electronics at the Pacific Vocational Institute (PVI) are analyzed. The unsatisfactory student persistence reflected inadequacies in the approaches used to instruct and in the textbooks utilized in these courses.

This report describes how modern principles of adult education were employed to identify these inadequacies and how the application of these principles was used to develop a new curriculum and a new book (appendix F). The new curriculum and its accompanying book not only incorporate the latest developments from the electronics industry, but they also incorporate the continuing application of adult education principles and practices.

The criteria for the selection of electronic components is discussed. The resulting component selection provides the students with a moderately priced kit that is easy to transport, and whose components find repeated application throughout the various experiments in the course.

The students' attendance records provide one index of the success achieved by the new course. These records show that the successful application of adult education principles has renewed the interest and promoted the active participation of continuing education students attending electronics courses.

Another indicative index of the success of the course is the result of field tests performed by other instructors at PVI as well as at other institutions. These results confirm that the new curriculum, the new book and the application of the recommended adult education practices provide the same successful responses as those experienced during the initial tests and development of the course.

ii

,

| ABSTRACT                                                                                   | ii |

|--------------------------------------------------------------------------------------------|----|

| ACKNOWLEDGEMENTS                                                                           | v  |

| INTRODUCTION                                                                               | 1  |

| THE CURRICULUM USED TO TEACH ELECTRONICS                                                   | 3  |

| STUDENT PERFORMANCE AND PERSISTENCE IN PREVIOUS PROGRAMS                                   | 5  |

| Day Program Students                                                                       | 5  |

| Continuing Education Students                                                              | 6  |

| IDENTIFICATION OF INADEQUACIES OF PREVIOUS APPROACHES                                      | 8  |

| The Old Curriculum                                                                         | 8  |

| The New Curriculum                                                                         | 10 |

| Teaching Practices                                                                         | 12 |

| Textbooks                                                                                  | 12 |

| TECHNICAL FACTORS LEADING TO THE DEVELOPMENT OF THE NEW<br>CURRICULUM AND THE NEW TEXTBOOK | 18 |

| DEVELOPMENT OF THE NEW CURRICULUM AND THE NEW TEXTBOOK                                     | 21 |

| Pre-requisites for the New Course                                                          | 21 |

| Title of the New Book                                                                      | 23 |

| SELECTION CRITERIA FOR LABORATORY COMPONENTS                                               | 25 |

| RECOMMENDATIONS FOR THE USE OF THE TEXTBOOK                                                | 28 |

| FIELD TESTING OF THE BOOK AND THE NEW COURSE                                               | 29 |

| INSIGHTS ACQUIRED FROM THE FIELD TEST                                                      | 31 |

| CONCLUSION                                                                                 | 32 |

APPENDICES

| A  | CURRICULUM COVERAGE OF THE TEN MONTH DAYTIME PROGRAM   | 33 |

|----|--------------------------------------------------------|----|

|    | Laboratory Materials in use for the Old Curriculum     | 36 |

| в. | THE NEW CURRICULUM                                     | 38 |

|    | Laboratory Materials for the New Curriculum            | 42 |

| С. | COST OF LABORATORY COMPONENTS FOR THE NEW CURRICULUM   | 43 |

| D. | ATTENDANCE RECORDS OF COURSES USING THE NEW CURRICULUM | 46 |

| Ε. | FIELD TESTING FROM WHITTIER UNION HIGH SCHOOL DISTRICT | 49 |

| F. | ELECTRONIC SYSTEMS BOOK                                | 51 |

.

# ACKNOWLEDGEMENTS

My sincere thanks to Dr. William S. Griffith for his encouragement during the development of the new course and the book (appendix F). His valuable suggestions and guidance will continue to assist me in future tasks.

I also acknowledge the late Dr. Coolie Verner who aided my early work in the field of Adult Education.

> Miro Angeles University of British Columbia August 1981

## INTRODUCTION

In this essay I am discussing the present teaching practices of electronics, in particular at post secondary education institutions. For the past three years I have taught this subject at the Pacific Vocational Institute in Burnaby, B. C., both during the day program and in the evening Continuing Education Program. This experience has brought me into close contact with both Day Program Students and Continuing Education Students. This close contact made me aware that the current practices in teaching this subject in the day program are successful as far as attracting sufficient students to justify giving the course and also that a large enough percentage of these students succeed in satisfying the course requirements. However, the same approaches did not seem to provide satisfactory results with the students of continuing education courses, who showed lack of involvement and a declining attendance after a few sessions of their course.

In this essay I describe both how I have attempted to identify and correct the basic weaknesses in the practices used to instruct the continuing education students, in accordance with the modern practices of adult education as elaborated in the literature, and the process that I followed in the preparation of a new textbook whose use requires approaches suitable for teaching adults, and which is meant to be used in a revised course.

This paper is organized into ten sections as follows: The curriculum used to teach electronics, Student performance and persistence in previous programs, Identification of inadequacies of previous approaches, Factors leading to the development of the new curriculum and the new book,

Development of the new curriculum and the new textbook, Selection Criteria for laboratory components, Recommendations for the use of the textbook, Field testing of the new book and the new course, Insights acquired from the field test, Conclusions. In the appendices the following materials are presented in addition to a copy of the new textbook: Curriculum coverage of the ten month daytime program, The new curriculum, Cost of laboratory components for the new curriculum, Attendance records of courses using the new curriculum, Field testing from Whittier Union High School District.

# THE CURRICULUM USED TO TEACH ELECTRONICS

As an electronics instructor in a ten-month program of Electronics taught at the Pacific Vocational Institute, I can describe the traditional curriculum and laboratory materials used for this subject, both during the ten-month day program, and during the four year Continuing Education Program.

The ten-month daytime curriculum<sup>1</sup> is a typical example of the organization of content taught in most post secondary electronics training centres throughout British Columbia. While I do not consider it totally inadequate for those students who can affort the time and are willing to immerse themselves in a course designed to train them in this discipline, I find both the content and the methods used in teaching it unsuitable for average adult students. I refer to this ten-month curriculum, when applied to continuing education courses, as the OLD CURRICULUM, to differentiate it from the proposed curriculum discussed in this essay and which is referred as the PROPOSED or NEW CURRICULUM.

The old curriculum is presented to the adult students as an imposed discipline whose planning does not involve their participation. The students confronted with this approach quite often fail to recognize how this curriculum will help them to understand, in a short period of time, the operation of modern electronics devices, unless they are prepared to devote a much longer time than they had previously anticipated. This extra time needed is not available to most of these students.

The Continuing Education program using this old curriculum also

Appendix A, Curriculum Coverage of the Ten Month Daytime Program.

utilizes the same laboratory facilities and techniques of the ten-month daytime program.<sup>2</sup> The continuing education program is offered two evenings per week during the winter sessions and students require four years to complete it.

The same basic material for the ten-month daytime courses is included in the continuing education courses, but under different names. For example, the first year continuous education courses are called Telecommunications Principles, Practical Mathematics and Engineering Science. The second year continuing education courses are called Telecommunications Principles A, Mathematics A and Computers A. The third and fourth years bear the letters B and C for each course respectively.

For the first year, Telecommunications Priniciples and Practical Mathematics are offered on Tuesdays and Thursdays respectively, from September to the first weeks in January. Engineering Science is then available, on the same days of the week, from January to the first weeks of May. The same schedule is followed for the second year, i.e. Telecommunications Principles A and Mathematics A are offered from September to the first weeks in January, and Computers A from January to the first weeks of May.

<sup>1</sup><sup>2</sup>Appendix A, Laboratory Materials in use for the Old Curriculum, p. 36.

Day Program Students

The enrollment for day programs in electronics is limited to a maximum of twenty students per class. Usually there are more applicants than spaces available for these courses. The selection of successful applicants is done on the basis of pre-requisites and date of the application for admission. The basic pre-requisites call for a certificate from secondary school, indicating the successful completion of the grade 12 mathematics and physics. Notification of eligibility to enroll in these courses is on short notice, usually less than a week. A total of 18 students normally register in a starting course. As a point of general observation and previous experience, during the first week, two to three students decide to withdraw from the course, and another two students quit within the next two weeks. The remaining students, fourteen to sixteen, usually persist to the end of the course.

The students who persist are usually very highly motivated. Some are sponsored by the Canadian Employment and Immigration Commission (C.E.I.C.) or other agencies, but in general they do not hold part-time positions. Thus, these students are able to spend full-time working on their studies. They are constantly involved with electronic equipment and appliances and have the opportunity to discuss problems in this area with more advanced students as well as with possible future employers. They often attend seminars offered by the local industry and they participate in field trips. All these contacts and exposure seem to strengthen their motivation, since they appear to be willing to study all the basic concepts, even those whose

usefulness is not apparent. In general they are active participants of the electronics discipline.

#### Continuing Education Students

The enrollment practices for continuing education students are similar to those of the day program. Although the academic background of the continuing education student is similar to that of the day program student, his persistence rate in these courses is much lower.

As an average, eighteen students have enrolled each September to take the first year courses, but no more than ten to twelve of them finish their first year. Of those students who finish the first year, only five to seven students enroll in second year courses.

Students in these courses are usually employed, though their employment may not be related to electronics. The great majority of them are employees of B. C. Telephone Company. Upon successful completion of their first year, this company revises and upgrades their work position. Therefore, it is in the students' interest to finish at least the first year course. Salary increases for second, third and fourth years of education are not as substantial as for the first year.

Other students who do not work for B. C. Telephone Company usually work for other electronics-related companies. They claim to be interested in improving their positions in the work force and in keeping abreast of the changes taking place in this rapidly advancing area.

Finally, there are students interested in a general understanding of this subject in order to appreciate the latest products from the electronics industry. In general, these last students are not interested in studying the fudamental theorems in great detail, since electronics is usually only of general interest to them. These students may work during the day on something that is unrelated to electronics. They lack contacts and exposure in the electronics industry and quite often do not discuss electronics matters at work. They often admit to being just observers on what is going on in electronics, rather than participants. Some of these students are not willing to spent time studying concepts unless an immediate application is found.

This last group of students does not enroll in more advanced courses because:

- a) Unless the student satisfies the pre-requisites for more advanced courses, he will not be admitted to them on the basis that the electronic equipment used in advanced laboratories could be hazardous to persons without their knowledge of safe and appropriate procedures.

- b) Even if they are accepted into the theory portion of more advanced courses, they would be unable to comprehend the advanced concepts because of their inadequate foundation in this area.

- c) The school will not run a course if the number of students is fewer than twelve, and usually there are insufficient applicants for these advanced courses.

Accordingly, few eligible continuing education students endure the first sessions of these courses, because these courses are based on a curriculum that offers no opportunities for their active participation. Instead of involvement, this old curriculum requires the students' acceptance of a coverage which most of them find unrelated to what they want to learn.

# IDENTIFICATION OF INADEQUACIES OF CURRENT APPROACHES

The Old Curriculum

The old curriculum requires the student to study the basic electrical coverage as it is defined from a disciplinary standpoint. Students often have difficulty identifying the purpose of this basic coverage because initially they do not have the knowledge to enable them to relate that basic coverage to the modern devices they want to assemble and operate. Also typically nobody explains the relationship to them. The coverage of this basic electrical material takes most of the initial time allocated in the old time schedules, a fact which discourages many students who do not have the desire to endure long periods of study in matters that do not seem related to their immediate occupational goals.

In these traditional courses the student is held responsible only for the material described by a rigid curriculum and is required to attend classes in which the instructor delivers canned audiovisual presentations without discussion. These students are not participants in the planning of their studies and they are not given the opportunity to learn how to define their goals or how to achieve them. Most of the students who endure the old curriculum do so in order to achieve an accreditation that eventually might be used to obtain a salary raise from the employers who subsidize part time studies. Regarding the expectation of a raise as a motivating factor we make reference to Malcolm S. Knowles. He considers the objective "being able to make more money" an important incentive to learning but he calls it an "interest" rather than a "need" and adds:

Interests are relevant to the adult educator's technology but in relation to his mission we are talking about something different and more fundamental - indeed, about something about which individuals are less conscious than they are of their interests. We are talking about the more ultimate needs and goals of human fulfillment. (1)

The fact that most students motivated by the expectation of a salary raise endure only one year of the old curriculum indicates that while their interests are satisfied, their ultimate needs are not being fulfilled.

The old curriculum does not consider the student's ever-changing needs and the contents of this curriculum are presented in a standard way to the student who is expected to accept their validity without question. This situation constitutes a violation of the modern practices of adult education, because, as is pointed out by Knowles:

> There is a distinct shift in emphasis in andragogy away from the transmittal techniques so prevalent in youth education the lecture, assigned readings, and canned audio-visual presentation - toward the more participatory experiential techniques. Indeed, "participation" and "ego-involvement" are

<sup>1</sup> Malcolm S. Knowles, The Modern Practice of Adult Education, (New York: Association Press, 1977), p. 23.

boldfaced words in the lexicon of the adult educator, with the assumption often being made that the more active the learner's role in the process, the more he is probably learning. (2)

The aftermath of using a standard curriculum without any consideration of differences among the adult students is that many of them leave the classroom after the first session and do not return.

The New Curriculum

The new curriculum relates more closely than the old to the developments that have attracted students to take a course in electronics. It teaches them how modern electronic circuits operate. By outlining the possible interconnections needed to produce the complex devices these students are eager to assemble, it makes the application of the knowledge readily apparent. A common example is that of students who want to learn electronics so that they can install visual displays in their cars, such as digital clocks, speedometers, tachometers or voltmeters. The new curriculum is designed to teach students as early as possible about the most common modern circuits used to make up those complex devices; how these circuits work; how to connect them; how to look for their corresponding technical specifications; how to evaluate their advantages and limitations; the kind of power supplies needed to operate them; how to select the components needed from technical catalogs; how to evaluate their cost; and how to assemble the devices.

<sup>2</sup>Malcolm S. Knowles, The Modern Practice of Adult Education, p. 45

· 10

I set out to develop the new curriculum following the guidelines of superior conditions of learning from Knowles<sup>3</sup> which call for a high level of student involvement. Thus, I have allowed the new curriculum to offer the student the opportunity to contribute suggestions regarding the depth of coverage as well as suggestions on special applications that they want to learn. This feature gives the students the opportunity to get involved in their own learning immediately at the beginning of their course.

Such involvement at the beginning of previous courses seldom took place, because the contents of previous curricula call for the lengthy coverage of basic material before the students can begin to appreciate how this coverage will satisfy their original interests in particular applications. Students taking courses using this old approach must endure a coverage that in its initial stages appears unsatisfactory and remote to their felt needs, failing thus to promote their involvement.

The approach and coverage of the new curriculum requires that the instructors find out, during the first session, what is it that the students want to learn and the type of applications in this field that interest them most. Then, based on the students' response, the instructors must set out to determine the necessary depth of coverage and extra materials needed to satisfy those desires in the shortest possible time. This approach is possible because of a new and careful selection of material coverge utilizing present technical innovations.

When I discussed the new plan and content for the achievement of

<sup>3</sup>Malcolm S. Knowles, The Modern Practice of Adult Education, p. 52.

their objectives with the students, I found they did not object to the challenge of participation, and willingly set out to research and study on their own. This corroborated Knowles' statement that learning is internally motivated and:

> The important implication for adult-education practice of the fact that learning is an internal process is that those methods and techniques which involve the individual most deeply in self-directed inquiry will produce the greatest learning. (4)

#### Teaching Practices

Some instructors claim that the old curriculum contents are not suitable for discussion, at least during the initial stages of the course. They feel that new students will require long periods of training before they can make any worthwhile contribution. Therefore, these instructors deliver their lectures using a factual approach without any discussion. These teaching approaches violate the modern practices of adult education because they fail to involve the students.

# Textbooks

Most of the texts suggested for previous courses in electronics are no more than factual presentations of the theory in this field.

<sup>4</sup>Malcolm S. Knowles, The Modern Practice of Adult Education, p. 51.

The following is a list of commonly recommended reference books for electronics courses at PVI:

Herbert W. Jackson, Introduction to Electric Circuits, (New Jersey: Prentice-Hall, 1981)

Bernard Grob & Milton S. Kiver, Applications of Electronics, (New York: McGraw-Hill, 1966)

Training Publications Division of the Naval Personnel Program Support Activity, Washington, D. C., Basic Electronics, (New York: Dover, 1973)

Robert L. Shrader, Electronic Communication, (New York: McGraw-Hill/ Gregg Division, 1980)

T. A. Lovelace, Engineering Principles, (Hong Kong: Thomas Nelson and Sons, 1976)

R. N. Renton, Telecommunication Principles, (Bath, Great Britain: The Pitman Press, 1973)

G. L. Danielson & R. S. Walker, Radio and Line Transmission, (London: Iliffe Books, 1969)

The design of the above books anticipates that the approach will be accepted by the students without question regarding their validity, therefore ' their approach is not conducive to student involvement and violates fundamental principles of adult education.

The circuit schematics presented in most textbooks are in general not meant to be assembled. These schematics are meant to illustrate isolated theoretical descriptions. Besides being incomplete, these schematics depict circuits that often will not work when connected as shown in these textbooks. This is why in most present day books the schematic diagrams are drawn quite small, since the author does not expect the student to attempt their assembly, therefore neither the author nor the publisher is concerned about their legibility in a laboratory setting. - Only persons with extensive knowledge of electronics would feel confident enough to even attempt assembling these circuits, which require a great deal of knowledge, resources and time. These persons must be willing to investigate the many sources of technical data and be able to read, interpret and understand such sources. They must also possess a working and practical knowledge of commercially available components and be familiar with the wide range of expensive laboratory equipment needed to assemble and test prototypes of these circuits. In essence, these persons must have a deep understanding of laboratory procedures, component selection, test procedures and trouble-shooting techniques and must feel quite confident in their ability to assemble projects. These persons are not average students and constitute only a small minority compared with the vast majority who are eager to attain an adequate level of expertise.

The average student who attends adult education courses becomes quite frustrated in his attempts to assemble a circuit from the skimpy information provided by ordinary textbooks because he does not have this advanced knowledge. To the average student the task of comprehending this kind of presentation is not only an immense obstacle in his learning but also inhibits his gaining the necessary confidence to proceed successfully with studies in his chosen field. This is probably one of the reasons many students become despondent in their efforts to learn electronics. Students who are determined to continue their studies using these books quite often find themselves unable to describe the operation of various circuits without making constant reference to the text. This is because these students have not been given the opportunity and guidance to become involved in the development, the practical assembly, and the testing of those circuits.

While searching for a suitable textbook to be used with the new proposed curriculum, it soon became apparent to me that none of the available books contained the desired coverage nor conformed to adult education standards. Many books were found to be out of date, some were too advanced for use in continuing education courses and still others could only be used as technical reference manuals.

The out-of-date books do not address the present needs of the students. Many of these books still show the use of obsolete devices, such as vacuum tubes, which are no longer commercially available.<sup>5</sup> Most of them do not consider integrated circuits in their coverage.

The advanced textbooks expect the learner to be familiar with all the basic literature, i. e. they assume that the learner has acquired most of the basic knowledge as well as most of the more advanced concepts (which take many years of intense study to acquire), in order to appreciate much of the material that the authors consider unnecessary to explain. These books are apparently intended for university students or graduates in the sciences and not for the average person who does not possess many of the pre-requisites.<sup>6</sup>

<sup>5</sup>Bernard Grob & Milton S. Kiver, Applications of Electronics,(New York: McGraw-Hill, 1966)

Training Publications Division of the Naval Personnel Program Support Activity, Washington, D. C., Basic Electronics, (New York: Dover, 1973)

Robert L. Shrader, Electronic Communication, (New York: McGraw-Hill/ Gregg Division, 1980)

T. A. Lovelace, Engineering Principles, (Hong Kong: Thomas Nelson and Sons, 1976)

R. N. Renton, Telecommunication Principles, (Bath, Great Britain: The Pitman Press, 1973)

G. L. Danielson & R. S. Walker, Radio and Line Transmission, (London: Iliffe Books, 1969)

<sup>6</sup>Joseph A. Edminister, Electric Circuits, (New York: McGraw-Hill, 1965) T. P. Sifferlen & V. Vartanian, Digital Electronics with Engineering Applications, (Englewood Cliffs, N. J. : Prentice-Hall, 1970) Another kind of book is the technical manual published for diverse electronics companies. These manuals are meant to be used only for the training of employees within the particular company that issues them. The manuals usually contain reference material about the construction and operation of the company's products and equipment. To understand their contents, and employee must receive instruction from a company's training supervisor, usually in specialized training centers where the different products and equipment are discussed. In general it is very difficult to interpret the contents of these manuals without the equipment or the guidance of a person conversant with it. Therefore, these manuals are unsatisfactory for self-directed studies. They can be classified only as reference material.<sup>7</sup>

Finally there are books of the "cookbook" type which contain a selection of circuit schematics collected from a wide range of designers. Many of these books advertise their projects as: "do-it-yourself electronics" and promise that all the projects are easy to build. The presentation of these circuits is not organized in an educational manner, since no educational outcomes are expected nor planned for the person who purchases the book. The purpose of the books is generally limited to serving as

<sup>7</sup>The following are examples of company publications using this approach:

IBM Systems Development Division, 1443 N1 Printer, (North Carolina: IBM Product Publications, 1968) Olivetti/General Electric, GE 115/2 CR 10 Subsystem, (Italy: General Electric Information Systems Division, 1966) Hewlett Packard, Model 2402A Integrating Digital Voltmeter, (Palo Alto, California: Hewlett Packard Company, 1969) The Decca Navigator Company, Loran C (Long Range Aid to Navigation) Model DL91, (Surrey, England: Decca Technical Publications Department, 1975)

reference material for experienced technicians who design electronic circuitry.<sup>8</sup>

The type of presentation used in technical manuals is useful when company trade procedures are to be kept relatively private among the employees of those companies. Unfortunately, many authors make use of similar presentation in their books. One of the immediate results is that these books appeal only to a few selected students.

David Hume<sup>9</sup> pointed out to me on a conversation held last May 1981, that the above textbook presentations appeal to some instructors, unsure of themselves, who find satisfaction from the admiration and respect that they seem to command when they interpret the content of those books to their students. Mr. Hume indicated also that these instructors generally do not appreciate books with clear presentations because such books eliminate the satisfaction that these instructors derive from interpreting obscure texts.

I find that this type of presentation leads to frustration for most students, and misleads them into thinking that the subject is beyond their capabilities unless they receive adequate help.

<sup>8</sup>Don Lancaster, TTL Cookbook, (Indiana: Howard W. Sams, 1977) Don Lancaster, CMOS Cookbook, (Indiana: Howard W. Sams, 1978)

<sup>9</sup>David Hume, Director of Extension Services, British Columbia Institute of Technology, Burnaby, B. C.

# TECHNICAL FACTORS LEADING TO THE DEVELOPMENT OF THE NEW CURRICULUM AND THE NEW TEXTBOOK

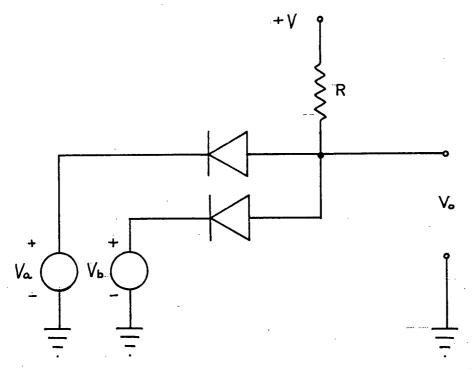

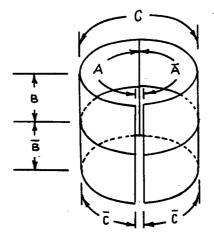

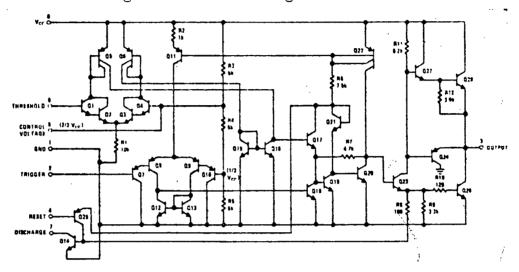

Present technical innovations have made possible the development, production and marketing of micro-miniature electronic circuits. These circuits are known as Integrated Circuits (IC's) and are available to the consumer in conveniently sealed packages. Compared with previous conventional circuits they are physically small, inexpensive, require small amounts of power to operate, are very reliable and can be used in many applications. These are the main reasons why they are replacing with an unprecedented rapidity the big, bulky, and expensive circuits that formerly were custom built for each particular application or piece of equipment.

Integrated circuits contain thousands of electronic components reduced by photographic means into microscopic sizes. They are then enclosed into small packages and are ready to be used. Their production in large quantities has permitted manufacturers to reduce their price, making their use economically attractive. The electronics equipment that uses integrated circuits is smaller, lighter, requires less power to operate, and its repair and maintenance are greatly facilitated by the easy replacement procedures possible only with integrated circuits, further reducing the costs of their operation.

Integrated circuits are compatible with different electronic configurations, and can be reused repeatedly. This universal acceptability of a common set of circuits is already paving the way to an overall standardization in the electronics industry that will affect all the present industrial processes. Examples of this acceptance can be found easily, such

as in the circuits used to represent voice and television images. These television images are being transmitted from country to country, where different and incompatible television systems may be in use, by decoding and translating digital information into their own television system prior to local re-broadcasting. Another example is the use of laser beams to carry telephone conversations, where these conversations are transmitted digitally. Even more recently, digital records have made their appearance in the consumer's market.

The present state of the electronics technology offers the possibility of new material coverage in order to give the student the option for a simpler and shorter approach to his learning. The long periods of training needed using traditional approaches discouraged many students from taking the course. Thus the new curriculum calls for a change of the traditional order of presentation of topics that does not hamper the students' future progress. The development of the new curriculum required the rearrangement of previous materials, the addition of new materials, and the application of the latest innovations in electronics.

Instead of teaching the fundamental ideas on the components and design procedures that make up an electronic circuit, the new curriculum begins by teaching the operation and use of its pre-assembled equivalent, which is what many students are eager to learn. The experience gained by the student while using and operating pre-assembled circuits can be used then to facilitate his understanding of the basic theorems and mathematical principles behind them. Thus the new curriculum provides the students with the basic practical applications of electronic circuits and facilitates their future progress and advancement in this field.

Many attempts have been made to modify the old curriculum in order to accelerate the coverage of basic material. This has been done to introduce students much sooner to the applications that they want to learn. However all of these attempts have been unsuccessful, since they involve the removal of material from and old curriculum which does not lend itself to such changes, and the students still have to learn the removed material at unplanned stages of their course.

The new course and textbook are designed to involve the student, so that he can develop the confidence and abilities exhibited by highly qualified technicians in the design, assembly, and testing of electronic circuits and thus come to understand the procedures and techniques of this field.

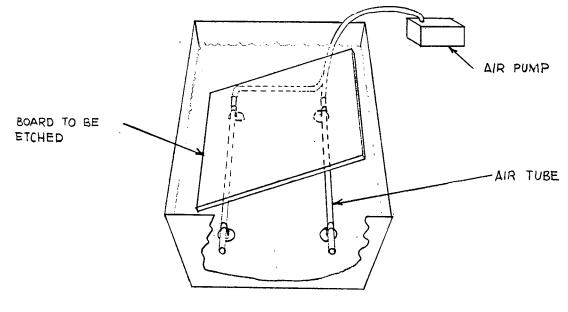

# DEVELOPMENT OF THE NEW CURRICULUM AND THE NEW BOOK

During the development of the new course and book, it seemed essential that relevant laboratory experiments were needed to follow any theoretical description mentioned in the text so that the student could verify that the theory is correct and thus proceed confidently to the next stages of his learning, because he now knows that what he is doing is right, not because it is written in a book but because the student himself has been able to verify it with actual electronic circuitry. The new course and new book call for the student to verify the theory behind each circuit at all levels of his training, from basic circuits to more advanced ones. This verification is facilitated with laboratory components whose careful selection allows the students to assemble, test, and prove to themselves that the theoretical statements in the book are indeed correct.<sup>1</sup>

# Pre-requisites for the New Course

The pre-requisites for the new course and the understanding of the book do not include university level mathematics or physics. In fact, the knowledge acquired by students who have completed courses such as tenth grade mathematics or physics is often sufficient to enable these students to complete the course successfully. Thus the course and its textbook become suitable for a great number of students, i. e. for students with related advanced studies as well as for those students that are newcomers to the field.

<sup>1</sup>Appendix F, Electronic Systems Book, p. 8

I have found that most of the advanced students generally welcome a thorough review of materials already familiar to them, because a review seems to refresh and reinforce their previously acquired knowledge. They also profit by learning new applications to this knowledge. As for the students with only a basic understanding of mathematics, they find that the material is explained in simple terms with plenty of analogies to which they can relate and understand.

The new curriculum and its book follow the procedures outlined by Knowles, who asserts:

The central dynamic of the learning process is thus perceived to be the experience of the learner, experience being defined as the interaction between an individual and his environment. The quality and amount of learning is therefore clearly influenced by the quality and amount of interactionbetween the learner and his environment and by the educative potency of the environment. The art of teaching is essentially the management of these two key variables in the learning process - environment and interaction which together define the substance of the basic unit of learning, a "learning experience." The critical function of the teacher, therefore, is to create a rich environment from which students can extract learning and then to guide their interaction with it so as to maximize their learning from it. (2)

This learning experience is accelerated by the confirming results from relevant laboratory experiments and produces the desired level of <sup>2</sup>Malcolm S. Knowles, The Modern Practice of Adult Education, p.51.

involvement of students as well as of the instructors who conduct the course. The application of these principles in the text has also permitted advanced students to use it as a self-study guide.<sup>3</sup>

Title of the New Book

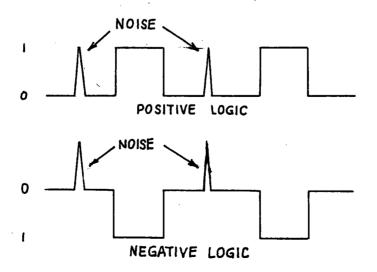

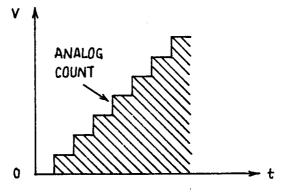

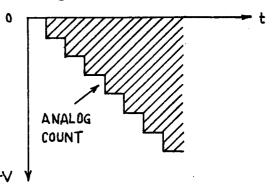

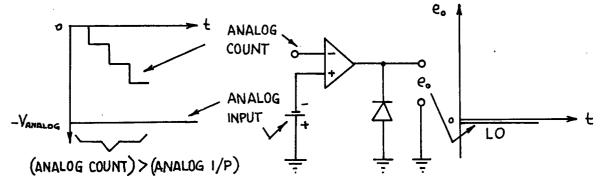

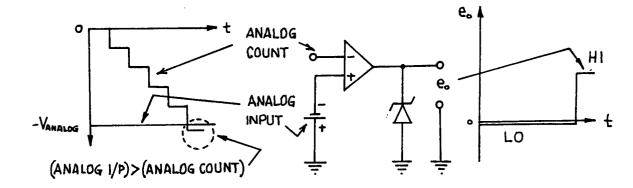

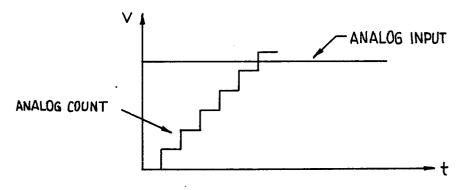

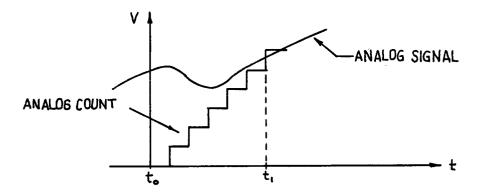

The title "ELECTRONIC SYSTEMS" was chosen for the textbook because it considers the circuits used in the evaluation, analysis and control of measurable physical phenomena. In present day technology, physical phenomena measurements are represented by equivalent values of voltage, known as ANALOG VOLTAGES, prior to their electronic processing. Electronic processing consists in storing, analyzing and comparing analog voltages against standard values that the designer or user may consider as desirable, e. g. the setting of an air conditioning dial to a desired temperature.

Twenty years ago, electronic processing was done using mostly analog devices, however these devices were useful to control only a limited number of physical applications. Now, thanks to the great versatility of available digital systems, that employ a universal mathematical system, the only restriction placed on analog voltages of any origin is their conversion into a digital form. This analog to digital conversion (ADC) combines both analog and digital techniques.

After the above conversion has taken place, the resulting figures are processed digitally and the answers converted back into analog voltage form. These analog results are then used to activate electrical controls that correct the intended physical phenomena. The digital to analog conversion (DAC) also makes use of digital and analog techniques. This book and the

<sup>3</sup>Appendix E, Field Testing from Whittier Union High School District.

new curriculum are concerned with ADC and DAC procedures, as well as with the basic processes taking place in the digital processor, therefore the contents cover both digital as well as analog techniques, and justify the title "ELECTRONIC SYSTEMS".

# SELECTION CRITERIA FOR LABORATORY COMPONENTS

As previously discussed, the development of integrated circuits offers countless possibilities to improve on previous approaches. Their availability has facilitated the development of this new curriculum, permitting the introduction of advanced circuits at much earlier stages of the students' training than was possible before. In the new coverage it is no longer necessary to discuss the principles that led to the design of these integrated circuits, nor the operation of each of the components used in their construction, because this is the primary concern of design engineers. Therefore the new coverage considers only their operation and applications, which is what most students want to learn.

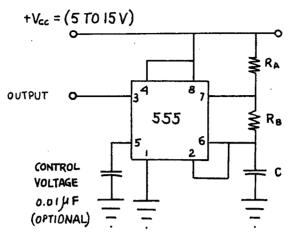

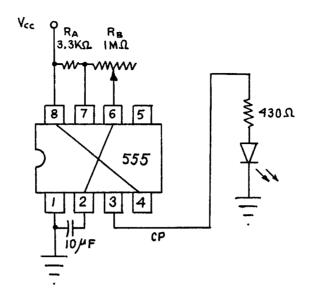

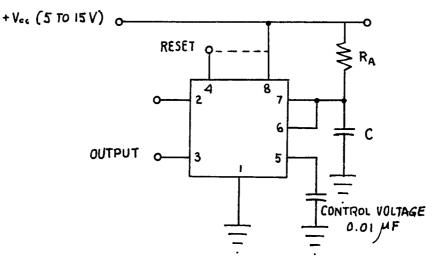

If a student were to assemble an equivalent circuit using the regular standard components, he would find that the resulting assembly occupies several hundred times the space of the original integrated circuit. The student not only would be faced with increased space requirements, but also would have to waive the advantages that integrated circuits have on the previous technology, such as reduced power requirements, low static interference between components due to their close proximity, and above all, low costs that result from their production in assembly lines. For example, the purchase of an oscillator circuit in integrated circuit form, such as the 555 and which has been pre-tested to insure its proper operation, costs only 38 cents.<sup>1</sup> On the other hand, the assembly of its equivalent circuit using standard components that require an area comparable to that of a

<sup>1</sup>Appendix C, Cost of Laboratory Components for the New Curriculum.

standard brief case, costs in the vicinity of \$70.00. Thus the new technology also offers immense possibilities to improve on the cost of the components used in previous teaching approaches.

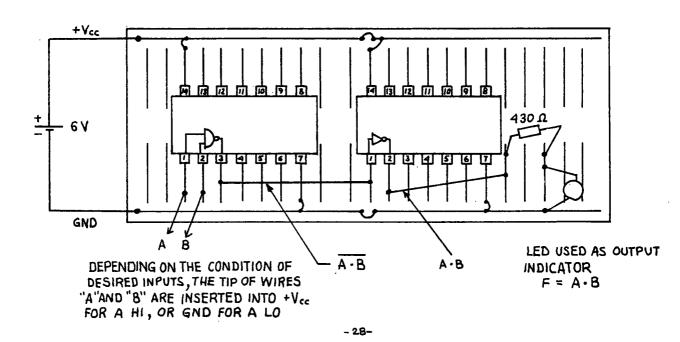

Up to the present, hundreds of dollars have been spent on standard laboratory equipment. If a student wants to purchase these standard laboratory facilities he would have to be prepared to invest at least \$1000.00 in order to purchase power supplies worth up to \$300.00, volt-ohmmeters worth up to \$200.00, signal generators worth up to \$200.00 and a few other pieces of test equipment. This estimate does not include oscilloscopes, since their unit price is close to \$1500.00. Compared with these costs, the use of integrated circuits described in the new curriculum and book amount to \$47.20.<sup>2</sup> The power supplies consist of inexpensive six volt batteries, that are sufficient to provide the power requirements of most integrated circuits. The components listed for the new curriculum also include the necessary parts to assemble an electronics test probe that is used as a voltage indicator throughout the course,<sup>3</sup> and the parts needed to assemble a signal generator.<sup>4</sup> It should be noted that the laboratory components used in standard laboratories and those proposed in the new curriculum are equally satisfactory in carrying out the experiments of the new curriculum, but not their price as indicated above.

The size of the components needed for this course, besides being within the economic reach of the students, facilitates their transportation. This factor allows students to take them home and carry out experiments there that otherwise would never have been possible using standard facilities.

<sup>2</sup>Appendix C, Cost of Laboratory Components for the New Curriculum.

<sup>3</sup>Appendix F, Electronic Systems Book, Section 1.

<sup>4</sup>Appendix F, Electronic Systems Book, Section 5.

Technical criteria for the selection of these components was based on their ease of handling and operation. Some specialized components can be damaged easily at the touch of the hand due to electrostatic charges in a human body. Special procedures are required for their handling. Their use was avoided to eliminate concerns that might distract the students while performing their laboratory experiments.

Finally, another criteria for the selection of laboratory components was their repeated use in different experimental configurations throughout the course. This consideration was meant to further reduce the cost of the components needed in the course without affecting the coverage of the book. This factor also helps students to realize that the same component can be used in different configurations to perform different functions.

## , RECOMMENDATIONS FOR THE USE OF THE TEXTBOOK

The proposed course and textbook are meant to provide the students with basic and fundamental coverage as well as with the advanced material required to understand and utilize the most recent developments in this field. They also aim to provide the students with the procedures needed to allow them to conduct their own inquiry and plan their own learning in this field. This is because the new curriculum is based on Knowles' guideline that the greatest learning is produced by methods and techniques that involve the students in their own self-directed inquiry. This does not mean that an instructor using the new curriculum should give up his responsiblility, but that he now has the option to use a process of reasoning and demonstration to convince the students of the utility of the objectives that he suggests.

Therefore instructors using the new curriculum and book are required to conduct class discussions in order to: consider the students' needs and goals, to help the students relate the new contents with their own goals, and to allow them to undertake reasonable objectives within the length of the course. Students with a sound knowledge and experience on technical matters can be expected to achieve much more in a shorter time than students who lack that kind of background. The new curriculum and book permit students of different backgrounds the opportunity to achieve their individual goals, providing the instructor is willing to coordinate and lead them in the achievement of their expectations.

# FIELD TESTING OF THE BOOK AND THE NEW COURSE

The first time the new curriculum was offered to students was during the winter session of 1979-1980 under the name of Electronic Systems Parts I and II. The students enrolled in this first course included high school teachers, engineers, electrical and electronics technicians as well as people with a general interest in this subject. Their diverse backgrounds provided the opportunity to test the efficacy of the new curriculum and its recommended teaching practices. The new curriculum proved effective in involving all the students in class without inhibiting the progress of the more advanced students. This involvement was evident by the excellent student attendance recorded from the beginning to the end of the course.<sup>1</sup>

During the initial winter session, I also carried out minor modifications on the curriculum under test, in order to improve the general continuity of its presentation. These changes led to the final preparation of the present curriculum in the summer of 1980,<sup>2</sup> and the completion and subsequent publication of the new book in September 1980.<sup>3</sup> This new curriculum was successfully tested once more during the winter session of 1980-1981.

The students performance has been assessed on the basis of their ability to design and assemble practical electronic devices, and not on a final exam. At the end of these courses each student has been requested to present projects that work as intended, according to the principles behind their operation. These students have shown a great degree of confidence in

<sup>1</sup>Appendix D, Attendance Records of Courses using the New Curriculum.

<sup>2</sup>Appendix B, The New Curriculum.

<sup>3</sup>Appendix F, Electronic Systems Book.

the selection of electronic components, in the assembly of circuits and in the use of test equipment. These factors corroborate the efficacy of the new curriculum that helps them achieve their desired goals at an earlier stage of their training than the longer periods previously expected from the old curriculum. The same findings have also been reported by other instructors at the Pacific Vocational Institute using this curriculum as well as at high school levels.<sup>4</sup>

<sup>4</sup>Appendix E, Field Testing from Whittier Union High School District

### - INSIGHTS ACQUIRED FROM THE FIELD TEST

The response from other instructors and teachers from PVI as well as from other institutions indicate that most of them have found the new curriculum and the new book most useful in their task. Their results confirm that there is an increased participation and involvement of students taking this course, and that advanced students have even managed to use the text as a guide to their self-directed study.<sup>1</sup>

Some instructors have mentioned that a few of their less advanced students have experienced difficulty understanding some basic mathematical concepts. Since the course calls for a basic knowledge of mathematics and electricity, I set to investigate the cause of these isolated difficulties. My impression is that in the introduction of new mathematical concepts, these instructors do not provide as many analogies as needed by these students so that they can relate the new concepts with their own experience. Therefore, in a second edition of this book more analogies will be included and others suggested to the instructors to further facilitate its readability to the largest possible number of interested students.

Additional material will include problems, more exercises and examples and the insertion of technical data as originally intended but withheld pending the permission to reprint from electronics manufacturers.

+ <sup>1</sup>Appendix E, Field Testing from Whittier Union High School District.

### CONCLUSION

At the Pacific Vocational Institute I observed a problem with continuing education courses in electronics. Students would enroll in beginners' courses but many of them would drop out after a few sessions. This situation seemed inconsistent with their initial interest. In my investigation of their reasons for discontinuing their course, it became apparent that they were discouraged by methods of instruction that failed to involve them and also by a curriculum whose contents did not appear related to the applications that they wanted to learn.

To solve this problem I constructed a new curriculum by combining two major developments: the modern principles of adult education as outlined by Knowles; and the most recent innovations that our present electronics technology has to offer, namely pre-assembled circuits. These two developments were put together to produce the new book "ELECTRONIC SYSTEMS" which requires adult education principles for its use and places great emphasis on the students' involvement.

The field tests done on the use of the new curriculum and the new book have basically confirmed the utility of the approach. The successful application of these principles is reflected by the popularity and interest that the course is enjoying, the regular attendance from participating students, the reports of successful field testing from other instructors and their financial backing in the purchase of books and accompanying electronic components.

<sup>1</sup>Appendix F, Electronic Systems Book.

### APPENDIX A

### CURRICULUM COVERAGE OF THE TEN MONTH DAYTIME PROGRAM

During the first month of the daytime program, electronics is taught with emphasis on the physical characteristics of the elements and materials used in electricity. The presentday theories about the atomic nature of electricity are discussed, as well as the conduction of electric currents through different media, i. e. solids, liquids and gases.

The Systeme International (SI) is introduced. To its basic three units to measure length, weight and time, a fourth unit is added: the AMPERE. This last unit is used to measure electrical currents, and together with the previous three units, it defines the essential aspects of an electrical system.

The need to represent quantities numerically is self-evident, because any measurement must be taken in relation or comparison with known values. A few examples of these comparisons are: twice as fast as, half as loud as, three times as heavy as, five times as far as.

The student is also taught that electrical quantities have a wide range of values, varying from millionths of a given quantity, to millions and billions of another quantity. This wide range of values brings the need for special notations, which are presented to the student as "Scientific Notation" or also called "Engineer's Representation of Numbers". In these notations, quantities are represented by a digit, 1 to 9, with or without a decimal, times the base number 10, and this base number may use positive or negative exponents as required, e.g.  $7.2 \times 10^6$ .

- Besides the above system, the student is introduced to the prefixes used by the electronics industry, such as MEGAhertz (one million hertz), or NANOsecond (one billionth of a second). The student is taught to relate the scientific notation to the industry's jargon.

The four basic elements that constitute an electric system are introduced: (1) Power Sources; (2) Conductors; (3) Control Elements, such as switches and fuses; (4) The Work-load, i. e. anything that requires electricity to do an intended amount of work.

During the second month, the student learns what physical characteristics of matter oppose the flow of electrical currents. The student gets inititated into the study of one of the three properties of electricity, i. e. RESISTANCE, which is the property that opposes the flow of electrical currents.

During the third, fourth and fifth month, the student learns electrostatics and magnetism, studies that lead him into the remaining two other properties of electricity, i. e. CAPACITANCE and INDUCTANCE.

During this period, the student is also introduced to circuit analysis techniques, that will enable him to predict how a given circuit will react to particular conditions of current and voltage, where the sources of energy for these studies consist of:

- a) Direct Current (DC), where the currents or voltages do not vary with respect to time.

- b) Alternating Current (AC), for given frequencies, where the currents or voltages alternate, being positive for one half a cycle and negative for the other half. The student is taught appropriate mathematical procedures, known as Complex

Ø

Variable, to help him determine the physical response of a circuit under this type of source.

c) Transient Conditions and response to Pulses. At this stage, the student needs to use more advanced mathematical procedures, in order to determine how a circuit will react to any particular pulse. These advanced mathematical procedures include the use of calculus.

The circuit analysis techniques are based on physical laws first defined by earlier scientists and that bear their names. These basic laws used in electricity are know as Ohm's Law, Kirchhoff's voltage law, and Kirchhoff's current law. These circuit analysis techniques include:

- a) Equivalent Circuits, where a circuit gets replaced by a dummy load without any effect on the source under study, and then the total current is defined, e. g. the loudspeaker in a radio may be replaced by a resistor, and though there is no sound, all the circuits continue normal operation.

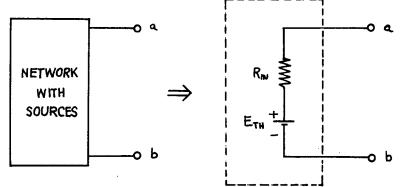

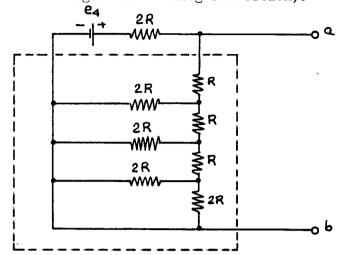

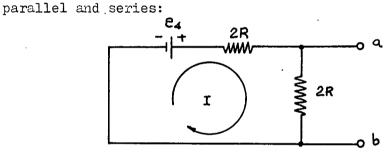

- b) Black Box Concept, which considers any circuit as a source together with an electrical component called impedance.

Impedance is the name of the combination of one or all the three basic properties of electricity, i. e. Resistance,

Capacitance and Inductance. Through this black box concept, a very complex circuit feeding power into a load, is replaced by a simple pair of elements, and the load will not miss any of its original supply circuits. As an example we can consider

AC/DC pocket calculators, which may be plugged into the power outlets or may be used with batteries.

The theorems that define the black box concept are known as: Thevenin's Equivalent Circuit and Norton's Equivalent Circuit.

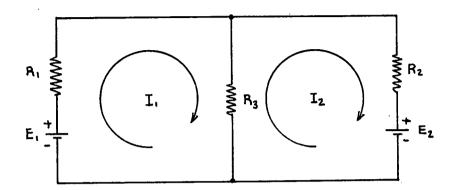

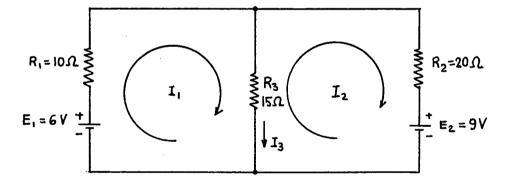

c) Loop Analysis Techniques, derived from Kirchhoff's voltage law.

d) Node Analysis Techniques, derived from Kirchhoff's current law.

In the sixth month, when the above principles and techniques have been mastered by the student, the student is introduced to devices that have the ability to amplify electrical signals. These devices are known as active components and include tubes and transistors.

The basic physical properties of matter are discussed in order to explain the operation of these devices.

During the seventh and eighthmonths, the student begins to study the basic electronic circuits. These basic circuits, common to any electronics application, fall under any of the three following groups: (1) Rectifiers; (2) Amplifiers; (3) Oscillators.

During the ninth and tenth months, the student begins to study specialized applications, such as: Radio Transmission, Radio Reception, Radar, Television, Microwave and Telephone Communications, Computers, Satellite Communications, Marine and Aircraft Electronics and Control Electronics.

Laboratory Materials in use for the Old Curriculum

The student is issued a laboratory kit. The kit contains tools and a set of discrete electrical components. Some of the tools include: soldering irons, pliers and screw drivers. The electrical components .36

include: resistors, capacitors, coils and chokes, transformers and connectors.

The test equipment is supplied as the experiments call for it. This equipment consists of Vacuum Tube Voltmeters, Volt-Ohmmeters and Oscilloscopes. The student also receives Power Supplies, Frequency Generators, Transistor and Tube Testers.

The student spends about four months on experiments that are strictly electrical in nature. These experiments use discret components of the passive type such as resistors, inductors and capacitors.

Another four months are spent in experiments that are electronic in nature. These experiments use active components, such as tubes and semiconductor devices. The semiconductors studied include: Rectifiers, Zener Diodes, Tunnel Diodes, Transistors and their applications to Amplifiers and Oscillators.

#### APPENDIX B

#### THE NEW CURRICULUM

The new curriculum has been covered in a new continuing education course at PVI. This new course has been taught in 32 evening sessions for a period of 16 weeks. Therefore, this appendix lists its coverage based on a weekly basis.

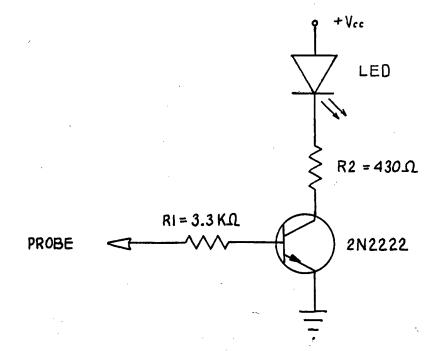

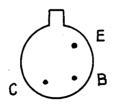

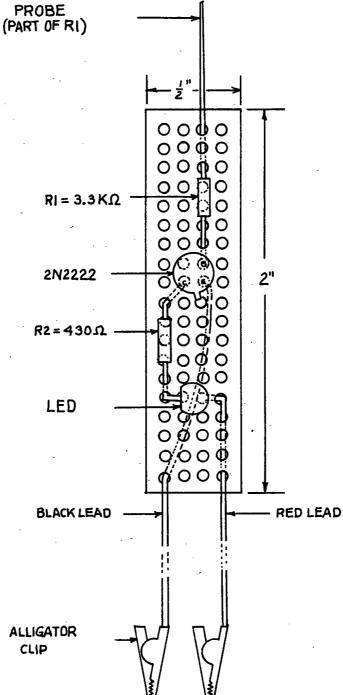

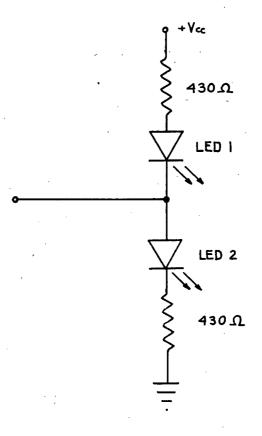

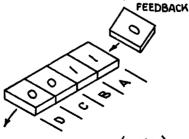

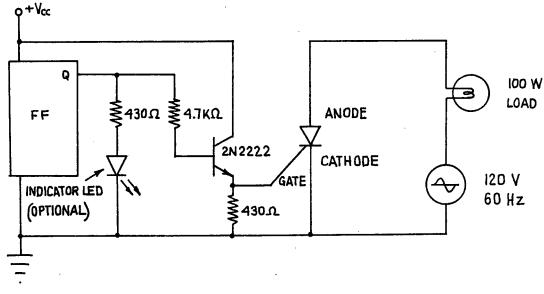

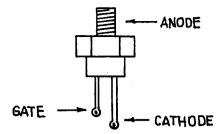

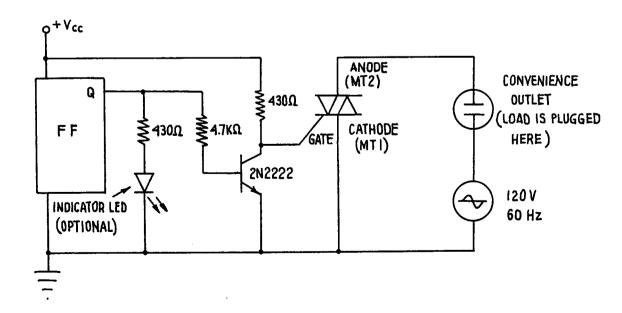

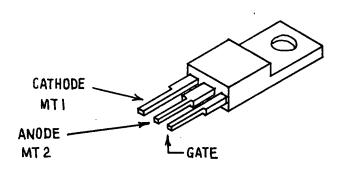

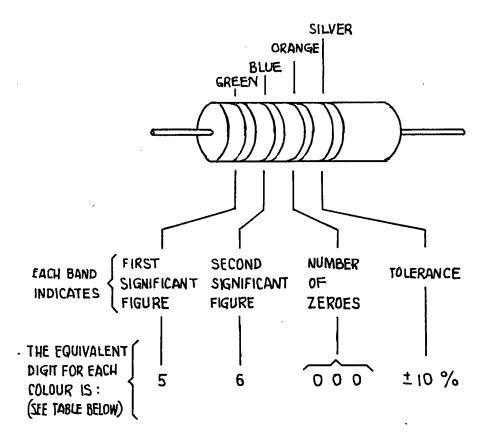

During the first week, the student is handed the electronic components used for the course. The student learns to identify them. This task includes the introduction to electrical color codes and the meaning of the physical size in these components. The student also learns to assemble a simple logical indicator, used to identify the presence of voltage. A basic explanation is given regarding the operation of transistors when used as ordinary switches in this indicator.<sup>1</sup>

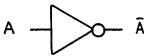

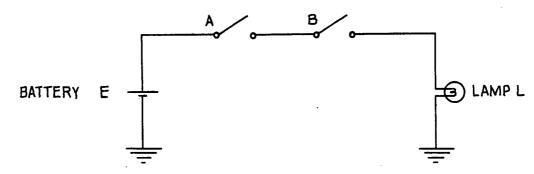

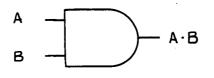

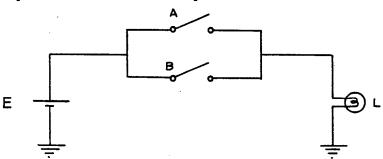

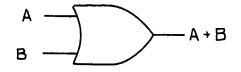

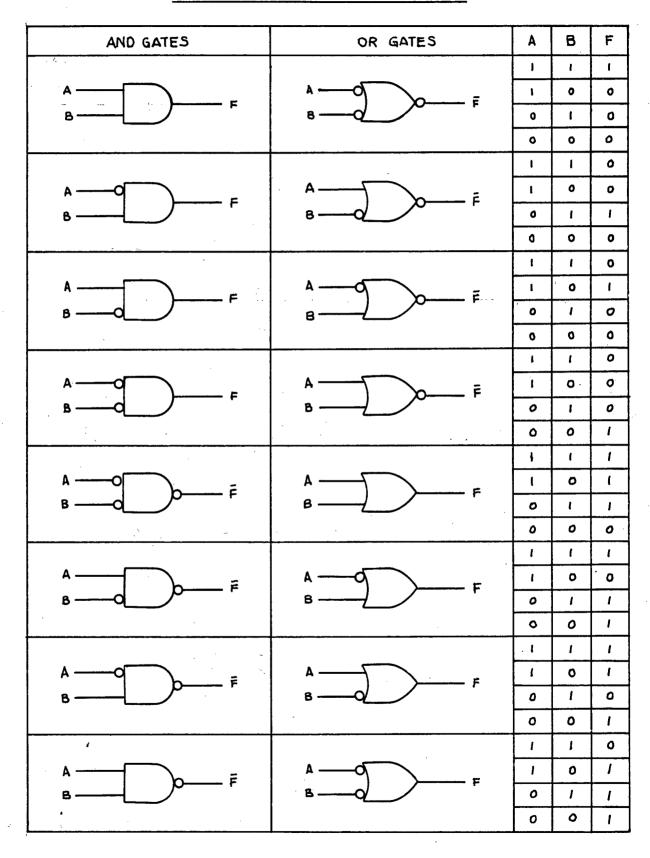

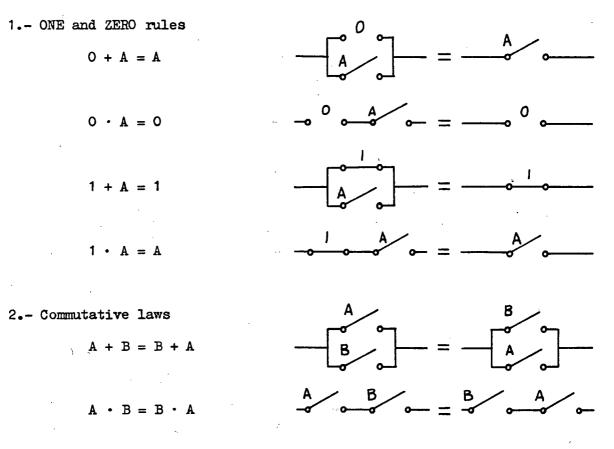

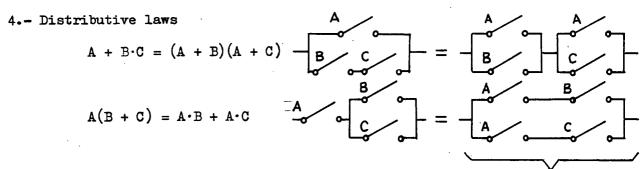

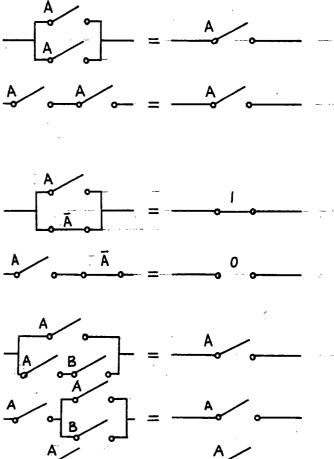

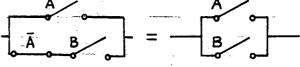

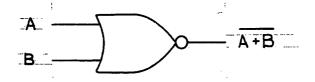

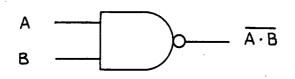

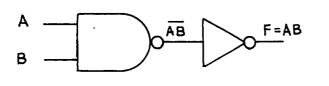

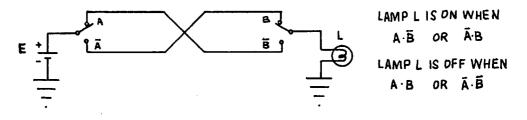

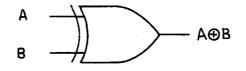

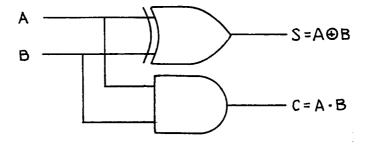

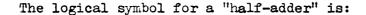

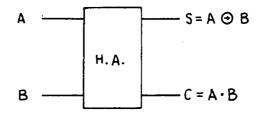

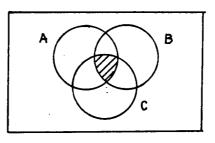

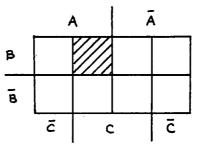

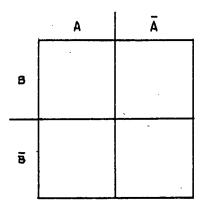

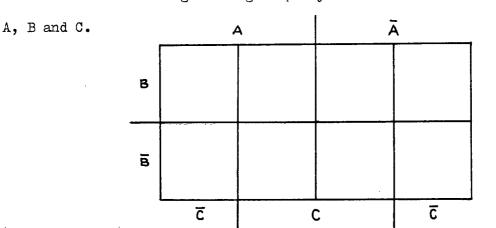

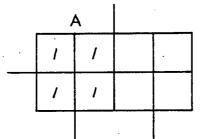

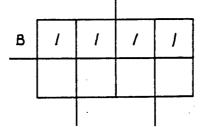

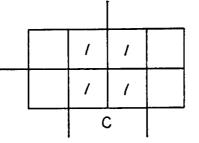

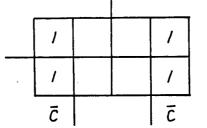

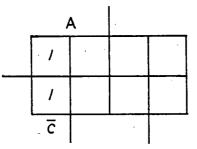

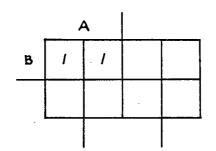

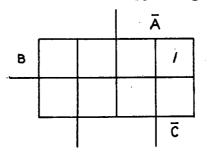

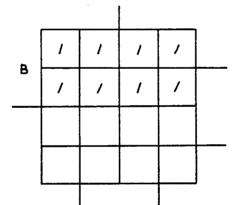

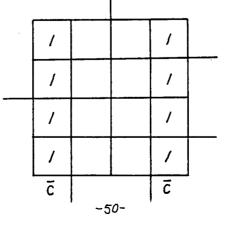

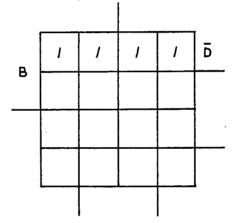

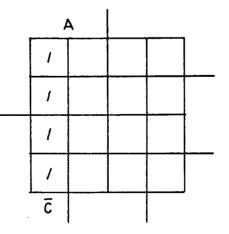

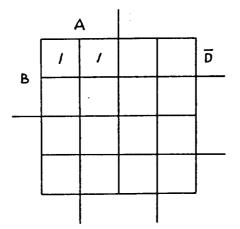

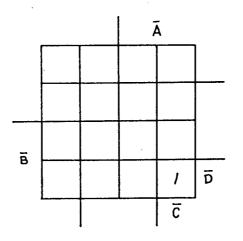

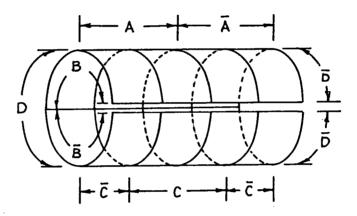

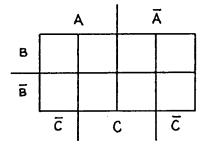

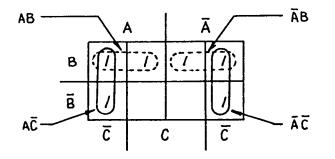

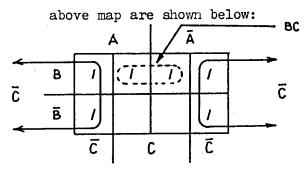

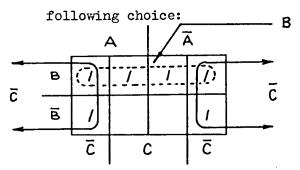

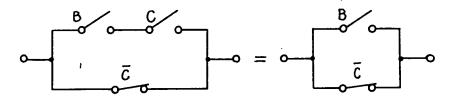

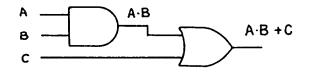

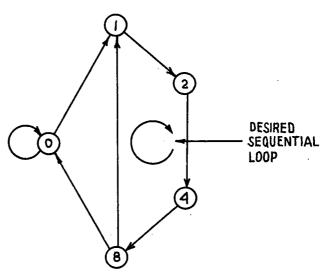

The second week, the student is introduced to Boolean Algebra. This is the algebra that defines the response of binary devices, i. e. those devices that have only two possible states like a switch which is either on or off. The student identifies the integrated circuits that will produce the boolean functions defined in class, and proceeds to assemble and verify the accuracy of the mathematical statements that define their operation.<sup>2</sup>

The third week, the student learns the laws of binary algebra and proceeds to corroborate their accuracy when the circuits described by this algebra are assembled and their response determined. The most basic form of binary addition is then introduced.

<sup>1</sup>Appendix F, Electronic Systems Book, p. 4. <sup>2</sup>Appendix F, Electronic Systems Book, Section 2

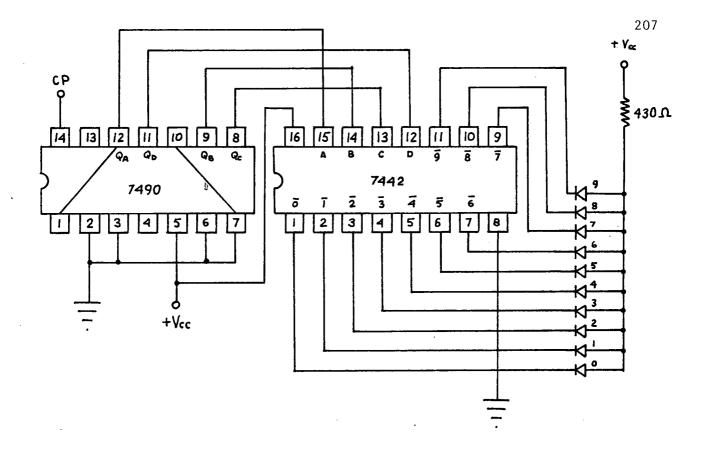

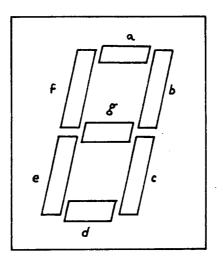

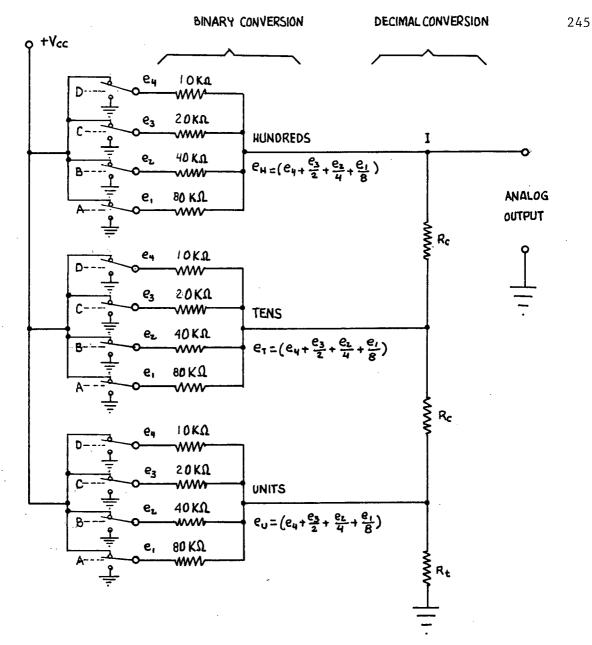

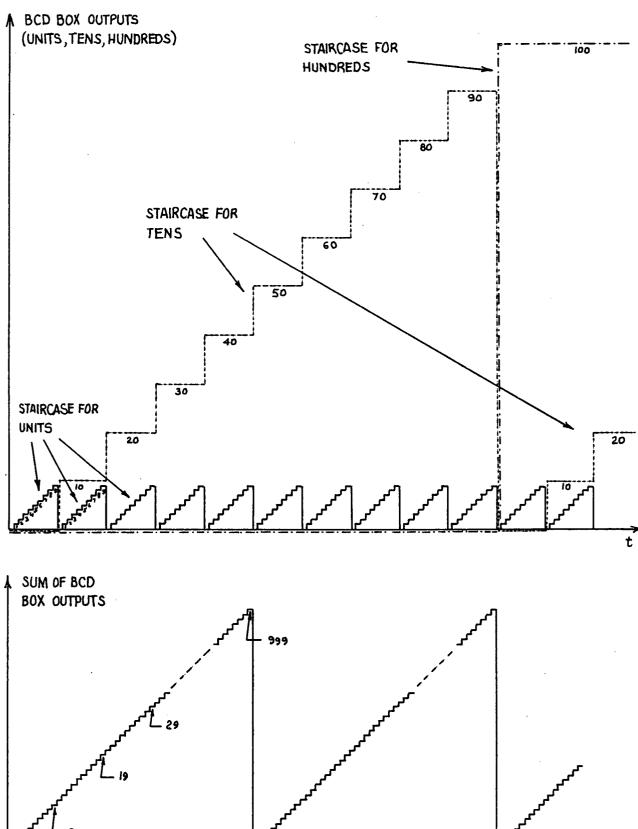

The fourth week the student learns the different number systems associated with computers to carry out arithmetic operations. He learns to interpret binary results and also to use electronic circuits capable of translating those answers to our decimal system using seven segment displays.

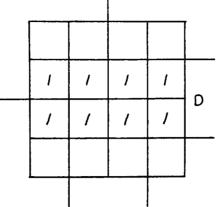

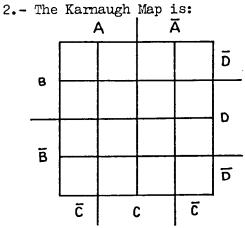

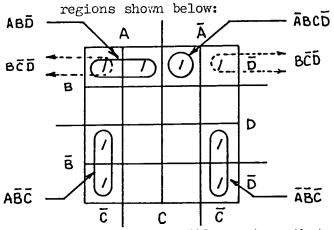

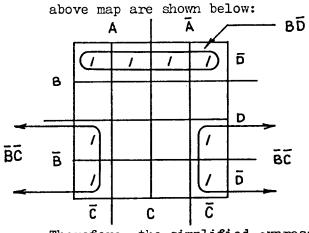

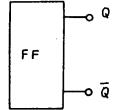

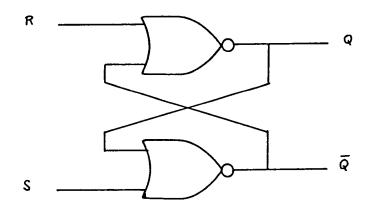

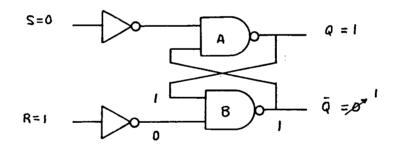

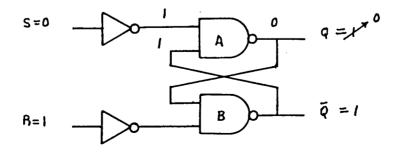

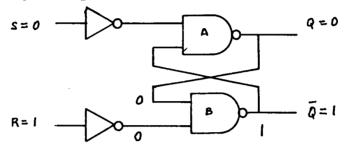

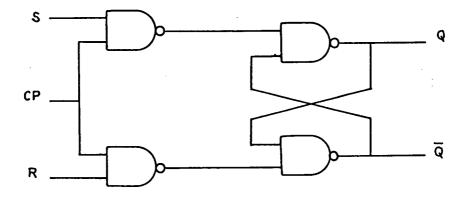

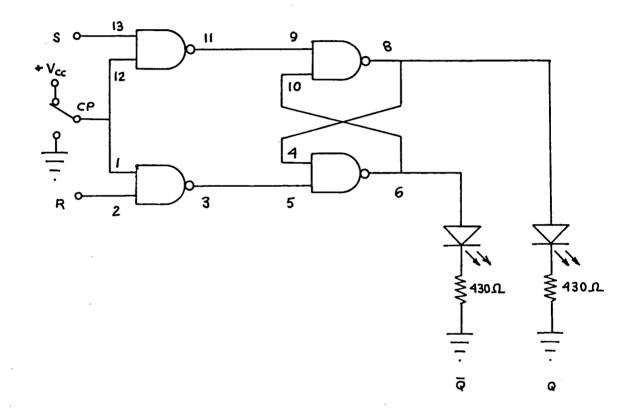

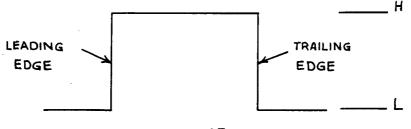

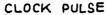

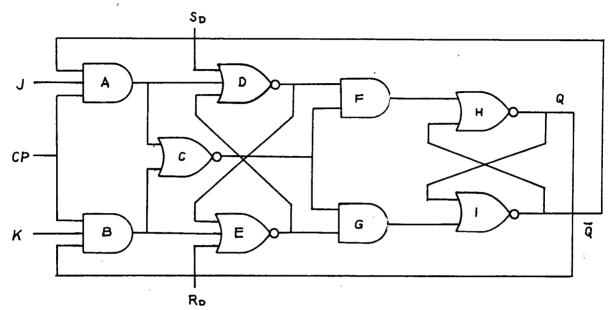

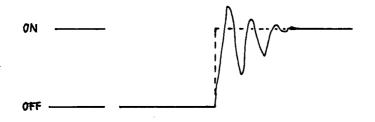

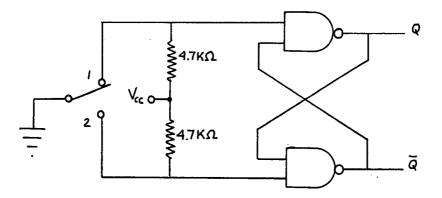

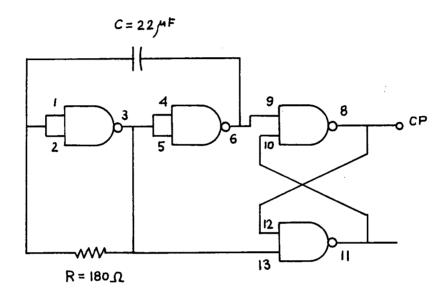

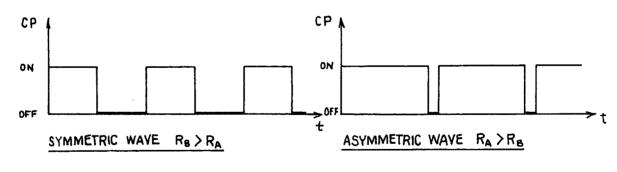

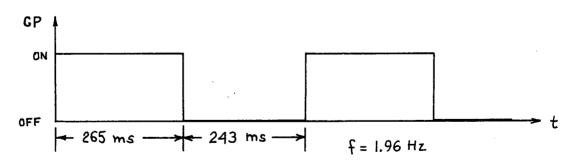

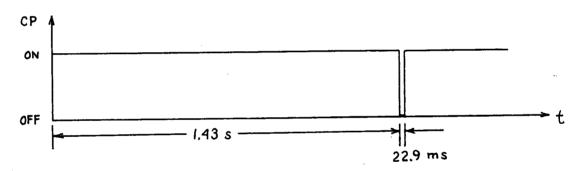

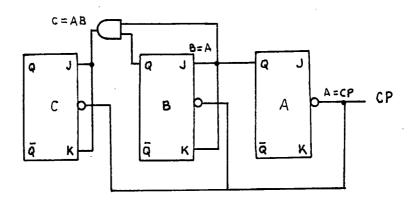

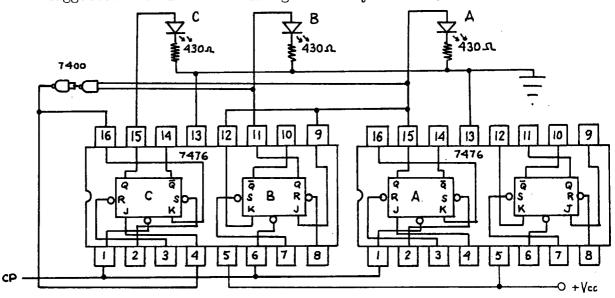

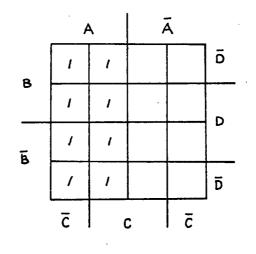

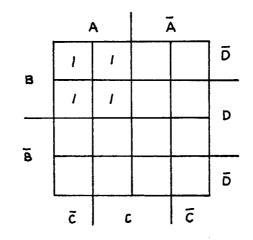

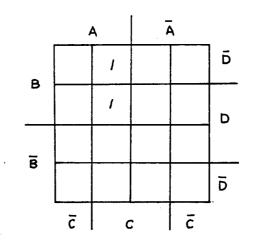

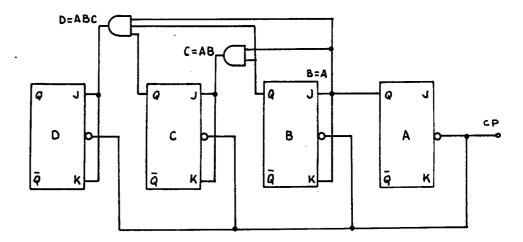

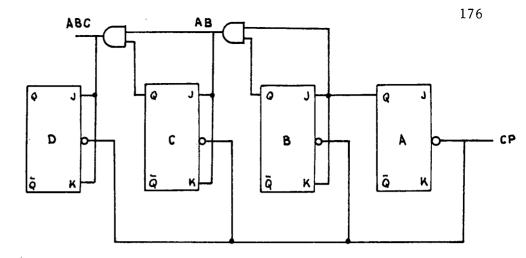

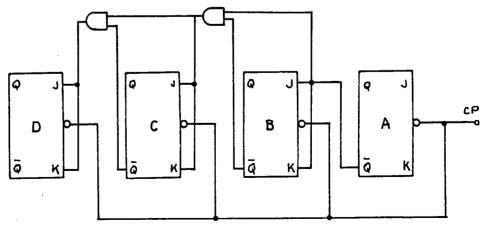

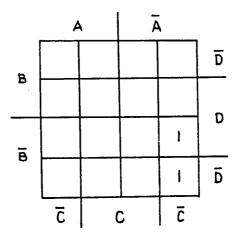

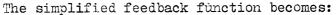

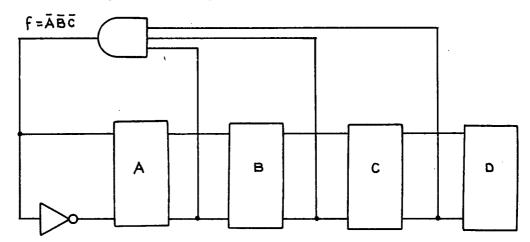

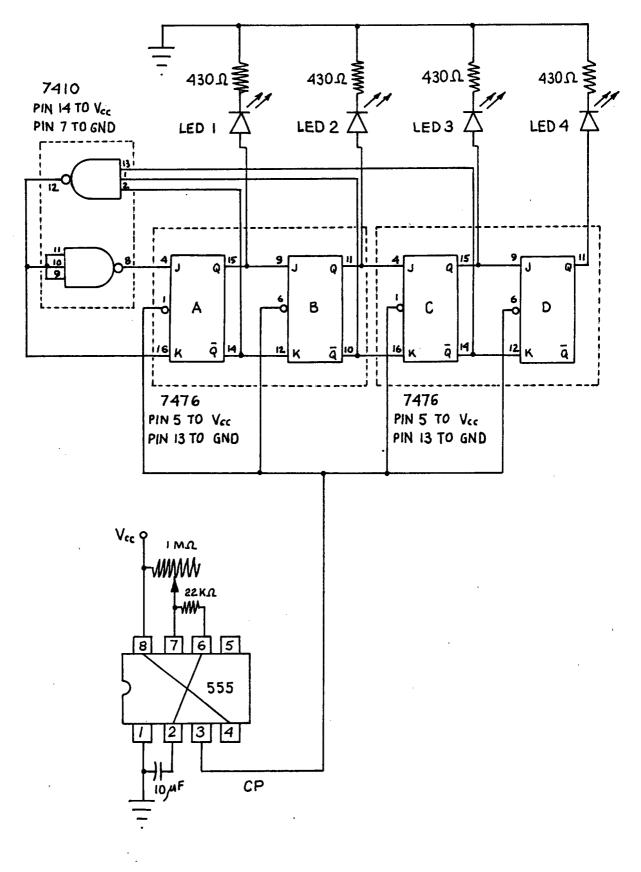

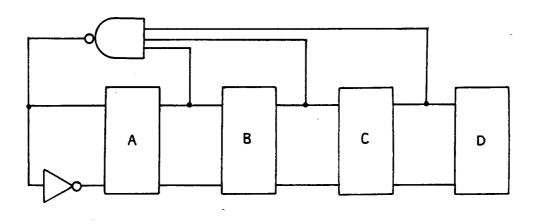

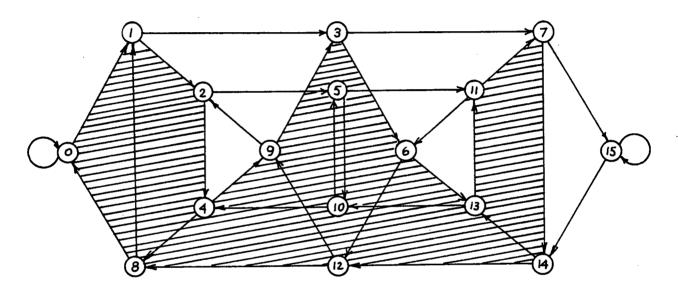

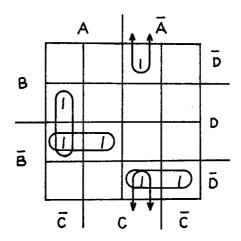

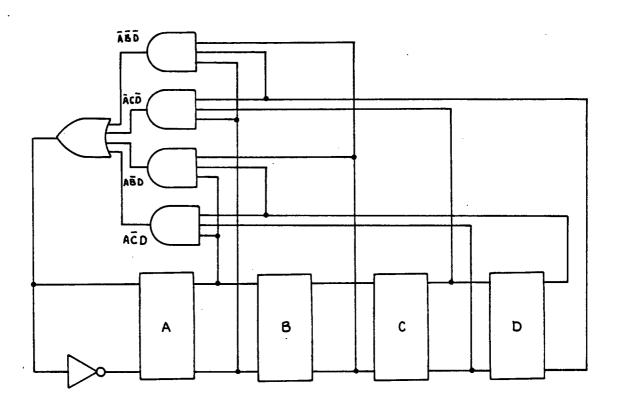

The fifth week, the student is introduced to graphical methods designed to simplify the boolean algebra expressions.<sup>3</sup> Complex boolean statements as well as their simplified versions are implemented with electronic components and the student verifies that both circuits yield the same response but one is simpler and more economical to build than the other. Now the student is intoduced to the importance of the time element in logical circuitry. He learns the basic forms of memory used by most computers, and relates the storage of information with the application of timing pulses called Clock Pulses (CP's).<sup>4</sup>

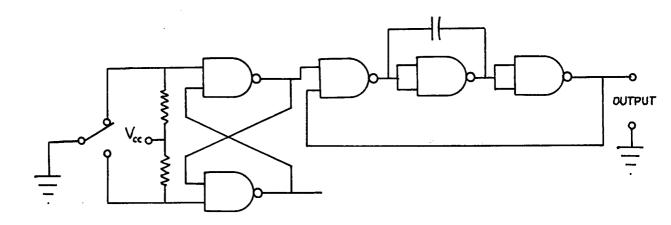

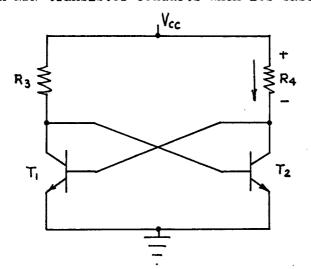

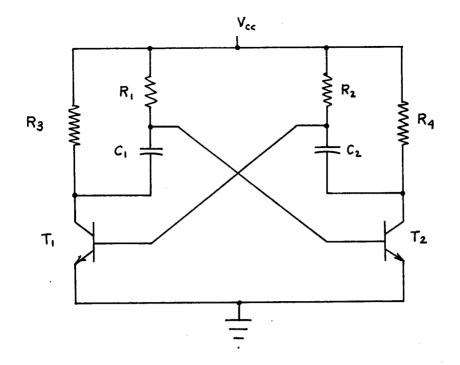

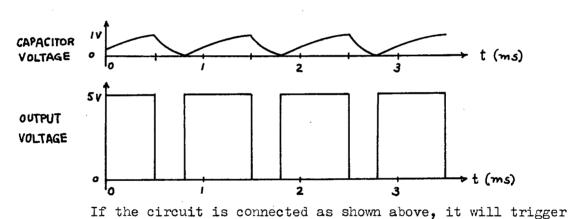

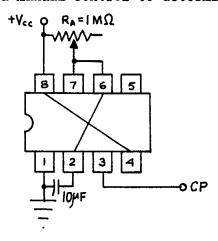

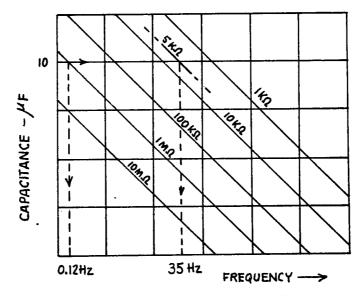

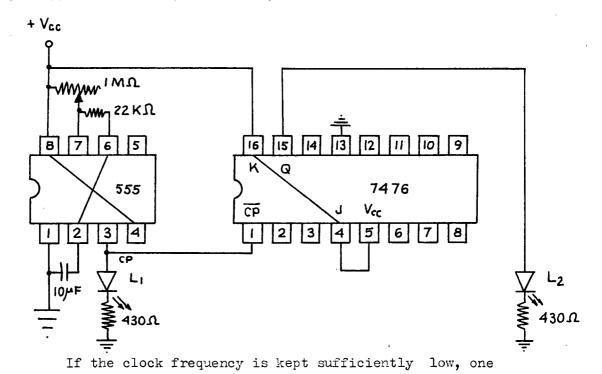

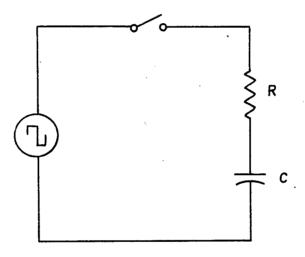

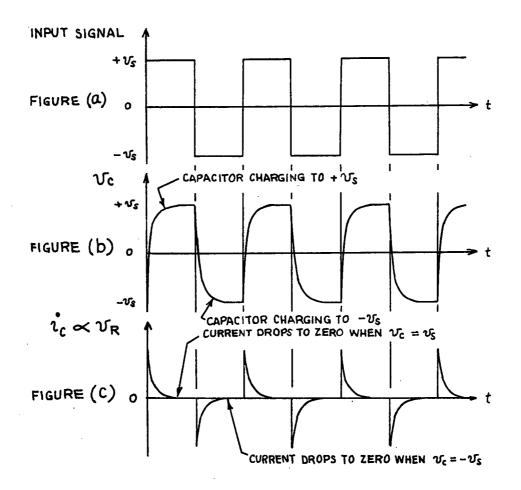

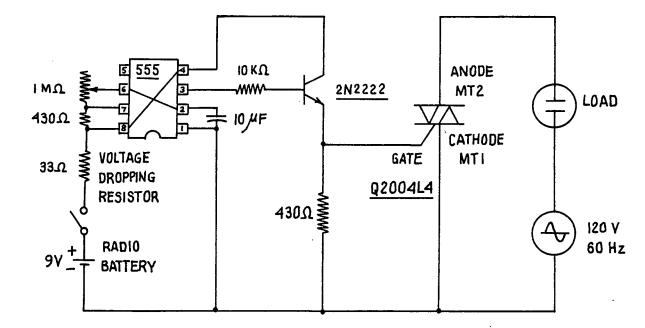

The sixth week, the student learns the operation of more sophisticated units of memory and connects the corresponding integrated circuits to test their performance. He also learns the basic operation of electronic oscillators, plus the role of capacitors in the production of oscillations, and proceeds to assemble several types of oscillators.<sup>5</sup>

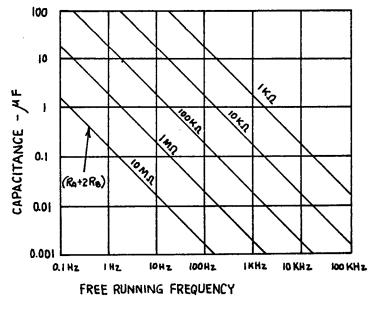

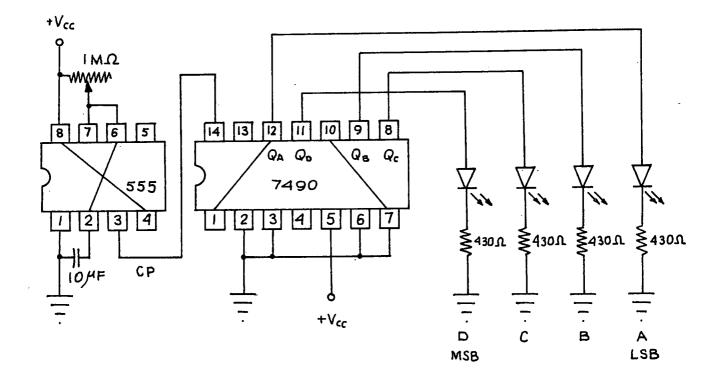

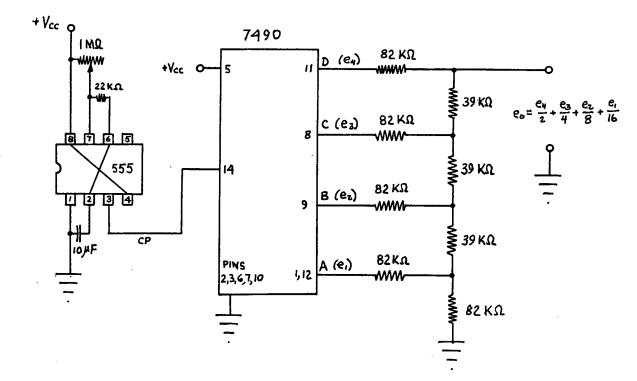

The seventh week, the student learns to use integrated circuit oscillators. The student calculates and measures their frequencies of oscillation and applies these frequencies to electronic counting circuits.<sup>6</sup>

<sup>3</sup>Appendix F, Electronic Systems Book, Section 3.

<sup>4</sup>Appendix F, Electronic Systems Book, Section 4.

<sup>5</sup>Appendix F, Electronic Systems Book, Section 5.

<sup>6</sup>Appendix F, Electronic Systems Book, Section 6.

When an oscilloscope is available, the student is introduced to its use, so that he can observe the waveforms taking place in different circuits. Special laboratory exercises have been provided for students that do not have an oscilloscope, so that they can still observe the behaviour of different frequencies of oscillation.

The eighth week the student learns how to produce any given count using electronic circuits.<sup>7</sup> Different applications' are found for counters such as: the measurement of time in digital clocks; the measurement of frequency in speedometers and tachometers; and the production of light chasing effects used in advertisements.

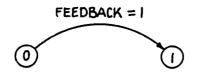

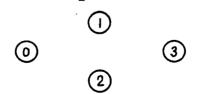

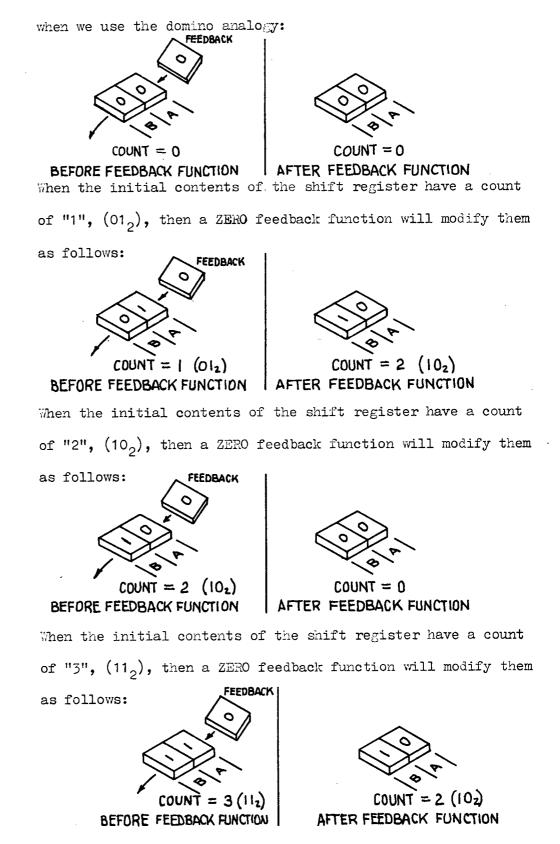

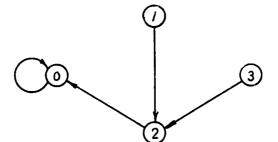

The ninth week the student is introduced to the Shift Register,<sup>8</sup> used to store strings of binary quantities. Their applications include the transmission of information between two separate electronic devices or the internal use within a digital system.

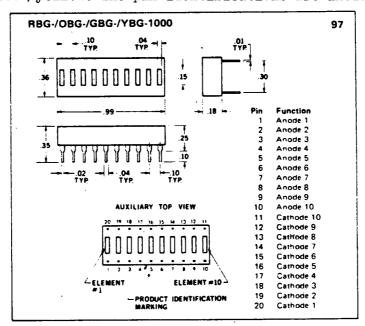

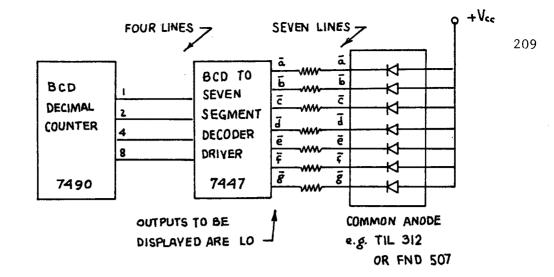

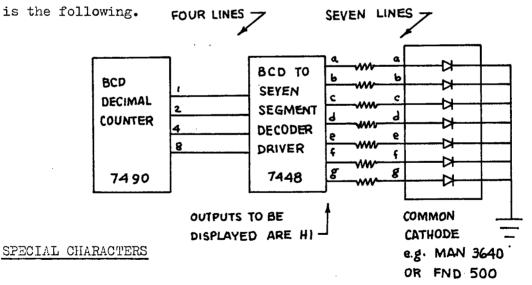

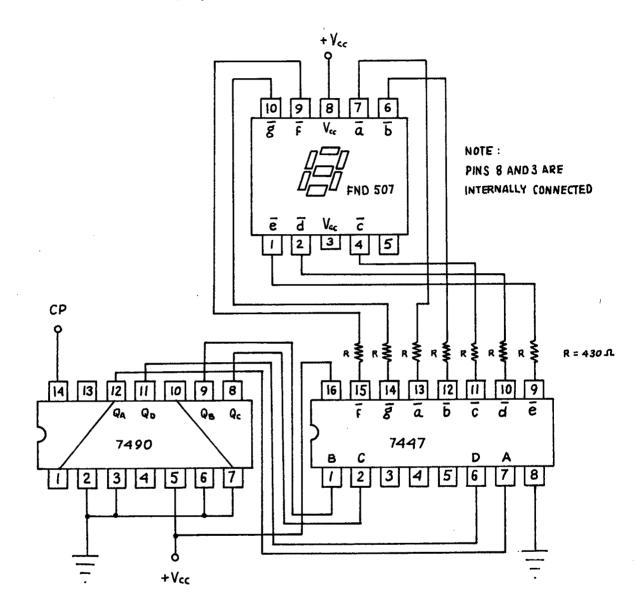

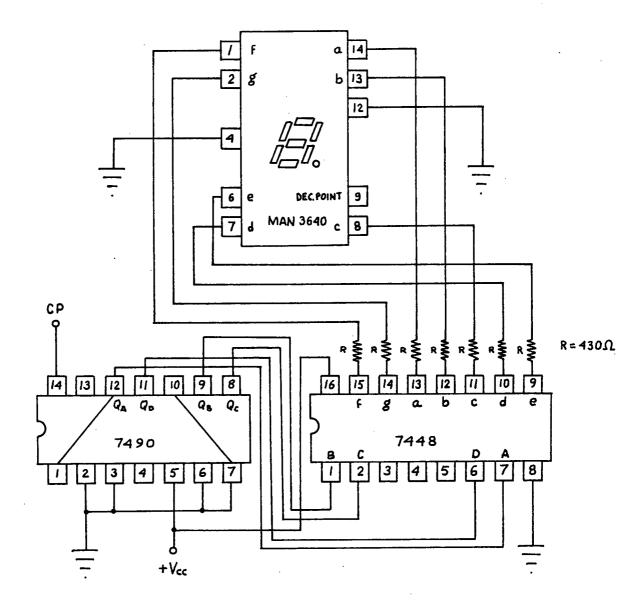

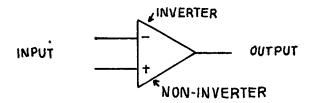

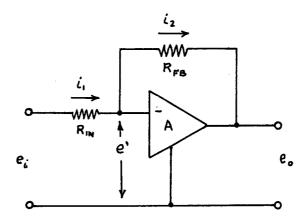

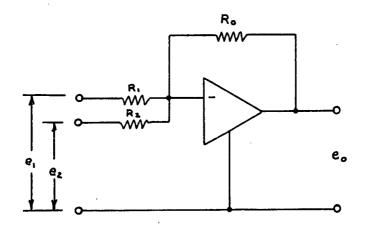

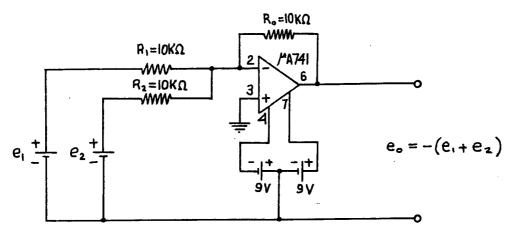

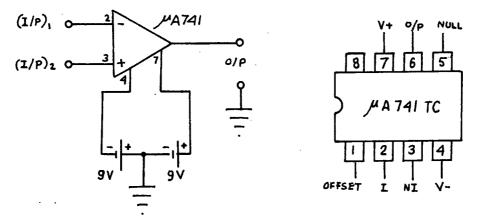

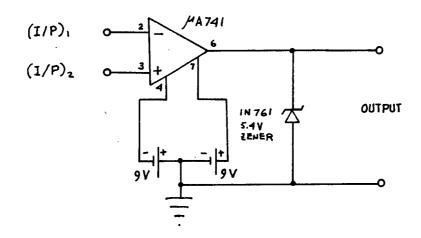

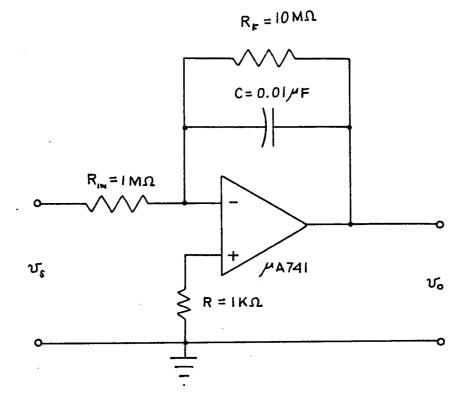

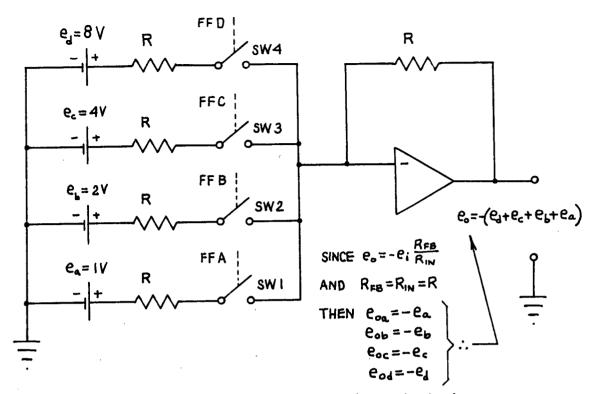

Visual Displays are covered during the tenth week, to decode the information stored in binary form and then display it in the more familiar decimal notation.<sup>9</sup> During this same week the student is introduced to the Operational Amplifier<sup>10</sup> and its applications. The student uses it to add two or more voltages and also to compare and detect the largest voltage from two different sources.

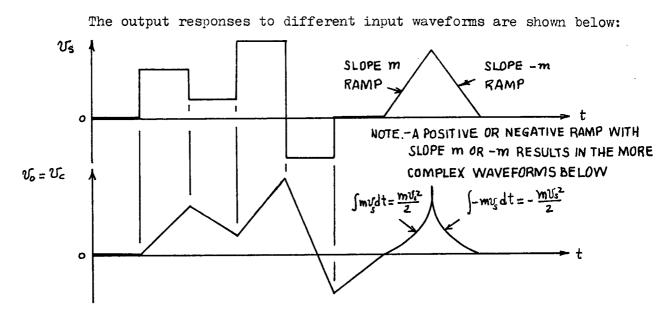

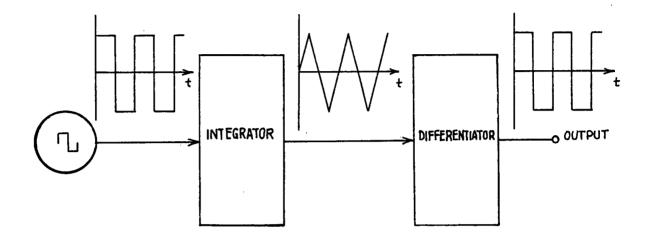

The eleventh week the student learns to use operational amplifiers to shape various waveforms. He uses them to transform triangular waves into square waves (differentiator-action), and square waves back into triangular waves (integrator-action). Waveshaping circuits find application in television circuits as well as in analogous computers. The student is also introduced

<sup>7</sup>Appendix F, Electronic Systems Book, Section 7

<sup>8</sup>Appendix F, Electronic Systems Book, Section 8

<sup>9</sup>Appendix F, Electronic Systems Book, Section 9

<sup>10</sup>Appendix F, Electronic Systems Book, Section 10

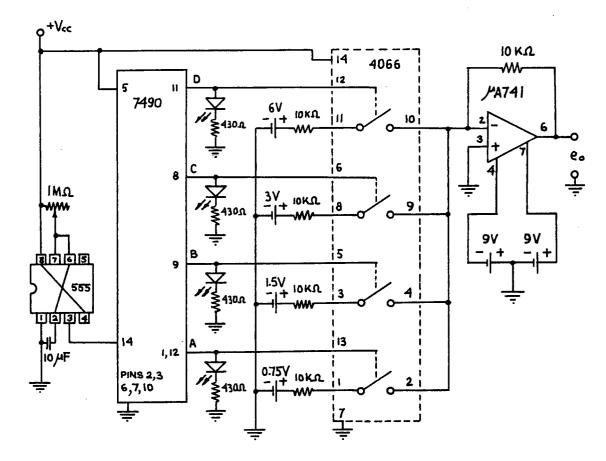

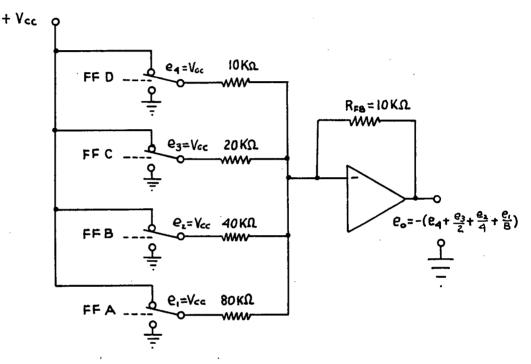

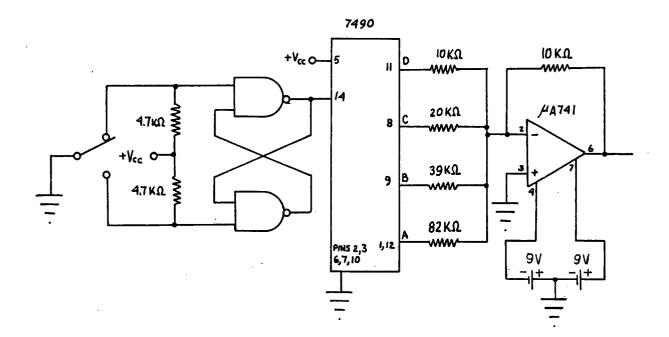

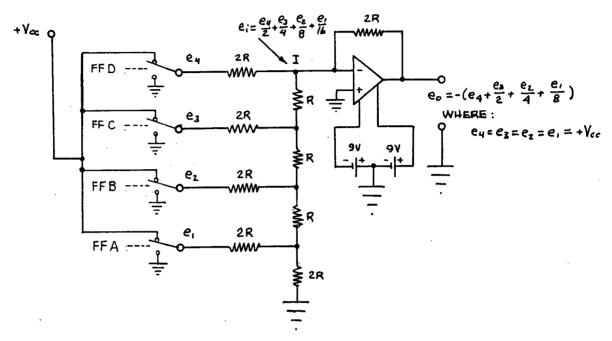

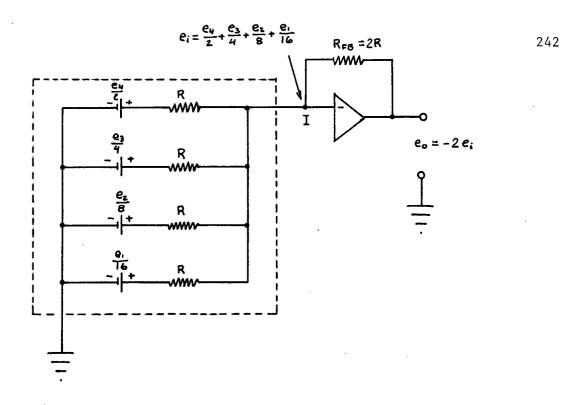

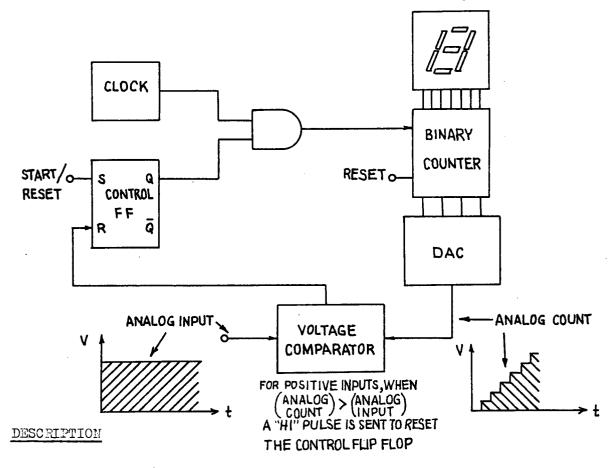

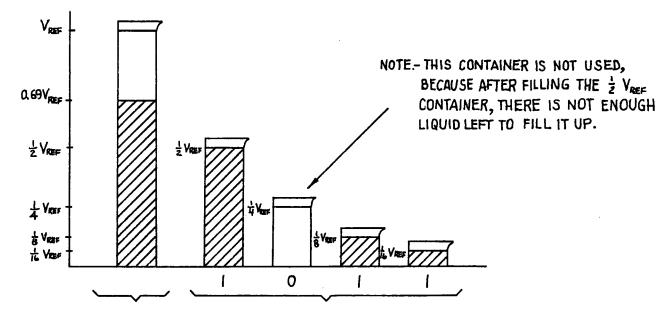

to the Digital to Analog Converter (DAC), a device that produces an output voltage proportional to the binary quantity stored in a register. The student is introduced to its various control applications such as brightness controls for illumination or speed controls for motors.

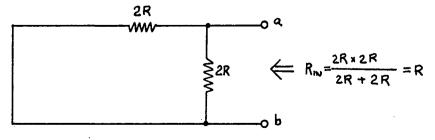

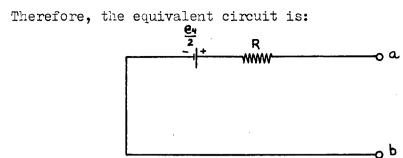

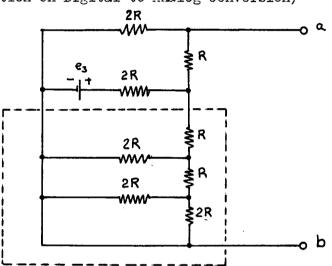

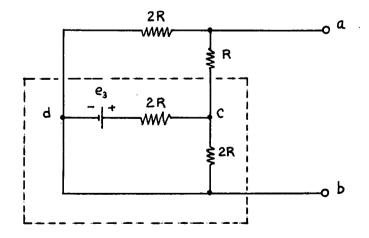

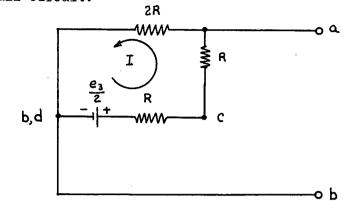

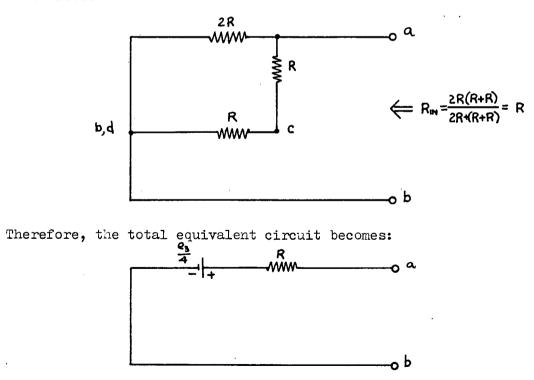

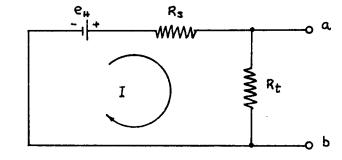

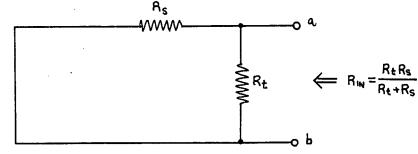

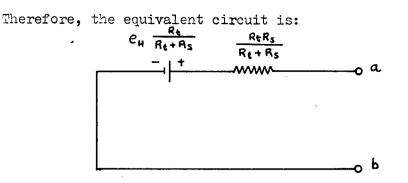

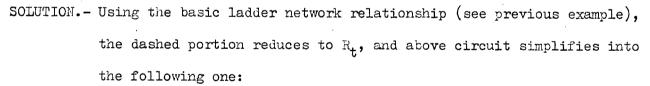

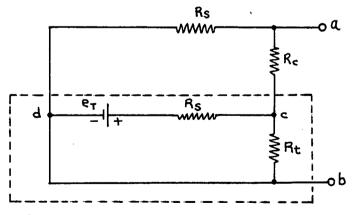

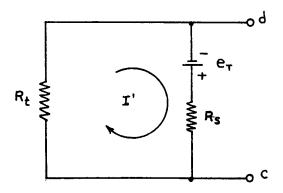

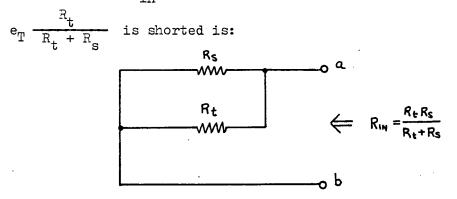

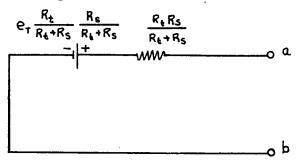

The twelfth week is spent learning the operation of more sophisticated types of Digital to Analog Conversion circuits. The student is introduced to equivalent circuits, such as those described by Thevenin's Theorem.<sup>11</sup>

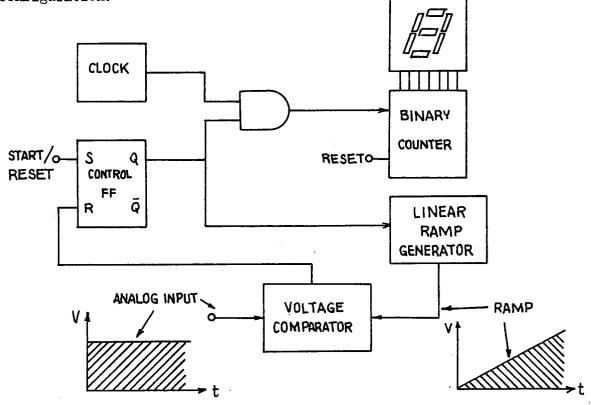

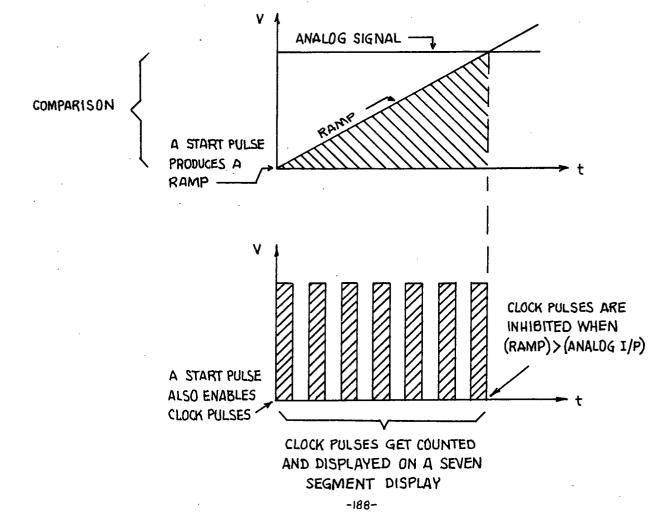

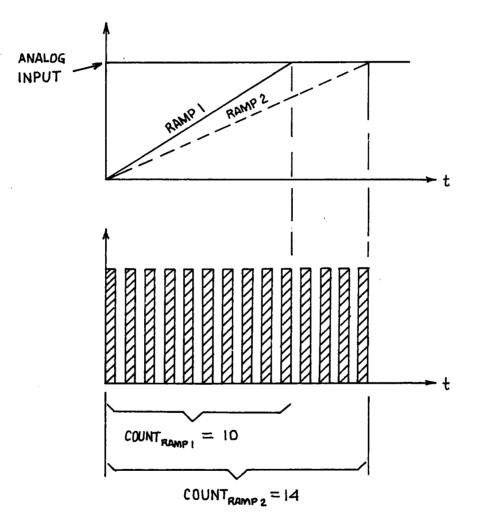

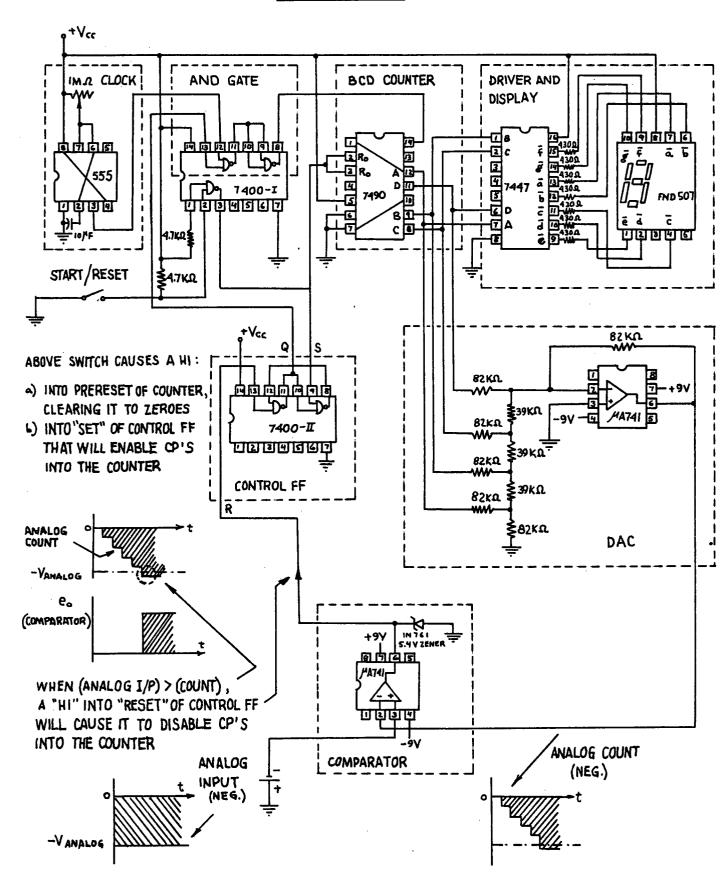

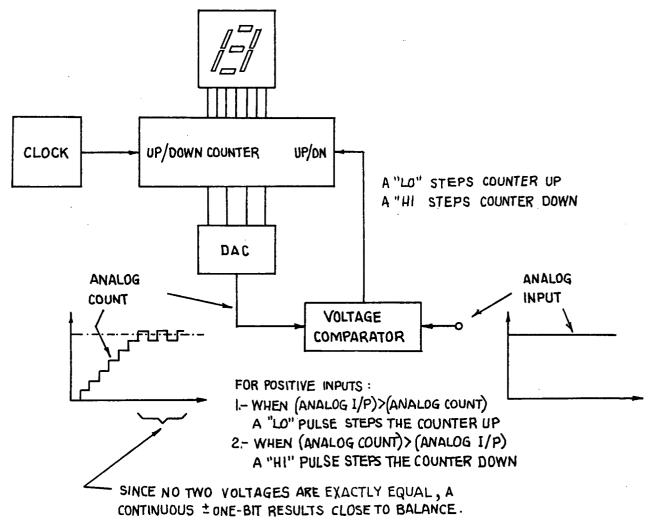

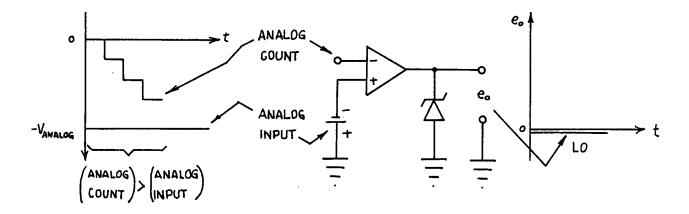

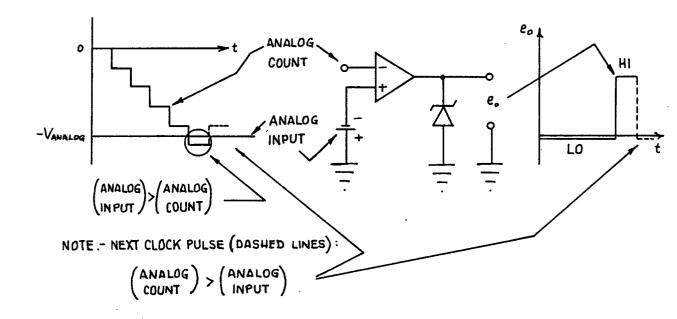

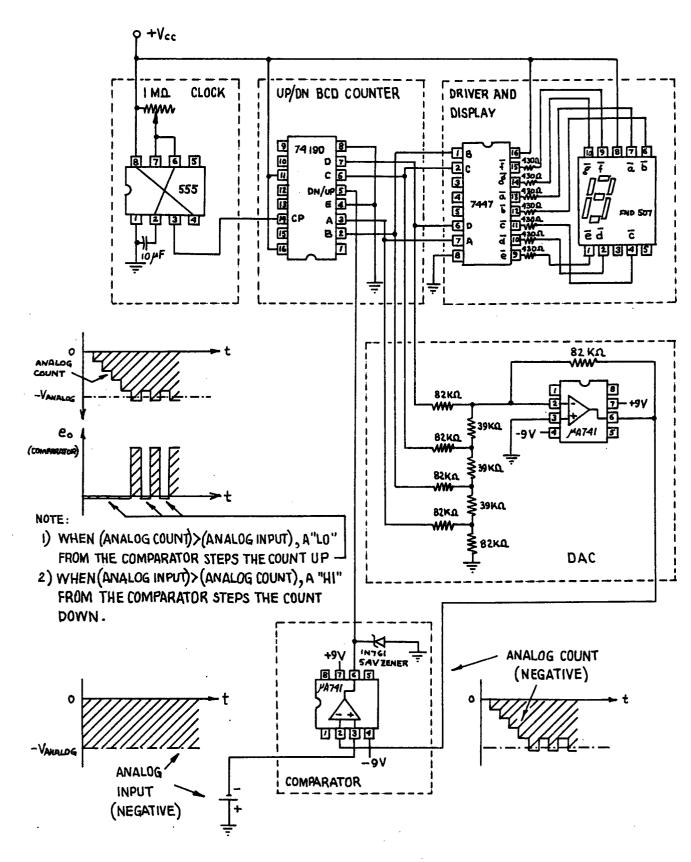

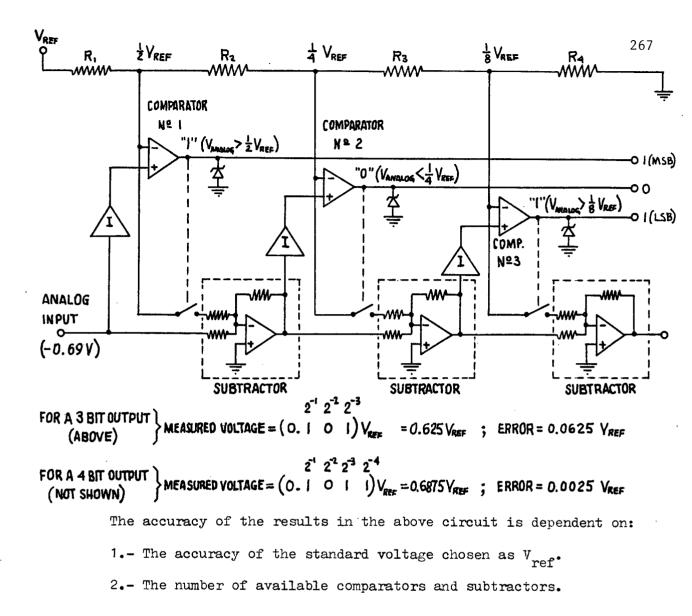

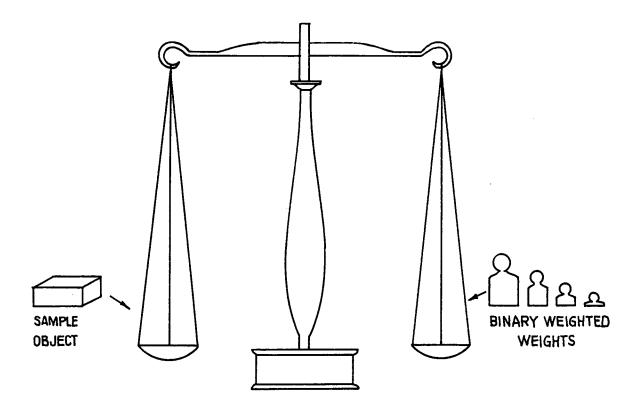

During the thirteenth week, the student is introduced to the Analog to Digital Converter (ADC). This is the electronic circuit used to convert the analogous voltages from external devices into binary quantities used for digital displays as well as in computer processing. The student learns different methods to obtain this conversion and assembles and calibrates his own circuits.

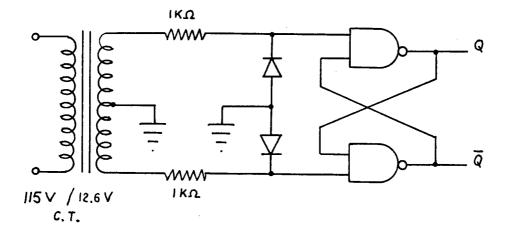

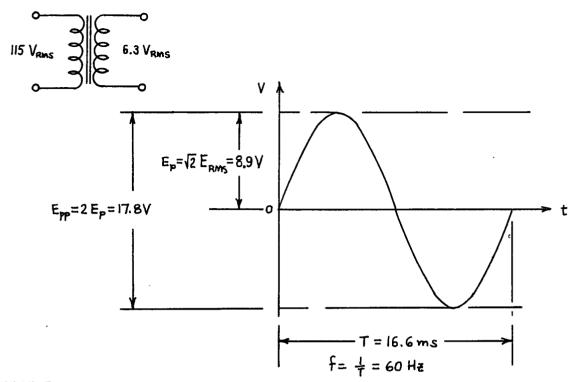

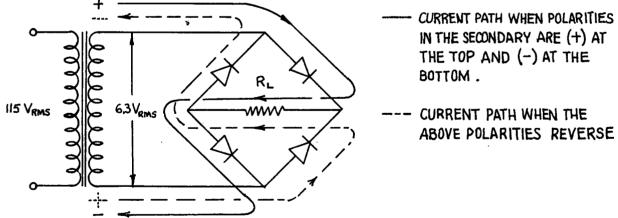

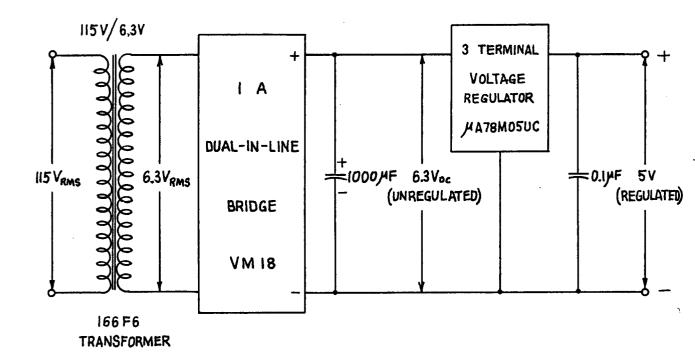

During the fourteenth week, other ADC methods are studied and their corresponding circuits are assembled and tested. During this week the student is also introduced to the design of power sources that use transformers and integrated circuits.

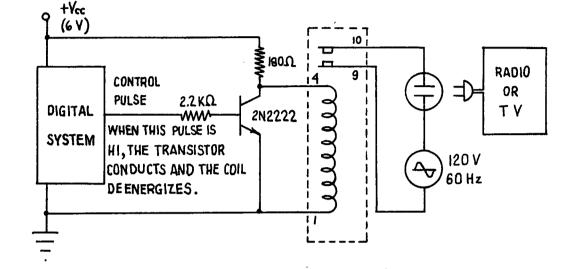

The fifteenth week, the student learns to interface systems powered by low voltages to external devices that operate at higher voltages. He learns to apply different isolating techniques.

The sixteenth week is spent learning computer languages and applying them to solve electrical circuit problems. As an example, the student learns to use the Ohm's Law Matrix,<sup>12</sup> to predict the response of electrical circuits to different applied voltages. The procedure described in the book is

> <sup>11</sup>Appendix F, Electronic Systems Book, p. 232 <sup>12</sup>Appendix F, Electronic Systems Book, p. 241.

easily programmed into a computer and yields answers in fractions of the time needed by other methods.

Laboratory Materials for the New Curriculum

The laboratory components for the new curriculum are listed in the new book.<sup>13</sup> They were selected on the basis of their ease of handling and operation as well as of their repeated use in different experiments throughout the course. Their cost is within the economic possibilities of interested students.<sup>14</sup> Once the students learn their operation and some of their uses, they usually find many other applications for them, extending thus their usefulness.

> <sup>13</sup>Appendix F, Electronic Systems Book, p. 8. <sup>14</sup>Appendix C, Cost of Laboratory Components for the New Curriculum.

### APPENDIX C

### COST OF LABORATORY COMPONENTS FOR THE NEW CURRICULUM

The following table lists the cost of the components needed for the new curriculum. The prices were quoted by the following local distributors on January 13, 1981.

> RAE Industrial Electronics Ltd./3455 Gardner Court/Burnaby, B. C. CAM GARD Industrial Electronics/2055 Boundary Road/ Vancouver, B. C. VARAH Electronics/2077 Alberta Street/Vancouver, B.C.

These distributors quoted prices for individual items but these prices were based on the purchase of one hundred units. The lowest price of each item was chosen as representative of the value of each component, and is listed on the last column to the right. It is felt that this is the cost that a careful shopper would normally have to pay for these components.

|  | ITEM                |         | PRICE |         |       |                 |

|--|---------------------|---------|-------|---------|-------|-----------------|

|  |                     | QTY/KIT | RAE   | CAMGARD | VARAH | LOWEST<br>TOTAL |

|  | INTEGRATED CIRCUITS |         |       |         |       |                 |

|  | 555                 | 1       | 0.45  | 0.38    | 0.75  | 0.38            |

|  | μ <b>Α741</b>       | 2       | 0.39  | 0.46    | 0.51  | 0.78            |

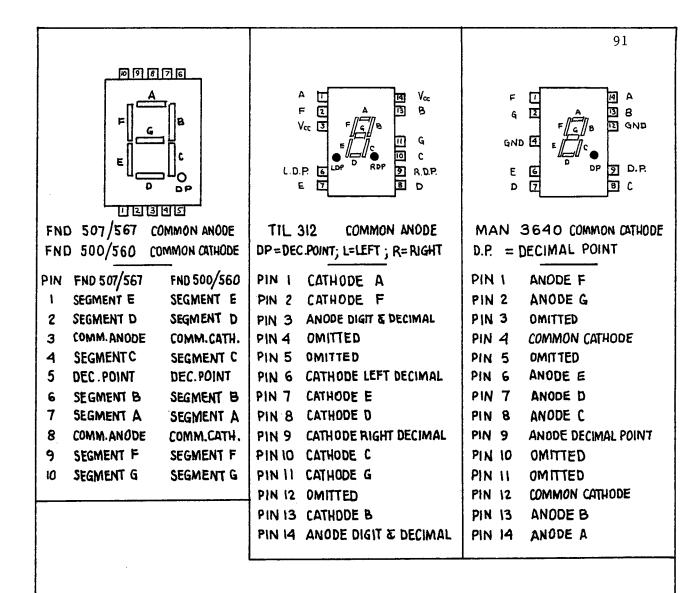

|  | FND 507             | 1       | 2.04  | 1.79    | 1.83  | 1.79            |

|  | 4066                | 1       | 0.95  | 0.89    | 1.06  | 0.89            |

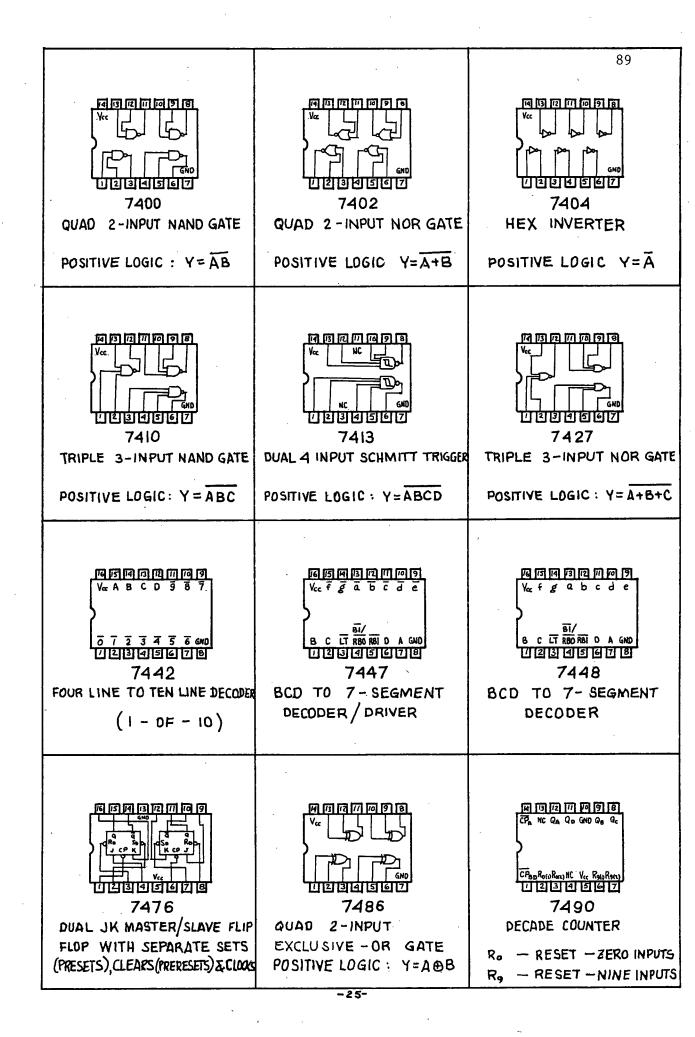

|  | 7400                | 2       | 0.35  | 0.36    | 0.46  | 0.70            |

|  | 7402                | 2       | 0.35  | 0.36    | 0.46  | 0.70            |

|  |                     |         |       |         |       |                 |

|   | ITEM           | QTY/KIT | PRICE   |         |       |                 |

|---|----------------|---------|---------|---------|-------|-----------------|

| - |                |         | RAE     | CAMGARD | VARAH | LOWEST<br>TOTAL |

|   | 7404           | 1       | 0.44    | NIL     | 0.49  | 0.44            |

|   | 7410           | 1       | 0.35    | 0.36    | 0.46  | 0.35            |

|   | 7413           | 1       | 0.63    | NIL     | 0.68  | 0.63            |

|   | 7427 )         | 1       | 0.62    | 0.42    | 0.49  | 0.42            |

|   | 7442           | 1       | 0.58    | NIL     | 0.97  | 0.58            |

|   | 7447           | 1       | 1.63    | 0.91    | 1.67  | 0.91            |

|   | 7476           | 2       | 0.50    | 0.43    | 0.52  | 0.86            |

|   | 7486           | 1       | 0.68    | 0.45    | 0.51  | 0.45            |

|   | 7490           | 2       | 0.53    | 0.45    | 0.92  | 0.90            |

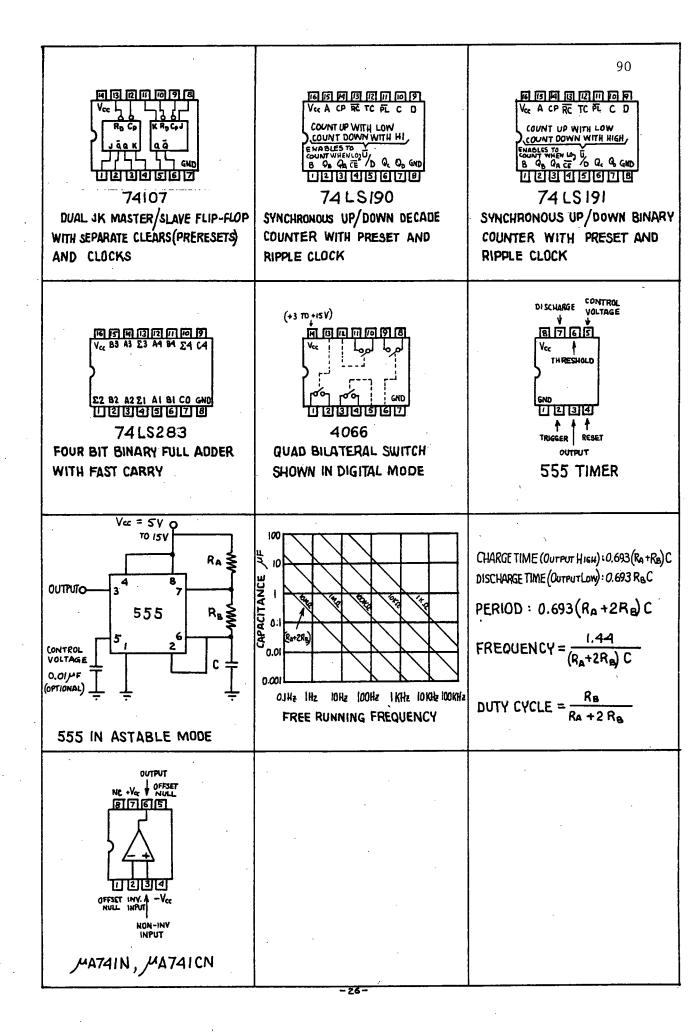

|   | 74107          | 2       | 0.77    | NIL     | 1.25  | 1.54            |

|   | 74LS190        | 1       | 2.72    | 0.82    | 1.81  | 0.82            |

|   | 74LS283        | 1       | 0.90    | NIL     | 2.23  | 0.90            |

|   |                |         |         |         |       |                 |

|   | SEMICONDUCTORS | ·       |         |         |       |                 |

|   | RED LED        | 5       | 15.50/h | 17.50/h | 0.46  | 0.78            |

|   | GREEN LED      | 5       | 31.00/h | 23.00/h | 0.51  | 1.15            |

|   | DIODE 1N4005   | 4       | NIL     | 5.99/h  | 0.15  | 0.24            |

|   | ZENER 1N761    | 1       | 0.20    | 0.12    | 2.81  | 0.12            |

|   | 2N2222         | 1       | 0.27    | 0.18    | 0.82  | 0.18            |

|   |                |         |         |         |       |                 |

|   | CAPACITORS     |         |         |         |       |                 |

|   | 10µF (16V)     | 1       | 0.85    | 0.13    | 0.20  | 0.13            |

|   | 22µF (16V)     | 1       | 1.36    | 0.13    | 0.20  | 0.13            |

|   |                |         |         |         |       |                 |

~

.

-

44

۰,

|                                       | PRIC    |        | Е       | E      |                 |

|---------------------------------------|---------|--------|---------|--------|-----------------|

| _ ITEM                                | QTY/KIT | RAE    | CAMGARD | VARAH  | LOWEST<br>TOTAL |

| RESISTORS                             |         |        |         |        |                 |

| 430 Ω ¼ W                             | 7       | 2.07/h | 2.03/h  | 1.64/h | 0.14            |

| 3.3 $k\Omega$ 4 W                     | 2       | 2.07/h | 2.03/h  | 1.64/h | 0.04            |

| 4.7 kΩ ½ W                            | 4       | 2.07/h | 2.03/h  | 1.64/h | 0.08            |

| 10 k $\Omega$ $\frac{1}{4}$ W         | 6       | 2.07/h | 2.03/h  | 1.64/h | 0.12            |

| 22 kn ½ W                             | 2       | 2.07/h | 2.03/h  | 1.64/h | 0.04            |

| 39 kn 4 W                             | 4       | 2.07/h | 2.03/h  | 1.64/h | 0.08            |

| 82 k $\Omega$ $\frac{1}{4}$ W         | 6       | 2.07/h | 2.03/h  | 1.64/h | 0.12            |

| 1 MΩ ¼ W                              | 1       | 8.19/h | 3.59/h  | 1.64/h | 0.03            |

| 2.2 MΩ ½ W                            | 2       | 9.27/h | 3.59/h  | 1.64/h | 0.07            |

| 1 MΩ Potentiometer<br>with thumbwheel | 2       | 0.49   | NIL     | 6.89   | 0.99            |

| ACCESSORIES                           |         |        |         |        |                 |

| BREADBOARD (SK-10)                    | 1       | 21.50  | NIL     | NIL .  | 21.50           |

| TRANS-BOX                             | 1       | NIL    | NIL     | NIL    | 7.22            |

| ጥሰጥለ፤ ረብድጥ ወጀው ሆነጥ                    |         |        |         |        | \$47.20         |

•

### APPENDIX D

### ATTENDANCE RECORDS OF COURSES USING THE NEW CURRICULUM

The following attendance records were compiled from the Continuing Education Registers at PVI. They correspond to the four times that the new curriculum has been covered in courses offered by this department. These courses were scheduled over a period of two consecutive winter-spring sessions.

1979 - 1980 SESSION (WINTER)

| Course Name: Electronic Systems Part I                  |

|---------------------------------------------------------|

| Scheduled dates: September 10, 1979 to November 5, 1979 |

| Number of sessions                                      |

| Number of enrolled students                             |

| Possible attendance (Students x Sessions)               |

| Absences                                                |

| Percentage of attendance                                |

|                                                         |

| Course Name: Electronic Systems Part II                 |

| Scheduled dates: November 7, 1979 to January 21, 1980   |

| Number of sessions                                      |

| Number of enrolled students                             |

| Possible attendance (Students x Sessions)               |

| Absences                                                |

| Percentage of attendance                                |

# 1979 - 1980 SESSION (SPRING)

| Course Name: Computers A and Computers B          |  |  |  |  |  |  |

|---------------------------------------------------|--|--|--|--|--|--|

| Scheduled dates: February 5, 1980 to May 13, 1980 |  |  |  |  |  |  |

| Number of sessions                                |  |  |  |  |  |  |

| Number of enrolled students                       |  |  |  |  |  |  |

| Possible attendance (Students x Sessions)         |  |  |  |  |  |  |

| Absences                                          |  |  |  |  |  |  |

| Percentage of attendance                          |  |  |  |  |  |  |

1980 - 1981 SESSION ( WINTER)

| Course Name: Electronic Systems Part I                   |     |  |  |  |

|----------------------------------------------------------|-----|--|--|--|

| Scheduled dates: September 15, 1980 to November 10, 1980 |     |  |  |  |

| Number of sessions                                       | 16  |  |  |  |

| Number of enrolled students                              | 20  |  |  |  |

| Possible attendance (Students x Sessions)                | 320 |  |  |  |

| Absences                                                 | 18  |  |  |  |

| Percentage of attendance                                 | 94% |  |  |  |

| Course Name: Electronic Systems Part II                |     |  |  |  |  |

|--------------------------------------------------------|-----|--|--|--|--|

| Scheduled dates: November 12, 1980 to January 19, 1981 |     |  |  |  |  |

| Number of sessions                                     | 1.6 |  |  |  |  |

| Number of enrolled students                            | 20  |  |  |  |  |

| Possible attendance (Students x Sessions)              | 20  |  |  |  |  |

| Absences                                               | 27  |  |  |  |  |

| Percentage of attendance                               | 92% |  |  |  |  |

### 1980 - 1981 SESSION (SPRING)

| Course Name: Electronic Systems Part II         |     |

|-------------------------------------------------|-----|

| Scheduled dates: March 18, 1981 to May 13, 1981 |     |

| Number of sessions                              | 16  |

| Number of enrolled students                     | 15  |

| Possible attendance (Students x Sessions)       | 40  |

| Absences                                        | 37  |

| Percentage of attendance                        | 85% |

# FIELD TESTING FROM WHITTIER UNION HIGH SCHOOL DISTRICT

# WHITTIER UNION HIGH SCHOOL DISTRICT

Whittier, California 90605

BOARD OF TRUSTEES: Joan Nay, President SUPERINTENDENT: Norman B. Eisen, Ed.D.

Jerry Sarchet, Ph.D., Vice President ASSOC. SUPT .: Earle K. Fisher

. Roy Salas, Clerk

Eve Burnett, Henri Pellissier, Members ASST. SUPTS.: Arthur T. Hobson, Ed.D.

Seabron A. Nolin, Ed.D.

50

March 27, 1981

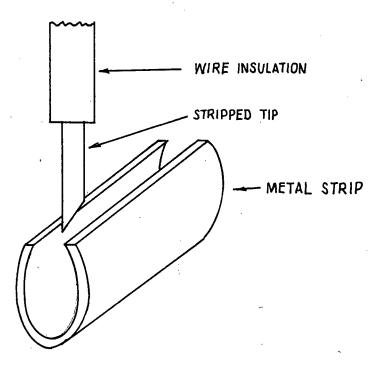

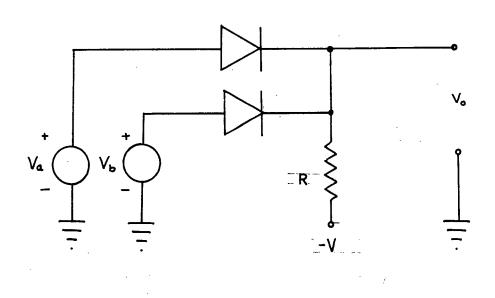

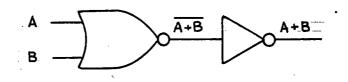

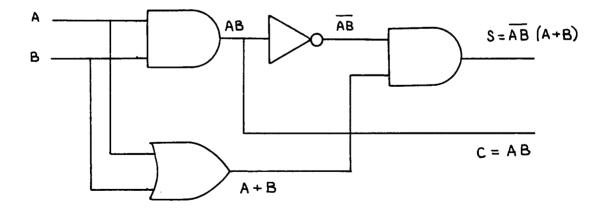

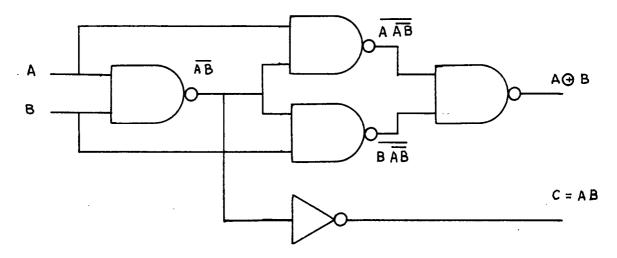

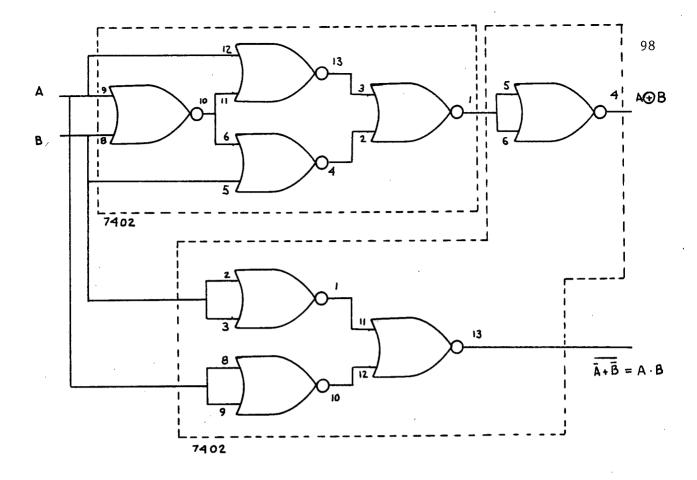

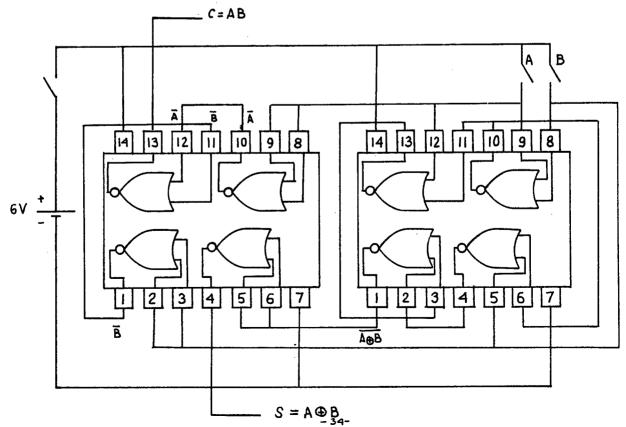

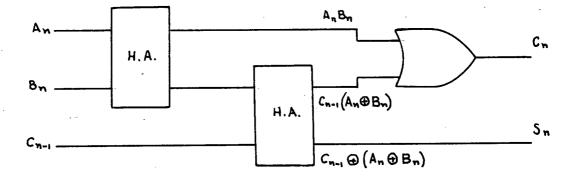

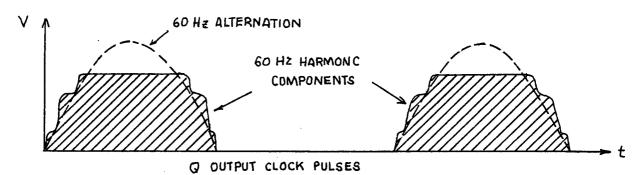

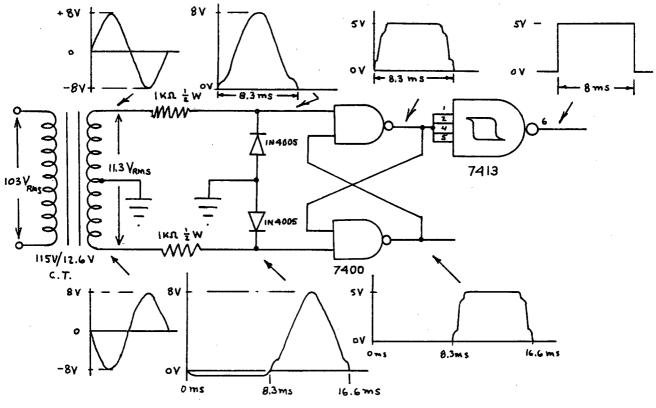

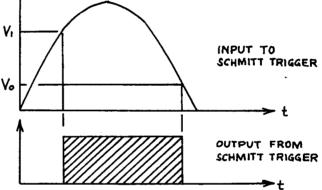

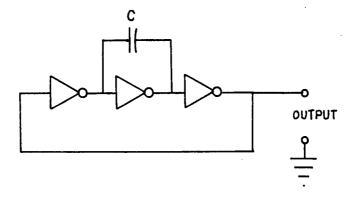

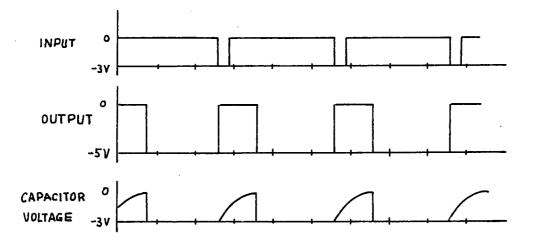

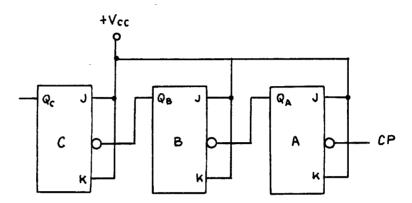

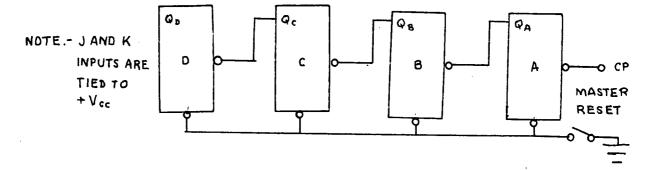

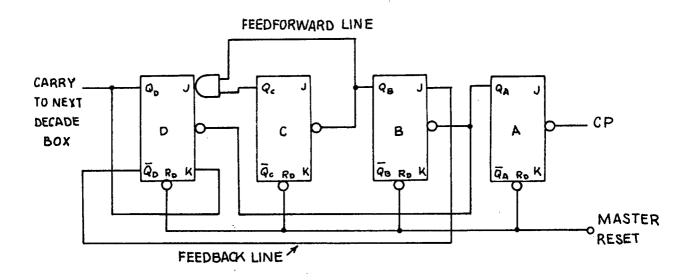

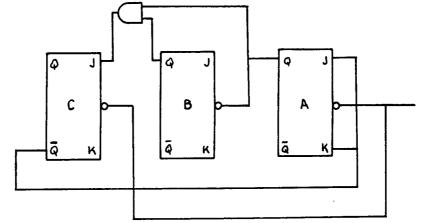

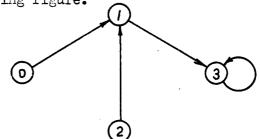

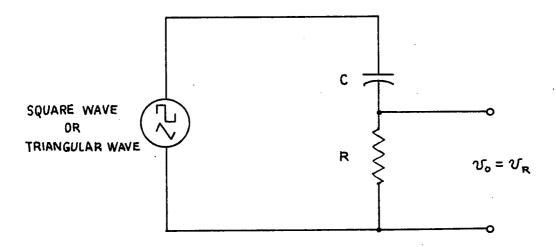

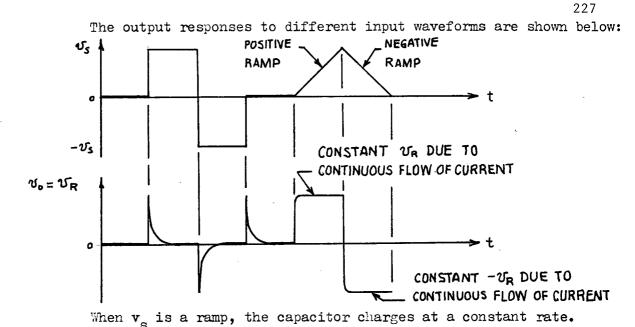

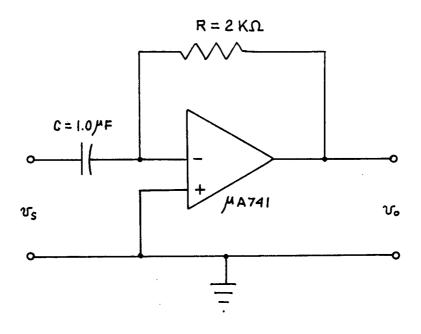

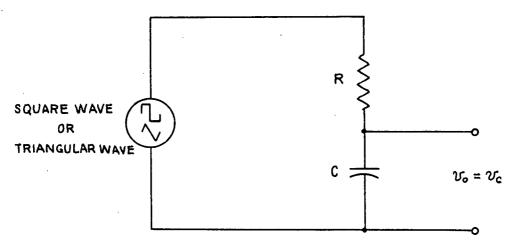

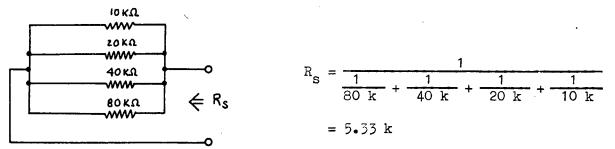

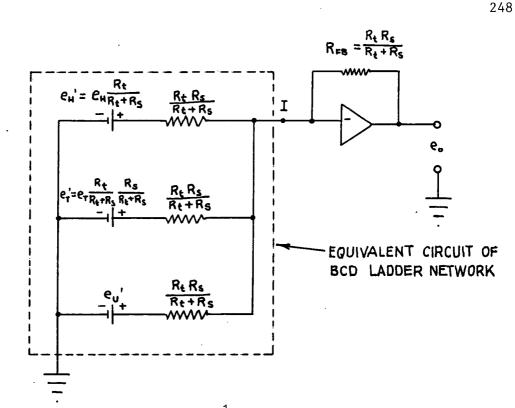

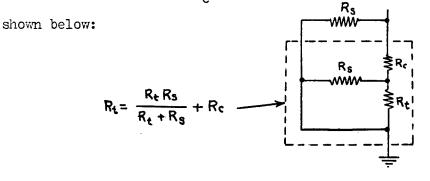

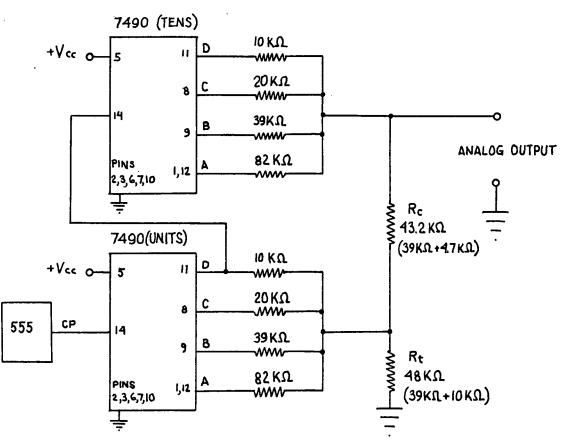

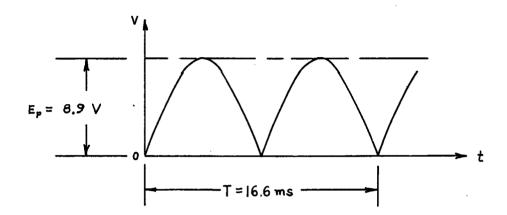

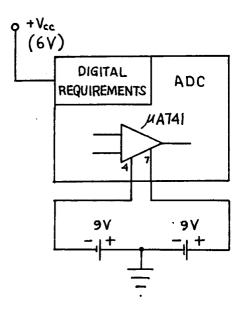

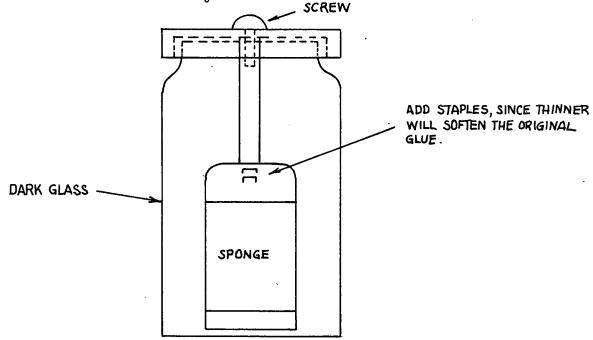

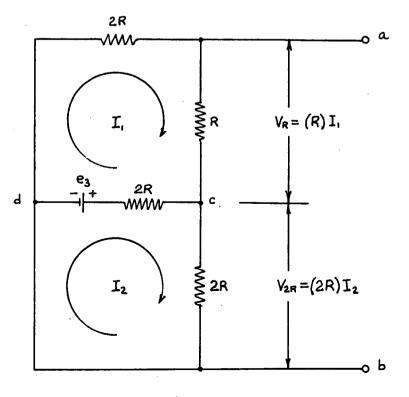

To Whom It May Concern: