### Formal Equivalence Checking of Software Specifications vs. Hardware Implementations

by

Xiushan Feng

B.Eng. Harbin Institute of Technology, 1997

M.Eng. Institute of Computing Technology,

Chinese Academy of Sciences, 2000

M.Sc. University of British Columbia, 2002

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

$\mathbf{in}$

THE FACULTY OF GRADUATE STUDIES

(Computer Science)

### THE UNIVERSITY OF BRITISH COLUMBIA

January 2007

© Xiushan Feng, 2007

### Abstract

Ever-growing complexity is forcing logic design to move above the register transfer level (RTL). For example, functional specifications are being written in software. These specifications are written for clarity, and are not optimized or intended for synthesis. Since the software is the target of functional validation, equivalence verification between the software specification and the RTL implementation is needed.

This thesis introduces new techniques to reduce the complexity of this verification and increase the capability of current verification techniques.

The first contribution improves the efficiency of sequential equivalence verification. I introduce a partitioned model checking approach using Annotated Control Flow Graphs (ACFG) to represent software specifications for sequential circuits. The approach partitions the software and hardware states based on the structure of the ACFG, and uses the flow and the edge annotations in the ACFG to guide the state-space exploration. Experimental results show that the new partitioned model checking approach runs faster than the standard global reachability analysis.

The second contribution increases the scalability of combinational equivalence verification between a high-level software specification and RTL. Unlike conventional RTL-to-gate combinational equivalence verification, there are fewer structural similarities between the two models, and it is harder to find equivalent points. Furthermore, each path through the software can compute a different result, and there are an exponential number of paths. I first adapt the concept of cutpoints from hardware verification and define the analogous concept of software cutpoints, then implement a proof-of-concept cutpoint approach in my verification tool for the TI C6x family of DSPs. Experimental results show large improvements in both runtime and memory usage. Next, I introduce cutpoints into the equivalence verification of software specifications vs. hardware implementations. I present a novel way to introduce cutpoints early, during the analysis of the software, rather than after a low-level hardware-equivalent has been generated, thereby avoiding the exponential enumeration of software paths as well as the logic blow-up of tracking merged paths. I evaluate this method on a challenge problem suggested by colleagues in industry. Experimental results show large improvements in runtime and memory usage due to the early cutpoint insertion.

## Contents

.

| Abstract             |                  |                                                                                                        |  |  |

|----------------------|------------------|--------------------------------------------------------------------------------------------------------|--|--|

| Contents             |                  |                                                                                                        |  |  |

| List of              | List of Tables   |                                                                                                        |  |  |

| List of Figures      |                  |                                                                                                        |  |  |

| List of              | List of Acronyms |                                                                                                        |  |  |

| Acknow               | Acknowledgments  |                                                                                                        |  |  |

| Chapte               | er 1 Iı          | $\mathbf{n}$ troduction                                                                                |  |  |

| 1.1                  | Motiva           | tion                                                                                                   |  |  |

| 1.2                  | Contri           | butions $\ldots \ldots 3$ |  |  |

|                      | 1.2.1            | ACFG-Based Partitioned Model Checking                                                                  |  |  |

|                      | 1.2.2            | Cutpoints for Embedded Software                                                                        |  |  |

|                      | 1.2.3            | Early Cutpoint Insertion for Combinational Circuits 5                                                  |  |  |

| 1.3                  | Thesis           | Outline                                                                                                |  |  |

| Chapter 2 Background |                  |                                                                                                        |  |  |

| 2.1                  | Forma            | l Verification                                                                                         |  |  |

| 2.2                  | Model            | Checking Introduction                                                                                  |  |  |

|                      | 2.2.1            | Modeling and Specification                                                                             |  |  |

|                                                 | 2.2.2  | Verification Algorithms                         | 16 |

|-------------------------------------------------|--------|-------------------------------------------------|----|

| 2.3                                             | Symbo  | olic Model Checking                             | 22 |

|                                                 | 2.3.1  | BDDs and SAT                                    | 22 |

|                                                 | 2.3.2  | Example for Symbolic Model Checking             | 29 |

| 2.4                                             | Indust | trially Scalable Verification Techniques        | 32 |

|                                                 | 2.4.1  | Bounded Model Checking                          | 32 |

|                                                 | 2.4.2  | Symbolic Simulation                             | 33 |

|                                                 | 2.4.3  | Combinational Equivalence Checking              | 35 |

|                                                 | 2.4.4  | GSTE                                            | 37 |

| 2.5                                             | More   | Abstraction Techniques                          | 39 |

|                                                 | 2.5.1  | Uninterpreted Functions                         | 40 |

|                                                 | 2.5.2  | Predicate Abstraction                           | 40 |

| 2.6                                             | Progra | am Analysis                                     | 43 |

|                                                 | 2.6.1  | Dependence Analysis                             | 44 |

|                                                 | 2.6.2  | Data Flow Analysis                              | 46 |

| Chapter 3 ACFG-Based Partitioned Model Checking |        |                                                 |    |

| 3.1                                             |        | luction                                         | 52 |

| 3.2                                             |        | ed Work                                         | 53 |

| •                                               | 3.2.1  | Software Specifications vs. Sequential Circuits | 53 |

|                                                 | 3.2.2  | Partitioned Model Checking                      | 54 |

| 3.3                                             | -      | tated Control Flow Graph                        | 55 |

| 3.4                                             |        | G-Based Model Checking                          | 58 |

| 3.5                                             |        | rimental Results                                | 62 |

|                                                 | ľ      |                                                 |    |

| Chapte                                          | ,      | Cutpoints for Embedded Software                 | 68 |

| 4.1                                             | Introd | luction                                         | 69 |

| 4.2                                             | Relate | ed Work                                         | 70 |

| 4.3                                             | Basic  | Verification Approach                           | 71 |

| 4.4                                          | Cutpo                           | ints for Software                                 | 74  |

|----------------------------------------------|---------------------------------|---------------------------------------------------|-----|

| 4.5                                          | Proof-of-Concept Implementation |                                                   |     |

| 4.6                                          | Exper                           | imental Results                                   | 81  |

| Chapte                                       | er 5 C                          | Cutpoints for Software vs. Combinational Circuits | 93  |

| 5.1                                          | Introd                          | uction                                            | 93  |

| 5.2                                          | Relate                          | d Work                                            | 94  |

| 5.3                                          | Challe                          | enge Problem: Instruction Length Decoder          | 96  |

| 5.4                                          | Verific                         | ation Algorithm                                   | 100 |

|                                              | 5.4.1                           | Preliminary Software Analysis                     | 101 |

|                                              | 5.4.2                           | Formal Equivalence Check                          | 103 |

| 5.5                                          | Exper                           | imental Results                                   | 107 |

|                                              | 5.5.1                           | Avoiding Path Enumeration                         | 111 |

|                                              | 5.5.2                           | Effect of Early Cutpoints                         | 113 |

|                                              | 5.5.3                           | Comparison with Other Tools                       | 114 |

|                                              |                                 |                                                   |     |

| Chapt                                        | er 6 (                          | Conclusion and Future Work                        | 115 |

| 6.1                                          | $\operatorname{Contr}$          | ibutions                                          | 115 |

| 6.2                                          | Futur                           | e Work                                            | 116 |

| Bibliography 118                             |                                 |                                                   | 118 |

| Appendix A ACFG Specification of SRT Divider |                                 |                                                   | 131 |

| Appen                                        | ıdix B                          | SRT Divider Gate-Level Circuit                    | 134 |

.

•

١

# List of Tables

| 3.1 | Unpartitioned Model Checking vs. ACFG Partitioned Model Checking | 66  |

|-----|------------------------------------------------------------------|-----|

| 3.2 | ACFG Partitioned Model Checking on Complete CFG                  | 67  |

| 4.1 | Software Pipeline Detailed Results                               | 84  |

| 4.2 | Block Move Detailed Results                                      | 91  |

| 4.3 | Convolution Detailed Results                                     | 91  |

| 4.4 | FIR Filter Detailed Results                                      | 92  |

| 5.1 | Toy Example                                                      | 107 |

| 5.2 | Circuit Sizes of Examples                                        | 111 |

| 5.3 | Path Enumeration vs. Linear BDD                                  | 112 |

| 5.4 | Linear BDD vs. Early Cutpoint                                    | 113 |

| 5.5 | hw-CBMC vs. Early Cutpoints                                      | 114 |

.

i.

,

# List of Figures

| 2.1  | Kripke Structure and Computation Tree           | 10 |

|------|-------------------------------------------------|----|

| 2.2  | Expressive Powers of Three Logics               | 15 |

| 2.3  | Algorithm to Compute the Least Fixpoint         | 17 |

| 2.4  | Fixpoint Characterization of CTL Operators      | 18 |

| 2.5  | Algorithm to Compute $\mathbf{EU}$ Operator     | 20 |

| 2.6  | Ordered Binary Decision Tree Example            | 23 |

| 2.7  | Reduction of Figure 2.6 to BDD                  | 24 |

| 2.8  | BDDs with Different Orderings for Function $f$  | 25 |

| 2.9  | Simple Gate Examples for SAT                    | 27 |

| 2.10 | Symbolic Model Checking Example                 | 30 |

| 2.11 | Combinational Equivalence Checking Example      | 36 |

| 2.12 | Cutpoint Example                                | 37 |

| 2.13 | Generic Example Circuit                         | 38 |

| 2.14 | Generic Example Assertion Graph                 | 38 |

| 2.15 | Algorithm for Reaching Definitions              | 48 |

| 2.16 | Algorithm for Live Variables                    | 51 |

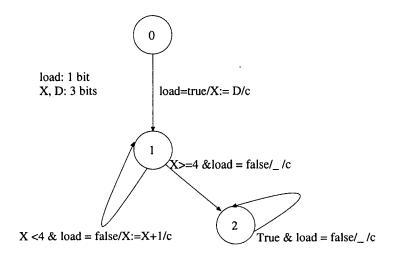

| 0.1  | ACTEC for a Connector Circurit                  | 57 |

| 3.1  | ACFG for a Counter Circuit                      |    |

| 3.2  | A Partitioned Model Checking Algorithm for ACFG | 61 |

| 3.3  | SRT Unsigned Fractional Division Algorithm      | 63 |

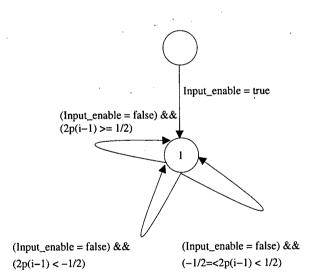

| 3.4  | ACFG for SRT Algorithm                          | 63 |

|      |                                                 |    |

| 3.5 | Example of ACFG Assignments            | 64  |

|-----|----------------------------------------|-----|

| 4.1 | Unpipelined Assembly Code              | 82  |

| 4.2 | Software Pipelined Assembly Code       | 83  |

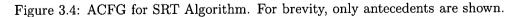

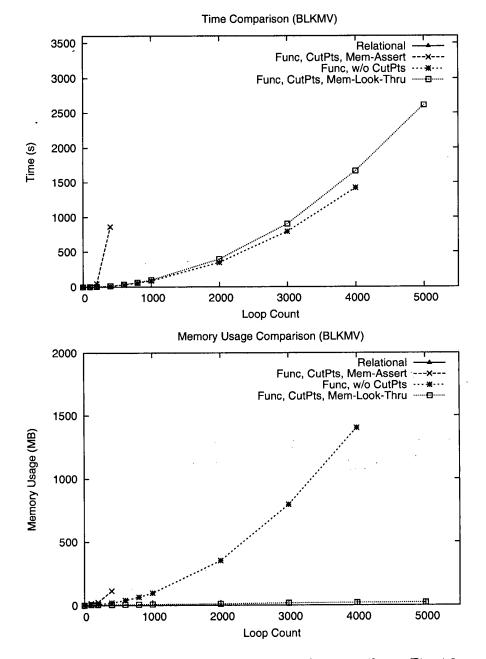

| 4.3 | Software Pipeline Results              | 85  |

| 4.4 | Block Move Results                     | 88  |

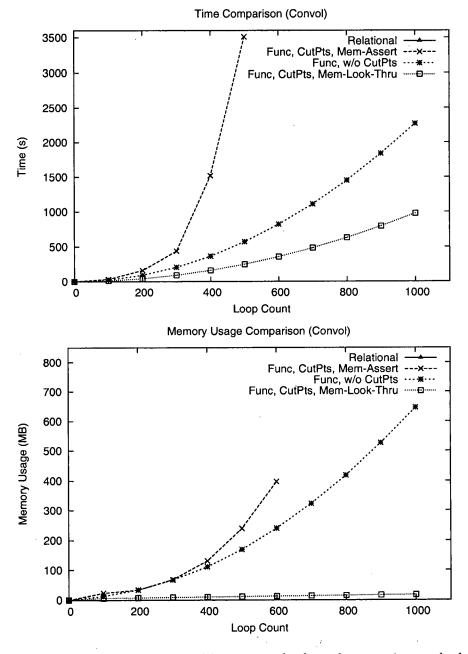

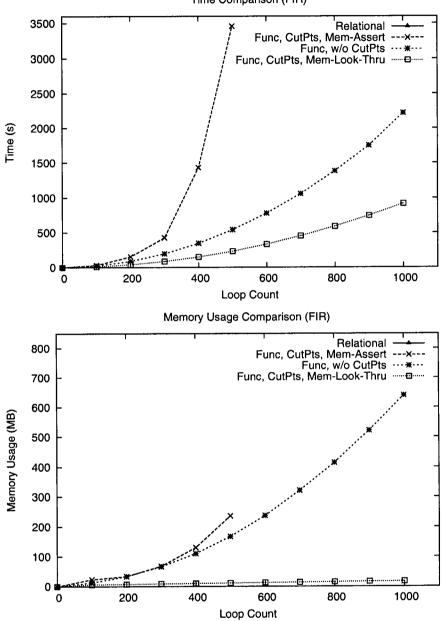

| 4.5 | Convolution Results                    | 89  |

| 4.6 | FIR Filter Results                     | 90  |

| 5.1 | IA-32 General Instruction Format       | 98  |

| 5.2 | Software Model Main Loop Pseudocode    | 99  |

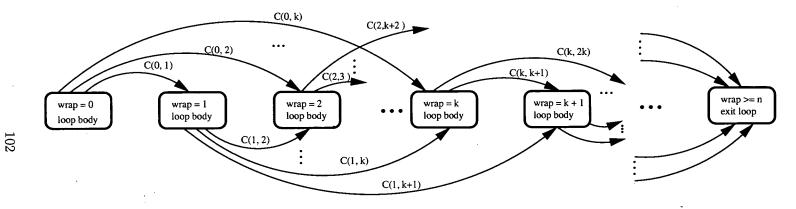

| 5.3 | Unrolled and Merged Control Flow Graph | 102 |

| 5.4 | Early Cutpoint Insertion               | 106 |

| 5.5 | C Code for TOY Example — Part 1        | 108 |

| 5.6 | C Code for TOY Example — Part 2        | 109 |

# List of Acronyms

| ACFG                 | Annotated Control Flow Graph                      |

|----------------------|---------------------------------------------------|

| BDD                  | Binary Decision Diagram                           |

| BLIF                 | Berkeley Logic Interchange Format                 |

| BMC                  | Bounded Model Checking                            |

| CFG                  | Control Flow Graph                                |

| CNF                  | Conjunctive Normal Form                           |

| $\operatorname{CTL}$ | Computation Tree Logic                            |

| CUDD                 | Colorado University Decision Diagram Package.     |

|                      | The CUDD package provides functions to manipulate |

|                      | Binary Decision Diagrams                          |

| DSP                  | Digital Signal Processing/Processor               |

| FIR                  | Finite Impulse Response                           |

| FPGA                 | Field Programmable Gate Array                     |

| GSTE                 | Generalized Symbolic Trajectory Evaluation        |

| IA-32                | Intel Architecture, 32-bit                        |

| ILD                  | Instruction Length Decoder                        |

| ISA                  | Instruction Set Architecture                      |

| LTL                  | Linear Temporal Logic                             |

| PLA .                | Programmable Logic Array                          |

| ROBDD                | Reduced Ordered Binary Decision Diagram           |

| RTL                  | Register Transfer Level                           |

|                      |                                                   |

х

| SAT  | Boolean SATisfiability                                                         |

|------|--------------------------------------------------------------------------------|

| SCC  | Strongly Connected Component                                                   |

| SIB  | Scale Index Base. Certain encodings of the $\mathrm{ModR}/\mathrm{M}$ by<br>te |

|      | require a second addressing byte (this SIB byte)                               |

| SRT  | A popular method for division in many processors.                              |

|      | Named for its creators (Sweeny, Robertson, and Toker).                         |

| SVC  | Stanford Validity Checker                                                      |

| TI   | Texas Instruments                                                              |

| VHDL | VHSIC (Very High Speed Integrated Circuit)                                     |

|      | Hardware Description Language                                                  |

| VLIW | Very Long Instruction Word                                                     |

. ж. т

. •

$\sim$

### Acknowledgments

First and foremost, I wish to thank my direct supervisor, Alan J. Hu. I enjoy his vast knowledge and owe him lots of gratitude for having a profound impact on this thesis. Throughout these years, he has given me much valuable advice on both research and life which I am very lucky to benefit from. Without him, this thesis would never have been completed.

I would also like to thank the other supervisory committee members, Eric Wohlstadter, Son Vuong, and Jin Yang for inspiration in many ways and valuable feedback on my research proposal and thesis. Thanks to my university examiners, Mark Greenstreet and Andre Ivanov, for helpful comments. Special thanks go to my external examiner, Robert B. Jones at Intel, for his suggestions on research examples and the enormous amount of time and effort that he put into my thesis.

I also owe my colleagues in the ISD lab thanks for helping me on this path and for making life at UBC more enjoyable. A special acknowledgment goes to Flavio M. De Paula for his solid industrial experience and help on questions about Verilog and VCS.

I would like to express my gratitude for my friends at UBC, particularly, Xiaodong Zhou and Jian Chen, for providing encouragement, exchanging knowledge, and serving as outlets for venting frustration during my graduate program. Last but not least, I must acknowledge my family for supporting me all the time. Thank you to my grandfather for encouraging me to pursue the PhD degree. Thank you to my mom and dad for always being supportive. Special thanks go to my wife, Shu, and my daughter, Ashley, without whose love, encouragement and patience, I would not have finished this thesis.

÷

### Chapter 1

### Introduction

### 1.1 Motivation

The traditional digital integrated circuit design process starts with a rough, highlevel description that gives the functionality of the circuit. The functional description can be defined using timing charts, state transition graphs, hardware description languages (e.g., Verilog or VHDL), or recent high-level design languages (SystemC, SystemVerilog, SpecC, etc.). After that, this functional specification is transformed into more detailed descriptions step-by-step. The steps include the following: architecture analysis, logic design, logic synthesis, and physical design.

Architecture analysis is the first step in the design flow. In this step, the human designers explore different architectural requirements, such as performance, area, and power. After that, the designers generate a behavior-level design, which describes the functionality of each unit, the interconnections, and the resource allocations. Scheduling (the task of determining start times of operations subject to precedence) and resource binding (the task of determining which modules will execute these operations) are two important steps for architecture analysis. After architecture analysis finishes, logic design is undertaken. In this step, the Register Transfer Level (RTL) of the design is manually generated. This RTL design includes Boolean formulas and timing information. Logic synthesis takes the output of logic design, i.e., RTL descriptions, and generates an optimized technology-specific network (netlist) of logic primitive modules (AND, OR, etc.) in a particular library. This step is often automatically executed by logic synthesis tools. Synthesis techniques of this step differ according to the nature of the circuit (combinational or sequential) or the intended implementation architecture (multilevel logic, PLA (Programmable Logic Array), or FPGA (Field Programmable Gate Array)).

Physical design is the last step in the design process. Design tools or humans generate the geometric patterns that define the physical circuit details that will be implemented on silicon. During this step, procedures such as floorplanning, placement, and routing are performed.

All the steps of the design process need equivalence verification checking to ensure that the implementation follows the specification and that there are no bugs introduced by manual design optimization or synthesis tools. For RTL or below, abundant research and tools are available to do these jobs. They have proven to be successful for many practical circuits. Considering the complexity of the design process and circuits, a new trend of design methodology is moving design and verification to higher levels. This is because with the increasing complexity of circuit design, functional verification is becoming more and more difficult. RTL simulation and verification have emerged as a major bottleneck of the design cycle. Increasingly, companies are writing high-level functional specifications in software, to allow much faster preliminary simulation. Such high-level functional specifications usually start in C or C-like languages. These specifications can be efficiently compiled into executable machine code to enable fast simulation [98]. In addition, these high-level specifications are flexible for modification and easy to maintain. Therefore, during the phases of architectural analysis and high-level design, the system designers can play with software specifications to achieve better performance or other goals by fast simulation. Just as the widespread adoption of logic synthesis generates the need

$\mathbf{2}$

for RTL-to-gate verification, analogously, the use of a high-level design methodology introduces a need for Software-to-RTL verification. Thus, it is necessary to use verification tools to determine the equivalence of software and hardware.

### **1.2** Contributions

Addressing formal equivalence checking of software specifications vs. hardware implementations, my thesis focuses on reducing the complexity of this verification and increasing the capability of current verification techniques. I have two major contributions: ACFG-based partitioned model checking and cutpoints for equivalence checking with software models.

### 1.2.1 ACFG-Based Partitioned Model Checking

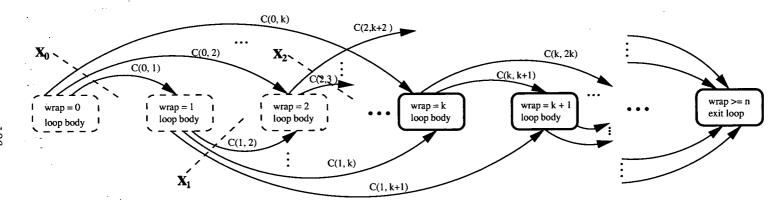

In [38], I introduced a partitioned model checking approach using Annotated Control Flow Graphs (ACFG) to represent software specifications for sequential circuits. To model check the hardware implementation against the ACFG, the standard approach is to build a single product automaton combining the ACFG and the hardware model and then performing reachability analysis on the combined model. However, such an approach is prone to the state explosion problem.

My model checking solution, instead, is based on GSTE-style model checking proposed in [96]. The key idea is to partition the software states and the hardware states based on the structure of the ACFG, and use the flow and the annotation on edges in the ACFG to guide and tailor the state space exploration. More specifically, I compute a simulation relation sim(e) for each edge e in the ACFG, such that the simulation relation tells us (1) what is the set of states the software model can be in on the particular edge e, and (2) for each such state, what is the corresponding set of possible states in the hardware model. The consequent on the edge is then checked against the simulation relation.

The experimental results show that in all test cases, the new partitioned

model checking approach runs faster, sometimes much faster, than global reachability analysis.

#### 1.2.2 Cutpoints for Embedded Software

Most work in my thesis is inspired by the success of RTL vs. gate-level combinational equivalence checking. A key technique behind this success is the idea of cutpoints [9, 12]: since the two combinational circuits are presumed to be structurally similar, there should be intermediate points in the two circuits that are logically equivalent. Heuristics search for such possibly equivalent intermediate points, and the tool first tries to prove such points equivalent. If successful, the equivalent logic behind the cutpoints is removed and replaced by a new primary input, thereby simplifying the verification problem. In general, the method is conservative (i.e., success proves equivalence, but failure doesn't prove inequivalence) because constraints on the cutpoint "inputs" are lost; various techniques re-introduce constraints to reduce this problem, e.g., [12].

We can see that cutpoints exploit the structural similarity of two combinational circuits, and therefore, simplify the verification. I believe that in verification of software specifications vs. hardware implementations, there exists a certain degree of similarity between the software model and the hardware implementation due to the similar functionality they have. Such similarities imply the existence of cutpoints. I give a definition of cutpoints for software: a cutpoint in software is some part of the program state at some point in one program, which is provably equal to some part of the program state at some point in another program.

Based on the above definition, I first apply software cutpoint theory to formal equivalence verification of embedded software to see the consequence of cutpoint insertion. In [36], I address several novel problems: how detailed will the cutpoint analysis be, how to find candidate cutpoints, and how to reduce false inequivalence. Then, I give solutions for the above questions and implemented a proof-of-concept

4

cutpoint approach in my prototype verification tool for the Texas Instruments (TI) C6x family of very long instruction word (VLIW) digital signal processors (DSPs).

I have run experiments using several test cases which include compileroptimized code and some expert hand-tuned DSP signal-processing routines from a TI-supplied library. Experimental results on these test cases show large improvements in runtime and memory usage over the previous state-of-the-art [60].

### **1.2.3** Early Cutpoint Insertion for Combinational Circuits

Building on the success of adapting the cutpoint idea to embedded software, I further introduce cutpoints into the formal equivalence verification of software specifications vs. hardware implementations [37].

Unlike the work for embedded DSP software, software paths in software specifications of hardware are more complicated. There are fewer similarities between the software specifications and hardware implementations — the same functionality is easy to describe sequentially in software, but it will be executed on highly parallel hardware. In addition, enumerating paths becomes difficult and suffers from exponential blow-up in the number of paths, and the corresponding equivalent points between the software and the hardware are not at all obvious. Fortunately, an analysis of the software can give us many high-level heuristics to guide the space exploration and abstraction. The first phase of my approach uses preliminary software analysis to unroll loops, merge paths as much as possible, and generate an unrolled graph. The second phase verifies the equivalence of the software and the hardware, while inserting cutpoints during the processing of the unrolled graph. The construction of the unrolled graph is linear in the size of the software (with all loop bodies instantiated). There is no exponential blow-up of path enumeration. In the formal equivalence checking phase, path conditions are computed on-the-fly. If some part of the program state at some point in the software is provably equal to some wire in the hardware, a new primary input is introduced in its place. This

reduces the complexity of both hardware and software. If this process can be continued to the outputs of the software specification and hardware implementation, then equivalence has been formally verified.

I have run experiments on an industry-suggested challenge problem. Experimental results show that early cutpoint insertion can complete more instances than previous approaches. On those instances that the previous approaches can complete, the early cutpoint insertion achieves typically a 100x improvement in runtime and a 20x improvement in memory usage.

### **1.3** Thesis Outline

Chapter 2 provides a brief overview of background material. The next three chapters (Chapter 3, 4, and 5) present thesis contributions. Chapter 3 describes the ACFG-based partitioned model checking approach. In Chapter 4, I introduce a definition of cutpoints for software and apply it to embedded software. Chapter 5 explains the early cutpoint insertion approach for verifying software against combinational circuits. Chapter 6 contains my conclusions and suggestions for future research directions.

### Chapter 2

### Background

This chapter provides the background material for my research. This background is drawn from two areas: formal verification and program analysis. Formal verification is a broad area and has many subtopics. To limit the scope of this thesis, I present only the background that is related to the problems addressed in my thesis. As for program analysis, I apply simple, light-weight, static analysis techniques: dependence analysis and data-flow analysis. Therefore, I provide only a brief material to program analysis. This chapter gives the general background of my thesis; the specific related work for Chapters 3-5 is in each chapter.

### 2.1 Formal Verification

Formal verification is a technique to prove (or in some cases, disprove) the validity of an implementation with respect to a given specification using mathematical methods. The term *implementation* refers to the actual model of the system. *Specification*, on the other hand, refers to certain properties of the system. Such properties are described using formal methods (e.g., logic languages, state graphs, etc.). Compared with traditional simulation-based testing and other general reliability measures, formal verification is precise, well-defined, and assures a small probability of bugs slipping through unnoticed. There are two major formal verification approaches: theorem proving and model checking.

In theorem proving, also known as deductive reasoning, the verification problem is described as a theorem in a formal theory. Given a set of axioms and a set of inference rules, the proof that the implementation realizes the specification is semi-automatically constructed and mechanically checked by a theorem prover (e.g., PVS [76], ACL2 [58], HOL [42], etc.) using deductive reasoning. With sufficient human ingenuity, any true (provable with the axiom system) theorem can eventually be proven. However, this approach is often time-consuming and is known to be labour-intensive, requiring considerable person-time to learn and use. In addition, there is no guarantee that the proving procedure will terminate.

Model checking, on the other hand, is less expressive, but can be fully automated and requires little time to learn. It is a technique to prove correctness of finite state concurrent systems. To be specific, the goal of model checking is to check whether a given model satisfies a given property using automatic decision procedures. Therefore, it guarantees termination. It has been successfully applied to digital sequential circuits and communication protocols. Since the focus of my thesis is on automatic formal verification, model checking is the more relevant approach to my work.

### 2.2 Model Checking Introduction

Model checking [24, 78] is a technique for automated verification of an implementation with respect to a specification. In order to perform model checking, three steps are performed: *modeling*, *specification*, and *verification*. In the step of modeling, we describe the system and convert the system into a formalism. Usually, the implementation of the system is described as a finite-state system (automaton). In the step of specification, we formulate properties as formulas in temporal logic (e.g., CTL, LTL, etc. described later) or some other formal description. At the last step, verification, efficient algorithms are used to traverse the model defined by the system and check if the specification holds or not. Commonly, a model-checking tool accepts an implementation and a property that the system is expected to satisfy. Then, the tool outputs "yes" if the given model satisfies the given properties. Otherwise, it generates a particular counterexample in the form of a sequence of states that violates the properties.

#### 2.2.1 Modeling and Specification

#### **Kripke Structure**

First, I introduce how to do the modeling. The implementation, which is also referred to as a design, system, or model in this thesis, is usually some sort of a finite-state automaton, which is represented as a *Kripke structure* in the model checking domain.

A Kripke structure is a model used to give semantics (definitions of when a specified property holds) for modeling temporal logics. In the model checking domain, a Kripke structure is a graph having the states of the system as nodes and state transitions of the system as edges. It also contains labelings of the states in the structure with properties that hold in each state. The following is the formal definition.

**Definition 2.1 (Kripke Structure)** Let AP be a non-empty finite set of atomic propositions that denotes the properties of individual states we are interested in. A Kripke structure is a four tuple  $M = (S, s_{init}, R, L)$ , where

- S is a finite set of states,

- $s_{init} \in S$  is the initial state,

- $R \subseteq S \times S$  is a transition relation,

L: S → 2<sup>AP</sup> is a labeling function that attaches observations to the system.

For a state s ∈ S, L(s) is the atomic propositions that hold in state s.

A path is an infinite sequence of states  $\pi = \pi_0, \pi_1, \pi_2, \pi_3...$  where  $(\pi_i \in S) \land ((\pi_i, \pi_{i+1}) \in R)$  for  $i \ge 0$ .  $\pi_j$  is forward reachable from  $\pi_i$  iff there exists a path to  $\pi_j$  and this path starts from  $\pi_i$ .  $\pi_i$  is backward reachable from  $\pi_j$  iff  $\pi_j$  is forward reachable from  $\pi_i$ .

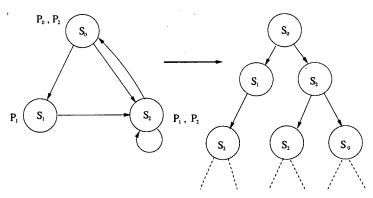

The Kripke structure can be unwound into an infinite tree with the initial state  $s_{init}$  as the root, and each path in the tree represents a possible sequence of computation. Figure 2.1 shows a Kripke structure and its equivalent infinite computation tree. There are three states in this Kripke structure  $\{s_0, s_1, s_2\}$ . The initial state is  $s_0$ . The transition relations R is the set  $\{(s_0, s_1), (s_0, s_2), (s_1, s_2), (s_2, s_2), (s_2, s_0)\}$ . The labeling function  $L = \{L(s_0) = \{P_0, P_2\}, L(s_1) = \{P_1\}, L(s_2) = \{P_1, P_2\}\}$ , where  $P_i$   $(0 \le i \le 2)$  is an atomic proposition.

Figure 2.1: Kripke Structure and Computation Tree

#### Specification — Temporal Logic

Now that we have the model defined, we can introduce properties to characterize paths on a Kripke structure.

In order to capture the properties, temporal logic — a formalism used to describe how system states will change over time — is used as the specification

language. In this thesis, I concentrate on *Computation Tree Logic* (CTL). It is a propositional, branching-time, temporal logic proposed by Clarke and Emerson in 1981 [24]. CTL, one of the most popular logics for practical model checking, uses atomic propositions as the basis, and formulas are constructed from logical operators, temporal operators and path quantifiers to make statements about the Kripke structure.

First, I will introduce the CTL\* (pronounced "CTL-star") logic [32]. CTL is a restricted subset of CTL\* where each of the temporal operators must be immediately preceded by a path quantifier. Informally, the operators are as follows.

- logical operators:  $\lor, \neg$

- temporal operators:

- Unary operators:

- \* **X** $\Phi$  Next ( $\Phi$  has to hold at the next state)

- \* **G** $\Phi$  Globally ( $\Phi$  has to hold on the entire subsequent path)

- \*  $\mathbf{F}\Phi$  Finally ( $\Phi$  eventually has to hold on the subsequent path)

- Binary operators:

- \*  $\Phi U \Psi$  Until ( $\Phi$  has to hold on the subsequent path until at some position  $\Psi$  holds)

- path quantifiers:

- A: All (for all computation paths from the current state)

- E: Exists (for at least one path from the current state)

The above operators and quantifiers can be used to express temporal properties of a Kripke structure. We are now ready to formally define the **syntax** of CTL\*.

There are two types of formulas over the Kripke structure — *state formulas* and *path formulas*.

**Definition 2.2** If f is a  $CTL^*$  state formula, it must be constructed by one of the following rules:

- f is an atomic proposition.

- $f = \neg g$ , where g is a state formula.

- $f = g \lor h$ , where g, h are state formulas.

- f = Ap, where p is a path formula.

- f = Ep, where p is a path formula.

**Definition 2.3** If p is a  $CTL^*$  path formula, it must be constructed by one of the following rules:

- p is a state formula.

- $p = \neg q$ , where q is a path formula.

- $p = q \lor r$ , where q, r are path formulas.

- p = Xq, where q is a path formula.

- p = Gq, where q is a path formula.

- p = Fq, where q is a path formula.

- p = q Ur, where q, r are path formulas.

$CTL^*$  is the set of finite-length state formulas that can be constructed by applying the above rules. Here are two examples of  $CTL^*$  formulas.<sup>1</sup>

•  $AG(Req \Rightarrow AFAck)$ : if a Req (*Request*) occurs, then it will be eventually acknowledged (Ack). This is a *liveness property*. A liveness property declares

<sup>&</sup>lt;sup>1</sup>In fact, these two formulas are also CTL formulas.

what should eventually happen. A simple counterexample to liveness properties is a path to a loop that does not contain the desired state, as such a loop represents an infinite path that never reaches the specified state.

AG(¬(pc<sub>1</sub> = CR<sub>1</sub>) ∨ ¬(pc<sub>2</sub> = CR<sub>2</sub>)): processes (pc<sub>1</sub>, pc<sub>2</sub>) will never be in their critical section (CR<sub>1</sub>, CR<sub>2</sub>) simultaneously. This is a safety property for a concurrent system. A safety property declares that something bad will never happen (or equivalently, what should always happen). Each violation of a safety property can be observed by looking at a finite history of the system behavior.

Before giving the semantics of CTL\*, I will define the meaning of the  $\models$  relation.

**Definition 2.4** If f is a CTL\* state formula, and M is a Kripke structure, the formula  $M, s \models f$  denotes that f holds at state s in the Kripke structure M.

**Definition 2.5** If f is a CTL\* path formula, M is a Kripke structure, and  $\pi$  is a path, the formula  $M, \pi \models f$  denotes that f holds along path  $\pi$  in the Kripke structure M.

Now, we are ready to define the semantics of CTL<sup>\*</sup>. Definition 2.6 gives the formal semantics of CTL<sup>\*</sup> over the Kripke structure.

**Definition 2.6** The relation  $\models$  is defined inductively as follows. In the following definitions, s is a state, M is a Kripke structure,  $f_1, f_2$  are state formulas,  $p_1, p_2$  are path formulas,  $\pi^n$  is the suffix of the path  $\pi$  that begins at  $\pi_n$ .

- If  $f_1 \in AP$ , then  $M, s \models f_1 \Leftrightarrow f_1 \in L(s)$ .

- $M, s \models \neg f_1 \Leftrightarrow M, s \not\models f_1.$

- $M, s \models f_1 \lor f_2 \Leftrightarrow M, s \models f_1 \text{ or } M, s \models f_2.$

- $M, s \models A(p_1) \Leftrightarrow \text{for all paths } \pi \text{ starting with } s, \text{ such that } M, \pi \models p_1.$

- $M, s \models E(p_1) \Leftrightarrow$  there exists a path  $\pi$  starting with s, such that  $M, \pi \models p_1$ .

- $M, \pi \models f_1 \Leftrightarrow s$  is the first state of  $\pi$  and  $M, s \models f_1$ . i.e., each state formula is also a path formula.

- $M, \pi \models \neg p_1 \Leftrightarrow M, \pi \not\models p_1.$

- $M, \pi \models p_1 \lor p_2 \Leftrightarrow M, \pi \models p_1 \text{ or } M, \pi \models p_2.$

- $M, \pi \models Xp_1 \Leftrightarrow M, \pi^1 \models p_1.$

- $M, \pi \models \mathbf{G}p_1 \Leftrightarrow \text{for all } k \ge 0, M, \pi^k \models p_1.$

- $M, \pi \models Fp_1 \Leftrightarrow$  there exists a  $k \ge 0, M, \pi^k \models p_1$ .

- $M, \pi \models p_1 U p_2 \Leftrightarrow$  there exists a  $k \ge 0$  such that  $M, \pi^k \models p_2$  and for all  $0 \le j < k, M, \pi^j \models p_1$ .

After such definitions, the model checking problem is reduced to: given an implementation represented by a Kripke structure M, and a specified property  $\phi$  in a certain temporal logic, determine whether  $M, s_{init} \models \phi$ .

As I said at the beginning of this section, CTL is more popular in the model checking domain due to its efficiency. Unlike CTL\*, in which a formula can be composed of arbitrary combinations of temporal operators and path quantifiers, the logic CTL, on the other hand, given the constraint that each of the temporal operators must be immediately preceded by a path quantifier, ends up with only 8 basic operators: **AX** and **EX**; **AG** and **EG**; **AF** and **EF**; **AU** and **EU**. It is proven that the model checking problem for CTL\* is in PSPACE and can be solved in time  $2^{O(|\phi|)} \times O(|S| + |R|)$  [33], which is exponential in the size of the property's formula. In contrast with CTL\*, the model checking problem for CTL is P-hard and can be solved in time  $O(|\phi| \times (|S| + |R|))$ , which is linear in the size of the Kripke structure and is linear in the size of the property's formula. This exponential time vs. linear time difference is due to CTL\*'s arbitrary combinations of temporal operators and path quantifiers, which introduces more expressive power but more expensive computations as well.

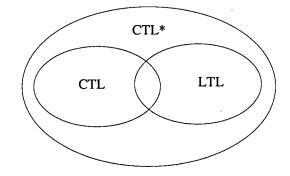

There is another temporal logic — linear temporal logic (LTL [77], proposed by Pnueli) which is also frequently used in the model checking. It is also a subset of CTL\*. Unlike CTL, the formulas of LTL don't have path quantifiers. Instead, LTL formulas are global, which means that every formula of LTL implicitly has the path quantifier **A** before it. Therefore, the holding of an LTL formula means the formula holds on all paths. It is impossible to say "there exists a path such that...". The complexity of LTL model checking is the same as that of CTL\*, however, LTL has less expressive power. Figure 2.2 shows the relationship of the expressive powers of CTL\*, CTL, and LTL. For example, there is no CTL formula that is equivalent to the LTL formula FGp (or A(FGp)) if we add the path quantifier **A** to avoid confusion). Likewise, there is no LTL formula that is equivalent to the CTL formula AG(EFp). The disjunction  $A(FGp) \lor AG(EFp)$  is a CTL\* formula that is not expressible in either CTL or LTL.

Figure 2.2: Expressive Powers of Three Logics

### 2.2.2 Verification Algorithms

#### **Fixpoint Characterization**

After we have defined the model (e.g., Kripke structure) and the specified properties (e.g., CTL\*, CTL, or LTL formulas) on this model, the model checking algorithm will exhaustively search the state space of the model to determine the truth of the specification. For example, we want to check whether EGf holds at the initial state, i.e., we want to check whether there exists an infinite path (starting from the initial state), along which f is always true at all future states. In order to do that, we need to compute the set of states that f holds at the current state and EGf holds for some successors (f holds at the first two states of the infinite path), i.e.,  $Q_1 = f \wedge EXEGf$ . For the successors in  $Q_1$ , we also need to check whether EGf holds or not for their successors. Then, we keep doing the same computation,  $Q_2 = f \wedge EXEG(Q_1)$ , etc., until we reach a set  $Q_{i+1}$  where  $Q_{i+1} = Q_i$ . We call this a fixpoint. If the initial state is inside the fixpoint, we have proven that EGf holds at the initial state. After some preliminary definitions [31], I will show how to use the fixpoint characterization for CTL operators.

**Definition 2.7 (Predicate)** Given a Kripke structure  $M = (S, s_{init}, R, L)$  and  $x \in 2^S$ , the set of states x defines a predicate PRED(x) on S. A state s satisfies PRED(x) iff  $s \in x$ . A set of predicates comes with a natural partial order due to set inclusion/implication.

For example, a state formula  $\phi$  in CTL is a predicate. If x is the set of states satisfying  $\phi$ , then  $M, s \models \phi \Leftrightarrow s \in x$ , where M is the given Kripke structure.

**Definition 2.8 (Predicate Transformer)** A predicate transformer  $\tau$  is a function that maps a predicate to another predicate. i.e,  $\tau: PRED(2^S) \to PRED(2^S)$ . The predicate transformer  $\tau$  is said to be monotonic, if  $P \Rightarrow Q$  implies  $\tau(P) \Rightarrow \tau(Q)$ . 1: function  $lfp(\tau)$ 2: Q := False;3:  $Q' = \tau(Q);$ 4: while  $(Q \neq Q')$  do 5: Q := Q';6:  $Q' = \tau(Q);$ 7: end while 8: return (Q);

Figure 2.3: Algorithm to Compute the Least Fixpoint

For example, the operator **EX** in CTL is a predicate transformer that maps  $\phi$  to **EX** $\phi$ , where  $\phi$  is a CTL formula.

**Definition 2.9 (Fixpoint)** A fixpoint of a predicate transformer  $\tau$  is a predicate Q such that  $\tau(Q) = Q$ . i.e, if a predicate Q doesn't change by applying the predicate transformer  $\tau$ , the predicate Q is a fixpoint of  $\tau$ . The theorem of Tarski-Knaster [91] ensures that a monotonic function  $\tau$  always has a least fixpoint  $(lfpZ.\tau(Z) = \bigwedge \{Q : \tau(Q) = Q\})$ , and a greatest fixpoint  $(gfpZ.\tau(Z) = \bigvee \{Q : \tau(Q) = Q\})$ .

Figure 2.3 lists the algorithm for computing the least fixpoint for the predicate transformer  $\tau$ .<sup>2</sup> For finite-state model checking, the algorithm terminates due to the fact that the model is a finite state system.

As I have mentioned, given a Kripke structure  $M = (S, s_{init}, R, L)$  and a CTL formula  $\phi$ , the model checking algorithm checks whether  $M, s_{init} \models \phi$ . This algorithm is equivalent finding the fixpoint Q for the predicate transformer corresponding to  $\phi$ , and then checking whether  $s_{init}$  satisfies Q to ensure that the formula  $\phi$  holds at the initial state  $s_{init}$ .

<sup>&</sup>lt;sup>2</sup>Unlike the algorithm that computes the least fixpoint, the algorithm for computing the greatest fixpoint gives the initial value of Q an assignment *True* instead of *False* in line 2 of Figure 2.3. The other lines are the same. In practical model checking problems,  $\tau$  is always monotonic.

- $p\mathbf{AU}q = \mathbf{lfp} \ Z[q \lor (p \land \mathbf{AX}Z)]$

- $p\mathbf{EU}q = \mathbf{lfp} \ Z[q \lor (p \land \mathbf{EX}Z)]$

- $\mathbf{AF}p = \mathbf{lfp} \ Z[p \lor \mathbf{AX}Z]$

- $\mathbf{EF}p = \mathbf{lfp} \ Z[p \lor \mathbf{EX}Z]$

- $\mathbf{AG}p = \mathbf{gfp} \ Z[p \land \mathbf{AX}Z]$

- $\mathbf{EG}p = \mathbf{gfp} \ Z[p \land \mathbf{EX}Z]$

Figure 2.4: Fixpoint Characterization of CTL Operators

Each of the CTL operators can be elegantly characterized as the least or greatest fixpoint of an appropriate predicate transformer, as shown in Figure 2.4 [31]. Therefore, the problem of finding the set of states that satisfies a CTL formula for a given Kripke structure is the same as the problem of finding a fixpoint for a predicate transformer using the algorithm in Figure 2.3. The computations for **EX** and **AX** in Figure 2.4 are as follows:

- $M, s \models \mathbf{EX}p \Leftrightarrow s \in \{s : \exists s'.R(s,s') \land (M,s' \models p)\}$ , or equivalently  $EXp = PRED(\{s : \exists s'.R(s,s') \land (M,s' \models p)\})$

- $M, s \models \mathbf{AX}p \Leftrightarrow s \in \{s : \forall s'.R(s,s') \land (M,s' \models p)\}$ , or equivalently  $AXp = PRED(\{s : \forall s'.R(s,s') \land (M,s' \models p)\})$

As an example, consider the EG operator. According to Figure 2.4,  $EGp = gfpZ[p \wedge EXZ]$ . We need to compute the greatest fixpoint for EG using the algorithm from Figure 2.3, except we start  $Q_0$  with an initial assignment *True*. The sequence of computations is:

- $Q_0 = True$

- $Q_1 = p \wedge \mathbf{EX}(Q_0) = p$

- $Q_2 = p \wedge \mathbf{EX}(Q_1) = p \wedge \mathbf{EX}(p)$

- $Q_3 = p \wedge \mathbf{EX}(Q_2) = p \wedge \mathbf{EX}(p \wedge \mathbf{EX}(p))$

- ...

. .•

• until  $Q_{i+1} = Q_i$

When we reach this fixpoint  $Q_i$ , every state that satisfies  $Q_i$  has a successor that satisfies p in the Kripke structure. In other words, for every state that satisfies  $Q_i$ , there is an infinite path starting from the state and p always holds on the path.

#### Explicit Model Checking Algorithm

A direct implementation of the fixpoint characterization is explicit state enumerating, i.e., we use some data structure to explicitly store states and use graph traversal algorithms to find the states which satisfy the formulas. I will give a short description for such an algorithm in this section.

Such an algorithm is presented as three steps below. Just as in graph colouring, the algorithm marks the set of states where each CTL subformula holds.

*First*, we can rewrite the formula  $\phi$  to  $\phi_{trans}$  which contains only atomic operators like  $\neg, \lor, \mathbf{EX}, \mathbf{EU}, \mathbf{EG}$ . The other CTL operators can be rewritten as follows:

- $\mathbf{A}\mathbf{X}p \Leftrightarrow \neg \mathbf{E}\mathbf{X}\neg p$

- $\mathbf{AG}p \Leftrightarrow \neg \mathbf{EF} \neg p$

- $\mathbf{AF}p \Leftrightarrow \neg \mathbf{EG}\neg p$

- **EF** $p \Leftrightarrow true$  **EU** $\neg p$

- $p\mathbf{AU}q \Leftrightarrow \neg(\neg p \mathbf{EU}\neg(p \lor q) \lor \mathbf{EG}\neg q)$

Second, for each subformula  $\phi_{sub}$  of  $\phi_{trans}$ , if  $\phi_{sub}$  is an atomic proposition or a formula which has already been handled, the algorithm marks the set of states that satisfies the subformula  $\phi_{sub}$ ; if  $\phi_{sub}$  is a formula which hasn't been handled, the algorithm recursively handles the subformula  $\phi_{sub}$ . This step will terminate when the whole formula  $\phi_{trans}$  has been handled.

Third, the algorithm checks whether the initial state is inside the final set of satisfied states, i.e., whether the formula  $\phi$  holds at the initial state  $s_{init}$ .

I take the **EU** operator as an example to explain how the second step works (the handling of the logic operators is straightforward according to their meanings, and handling of the atomic propositions is just a simple searching and marking algorithm).

The input is: a set of states  $S_p$  that satisfies formula p and a set of states  $S_q$  that satisfies the formula q (i.e., assume p and q have been handled). We need the set of states where  $p \in Uq$  holds.

```

function EU(S_p, S_q)

mark states S_q;

while new state is found do

if there is a state in S_p that has some successor state marked then

mark it;

end if

end while

return all marked states;

```

#### Figure 2.5: Algorithm to Compute EU Operator

Figure 2.5 shows the algorithm, which starts from  $S_q$ , and performs backward reachability using only states in  $S_p$ . It terminates because it is a monotonic function in the finite state space of the Kripke structure. We can see that the algorithm makes progress of at least one state per iteration, and for each iteration, it visits each state and edge at most once. Therefore, the algorithm is quadratic in the size of the Kripke structure, i.e., the complexity of the simple depth-first algorithm for the **EU** operator is  $O(|S| \times (|S| + |R|))$ , where |S| is the size of the state space and |R| is the number of edges in the Kripke structure. A more efficient algorithm is realized by remembering visited states and using backward breadth-first searching. Such an algorithm avoids visiting any state twice. The improved algorithm has complexity O(|S| + |R|).

Similarly, we can introduce algorithms for the **EX** and **EG** operators. The algorithm for **EX**p is easy. It simply marks all predecessors of states  $S_p$ . An efficient algorithm for **EG**p is a little bit complicated. It needs to find an infinite path on which p always holds. In order to do that, we first restrict the Kripke structure to states satisfying p (i.e., remove all the other states and edges), then identify the maximal non-trivial Strongly Connected Components (SCC).<sup>3</sup> On such SCCs, **EG**p holds. By doing so, our problem is reduced to finding a path from the initial state to such SCCs on which p always holds (such a path is finite!). We can use a breath-first searching on the simplified Kripke structure. This algorithm has the same complexity as the efficient algorithm for the **EU** operator.

Therfore, the complexity of the model checking algorithm for a CTL formula  $\phi$  is  $O(|\phi| \times (|S| + |R|))$ , i.e., it is linear in the size of the formula, and is linear in the size of the Kripke structure.

Although the CTL model checking algorithm is linear in the size of the Kripke structure, the size of the Kripke structure is exponential in the number of variables and concurrent components. For example, given a concurrent system with n components and m local states inside each component, the Kripke structure for such a system will have  $m^n$  global states! Such an exponential state space may introduce the biggest limitation of model checking, which is called the *state explosion problem*. With this state explosion, explicitly representing states often turns out to be impractical. In order to attack this problem, techniques, such as Boolean algebra, are used to implicitly represent sets of states and transition relations. By using Boolean formulas, the size of states that model checking can handle is greatly increased. In the next section, I will present such an approach.

<sup>&</sup>lt;sup>3</sup>A component is strongly connected iff every node can be reached from every other node. Non-trivial means this SCC has  $\geq 2$  states or has one state with a self-loop

### 2.3 Symbolic Model Checking

Symbolic Model Checking usually uses BDDs, SAT, or mixed BDDs and SAT to prove the validity or to represent states and transition relations. In this section, I will introduce BDDs and SAT first. After that, I will explain the symbolic model checking approach by using an example.

#### 2.3.1 BDDs and SAT

### BDDs

In 1986, Bryant [14] proposed Reduced Ordered Binary Decision Diagrams (ROB-DDs, or BDDs for short) by imposing restrictions on the representation first introduced by Lee [64] and Akers [2]. BDDs are efficient representations for Boolean formulas due to their compactness and canonicity. Canonicity is particularly useful: given equivalent Boolean formulas, BDDs for these formulas will be identical (for the same BDD variable ordering, described later). Therefore, the equivalence of two Boolean formulas can be reduced to comparisons of BDDs which can be checked in constant time. This canonicity, therefore, allows substantial subformula sharing, often resulting in the compactness of BDDs.

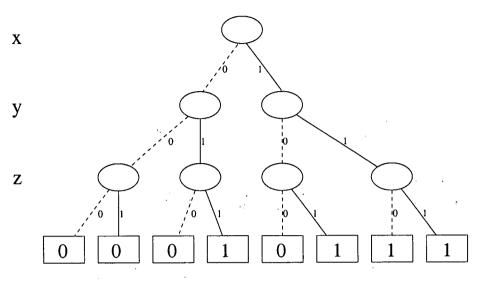

BDDs originate from ordered binary decision trees. Figure 2.6 is an example of an ordered binary decision tree for the Boolean function f(x, y, z) = (xy+xz+yz). The variable ordering is given as x < y < z.

In Figure 2.6, each non-terminal vertex is labeled by a variable name x, y, zand has two children: one child is the case that the variable is assigned to the value 0 (0-arc, dashed lines), the other child is the case that the variable is assigned to the value 1 (1-arc, solid lines). Each terminal vertex is labeled 0 or 1 which is determined by the function f.

Figure 2.6: Ordered Binary Decision Tree Example

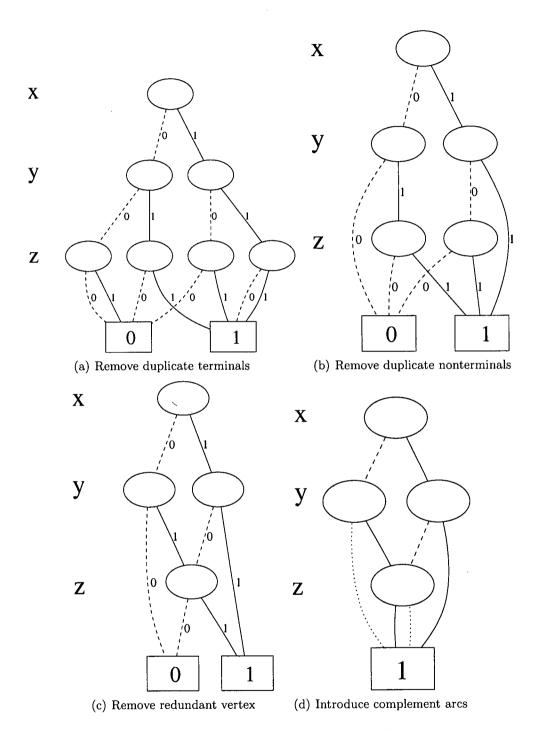

A BDD is an ordered decision tree where we remove duplicate terminals, remove duplicate nonterminals, and remove redundant vertices. i.e. all isomorphic subtrees are combined, all nodes with isomorphic children are eliminated. Figure 2.7 shows how to do these steps. After these simplifications, the BDD is canonical under a given variable ordering. The BDD for function f is given in Figure 2.7(c). The size of a BDD can be further reduced by introducing complement arcs, which point to the negation of the original function. To keep the canonicity, a complement arc can only be assigned to the pre-specified arc, i.e., we only do negation for the case when a variable is assigned to the value 0. For example, a more simplified BDD (Figure 2.7(d)) is given by introducing complement arcs to 0-arc (dotted lines).

BDDs have proven to be a successful representation for model checking on many practical systems. However, for larger industry-size systems, the BDD-based verification tools can not produce results due to the exponentially increasing BDD size, which blows up beyond the memory capabilities of most machines. This is commonly known as the *BDD blow-up problem*.

•

·. .

•

Figure 2.7: Reduction of Figure 2.6 to BDD

.

Figure 2.8: BDDs with Different Orderings for Function f

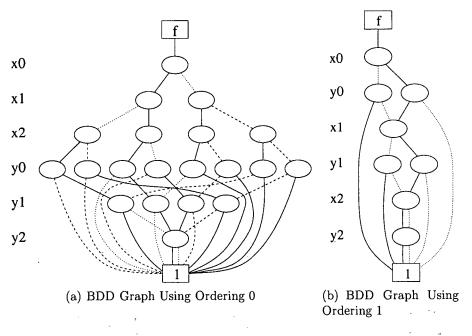

Another limitation of BDD-based approaches is that the size of the BDD depends heavily on the variable ordering. For example, the 3-bit comparator function  $f(x_0, x_1, x_2, y_0, y_1, y_2) = (x_0 \leftrightarrow y_0) \land (x_1 \leftrightarrow y_1) \land (x_2 \leftrightarrow y_2)$  has different BDD graphs given different variable orderings. For example, given a variable ordering  $x_0 < x_1 < x_2 < y_0 < y_1 < y_2$  (Ordering 0), we have a BDD graph Figure 2.8(a); given another variable ordering  $x_0 < y_0 < x_1 < y_2 < y_2$  (Ordering 1), we have a BDD graph Figure 2.8(b). These two BDD graphs were generated using the *CUDD* package [89] and *dot* [41].

Finding the best variable ordering is an NP-complete problem. Moreover, there exist some functions (such as the middle output of a combinational circuit to multiply integers) that can not be represented efficiently regardless of the variable ordering. Several BDD ordering techniques including static and dynamic ones have been proposed to try to solve the BDD blow-up problem, e.g., [69, 79, 80].

#### SAT

For large systems, where BDDs blow up, Boolean satisfiability (SAT) solvers can be an alternative to manipulate Boolean formulas. SAT has received much attention by the scientific community since any NP problem can be translated into an equivalent SAT problem in polynomial time (Cook's theorem [27]). Aside from its important position in complexity theory, SAT techniques are widely used in electronic design automation, especially in the formal verification domain, e.g., such applications include ATPG (Automatic Test Pattern Generation) [20], Symbolic Model Checking [10], Bounded Model Checking [88], etc.

Unlike BDDs, the direct representation of the model as Boolean formulas does not suffer from the space explosion, but it is not canonical and requires additional efforts to check the equivalence of the formulas. SAT is still an active research area and for certain classes of problems, modern state-of-the-art SAT solvers can greatly outperform BDDs.

In the following standard definitions, e.g., [52], I will give the basic concepts of the SAT problem.

**Definition 2.10 (Literal)** A literal is either a variable p or its negation  $\neg p$ . The first case is called a positive literal; the second is called a negative literal.

**Definition 2.11 (Clause)** A clause is a finite disjunction of literals, e.g.,  $l_1 \vee l_2 \vee l_3...$ , where  $l_i$  is a literal.

**Definition 2.12 (Conjunctive Normal Form)** A propositional formula is in Conjunctive Normal Form (CNF) if it is a finite conjunction of clauses, e.g.,  $C_1 \wedge C_2 \wedge C_3...$ , where  $C_i$  is a clause.

**Definition 2.13 (CNF SAT Problem)** Given a propositional formula F in CNF, the SAT problem consists of assigning values to a set of Boolean variables of F, such

that they satisfy F, i.e., a CNF formula is satisfiable if at least one set of assignments to the variables of the formula makes it evaluate to true.

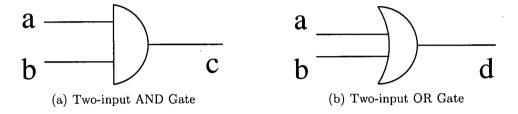

Given the above definitions. I will use simple AND and OR gates to show how to use SAT to represent states and do equivalence checking.

Figure 2.9: Simple Gate Examples for SAT

In Figure 2.9(a), we have a two-input AND gate. A logic formula for this gate is  $(\bar{a} \rightarrow \bar{c}) \wedge (\bar{b} \rightarrow \bar{c}) \wedge (a \wedge b \rightarrow c)$  (If any input is equal to 0, the output is 0. If both inputs are equal to 1, the output is 1). After simplifying this expression, we get a CNF formula:

$$F = (a \lor \overline{c}) \land (b \lor \overline{c}) \land (\overline{a} \lor \overline{b} \lor c).$$

This propositional formula has three variables (a, b, c) and three clauses. Assignments (0,1,0), (1,0,0), (1,1,1), (0,0,0) to the 3-tuple (a, b, c) are satisfying assignments of F. These assignments essentially are the truth table for this AND gate, i.e., the state space of it.

Using the same approach, the logic formula for the two-input OR gate in Figure 2.9(b) is:

$$G = (\bar{a} \lor d) \land (\bar{b} \lor d) \land (a \lor b \lor \bar{d}).$$

Having these two propositional formulas in CNF form for our AND gate and OR gate, we can do equivalence checking of the outputs, i.e., whether c is equivalent to d given the same inputs a and b (a trivial example, but it illustrates the point). What we need to do is to check:

$$AND(a,b) = OR(a,b)$$

$$\iff (c = AND(a,b)) \land (d = OR(a,b)) \land (c = d)$$

$$\iff F \land G \land (d \lor \bar{c}) \land (\bar{d} \lor c)$$

Obviously, we need to check all possible values of a and b, i.e.,

$$\forall a, b; AND(a, b) = OR(a, b).$$

However, SAT solvers usually give a satisfying assignment for a propositional formula in CNF and can not prove the above formula directly. Fortunately, such a universalquantified logic formula is logically equivalent to the negation of an existentialquantified logic formula. So, in practice, we check its equivalent form, i.e.,

$$\forall a, b; AND(a, b) = OR(a, b)$$

$$\iff \neg(\neg(\forall a, b; AND(a, b) = OR(a, b))$$

$$\iff \neg(\exists a, b; AND(a, b) \neq OR(a, b))$$

$$\iff \neg(\exists a, b; (c = AND(a, b)) \land (d = OR(a, b)) \land (c \neq d))$$

$$\iff \neg(\exists a, b; F \land G \land (d \lor c) \land (\bar{d} \lor \bar{c}))$$

Therefore, if we can find a satisfying assignment for

$$F \wedge G \wedge (d \vee c) \wedge (\bar{d} \vee \bar{c}),$$

it will be a counterexample to falsify the property (c = d) that we want to prove. If such an assignment doesn't exist, we prove the equivalence. In our example, assignments (0, 1, 0, 1) and (1, 0, 0, 1) to the 4-tuple (a, b, c, d) are satisfying assignments for the above CNF. They are the counterexamples for the equivalence checking of our AND gate and OR gate.

The above simple example shows the basic approach of formal verification using SAT. It can be easily applied to large circuits. A combinational circuit can be represented by a conjunction of CNF formulas of its gates. A sequential circuit can be unrolled a finite number of times. Then, the resulting combinational circuit is converted to CNF and handed to a SAT decision procedure to find a counterexample whose length is less than the number of unrollings. (Note that this approach is bounded model checking (BMC), described later)

In order to find a satisfying assignment to a CNF formula, SAT procedures need to explore the search tree. In such a search tree, nodes are variables and edges are assignments (either 1 or 0 for each variable). A solution is given by a sequence of nodes and edges (variables and assignments). The search tree can be very large. Numerous techniques have been proposed to prune the search tree. Just as in BDD-based techniques, SAT solvers are also heavily effected by the variable ordering.

There is much research carried out for high-speed SAT solvers (e.g., [71, 66, 99]). This field is active and researchers are continuing to make progress toward their goals.

#### 2.3.2 Example for Symbolic Model Checking

With the help of BDDs or SAT for Boolean formulas, we can proceed to symbolic model checking [68]. Symbolic model checking algorithms operate on sets of states instead of individual states. Therefore, some regularities in the structures of the sets can be exploited. Intuitively, the "complexity" of representing the state space is much less with symbolic representations as opposed to enumerating individual states.

In this section, I will give an example to show how to do symbolic model checking. As mentioned in the previous section, BDDs and SAT are commonly used techniques to handle Boolean formulas. Especially BDDs traditionally have been used as the underlying representation for symbolic model checkers (e.g., SMV [21], VIS [13], Bebop [5], Ever [50], etc.) for their efficiency. In this section, I will focus on BDD-based unbounded symbolic model checking. SAT-based bounded model checking will be introduced in the next section.

ĺ

Figure 2.10: Symbolic Model Checking Example

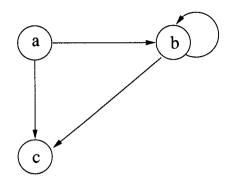

Consider a simple example that illustrates the basic ideas of BDD-based symbolic model checking. In Figure 2.10, instead of enumerating the explicit states a, b, and c, two state variables,  $x_1, x_2$ , are introduced. We encode states as follows:

$$a = \bar{x_1} \bar{x_2}$$

$$b = \bar{x_1} x_2$$

$$c = x_1 x_2$$

Therefore, the state transition relation of this state graph is

$$R = (\bar{x_1}\bar{x_2} \wedge \bar{x_1}'x_2')$$

$$\lor (\bar{x_1}\bar{x_2} \wedge x_1'x_2')$$

$$\lor (\bar{x_1}x_2 \wedge \bar{x_1}'x_2')$$

$$\lor (\bar{x_1}x_2 \wedge x_1'x_2')$$

where  $x_1, x_2$  represent the current states and  $x_1', x_2'$  represent the next states.

Now, we have Boolean encodings for states and the state transition relation which all can be represented as BDDs. Then, we will apply the core operation of symbolic model checking — image computation. Image computation computes the set of states that are reachable in one step from another set of states. The definitions of post-image and pre-image are as follows:

$\textit{post-image}(S) := \{s' \mid \exists s.R(s,s') \land s \in S\}$

$pre\text{-}image(S) := \{s \mid \exists s'. R(s, s') \land s' \in S\}$

where R is the transition relation, s, s' are states.

From the definitions, we can find that *post-image* and *pre-image* computes the successors and predecessors respectively for a set of states. In addition, from the definition of the CTL operator **EX**, we also find that **EX** is the pre-image computation.

I take the post-image computation as an example. In Figure 2.10, if we start from state a (i.e.,  $\bar{x_1}\bar{x_2}$ ), and compute the next states of a by applying the transition relation R. We just compute the conjunction  $(\bar{x_1}\bar{x_2}) \wedge R$  and get  $(\bar{x_1}\bar{x_2} \wedge \bar{x_1}'x_2') \vee (\bar{x_1}\bar{x_2} \wedge x_1'x_2')$ . After that, we need to do *Existential Quantification* on the current variables. The definition of existential quantification is:  $\exists x.f = f_{x \leftarrow 0} \vee f_{x \leftarrow 1}$ . i.e., compute the cases when x is equal to 0 and 1 respectively, then combine the two cases together. In this way, we can remove the variable x. After quantifying out all the current state variables, we get the successors of state a, which satisfy  $\bar{x_1}'x_2' \vee x_1'x_2'$ . (In Figure 2.10, they are states b and c.) If we need to change the next states as our new current states, we also need to swap x and x' and then get  $x_1x_2 \vee \bar{x_1}x_2$ .

The pre-image computation is similar to the post-image computation, except quantification is on the next-state variables. Instead of computing the next states, pre-image computes previous states.

As shown in our example, post-image and pre-image computations can be used for forward reachability analysis and backward reachability analysis respectively. Reachability analysis iteratively performs the above image computations until a fixpoint is reached. In addition to its essential computation in model checking algorithms, pre-image (i.e., **EX**) can also be used in counterexample generation. Once a bad state is forward reached, the formal verification tools can give a sequence of states that leads to this bad state using backward image computation.

Image computation is one of the major bottlenecks in symbolic formal verifi-

cation core. There are many techniques to address it, such as partitioned transition relation [17] and early quantification [48]. Partitioned transition relation is a technique, in which instead of a monolithic transition relation R, some small pieces of relations are given. Image computation uses these pieces to compute images, then conjoins the results. Early quantification means that instead of quantifying variables after conjoining the entire transition relation, we quantify them early when they can be safely quantified.

# 2.4 Industrially Scalable Verification Techniques

Symbolic model checking has been proven to be very successful when applied to hardware system [18, 19, 68]. However, the state explosion of model checking still prevents it scaling to large designs (either out of memory due to BDD blow-up or time out for SAT solvers). In industry, there are some other techniques which are widely used to attack state explosion. In the next section, I will present some of them that are related to my thesis.

#### 2.4.1 Bounded Model Checking

We have known that in symbolic model checking, if the number of state variables is big, the BDDs for the transition relation and for sets of states are likely to be big. Symbolic model checking on such a model may become impossible due to the BDD blow-up. To avoid this problem, we can do bounded model checking instead of full model checking. Bounded Model Checking (BMC) was first proposed by Biere et al. in 1999 [10]. By using SAT procedures, it presents another approach for model checking. The basic idea of BMC is to search for a counterexample in executions whose length is bounded by some integer k. If no bug is found then BMC increases k until either a bug is found, or some pre-specified upper bound (Completeness Threshold) is reached (or in practice, until the tool runs out of time). The BMC problem can be efficiently reduced to a satisfiability problem, and can therefore be solved by SAT methods rather than BDDs.

Copty et al. [28] give a detailed comparison of performing BMC on top of a SAT solver (SIMO), and performing symbolic model checking on top of a BDD package, in an industrial setting. The designs are taken from Intel's *Pentium* 4, with over 1000 model variables. The experiments clearly show that BMC has advantages in both capacity and productivity over BDD-based symbolic model checkers for most cases. The improved productivity comes from the fact that normally BDD-based techniques need more manual guidance in order to optimize their performance. Now, BMC is a complementary technique to symbolic model checking.

However, the bound introduced in BMC also brings drawbacks for this approach. Determining whether a completeness threshold is large enough to find the inconsistencies is a hard problem. If the completeness threshold is not big enough, BMC is incomplete. And from the experiment results, if the bound k is big, BMC cannot outperform BDD-based techniques [28].

#### 2.4.2 Symbolic Simulation

For large circuits where formal verification fails, there is simulation, which is the traditional method for testing and debugging hardware designs. In conventional simulation, one simulation run can only verify one test case. In order to fully verify a design, the simulation tool must exhaustively simulate the entire set of test cases, which is too expensive. In symbolic simulation [15], the set of test values is encoded symbolically to represent any value instead of being a specific element of the set. This allows the simulation tool to compute information on the entire set of values in a single simulation run. Such symbolic simulators can greatly accelerate the simulation.

For example, a 2-input AND gate has two inputs A and B. The output is C. In order to completely simulate the gate, a conventional simulator would try all possible input cases  $\{(A = 0, B = 0), (A = 0, B = 1), (A = 1, B = 0), (A = 1, B =$

1)}. The symbolic simulator, on the other hand, treats the inputs symbolically (A, B) and gives an output  $C = A \wedge B$  by one simulation run.

In order to prove the equivalence of two circuits, decision procedures need to verify the symbolic-simulation outputs, which usually are represented as Boolean expressions. Traditionally, BDDs are the most popular technique for decision procedures due to their canonicity. To avoid BDD blow-up, SAT-based techniques are another candidate for some applications. More general-purpose decision procedures, which handle logics beyond Boolean logic are also available. For example, SVC (Stanford Validity Checker) [7] is an automatic decision procedure for quantifierfree first order formulas with equality, uninterpreted functions, and arrays.

In addition to hardware verification, software verification also can be addressed by symbolic simulation. In my thesis, I need to verify software specifications vs. hardware implementations. It is possible to do symbolic simulation for both the software specifications and hardware implementations. Just as for hardware, symbolic simulation on software could greatly accelerate the simulation.

However, symbolic simulation for software introduces many challenges. The inherent exponential complexity of verification can not be avoided. Such a complexity may appear in the length of output expressions and causes memory blow up; or may appear in decision procedures and causes time out or memory blow up. Furthermore, loop handling may be impossible. If the symbolic simulator cannot determine the termination condition for a loop, it will iterate the loop infinitely which eventually causes memory blow up if there is no other technique to exit the loop.

In spite of the above limitations, symbolic simulation is an efficient approach to do verification for some problems. It is one of the techniques that I rely on for my research.

#### 2.4.3 Combinational Equivalence Checking

Most work in my thesis leverages the success of RTL vs. gate-level equivalence checking of combinational circuits (e.g., [55] is a good survey). In this section, I will introduce some basic background for combinational equivalence checking.

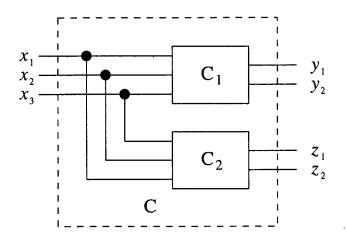

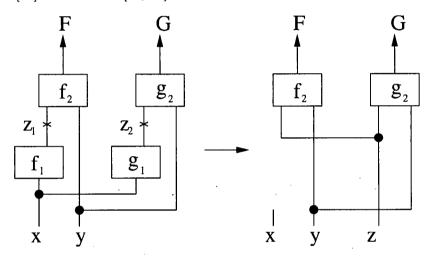

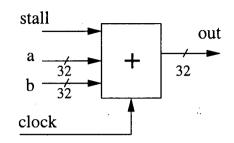

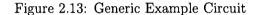

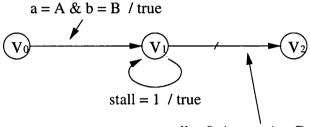

The goal of combinational equivalence checking is to check whether two combinational circuits are functionally equivalent (i.e., for all possible inputs, both combinational circuits have the same outputs). The basic mathematical tool for reasoning about digital circuits is Boolean algebra (using BDD or SAT). Therefore, the equivalence of two circuits corresponds to the problem of determining the equivalence of Boolean formulas.