#### Train Set Bus Controller

by

Nana S. Kender

Diploma de inginer, Universitatea Tehnica Timisoara, Romania, 1994

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Master of Science

in

THE FACULTY OF GRADUATE STUDIES

(Department of Computer Science)

we accept this thesis as conforming to the required standard

#### The University of British Columbia

December 1998

© Nana S. Kender, 1998

In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Department of COMPUTER SCIENCE

The University of British Columbia Vancouver, Canada

Date <u>Nec. 18</u>, 1998

## **Abstract**

This thesis presents the design of a bus interface for a computer controlled train set. This design is useful for experiments in real-time control and embedded systems. The design was based on an experimental methodology based on modeling both hardware and software with programs in a guarded command language. The successful completion of this design provides empirical support for this approach.

## Contents

| A۱              | bstra | nct .                                                  | ii |  |  |

|-----------------|-------|--------------------------------------------------------|----|--|--|

| Contents        |       |                                                        |    |  |  |

| List of Figures |       |                                                        |    |  |  |

| 1               | Int   | roduction                                              | 1  |  |  |

|                 | 1.1   | Train set project                                      | 2  |  |  |

|                 | 1.2   | Summary of thesis contributions                        | 3  |  |  |

| 2               | Co    | -Design                                                | 4  |  |  |

|                 | 2.1   | What Is Co-Design?                                     | 4  |  |  |

|                 | 2.2   | Current Issues in Co-Design                            | 7  |  |  |

|                 | 2.3   | Models and Specification Languages for Co-design       | 8  |  |  |

|                 | 2.4   | System Modeling and Co-simulation                      | 10 |  |  |

|                 | 2.5   | Summary                                                | 10 |  |  |

| 3               | Bu    | s Interface Specification                              | 11 |  |  |

|                 | 3.1   | The train set                                          | 11 |  |  |

|                 |       | 3.1.1 Acknowledgments and brief history of the project | 11 |  |  |

|                 |       | 3.1.2 Description of train set components              | 12 |  |  |

|                 | 3.2   | The existing design                                    | 14 |  |  |

|                 | 3.3   | The proposed design                                    | 14 |  |  |

|                 | 3.4   | The train-bus                                          | 15 |  |  |

|                 |       | 3.4.1 High-level design choices                        | 16 |  |  |

|                 |       | 3.4.2 Logical details                                  | 16 |  |  |

|                 |       | 3.4.3 Electrical details                               | 16 |  |  |

|                 |       | 3.4.4 Comparison with other bus-schemes                | 20 |  |  |

|                 | 3.5   | The ISA to train-bus interface                         | 20 |  |  |

|                 | 3.6   | Summary                                                | 24 |  |  |

| 4                                     | $\mathbf{Sp}$                             | ecification Language                                              | <b>25</b> |  |  |

|---------------------------------------|-------------------------------------------|-------------------------------------------------------------------|-----------|--|--|

|                                       | 4.1                                       | Why ST ?                                                          | 25        |  |  |

|                                       | 4.2                                       | Synchronized Transitions                                          | 26        |  |  |

|                                       |                                           | 4.2.1 Combinators                                                 | 26        |  |  |

|                                       |                                           | 4.2.2 Modular Designs                                             | 27        |  |  |

|                                       |                                           | 4.2.3 ST for Co-design                                            | 28        |  |  |

|                                       | 4.3                                       | Summary                                                           | 37        |  |  |

| 5                                     | $\mathbf{T}\mathbf{h}$                    | e Design                                                          | 38        |  |  |

|                                       | 5.1                                       | ST model design                                                   | 38        |  |  |

|                                       |                                           | 5.1.1 The FIFO Buffers                                            | 38        |  |  |

|                                       |                                           | 5.1.2 The Control Logic                                           | 44        |  |  |

|                                       |                                           | 5.1.3 ST simulations                                              | 51        |  |  |

|                                       | 5.2                                       | Implementation Decisions                                          | 51        |  |  |

|                                       | 5.3                                       | From ST to VHDL                                                   | 52        |  |  |

|                                       |                                           | 5.3.1 Clock signal                                                | 52        |  |  |

|                                       |                                           | 5.3.2 Sensitivity lists                                           | 52        |  |  |

|                                       |                                           | 5.3.3 On mixing ST combinators                                    | 52        |  |  |

|                                       | 5.4                                       | Summary                                                           | 53        |  |  |

| 6                                     | Eva                                       | aluations and future work                                         | 54        |  |  |

|                                       | 6.1                                       | Testing the train controller board                                | 54        |  |  |

|                                       |                                           | 6.1.1 Problems I encountered while going through the whole design |           |  |  |

|                                       |                                           | process                                                           | 58        |  |  |

|                                       | 6.2                                       | ST for co-design                                                  | 58        |  |  |

|                                       | 6.3                                       | Conclusions                                                       | 59        |  |  |

|                                       | 6.4                                       | Future work                                                       | 59        |  |  |

|                                       |                                           | 6.4.1 Completing the train-bus design                             | 59        |  |  |

|                                       |                                           | 6.4.2 Better CAD support for ST based design                      | 60        |  |  |

| Bibliography 61                       |                                           |                                                                   |           |  |  |

| Appendix A ST code for the controller |                                           |                                                                   | 63        |  |  |

| Aı                                    | Appendix B ST cell instantiation diagrams |                                                                   |           |  |  |

| Aj                                    | Appendix C VHDL code                      |                                                                   |           |  |  |

| Appendix D Board Schematics           |                                           | 82                                                                |           |  |  |

## List of Figures

| 3.1  | The track topology                                   |

|------|------------------------------------------------------|

| 3.2  | The old architecture                                 |

| 3.3  | The proposed architecture                            |

| 3.4  | Voltage shifts at imbalanced changes of signal lines |

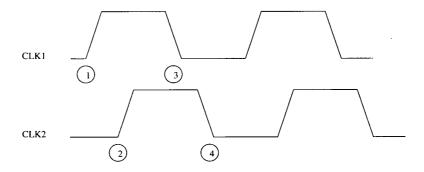

| 3.5  | A 4-phased Train-Bus Protocol                        |

| 3.6  | The train-bus clocks                                 |

| 3.7  | Standard ISA cycle                                   |

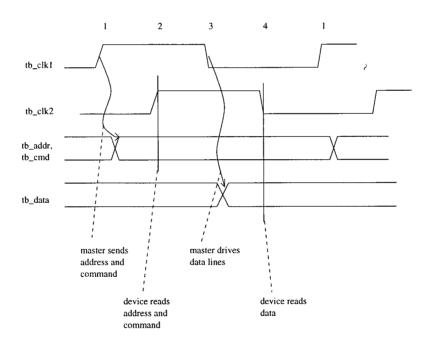

| 3.8  | A write to a device on the train-bus                 |

| 4.1  | A direct mapping of the ST 3-bit counter to hardware |

| 4.2  | The counter modulo-21                                |

| 4.3  | The differential clock generator                     |

| 4.4  | Instantiations of the counter cells                  |

| 4.5  | State Diagram for the Command Dispatcher             |

| 4.6  | ST code for the dispatcher cell                      |

| 4.7  | State Diagram for the Retiring of a Command          |

| 4.8  | ST code for the retire cell                          |

| 5.1  | Bus Controller - Register View                       |

| 5.2  | The need for an additional data-write buffer         |

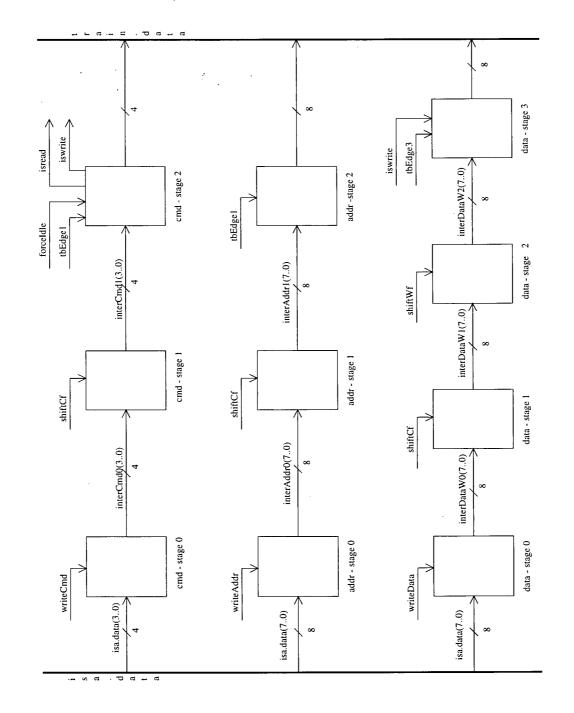

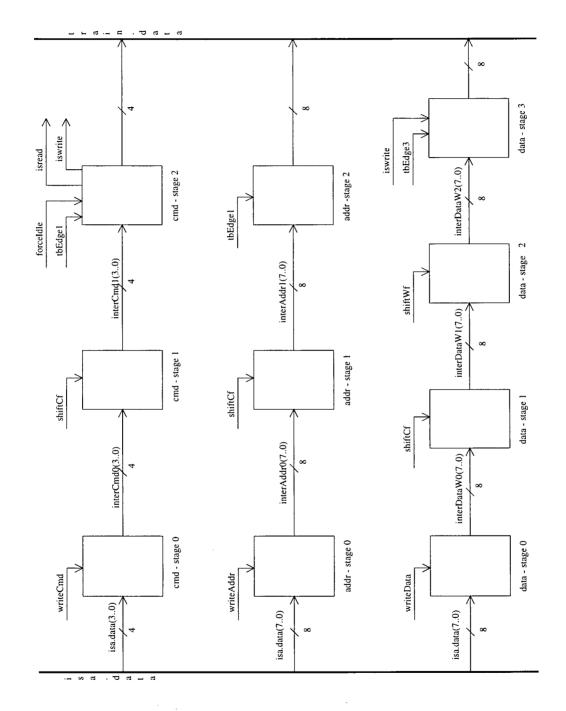

| 5.3  | The "out-FIFOs": Cmd, Addr and Data-Write 42         |

| 5.4  | State Diagram for Module driver.sti                  |

| 5.5  | The state variable declaration                       |

| 5.6  | Function definitions for the quontroller cell 47     |

| 5.7  | Command FIFO control signals                         |

| 5.8  | Data-Write FIFO control signals                      |

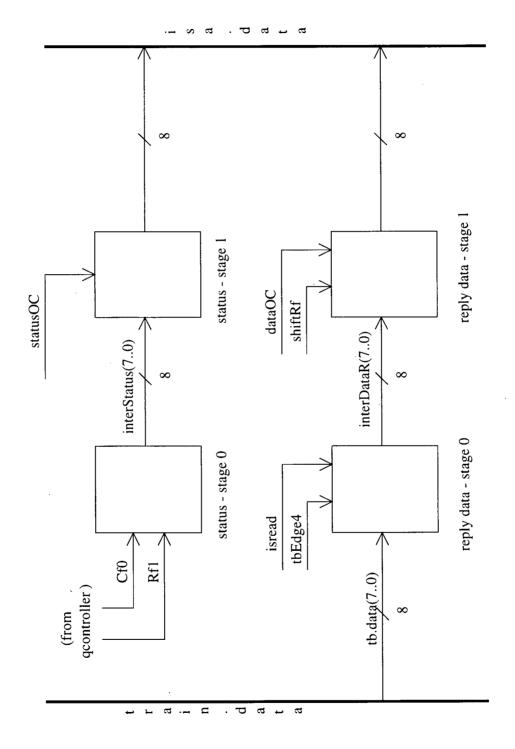

| 5.9  | Result FIFO control signals                          |

| 5.10 | Qcontroller module: forcing an idle train-bus cycle  |

| 5.11 | The special buffer for Command-FIFO stage 2 50       |

| 6.1 | (                                                                   |    |

|-----|---------------------------------------------------------------------|----|

|     | and function definitions                                            | 55 |

| 6.2 | Sample test application (in C++) for the bus controller: main func- |    |

|     | tion body                                                           | 56 |

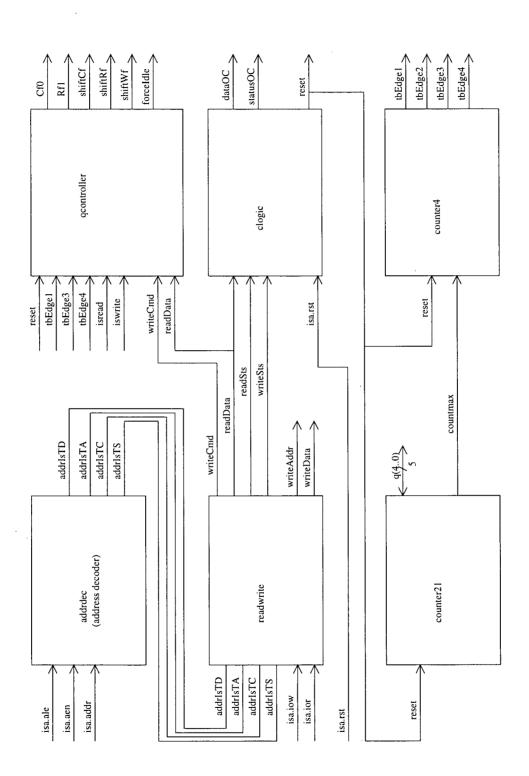

| B.1 | The "out-FIFOs": Cmd, Addr and Data-Write                           | 72 |

| B.2 | The "in-FIFOs": Status and Data-Read                                | 73 |

| B.3 | The Control Logic Cells                                             | 74 |

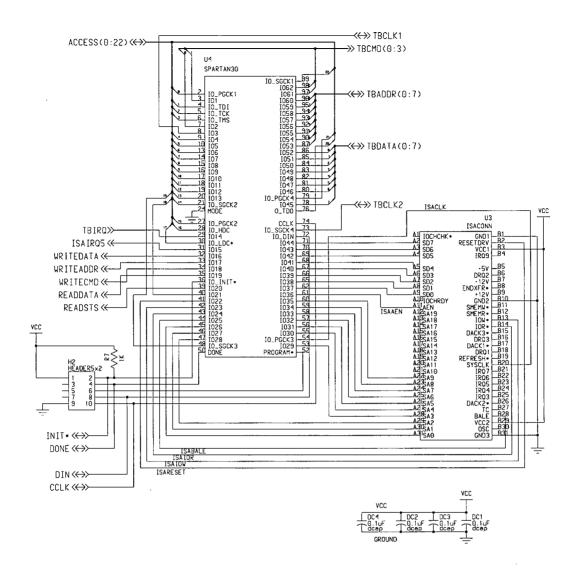

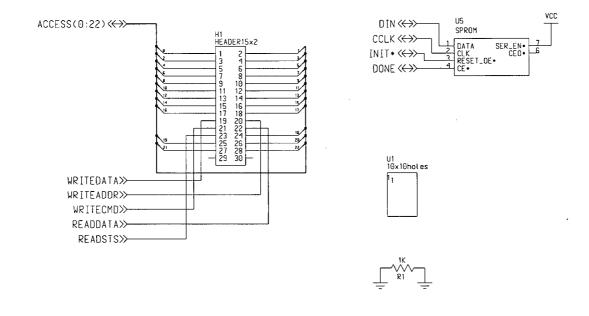

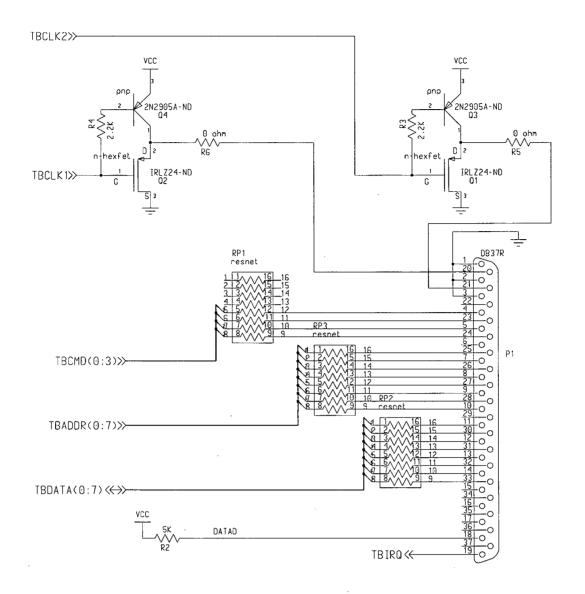

| D.1 | Board schematic sheet 1                                             | 33 |

| D.2 | Board schematic sheet 2                                             | 34 |

| D.3 | Board schematic sheet 3                                             | 35 |

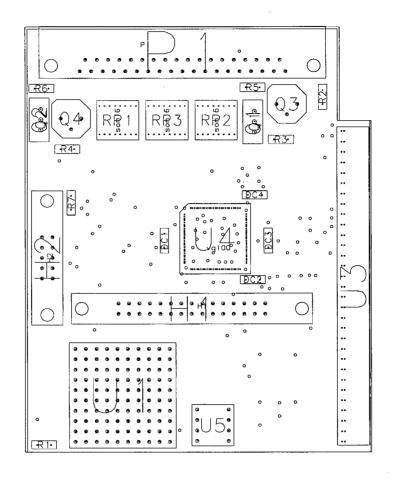

| E.1 | The controller board with components                                | 37 |

|     |                                                                     | २२ |

In memoria tatalui meu. To the memory of my Dad.

## Chapter 1

## Introduction

Embedded systems can be found everywhere from airplanes to doorknobs. As embedded systems have become more widespread and more complicated, interest in systematic approaches to their design has grown as well. An embedded system differs from a general purpose computer by its specialization for a particular group of tasks; often the system has to deal with interfacing and communication between a wide variety of sensors (i.e. input devices) and actuators (i.e. output devices). Design specification plays an important role in the design process.

Embedded systems are inherently concurrent. There are the sensors to be monitored, the actuators for process control, and several software tasks may coordinate all these activities. If we take as an example the automatic control of trains on the same track system, several trains move on the track at the same time; position sensors need to be monitored, each train has its own set of geographic objectives and time schedule. This raises a coordination problem: avoiding collisions and fulfilling the schedule requirements. Our model train set – a research project in the Integrated System Design lab, see section 1.1 – includes several pieces of hardware, each with its own notion of time: the host computer, the ISA bus, the train bus, the switch controllers, the sensor interfaces, the signaling protocol on the track by which commands are sent to the speed controllers in each train. These all operate concurrently.

Concurrency may introduce non-determinism. Most hardware description languages (HDLs) generally have deterministic semantics to appeal to designer intuition and to simplify synthesis. Multiple notions of time, multiple clock-rates, and non-determinism are hard or impossible to represent in such commonly used frameworks. Although many HDLs prevent the designer from expressing non-determinism in their models, this does not ensure that reality will cooperate: events may occur in the implementation in orders that were not considered by the HDL model. Such

incomplete modeling can lead to errors in the final design.

This thesis uses a concurrent programming language, Synchronized Transitions (ST), for design specification. An introductory description of the language is given in chapter 4. It consists of a set of state variables and transitions; transitions can be combined either synchronously or asynchronously. Considering the train set example, we have components that operate synchronously but at different speeds so there may not be a synchronous way to describe their interaction; also the software that controls the whole application can issue commands at its own pace, which should not have to be predictable. Here, the concurrency and non-determinism inherent in the ST language provide a natural way to model the design.

ST was originally proposed by Ravn and Staunstrup [14] and has been used extensively for design and verification of both synchronous and asynchronous circuits. Much of this work has been done by students at the Danish Technical University in Lyngby. The ST compiler used allowed either synchronous or asynchronous descriptions, but not both; mixing the two kinds of operators was not allowed. The ST version used in this thesis removes this limitation.

The mixing of combinators in UBC ST provides a natural way to express concurrency and non-determinism encountered in co-design. The utility of this approach is demonstrated by using it to design a bus interface for a computer controlled train set. A more detailed description of the necessity and usefulness of mixing combinators is given in chapter 4; chapter 5 shows in what way this feature affects the translation from ST to VHDL.

#### 1.1 Train set project

Chapter 3 presents the train set. The train set is a test bed for embedded system design in the Integrated System Design lab in the Computer Science department at the University of British Columbia. It consists of a model train set (with tracks, engines and cars) connected to a computer via a parallel bus. The test bed is used for studying and illustrating safe implementations (e.g. running the trains without accidents) in an integrated software/hardware system.

The project was started in 1992 by two former graduate students, and although it has been operational, several factors have determined the decision for important design changes. These are explained in detail in chapter 3. The main concern are electrical problems (transmission line effects) and design modularity; also the possibility to use the project for design verification studies.

#### 1.2 Summary of thesis contributions

The research undertaken for this thesis included the design, implementation, and test of a useful interface for real-time control and embedded system research. The design is more modular than the previous design and it allows a standard computing platform to be used for the controller. The thesis offers a documented design for future verification projects.

Furthermore, this thesis proposes a methodology for hardware/software codesign. The train bus controller represents a component of interest from a co-design point of view: an interface between two buses with two different clocking methodologies. This design process was an experiment to validate the design methodology. The ST language provided the framework for co-simulation. The ST design model was used – with manual translations – for board layout and component programming. Currently, we do not have automatic synthesis and layout tools based on ST. Instead, the detailed ST description was translated to VHDL. Although this is not an efficient design approach, it allowed a comparison of ST with VHDL.

Chapter 6 gives an evaluation of the chosen methodology and test results. It summarizes the accomplishment of this thesis and suggests further work.

### Chapter 2

## Co-Design

#### 2.1 What Is Co-Design?

Co-design refers to a common framework for designing the hardware and software architectures for an embedded system. "Embedded system" is a definition for a very wide range of digital systems used mostly in dedicated applications, containing analog circuitry and often mechanical parts as well. Co-design has become a strategic technology for systems as simple as household items like thermostats or answering machines, as well as for complicated medical instrumentation, automobile control systems, or "fly by wire" aircrafts.

While the design of general purpose computers aims at a solution which minimizes cost while maximizing speed, storage capacity etc. for a broad range of applications, embedded systems are very application specialized. The application domain also dictates the co-design methodology for a particular embedded system. Apart from cost constraints, these systems also often have power, weight, and physical size limits (Wolf [21]); embedded systems usually have to meet hard real-time deadlines.

For general purpose computers, requirements are relatively well defined: the instruction set determines the correct behaviour of the processor, and performance targets for benchmarks give high-level timing properties. For embedded systems, specifications must describe the interaction of the system with its environment, and producing a correct and complete specification can be much more challenging. For example, consider the design of an ignition and fuel-injection controller for an engine. The designer's intention may be in terms of performance and efficiency of the engine with its controller. Thus, a specification for the controller must include a detailed model of the engine. Such a model may not be available at early stages in the design.

Adding to the difficulty of the co-design problem is also the fact that in embedded systems, as the name says, the computing part is embedded, therefore hard to access for debugging. Traditional break-point debugging is often infeasible for embedded designs. Again, consider the example of the engine controller: the embedded system operates in a real-time environment. The only way to test the controller is when it is connected to an engine. If the software stops at a breakpoint, the engine will stop running.

Given the specification of a system which may include hardware, software, analog and mechanical components, co-design represents the process of going from the specification level to the implementation level. A typical co-design flow is hard to give since co-design tools differ in how they delimit the design steps, but a generic co-design methodology would include some key phases such as (see Gajski et al. [5]):

- Specification: stating system requirements and building a model of the design from these. If we take the engine control example, design specification includes [9]: (a) identifying the tasks of the system in this case providing the correct amount of fuel and firing spark plugs at the right time, (b) identifying the inputs to the controller, such as signals from the crank position sensor or the manifold pressure sensor, (c) usually making abstraction of details, deciding how the system is going to fulfill its tasks. This includes dealing with deadlines, with obstacles to correct functioning such as noise –, with power constraints, safety requirements, etc. In other words, design specification gives a description of the design as the outside world expects it to behave.

- Allocation & Partitioning: In general, a specification should describe what the system is supposed to to, and an implementation describes how it does it. However, most work on specification for co-design has been done by the CAD community with a goal of automatic design synthesis from the specification. To make this goal practical, specifications for co-design tend to include top-level design decisions. For example, a specification may be in terms of a collection of communicating processes [15] or as a "control data flow graph" [11]. Each process can be implemented in either hardware or software, and the specification describes the data and control interactions between these processes.

Allocation is the process of choosing the type and number of components for implementation. partitioning defines the mapping of functions and/or processes from the specification onto the allocated components. Most often allocation and partitioning constitute one step only since if the partitioning is not satisfactory, a different allocation may be tried. Much work has been done towards CAD tools for this step of co-design [7, 12, 11]. There is usually

no single optimal solution to this allocation & partitioning problem; there are trade-offs that need to be balanced. For example, one might want to put all the functions into a general system processor to minimize cost. However, such a processor may not be fast enough to handle everything. For the engine controller, there may be one processor that computes the injector setting and spark timing. A second processor may handle the real-time interface with the engine. A dedicated DSP may process some of the data that is sampled to assess the engine's operation. An ASIC may provide communication between these processors.

• Scheduling: The operation of the embedded system is partitioned to tasks, and tasks have been assigned to various kinds of CPUs, ASICs, etc. The same hardware component may handle several tasks. This is why scheduling is needed. Taking the engine controller example, there are operations that need to be done for every rotation of the crankshaft: actuating fuel injectors and firing spark plugs. These have real-time constraints. There are operations that can be done on a longer time scale, but still must be fast compared to human response time: computing the amount of fuel to be injected, setting the throttle valve in the intake manifold. There are computations that can be done on an even longer time scale: changing mode of operation based on engine temperature, air temperature, oxygen content in exhaust, etc. These processes need to be scheduled so that all deadlines are met.

There are many approaches to solve this NP-hard problem. One that takes into account non-determinism (the impossibility to predict task execution times) is the work of Gerber et al. [6]: an offline component checks if there is a possible scheduling to meet all constraints and then produces a calendar that has lower and upper bound functions for the start times of the tasks rather than absolute numeric conditions. The online component then fills in the numeric values of the parameters inside the functions as they become known (the parameters in the bound functions of one task are start and execution times of other tasks). Other approaches, as reviewed by R.Camposano et al. in [4], are

- ASAP/ALAP (as soon as possible/as late as possible) scheduling;

- List scheduling the difference between the ASAP and ALAP times are computed for all the tasks; this denotes the *mobility* of a task. The task with the least mobility has the highest priority. Other criteria for priority can also be used.

- Force-directed also starts from computing the ASAP/ALAP difference,

then the algorithm builds a model of "operation density" using the prob-

abilities of operations to fall into certain execution steps. From here there may be different variations of summing up these probabilities and deciding on the actual scheduling.

- Path-based each of the possible execution paths is scheduled, then the path schedules are merged to form a single state transition graph.

- heuristic approaches: "percolation" scheduling, and scheduling by simulated annealing or simulated evolution. These are based on an initial (trivial or random) schedule from which better solutions are iteratively generated using heuristics.

- Communication Synthesis: components need to communicate with each other. This communication can be implemented using shared memory, buses, special serial links, etc. In the case of our train set, communication happens through a special network a bus with an established protocol. For the engine controller it is signal lines, that is serial ports, that connect the controller to sensors and actuators.

Analysis and validation is necessary after every step. In our case, the bus controller fits into the context of a bigger co-design research project, the train set described in the next chapter. The enumerated design steps apply mostly only to the train set as a whole. For the controller, the choices for allocation and partitioning were quite straightforward, as described in chapter 5.

#### 2.2 Current Issues in Co-Design

A good reference for the reader regarding current issues in co-design is an IEEE roundtable [16] where seven designers were invited to express their views on the definitions, characteristics and shortcomings of co-design. This roundtable actually shows how vaguely defined the term co-design still is. For instance, Paulin sees co-design as all-hardware, programmable or not, while Harr says designers start from the premise that everything should be done in software and only the necessary hardware should be included.

Nagasamy points out that the "co" in co-design should stand for "concurrent and cooperative design", and that the real challenge lies in designing the software along with the hardware. Agnew embraces this viewpoint too. Having different teams working independently on hardware and on software is not really co-design. Ernst prefers calling it computer-aided co-design because it is the CAD support that unifies hardware and software development, but he further states that no decent tools exist that go all the way down from specification to Register Transfer Level

(RTL) code, which is due the variety of target architectures. Wolf [20] also points out pressing needs for CAD tools in several design phases such as co-simulation, restructuring and partitioning of processes, system- and program-level evaluation.

In Paulin's opinion [16], the main issue in co-design is compilers for the diversity of processor architectures and the real-time constraints typical to embedded systems. But Nagasamy sees a single pressing issue, which is the capture of the design engineer's specification. Paulin and Harr agree this time that the design process in most cases starts from an incomplete specification; such specifications are assumed complete and accurate before design starts, in other words, this high-level description is usually not "debugged". An impressive percentage of the roundtable article is taken by arguments for the need for good specifications. Yasuura comes right out and says academics should focus on a new specification model.

#### 2.3 Models and Specification Languages for Co-design

As Staunstrup states in [19], the aim of high-level design techniques is to reduce design time and effort by moving decisions upwards in the abstraction level of the design models. As designs become larger, the details are too many to be all grasped by one designer. Models are necessary for design overview. As electronic designs become more complex they push the abstraction levels of models upwards, making it common today to describe hardware circuitry in a similar way to the abstraction found in software.

In other words, designing hardware and software is not that much different anymore. The delimitations of hardware and software components within an application become less evident, and the designer needs to be able to model his design in a manner general enough to cover both hardware and software, without any commitment from the start as to what should be implemented in hardware and what in software. But most existing modeling tools and languages today start from either pure hardware description (for example Gupta and DeMicheli's approach [7]), pure software description (for example COSYMA [12]), or mixtures of both but clearly delimited by using a different language for each (like CoWare [15] and Ptolemy [8]).

Vulcan [7] is a hardware-software cosynthesis system which performs automated partitioning on an internal graph representation; initially, the design is specified in HardwareC, a subset of C. Vulcan starts from assuming an all-hardware design and then performs repeated iterations of trying to move parts of the design to software; the criteria are: (a) whether time constraints are still satisfied and (b) minimizing communication overheads. Vulcan can handle parallel processes: hardware and software components may run in parallel [11]. The method targets systems

consisting of ASICs and a CPU to reduce ASIC size.

COSYMA [12] is quite similar to Vulcan, except it starts from an all-software assumption of a design specified in C\*. C\* is a superset of C with added features to allow for timing constraints, task concepts and task communication. COSYMA targets systems consisting of one CPU and one ASIC for processor speed-up. As mentioned, it is a "software-oriented" approach; hardware is added only where necessary because timing constraints are violated by the all-software solution. It is an automated software-oriented partitioning tool with hardware extraction when needed.

LYCOS [11] is another automated partitioning tool. It also starts from translating specifications to an internal graph representation, but it aims at not to limit the designers in using the specification language they prefer; it currently supports C and VHDL but the research group is working towards including other specification languages among the accepted ones – including Synchronized Transitions. The way it works is that based on the internal representation graph, LYCOS generates "Basic Building Blocks" which later can be moved between hardware and software. The partitioning algorithm – PACE – is based on elaborate methods for estimating software execution time, hardware execution time and hardware area size.

CoWare [15] is a hardware-software co-design environment which aims at integrating hardware and software components that were specified, implemented, simulated in different languages and with different tools. A similar approach is found in Ptolemy [8]; partitioning and mapping is done at the very beginning of the design process. CoWare uses notions such as processes, ports, channels, protocols, communication mechanisms – Ptolemy has blocks with portholes – the idea is that after hardware and software components are produced by different tools, they need to be interfaced correctly to result in the final system. These approaches do not solve the problem of the separate design of hardware and software for an embedded system, from the root of the problem, but aim at helping the designer "glue" the components together in a correct and reliable way at the end.

The computational model of a design is a "delicate balance between abstract and concrete" (Staunstrup [19]): if it is too concrete, the designer is constrained by low-level decisions in early phases; if it is too abstract, it may become difficult at later stages to make an efficient realization. However, it should be abstract enough to describe computations in a range of technologies.

#### 2.4 System Modeling and Co-simulation

As mentioned above in section 2.1, the process of going through various levels of abstraction of the design model requires simulation after the model for each level has been established, to make sure the model still respects the initial system requirements. If design is actually co-design of hardware and software, then simulation has to become co-simulation of hardware and software, since we want to simulate the system as a whole and not just isolated components.

From the examples given in the previous section, we can conclude that system-level specifications can be viewed as homogeneous – when a single language is used, like in [7], [12] - or heterogeneous, where different languages are used for hardware parts and software parts ([11], [8], [15]). This thesis uses and emphasizes the benefits for the former, using ST as the single language for modeling the design. A most common example for heterogeneous specifications on the other hand is the mixed C-VHDL model. Heterogeneous specification approaches make co-simulation more complex and difficult since they have to deal with interfacing, translating protocols, etc.

#### 2.5 Summary

Co-design is a relatively new field of computer science, and one in which designer's efforts to cope with the difficulties of the moment have had to be "quick fixes" for the simple reason that industry and market did not have time to wait for "elegant" solutions. Although much work has been done by academia to address the most pressing needs in industry, some issues, as mentioned in section 2.2, are still not at all addressed, or in our opinion not satisfactorily solved. Some of these issues, which the present thesis addresses, are:

- high-level specification with possibilities for automatic verification;

- modeling concurrency and non-determinism inherent to embedded systems;

- providing a single specification language for both hardware and software modeling the design as a whole rather than splitting it into hardware and software from the start.

## Chapter 3

## **Bus Interface Specification**

#### 3.1 The train set

As mentioned in chapter 1, the train set is a model train set built and used in our lab for real-time application experiments.

#### 3.1.1 Acknowledgments and brief history of the project

Since the train bus project was started several years ago and many students (and 2 faculty members) contributed to its design, I will give a brief history of the work:

- 1992: First train-set built. The idea to do a train set was Dr.Carl Seger's based on a similar set-up at the University of Waterloo. The hardware was designed and built by Andy Martin and Eric Borm. Mike Donat and Nancy Day wrote demonstration software (to move trains randomly without collisions).

- 1993: Train-set considered in class project in CpSc 513. A bus-based design was chosen. The existing buses were evaluated and we chose our own design for reasons of scalability and potential for verification (see section 3.4.4). The original train-bus protocol was worked out in a project involving Catherine Leung and Dwight Makaroff.

- 1994: David Weih wrote an ST model for the ISA to train-bus interface.

- 1995: Mohammad Darwish designed hardware for the bus interface based on David's code.

- 1996: Dr.Mark Greenstreet recognized the ground shift problem. His solution to this (see section 3.4.3) involved changing the protocol from two-phase to four-phase; also adding series resistors to drivers for signals other than the

clocks; using complementary signaling for clocks to improve robustness. It appears that complementary signaling is not needed for other signals; doing so would result in an unwieldy number of wires in the bus.

• 1996: I took over the project.

#### 3.1.2 Description of train set components

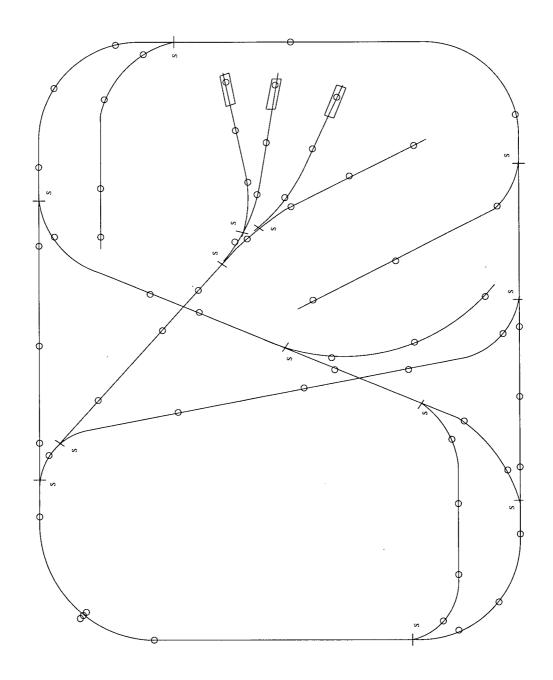

Figure 3.1 is a diagram of the train track system; it shows tracks, switches (marked with an "S") and position sensors (small circles). The train set has been working with three trains in the past; they are shown in the starting position.

There are about 18 meters of track, 13 track switches and 60 position sensors. The sensors are photo-darlington transistors that detect the shadow of a train as it passes over the sensor. The train engines include decoder chips like the ones used in infrared (IR) controllers for TVs, VCRs etc. Commands are sent to the trains by pulsing the power supply that drives the track. Each such command has 9 bits: 5 bits specify a train, and 4 specify the speed. Each train has 8 forward and 8 reverse speeds. There are 32 train addresses, but not enough room on the track for that many trains. Typically, the train set has been operated with three trains.

The figure-8 type of track layout requires a polarity reverser. Trains may start in the same direction and end up facing each other. This means that if initially both had all the right wheels touching the positive rail and all the left wheels touching the negative rail, eventually one of them will have all the right wheels negative; that train went across a polarity reverser. Polarity reversal means there must be electrical breaks in the rails. Furthermore, the engines draw current from all of their wheels, which means that all of the wheels on one side of the engine are connected in parallel. The polarity reverser is a segment of track that is electrically isolated from the segments before and after it. As a train approaches this segment, the segment is connected to the power supply in the same polarity as the segment that the train is currently on. This allows the train to safely cross onto the reverser. When the train is fully on the reverser, the polarity of the reverser is flipped. This allows the train to safely continue on to the next segment. The trains have bridge rectifiers in them so they can accept power of either polarity without changing direction. The direction control is independent of the polarity of the tracks. The power is DC (a reverser would still needed if AC power were used).

The difference between the existing and the proposed train set is in the implementation of the controller. The existing train-set was implemented by two former graduate students in 1992, as described in section 3.2. The necessity for a more modular design which could better serve design and verification experiments

Figure 3.1: The track topology

became evident later. A key piece of the new design is a bus interface, which is the focus of this thesis.

#### 3.2 The existing design

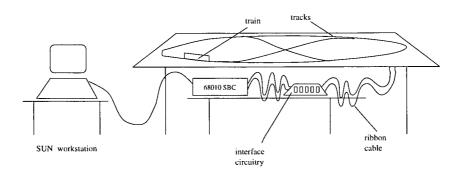

Figure 3.2: The old architecture

Figure 3.2 shows the existing train controller architecture. Programs are written and cross-compiled on the SUN workstation. Executables are then downloaded over a serial link to the single board computer (SBC). A MOTOROLA 68010 based controller was used because UNIX doesn't provide real-time guarantees; the simpler computer can respond to real time events. The 68010 SBC communicates with the interface hardware using its parallel port. This involves using undocumented features of the parallel port to allow data to be read from the port.

The interface hardware consists of 31 TTL chips in addition to some discrete components for the speed controller and to read the photo transistors. There is a rats nest of wires under the track layout table, to connect to the switches and sensors in the track. The design is monolithic and incompletely documented, which makes any hardware modification difficult and unreliable.

#### 3.3 The proposed design

To support more experimentation, we wanted a more modular design. An adequately documented design is also a prerequisite for verification. The key change is to make the control and sensor hardware distributed. This will allow individual pieces to be replaced for design experiments.

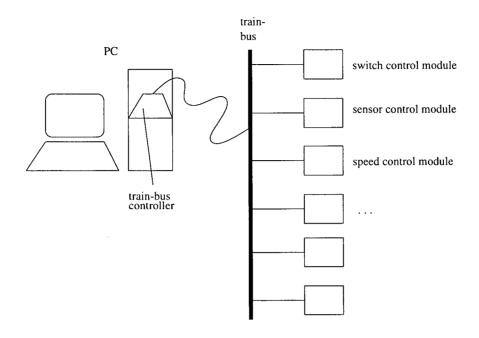

Figure 3.3: The proposed architecture

Figure 3.3 presents the proposed architecture for the train set control. The software will run on a PC as the host computer; the train-bus controller will be a PC-board. We chose a PC-based controller because PCs are readily available, cheap, and provide a popular software development environment. This also means we can further expand the design in the future – we can add other interfaces, such as network cards to communicate with other computers during experiments. The use of DOS makes it possible for an application to override all operating system functionality, thus making real-time applications possible.

The separate modules for each control and sensor function allow the design to be modified one piece at a time; they provide an alternative to the monolithic rats nest of wires of the current design.

#### 3.4 The train-bus

The decentralization of the design requires an organized means of communication between the modules. This is the train-bus, which provides a simple interface to sensor and actuator modules. The simple design should help teaching and verifi-

cation research.

#### 3.4.1 High-level design choices

A parallel bus was chosen for teaching and verification purposes. Also, a protocol for the bus had to be established: it should be synchronous, master-slave. This should make it easier to teach to CS grad students with little hardware experience. Bus operations are simple. There is a clear mapping of wires to functions (unlike a serial bus where the same wire carries several different logical signals at different times). We hope that this will make formal verification easier as well.

From a mechanical point of view, the decision was for ribbon cable. Devices can be connected via crimp connectors. The bus goes under most of the track so that sensor and switch modules can be close to the devices that they sense or control. We expect to use between 5 and 15 meters of ribbon cable. This makes it impractical to ensure tight control of electrical properties.

#### 3.4.2 Logical details

The wires of the train-bus are split into logical groups as follows:

- 8 wires for data

- 8 wires for address

- 4 wires for command

The justification for choosing these numbers is as follows: for address, 4 bits presented a risk for running out of device addresses if the design was successful. 8 bits offer 256 distinct addresses, which seems large enough to be a safe choice (since slave devices may be controllers that can handle several sensors/actuators). For data, an 8 bit bus is small enough to keep the bus from having too many wires and seems adequate for typical control applications. The 4 bits for command offer 16 possible commands, which means again flexibility for future extensions.

#### 3.4.3 Electrical details

This section presents some issues that need to be considered when implementing a long bus with many devices. The devices draw no DC power. The bus operates at a relative low clock frequency, giving the signals time to settle to valid digital values. However the low frequency does not mean we can completely ignore high-frequency effects. Ringing, spurious triggering, etc. are all possibilities because the logic devices can drive their outputs with small rise and fall-times, the ribbon cable

can transmit relatively high-frequency signals, and the logic devices can respond on short time-scales. We have to make sure that this sensitivity to short-time scale behaviour doesn't cause the system to malfunction.

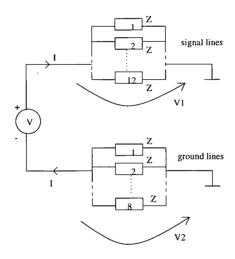

Our concern is about reflections and about power voltage shifts that may occur for imbalanced changes of the signals. According to Kirchhoff's current law, the current through the ground circuit must equal the current through the signal wires. The signal wires each have their own impedance so it will take a certain time for the data/address lines to become low, during which the ground voltage level is shifted upwards. As a worst case example, let's see what happens if 8 address and 4 command wires happen to change in the same direction at the same time (later in this section, figure 3.5 and the related explanation show why we are considering this example). We get the voltage divider effect shown in figure 3.4, where V1/V2 = 2/3 and V1 + V2 = 5, which means that the signal lines will go to 2V (instead of 5V) and the 8 ground lines will go to -3V.

Figure 3.4: Voltage shifts at imbalanced changes of signal lines

The signal lines of the train bus are very long and have to be analyzed as transmission lines. Reflection along the cable lines causes the power lines to bounce back and forth after such shifts, and since ground is the reference voltage, the circuit behaves as if the signal lines would bounce. Even if power shifts would not be a problem, reflection means that every time we have a transitions at the driving end of a line, this voltage change will travel along the cable and get reflected at the other end, which results in ringing on the signal lines.

We apply a strategy to deal with this problem:

- We use series resistors to limit drive current for address, data, and command. The impedance of the ribbon cable was measured (about 70 ohms). Using 680 ohm series resistors gives a total drive impedance of 680/12 = 56 ohms (for the worst case considered, of 12 wires switching simultaneously). Ground impedance is 70/8 = 9 ohms. Thus, we expect a worst-case ground shift of about 1 volt.

- We use differential clocking, so clock signals should have minimal contribution to ground shift. Also, with the 4-phase protocol, address and command lines are changing at different times from data lines (less wires that may change level at the same time). A timing diagram of the new protocol is shown in figure 3.5. The actions corresponding to the 4 marked clock edges are as

Figure 3.5: A 4-phased Train-Bus Protocol

#### follows:

- 1. controller sends address and command;

- 2. device reads address and command;

- 3. controller or device sends data (depending if it was a read or a write);

- 4. data received.

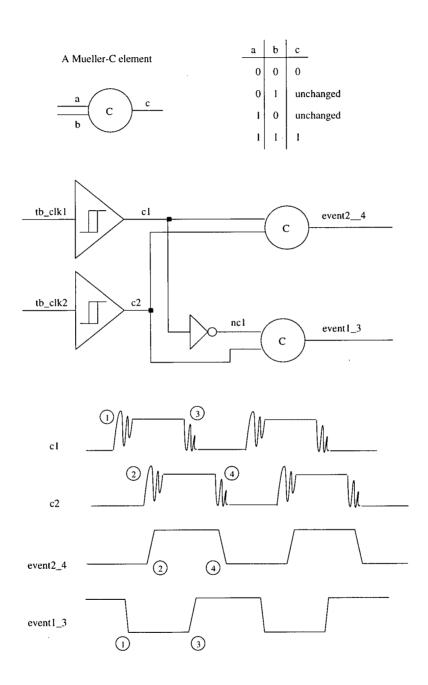

- We use Schmitt-triggers and C-element clock debouncers, as in figure 3.6. The Schmitt triggers annihilate slight variations on the signal lines, while the Mueller-C element eliminates ringing. That is, one signal can oscillate until the other one changes, without causing problems.

As a summary, we make the clock distribution robust and we only look at the address, data, and command signals at times when they are guaranteed to have settled.

Figure 3.6: The train-bus clocks

#### 3.4.4 Comparison with other bus-schemes

- HP-IB: (Hewlett Packard Instrumentation Bus interface, or GP-IB or IEEE 488 standard) This bus standard has similar bandwidth (also 8 bit parallel data). It allows a limited number of devices to connect (15). Devices present a DC load, which limits scalability.

- IIC: This is a serial, twisted pair interface standard for embedded controllers. It would require less wiring and we could use micro-controller chips that have the interface hardware built-in. In that case however, all the design details would be buried in those microcontrollers. We believe that it would be difficult to write a satisfactory formal model for such a controller. This would be a barrier to our verification efforts. Also, hiding all of the hardware would make the design be of less pedagogical value

#### 3.5 The ISA to train-bus interface

As mentioned in section 3.3, the proposed design uses a controller between the host PC and the train bus; the controller is the interface between the ISA-bus and the train-bus.

The design of this interface is the subject of this thesis: the interface is needed before other modules can be built and tested. Also, interfacing between two different bus protocols with two different sets of timing requirements provides an interesting design example.

#### The ISA bus

We used the PC's Industry Standard Architecture (ISA) bus because it's simple and we do not need the higher performance of other PC buses. Following is a very brief description of the ISA-bus, presenting only details relevant for our application. More information can be found in [17].

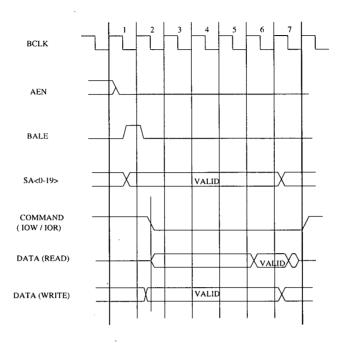

A standard ISA 8-bit I/O cycle is given in figure 3.7.

The meanings of the signal names are:

- BCLK bus clock: the ISA clock;

- AEN address enable. This line is driven by the platform circuitry as an indication to ISA resources not to respond to the address and I/O command lines when the DMA controller is the bus owner.

Figure 3.7: Standard ISA cycle

- BALE bus address latch enable. This signal is driven by the platform CPU

to indicate when the address lines are valid. This signal is used to latch the

address lines.

- SA(0-9) the address lines.

- IOW I/O write: indicates a write cycle to an input/output port;

- IOR I/O read: similar as above;

The cycle starts with a rising edge of BALE. On the falling edge of BALE, the address is guaranteed to be valid (on lines SA0-9). On the rising edge of BCLK<sub>3</sub> we are guaranteed to have the correct value for the command lines. There are two separate lines for read and for write: IOR and IOW, both active low. If neither is driven low, this means the cycle is not an IO-access. If it is an IO-write cycle, the data to be written is already valid at the falling edge of IOW. If it is an IO-read cycle, the data must be valid on the fifth rising edge of BCLK after IOW goes low (BCLK<sub>7</sub> in the figure).

The ISA-bus supports many other operations. For example, there are "early read" and "early write" operations that can be performed if the device asserts the

appropriate signals. Alternatively, the device can signal that it is not ready and the bus stalls until the device indicates that it is ready. We use the default timings for simplicity. There are also 16-bit transfer cycles for both IO and memory operations, but we do not need to use these.

#### Read and write transactions on the train-bus

A timing diagram for the 4-phase clocking was shown in figure 3.5. The train-bus protocol operates on a master-slave basis; the controller is always the master of the train bus, while the devices connected to it are the slaves. Regardless of the direction of the transfer, it is always the master who initiates it. The least significant bit of the command specifies whether it is a command of type write or read, so there are 8 write commands and 8 read commands possible. The signal diagram for a write command on the train-bus is shown in figure 3.8 (a write to a device connected to the train-bus). On the rising edge of  $tbclk_1$  (clock-event #1), the master (the

Figure 3.8: A write to a device on the train-bus

bus controller) sends the address of the device the command is intended for, and the actual command. On the following clock event (#2), the rising edge of  $tbclk_2$ , the devices decode the address and command lines. On the falling edge of  $tbclk_1$  (clock-event #3) the master drives the data lines with the information intended for

the addressed device, and on the falling edge of  $tbclk_2$  (clock-event #4) the device that decoded its own address on event #2 will read the data.

A read is quite similar except the direction of the data transfer is reversed so on clock-event #3 the slave device (instead of the master) is the one who drives the data lines with the requested data, and it is the master who reads the data lines on clock-event #4.

#### The top-level controller design

We can model the design as a Finite State Machine (FSM) for the ISA bus on one end, another FSM for the train-bus at the other end, and FIFOs in-between for communication.

The application running on the PC, i.e., performing write and read transactions on the ISA-bus, will see the controller as a collection of registers. We need one for Data, Address and Command each, and then we also need one for Status because we need to know when the controller is ready to accept a new command; and since the train-bus operates at a much lower frequency than the ISA-bus, this means we must have a way to inform the application when there is requested data available to read. So our Status register has two bits of information, Cf0 (Command FIFO stage 0 is full) and Rf1 (Result FIFO stage 1 is full). The application must also be able to reset the controller; this is done by performing a write to the Status register. Every program running on the host computer for the train-set control will need to start by doing a write to this register. Note that the Status register may be both read and written, as well as the Data register; but the Address and Command registers may only be written.

Before sending a command, the program has to check whether the controller is ready for a new command, so it needs to read the Status register until the Cf0 bit indicates the FIFO has room in its bottom stage for a new command. The controller guarantees that only the application can set this bit, so once it was read as empty, it will stay so until the application issues a new command, that is, performs a write to the Command register. The application may write to the Address and Data registers without changing the status of the controller; only a write to the Command register changes that. A write to the Command register will cause the FIFOs to advance even if there were not new values supplied to the Data and Address registers. This means that if a new write command was issued for instance, the last values written into those registers will be used for the new command.

As mentioned in the section above, the controller does not need to know about the exact command, only about the transfer direction (read/write). A write command does not need to be retired, but a read command does, because when

issuing the command the application only asks for the data, and then it has to wait until the device provides the requested data. To retire a command, the program needs to read the Status register until the Rf1 bit indicates that the result FIFO has new data available; then it may perform a read from the Data register to get the actual data value. As with Cf0, the controller guarantees that once Rf1 became high, it will stay so until the program performs a read from the Data register, which is the only way to reset this bit. The controller also guarantees that the data read is always in the order the read commands were dispatched. Due to the FIFOs, we may have several train-bus transactions outstanding at any time; however, the condition for correct operation of the controller is that operations are completed in the same order that they were issued by the program.

#### 3.6 Summary

We presented the train-set – the history of the project, the description of its components, and the train-bus. For the train-bus we justified the choice for the type of the bus (and the number of wires) as well as for the protocol. We explained the electrical considerations that were the reason for changing the protocol from two-phase to four-phase.

We further justified the choice for a PC-platform for the bus-controller. The circuit is an interface between the ISA bus on the PC and the train-bus on the experimental train set up; we described the protocols used in each of these buses, and the interaction between the two protocols.

### Chapter 4

## Specification Language

#### 4.1 Why ST?

An important issue in co-design is correct design specification capture (Nagasamy, [16]; Wolf, [20]). Because of the complex application nature of embedded systems, a clean and complete specification is both very important and hard to achieve. The penalty of specification errors grows with the time until detection.

Embedded systems can contain hardware, software, analog circuits, and mechanical parts. Interfacing them correctly is as important as it is challenging. The components are working at the same time, often at different rates. This is why writing specifications in sequential programming languages may not be accurate.

Staunstrup [19] makes a strong case for the use of concurrent programming languages in the design of embedded systems: for such systems, the order of external events and computation systems cannot be known in advance or prescribed, so sequential languages are not adequate since the operation sequence is unknown. Concurrent models are more appropriate since they can model non-determinacy, simultaneity, and multiprocessing, which arise in embedded systems.

Synchronized Transitions (ST) [18] is a concurrent programming language that will be described in section 4.2. It is easy to learn and use, yet very powerful for modeling. Its advantages address many of the current co-design problems (some cited above) and bottlenecks.

A major co-design bottleneck is in the design flow from specification to implementation (Nagasamy, [16]). In that respect, ST code is easy to translate to either another programming language like C or a hardware description language like VHDL. Key areas of co-design like partitioning and co-simulation are also helped by using ST. The same notation is used to model both hardware and software. Although we cannot claim we have practical synthesis techniques for going from an

arbitrary ST program to a hardware implementation or to an efficient software implementation, we do have techniques that work if the program is written in a certain style. However, the styles that are suitable for hardware implementation are not the same as the styles that are suitable for software implementation.

We also take a refinement based approach. The design starts with a high-level program that models the key behaviours of the intended system. This program is successively refined, adding more detail at each step, until we get something we can implement. Although there may be little or no distinction between hardware and software at the most abstract level, we tend to head towards hardware-specific or software specific styles for different parts of the program in this refinement process. Thus, partitioning is done by the designer as part of the refinement process.

Co-simulation is done naturally since everything, hardware and software, is modeled in the same ST program.

Last but not least, verification, or rather co-verification, is well supported by ST. It can even be done automatically [10, 13]

#### 4.2 Synchronized Transitions

Synchronized Transitions (ST) is a concurrent programming language. In ST a design is modeled as a set of independent **transitions**. Transitions consist of a **guard** and a **multi-assignment**. For example

$$\ll a \ AND \ b \rightarrow c := d \gg$$

is read "a and b enables c gets d". "a AND b" is the guard of this transition; in other words, the assignment c := d can only be executed if the guard evaluates to true. A transition is said to be **enabled** if the guard is satisfied.

Transitions are executed **atomically**, i.e. the evaluation of the guard and performing the multi-assignment is a single indivisible operation.

#### 4.2.1 Combinators

ST offers three transition combinators,  $\|$ , \* and +. If two or more transitions are combined with the **asynchronous** combinator,  $\|$ , then at each step in program execution, one is selected **non-deterministically** from those that are enabled. For example, if we have

$$\ll \quad a \to c := d \quad \gg$$

$$\parallel \ll \quad b \to e := f \quad \gg$$

then if only one of a or b holds, the corresponding assignment will be executed; however, if both hold, one of the transitions will be chosen, but the choice is not specified by the program. This allows abstract models to describe a wide class of behaviours. It also provides an opportunity for optimization when deriving an implementation. For example, the implementation may choose which transition to execute to maximize performance or minimize the amount of hardware required, or to optimize some trade-offs. The final implementation is often completely deterministic.

The operands of the **product** combinator, \*, are performed as a single, atomic state transition.

$$\ll a \rightarrow c := d \gg$$

$* \ll b \rightarrow e := f \gg$

is equivalent to

$$\ll a \text{ AND } b \rightarrow c, e := d, f \gg$$

in other words the combined transitions are enabled only if both of their guards are enabled.

For transitions combined with the **synchronous** combinator, +, at each step during program execution all enabled transitions are executed as a single atomic operation. For example, if we have:

this means that if only one of a, b is true, then only the corresponding assignment is executed, and if both a and b are true, then the two assignments are executed as an atomic operation.

Any transition or combination of transitions that causes a write conflict is illegal. A write conflict occurs when there is more than one assignment to the same variable in the same atomic operation. A write conflict can occur if transitions are erroneously combined with the + or the \* operator, or even within a single transitions if the same variable is used more than once on the left side of a multiassignment: for example, if two array elements, a(i) and a(j) are on the left side, and i=j holds when the transition is enabled.

#### 4.2.2 Modular Designs

A solution to dealing with increasingly complex designs is making them modular. A modular design can be flat, i.e. all modules communicating on the same level, or hierarchical – a module can contain other modules in its internal structure.

Synchronized Transitions supports modular and hierarchical designs through the use of **cells** - collections of state variables and transitions. In a hardware analogy, cells are like subcircuits. One cell may have several different instantiations just like a circuit may have many instances of the same subcircuit with different external connections. Likewise, a cell may be composed of other cells just as a circuit design may consist of a hierarchy of subcells. An ST program has a **top cell** that is the root of this cell hierarchy.

The interface of a cell to the outside world are its formal parameters. These can be of type *static* or *state*. Formal parameters that have been declared as STATE variables are bound to storage locations (like latches on a chip or memory locations of a process) when the cell is instantiated. Both the cell and its parent can read or write these parameters, which provides a mechanism of communication between cells. The values of STATIC parameters are bound when the cell is instantiated and are typically used to control the size of data structures or control recursive instantiations. The default for formal parameters is STATE.

ST also has arrays, records and functions, which have the usual interpretation. ST programs can be split into modules; each module consists of a definition part (file .std) and an implementation part (file .sti). This eases the writing and maintaining of the program; however, a module can contain descriptions of several cells, so *program* modules do not necessarily have a clear mapping to the *design* modules (the cells); this depends on the programmer's way of organizing his program files.

ST also allows a module to be written with the definition part in ST and the implementation part in C. This is a way to refine an abstract ST description to detailed code.

#### 4.2.3 ST for Co-design

#### Modeling synchronous circuitry with +

Let's take a three-bit synchronous counter. In ST, it would be described as follows:

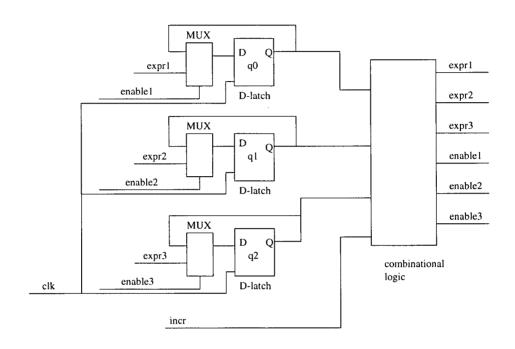

A diagram of the digital circuitry to implement this is shown in figure 4.1. "expr<sub>i</sub>" in this case mean just "NOT  $q_i$ ", but they could be more complicated in other examples (here we could just have taken them from the negated output of the

D-latch, but we wanted to illustrate an approach); "enable<sub>i</sub>" is high if transition i is enabled and low otherwise. For example, if  $enable_1$  is high, on the next clock cycle the q0 latch will load  $expr_1$ , otherwise it will keep its old value.

Figure 4.1: A direct mapping of the ST 3-bit counter to hardware

This hardware can be described in VHDL as follows:

```

end component;

component comb_logic

port( in1, in2, in3, in4: in std_logic;

out1, out2, out3, out4, out5, out6: out std_logic );

end component;

signal expr1, expr2, expr3: std_logic;

signal enable1, enable2, enable3: std_logic;

signal d0, d1, d2: std_logic;

signal q: std_logic_vector(2 downto 0);

begin

m1: mux( q(0), expr1, enable1, d0);

m2: mux( q(1), expr2, enable2, d1);

m3: mux(q(2), expr3, enable3, d2);

q0: d_latch( d0, clk, q(0) );

q1: d_latch( d1, clk, q(1) );

q2: d_latch( d2, clk, q(2) );

c: comb_logic( q(0), q(1), q(2), inc,

expr1, expr2, expr3, enable1, enable2, enable3);

end struct:

```

where the the multiplexer and the D-latch are regular multiplexers and D-latches and the combinational logic performs the logic operations described in the ST code.

### Mixing combinators: non-determinism to model multiple clock domains

As mentioned, the train-bus controller is an interface between two synchronous buses operating at different clock rates. A description of this in ST would look like:

```

(isa1 + isa2 + isa3 + ...)

\parallel isaTOtrainbusFIFO()

\parallel trainbusTOisaFIFO()

\parallel (tb1 + tb2 + tb3 + ...)

```

where isa1, isa2, ... are transitions synchronous to the ISA-bus and tb1, tb2, ... are transitions synchronous to the train-bus. Note that this ST model does not state the relative frequency of the ISA-bus and the train-bus and is robust to changes in the train-bus frequency. In other words, we do not have to worry about frequency details at this high-level description stage.

To refine this model for a particular clock frequency, even a specific clocking protocol, we can write:

```

(isa1 + isa2 + isa3 + ...)

+ isaTOtrainbusFIFO()

+ trainbusTOisaFIFO()

+ trainbusClockGenerator()

+ \ll tbEdge1 \gg *(tb1a + tb1b + tb1c + ...)

+ \ll tbEdge2 \gg *(tb2a + tb2b + tb2c + ...)

+ \ll tbEdge3 \gg *(tb3a + tb3b + tb3c + ...)

+ \ll tbEdge4 \gg *(tb4a + tb4b + tb4c + ...)

```

The asynchronous combinator || has disappeared and the synchronous combinator + is used instead, since we went from a high-level description of components operating at different speeds, to a refined (lower-level) description where we already decided about the clocking methodology.

Note there are transitions without any actions in the example above (e.g.  $\ll tbEdge1 \gg$ ); when combined with the product operator \*, such transitions act as guards for the transitions they are combined with. The execution of this code looks as follows: at every execution step, the following group of transitions will be executed as an atomic operation:

- every enabled transition from the *isa*-group;

- every enabled transition from the trainbusTOisaFIFO-group;

- every enabled transition from the *isaTOtrainbusFIFO*-group;

- the counter model is incremented; the counter divides the ISA-clock signal to generate the clocking required for the train-bus. In our case, this is a 4-phase clocking which means the events of interest are the rising and falling edges of two differential clocks (tbEdge1 to tbEdge4).

- whenever  $tbEdge_i$  is true, every enabled transition from the group  $tb_i$  is executed.

The train-bus clock generator is modeled in a similar fashion. It consists of two cells, a counter modulo 21 and a counter modulo 4 that generates the two delayed clocks phi<sub>1</sub>, phi<sub>2</sub> and the pulses corresponding to the 4 edges (rising and falling for the two clocks).

The "counter21" cell (in figure 4.2) is a value of a CELL type, its value is given by the initializer expression, which is roughly a lambda expression. The type definition for the CELL type defines the types and storage classes of the parameters

Figure 4.2: The counter modulo-21

for the cell. The code is straightforward: it generates a positive pulse for *inc* every 21 execution steps.

The counter4-cell (see figure 4.3) uses the output of the modulo-21 counter to toggle  $phi_1$ ; and  $phi_2$  follows  $phi_1$  by a delay equal to the period of the signal inc. This means that if we use the four events corresponding to the 4 edges of the signals  $phi_1$  and  $phi_2$ , they will be separated by periods equal to the inc period, and if we look at the set of 4 events, they will repeat after a period of 4 \* period(inc).

The two cells are connected in the main cell of the controller hierarchy as shown in figure 4.4. The full code of this cell, with comments, can be found in appendix A; the purpose of the above fragment was just to illustrate that we need 3 of the 4 events to control the operations of some of the FIFO buffers, so we presented these actions in a simplified way.

#### Mixing combinators: non-determinism to model the environment

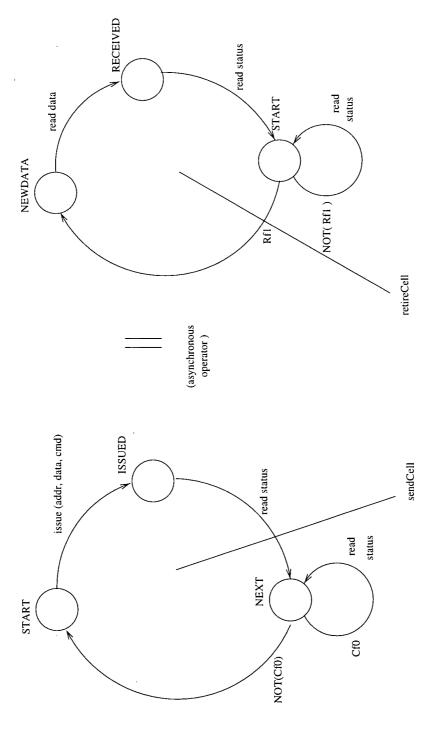

The non-determinism of ST can be used to model the environment for a design. For example, the train-bus controller should work with any legal software running on the PC, and we do not want to limit our model to describing one specific program. The ST model for the ISA interface can perform any sequence of ISA reads and writes that correspond to legal transactions with the bus controller. Figure 4.5 gives a state diagram of a "dispatcher" cell – a cell modeling the legal actions a train-set control software may take to send commands to the train-bus. Note that from state START, several actions may be taken without any condition specified on the arrows

Figure 4.3: The differential clock generator

Figure 4.4: Instantiations of the counter cells

Cf0 = Command FIFO stage 0 is full

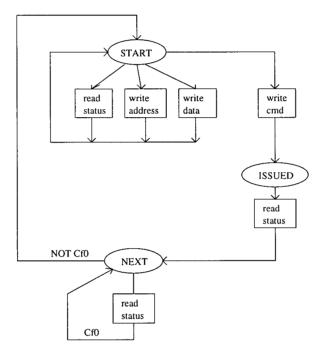

Figure 4.5: State Diagram for the Command Dispatcher

Figure 4.6: ST code for the dispatcher cell

towards these actions; this means that from state START, any of "read status", "write address", and "write data" can be done without advancing to the following state; only writing a command advances the state machine to ISSUED. After we issued a command, we cannot issue the next before we know the controller is ready to accept a new command, which is signaled by the Cf0 status bit being false. Cf0 is an acronym for "Command FIFO, stage 0"; Cf0 being true indicates that the stage that accepts a new command is full. So the state machine stays in the intermediary state "NEXT" until the status bit Cf0 indicates a new command can be dispatched, and the state machine moves back to START. Also note that since we have a choice of actions in the START state, it means the order of sending the data and address components is not specified; what's more, we can dispatch a new command without providing new data and/or address values; in that case, the last written data and address values will be the ones sent onto the train-bus.

The ST code for such a cell is presented in figure 4.6. The non-determinism of the choice between the actions that can be taken from the START state is modeled by using the asynchronous combinator ||.

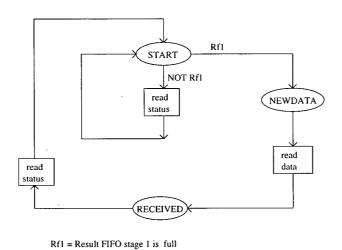

We also need a model of a cell that can retire data requested by a previous read command. The state diagram for such a "retire" cell is given in figure 4.7. It is similar to the one for the dispatcher, but simpler because there is not a choice of actions that can be done from a certain state. A new response can only be read if another status bit, Rf1 (which stands for "response FIFO 1 full), is true. The corresponding code is in figure 4.8.

The application program will look like:

Figure 4.7: State Diagram for the Retiring of a Command

```

<< state = START >> * (

<< NOT Rf1 >> * ReadStatus()

+ << Rf1 >> * << state := NEWDATA >>

)

+ << state = NEWDATA -> state := RECEIVED >> * ReadData()

+ << state = RECEIVED -> state := START >> * ReadStatus()

```

Figure 4.8: ST code for the retire cell

dispatchCell()

|| retireCell()

This allows the client to perform split-transaction operations – i.e., the client may dispatch a new command while one or more previous commands are still outstanding; the client is guaranteed to have the commands retired in the order they were dispatched.

### 4.3 Summary

After reviewing some of the problems that the co-design community is faced with, we are proposing the use of Synchronized Transitions as a specification language for co-design. The language has been extensively used for hardware design by other research groups, and the book published about ST [18] mentions the possibility of using it for co-design. We enumerate the features of ST that make it suitable for embedded system design, and give examples of the use of ST's synchronous and asynchronous combinators. The use of both combinators in the same design model has not been applied in previous research with ST. We explain the advantages of removing this limitation (i.e., not being able to mix the two types of combinators) by giving examples of how we apply this new method to our train-bus controller design.

## Chapter 5

# The Design

The bus controller is an interface between two buses running at different speeds and having different clocking methodologies and protocols. It consists essentially of buffers and logic to control the buffering so that the two protocols are respected.

### 5.1 ST model design

#### 5.1.1 The FIFO Buffers

#### Sending commands to the train-bus

As described in chapters 3 and 4, the train-bus can be logically split into train-data, train-address and train-command. Sending a command means sending the three components; data and address are optional and the order of sending them does not matter (as shown in figure 4.5). Because the two buses run at different speeds – the ISA bus goes 84 times faster than the train bus – FIFOs are used to temporarily store the information until it can be sent out to the trainbus. A new command can only be sent if the FIFO is not full. The commands that are implemented so far are of type read, write and idle.

#### A register view of the bus controller

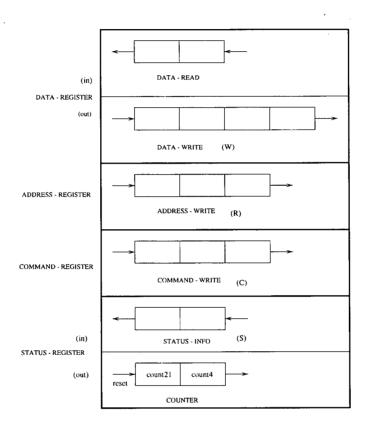

The PC sees the bus controller as a collection of registers it can write to/read from. The four registers are *Data*, *Address*, *Command* and *Status*, and their addresses are (in hexadecimal) 0x300, 0x304, 0x308, 0x30C.

A register view of the bus controller is given in figure 5.1. The number of stages for each FIFO is shown there as well: 3 for Address and Command, 4 for Data-Write, 2 for Data-Read and Status-Read. A write to the Status register

causes a reset of the whole controller; the picture shows the two stages of the counter generating the clocks (see section 4.2.3, figures 4.2 and 4.3), which have all outputs set to "0" on reset. The data-write FIFO has an additional stage compared to the address and command ones, because of the four-phase clock - this FIFO is being read at a different clock edge.

Figure 5.1: Bus Controller - Register View

The top stages of the Address (A) and Command (C) FIFOs are being read at tbEdge1, while the top stage of the Data-Write (W) FIFO is being read at tbEdge3. The A and C FIFOs advance when the shiftCf (shift Command FIFO) signal is high, and that signal goes high whenever the last C-FIFO stage is empty. But that stage could be empty when the last W stage is not. On the other hand, new commands may be sent by the application to the controller if the C-FIFO is not full. That means we could send a new data component to the W-FIFO when the W-FIFO is still full, if it doesn't advance on the same signal. This is why an additional W stage was added, to buffer the delay from tbEdge1 to tbEdge3. In