# Methodology to Forecast a BTI-Induced Accelerated Aging Test Result

by

Parvez Anwar Chanawala

B.Tech., Indian Institute of Technology Delhi, 2018

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

The Faculty of Graduate and Postdoctoral Studies

(Electrical and Computer Engineering)

#### THE UNIVERSITY OF BRITISH COLUMBIA

(Vancouver)

June 2022

© Parvez Anwar Chanawala 2022

The following individuals certify that they have read, and recommend to the Faculty of Graduate and Postdoctoral Studies for acceptance, the thesis entitled:

Methodology to Forecast a BTI-Induced Accelerated Aging Test Result

submitted by Parvez Chanawala in partial fulfillment of the requirements for

the degree of Master of Applied Science

in Electrical and Computer Engineering

#### **Examining Committee:**

André Ivanov, Electrical and Computer Engineering, UBC Supervisor

Prashant Nair, Electrical and Computer Engineering, UBC Supervisory Committee Member

Steve Wilton, Electrical and Computer Engineering, UBC

Additional Examiner

### Abstract

Integrated circuits are stressed at temperature and voltage levels beyond their nominal ratings for long durations (~100s of hrs) during their development stage to study their reliability under nominal conditions. This is crucial to understand their operating lifetimes (typically in years) in their actual fields of use. The conventional HTOL test (an industry-standard reliability test to determine the intrinsic failure rate of ICs) is remarkably short as compared to the ICs' operating lifetime but still requires 1,000 hrs of elapsed test time. Future ICs' development may involve less time for such reliability tests due to the recent concerns being highlighted by most semiconductor manufacturers on reducing a product's time to market. To partially answer such concerns, I am introducing a methodology that models the results of such reliability tests.

To verify the feasibility of this method, several reliability experiments were conducted on Zynq-7000 FPGAs. To successfully perform those experiments, a reliability test platform was developed that can sustainably execute a high-temperature test for 1,000 hrs and requires minimum human intervention during the experiment. This platform is built on a commercial PYNQ-Z1 board that embeds the Zynq-7000 FPGA chip. To quantify the impact of thermal stress, several copies of a ring-oscillator-based test structure were implemented on the chip. Their free-running frequency was considered as a reference parameter to measure degradation.

I leverage an existing transistor-level aging model to develop a circuit-level aging model that can mathematically describe a circuit parameter's degradation as a function of time. This circuit-level aging model is then fitted onto the degradation data collected for a relatively shorter time frame to compute its parametric constants. Finally, with the known parametric constants, the model is used to determine how it fits the actual degradation data of the entire experiment.

An analysis reveals that the first  $\sim 400$  hrs of degradation data has suf-

ficient information to forecast within a 3% accuracy margin the degree of degradation accomplished until the end of a 1,000-hour-long experiment. Subsequently, the analysis is applied to other test durations to study the effectiveness of this approach to other industry-standard reliability tests which are shorter than HTOL.

### Lay Summary

To predict the reliability of a semiconductor device, it must pass through several industry-standard reliability tests where each test lasts for hundreds of hours. One such reliability test is HTOL (High-Temperature Operating Life) which is the longest, wherein the devices are stressed for 1,000 hrs at 125 °C to accelerate their aging process. This helps to determine the device's failure rate in its stipulated lifetime. However, due to such a long duration, the HTOL test at times negatively impacts a product's time to market. This can be prevented by predicting the test results in a significantly shorter time frame. This defined the primary goal of this research where an attempt is made to forecast the result of an accelerated aging test with a unique systematic approach. The feasibility of that approach was verified on Xilinx 28nm FPGAs by conducting several reliability experiments across temperatures for different test durations.

### Preface

This thesis is the result of work carried out by myself, under the supervision of Dr. André Ivanov and the mentorship of Dr. S. A. Sheikholeslam.

Chapter 2 is based on the works primarily conducted by my research colleague, who at the time was a postdoctoral fellow, Dr. S. A. Sheikholeslam. I was responsible for testing and verifying the *Self-heating Module*, *Ring Oscillator (RO) Module*, and *TestChip Driver (TestChip.py)* of the TYNQ platform. I was the lead researcher for the experiments located in Chapters 4 and 5 where I was responsible for all significant areas of concept formation, data collection and analysis, and the manuscript composition.

A portion of Chapters 4 and 5 have been accepted for publication. P. Chanawala, I. Hill, S. A. Sheikholeslam, and A. Ivanov, "Prediction of thermally accelerated aging process at 28nm," in 2022 IEEE European Test Symposium (ETS), in press. I conducted all the experiments, data collection and analysis and composed most of the manuscript. Dr. S. A. Sheikholeslam developed the test platform to conduct the experiments, contributed to data analysis and manuscript edits. I. Hill contributed to data analysis and manuscript edits. Dr. A. Ivanov was the supervisory author on this project, providing guidance and feedback and contributing to manuscript edits.

Another portion of Chapters 4 and 5 is used to prepare a draft. P. Chanawala, I. Hill, S. A. Sheikholeslam, and A. Ivanov, "Forecasting Reliability Test Result from Partial Data for BTI-Induced Aging,". I conducted all the experiments, data collection and analysis and composed most of the draft. Dr. S. A. Sheikholeslam developed the test platform to conduct the experiments, contributed to data analysis and draft edits. I. Hill contributed to data analysis and draft edits. Dr. A. Ivanov was the supervisory author on this project, providing guidance and feedback and contributing to draft edits.

# Table of Contents

| A            | bstra       | $\operatorname{ict}$ ii                      |

|--------------|-------------|----------------------------------------------|

| La           | y Su        | ımmary iv                                    |

| Pı           | refac       | e                                            |

| Ta           | able        | of Contents vi                               |

| Li           | ${f st}$ of | Tables ix                                    |

| Li           | ${f st}$ of | Figures                                      |

| $\mathbf{A}$ | ckno        | wledgements xiii                             |

| D            | edica       | ation xiv                                    |

| 1            | Intr        | roduction and Motivation                     |

|              | 1.1         | Reliability of Semiconductor Devices         |

|              | 1.2         | Research Focus                               |

|              | 1.3         | Reliability Physics of Semiconductor Devices |

|              | 1.4         | Aim of the reliability experiments           |

|              | 1.5         | Overview of the thesis structure             |

|              |             | 1.5.1 Part I                                 |

|              |             | 1.5.2 Part II                                |

| 2            | Rel         | iability Test Platform                       |

|              | 2.1         | FPGA 7                                       |

|              | 2.2         | TYNQ 8                                       |

|              |             | 2.2.1 TYNQ: Hardware                         |

|              |             | 2.2.2 TYNQ: Software                         |

|              | 2.3         | Conclusion                                   |

| 3 | Rel | iability Experiment Structure                                |  |  |  |  |  |

|---|-----|--------------------------------------------------------------|--|--|--|--|--|

|   | 3.1 | Necessity for Structuring the Reliability Experiments 16     |  |  |  |  |  |

|   | 3.2 |                                                              |  |  |  |  |  |

|   |     | 3.2.1 Power Supply with Battery Back-up [HW] 17              |  |  |  |  |  |

|   |     | 3.2.2 Self-heating Module [HW]                               |  |  |  |  |  |

|   |     | 3.2.3 Circuit Under Test (CUT or BTI Sensor) Module [HW]     |  |  |  |  |  |

|   |     | 3.2.4 Python-Based Script experiment_flow.py [SW] 21         |  |  |  |  |  |

|   | 3.3 | Structure of the Experimental Setup                          |  |  |  |  |  |

|   | 3.4 | Flow of the Reliability Experiments                          |  |  |  |  |  |

|   | 3.5 | Conclusion                                                   |  |  |  |  |  |

| 4 | The | ermal Stress Experiments                                     |  |  |  |  |  |

| • | 4.1 | Aim                                                          |  |  |  |  |  |

|   | 4.2 | General Test Setup                                           |  |  |  |  |  |

|   | 4.3 | Experiments                                                  |  |  |  |  |  |

|   | 4.5 | 4.3.1 135 °C and 125 °C Thermal Stress Experiments 33        |  |  |  |  |  |

|   |     | 4.3.2 110 °C Thermal Stress Experiment                       |  |  |  |  |  |

|   |     |                                                              |  |  |  |  |  |

|   |     | 1                                                            |  |  |  |  |  |

|   | 4.4 | 4.3.4 145 °C Thermal Stress Experiment                       |  |  |  |  |  |

|   | 4.4 | Conclusion                                                   |  |  |  |  |  |

| 5 | Res | sults Analyses                                               |  |  |  |  |  |

|   | 5.1 | Introduction                                                 |  |  |  |  |  |

|   |     | 5.1.1 CUT Frequency Degradation Model 40                     |  |  |  |  |  |

|   | 5.2 | Analysis I                                                   |  |  |  |  |  |

|   |     | 5.2.1 125 °C and 135 °C Thermal Stress Experiments 41        |  |  |  |  |  |

|   |     | 5.2.2 Curve Fitting Algorithms                               |  |  |  |  |  |

|   |     | 5.2.3 Discrepancy Between the Predicted and Actual Curve 45  |  |  |  |  |  |

|   |     | 5.2.4 110 °C, 33 °C and 145 °C Thermal Stress Experiments 47 |  |  |  |  |  |

|   |     | 5.2.5 Degradation Data Sampling Rate 49                      |  |  |  |  |  |

|   | 5.3 | Analysis II: Prediction Data Size vs Test Duration 51        |  |  |  |  |  |

|   | 5.4 | Conclusion                                                   |  |  |  |  |  |

| 6 | Cor | nclusion and Future Work                                     |  |  |  |  |  |

| - | 6.1 | Answer to the Main Research Question                         |  |  |  |  |  |

|   | 6.2 | Summary of the Research Work                                 |  |  |  |  |  |

|   | 0.4 | 6.2.1 TYNQ Performance                                       |  |  |  |  |  |

|   |     | 6.2.2 Experimental Result Adaptability                       |  |  |  |  |  |

|   | 6.3 | Recommendations for Future Work                              |  |  |  |  |  |

|   | 0.0 |                                                              |  |  |  |  |  |

| Bi           | bliography                           | 59 |

|--------------|--------------------------------------|----|

| Ap           | opendices                            |    |

| $\mathbf{A}$ | 6-input Look-up Table with 1 Output  | 63 |

| В            | 6-input Look-up Table with 2 Outputs | 64 |

| $\mathbf{C}$ | Frequency Counter                    | 65 |

| D            | TYNQ TestChip Driver                 | 67 |

| $\mathbf{E}$ | CUT's MUX stage                      | 68 |

| $\mathbf{F}$ | Temperature Regulation               | 69 |

| $\mathbf{G}$ | Read CUT Frequency                   | 70 |

| Н            | Data Capture and Storage             | 71 |

| Ι            | Dispatch Email                       | 73 |

| J            | Frequency vs. Temperature Phase      | 75 |

| K            | Stress and Measurement Phase         | 76 |

| ${f L}$      | Clock Divider                        | 77 |

# List of Tables

| 1.1 | Reliability Requirements for Different Semiconductor Markets                                                                                                                 | 1  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | The Duration of the Thermal Stress Experiments Frequency degradation of 20 ${\bf CUTs}$ of ${\bf RO2\_3}$ batch at 135 $^o{\bf C}$                                           |    |

| 5.2 | An Illustration of the Error Calculation Between Two Curves Thermal Stress Experiments' Prediction Summary $Prediction\ Data\ Size\ Required\ for\ \leq 5\%\ Discrepancy\ .$ | 49 |

| 6.1 | Possible Future Research Avenues                                                                                                                                             | 58 |

# List of Figures

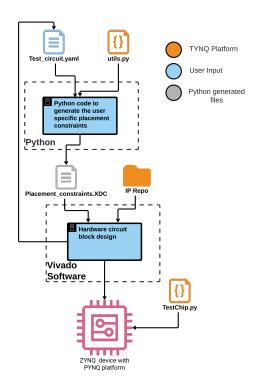

| 2.1 | [1] A structural illustration of the TYNQ platform. TYNQ                 |    |

|-----|--------------------------------------------------------------------------|----|

|     | consists of a set of IPs stored in the <i>IP Repo</i> , a Python utility |    |

|     | module utils.py to generate user-specific placement constraint           |    |

|     | files for IPs, and a driver module TestChip.py was used to               |    |

|     | enable user interaction with the IP circuits                             | 8  |

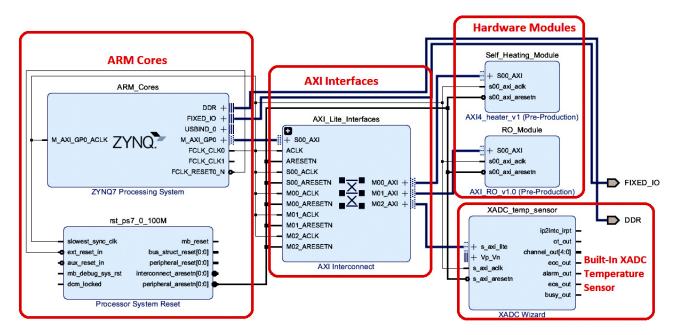

| 2.2 | Vivado Block Design window: The connection of the IP blocks              |    |

|     | (Hardware Modules) with the Zynq-7000 SoC processing                     |    |

|     | system (ARM Cores) via the AXI-Lite Interface (AXI In-                   |    |

|     | terfaces)                                                                | 9  |

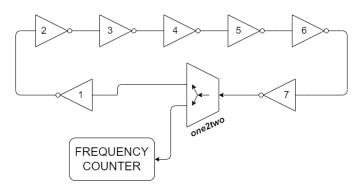

| 2.3 | [1] TYNQ's RO Architecture                                               | 10 |

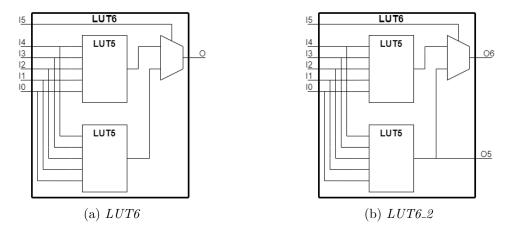

| 2.4 | [2] 6-Input Look-up Tables on Zynq-7000 SoC FPGAs with                   |    |

|     | varied numbers of outputs                                                | 10 |

| 2.5 | The Vivado IP Customization window: A RO Module cus-                     |    |

|     | tomization of its number of stages (Num Stages) and the total            |    |

|     | number of ROs (Num Oscillators)                                          | 11 |

| 2.6 | [1] A Self-heating Module circuit diagram displaying six SHE             |    |

|     | blocks with their respective control signals received from the           |    |

|     | AXI Slave Interface. Each SHE block consists of numerous                 |    |

|     | SHEs                                                                     | 12 |

| 2.7 | The Vivado IP Customization window: A Self-heating Mod-                  |    |

|     | <b>ule</b> customization of the total number of blocks (Num Blocks)      |    |

|     | and number of heating elements per block (Block Size)                    | 13 |

| 3.1 | Circuit Under Test (CUT) Architecture                                    | 19 |

| 3.2 | The implementation of the <b>CUT</b> stages on a CLB. The BLUE           | 10 |

| 0.2 | blocks are the inverter stages. The YELLOW block is the                  |    |

|     | MUX stage. The GREEN connections are the routing nets.                   |    |

|     | The PINK net connects the MUX stage to the Frequency                     |    |

|     | Counter                                                                  | 20 |

|     |                                                                          |    |

| 3.3          | Graph illustrating the measured temperature profile from the results obtained during our experiments that used the fix_temperature function to regulate die temperatures to the desired temperature.                                                                                                                                                             | ature                           |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|              | ature level. During these experiments, the temperature level                                                                                                                                                                                                                                                                                                     | 22                              |

| 0.4          | was found to be within $\pm 1^{\circ}$ C of the desired level                                                                                                                                                                                                                                                                                                    | 22                              |

| $3.4 \\ 3.5$ | Complete Structure of the Experimental Setup                                                                                                                                                                                                                                                                                                                     | <ul><li>24</li><li>25</li></ul> |

| 4.1          | An image showcasing our experiment setup in the laboratory. The PYNQ-Z1 board was placed within a glass container filled with fibreglass (yellow). CyberPower 1500VA is the UPS providing power-backup and surge protection. Prior to the launch of an experiment, some fibreglass was placed on the board, along with the container's lid (shown in red color). | 29                              |

| 4.2          | The Vivado IP Customization window: <b>CUT Module</b> customization of its number of stages (Num Stages) and the total                                                                                                                                                                                                                                           | 29                              |

|              | number of CUTs (Num Oscillators)                                                                                                                                                                                                                                                                                                                                 | 30                              |

| 4.3          | The Vivado Block Design of the system implemented on the                                                                                                                                                                                                                                                                                                         |                                 |

|              | Zynq XC7Z020-1CLG400C. A highlighted instantiation of six                                                                                                                                                                                                                                                                                                        |                                 |

|              | CUT Modules, the Self-heating Module (HEATER EL-                                                                                                                                                                                                                                                                                                                 |                                 |

|              | EMENTS) and the Temperature Sensor (XADC)                                                                                                                                                                                                                                                                                                                        | 31                              |

| 4.4          | The Zynq XC7Z020-1CLG400C layout. A highlighted placement of the 120 CUTs, the heater elements and the XADC                                                                                                                                                                                                                                                      |                                 |

|              | (Temperature Sensor)                                                                                                                                                                                                                                                                                                                                             | 32                              |

| 4.5          | The Zynq XC7Z020-1CLG400C layout. A zoomed image of the 120 CUTs placement, showcasing the uniform distribu-                                                                                                                                                                                                                                                     |                                 |

|              | tion of 20 CUTs of each of the six batches                                                                                                                                                                                                                                                                                                                       | 32                              |

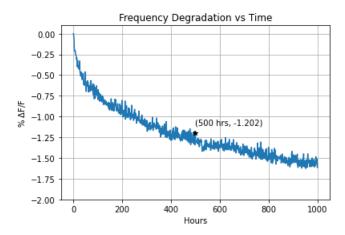

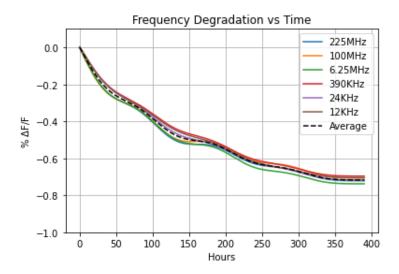

| 4.6          | Frequency degradation of "RO2_3" (390KHz) batch at 135 °C.                                                                                                                                                                                                                                                                                                       | 34                              |

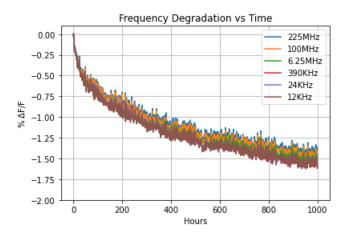

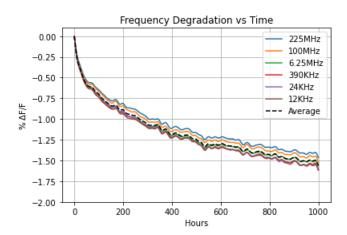

| 4.7          | Frequency degradation of the six batches at 135 °C (unfiltered).                                                                                                                                                                                                                                                                                                 | 35                              |

| 4.8          | Frequency degradation of the six batches at 135 °C                                                                                                                                                                                                                                                                                                               | 35                              |

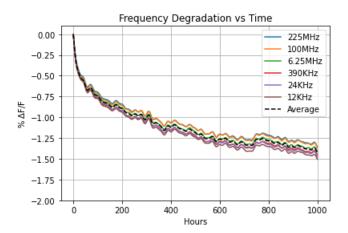

| 4.9          | Frequency degradation of the six batches at 125 °C                                                                                                                                                                                                                                                                                                               | 36                              |

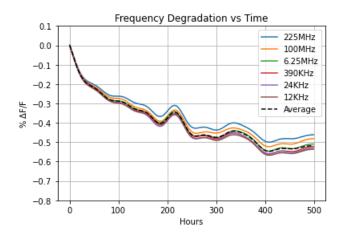

| 4.10         | Frequency degradation of the six batches at 110 °C                                                                                                                                                                                                                                                                                                               | 37                              |

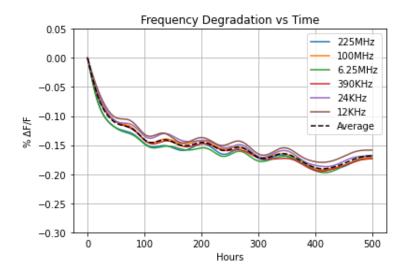

| 4.11         | Frequency degradation of the six batches at 33 °C                                                                                                                                                                                                                                                                                                                | 38                              |

| 4.12         | Frequency degradation of the six batches at 145 °C                                                                                                                                                                                                                                                                                                               | 39                              |

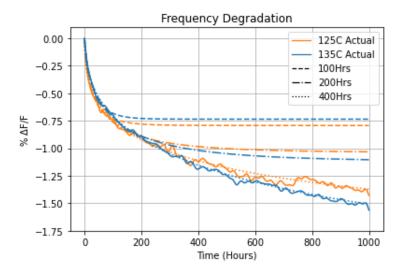

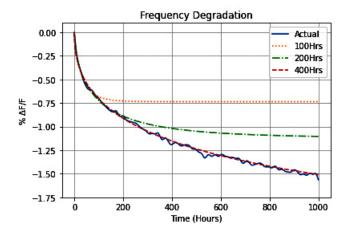

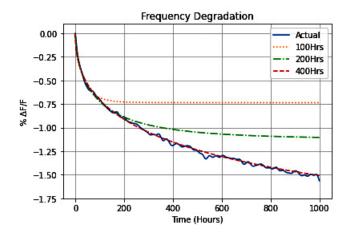

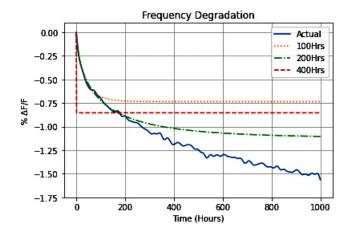

| 5.1          | The 'Actual' (solid) vs. 3-'Predicted' Degradation curves                                                                                                                                                                                                                                                                                                        | 42                              |

| 5.2          | trf algorithm: 'Actual' vs. 3-'Predicted' Degradation curves.                                                                                                                                                                                                                                                                                                    | 44                              |

| 5.3          | dogbox algorithm: 'Actual' vs. 3-'Predicted' Degradation                                                                                                                                                                                                                                                                                                         |                                 |

|              | curves                                                                                                                                                                                                                                                                                                                                                           | 44                              |

| 5.4          | lm algorithm: 'Actual' vs. 3-'Predicted' Degradation curves                                                                                                                                                                                                                                                                                                      | 45                              |

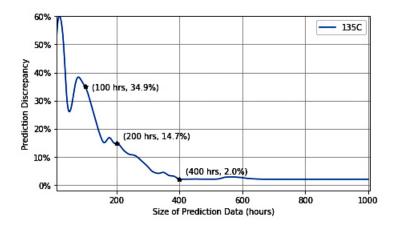

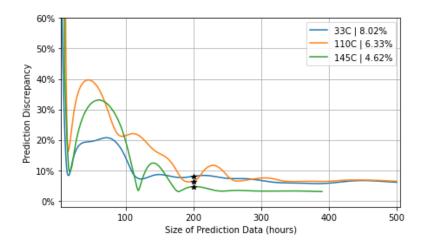

| 5.5  | Variation in <i>Prediction Discrepancy</i> on increasing the size of  |    |

|------|-----------------------------------------------------------------------|----|

|      | the Prediction Data at 135 °C. Highlighted points for predic-         |    |

|      | tion data sets of size 100 hrs, 200 hrs and 400 hrs                   | 46 |

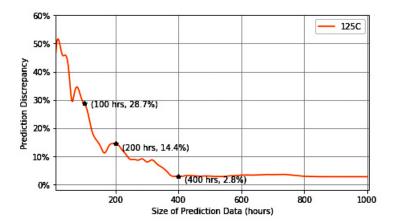

| 5.6  | Variation in <i>Prediction Discrepancy</i> on increasing the size of  |    |

|      | the Prediction Data at 125 °C. Highlighted points for predic-         |    |

|      | tion data sets of size 100 hrs, 200 hrs and 400 hrs                   | 47 |

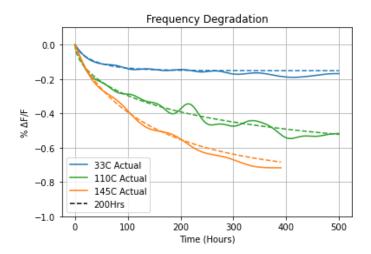

| 5.7  | 'Actual' (solid) and 'Predicted' ('') degradation curves for          |    |

|      | the 145 °C, 110 °C and 33 °C experiments                              | 48 |

| 5.8  | Variations in <i>Prediction Discrepancy</i> on increasing the size of |    |

|      | the Prediction Data. Label contains the values of the high-           |    |

|      | lighted points for prediction data set size of 200 hrs                | 49 |

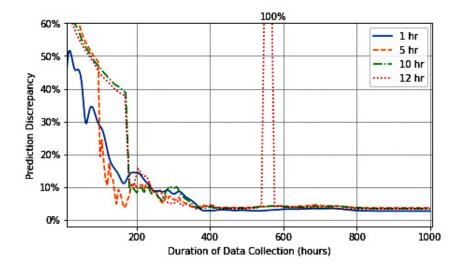

| 5.9  | Variation in the <i>Prediction Discrepancy</i> curve on reducing the  |    |

|      | sampling rate from once per hour to once per 12 hrs                   | 50 |

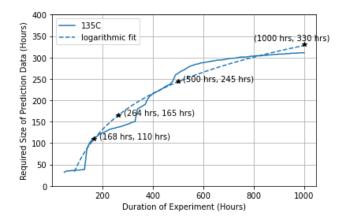

| 5.10 | Actual (solid) and logarithmic fit ('') curves representing           |    |

|      | the variation in minimum required size of <i>Prediction Data</i>      |    |

|      | for different duration of experiments to reach a discrepancy          |    |

|      | of $\leq 5\%$ at 135 °C                                               | 52 |

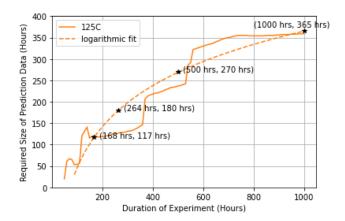

| 5.11 | Actual (solid) and logarithmic fit ('') curves representing           |    |

|      | the variation in minimum required size of <i>Prediction Data</i>      |    |

|      | for different duration of experiments to reach a discrepancy          |    |

|      | of $\leq 5\%$ at 125 °C                                               | 53 |

### Acknowledgements

I would like to express my deepest appreciation to my supervisor Dr. André Ivanov for providing his invaluable knowledge and expertise. I also could not have undertaken this journey without my defence committee, who generously provided their constructive feedback. Additionally, this endeavour would not have been possible without the generous support from the Huawei-UBC Joint Lab and NSERC, who financed my research.

I am also grateful to my research colleagues for their editing help, advice and suggestions. I would like to express my deepest gratitude to Dr. S. Arash Sheikholeslam for his regular technical support and guidance. I would also like to acknowledge the hardware support provided by Professor Guy Lemieux for my experiments.

Lastly, I would be remiss in not mentioning my family, especially my parents and my sister. Their belief in me has kept my inspiration and motivation high during this process. I would also like to thank my friends and community for all the entertainment and emotional support.

# Dedication

To my parents and sister

### Chapter 1

### Introduction and Motivation

### 1.1 Reliability of Semiconductor Devices

The reliability of a semiconductor device can be understood as the duration (usually in years) for which a device will consistently perform to its expectations when operated under nominal conditions. Different semiconductor markets have diverse reliability requirements, as shown in Table 1.1. Many factors influence these requirements. The important component to be comprehended is how the semiconductor industry estimates the reliability of their semiconductor devices within a time-frame that is relatively much shorter than a device's expected operating lifetime. In simple terms, reliability is estimated by accelerating the aging process of a semiconductor device and subsequently analyzing its performance which is expected to be equivalent to that of a device that has been operated under nominal conditions for a duration equivalent to its required operating lifetime.

To determine and qualify the reliability of silicon ICs, the JEDEC (Joint Electron Device Engineering Council) defined several standard reliability tests for the semiconductor industry [3]. Often these standards are used as the basis to develop market-specific qualification tests.

Table 1.1: Reliability Requirements for Different Semiconductor Markets

| Specification      | Consumer  | Medical    | Automotive | Aerospace    |

|--------------------|-----------|------------|------------|--------------|

|                    |           |            |            | and Military |

| Operating          | 3-5 years | 7-10 years | 15 years   | 30 years     |

| ${\bf Lifetime^*}$ |           |            |            |              |

<sup>\*</sup>The values in the table are a rough estimate based on various sources [4-9].

There are different aspects of reliability which are studied by each of the JEDEC's reliability tests. For example, in high temperature operating life-

time (HTOL) tests [10], the devices are stressed to determine their intrinsic failure rate during their expected operating lifetimes. In the early life failure rate (ELFR) tests [11], the stress conditions are designed to determine the failure rate during the initial phase of the ICs life. High temperature storage life (HTSL) tests [12] are performed to study the reliability of ICs that are not used immediately after production, but kept in storage for months for future use. Likewise, JEDEC defines various other reliability tests, and each of these have their own specific stress conditions, like die-temperature and voltage level, test duration, number of devices to be tested and pass/fail criteria [13].

### 1.2 Research Focus

An HTOL reliability test, whose stress conditions are described in JESD22-A108 [10], is particularly interesting. During an HTOL test, the devices are stressed for 1,000 hrs at 125 °C and a supply voltage of  $\sim 1.0$ -1.4\*V<sub>CC</sub>, because both temperature and voltage have been found capable of accelerating the aging process of a semiconductor device. This is remarkable at being one of the longest industry-standard reliability tests that consist of simultaneously testing 231 units (77 units x 3 lots) during which test none should fail, or else the entire test must be repeated with fresh lots. At times, this difficult requirement adds significant delay in a product's time to market. In the semiconductor industry, a product's time to market plays a crucial role in determining it's success. This implies that any such potential delay in a product's release can result in the loss of the company's respective market share, in turn impacting the company's revenue. Therefore, a reduction in this reliability test duration is of considerable importance.

Research is already underway to reduce test duration. One potential research avenue is the study of the Acceleration Factor (the factor by which the aging accelerates) during the HTOL test. S.W. Pae et al. in [14] and Robert Kwasnick et al. in [15], identified that the  $V_{AF}$  (voltage acceleration factor) has significantly increased with advancements in the process node, thereby implying that the 1,000-hour HTOL is an over-estimation of the intended operating lifetime. This suggests reducing the HTOL test duration in accordance with the  $V_{AF}$  of the respective technology. However, this approach is subject to fabrication technology.

Another potential approach to shorten duration is by predicting the HTOL test results. L. Yu et al. in [16] describe a method to select devices that could potentially "pass" such reliability tests, whereas W.T.K Chien et al. in [17] use WLR (Wafer Level Reliability) test results to predict HTOL test results. The latter approach is reasonable but still requires a correlation between the two reliability tests. Such works are primarily concerned with product-level  $V_{min}$  shifts or quick strategies for chip binning, whereas the research work described in this thesis, takes a more fundamental approach.

In this approach, an existing transistor-level aging model was leveraged to develop the circuit-level aging model which mathematically represents the degradation in a circuit parameter as a function of time. The value of the coefficient(s) of that circuit-level aging model are determined by merging the model's algebraic equation with the accelerated aging test data collected for a significantly shorter time frame. After obtaining the value of the coefficient(s), the model is used to generate a predicted degradation curve which can enable us to estimate the degradation in the remainder of the experiment. To measure the accuracy of prediction, the predicted degradation curve is compared to the actual degradation curve of the accelerated aging test.

To verify the feasibility of this approach, a significant amount of aging-test data was required. For that reason, several accelerated aging tests were conducted. To conduct those accelerated aging tests, we built a reliability test platform which could partially emulate the HTOL test conditions. The reliability test platform must provide a **stable** and **uninterrupted** operation, and maintain the desired **high temperature** for at least **1,000 hrs**. To achieve this, an **FPGA** (**Field-programmable Gate Array**) was chosen as a test platform because it is most readily available, has a relatively faster development time than ASICs for sensor-circuits and test setups, and has been successfully employed as a proxy in various reliability studies [18–23]. Most of such studies are either concerned with characterizing the influence of various aging phenomena on FPGAs, or with developing methodologies to improve FPGAs' operating lifetimes.

### 1.3 Reliability Physics of Semiconductor Devices

To better understand the approach, it is essential to understand the physics behind the aging of semiconductor devices, particularly as applied to the aging mechanisms that are of interest to this work.

- 1. Bias Temperature Instability (BTI): One of the most dominant aging mechanisms that occur in transistors, especially in current technology nodes, is BTI [24]. BTI-induced aging increases the threshold voltage ( $V_T$ ) and reduces the mobility ( $\mu$ ) of a transistor under temperature and/or  $V_{GS}$  stress [25]. Consequently, BTI degrades a transistor's performance in terms of its current driving capability and switching speed, resulting in circuit slowdown.

- 2. Hot Carrier Injection (HCI): Like BTI, HCI is also characterized by the shift in the  $V_T$  and  $\mu$  of a transistor, resulting in circuit slow-down. Although BTI and HCI have the same effect, charge carriers in the channel are responsible for HCI, since they gain sufficiently high velocity to get injected into the gate-dielectric [26].

- 3. Time-Dependent Dielectric Breakdown (TDDB): TDDB is characterized by the accumulation of oxide defects in the gate dielectric due to the application of the electric field ( $V_{GS}$ ) in transistors. Unlike BTI and HCI, TDDB does not affect the  $V_T$  or  $\mu$  of a transistor, but appears as the immediate failure of a transistor by effectively shorting the gate to the channel via the dielectric [4].

- 4. **Electromigration (EM):** EM is an aging mechanism that occurs in interconnects in metal wires. It is characterized by an increase in the interconnect resistance, caused by atomic drift in the direction of the electrons. Consequently, it increases the voltage drop across the interconnects, resulting in circuit slowdown. EM has an intense effect on the circuits that experience unidirectional current flow [27].

During an HTOL test, the accelerated aging observed in the devices is the cumulative result of all these aging mechanisms. The interaction amongst these mechanisms is complex and difficult to separate. However, if the test circuit and test conditions are chosen appropriately, we can enhance the effects of individual mechanisms. Therefore, as the first step toward this approach, the number of variables that impact the aging process were reduced so that the results can be conclusive. For that reason, our study's test circuit and conditions were set to enhance the effect of only one aging mechanism, chosen as being the **BTI**. Since **BTI** and **HCI** leads to circuit slowdown, their effects can be quantified by measuring the degradation in

a circuit's parameter. Thus, our initial aim was to capture the effects of these mechanisms on circuits implemented on FPGAs. However, **HCI** was found to have negligible contribution at high temperatures. Therefore, the analyses were modified to focus on **BTI**.

To emulate the HTOL test conditions, we were required to simultaneously increase the temperature and voltage of the test chip. However, the supply voltage to the test chip, i.e. FPGA, was preset by the manufacturer using an external power regulator chip; both of which were embedded by default onto the PYNQ-Z1 board [28] (a commercial board that embeds the FPGA chosen for testing). Therefore, in our first step we could only increase the chip temperature to accelerate the aging process, thereby only partially emulating the HTOL test conditions.

### 1.4 Aim of the reliability experiments

This research mainly seeks to determine the feasibility of forecasting an accelerated aging test result from the data collected for a significantly shorter time frame. Further, our experiments were conducted at a wide range of temperatures (above nominal) to validate the consistency in the results across diverse temperature ranges.

Since forecast accuracy depends upon the quantity of data used for estimation, it was essential to analyze the discrepancy between the predicted and true values, of the accelerated aging test results, as a function of the time frame and sampling rate of the data collection. To study the benefit of this approach to other standard reliability tests conducted over a much shorter duration, including HAST and ELFR, the time-frame requirements for data collection as the duration of the experiment changed, to achieve a given level of prediction accuracy, was also analyzed.

### 1.5 Overview of the thesis structure

The thesis is organized into two parts. The first focuses on explaining the reliability test platform and its features. The second portion describes the reliability experiments conducted on the platform used and a detailed analysis of their results.

#### 1.5.1 Part I

The first section covers the test platform and the flow of the experiments performed using it. Chapter 2 describes various features and modules of the reliability test platform. Chapter 3 discusses the importance of structuring the reliability experiments. It also explains the importance of automation in our experiments that made it possible to conduct the long-duration tests with minimal human intervention.

#### 1.5.2 Part II

The second part covers the results obtained from the thermal stress experiments and various analyses of those results. Chapter 4 describes the setup of each of the thermal stress experiments conducted on the reliability test platform, and their measurement results. It also highlights the limitations of the test platform, indicating scope for improvement. Chapter 5 contains multiple levels of analysis that are performed on the measurement results to illustrate the feasibility of the approach. It also discusses about the benefit of the approach to other standard reliability tests of shorter duration than HTOL.

Following the analyses, Chapter 6 makes some conclusive remarks on this study, and presents new insights that arose during the process. It also describes a few limitations encountered during this approach and some final suggestions for future work that could make this approach more widespread than it currently is.

### Chapter 2

### Reliability Test Platform

### 2.1 FPGA

To perform all the thermal stress experiments that are described in this thesis the PYNQ-Z1 [28] board was employed to build the reliability test platform. PYNQ-Z1 embeds Xilinx's Zynq XC7Z020-1CLG400C chip which is a member of the Zynq-7000 SoC [29] family of FPGAs built on 28nm technology and is also the device under test (DUT). In the past, FPGAs have been widely used to study transistor and circuit-level aging and reliability for two primary reasons. The first is the motivation to increase the operating lifetime of FPGAs by characterizing the aging mechanisms and their effects that impact FPGA performance over the long run [19–23]. The second is to use the FPGAs as proxies to address the more general interest in the aging of transistors and the reliability of circuits used in custom ICs [18, 30].

In either scenarios, the test platform built to conduct those experiments rely on external lab equipment and measurement instruments, which makes their test setups difficult to replicate making results' reproducibility a challenge. To overcome this, the reliability test platform described here is embedded into the device under test, facilitating recreating the test setup.

### 2.2 **TYNQ**

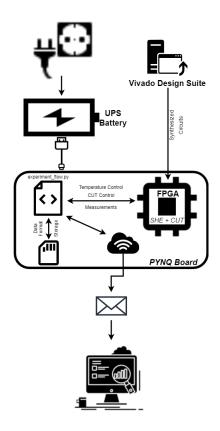

The reliability test platform is Test TYNQ [1]: platform PYNQ-Z1 board [28]. Figure 2.1 highlights the principal elements of TYNQ and their functional relationships. The *IP Repo* element is a repository containing a customizable set of programmable logic test circuits (IP blocks). The development of all the IPs took place in Xilinx Vivado Design Suite -HLx Editions - 2020.1 software. These IPs when implemented on the FPGA chip, interact with the ARM cores of the FPGA through the AXI protocol [31]. The specific communication link between these IPs and the ARM cores is enabled via a set of specially developed drivers coded in Python. While the focus was on developing a test platform to conduct experiments on Zynq-7000 SoC devices, TYNQ is a platform that can be adopted to conduct similar experiments on any devices that support the PYNQ framework. Python codes, programmable logic circuit's bit-streams, and user manuals (wiki) can all be found in the following repository: https:// github.com/sarashs/TYNQ.

Figure 2.1: [1] A structural illustration of the TYNQ platform. TYNQ consists of a set of IPs stored in the IP Repo, a Python utility module utils.py to generate user-specific placement constraint files for IPs, and a driver module TestChip.py was used to enable user interaction with the IP circuits.

TYNQ's features are classified into two categories: hardware and software. Each class consists of several modules but the description here will be limited to the modules that were adopted to conduct the experiments described in this thesis.

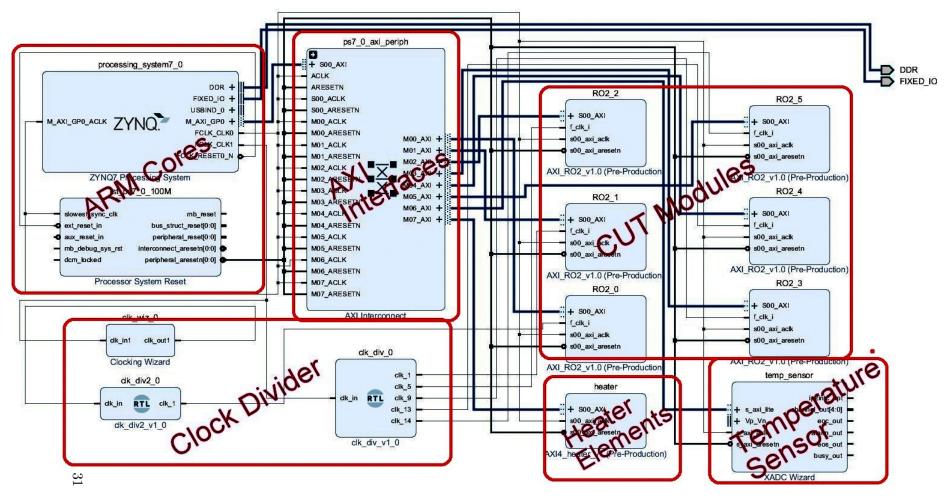

### 2.2.1 TYNQ: Hardware

TYNQ's test infrastructure hardware modules (IP blocks) are customizable and designed to connect to the Zynq-7000 SoC processing system (ARM cores) via AXI-Lite interfaces as shown in Figure 2.2. The current version of TYNQ includes five core modules: Ring Oscillator (RO), BTI Sensor, HCI Sensor, Self-heating Module and Temperature Sensor Module [1]. BTI, HCI and Temperature Sensor Modules are out of the scope of this work, and so will not be described here.

Figure 2.2: Vivado Block Design window: The connection of the IP blocks (Hardware Modules) with the Zynq-7000 SoC processing system (ARM Cores) via the AXI-Lite Interface (AXI Interfaces).

### Ring Oscillator (RO) Module

Ring Oscillators have been widely used as basic test architectures to perform various kinds of accelerated aging and reliability experiments [18, 20, 21, 30]. A shift in their frequency is applied as a measure to capture change in the circuit's environmental conditions (including voltage and temperature), and/or to study drift in its transistors' parameters (such as  $\mu$  and  $V_T$ ), caused by

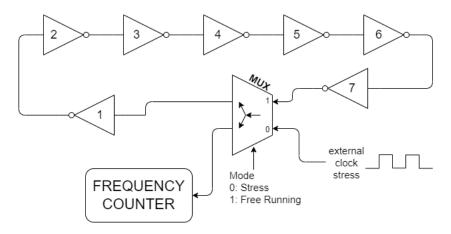

aging. For the experiments discussed in this thesis, the TYNQ's RO architecture, illustrated in Figure 2.3, was modified because the given RO architecture lacks control over the oscillation frequency. The voltage signals between any two stages are not exactly square waves and neither possesses a precise 50% duty cycle. To have achievable control over the frequency of oscillation, sharp voltage transitions and steady voltage levels at all nodes, and to be able to guarantee that the stress on the oscillator is a quasi-ideal AC stress of 50% duty cycle, the architecture was modified to that portrayed in Figure 3.1. The modified circuit architecture is described in detail in the next chapter.

Figure 2.3: [1] TYNQ's RO Architecture.

Figure 2.4: [2] 6-Input Look-up Tables on Zynq-7000 SoC FPGAs with varied numbers of outputs.

Each inverter stage in the RO architecture is built upon a 6-input (I0, I1,..., I5) Look-up table LUT6 with a single output O, shown in Figure 2.4a. Only 'I0' is used for input whereas the remaining inputs are set to 0 and the SRAM bits (constituting the output values for each input combination) are pre-set to define the boolean function, NOT. Appendix A contains this inverter's Verilog instantiation code. Along with an odd number of inverter stages, the RO module possesses an additional stage, one2two, which does not invert its input but duplicates it to two different nets: one feeding input back to #1 inverter and the other to the  $Frequency\ Counter$ , to monitor the oscillation frequency of the RO. This stage was also constructed from a 6-input Look-up table, but has two outputs,  $LUT6_-2$ , as shown in Figure 2.4b. Appendix B contains the Verilog instantiation code of the one2two stage.

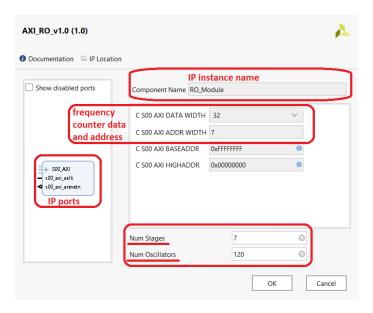

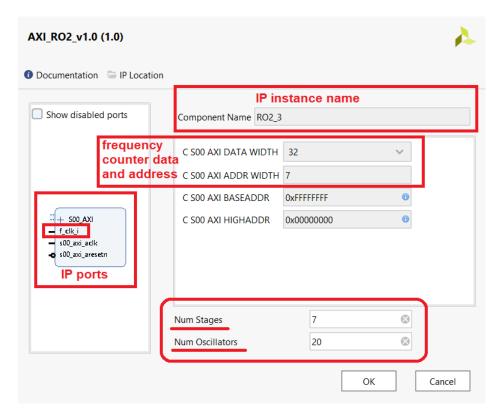

The RO module has the flexibility to set the number of inverter stages in each ring oscillator, and the total number of such oscillators, to be implemented on the FPGA. These settings can be found during the instantiation of the RO IP under the IP customization window in Vivado software, as shown in Figure 2.5. The *frequency counter* data and address widths were predefined. However, a user can modify them by manipulating the source code.

Figure 2.5: The Vivado IP Customization window: A **RO Module** customization of its number of stages (*Num Stages*) and the total number of ROs (*Num Oscillators*).

#### Self-heating Module

The purpose of this module is to raise the chip temperature to the desired levels to thermally stress the test circuits (like **Ring Oscillators**) that are implemented on the same chip, thereby removing dependency on the external temperature controllers known as thermal chambers (including ovens and thermostream) which are expensive and not necessarily available/accessible to all.

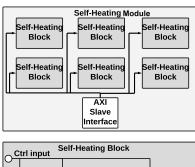

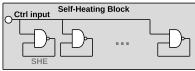

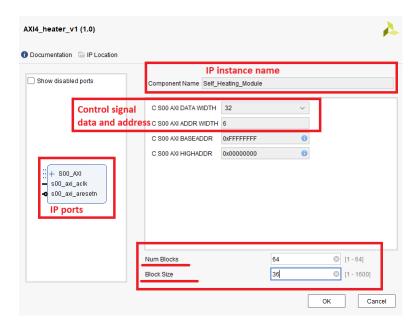

TYNQ's Self-heating Module [1] consists of numerous identical SHE blocks (selfheating blocks), in which each block is controlled with an input signal received from the processing system via the AXI slave interface, as shown in the Figure 2.6. Each block is composed of several identical Self-heating Elements (SHEs). Each SHE is a controlled single-staged RO, as proposed by A. Amouri et al. [32, 33]. The module has the flexibility to set the number of SHEs per block and the total number of such blocks, to be implemented on the FPGA. These settings can be found during the instantiation of the Self-heating Module under its IP customization window in the Vivado software, as shown in Figure 2.7. Note that the SHEs consume a significant degree of power and therefore, the maximum possible number of instantiated SHEs depends on the maximum power limit setting of the PYNQ board.

Figure 2.6: [1] A Self-heating Module circuit diagram displaying six SHE blocks with their respective control signals received from the AXI Slave Interface. Each SHE block consists of numerous SHEs.

The Zynq-7000 SoC FPGA has a built-in ADC (labelled XADC), which consists of a temperature and on-chip power supply voltage sensors. TYNQ's Self-heating Module utilizes the temperature sensor's reading as a feedback parameter to regulate the die temperature. The module is customizable and its configuration is based on two parameters  $Num\_blocks$  (the total number of SHE blocks) and  $Num\_SHE\_per\_block$  (the total number of SHEs per block), thereby setting the total number of SHEs to  $Num\_blocks \times Num\_blocks$

Figure 2.7: The Vivado IP Customization window: A **Self-heating Module** customization of the total number of blocks (*Num Blocks*) and number of heating elements per block (*Block Size*).

Num\_SHE\_per\_block. The temperature is regulated through the TestChip Driver (a TYNQ's software module) which implements a control loop running on the processing system to individually turn each of the SHE blocks ON or OFF by following a default temperature control algorithm [1], which is as follows:

```

i \leftarrow 0 SHE\_Blocks[0:Num\_blocks-1] \leftarrow OFF {Turn off all of the blocks.} while True do if T_{current} < T_{desired} \pm T_{tolerance} then SHE\_Blocks[i] \leftarrow ON i \leftarrow i+1 if i == Num\_blocks then i \leftarrow Num\_blocks-1 end if else if T_{current} > T_{desired} \pm T_{tolerance} then SHE\_Blocks[i] \leftarrow OFF i \leftarrow i-1 if i < 0 then

```

```

i \leftarrow 0

end if

else

Pass

end if

end while

```

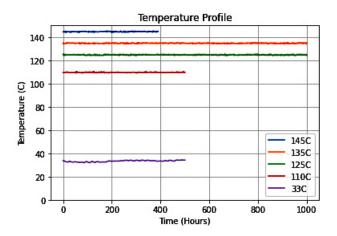

where  $T_{current}$  is the instantaneous temperature measured by the XADC,  $T_{desired}$  is the desired chip temperature, and  $T_{tolerance}$  is the acceptable temperature deviation range. The algorithm is customizable such that a user can implement a stricter control algorithm for greater precision. For the experiments described in the thesis, this simple algorithm provided acceptable  $(\pm 1^{o}\text{C})$  temperature control.

### 2.2.2 TYNQ: Software

The hardware modules of TYNQ interact with the FPGA's processing system via a set of specifically developed drivers collectively referred to as the **TestChip Driver** [1], represented in Figure 2.1 by the block, **TestChip.py**. To aid users in placing the hardware module circuits in a desired configuration on the FPGA, the TYNQ platform provides a set of "utility" Python codes [1], represented by the **utils.py** block which generates user-specific placement constraint files for each of those hardware modules. These software modules are fully described in the TYNQ's repository. Their brief highlights are as follows.

#### TestChip Driver (TestChip.py)

This software establishes a communication link between the user and all the hardware modules implemented on the FPGA, via the PYNQ framework. Specifically, this script enables the user, during an experiment, to read the frequency measurement from the Frequency Counters of all the RO Modules, and the instantaneous on-chip temperature and voltage levels, and regulate the die temperature by controlling the Self-heating Module. For the reliability experiments later discussed in this thesis, this module was extended by adding certain features that aid in the automation of the experiment. These features will be discussed in the next chapter. The default set of implemented functions is provided in Appendix D.

#### Python Utility Module (utils.py)

The purpose of this module is to enhance users' ability to generate constraint (placement) files for the aforementioned hardware modules as per their desired configurations. For instance, if it is necessary to place ROs or their stages and/or thousands of SHEs in a particular pattern, the Python Utility module can generate their necessary constraint files. Further details regarding the utility module as well as tutorials and examples are provided in the repository.

### 2.3 Conclusion

This chapter briefly described various features of the reliability test platform: TYNQ, compatible with the Xilinx 7000 series FPGA devices that supports the PYNQ framework. Each of the modules described plays an important and unique role in all the experiments: the Self-heating Module helps to raise and maintain the die temperature whereas the RO Module acts as a test circuit to quantify the impact of thermal stress. The Python Utility Module made it feasible to generate placement commands for hundreds of ring oscillators and thousands of required SHEs whereas the **TestChip Driver** provided a means to centrally communicate with all the hardware modules. The next chapter describes the structure and flow of the long reliability experiments which were built upon the modules of the TYNQ platform.

### Chapter 3

## Reliability Experiment Structure

# 3.1 Necessity for Structuring the Reliability Experiments

Every semiconductor device undergoes some aging process throughout its lifetime, due to which its performance degrades. This degradation in performance needs to be predicted by the semiconductor manufacturers to understand the reliability of their devices. JEDEC defined several standard reliability tests for the semiconductor industry to aid manufacturers in determining the reliability of their semiconductor devices. During these reliability tests, only a certain number of devices (also called sample size) across different lots are stressed under elevated environmental conditions of temperature and voltage. These conditions aid to accelerate certain aging mechanisms, so that the minimum reliability of that device, under nominal operating conditions, can be predicted. In general, such tests are termed reliability tests.

All the reliability experiments performed during this research work were conducted at high temperatures relative to ambient, while the voltages remain at their nominal levels. The experiment setup was aimed to emulate the HTOL test conditions, wherein the duration of the experiments was targeted for 1,000 hrs with a temperature of 125  $^{\rm o}$ C. However, to measure the consistency of this approach across diverse temperatures, as discussed in Chapter 1, the experiments were carried out at temperatures ranging from 33  $^{\rm o}$ C to 145  $^{\rm o}$ C.

There are numerous challenges to achieve the task of conducting a reliability experiment that remain uninterrupted for 1,000 hrs. A few examples are:

1. An interruption in power supply, or stress signal, even for a couple of

seconds, can let the test chip go under unanticipated recovery which can affect our measurements and subsequent analysis. To overcome this a UPS battery backup that also provides power surge protection was installed.

- 2. An inconsistent distribution of heat on the test chip can change the value of the measurement parameter. This remains a major limitation of our TYNQ platform for temperatures during which most of the SHEs remain OFF.

- 3. The 1,000-hour capture and storage of degradation data can lead to memory overflow which can potentially freeze the experiment. This was overcome by setting up an appropriate number of hourly measurements and storing them into a concise file format that requires only a fraction of MBs of space.

The next section discusses a few crucial components of the reliability experimental setup, and how they come together to provide a structure for the experiment. The subsequent section will describe the final execution flow of the experiment.

### 3.2 Crucial Components for a Reliability Experimental Setup

All the reliability experiments conducted during this research were automated. Once an experiment was launched, there was practically no control over it. This was purposefully done because the test needs to run uninterrupted for at least 1,000 hrs to emulate HTOL test conditions. For that matter, human intervention during the experiment needed to be minimized, so that all our experiments could be a quasi-exact replicas of one another. The automation of experiments requires the combined support of software [SW] and hardware [HW].

### 3.2.1 Power Supply with Battery Back-up [HW]

Since the reliability experimental setup cannot tolerate any kind of power supply interruption(s), it is necessary for it to possess a supply containing a battery back-up, preferably with surge protection. 1,000 hrs is equivalent to 42 days, which means users must be aware of any planned power outage(s)

in the one-and-one-half month window, beginning from the time when the experiment is launched.

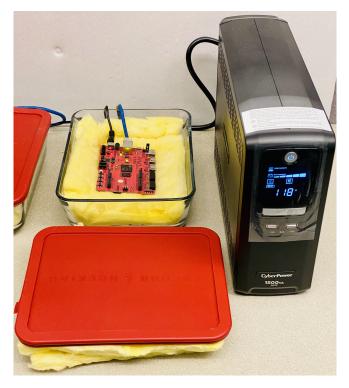

UPS batteries are a good fit for short-term (several hours of) supply. Thus, the "CyberPower 1500VA 10-Outlet UPS Battery Back-Up (LX1500GU-FC)" was adopted for the research work. It was estimated that it could support two of the reliability experiments simultaneously for ~5 hrs. In the event of a power interruption, it would have been able to switch over to its battery supply within 4ms, which we felt to be sufficiently rapid for the test platform to be completely unaware of any variety of power interruption. This was verified by manually unplugging the UPS from the power-line during a trial experiment. The UPS device also supported power surge protection, which was crucial since an unprotected power surge has the potential to damage a test chip. In fact, one of the initial experiments was not only interrupted but the test chip likewise damaged due to a power surge event in the facilities. That experiment along with the rest, and their results, are discussed in the subsequent chapters.

### 3.2.2 Self-heating Module [HW]

To raise the die temperature to conduct thermal stress experiments, the  $Self-heating\ Module$  of the TYNQ platform was employed. The module's SHEs generate the required amount of heat to raise the temperature to the desired level (with a maximum achievable level of 145 °C with 2,304 SHEs), and the on-chip XADC (comprising a temperature sensor) serves as a feedback parameter to regulate the temperature throughout the experiment. A total of 2,304 SHEs was implemented, as displayed in Figure 4.4, (36  $SHE\_blocks$  and 64 SHEs per block), along with their respective control circuitry that serves to turn the individual blocks on or off. The combination of [36 \* 64] was estimated by following a trial-and-error method. Although there are multiple possible combinations to achieve the same number of SHEs, the [36 \* 64] combination was found to provide a stable temperature for the given temperature regulation function: the  $fix\_temperature$  of the **TestChip Driver** module. The  $fix\_temperature$  function enables the user to automate the process of temperature regulation during an experiment.

# 3.2.3 Circuit Under Test (CUT or BTI Sensor) Module [HW]

To quantify the impact of thermal stress, a ring oscillator (RO)-based architecture was used, as illustrated in Figure 3.1. This is a modified version of the TYNQ's hardware **RO Module**. This architecture is similar to M. Naouss *et al.*'s [30], with the addition of an on-chip digital *Frequency Counter* that monitors the frequency of the **CUT** throughout the experiment, thus aiding in the experiment's automation. The free-running frequency of this RO is a reference parameter against which the degradation (aging) degree is measured.

Figure 3.1: Circuit Under Test (CUT) Architecture.

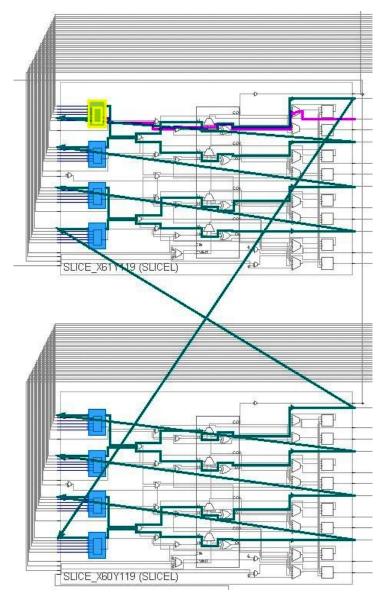

The number of inverter stages in the **CUT** was chosen to be seven since the size of the configurable logic blocks (CLB) is limited to eight LUTs per CLB. Longer **CUTs** require multiple CLBs which increases the routing length for inter-CLB connections, thus adding more unwanted elements to this BTI sensor circuit. Figure 3.2 shows the implementation of a single **CUT** in a CLB.

Figure 3.2: The implementation of the **CUT** stages on a CLB. The BLUE blocks are the inverter stages. The YELLOW block is the MUX stage. The GREEN connections are the routing nets. The PINK net connects the MUX stage to the *Frequency Counter*.

Additional functional and implementation details of the  ${f CUT}$  are as follows:

- Inverter #: Each inverter is implemented on the LUT6 (6-input 1-output) described earlier in the TYNQ's RO Module.

- MUX: The MUX stage is implemented on LUT6.2. It controls the two modes of operation of CUT: STRESS and MEASUREMENT. In the STRESS mode, the entire chain of seven inverters oscillates at the external clock's frequency whereas in the MEASUREMENT mode CUT is left to run at its free-running frequency. MUX also duplicates the selected input signal to two nets: one returns to Inverter #1 and the other to the Frequency Counter. Appendix E contains the Verilog instantiation of this MUX.

- "external clock": This is a clock signal generated from on-chip the FPGA using ZYNQ7 Processing System -> PL Fabric Clocks -> IO PLL. The clock signal performs as an external clock/AC stress signal to the CUT. The purpose of this clock signal is to allow for a controllable AC stress signal.

The *Mode* signal to the **CUT** was controlled from the modified TYNQ's **TestChip Driver** module, discussed in the latter sections, which further aided in automating the experiment. The IP of the **CUT Module** can be found in the following GitHub repository: https://github.com/quanta7/CUT-Circuit-Under-Test/tree/main/ip\_repo.

### 3.2.4 Python-Based Script experiment\_flow.py [SW]

To automate the tests, the **TestChip Driver** module (one of the TYNQ's software modules), was extended to include some important features pertaining to the requirements of the reliability experiments, and was re-named the *experiment\_flow.py* because it controlled the entire flow of the experiment. Some important features defined in the script that are related to the experiment are as follows:

#### Temperature Regulation

The fix-Temperature function defines the temperature regulation feature by controlling each of the SHE blocks independently. This feature takes input (XADC-temp()) from the built-in temperature sensor and enables/disables each of these SHE blocks to control the total heat generation so as to regulate the temperature during the experiment. Appendix F contains the

fix\_temperature function script that executes this task. Figure 3.3 illustrates the temperature profile achieved during the experiments that used this feature to regulate die temperature.

Figure 3.3: Graph illustrating the measured temperature profile from the results obtained during our experiments that used the fix\_temperature function to regulate die temperatures to the desired temperature level. During these experiments, the temperature level was found to be within  $\pm 1^{\circ}$ C of the desired level.

#### **CUT Control**

Recall that the **CUT** shown in Figure 3.1 has two modes of operation controlled via the *Mode* signal. The python script (*experiment\_flow.py*) has a control over this particular signal for each of the **CUTs** implemented on the test chip. This handle is provided by the *en\_feedback* function (added to the **TestChip Driver**), which allows the user to switch between both the modes of operation. The function definition below shows, how the *Mode* signal for all the 20 **CUTs** inside a **CUT Module** can simultaneously be either set to '1' or '0'.

#### Read Frequency

There are more than 100 **CUTs** implemented in every experiment on each FPGA, that simultaneously undergo degradation, and the digital frequency counters continuously monitor their frequency. This feature reads the frequency value stored simultaneously in all the counters and stores it for further formatting and transmission. Appendix G contains the *read\_multi\_RO* function script that reads the oscillation frequency of the input **CUTs**.

#### Data Format and Storage

Apart from the frequency of **CUTs**, we also measured various internal voltage levels (those that are accessible to the user), die temperatures and the time instants of measurement. At each hour of the experiment, this information is captured, organized and stored in a file in a pre-defined format. The files generated were stored locally on the microSD card of the PYNQ-Z1 board. The record function in Appendix H performed this job by taking some basic inputs: the FPGA bitstream (an implementation image of all the circuits), durations of measurement, sampling step sizes, numbers of **CUTs**, and the desired temperature levels, respectively. The sampling step size duration was set according to the time consumed by the ZYNQ processing system to measure, hold and transfer the frequency counter data. This prevented the system from entering into standby during every call of data measurement and transfer.

#### Dispatch Email

This feature sends an email containing an attachment of the new files generated every hour. This is primarily done to prevent data loss during unforeseen scenarios. The function sendemail in Appendix I performs this task. Potential errors, including discontinuity in internet connections, could freeze this function (and the experiment) if they coincided with the time instant when this function was called. For its seamless operation, errors rising due to such scenarios should be handled in the function definition. This function needs a sender's Gmail address and password prior to the launch of every experiment. However, with the upcoming changes from May 30, 2022 onward in Google's Security and Privacy Settings, a third-party application such as this PYNQ framework on which the test platform was built, would no longer be able to sign into a Google account using only the email address and password. Thus, a user should modify the function in accordance to support their respective organization's webmail services.

#### 3.3 Structure of the Experimental Setup

The entire physical structure of the experiment is shown in Figure 3.4. The PYNQ board always received its power supply from the UPS to remain immune from any power interruption(s) and power surge(s). All bitstream files from the Vivado software were stored on the microSD card of the PYNQ board prior to the launch of the experiment. The experiment\_flow.py controlled the stress experiment on FPGA while simultaneously communicating with a microSD card (embedded on the PYNQ-Z1 board) to store the data, and the PYNQ board's web connectivity to transmit the data over the web.

Figure 3.4: Complete Structure of the Experimental Setup.

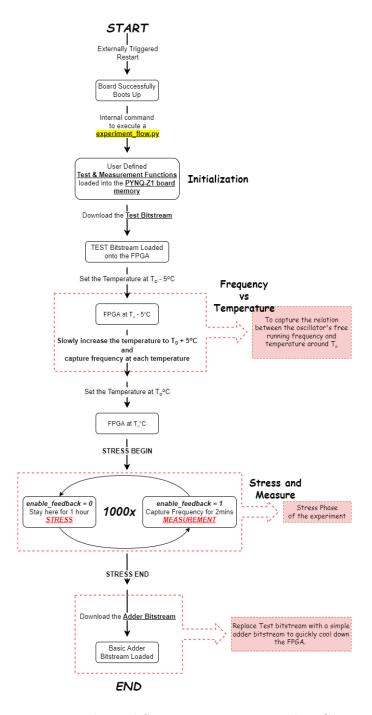

Figure 3.5: Thermal Stress Test Execution Flow Chart.

#### 3.4 Flow of the Reliability Experiments

The earlier sections briefly discussed various software and hardware components which together made the experimental automation feasible. This section describes the automated executional flow of the experiments as represented in Figure 3.5. The entire flow of the experiment was divided into three phases: *Initialization*, *Frequency vs Temperature* and *Stress and Measure*. The intermediate phase of *Frequency vs Temperature* was not useful if the temperature regulation feature performed to its expectations. Note that the entire flow of the experiment was open-loop, i.e. at each step in the flow, the system assumed that all the previous step(s) had been successfully executed and never attempted to verify the success/failure of the previous step.

- 1. Initialization: In this phase, the experiment\_flow.py script was loaded into the PYNQ-Z1 memory. Since this script controlled the entire flow, from this point forward, this python script became the sole driver of the experiment. Subsequently, the test bitstream (FPGA circuits implementation image) was downloaded onto the FPGA. A successful download meant all the SHEs and CUTs were in place. Following this, a command from the script began to increase the temperature of the chip to T<sub>0</sub>-5 °C (T<sub>0</sub> being the stress temperature) by using its Temperature Regulation feature.

- 2. Frequency vs Temperature: After the temperature reached [T<sub>0</sub>-5 °C] (T<sub>0</sub> being the stress temperature), it was raised in steps of 2°C (up to T<sub>0</sub>+5 °C) to measure the frequency of CUTs at every step. The measured data was stored, and its copy also transmitted over the web using the Dispatch Email feature. This measurement was performed to capture the relationship between frequency and temperature, which could be used, if necessary, during the data analysis. Later, the chip temperature was achieved ~T<sub>0</sub>°C. The portion of the experiment\_flow.py that executed Phases 1 and 2 is shown in the Appendix J.

- 3. Stress and Measure: In this phase, the CUT was stressed for an hour at the *external clock* frequency, and then its free-running frequency was measured over a window of 2 minutes (measuring multiple times to increase the precision) using the **Read Frequency** feature. Subsequently, the measured data was stored locally using the **Data Format and Storage** feature, and also transmitted over the web.

This was repeated 1,000 times. This switching between different modes was possible with the help of the **CUT Control** feature. The python script that performed this repetitive operation and regularly dispatch the data as email attachments is shown in Appendix K.

#### 3.5 Conclusion

In this chapter we examined various crucial HW and SW components of the experimental setup, and how they combine to build the complete structure of the reliability experiment. We also looked at various features of these components that served to make the automation of the 1,000-hourlong experiment feasible. With the reliability test platform in place and by creating a structure based on it, we conducted several thermal stress experiments whose results and analyses are discussed in the next chapters.

## Chapter 4

# Thermal Stress Experiments

#### 4.1 Aim

Previous chapters looked at the reliability test platform, its various hardware and software components that provided the necessary features to run the experiment over a long duration, and the structures of the experiments that enabled automation and uninterrupted flow. In this chapter, all the reliability experiments conducted and their measurement results are reported.

#### 4.2 General Test Setup

Figure 4.1 portray the physical setup of the reliability experiment. This setup was placed in one of UBC's ECE laboratories. The PYNQ-Z1 board was connected to the internet via a LAN (Local Area Network) connection. The board was kept within a glass chamber filled with fibreglass. Fibreglass has a very high melting temperature ( $\approx 1500$  °C). This property makes it a viable option for our setup for use in insulation, causing the heat to remain trapped and allowing the test chip to easily increase to the desired temperature. In the case of any electric failure on the board, the fibreglass would not have been melted by the resulting transient excessive heat.

During each experiment, a total of six batches of the **CUT Module** were implemented on the FPGA, with each batch consisting of 20 **CUTs**. Each batch received a unique external clock signal that remained unchanged throughout the experiment. For the six batches, there were six different clock signals covering a wide range of frequencies: 225 MHz, 100 MHz, 6.25 MHz, 390 KHz, 24 KHz and 12 KHz. This was done primarily to capture the contribution of another aging mechanism HCI, since HCI occurs during transistor switching, implying that batch stressed at a higher clock frequency would be expected to show significantly higher HCI-induced degradation. To render all these frequencies a basic clock divider circuit was implemented us-

Figure 4.1: An image showcasing our experiment setup in the laboratory. The PYNQ-Z1 board was placed within a glass container filled with fibre-glass (yellow). *CyberPower 1500VA* is the UPS providing power-backup and surge protection. Prior to the launch of an experiment, some fibreglass was placed on the board, along with the container's lid (shown in red color).

ing D Flip-Flops (D-FFs). Its Verilog instantiation source code is provided in Appendix L.

Figure 4.2 displays the Vivado IP customization window of an instantiation of the **CUT Module** with the name "RO2-3". The IP ports in the customization window has an additional port of  $f_-clk_-i$  which does not exist in the IP ports of the **RO Module** (Figure 2.5). The  $f_-clk_-i$  port was introduced to feed the **external clock** signal to all the **CUTs** inside the **CUT Module**. The block design of the entire system on the FPGA is illustrated in Figure 4.3 and its placement on the chip is highlighted in Figure 4.4.

Figure 4.2: The Vivado IP Customization window: **CUT Module** customization of its number of stages (*Num Stages*) and the total number of **CUTs** (*Num Oscillators*).

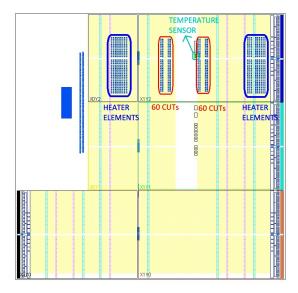

Figure 4.3: The Vivado Block Design of the system implemented on the Zynq XC7Z020-1CLG400C. A highlighted instantiation of six **CUT Modules**, the **Self-heating Module** (HEATER ELEMENTS) and the Temperature Sensor (XADC).

Figure 4.4: The Zynq XC7Z020-1CLG400C layout. A highlighted placement of the 120 **CUTs**, the heater elements and the XADC (Temperature Sensor).

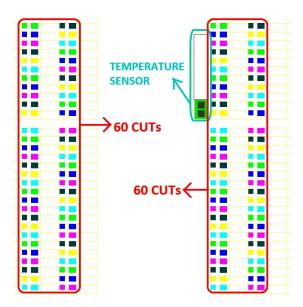

Figure 4.5: The Zynq XC7Z020-1CLG400C layout. A zoomed image of the 120  ${\bf CUTs}$  placement, showcasing the uniform distribution of 20  ${\bf CUTs}$  of each of the six batches.

#### 4.3 Experiments

This section describes the measurements obtained in the thermal stress experiments, each conducted on a different chip. The fixed test execution flow of Figure 3.5 was maintained for all the experiments. The duration of each of those experiments is shown in Table 4.1. The stress temperature of 145 °C was observed to be the maximum achievable temperature on the chip. The minimum ambient temperature that we could achieve by employing a mini-refrigerator was 0 °C, but due to the unavoidable heating of the chip, the minimum attainable die temperature was measured at  $\sim 33$  °C. The temperature level of 125 °C was chosen in accordance with the HTOL test conditions. The 110 °C and 135 °C stress temperature experiments were added to expand the scope of the experiments to study the activation energy  $(E_a)$  of the **BTI** aging mechanism. Although it was proposed that all the experiments be conducted for 1,000 hrs, some needed to be curtailed to shorter durations because the test setup was concurrently being modified. Experiments #1 and #2 were the longest experiments, and were conducted when the reliability test platform was in a more stable state than it had been during the Experiments #3, #4 and #5. The measurements from each experiment are described in this section. A detailed analysis of those results will be covered in the subsequent chapter.

Table 4.1: The Duration of the Thermal Stress Experiments

| EXP. | Experiment         |                 |  |  |  |

|------|--------------------|-----------------|--|--|--|

| No.  | Stress Temperature | Stress Duration |  |  |  |