### Software-Hardware Co-design for Energy Efficient Datacenter Computing

by

Tayler Hicklin Hetherington

B.A.Sc., The University of British Columbia, 2011

### A DISSERTATION SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### **Doctor of Philosophy**

in

# THE FACULTY OF GRADUATE AND POSTDOCTORAL STUDIES

(Electrical and Computer Engineering)

The University of British Columbia (Vancouver)

October 2019

© Tayler Hicklin Hetherington, 2019

The following individuals certify that they have read, and recommend to the Faculty of Graduate and Postdoctoral Studies for acceptance, the dissertation entitled:

Software-Hardware Co-design for Energy Efficient Datacenter Computing

submitted by Tayler Hicklin Hetherington in partial fulfillment of the requirements

for the degree of Doctor of Philosophy

in Electrical and Computer Engineering

#### **Examining Committee:**

Tor M. Aamodt, Electrical and Computer Engineering Supervisor

Mieszko Lis, Electrical and Computer Engineering Supervisory Committee Member

Margo Seltzer, Computer Science University Examiner

Sudip Shekhar, Electrical and Computer Engineering University Examiner

Emmett Witchel, The University of Texas at Austin, Computer Science External Examiner

#### **Additional Supervisory Committee Members:**

Steve Wilton, Electrical and Computer Engineering Supervisory Committee Member

## Abstract

Datacenters have become commonplace computing environments used to offload applications from distributed local machines to centralized environments. Datacenters offer increased performance and efficiency, reliability and security guarantees, and reduced costs relative to independently operating the computing equipment. The growing trend over the last decade towards server-side (cloud) computing in the datacenter has resulted in increasingly higher demands for performance and efficiency. Graphics processing units (GPUs) are massively parallel, highly efficient accelerators, which can provide significant improvements to applications with ample parallelism and structured behavior. While server-based applications contain varying degrees of parallelism and are economically appealing for GPU acceleration, they often do not adhere to the specific properties expected of an application to obtain the benefits offered by the GPU.

This dissertation explores the potential for using GPUs as energy-efficient accelerators for traditional server-based applications in the datacenter through a software-hardware co-design. It first evaluates a popular key-value store server application, Memcached, demonstrating that the GPU can outperform the CPU by  $7.5 \times$  for the core Memcached processing. However, the core processing of a networking application is only part of the end-to-end computation required at the server. This dissertation then proposes a GPU-accelerated software networking framework, GNoM, which offloads all of the network and application processing to the GPU. GNoM facilitates the design of MemcachedGPU, an end-to-end Memcached implementation on contemporary Ethernet and GPU hardware. MemcachedGPU achieves 10 Gbit line-rate processing at the smallest request size with 95-percentile latencies under 1.1 milliseconds and efficiencies under 12

microjoules per request. GNoM highlights limitations in the traditional GPU programming model, which relies on a CPU for managing GPU tasks. Consequently, the CPU may be unnecessarily involved on the critical path, affecting overall performance, efficiency, and the potential for CPU workload consolidation. To address these limitations, this dissertation proposes an event-driven GPU programming model and set of hardware modifications, EDGE, which enables any device in a heterogeneous system to directly manage the execution of pre-registered GPU tasks through interrupts. EDGE employs a fine-grained GPU preemption mechanism that reuses existing GPU compute resources to begin processing interrupts in under 50 GPU cycles.

## Lay Summary

This dissertation explores the potential to improve the performance, efficiency, and cost of datacenter computing through the use of highly parallel and efficient hard-ware accelerators, specifically graphics processing units. However, the types of applications that typically reside in a datacenter are often not considered to be well suited for graphics processing units. This dissertation explores how a popular datacenter application performs on contemporary graphics processing units, highlighting sizable improvements over traditional datacenter hardware. This dissertation then proposes a general software framework for accelerating datacenter applications on graphics processing units, recognizing that all of the computation from receiving a request to sending the reply must be accounted for to achieve the full benefits of the efficient parallel computing hardware. Finally, this dissertation identifies limitations with contemporary graphics processing units and proposes hardware and software enhancements to further improve the usability, performance, and efficiency of graphics processing units in the datacenter.

## Preface

This section lists my publications that were completed at The University of British Columbia, discusses how they are incorporated into this dissertation, and highlights my contributions to this dissertation.

The publications are listed in chronological order as follows:

- [C1] Tayler H. Hetherington, Timothy G. Rogers, Lisa Hsu, Mike O'Connor, Tor M. Aamodt. Characterizing and Evaluating a Key-Value Store Application on Heterogeneous CPU-GPU Systems [69]. In Proceedings of the IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), pp. 88-98, April 2012.

- [C2] Tayler H. Hetherington, Mike O'Connor, Tor M. Aamodt. MemcachedGPU: Scaling-up Scale-out Key-value Stores [70]. In Proceedings of the Sixth ACM Symposium on Cloud Computing (SoCC), pp. 43-57, August, 2015.

Chapter 2. This chapter combines and expands on the material that was presented in [C1] and [C2] to describe the necessary background information for this dissertation.

Chapter 3. A version of this material has been published as [C1]. In [C1], I was the lead investigator responsible for conducting the research and writing the majority of the manuscript under the guidance of Dr. Tor M. Aamodt and with input from Mike O'Connor and Lisa Hsu. Timothy G. Rogers implemented an initial version of the Memcached GPU code, which was targeted towards the GPGPU-Sim software simulator, conducted the corresponding simulator experiments, and wrote the related results sections (Section 3.4.2 and Section 3.4.2). I was responsible for

implementing and evaluating the control-flow simulator, implementing a new version of Memcached targeted towards GPU hardware, conducting the Memcached GPU hardware experiments, analyzing the results, and writing the corresponding portions of the manuscript.

Chapter 4. A version of this material has been published as [C2]. In [C2], I was the lead investigator responsible for conducting the research, implementing the software frameworks, performing the experiments, collecting and analyzing the results, and writing the manuscript under the guidance of Dr. Tor M. Aamodt and with input from Mike O'Connor.

Chapter 5. In this chapter, I was the lead investigator responsible for conducting the research, implementing the proposed event-driven GPU execution programming model and corresponding GPU architectural enhancements in the evaluated software simulation frameworks, conducting the majority of experiments, analyzing the results, and writing the chapter under the guidance of Dr. Tor M. Aamodt. Maria Lubeznov evaluated the performance overheads of concurrent CPU applications and GPU networking workloads and collected the corresponding data. Following this dissertation, a modified version of the material presented in this chapter was published in the International Conference on Parallel Architectures and Compilation Techniques (PACT) 2019 [71].

Chapter 6. This chapter combines and expands on the related work sections that were presented in [C1] and [C2] with the related work in Chapter 5.

## **Table of Contents**

| Ab  | strac                                              | tiii                                                                                                                                                                           |

|-----|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| La  | y Sun                                              | nmary v                                                                                                                                                                        |

| Pre | eface                                              | vi                                                                                                                                                                             |

| Tal | ble of                                             | Contents viii                                                                                                                                                                  |

| Lis | t of T                                             | ables                                                                                                                                                                          |

| Lis | t of F                                             | ïgures                                                                                                                                                                         |

| Lis | t of A                                             | bbreviations                                                                                                                                                                   |

|     |                                                    |                                                                                                                                                                                |

| Ac  | know                                               | ledgments                                                                                                                                                                      |

|     |                                                    | ledgments                                                                                                                                                                      |

|     | dicati                                             |                                                                                                                                                                                |

| De  | dicati                                             | on                                                                                                                                                                             |

| De  | dicati<br>Intro                                    | on                                                                                                                                                                             |

| De  | dicati<br>Intro<br>1.1                             | on       xxv         oduction       1         Computing Trends       2                                                                                                         |

| De  | dicati<br>Intro<br>1.1<br>1.2                      | on       xxv         oduction       1         Computing Trends       2         GPUs and the Datacenter       6                                                                 |

| De  | dicati<br>Intro<br>1.1<br>1.2<br>1.3               | on       xxv         oduction       1         Computing Trends       2         GPUs and the Datacenter       6         Thesis Statement       9                                |

| De  | dicati<br>Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | on       xxv         oduction       1         Computing Trends       2         GPUs and the Datacenter       6         Thesis Statement       9         Contributions       11 |

|   |     | 2.1.1 GPU Programming Model                   | 5 |

|---|-----|-----------------------------------------------|---|

|   |     | 2.1.2 GPU Architecture                        | 7 |

|   |     | 2.1.3 GPU Memory Transfers                    | 1 |

|   |     | 2.1.4 CUDA Dynamic Parallelism                | 2 |

|   |     | 2.1.5 Kernel Priority and Kernel Preemption   | 2 |

|   |     | 2.1.6 Current GPU Interrupt Support           | 3 |

|   |     | 2.1.7 GPU Persistent Threads                  | 4 |

|   |     | 2.1.8 GPU Architectural Irregularities        | 5 |

|   | 2.2 | Memcached                                     | 9 |

|   | 2.3 | Network Interfaces and Linux Networking       | 1 |

|   | 2.4 | Event and Interrupt-Driven Programming    32  | 2 |

| 3 | Eva | luating a Key-Value Store Application on GPUs | 4 |

|   | 3.1 | Porting Memcached                             | 9 |

|   |     | 3.1.1 Offloading GET Requests                 | 9 |

|   |     | 3.1.2 Memory Management                       | 2 |

|   |     | 3.1.3 Separate CPU-GPU Address Space          | 3 |

|   |     | 3.1.4 Read-only Data                          | 4 |

|   |     | 3.1.5 Memory Layout                           | 4 |

|   |     | 3.1.6 SETs and GETs $\ldots$ 4.4              | 5 |

|   | 3.2 | Control-Flow Simulator (CFG-Sim)              | 6 |

|   | 3.3 | Experimental Methodology                      | 8 |

|   |     | 3.3.1 Hardware and Simulation Frameworks      | 8 |

|   |     | 3.3.2 Assumptions and Known Limitations       | 1 |

|   |     | 3.3.3 Validation and Metrics                  | 3 |

|   |     | 3.3.4 WikiData Workload                       | 3 |

|   | 3.4 | Experimental Results                          | 4 |

|   |     | 3.4.1 Hardware Evaluation                     | 4 |

|   |     | 3.4.2 Simulation Evaluation                   | 1 |

|   | 3.5 | Summary                                       | 0 |

| 4 | Mer | mcached GPU                                   | 2 |

|   | 4.1 | GPU Network Offload Manager (GNoM)            | 6 |

|   |     |                                               |   |

|   |     | 4.1.1   | Request Batching                       | 76  |

|---|-----|---------|----------------------------------------|-----|

|   |     | 4.1.2   | Software Architecture                  | 78  |

|   | 4.2 | Memc    | cachedGPU                              | 85  |

|   |     | 4.2.1   | Memcached and Data Structures          | 85  |

|   |     | 4.2.2   | Hash Table                             | 88  |

|   |     | 4.2.3   | Post GPU Race Conditions on Eviction   | 92  |

|   | 4.3 | Experi  | imental Methodology                    | 94  |

|   |     | 4.3.1   | GNoM and MemcachedGPU                  | 95  |

|   |     | 4.3.2   | Hash-Sim (Hash Table Simulator)        | 97  |

|   | 4.4 | Experi  | imental Results                        | 98  |

|   |     | 4.4.1   | Hash Table Evaluation                  | 99  |

|   |     | 4.4.2   | Impact of Linux Kernel Bypass          | 107 |

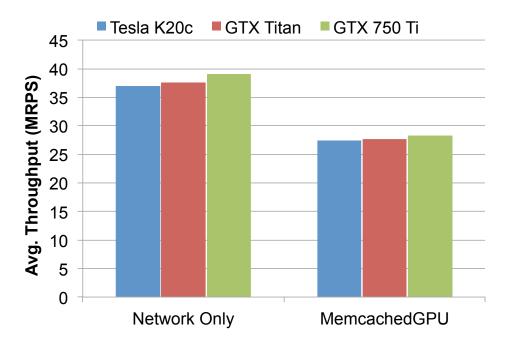

|   |     | 4.4.3   | MemcachedGPU Evaluation                | 108 |

|   |     | 4.4.4   | Workload Consolidation on GPUs         | 115 |

|   |     | 4.4.5   | MemcachedGPU Offline Limit Study       | 118 |

|   |     | 4.4.6   | Comparison with Previous Work          | 121 |

|   | 4.5 | Summ    | nary                                   | 124 |

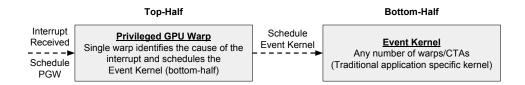

| 5 | EDO | GE: Eve | ent-Driven GPU Execution               | 126 |

|   | 5.1 | Motiva  | ation for Increased GPU Independence   | 127 |

|   | 5.2 | Suppo   | orting Event-Driven GPU Execution      | 132 |

|   | 5.3 | GPU I   | Interrupts and Privileged GPU Warps    | 135 |

|   |     | 5.3.1   | Interrupt Partitioning and Granularity | 137 |

|   |     | 5.3.2   | Privileged GPU Warp Selection          | 138 |

|   |     | 5.3.3   | Privileged GPU Warp Preemption         | 140 |

|   |     | 5.3.4   | Privileged GPU Warp Priority           | 141 |

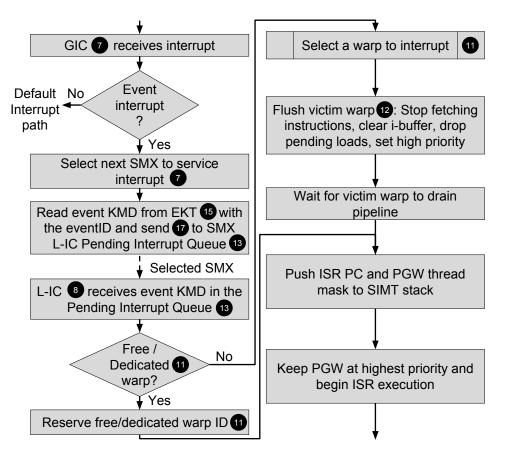

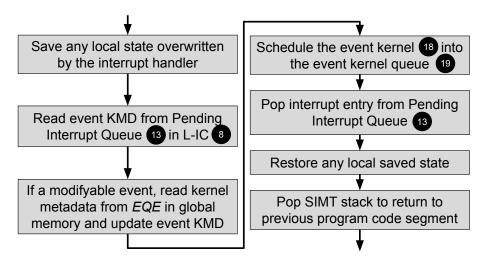

|   |     | 5.3.5   | Interrupt Flow                         | 143 |

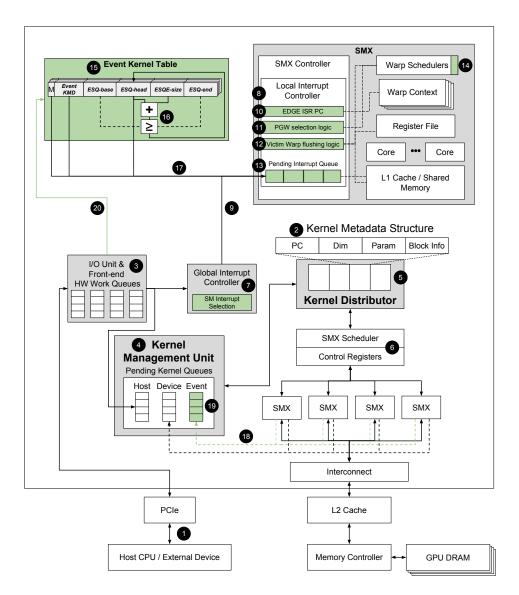

|   |     | 5.3.6   | Interrupt Architecture                 | 143 |

|   | 5.4 | Event-  | -Driven GPU Execution                  | 146 |

|   |     | 5.4.1   | Event Kernels                          | 146 |

|   |     | 5.4.2   | EDGE Architecture                      | 151 |

|   |     | 5.4.3   | Wait-Release Barrier                   | 152 |

|   | 5.5 | Experi  | imental Methodology                    | 156 |

|   | 5.6  | Experi         | imental Results                                                                   | 157        |

|---|------|----------------|-----------------------------------------------------------------------------------|------------|

|   |      | 5.6.1          | GPU Interrupt Support                                                             | 158        |

|   |      | 5.6.2          | Event Kernels                                                                     | 165        |

|   |      | 5.6.3          | Wait-Release Barrier                                                              | 169        |

|   | 5.7  | Summ           | ary                                                                               | 172        |

| 6 | Rela | ted Wo         | ork                                                                               | 174        |

|   | 6.1  | Relate         | ed Work for Accelerating Server Applications and Network                          |            |

|   |      | Proces         | ssing on GPUs                                                                     | 174        |

|   |      | 6.1.1          | Memcached and Server-based Applications                                           | 174        |

|   |      | 6.1.2          | GPU Networking                                                                    | 180        |

|   | 6.2  | Relate         | d Work on Event-Driven GPU Execution and Improving                                |            |

|   |      | GPU S          | System Support                                                                    | 183        |

| 7 | Con  | clusion        | s and Future Work                                                                 | 190        |

|   | 7.1  | Conclu         | usions                                                                            | 190        |

|   | 7.2  | Future         | Research Directions                                                               | 195        |

|   |      | 7.2.1          | Control-Flow Simulator                                                            | 195        |

|   |      | 7.2.2          | Evaluating GNoM on Additional Applications and Inte-                              |            |

|   |      |                | grated GPUs                                                                       | 197        |

|   |      | 7.2.3          | Larger GPU Networking Kernels                                                     | 198        |

|   |      | 7.2.4          | Stateful GPU Network Processing                                                   | 198        |

|   |      | 7.2.5          | Accelerating Operating System Services on GPUs                                    | 199        |

|   |      |                |                                                                                   |            |

|   |      | 7.2.6          | Networking Hardware Directly on a GPU                                             | 199        |

|   |      | 7.2.6<br>7.2.7 | Networking Hardware Directly on a GPUScalar Processors for GPU Interrupt Handling | 199<br>200 |

|   |      |                | · ·                                                                               |            |

|   |      | 7.2.7          | Scalar Processors for GPU Interrupt Handling                                      | 200        |

## **List of Tables**

| Table 1.1 | Comparing GPU and CPU theoretical performance and effi-            |  |

|-----------|--------------------------------------------------------------------|--|

|           | ciency over previous architecture generations. The GPU values      |  |

|           | were obtained from an NVIDIA whitepaper [131]. The CPU             |  |

|           | value were obtained from Intel processor specifications [83] and   |  |

|           | calculated using: FLOPS = number of cores $\times$ peak clock fre- |  |

|           | quency $\times$ flops per cycle                                    |  |

| Table 3.1 | GPU hardware specifications                                        |  |

| Table 3.2 | CPU hardware specifications                                        |  |

| Table 3.3 | GPGPU-Sim configuration                                            |  |

| Table 4.1 | Server and client configurations                                   |  |

| Table 4.2 | Server NVIDIA GPUs                                                 |  |

| Table 4.3 | GET request throughput and drop rate at 10 GbE 108                 |  |

| Table 4.4 | Concurrent GETs and SETs on the Tesla K20c                         |  |

| Table 4.5 | Comparing MemcachedGPU with previous work                          |  |

| Table 5.1 | EDGE API extensions                                                |  |

| Table 5.2 | Gem5-GPU configuration                                             |  |

# **List of Figures**

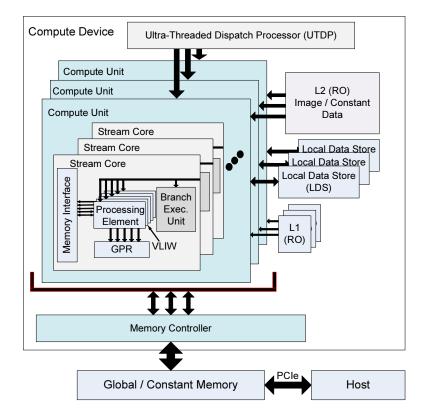

| Figure 2.1 | High-level view of an AMD-like GPU architecture assumed in     |    |

|------------|----------------------------------------------------------------|----|

|            | this dissertation.                                             | 18 |

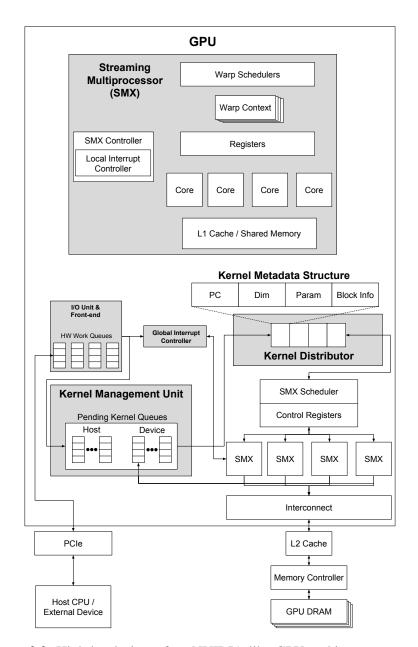

| Figure 2.2 | High-level view of an NVIDIA-like GPU architecture assumed     |    |

|            | in this dissertation.                                          | 19 |

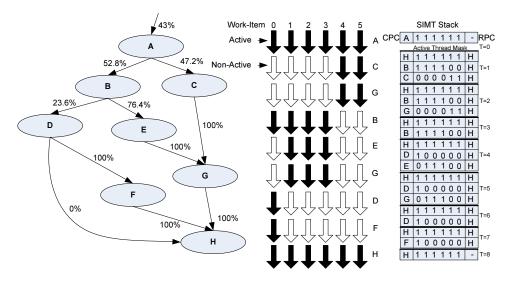

| Figure 2.3 | SIMT execution example.                                        | 26 |

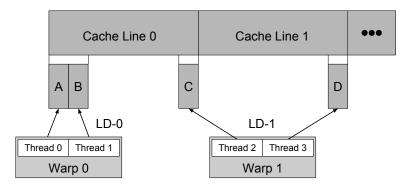

| Figure 2.4 | GPU memory request coalescing                                  | 28 |

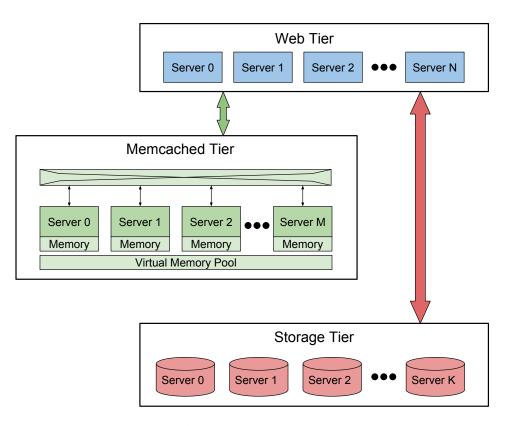

| Figure 2.5 | Memcached.                                                     | 29 |

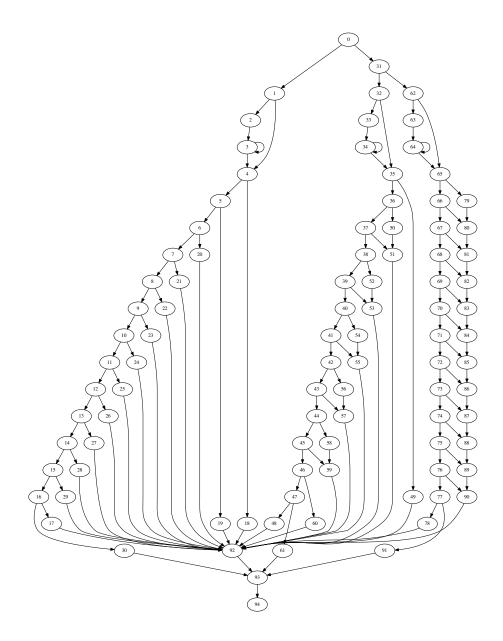

| Figure 3.1 | Control Flow Graph (CFG) from Memcached's Jenkins hash         |    |

|            | function.                                                      | 37 |

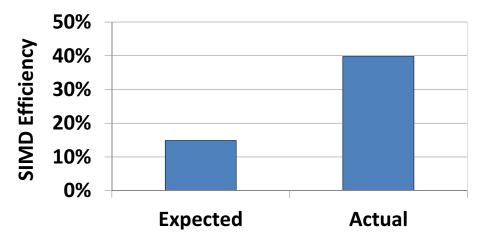

| Figure 3.2 | Memcached SIMD efficiency: Expected vs. Actual                 | 39 |

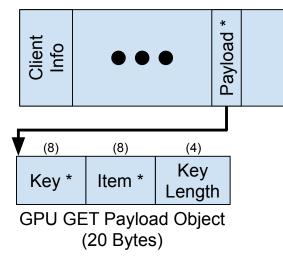

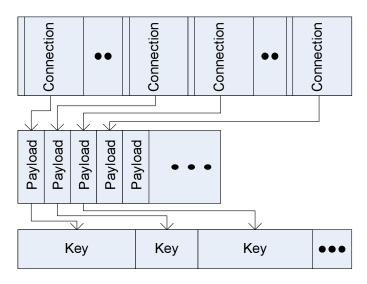

| Figure 3.3 | GPU GET Payload object. The original Memcached Connec-         |    |

|            | tion object contains a large amount of information about the   |    |

|            | current Memcached connect, the requesting client network in-   |    |

|            | formation, and the current state of the Memcached request.     |    |

|            | The GPU Payload object contains a much smaller subset of       |    |

|            | the relevant information required to process the GET request   |    |

|            | on the GPU                                                     | 41 |

| Figure 3.4 | Contiguous memory layout.                                      | 45 |

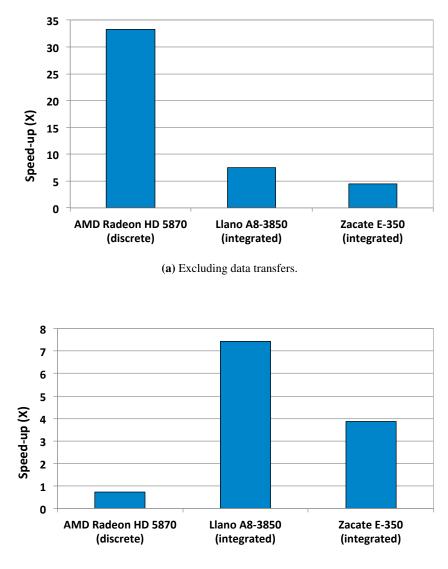

| Figure 3.5 | Memcached speed-up vs. a single core CPU on the discrete       |    |

|            | and integrated GPU architectures. Each batch of GET requests   |    |

|            | contained 38,400 requests/batch                                | 56 |

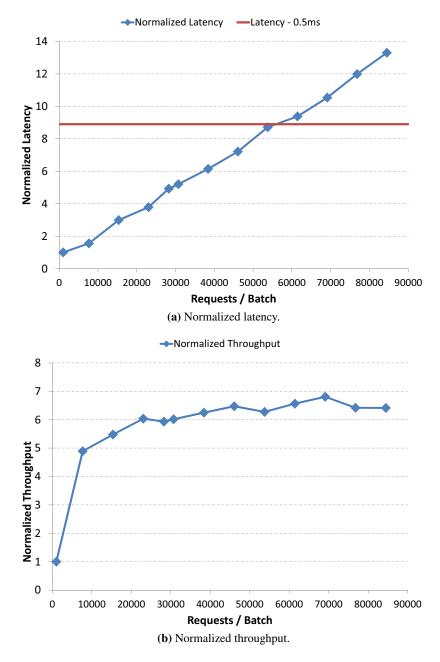

| Figure 3.6 | Throughput and latency while varying the request batch size on |    |

|            | the AMD Radeon HD 5870 (normalized to 1,024 requests/batch).   | 58 |

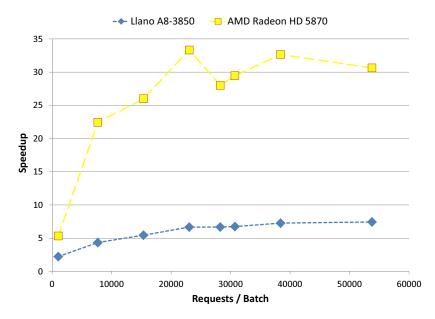

| Figure 3.7  | Speed-up of AMD Radeon HD 5870 and Llano A8-3850 vs.              |    |

|-------------|-------------------------------------------------------------------|----|

|             | the Llano A8-3850 CPU at different request batch sizes            | 59 |

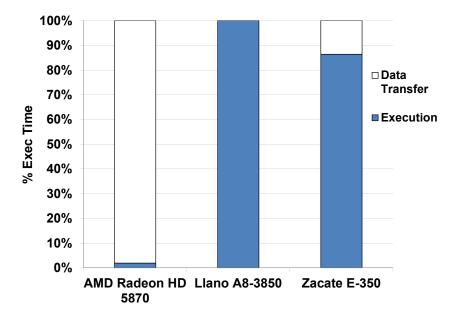

| Figure 3.8  | Memcached overall execution breakdown (23,040 requests/-          |    |

|             | batch)                                                            | 60 |

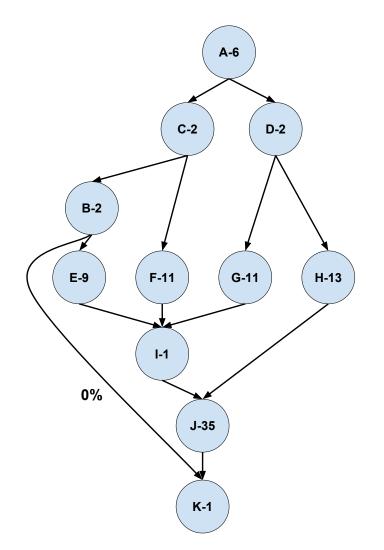

| Figure 3.9  | Example control-flow graph with an error handling branch          |    |

|             | from $B$ to $K$ . Each basic block contains the basic block       |    |

|             | identifier and the number of instructions in that basic block     |    |

|             | (Basic Block ID-# Instructions). All branches have a non-zero     |    |

|             | branch outcome probability except for $B$ to $K$ , which is never |    |

|             | taken                                                             | 62 |

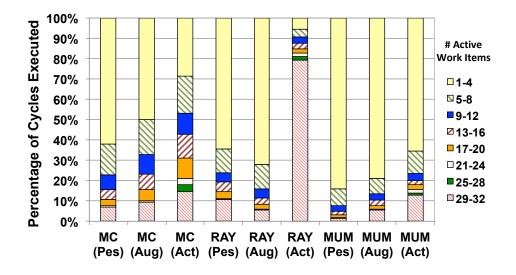

| Figure 3.10 | SIMD efficiency.                                                  | 64 |

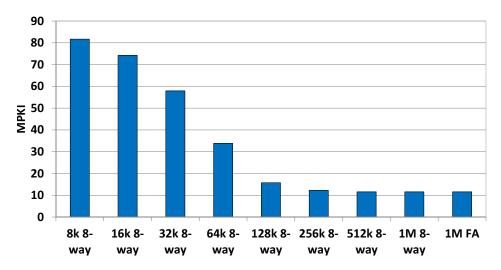

| Figure 3.11 | L1 data cache misses per 1,000 instructions at various config-    |    |

|             | urations. FA = Fully Associative.                                 | 66 |

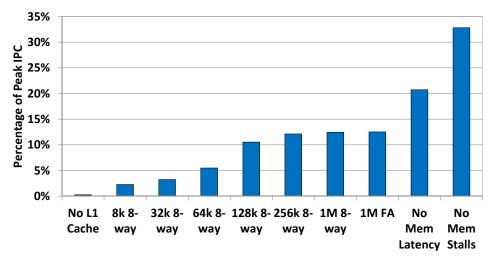

| Figure 3.12 | Performance as a percentage of peak IPC with various realistic    |    |

|             | L1 data cache configurations and two idealized memory systems.    | 66 |

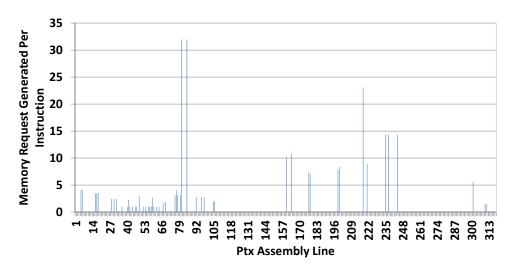

| Figure 3.13 | Memory requests generated per instruction for each static PTX     |    |

|             | instruction                                                       | 68 |

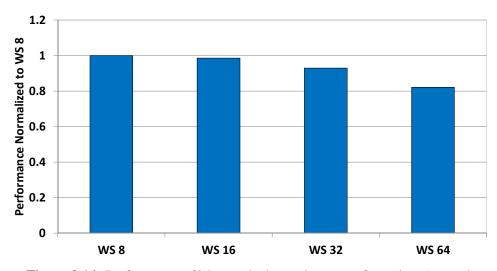

| Figure 3.14 | Performance of Memcached at various wavefront sizes (nor-         |    |

|             | malized to a warp size of 8)                                      | 69 |

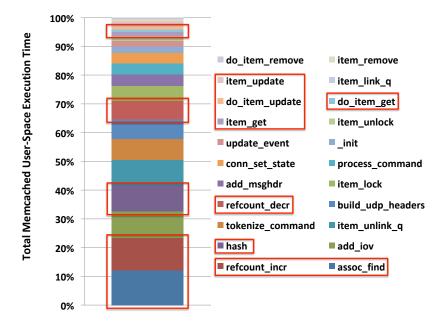

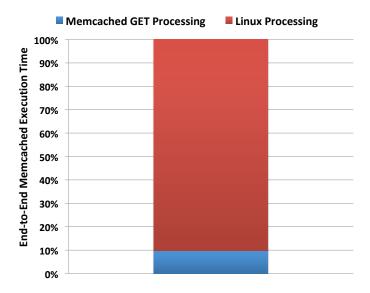

| Figure 4.1  | Breakdown of the baseline Memcached request processing            |    |

|             | time for a single <i>GET</i> request on the CPU                   | 73 |

| Figure 4.2  | End-to-end breakdown of user-space and Linux Kernel pro-          |    |

|             | cessing for a single GET request on the CPU                       | 74 |

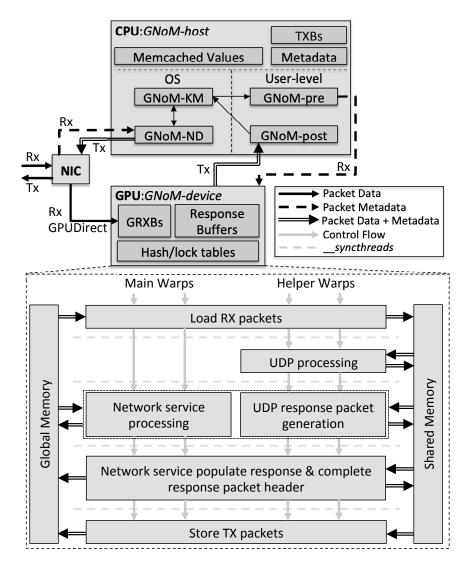

| Figure 4.3  | GNoM packet flow and main CUDA kernel. The figure                 |    |

|             | contains the three main components, the NIC, CPU, and GPU,        |    |

|             | and the corresponding GNoM software frameworks that run           |    |

|             | on each device. The solid black arrows represent data flow, the   |    |

|             | dashed black errors represent metadata flow (e.g., interrupts,    |    |

|             | packet pointers), the double black arrows represent packet        |    |

|             | data and packet metadata, the solid grey arrows represent GPU     |    |

|             | thread control flow, and the dashed grey lines represent GPU      |    |

|             | synchronization instructions.                                     | 77 |

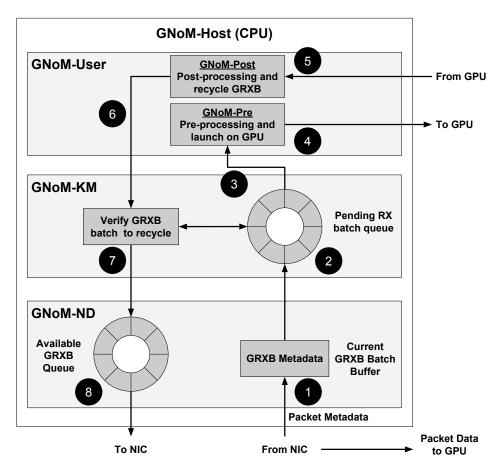

| Figure 4.4  | Software architecture for GNoM-host (CPU)                           | 79  |

|-------------|---------------------------------------------------------------------|-----|

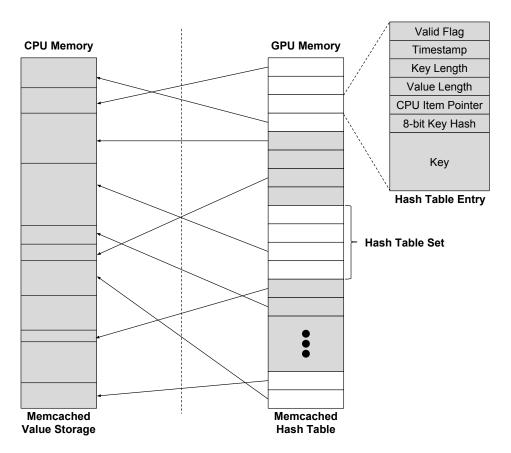

| Figure 4.5  | Partitioning the Memcached hash table and value storage be-         |     |

|             | tween the CPU and GPU.                                              | 86  |

| Figure 4.6  | Race condition between dependent SET and GET requests in            |     |

|             | MemcachedGPU                                                        | 93  |

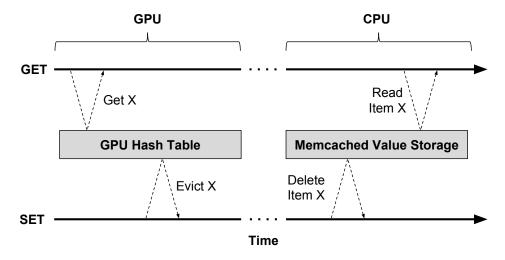

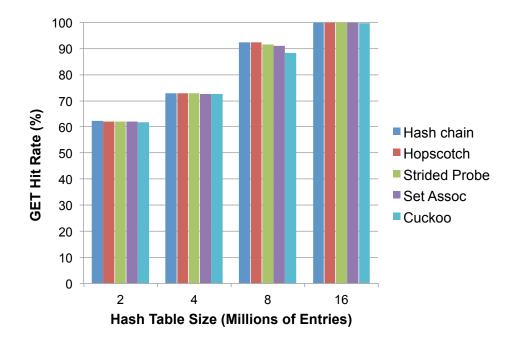

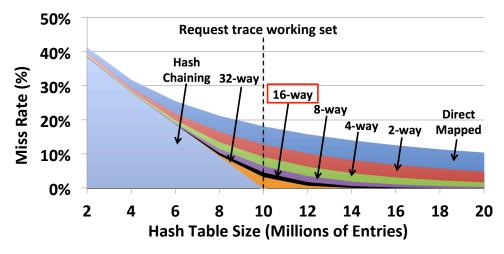

| Figure 4.7a | Zipfian: Comparing the hit rate for different hash table tech-      |     |

|             | niques and sizes under the Zipfian request distribution. The        |     |

|             | request trace working size is 10 million entries                    | 103 |

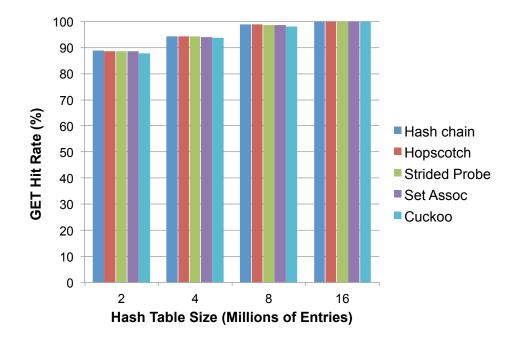

| Figure 4.7b | Latest: Comparing the hit rate for different hash table tech-       |     |

|             | niques and sizes under the Latest request distribution. The re-     |     |

|             | quest trace working size is 10 million entries                      | 104 |

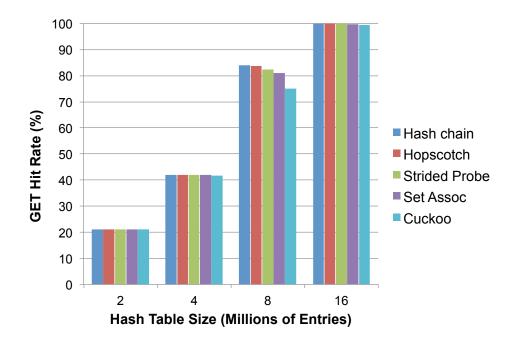

| Figure 4.7c | Uniform Random: Comparing the hit rate for different hash           |     |

|             | table techniques and sizes under the Uniform Random request         |     |

|             | distribution. The request trace working size is 10 million entries. | 105 |

| Figure 4.8  | Miss-rate versus hash table associativity and size compared to      |     |

|             | hash chaining for a request trace with a working set of 10 mil-     |     |

|             | lion requests following the Zipf distribution.                      | 106 |

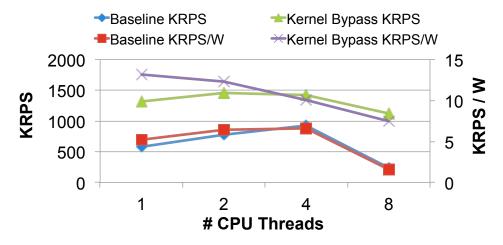

| Figure 4.9  | Impact of Linux Kernel bypass for GET requests vs. the base-        |     |

|             | line Memcached v1.5.20.                                             | 107 |

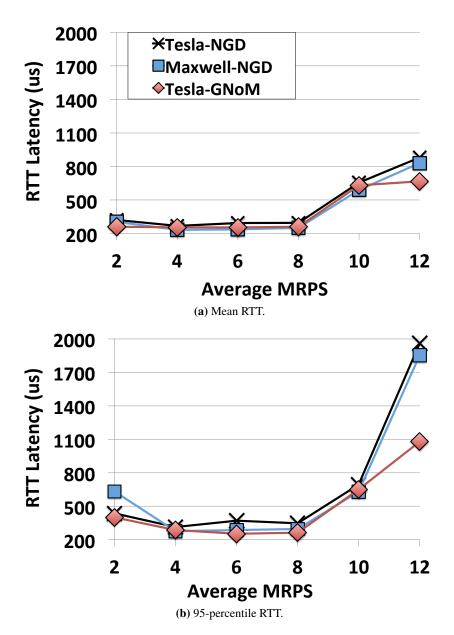

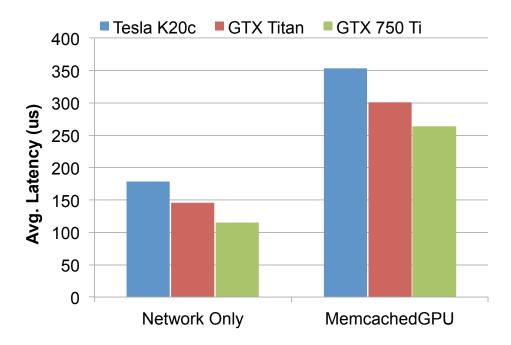

| Figure 4.10 | Mean and 95-percentile round trip time (RTT) latency versus         |     |

|             | throughput for Tesla GPU with GNoM and NGD, and Maxwell             |     |

|             | with NGD.                                                           | 110 |

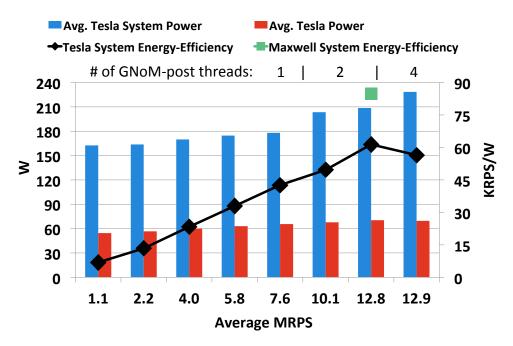

| Figure 4.11 | Total system and GPU power (left axis) and total system             |     |

|             | energy-efficiency (right axis) versus throughput for Mem-           |     |

|             | cachedGPU and GNoM on the NVIDIA Tesla K20c. The                    |     |

|             | total system energy-efficiency for the Maxwell system is also       |     |

|             | shown at the peak throughput with two GNoM-post threads.            |     |

|             | The number of GNoM-post threads are shown above the                 |     |

|             | graph, with 1 thread for 1.1 to 7.6 MRPS, 2 threads for 10.1 to     |     |

|             | 12.8 MRPS, and 4 threads for 12.9 MRPS.                             | 111 |

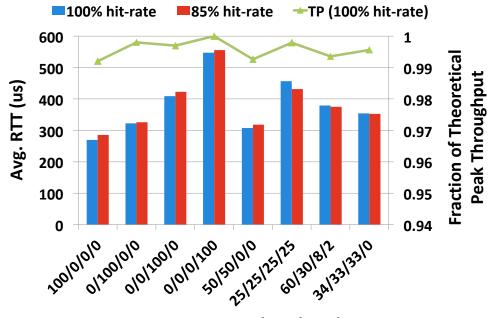

| Figure 4.12 | Impact of varying the key length mixture and hit-rate on round                                   |     |

|-------------|--------------------------------------------------------------------------------------------------|-----|

|             | trip time (RTT) latency (left axis) and throughput (right axis)                                  |     |

|             | for MemcachedGPU and GNoM on the NVIDIA Tesla K20c.                                              |     |

|             | RTT latency is measured at 4 MRPS. Throughput is shown as                                        |     |

|             | the average fraction of peak throughput (at 10 Gbps) obtained                                    |     |

|             | for a given key distribution. The key distributions are broken                                   |     |

|             | down into four sizes (16B, 32B, 64B, and 128B) and the labels                                    |     |

|             | indicate the percentage of keys with the corresponding length.                                   | 113 |

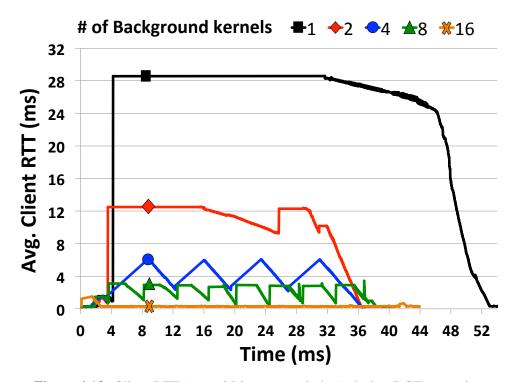

| Figure 4.13 | Client RTT (avg. 256 request window) during BGT execution                                        |     |

|             | for an increasing number of fine-grained kernel launches                                         | 116 |

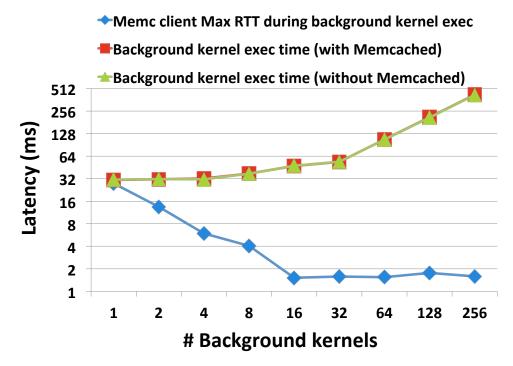

| Figure 4.14 | Impact on BGT execution time with an increasing number of                                        |     |

|             | kernel launches and max client RTT during BGT execution.                                         | 117 |

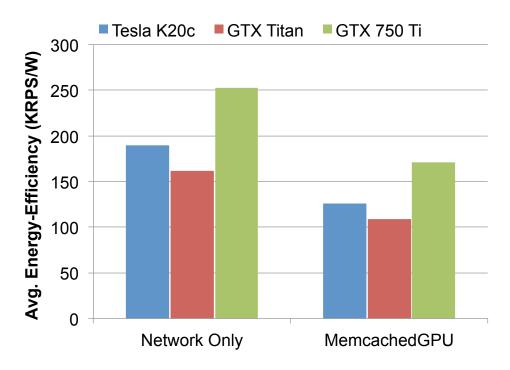

| Figure 4.15 | Offline <i>GNoM</i> throughput - 16B keys, 96B packets                                           | 118 |

| Figure 4.16 | Offline GNoM processing latency - 16B keys, 96B packets                                          | 119 |

| Figure 4.17 | Offline GNoM energy-efficiency - 16B keys, 96B packets                                           | 120 |

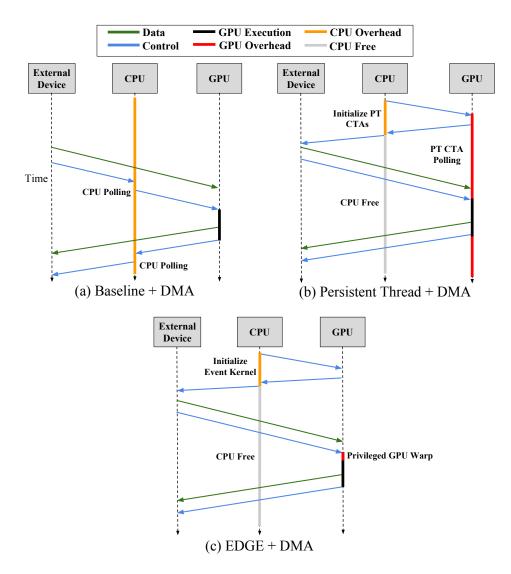

| Eiman 5 1   | Example of the date and control flow when an external device                                     |     |

| Figure 5.1  | Example of the data and control flow when an external device                                     |     |

|             | launches tasks on the GPU for the baseline CUDA streams,<br>Dereistent Threads $(PT)$ and $EDCE$ | 128 |

| Eigung 5 2  | Persistent Threads ( <i>PT</i> ), and <i>EDGE</i>                                                | 128 |

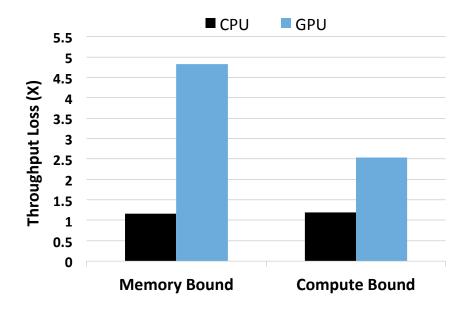

| Figure 5.2  | Evaluating the loss in throughput for CPU compute and mem-                                       |     |

|             | ory bound applications (Spec2006) when running concurrently                                      |     |

|             | with and a GPU networking applications. The GPU's reliance                                       |     |

|             | on the CPU to launch kernels leads to inefficiencies for both                                    | 120 |

| Eigen 5 2   | devices                                                                                          | 129 |

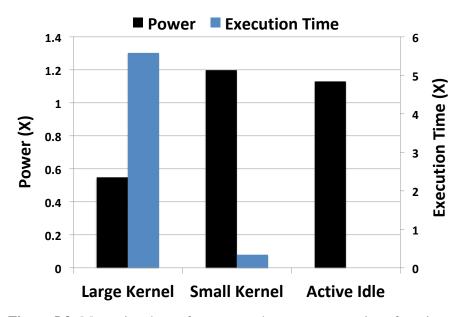

| Figure 5.3  | Measuring the performance and power consumption of persis-                                       |     |

|             | tent threads ( <i>PT</i> ) versus the baseline CUDA stream model for                             |     |

|             | a continuous stream of large and small matrix multiplication                                     |     |

|             | kernels. Active Idle measures the power consumption of the                                       | 120 |

| <b>F</b> '  | polling <i>PT</i> threads when there are no pending tasks                                        | 130 |

| Figure 5.4  | EDGE interrupt partitioning.                                                                     | 137 |

| Figure 5.5  | Interrupt controller logic (reference Figure 5.7)                                                | 142 |

| Figure 5.6  | Interrupt service routine (reference Figure 5.7)                                                 | 144 |

| Figure 5.7  | EDGE GPU Microarchitecture. Baseline GPU diagram in-                                       |     |

|-------------|--------------------------------------------------------------------------------------------|-----|

|             | spired by [87, 111, 155, 175]. EDGE components are shown                                   |     |

|             | in green                                                                                   | 145 |

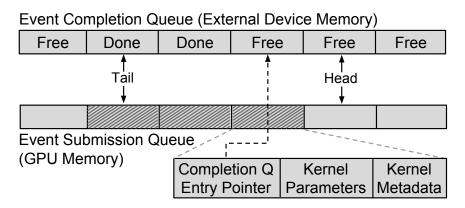

| Figure 5.8  | Event submission and completion queues.                                                    | 147 |

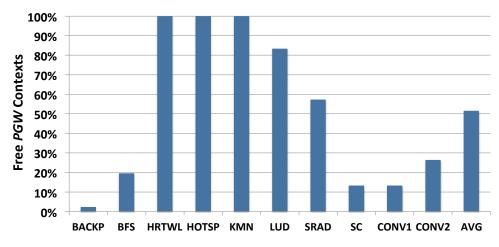

| Figure 5.9  | Percentage of cycles a free warp context is available for                                  |     |

|             | a PGW. This limits the amount of time a warp must be                                       |     |

|             | preempted to schedule the <i>PGW</i>                                                       | 158 |

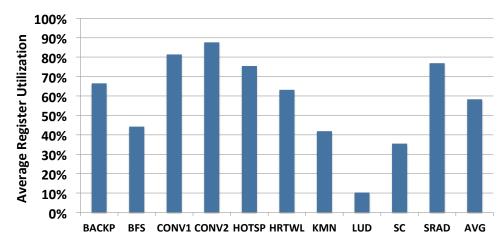

| Figure 5.10 | Average register utilization of Rodinia benchmarks on Gem5-                                |     |

|             | GPU. Register utilization is measured for each cycle and aver-                             |     |

|             | aged across all cycles of the benchmark's execution                                        | 159 |

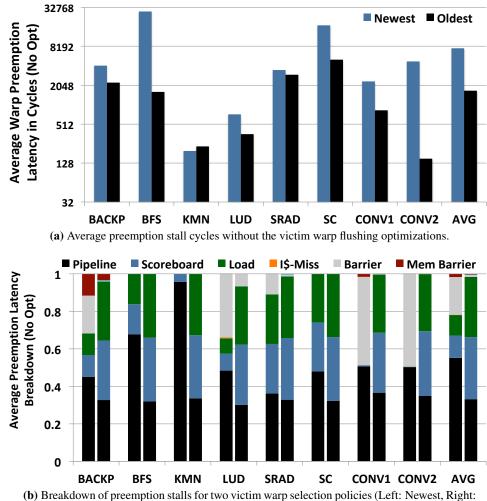

| Figure 5.11 | Interrupt warp preemption stall cycles                                                     | 161 |

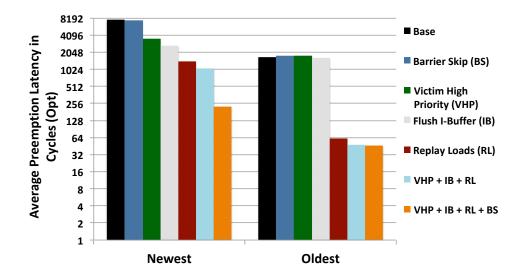

| Figure 5.12 | Preemption stall cycles with the victim warp flushing                                      |     |

|             | optimizations applied averaged across the Rodinia and Con-                                 |     |

|             | volution Benchmarks. Base is the baseline preemption latency                               |     |

|             | without any optimizations applied (Figure 5.11a). Barrier                                  |     |

|             | Skip immediately removes a victim warp if waiting at a barrier.                            |     |

|             | Victim High Priority sets the victim warp's instruction fetch                              |     |

|             | and scheduling priority to the highest. Flush I-Buffer flushes                             |     |

|             | any pending instructions from the victim warp's instruction                                |     |

|             | buffer. Replay Loads drops any in-flight loads from the victim                             |     |

|             | warp and replays them when the victim warp is rescheduled                                  |     |

|             | after the ISR completes.                                                                   | 163 |

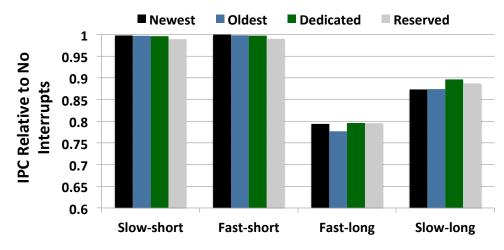

| Figure 5.13 | Average impact of the <i>PGW</i> selection, interrupt rate, and ISR                        |     |

|             | duration on concurrent tasks' IPC (x-axis labels are <i><interrupt< i=""></interrupt<></i> |     |

|             | rate>- <interrupt duration="">)</interrupt>                                                | 164 |

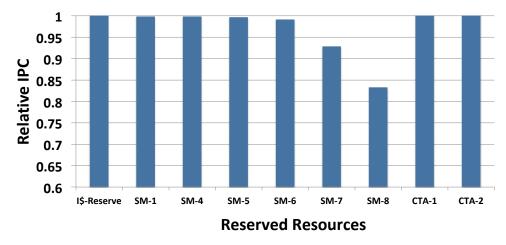

| Figure 5.14 | Impact on the Convolution kernel's IPC when reserving re-                                  |     |

|             | sources for the <i>PGW</i> and MemcachedGPU GET kernel                                     | 165 |

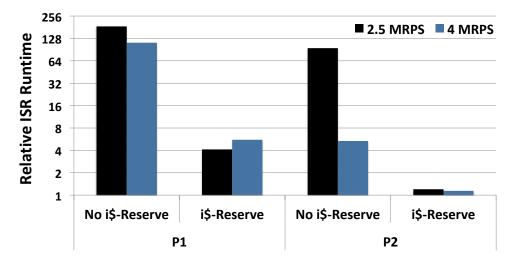

| Figure 5.15 | Average ISR runtime with CONV1 and MEMC kernels at                                         |     |

|             | varying MEMC launch rate relative to a standalone ISR. The                                 |     |

|             | runtime is measured with and without reserving the instruction                             |     |

|             | cache entries for the ISR (i\$-Reserve) and for both the P1 and                            |     |

|             | P2 event kernel priorities. The ISR requires three entries in                              |     |

|             | the instruction cache.                                                                     | 166 |

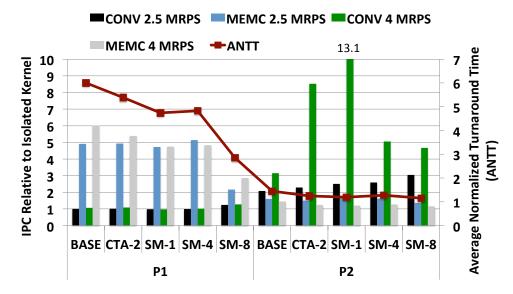

| Figure 5.16 | Runtime of the Convolution and Memcached kernels at dif-       |     |

|-------------|----------------------------------------------------------------|-----|

|             | ferent request rates and resource reservation techniques, rel- |     |

|             | ative to the isolated kernel runtimes, and average normalized  |     |

|             | turnaround time.                                               | 167 |

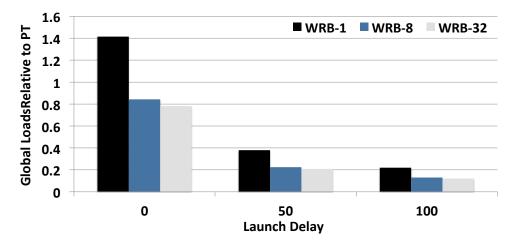

| Figure 5.17 | GPU global load instructions issued relative to Persistent     |     |

|             | Threads ( <i>PT</i> )                                          | 170 |

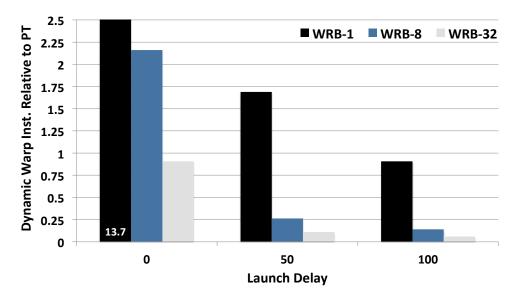

| Figure 5.18 | Dynamic warp instructions issued relative to Persistent        |     |

|             | Threads ( <i>PT</i> )                                          | 171 |

## **List of Abbreviations**

- ALM Adaptive Logic Modules

- API Application Programming Interface

- ASIC Application-Specific Integrated Circuit

- **CDP** CUDA Dynamic Parallelism

- CFG Control Flow Graph

- **CLB** Configurable Logic Blocks

- **CMP** Chip Multiprocessor

- **CPC** Current Program Counter

- **CPU** Central Processing Unit

- CTA Cooperative Thread Array

- **CU** Compute Units

- CUDA Compute Unified Device Architecture

- **DLP** Data-Level Parallelism

- **DMA** Direct Memory Access

- **DNA** Direct NIC Access

- EDGE Event-Driven GPU Execution

- FLOPS Floating-Point Operations Per Second

- FPGA Field-Programmable Gate Array

- GNOM GPU Network Offload Manager

- GPGPU General-Purpose Graphics Processing Unit

- GPU Graphics Processing Unit

- HLS High-Level Synthesis

- HPC High Performance Computing

- IAAS Infrastructure-as-a-Service

- **ILP** Instruction-Level Parallelism

- **IPDOM** Immediate Post Dominator

- **KDU** Kernel Dispatch Unit

- KMD Kernel Metadata Structure

- KMU Kernel Management Unit

- LRU Least Recently Used

- MSI-X Message Signalled Interrupts

- NAPI New API

- NIC Network Interface Card

- PAAS Platform-as-a-Service

- PC Program Counter

- PCIE Peripheral Control Interface Express

- PGW Privileged GPU Warp

- PKQ Pending Kernel Queue

- PT Persistent Threads

- PTX Parallel Thread Execution

- **RDMA** Remote Direct Memory Access

- **RLP** Request-Level Parallelism

- **RPC** Reconvergence Program Counter

- **RPS** Requests per Second

- **RSS** Receive Side Scaling

- **RTT** Round-Trip Time

- **RX** Receive

- SAAS Software-as-a-Service

- SIMD Single-Instruction Multiple-Data

- SIMT Single-Instruction Multiple-Thread

- **SKB** Socket Buffers

- SM Streaming Multiprocessor

- SMX Streaming Multiprocessor

- TCO Total Cost of Ownership

- **TDP** Thermal Design Power

- TLP Thread-Level Parallelism

- TMD Task Meta Data

- TOS Top of Stack

- **TPU** Tensor Processing Unit

- TX Transmit

**UTDP** Ultra Thread Dispatch Processor

VM Virtual Machine

## Acknowledgments

None of this work would have been possible without the support of countless people and organizations. First and foremost, I would like to thank my advisor, Professor Tor Aamodt, for the many years of guidance, support, wisdom, and motivation. Thank you for providing the opportunity to pursue my ideas and helping me to improve them, for your invaluable insights into our field, research, and teaching, for sending me around the world, and for always pushing me to do high-quality research. Your passion and dedication will always be an inspiration to me.

I would especially like to thank my family and friends for helping me throughout this journey. To my father – thank you for everything. You ignited my love for computers; you inspired me to become an Engineer; you taught me that a good scotch with friends is worth the extra weight to carry up a mountain; but most importantly, you are the reason I am the man I am today. To my mother – thank you for all of your love, support, patience, forced breaks, meals, hospital trips, ... the list goes on. You walked with me through the door of my first undergraduate classroom - I am excited to walk off campus with you in the end. To my brother – thank you for your levelheadedness, for always being someone that I can talk to, and for all of the great experiences we have shared. I love that we had the opportunity to work side-by-side throughout our time at UBC and look forward to our many adventures in the future. To my peanut – getting to know you will always be my best memory from UBC. Thank you for your love, for keeping me sane, and for all of your help along the way. I could not have done this without you. Merci. To my grandparents, aunts, uncles, and cousins – thank you for always being there to support me and for helping me to enjoy my other passions. It means so much to me. To my friends - thank you for all of the happiness that you bring to my life and for sticking with me through the countless late nights and "sorry, I can't make it"s.

Thank you to all of the amazing colleagues and co-authors I had the privilege of working with and learning from. Specifically, I would like to thank Mike O'Connor for his invaluable industry knowledge and support, which helped shape my research. To all of the UBC friends I had the pleasure of working with -Wilson Fung, Ali Bakhoda, Tim Rogers, Shadi Assadikhomami, Andrew Boktor, Ahmed ElTantawy, Hadi Jooybar, Ayub Gubran, Dave Evans, Rimon Tadros, Inderpreet Singh, Arun Ramamurthy, Dongdong Li, Amruth Sandhupatla, Maria Lubeznov, Deval Shah, Amin Ghasemazar, Bo Fang, Rohit Singla, Salma Kashani, Hassan Halawa, Jimmy Kwa, Johnny Kuan, Xiaowei Ren, Samer Al-Kiswany, Derick Hsieh, Ryan Jung, Alvin Lam, Dillon Yang, Jimmy Chao, Sheldon Sequeira, Oscar Hou, John Kang, and Chris Eng (and many others) – thank you for making this such a memorable experience. Thank you to all of my colleagues and friends at Oracle Labs who supported me while I finished my PhD. I would also like to thank the members of my qualifying, department, and final university PhD exams, Professor Steve Wilton, Professor Mieszko Lis, Professor Matei Ripeanu, Professor Sathish Gopalakrishnan, Professor Margo Seltzer, Professor Sudip Shekhar, and my external examiner, Professor Emmett Witchel, for their insightful feedback and contributions to improving the work in this dissertation. Additionally, I would like to thank all of the professors I had the opportunity to learn from over the years.

Lastly, I would like to acknowledge the funding sources that made it possible to pursue graduate school – the Natural Sciences and Engineering Research Council of Canada (NSERC) for providing the CGS-D3 and CGS-M, The University of British Columbia for providing multiple awards, and all others who contributed throughout my graduate and undergraduate studies.

To my mother, Roberta Hicklin, and father, Darrin Hetherington.

### **Chapter 1**

## Introduction

Enter the age of computing. Over the past few decades, modern computing systems have rapidly integrated themselves deeply into many aspects of life, ranging from driving research, progressing modern science and medicine, exploring the universe, and managing the world's economy, to playing games, watching our favourite shows, and staying connected with family and friends. Regardless of the task, there is an ever increasing need for higher performance and efficiency.

Improvements in performance enable new classes of applications not previously before possible. Take machine learning and deep learning, for example. In 1957, Cornell Aeronautical Laboratory introduced the concepts of the perceptron and neural networks used for pattern recognition [151]. However, it was nearly 50 years later before deep learning for pattern recognition began its rise [72]. Fastforward to today where large tech companies such as Google [90], Amazon [8], Oracle [138], Microsoft [120], and Facebook [51] employ machine learning and deep learning in many of their computing centers and products. A large contributor to this accelerated growth in deep learning is the improvements in microprocessor performance. However, these performance improvements must be met with increases in energy efficiency to remain feasible as computing systems continue to scale up and scale out [20].

### **1.1 Computing Trends**

Traditionally, the rapid performance improvements of integrated-circuits (IC) in microprocessors has been driven by two main factors: Moore's law [121] and Dennard Scaling [43]. Moore's law states that the number of transistors on an IC will double roughly every 18-24 months, whereas Dennard states that voltage and current, and hence dynamic power, is proportional to the dimensions of the transistor. The combination of these factors enables the transistor switching frequency (clock frequency) on ICs to increase without increasing dynamic power and enables more transistors to fit on an IC within similar size and power constraints. As a result, general-purpose central processing units (CPUs) have enjoyed consistent improvements in single-threaded performance from generation to generation.

However, Dennard scaling has begun to break down over the last decade as we approach the physical limits of transistor sizes and other factors, such as the increasing contribution of transistor leakage current, reduce the ability to continue decreasing power proportionally with smaller transistor sizes. Consequently, powering and cooling the larger number and higher density of transistors on ICs are becoming prohibitively more expensive (referred to as the "power wall" [15, 122]) and has limited the opportunity to continue increasing the clock frequency as a means to improve performance. This has driven many architectural enhancements to utilize the additional transistors, such as exploiting instruction-level parallelism (ILP) through out-of-order processing and branch prediction, to further improve single-threaded performance. While effective, there is only so much parallelism that can be extracted from single-threaded programs, which, along with high memory latencies, limits the potential gains from ILP. This has motivated the microprocessor industry to transition towards parallel computing architectures, such as chip-multiprocessors (CMPs), to combat the diminishing returns in single-threaded optimizations [98].

CMPs consist of multiple independent CPU cores integrated on a single chip, typically sharing portions of the memory system and input/output (I/O) interfaces to communicate with each other and the outside world. CMPs enabled many new opportunities to improve performance over single core systems. Multiple programs can operate concurrently on different cores in a form of spatial mul-

titasking, instead of temporal multitasking on a single core, or individual programs can explicitly define parallel sections of the code to be handled by multiple threads across different cores using parallel application program interfaces (APIs) [19, 84, 94, 109, 133, 137]. Operating systems – privileged system software responsible for the control, management, and security of microprocessor systems – efficiently schedule programs and threads to multiple cores to improve overall system throughput relative to single core systems. Modern CMPs commonly have on the order of 10s of cores and may consist of multiple homogeneous cores, such as Intel's x86 Core-i architectures [167], or heterogeneous cores, such as ARM's big.LITTLE architecture [14]. The trend for adding more cores has continued to push forward as transistor sizes decrease. For example, Intel's Xeon E7 processors contain 24 cores and can be combined in multi-socket server systems for up to 192 cores [81].

However, recent concerns about "dark silicon", in which only a fraction of a chip can be actively utilized within a given power envelope [48, 66, 118], have introduced challenges with multicore scaling to improve performance. This has lead to an increasing focus on specialized accelerators and massively multi-core systems, such as graphics processing units (GPU), field-programmable gate-arrays (FPGA), and application-specific integrated-circuits (ASIC). Such architectures can provide very high levels of performance and efficiency for specific classes of applications, but may give up the flexibility and programmability inherent in general-purpose processors. ASICs are at the extreme end of this scale, providing dedicated hardware solutions to specific operations and applications at the cost of generality and programmability. In contrast to general-purpose processors, which often require multiple steps to perform a single operation to maintain a level of generality, ASICs can directly implement the operation efficiently in hardware. However, while ASICs may contain a level of programmability, they are tied to a specific class of applications and cannot easily evolve with the application. Additionally, ASICs require hardware design and implementation, which increase the complexity and cost relative to software-only solutions.

FPGAs, on the other hand, fall in the middle of the scale as reprogrammable hardware devices. Internally, FPGAs contain many reconfigurable hardware blocks capable of implementing any logic function, dedicated hardware blocks,

I/O blocks, and a reconfigurable interconnection fabric for connecting these components [7, 113, 114, 180]. The FPGA architecture enables high levels of performance and efficiency for certain applications, but the reprogrammability reduces the benefits relative to ASICS [100]. FPGAs are programmed using hardware design languages (HDL), such as Verilog or VHDL, and can be reprogrammed to evolve with changing applications. However, programming in an HDL is still considerably more difficult than programming in software [154] and reprogramming times can be on the order of milliseconds to seconds [142, 147], which imposes challenges when implementing multitasking on FPGAs. While the ease of programming has improved on recent FPGAs with support for higher-level software languages through high-level synthesis (HLS), such as OpenCL [36] and CUDA [142], current HLS solutions tend to achieve improvements in developer productivity by trading off the quality of results [12].

GPUs, the focus of this dissertation, are massively multi-threaded, many-core, throughput-oriented architectures traditionally designed to accelerate graphics applications. Graphics processing often involves performing multiple thousands of similar and independent computations on different pixels, resulting in large amounts of data-level parallelism (DLP). GPUs exploit this parallelism by concurrently executing multiple independent operations on a single-instruction, multiple-data (SIMD) architecture to provide significant gains in performance and efficiency. Fortunately, this property of high DLP is not exclusive to graphics applications. Over the past decade, GPUs have evolved into general-purpose GPUs (GPGPU), increasing the scope of applications that can benefit from the GPU's high-efficiency architecture to non-graphics applications with sufficient DLP. Contemporary GPGPUs are programmed in high-level, parallel software languages, such as CUDA or OpenCL.

At their core, GPGPUs consist of hundreds to thousands of small, lowfrequency, in-order cores grouped together into SIMD processing engines, commonly referred to as streaming multiprocessors (SMs) or compute units (CU), and high-bandwidth memory (the GPGPU architecture and programming model are described in detail in Section 2.1). Unlike CPUs, which aim to improve performance through high clock frequencies and aggressive ILP optimizations, GPUs focus on exploiting fine-grained multi-threading (FGMT). Assuming

**Table 1.1:** Comparing GPU and CPU theoretical performance and efficiency over previous architecture generations. The GPU values were obtained from an NVIDIA whitepaper [131]. The CPU value were obtained from Intel processor specifications [83] and calculated using: FLOPS = number of cores  $\times$  peak clock frequency  $\times$  flops per cycle.

| Architecture (Year)             | IC fab.              | TDP | GFLOPS | GFLOPS/W |

|---------------------------------|----------------------|-----|--------|----------|

| GPU NVIDIA Volta ('17)          | 12nm<br>FFN          | 300 | 15,700 | 52.3     |

| GPU NVIDIA Pascal ('16)         | 16nm<br>Fin-<br>FET+ | 300 | 10,600 | 35.3     |

| GPU NVIDIA Maxwell ('15)        | 28nm                 | 250 | 6,800  | 27.2     |

| GPU NVIDIA Kepler ('13)         | 28nm                 | 235 | 5,000  | 21.3     |

| CPU Intel 8th gen core i9 ('18) | 14nm                 | 45  | 921.6  | 20.5     |

| CPU Intel 8th gen core i7 ('18) | 14nm                 | 45  | 825.6  | 18.3     |

| CPU Intel 7th gen core i7 ('17) | 14nm                 | 45  | 524.8  | 11.7     |

| CPU Intel 6th gen core i7 ('16) | 14nm                 | 45  | 473.6  | 10.5     |

ample amounts of structured parallelism in the application, FGMT can hide the effects of long latency operations by seamlessly switching between thousands of concurrently operating GPU thread contexts. Coupled with the lower clock frequency, FGMT trades off single-threaded performance with high throughput processing to improve overall performance and energy-efficiency.

Consider the comparison in Table 1.1, which presents the theoretical peak performance and energy-efficiency of different NVIDIA GPUs and Intel CPUs across multiple generations. The table also presents the IC fabrication process and year the processor was released. Performance is measured in billions of single-precision floating-point operations per second (GFLOPS) and energy-efficiency is measured in peak GFLOPS versus the thermal design power (TDP) (GFLOPS/W). As can be seen, the latest NVIDIA Volta GPU (GV100) provides over  $17 \times$  the compute throughput and  $2.6 \times$  higher energy-efficiency than the latest Intel CPU (Core i9-8950HK). While the Volta has a superior technology fabrication process, even the Maxwell and Kepler architectures with twice the transistor size are able to provide higher performance and energy-efficiency than the latest Intel CPU. However, there are many limitations in the properties of applications that can actually benefit from GPU acceleration, which introduces challenges with exploiting the available parallelism offered by the GPU architecture. This dissertation argues that the perceived bar for the types of applications that can obtain benefits from the GPU is often too high and that GPUs should be considered as efficient accelerators for a broader class of applications. Specifically, this dissertation explores the potential for using GPUs to improve the performance and efficiency of datacenter applications containing ample request-level (packet-level) parallelism, using Memcached [115] (Section 2.2) as an example.

### **1.2 GPUs and the Datacenter**

The initial applications to pioneer the road for GPGPU computing belonged to the domain of scientific and high-performance computing (HPC) and were able to attain large performance improvements using GPUs [59]. These types of applications are highly structured and well suited for the GPU's SIMD architecture. Furthermore, the GPU is able to match these high levels of performance with efficiency. In fact, as of June 2017, GPUs were used as accelerators in all ten of the top ten most efficient supercomputers (GFLOPS/W), as indicated by the Green500 list [165], while also appearing in two out of the top five supercomputers (TFLOPS) [166]. However, HPC represents a relatively small segment of the overall computing market. According to the IDC, in 2015 the overall server market, such as those found in a datacenter (described below), had revenues of \$55.1 billion [78] compared to \$11.4 billion for HPC servers [25, 53], which has been a consistent trend over the previous six years (\$43.2 billion [76] for the overall server marked compared to \$8.6 billion [77] for HPC in 2009). Consequently, improving the performance and efficiency of datacenter applications can have significant economic benefits.

Modern datacenters are massive buildings containing thousands of servers, memory, non-volatile storage, network hardware, and power and cooling systems. Server-side ("cloud") computing in datacenters has become an increasingly popular computing environment with the growth in Internet services and provides many benefits relative to independently managing custom computing resources [20]. Datacenters offer large amounts of computing potential, services, scalability, security, and reliability guarantees, which enable vendors and customers to easily deploy, manage, and tailor the computing environment to their applications' needs. Services such as Software-as-a-Service (SaaS), Platform-as-a-Service (PaaS), and Infrastructure-as-a-Service (IaaS) provide varying levels of control for, and support of, the software and hardware resources within the datacenter [6]. Additionally, computing resources can be shared across multiple applications, known as workload consolidation, which improves efficiency through higher utilization and reduces costs for both vendors and customers [20, 105].

Datacenters also simplify the development and maintenance of software. Software vendors can frequently and transparently distribute updates to applications running in the datacenter on known software and hardware configurations, instead of distributing updates to a variety of different types of client hardware and software systems [20]. Furthermore, existing applications tend to be frequently updated and new datacenter applications with varying processing requirements are rapidly deployed, referred to as workload churn, which places generality and flexibility requirements on the hardware resources to be able to support the continuously evolving applications.

Together, the hardware resources in the datacenter can consume tens of megawatts [20]. Reducing energy consumption is therefore a key concern for datacenter operators. At the same time, typical datacenter workloads often have strict performance requirements, which makes obtaining higher energy efficiency through "wimpy" nodes [11] that give up single-threaded performance nontrivial [73, 147]. Additionally, high workload churn introduces challenges with deploying high-efficiency ASICs to accelerate datacenter applications, as the hardware has been specifically designed for a certain class of applications. Consequently, datacenters have traditionally relied on general-purpose processors as the main computing resources. Recently, however, the use of specialized processors in the datacenter to address performance and efficiency limitations has been growing. For example, Facebook's Big-Basin [103] utilizes racks of tightly coupled discrete GPUs for improving machine learning performance; Google uses GPUs [39] and custom Tensor Processing Units (TPU) [90] for improving machine learning performance; and Microsoft uses FPGAs for Bing web search [147] and hardware microservices [27], such as encryption [29]. Along with an increase

in specialized accelerators, datacenters have begun to shift towards rack-scale computing [82], where communicating components in a disaggregated computing [107] system reside in separate racks to increase utilization and efficiency. In such an environment, applications reserve only the resources they require (e.g., computing resources, accelerators, memory, storage), as opposed to underutilizing over-provisioned servers. In order to be effective, the communication overhead between components in separate racks must be minimized.

As highlighted above, GPUs are becoming commonplace accelerators in datacenters. One of the key reasons for this is the GPU's ability to provide very high levels of performance and energy-efficiency. However, the classes of applications taking advantage of the GPUs are limited and, for example, frequently marketed towards machine learning and scientific computing [61]. While these applications have been the driving force for the inclusion of GPUs in the datacenter, there is a large fraction of more traditional datacenter applications, such as web services and databases, that are not often considered for GPU acceleration. This dissertation asks the question, can these types of network-centric applications also benefit from the high performance and efficiency provided by contemporary GPUs? These types of server applications typically contain large amounts of thread-level (TLP) or request-level (RLP) parallelism [98]. For example, Facebook uses an in-memory web caching service, Memcached [115], to alleviate network traffic to expensive backing databases, which is responsible for handling billions of network requests per second (RPS) across multiple servers [124]. This results in significant amounts of parallelism across network requests. However, there are many challenges with exploiting this available parallelism on contemporary GPUs due to the irregular behavior associated with the network-centric server applications.

First, while multiple network requests may perform the same high-level operation in parallel, such as retrieving a piece of data from the server, there may be drastically different types or amounts of operations performed within the request. For example, varying network packet sizes can result in a different number of iterations to process, or different packet contents may trigger additional levels of processing. This leads to decreased utilization and efficiency on the GPU's SIMD architecture (Chapter 2 and Chapter 3). Second, the data access patterns across multiple similar network requests can not be known a priori and may be highly distributed across the GPU's memory. This decreases the memory bandwidth utilization, reducing both performance and efficiency (Chapter 2 and Chapter 3). Third, networkbased server applications tend to have strict latency constraints [41], which is complicated by the GPU's high-throughput oriented architecture with relatively low single-threaded performance. Additionally, GPUs require large amounts of parallel computation to provide the high levels of performance and efficiency. This translates to network request batching, and hence increased latency, when accelerating network requests on the GPU (Chapter 4). Fourth, because network requests are coming off of the network, an efficient framework is required to manage the data and computation movement across communicating components within the heterogeneous environment (Chapter 4). Fifth, network packet processing in current operating systems can contribute to a large fraction of the total end-to-end network application latency. Without also considering the network processing, the benefits of using a GPU for the remaining application processing are limited by Amdahl's law (a measure of the total potential performance gains given the fraction of total computation able to be parallelized) (Chapter 4). Finally, contemporary GPUs are considered as offload accelerators, which traditionally rely on the CPU for managing the launching and completion of GPU tasks. As a result, even if the GPU is responsible for all of the network and application processing, the CPU must still be involved on the critical path using the standard GPU programming interfaces. This increases programming complexity, reduces performance and efficiency, and unnecessarily reduces the ability for the CPU to concurrently work on other tasks (Chapter 5). Each of these challenges must be addressed to obtain any benefits from GPU acceleration of datacenter applications.

### **1.3 Thesis Statement**

This dissertation explores the potential to utilize GPUs as energy-efficient accelerators for server-based applications in the datacenter through a software-hardware co-design. Datacenters are important and ubiquitous computing environments with strict requirements for high performance, high efficiency, and generality. While general-purpose GPUs are capable of providing significant gains in both performance and efficiency for certain applications, traditional server-based applications do not often adhere to the specific properties expected of an application to obtain the benefits offered by the GPU. This dissertation highlights that the GPU can be used to accelerate such applications through a top-down approach – evaluating the behavior of a popular datacenter application (Memcached) on contemporary GPU hardware and proposing a full end-to-end software stack for accelerating network services on contemporary GPUs – and a bottom-up approach – proposing a novel hardware mechanism and modifications to the GPGPU programming model to improve the independence, efficiency, and programmability of GPUs in a heterogeneous system, such as the datacenter.

This dissertation first performs a detailed characterization and evaluation of Memcached, a high-performance distributed key-value store application, on contemporary GPUs. Compared to traditional GPGPU applications, Memcached is highly irregular in terms of control flow and data access patterns. From an initial evaluation, it might reasonably appear that such an application would perform poorly on a GPU. This dissertation highlights that even in light of the irregular behavior, an application such as Memcached can be redesigned to take advantage of the GPU's high computational capacity and memory bandwidth to achieve improvements in request throughput. Additionally, this dissertation assists with understanding the potential SIMD utilization of an irregular application on a GPU, prior to actually spending the time to implement the application on a GPU, through the use of a custom control-flow simulator.

However, the actual server application processing is only part of the full endto-end processing required to service a network request. For example, the network packet processing is performed in the operating system on the CPU prior to the server application. As a result, the gains achieved by offloading only the application processing to the GPU are limited by Amdahl's law. This dissertation proposes a complete end-to-end software framework, GPU Network offload Manager (*GNoM*), for offloading both the network and server application processing to the GPU. *GNoM* addresses many of the challenges with achieving high-throughput, low-latency, and energy-efficient processing on the GPU's throughput-oriented architecture, facilitating the development of server-based applications on contemporary GPU and Ethernet hardware.

Using GNoM, this dissertation proposes MemcachedGPU, an end-to-end im-

plementation of Memcached on a GPU. Multiple components in Memcached are redesigned to better fit the GPU's architecture and communicating components in a heterogeneous environment. MemcachedGPU is evaluated on both high-performance and lower power GPUs and is capable of reaching 10 Gbps line-rate processing with the smallest Memcached request size (over 13 million requests per second (MRPS)) at efficiencies under 12 *u*J per request. Furthermore, MemcachedGPU provides a 95-percentile round-trip time (RTT) latency under 1.1ms at peak throughputs. Together, *GNoM* and MemcachedGPU highlight the GPU's potential for accelerating such server-based applications.

GNoM aims to offload all of the network and application processing to the GPU. However, contemporary GPUs are often considered as second-class computing resources, which require interactions with the host CPU to manage the launching and completion of tasks on the GPU. As a result, even if all of the required endto-end processing can be performed on the GPU, the CPU is still required to handle I/O and control between GPU and other third-party devices, such as the network interface. This dissertation proposes an event-driven GPU programming model and corresponding hardware modifications, EDGE, to enable any device in a heterogeneous system to manage the execution of GPU tasks. EDGE pre-registers tasks on the GPU and utilizes fine-grained preemption to execute privileged threads capable of triggering the execution of these tasks. *EDGE* exposes the GPU's interrupt interface to completely bypass the CPU, which improves performance and efficiency, reduces system complexity, and frees up the CPU to work on other tasks. This dissertation also proposes a new GPU barrier instruction, the *wait-release barrier*, which blocks GPU threads indefinitely until being released by the privileged GPU threads in response to an event. The wait-release barriers can help to reduce the overheads of persistently running GPU software frameworks, which continuously poll in-memory work queues for new tasks.

### **1.4 Contributions**

This dissertation makes the following contributions:

1. It argues that GPU's should be considered as accelerators for datacenter network services with ample request-level parallelism by contrasting a pro-

grammer's intuition of an application's potential execution behavior on a GPU with the actual behavior, highlighting that the appearance of irregular control-flow and data-access patterns do not necessarily result in negative performance on a GPU.

- 2. It describes the methodology used to port Memcached to run on integrated CPU-GPU and discrete GPU architectures, focussing on GPU-only performance with minimal modifications to Memcached's internal implementation and data structures.

- 3. It characterizes and evaluates Memcached on both integrated CPU-GPU and discrete GPU architectures. To provide deeper insights, this dissertation evaluates the behavior of Memcached on a cycle-accurate GPGPU simulator [1].

- 4. It presents the initial design of a control flow simulator, CFG-Sim, which can assist GPGPU developers in understanding the potential GPU SIMD utilization of an application prior to actually porting the application to a GPU.

- 5. It presents *GNoM* (GPU Network Offload Manager), a software system for efficient UDP network and application processing on GPUs, and evaluates the feasibility of achieving low-latency, high-throughput (10 GbE line-rate), and energy-efficient processing at any request size on commodity Ethernet and GPU hardware.

- 6. It describes the design of MemcachedGPU, an accelerated key-value store that leverages *GNoM* to run efficiently on a GPU, and addresses the challenges associated with partitioning a key-value store across heterogeneous processors. Compared to the initial GPU version of Memcached, MemcachedGPU optimizes for both throughput and latency in a full end-to-end design. Additionally, this dissertation compares MemcachedGPU against prior accelerated Memcached implementations.

- 7. It explores the potential for workload consolidation on GPUs during varying client demands while maintaining a level of QoS for a higher priority GPU network-based application.

- 8. It highlights the limitations with contemporary GPUs being considered as second-class computing resources and discusses the need for increased independence of such accelerators to improve performance and efficiency in the datacenter. To this end, this dissertation proposes *EDGE*, an event-driven programming model, API, and corresponding GPU hardware modifications to enable increased GPU independence for applications that primarily use the GPU.

- 9. It proposes and evaluates a fine-grained, warp-level (Section 2.1.1) GPU interrupt and preemption mechanism, which triggers a set of privileged GPU warps (*PGWs*) from any device in a heterogeneous system through *EDGE* for initiating and managing tasks internally on the GPU.

- 10. It proposes a new GPU barrier instruction, the wait-release barrier, which halts the execution of specific GPU threads indefinitely until being released by an event, and highlights the benefits of the wait-release barrier to reduce the polling overheads of a persistent GPU thread style of programming.

- 11. It evaluates *EDGE* in a multiprogrammed environment and highlights the ability to achieve the performance and simplicity of the baseline CUDA programming model with the flexibility of software-only workarounds aimed to increase the independence of GPUs.

# 1.5 Organization

The rest of this dissertation is organized as follows:

- Chapter 2 discusses the relevant background information for this dissertation, such as the GPU architecture and programming models evaluated in this study, the Memcached key-value store application, networking, and the event-driven programming model.

- Chapter 3 presents the initial evaluation into porting Memcached, an irregular key-value store datacenter application, to both integrated and discrete GPU hardware, and provides deeper insights into the behavior of Memcached on a GPU via a GPGPU simulator.

- Chapter 4 tackles the challenges with implementing Memcached on a GPU in a complete end-to-end system. This chapter proposes *GNoM*, a software framework for accelerating both network and application processing for network-based applications on contemporary GPU hardware. This chapter then presents the end-to-end design and implementation of MemcachedGPU, which utilizes *GNoM* to achieve 10 GbE line-rate processing for any Memcached packet size on both high-performance and low-power discrete GPUs. This chapter also highlights the potential for workload consolidation on GPUs in the datacenter while maintaining a level of QoS for high-priority network applications.

- Chapter 5 identifies limitations with the current system and architectural support for considering GPUs as first-class computing resources in a heterogeneous environment, which rely on the CPU to act as the middleman for control and task management. This chapter proposes *EDGE*, an event-driven programming model and corresponding modifications to the GPU architecture, to enable third-party devices in a heterogeneous environment to directly manage tasks on the GPU.

- Chapter 6 discusses the related work for this dissertation.

- Chapter 7 concludes this dissertation and discusses directions for future work.

# **Chapter 2**

# Background

This chapter presents the relevant background information for this dissertation. It first describes the GPU programming model, details two GPU architectures evaluated throughout this research, and discusses irregularities that arise in the GPU thread control-flow and memory systems. This chapter then discusses GPU system-level frameworks and current support for interrupts on GPUs. Next, this chapter details a key-value store application, Memcached, which is evaluated throughout this dissertation. Finally, this chapter provides an overview of the relevant networking and event-driven programming background.

# 2.1 Graphics Processing Units (GPUs)

This section details the contemporary GPU programming model and GPU architectures assumed in this dissertation.

## 2.1.1 GPU Programming Model

GPUs are high throughput-oriented offload accelerators traditionally designed for graphics. GPUs have since evolved into general-purpose processors, namely general-purpose graphics processing units (GPGPUs), capable of providing high-throughput, energy-efficient processing for data parallel software, such as high-performance computing (HPC). In this dissertation, the terms GPUs and GPGPUs are used interchangeably.