## A Model for Thread and Memory Placement on NUMA Systems

by

#### Justin Funston

B.Sc. Computer Science, Gonzaga University, 2010

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### **Doctor of Philosophy**

in

# THE FACULTY OF GRADUATE AND POSTDOCTORAL STUDIES

(Electrical and Computer Engineering)

The University of British Columbia (Vancouver)

January 2018

© Justin Funston, 2018

## **Abstract**

The problem of placement of threads, or virtual cores, on physical cores in a multicore system has been studied for over a decade. Despite this effort, we still do not know how to assign virtual to physical cores on a non-uniform memory access (NUMA) system so as to meet a performance target while minimizing resource consumption. Prior work has made large strides in this area, but these solutions either addressed hardware with specific properties, leaving us unable to generalize the models to other systems, or modeled much simpler effects than the actual performance in different placements.

An interdependent problem is how to place memory on NUMA systems. Poor memory placement causes congestion on interconnect links, contention for memory controllers, and ultimately long memory access times and poor performance. Commonly used operating system techniques for NUMA memory placement fail to achieve optimal performance in many cases.

Our contribution is a general framework for reasoning about workload placement and memory placement on machines with shared resources. This framework enables us to automatically build an accurate performance model for any machine with a hierarchy of known shared resources. Using our methodology, data center operators can minimize the number of NUMA (CPU+memory) nodes allocated for an application or a service, while ensuring that it meets performance objectives. More broadly, the methodology empowers them to efficiently "pack" virtual containers on the physical hardware. We also present an effective solution for placing memory that avoids congestion on interconnects due to memory traffic and additionally selects the best page size that balances translation lookaside buffer (TLB) effects against more granular memory placement. The solutions proposed can sig-

nificantly improve performance and work at the operating system level so they do not require changes to applications.

## Lay Summary

Modern server-class computer hardware is becoming increasingly complex as hardware designers scale core counts. This hardware runs important applications like scientific simulations, databases, and machine learning, and represents a significant portion of the worlds electricity usage. Software must be carefully designed and optimized to get the most out of such hardware, otherwise performance can suffer and energy is wasted. This work presents insights and analysis into how software interacts with modern server-class hardware, and proposes techniques and algorithms to automatically optimize software for it. The solutions proposed can significantly improve performance and work at the operating system level so they do not require changes to applications.

## **Preface**

The research chapters of this dissertation (Chapters 2–5) span multiple related projects done in collaboration, all of which are previously published or currently under peer-review. Chapter 2 is the culmination of the projects and represents the bulk of my personal contributions.

At the time of this writing, the work in Chapter 2 is under peer-review as:

Justin Funston, Maxime Lorrillere, David Vengerov, Baptiste Lepers Jean-Pierre Lozi, Vivien Quema, and Alexandra Fedorova. A Practical Model for Placement of Workloads on Multicore NUMA Systems. Submitted to the 13th European Conference on Computer Systems.

I was the lead investigator responsible for research direction, experiment design, data analysis, and solution design. Maxime Lorrillere conducted the experiments in Section 2.5 and Section A.1, implemented the fast memory migration mechanism in Section 2.5, and wrote Section 2.5 of the manuscript. I wrote the majority of the rest of the chapter's manuscript and conducted all other experiments in the chapter. Other co-authors provided technical and editorial advice.

Chapter 3 is a modified version of previously published work. It is ©2012 IEEE, reprinted with permission from:

Justin R. Funston, Kaoutar El Maghraoui, Joefon Jann, Pratap Pattnaik, and Alexandra Fedorova. 2012. An SMT-Selection Metric to Improve Multithreaded Applications Performance. In *Proceedings of the 26th International Parallel & Distributed Processing Symposium (IPDPS 12)*. IEEE, Washington, DC, USA, 1388–1399. https://doi.org/10.1109/IPDPS.2012.125 I was the lead investigator responsible for research direction, experiment design, data analysis, and solution design, and I wrote the majority of the manuscript. Co-authors provided technical and editorial advice.

Chapter 4 is a modified version of previously published work. It is ©2013 ACM, reprinted with permission from:

• Mohammad Dashti, Alexandra Fedorova, Justin Funston, Fabien Gaud, Renaud Lachaize, Baptiste Lepers, Vivien Quema, and Mark Roth. 2013. Traffic Management: A Holistic Approach to Memory Placement on NUMA Systems. In *Proceedings of the 18th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS 13)*. ACM, New York, NY, USA, 381–394. https://doi.org/10.1145/2451116.2451157

Mohammad Dashti, Fabien Gaud, and I jointly conducted the initial investigation into NUMA effects, including the discovery of the importance of congestion over locality (reported in Section 4.1 and Section 4.2). I designed and implemented the page-level replication mechanism described in Section 4.3.3 with debugging help from Fabien Gaud. I wrote the sections of the manuscript relevant to my contributions. Fabien Gaud designed and implemented the Carrefour algorithm. All co-authors including myself provided technical and editorial advice.

Chapter 5 is a modified version of previously published work:

Fabien Gaud, Baptiste Lepers, Jeremie Decouchant, Justin Funston, Alexandra Fedorova, and Vivien Quema. 2014. Large Pages May Be Harmful on NUMA Systems. In *Proceedings of the 2014 USENIX Annual Technical Conference (ATC 14)*. USENIX Association, Berkeley, CA, USA, 231–242.

I conducted the initial investigation into NUMA and large pages, including the discovery and analysis of the hot page and page-level false sharing problems (reported in Section 5.2 and Section 5.3.1), and wrote the sections of the manuscript relevant to my contributions. Fabien Gaud and Baptiste Lepers designed and implemented the Carrefour-LP algorithm. All co-authors including myself provided technical and editorial advice.

# **Table of Contents**

| Al | bstrac  | ct                                                         | ii  |

|----|---------|------------------------------------------------------------|-----|

| La | ay Sui  | mmary                                                      | iv  |

| Pr | eface   |                                                            | v   |

| Ta | ble o   | f Contents                                                 | vii |

| Li | st of ' | Tables                                                     | хi  |

| Li | st of l | Figures                                                    | xii |

| Gl | lossar  | y                                                          | ΧV  |

| A  | cknov   | vledgments                                                 | kvi |

| 1  | Intr    | oduction                                                   | 1   |

|    | 1.1     | Background                                                 | 3   |

| 2  | A M     | Iodel for Placement of Workloads on Multicore NUMA Systems | 6   |

|    | 2.1     | Introduction & Motivation                                  | 7   |

|    | 2.2     | Background & Related Work                                  | 9   |

|    |         | 2.2.1 State of the Art                                     | 9   |

|    |         | 2.2.2 Assumptions and Limitations                          | 12  |

|    | 2.3     |                                                            | 15  |

|    | 2.4     | Performance Predictions                                    | 20  |

|   |      | 2.4.1   | Predicting Performance Categories                       | 22 |

|---|------|---------|---------------------------------------------------------|----|

|   |      | 2.4.2   | Predicting Performance with Machine Learning            | 25 |

|   |      | 2.4.3   | Results                                                 | 27 |

|   | 2.5  | Using   | the Model in Practice                                   | 32 |

|   |      | 2.5.1   | A Potential Use Case                                    | 32 |

|   |      | 2.5.2   | Memory Migration Overhead                               | 34 |

|   | 2.6  | Summ    | ary                                                     | 38 |

| 3 | An S | SMT-Se  | lection Metric                                          | 39 |

|   | 3.1  | Backg   | round & Motivation                                      | 40 |

|   | 3.2  | The SN  | MT-Selection Metric                                     | 44 |

|   |      | 3.2.1   | SMTsm on IBM's POWER7 Processor                         | 47 |

|   |      | 3.2.2   | SMTsm on Intel's Nehalem Processor                      | 48 |

|   | 3.3  | Experi  | mental Methodology                                      | 50 |

|   |      | 3.3.1   | System Configuration                                    | 50 |

|   |      | 3.3.2   | Benchmarks                                              | 50 |

|   | 3.4  | Evalua  | tion                                                    | 52 |

|   |      | 3.4.1   | SMT-Selection Metric (SMTsm) Evaluation                 | 52 |

|   |      | 3.4.2   | SMTsm Evaluation at a Lower-SMT Level                   | 56 |

|   |      | 3.4.3   | Metric Evaluation Across Chips                          | 58 |

|   | 3.5  | Applyi  | ing the SMT-Selection Metric                            | 60 |

|   |      | 3.5.1   | Using Gini Impurity to Decide on a Good SMTsm Threshold | 61 |

|   |      | 3.5.2   | Using the Average PPI (Percentage Performance Improve-  |    |

|   |      |         | ment) Method to Decide on a Good SMTsm Threshold        | 62 |

|   | 3.6  | Relate  | d Work                                                  | 64 |

|   | 3.7  | Summ    | ary                                                     | 67 |

| 4 | NUN  | MA Tra  | ffic Management through Memory Placement                | 68 |

|   | 4.1  | Backg   | round                                                   | 69 |

|   | 4.2  | Traffic | Congestion on Modern NUMA Systems                       | 70 |

|   | 4.3  | Design  | and Implementation                                      | 74 |

|   |      | 4.3.1   | The Mechanisms                                          | 74 |

|   |      | 4.3.2   | The Algorithm                                           | 76 |

|    |      | 4.3.3    | Implementation                          | 79  |

|----|------|----------|-----------------------------------------|-----|

|    | 4.4  | Evalua   | ition                                   | 83  |

|    |      | 4.4.1    | Testbed                                 | 84  |

|    |      | 4.4.2    | Single-Application Workloads            | 85  |

|    |      | 4.4.3    | Multi-Application Workloads             | 90  |

|    |      | 4.4.4    | Overhead                                | 94  |

|    |      | 4.4.5    | Impact on Energy Consumption            | 95  |

|    |      | 4.4.6    | Discussion: Hardware Support            | 95  |

|    | 4.5  | Relate   | d Work                                  | 97  |

|    | 4.6  | Summ     | ary                                     | 101 |

| _  | _    |          | NYDA G                                  | 400 |

| 5  |      |          | s on NUMA Systems                       | 102 |

|    | 5.1  |          | round                                   | 102 |

|    | 5.2  | •        | Pages and Adverse NUMA Effects          | 104 |

|    |      | 5.2.1    | Experimental Platform                   | 104 |

|    |      | 5.2.2    | Large Pages on Linux                    | 104 |

|    | 5.3  | Solution | ons                                     | 107 |

|    |      | 5.3.1    | Page Balancing is Not Enough            | 109 |

|    |      | 5.3.2    | Carrefour-LP                            | 110 |

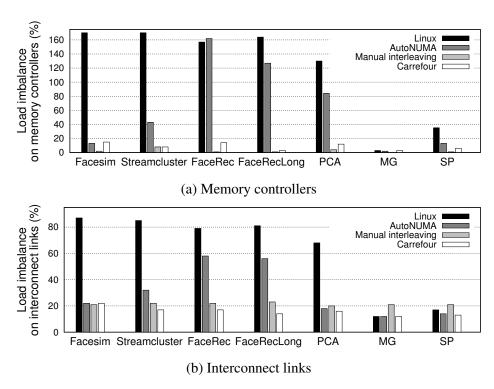

|    | 5.4  | Evalua   | tion                                    | 115 |

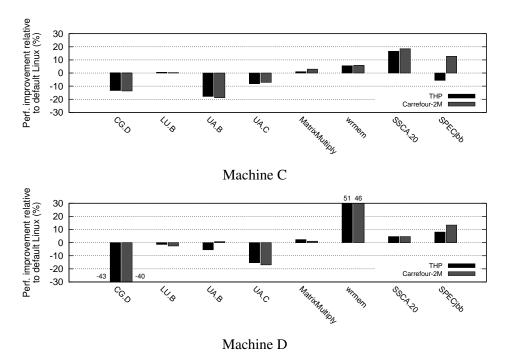

|    |      | 5.4.1    | Performance Evaluation                  | 115 |

|    |      | 5.4.2    | Overhead Assessment                     | 119 |

|    |      | 5.4.3    | Discussion                              | 120 |

|    |      | 5.4.4    | Very Large Pages                        | 121 |

|    | 5.5  | Relate   | d Work                                  | 121 |

|    |      | 5.5.1    | Large Pages and TLB Performance         | 121 |

|    |      | 5.5.2    | Large Page Support and Optimization     | 122 |

|    | 5.6  | Summ     | ary                                     | 123 |

| 6  | Con  | alugian  |                                         | 124 |

| 6  | Con  | Clusion  | • • • • • • • • • • • • • • • • • • • • | 124 |

| D. | 1 10 | 1        |                                         | 100 |

| A | Supp        | porting Materials                                    | 142 |

|---|-------------|------------------------------------------------------|-----|

|   | <b>A.</b> 1 | Non-Interference of Workloads on Separate NUMA Nodes | 142 |

|   | A 2         | Performance Prediction Results for the ML Model      | 143 |

## **List of Tables**

| Table 1.1 | Summary of related work and their capabilities                | 3   |

|-----------|---------------------------------------------------------------|-----|

| Table 2.1 | Scheduling concerns for the AMD test system                   | 14  |

| Table 2.2 | Fast memory migration evaluation                              | 34  |

| Table 4.1 | NUMA traffic congestion effects                               | 73  |

| Table 4.2 | Statistics used by the Carrefour algorithm                    | 76  |

| Table 4.3 | Number of pages replicated, interleaved, and co-located       | 89  |

| Table 4.4 | Carrefour performance improvement over Linux                  | 90  |

| Table 4.5 | Carrefour performance improvement for multiple applications . | 91  |

| Table 5.1 | NUMA and TLB metrics for selected benchmarks                  | 106 |

| Table 5.2 | Detailed metrics for workloads using Carrefour-2M             | 111 |

| Table 5.3 | CG.D, UA.B, and UA.C NUMA metrics                             | 117 |

| Table 6.1 | Scheduling concerns for an AMD Zen system                     | 125 |

# **List of Figures**

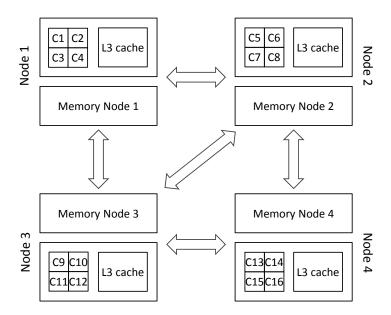

| Figure 1.1  | An example NUMA system                                             | 4  |

|-------------|--------------------------------------------------------------------|----|

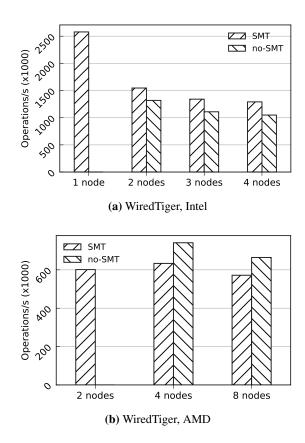

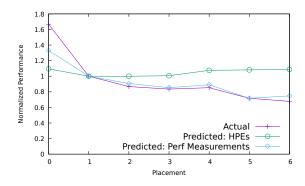

| Figure 2.1  | WiredTiger performance for various workload placements             | 8  |

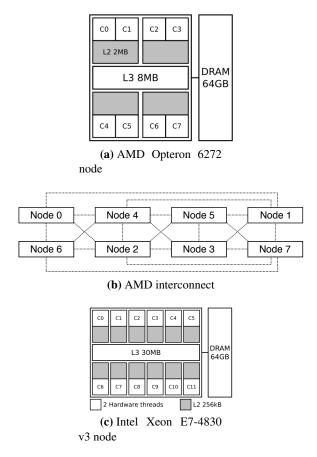

| Figure 2.2  | Test systems used                                                  | 15 |

| Figure 2.3  | Three example performance clusters                                 | 23 |

| Figure 2.4  | Prediction results for <i>postgres-tpcc</i> on the AMD test system | 28 |

| Figure 2.5  | Prediction results for <i>spark-pr-lj</i> on the Intel test system | 28 |

| Figure 2.6  | Prediction results for <i>kmeans</i> on the AMD test system        | 28 |

| Figure 2.7  | Prediction results for <i>canneal</i> on the Intel test system     | 29 |

| Figure 2.8  | Prediction results for $dc.B$ on the AMD test system               | 29 |

| Figure 2.9  | Prediction results for $ft.C$ on the Intel test system             | 29 |

| Figure 2.10 | Prediction results for <i>frequine</i> on the Intel test system    | 30 |

| Figure 2.11 | Prediction results for <i>kmeans</i> on the Intel test system      | 30 |

| Figure 2.12 | Prediction results for WTbtree on the Intel test system            | 30 |

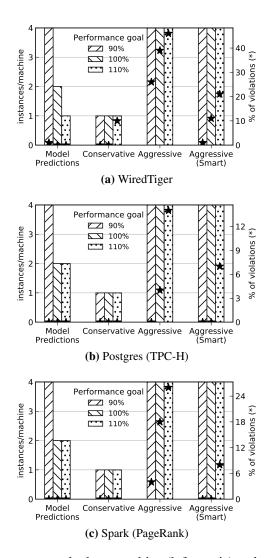

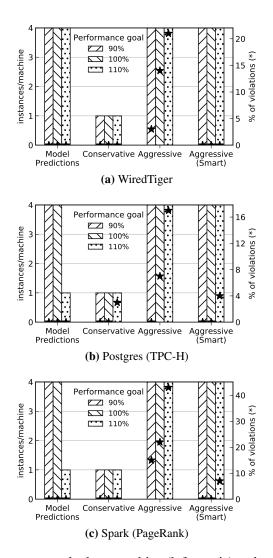

| Figure 2.13 | Use-case evaluation, AMD system                                    | 35 |

| Figure 2.14 | Use-case evaluation, Intel system                                  | 36 |

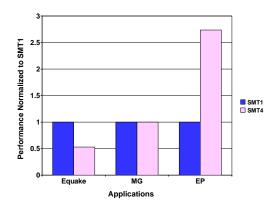

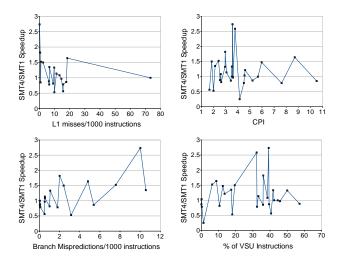

| Figure 3.1  | Comparison of performance with SMT1 vs. SMT4                       | 41 |

| Figure 3.2  | SMT speedup versus simple metrics                                  | 42 |

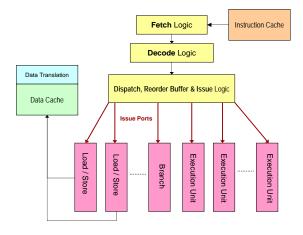

| Figure 3.3  | A generic processor execution engine                               | 45 |

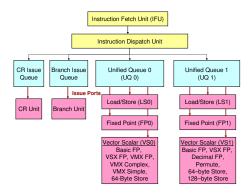

| Figure 3.4  | IBM POWER7 out-of-order execution engine                           | 47 |

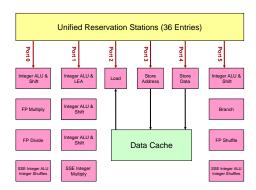

| Figure 3.5  | Intel Nehalem out-of-order execution engine                        | 49 |

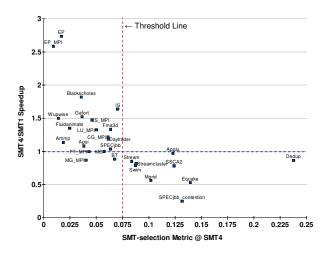

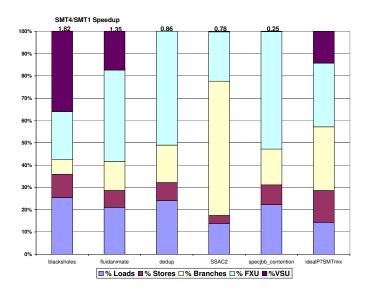

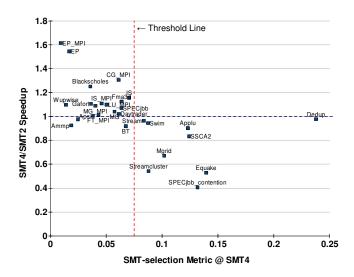

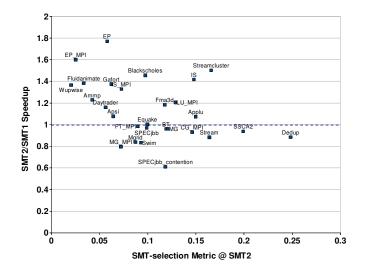

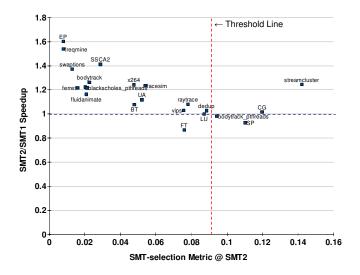

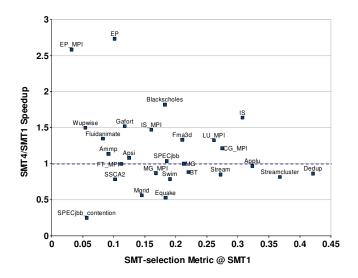

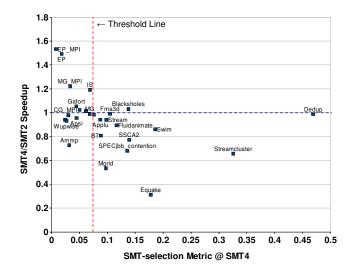

| Figure 3.6  | SMTsm @SMT4 vs. SMT4/SMT1 on POWER7                                | 53 |

| Figure 3.7  | Instruction mix of five benchmarks on POWER7                       | 53 |

| Figure 3.8  | SMTsm @SMT4 vs. SMT4/SMT2 on POWER7                     | 54  |

|-------------|---------------------------------------------------------|-----|

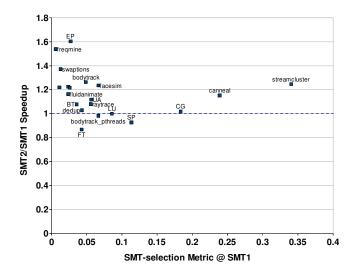

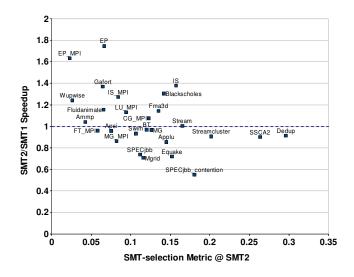

| Figure 3.9  | SMTsm @SMT2 vs. SMT2/SMT1 on POWER7                     | 54  |

| Figure 3.10 | SMTsm @SMT2 vs. SMT2/SMT1 on Intel Nehalem              | 56  |

| Figure 3.11 | SMTsm @SMT1 vs. SMT4/SMT1 on POWER7                     | 57  |

| Figure 3.12 | SMTsm @SMT1 vs. SMT2/SMT1 on Intel Nehalem              | 57  |

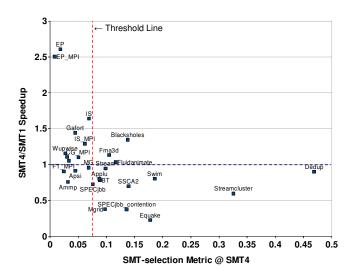

| Figure 3.13 | SMTsm @SMT4 vs. SMT4/SMT1 on 2xPOWER7                   | 58  |

| Figure 3.14 | SMTsm @SMT4 vs. SMT4/SMT2 on 2xPOWER7                   | 59  |

| Figure 3.15 | SMTsm @SMT1 vs. SMT2/SMT1 on 2xPOWER7                   | 59  |

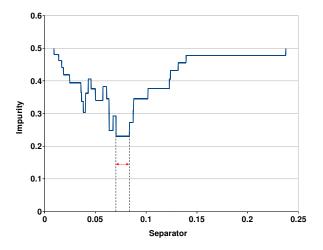

| Figure 3.16 | Gini impurity for potential thresholds for the SMTsm    | 62  |

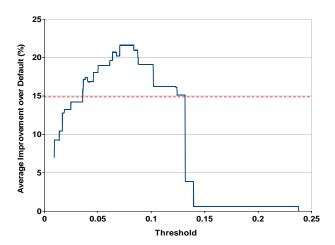

| Figure 3.17 | Average performance improvement vs. SMTsm               | 64  |

| Figure 4.1  | Performance by thread and memory configuration          | 71  |

| Figure 4.2  | Streamcluster IC imbalance by memory configuration      | 75  |

| Figure 4.3  | Global decisions in Carrefour                           | 77  |

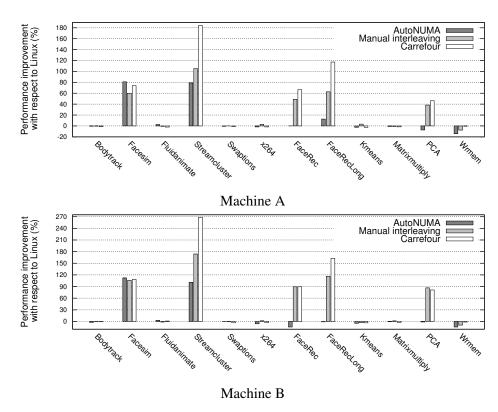

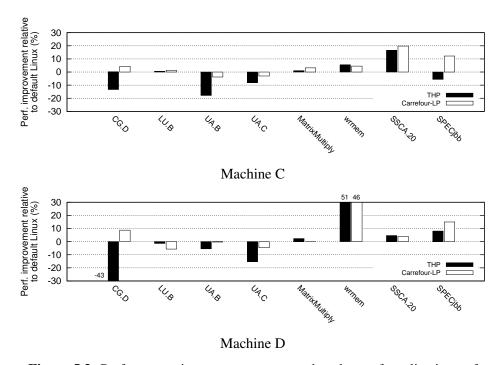

| Figure 4.4  | Carrefour evaluation, PARSEC/Metis                      | 86  |

| Figure 4.5  | Carrefour evaluation, NAS                               | 87  |

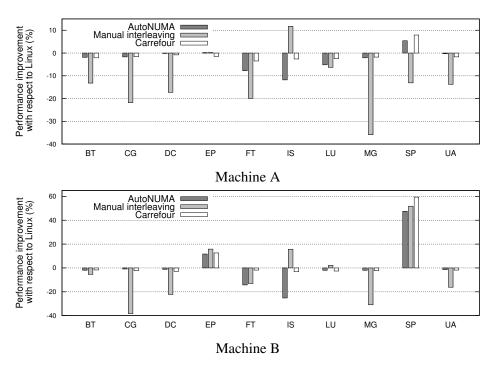

| Figure 4.6  | Load imbalance for selected benchmarks                  | 88  |

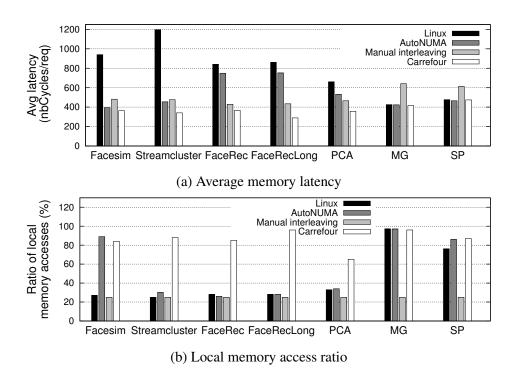

| Figure 4.7  | Latency and locality for selected benchmarks            | 89  |

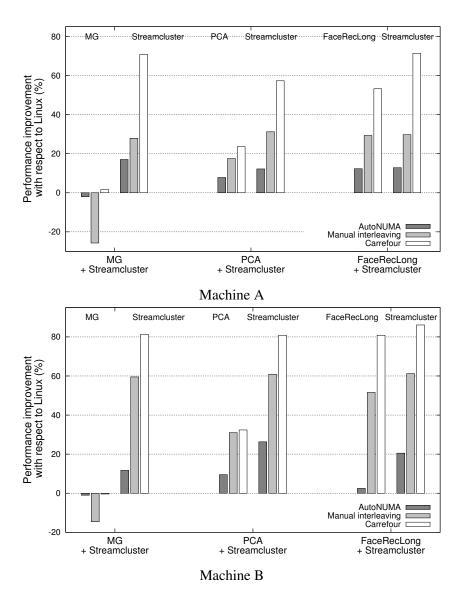

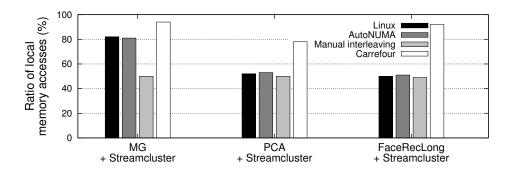

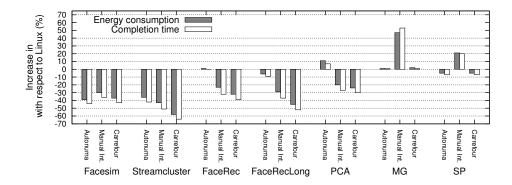

| Figure 4.8  | Carrefour evaluation, multi-application workloads       | 92  |

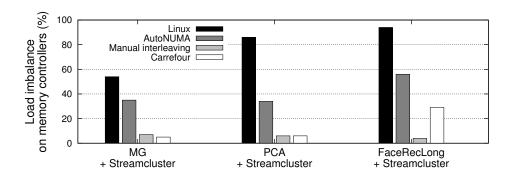

| Figure 4.9  | Multi-application memory controller imbalance           | 93  |

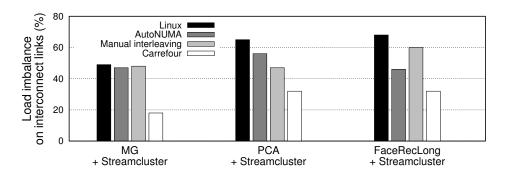

| Figure 4.10 | Multi-application interconnect imbalance                | 93  |

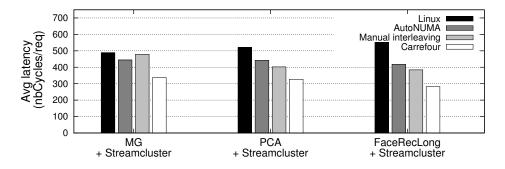

| Figure 4.11 | Multi-application memory latency                        | 93  |

| Figure 4.12 | Multi-application local memory access ratio             | 94  |

| Figure 4.13 | Effect of Carrefour on energy consumption               | 96  |

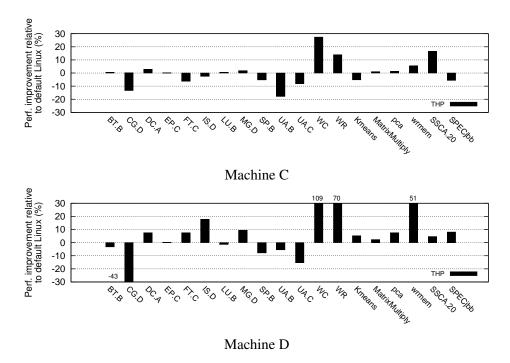

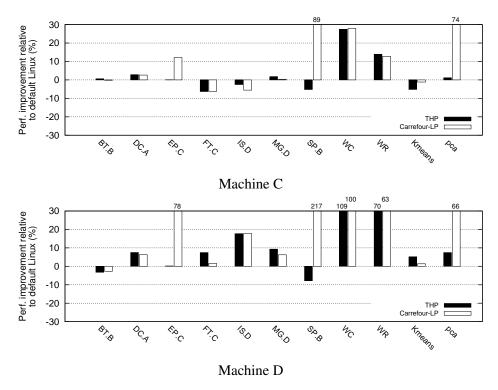

| Figure 5.1  | THP performance improvement over Linux                  | 107 |

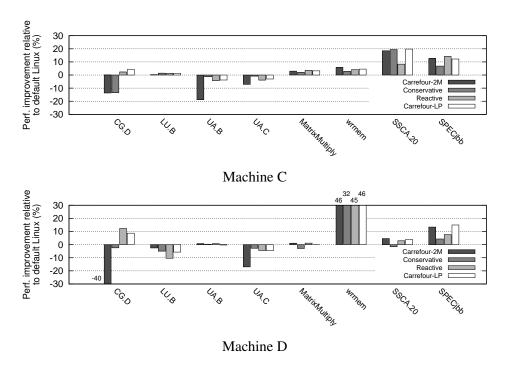

| Figure 5.2  | Carrefour-2M evaluation                                 | 108 |

| Figure 5.3  | Carrefour-LP evaluation on selected applications        | 116 |

| Figure 5.4  | Evaluation of Carrefour-LP's components                 | 117 |

| Figure 5.5  | Carrefour-LP evaluation on remaining applications       | 119 |

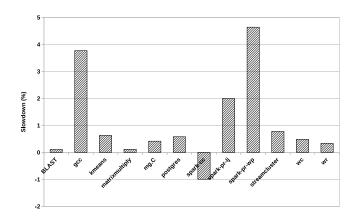

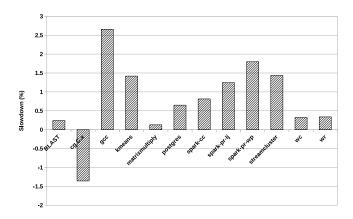

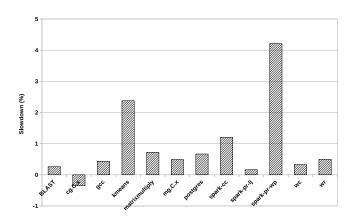

| Figure A.1  | Slowdown with cg.C as the interfering workload          | 143 |

| Figure A.2  | Slowdown with mg.C as the interfering workload          | 143 |

| Figure A.3  | Slowdown with streamcluster as the interfering workload | 144 |

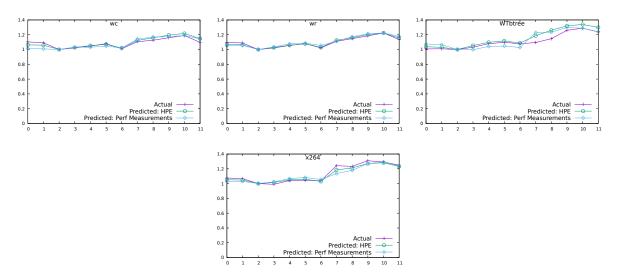

| Figure A.4 | Accuracy of predictions on the AMD system   | 147 |

|------------|---------------------------------------------|-----|

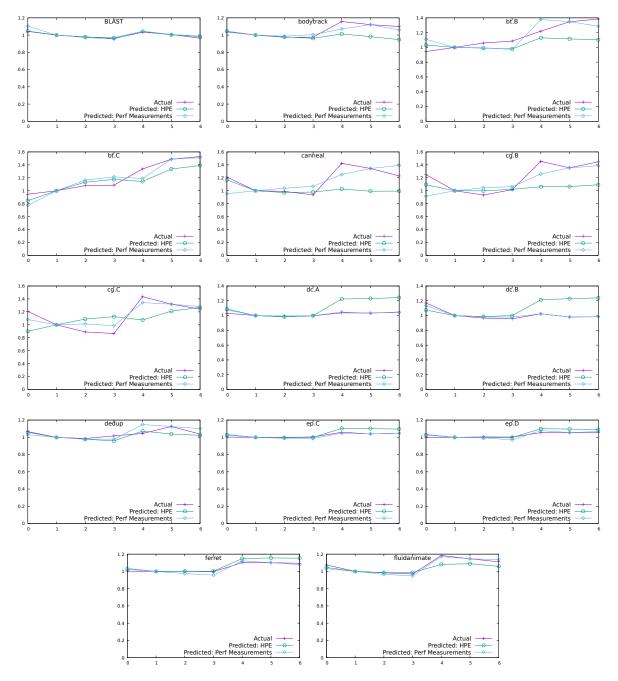

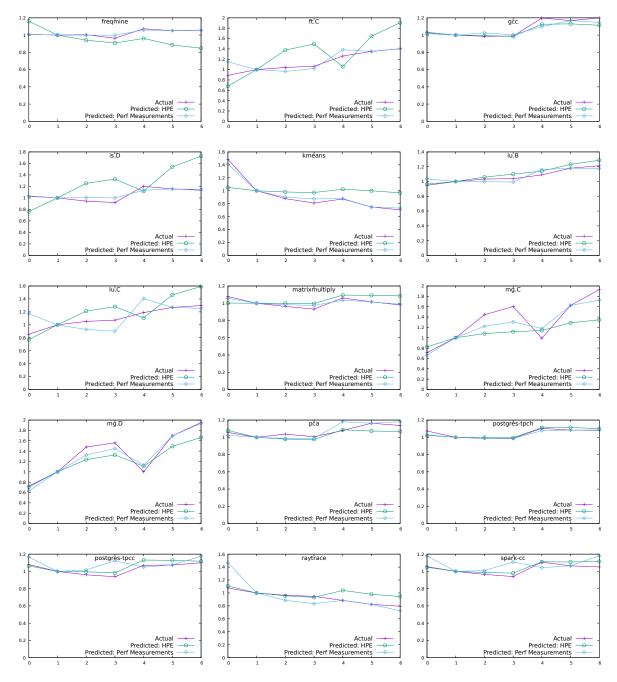

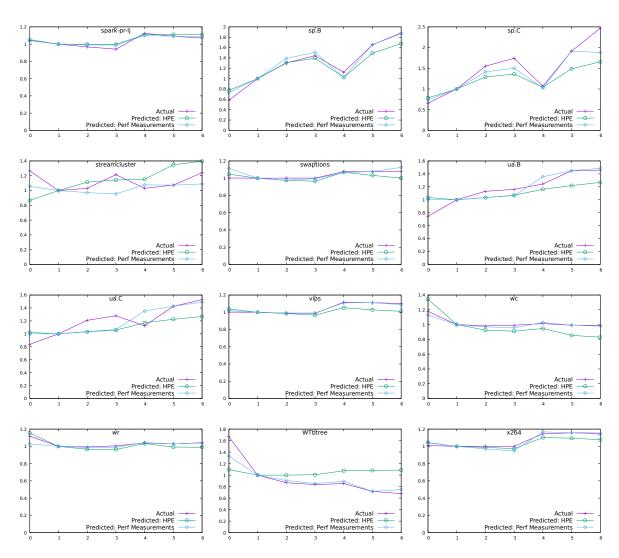

| Figure A.5 | Accuracy of predictions on the Intel system | 150 |

## Glossary

**CMP** Chip multiprocessing

HPE Hardware performance event, a.k.a. hardware performance counter

**IBS** Instruction-based sampling

IC Interconnect

**IPC** Instructions per cycle

ML Machine learning

**NUMA** Non-uniform memory access

**SMP** Symmetric multiprocessing

**SMT** Simultaneous multithreading

**THP** Transparent huge pages

**TLB** Translation lookaside buffer

## Acknowledgments

I give my warmest thanks to my advisor Dr. Fedorova for her peerless guidance and for helping me achieve my potential as a researcher. I would also like to thank all of my collaborators and co-authors for their essential hard work and insight.

I would like to thank my family for all of their love and support.

Lastly I would like to thank IBM for the internship that led to the research in Chapter 3, and Oracle Labs and the British Columbia Innovation Council for funding the work of Chapter 4.

## Chapter 1

## Introduction

Data centers use 2% of the electricity consumed in the United States [85] and 3% of the world's [17] electricity. These data centers run important applications such as scientific simulations, data analytics, web servers, and databases, and the applications often have strict performance requirements. In order to keep power consumption under control hardware designers have introduced systems with continually increasing core counts and power control features to reduce energy usage when parts of the system are idle. Using a smaller number of larger systems (i.e. systems with more cores) can be 25%–33% more power efficient than using twice as many systems of half the size (based on our own experiments, vendor specifications [3], and previous studies [13]).

Increasing core counts, though, come at the cost of increased hardware complexity and architectural trade-offs made for scalability. Applications and system software must be designed and optimized with the hardware architecture in mind, otherwise performance can suffer. This dissertation focuses on how system software can optimize the performance of applications running on the large server-class systems typically used in data centers, and on how data center operators can make reliable performance trade-offs for better server utilization or reduced power consumption. The first step in doing so is choosing the level of parallelism an application should use (in other words, how many cores it runs on). Due to scalability limits or load patterns, it is not always beneficial to give all the cores of system to a single application. Additionally, in cloud environments it is common for cus-

tomers to pay for a set number of cores upfront, so the problem of determining how many cores to use is moot in that case. A comprehensive solution on how to determine the level of parallelism for an application is beyond the scope of this dissertation, but the primary contribution of Chapter 3 is a solution for it applicable to simultaneous multithreading (SMT) hardware.

The second step after the number of cores has been determined is to choose which cores to use. The choice of cores to use, which we call a placement, affects what hardware resources are available to the application which in turn affects performance and power usage. Section 1.1 gives an overview of the relevant hardware resources and how they affect applications. The key complicating factor for selecting a placement is that different applications have different needs for hardware resources. The primary contribution of Chapter 2 is a practical model for workload placement. Our model does not require modifying applications, can be easily adapted to various architectures, and can be used to predict the performance of different placements. Performance prediction, as opposed to simply finding the best performing placement, is crucial because it allows trade-offs to be made. Most of the extensive previous research in the area does not attempt to predict performance, only handles a single type of hardware resource (for example, only considering beneficial cache sharing but not taking into account SMT sharing of functional units or other hardware resource sharing), requires expert knowledge and manual tweaking to adapt to a new architecture (usually because one would need to write carefully designed micro-benchmarks for new hardware resources), or is not deployable online because new applications would require several offline profiling runs. Table 1.1 provides an overview of significant related work and their respective short-comings compared to our solution described in Chapter 2. A detailed description of related work is provided in Section 2.2.

Predicting the performance of workload placements allows for one especially important trade-off. For many applications, using fewer hardware resources will only have a minimal or moderate effect on performance. If data center operators or cloud server providers can predict these cases and the performance impact is within acceptable tolerances, then they can use remaining hardware resources to pack additional workloads or applications onto the same server. This increases utilization and efficiency and ultimately reduces energy usage. Section 2.5 evaluates specific

scenarios where our workload placement solution can increase server utilization while maintaining performance goals.

The final step after workload placement is memory placement. Large multicore systems often have a non-uniform memory access (NUMA) architecture (described in more detail in Section 1.1), which means that memory placement can also affect performance. Better memory placement will reduce contention for hardware resources which in turn reduces memory access times. Chapters 4 and 5 describe our solution to the memory placement problem, which provides significant performance benefits over standard techniques.

|                           | Predicts<br>Performance | Multiple<br>Hardware<br>Resources | Easily<br>Adapted | Deployable<br>Online |

|---------------------------|-------------------------|-----------------------------------|-------------------|----------------------|

| Chapter 2's<br>Solution   | Y                       | Y                                 | Y                 | Y                    |

| Pandia [49]               | Y                       | Y                                 | N                 | N                    |

| <b>SMiTe</b> [105]        | Y                       | Y                                 | N                 | Y                    |

| Bubble-Flux [101]         | Y                       | Y                                 | N                 | Y                    |

| Asymsched [59]            | N                       | N                                 | Y                 | Y                    |

| <b>DINO</b> [107]         | N                       | N                                 | Y                 | Y                    |

| Thread<br>Clustering [93] | N                       | N                                 | Y                 | Y                    |

**Table 1.1:** Summary of related work and their capabilities

### 1.1 Background

Modern server-class systems have a complex hierarchy of shared resources, which is a necessity to scale them to high core counts. Figure 1.1 shows an example NUMA system. At the lowest level of the hierarchy is a hardware context (also known as a hardware thread or, confusingly, as a core on some architectures). The hardware context contains everything required to track the execution state of a software thread such as the program counter and registers. When a software thread is assigned to a hardware context it can execute on the CPU.

At the next level of the hierarchy is the physical core. A physical core en-

**Figure 1.1:** A modern NUMA system, with four nodes and four cores per node. ©2013 ACM, reprinted with permission from [36].

compasses data and instruction caches, functional units (the ALU, branch units, load/store units, etc.), and the instruction decode and dispatch units. Simultaneous multithreading (SMT) is a feature that places multiple hardware contexts onto a single physical core. The physical core's resources are shared between hardware contexts, although on some architectures some of the resources may be duplicated for each context (for example, each hardware context might get its own L1 cache but have to share the L2 cache with other contexts). In general, SMT can improve the overall throughput of the system but each software thread has lower performance than if it is able to execute alone on the physical core because of the competition for core resources. If the application heavily shares data between threads and benefits from very low latency communication between threads then SMT can actually improve individual threads' performance (the kmeans benchmark on our AMD test system, shown in Figure A.4, is one such instance).

At the highest level of the hierarchy is the non-uniform memory access (NUMA) node. A NUMA node contains a set of cores and an associated set of locally connected memory. Programs can access memory on any NUMA node from any core

transparently without special consideration. The operating system decides which NUMA node to allocate memory on. Memory accesses to the local memory have a lower latency. NUMA nodes are connected by interconnect (IC) links, so memory accesses to remote memory travel over the IC links and have a higher latency. Cores on the same NUMA node typically share an L3 cache, the memory controller, and the IC links. So, if all the cores on a NUMA node are performing very memory-intensive computations then the bottleneck will likely be the shared memory subsystem and performance will suffer.

If software does not take into account all of these shared resources then contention for the resources results in poor performance, sometimes resulting in slow-downs of  $2\times$  or more! The following chapters analyze the performance effects in detail and propose practical and effective solutions.

## Chapter 2

# A Model for Placement of Workloads on Multicore NUMA Systems<sup>1</sup>

Data center operators balance two objectives: providing a satisfactory experience for the customer and efficiently allocating the hardware that runs customer virtual instances or operator services. We believe that hardware provisioning should not be a guessing game. No one should have to allocate more hardware than needed just out of the fear that providing less could violate a service-level objective.

Unfortunately, mapping threads, or virtual CPUs (vCPUs), to physical cores on multicore NUMA systems is still like playing a guessing game. Modern NUMA systems consist of several nodes that share various resources. Cores within a node may share SMT pipelines and caches. Nodes themselves share an interconnect, which may be asymmetric, providing higher bandwidth for some links than for others and for some directions of communication than for others (e.g., Figure 2.2).

The challenge of placing workloads on a NUMA system has to do with complex interactions between the workload and the hardware. Our solution, presented in this chapter, consists of two main contributions. First, is an **abstract machine model** (Section 2.3) that abstracts hardware resources and provides a practical way

<sup>&</sup>lt;sup>1</sup>This chapter is an expanded version of work currently under peer-review as [45]

to represent placements. Second, we build on the abstract machine model to build a **performance prediction model** (Section 2.4) that predicts the performance of important placements.

**Attribution:** Maxime Lorrillere conducted the experiments in Section 2.5 and Section A.1, implemented the fast memory migration mechanism in Section 2.5, and wrote Section 2.5 of the manuscript. I wrote the majority of the rest of the chapter's manuscript, was responsible for all areas of research, and conducted all other experiments in the chapter.

### 2.1 Introduction & Motivation

Consider Figure 2.1a, which shows performance of MongoDB's WiredTiger key-value store [4] on a NUMA Intel machine. This workload, which runs a BTree search using 24 threads, runs almost twice as fast when all of the threads are placed on a single node, as opposed to being spread across two or more nodes. On Figure 2.1b, on the other hand, we see that the same workload configured with 16 threads on an AMD NUMA system runs much faster when it has four nodes at its disposal, rather than two<sup>2</sup>. On the Intel system, this application prefers having all of its threads co-located on a single NUMA node and using SMT because it enjoys lower communication latencies. On the AMD machine, on the other hand, it suffers from contention for shared resources when all of its threads are crowded on a small number of nodes. How can a data center operator know, save for trying all possible placements, that to achieve the best possible performance this container should be placed on a single node on an Intel system but on four nodes (without SMT) on an AMD system? This is an example of questions that we aim to answer in this work.

The observations detailed in the previous paragraph are not new and were studied in our community for more than a decade [21–23, 36, 41, 46, 48, 49, 56, 57, 59, 69, 87, 101, 105, 107, 108]. Yet, as we elaborate in Section 2.2, we still do not have a method for deciding how a particular *placement*, a mapping of vCPUs to physical cores, on an arbitrary multicore system will affect performance of an

<sup>&</sup>lt;sup>2</sup>With eight cores/node we could not fit all threads on a single node without creating contention for CPU cycles.

**Figure 2.1:** Throughput of the WiredTiger key-value store on two NUMA systems according to the number of nodes.

unknown workload.

We propose a general framework for reasoning about workload placement on machines with shared resources. Our methodology is not tied to a particular machine, specific shared resources or certain hardware performance events. We abstract a multicore machine as a collection of shared resources, called scheduling concerns, where each concern produces a score indicating how many threads use the resource in a given placement. Vectors of scores uniquely identify distinct placements: placements that differ with respect to resource usage. Our abstraction relies on important simplifications (see Section 2.2.2) that enable us to dramatically reduce the number of distinct placements from billions of all possible to dozens, and makes the problem tractable.

We develop a methodology to automatically build a model for predicting performance in all distinct Pareto-efficient placements, given a specification of a machine's scheduling concerns and observations of the workload at runtime. Our model predicts performance to within 5% of actual on average. With the resulting model users can make decisions such as "give application X as few NUMA nodes as possible while making sure that its throughput remains above Y operations per second". Our framework is flexible: a previously unmodeled shared resource can be added to the model as a new scheduling concern and the model is updated automatically. We do not have to manually redesign the model for every new machine.

Many performance models similar to ours used hardware performance events (HPE), observed on a *single* placement as model features [12, 46, 56, 59, 101, 107]. *Our results show that single-placements HPEs cannot produce a reliable performance model on complex modern systems*. Our solution uses actual *performance observations* on two different placements as model input features and does not require selecting hardware performance events that *may* correlate with performance<sup>3</sup>.

Our method requires running a workload for a short period of time in two different placements before it can generate performance predictions, so it can be used online. Nevertheless, migrating the workload from one placement to another can be costly, because we may need to migrate memory between NUMA nodes. To evaluate this effect, we analyze and improve on migration overheads in Linux. Our results should help potential users decide when our method is viable for an online deployment.

## 2.2 Background & Related Work

#### 2.2.1 State of the Art

Workload placement on multicore systems has been explored for over a decade. Early studies examined contention between single-threaded applications for a specific resource, such as the SMT instruction pipeline [46, 87], or shared caches and memory controllers [43, 69, 101, 107]. Later work extended the techniques to

<sup>&</sup>lt;sup>3</sup>HPEs, such as instructions/cycle may be used for performance measurements, but any other application-specific metric is acceptable.

multithreaded workloads and to additional resource combinations, such as SMT and shared caches [105], memory controllers and the shared interconnect [36, 59]. While laying a crucial foundation for our work, these prior techniques did not provide a general solution for reasoning about such systems.

For instance, the DIO algorithm [107] showed us how to avoid interference for shared memory controllers. A simplified version of the algorithm is as follows: monitor the memory-intensiveness of running threads using HPEs for a sampling period, sort threads by memory-intensiveness, and then place threads on domains sharing memory resources such that the aggregate memory-intensiveness is balanced on domains. This algorithmic approach returns a new thread placement it considers to be optimal. In the absence of unaccounted for resources affecting the performance of the thread placement, the algorithm improves performance. Note that it does not try to predict how much performance will improve, and only handles one set of shared resources.

The AsymSched algorithm of Lepers et al. [59] showed us how to place applications on machines with asymmetric interconnects, by using knowledge of the topology and the application's traffic patterns to place threads on nodes with good interconnect connectivity.

Other previous scheduling algorithms pursued a goal of placing threads that share data near each other (e.g. sharing a cache or on the same NUMA node). Tam et al. [93] provided a scheduling algorithm aimed at maximizing the benefit of thread sharing. It is similar in approach to DIO. Thread sharing is measured online and then the algorithm enacts a new thread placement that optimizes the overall sharing on the system. As with DIO, it does not attempt to predict performance.

Techniques used in prior work did not allow for automatic combination of several models. Every contention model required manual design: careful selection of hardware performance events [36, 43, 56, 59, 107] or even manual crafting of artificial "probe" workloads or "Rulers" [101, 105] that must be run side-by-side with the target workloads to determine their sensitivity to contention.

Most existing scheduling algorithms have a common structure. As inputs, they take knowledge of the hardware and some online metrics from the application (usually obtained from HPEs). Then as an output they suggest a thread placement that should provide optimum performance with respect to the resources they individu-

ally account for.

A comprehensive solution should account for all the hardware resources that matter to thread placement, but combining existing algorithms is difficult. There is no baseline for comparing the importance of one algorithm over another. If the algorithms suggest conflicting thread placements, then it is necessary to balance the performance effect of each algorithm against the other, but as discussed the algorithms can at best only say whether a given placement is better or worse than another. They cannot predict the performance effect so the scheduler has no way to know which algorithm should be followed or if a compromise is best.

One could try to develop a new algorithm that incorporates the ideas of the original algorithms. It would require extensive manual testing and tuning to determine the best way to balance the concerns, would likely be sensitive to differing workloads and hardware, and would require expert knowledge that covers both of the original algorithms. All of these are serious downsides to the approach.

The state of Linux scheduler exemplifies these difficulties. The Linux scheduler attempts to address many thread placement concerns, but it does so in an adhoc way with many heuristics and hacks. In one of our previous works we discovered four major bugs in the Linux scheduler, which resulted in a 22% to 138x performance impact in extreme cases [61].

System identification is a well-studied area in the field of control systems [30, 31, 60]. The goal of system identification is to model a system's outputs given some number of inputs. For our purposes, the inputs would be the workload placement and the dynamic application behavior and the output we want to model is the application's performance. The main difficulty is that system identification generally assumes that the inputs are easily measurable and real-valued, for example, an input voltage. This does not apply in our case of workload placement. Deciding exactly what to use as inputs to our model and how to quantify them is an important and difficult problem on its own, and is discussed in the following sections. For this reason we approached the problem with the field of machine learning in mind, rather than system identification.

Dwyer et al. used an automated model-building methodology, where automatically selected features (from all HPEs available on the machine) were fed into a variety of machine-learning models [41]. However, the model predicted a rather sim-

ple outcome: a performance degradation when a target workload was co-scheduled with an interfering one, and not the performance in different placements. Consistent with our finding that HPEs observed in a single placement are poor model features, Dwyer's study reported rather poor prediction accuracy in many cases.

A recent system, Pandia [49], made significant advances. It accurately predicts relative performance of different workload placements on multicore NUMA machines. It can also predict relative performance of an application with different numbers of threads, but such predictions in Pandia require performance observations of six runs with different thread counts, which is difficult to do online because most real applications cannot easily reconfigure their thread count on demand. Despite addressing many limitations of previous work and producing remarkably accurate performance predictions, fundamentally Pandia still relies on the machine-specific modelling methodology that prevents easily transferring results to other systems. Pandia's authors capture factors that contribute to performance, such as cache contention, latency of communication, and load balancing, in a set of machine-specific equations. If the model had to be adapted to another machine, for example one with an asymmetric interconnect, the equations would have to be manually reformulated.

We believe that investing that much effort into designing new models for every new type of hardware puts an unreasonable burden on system engineers. Essentially, while there is significant existing theory for scheduling with respect to time-sharing [86, 100], there is not any developed theory or framework for space-sharing. Instead, we sought a future-proof methodology that uses easily available information about a machine's shared resources and automatically builds an accurate performance model.

#### 2.2.2 Assumptions and Limitations

To make our methodology robust and extensible we make a few simplifying assumptions, which we describe here.

**Identically scored placements yield identical performance.** As we explain in Section 2.3, a placement is identified by how many vCPUs share each hardware resource. We refer to the degree of sharing for a resource as the *score*; a vector

of scores thus identifies a placement. Placements with identical score vectors are deemed to yield identical performance for a given workload. This statement assumes that our machine model must be aware of all shared resources that might yield variations in performance. This assumption is made by most solutions in this space, because one can only model the factors of which one is aware. A radically different approach would be a statistical technique that searches for an optimally performing placement by trying a sufficient number of random placements [76]. Unfortunately, the best known techniques require trying *thousands* of placements and assumes that performance in all placements fits a Generalized Pareto distribution — an assumption that does not hold in our case.

A workload is encapsulated in a virtual container. This assumption sits well with many data centers that use virtualization for a variety of reasons. In our case, it makes the problem easier to solve than if we viewed a workload as an amorphous collection of threads. With a thread-centric view, the degree of concurrency can unpredictably change, either because of application logic or because of OS scheduling decisions. When it changes, performance can be affected because of intra-application scaling issues or because of the change in pressure on shared resources. Combining both effects in a single model is cumbersome: we concluded that for robustly accurate predictions that do not require offline runs we need to train a separate model for each feasible number of vCPUs in a container. Managed cloud environments present their offerings as a menu of virtual instances with a fixed number of vCPUs per instance. For example, AWS offers a dozen instances with the number of different core counts limited to ten [5]. So we can feasibly train a separate model for each machine and each vCPU count. We are not interested in finding the optimal number of threads or vCPUs for the workload; for that, users can leverage other tools [49, 90].

We also assume that each vCPU of the container is performing roughly the same type of work. This assumption is not very strict though; we have workloads in our test set that have database maintenance threads or garbage collection threads in addition to worker threads and these workloads still work well with our model.

A NUMA node is a unit of resource allocation. We assume that vCPUs are allocated to containers in units of entire NUMA nodes. That is, given a virtual

| Concern      | Score                                    | Resources                                                                     | Cost? | Inverse Perf? |

|--------------|------------------------------------------|-------------------------------------------------------------------------------|-------|---------------|

| L2/SMT       | Number of L2 caches in use               | L2 cache, instruc-<br>tion fetch and de-<br>code, and floating<br>point units | Y     | Y             |

| L3           | Number of L3 caches in use               | L3 cache, memory controller, and bandwidth to DRAM                            | Y     | Y             |

| Interconnect | Aggregate bandwidth between nodes in use | Interconnect bandwidth                                                        | N     | N             |

**Table 2.1:** Scheduling concerns used on our AMD test system (shown in Figure 2.2).

container the goal is to decide across how many NUMA nodes to spread the container; we do not co-locate different containers on the same node. We rely on this observation to make the problem tractable. Modelling contention among different containers on the same NUMA node is much more difficult. On the other hand, if multiple containers on the same machine are mapped to different NUMA nodes, they can co-exist without interference if the nodes used for different containers do not share interconnect links, which is a configuration easy to enforce. We confirmed that this property holds experimentally and the results are shown in A.1.

We consider only balanced placements. A balanced placement is one where the number of vCPUs is evenly divisible by any number of shared resource units considered for placement. For instance, if we have shared L3 caches on the system, we will only consider placements where the number of vCPUs sharing each L3 cache is equal. Uneven sharing can cause unpredictable performance effects on the workload, for example by creating stragglers, so we choose to not model these effects. Since we are already assuming that resources will be allocated to containers in multiples of NUMA nodes the balance assumption is not very limiting.

**Figure 2.2:** The two systems used in this chapter. The first is a quad AMD Opteron 6272. It has eight NUMA nodes (schematically shown in Figure 2.2a) connected with an asymmetric interconnect (Figure 2.2b) and a total of 64 cores. Pairs of cores share the instruction front-end, L2 cache, and floating point units. The second system is a quad Intel Xeon E7-4830 v3 with four NUMA nodes (Figure 2.2c) and 96 hardware threads (12 physical cores per node with SMT). The interconnect (not shown) is symmetric.

### 2.3 Abstract Machine Model

A major obstacle to a solution to the virtual core placement problem is the sheer number of possible placements. For 16 virtual cores on a 64 core system the number of possible placements is the combinations of 16 objects chosen from a set of 64, which is on the order of  $10^{14}$ .

It is essential to exploit the symmetry in the system to reduce the number of placements to a manageable number. By this we mean that for most types of shared resources it does not matter *which* shared resources are being used but *how much* of the shared resources is available to the workload, and having a way to quantify this would allow us to eliminate the vast majority of placements by only considering those that are actually relevant with respect to performance.

We tackle this with the concept of *scheduling concerns*. A single scheduling concern is responsible for a single hardware resource, or an inseparable set of hardware resources that affect the performance of thread placements. The primary purpose of a scheduling concern is to provide a numerical score when given a thread placement as input. The score represents the utilization of the particular resource and it only depends on the vCPU placement, not the dynamic behavior of a workload. A simple example is an "L2 cache" resource. The scheduling concern for the L2 cache measures the utilization of L2 caches on a system where there are multiple L2 caches shared by sets of cores, so the score would simply be the number of L2 caches in-use by vCPUs. The score remains constant with respect to the symmetry of the hardware resource the concern encompasses. So, two placements might use completely different NUMA nodes but if they use the same number of L2 caches then they will both have the same L2 cache score. A vector of numeric scores for all scheduling concerns uniquely identifies each placement that is distinct with respect to sharing of resources.

There are two additional pieces of information a scheduling concern needs in order to identify the important placements. The first is whether the concern's score is proportional to the user's cost, which is the case for resources like NUMA nodes because fewer nodes (lower score) means more containers can be packed onto a system. If a lower score for a resource only meant worse performance, we could simply discard placements with a lower score for that resource (all other scores being equal) from our list of important placements. But since we want users to be able to make cost-performance trade-offs, placements with lower scores but potentially lower cost could still be relevant. The second piece of information needed by a scheduling concern is whether the resource encompassed by a concern can ever have an inverse relationship with performance. For some resources, like

the L2 cache, a higher score is usually better, but for some workloads such as those showing cooperative cache sharing, a smaller score (using fewer L2 caches) may actually improve performance. For other resources, like the shared interconnect described below, a lower score will never improve performance and would not result in a lower cost for the user, so we can safely ignore placements with lower scores when everything else is equal.

In practice, a single scheduling concern may cover multiple shared resources because some resources are inseparable with respect to thread placement. Threads sharing a physical core via SMT typically share a cache, the instruction front-end, and functional units. In cases like this, a single scheduling concern is still sufficient.

Our AMD test system (shown in Figure 2.2) has multiple NUMA nodes, an asymmetric interconnect, and a form of SMT. For this system we developed the scheduling concerns shown in Table 2.1. For the L2/SMT and L3 concerns, the score for a particular placement can be calculated directly from information provided by the operating system. The OS also provides information on the interconnect topology, but it is simpler and more accurate to measure the aggregate bandwidth with a benchmark for each possible combination of nodes (we use *stream* [67] for our measurements). Each concern is relatively simple, easy to implement, and can be developed independently. Since it does not require a performance expert, we envision the specification of scheduling concerns being provided as part of system BIOS.

It is easy to see how scheduling concerns could be developed for other hard-ware resources. For example, a system with asymmetric CPUs could have a CPU concern where the score is the frequency of the CPUs in use, or a concern that accounts for some nodes being closer to I/O links, where the score is 1 if the nodes in use are near I/O links and 0 otherwise.

Next, from the concerns and hardware topology we need to derive the *important placements*. An important placement must have three properties: (1) conform to our balanced assumption, (2) be feasible: i.e., not assign more than one vCPU to a single hardware thread, and (3) not be superseded by a strictly better placement.

Given a score s and the number of vCPUs v, the balance property is encoded as  $v \mod s = 0$ , and the feasibility property is encoded as  $v/s \le Capacity$ , where capacity is the number of hardware threads available in a single instance of the re-

source: e.g. there are eight hardware threads per L3 cache on our AMD test system. We also define the *Count* of a concern as the total number of that resource on the system, so our AMD test system has an *L2Count* of 32 for example. The first step in generating important placements is generating the possible scores that satisfy the balance and feasibility requirements individually. This is done for each scheduling concern that can affect cost or have an inverse relationship with performance. For our AMD test system this step is shown in Algorithm 1.

The next step is computing possible packings of the system, i.e. combinations of placements that fill the entire machine. Recall that we already know how many vCPUs each instance/container will use (based on our assumptions in Section 2.2.2). Depending on the specific placement used, a container may or may not use all available NUMA nodes. If it does not use all available NUMA nodes, then more containers can be packed onto the system. This step computes the packings based on the possible scores generating in the previous step. Specifically, we are using the score of the scheduling concern that corresponds to the highest level of the hierarchy and our unit of resource allocation, which in our case is the L3 scheduling concern. The packings are generated with a recursive method shown in Algorithm 2.

Next, as shown in Algorithm 3, packings that are duplicates and packings that are not Pareto-efficient with respect to the interconnect score are filtered out (since the interconnect concern does not affect cost and cannot have an inverse relationship with performance). Because the L2 and L3 scores can affect cost or have an inverse relationship with performance, placements are not filtered based on them. Lastly, the placements that make up the remaining packings are "expanded" by calculating which L2 scores are feasible for the number of nodes in use, and then the complete placement is added to the list of important placements. If the system in question has a deeper hierarchy, with another scheduling concern below the L2 concern, for example, then the L2 scores would be expanded first and then the scheduling concern below it would be expanded based on the expanded and feasible L2 scores. In general, "score expansion" starts at the highest level of the hierarchy not including the scheduling concern used in generating packings, and then goes downward to the lowest level.

As an example of Pareto-efficient packing, on our AMD test system we know

#### **Algorithm 1** Generating possible L2 and L3 scores

```

L3Scores = List()

for i \leftarrow 1, L3Count do

if v/i \leq L3Capacity \land v \mod i = 0 then

L3Scores.append(i)

end if

end for

L2Scores = List()

for i \leftarrow 1, L2Count do

if v/i \leq L2Capacity \land v \mod i = 0 then

L2Scores.append(i)

end if

end for

return L3Scores, L2Scores

```

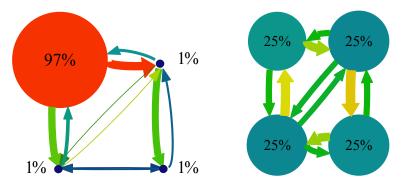

we need to keep the four-node placement that uses nodes  $\{2,3,4,5\}$  because it is the four-node placement with the highest interconnect score. Therefore the placement using nodes  $\{0,1,6,7\}$  is also an important placement and will be kept because it is the placement that can be packed with the best four-node placement. Continuing, suppose that we consider a four-node placement that uses nodes  $\{0,1,4,5\}$ . If we were to use this placement at runtime, the remaining set of four nodes, potentially used for another workload, is  $\{2,3,6,7\}$ . Both of these placements have poor interconnect scores, in part because there is a two-hop distance between nodes  $\{0,5\}$  and nodes  $\{3,6\}$ . Instead, we can pack the machine with a better combination of four-node placements:  $\{0,2,4,6\}$  and  $\{1,3,5,7\}$ . Using this observation, the vectors for placements  $\{0,2,4,6\}$  and  $\{1,3,5,7\}$  will be kept over the worse pair of four-node placements.

After this process is complete, we are left with the important placements. For our AMD system we have 12 of them: two 8-node placements (one sharing L2 caches and one not), two 2-node placements (with the best and second-best interconnect score), and eight 4-node placements (half sharing L2 caches, half not, and various interconnect scores relevant for packing). Our Intel test system (Figure 2.2), on the other hand, only uses an L2/SMT concern and an L3 concern. With 24 virtual cores per container, it has seven important placements which are all of the placements that satisfy the balance and feasibility constraints: a one node

#### Algorithm 2 Generating packings of placements

```

Packings = List()

procedure MAKEPACKINGS(L3Scores, NodesLeft, CurrentPacking)

for all L3S in L3Scores do

if L3S > len(NodesLeft) then

continue

end if

for all n in Combinations(NodesLeft, L3S) do

Remaining = NodesLeft - n

NewPacking = CurrentPacking.append(n)

if len(Remaining) > 0 then

MakePackings(L3Scores, Remaining, NewPacking)

else

Packings.append(NewPacking)

end if

end for

end for

end procedure

return Packings

```

placement sharing L2 caches, two 2-node placements, two 3-node placements, and two 4-node placements.

#### 2.4 Performance Predictions

Automatic model-building techniques learn how to map a set of features describing data to a predicted outcome. The outcome we would like to model is a vector of performance values in all important placements, relative to a baseline placement. For example, if there are three important placements, and the performance in the second and third is 20% and 30% better than that in the first baseline placement, the performance vector will be: [1.0,0.8,0.7]. Our data elements are executions of workloads in different placements, and the features are some metrics describing the execution.

One way to frame the problem is to predict a *performance category*. That is, assuming that our target workloads can be categorized according to their performance vectors, we can train the model to predict the category and then use the

## Algorithm 3 Generating important placements

```

Nodes = range(0, L3Count)

Packings = MakePackings(L3Scores, Nodes, List())

Remove duplicates from Packings

for all (a,b) in Permutations(Packings, 2) do

if L3 Scores in a \neq L3 Scores in b then

continue

end if

aIC = Sorted interconnect scores of a placements

bIC = Sorted interconnect scores of b placements

ToRemove = True

for i in range(0, len(aIC)) do

if aIC[i] > bIC[i] then

ToRemove = False

end if

end for

if ToRemove then

Remove a from Packings

end if

end for

ImportantPlacements = List()

for all Placements p in Packings do

n \leftarrow L2Count/L3Count

L3S = L3 Score of p

for all L2S in L2Scores do

if n \cdot L3S \ge L2S then

ImportantPlacements.append(p)

end if

end for

end for

return ImportantPlacements

```

category's average vector as the predicted outcome.

We begin by presenting an implementation of this idea (Section 2.4.1). Our first method runs a workload in two or three configurations in order to narrow down the performance category to which it belongs. Although this is not the final method we use, it demonstrates the fundamental benefits of using actual observations of performance as predictive features of the model. Our final method (Section 2.4.2) uses

performance observations in two configurations as input features into a machine learning (ML) model. Section 4.4 shows that relying only on hardware performance events (HPE) that may correlate with performance is not nearly as effective as using the measurements of actual performance.

## 2.4.1 Predicting Performance Categories

Although there is an infinite number of possible workloads and a complex interaction between scheduling concerns, we observed that workloads fall into a relatively small number of categories where each category has very similar performance vectors and is representative of a specific relationship to scheduling concerns. For example, workloads that are not memory intensive and are not adversely affected by sharing SMT contexts would belong to the same category (where thread placement does not matter). Another category would be one where using fewer NUMA nodes and fewer physical cores greatly hurts performance, and so on.

To discover these categories, we use the clustering algorithm k-means, which uses performance vectors as the elements. It partitions the elements into k clusters so as to minimize the within-cluster sum of squares (i.e., Euclidean distance) between the vectors. We select the value of k that maximizes the average Silhouette coefficient [6, 79] over all data points, which is the standard practice in the field.

The set of applications we experimented with are drawn from the NAS Parallel Benchmark suite [11], Parsec suite [20], the Metis map-reduce benchmarks [65], and BLAST [7]. Also included are the Linux kernel compile gcc benchmark, two Spark graph workloads, TPC-C [95] and TPC-H [96] on Postgres and a WiredTiger [4] BTree benchmark. Workloads were run using  $1 \times c$  containers and configured to use 16 vCPUs on the AMD system and 24 vCPUs on the Intel system (Fig. 2.2). Within containers, the number of application threads is set so as to achieve > 70% CPU utilization on each core, typical of what is done in practice.

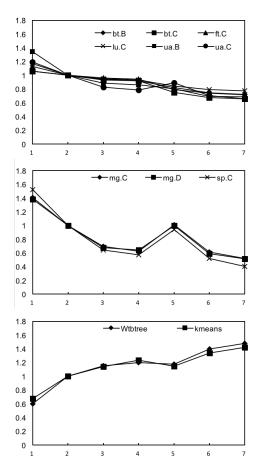

The workloads on our Intel test system were clustered into six groups. Figure 2.3 shows the performance by placement for the workloads found in three example clusters. Considering the similarity of performance curves in each cluster, it is clear that clustering has worked well in this case. An inspection of the remaining clusters and the clusters produced on our AMD test system showed similar results.

**Figure 2.3:** Performance by placement for workloads in three example clusters on Intel. The x-axis shows the placement ID. The y-axis shows performance relative to the baseline placement (#2).

This procedure helps to determine the quality and completeness of the training workloads. If k-means cannot create good clusters, then the training set could be incomplete. In our case the quality of clusters is good overall, but some clusters, e.g., the one with *kmeans* and *WTbtree*, contains only two elements and could benefit from adding other workloads.

It also leads to an intuitive method for making performance predictions: run the workload in several placements by trying them during the first few seconds of the execution without interrupting the workload, measure the performance in each, and based on those results use the process of elimination to determine the category to which it belongs. Once we know the category we can use category's average performance per-placement as the predictions.

The workload must first be run on the baseline placement; our performance measurements are all normalized to this placement so it is required but does not provide any information about the workload. Every placement tried thereafter helps narrow down the category to which the workload belongs (if the performance is outside of the range of performance values seen during training for a particular category then we can conclude it does not belong to that category) until only the workload's predicted category remains. The full algorithm for determining a workload's category, which we call the *iterative method*, is shown in Algorithm 4.

For an arbitrary system, the worst-case number of measurement placements needed to complete Algorithm 4 is min(n-1,k) where n is the number of important placements and k is the number of clusters. This worst-case happens when only a single cluster can be eliminated per measurement placement. Real-world systems are likely to have a much better worst-case though, such as our test systems which only require three placements in the worst-case. This is because there are likely to be some correlations between clusters and correlations between scheduling concerns. For example consider a system that has cluster A, cluster B, and some number of other clusters. Cluster A prefers having more L3 caches and more L2 caches, and because memory intensiveness affects both L2 and L3 cache preferences there is no cluster that prefers more L3 caches and prefers fewer L2 caches. Cluster B prefers more L2 caches but does not care how many L3 caches it has. A single measurement placement showing that a workload prefers fewer L2 caches eliminates both cluster A and cluster B. Similarly a single placement could eliminate both cluster A or B and clusters that prefer fewer L2 caches. In this way we are likely to avoid the theoretical worst-case on real systems.

On our test systems the iterative method requires trying only two or three placements (including the baseline) to determine a workload's category and produces fairly accurate predictions. For example, 29 out of the 41 workloads on our Intel test system have predictions within 6% of the actual performance, but the other workloads have at least one placement that has a prediction error around 20%.

The key insight we draw from the iterative method is that performance mea-

surements from multiple placements have very high predictive power due to the fact that workloads tend to belong to distinct categories with respect to their performance behavior. This motivates our approach of using performance measurements as inputs into a ML model, which is described in the next section.

Algorithm 4 Iterative method for determining performance category

```

for all Cluster c in Clusters do

for each Placement p do

min = min. performance within Cluster for p

max = max. performance within Cluster for p

Interval of c for placement = [min, max]

end for

end for

Excluded = List()

Run baseline placement and measure performance

while len(excluded) < len(c)-1 do

Pop next placement from p

Run next placement and measure performance

for each Interval for placement do

if Performance is outside interval then

Append cluster belonging to interval to excluded

end if

end for

if Performance is outside all intervals then

Find closest interval and exclude all other clusters

end if

if All clusters excluded then

Return no cluster

end if

end while

return cluster not in excluded

```

# 2.4.2 Predicting Performance with Machine Learning

While the method of predicting performance categories using the process of elimination is intuitive and robust, it uses a category's average as the predicted outcome, which is a rather rough measure. We found that we can achieve higher accuracy with a more refined modeling technique. Our final approach directly predicts per-

formance vectors using a machine learning model, a multi-output *Random Forest* regressor. In other words, the model produces one predicted output per placement. As inputs, the model uses performance measurements observed in two different placements: a baseline and one additional. These placements were selected during the model training as those yielding the highest accuracy.

The random forest model has significantly better accuracy for this problem than other regression models like neural networks, support vector machines, and nonlinear regression. Many regression models rely on an assumption that the data fits a particular shape (for example, logarithmic or polynomial) but the data in our case has many instances of step-function and piece-wise behavior. A random forest requires no assumption of the shape of the data. Neural networks do not have this assumption either but they tend to require much more training data to be effective.

An alternative to regression is a search-based machine learning approach. In this case, a machine learning algorithm could continually try placements until the goal is reached. The benefit of this approach is that potentially it would not need to rely on training workloads. A major downside though is that it would require many more placements to be tried which requires migrating memory and would have a prohibitive performance cost. For this reason we focused on the regression approach.

Finally, to evaluate our new approach relative to the best known practices we also train a multi-output *Random Forest* regressor using HPEs observed in a single baseline placement as input features. The best baseline placement was identified during training.

Modern machines have many hundreds of HPEs, some more than 1000 [103]. Sampling that many online cannot be done without large sampling errors. One option is to include the list of important HPEs in the specification of each scheduling concern. This assumes that the engineer providing the specification somehow knows which counters would work best — an assumption we found to be not in the spirit of maximally automating the prediction process. Another approach is to obtain measurements with all possible HPEs during training and use feature selection methods to identify the best predictors, similarly to [41]. This approach is automatic, but increases the training time from hours to weeks. For example on our Intel machine with nearly 1000 performance events, the time to measure all coun-

ters for our training set while ensuring acceptable sampling error would amount to 66 days.

Instead we used a combination of the manual and automatic approaches. We started with a set of plausible features (41 HPE derived metrics on our Intel test system and 25 on our AMD test system) covering cache, memory, TLB, interconnect, and pipeline behavior, which are metrics commonly used in similar work. We then used *Sequential Forward Selection* [39, 54] (SFS) to pick the best ones. SFS involves iterating over all potential features, selecting the one that improves prediction accuracy the most, and then repeating this process until prediction accuracy no longer improves. On the AMD test system the SFS process results in four features: the L3 cache misses per cycle, the L1 cache miss rate per instruction, the TLB misses per cycle, and the cache sharing percentage (calculated from the states of cache lines as they are evicted). On the Intel test system, three features were selected: the percentage of stall cycles where at least one memory request was pending, the cache sharing percentage (calculated from the states of cache lines as they are inserted), and the L2 cache misses per instruction caused by the prefetcher.

We also tried adding both performance measurements and HPEs as model inputs, but this did not improve accuracy at all on our AMD system and only marginally improved accuracy for two workloads on our Intel system. In the end we had two model variants to compare: the first one used as inputs the actual performance measurements observed in two placements, and the second one used only the HPEs observed in a single placement.

#### 2.4.3 Results

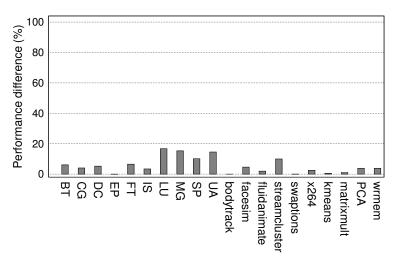

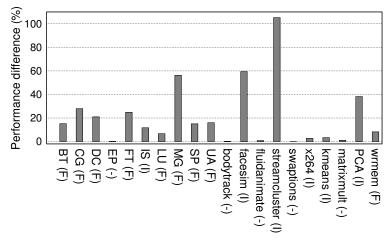

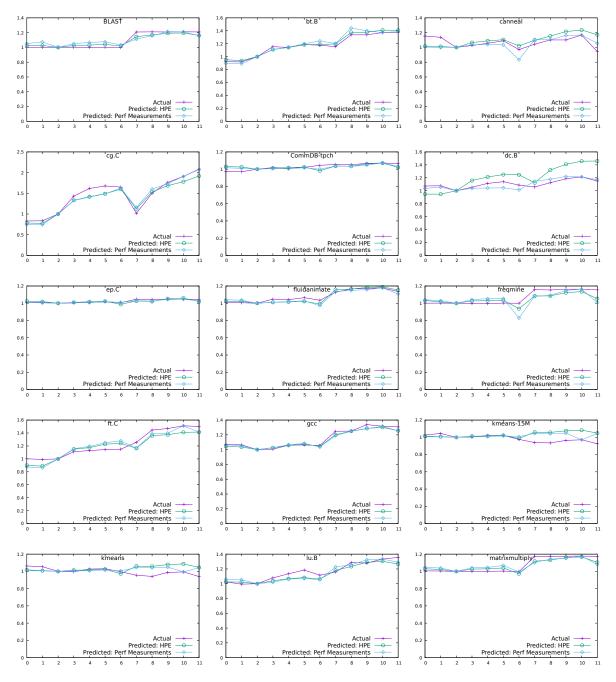

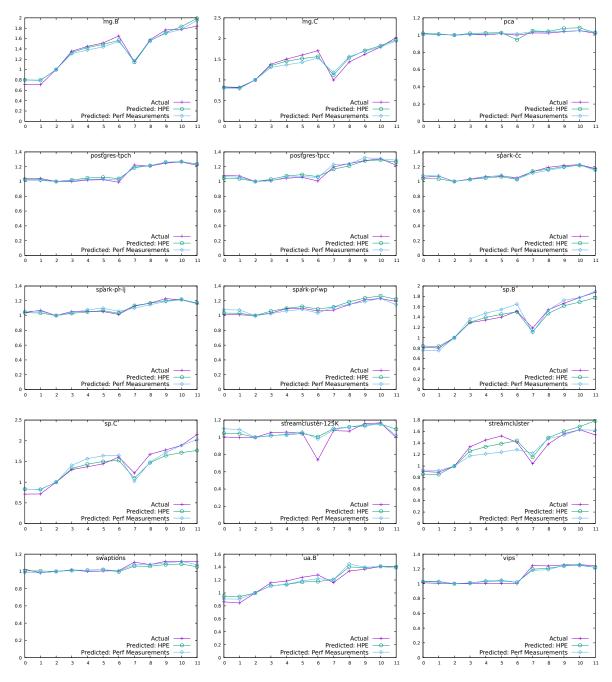

The full per-benchmark performance prediction results for the AMD test system are provided in the appendix in Figure A.4 and for the Intel test system in Figure A.5. The figures for the benchmarks discussed in this section are also provided here for ease of reference.

The results are per-application cross-validated. For example, when training the model that will be used for predicting a Spark workload neither the data from *spark-cc* (a Spark connected components algorithm run on the LiveJournal database) nor *spark-pr-lj* (a PageRank algorithm run on the LiveJournal database) is included

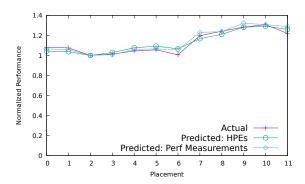

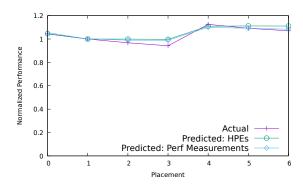

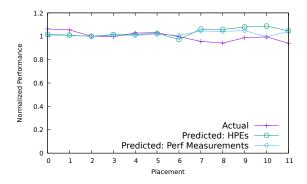

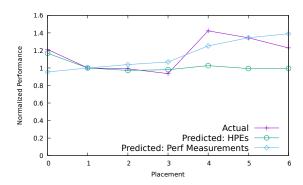

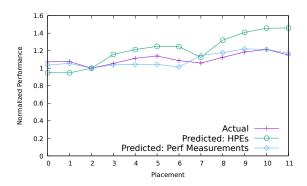

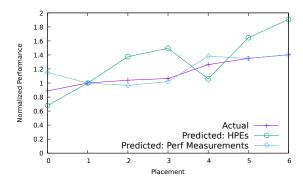

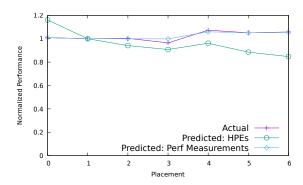

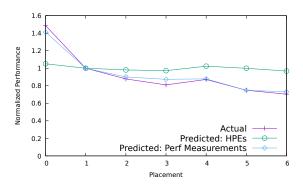

**Figure 2.4:** Prediction results for *postgres-tpcc* on the AMD test system.

**Figure 2.5:** Prediction results for *spark-pr-lj* on the Intel test system.

Figure 2.6: Prediction results for *kmeans* on the AMD test system.

**Figure 2.7:** Prediction results for *canneal* on the Intel test system.

**Figure 2.8:** Prediction results for *dc.B* on the AMD test system.

**Figure 2.9:** Prediction results for *ft.C* on the Intel test system.

**Figure 2.10:** Prediction results for *frequine* on the Intel test system.

**Figure 2.11:** Prediction results for *kmeans* on the Intel test system.

**Figure 2.12:** Prediction results for *WTbtree* on the Intel test system.

in the training.

Overall the accuracy when using only the actual performance measurements as model features is high. The predicted performance is within 4.4% of actual on average on the AMD system, and within 6.6% on Intel. Postgres running the TPCC benchmark (*postgres-tpcc*) on the AMD test system (Figure 2.4) and *spark-pr-lj* on the Intel test system (Figure 2.5) are examples where the predictions are very accurate.

There are a few cases where the training set did not include any workloads that behaved similarly to the predicted benchmark, which results in poor predictions. For example *kmeans* on the AMD system (Figure 2.6), which was the only benchmark in our training set that preferred SMT, or *canneal* on the Intel system (Figure 2.7). As explained in Section 2.4, we can identify weaknesses in the training set using the performance clusters, so it is straightforward to figure out where extra time and effort could be spent on adding new training workloads.

Prediction accuracy when using only the HPEs from a single placement was a lot less reliable. On the AMD system it produced good results overall, but the accuracy was still noticeably worse for dc.B (Figure 2.8) compared to the model variant that relied only on actual performance measurement. The real shocker is the results on Intel, where the model relying only on HPEs produced many poor predictions. It completely missed the performance trend for ft.C (Figure 2.9) and freqmine (Figure 2.10), produced errors of over 40% for ft.C (Figure 2.11) and ft.C (Figure 2.12), and is noticeably worse for several other workloads. Using both the actual performance measurements and HPEs yielded small accuracy improvements on the Intel system, but made no difference on the AMD system.

An example of why HPEs observed in a single placement could have poor predictive power, and one of the reasons why the Intel system produced worse predictions, is predicting the effect of inter-thread communication latency. There is a huge latency difference for communication between a single-node placement and placements including more than one node. For some applications, reduced inter-thread communication latency when all threads are running on a single node has a major performance impact, as is the case for *WTbtree*. Separating the sensitivity to latency from overall memory intensiveness (which can be measured by the cache miss rate) is difficult to do with HPEs. Similarly, it is also very difficult to deter-

mine if a workload's working set will fit in a given number of L3 caches by only measuring HPEs on a single placement. We conclude that, contrary to prior belief, single-placement HPE observations are not reliable features for modelling performance on multicore NUMA systems.

# 2.5 Using the Model in Practice

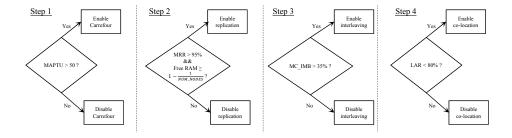

There are many ways in which data center operators can use our model. To illustrate one potential use case we set up a scenario where the user would like to pack as many instances of a given virtual container into a physical server while respecting a performance target. To assess the overheads, we measure the costs of container migration on our test systems (the overhead of prediction inference is negligible).

## 2.5.1 A Potential Use Case