# INVESTIGATION OF BRIDGELESS SINGLE-PHASE SOLUTIONS FOR AC-DC POWER FACTOR CORRECTED CONVERTERS

by

Md. Muntasir Ul Alam

M.E.Sc., Western University, 2010 B.Sc., Islamic University of Technology, 2006

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

in

The College of Graduate Studies

(Electrical Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

(Okanagan)

July 2017

© Md. Muntasir Ul Alam, 2017

The undersigned certify that they have read, and recommend to the College of Graduate Studies for acceptance, a thesis entitled:

# INVESTIGATION OF BRIDGELESS SINGLE-PHASE SOLUTIONS FOR AC-DC POWER FACTOR CORRECTED CONVERTERS

Submitted by Md. Muntasir Ul Alam in partial fulfillment of the requirements of The degree of DOCTOR OF PHILOSOPHY.

Dr. Wilson Eberle, Associate Professor, School of Engineering, UBC

Supervisor, Professor

Dr. Thomas Johnson, Associate Professor, School of Engineering, UBC

**Supervisory Committee Member, Professor**

Dr. Loïc Markley, Assistant Professor, School of Engineering, UBC Supervisory Committee Member, Professor

Dr. Shahria Alam, Associate Professor, School of Engineering, UBC University Examiner, Professor

Dr. Yunwei Li, Professor, Faculty of Engineering, University of Alberta External Examiner, Professor

17 July 2017

(Date submitted to Grad Studies)

**Additional Committee Members include:**

Dr. Sumi Siddiqua, Associate Professor, School of Engineering, UBC

Neutral Chair

#### **Abstract**

In modern power supplies and battery chargers, a front-end power factor correction (PFC) AC-DC converter is used to comply with regulatory requirements for input current harmonics. The prevalence of standards and recommended practices to meet harmonic current limits has gained, and continues to gain, momentum over recent years. Additionally, the improvement of overall converter efficiency is critical for the emergence and acceptance of these converter technologies, to meet the standard of efficiency and power factor requirements.

This dissertation presents some innovative solutions for bridgeless non-isolated and isolated PFC AC-DC converters. All proposed converter solutions realize bridgeless converter operation to reduce conduction losses and operate in hybrid resonant pulse-width-modulation (HRPWM) mode. The PWM switches share the same gating signal, so the converter does not need extra circuitry to sense the positive and negative ac input line-cycle operation.

The first contribution is a non-isolated bridgeless AC-DC converter, which has inherent inrush current-limiting capabilities. The converter architecture also enables simple implementation of lightning and surge protection systems. Moreover, this converter can survive sustained over-voltage events and can limit the voltage stress on the converter and downstream components.

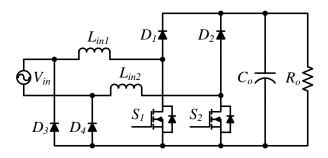

The second contribution is a non-isolated bridgeless AC-DC converter, which realizes soft-switching operation to reduce switching losses. This converter can operate at high switching frequency to increase power density.

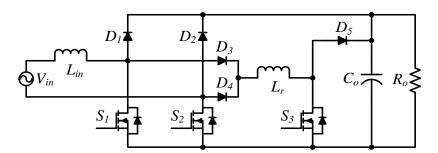

The third contribution is a three-level non-isolated bridgeless AC-DC converter, which has high voltage gain. This converter also provides soft-switching operation of all the power devices. Due to the three level architecture, all commutations occur with a voltage level equivalent to half the output voltage, which further reduces switching losses. This converter can utilize lower voltage rated devices, which reduces system cost.

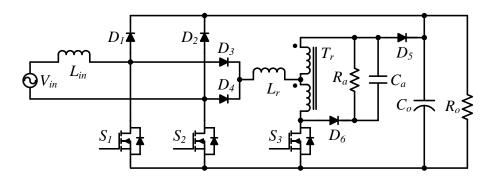

The final contribution is a single-stage bridgeless isolated AC-DC converter. This converter shows low conduction loss due to bridgeless operation and low voltage stress of the secondary diodes, low switching loss due to soft-switching operation, and a transformer that has no dc magnetizing current and does not store energy. These characteristics minimize the transformer size and increases transformer efficiency.

#### **Preface**

I am the lead investigator for this research work, responsible for performing literature survey, topology investigation, theoretical analysis, design, simulation and experimentation. This work was done under the guidance of my thesis supervisor Dr. Wilson Eberle. This work was also supervised by Dr. Fariborz Musavi, Dr. Deepak Gautam, Mr. Chris Botting and Mr. Nicholas Dohmeier of Delta-Q Technologies Corp. This thesis contains four contribution chapters that present results that have been published or going to be submitted for consideration in the form of IEEE refereed papers and scientific journals of which I am the lead author.

### **Table of Contents**

| Abstract                                                               | iii   |

|------------------------------------------------------------------------|-------|

| Preface                                                                | v     |

| Table of Contents                                                      | vi    |

| List of Tables                                                         | ix    |

| List of Figures                                                        | X     |

| List of Abbreviations                                                  | XV    |

| Acknowledgements                                                       | xvii  |

| Dedication                                                             | xviii |

| 1 Introduction                                                         | 1     |

| 1.1 General Background                                                 | 3     |

| 1.1.1 Total Harmonic Distortion                                        | 3     |

| 1.1.2 Power Factor                                                     | 3     |

| 1.1.3 Hard-Switched Converters                                         | 6     |

| 1.1.4 Soft-Switched Converters                                         | 7     |

| 1.2 Research Motivation                                                | 8     |

| 1.3 Thesis Organization                                                | 9     |

| 2 Literature Review                                                    | 11    |

| 2.1 Non-isolated AC-DC PFC Topologies                                  | 12    |

| 2.1.1 Passive AC-DC PFC Topologies                                     | 12    |

| 2.1.2 Active AC-DC PFC Topologies                                      | 14    |

| 2.2 Single-stage isolated AC-DC PFC Topologies                         | 20    |

| 2.3 Summary                                                            | 23    |

| 3 A Hybrid Resonant Bridgeless AC-DC Power Factor Correction Converter | 25    |

| 3.1 Overview                                                           | 25    |

| 3.2 Proposed Converter Operating Principles                            | 27    |

| 3.2.1 Resonant Frequency Operation                                     | 28    |

| 3.2.2 Above Resonance Operation                                        | 29    |

| 3.2.3 Below Resonance Operation                                        | 31    |

| 3.3 Modes of Operation                                                 | 33    |

| 3.4 Operation during Startup and In-rush Considerations                | 36    |

| 3.5 Analysis and Design                                                | 37    |

| 3.5.1 DC Voltage Conversion Ratio                                      | 37    |

|                                                                        | vi    |

| 3.5.3 Design Example                                        |                                   |

|-------------------------------------------------------------|-----------------------------------|

| 3.7 Summary                                                 |                                   |

| 4 A Soft-Switching Bridgeless AC-DC Power Factor Correcti   | 50 Converter                      |

|                                                             |                                   |

|                                                             | 51                                |

| 4.1 Overview                                                | 56                                |

| 4.2 Modes of Operation                                      |                                   |

| 4.3 Analysis and Design                                     | 56                                |

| 4.3.1 DC Voltage Conversion Ratio                           |                                   |

| 4.3.2 Voltage Stress Analysis                               | 56                                |

| 4.3.3 ZVS Condition for the Switches                        | 57                                |

| 4.3.4 Design Methodology                                    | 58                                |

| 4.3.5 Converter Loss Analysis                               | 59                                |

| 4.4 Experimental Results                                    | 61                                |

| 4.5 Summary                                                 | 71                                |

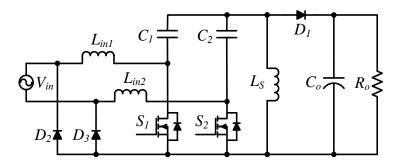

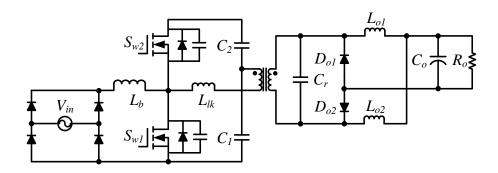

| 5 A High Voltage Gain Soft-Switching Bridgeless AC-DC Po    | wer Factor Correction Converter72 |

| 5.1 Overview                                                | 72                                |

| 5.2 Modes of Operation                                      | 73                                |

| 5.3 Analysis and Design                                     | 78                                |

| 5.3.1 DC Voltage Conversion Ratio                           | 78                                |

| 5.3.2 ZVS Requirements for the Switches                     | 79                                |

| 5.3.3 Design Methodology                                    | 80                                |

| 5.3.4 Converter Loss Analysis                               | 80                                |

| 5.4 Experimental Results                                    | 82                                |

| 5.5 Summary                                                 | 88                                |

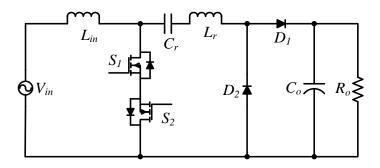

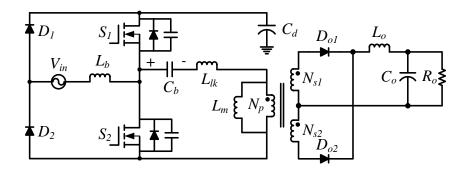

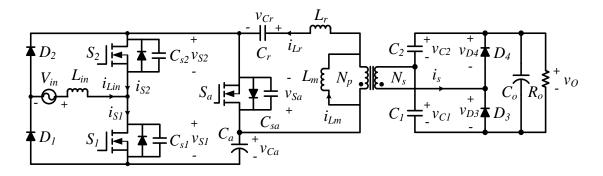

| 6 A Soft-Switching Bridgeless Isolated Single-Stage AC-DC F | FC Converter90                    |

| 6.1 Overview                                                | 90                                |

| 6.2 Modes of Operation                                      | 91                                |

| 6.3 Analysis and Design                                     | 96                                |

| 6.3.1 DC Voltage Conversion Ratio                           | 96                                |

| 6.3.2 ZVS Conditions for the Switches                       | 97                                |

| 6.4 Simulation Results                                      | 99                                |

| 6.5 Summary                                                 | 103                               |

| 7   | Conclusions                                                                  | 104 |

|-----|------------------------------------------------------------------------------|-----|

|     | 7.1.1 A Hybrid-Resonant Bridgeless AC-DC Power Factor Correction Converter   | 104 |

|     | 7.1.2 A Soft-Switching Bridgeless AC-DC PFC Converter                        | 104 |

|     | 7.1.3 A High Voltage Gain Soft-Switching Bridgeless AC-DC PFC Converter      | 105 |

|     | 7.1.4 A Soft-Switching Bridgeless Single-stage AC-DC PFC Converter           | 106 |

|     | 7.1.5 Comparison and Feature Summary of the Proposed Topologies              | 106 |

| 7   | 7.2 Future Work                                                              | 107 |

|     | 7.2.1 Experimental Validation of Bridgeless Single-stage AC-DC PFC Converter | 107 |

|     | 7.2.2 Interleaved Soft-switching AC-DC PFC Converter                         | 107 |

|     | 7.2.3 High Frequency Converter Operation                                     | 108 |

| Ref | ferences                                                                     | 109 |

| Ap  | pendix                                                                       | 115 |

## **List of Tables**

| Table 3.1 Design specifications                                     | 38  |

|---------------------------------------------------------------------|-----|

| Table 3.2 List of key converter components                          | 40  |

| Table 4.1 Design Specifications                                     | 58  |

| Table 4.2 Key components for the HRPWM converter.                   | 62  |

| Table 4.3 Key components for the conventional boost PFC converter   | 62  |

| Table 5.1 Design Specifications                                     | 80  |

| Table 5.2 Key components for the high gain ZVS HRPWM converter.     | 82  |

| Table 5.3 Key components for the conventional PFC converter.        | 82  |

| Table 7.1 Comparison and feature summary of the proposed topologies | 107 |

## **List of Figures**

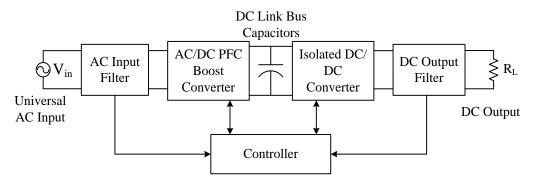

| Figure 1.1 Simplified system block diagram of a universal two-stage converter system                 | 2  |

|------------------------------------------------------------------------------------------------------|----|

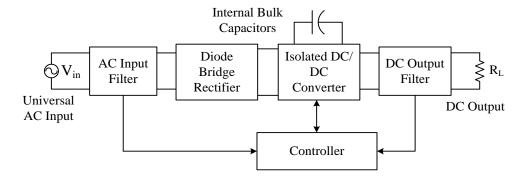

| Figure 1.2 Simplified system block diagram of a universal single-stage converter system              | 2  |

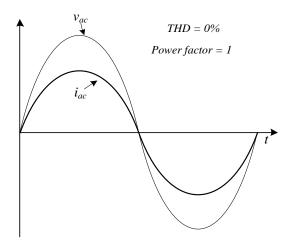

| Figure 1.3 Ideal input current and voltage with unity power factor and no current distortion         | 5  |

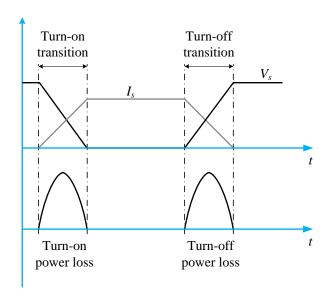

| Figure 1.4 Turn-on and turn-off transition in a hard-switched converter.                             | 6  |

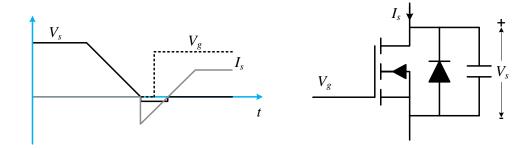

| Figure 1.5 Zero Voltage Switching (ZVS)                                                              | 7  |

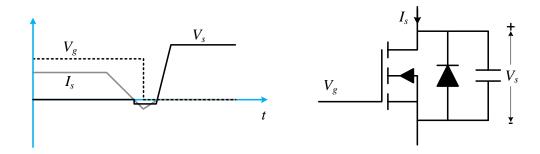

| Figure 1.6 Zero Current Switching (ZCS).                                                             | 8  |

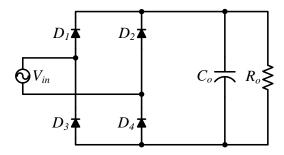

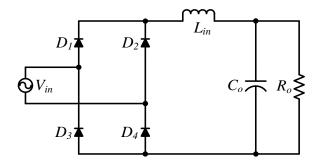

| Figure 2.1 Uncontrolled full-wave rectifier.                                                         | 13 |

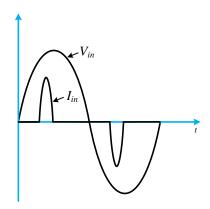

| Figure 2.2 $V_{in}$ and $I_{in}$ of uncontrolled full-wave rectifier with capacitive filter.         | 13 |

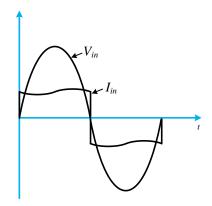

| Figure 2.3 Uncontrolled full-wave rectifier with inductive filter                                    | 14 |

| Figure 2.4 $V_{in}$ and $I_{in}$ of uncontrolled full-wave rectifier with inductive filter           | 14 |

| Figure 2.5 Conventional boost PFC converter.                                                         | 15 |

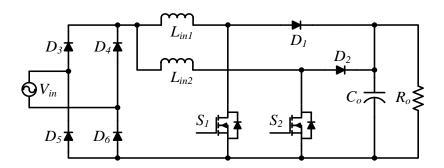

| Figure 2.6 Interleaved boost PFC converter.                                                          | 16 |

| Figure 2.7 Bridgeless boost PFC converter.                                                           | 16 |

| Figure 2.8 Semi-bridgeless boost PFC converter                                                       | 17 |

| Figure 2.9 Soft-switching bridgeless boost PFC converter proposed in [34].                           | 17 |

| Figure 2.10 Soft-switching bridgeless boost PFC converter proposed in [35].                          | 18 |

| Figure 2.11 Totem-pole PFC boost converter.                                                          | 18 |

| Figure 2.12 Converter topology proposed in [40]                                                      | 19 |

| Figure 2.13 Converter topology proposed in [46]                                                      | 19 |

| Figure 2.14 Converter topology proposed in [54]                                                      | 20 |

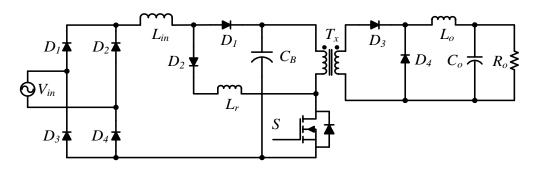

| Figure 2.15 CCM single-stage PFC topology proposed in [56], [57].                                    | 21 |

| Figure 2.16 CCM single-stage PFC topology proposed in [58]                                           | 21 |

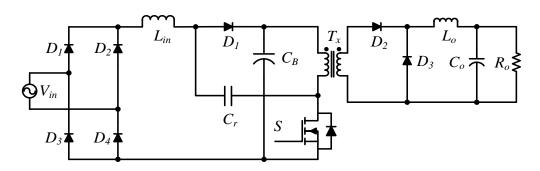

| Figure 2.17 ZVZCS single-stage PFC topology proposed in [61]                                         | 22 |

| Figure 2.18 Bridgeless single-stage half-bridge PFC topology proposed in [65]                        | 23 |

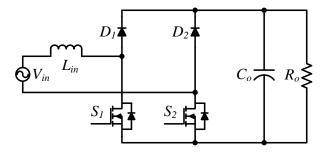

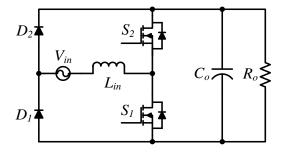

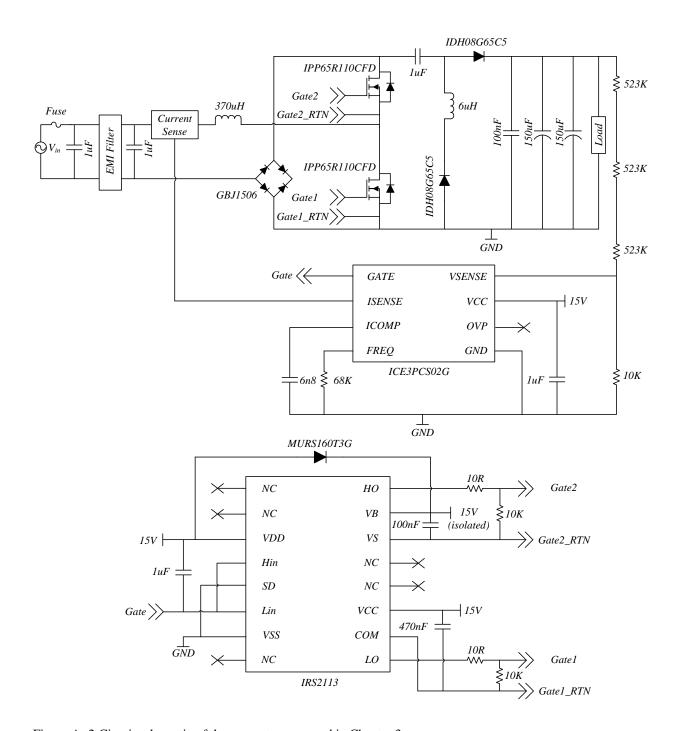

| Figure 3.1 Proposed HRPWM PFC converter.                                                             | 28 |

| Figure 3.2 Waveforms for gating signal and current through $S_1$ and $D_2$ during resonant frequency |    |

| operation.                                                                                           | 29 |

| Figure 3.3 Converter operation during $t_1$ - $t_2$                                                  | 29 |

| Figure 3.4 Waveforms for gating signal and current through $S_1$ and $D_2$ during above-resonance    |    |

| operation.                                                                                           | 30 |

| Figure 3.5 Converter operation during $t_1$ - $t_2$                                                  | 30 |

| Figure 3.6 Converter operation during t <sub>2</sub> -t <sub>4</sub>                                 | 31 |

| Figure 3.7 V | Waveforms for gating signal and current through $S_1$ and $D_2$ during below-resonance                        |    |

|--------------|---------------------------------------------------------------------------------------------------------------|----|

| o            | peration.                                                                                                     | 32 |

| Figure 3.8 C | Converter operation during $t_1$ - $t_2$                                                                      | 32 |

| Figure 3.9 F | Proposed HRPWM converter waveforms in CCM.                                                                    | 34 |

| Figure 3.10  | HRPWM bridgeless topology conduction path during <i>Interval-1</i>                                            | 34 |

| Figure 3.11  | HRPWM bridgeless topology conduction path during <i>Interval-2</i>                                            | 35 |

| Figure 3.12  | HRPWM bridgeless topology conduction path during <i>Interval-3</i>                                            | 35 |

| Figure 3.13  | Inrush current path for positive line cycle.                                                                  | 36 |

| Figure 3.14  | Equivalent circuit during startup neglecting the low impedance of $C_o$ .                                     | 36 |

| Figure 3.15  | Proposed converter experimental prototype.                                                                    | 40 |

| Figure 3.16  | Proposed converter experimental waveforms at 5ms/div of input voltage, $V_{in}$ (ch3: 50                      |    |

|              | V/div), input current, $I_{in}$ (ch 1: 10 A/div) and output voltage, $V_o$ (ch2: 200 V/div) at $V_{in}$ =     |    |

|              | 120 V, $V_o = 400$ V, $P_o = 650$ W and $f_s = 70$ kHz                                                        | 41 |

| Figure 3.17  | Proposed converter experimental waveforms at $5\mu s/div$ of voltage across switch $S_I$ , $V_{SI}$           |    |

|              | (ch2: 100 V/div) and gating signal for $S_I$ , $V_g$ (ch3: 5 V/div) at $V_{in} = 120$ V, $V_o = 400$ V, $P_o$ |    |

|              | = 650 W and $f_s$ = 70 kHz.                                                                                   | 42 |

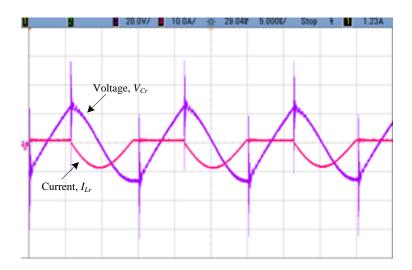

| Figure 3.18  | Proposed converter experimental waveforms at $5\mu s/div$ of voltage across capacitor $C_r$ , $V_{Cr}$        |    |

|              | (ch 3: 20 V/div) and current through inductor $L_r$ , $I_{Lr}$ (ch 4: 10 A/div) at $V_{in} = 120$ V, $V_o =$  |    |

|              | 400 V, $P_o = 650$ W and $f_s = 70$ kHz                                                                       | 43 |

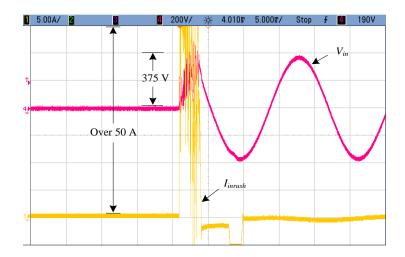

| Figure 3.19  | Conventional boost converter experimental waveforms at 5ms/div of inrush current, $I_{inrush}$                |    |

|              | (ch 1:5A/div), and input voltage, $V_{in}$ (ch 4:200V/div) at $V_{in} = 265$ V, $V_o = 0$ V                   | 43 |

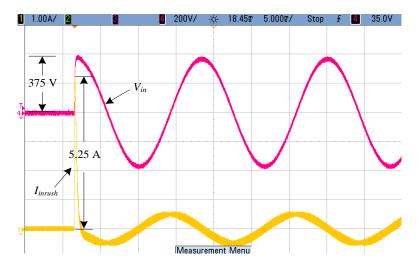

| Figure 3.20  | Proposed converter experimental waveforms at 5ms/div of inrush current, $I_{inrush}$ (ch                      |    |

|              | 1:1A/div), and input voltage, $V_{in}$ (ch 4:200V/div) at $V_{in} = 265$ V, $V_o = 0$ V                       | 44 |

| Figure 3.21  | Conventional boost converter experimental waveforms at 5ms/div of withstand input                             |    |

|              | voltage, $V_{in}$ (ch1: 200 V/div), voltage across boost switch, $V_s$ (ch 2: 200 V/div) and output           |    |

|              | voltage, V <sub>o</sub> (ch4: 100 V/div)                                                                      | 45 |

| Figure 3.22  | Proposed converter experimental waveforms at 5ms/div of with<br>stand input voltage, $V_{in}$                 |    |

|              | (ch1: 200 V/div), voltage across boost switch, $V_{sI}$ (ch 2: 200 V/div), voltage across                     |    |

|              | resonant capacitor $C_r$ , $V_{Cr}$ (ch 3: 100 V/div) and output voltage, $V_o$ (ch4: 100 V/div)              | 45 |

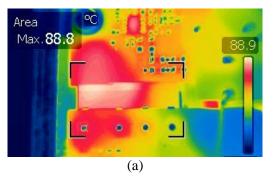

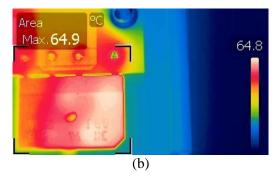

| Figure 3.23  | Thermal image of diode bridge rectifier of boost PFC converter at 650W.                                       | 46 |

| Figure 3.24  | Thermal image of diode bridge rectifier of proposed converter at 650W.                                        | 46 |

| Figure 3.25  | Proposed HRPWM converter measured efficiency as a function of output power at $f_s = 70$                      |    |

|              | kHz.                                                                                                          | 47 |

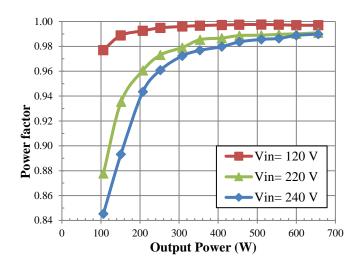

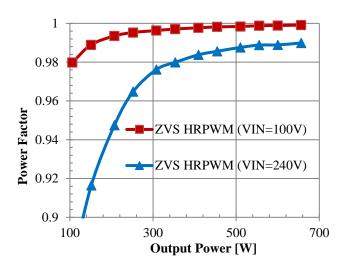

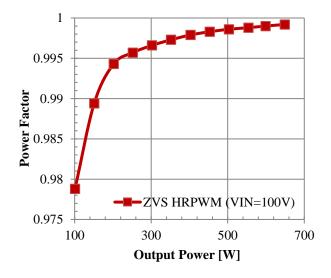

| Figure 3.26 Proposed HRPWM converter power factor as a function of output power at $f_s$ = 70 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

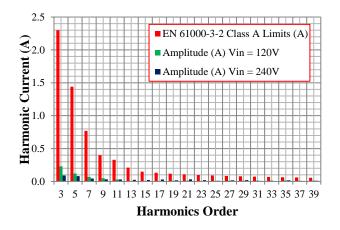

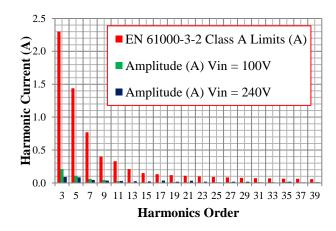

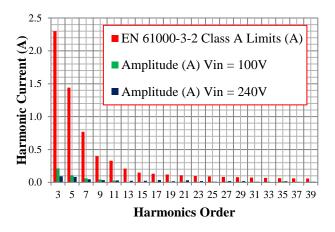

| Figure 3.27 Input current harmonics at $V_{in}$ = 120 V and 240 V at full load condition for proposed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       |

| converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                    |

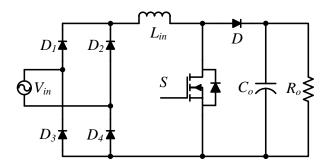

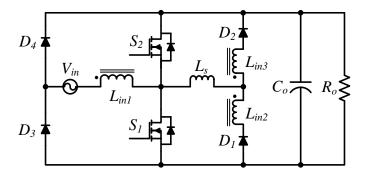

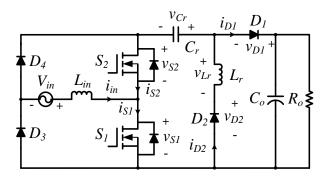

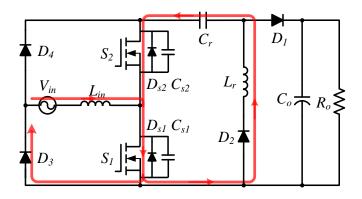

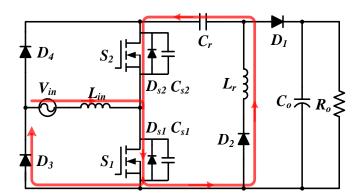

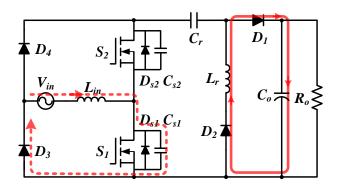

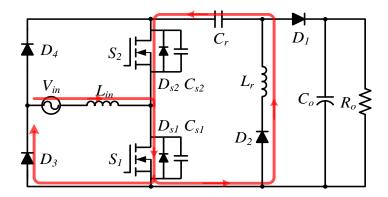

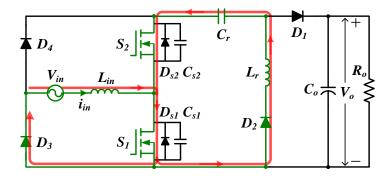

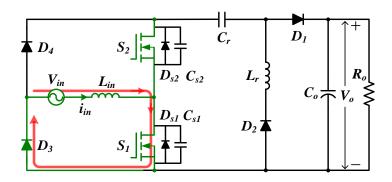

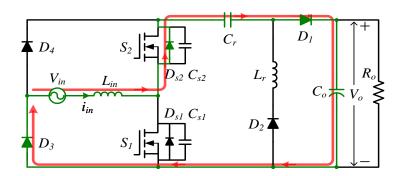

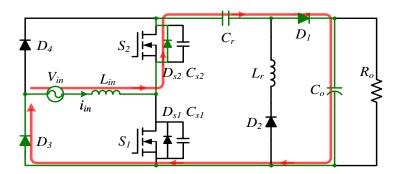

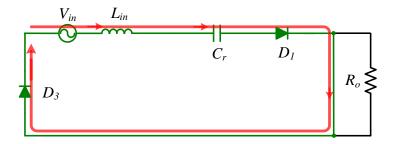

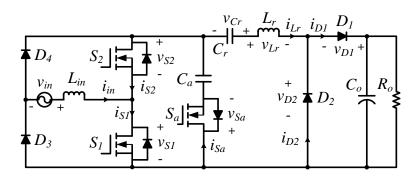

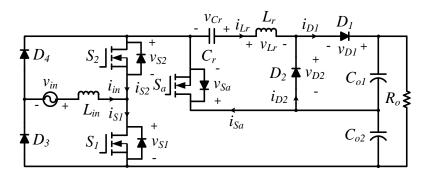

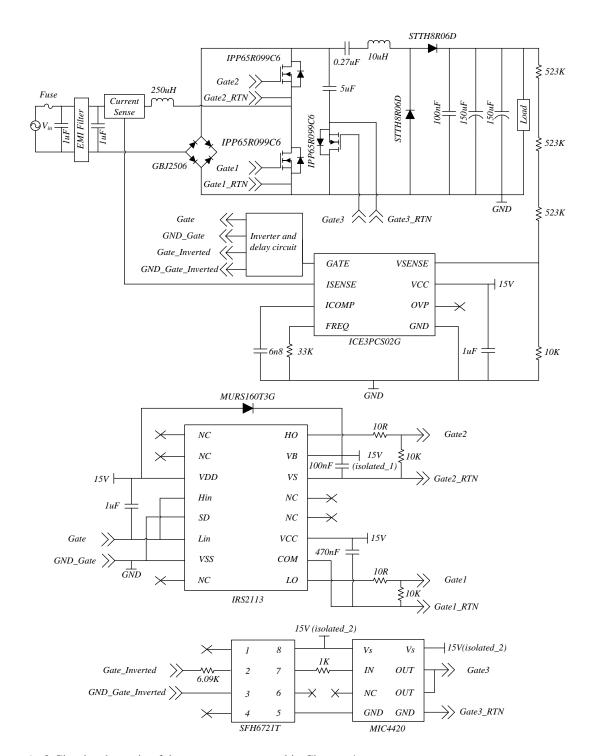

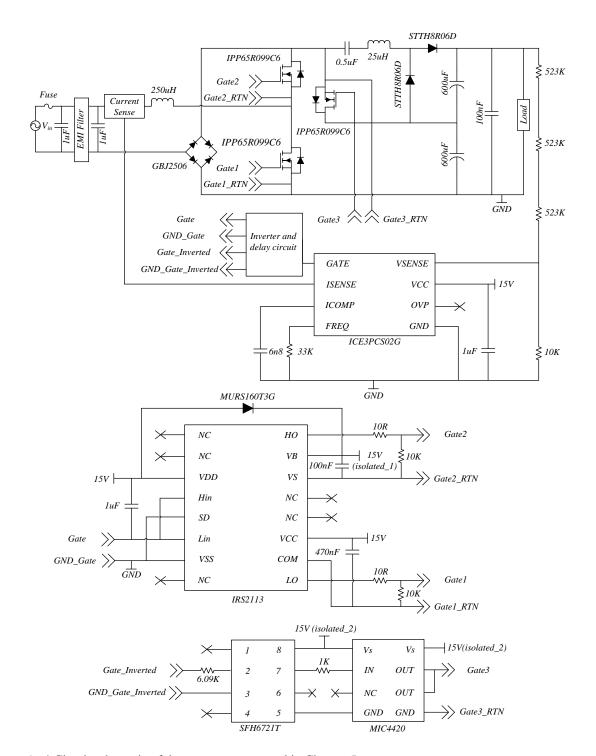

| Figure 4.1 Proposed soft-switching bridgeless AC-DC PFC converter topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51                    |

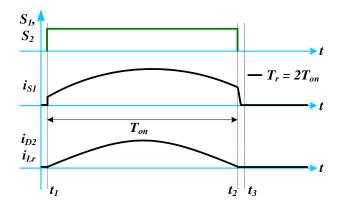

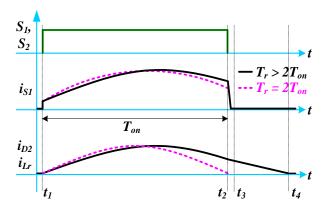

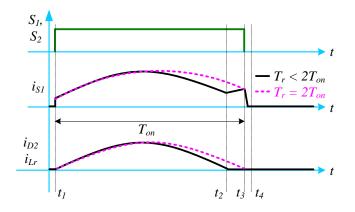

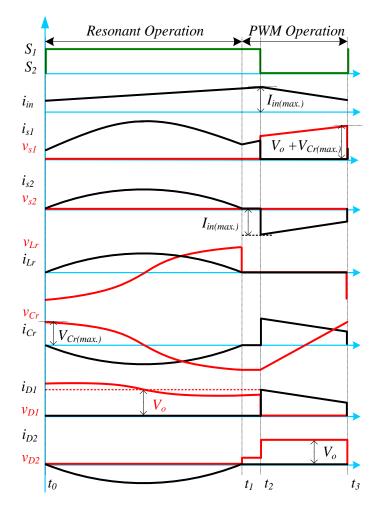

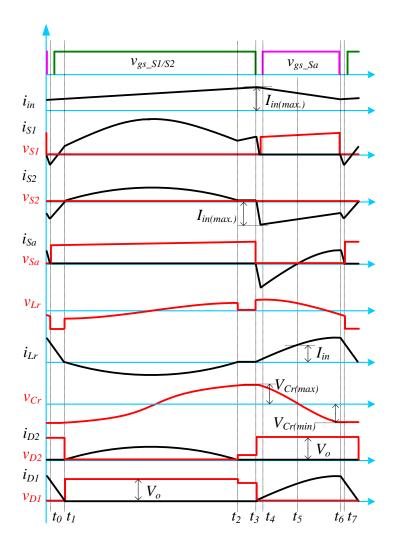

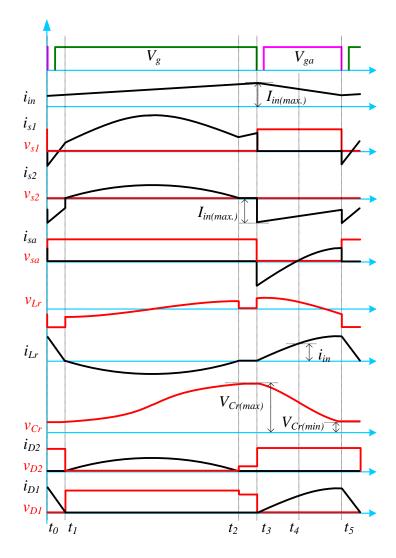

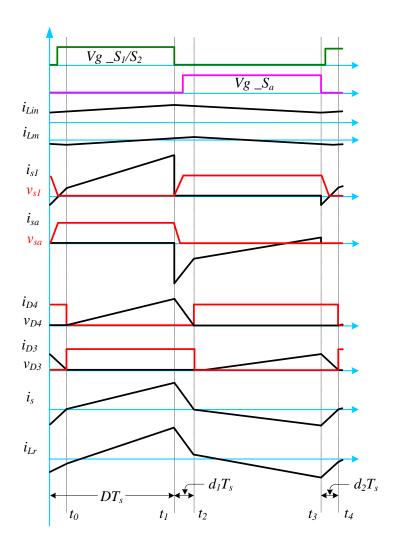

| Figure 4.2 Proposed soft-switching HRPWM converter waveforms in CCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52                    |

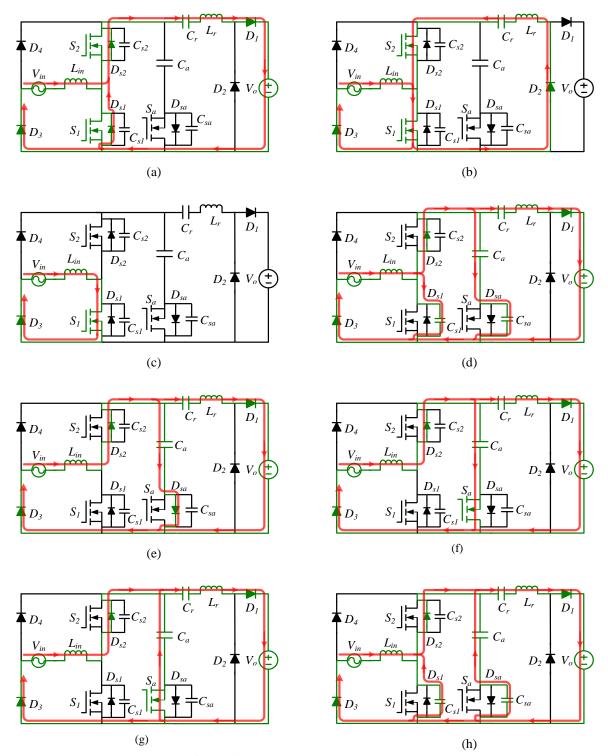

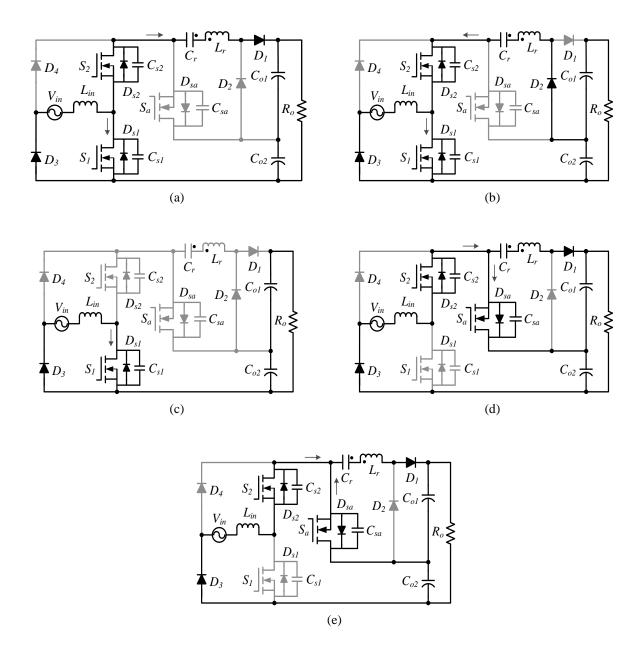

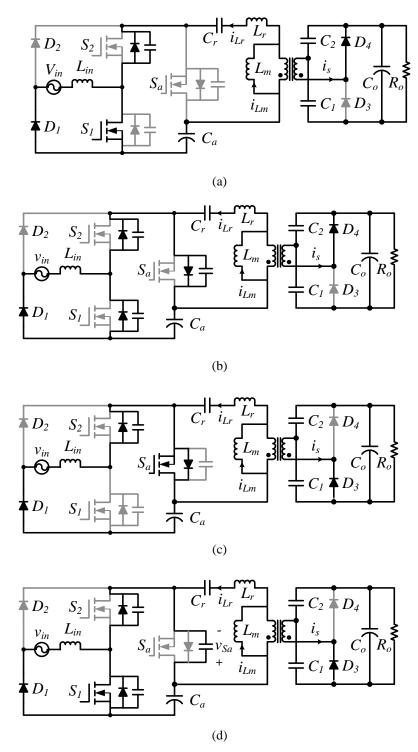

| Figure 4.3 Proposed converter modes of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 55                    |

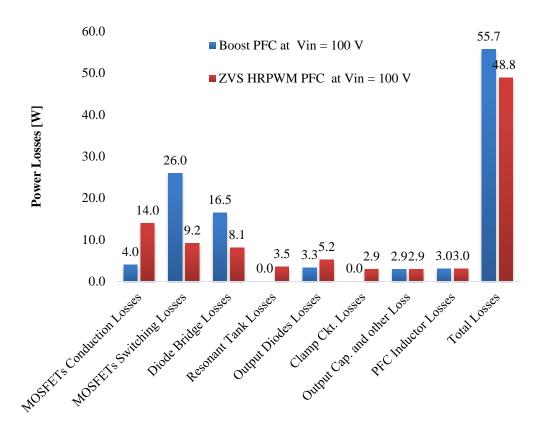

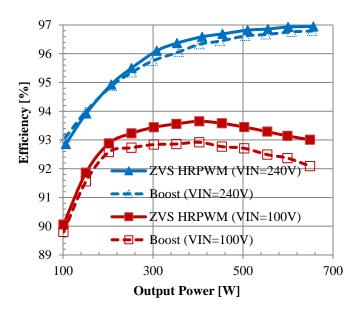

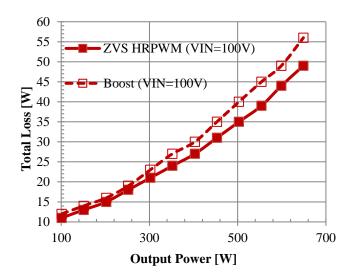

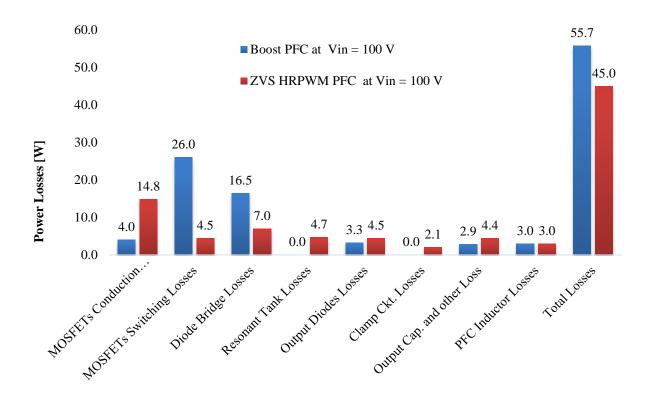

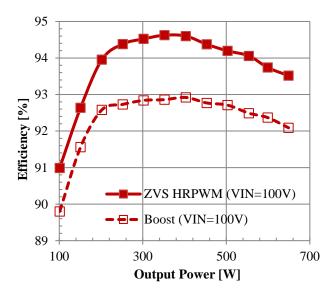

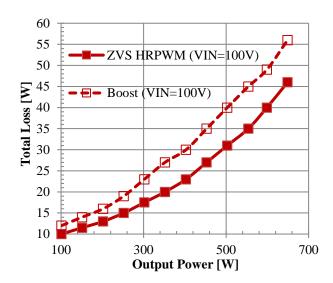

| Figure 4.4 Loss distribution comparison at $V_{in} = 100 \text{ V}$ , $f_s = 150 \text{ kHz}$ , $P_o = 650 \text{ W}$ , $V_o = 400 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60                    |

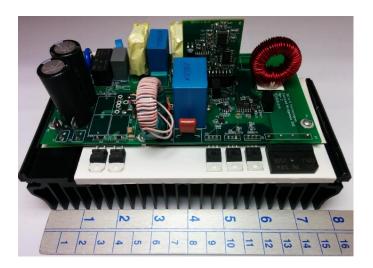

| Figure 4.5 Proposed converter experimental prototype.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                    |

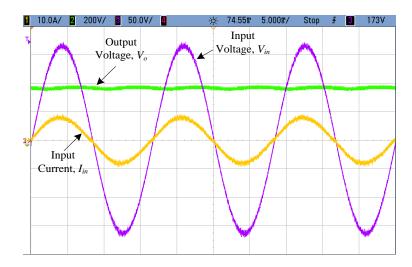

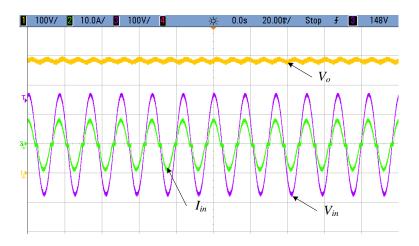

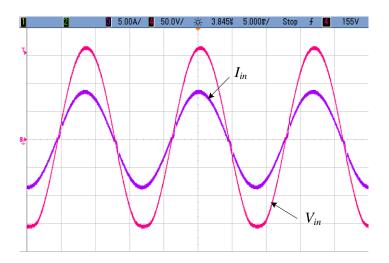

| Figure 4.6 ZVS HRPWM converter experimental waveforms at 20ms/div of input voltage $V_{in}$ (ch3:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| 100 V/div), input current $I_{in}$ (ch2: 10 A/div) and output voltage $V_o$ (ch1: 100 V/div) at $V_{in}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | =                     |

| 120 V, $V_o = 400$ V, $P_o = 650$ W and $f_s = 150$ kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63                    |

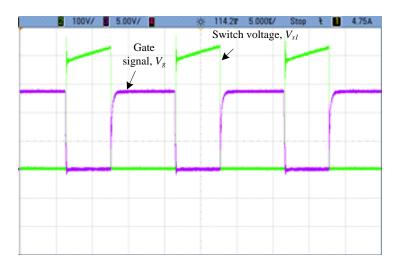

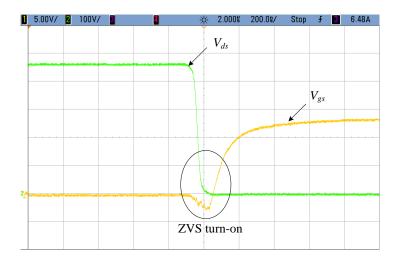

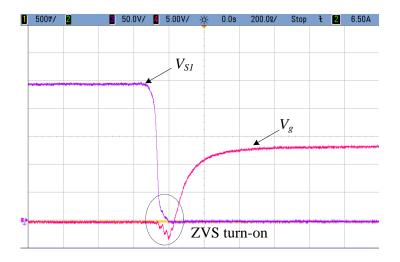

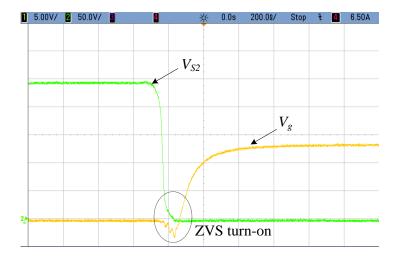

| Figure 4.7 ZVS HRPWM converter experimental waveforms at 200ns/div of voltage across switch S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ,<br>,                |

| $V_{ds}$ (ch2: 100 V/div) and gating signal for $S_I$ , $V_{gs}$ (ch1: 5 V/div) at $V_{in} = 120$ V, $V_o = 400$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ι,                    |

| $P_o = 650 \text{ W} \text{ and } f_s = 150 \text{ kHz.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64                    |

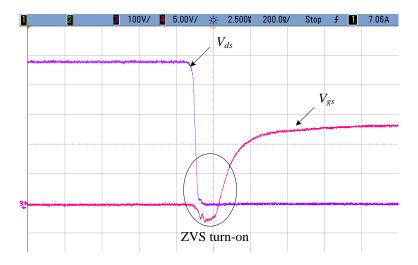

| Figure 4.8 ZVS HRPWM converter experimental waveforms at 200ns/div of voltage across switch S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ,<br>1 <sub>2</sub> , |

| $V_{ds}$ (ch3: 100 V/div) and gating signal for $S_2$ , $V_{gs}$ (ch4: 5 V/div) at $V_{in} = 120$ V, $V_o = 400$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ΄,                    |

| $P_o = 650 \text{ W} \text{ and } f_s = 150 \text{ kHz.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64                    |

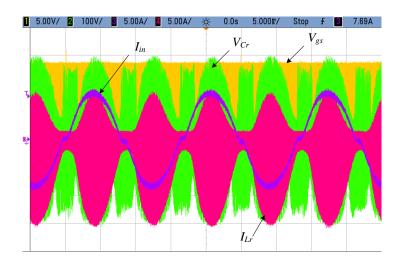

| Figure 4.9 ZVS HRPWM converter experimental waveforms at 5ms/div of voltage across capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |

| $C_r$ , $V_{Cr}$ (ch 2: 100 V/div), current through inductor $L_r$ , $I_{Lr}$ (ch 4: 5 A/div), input current $I_{in}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       |

| (ch3: 5 A/div) and gating signal for $S_I$ , $V_{gs}$ (ch1: 5 V/div) at $V_{in} = 120$ V, $V_o = 400$ V, $P_o =$ |                       |

| 650 W and $f_s = 150 \text{ kHz.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65                    |

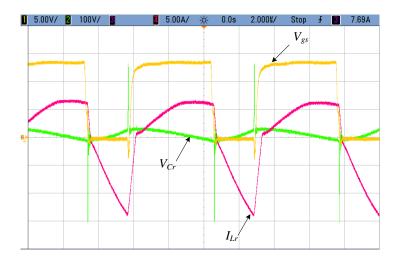

| Figure 4.10 ZVS HRPWM converter experimental waveforms at $2\mu s/div$ of voltage across capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |

| $C_r$ , $V_{Cr}$ (ch 2: 100 V/div), current through inductor $L_r$ , $I_{Lr}$ (ch 4: 5 A/div) and gating sign.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | al                    |

| for $S_I$ , $V_{gs}$ (ch1: 5 V/div) at $V_{in} = 120$ V, $V_o = 400$ V, $P_o = 650$ W and $f_s = 150$ kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                    |

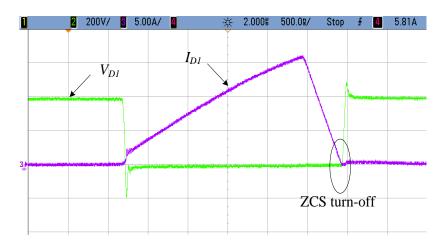

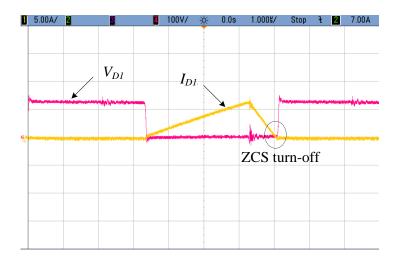

| Figure 4.11 ZVS HRPWM converter experimental waveforms at 500ns/div of voltage across diode in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\mathcal{O}_{1}$ ,   |

| $V_{DI}$ (ch 2: 200 V/div) and current through diode $D_I$ , $I_{DI}$ (ch 3: 5 A/div) at $V_{in} = 120$ V, $V_{in} = 120$ | 0                     |

| = 400 V, $P_o$ = 650 W and $f_s$ = 150 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66                    |

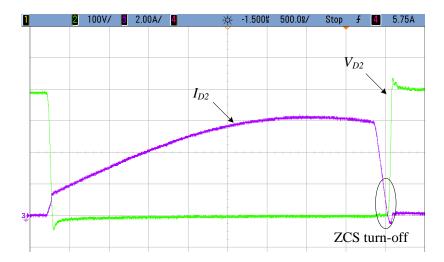

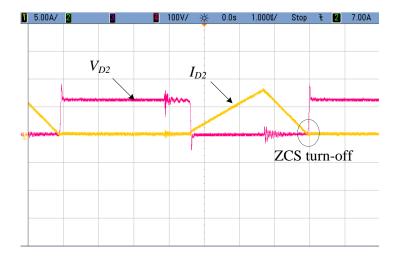

| Figure 4.12 ZVS HRPWM converter experimental waveforms at 500ns/div of voltage across diode in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\mathcal{D}_2$ ,     |

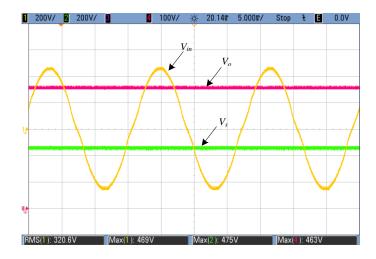

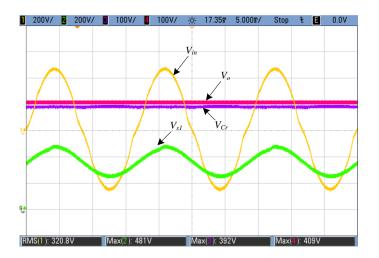

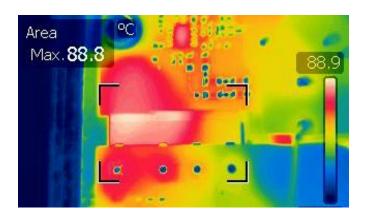

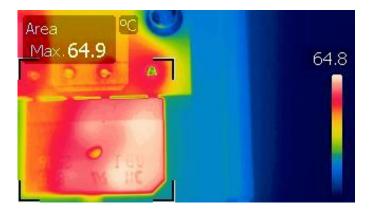

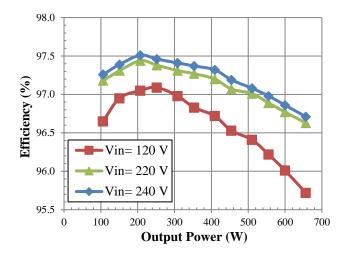

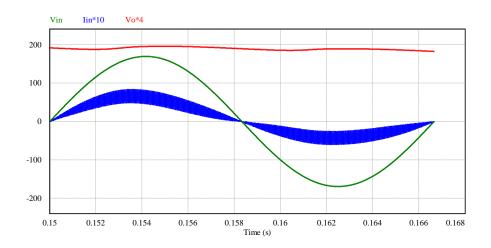

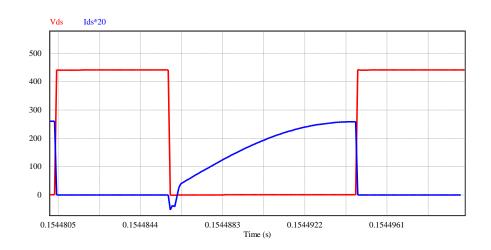

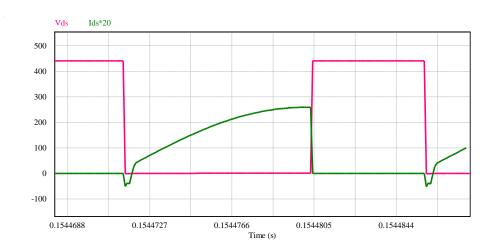

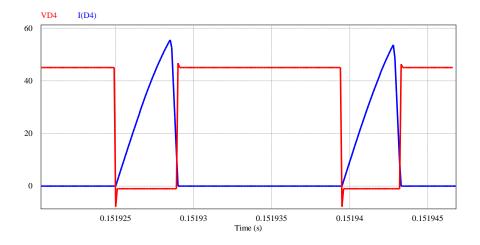

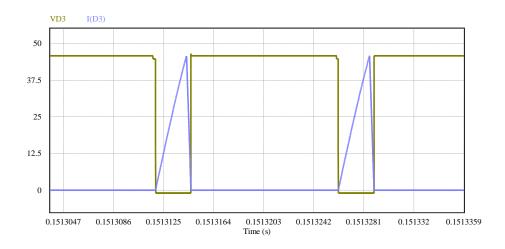

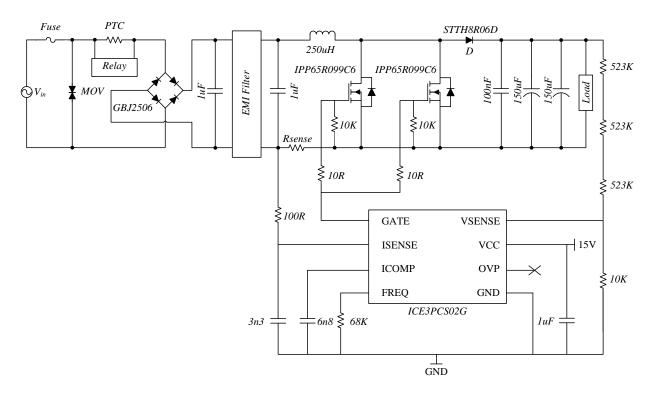

| $V_{D2}$ (ch 2: 100 V/div) and current through diode $D_2$ , $I_{D2}$ (ch 3: 2 A/div) at $V_{in} = 120$ V, $V_{in} = 120$ | 0                     |