#### A Mix-Grained Architecture for Improving HLS-Generated Controllers on FPGAs

by

Shadi Assadikhomami

B.Sc., Sharif University of Technology, 2013

#### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### **Master of Applied Science**

in

# THE FACULTY OF GRADUATE AND POSTDOCTORAL STUDIES

(Electrical and Computer Engineering)

The University Of British Columbia (Vancouver)

June 2017

© Shadi Assadikhomami, 2017

### Abstract

With the recent slowdowns in traditional technology scaling, hardware accelerators, such as Field Programmable Gate Arrays (FPGAs), offer the potential for improved performance and energy efficiency compared to general purpose processing systems. While FPGAs were traditionally used for applications such as signal processing, they have recently gained popularity in new, larger scale domains, such as cloud computing. However, despite their performance and power efficiency, programming FPGAs remains a hard task due to the difficulties involved with the lowlevel design flow for FPGAs. High-Level Synthesis (HLS) tools aim to assist with this time-consuming task by supporting higher level programming models which significantly increases design productivity. This also makes the use of FPGAs for large scale design development for evolving applications more feasible.

In this thesis we explore the potential of modifying the current FPGA architecture to better support the designs generated by HLS tools. We propose a specialized mix-grained architecture for Finite State Machine (FSM) implementation that can be integrated into existing FPGA architectures. The proposed mix-grained architecture exploits the characteristics of the controller units generated by HLS tools to reduce the control-path area of the design. We show that our proposed architecture reduces the area of the next state calculation in FSMs by more than 3X without impacting the performance and often reducing the critical path delay of the next state calculation in FSMs.

### Lay Summary

Programming low-level, dedicated hardware computing systems, such as Field-Programmable Gate Arrays (FPGAs), is more challenging and time consuming compared to programming higher-level software for general-purpose processors. Despite the difficulties associated with programming hardware, FPGAs still remain an appealing solution over general-purpose processors for many applications due to their higher efficiency. High-Level Synthesis (HLS) aims to ease the hardware programming by enabling the use of higher-level software languages to program FPGAs. However, there is generally a trade-off between programmability and efficiency when using HLS tools, which can often result in a less efficient hardware design than programming FPGAs using low-level programmability and efficiency when programming FPGAs using HLS tools. We propose a novel modification to current FPGA architectures that exploits common properties of HLS-generated designs to improve the FPGAs efficiency by reducing the total area of the hardware design.

## Preface

This dissertation is based on a research project conducted by myself under the supervision and guidance of Professor Tor M. Aamodt. I assisted with defining the problem space and was responsible for identifying challenges within this problem space, and designing and modelling the architecture to evaluate the proposed solution. I also conducted the experiments and collected all of the data represented in this dissertation, except the data shown in Section 3.1.4 which has been collected by Jennifer Angelica with my assistance under the supervision of Professor Aamodt.

# **Table of Contents**

| Ab         | strac           | t                                                               | ii  |  |  |

|------------|-----------------|-----------------------------------------------------------------|-----|--|--|

| Lay        | y Sun           | nmary                                                           | iii |  |  |

| Pre        | eface           |                                                                 | iv  |  |  |

| Tał        | ole of          | Contents                                                        | v   |  |  |

| Lis        | t of T          | Tables   v                                                      | iii |  |  |

| Lis        | t of F          | ligures                                                         | X   |  |  |

| Lis        | t of A          | Abbreviations                                                   | iii |  |  |

| Acl        | Acknowledgments |                                                                 |     |  |  |

| Dedication |                 |                                                                 |     |  |  |

| 1          | Intro           | oduction                                                        | 1   |  |  |

|            | 1.1             | Motivation                                                      | 3   |  |  |

|            | 1.2             | Contributions                                                   | 4   |  |  |

|            | 1.3             | Organization                                                    | 4   |  |  |

| 2          | Back            | ground                                                          | 6   |  |  |

|            | 2.1             | FPGA Architecture                                               | 6   |  |  |

|            | 2.2             | Finite State Machines                                           | 7   |  |  |

|            |                 | 2.2.1 Finite State Machine Definition and Representation Models | 7   |  |  |

|   |     | 2.2.2    | Finite State Machine Implementations 9 |

|---|-----|----------|----------------------------------------|

|   | 2.3 | Hardw    | are Design Flow                        |

|   | 2.4 | High-L   | Level Synthesis                        |

| 3 | Con | trol-Pat | th Optimization                        |

|   | 3.1 | Finite   | State Machine Analysis 13              |

|   |     | 3.1.1    | Preliminaries                          |

|   |     | 3.1.2    | FSM Characteristic                     |

|   |     | 3.1.3    | HLS-Generated Finite State Machines    |

|   |     | 3.1.4    | Data Flow Height Experiment            |

|   | 3.2 | Specia   | lized FSM Block                        |

|   |     | 3.2.1    | Design Space Exploration               |

|   |     | 3.2.2    | Mix-Grained Architecture               |

|   |     | 3.2.3    | Input Sequence Encoder Unit            |

|   |     | 3.2.4    | Coarse-Grained Fabric                  |

|   | 3.3 | Fractur  | rable FSM Hard Blocks                  |

|   |     | 3.3.1    | FSM Partitioning                       |

|   |     | 3.3.2    | Fracturable FSM Block Architecture     |

|   | 3.4 | State A  | Assignment Algorithm                   |

|   | 3.5 | Mappi    | ng to the Specialized FSM Architecture |

|   |     | 3.5.1    | Applying the Size Checking Pass        |

|   |     | 3.5.2    | Fine-Grained Mapping                   |

|   |     | 3.5.3    | Coarse-Grained Mapping                 |

|   | 3.6 | Putting  | g it All Together                      |

|   |     | 3.6.1    | Generating the FSM                     |

|   |     | 3.6.2    | State Assignment                       |

| 4 | Exp | eriment  | al Methodology                         |

|   | 4.1 |          | marks                                  |

|   | 4.2 |          | Extraction                             |

|   | 4.3 |          | nd Delay Model                         |

|   | 4.4 |          | Flow                                   |

|   | 4.5 |          | ng to the Next State Generation Block  |

|   |     |          |                                        |

| 5   | Expe         | erimental Results                              | 58 |  |

|-----|--------------|------------------------------------------------|----|--|

|     | 5.1          | Next State Generation Block Size               | 58 |  |

|     | 5.2          | Area Improvement                               | 61 |  |

|     | 5.3          | Delay Improvement                              | 63 |  |

|     | 5.4          | Resource Usage of the Mix-Grained Architecture | 65 |  |

|     | 5.5          | FSM Area                                       | 67 |  |

|     | 5.6          | Impact of HLS Directives on the Generated FSMs | 68 |  |

|     | 5.7          | Efficiency of the Fracturable FSM Block        | 71 |  |

| 6   | Rela         | ted Work                                       | 74 |  |

| 7   | Futu         | re Work                                        | 77 |  |

| 8   | Con          | clusion                                        | 79 |  |

| Bil | Bibliography |                                                |    |  |

# **List of Tables**

| Table 3.1 | Input sequence encoder generation: the original transition table       |    |

|-----------|------------------------------------------------------------------------|----|

|           | is given in (a), the reduced table is given in (b). {cs, active        |    |

|           | input(2bits)} will be used to address the memory instead of {cs,       |    |

|           | inputs(10 bits)}                                                       | 42 |

| Table 3.2 | Memory content                                                         | 48 |

| Table 4.1 | Number of lines of actual C code, excluding comments, for the          |    |

|           | evaluated benchmarks                                                   | 52 |

| Table 4.2 | Characteristics of the FSMs extracted from MachSuite                   | 53 |

| Table 4.3 | Characteristics of the FSMs extracted from HLS datacenter bench-       |    |

|           | marks                                                                  | 54 |

| Table 5.1 | The sizing configuration of the elements of the next state gen-        |    |

|           | eration block                                                          | 61 |

| Table 5.2 | Fraction of next state calculation logic area to total design area     |    |

|           | for sqlite_lookupName and sqlite_getToken functions from the           |    |

|           | HLS datacenter benchmark set                                           | 68 |

| Table 5.3 | Block size checking for the <i>sql_ln_fsml</i> indicating that it does |    |

|           | not fit to one FSM block, since it requires larger memory unit         |    |

|           | and more state bits than what is provided by the FSM block.            | 71 |

| Table 5.4 | Memory unit size requirement for each partition after partition-   |    |

|-----------|--------------------------------------------------------------------|----|

|           | ing the FSM. Row 4 indicates that FSM partition A requires a       |    |

|           | memory unit of size 120 and FSM partition B requires a mem-        |    |

|           | ory unit of size 88, thus they both can be mapped to a fracturable |    |

|           | FSM block.                                                         | 73 |

|           |                                                                    |    |

# **List of Figures**

| Basic FPGA architecture [15]                                   | 7                         |

|----------------------------------------------------------------|---------------------------|

| Digital systems structure                                      | 8                         |

| The state transition graph of a Mealy FSM                      | 9                         |

| General structure of finite state machines                     | 10                        |

| Memory-based implementation of FSMs                            | 11                        |

| Branch-free path (shown in green). Each path starts and ends   |                           |

| with a vertex with fan-out degree of greater than 1 (shown in  |                           |

| red). Note that vertices that belong to a branch-free path can |                           |

| have more than one fan-in edge                                 | 15                        |

| An example of the state encoding for the states that belong to |                           |

| branch-free paths.                                             | 16                        |

| Equivalent FSM construction                                    | 20                        |

| Fan-out degree frequency in the equivalent FSMs of Mach-       |                           |

| Suite benchmarks and Spec CPU2006 INT                          | 21                        |

| High-level view of the specialized FSM architecture            | 23                        |

| Number of active inputs per state calculated as average over   |                           |

| 46 FSMs extracted from 21 benchmarks generated by HLS.         |                           |

| Details of the benchmarks are described in Chapter 4           | 25                        |

| Edge distribution: number of transitions per state calculated  |                           |

| as an average over 46 FSMs extracted from 21 benchmarks        |                           |

| generated by HLS. Details of the benchmarks are described in   |                           |

| Chapter 4                                                      | 25                        |

| Next state generation block                                    | 26                        |

|                                                                | Digital systems structure |

| Figure 3.9  | Memory content                                                     | 28 |

|-------------|--------------------------------------------------------------------|----|

| Figure 3.10 | Path refinement                                                    | 35 |

| Figure 3.11 | An example C code: the example shows a while loop with four        |    |

|             | consecutive instructions each with a data dependency on the        |    |

|             | previous instruction. Additionally each instruction performs       |    |

|             | an operation that has a different latency in hardware such as      |    |

|             | division, multiply, shift, and add                                 | 43 |

| Figure 3.12 | State assignment example                                           | 44 |

| Figure 3.13 | Next state generation block - transition from a memory state to    |    |

|             | a memory state                                                     | 48 |

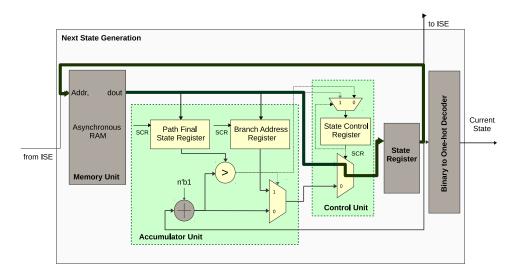

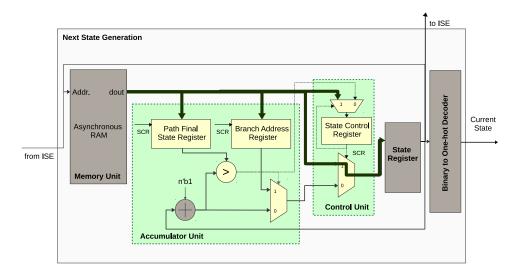

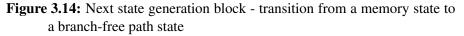

| Figure 3.14 | Next state generation block - transition from a memory state to    |    |

|             | a branch-free path state                                           | 49 |

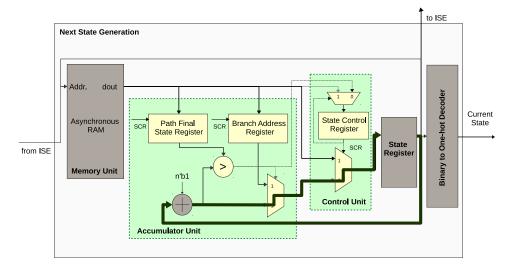

| Figure 3.15 | Next state generation block - transition from a state of a branch- |    |

|             | free path to another state on the same path                        | 49 |

| Figure 3.16 | Next state generation block - transition from the last state of a  |    |

|             | branch-free path to a memory state                                 | 50 |

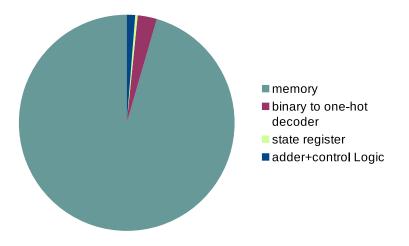

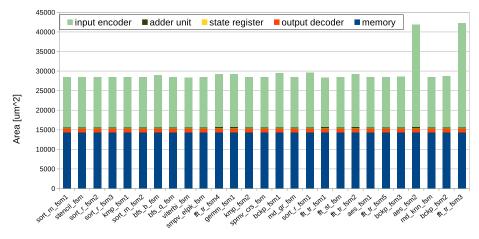

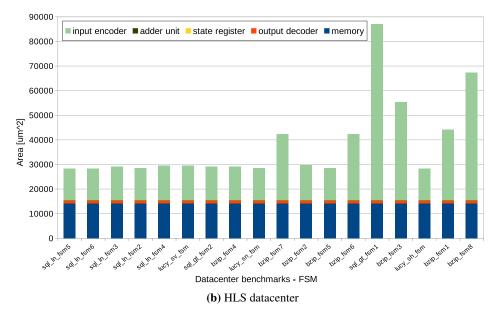

| Figure 5.1  | Area breakdown of the coarse-grained fabric                        | 59 |

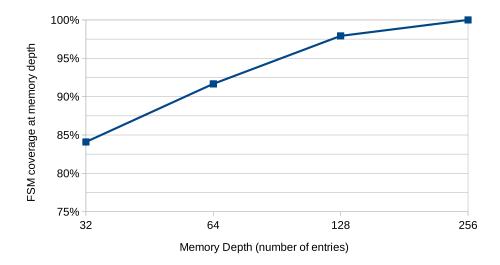

| Figure 5.2  | FSM coverage vs. memory depth in number of entries. Ap-            |    |

|             | proximately 98% of the evaluated FSMs fit into a memory with       |    |

|             | a depth of 128 entries.                                            | 59 |

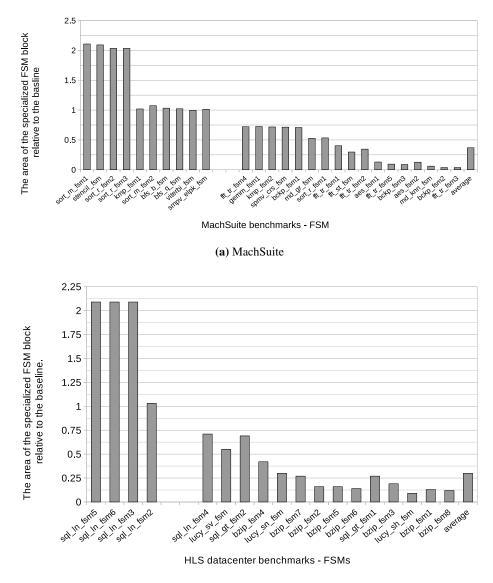

| Figure 5.3  | Area improvement of the specialized FSM architecture, which        |    |

|             | includes the area of the input sequence encoder and next state     |    |

|             | generation block relative to the baseline                          | 63 |

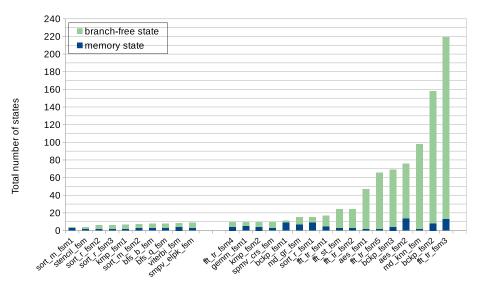

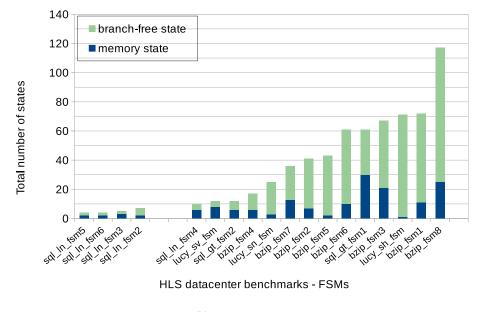

| Figure 5.4  | FSM size along with the breakdown of the states that are part      |    |

|             | of branch-free paths and states that reside in memory              | 64 |

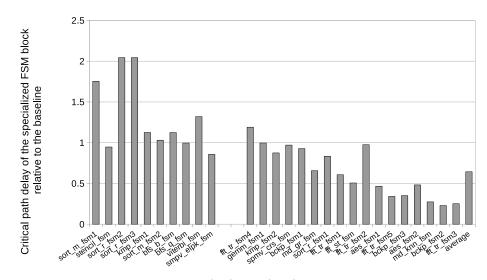

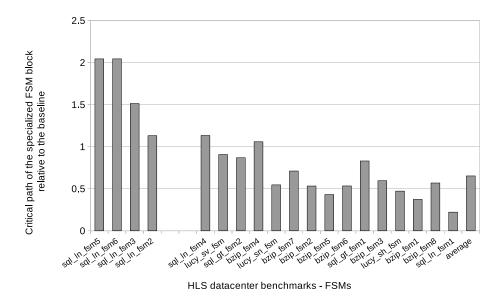

| Figure 5.5  | Critical path delay improvement of the specialized FSM archi-      |    |

|             | tecture which includes the critical path of the input sequence     |    |

|             | encoder and next state generation block relative to the baseline   | 66 |

| Figure 5.6  | Area breakdown of the mix-grained FSM architecture for the         |    |

|             | FSMs extracted from the evaluated benchmarks                       | 67 |

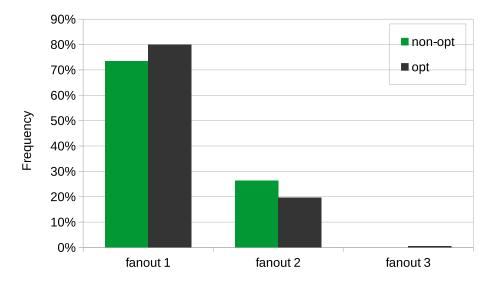

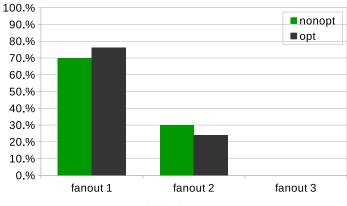

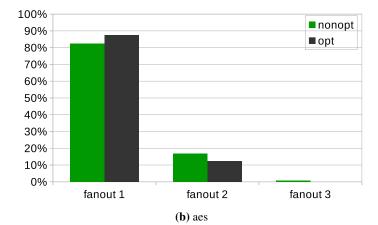

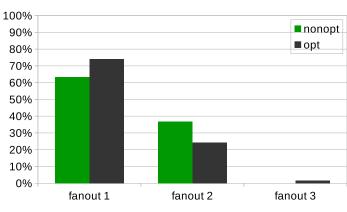

| Impact of applying HLS optimization directives on <i>backprop</i> , |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| aes, and radix sort benchmarks from MachSuite. The x-axis           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| shows the number of reachable next states per state. For ex-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ample, fan-out 1 is an indicator for states that only have one      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| next state. This figure shows that the optimization increases       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| the percentage of branch-free path                                  | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Impact of applying HLS optimization directives on aes, back-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| prop, and radix sort benchmarks from MachSuite                      | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

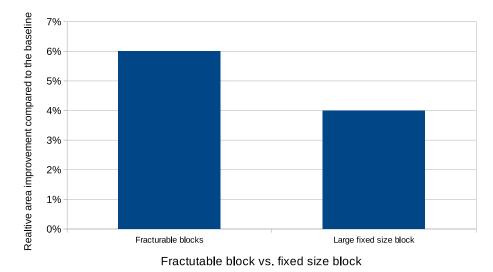

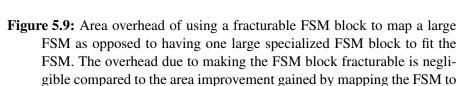

| Area overhead of using a fracturable FSM block to map a large       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FSM as opposed to having one large specialized FSM block to         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| fit the FSM. The overhead due to making the FSM block frac-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| turable is negligible compared to the area improvement gained       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| by mapping the FSM to the hard FSM block                            | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                     | <i>aes</i> , and <i>radix sort</i> benchmarks from MachSuite. The x-axis shows the number of reachable next states per state. For example, fan-out 1 is an indicator for states that only have one next state. This figure shows that the optimization increases the percentage of branch-free path Impact of applying HLS optimization directives on <i>aes</i> , <i>backprop</i> , and <i>radix sort</i> benchmarks from MachSuite Area overhead of using a fracturable FSM block to map a large FSM as opposed to having one large specialized FSM block to fit the FSM. The overhead due to making the FSM block fracturable is negligible compared to the area improvement gained |

## **List of Abbreviations**

- **CPU** Centeral Processing Unit

- GPU Graphic Processing Unit

- **DSP** Digital Signal Processor

- ASIC Application-Specific Integrated Circuit

- HLS High-Level Synthesis

- FPGA Field Programmable Gate Array

- CGRA Coarse Grain Reconfigurable Architecture

- FSM Finite State Machine

- CDFG Control/Data Flow Graph

- DCG Directed Cyclic Graph

- **RAM** Random Access Memory

- LUT Look-Up Table

- HDL Hardware Description Language

- **RTL** Register-Transfer Level

- CAD Computer Aided Design

- SOC System On a Chip

### Acknowledgments

I would like to thank my supervisor, Professor Tor M. Aamodt, for the valuable guidance, support, and insight he provided during these years and for giving me the opportunity to do high-quality research. This work would have not been possible without him. I also gratefully acknowledge the funding provided by the Natural Sciences and Engineering Research Council of Canada (NSERC) that made my research possible.

I would like to thank everyone in the computer architecture group at UBC, including the graduate students and undergraduate interns, who I had the opportunity to work with. I would also like to thank my former lab-mates, Tim Rogers, Ahmed ElTantawy, and Andrew Boktor, and my friends from the SOC group, Fatemeh Eslami and Hossein Omidian, for their kind help, advice, and sharing their knowledge and experience with me. I would like to specially thank my best friend and a senior PhD students in our group, Tayler Hetherington, for his help, support, feedback, and everything I have learned from him during these years.

And last but not least, I would like to thank my family who taught me to never give up and fight for my goals, and for their invaluable support throughout my life.

To my parents

### **Chapter 1**

### Introduction

Since their emergence, computing systems have undergone a series of revolutionary improvements in their performance, energy efficiency and cost-effectiveness. These improvements were achieved by architectural innovations and advancements in the semiconductor industry. Advancements in semiconductor technologies provide large improvements to computing systems by drastically increasing the amount of processing capability per unit of area and power. Historically, these advancements have followed Moore's law [22], which states that the number of transistors on a chip will double approximately every two years and Dennard Scaling [8], which states that the power density of transistors remains constant as their size scales down which enables smaller and faster transistors. However, in recent years, Moore's law and Dennard scaling have slowed, resulting in diminishing returns from semiconductor improvements.

Additionally, to broaden the scope of applications able to benefit from such computing systems, architectures were designed with generality in mind, such as the CPU. However, due to the slowdowns in the rate of improvements for computing systems, there has been a shift towards using alternative architectural designs and specialized hardware accelerators to keep up with the growing computational demands of today's applications.

Hardware accelerators are customized circuits that are designed for performing a particular set of tasks [28]. They have shown great potential to improve the performance and energy efficiency of applications by eliminating the overheads that come with having a more general purpose architecture. Graphic Processing Units (GPUs), Application-Specific Integrated Circuits (ASICs), Digital Signal Processors (DSPs), and Field Programmable Gate Arrays (FPGAs) are examples of the most common hardware accelerators [28].

These accelerators range in their level of specialization and programmability. Similar to CPUs, GPUs offer a high degree of programmability, however, are designed to accelerate a class of applications with large amounts of data-level parallelism. In contrast, ASICs are designed to perform a specific set of tasks with dedicated hardware at the cost of little to no programmability. FPGAs bridge the gap between programmable processors and dedicated hardware accelerators by providing a reconfigurable and programmable hardware platform. FPGAs improve the flexibility over ASICs, while maintaining a portion of the improvements in performance and energy efficiency of a hardware design compared to a general purpose architecture.

More recently, FPGAs have been gaining popularity in domains they have not typically been used for, such as cloud computing [[39], [38]]. Some of of the world's biggest datacenters, such as Microsoft and Baidu, are now deploying FP-GAs in their servers [[44], [23], [6]], and Amazon is now offering FPGA cloud instances in the amazon web services[3]. Additionally, with the acquisition of Altera by Intel in 2015 [13], FPGAs may become more closely tied to general purpose architectures, making them more accessible and increasing the use in new markets, such as Cloud computing.

FPGAs are traditionally programmed using hardware design languages (HDLs), such as Verilog or VHDL. Hardware design is notoriously more difficult compared to software development. This is one of the main issues with using FPGAs for accelerating large scale applications. However, recent advances in high-level synthesis (HLS) significantly increase the productivity of hardware design by enabling the designers to use higher level software programming languages, such as C/C++ and OpenCL, which makes FPGAs easier to use for accelerating larger scale applications. Therefore, HLS is now becoming a part of the main hardware design flow [[7], [42]]. This raises the question - can we modify the FPGA architecture and CAD flow such that they can be more efficiently used by HLS tools? In this dissertation we aim to answer this question by exploring the potential of improving

the architecture of FPGAs to better tune them for HLS design flow by analyzing the characteristics and requirements of designs generated by HLS tools.

#### **1.1 Motivation**

FPGA architecture consists of an array of generic programmable logic blocks and programmable routing switches that enables them to implement any logic function. This flexibility comes with the cost of area, performance, and power overhead that causes the FPGAs implementation of a given design to be at least an order of magnitude larger than the ASIC implementation, with a critical path delay ratio of about 3 to 4 [14]. To bridge this gap, FPGA designers have introduced hard blocks such as mutiplier/accumulator, block memories, and floating point units to modern FPGA architecture to mimic efficiency of ASICs for a common set of operations[17]. Hard blocks are ASIC-like hardware units that are less programmable, but more efficient than programmable logic blocks. Despite their efficiency improvements, the area of underutilized hard blocks is wasted, therefore, the hard block architecture must consist of function units and logic operations that are commonly used among a representative set of important FPGA applications.

The existing hard blocks on FPGA architectures have been designed to accelerate the operations that are common among the original application domains that were using FPGAs. However, the recent shift to use FPGAs in new domains with varying processing requirements raises the question - are there other common operations among these new application domains that can benefit from being mapped to hard blocks? The same question can be asked regarding the recent increased popularity in the use of HLS tools - Due to their automated nature to generate hardware designs, as opposed to a human hardware designer approach, is it possible that they generate any special structure in hardware that can be exploited by new hard blocks?

In this work, we aim to answer this question by studying the controller unit hardware generated by HLS tools. HLS tools often generate large explicit controller units that are modelled by finite state machines. These control units can have a big influence on the total area of the design in cases where the realization of the data path requires a large number of states and control signals [20]. In this dissertation we analyze the characteristics of the finite state machines that are generated by HLS tools and argue that these state machines all share common behaviours that can be exploited to design an alternative hardware implementation for such FSMs. We evaluate our proposed architecture by detecting and extracting the FSM as a standalone circuit from the application and compare it against the baseline FSM implemented purely in FPGA soft logic. We show that our proposed architecture has a great potential to reduce the area implementation of the next state generation logic in FSMs as well as reducing its critical path delay.

#### **1.2 Contributions**

This thesis makes the following contributions:

- Identifying common characteristics among state machines generated by HLS-tools.

- Proposing a novel architecture to improve area efficiency of next state calculation logic in FSM implementation without affecting performance.

- Proposing a novel state encoding technique which exploits certain properties of HLS-generated FSM described in Section 3.1.2.

- Evaluating the the area and delay improvement of the proposed architecture compare to a baseline FPGA architecture which shows an average area reduction of 70% as well as critical path delay reduction of 45%.

#### 1.3 Organization

The rest of this dissertation is organized as follows:

• Chapter 2 first details the background FPGA architecture used in this dissertation. It then provides the necessary background on finite state machines as an important part of digital systems.

- Chapter 3 performs analysis on FSM characteristics and presents a novel configurable architecture to improve the area efficiency of FSM implementation on FPGAs.

- Chapter 4 presents the methodology used to implement and evaluate the designs introduced in Chapter 3.

- Chapter 5 evaluates the area/delay improvements of the proposed specialized FSM architecture.

- Chapter 6 discusses related work.

- Chapter 7 discusses directions for potential future work.

- Chapter 8 concludes the dissertation.

Next section describes the necessary background for this work.

### **Chapter 2**

### Background

This chapter presents the necessary background information to understand the contributions of this Thesis. First, this chapter describes the architecture of contemporary FPGAs. It then discusses the required background to understand the finite state machines and their traditional implementation methods on FPGAs. Finally, this chapter provides a brief summary of the standard hardware design flow and the addition of High-Level Synthesis (HLS) tools to this flow.

#### 2.1 FPGA Architecture

A traditional FPGA architecture consists of an array of generic logic blocks that are connected via configurable routing channels. The main components of these logic blocks are n-input (normally 6-input) Look-Up Tables (LUTs), small one-bit hard adders, and optional flip-flops that enable registering the output of the block. A n-input LUT can be configured to implement any logic function that maps the n-bit input to a 1-bit output. Therefore, using LUTs in logic blocks turns them into generic flexible blocks that are capable of implementing any logic function [15].

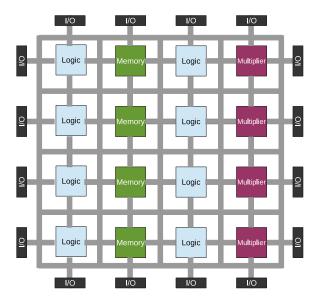

As discussed in the Chapter 1, in modern FPGA architectures some of these generic blocks are replaced by hard blocks such as multiply-add, floating point operations, and memory blocks to improve the efficiency of these specific set of operations [14]. This is shown in Figure 2.1.

Figure 2.1: Basic FPGA architecture [15]

#### 2.2 Finite State Machines

In this section we present background information for Finite State Machines (FSMs) as an important part of digital circuit design and review the alternative methods of implementing FSMs on FPGAs.

#### 2.2.1 Finite State Machine Definition and Representation Models

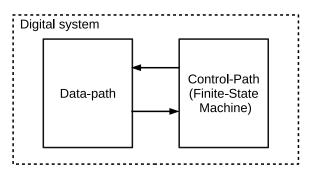

Logic circuits consist of two main parts: data-path and control-path. The controlpath is also known as the control unit. The general block diagram of digital circuits is shown in Figure 2.2. The data-path can be described as functional units that perform the computational tasks (data operations) in an application [21]. The control unit, on the other hand, generates the control signals required to direct the operation of data-path according to the timing constraints, data, and control dependencies in an application. Finite state machines are a common way to describe the control path in logic circuits. As the name suggests, an FSM is composed of a limited set of states and the corresponding transitions between these states. Each

Figure 2.2: Digital systems structure

state corresponds to a specific state in the real design. The transition between these states happens based on the *current state* of the system and the set of inputs to the FSM. Each states has a set of associated control signals that are dependant on the current state of the system and, potentially, the input signals. In a Moore FSM the output signals are defined only based on the current state of the system, where as in a Mealy model both inputs and current state are used to determine the value of output signals.

#### **State Transition Table**

A state transition table is one of the common ways of representing an FSM. The state transition table is a truth table, where the inputs and current state form the input column of the table, while the output column contains the next state value and outputs of the FSM. It is a simple method to define the state transitions and the values of output signals based on the current state and inputs.

#### **State Transition Diagram**

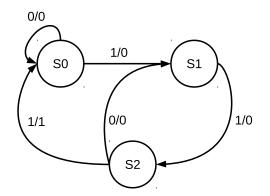

The state transition diagram is the equivalent graph-based representation of the state transition table [21]. A state transition diagram is a directed cyclic graph (DCG) G = (V, E) where each vertex  $v_i \in V$  represent a unique state and each edge  $e_{ij} \in E$  shows a transition from the corresponding state  $v_i$  to the  $v_j$ . The edge labels indicates the input sequence that causes the corresponding transition. Depending on the FSM model, Mealy or Moore, the output of each states will be either part of

Figure 2.3: The state transition graph of a Mealy FSM.

the edge or vertex label respectively. This is shown in Figure 2.3

#### 2.2.2 Finite State Machine Implementations

There are two main approaches to implement FSMs on FPGAs, which are discussed below.

#### **LUT-Based Implementation**

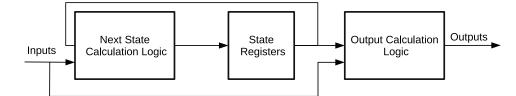

A LUT-based implementation is the common conventional way to implement FSMs on FPGAs. Figure 2.4 shows the block diagram of an FSM. It consists of state registers to hold the current state value, and combinational logic to calculate the next state value and output signals. The combinational logic is implemented using FP-GAs' LUT-based logic blocks. However, the flexibility of LUTs to implement any logic function comes at cost of increased area, power, and performance. Logic minimization algorithms and state assignment techniques are used to find the optimal combination circuits, which realize the state transfer function and output function [21].

#### **RAM-Based Implementation**

After embedded block RAMs were introduced to FPGA architectures, a large body of research investigated the benefits of using block RAMs as an efficient method

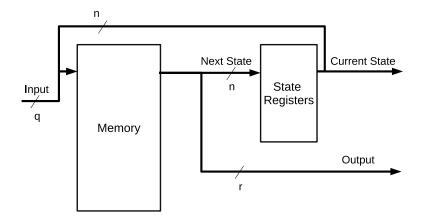

Figure 2.4: General structure of finite state machines

for implementing FSMs [[26], [34], [30], [31]]. RAM-based FSM implementations have a great potential to reduce the area usage by utilizing less of the FPGA's routing and logic resources, which consequently improves the area and power consumption of the design. Figure 2.5 shows an example of a RAM-Based FSM implementation. In this example, the FSM has q inputs, r outputs, p states, which requires a n-bit encoding. The state value will be stored in a n-bit register and together with the input, form the address to the memory unit to look up the value of the next state and output signals. Such a memory unit will have  $2^{(n+q)}$  entries of size (n+r) to accommodate the next sate and output values for all the combinations of current state and input values. However, one potential problem with such implementation is the exponential growth in memory size with an increase in number of states and inputs. For the scenario where there are several inactive inputs at each states that do not contribute to the next state calculation, a potential solution has been proposed that utilizes a selecting mechanism to choose the active inputs at each state to address the memory locations in order to avoid the unnecessary increase in the memory size [10].

#### 2.3 Hardware Design Flow

Programming hardware tend to be more difficult compared to software development. The traditional hardware design flow requires designers to use low-level hardware description languages such as Verilog and VHDL, to directly describe a given high-level algorithm. This description is typically at register transfer level (RTL) where a circuit is described by its logic operation, registers, and their corresponding data flow. The RTL design will then be mapped to an FPGA using the Electronic Design Automation (EDA) tools , which after synthesizing the RTL de-

Figure 2.5: Memory-based implementation of FSMs

sign into a gate-level netlist and applying the logic optimization techniques, try to map the design onto an FPGA architecture in an iterative manner.

The very low-level nature of RTL design, various design constraints and requirements, and long EDA process makes the hardware design a very challenging and time-consuming task compared to the typical sequential programming in software. On the other hand, the large scale and evolving nature of applications in new domains, such as cloud computing, makes the hardware design for applications in such domains even more challenging. Therefore, to make FPGAs a more feasible solution, there needs to be a mechanism to ease the hardware programming, such as high-level synthesis (HLS), which is described below.

#### 2.4 High-Level Synthesis

High-level synthesis (HLS) tools try to assist with this issue by raising the level of abstraction and letting the designer use a high-level language such as C/C++ or OpenCL for describing the desired algorithm to generate an RTL design.

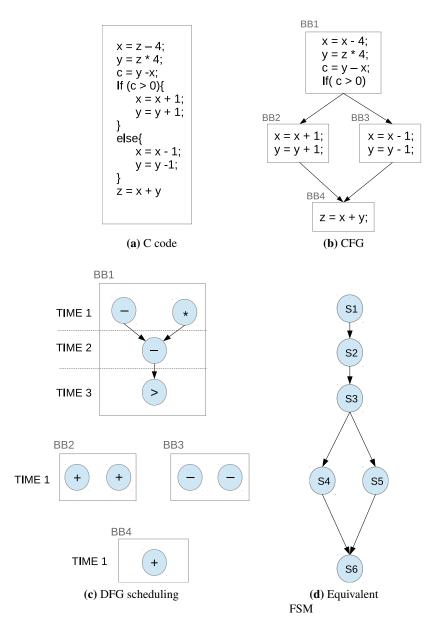

HLS tools are becoming increasingly popular due to the recent improvements in their underlying algorithms, which has enabled them to generate RTL designs that have comparable quality with a hand-coded RTL design by an expert hardware designer [7]. High-level synthesis tools use the control/data flow graph (CDFG) of a given program as the main starting point to generate the corresponding RTL design. Similar to the logic circuit describe in Section 2.2.1, the generated hardware is composed of two main parts: (1) datapath and (2) control path.

The datapath corresponds to the operations and data flow in the the given highlevel program while also taking the resource constraints of the target FPGA architecture, such as number of available specific hardware units, into account [7]. The control path is described using an FSM which is constructed after performing two main tasks: (1) scheduling and (2) binding. Scheduling is the process of identifying the cycle in which each operation can be performed given the timing/resource constraints of the target architecture and control and data dependencies in the input application [7]. Binding is the process of mapping the given operations and variables to hardware units that are capable of implementing them while also taking the resource constraints into account [7]. For example, an addition operation is mapped to an adder on the FPGA. If the schedule allows for 20 additions to be performed on the same cycle given the data dependencies, but there are only 10 hardware addition units, the binding task will modify the schedule to perform these operations over two cycles. In a scenario where same hardware unit is shared between multiple operations, the input sources to each operation and the output connections will be defined based on the output of the FSM.

### **Chapter 3**

# **Control-Path Optimization**

This chapter studies the potentials of using specialized hardware blocks for implementing Finite State Machines (FSMs) to improve the area efficiency and performance of the control unit portion of the RTL designs generated by high-level synthesis tools. We propose a novel configurable mixed-grained architecture, that makes use of unique characteristics of the FSMs generated by HLS tools to reduce the silicon area that is required for FSM implementation. This is achieved without affecting the control unit performance and, in most of the cases, improves the critical path delay as well.

The rest of the chapter is organized as follows: First we perform analysis on selected characteristics of finite state machines. We show that these characteristics can be used to design an architecture that more efficiently uses the silicon area compared to conventional LUT-based implementation of state machines. We then describe our proposed architecture in detail and a proposed state encoding technique that has been developed in order to better exploit these specialized FSM blocks. Finally we describe the technology mapping algorithm that we have developed to map a given finite state machine to specialized FSM blocks.

#### **3.1** Finite State Machine Analysis

In this section we define and analyze specific characteristics of Finite State Machines that can be exploited to design a custom FSM block. We then present the required state encoding technique to be able to efficiently utilize the custom FSM blocks. Finally, we show that Finite State Machines generated using High-Level Synthesis tools always demonstrate such characteristics, hence they are great candidates to benefit from our proposed customized blocks.

#### 3.1.1 Preliminaries

This section presents the preliminaries for our Finite State Machine analysis.

Definition 1. State Transition Diagram: Finite state machines can be represented by their state transition diagram. State transition diagram is a directed cyclic graph (DCG) G = (V, E) where each vertex  $v_i \in V$  represent a unique state and each edge  $e_i \in E$  shows a transition between two corresponding states (vertecis). In the rest of this chapter, we refer to vertices and states interchangeably.

*Definition 2.* **Directed Path**: Directed path is a finite sequence of edges following the same direction which connect a sequence of vertices.

*Definition 3.* **Vertex degree**: The degree of a vertex of a graph is defined as the number of edge incidents to the vertex. In DCGs, the vertex degree can be grouped into *fan-in degree* and *fan-out degree* which represent the number of incoming edges and outgoing edges of a vertex respectively.

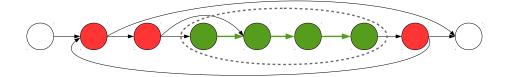

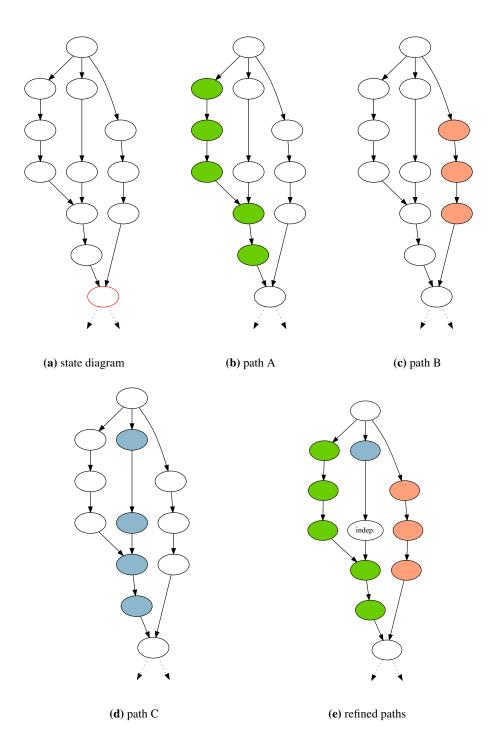

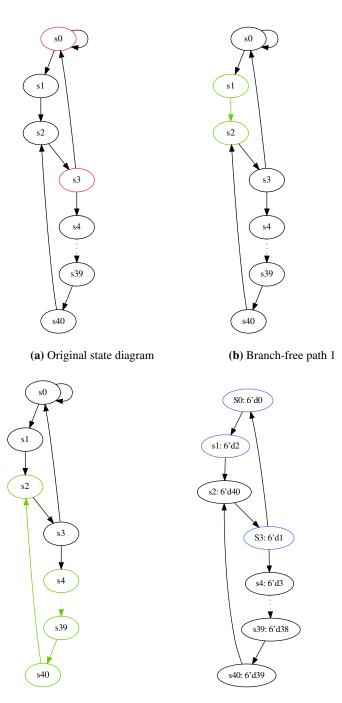

*Definition 4.* **Branch-Free Path**: Given a DCG, we define a branch-free path to be a directed path where each vertex has at most one fan-out edge but can have more than one fan-in edge. An example of a graph with branch-free paths is shown in Figure 3.1.

#### **3.1.2 FSM Characteristic**

Using the definitions in the previous section, we now can describe two specific properties of FSMs that can be exploited to reduce the area usage and improve critical path delay of FSM implementations.

**Figure 3.1:** Branch-free path (shown in green). Each path starts and ends with a vertex with fan-out degree of greater than 1 (shown in red). Note that vertices that belong to a branch-free path can have more than one fan-in edge.

#### **Abundance of Branch-Free Paths**

If the state transition graph of a finite-state machine has long branch-free paths, then consecutive states in each path can be assigned consecutive state values (state encoding) such that next state value can be calculated with a simple increment operation. This leads to a new state encoding where branch-free paths have simple increasing state encoding. This is shown with an example in Figure 3.2. The graph represents part of the state transition diagram of an FSM which contains two branch-free paths labelled with the proposed encoding. Note that the blank states are not part of any branch-free path since they have fan-out degree of 2. Consider the top path with the length equal to n, if the first state in this path is assigned the state encoding X, then following states in the path will be assigned X + 1, X + 2, ..., X + n - 2, and X + n - 1 until a non branch-free state is reached. The same rule applies to the second path with the length equal to m where the first state of the path is assigned the state encoding Y and the following states in the path will be assigned Y + 1, Y + 2, ..., Y + n - 2, and Y + n - 1. Hardware implementation for such state machine has an opportunity to reduce the silicon area, since the next state calculation logic for states that belong to branch-free paths can be realized with a simple adder along with small control logic in hardware. Section 3.2.4 provides more detail on how this adder unit is utilized in our proposed architecture for implementing FSMs.

Figure 3.2: An example of the state encoding for the states that belong to branch-free paths.

#### Low Fan-Out Degree

For a given FSM, the maximum number of possible next states for any given state can be calculated using the following equation:

$$min(2^q, p)$$

Where q is equal to the total number of inputs to the state machine and p represent the total number of states. However, not all of the input signals are active in different states, therefore the number of reachable states from a given state can be, and often is, far less than the maximum. For each given state, the fan-out degree represent the number of reachable states from that given state.

For the state machines with abundance of branch-free paths, the remaining states which are not part of any branch-free path form a smaller subset of the state machine. If the states that belong this subset have low fan-out degree, there is potential for a hybrid memory-based FSM implementation that is independent of the input size. Section 3.2.4 provides more detail on how a small memory unit is incorporated to our proposed architecture for implementing the next state calculation of the states the do not belong to a branch free path.

#### 3.1.3 HLS-Generated Finite State Machines

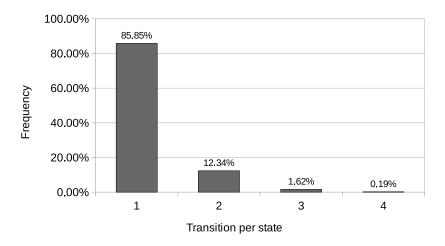

The results of the analysis on the finite state machines extracted from two sets of HLS benchmarks used in this thesis are presented in Figure 3.6 and Figure 3.7. The details of these benchmark sets are described in Chapter 4. The RTL code for these benchmarks is generated using Vivado HLS, an HLS tool by Xilinx [42].

For the MachSuite benchmarks, we used the default set of HLS optimization directives that were shipped with the benchmarks such as loop unrolling, loop pipelining, and memory partitioning. In Section 5.6, we specifically analyze the impact of applying HLS optimization directives on generated FSMs by looking at three benchmarks from MachSuite. The HLS directives are obtained using the methodology and results described in [18] which aim to minimize the area-delay product of the generated RTL design. As the results suggest, the size of FSMs and fraction of branch-free paths are not negatively impacted (i.e. the branch-free paths still exist and are a large fraction of total states). In fact, for these three benchmarks, the fraction of branch-free paths actually increases.

For the datacenter benchmarks, BZIP, Lucy, and SQLite (getToken function), HLS optimization directives were applied while generating the RTL design. For the the remaining benchmarks/functions in this benchmark set, no optimization were applied. However, based on our analysis in Section 5.6, we expect a similar behaviour to the result shown for optimizing Machsuite. Applying and evaluating full optimizations on all benchmarks is left to future work.

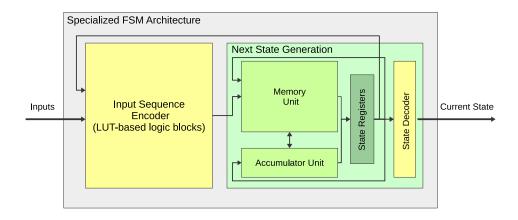

Figure 3.6 shows that more than 80% of the states in each FSM do not require any input and only have one possible next state, which means they belong to a branch-free path. Figure 3.7, which shows the fan-out-degree (transitions per state) statistics also indicates that there is at most 4 reachable next states for any given state. Therefore, finite state machines coming from HLS-generated RTL codes have a great potential to benefit from our proposed architecture.

#### 3.1.4 Data Flow Height Experiment

The FSM analysis on the HLS benchmark sets exposed two common patterns: low fan-out degree and long branch-free paths. This raises the question: what is the cause of the low fan-out degree and long branch-free paths in FSMs among all of the HLS generated RTL codes? Our hypothesis is that these common patterns are caused by data dependent instructions and the latency of instructions within a basic block. To evaluate our hypothesis of data-dependence leading to branch-free paths, we look at the mechanisms used by HLS tools to generate the RTL code for a given application. As discussed in the background section, HLS tools rely on the control/data flow graph (CDFG) of an application and consider the resource and

timing constraints of the target hardware to perform scheduling. The outcome of scheduling is used to generate the control unit and, consequently, the FSM that will direct the operations of the data path.

To understand the impact of data-dependence on scheduling, we mimic the behaviour of an HLS scheduler by constructing a simplified equivalent FSM of a given program from the control flow and data flow graph. Our simplified equivalent FSM assumes that there are infinite resources on the FPGA, the latency of any instruction is one cycle, and that data-dependent instructions cannot take place on the same cycle. These simplifications aim to limit the scheduling to data dependent instructions.

The following steps describe how the simplified equivalent FSM is constructed. Figure 3.3 visualizes this process for the program shown in Figure 3.3a.

- Step 1: Construct the control flow graph (CFG) of the program (Figure 3.3a).

- Step 2: Construct the data flow graph (DFG) for each of the basic blocks in the CFG. Each node of a DFG shows an operation and edges are representative of data dependencies among these operations (Figure 3.3b).

- **Step 3**: Apply unconstrained list scheduling [21] separately on each of the data flow graphs, with the simplifications described above (Figure 3.3c).

- Step 4: Given that each of these data dependent operations may be performed by functional units that require appropriate control signals, each of these operations needs to be a separate state in the equivalent FSM. Replace every cycle of each scheduled DFG with a corresponding state in the equivalent FSM (Figure 3.3d).

- Step 5: Finally, connect the states to construct the equivalent FSM. For the states belonging to the same scheduled DFG (within a basic block), apply an edge directly between the states. To construct the transitions between states in different DFGs, replace each control edge between two basic blocks in the CFG with an equivalent edge between states in the FSM. The equivalent edge connects the last state of the predecessor basic block (i.e., cycle N of

the DFG for the predecessor basic block) with the first state in the successor basic block (i.e., cycle 0 of the DFG for the successor basic block)(Figure 3.3d).

The equivalent FSM constructed by this approach is a naive representation of the FSM that is generated by HLS tools for a given program. For example, multiple operations may be able to be performed on a single cycle, long latency instructions may result in multiple states, or there may be resources limitations in the number of operations that can occur per cycle. However, the simplified FSM maintains the impact of data dependence. We use our simple approach to perform analysis on the equivalent FSMs of SPEC2006 INT benchmarks[32]. Along with the Machsuite HLS benchmarks, we chose the SPEC2006 INT benchmark suite to compare the behaviour of the benchmarks that are and are not necessarily written for HLS.

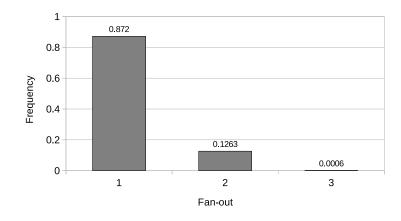

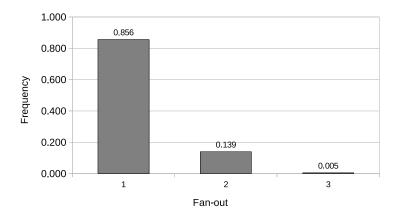

Figure 3.4a presents the fan-out degree of the equivalent FSM for both the Machsuite and SPEC CPU2006 INT benchmark suites. As can be seen, both benchmarks demonstrate very similar behaviour in the fan-out degree, with over 85% of the states having a single next state. Based on our construction of the equivalent FSM, these single fan-out edges are caused by data dependencies. However, they are independent of input as the timing schedule is predetermined in advance.

Although the simplifications in the equivalent FSM may affect the result of the fan-out degree experiment, the impact will mostly affect the number of states with fan-out degree equal to 1. The result of this experiment (Figure 3.4) shows a very large ratio between single and multi fan-out degrees. Hence, we believe that even with the assumptions discussed above, the equivalent FSM provides a good approximation of the actual FSM to highlight the existence of a large fraction of nodes with a single fan-out edge.

#### **3.2 Specialized FSM Block**

In this section, we first discuss the potential approaches to optimize the implementation of HLS-generated FSMs. We then describe our proposed specialized configurable architecture that takes advantage of the HLS-generated FSM characteristics to implement the FSMs in a more area/delay efficient manner. We also provide

Figure 3.3: Equivalent FSM construction

(b) Spec CPU2006 INT

data that justifies the main design decisions that lead to the final architecture of this hybrid architecture.

#### **3.2.1** Design Space Exploration

There are different approaches to exploit the properties of HLS-generated FSMs to optimize the FSM implementation on FPGAs. These approaches along with their benefits and drawbacks are described below:

#### **Specialized Hard Blocks**

One potential solution is to introduce a specialized hard block to FPGA Architecture that is designed to only implement the HLS-generated FSMs. Such specialized hard block is extremely efficient compared to the FPGA LUT-based logic blocks due to the reduced overhead that comes with the flexibility of LUT-based logic blocks. In this thesis, we propose and evaluate a novel mix-grained architecture that makes use of such hard blocks to improve the efficiency of FSM implementation on FPGAs.

#### Soft-Logic and Block RAMs

Another potential approach is to use FPGA soft-logic to implement an adder unit that interacts with the existing embedded memories on FPGAs to implement the FSM in a more efficient manner. In this approach, the synthesis tool is responsible to transform the FSM description to a logic circuit that implements the FSM using an adder, control logic, and memory.

This approach does not require any modification to the existing FPGA architecture. However, due to the overhead of the soft-logic implementation of the adder and control logic along with using programmable routing between the adder, control logic, and memory unit, this solution is not as efficient as having specialized hard blocks. Evaluation of this approach is left to future work.

#### **Modified Block RAMs**

Another solutions is to modify the existing block RAMs on FPGAs by adding a hard adder and control logic to these blocks such that they can support our proposed FSM implementation. This is a promising approach, however, the existing block RAMs on FPGAs are typically synchronous memories. Therefore, digital designs that are not latency tolerant are not able to be mapped to such block RAMs, since a synchronous memory read adds one cycle delay to the state calculation process. Evaluation of this approach is left to future work.

Figure 3.5: High-level view of the specialized FSM architecture

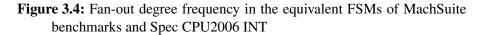

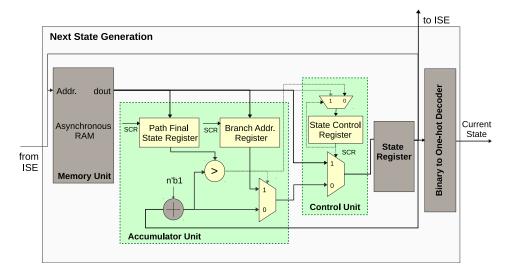

#### 3.2.2 Mix-Grained Architecture

Our proposed architecture consists of both fine-grained (soft) and coarse-grained (hard) logic that are connected via hard (or flexible FPGA) routing, which together form the mix-grained architecture. The high-level architecture is illustrated in Figure 3.5. The coarse-grained part of this architecture implements the next state calculation and consists of two main units, the accumulator unit and memory unit. The accumulator unit takes care of state calculation for the states that belong to the branch-free paths, while the memory unit stores the next states for the remaining states, along with some metadata that will be described later. As previously mentioned, these remaining states tend to have a low fan-out degree, which makes them well suited to be stored in memory, since fan-out degree directly corresponds to the number of entries per-state in memory. The fine-grained part of this architecture takes the current state and input signals and tries to minimize the address space of the memory unit, and hence, the memory size. As mentioned in Section 3.1.3, the reduction of the state address space is possible since the number of reachable states from a given state is often much less than the maximum possible number of reachable states.

The following sections describe the the coarse-grained and fine-grained parts of the proposed architecture in more detail.

#### 3.2.3 Input Sequence Encoder Unit

The input sequence encoder unit implements a configurable encoder using the FPGA soft logic. Figure 3.6 and Figure 3.7 explain the intuition behind having such unit. At each state of the state machine only a subset of input signals impact the state transition. This subset of inputs are called *active inputs*. FSMs extracted from our benchmarks sets have variable number of inputs ranging from 3 to 56, however, the number of active inputs at each state is much less for these benchmarks (characteristics of FSMs are listed in detail in Chapter 4). As shown in Figure 3.6, the number of state machine active inputs per state varies from 0 to 5, however, the number of next reachable states from a given state (i.e number of fanouts per node in the state transition graph) does not exceed 4. This means that the choice of next state, which corresponds to the memory address, can be represented by only 2 bits instead of 56. Therefore, we use a simple encoder that maps the possible large input sequence for the state machine to a smaller sequence of length log<sub>2</sub> (maximum number of reachable states per state). This significantly reduces the size of the memory unit that is used for next state calculation as it enables us to avoid storing don't care data for unreachable states. The input sequence encoder unit can be easily implemented on a LUT-based cluster as part of the conventional FPGA architecture.

#### 3.2.4 Coarse-Grained Fabric

The coarse-grained fabric corresponds to the "Next State Generation" block in Figure 3.5. By analyzing the edge distribution of the state transition graphs among our benchmark suite (discussed more in Chapter 4), we observed abundance of branch-free paths, states with only one next state where the transition between states is input-independent. In Section 3.4 we describe a simple encoding that enables using a single accumulator in order to calculate the next state value for such states.

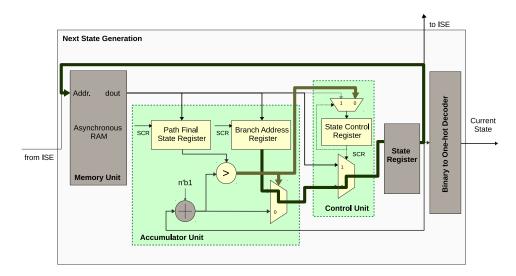

Figure 3.8 presents a detailed breakdown of the next state generation block shown in Figure 3.5. The following subsections describe each of the components in more detail.

There are timing requirements for the FSM block that require delay of certain

**Figure 3.6:** Number of active inputs per state calculated as average over 46 FSMs extracted from 21 benchmarks generated by HLS. Details of the benchmarks are described in Chapter 4.

**Figure 3.7:** Edge distribution: number of transitions per state calculated as an average over 46 FSMs extracted from 21 benchmarks generated by HLS. Details of the benchmarks are described in Chapter 4.

data. For example, metadata read from an entry in memory corresponds to the next state and in case of the branch-free paths, metadata is used for the entire path as

such we require a mechanism to save the metadata. That is why we use the registers to delay the metadata by one cycle such that they apply to the next state and in the case of the branch-free path to the l next following state where l is the length of the path. "Path Final State Register", "Branch Address Register", and "State Control Register" are the registers that we have used for this purpose which are explained in detail below.

Figure 3.8: Next state generation block

#### **Accumulator Unit**

This unit is responsible for calculating the next state values for the trailing inputindependent states on a branch-free path. After applying the proposed state encoding, the next state value for states that belong to a given branch-free path in a state transition graph can be calculated using a simple accumulator along with some extra information, which are described below:

• Adder: The adder is the main part of the accumulator unit. It takes in the current state and increments the value to calculate the next state in the branch-free path. It has two inputs: a single 1-bit value set to one, and the current state value coming from the output of the state register.

- **Control logic**: While an adder is enough to calculate the next state value for the branch-free states, it is not sufficient to determine when we have reached the end of the branch-free path. Additionally, once we have reached the end of the branch-free path, we need to read the next state value from memory. However, the address to this state is not just the current state encoding, since the memory address space is separate from the state encoding for branch-free paths. Therefore, we use two metadata registers to store this information for each path.

- The **Path Final State Register** is set to the state value of the last state on the path. This is used to mark the ending state of the path.

- The Branch Address Register is set to the address we should read from the memory once we have reached the end of the branch-free path.

- The comparator is used to compare the values of the path final state register with the output of the accumulator, and then generates the control signal which decides if the next state value should come from the accumulator or the Branch Address Register.

#### **Memory Unit**

The memory unit is responsible for storing the next state value for the sates that do not belong to a branch-free path along with some metadata to assist with the transition from the accumulator unit to memory unit. To avoid adding an extra cycle delay to the next state calculation, an asynchronous memory block must be used for this unit. Figure 3.9 shows the content of a row in memory. It consist of four main fields: (1) Next State Value (2), Path Final State, (3) Branch Address, and (4) State Control bit. The first and fourth fields always have a valid value, however the second and third fields will only be valid in the case where next state belong to a branch-free path. In this case, the contents of these two fields will be registered into the registers described in the accumulator unit, as described above. The last field, state control bit, is used to determine if the source of the next state value should be the accumulator unit or memory unit. This field will be registered into the control unit register that will be described below.

The depth of the memory is dependent on the non-branch-free states and edge distribution and the width is based on the next state plus metadata. In Chapter 5 we describe how we size the memory unit in detail.

| Next State Value | Path Final State | Branch Target | State Control |

|------------------|------------------|---------------|---------------|

|------------------|------------------|---------------|---------------|

Figure 3.9: Memory content

#### **Control Unit**

The control unit is responsible for selecting the source of the next state value between the accumulator unit and memory unit using a multiplexer which is controlled by the "State Control Register". The State Control Register can be set in two different ways: (1) The State Control Field of the memory unit for the given state Figure 3.9, or (2) the result of the comparator in the accumulator unit which marks the termination of the branch-free path, Figure 3.8). At any given time, either the memory unit or the accumulator unit is active and responsible for calculating the next state value. The active unit is responsible for selecting whether the same unit is active on the next cycle or the other unit is active on the next cycle. This is implemented as a feedback loop from the State Control Register to the select signal of the multiplexer feeding the State Control Register. This continues to select the same unit until that unit signals a transition by toggling zero to one or vice versa.

#### **State Decoder**

We provide an optional binary to one-hot decoder at the output of this block to enable more efficient binary to one-hot conversion if required by the rest of the circuit.

# 3.3 Fracturable FSM Hard Blocks

The size of finite state machines can vary significantly among different applications. As mentioned in Chapter 2, any hard block on FPGAs will be wasted if not fully utilized by the applications, leading to fragmentation in the hard blocks. Therefore, to be able to efficiently accommodate state machines with various number of states, we propose fracturable FSM hard blocks. The main idea behind having fracturable FSM blocks is to tailor the block size such that it accommodate the state machines with an average size while supporting combination of two blocks such that they can accommodate large FSMs that do not fit into just one block. To map a large state machine to multiple smaller combined blocks, the state machine needs to be partitioned to multiple sub state machines, and the architecture should enable fast transition between these blocks. In this work we only look at partitioning state machines to two sub-machine which enables us to accommodate all the FSM benchmarks that we use, however, our approach can be easily applied to more partitions. We first describe our partitioning method and then propose minor modifications to the FSM hard block to support FSM block combination.

#### 3.3.1 FSM Partitioning

Given an input graph G = (V, E), the objective of bi-partitioning problem is to partition the vertex set V into two disjoint subsets with the main goal of minimizing the number of edges between two subsets. The FSM partitioning (decomposition) problem is a famous problem [21] with plenty of possible solutions which are mainly proposed to target complex state machines. For the purpose of partitioning HLS-generated FSMs, which are less complex in terms of the number of transition between different states, we chose a classic algorithm known as Fiduccia-Matheyses partitioning algorithm [9] and, with an example in Chapter 5, show that it works very well for the state machines that are generated by HLS tools. Fiduccia-Matheyses partitioning algorithm is an iterative mincut heuristic algorithm with a linear computation time with respect to the size of the input graph.

#### 3.3.2 Fracturable FSM Block Architecture

When splitting an FSM over multiple fracturable blocks, every state transition across two different blocks requires control signals that enable switching between these blocks. For example, if the current state X is mapped to the fracturable block A and the next state Y is mapped to the fracturable block B, then when the transition occurs, the state register of block A must enter the idle state (described later), and the state register of block B must be updated to Y. To enable this switching between the blocks, state X must carry the metadata that controls this transition. A potential candidate to store this metadata is the memory unit. If the states that mark the transition across fracturable blocks are stored in memory, an extra field on each memory row can be used to store the required metadata for transitioning across the blocks. In this example, state X must be stored in memory. For this work, we only allow splitting the FSM over two fracturable blocks, thus a single bit in memory is sufficient to indicate whether the next state should be calculated in this block or the other fracturable block that implements the same FSM

By transitioning to another fracturable block, we enter a new state which can either be mapped to the memory unit or accumulator unit. As described in Section 3.2.4, if this state is mapped to the accumulator unit the control registers, specifically, Path Final State Register, Branch Address Register, and State control Register must be updated as well. This requires extra multiplexer logic that allows setting the value of these registers from multiple sources which are the memory unit on the same block as well as the memory unit on the other fracturable block. To simplify this scenario and reduce the overhead logic, we decide to only map this state to the memory unit to avoid the need for updating the control registers described above.

To summarize, for any transition across two fracturable blocks, both current state and next state must be stored in memory. Although this increases the required memory size to accommodate the FSM, a proper partitioning algorithm that aims to reduce the number of transitions between blocks can limit this memory overhead to only a few extra entries.

Additionally, we must add a multiplexer before the state register in each fracturable block to allow updating the state value using the data stored in the other fracturable block, for the scenario where there is a transition between two blocks. We dedicate the state value *zero* as the idle state. Once the state calculation tasks gets transferred over to the other fracturable block, the inactive block will enter the idle state by updating its state register to *zero*.

The overheads and issues of splitting the FSM over more than two fracturable blocks are discussed in Chapter 5.

# **3.4** State Assignment Algorithm