# IMPLEMENTING DIGITAL CONTROL TO IMPROVE CONTROL BANDWIDTH AND DISTURBANCE REJECTION ON A LLC RESONANT DC-DC POWER CONVERTER

by

Yubo Lei

B.A., The University of British Columbia, 2012

# A THESIS SUBMITTED IN PARITAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

The Faculty of Graduate and Postdoctoral Studies

(Electrical & Computer Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

(Vancouver)

July 2015

©Yubo Lei, 2015

#### **Abstract**

In this thesis, the implementation of an adaptive digital control scheme and the development process to implement it for an existing analog controlled LLC resonant converter is presented. The goal is to improve the dynamic performance (aka control bandwidth) and the disturbance rejection ability of the closed loop system using digital control. A brief analysis of the experimented on LLC resonant converter and simulations of its control-to-output frequency response characteristics under different operating conditions are initially performed in order to show its non-linear behavior. Then the design process and requirements for both the digital and analog components to make the existing LLC converter compatible with a digital signal microcontroller is presented in detail. The digital signal microcontroller (DSC), ADC, DPWM, sampling period, interrupt service routine (ISR), and the 2P2Z digital compensator implementation will be overviewed. Analog components such as the voltage/current sensors, the VCO, and other analog interfacing components will also be presented. After that, the complete design process to achieve optimized digital compensators for several different operating points is presented. This design process introduces the method of using either the uncompensated loopgain frequency response data collected empirically from the physical converter or from a PSIM simulation and then using MATLAB's System Identification software toolbox to generate an estimated mathematical model based on frequency response data. A digital compensator is then designed based on the estimated mathematical model. A comparison between the PSIM simulation and the empirical data of the LLC converter's plant frequency response for several different operating conditions is also presented. A digital adaptive compensator algorithm is implemented so that the most optimized compensator design for a given converter operating range is selected. The algorithm uses the output voltage and current to determine the operating point of the converter, which then access a software look-up-table (LUT) for the optimized compensator. A complete prototype is built to experimentally validate the digital design process and the performance results of a classical single compensator design is compared with the adaptive compensator design in order to show the benefits of the adaptive compensator control scheme.

#### **Preface**

The experiments presented in this thesis were performed on a commercially available power converter provided by Delta-Q Technologies. Furthermore, some of the analog components presented in this thesis were part of the original LLC converter design such as the VCO and gain inverter op-amp circuit. Some components were also modified from their original design to better fit the digital design needs such as the sensors. All the prototyping work done was at Delta-Q technologies laboratories. My contributions include implementing digital control on the pre-existing LLC resonant power converter (model: IC650), which involved collecting data necessary to model the converter, using MATLAB to produce estimated models, and programming the digital signal microcontroller to implement the adaptive control algorithm.

## Table of Contents

| Abstra  | act                                                         | ii    |

|---------|-------------------------------------------------------------|-------|

| Prefac  | ce                                                          | iii   |

| Table   | of Contents                                                 | iv    |

| List of | f Tables                                                    | vii   |

| List of | f Figures                                                   | viii  |

| List of | f Symbols                                                   | xiii  |

| List of | f Abbreviations                                             | xiv   |

| List of | f Units and Prefixes                                        | xvi   |

| Ackno   | owledgements                                                | xvii  |

| Dedic   | eation                                                      | xviii |

| 1 In    | ntroduction                                                 | 1     |

| 1.1     | Overview                                                    | 1     |

| 1.2     | Digital Control                                             | 1     |

| 1.3     | Motivation and Objective                                    | 4     |

| 1.4     | Outline                                                     | 5     |

| 2 L     | Literature Review                                           | 7     |

| 2.1     | Resonant Converters                                         | 7     |

| 2.2     | LLC Resonant Converter                                      | 9     |

| 2.3     | LLC Converter Design Specifications                         | 13    |

| 2.4     | LLC Plant Frequency Response                                | 14    |

| 3 I     | Digital Design Infrastructure Components and Considerations | 19    |

| 3.1     | Digital Design Infrastructure Overview                      | 19    |

| 3.2     | Digital Components & Consideration                          | 21    |

| 3       | 3.2.1 Analog-to-Digital Converter (ADC)                     | 21    |

| 3.2.2     | High Resolution PWM (HRPWM)              | 22 |

|-----------|------------------------------------------|----|

| 3.2.3     | Digital 2P2Z Compensator                 | 25 |

| 3.2.4     | Sampling Rate                            | 26 |

| 3.2.5     | Interrupt Selection                      | 30 |

| 3.3 An    | alog Components: Sensors & Filters & VCO | 30 |

| 3.3.1     | RC Low-pass Filter                       | 30 |

| 3.3.2     | Gain Inverting Op-amp Circuit            | 33 |

| 3.3.3     | Voltage Controlled Oscillator (VCO)      | 33 |

| 3.3.4     | Voltage Sensor                           | 34 |

| 3.3.5     | Current Sensor                           | 36 |

| 4 Digital | Controller Design Implementation Process | 38 |

| 4.1 Ov    | verview                                  | 38 |

| 4.2 Fre   | equency Response Data                    | 39 |

| 4.2.1     | Venable Frequency Response Analyzer      | 40 |

| 4.2.2     | PSIM                                     | 44 |

| 4.2.3     | PSIM vs Venable Frequency Response Data  | 47 |

| 4.3 MA    | ATLAB System Identification Process      | 52 |

| 4.4 Co    | mpensator Design & Performance Results   | 60 |

| 4.4.1     | MATLAB SISO Toolbox                      | 60 |

| 4.4.2     | Compensator Design                       | 61 |

| 4.4.3     | Compensator and Performance Results      | 67 |

| 5 Adapti  | ve Digital Control Software Architecture | 77 |

| 6 Experi  | mental Validation & Results              | 81 |

| 6.1 Pro   | ototype Setup and Design                 | 81 |

| 6.2 Ex    | perimental Data & Performance Results    | 82 |

|           |                                          |    |

| 7   | Conclu    | sions and Future Work                                                       | 93    |

|-----|-----------|-----------------------------------------------------------------------------|-------|

| 7   | 7.1 Co    | onclusions                                                                  | 93    |

|     | 7.1.1     | Considerations of Implementing Digital Design on an Existing Analog Control | olled |

|     | Conve     | rter                                                                        | 93    |

|     | 7.1.2     | Effectiveness of the Empirical Data Modelling Approach                      | 94    |

|     | 7.1.3     | Performance Improvements with Adaptive Compensation Design vs Single        |       |

|     | Compe     | ensation Design                                                             | 94    |

|     | 7.1.4     | Venable vs PSIM Frequency Response Data Accuracy                            | 95    |

|     | 7.1.5     | Obtaining the Frequency Response Data More Quickly and Efficiently          | 95    |

| 7   | 7.2 Fu    | ture Work                                                                   | 96    |

| Bil | bliograph | ıy                                                                          | 97    |

| Аp  | pendices  |                                                                             | 101   |

| A   | Appendix  | A: TI C2000 Piccolo TMSF28035 Specifications                                | 101   |

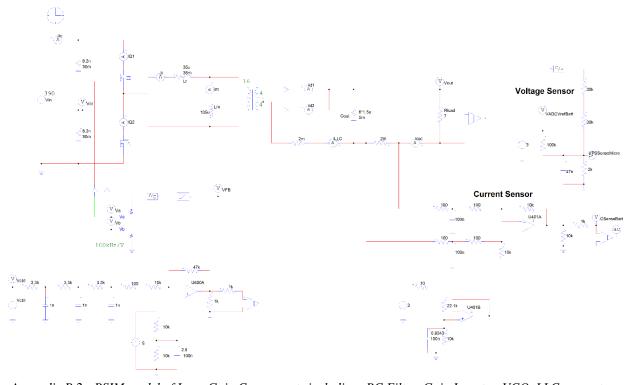

| A   | Appendix  | B: PSIM Simulation Schematics                                               | 103   |

## List of Tables

| Table 2.1 - Full-Wave rectifier compared to Full-Bridge rectifier                        | . 11 |

|------------------------------------------------------------------------------------------|------|

| Table 2.2 - LLC Converter Specifications and component values                            | . 14 |

| Table 2.3 - Voltage Plant switching frequency for various operating points               | . 16 |

| Table 2.4 - Current Plant switching frequency for various operating points               | . 18 |

| Table 3.1 - Conventional PWM resolution vs HRPWM resolution                              | . 25 |

| Table 3.2 - Sampling frequency, sampling period, # of cycles for 60MHz CPU               | . 27 |

| Table 3.3 - Summary of sample timings for different sample window values                 | . 28 |

| Table 3.4 – Percentage CPU utilization for the interrupt service routine implemented     | . 29 |

| Table 4.1 - Compensation stability objectives                                            | . 61 |

| Table 4.2 - Optimized adaptive compensator designs using MATLAB SISO for continuous tin  | ne   |

| and converted into discrete-time using bilinear transformation with a sampling period of |      |

| T <sub>s</sub> =1/400kHz                                                                 | . 68 |

| Table 4.3 - Step Response Settling Times for Single Compensator vs Adaptive Compensator  |      |

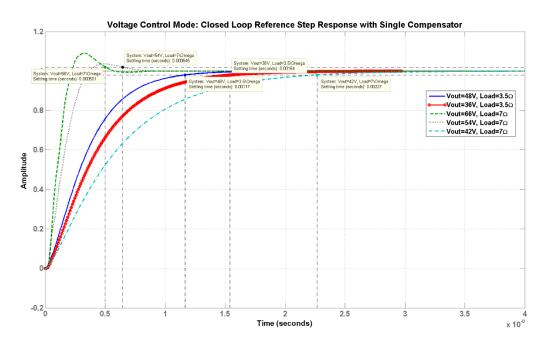

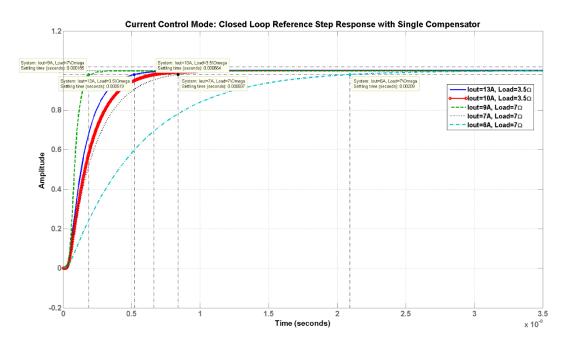

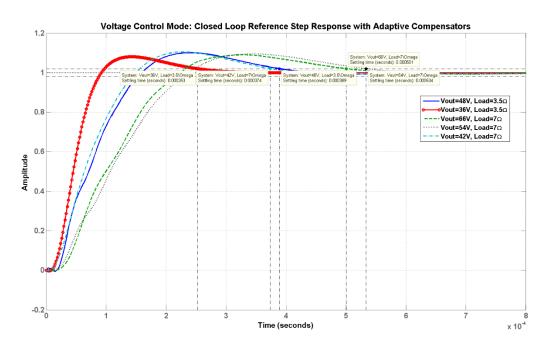

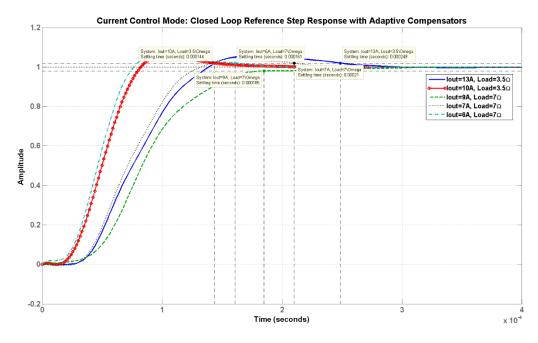

| Design (Simulated)                                                                       | . 74 |

| Table 4.4 - Single compensator performance results (MATLAB Simulated)                    | . 75 |

| Table 4.5 - Adaptive compensation performance results (MATLAB Simulated)                 | . 76 |

| Table 6.1 – Single digital compensator experimental performance results                  | . 85 |

| Table 6.2 - Adaptive digital control compensation experimental performance results       | . 86 |

## List of Figures

| Figure 1.1 - Simplified block diagram of power converter with digital signal controller        | 2    |

|------------------------------------------------------------------------------------------------|------|

| Figure 2.1 - Series Resonant Converter (SRC)                                                   | 7    |

| Figure 2.2 - Parallel Resonant Converter (PRC)                                                 | 8    |

| Figure 2.3 - Series Parallel Resonant Converter (SPRC) LCC                                     | 8    |

| Figure 2.4 - LLC Resonant Converter                                                            | 9    |

| Figure 2.5 - Full-Bridge & Half-Bridge switching circuits                                      | 10   |

| Figure 2.6 - LLC Resonant Tank                                                                 | 10   |

| Figure 2.7 - Full-Bridge (left) and Half-Bridge (right) rectifier                              | 11   |

| Figure 2.8 - Typical LLC Converter DC gain characteristic                                      | 12   |

| Figure 2.9 - LLC resonant converter basic design and component values                          | 13   |

| Figure 2.10 - LLC circuit setup for the plant control-to-output frequency response measurement | ent  |

|                                                                                                | 14   |

| Figure 2.11 - LLC Voltage Plant frequency response with Load= $3.5\Omega$ (PSIM Simulation)    | 15   |

| Figure 2.12 - LLC Voltage Plant frequency response with Load= $7\Omega$ (PSIM Simulation)      | 16   |

| Figure 2.13 - LLC Current Plant frequency response with Load= $3.5\Omega$ (PSIM Simulation)    | 17   |

| Figure 2.14 - LLC Current Plant frequency response with Load= $7\Omega$ (PSIM Simulation)      | 17   |

| Figure 3.1 – High-level block diagram of the digital control infrastructure for the LLC conver | rter |

|                                                                                                | 19   |

| Figure 3.2 - Continuous to discrete signal conversion                                          | 21   |

| Figure 3.3 - Limit cycle effect                                                                | 23   |

| Figure 3.4 - Conventional generated PWM resolution calculation                                 | 23   |

| Figure 3.5 - Micro edge positioner (MEP) concept                                               | 24   |

| Figure 3.6 – Graphical representation of a 2P2Z IIR Filter with a saturation limit             | 26   |

| Figure 3.7 - Processor bandwidth vs control code                                               | 27   |

| Figure 3.8 - ADC sequential sample timing                                                      | 28   |

| Figure 3.9 - PWM signal low pass filtered to a desired analog signal                           | 30   |

| Figure 3.10 - Decomposition of PWM signal                                                      | 31   |

| Figure 3.11 - RC 3 <sup>rd</sup> order low-pass filter                                         | 31   |

| Figure 3.12 - Frequency response of RC 3 <sup>rd</sup> order low-pass filter (PSIM vs Venable) | 32   |

| Figure 3.13 - Gain Inverting Op-amp (Gain Inverter)                                                | 33                         |

|----------------------------------------------------------------------------------------------------|----------------------------|

| Figure 3.14 - NCP1395 VCO operating frequency range                                                | 34                         |

| Figure 3.15 - Voltage Sensor for the Load                                                          | 34                         |

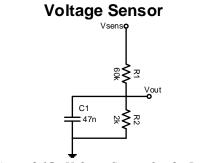

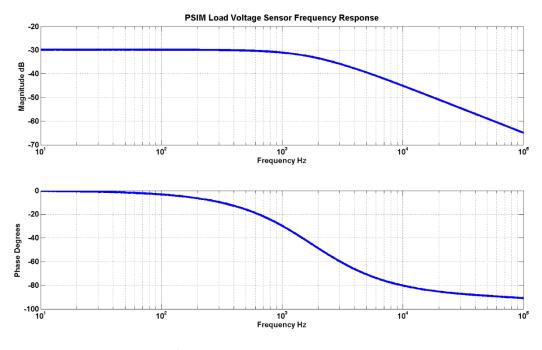

| Figure 3.16 - Voltage Sensor Frequency Response (PSIM)                                             | 35                         |

| Figure 3.17 - Current Sensor for the Load                                                          | 36                         |

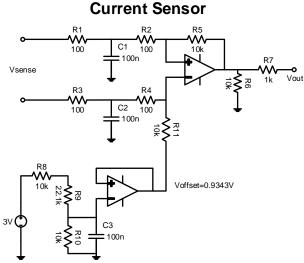

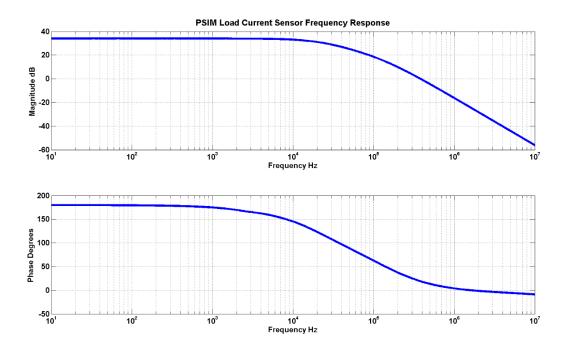

| Figure 3.18 - Current Sensor Frequency Response (PSIM Simulation)                                  | 37                         |

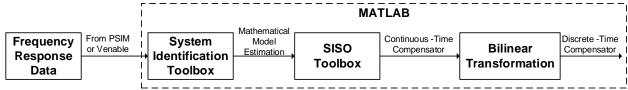

| Figure 4.1 - High Level Overview of Digital Controller Design Process                              | 39                         |

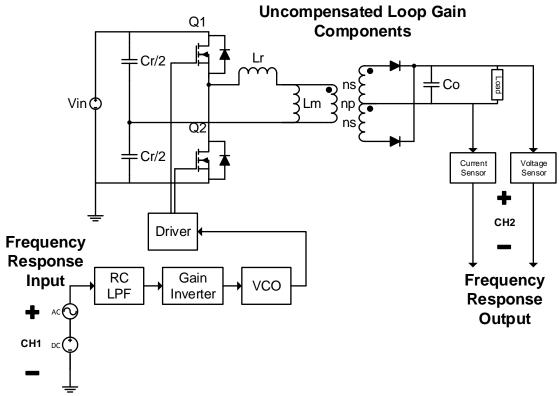

| Figure 4.2 - Uncompensated loop gain frequency response components                                 | 40                         |

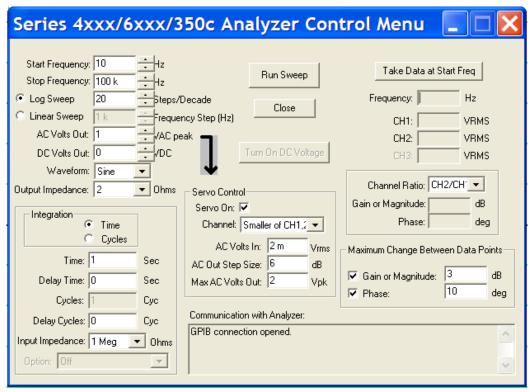

| Figure 4.3 – Venable Software Program Frequency Response Analyzer Control Menu Settin              | gs 41                      |

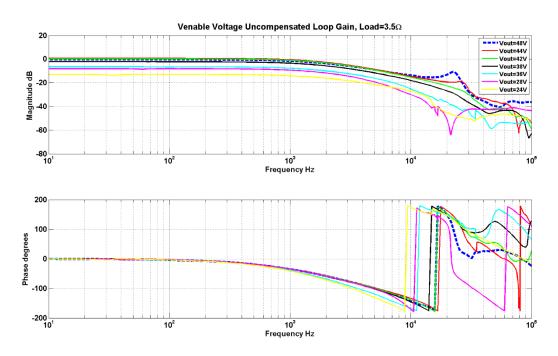

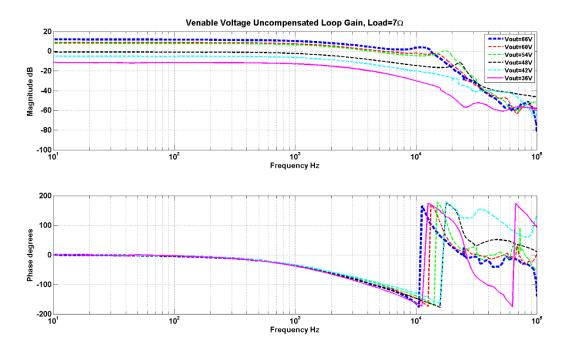

| Figure 4.4 - Venable uncompensated voltage loop gain with load=3.5 $\Omega$ (physical measurem     | ent                        |

| data)                                                                                              | 42                         |

| Figure 4.5 - Venable uncompensated voltage loop gain with load= $7\Omega$ (physical measurement    | ıt                         |

| data)                                                                                              | 42                         |

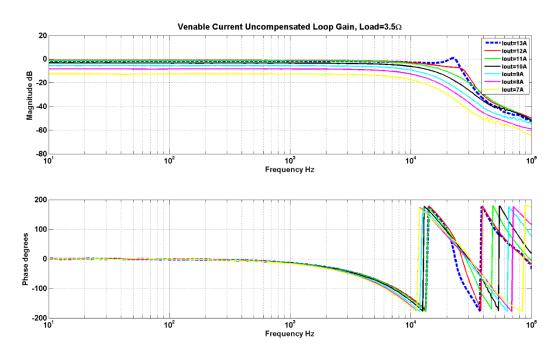

| Figure 4.6 - Venable uncompensated current loop gain with load= $3.5\Omega$ (physical measurement) | ent                        |

| data)                                                                                              | 43                         |

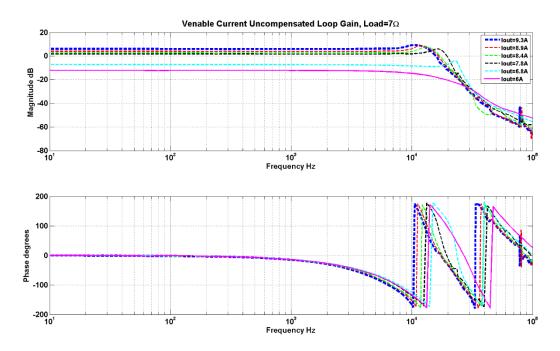

| Figure 4.7 - Venable uncompensated current loop gain with load= $7\Omega$ (physical measurement    | t                          |

| data)                                                                                              | 43                         |

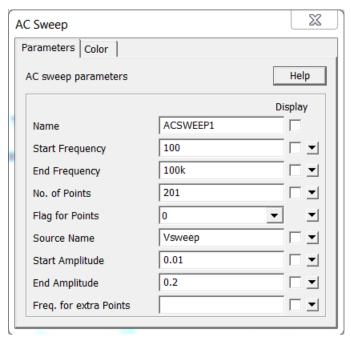

| Figure 4.8 - PSIM AC Sweep setting                                                                 | 44                         |

|                                                                                                    |                            |

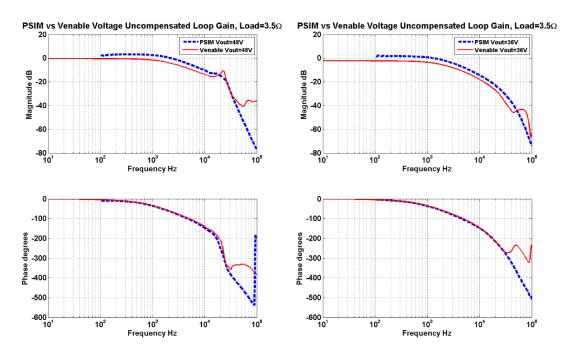

| Figure 4.9 - PSIM uncompensated voltage loop gain with load= $3.5\Omega$                           | 45                         |

| Figure 4.9 - PSIM uncompensated voltage loop gain with load= $3.5\Omega$                           |                            |

|                                                                                                    | 45                         |

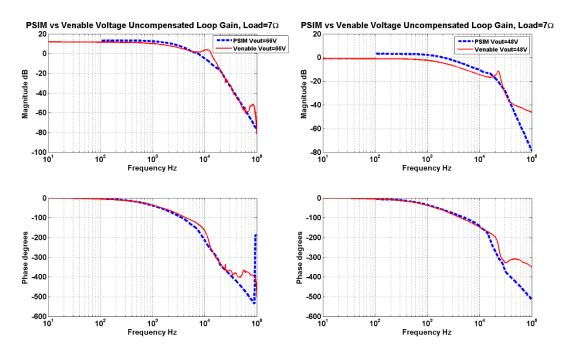

| Figure 4.10 - PSIM uncompensated voltage loop gain with load= $7\Omega$                            | 45<br>46                   |

| Figure 4.10 - PSIM uncompensated voltage loop gain with load= $7\Omega$                            | 45<br>46<br>46             |

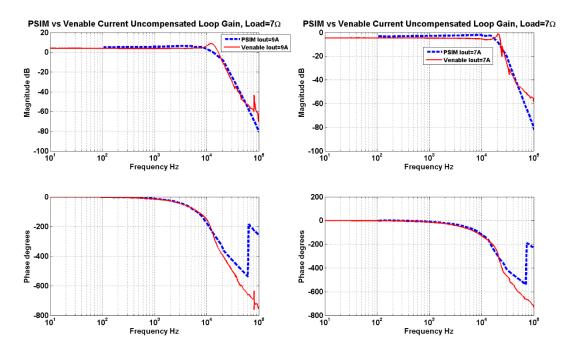

| Figure 4.10 - PSIM uncompensated voltage loop gain with load= $7\Omega$                            | 45<br>46<br>46<br>47       |

| Figure 4.10 - PSIM uncompensated voltage loop gain with load= $7\Omega$                            | 45<br>46<br>46<br>47<br>48 |

| Figure 4.10 - PSIM uncompensated voltage loop gain with load= $7\Omega$                            | 45<br>46<br>46<br>47<br>48 |

| Figure 4.10 - PSIM uncompensated voltage loop gain with load= $7\Omega$                            | 45<br>46<br>46<br>47<br>48 |

| Figure 4.10 - PSIM uncompensated voltage loop gain with load= $7\Omega$                            | 45<br>46<br>47<br>48<br>48 |

| Figure 4.10 - PSIM uncompensated voltage loop gain with load= $7\Omega$                            | 45<br>46<br>47<br>48<br>48 |

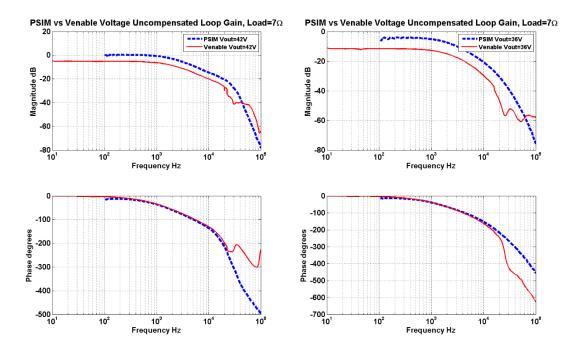

| Figure 4.19 - Uncompensated voltage loop gain, Vout=42V & 36V, Load=7Ω (PSIM vs            |        |

|--------------------------------------------------------------------------------------------|--------|

| Venable)                                                                                   | 50     |

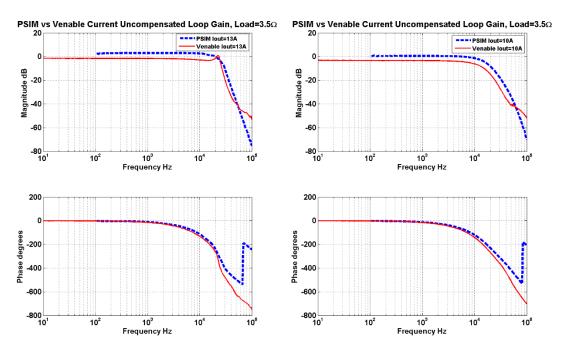

| Figure 4.20 - Uncompensated current loop gain, Iout=13A & 10A, Load=3.5Ω (PSIM vs          |        |

| Venable)                                                                                   | 51     |

| Figure 4.21 - Uncompensated current loop gain, Iout=9A & 7A, Load=7Ω (PSIM vs Venab        | le) 51 |

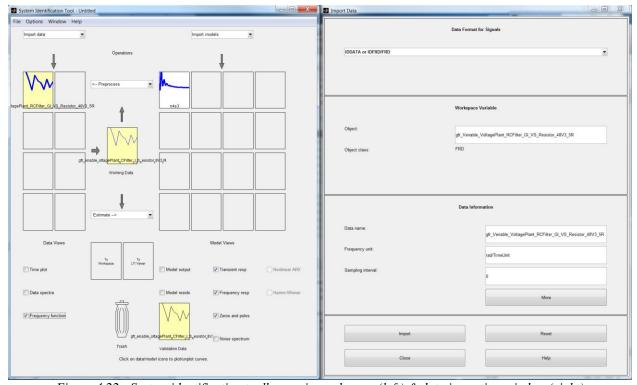

| Figure 4.22 - System identification toolbox main workspace (left) & data importing window  | 7      |

| (right)                                                                                    | 53     |

| Figure 4.23 - System identification toolbox model estimation structure GUI (right) & model | ĺ      |

| order selection (left)                                                                     | 54     |

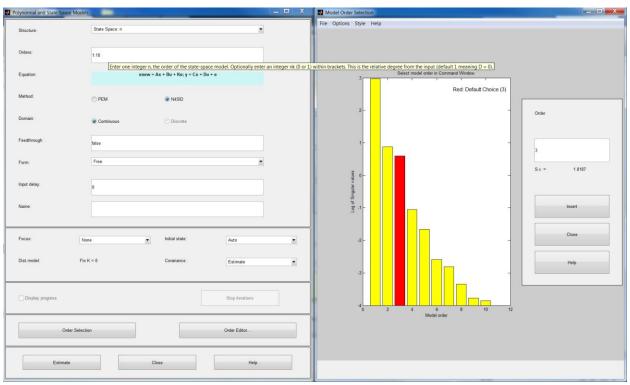

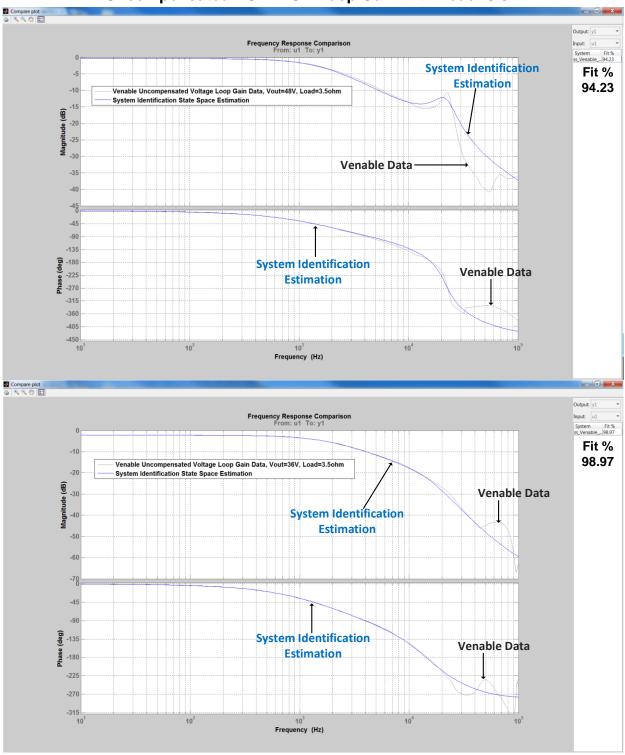

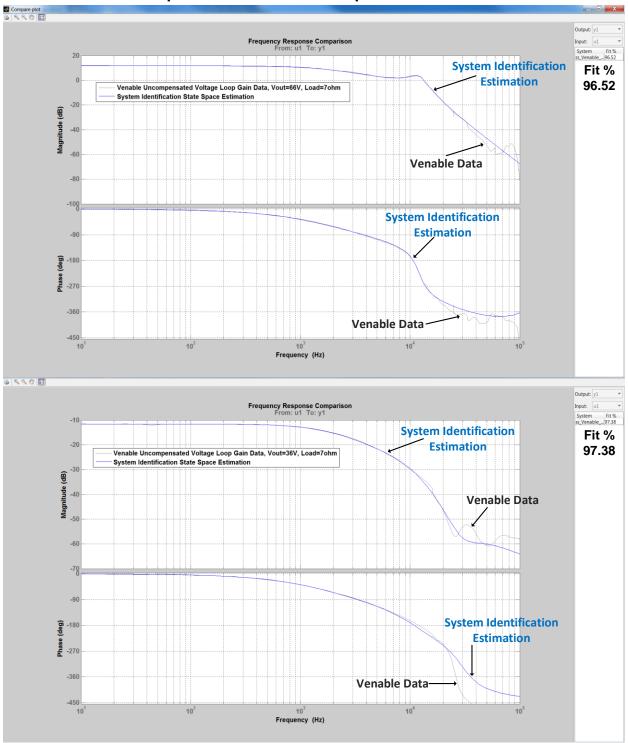

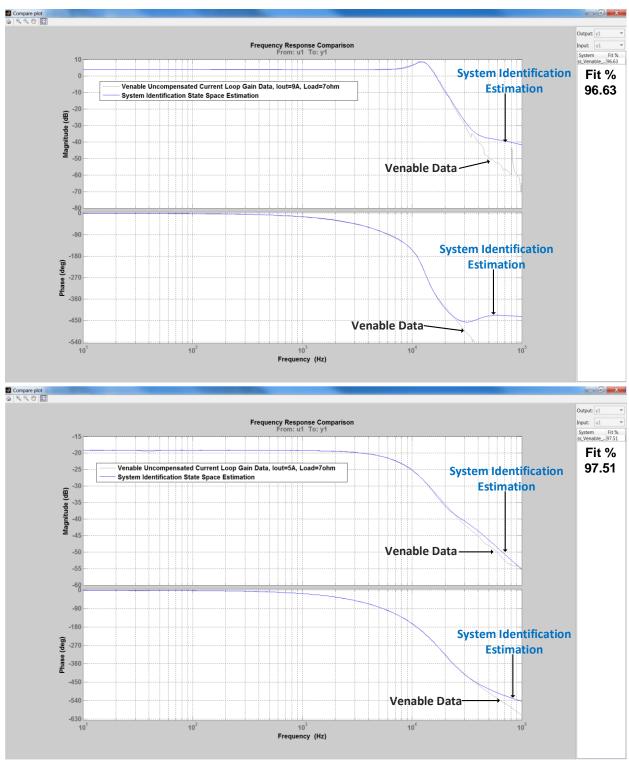

| Figure 4.24 - Uncompensated voltage loop gain, Venable data vs State-space estimation,     |        |

| Load= $3.5\Omega$                                                                          | 56     |

| Figure 4.25 - Uncompensated voltage loop gain, Venable data vs State-space estimation,     |        |

| Load= $7\Omega$                                                                            | 57     |

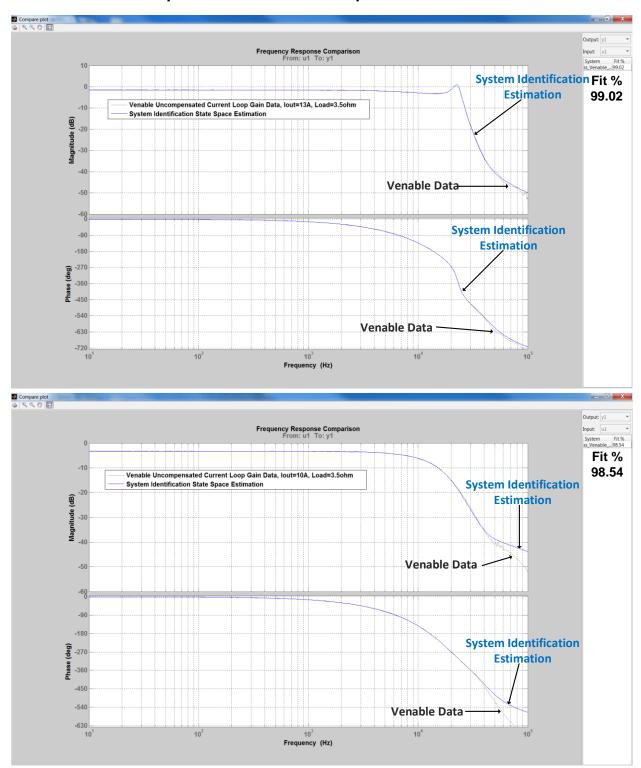

| Figure 4.26 - Uncompensated current loop gain, Venable data vs State-space estimation,     |        |

| Load= $3.5\Omega$                                                                          | 58     |

| Figure 4.27 - Uncompensated current loop gain, Venable data vs State-space estimation,     |        |

| Load= $7\Omega$                                                                            | 59     |

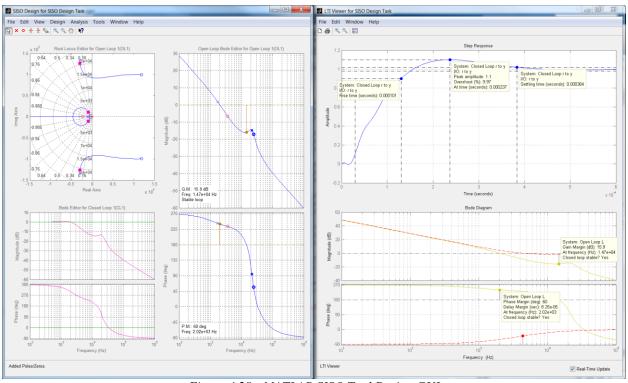

| Figure 4.28 - MATLAB SISO Tool Design GUI                                                  | 60     |

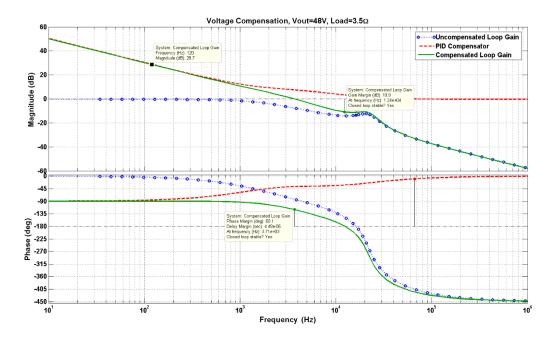

| Figure 4.29 - Frequency response of: uncompensated loop gain, compensator, compensated     | loop   |

| gaingain                                                                                   | 63     |

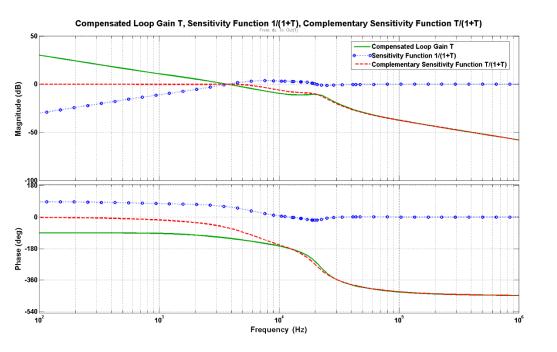

| Figure 4.30 - Frequency response of: compensated loop gain, sensitivity function,          |        |

| complementary sensitivity function                                                         | 64     |

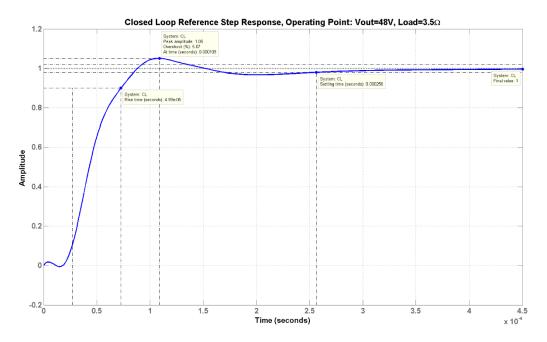

| Figure 4.31 - Closed-loop reference step response                                          | 65     |

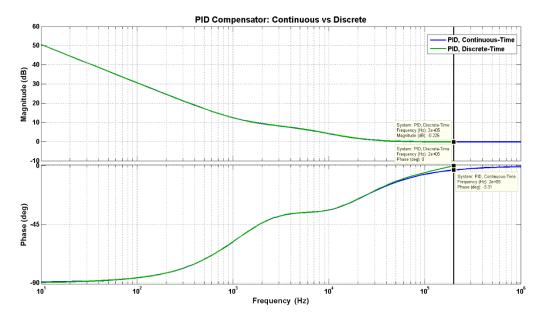

| Figure 4.32 - Continuous vs discrete compensator                                           | 67     |

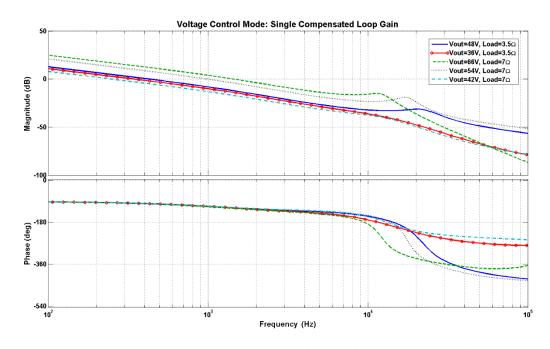

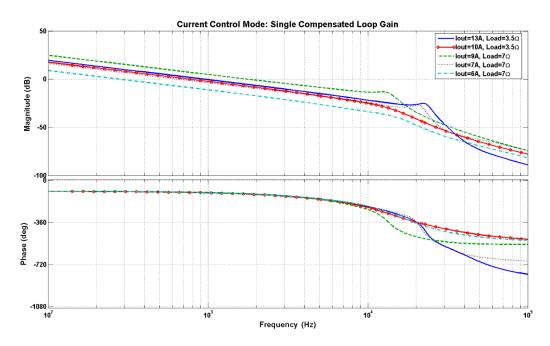

| Figure 4.33 - Single compensation control voltage loop gain (Simulated)                    | 69     |

| Figure 4.34 - Single compensation control current loop gain (Simulated)                    | 70     |

| Figure 4.35 - Closed loop (Voltage Mode Control) reference step response with single       |        |

| compensator (Simulated)                                                                    | 70     |

| Figure 4.36 - Closed loop (Current Mode Control) reference step response with single       |        |

| compensator (Simulated)                                                                    | 71     |

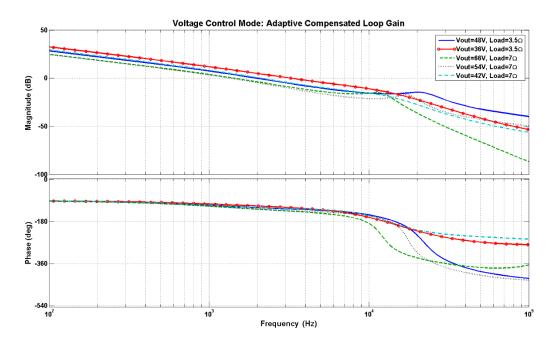

| Figure 4.37 - Adaptive compensation control voltage loop gain (Simulated)                  | 72     |

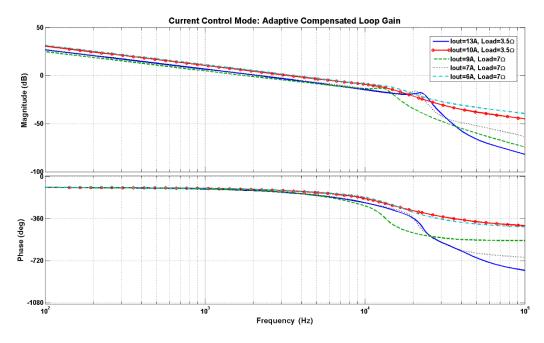

| Figure 4.38 - Adaptive compensation control current loop gain (Simulated)                   | . 72 |

|---------------------------------------------------------------------------------------------|------|

| Figure 4.39 - Closed loop (Voltage Mode Control) reference step response with adaptive      |      |

| compensator (Simulated)                                                                     | . 73 |

| Figure 4.40 - Closed loop (Current Mode Control) reference step response with adaptive      |      |

| compensator (Simulated)                                                                     | . 73 |

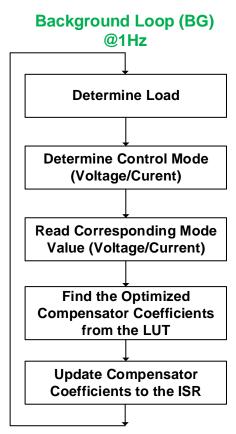

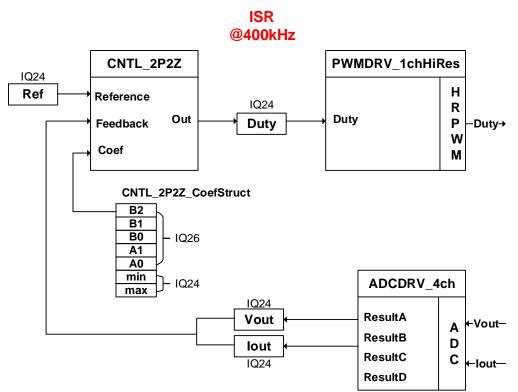

| Figure 5.1 – Adaptive control software architecture overview                                | . 77 |

| Figure 5.2 - Background loop (BG) in charge of selecting optimal compensator for a range of |      |

| operating points                                                                            | . 78 |

| Figure 5.3 - Interrupt service routine (ISR) control loop                                   | . 79 |

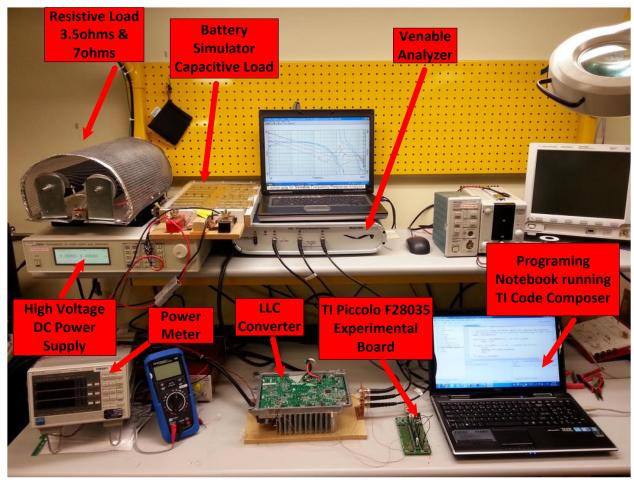

| Figure 6.1 - Experimental prototype lab bench setup for digital control of LLC converter    | . 81 |

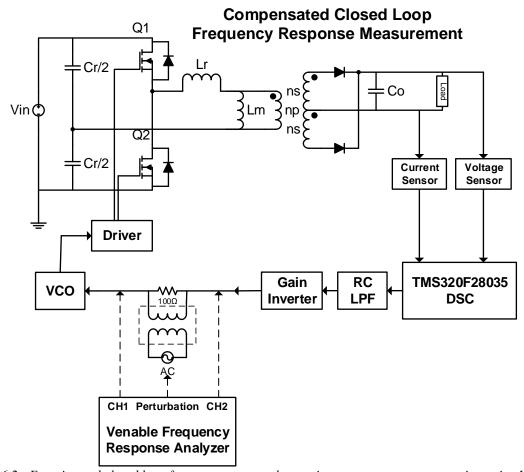

| Figure 6.2 - Experimental closed loop frequency response loop gain measurement setup        |      |

| overview using Venable                                                                      | . 82 |

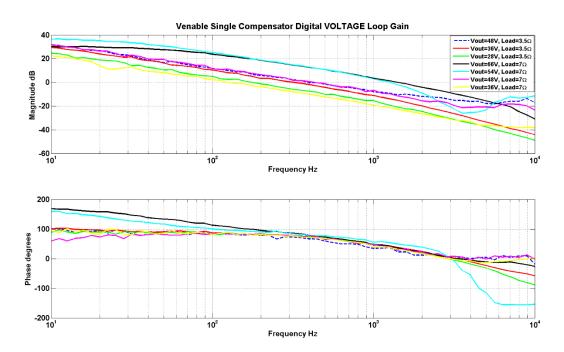

| Figure 6.3 - Single compensation digital voltage loop gain (Experimental Data)              | . 83 |

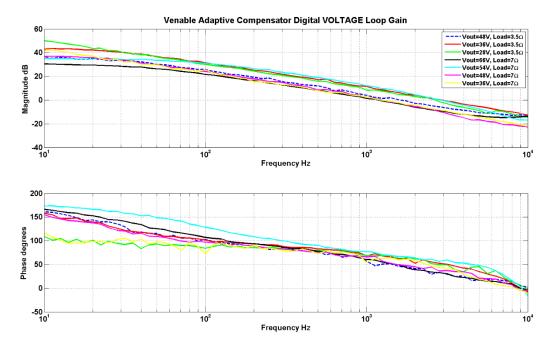

| Figure 6.4 - Adaptive compensation digital voltage loop gain (Experimental Data)            | . 83 |

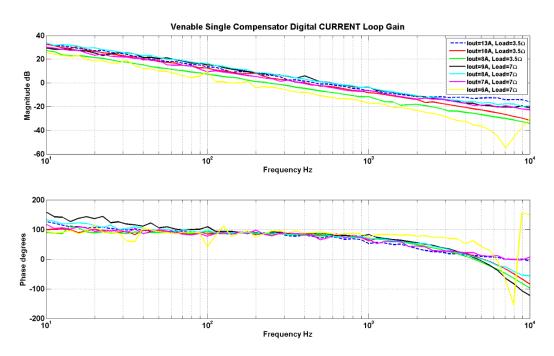

| Figure 6.5 - Single compensation digital current loop gain (Experimental Data)              | . 84 |

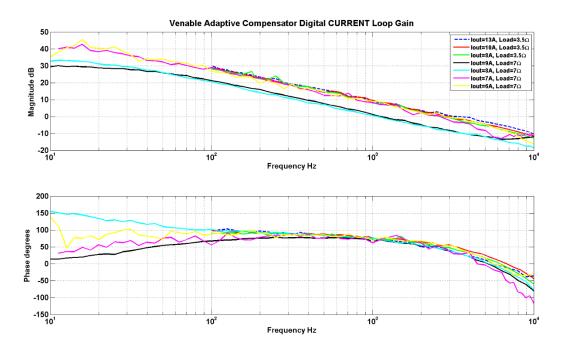

| Figure 6.6 - Adaptive compensation digital current loop gain (Experimental Data)            | . 84 |

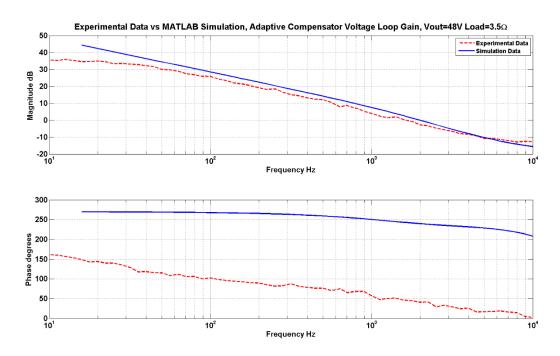

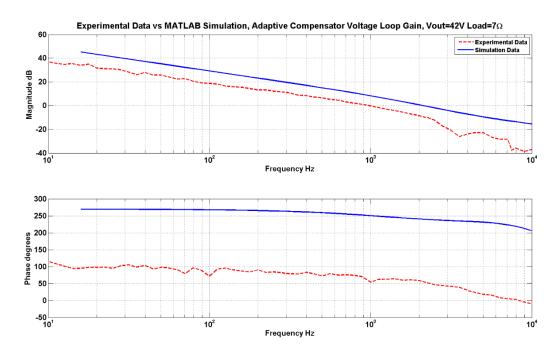

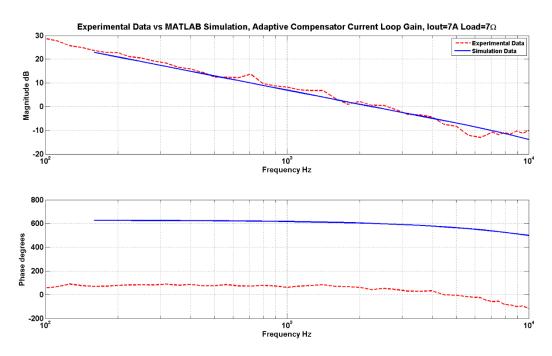

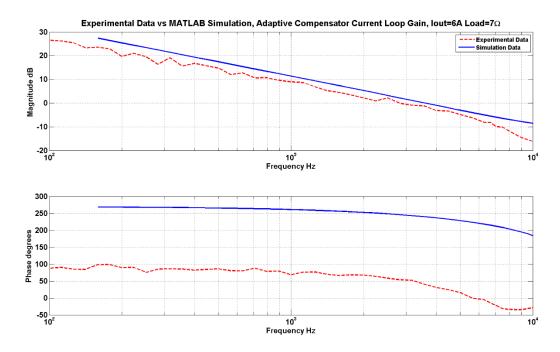

| Figure 6.7 – Venable experimental data vs MATLAB simulation, Adaptive Compensation,         |      |

| Voltage Loop Gain, Vout=48V Load=3.5Ω                                                       | . 87 |

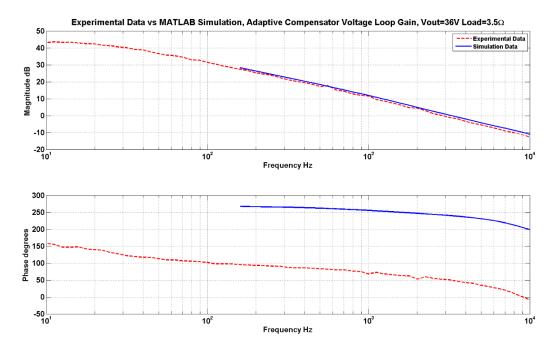

| Figure 6.8 - Venable experimental data vs MATLAB simulation, Adaptive Compensation,         |      |

| Voltage Loop Gain, Vout=36V Load=3.5Ω                                                       | . 87 |

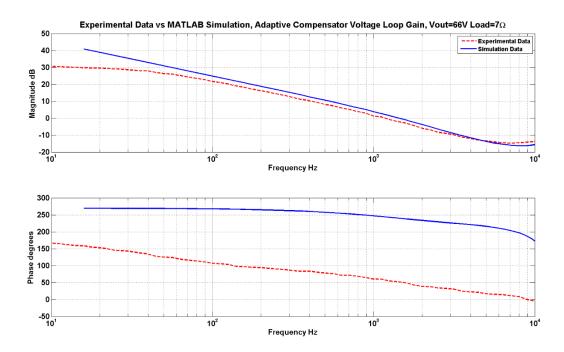

| Figure 6.9 - Venable experimental data vs MATLAB simulation, Adaptive Compensation,         |      |

| Voltage Loop Gain, Vout=66V Load=7Ω                                                         | . 88 |

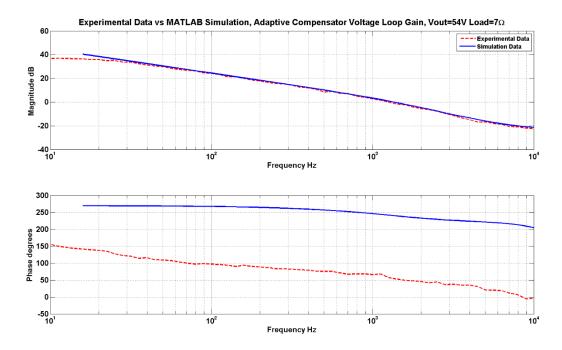

| Figure 6.10 -Venable experimental data vs MATLAB simulation, Adaptive Compensation,         |      |

| Voltage Loop Gain, Vout=54V Load=7Ω                                                         | . 88 |

| Figure 6.11 - Venable experimental data vs MATLAB simulation, Adaptive Compensation,        |      |

| Voltage Loop Gain, Vout=42V Load=7Ω                                                         | . 89 |

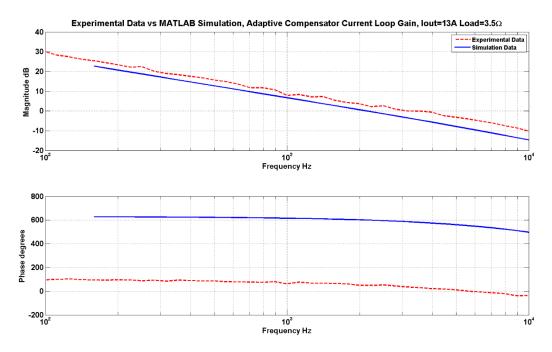

| Figure 6.12 - Venable experimental data vs MATLAB simulation, Adaptive Compensation,        |      |

| Current Loop Gain, Iout=13A Load=3.5Ω                                                       | . 89 |

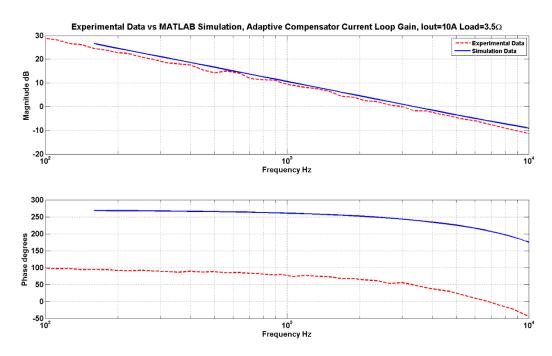

| Figure 6.13 - Venable experimental data vs MATLAB simulation, Adaptive Compensation,        |      |

| Current Loop Gain, Iout=10A Load=3.5Ω                                                       | . 90 |

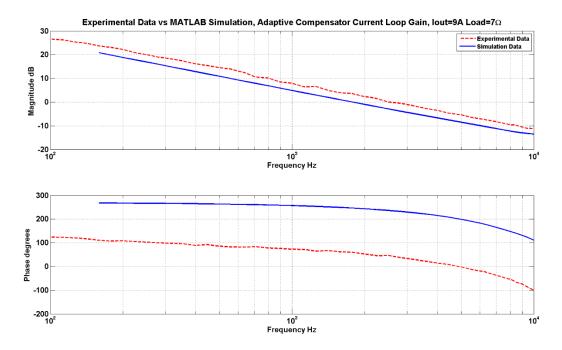

| Figure 6.14 - Venable experimental data vs MATLAB simulation, Adaptive Compensation, |      |

|--------------------------------------------------------------------------------------|------|

| Current Loop Gain, Iout=9A Load=7Ω                                                   | . 90 |

| Figure 6.15 - Venable experimental data vs MATLAB simulation, Adaptive Compensation, |      |

| Current Loop Gain, Iout=7A Load=7Ω                                                   | . 91 |

| Figure 6.16 - Venable experimental data vs MATLAB simulation, Adaptive Compensation, |      |

| Current Loop Gain, Iout=6A Load=7Ω                                                   | . 91 |

## **List of Symbols**

$n_{th}$  numerator coefficient of 2P2Z transfer function  $a_n$  $n_{th}$  denominator coefficient of 2P2Z transfer function  $b_n$  $C_r$ Resonant Tank Capacitor  $C_{s}$ Series Resonant Tank Capacitor  $C_{sr}$ Series Resonant Tank Capacitor for the Series Resonant Parallel Converter Parallel Resonant Tank Capacitor for the Series Resonant Parallel Converter  $C_{pr}$ **Cross-over Frequency**  $f_c$ Resonant Frequency  $f_o$ **Switching Frequency**  $f_{sw}$  $G_o$ Controller Gain Gain Margin  $g_m$ Magnetizing Inductor  $L_m$  $L_r$ Resonant Inductor **Transformer Ratio** n

Q Quality Factor

$T_s$  Sampling Period  $V_c$  Control Voltage

$V_{sq}$  Square Wave Voltage

$\theta_m$  Phase Margin

#### List of Abbreviations

2P2Z Two Pole Two Zero

AC Alternating Current

ADC Analog-to-Digital Converter

CLA Control Law Accelerator

CPU Central Processing Unit

DC Direct Current

DPWM Digital Pulse-Width Modulation

DSC Digital Signal Controller

DSP Digital Signal Processing

FLC Fuzzy Logic Control

FRA Frequency Response Analyzer

GUI Graphic User Interface

HRPWM High Resolution Pulse Width Modulator

IIR Infinite Impulse Response

ISR Interrupt Service Routine

LPF Low-pass Filter

LSB Least Significant Bit

MAC Multiply and Accumulate

MEP Micro Edge Positioner

MSPS Million Samples per Second

OCP Overcurrent Protection

OE Output-Error

OVP Overvoltage Protection

PI Proportional-Integral

PID Proportional-Integral-Derivative

PRC Parallel Resonant Converter

PWM Pulse-Width Modulation

RC Resistor Capacitor

SISO Single Input Single Output

SMPS Switch Mode Power Supply

SOC Start of Conversion

SPRC Series Parallel Resonant Converter

SRC Series Resonant Converter

VCO Voltage Controlled Oscillator

ZVS Zero Voltage Switching

## List of Units and Prefixes

| <sup>12</sup> )                    |

|------------------------------------|

| <sup>12</sup> )<br><sup>-9</sup> ) |

|                                    |

| <sup>-9</sup> )                    |

|                                    |

$Mega~(10^6)$

M

#### Acknowledgements

I would like to express my sincere gratitude towards my university supervisor, Dr. William Dunford for his guidance throughout my graduate studies. Mainly, I would like to thank him for giving me the opportunity to pursue my interest in this rewarding field and his always welcome insights in both academia and life. I am very grateful for his patience and support.

I would also like to thank Delta-Q for generously allowing me to use their lab space, equipment, and for their financial support. Most of all, I would like to thank the employees at Delta-Q. I would like to thank my industrial supervisors Chris Botting, Murray Edington, and Dr. Fariborz Musavi. I would also like to thank Delta-Q's hardware team: Marian Craciun for his valuable time and experienced insight into real world applications, Deepak Gautam for all his kind help and guidance, and David Matalpi for all his help and hands-on expertise. Special thanks to Muntasir Alam for his friendship and support. Finally, I would like to thank all the Delta-Q employees I have had the pleasure of getting to know.

Next, I would like to thank the Natural Sciences and Engineering Research Council of Canada (NSERC) for their generous financial support. I would also like to thank Mr. Brian Bella of the Faculty of Graduate Studies at UBC for his assistance with the NSERC IPS scholarship application.

Lastly, I would like to thank my family and friends for their support over the years. To my parents, thank you for your endless love, support, and encouragement throughout my life.

| _   | •   |         |     |

|-----|-----|---------|-----|

| Ded | 100 | 141     | n   |

| DEU | ILC | 1 L I I | ווע |

Dedicated to my parents.

#### 1 Introduction

#### 1.1 Overview

Switch-mode power supplies (SMPS) drive many of today's industrial applications because of their superior performance, efficiency, size, and cost [1], [2], [3]. The increased demand to provide tightly regulated voltage and current to the load has sparked interest in more advanced control algorithms for SMPS. Many applications demand strict regulation of output voltage or current while maintaining good dynamic performance during transients, which means voltage or current deviation should be small and settle to the reference value quickly [1], [4]. This requires a well-designed closed loop controller to give the system a high feedback loop bandwidth. However, achieving a high feedback loop bandwidth with analog components is challenging because converter characteristics change with varying operating conditions such as load, input voltage, and component variations [5]. This thesis presents the design process and implementation of digital control on a DC-DC LLC resonant converter in order to improve overall dynamic performance and disturbance rejection. In addition, although not the main focus of this thesis, it is still important to describe the LLC converter characteristics which will be presented in Chapter 2.

#### 1.2 Digital Control

Digital control of power converters offers many advantages over their analog counterparts. Digital control is more flexible, reliable, provides better integration, cost-effective, and less susceptible to noise [6], [7]. The following is a more detailed list of the advantages associated with digital control over analog control for power converter applications [1]:

- The ability to implement sophisticated algorithms for increasing efficiency and dynamic performance of power converters.

- The flexibility of reconfiguring control parameters without the need for changes in hardware.

- Less susceptible to controller component variation and noise sensitivity.

- Integration of multiple functionalities on one microcontroller helps reduce cost.

Because of these benefits, digital control is becoming more popular in high frequency DC-DC converters. The transition from analog control to widespread digital control has been slow

because operating at high frequencies requires high performance processors, analog-to-digital converters (ADCs), and digital pulse-width modulators (DPWMs), all of which comes at a price. However, recent technological advances are making low cost high performance digital signal controllers (DSC) possible (a DSC is a microcontroller specially designed to provide fast signal processing abilities) [8]. There are also challenges to keep in mind when implementing digital control. Limited resolution of the ADC and DPWM leads to quantization errors, high frequency operations can result in low resolution DPWM that may lead to limit cycle oscillations, and a slow processor clock speed limits the control bandwidth of the system [8], [9].

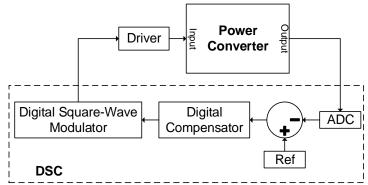

Figure 1.1 - Simplified block diagram of power converter with digital signal controller

Figure 1.1 shows a simplified block diagram of a power converter being controlled by a DSC and some inner components of the DSC. The power converter output signal is fed into the ADC, which digitizes the signal. The digital signal is subtracted from the reference signal and the error is fed into the digital compensator for computation. The calculated value of the digital compensator is normalized and is fed into the digital square wave modulator, which can vary duty cycle or frequency.

In [6], the author presents a method for digital voltage mode control on a nonresonant-coupled parallel resonant converter. It was found that the nonresonant-coupled parallel resonant converter's control-to-out frequency response shape did not change much under different operating conditions. It was found that only the magnitude (or gain) of the frequency response changed. As a result, a gain-scheduled digital controller was proposed which adaptively varies the gain of the digital compensator in order to compensate for the changing frequency response of the converter under different operating conditions. The author used Saber simulation software to simulate the gain at the 10kHz point over the entire converter operating range and constructed a look-up-table of 32x32 gain value points for the different operating points. It was shown that

the gain-scheduled digital control method increased bandwidth performance by four times over a classical analog control approach while not compromising stability margins. The digital implementation however did result in higher sub-harmonic noise in the converter's output compared with the analog implementation. The author claims such noise can be improved upon with a higher resolution digital PWM output. There is however, an issue with this control technique for LLC resonant converters. The non-resonant parallel converter can only operate above resonant frequency in order to achieve zero-voltage switching (ZVS). As a result, its frequency response characteristics do not have the double pole effect experience by LLC converters operating close to or below resonant frequency. That is to say, the LLC frequency response shape varies much more under different operating conditions. Therefore, simply changing the gain may not enough to ensure best performance.

In [10], the author presents a digital control scheme for charging a capacitor using a high voltage output LCC resonant converter. The control scheme uses current control mode (for constant current charging) and voltage control mode (for constant voltage charging). A large signal state-space model of 18 operating points throughout the charging cycle was developed using a generalized averaging modeling method with MATLAB. The author implemented a gain-scheduled PI controller for each operating point where the output current was used as the gain-scheduling variable for determining the correct gain value. It was found that the transition from current control mode to voltage control mode during the charging cycle produces a large step change because the difference between the output voltage and reference voltage was large. As a result, the control loop will introduced to a large step change, which would introduce a large voltage overshoot. The author's solution to this issue is to add an adaptive first order lowpass voltage reference filter in order to ensure no overshoot during the transition. The adaptive filter adapts the voltage level of the current to voltage mode transition and adapts the filter corner frequency to the rate of the voltage rise measured for a given load with a constant current. A disadvantage in adding this extra filter is the sacrifice in rise time (or bandwidth) of the control system.

In [11], the authors implements and compares a digital PID and fuzzy logic controller (FLC) on a half-bridge DC/DC LLC resonant converter. The inputs to the FLC are the *error*, the *difference of error*, and the *sum of error* and they are divided into nine triangular membership functions with a total of 81 rules. Each rule consists of a weighting factor and the degree of

change of switching frequency. The authors' simulation and experimental results indicated that the fuzzy logic controller was able to achieve faster dynamic response in comparison with the PID controller. A load variation experiment showed that the output voltage responded to a step change in load in about 15ms for the PID controller whereas the fuzzy logic controller responded to the same step change in about 5ms.

In [12], the author presents an adaptive digital PID control scheme in order to improve the dynamic performance of power converters. The main idea is to have a slower but more stable PID controller for steady-state operations and a faster PID controller during the transients. The Kp and Ki constants in the PID controller are increased during the transient in order to achieve a higher temporary bandwidth which corresponds to improved dynamic performance. The adaptive controller observes the error caused by the difference between the output voltage and reference voltage. Once the error is outside a pre-defined threshold, the Ki and Kp values are increased abruptly to a large value in order to increase the bandwidth and speed of the closed loop system. The controller then monitors when the error signal starts to reach steady state and then gradually reduce the Ki and Kp values to their original steady-state values. The author built a proof of concept experimental prototype of the digital adaptive control scheme on a single-phase DC-DC buck converter. Experimental results showed a 26% reduction in voltage overshoot and a >50% reduction in settling time for a particular case of a step load change compared to a conventional PID.

#### 1.3 Motivation and Objective

Advantages such as higher efficiency, greater power density, lower component stress, and higher switching frequency make DC-DC resonant converters topologies more attractive over their traditional PWM counterparts [6], [13]. However, the main disadvantage of resonant converters is that they require complex control because of their sensitivity to operating conditions and parameter tolerances. Because of the complex control nature of resonant converters, they stand the most to benefit from digital control [5].

In traditional analog design, a controller is designed for a particular power operating point. The controller is designed with a reduced bandwidth so that stable operation under varying conditions and parameters can be maintained. Such design often greatly limits the dynamic performance and disturbance rejection of the system. Attempting to increase the gain and

bandwidth of the system further may cause instability during both steady state and dynamic operations [1].

The main objective of this thesis is to improve the dynamic performance and the AC line ripple rejection ability on a commercially available analog controlled DC-DC LLC resonant converter by implementing digital control. In order to design a compensator, a mathematical model of the power converter is needed. Because of the non-linear nature of resonant converters, it is difficult to model them with traditional mathematical modelling methods and those methods are either over simplified (such as the using the first harmonic approximation), not very accurate, or overly complex and difficult to use. As a result, this thesis also presents an approach to accurately model a resonant power converter while simplifying and speeding up the modelling process, which would avoid the inaccurate/complex traditional mathematical modelling methods. As will be discussed later, this approach involves empirically gathering the frequency response data from the physical converter. With the frequency response data, a mathematical transfer function is estimated using a software tool and then the compensator is designed.

#### 1.4 Outline

This thesis is organized into seven chapters. In Chapter 1, the importance and advantages of digital control is introduced and the motivation to implement digital control on a resonant converter is established. Some previous digital control work done on power converters are also presented along with a summary of their advantages and disadvantages.

Chapter 2 provides a brief literature review of some basic resonant converter topologies. The LLC resonant converter experimented on in this thesis is presented in more detail along with its specifications. In addition, a simulation of the LLC converter's control-to-output frequency response for several different operating conditions is shown to emphasize its dynamic differences.

In Chapter 3, a detailed overview of the design infrastructure and analysis of the components used to implement digital control on the LLC resonant converter is presented. Digital design considerations such as the digital signal microcontroller (DSC), analog-to-digital converter (ADC), digital PWM (DPWM), sampling rate, and more are covered. In addition, the analog components needed to integrate the DSC with the LLC converter are presented.

In Chapter 4, the complete design process to achieve optimized digital compensators for varying operating points of the LLC converter is presented. The process involves introducing an approach of modelling the LLC resonant converter by gathering its uncompensated loop-gain frequency response data for various operating points and then using MATLAB to estimate mathematical models based on gathered data. With the estimated models, optimized digital compensators are designed. A comparison between the simulated PSIM control-to-output frequency response and the physically measured data is also presented and analyzed. An overview of the hardware and software tools used in the digital compensator design process will also be shown. Finally, a summary of the performance result of a single compensation design vs an adaptive compensation design is shown. (The performance is evaluated by the system's stability margins, bandwidth, and 120Hz disturbance rejection ability.)

Chapter 5 provides an overview of the digital control software architecture. Details on the adaptive compensation algorithm, which includes the responsibilities of the background loop and interrupts service routine task are covered.

Chapter 6 presents the experimental results to validate the work done in this thesis. First, an overview of the experimental prototype lab bench setup is shown. The modifications performed on the closed loop digital controlled system done to obtain the experimental loop-gain frequency response is measurements are presented. Next, the experimental data and performance results of the digitally compensated loop gain will be presented. Finally, comparisons between the experimental data and simulation will be shown.

Chapter 7 summarizes the work done in this thesis and provides further discussion insight regarding the overall work. Future work and possible improvements are also discussed.

#### 2 Literature Review

This chapter provides a review of the fundamental operation and characteristics of some common resonant converter topologies as well as highlighting their limitations. More emphasis will be placed on the LLC resonant converter topology and the specification for the LLC converter experimented on in this thesis is presented. Furthermore, the LLC converter's control-to-output (plant) frequency response for several different operating conditions is shown.

#### 2.1 Resonant Converters

A resonant converter contains a resonant tank that consists of L-C type networks. The resonant tank is driven by a periodic (voltage or current) square wave which results in the voltage and current of the resonant tank varying sinusoidally [14]. Frequency modulation is used to control the resonant type converter. Varying the switching frequency changes the impedance of the resonant tank, which results in the regulation of the voltages and currents [15]. There are three main well-known topologies for resonant converters: the series resonant converter SRC, the parallel resonant converter PRC, and the series-parallel resonant converter SPRC. The following is a brief overview of these topologies along with their advantages and disadvantages.

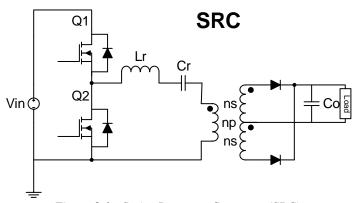

The series resonant converter (SRC) shown in Figure 2.1 [16] has a resonant tank consisting of an inductor Lr and a capacitor Cr in series.

Figure 2.1 - Series Resonant Converter (SRC)

As discussed in [16], the SRC acts like a voltage divider by having its resonant tank in series with the load. By changing the impedance of the resonant tank, the voltage divider equation will change therefore changing the gain of the converter. Because the load is in series with the resonant tank, the circulating energy in the tank is small which means less conduction losses. The DC gain of the SRC is always lower than one. A gain of one is achieved at resonant

frequency where the impedance of the series resonant tank is small and all the input voltage drops on the load. The SRC is non-ideal for practical DC-DC converter applications because it requires a high range of switching frequencies for light load regulation. It also has high circulating energy that results in conduction losses and the switches experience high turn off current.

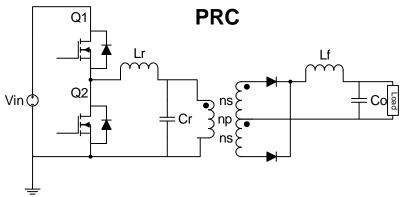

Figure 2.2 - Parallel Resonant Converter (PRC)

The parallel resonant converter (PRC) is shown in Figure 2.2 [16]. It is essentially a series resonant converter expect for the fact the load is in parallel with the resonant capacitor. The converter's operating region is much smaller compared to the SRC and can have a DC gain greater than one. The main problem of the PRC is its high circulating current even at no load conditions because the load is in parallel with the resonant capacitor. Therefore, the PRC experiences even higher conduction losses. The PRC also suffers from high turn off current just like the SRC [16].

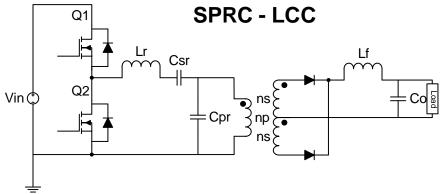

Figure 2.3 - Series Parallel Resonant Converter (SPRC) LCC

A LCC type series parallel resonant converter SPRC shown in Figure 2.3 [16] can been viewed as a combination of the SRC and the PRC. The resonant tank consists of three resonant components: Lr, Csr, and Cpr. The LCC combines the good characteristics of the SRC and the

PRC by having less circulating current and smaller sensitivity to load change. However, it still suffers with wide input ranges, which leads to high conduction and switching losses under high input voltages [16].

#### 2.2 LLC Resonant Converter

In this section, the LLC converter is presented in more detail and its advantages over the series resonant converter (SRC), parallel resonant converter (PRC), and the LCC series parallel resonant converter (SPRC) is presented.

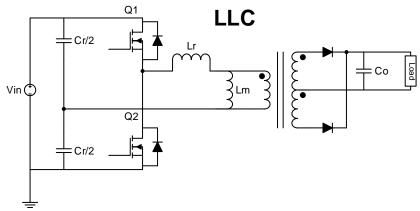

Figure 2.4 - LLC Resonant Converter

The LLC resonant converter shown in Figure 2.4 [17] is essentially the dual of the LCC resonant converter. Its resonant tank is composed of two inductors (Lr and Lm) and one capacitor (Cr). The major advantage of the LLC resonant converter is it allows for zero-voltage switching (ZVS) operation for a variety of loads. It can also operate with a narrow switching frequency range [17]. Another advantage of LLC compared to the LCC topology is the two inductors Lr and Lm of the LLC can be combined into one physical component therefore saving cost whereas the LCC converter requires two large high cost capacitors [18].

The LLC resonant converter can be broken down into four sections: the bridge inverter, the LLC resonant tank, the high frequency transformer, and the rectifier [19].

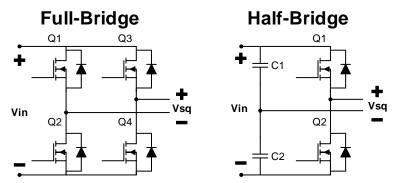

Figure 2.5 - Full-Bridge & Half-Bridge switching circuits

A full-bridge and half-bridge inverter is shown in Figure 2.5 (the half-bridge inverter is used for this thesis). It is the first stage of the LLC converter, which converts a DC input voltage into a square wave of switching frequency ( $f_{sw}$ ). The duty cycle of the square wave is typically 50% with a small dead time to help with zero voltage switching (ZVS). The mathematical equation of the square wave  $V_{sq}$  generated by the half-bridge inverter is shown in Equation 2-1 [15] where d represents the duty cycle.

$$V_{sq} \approx \frac{4}{\pi} \frac{V_{in}}{2} \sin(\pi \frac{d}{2}) \sin(\omega t)$$

Equation 2-1

Ultimately, the main advantage of a half bridge is its reduced cost (because of fewer switches) with the sacrifice of increased power loss because of the increased RMS current going through the switches (which causes increased losses) [19]. The half-bridge is usually used for lower power levels (<1000W) where the power loss is deemed acceptable compared to the decrease in cost [16].

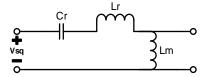

Figure 2.6 - LLC Resonant Tank

The square wave generated by the half-bridge inverter is fed into the resonant tank as shown in Figure 2.6. The LLC tank consists of a series resonant inductor Lr, a series resonant capacitor Cr, and a parallel resonant inductor Lm. It is shown in [20] that the impedance of the resonant tank can be varied by changing the frequency of the square wave fed into it.

The high frequency transformer shown in Figure 2.4 is used to decrease/increase the secondary side voltage and provide galvanic isolation to the input for safety. Using integrated

magnetic technology for the transformer allows the Lr and Lm inductors to be a part of the same magnetic structure, which is useful in terms of increasing the converter's power density [18], [21].

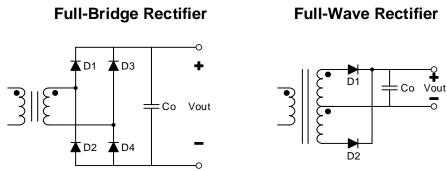

Figure 2.7 - Full-Bridge (left) and Half-Bridge (right) rectifier

The last stage of the LLC resonant converter is the bridge rectifier with a capacitor output filter Co as shown in Figure 2.7 [19]. Figure 2.7 shows both a full-bridge and a full-wave rectifier. The function of this section is to transform the scaled AC voltage output from the transformer to a DC output.

| Full-Wave compared to Full-Bridge Rectifier |        |            |           |                      |                      |             |

|---------------------------------------------|--------|------------|-----------|----------------------|----------------------|-------------|

| Diode                                       | # of   | Diode      | # of      | R <sub>sec</sub> per | I <sub>RMS</sub> per | Transformer |

| Voltage                                     | Diodes | Conduction | Secondary | winding              | winding              | Secondary   |

| Rating                                      |        | Losses     | Windings  |                      |                      | loss        |

| ×2                                          | ÷2     | ÷2         | ×2        | ×2                   | $\times \sqrt{0.5}$  | ×2          |

Table 2.1 - Full-Wave rectifier compared to Full-Bridge rectifier

As summarized in Table 2.1 [19], the diodes of the full-wave rectifier experience twice the voltage compared to the full-bridge rectifier. However, the full-wave rectifier only has two diodes while the full-bridge rectifier has four diodes resulting in the full-wave rectifier having half the total diode conduction losses. The full-wave has two secondary windings therefore the resistance is doubled for the same winding area. Each winding in the full-wave rectifier caries a RMS current that is  $\sqrt{0.5}$  times the RMS current of the full-bridge rectifier. In all, the total secondary winding copper losses of the full-wave rectifier is two times more compared to the full bridge rectifier. The full-bridge rectifier's advantage of experiencing only half the amount of voltage when compared with the full-wave rectifier makes it a good candidate for high output voltage applications. The full-wave rectifier is best used for low output voltages and high

currents applications because of its lower conduction losses (the full-wave rectifier is used in this thesis).

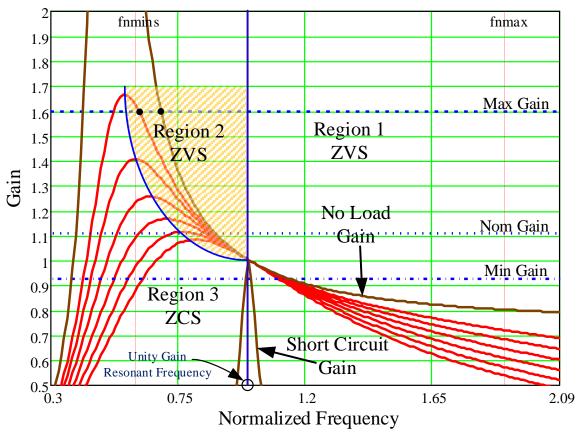

Figure 2.8 - Typical LLC Converter DC gain characteristic

Figure 2.8 [22] shows the normalized gain vs frequency characteristic of a LLC converter. As can be seen from Figure 2.8, the characteristics are split into three regions (the boundaries shown by the solid blue lines): Region 1, Region 2, and Region 3. It is desirable to operate the converter under ZVS conditions therefore the converter is operated in Region 1 and Region 2. Region 1 and 2 are located on the negative gradient of the DC gain curve and Region 3 is located on the positive gradient [23]. The resonant frequency  $f_0$  of the circuit is dependent on the series resonant inductor Lr and series resonant capacitor Cr that can be seen in Equation 2-2 [20].

$$f_o = \frac{1}{2\pi\sqrt{(L_r C_r)}}$$

Equation 2-2

The magnetizing inductor Lm introduces a second resonant frequency when there is not load and it is given by Equation 2-3 [13], [20].

$$f_p = \frac{1}{2\pi\sqrt{(L_r + L_m)C_r}}$$

Equation 2-3

The LLC converter can operate in three modes depending on the input voltage and load conditions. The three modes of operations are [12], [20], [18]:

- At resonant frequency operation,  $f_{sw}=f_o$ .

- Above resonant frequency operation,  $f_{sw}>f_o$ .

- Below resonant frequency operation, f<sub>sw</sub><f<sub>o</sub>.

## 2.3 LLC Converter Design Specifications

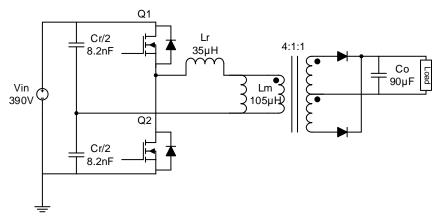

Figure 2.9 - LLC resonant converter basic design and component values

Figure 2.9 illustrates a simplified schematic of the LLC resonant converter design and its component values used for this research. The converter is designed for an optimal 48V output and maximum 650W output power. The switches Q1 and Q2 are driven using complementary 50% duty cycle square waves and the square wave's frequency is varied to control the converter. The specifications and component values of the converter are summarized in Table 2.2. These values represent the commercially available converter's design used in this thesis.

| LLC Converter Specifications       |                   |                             |  |

|------------------------------------|-------------------|-----------------------------|--|

| Parameter                          | Symbol            | Value                       |  |

| Resonant Inductor                  | Lr                | 35 [μH]                     |  |

| Resonant Capacitor                 | Cr                | 2×8.2 [nF]                  |  |

| Magnetizing Inductor               | Lm                | 105 [μΗ]                    |  |

| Transformer Ratio                  | n                 | 4:1:1                       |  |

| Output Capacitor                   | Co                | 6×1.5 [nF]                  |  |

| Resonant Frequency                 | fr                | 210 [kHz]                   |  |

| 2 <sup>nd</sup> Resonant Frequency | fp                | 105 [kHz]                   |  |

| Switching Frequency Range          | fsw               | 150 – 450 [kHz]             |  |

| Input Voltage                      | Vin               | 370 – 410 (390 nominal) [V] |  |

| Output Voltage                     | Vo                | 36 – 72 (48 nominal) [V]    |  |

| Max Load Current                   | Io <sub>max</sub> | 13 [A]                      |  |

| Max Output Power                   | Poutmax           | 650 [W]                     |  |

Table 2.2 - LLC Converter Specifications and component values

#### 2.4 LLC Plant Frequency Response

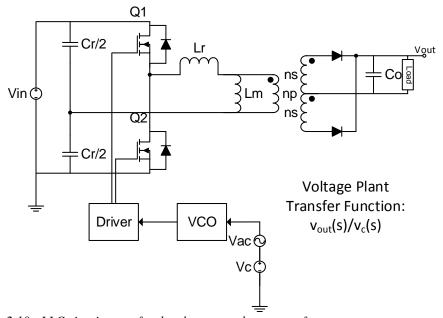

$\textit{Figure 2.10-LLC circuit setup for the plant control-to-output frequency response \textit{measurement}}$

It is important to highlight how the LLC converter's plant dynamic characteristics change with the operating points. In this context, the operating points are effected by variations in the output voltage, output current, and load [21]. Figure 2.10 [16] illustrates how the control-to-output frequency response (or plant) was measured. The control voltage Vc is a DC voltage which sets the operating point for a given load. Then a perturbing small signal sinusoid voltage Vac of varying frequencies is added. The combined voltage of Vc and Vac is then fed into the voltage-controlled oscillator (VCO) which drives the switching frequency of LLC converter. The

control-to-output frequency response of the voltage plant is given by Equation 2-4. The current plant is given by Equation 2-5.

$$Voltage\ Plant\ Transfer\ Function = \frac{\widehat{v_{out}}}{\widehat{v_c}}$$

Equation 2-4

$$Current\ Plant\ Transfer\ Function = \frac{\widehat{\iota_{out}}}{\widehat{v_c}}$$

Equation 2-5

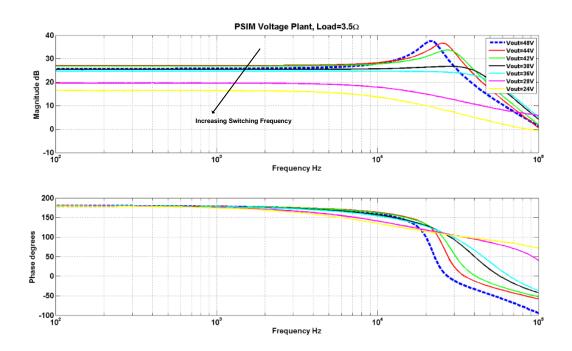

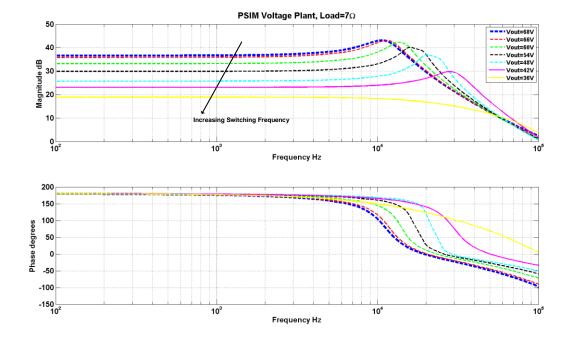

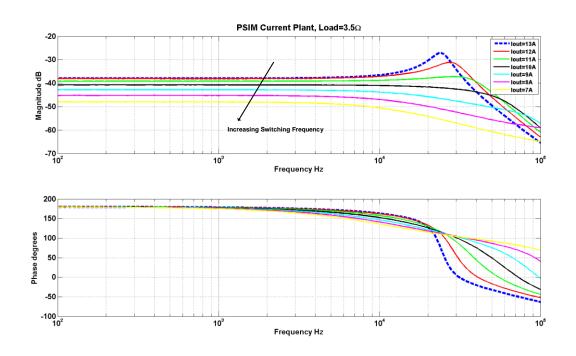

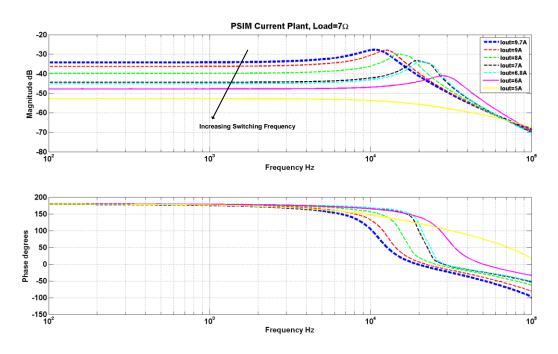

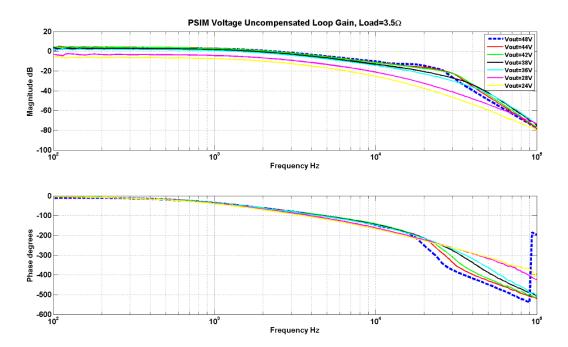

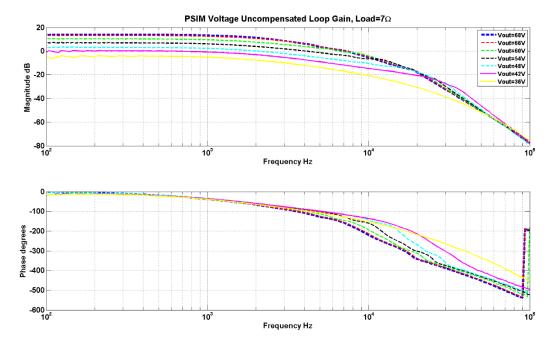

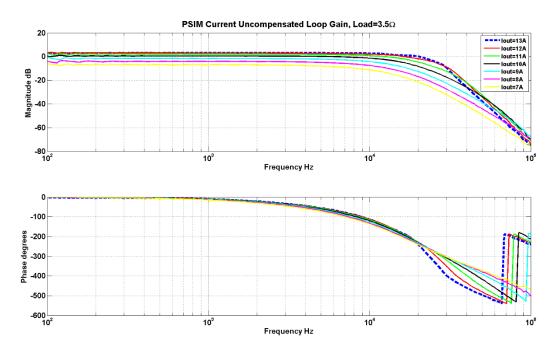

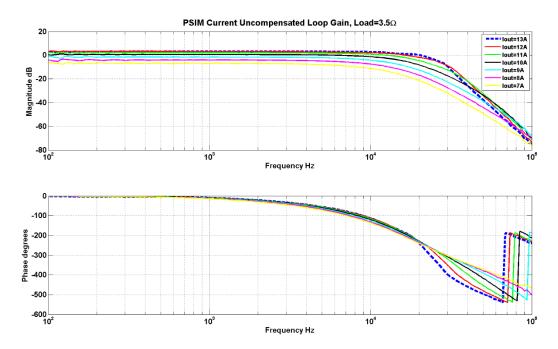

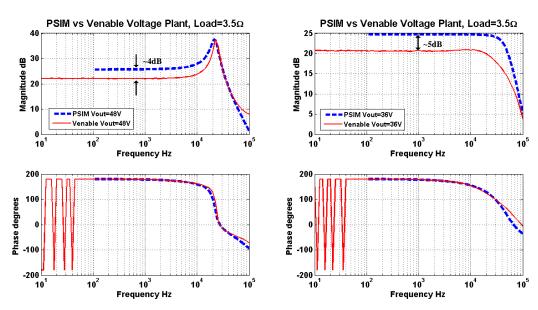

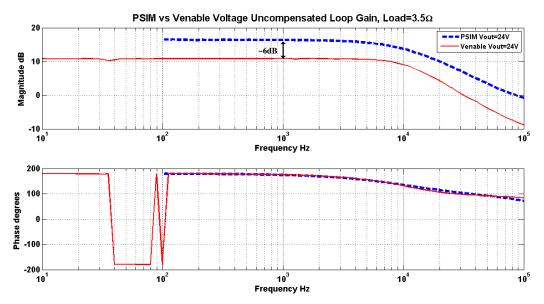

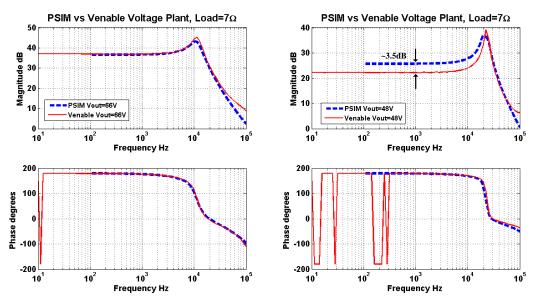

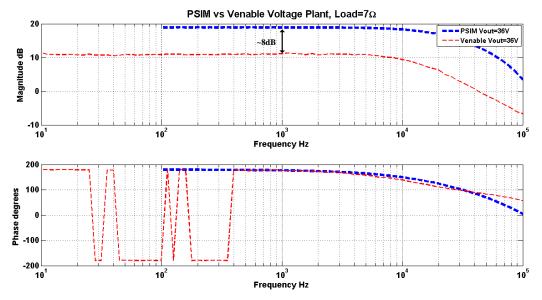

Figure 2.11 (Voltage Plant with Load=3.5  $\Omega$ ), Figure 2.12 (Voltage Plant with Load=7  $\Omega$ ), Figure 2.13 (Current Plant with Load=3.5  $\Omega$ ), and Figure 2.14 (Current Plant with Load=7  $\Omega$ ) help illustrate the plant variations under varying operating conditions and are simulated in PSIM. Two loads (3.5 $\Omega$  and 7 $\Omega$ ) are considered over a range of output voltages and currents. It is noticed that the plant appears somewhat like a second order system where operations at, near, or below resonance appear to have a high Q factor. Operations above resonance results in the system poles splitting from a complex pole pair into two real poles [24]. It is also noticed that the overall shape of the magnitude and phase are very similar below 10kHz for the various operating points. The main difference is the magnitude (that can vary as high as 30dB) and the varying Q factor, which makes control design difficult.

Figure 2.11 - LLC Voltage Plant frequency response with Load= $3.5\Omega$  (PSIM Simulation)

Figure 2.12 - LLC Voltage Plant frequency response with Load= $7\Omega$  (PSIM Simulation)

Table 2.3 summarizes the switching frequencies corresponding to the different output voltages for the plant frequency response in Figure 2.11-Figure 2.12. The lowest switching frequency is 155kHz and the highest is 380kHz.

| <b>Operating Point</b> |           | <b>Switching Frequency (fc)</b> |

|------------------------|-----------|---------------------------------|

| Vout                   | Load      |                                 |

| 48V                    | 3.5Ω      | 208kHz                          |

| 44V                    | 3.5Ω      | 227kHz                          |

| 42V                    | 3.5Ω      | 236kHz                          |

| 38V                    | 3.5Ω      | 256kHz                          |

| 36V                    | 3.5Ω      | 265kHz                          |

| 28V                    | 3.5Ω      | 329kHz                          |

| 24V                    | 3.5Ω      | 380kHz                          |

| 68V                    | $7\Omega$ | 155kHz                          |

| 66V                    | $7\Omega$ | 158kHz                          |

| 60V                    | $7\Omega$ | 169kHz                          |

| 54V                    | 7Ω        | 182kHz                          |

| 48V                    | 7Ω        | 209kHz                          |

| 42V                    | 7Ω        | 245kHz                          |

| 36V                    | $7\Omega$ | 298kHz                          |

Table 2.3 - Voltage Plant switching frequency for various operating points

Figure 2.13 - LLC Current Plant frequency response with Load= $3.5\Omega$  (PSIM Simulation)

Figure 2.14 - LLC Current Plant frequency response with Load= $7\Omega$  (PSIM Simulation)

Table 2.4 summarizes the switching frequencies corresponding to the different output currents for the plant frequency response in Figure 2.13-Figure 2.14. The lowest switching frequency is 155kHz and the highest is 372kHz.

| <b>Operating Point</b> |           | <b>Switching Frequency (fc)</b> |

|------------------------|-----------|---------------------------------|

| Iout                   | Load      |                                 |

| 13A                    | 3.5Ω      | 220kHz                          |

| 12A                    | 3.5Ω      | 236kHz                          |

| 10A                    | 3.5Ω      | 253kHz                          |

| 9A                     | 3.5Ω      | 272kHz                          |

| 8A                     | 3.5Ω      | 297kHz                          |

| 7A                     | 3.5Ω      | 329kHz                          |

| 6A                     | 3.5Ω      | 372kHz                          |

| 9.7A                   | $7\Omega$ | 155kHz                          |

| 9A                     | $7\Omega$ | 163kHz                          |

| 8A                     | $7\Omega$ | 179kHz                          |

| 7A                     | $7\Omega$ | 204kHz                          |

| 6.8A                   | $7\Omega$ | 209kHz                          |

| 6A                     | 7Ω        | 245kHz                          |

| 5A                     | $7\Omega$ | 310kHz                          |

Table 2.4 - Current Plant switching frequency for various operating points

# 3 Digital Design Infrastructure Components and Considerations

The purpose of this chapter is to provide an overview of the components required to realize digital control on an existing analog controlled LLC converter. The objective is to implement a digitally controlled prototype with minimal modifications to the existing converter. The practical requirements components such as the sensing circuitry, the digital controller, and other digital design aspects will also be explored. For a designer, this is a useful way to determine the benefits of digital control without having to re-design a converter system for digital control.

# 3.1 Digital Design Infrastructure Overview

In this section, an overview of the digital design infrastructure and its components are given. A general explanation of each component, why they are needed, and how they interact with one another is given. In addition, some brief comments on certain design decisions are noted.

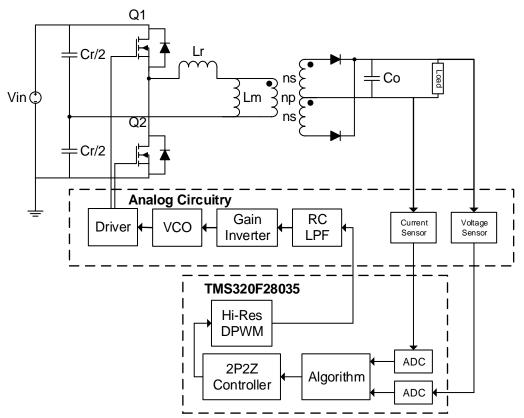

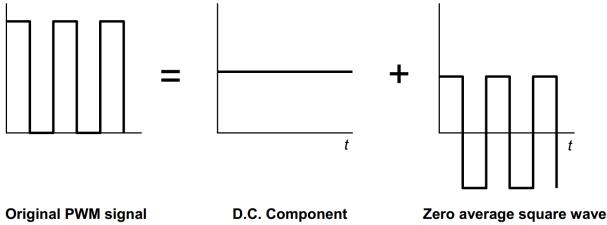

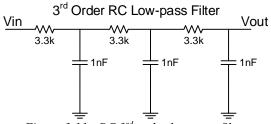

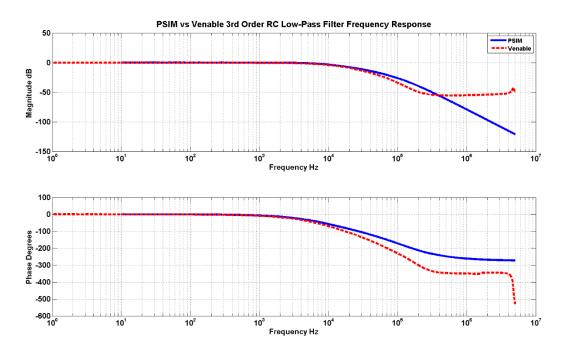

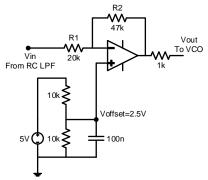

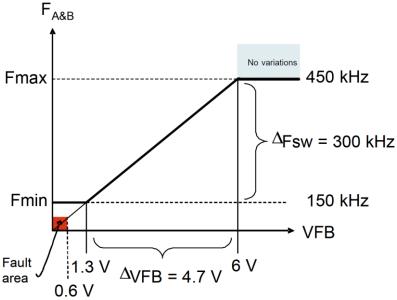

Figure 3.1 – High-level block diagram of the digital control infrastructure for the LLC converter

Figure 3.1 illustrates a high-level overview of the digital control infrastructure for the LLC converter. The system can operate in either current control mode or voltage control mode. The output current and voltage from the converter are fed into analog sensors, which are designed to scale the values to be compatible with the digital signal controller's (DSC) ADC. The Texas Instrument C2000 Piccolo TMS320F28035 is selected as the DSC. The DSC then performs all the necessary control logic (which is explained in more detail in Chapter 5) and outputs a digital PWM (DPWM) square wave. The PWM signal is fed into a RC low pass filter (LPF) in order to be smoothed out into a DC like voltage. The DC voltage is then fed into a gain inverter circuit, which functions to scale the voltage to a compatible range for the VCO input. It also inverts the DC signal (which is to say as the input to the gain inverter increases, the output will decrease and vice versa). This behaviour is implemented in order to compensate for the natural 180° phase offset of the LLC converter plant which is shown in Figure 2.11-Figure 2.14. The output of the gain inverter is then fed into the voltage-controlled oscillator (VCO) which then drives the switches. Note that since the VCO is designed to take an input DC voltage, the PWM signal from the DSC had to be low pass filtered hence the need for the RC LPF.

The reason why the DSC was not chosen to drive the LLC switches directly with frequency modulation was that it was decided safest to keep the already built in integrated circuit (IC) VCO chip to drive the switches. The built in VCO contains already integrated over voltage and current protection along with some other safety mechanisms, which was well test, and proven to work. Therefore, keeping the VCO allows for safer prototyping new control designs and performing tests. However, in order to implement digital control on the LLC converter while keeping the VCO, extra circuitry had to be introduced which were the third order RC low-pass filter and gain inverter circuit. As will be discussed later, adding these extra components introduces non-idealities and reduces the maximum potential system bandwidth. However, because the goal of this thesis is to provide a proof-of-concept on the benefits of a digital control vs analog control and to provide a simpler more accurate method of modelling a resonant converter, the disadvantages introduced by adding these extra components does not hinder accomplishing the goals.

## 3.2 Digital Components & Consideration

The following sections provide an overview and detail of some of the key features of the Texas Instruments C2000 Piccolo DSC that are needed to implement digital control on the LLC converter. A general summary of the DSC features is taken from the Texas Instruments TMS320F2803x datasheet [25] and shown in Appendix A: TI C2000 Piccolo TMSF28035 Specifications. The main features to take note of are: it has a fixed point 60MHz CPU, it is capable of fast interrupt and response processing, it has a programmable control law accelerator (CLA) (which is a separate floating point math processing unit), an on chip analog to digital converter (ADC), and a digital high resolution pulse width modulation (HRPWM) unit.

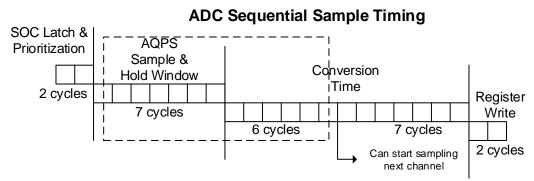

### 3.2.1 Analog-to-Digital Converter (ADC)

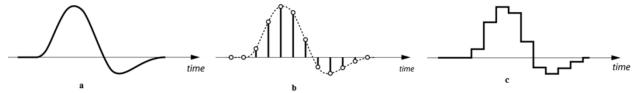

The analog output voltage and current signals are fed into their corresponding sensors which are then converted to digital signals with the help of the built in ADC module. To convert the continuous time signal to discrete time, the ADC samples the waveform at some sampling frequency usually in the kHz for power converters. Higher sampling rates produce better accuracy, but at the cost of increased CPU utilization [26], [27]. The sampled value is captured and then held until the next sampled value. Figure 3.2 [15] illustrates this process.

Figure 3.2 - Continuous to discrete signal conversion

The TMS320F28035 ADC module has a 12bit resolution and can take a maximum input voltage of  $V_{max} = 3.3V$  [28]. The resolution indicates the number of discrete values it can produce over a range of analog values. For a resolution of 12bits we have  $2^{12}$  (4096) discrete values that can be used to map an analog signal. The resolution for the ADC can be calculated using Equation 3-1 [28], where  $V_{max} = 3.3V$ ,  $V_{min} = 0V$ , and n represents the number of bits.

$$Res = \frac{V_{max} - V_{min}}{2^n - 1}$$

Equation 3-1

Plugging in these values will give us the resolutions of the ADC:

$$Resolution = \frac{3.3 - 0}{4096 - 1} \approx 805 \mu V$$

Equation 3-2

The resolutions determine the magnitude of the quantization error. However thanks to the high resolution 12bit ADC, the quantization error is not a huge factor for this application.

### 3.2.2 High Resolution PWM (HRPWM)

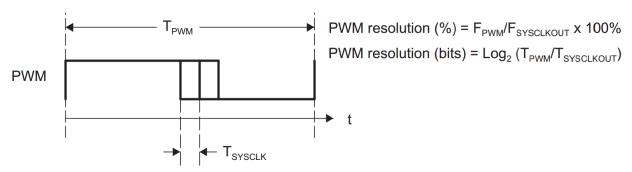

The TMS320F28035 digital PWM (DPWM) module can generate a variable duty cycle square wave signal of magnitude 3.3V. As shown in [29], the precision of the PWM signal is dependent on the system clock speed, which is 60MHz for the TMS320F28035. A 60MHz clock speed provides a period of 16.67ns (1/60MHz) which is the minimum time step possible. Although a 16.67ns time step may seem very small, there will be resolution issues when operating at high PWM frequencies.

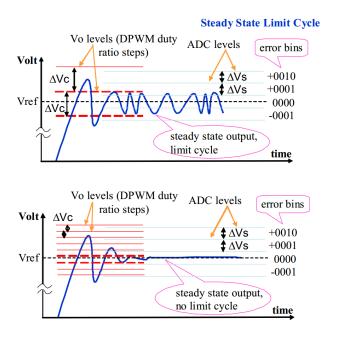

A high PWM duty cycle resolution is desirable not only for higher accuracy but also for stability. Digitally controlled switch-mode converters operating in closed loop have the possibility of building up limit cycles. The term limit cycle is used to describe the presence of oscillations occurring in the regulated output under steady-state operation that are the results of quantization errors in the control loop [30]. For a DPWM, limit cycles appear when the least significant bit (LSB) of the DPWM resolution is changing the output by a value that is larger than the resolution of the ADC [30], [31]. In other words, limit cycles occur when the DPWM bit resolutions is lower than the ADC bit resolution.

Figure 3.3 [32] show an example of the limit cycle effect. The top plot shows the delta ADC levels ( $\Delta Vs$ ) to be smaller than the delta DPWM duty ratio steps ( $\Delta Vc$ ) or in other words, the ADC resolution is higher than the DPWM resolution. Because of the lower DPWM resolution, the output voltage (Vo) has difficulty matching the reference signal therefore, it oscillates between the DPWM step values. The bottom plot in Figure 3.3 shows the delta ADC levels ( $\Delta Vs$ ) to be larger than the delta DPWM duty ration steps ( $\Delta Vc$ ) or in other words, the ADC resolution is lower than the DPWM resolution. In this case, because of the higher DPWM resolution, the output voltage is able to match the reference signal resulting in no limit cycle oscillation occurring.

The limit cycle issue is traditionally overcome by either reducing the ADC resolution, which results in lower output regulation accuracy, or by increasing the DPWM duty cycle resolution, which can be accomplished by decreasing the PWM frequency, dithering, or by hardware acceleration [30], [33]. In this thesis, the high ADC resolution will be kept at 12bits and the TMS320F28035 high resolution PWM (HRPWM) feature will be used in order increase the DPWM resolution while maintaining a high PWM frequency. A high PWM frequency is desirable because of the RC filter, which is explained more in Section 3.3.1.

Figure 3.4 - Conventional generated PWM resolution calculation

Figure 3.4 [29] shows the resolution calculations for a conventionally generated PWM signal. Using the equations in Figure 3.4, it calculated that if the PWM frequency was set to 500kHz and system clock is 60MHz, the PWM resolution would be approximately 7bits which is less than the 12bit ADC resolution. This is not ideal because the lower PWM resolution will introduce the limit cycle effect. In order to achieve a 12bit resolution or higher for the PWM resolution, the PWM frequency has to be lower than 15kHz which is not high enough for the RC

filter (further explanation in Section 3.3.1). Fortunately, the TMS320F28035 DSC has a high-resolution PWM (HRPWM) module, which can extend the time resolution capabilities of the conventionally derived PWM.

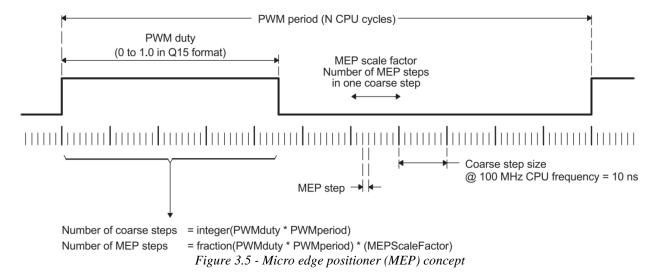

The HRPWM is based on a micro edge positioner (MEP) technology that positions several edges in between one conventional system clock time step. This decreases the time step to potentially 150ps instead of the conventional 16.67ns time step for a 60MHz system clock [29]. Figure 3.5 [29] demonstrates the MEP concept.

Table 3.1 summarized the resolution comparison between the conventionally generated PWM and the HRPWM. The percentage resolution and bit resolution for varying PWM frequencies using a 60MHz system clock is compared. It is noted that in order to keep the bit resolution above the 12bit ADC resolution, the HRPWM frequency should not pass 1MHz. This is a substantial improvement over the conventional PWM resolution, which only allows 15kHz for a 12bit resolution.

| Resolution for PWM and HRPWM @60MHz System Clock |                        |                  |      |       |  |  |

|--------------------------------------------------|------------------------|------------------|------|-------|--|--|

| PWM Frequency                                    | <b>Conventional PW</b> | HRPWM Resolution |      |       |  |  |

| (kHz)                                            | Bits                   | %                | Bits | %     |  |  |

| 20                                               | 11.6                   | 0.0              | 18.1 | 0.000 |  |  |

| 50                                               | 10.2                   | 0.1              | 16.8 | 0.001 |  |  |

| 100                                              | 9.2                    | 0.2              | 05.8 | 0.002 |  |  |

| 150                                              | 8.6                    | 0.3              | 15.2 | 0.003 |  |  |

| 200                                              | 8.2                    | 0.3              | 14.8 | 0.004 |  |  |

| 250                                              | 7.9                    | 0.4              | 14.4 | 0.005 |  |  |

| 500                                              | 6.9                    | 0.8              | 13.4 | 0.009 |  |  |

| 1000                                             | 5.9                    | 1.7              | 12.4 | 0.018 |  |  |

| 1500                                             | 5.3                    | 2.5              | 11.9 | 0.027 |  |  |

| 2000                                             | 4.9                    | 3.3              | 11.4 | 0.036 |  |  |

Table 3.1 - Conventional PWM resolution vs HRPWM resolution

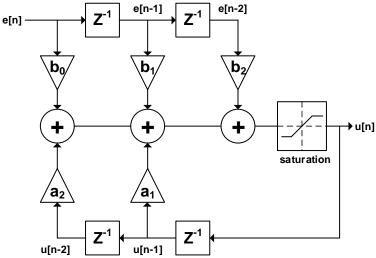

#### 3.2.3 Digital 2P2Z Compensator

A two pole two zero (2P2Z) infinite impulse response (IIR) filter structure is used for the voltage and current compensator. The discrete transfer function of the 2P2Z compensator is shown in Equation 3-3 [34] where  $z^{-n}$  represents a unit delay of n sample time steps.

$$\frac{U[z]}{E[z]} = \frac{b_2 z^{-2} + b_1 z^{-1} + b_0}{1 - a_1 z^{-1} - a_2 z^{-2}}$$

Equation 3-3

Equation 3-3 can also be represented in difference equation form as shown in Equation 3-4 [34] where u[n] represents the present controller output, u[n-1] represents the controller output from the previous cycle, u[n-2] represents the output from two cycles previously. The same is concept applies to e[n] which represents the controller input.

$$u[n] = a_1 u[n-1] + a_2 u[n-2] + b_0 e[n]$$

Equation 3-4

$$+ b_1 e[n-1] + b_2 e[n-2]$$

Figure 3.6 shows the 2P2Z controller graphically. A saturation limit is used so that the output is bound to a specific range [35].

Figure 3.6 – Graphical representation of a 2P2Z IIR Filter with a saturation limit

The advantage of this type of IIR filter structure is that it can be expanded to a more complex 3P3Z filter by simply adding extra  $z^{-3}$  and  $b_3$  and  $a_3$  terms. However, this will require more memory and higher computation times [36].

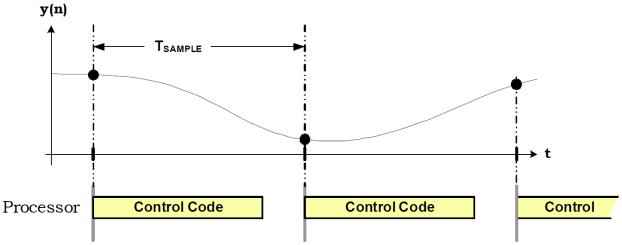

### 3.2.4 Sampling Rate

One main disadvantage with digital control is its limited bandwidth when compared to analog control [37]. Choosing the sampling rate (or sampling frequency) is very important when implementing digital control. A high sampling rate allows for a high closed loop bandwidth and better high frequency signal representation [38]. Choosing a sampling rate is application specific. For power converters, it is desirable to have the sampling rate to be as fast as possible especially for high dynamic performance applications [39]. The sampling rate is limited by the CPU clock speed, complexity of the control code, and hardware capabilities. In order to achieve real-time control for a closed loop system, the control code should be finished processing before the next sample period. Increasing the sampling rate would decrease the period before the next sample therefore providing less time for the control code to complete. Figure 3.7 [32] illustrates this concept.

Figure 3.7 - Processor bandwidth vs control code

Table 3.2 shows several sample frequencies with their corresponding sampling period and the number of clock cycles for a processor clock speed of 60MHz (1 cycle = 16.67ns). The number of clock cycles corresponds to the amount of software code instructions that can be executed. The number of cycles is calculated by dividing the sampling frequency's sampling period by the 60MHz period or by dividing the 60MHz by the sampling frequency. As can be seen, the number of instructions is extremely limited at high sampling rates. A sampling rate of 1MHz or over would overload the processor for a single closed 2P2Z control loop as will be shown later.

| Sampling Frequency (kHz) | Sampling Period (ns) | # of cycles for 60MHz CPU:<br>(Sampling Period)/(16.67ns) |

|--------------------------|----------------------|-----------------------------------------------------------|

| 100                      | 10000                | 600                                                       |

| 250                      | 4000                 | 240                                                       |

| 400                      | 2500                 | 150                                                       |

| 500                      | 2000                 | 120                                                       |

| 750                      | 1333                 | 80                                                        |

| 1000                     | 1000                 | 60                                                        |

| 1500                     | 667                  | 40                                                        |

| 2000                     | 500                  | 30                                                        |

Table 3.2 - Sampling frequency, sampling period, # of cycles for 60MHz CPU