## Leveraging distributed explicit-state model checking for practical verification of liveness in hardware protocols

by

**Brad Bingham**

M.Sc., The University of British Columbia, 2007B.Sc., The University of Victoria, 2005

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

in

THE FACULTY OF GRADUATE AND POSTDOCTORAL STUDIES (Computer Science)

#### THE UNIVERSITY OF BRITISH COLUMBIA

(Vancouver)

April 2015

© Brad Bingham, 2015

## Abstract

Protocol verification is a key component to hardware and software design. The proliferation of concurrency in modern designs stresses the need for accurate protocol models and scalable verification tools. Model checking is an approach for automatically verifying properties of designs, the main limitation of which is state-space explosion. As such, automatic verification of these designs can quickly exhaust the memory of a single computer.

This thesis presents PREACH, a distributed explicit-state model checker, designed to robustly harness the aggregate computing power of large clusters. The initial version verified *safety* properties, which hold if no error states can be reached. PREACH has been demonstrated to run on hundreds of machines and explore state space sizes up to 90 billion, the largest published to date.

Liveness is an important class of properties for hardware system correctness which, unlike safety, expresses more elaborate temporal reasoning. However, model checking of liveness is more computationally complex, and exacerbates scalability issues as compared with safety. The main thesis contribution is the extension of PREACH to verify two key liveness-like properties of practical interest: deadlock-freedom and response. Our methods leverage the scalability and robustness of PREACH and strike a balance between tractable verification for large models and catching liveness violations.

Deadlock-freedom holds if from all reachable system states, there exists a sequence of actions that will complete all pending transactions. We find that checking this property is only a small overhead as compared to safety checking. We also provide a technique for establishing that deadlock-freedom holds of a *parameterized system* — a system with a variable number of entities.

Response is a stronger property than deadlock-freedom and is the most common liveness property of interest. In practical cases, fairness must be imposed on system models when model checking response to exclude those execution traces deemed inconsistent with the expected underlying hardware. We implemented a novel twist on established model checking algorithms, to target response properties with action-based fairness. This implementation vastly out-performs competing tools.

This thesis shows that tractable verification of interesting liveness properties in large protocol models is possible.

## Preface

The work of this thesis was mostly conducted at the Integrated Systems Design Lab at the University of British Columbia, Point Grey campus. Some development of the PREACH tool and experiments were done at Intel Corporation (Ronler Acres), in Hillsboro, Oregon. Chapters 3 – 6 are based on publications that have already appeared. Accordingly, some of the text and figures are based upon material written or drawn by my co-authors. These publications, along with my role in the research and writing are described in detail below.

- Chapter 3 is based on: Brad Bingham, Jesse Bingham, Flavio M. de Paula, John Erickson, Gaurav Singh, and Mark Reitblatt. Industrial strength distributed explicit state model checking. In *Parallel and Distributed Model Checking (PDMC)*, pages 28–36, IEEE Computer Society, 2010.

- Chapter 5 is based on: Brad Bingham, Mark Greenstreet, and Jesse Bingham. Parameterized verification of deadlock freedom in symmetric cache coherence protocols.

In Formal Methods in Computer-Aided Design (FMCAD), pages 186–195, FMCAD Inc., 2011.

- 3. Chapter 4 is based on: Brad Bingham, Jesse Bingham, John Erickson, and Mark Greenstreet. Distributed explicit state model checking of deadlock freedom. In Computer Aided Verification (CAV), volume 8044 of Lecture Notes in Computer Science, pages 235–241, Springer-Verlag, 2013.

4. Chapter 6 is based on: Brad Bingham and Mark Greenstreet. Response property checking via distributed state space exploration. In *Formal Methods in Computer Aided Design (FMCAD)*, pages 15–22, FMCAD Inc., 2014.

In addition, Chapter 2 has small portions that originated from the above publications. My individual contributions to publication 1 include

- Created the initial prototype of the distributed model checking algorithm.

- Implemented and evaluated various approaches to load balancing to address both performance and thread crashes.

- Gathered statistics on Erlang communication throughput and latency relative to message size, motivating state-batching optimizations.

For the other publications, I performed the bulk of the research, with co-authors contributing with brain-storming discussions, manuscript writing and feedback. While they are not co-authors on publication 4, Jesse Bingham helped by running our tool on proprietary Intel models, and Jim Grundy provided some models he authored which we used as benchmarks.

# **Table of Contents**

| Abstra  | ict                                 |

|---------|-------------------------------------|

| Preface | e                                   |

| Table o | of Contents                         |

| List of | Tables                              |

| List of | Figures                             |

| List of | Algorithms                          |

| List of | Acronyms                            |

| Acknov  | f wledgments                        |

| Dedica  | ation                               |

| Chapte  | er 1 Introduction                   |

| 1.1     | Formalized Problem                  |

| 1.2     | The Explicit-State Approach         |

| 1.3     | Verification Methods of this Thesis |

| 1.4     | Thesis Statement                    |

|         | 1.4.1 Contributions                 |

|        | 1.4.2 Roadmap                                | 17 |

|--------|----------------------------------------------|----|

| Chapte | er 2 Related Work                            | 18 |

| 2.1    | Preliminaries                                | 18 |

|        | 2.1.1 Temporal Logic                         | 19 |

|        | 2.1.2 The Mur $\varphi$ Description Language | 20 |

| 2.2    | Parallel and Distributed Model Checking      | 24 |

|        | 2.2.1 Model Checking Deadlock Freedom        | 29 |

| 2.3    | Parameterized Verification                   | 30 |

| 2.4    | Model Checking LTL Formulas                  | 32 |

| 2.5    | Summary                                      | 39 |

| Chapte | er 3 The PReach Model Checker                | 41 |

| 3.1    | Algorithm                                    | 42 |

| 3.2    | Crediting                                    | 45 |

| 3.3    | Light Weight Load Balancing                  | 46 |

| 3.4    | Batching of States                           | 50 |

| 3.5    | PREACH Pseudocode                            | 52 |

| 3.6    | Results                                      | 54 |

| Chapte | er 4 Model Checking of Deadlock Freedom      | 57 |

| 4.1    | Overview                                     | 58 |

|        | 4.1.1 Specification Syntax                   | 61 |

| 4.2    | Algorithms                                   | 62 |

|        | 4.2.1 Local Search                           | 63 |

|        | 4.2.2 Pass-the-Path                          | 64 |

|        | 4.2.3 Outstanding Search Table               | 64 |

|        | 4.2.4 Implementation Notes                   | 66 |

| 12     | Parformance                                  | 67 |

| 4.4    | Summa   | ary                                           | 8 |

|--------|---------|-----------------------------------------------|---|

| Chapte | er 5 P  | arameterized Deadlock Freedom                 | 3 |

| 5.1    | A Simp  | ple Example                                   | 5 |

| 5.2    | Formal  | Framework                                     | 0 |

|        | 5.2.1   | Mixed Abstractions                            | 1 |

|        | 5.2.2   | Insufficiency                                 | 5 |

|        | 5.2.3   | Parameterized Systems                         | 6 |

|        | 5.2.4   | Undecidability                                | 8 |

| 5.3    | Syntac  | tical Abstraction                             | 9 |

|        | 5.3.1   | Syntax and Restrictions                       | g |

|        | 5.3.2   | Abstraction                                   | 1 |

| 5.4    | Verifyi | ng Universal Quiescence                       | 4 |

|        | 5.4.1   | Universally Quantified Quiescence             | 4 |

|        | 5.4.2   | Abstract Rule Tags                            | 6 |

|        | 5.4.3   | Heuristics                                    | 8 |

| 5.5    | Case S  | tudies                                        | 2 |

|        | 5.5.1   | Automatic Deadlock Freedom Predicates         | 3 |

|        | 5.5.2   | The German Protocol                           | 4 |

|        | 5.5.3   | The FLASH Protocol                            | 6 |

| 5.6    | Discuss | sion                                          | 7 |

|        | 5.6.1   | Permutations on More than One Abstracted Node | 7 |

|        | 5.6.2   | Local Rule Generalizations                    | 8 |

|        | 5.6.3   | Automatic Strengthening                       | g |

| Chapte | er 6 D  | Distributed Response Property Checking        | 1 |

| 6.1    | Introdu | action                                        | 2 |

| 6.2    | Overvi  | ow. 11                                        | 1 |

|         | 6.2.1 Preliminaries                        |

|---------|--------------------------------------------|

|         | 6.2.2 A Note about Stuttering              |

| 6.3     | Algorithm                                  |

|         | 6.3.1 Worst-Case Time Complexity for OWCTY |

| 6.4     | Distributed Implementation                 |

| 6.5     | Optimizations                              |

|         | 6.5.1 Saved Expansions                     |

|         | 6.5.2 Dynamic Kernel                       |

|         | 6.5.3 Deletion by Predecessor Counting     |

| 6.6     | Results                                    |

| 6.7     | Comparison with DiVinE                     |

| 6.8     | Conclusions and Future Work                |

| Chapte  | er 7 Conclusions                           |

| 7.1     | Contributions Recap                        |

| 7.2     | Future Work                                |

| Bibliog | graphy                                     |

| Appen   | dix A German's Protocol                    |

| Appen   | dix B HIR Proofs                           |

| Appen   | dix C Heuristic Examples                   |

| C.1     | Discharging AEG                            |

| C.2     | Discharging AUG                            |

# List of Tables

| 1.1 | Verification methods                                       | 9   |

|-----|------------------------------------------------------------|-----|

| 3.1 | Large model experiments                                    | 55  |

| 4.1 | Performance of DF checking algorithms                      | 70  |

| 5.1 | Mapping of types from concrete system to mixed abstraction | 92  |

| 5.2 | Heuristics for ruleset tag/property pairs                  | 99  |

| 5.3 | List of chapter symbols                                    | 110 |

| 6.1 | PREACH-RESP benchmark results                              | 132 |

# List of Figures

| 2.1 | Stern-Dill DEMC flow-chart                                      | 26 |

|-----|-----------------------------------------------------------------|----|

| 3.1 | Kumar/Mercer load balancing                                     | 47 |

| 3.2 | Light weight load balancing                                     | 47 |

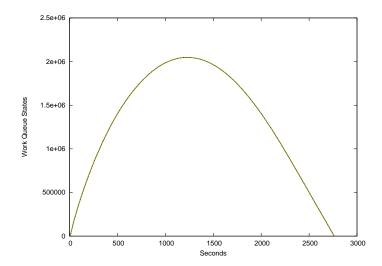

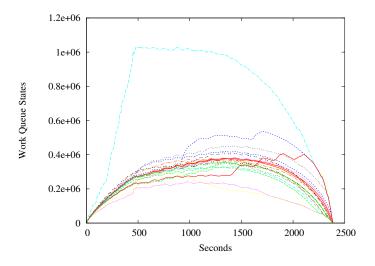

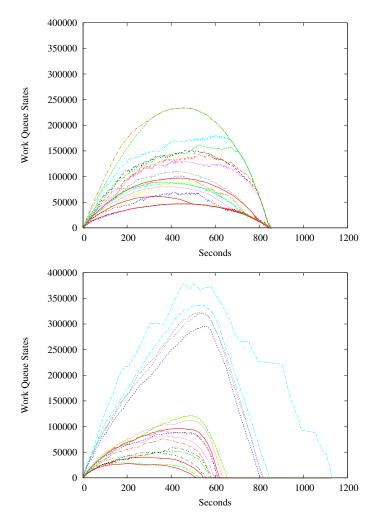

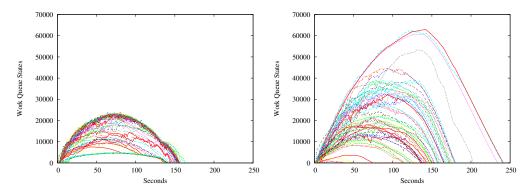

| 3.3 | Load balancing effect on work queues                            | 49 |

| 3.4 | LDash model load balancing                                      | 50 |

| 3.5 | SCI model load balancing                                        | 50 |

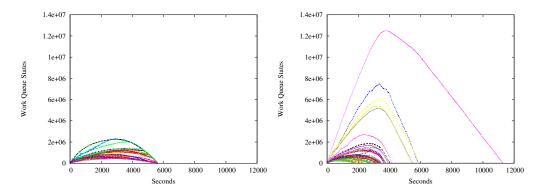

| 3.6 | State batching effect                                           | 52 |

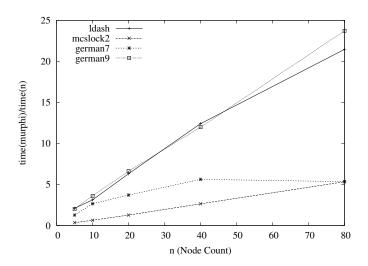

| 3.7 | Speed up experimental results                                   | 56 |

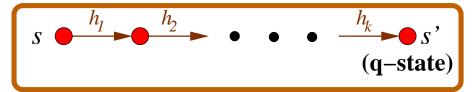

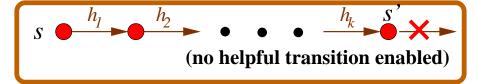

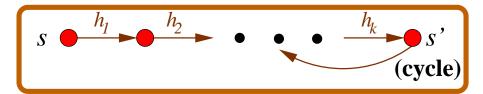

| 4.1 | Illustration of deadlock freedom                                | 58 |

| 4.2 | Outcomes of a witness search                                    | 60 |

| 4.3 | A subgraph that does not satisfy DF                             | 63 |

| 4.4 | PtP/OST example                                                 | 65 |

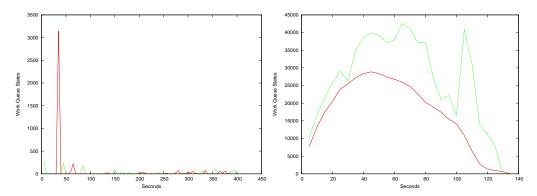

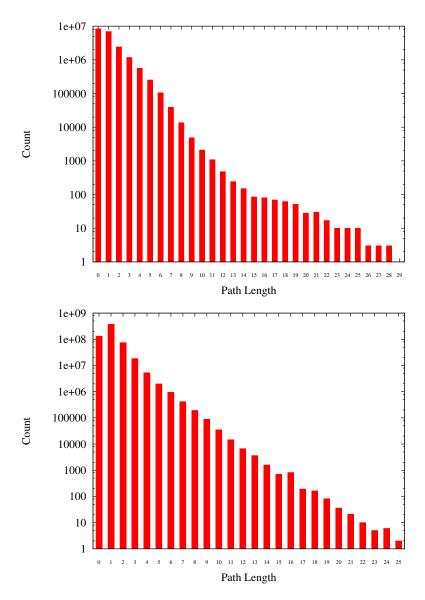

| 4.5 | Histograms of path lengths in PtP mode                          | 71 |

| 4.6 | Path length histogram for intel_in PtP mode                     | 72 |

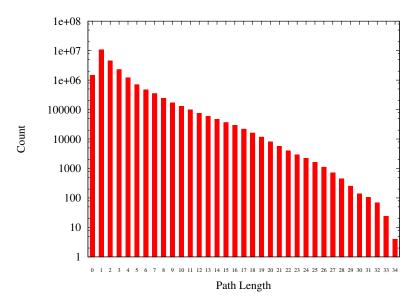

| 4.7 | Memory usage of ST                                              | 72 |

| 5.1 | Program Turn (mutual exclusion by turn setting)                 | 76 |

| 5.2 | The $\mathrm{Mur} \varphi$ system for program TURN              | 77 |

| 5.3 | $\mathrm{Mur} \varphi$ system for the mixed abstraction of TURN | 78 |

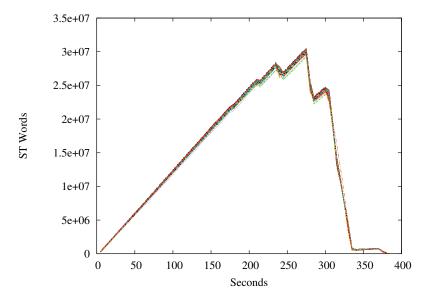

| 5.4 | Finding paths through permutation                               | 80 |

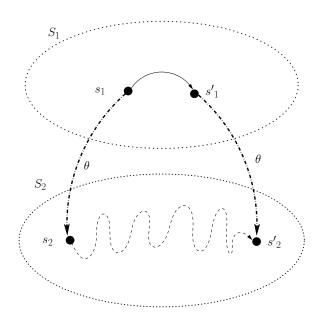

| 5.5 | Simulation of $S_1$ by $S_2$                                                |

|-----|-----------------------------------------------------------------------------|

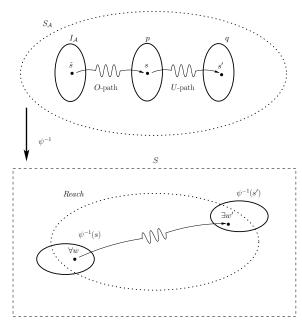

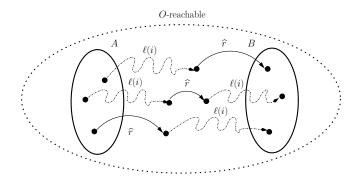

| 5.6 | Illustration of Lemma 1                                                     |

| 5.7 | Illustration of $\mathcal{A}_{\ell(i)} \models AG(A \to EF_{\widehat{r}}B)$ |

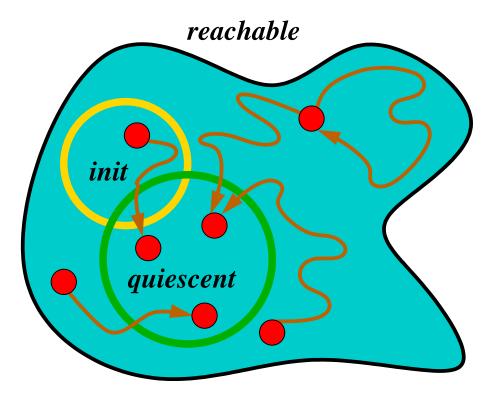

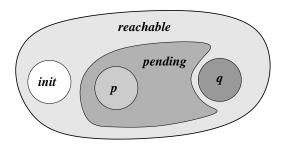

| 6.1 | Sets of interest when checking $\Box(p \to \Diamond q)$                     |

| 6.2 | Example of PTFA updates                                                     |

| 6.3 | Response property MC plots for German6                                      |

| 6.4 | Response property MC plots for peterson6_wf                                 |

| 6.5 | Response property MC plots for snoop2                                       |

| C.1 | Schema for proving ruleset ABS_SendGntS2 is underapproximate                |

| C.2 | Schema for proving ruleset ABS SendGntE1 is underapproximate 173            |

# List of Algorithms

| 2.1 | Basic distributed cycle detection    |

|-----|--------------------------------------|

| 2.2 | One-Way-Catch-Them-Young (OWCTY)     |

| 2.3 | Maximum Accepting Predecessor (MAP)  |

| 2.4 | A LTL DEMC algorithm                 |

| 3.1 | Stern-Dill DEMC                      |

| 3.2 | PREACH DEMC                          |

| 6.1 | OWCTY at a high level                |

| 6.2 | PREACH-RESP root process             |

| 6.3 | PREACH-RESP worker process           |

| 6.4 | PREACH-RESP EXPANDANDSEND subroutine |

## List of Acronyms

BDD Binary Decision Diagram

CEGAR Counter-Example Guided Abstraction Refinement

CMP Chou-Mannava-Park

CTL Computation Tree Logic

DEMC Distributed Explicit-state Model Checking

DF Deadlock-Freedom

DFS Depth-First Search

EMC Explicit-state Model Checking

FSCC Fair Strongly Connected Component

HIR Heuristic Inference Rule

LTL Linear Time Logic

OA Over-Approximate

OST Outstanding-Search Table

OWCTY One-Way-Catch-Them-Young

PTFA Predecessor Trace Fair Actions

PtP Pass-the-Path

SCC Strongly Connected Components

ST Search Table

UA Under-Approximate

WHT Witness Hash Table

## Acknowledgments

Thanks to Mark Greenstreet for his supervision. His patience, advice and enthusiasm have been a constant inspiration. My supervisory committee of Alan Hu, John Harrison and Karthik Pattabiraman have all been helpful sources with regard to my studies. Thanks to Flavio M. de Paula, Jesse Bingham and John Erickson for all their hard work on the PREACH project — without them this thesis would not exist. Flemming Andersen also provided invaluable support on this project, which included guidance during two internships with his group. I thank John Erickson and Jim Grundy for their mentorship during these work terms. I appreciate the kindness and support from the ISD lab students over the years, and my good friends at UBC and beyond. Finally, I thank my family members for their deep interest in my education, and for always lending a hand.

For my parents, Rosemary and Paul, my role models in life.

## Chapter 1

## Introduction

Concurrency pervades modern hardware and software. From instruction-level parallelism exploited in CPU execution pipelines, to multiple threads running on a multicore machine, to a fully distributed computation on a compute cluster, concurrency is critical to performance. Modern CPU designs are becoming increasingly parallel. Energy and temperature considerations with current technologies prohibit faster clock speeds [97]. Because single-core performance has reached its limit, multicore architectures are proliferating [3]. Such hardware designs require careful considerations for the protocols that support this concurrency through inter-core and inter-cache communication.

These hardware protocols are often devised and described at a high level by computer architects. The concurrent nature of these protocols make them particularly prone to subtle design bugs, as it is difficult for the human to consider all possible interleavings of concurrent events. Unchecked, any fundamental bugs or mistakes may not be exposed until the protocol has been implemented in a hardware description language, amid many other details, and simulations are run. But as simulation is almost necessarily incomplete with respect the the possible inputs, these bugs may escape to later stages of design and ultimately persist into fabricated chips and sold to customers. Errors that are discovered late in this design, implementation and production process can have extremely expensive

consequences. Economically, we wish to catch these bugs as early in the design cycle as possible, for example, before a hardware description exists. This drives the effort known as formal verification — the attempt to prove formal properties of a computer chip design. Automated methods are easiest to use, but can require massive computational resources. To harness the required resources, we seek to scale our verification capabilities and make use of clusters of commodity machines.

Let's consider a simple example protocol that controls a traffic light. Suppose the light controls 4 directions: north, south, east, west, and has the standard green, yellow and red signals. A controller will dictate which signals are on when the traffic light is first powered on, and then how they change over time from there. The controller uses a timer to measure how long to stay in the current state before changing. It may also use additional information such as the time of day or sensory data that indicates the presence of a waiting vehicle. At the protocol level, we omit this timing information and consider what the controller allows as far as changes to the signals. For example, we wouldn't expect a good controller to allow a light to transition from green directly to red; we would expect a yellow light in between. For a simple controller, the *state* of the traffic light is precisely the signals that are turned on in the 4 directions.

How do we check if our controller is correct? One approach is to simply test it out and see if any accidents occur. Perhaps this is done in a controlled environment where no moving cars are involved. But how much of this testing is sufficient? Ideally we would like to exhaustively check every possible configuration and make sure all of them are okay. We need a formal notion of which states are "bad states"; such a description is called a safety property. A safety property of this system could be "if north is green then east is red", as we can all agree that violating this statement is indeed quite unsafe. But establishing safety isn't enough for a traffic light. Indeed, a light that has all 4 signals turned red forever is safe, but not very functional. This motivates the notion of liveness properties, that reason about events that will eventually occur. A liveness property of this system

could be "north will eventually be green", because otherwise the southbound cars could wait indefinitely.

Once we decide on safety and liveness properties, we can use verification tools to automatically verify them. To show safety, we need to exhaustively list all states that the system allows, and check that none of them meet the "bad" criteria. Liveness is more difficult, as this reasons about sequences of states that may be of unbounded length. The computational cost of both of these checks is mainly determined by the number of reachable states, that is states that could occur in the controller. Unfortunately, this number tends to increase rapidly as more detail is added to the system. In this example, determining the number of reachable states of this system would require a more formal description, but in practice it is often proportional to the number of possible states. Assuming that exactly one signal is always on in every direction, the number of possible states for this system (recalling there are 4 directions and 3 signals), is  $3 \times 3 \times 3 \times 3 = 3^4 = 81$ . How does this change if more detail is added to the system? Suppose that instead of 4 directions we have an addition direction to consider (say, from the north-west), and in addition there's a left turn arrow, *i.e.* there's now 5 directions and 4 signals. Now the number of possible states is  $4^5 = 1024$ , a huge increase. This is an example of combinatorial explosion.

In order to deal with state-explosion, many ideas have been proposed. One of our main approaches is to *distribute* the exhaustive check among many computers, to leverage their aggregate memory and computing power. Such techniques are incentivized by modern computers, as commodity multicore machines connected via commodity networks are sufficient to drastically increase our verification capabilities.

Much of this thesis focuses on the liveness problem. But with most verification research, it's best to address safety first, as it is easier to deal with. Thus we present our tool called PREACH, which lists all possible states of a system and checks them for safety. The motivation for this model checker was straightforward, as we had colleagues in industry with large model checking problems, and existing tools lacked the robustness and

scalability they needed. PREACH can handle systems with enormous numbers of states — on the order of billions — using a hundred machines or more. While the original PREACH was very effective for verifying safety properties, it highlighted the need to check liveness properties, which are generally harder to deal with. Because it involves reasoning about sequences of states, model checking of liveness is susceptible to a much more severe form of the combinatorial explosion problem than safety. Furthermore, reasoning about sequences introduces mathematical technicalities that can make the properties to be checked incomprehensible to the architects. To address both the computational and the psychological complexity of liveness checking, we consider three special cases that both simplify the problem and address a large number of the liveness issues that arise in practice. In particular, we extend PREACH to check for deadlock-freedom and response properties.

In the context of the traffic light example, a deadlock freedom property could be "if new cars stop arriving at the intersection, all waiting cars will eventually face a green light". This is important for hardware designs as it can demonstrate that the system will not get "stuck" in a state where pending operations cannot complete. An example response property is "every car that arrives will eventually face a green light". This is a stronger statement than the deadlock freedom property, as it says something about liveness of the intersection even when there's a steady stream of traffic. In practice, this is a more difficult property to specify and verify. Finally, we also give a method for proving parameterized deadlock freedom properties. This means that we could show that an intersection with any number of directions satisfies a deadlock freedom property. Such techniques are of particular importance when combinatorial explosion exhausts the capacity of our verification tools.

In summary, this dissertation attacks the problem of automatically proving liveness properties of real industrial hardware protocols. We proceed in the next section by formalizing the problem and our contributions using standard verification terminology.

#### 1.1 Formalized Problem

Consider the problem of verifying correctness of a hardware design. Often, a verification engineer will formally express some key aspects of the design in a specification language, which implicitly describes a directed graph called a transition system (or simply a system). This is typically achieved by stating system variables, initial conditions on their values, and conditions for changes to their values. Such descriptions vary in detail, ranging from the protocol level, which models event-based nondeterministic behavior, to cycle-accurate models to bit-accurate models. The properties we would like to prove about the system are often categorized as safety properties and liveness properties. These are formally distinguished below, but a commonly used intuitive taxonomy quotes Lamport: "something will not happen" for the former and "something must happen" for the latter [80]. Model checking [44] refers to algorithms and tools for automatically verifying these properties. In this thesis, we focus on *explicit-state* model checking (EMC), which represents each state (a valuation of the system variables) as a distinct object in memory. The state-space explosion problem limits the effectiveness of model checking; as more detail is added to the model the number of possible states grows exponentially. Typically the number of reachable states grows in proportion to the number of possible states, which places increasing demands on computational resources.

Each vertex of the system corresponds to a state; the arcs of the system are called transitions. If p is a predicate over the system variables, then the set of states with a variable valuation that satisfies p are called p-states. The transition system includes a predicate for the initial states. State s is called reachable if there is a path from an initial state to s. A trace is a walk of possibly infinite length that begins at an initial state. Except in highly degenerate transition systems, there are an uncountably infinite number of traces. We define a safety property as an assertion over all traces for which a counterexample trace has finite length. An example is "Always p", which means that every reachable state is a p-state. Verifying a safety property using EMC amounts to enumerating the reachable

states and checking something "local" to each state. A liveness property is an assertion over all traces for which a counterexample trace has infinite length. An example is "Eventually Always p", which means that every infinite trace has an infinite postfix of p-states. Liveness properties are more computationally intensive to verify because they require reasoning over traces rather than reachable states; liveness verification calls for algorithms that detect and analyze strongly connected components of the state transition graph [47, Section 22.5].

To cope with state-space explosion and computers with limited memory, judicious choices must be made when deciding which aspects of the design are included in the model. If a model checking procedure exhausts memory resources, then removing details from the model will usually reduce the size of the reachable state space. Suppose the model in question has is parameterized by an integer that monotonically increases the reachable state space size. Then, reducing the value of this parameter may render model checking tractable. For example, a cache coherence protocol description may be parameterized by the number of caches; clearly increasing this number leads to a greater number of variables and concurrent transitions, and a larger reachable state-space. Perhaps the design of interest has 32 caches, but we can only model check the protocol model with 4 caches. The expectation is that safety or liveness violations in the smaller model will have analogous violations in the real design, thus increasing our confidence when model checking succeeds. Of course, this is does not rule out the possibility that 32 cache design allows violations that are only present with more than 4 caches. Two different approaches for further improving confidence are: (1) using tools and techniques to increase our model checking capacity, and (2) using a parameterized verification technique, which proves something about the cache design for any parameter value, including 32. Both approaches are explored in this thesis.

Despite the complementary nature of safety and liveness, the majority of verification research and practice focuses on the former. This is due to safety being easier conceptually, theoretically and computationally. Our view is that liveness checking is a crucial component of the verification task. Not only is liveness usually a desirable property for systems to

adhere to, but liveness checking can also catch modeling errors. Suppose the user intends to specify a system that will have reachable states S, but the user makes a mistake when writing the model and the resulting system only reaches a subset of the intended states  $\hat{S} \subset S$ . If all states of  $\hat{S}$  satisfy safety but some state of  $S \setminus \hat{S}$  does not, then the safety violation will be obscured by the user error. However, simple liveness checks can reveal errors that were hidden by a modelling mistake and give the user confidence that the corrected model faithfully captures the system as intended.

In this thesis we focus on two specific classes of properties of finite state systems. Because we emphasize industrial application, we choose properties that practicing designers will find easy to interpret. Likewise, our emphasis on large-scale problems leads us to choose properties that are both useful to the designer *and* computationally tractable for automatic verification.

The first liveness property that we consider is deadlock-freedom (DF). The basic idea is that given a system model, we identify some actions as injecting new transactions into the system (for example, requesting a read to or write from memory); other actions make progress on some pending transaction; and some actions complete one or more pending transactions. Let q denote quiesence, a description of states in which there are no pending transactions.DF states that from any reachable state, the model can reach a q-state; in other words, all pending tasks can be completed. In CTL (computational tree logic — described in more detail in Section 2.1), we can express DF as AGEF q. AG means "along all paths (i.e. at all reachable states), and EF q means "there exists a path to a q state". Thus, AGEF q is CTL for "from every reachable state, there is a path to a state that satisfies q." We present efficient approaches for verifying DF, which can also be applied to the more general version AG ( $p \to EF q$ ) which means "from any reachable state that satisfies p, there exists a path to a state that satisfies q." Note that the existence of a path does not guarantee that the path is taken. For example, an unending sequence of new tasks that pre-empt some older task might continue to arrive; or the model may allow the system

to make non-deterministic choices, only some of which lead to completing all pending tasks. To show that every task is eventually completed, we need a stronger property than DF.

Intuitively, a response property says that every request for some service is eventually granted. Let p-states be those in which the service has been requested, and q-states be those in which the service has been completed. A response property specifies that every trace that reaches a p-state will later reach a q-state. In CTL we write this as AG ( $p \to AFq$ ); this means that from all reachable p-states (AGp), all paths eventually reach a q-state. In contrast, the E in EFq (as used to describe DF) says that there exists a path along which q is eventually satisfied.

Adding a bit more notation, well note that there are two commonly used logics for reasoning about liveness: CTL and LTL (linear-time logic). The differences are described in Section 2.1 — neither is strictly more expressive than the other. In LTL,  $\Box$  indicates "henceforth" (*i.e.* the property holds for all subsequent states) and  $\Diamond$  denotes "eventually" (*i.e.* the property holds for some subsequent state). The CTL formula AG  $(p \to AFq)$  is equivalent to the LTL formula  $\Box(p \to \Diamond q)$ . When describing response properties, the LTL notation is more commonly used in the research literature, and we will use the LTL notation here<sup>1</sup>.

In practice, it is necessary to impose fairness assumptions on the system that formally express which traces are deemed to be realistically allowed by the expected underlying implementation. For example, an arbiter that always grants to one requester and not the other could be viewed as unrealistic and ruled out using fairness. More generally, most models consist of many concurrently operating subsystems. It is common to have a scenario with entities a, b, and c where a makes a request of b while c can continue indefinitely working on its own. Without fairness, we must consider traces where a makes a request and all subsequent actions are those of c. For many models, it is unrealistic to consider scenarios where c performs an arbitrary number of actions while b does nothing. We need

<sup>&</sup>lt;sup>1</sup>Some authors use G instead of  $\square$  and F instead of  $\lozenge$  in LTL formulas. We use  $\square$  and  $\diamondsuit$  notation as it will not be confused with the CTL notation that describes DF properties.

| Property Type       | Increasing Capacity    | Parameterized   |

|---------------------|------------------------|-----------------|

| Safety              | PREACH MC [22]         | CMP Method [40] |

| Deadlock-Freedom    | PREACH-DF MC, CTL MC   | [23]            |

| Response Properties | LTL MC, PREACH-RESP MC | [93, 18, 56]    |

Table 1.1: Verification methods

a way to exclude these unrealistic, also referred to as unfair, traces. If Fair is a predicate over traces expressing these assumptions, then  $Fair \to \Box(p \to \Diamond q)$  says that every fair trace that includes a p-state will include a q-state in the future, or equivalently, that any trace that visits a p-state and then cycles forever without visiting a q-state necessarily violates fairness.

We expect designers are more interested in response properties than DF because it guarantees something good will happen as opposed to it merely being possible. However, DF avoids the technical and conceptual difficulties associated with specifying fairness, is less computationally complex, and we believe many real protocols that violate response in fact also violate DF. Intuitively, DF can express that pending transactions in the system can complete if new transactions stop being injected. On the other hand, response properties can reason about a particular kind of transaction always eventually completing regardless of other activities.

The cross product of the property types {Safety, Deadlock-Freedom, Response Property} and the goals of {increasing capacity, parameterized verification} gives 6 pairs, as summarized in Table 1.1. We briefly cover this table and expand on each entry in Section 1.3.

The work of this thesis is formulated using the specification language of the  $\text{Mur}\varphi$  model checker [52], a guarded command language [50] for finite state transition systems. However, we believe the methods are general to the languages used by other model checkers [65, 41, 5].

Model checking of safety properties has several well-understood enhancements that

aim to increase capacity, including abstraction, symmetry reduction and partial order reduction. Our contribution in this area is the distributed explicit-state model checking (DEMC) tool called PREACH, which utilizes the aggregate memory of hundreds of machines and is entirely compatible<sup>2</sup> with these other techniques. We have extended PREACH to check both DF (PREACH-DF) and response properties (PREACH-RESP) in a distributed environment.

Parameterized verification is known to be an undecidable problem, so human guidance is usually a key ingredient. There are a number of previous works for both safety and liveness properties in this area. The Chou-Mannava-Park (CMP) method [40] for safety properties has been demonstrated as an effective approach when applied to  $\text{Mur}\varphi$  models with a symmetric parameter. We built upon this method and developed a theory for proving parameterized DF properties, also using  $\text{Mur}\varphi$  models with a symmetric parameter, that relies on PREACH support for MC-DF checks [23]. See Chapter 2 for a survey of techniques that deal with proving that LTL formulas hold in parameterized systems.

To summarize, this thesis addresses the following problem.

The ubiquity of highly concurrent hardware and software designs calls for verification tools that support both safety and liveness. Given the conceptual and computational complexity of specifying and verifying liveness, we need verification methods that support straightfoward liveness properties and that can be applied to industrial-scale problems.

#### 1.2 The Explicit-State Approach

Before I discuss our contributions that utilize explicit-state model checking, it is important to justify the use of this old and simple method. Indeed, landmark contributions have

<sup>&</sup>lt;sup>2</sup>Abstraction can be performed to generate the input model, and symmetry reduction is built in to the  $Mur\varphi$  front-end. Partial order reduction, on the other hand, is not supported by PREACH but it has been investigated in a parallel model checking setting [100].

been made with symbolic model checking techniques that represent a set of states (or approximation thereof) with a boolean formula over system variables, and the next-state function with boolean formula over primed and unprimed variables. The first widespread symbolic model checkers used  $binary\ decision\ diagrams\ (BDD)\ [35]$  and demonstrated that the state-space explosion can be curbed for many systems of practical importance [90]. Since then, other symbolic approaches have been employed, including those that utilize SAT queries and interpolants [95, 33]. These methods are necessary for what is referred to as  $hardware\ model\ checking$ , where a sequential circuit is modeled as an and-inverter graph with some modest number of input wires. Explicit-state model checking (EMC) is often infeasible for these kinds of models as the number of input combinations blows up exponentially. However, we note that while symbolic approaches are essential for certain problem domains, there is no "silver bullet" to dealing with state-space explosion. As noted by Hu [67, Section 1.2.3], there are  $2^{2^n}$  boolean functions on n variables, and any representation scheme that uses a polynomial number of bits O(P(n)) can represent at most  $2^{O(P(n))}$  of these functions.

EMC tends to be appropriate when the reachable state space features sufficient non-uniformity. In such cases, symbolic expressions may degenerate to a large formula that resembles a disjunction of conjuncts, where each conjunct describes only a small number of states. Then, symbolic operations will in a sense require just as much work as explicit-state, but with a larger constant factor in terms of time and memory cost. The aforementioned work by Chou et al. [40] suggests that EMC is the right choice when checking cache coherence protocols. To paraphrase:

- 1. BDD performance is more sensitive to the data structures used to describe the protocol;

- 2. EMC can take advantage of symmetry reduction [70];

- 3. EMC is better suited for disk-based techniques;

4. SAT-based methods are not known to outperform BDD-based methods on cache coherence protocols.

In addition, EMC seems to be better suited for distributed implementations, at least compared with BDDs. Existing approaches involve maintaining the BDD on a single machine until it is about to exceed the memory capacity, and then carefully split the BDD in order to balance memory usage among two machines and minimize duplication [61, 60]. In contrast, distributing the reachable state space among machines is trivially achieved by using a uniform random hash mapping [104]. We note that Bradley's original IC3 model checking paper involves experiments that use multiple cores and machines, but appears to saturate in performance at 8 to 12 threads [33]. There are also promising IC3 methods for showing liveness [34], but to our knowledge the parallel performance has not been investigated.

#### 1.3 Verification Methods of this Thesis

PREACH (Parallel REACH ability) is a distributed explicit-state model checker based on Mur $\varphi$  [22]. It is designed to be scalable and harness the aggregate computing power of clusters of machines. PREACH verifies Mur $\varphi$  models and borrows Mur $\varphi$ 's C++ implementations of key model checking components, such as a hash table to store states and compilation of Mur $\varphi$  models to C++ code for the efficient computation of state successors. The main module that handles communication and coordination of threads is written in the functional language Erlang [2] and is roughly 1000 lines of code. This separation of the distributed algorithm from model checking details offers both efficiency and simplicity. Our experiments have shown that in addition to linear speedups, PREACH can utilize hundreds of compute nodes to explore the state space of the largest Mur $\varphi$  models ever checked — on the order of 100 billion states. The clean code and extensibility of PREACH has been leveraged in subsequent projects [23, 26, 27].

First, we implemented a sequential DF checking procedure as part of a method for parameterized verification of DF [23]. For a symmetric system  $\mathcal{S}$  described in a guarded command language and parameterized by n, we seek to show that for any n, each reachable state of S(n) has a path to some q-state, i.e.,  $S(n) \models \mathsf{AGEF}\,q$ , where q is a predicate<sup>3</sup>. Our approach is inspired by, and builds upon the CMP method [40] which establishes properties of the form  $S(n) \models AGp$  for predicate p, which may include universal quantifiers over the parameterized set. They use a counter example guided abstraction refinement (CEGAR) approach [45]. First, an abstraction  $\mathcal{A}$  of  $\mathcal{S}(n)$  for every n > k is computed, which essentially keeps k fixed parameter entities fully modeled, and overapproximates the behavior of all others. Next, a trace of  $\mathcal{A}$  is found via model checker that reaches a  $\neg p$ -state. The user examines the trace and devises a non-interference lemma  $\phi_1$  which is the abstraction of an assumed invariant of S(n). The intention is that if  $\phi_1$  holds of S(n)for all n > k, then the spurious trace cannot occur. This is achieved by strengthening  $\mathcal{A}$ with  $\phi_1$  by restricting when actions of the abstracted parameter entities may occur, and model checking is used again to verify AG  $(p \wedge \phi_1)$ . The user continues this process until the abstraction satisfies  $AG(p \wedge \phi_1 \wedge ... \wedge \phi_m)$ , a counterexample is found, or the user is unable to find the next useful  $\phi_i$ . If  $AG(p \wedge \phi_1 \wedge ... \wedge \phi_m)$  is established, the assumed invariants along with p are actual invariants of S(n) because A simulates S(n) for n > k.

Adapting this method to proving parameterized DF presents challenges. We need to show that every reachable state in S(n) has a "witness" — a path to some q-state. In order to find such paths, it's often necessary to include the actions of abstracted parameter entities. However, because the abstraction *overapproximates* these actions, it is unsound to assume that they may occur as there's no guarantee that corresponding actions exist in the concrete system.

Suppose we have used the CMP method to verify some safety properties of param-

$<sup>^{3}</sup>$ Typically, q is universally quantified over the parameterized set, and is interpreted by to the set of *quiescent* states. In cache coherence protocols, this corresponds to states where there are no pending messages.

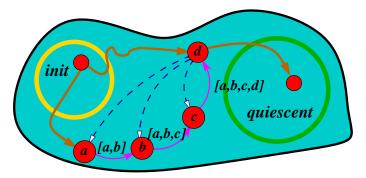

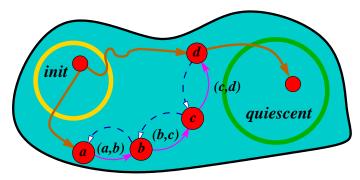

eterized system  $\mathcal{S}(n)$  via abstract system  $\mathcal{A}$ . As the transitions of  $\mathcal{A}$  are overapproximate, there could exist reachable states for which no concrete analogue is reachable in S(n) (for any n). In our method, we employ a mixed abstraction which augments  $\mathcal{A}$  with underapproximate transitions U; denote the overapproximate transitions with O. Transitions of U are guaranteed to have a concrete analogue, and thus soundly imply existential path properties in S(n). To check such properties, we use state space enumeration to explore states reached through O-transitions, and for each reachable state a path is found composed of U-transitions to a q-state. PREACH implements this model checking procedure. If there exists a reachable state  $\tilde{s}$  for which there is no *U*-path to a *q*-state, a counterexample trace is generated. Following an analogous CEGAR procedure to that of the CMP method, the user must either prove that  $\tilde{s}$  is unreachable by strengthening O, or that such a path should exist from  $\tilde{s}$  by weakening U. The latter is done by using inference rules that we refer to as "heuristics" [23]; see Chapter 5. The proof obligations of heuristics are discharged by model checking the mixed abstraction as described above. We applied this method to both the German and FLASH cache coherence protocols as case studies where DF for any number of caches was established.

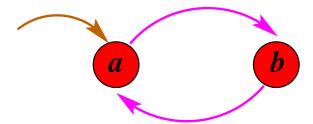

Following up on this work we designed and implemented two distributed algorithms for verifying DF of systems. The user provides both the quiescent predicate q, along with a set of helpful transitions  $\mathcal{H}$  that are expected to be a sufficient set to form a path from every reachable state to some q-state. Similar to the paths formed using U-transitions above, both algorithms perform a directed search using only  $\mathcal{H}$ -transitions. Identifying these transitions provides an expression of designer intent. This approach allowed us to discover a bug in the Peterson mutual exclusion model that had persisted in the  $\operatorname{Mur}\varphi$  distribution for about 20 years. We found that in most cases the average search path is short and PREACH can perform this lightweight liveness check for a small additional overhead as compared to safety checking.

To attack the verification of a response properties, we implemented a variant of

the One-Way-Catch-Them-Young (OWCTY) algorithm [73, 38] in PREACH, capable of checking response properties on systems augmented with fairness on actions. Previous OWCTY algorithm descriptions were aimed at checking arbitrary LTL formulas, used data structures that respresented states sets with full state descriptors, and generally did not include fairness assumptions. In PREACH, states are hashed to 40 bit descriptors, so that checking membership of a set is easy but member states cannot easily be reconstructed. Our approach uses forward reachability only, and augments the hash table entries with various bookkeeping bits to emulate membership in the various sets. We have found this implementation to be capable of checking response properties on fair systems with hundreds of millions of reachable states.

#### 1.4 Thesis Statement

Given some hardware design model, the class of properties that can be described as DF or response are of practical interest. Capacity constraints limit the effectiveness of automatic, sequential model checking approaches, especially for protocol level descriptions. Many designs can be modeled as a system that is parameterized, for example by number of caches or addresses. Two approaches are to set the parameter as large as our model checking tools and hardware resources allow, or to employ a parameterized verification method. These approaches trade-off human effort with strength of the verification result with respect to the original design. Another trade-off is verifying response properties versus DF; the former is a stronger result, but the latter is easier both from a computational and human effort perspective. Regardless of the approach, there is particular importance to mitigate the burden on the user. By leveraging the stable, tested and large scale distribution of the state-space provided by the PREACH model checker, we are able to achieve scalable methods for liveness verification.

This brings us to the thesis statement:

This thesis develops and demonstrates tractable, practical and scalable distributed explicit-state model checking methods for establishing liveness properties of practical importance for large-scale models of hardware protocols.

#### 1.4.1 Contributions

- 1. PREACH: an industrial strength parallel, explicit-state model checker capable of checking the largest published  $\text{Mur}\varphi$  models by distributing the computation across hundreds of machines. My contributions include:

- (a) Created the initial prototype of the distributed model checking algorithm.

- (b) Implemented and evaluated various approaches to load balancing to address both performance and thread crashes.

- (c) Gathered statistics on Erlang communication throughput and latency relative to message size, motivating state-batching, load balancing, and other optimizations.

- 2. Parameterized DF: A novel method for establishing DF properties in symmetric parameterized systems. This is the first work in parameterized DF, and complements the CMP method for parameterized safety properties.

- 3. PREACH-DF: Two approaches for DEMC of DF. Shows that given simple and easily available user input, can model check DF on large models for a small overhead compared with state-space enumeration.

- 4. PREACH-RESP: A novel algorithm implementation for distributed explicit-state model checking of response properties on fair systems. Demonstrated that in practice the OWCTY algorithm takes only a modest constant number of expansions per state far less than the worst-case performance.

#### 1.4.2 Roadmap

The rest of the thesis is organized as follows. Chapter 2 is related work, comparing and contrasting our contributions with literature in DEMC, parameterized verification, and LTL model checking. The Section 2.1 provides technical background and some definitions used throughout the thesis. Chapter 3 summarizes the PREACH model checker. Chapter 5 explains our approach to parameterized DF proofs. Chapter 6 covers the implementation of the distributed OWCTY-like algorithm. Finally, Chapter 7 summarizes the thesis and points to areas of future work.

## Chapter 2

## Related Work

Here, we survey the related research from the literature and compare it with our work. First, Section 2.1 provides some definitions, notation for CTL and LTL temporal logics and background for the  $Mur\varphi$  description language. These are used throughout the rest of this thesis and are relevant to related work. The next three sections divide the previous work into categories. Section 2.2 describes parallel and distributed explicit-state model checking with a focus on tools. Section 2.3 examines parameterized verification with an emphasis on techniques. Section 2.4 describes LTL model checking with a focus on algorithms. We conclude with a summary in Section 2.5 that puts the contributions of this thesis into context.

#### 2.1 Preliminaries

A system S is a triple (S, I, T) where S is a set of states,  $I \subseteq S$  are the initial states, and  $T \subseteq S \times S$  is the transition relation. System S may be viewed as a digraph G = (S, T). The reachable states of a system are the states s for which a path exists in G from an initial state to s. A trace is a walk of possibly infinite length in G from an initial state. If  $S' \subseteq S$ , let  $\langle S' \rangle$  be the subgraph of G induced by the vertices of S'.

A system has a set of variables each with finite range that each state is a valuation

of. If p is a predicate on state variables, then we say that s is a p-state if p(s) is true. We sometimes overload this terminology; if A is a set of states, then an A-state is a member of A. If v is a variable of S and s is a state, then v(s) is the value of v in s.

#### 2.1.1 Temporal Logic

Here we give a brief explanation of CTL and LTL. For a formal description, see [68].

CTL is a logic over paths of G, and are meaningful in any state of G. Symbols A and E are branching quantifiers, where A means "for all paths from the current state" and E means "at least one path from the current state". Each branching quantifier is immediately followed by a path-specific quantifier:

- $X \phi$  means  $\phi$  holds in the next state on the path.

- F  $\phi$  means  $\phi$  holds eventually on the path.

- $\mathsf{G} \phi$  means  $\phi$  holds everywhere on the path.

- $[\phi \ \mathsf{U} \ \psi]$  means that  $\phi$  holds at least until some state where  $\psi$  holds, and that  $\psi$  eventually holds.

- $[\phi \ \ W \ \psi]$  means that  $\phi$  holds at least until some state where  $\psi$  holds. If  $\phi$  holds everywhere on the path then  $\phi \ U \ \psi$  holds for any  $\psi$ .

Here,  $\phi$  and  $\psi$  are CTL formulas consisting of braching/path-specific quantifier pairs or state predicates. CTL formulas may be combined with the usual logic connectives:  $\neg$ ,  $\wedge$ ,  $\vee$  and  $\rightarrow$ .

Unless otherwise stated, when we say that CTL formula  $\psi$  holds in  $\mathcal{S}$ , it means that  $\psi$  holds in every initial state. As examples,

- AG p means "always-globally p", or p holds in all states along all paths;

- AGAF p means "always-globally, always-eventually p", or in all states along all paths, p holds eventually

• AGEF p means "always-globally, exists-eventually p", or in all states along all paths, there exists a path to a state where p holds.

LTL is a logic over all infinite traces the system allows. As with CTL, the logical connectives have the usual meaning and p is a state predicate. As LTL reasons over a set of traces, there is no notion of branching quantifiers, only path-specific quantifiers:

- $\square \phi$  means  $\phi$  holds everywhere along the trace.

- $\Diamond \phi$  means  $\phi$  holds eventually along the trace.

- $\bigcirc \phi$  means  $\phi$  holds in the next state on the trace.

- $\phi \ \mathcal{U} \ \psi$  means that  $\phi$  holds at least until  $\psi$  holds, and  $\phi$  eventually holds along the trace.

- $\phi \mathcal{R} \psi$  means that  $\phi$  holds at least until  $\psi$  holds, but  $\phi$  need not eventually hold along the trace.

- p means that p holds in the first state of the trace.

We use both CTL and LTL in this thesis. Neither is strictly more expressive than the other. For example, the CTL formula AGEF p cannot be expressed in LTL, and the LTL formula  $\Diamond \Box p$  cannot be expressed in CTL. Even though response properties are expressible in both CTL and LTL, we choose standard LTL notation as it is consistent with the literature on response properties.

#### 2.1.2 The $Mur\varphi$ Description Language

Here we give an overview of the Mur $\varphi$  description language which is the input language of the Mur $\varphi$  model checker [52] and PREACH. For the Mur $\varphi$  user manual and a tutorial, see [98, Murphi 3.1]. Examples of full Mur $\varphi$  models can be found in Figures 5.2 and 5.3, as well as Appendix A.

A Mur $\varphi$  system gives the variables that dictate the state space, a predicate for the initial states, and implicitly describe the transition graph through a sequence of guarded commands, or rules. It also contains a list of state invariants. When model checking commences, initial states are constructed and then their successors computed according to the list of rules. Each rule has a guard, which is a predicate on states. If the guard holds true in state s, the rule is said to fire and the command part of the rule specifies an atomic update to apply to s to generate successor state s'. If all reachable states satisfy all invariants, model checking completes once all reachable states have been visited. If some reachable state does not satisfy an invariant, checking halts and a counterexample trace is printed.

We will construct a traffic light controller model as an example, to highlight the various syntactic elements.

The keyword const is used to specify constants.

```

const NUM_DIRECTIONS 4;

```

The keyword type is used for type definitions. Some built-in types include boolean and num (for integer values). In order to exploit symmetry reduction, a scalarset type must be used.

```

type DIR : scalarset(NUM_DIRECTIONS);

```

This indicates an index set of symmetric entities. The values of the indices cannot be compared with less-than or greater-than, only for equality. Enumerated, record and array types can be defined.

```

COLOR: enum green, yellow, red;

SIGNAL: record color : COLOR; waiting_car: boolean; end;

```

The system variables come next, using the keyword var. In our example, the only variable is an symmetric array of type SIGNAL:

```

var intersection: array[DIR] of SIGNAL;

```

The startstate keyword precedes a command for the initial states. These assignments are atomic, and take the form variable := value;. For loops may be used to range over index sets such as scalarsets. The initial assignment may be given a name — here we choose the Init.

```

startstate "Init"

for d : DIR do

intersection[d].color := red;

intersection[d].waiting_car := false;

end;

end;

```

This will initialize each direction's color to red and set the waiting car flag to false. Note that any uninitialized variables will be set to the special value undefined, regardless of type. It is a  $\text{Mur}\varphi$  runtime error to read a variable with value undefined unless it is with the special function is undefined.

A ruleset is a group of rules generated from an index set. For example, we could use the following to allow green to yellow transitions for all directions.

Mur $\varphi$  predicates (and guards) may include the symbols &, |, !, ->, = and != for logical and, or, not, implication, and comparing for equality and inequality, respectively. Some other rules we might want:

```

ruleset d: DIR do

rule "yellow_to_red"

```

```

intersection[d].color = yellow

==>

intersection[d].color := red;

end;

rule "red_to_green"

intersection[d].color = red

intersection[d].color := green;

end:

rule "car_arrives"

!intersection[d].car_waiting

intersection[d].car_waiting := true;

end;

rule "car_proceeds"

intersection[d].car_waiting & intersection[d].color = green

intersection[d].car_waiting := false;

end;

```

Finally, we include invariants that all states must satisfy, otherwise  $\operatorname{Mur}\varphi$  will halt with a counterexample trace. This also introduced forall expressions that form a conjunct of predicates depending on values from an index set.

```

invariant "No_Collision"

forall d1 : DIR do forall d2 : DIR do

i != j ->

((intersection[d1].color = green & intersection[d1].car_waiting) ->

!(intersection[d1].color = green & intersection[d1].car_waiting))

end end;

```

This invariant says that at most one direction will have a car waiting and a green signal at a time. But this invariant doesn't hold of our current system, as all 4 directions

might be green with a car waiting. We could address this by only allowing a change from red to green when all lights are red, changing the guard of rule red\_to\_green.

This new system satisfies the invariant, but probably isn't a good traffic light since at most one direction can be green at a time. In order to allow opposing directions to both be green at once would likely require us to rethink the types and symmetry. We won't go into this level of detail, as what we have presented is enough to follow the  $Mur\varphi$  code of this thesis.

# 2.2 Parallel and Distributed Model Checking

The two most common methods of performing model checking are explicit-state space enumeration and the use of symbolic representations. For some industrial protocols, explicit-state model checking is considered to be the more effective verification technique [104], and hence is employed by numerous tools such as  $Mur\varphi$  [52], SPIN [65], TLC [114] and Java PathFinder [63]. Most of these model checkers explore the state space in a sequential manner which can be a hindrance in terms of both memory usage and runtime when verifying systems with a large state space. This motivates the use of distributed explicit-state model checking (DEMC) tools. These tools may be categorized into those that handle safety only [104, 82, 96, 32] and those that handle some form of liveness [13]. DEMC for safety properties has received more attention. Generally, liveness checking is more complex both computationally and conceptually, yet it remains of industrial importance. To address this need, the main focus of this thesis is to design scalable solutions for interesting liveness properties of real models.

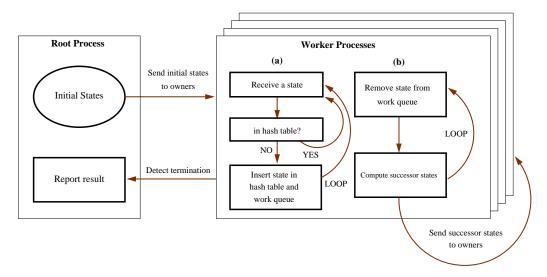

The PREACH model checker [22] is an implementation of the Stern-Dill algorithm for DEMC [106]. It reuses back-end computation components of the Mur $\varphi$  model checker [52] and reads models written in the Mur $\varphi$  language, which has become the *de facto* industry standard for modelling hardware protocols. This algorithm statically partitions the state space among processing nodes according to a uniform hash function, where each node is said to *own* a set of states. When a state is expanded, the successors are sent to their respective owners where they are stored and subsequently queued for expansion, and duplicate states are ignored. Thus, state ownership specifies the compute node that is responsible for storing a given state. In PREACH, a hash table implementation borrowed from Mur $\varphi$  [103] is used for each node to record the states it has encountered. See Figure 2.1 for a flow-chart overview of Stern-Dill DEMC.

The fact that state ownership is independent of which compute node performs the expansion leads to load balancing schemes on the states that are queued for expansion (the work queue). That is, as long as a given state is initially sent to its owner to check for hash table membership, any compute node may perform the state expansion step. The need for load balancing in DEMC has previously been identified by Behrmann in the context of timed automata model checking [19], and later by Kumar and Mercer [77]. We contrast the latter scheme with that of PREACH in Section 3.3. Also, when the work queue becomes long, we may store most of its states on disk [105] to keep the majority of main memory dedicated to the hash table. Because the work queue is written and read sequentially with large blocks of states per disk access, using disk storage has minimal impact on performance compared with using memory only. States are batched into messages with typically 100 to 1000 states before sending between compute nodes. This batching method has been used by others in the context of DEMC [106, 96].

The closest tool to PREACH is a model checking tool that has been extensively described in the literature called DiVinE [111, 12, 10, 4, 6, 7, 13]. The tool originated in Jiří Barnat's PhD work [15], and the project has been ongoing since. Initially the tool was

Figure 2.1: Stern-Dill DEMC flow-chart. Initial states are computed by a designated root process and then sent to their respective owners. These worker processes receive incoming states and check them for membership in a hash table. If the state is present, it is ignored. Otherwise, the state is inserted into the hash table and queued for expansion. Worker processes alternate between threads (a) and (b), where the former receives states and the later computes state successors and sends them off to owners. Termination is detected by the root process when all reachable states have been expanded or a state that violates safety is found.

intended to take advantage of distributed memory for model checking LTL formulas, and served as a platform for algorithm evaluation and comparison. This led to further research of algorithms and computing environments. Barant, Brim, and Ročkai [8] investigated the restricted problem of model checking weak LTL formulas using DiVinE. An LTL formula is weak if the product automaton of the formula and system that accepts counterexamples has the property that in a given SCC every state is either accepting or none of them are accepting. The same authors wrote an insightful paper on the challenge of applying partial order reduction in a parallel setting [10]. On the compute environment side, DiVinE was extended to run on CUDA enabled graphics cards [4]. They were able to utilize two graphics cards to speed up the model checking computation, the only work I am

aware of to do so. This work was for LTL model checking using the MAP Algorithm (see Algorithm 2.3). The initial state space is enumerated on a single multicore machine, and then the reachable state graph is converted to a sparse matrix representation. This graph representation is partitioned into at most two pieces and copied to the memory of the CUDA devices where the MAP algorithm runs. DiVinE has also been used to evaluate the benefit of exploiting Flash memory for model checking algorithms that formerly utilized magnetic disk to store states [6]. Recently, DiVinE 3.0 was released with features aimed at software model checking [7]. Taking as input LLVM bytecode, it is capable of model checking C/C++ programs, along with other languages that compile to LLVM.

While the DiVinE tool has explored many aspects of parallel and distributed LTL model checking, its scalability and applicability to industrial problems is unconfirmed. One publication reports it handling state spaces consisting of as many as 419 million states [11]. However, another researcher has reported scalability issues when running DiVinE on 16 machines [54]. The developers of DiVinE state that it is likely to crash when the compute nodes are heterogenous, as it is targeted towards homogeneous clusters [13]. DiVinE has no explicit algorithms for dealing with strong fairness assumptions, and model checking with more than a handful of these assumptions renders the computation intractable (more details provided in Section 6.7). While DiVinE has optimizations for models with weak fairness assumptions [16], it is only possible to attach weak fairness to all rules, not a subset. Thus, DiVinE cannot catch the Mur $\varphi$  Peterson bug explained in Chapter 4. DiVinE is unable to verify our notion of deadlock-freedom, as it cannot be specified in LTL. As far as I am aware, the benchmarks used to measure performance of DiVinE are substantially smaller than the problems arising from real, industrial coherence and communication protocols considered in this dissertation.

LTSmin [32] is a model checking tool that handles a variety of model inputs and supports (sequential) explicit-state, symbolic BDD-based, and DEMC of safety. It is designed in a modular fashion where input models are translated into an internal representation

that the model checking algorithms use, so it is straightforward to add new modelling languages. The  $Mur\varphi$  language is not currently supported, nor is DEMC of liveness properties. The majority of work surrounding LTSmin appears to focus on multicore, shared memory model checking [85]. One paper that deals specifically with DEMC attacks the problem of model checking models with unbounded recursive data types [31]. In these models, states are not restricted to a fixed size, which leads to difficulties when hashing, distributing and comparing for equality. The largest model verified with LTSmin's DEMC approach is about 570 million states [32].

Some other examples of well-known explicit-state parallel model checkers are adaptations of  $\operatorname{Mur}\varphi$  and SPIN. "Parallel  $\operatorname{Mur}\varphi$ " [104] is a parallel version of the  $\operatorname{Mur}\varphi$  model checker [52] based on parallel and distributed programming paradigms. Eddy  $\operatorname{Mur}\varphi$  [96] has improved speed over Parallel  $\operatorname{Mur}\varphi$  by the separation of concerns between next-state generation and communication during distributed model checking. It was intended to be a distributed model checker for  $\operatorname{Mur}\varphi$ . Unlike previous work, Eddy  $\operatorname{Mur}\varphi$  was implemented to take advantage of emerging multicore CPUs by using two MPI threads per compute node (one for computation and one for communication). As of this date, there is no active maintainer of Eddy  $\operatorname{Mur}\varphi$ . We have found that a recent version the software reports inconsistent numbers of reachable states on multiple runs for the same, simple models. Thus, we do not believe that Eddy  $\operatorname{Mur}\varphi$  is trustworthy in its current form. The 4500+ lines of C++ code that comprise Eddy make it more complicated than PREACH. The simplicity and stability of PREACH make it the obvious foundation for our investigation of DEMC for liveness properties.

PSpin has also been used for performing distributed model checking with the capability of handling up to 2.8 million states [82]. A distributed version of the Spin model checker [65] for checking safety only, PSpin departs somewhat from the Stern-Dill approach by allowing the hash function to be less uniform. Using a hash function that only depends on subset of the system variables can in some cases improve performance. In particular,

this non-uniform hashing exploits the structure of models written in Spin's specification language, Promela. These models describe the system through processes with some independence between them. Therefore, if many transitions only change variables that the hash function does *not* depend on, successor states need not be communicated to another worker and remain locally owned. The PSpin work shows that with ratios between the worker with the least states and the worker with the most states of as low as 0.71, large performance gains are possible when compared with uniform hashing. DEMC has also been studied for models described by Petri nets [75, 20].

### 2.2.1 Model Checking Deadlock Freedom

Our approach for verifying the deadlock freedom property AGEFq involves firing helpful transitions provided by the user. This essentially finds paths that follow pending system transactions (say, servicing a cache-miss) to completion, and q-states describe states with no pending transaction. This is reminiscent of techniques used in other verification contexts. Pipeline flushing used by Burch and Dill in their seminal paper [37] shows refinement of processor pipelines by completing in-flight instructions that are beyond a commit point as part of the refinement map. The idea of iteratively firing certain commands to complete in-flight transactions is also similar to the *completion functions* used by Park and Dill [101], though again their goal was to verify refinement. Neither DiVinE [12] nor Eddy [96] are capable of checking CTL properties such as AGEFq, and as mentioned above, neither has been applied to large scale problems as has been done with PREACH [22]. Our approach differs from the classical CTL model checking algorithm [44], which performs a pre-image fix-point computation from q to compute the set of states that satisfy  $\mathsf{EF} q$ , and then checks that the reachable states are contained in this set. With an explicit-state algorithm computing the pre-image fixpoint of q can be expensive. Suppose a  $Mur\varphi$  rule has an update of the form var := expr, where the rule guard and expr is independent of var. Then, var could have any type-consistent value in a previous state, many of which could

be unreachable states in the system. By using a forward search, we ensure that the space and time complexity is proportional to that of doing (explicit) state-space exploration. Doing CTL model checking only using forward searches has been investigated for symbolic model checking, e.g. the work of Iwashita et al. [72]. They show that using forward search only offers performance improvements for many CTL properties.

### 2.3 Parameterized Verification

Our work in verifying parameterized deadlock-freedom builds upon the CMP method [40] for verifying parameterized safety properties. The CMP method has motivated other works, including its formalization [76], automation [28], and application to industrial protocols [107, 99].

There have been many previous efforts to extend compositional techniques to parameterized safety property verification [42, 92, 93, 40, 76, 86, 28, 83, 99]. Pioneering work by Clarke et al. [42] showed that a mutual exclusion scheme with n nodes arranged in a ring that passed around a token was correct for all n. This was established by means of a bisimulation between a system with k nodes and one with k+1 nodes for all k>1. The logic to describe parameterized properties was Indexed CTL\* (or ICTL\*), which is CTL\* without the next-time operator<sup>1</sup>, and indexed formulas of the form  $\bigwedge_i f(i)$  or  $\bigvee_i f(i)$  where i ranges over the nodes and f is a predicate over variables local to that node. More recently, the work of Lv et al. [86] gives a technique for automatic strengthening of a CMP-like abstraction of symmetric systems. If the abstraction has m concrete nodes, they instantiate a system with m+1 nodes and use invariants of this system as proposed variants of the abstraction.

As for liveness-like properties, there are several notable works. McMillan's work on using compositional methods for LTL liveness properties [91] was applied to parametric liveness verification of the FLASH coherence protocol [93]. Using SMV, the user can

<sup>&</sup>lt;sup>1</sup>CTL\* is a logic that is a superset of both CTL and LTL.

automatically generate a sound abstraction, and then use lightweight theorem-proving commands for concretizing additional caches or proposing user-devised noninterference lemmas, based on counter example analysis. Although [93] focuses on a proof of safety, the same framework was used to show that whenever the directory is in the pending state, it is eventually not pending [94]. McMillan's proof relies on a handful of lemmas and fairness assumptions, designed and proven within SMV.

Fang et al. proposed an interesting technique called invisible ranking [56] which attempts to automatically guess ranking functions to prove response properties. The associated proof obligations (from [88]) are decided using some small-model theorems (conditions under which it is sufficient to check some property on only a small instantiation of the parameterized system) and BDD based methods for proposing invariants for the parameterized system. The authors have previously use what they refer to as counter abstraction for parameterized liveness verification [102]. Here, liveness of parameterized mutual exclusion protocols is established by an abstraction that maps counter variables to have a range of  $\{0, 1, \infty\}$ .

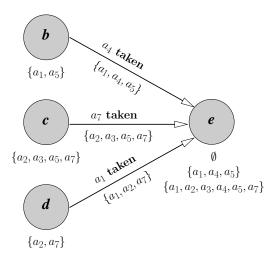

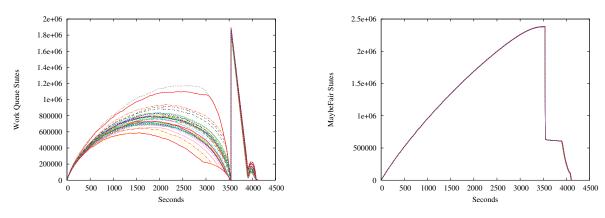

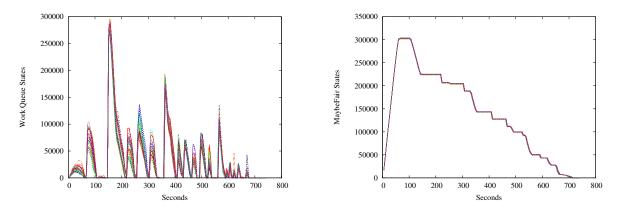

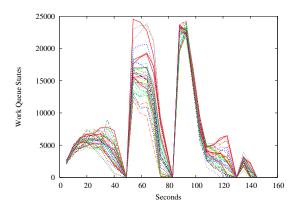

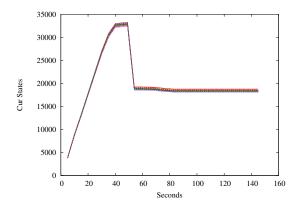

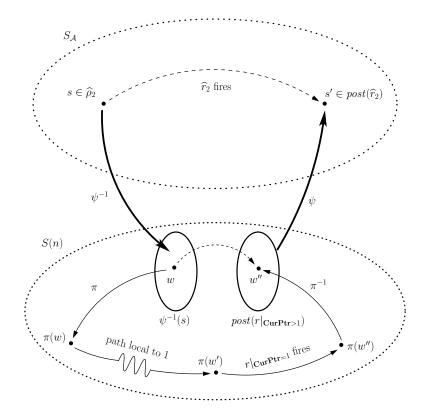

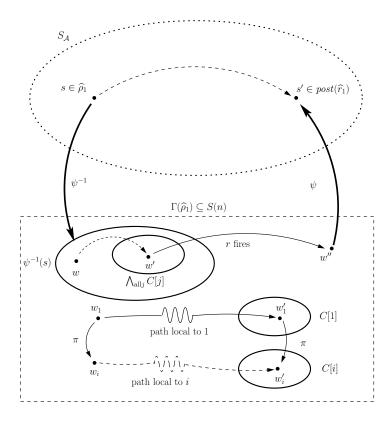

Baukus et al. employ WS1S (Weak Second-order theory of 1 successor — a decidable second-order logic) to perform liveness verification of parameterized systems [17], and verify response properties for the German protocol as a case study [18]. Like our approach, human effort is required, to select both abstract predicates and ranking predicates needed to create an appropriate abstraction. The complexity of deciding WS1S is well-known to be super-exponential, hence scalability of this approach seems unlikely. It is unclear if WS1S is expressive enough to model array variables indexed by the parametric type and with values over the parametric type. Such variables appear in the  $\text{Mur}\varphi$  description of the Flash protocol.