# SHARED INSTRUCTION-SET EXTENSIONS FOR SOFT MULTIPROCESSOR SYSTEMS IMPLEMENTED ON FIELD-PROGRAMMABLE GATE ARRAYS

by

Erin Johnston

BASc, The University of British Columbia, 2010

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE COLLEGE OF GRADUATE STUDIES

(Electrical Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

(Okanagan)

December 2012

© Erin Johnston, 2012

#### Abstract

Soft-core embedded systems implemented on FPGAs offer a high level of flexibility. Application specific customizations can be added in the form of extensions to the processor's regular instruction-set. These custom instructions benefit run-time performance, but come at the cost of increased resource usage. Reducing the overall FPGA area required to implement a system will decrease static power consumption and allow a smaller, cheaper device to be used. There is a constant effort to reduce area and power consumption while maintaining performance benefits attained through customizations.

This thesis presents a new architecture to share custom instruction units among multiple processors in a system. This implementation allows run-time performance benefits to be maintained while decreasing the overall resource usage. The shared architecture is implemented using an arbitrator to determine processor access to each custom instruction in a set. Custom instruction inputs and outputs are controlled using additional multiplexors and selection hardware. Results for a sample system using fine-grained custom instructions show that sharing can reduce the implementation area by up to 24% with minimal impact to the critical path delay. This reduction remains high at 19% for a coarse-grained case study of an encryption algorithm called SHA.

The custom instruction configuration depends on the application being performed. A benchmark generator and simulator are also developed to evaluate candidates for custom instruction implementation and efficiently explore the design space. The overall run-time performance of the candidate systems can also be evaluated using these tools. The simulator can also be used with an input trace to determine cycle accurate run-time performance for a real application, without requiring the entire system to be designed and implemented in hardware. The simulator shows up to 53% run-time improvement for a shared fine-grained system over a system with no custom instructions. Hardware run-time results for the coarsegrained case study improve run-time up to 13.5% over a system with no custom instructions.

# **Table of Contents**

| Abstract                             | ii  |

|--------------------------------------|-----|

| Table of Contents                    | iii |

| List of Tables                       | vi  |

| List of Figures                      | vii |

| List of Abbreviations                | X   |

| List of Operation Symbols            | xi  |

| Acknowledgements                     | xii |

| 1 Chapter: Introduction              | 1   |

| 1.1 Background Information           | 1   |

| 1.1.1 Market Trends                  | 1   |

| 1.1.2 Field-Programmable Gate Arrays | 3   |

| 1.1.3 Instruction-Set Extensions     | 6   |

| 1.1.3.1 Overview                     | 6   |

| 1.1.3.2 CAD for ISEs                 | 7   |

| 1.1.3.3 Benefits of ISEs             | 12  |

| 1.1.4 Multi-core Systems             | 14  |

| 1.2 Research Objectives              | 15  |

| 1.3 Previous Work                    | 16  |

| 1.3.1 Shared Fabric                  | 18  |

| 1.3.2 Shared Fixed Blocks            | 19  |

| 1.4 Thesis Organization              | 21  |

| 2      | Ch                                                         | apter: Shared Instruction Architecture                                                                                                                                                                                        | 22                         |

|--------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|        | 2.1                                                        | Proposed Solution                                                                                                                                                                                                             | 22                         |

|        | 2.2                                                        | Implementation Overview                                                                                                                                                                                                       | 24                         |

|        | 2.3                                                        | Implementation Details                                                                                                                                                                                                        | 25                         |

|        | 2.                                                         | 3.1 Front-End Sharing Hardware                                                                                                                                                                                                | 28                         |

|        | 2.                                                         | 3.2 Back-End Sharing Hardware                                                                                                                                                                                                 | 31                         |

|        | 2.4                                                        | Custom Instructions                                                                                                                                                                                                           | 32                         |

|        | 2.                                                         | 4.1 Fine-Grained Instructions                                                                                                                                                                                                 | 32                         |

|        |                                                            | 2.4.1.1 Experimental Framework                                                                                                                                                                                                | 37                         |

|        |                                                            | 2.4.1.2 Varied Processor Resource Usage and Critical Path Delay                                                                                                                                                               | 38                         |

|        |                                                            | 2.4.1.3 Fixed Processor Resource Usage and Critical Path Delay                                                                                                                                                                | 42                         |

|        | 2.                                                         | 4.2 Coarse-Grained Instructions                                                                                                                                                                                               | 44                         |

|        | 2.5                                                        | Summary                                                                                                                                                                                                                       | 46                         |

|        |                                                            |                                                                                                                                                                                                                               |                            |

| 3      | Ch                                                         | apter: Simulating Run-time Behaviour                                                                                                                                                                                          | 47                         |

| 3      | <b>Ch</b> 3.1                                              | Benchmark Generator                                                                                                                                                                                                           |                            |

| 3      |                                                            |                                                                                                                                                                                                                               | 48                         |

| 3      | 3.1                                                        | Benchmark Generator                                                                                                                                                                                                           | 48                         |

| 3      | 3.1                                                        | Benchmark Generator  Run-Time Simulator  Fine-Grained Run-Time Results                                                                                                                                                        | 48                         |

| 3      | 3.1<br>3.2<br>3.3                                          | Benchmark Generator  Run-Time Simulator  Fine-Grained Run-Time Results                                                                                                                                                        | 48<br>51<br>53             |

| 3<br>4 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                            | Benchmark Generator  Run-Time Simulator  Fine-Grained Run-Time Results  Processor and Instruction Utilization                                                                                                                 | 48<br>51<br>53             |

|        | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                            | Benchmark Generator  Run-Time Simulator  Fine-Grained Run-Time Results  Processor and Instruction Utilization  Summary                                                                                                        | 48<br>51<br>53<br>55       |

|        | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>Ch                      | Benchmark Generator  Run-Time Simulator  Fine-Grained Run-Time Results  Processor and Instruction Utilization  Summary  apter: Coarse-Grained Case Study                                                                      | 48<br>51<br>53<br>55<br>57 |

|        | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br><b>Ch</b><br>4.1<br>4.2 | Benchmark Generator  Run-Time Simulator  Fine-Grained Run-Time Results  Processor and Instruction Utilization  Summary  sapter: Coarse-Grained Case Study  Secure Hash Algorithm (SHA)                                        | 48<br>51<br>53<br>55<br>57 |

|        | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br><b>Ch</b><br>4.1<br>4.2 | Benchmark Generator  Run-Time Simulator  Fine-Grained Run-Time Results  Processor and Instruction Utilization  Summary  sapter: Coarse-Grained Case Study  Secure Hash Algorithm (SHA)  Coarse-Grained Custom Instruction-Set | 48495153555757             |

| 4.3.2     | Coarse-Grained Run-Time Results                        | 65 |

|-----------|--------------------------------------------------------|----|

| 4.3.3     | Processor and Instruction Utilization                  | 70 |

| 4.4 S     | Summary                                                | 71 |

| 5 Chap    | ter: Conclusion                                        | 73 |

| 5.1 L     | imitation of the Work                                  | 75 |

| 5.2 F     | Future Work                                            | 76 |

| 5.3 L     | List of Contributions                                  | 77 |

| Reference | es                                                     | 78 |

| Appendi   | ces                                                    | 82 |

| Append    | lix A - Fine-Grained Custom Instruction Implementation | 82 |

| Append    | lix B - Case Study Implementation                      | 85 |

| B.1       | SHA Application                                        | 85 |

| B.2       | Coarse-Grained Custom Instruction Implementation       | 87 |

|           |                                                        |    |

# **List of Tables**

| Table 1. | One-hot to binary priority encoder truth table for a 12 processor system       | 30 |

|----------|--------------------------------------------------------------------------------|----|

| Table 2. | Attributes of custom instructions assumed when generating the custom           |    |

|          | instruction-set.                                                               | 33 |

| Table 3. | Resource usage for fine-grained systems sharing one custom instruction unit    | 38 |

| Table 4. | Critical path delay for systems with varying cores sharing one custom          |    |

|          | instruction unit. Each custom instruction unit has 9 fine-grained instructions | 41 |

# **List of Figures**

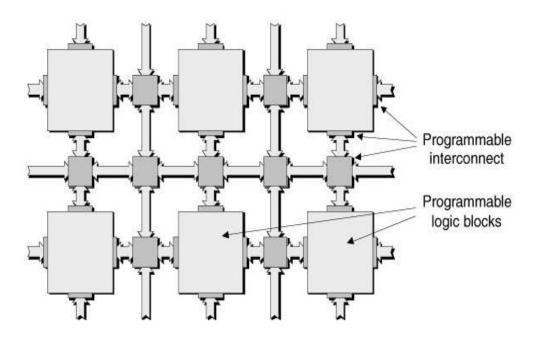

| Figure 1. FPGA island style architecture [5].                                       | 4  |

|-------------------------------------------------------------------------------------|----|

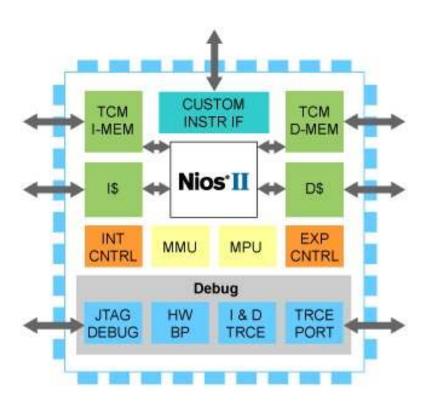

| Figure 2. Nios II soft-core processor [10]                                          | 5  |

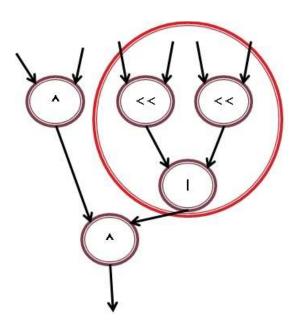

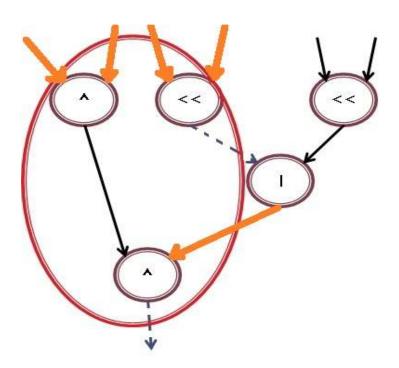

| Figure 3. Directed acyclic graph showing custom instruction selection.              | 8  |

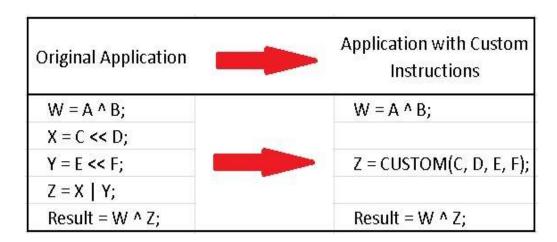

| Figure 4. Application code replaced with single custom instruction call.            | 9  |

| Figure 5. Custom instruction convexity and register file constraint.                | 10 |

| Figure 6. Software vs custom instruction parallelism.                               | 13 |

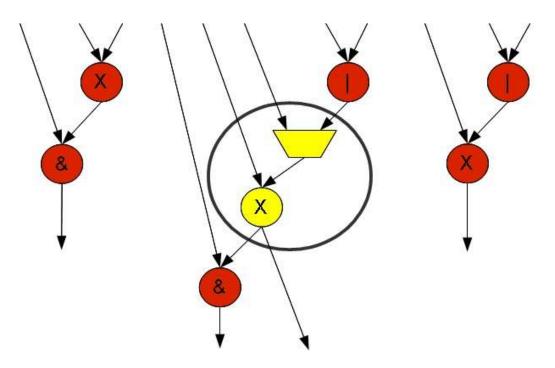

| Figure 7. Shared logic between multiple custom instructions.                        | 17 |

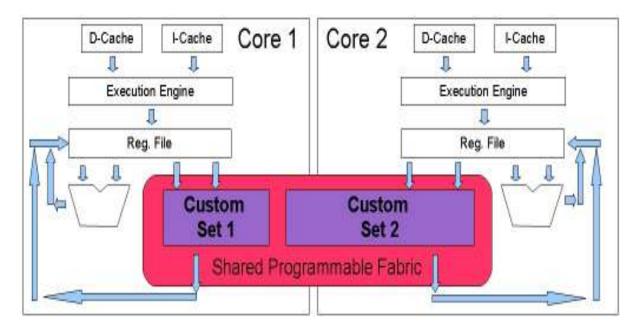

| Figure 8. Shared programmable fabric architecture.                                  | 18 |

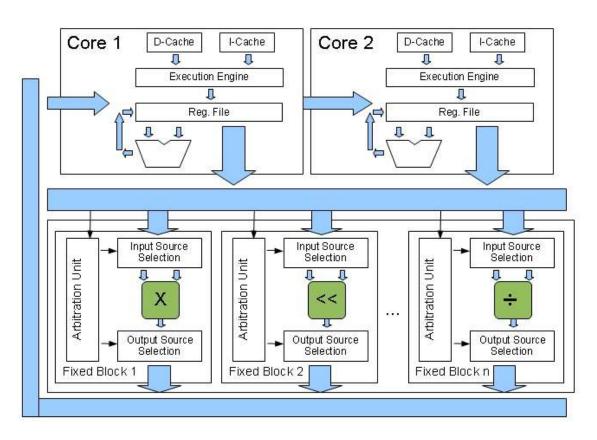

| Figure 9. Shared fixed block architecture.                                          | 20 |

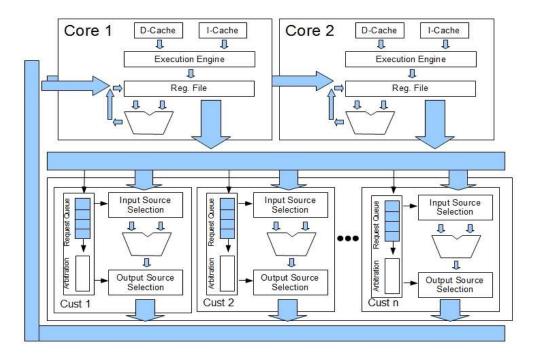

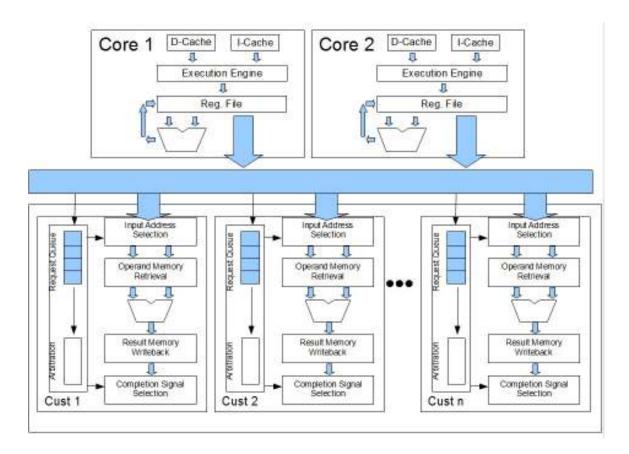

| Figure 10. Proposed architecture with instruction-set extensions shared between two |    |

| cores                                                                               | 23 |

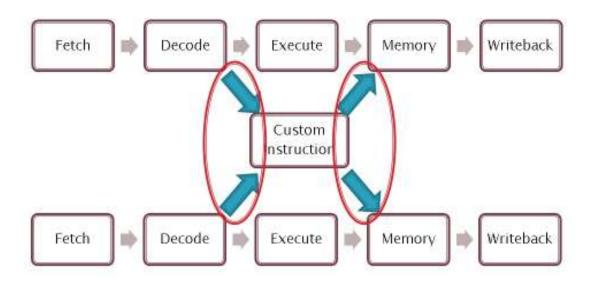

| Figure 11. Shared custom instruction-set extension pipeline.                        | 26 |

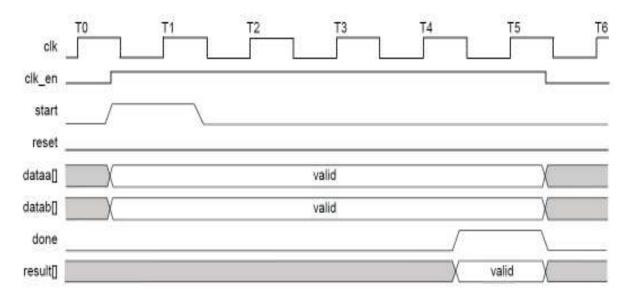

| Figure 12. Multi-cycle custom instruction timing diagram [35]                       | 28 |

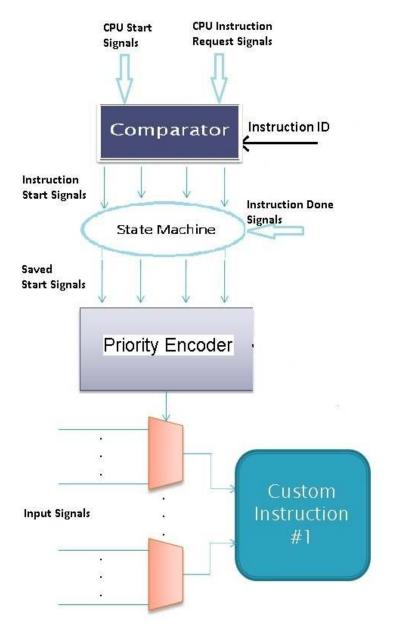

| Figure 13. Front-end sharing hardware block diagram.                                | 29 |

| Figure 14. Back-end sharing hardware block diagram.                                 | 31 |

| Figure 15. Average custom instruction shape and layout.                             | 35 |

| Figure 16. Set of nine custom instructions used for the proposed architecture       | 36 |

| Figure 17. Execute phase timing for custom instruction.                             | 40 |

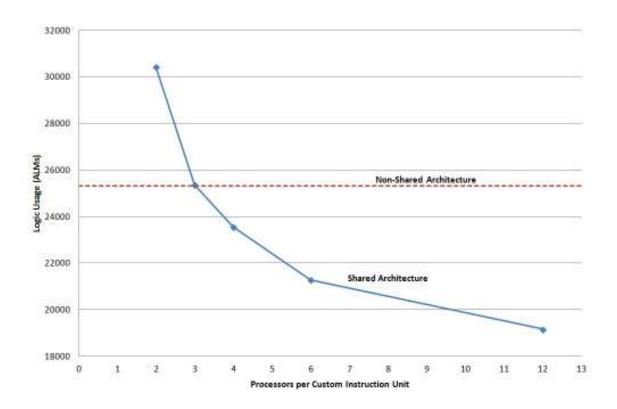

| Figure 18. Resource usage for a system with 12 cores and with varying degrees of    |    |

| sharing. Each custom-instruction unit has 9 fine-grained instructions.              | 42 |

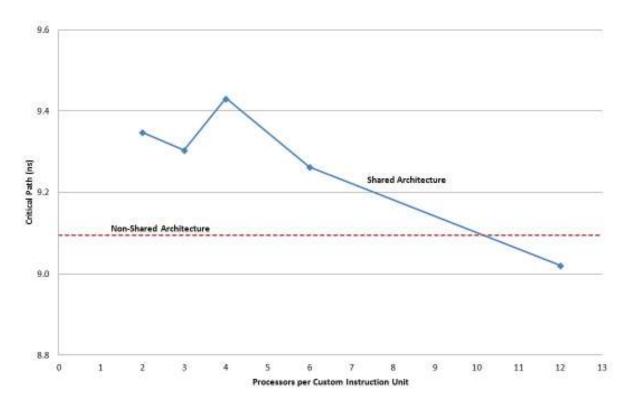

| Figure 19 | Critical path delay for a system with 12 cores and with varying degrees of      |    |

|-----------|---------------------------------------------------------------------------------|----|

|           | sharing. Each custom-instruction unit has 9 fine-grained instructions.          | 44 |

| Figure 20 | Proposed architecture for coarse-grained instruction-set extensions shared      |    |

|           | between two cores.                                                              | 45 |

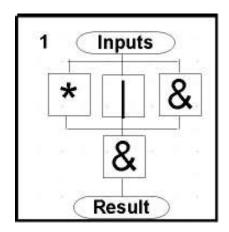

| Figure 21 | . Four operation custom instruction requiring 11 cycles in software or 2 cycles |    |

|           | in hardware.                                                                    | 49 |

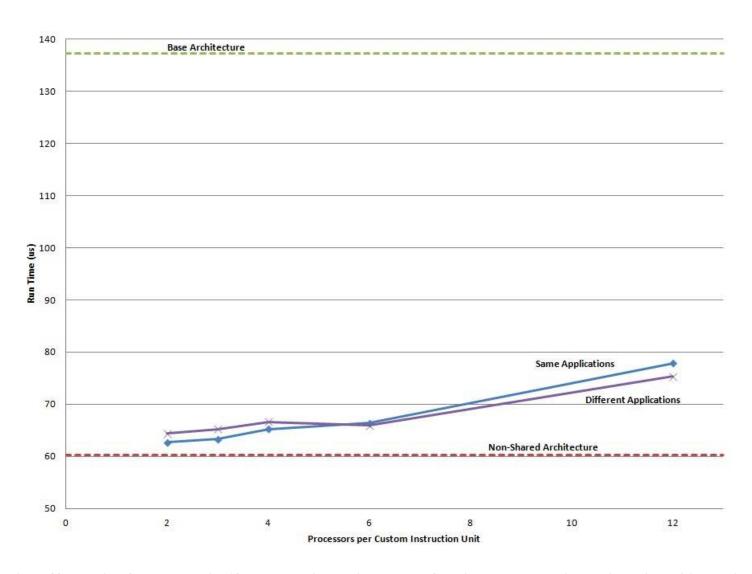

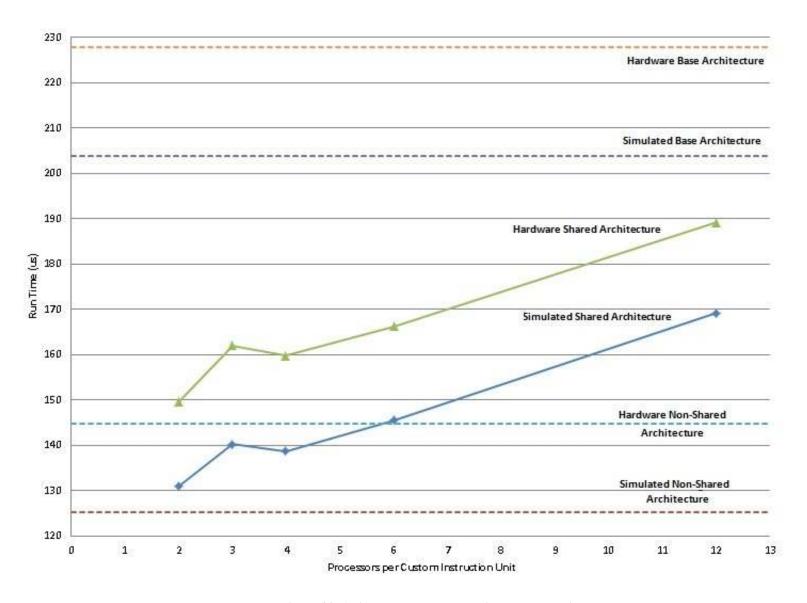

| Figure 22 | 2. Run-time for a system with 12 cores and with varying degrees of sharing.     |    |

|           | Each custom instruction unit has 9 instructions.                                | 52 |

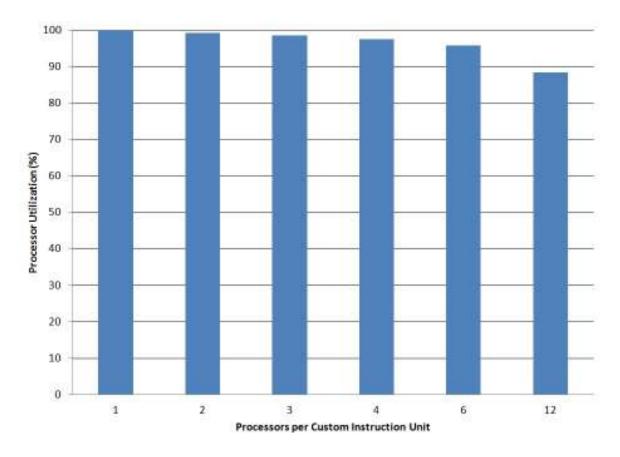

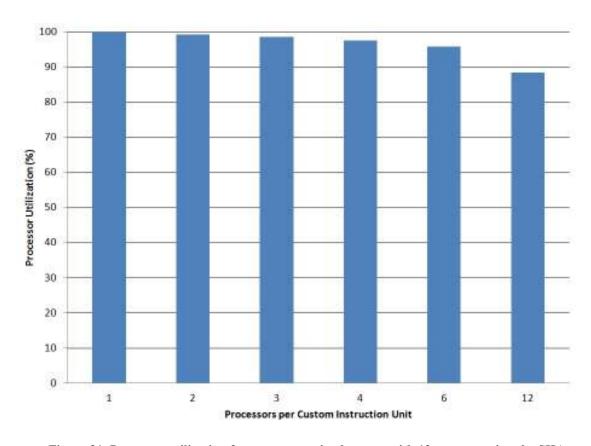

| Figure 23 | Processor utilization for a fine-grained system with 12 cores running the       |    |

|           | same application with varying degrees of sharing.                               | 54 |

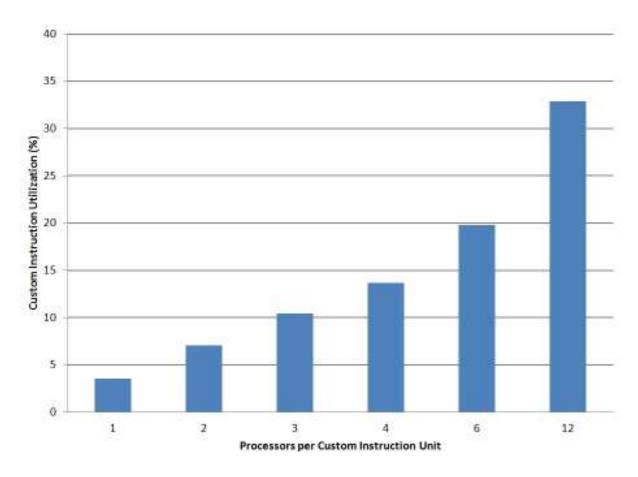

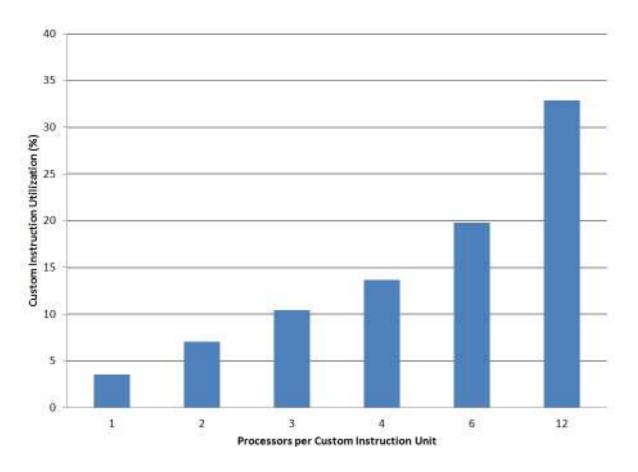

| Figure 24 | Custom instruction utilization for a fine-grained system with 12 cores          |    |

|           | running the same application with varying degrees of sharing.                   | 55 |

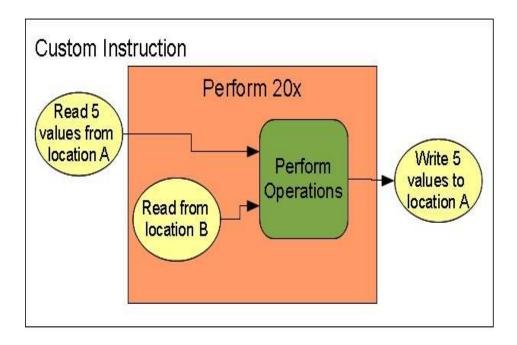

| Figure 25 | . Coarse-grained SHA custom instruction operation.                              | 59 |

| Figure 26 | . Resource usage for a system with 12 cores and with varying degrees of         |    |

|           | sharing. Each custom instruction unit has 4 coarse-grained instructions         | 60 |

| Figure 27 | Critical path delay for a system with 12 cores and with varying degrees of      |    |

|           | sharing. Each custom instruction unit has 4 coarse-grained instructions         | 61 |

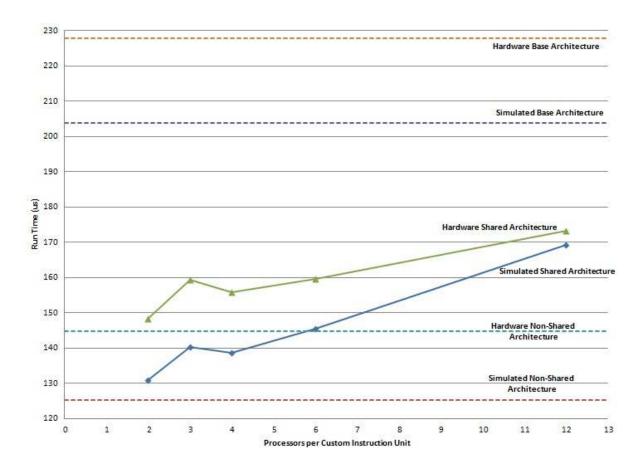

| Figure 28 | . Modelsim waveform used to determine application trace.                        | 64 |

| Figure 29 | . Hardware and simulated run-time for a system with 12 cores and with           |    |

|           | varying degrees of sharing. Each custom instruction unit has 4 instructions     | 66 |

| Figure 30 | . Adjusted hardware and simulated run-time results.                             | 69 |

| Figure 31 | . Processor utilization for a coarse-grained system with 12 cores running the   |    |

|           | SHA encryption algorithm with varying degrees of sharing.                       | 70 |

| Figure 32 | . Custom instruction utilization for a coarse-grained system with 12 cores |  |

|-----------|----------------------------------------------------------------------------|--|

|           | running the SHA encryption algorithm with varying degrees of sharing       |  |

## **List of Abbreviations**

ALM Adaptive Logic Module

ALU Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

CAD Computer Aided Design

DMA Direct Memory Access

FIPS Federal Information Processing Standard

FPGA Field-Programmable Gate Array

GPP General-Purpose Processor

GPU Graphics Processing Unit

HAL Hardware Abstraction Layer

HDL Hardware Description Language

IP Intellectual Property

ISE Instruction-Set Extension

MtM More than Moore

NIST National Institute of Security and Technology

NRE Non-Recurring Engineering

RISC Reduced Instruction-Set Architecture

SHA Secure Hash Algorithm

SIMD Single Instruction, Multiple Data

SoC System on Chip

TIE Tensilica Instruction Extension

# **List of Operation Symbols**

- X, \* Multiply

- + Add

- << Left-shift

- ^ Exclusive-or

- Logical or

- & Logical and

# Acknowledgements

First, I would like to thank my supervisor Dr. Peter Hallschmid. It is due to his encouragement that I endeavored to pursue graduate studies. He spurred my interest in research and asking endless questions.

I would like to thank my parents for encouraging me to keep learning. They have provided unlimited support and have always pushed me to do my best. Also, I would like to thank Ben, my roommates, and the rest of my family for their support and understanding while I completed my work.

This work was supported by NSERC and through hardware and software donations provided by Altera.

# 1 Chapter: Introduction

# 1.1 Background Information

Embedded systems are compact designs that implement specific applications or controls under a specific set of power, cost, speed, and/or reliability constraints. They usually comprise of one or many processing cores, on-chip memory, and input and output peripherals such as radio frequency transmitters, biosensors, and actuators. We encounter embedded systems every day in our cell phones, vehicles, navigation systems, MP3 players, and gaming consoles, to name a few. They can also be found in more complex devices such as aircraft guidance systems and medical devices. The cost and performance requirements for such devices are constantly evolving and pushing design to new levels.

#### 1.1.1 Market Trends

The need to produce faster, more complex systems is constantly competing with the desire to fit designs into a smaller area and to consume less power. According to Moore's law [1] which was stated in 1965, the number of transistors on an integrated circuit will double roughly every two years. This trend has held true since that time, with semiconductor companies striving to meet or beat this goal.

Moore's law has pushed more than just the limits of integrated circuit design and transistor technology. In order to keep up with the scaling designs, engineers require more sophisticated computer aided design (CAD) tools. Despite advancing tools, a productivity gap trend is still occurring. This means there is an increasing gap between design complexity and engineer productivity.

Along with increasing complexity and reduced productivity, increasing time-to-market demands also means less time for revisions and testing, forcing more engineers per design task. Extra manpower and technological demands can start to make development costs unreasonable.

One option for reducing costs is to develop using a system-on-chip (SoC). According to Chang et al [2], an SoC incorporates a programmable processor, on-chip memory, interfaces to peripheral devices, and predesigned and pre-verified accelerating modules. These modules are referred to as intellectual property (IP) components. SoCs are favorable because they can help reduce development time and, therefore, overall cost.

SoCs can be verified on field-programmable gate arrays (FPGAs) to ensure correct functionality before fabrication. However, SoCs still have high non-recurring engineering (NRE) costs associated with masks and fabrication, which according to Margarshack and Paulin [3] is the main explanation for the growth in FPGAs. The convenience of an SoC depends on the availability of the IP components and the ease of use of the design platform. This type of embedded system offers programmability which allows for a wider variety of applications. Starting with a base system that includes a processor and memory, IP components and programmed customizations can be added to a system to tailor it to an application or application domain. Using a programmable device gives the designer better control over the system customization.

A second approach is to use advanced design tools such that system customizations can be created in a high-level language. Using a higher level of abstraction keeps the designer removed from transistor-level intricacies. For example, programmable logic allows the designer to create customizations using a hardware description language (HDL).

Synthesis tools are then used to compile the HDL and translate it to board-level connections. The engineer must have knowledge of the hardware and logic, but is not required to design the actual layout. Using IP components raises the level of abstraction even higher by allowing the engineer to provide parameters and then automatically generate the component.

Despite the urgent need to mitigate the productivity gap, some industry trends have led to increases in the productivity gap such as the increased use of multiprocessor systems.

Although multiprocessor systems have led to another level of complexity to designs that further increases the productivity gap, work by Borkar [4] describes the reasoning and benefits behind the growing trend toward multiple cores. First, implementing multiple smaller processors can actually decrease the individual complexity and improve power performance over a single, large core. Also, it is easier to distribute the load and optimize for frequency on each processor.

## 1.1.2 Field-Programmable Gate Arrays

An FPGA is a programmable logic device that can be reconfigured after manufacturing. FPGAs are the most common form of programmable logic and can be configured to perform complex logical operations and even store results in memory blocks and registers. A typical island-style FPGA architecture is shown in Figure 1.

Figure 1. FPGA island style architecture [5].

Programmable logic blocks are surrounded by programmable interconnect or routing channels. Each of the logic blocks make up a small portion of the overall circuit. By connecting these blocks using the interconnect, a larger, more complex circuit can be formed.

FPGAs can be used instead of application-specific integrated circuits (ASICs) to implement highly customized embedded system designs. While ASICs are designed in much the same way as systems on FPGAs, ASICs have much higher NRE costs associated with fabrication. Zuchowsky et al [6] discuss how even though performance and density for ASICs still lead over FPGAs, the flexibility and time-to-market make FPGAs highly appealing. Two companies occupy the majority of the FPGA market: Altera [7] and Xilinx [8]. According to Altera [9], FPGAs offer a variety of advantages over ASICs such as a shorter time to market and lower non-recurring engineering costs. Much of the design effort and cost created by designing an ASIC are eliminated using an FPGA. They have a long product life and can be reprogrammed by the designer for testing and changing needs.

FPGAs are available that implement either hard or soft processing cores. A hard-core processor is a core implemented from a predefined block. This is a fixed resource and cannot be reprogrammed or customized after fabrication. A soft-core processor is a core implemented by programming the logic blocks of the FPGA to act as a microprocessor. It is a predesigned intellectual property core that is easily synthesized and highly flexible. Soft-core processors are found in many everyday systems and are undetected by the end user. They can be found in voice over IP systems, routers, electronic signs, security systems, and vehicles.

Figure 2. Nios II soft-core processor [10].

According to Tong et al [11], the three leading soft-core processor providers are Altera with the Nios II, Xilinx with the MicroBlaze and PicoBlaze, and Tensilica with the Xtensa. Figure 2 shows a Nios II core surrounded by design options including instruction and data cache, a memory management unit, and debug hardware. All three companies use reduced instruction-set computer (RISC) cores and have options for pre-made fixed hardware block customizations or user-defined hardware modules. Fixed block implementations include multipliers, barrel shifters, and dividers. Custom implementations change from system to system and are specific to the task being performed.

#### 1.1.3 Instruction-Set Extensions

#### **1.1.3.1** Overview

Embedded system customization can come in many different forms. On a customizability spectrum, soft-core systems implemented on FPGAs lie between general-purpose processors (GPPs) and fixed logic processors. GPPs are robust microprocessors that are flexible in their application, serving a wide array of tasks from computation to communication to display. ARM is a well-known producer of GPPs that are often found in cell phones, MP3 players, and game consoles [12]. GPPs are purchased and ready to use "off-the-shelf", but do not provide the performance of a customized processor. At the other end of the customizability spectrum lie fixed logic processors. These are complete microprocessors designed for one specific purpose. They offer high performance, but unlike a GPP are not portable to other tasks. Fixed-logic processors have extremely high NRE costs and require significant time to design and manufacture.

Soft-core systems implemented on FPGAs provide a tradeoff between the flexibility of a GPP and the performance of a fixed-logic processor. They can be designed or reconfigured for varying applications, but offer customizability through instruction-set extensions (ISEs). ISEs are a form of soft-processor customization in which the instruction-set can be extended with custom instructions tailored to an application or application domain. ISEs are not an entire custom processor, but rather additions to a base core. The customizability options described are certainly not the only options available, as works like that by Clark et al [13] blur the lines by combining GPPs with custom hardware.

Several companies offer processors configurable with ISEs: Stretch and the previously mentioned Altera, Xilinx, and Tensilica. Both Altera [7] and Xilinx [8] products require the user to define custom instructions using an HDL. Stretch [14] tools allow users to automatically create ISEs using only C/C++. Tensilica [15] allows developers to produce custom instructions in one of two ways. First, custom instructions can be defined by the user in the Tensilica Instruction Extension (TIE) language. The other option is to use the Xpress tool that will automatically generate custom instructions in the TIE language based on the application source code.

#### **1.1.3.2 CAD for ISEs**

ISEs can range in size and complexity from a few simple operations to an entire coprocessing unit. Custom instructions comprising of few operations are referred to as finegrained custom instructions. Fine-grained instructions use hard-coded values and inputs

passed to the custom instruction as operands. They are defined by selecting critical clusters

of operations from the application to be executed on the processor.

Larger ISEs are called coarse-grained custom instructions, and they often take the place of an entire function or application in software. Coarse-grained instructions often require a greater number of operands that can be hard-coded, passed to the custom instruction, or retrieved directly from memory. For both types, custom instructions are implemented in hardware as a single, complex instruction. For example, Figure 3 shows a directed acyclic graph representation of a small section of application code. Each node or vertex represents an operation, and each arrow or edge represents the operands associated with it. The encircled section of the graph shows a candidate for fine-grained custom instruction implementation.

Figure 3. Directed acyclic graph showing custom instruction selection.

The three selected operations in Figure 3 will be implemented in hardware, and all calls in the application following this pattern will be replaced with a single call to the custom instruction. Figure 4 is the application code represented by the directed acyclic graph in Figure 3.

After implementing the selected instructions in hardware, the three operations, shown on the left, in the original application are replaced with a single custom instruction call, shown on the right. The syntax for using the custom instruction will vary depending on the processor being used, but they are often a simple macro or function call. There are many works, such as that by Peymandoust et al [16], that not only select custom instructions from application source code, but also replace lines of code in the original application with calls to the custom instructions.

Figure 4. Application code replaced with single custom instruction call.

When evaluating candidate custom-instructions, the primary figure-of-merit is the speed increase gained by running the operations in hardware and the frequency of execution in the application. Unfortunately, not all candidate sets of instructions can be selected for implementation due to constraints imposed by the hardware. In particular, the processor's register file limits the number of inputs and outputs that can be used for any instruction, including custom instructions. Further, a sub-graph convexity constraint must also be adhered to as discussed in Atasu et al [17].

Figure 5 shows the same directed acyclic graph from Figure 3, but with a different set of encircled operations. This sub-graph is not a valid selection for custom instruction implementation for two reasons: it is not a convex sub-graph, and the register file constraints are violated. In the figure, the output from the *left-shift* becomes an input to the *or*, an operation that is not contained within the sub-graph. The output from the *or* then becomes an input to the *exclusive-or*, an operation that is again within the sub-graph. To satisfy the convexity constraint, the flow of operands within a custom instruction cannot leave the sub-graph and then re-enter. This selection also violates the most common register file constraints which allow two or four inputs and one output. In Figure 5, bold arrows represent inputs to the selection, and dashed arrows represent outputs. This custom instruction selection shows a total of five inputs and two outputs.

Figure 5. Custom instruction convexity and register file constraint.

Although obeying register file constraints is the easiest method to implementing custom instructions, it limits the performance gains achievable with larger custom instructions. One workaround is to access memory directly from within the custom instruction using direct-memory-access (DMA). This is useful for cases in which a much greater number of inputs or outputs are required than the register file will allow. Temporary inputs and outputs are not stored by the register file, but rather are kept within the custom instruction until the final outputs are produced.

A simpler method, that can be used when just a few extra inputs or outputs are needed, is to pipeline the custom instruction with additional custom instructions designed to read/write additional operands to/from the register file. For example, an instruction requiring four inputs and one output, but with a register file constraint of two inputs and one output, could use the first custom instruction call to load the first two inputs. These inputs are then saved within the custom instruction while a second custom instruction call is made that loads the next two inputs. This second call to the custom instruction then performs the operations, and the result can be returned at the end of its execution.

Although ISEs can result in significant performance gains, they come at the cost of increased area and static power. The impact of additional logic is especially important to consider for FPGA implementations in which even a small improvement in area could lead to a much cheaper part. Thus, with the addition of each new instruction, one must carefully consider the implications on resource usage and the predicted impact on run-time performance. In a multiprocessor system, both the performance benefits and area drawbacks are multiplied with the addition of each custom instruction.

#### 1.1.3.3 Benefits of ISEs

The impact of custom instruction implementation is reduced run-time and reduced dynamic power dissipation. By replacing a cluster of operations in the application with one custom instruction call, execution cycles are saved in several ways. First, the Von Neumann bottleneck [18], caused by the latency in transfers between the processor and memory, is reduced. Even the fastest processors are limited by this transfer rate and spend time stalled, waiting for data and instructions. ISEs require fewer fetches from instruction memory or cache thus reducing the bottleneck. Only one instruction call is required to perform an entire set of operations.

ISEs also save execution cycles when parallelism is exploited. Parallelism is the ability of a system to execute multiple tasks at the same time. Instruction-level parallelism is the execution of multiple instructions at once. Only instructions that do not depend on each other's results can be executed in parallel. According to Callahan and Wawrzynek [19], reconfigurable systems such as those implemented on an FPGA can easily capitalize on the benefits of thread-level parallelism. Sequential programs are reduced in length when basic blocks are converted to a hardware implementation and multiple instructions execute at the same time.

Custom instructions employ a form of instruction-level parallelism to reduce run-time over the original application. For example, Figure 6 shows a section of code that is implemented sequentially in software. When implemented as a custom instruction in hardware, the first three levels can be executed at the same time, since one does not depend on the result from another. This improves run-time which in turn reduces overall power consumption.

| Level | Software      | Hardware  |               |           |

|-------|---------------|-----------|---------------|-----------|

| 1     | c = a * b     | c = a * b | d = a   b     | e = a & b |

| 2     | d = a   b     |           | x = c & d & e |           |

| 3     | e = a & b     |           |               |           |

| 4     | x = c & d & e |           |               |           |

Figure 6. Software vs custom instruction parallelism.

The addition of custom instructions can also benefit the system in other ways such as requiring a reduced instruction memory due to a smaller application code. Also, the use of constants in an application can be a challenge for the processor if the constant length cannot be represented properly in an instruction op-code. The value must either be pulled from a literal pool, or the operation must be broken down into multiple instructions. Constants in custom instructions, however, are implemented in the hardware.

Finally, ISEs affect the number of registers and the number of accesses to the register file required. Energy is saved when operations are combined into a single custom instruction and fewer register file accesses are needed. Assembly code is also generated much easier during program compilation when custom instructions are used. First, there are fewer instructions and lines of code to compile. Second, "register pressure" is reduced during register allocation because fewer registers are needed to complete the same computation. This is because many of the temporary values normally needed now reside within the custom instruction.

### 1.1.4 Multi-core Systems

As mentioned in Section 1.1.1, there is a growing trend towards multi-core systems. According to Wolf [20], strict performance requirements and power and cost constraints have pushed engineers to develop multiprocessor systems. In multiprocessor systems, performance benefits are seen as each processor is customized for its application. Rather than using one large processor to perform a variety of tasks, multiple cores can be used to execute specific tasks.

Compared to separate implementations, multiprocessor systems on a single chip can reduce cost and size by providing the opportunity for resource sharing among cores.

Resources are better utilized by sharing, and costly space can be eliminated or freed up for other custom accelerators. Although multiprocessor systems are often used with GPPs, they are easily implemented using soft-cores on FPGAs. Also, multi-core systems on FPGAs can exploit the benefits of customizability and resource sharing.

When applied to multi-core architectures, ISEs introduce heterogeneity. The instruction-set of each core is tailored to its assigned task, thus maximizing performance and reducing dynamic power. Heterogeneous multi-core architectures of this type can be created with low non-recurring costs and high flexibility when implemented on a programmable fabric. Biswas et al [21] [21] show that, with just one large ISE, the average application speed increase is 1.4 times while the energy savings can reach up to 40%. These savings are even more significant when applied to a multiprocessor system, where each core has the opportunity to use custom instructions.

### 1.2 Research Objectives

The goal of this research is to evaluate the impact of resource sharing, in the form of ISEs, among customizable processors implemented on an FPGA. The effects on FPGA area and system run-time will be monitored. This thesis will focus on two types of ISEs: fine-grained custom instructions and coarse-grained custom instructions. Both types will be considered in the evaluation of customizable processors.

A method will be determined for increasing multiprocessor system performance through custom instructions while meeting strict area constraints. The design space will be thoroughly explored to increase performance and reduce area for a wide range of applications. The focus will be on resource sharing in soft-core multiprocessor systems that promote flexibility and easily allow for modifications.

To accomplish these objectives, a new architecture must be developed that will maintain run-time benefits incurred by custom instructions, but will also decrease the FPGA resource usage. The design should be developed using concepts that apply to any soft-core multiprocessor system.

More specifically, this research has two main objectives:

- An architecture will be proposed that maintains the performance benefits of ISEs

while reducing implementation area and power consumption to lower device

costs.

- 2. The system will be fully evaluated to assess both the benefits and drawbacks concerned with run-time, area, and power. The solution will be compared to previous works to ensure it is original and makes a contribution to custom computing.

#### 1.3 Previous Work

Previous works have defined algorithms to select custom instructions for an application or application domain [22] [23] [24] [25] [26]. These algorithms often require parameters regarding register file constraints to enumerate possible custom instruction candidates. Then, based on performance benefits and frequency of use, candidates are selected for custom instruction implementation. Some algorithms aim for smaller instructions with greater frequency of use, while others try to find the largest grouping possible assuming this will produce the greatest performance benefit. Chen et al [24] and Yu and Mitra [25] focus mainly on the speed of the algorithm in an attempt to reduce design time.

Algorithms to select shared ISEs for multiprocessor systems are not within the scope of this research; however, future work is needed in this area to define an algorithm specific to multi-core systems. It would also be beneficial for algorithms to be developed capable of selecting custom instruction candidates across multiple similar applications. To date, few of the previous works have delved into multi-core systems and none have proposed architectures to share custom instructions.

Previous works by Lin and Fei [27], Dinh, Chen, and Wong [28], and Zuluaga and Topham [29] developed methods for sharing logic between more than one custom instruction for a single processor. In the directed acyclic graph representation of a sample program in Figure 7, the operations depicted on the left and the operations depicted on the right share common logic, the multiplier. The instruction in the center has an added multiplexor to combine the two sets of operations, reducing the overall implementation area.

These works differ from the proposed solution in that this is designed for sharing operations within a custom instruction unit for a single processor system. Instead, it is proposed that entire instructions be shared between multiple processors.

Figure 7. Shared logic between multiple custom instructions.

Lam and Srikanthan [30] developed an efficient method for determining the area of custom instruction candidates before implementation. Results show that the area estimates are within 8% of the actual implementation size. The usefulness of this algorithm is its ability to rule out costly custom instruction candidates thus leaving space for other, more area-efficient, instructions. Future work could have this solution to the area constraint problem combined with the proposed approach to provide even greater area savings.

Two other works [31] [32] propose architectures for sharing fabric and sharing fixed blocks, respectively, among multiprocessor systems. These papers and how they differ from the proposed solution to the area constraint and performance problems are described in more detail in Sections 1.3.1 and 1.3.2.

#### 1.3.1 Shared Fabric

Chen and Mitra [31] propose an architecture for multi-core systems in which more than one core can share a programmable fabric for implementing custom instructions. In doing so, cores that can benefit from a large number of custom instructions can have a greater share of the fabric. This work focuses on improving performance through better system organization. It does not reduce the overall area, but simply makes better use of the available space.

Figure 8. Shared programmable fabric architecture.

Consider an example non-shared, two processor system where each core may place up to four custom instructions on its own programmable fabric. For some applications, it may be beneficial for one processor to implement three custom instructions and the other to implement five custom instructions. This problem is solved by sharing the fabric as shown in Figure 8. Although each processor can still only access its own custom instructions, space for eight custom instructions can now be divided unequally among the processors.

This approach differs from the proposed method in that it has two systems sharing space for their custom instructions rather than having actual custom instructions shared. This approach does not reduce the size of the system, but rather it allows one core to make use of space unused by other cores.

#### 1.3.2 Shared Fixed Blocks

Another method for reducing resource-usage in multiprocessor systems was explored by Sheldon et al [32]. In this paper, fixed hardware blocks are shared, or "conjoined" among multiple processors to minimize area in FPGAs. Results showed that, for two processor systems, area can be reduced by an average of 16% while causing less than 1% cycle-count overhead. The focus of this work was strictly on fixed hardware blocks such as multipliers and barrel shifters.

To select the combination of shared and non-shared fixed hardware blocks for implementation, the knapsack problem as described by Kellerer et al [33] is used. The knapsack problem describes an area constraint and a set of implementations greater than the allowed area. An algorithm is used to select which combination will produce the most benefit by being implemented in the constrained area.

To be more specific, this is a disjunctively constrained knapsack problem, meaning that if one choice is selected for implementation, others may be eliminated. For example, choosing to implement an individual multiplier for core 1 and an individual multiplier for core 2 can eliminate the option of having a shared multiplier between cores 1 and 2.

Figure 9 is a block diagram of the shared fixed hardware block architecture. It is similar in concept to the ideas presented in this thesis, however, fixed functional units are shared rather than custom instructions. Further, the proposed architecture is never synthesized or physically implemented on an FPGA. This means that the area results provided are an estimate based on the removal of individual blocks. Also, the additional sharing hardware such as multiplexors and an arbitration unit are not described in detail or estimated in size.

Figure 9. Shared fixed block architecture.

The work presented in this thesis differs from previous work in that it focuses on sharing ISEs. Although extra hardware is required for arbitration and signal selection in a system with sharing, the area overhead is overcome through the reduction in custom instruction implementations. Aside from reducing the required FPGA size, the advantage to resource sharing for ISEs is that the area made available can be used to implement additional custom instructions thus leading to further performance gains. This thesis clearly outlines the hardware overhead required for custom instruction sharing and provides run-time results that take any critical path penalties into account.

### 1.4 Thesis Organization

This thesis is organized into five chapters. Chapter 1 has outlined the motivation for this work, research objectives, and previous work. Chapter 2 describes the shared instruction architecture. It discusses two types of custom instructions and provides resource usage and critical path delay results. A simulator used to determine run-time operation and results is presented in Chapter 3 along with a benchmark generator used to quickly explore the design space. This simulator is verified with a case study in Chapter 4. Critical path delay and resource usage results are provided for the case study. Chapter 5 is a summary of all results and conclusions. Future work stemming from this research is also discussed.

# 2 Chapter: Shared Instruction Architecture

In this chapter, the shared instruction architecture is presented. A description of the proposed solution is provided in Section 2.1. Section 2.2 gives a general overview of the architecture. It describes the flow, from a processor's request to use the custom instruction, until the result is produced. In Section 2.3, finer details of the implementation are presented. The two types of custom instructions, fine-grained and coarse-grained, are introduced, and a design example is analyzed for resource usage and critical path delay in Section 2.4. A summary of all findings and key points from this chapter is discussed in Section 2.5.

## 2.1 Proposed Solution

To satisfy area and power constraints while maintaining increased performance, an architecture is proposed in which ISEs are shared between two or more cores. As shown in the two-core example in Figure 10, each processor core retains its own arithmetic logic unit (ALU), but shares a set of ISEs. In the case that a custom instruction is simultaneously requested by more than one core, the requests are queued and then executed consecutively via an arbitrator. A small amount of additional hardware is added to each processor to map the inputs and outputs to and from the correct core.

Figure 10. Proposed architecture with instruction-set extensions shared between two cores.

ISE sharing can benefit the system in one of two ways depending on the relative importance of cost versus run-time performance. First, the resources made available by allowing custom instruction sharing can be used to add additional custom instructions, thus leading to further run-time performance gains. Alternatively, a smaller FPGA can be used to implement the same design, if custom instructions are shared, thus reducing per part cost and static power dissipation.

In order to take advantage of custom instruction sharing, several challenges must be addressed. First, an architecture must be defined that provides run-time instruction sharing without significantly increasing critical path delay. There must be a way to evaluate each system and a way to test its limits under a variety of run-time conditions. Second, there must be compiler support such that ISEs are selected to maximize performance and to reduce implementation area through sharing opportunities.

The research presented in this thesis focuses on the first of these challenges. More specifically, an architectural framework is proposed in which custom instructions are shared between processors. This framework is implemented using Nios-II soft processors in a shared instruction-memory arrangement. The system was specified in a hardware description language (HDL) in a scalable way such that hardware can be easily generated for any number of processors, any degree of processor sharing, and any number of custom instructions. To the best of the author's knowledge, this is the only work that addresses the sharing of custom instructions between processors.

# 2.2 Implementation Overview

The proposed architecture allows processor cores to access a shared set of custom instructions, as was shown in Figure 10. In the normal operation of a single core, operands from the register file can be directed to either the ALU or the custom instruction unit. In the proposed architecture, inputs to the custom instruction unit are multiplexed to allow for operands to be provided by multiple cores. Multiplexing is controlled by an arbitration unit that also controls to which core the output is forwarded.

The arbitration unit is comprised of priority selection circuitry and a mechanism for queuing cores. When multiple cores request the use of an instruction simultaneously, the arbitrator determines which core will have access to the custom instruction based on a fixed priority scheme. All other processors in the queue are stalled until the instruction is released, after which the core with the next highest priority is allowed to proceed.

This architecture is designed for systems where multiple processors are running the same or similar applications. This allows for custom instructions to be selected that can be used by and can benefit all the processors in a system. The main goal is to reduce the overall FPGA implementation area; a reduced implementation area requires a smaller, less costly FPGA. Alternatively, the area saved by sharing could be used to implement additional custom instructions that will further benefit the performance of the system. While trying to improve the density of the design, it is important that run-time performance is still improved over a system that does not use custom instructions to execute the application. In Chapters 3 and 4, run-time results are provided for the proposed architecture for fine-grained and coarse-grained ISEs, respectively. A comparison is made to the run-time of architectures that do not share custom instructions.

# 2.3 Implementation Details

The proposed architecture was implemented for a Stratix III FPGA using Nios-II/s soft processors. According to the Nios II Processor Reference Handbook [34], each Nios II/s core uses less than 700 adaptive logic modules (ALMs) of the 56,800 ALMs available on the Statrix III device. An ALM is the basic building block of programmable hardware in which the digital logic on some FPGAs is built. ALMs can have up to eight inputs and eight outputs used in several implementation combinations. Resource usage results will be determined in units of ALMs so that comparisons can be made fairly between all systems.

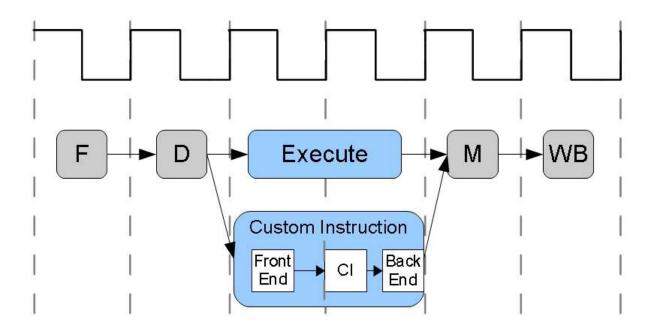

The Nios II/s core uses static branch prediction and can have up to a 64KB instruction cache. No data cache is available for this core. The core uses a five stage instruction pipeline comprised of *fetch*, *decode*, *execute*, *memory*, and *writeback*. During the *fetch* stage, instructions are retrieved from memory and the next program counter value is predicted. The *decode* stage then takes place to read the register file and create the datapath control signals. Next, the *execute* stage performs the decoded instruction. When the *execute* stage has finished, data is written to memory during the *memory* stage. Finally, the register file is updated in the *writeback* stage. Figure 11 depicts the new five-stage pipeline for a shared custom instruction-set architecture.

Figure 11. Shared custom instruction-set extension pipeline.

As for a single processor system, the custom instruction hardware replaces the regular execute stage performed by the arithmetic logic unit (ALU). For the proposed architecture, each processor retains its own ALU, but shares custom instruction units. The encircled areas on the figure represent the additional hardware required to implement sharing, which is the same regardless of the custom instruction unit. The custom instruction unit is like a "black box" that can be replaced with different instructions for each application.

In the proposed sharing architecture, all standard Nios II multi-cycle custom instruction signaling is maintained. These include the instruction *request ID*, two input operands, the *result* signal, the *start* signal, and the *done* signal. The *request ID* indicates which instruction the processor would like to execute. The *start* signal indicates a request has been made by the processor to execute a custom instruction. The *done* signal indicates that the custom instruction has finished executing and a valid result is available. The *start* and *done* serve as handshaking controls thus allowing instructions to take multiple clock cycles to execute.

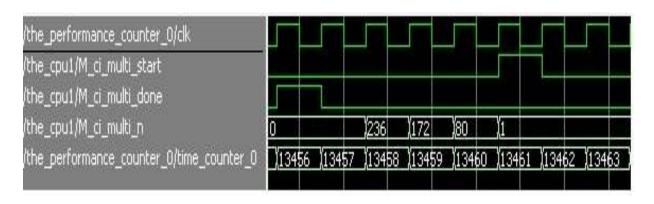

A multi-cycle custom instruction timing diagram is shown in Figure 12. The *start* signal is set high to indicate the processor's request for the custom instruction. At this time, the inputs must be valid and remain constant until the end of the custom instruction. When execution is complete, the *done* signal is set high by the custom instruction to indicate a valid *result* is waiting for the processor. The instruction *request ID* must also remain constant for the duration of the instruction. The processor uses this signal to select the correct *result* for the extended case where there are multiple instruction options.

Figure 12. Multi-cycle custom instruction timing diagram [35].

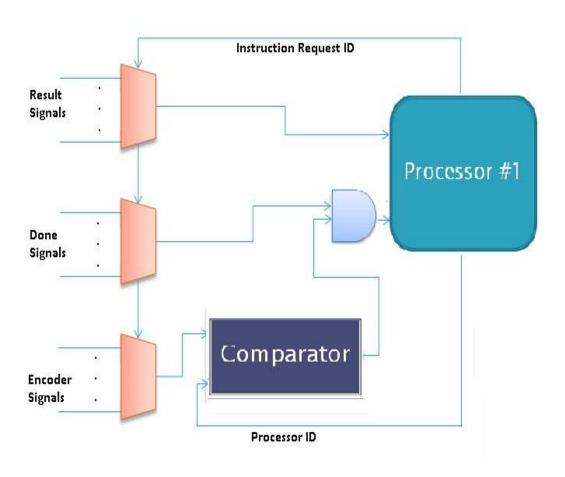

## 2.3.1 Front-End Sharing Hardware

The front-end of each custom instruction contains data multiplexers, a priority-encoder, and hardware to latch start signals from all processors. Because processors normally only hold the *start* signal high for one clock cycle as shown in Figure 12, the request must be queued thus preventing the request from being lost if the instruction is currently in-use. The *start* signal is only saved for a particular custom instruction if the processor's instruction *request ID* signal matches the instruction's id. This is performed by a comparator as shown in the block diagram depicting the front-end hardware in Figure 13. The saved *start* signal is released when the corresponding *done* signal matching the processor and instruction is received.

Figure 13. Front-end sharing hardware block diagram.

The saved *start* signals from all processors are connected to a priority encoder. A one-hot to binary encoder is used to give precedence to one processor when there are multiple requests. The truth table for such an encoder is given in Table 1 for a system with 12 processors. The output, or *select* signal, is determined based on the saved *start* signals from each processor, P0 through P11. If multiple processors are requesting the instruction, the processor with the lowest ID is given priority, and all other signals are ignored. The output from the encoder selects the correct input data which is fed into the custom instruction. This entire front-end set of components is required for each custom instruction to provide a fast and area-efficient mechanism for arbitration.

Table 1. One-hot to binary priority encoder truth table for a 12 processor system.

| P0 | P1 | P2 | Р3 | P4 | P5 | Р6 | P7 | Р8 | Р9 | P10 | P11 | Select |

|----|----|----|----|----|----|----|----|----|----|-----|-----|--------|

| 1  | х  | х  | х  | х  | х  | х  | х  | х  | х  | Х   | Х   | 0000   |

| 0  | 1  | х  | х  | х  | X  | х  | х  | х  | х  | х   | Х   | 0001   |

| 0  | 0  | 1  | х  | х  | х  | х  | х  | х  | х  | х   | х   | 0010   |

| 0  | 0  | 0  | 1  | х  | X  | х  | х  | х  | х  | х   | х   | 0011   |

| 0  | 0  | 0  | 0  | 1  | X  | х  | х  | х  | х  | х   | х   | 0100   |

| 0  | 0  | 0  | 0  | 0  | 1  | х  | х  | х  | х  | х   | х   | 0101   |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | х  | х  | х  | х   | х   | 0110   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | х  | х  | х   | х   | 0111   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | х  | х   | х   | 1000   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | х   | х   | 1001   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1   | х   | 1010   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 1011   |

# 2.3.2 Back-End Sharing Hardware

When a *result* is produced by a custom instruction, it must be forwarded to the correct processor. The processor's instruction *request ID* signal is used to select the priority encoder output, *done* signal, and *result* signal from the corresponding instruction. As shown in Figure 14, the priority encoder output and the processor identification number are then compared. If these values match, the *done* signal is accepted by using the *and* gate shown. Upon receiving a high *done* signal, the processor will then latch the *result* value present. This ensures that a processor does not erroneously select a result belonging to another processor with higher priority. This entire back-end set of components is required for each processor core.

Figure 14. Back-end sharing hardware block diagram.

### 2.4 Custom Instructions

As shown in Figure 13, the custom instruction unit is a "black box" within the shared architecture. Custom instructions can be tailored per application either manually or automatically while the infrastructure used to support sharing remains the same. Two types of custom instructions can be implemented: fine-grained and coarse-grained. Fine-grained instructions are made from smaller sections of source code and use few inputs. They usually execute in just a few clock cycles and are closely coupled with the pipeline. Coarse-grained instructions replace large sections of source code and can use a whole array of inputs.

Typically, a system with fine-grained instructions will spend less time in each custom instruction, but use them more frequently than coarse-grained instructions. Examples of fine-grained instructions along with an implementation example are given in Section 2.4.1.

Coarse-grained instructions are described in Section 2.4.2 with an explanation of the required architecture adjustments.

#### 2.4.1 Fine-Grained Instructions

Typically, fine-grained instructions are selected from application source code based on register file constraints, speed increase, frequency, and hardware implementation cost. As mentioned previously, several algorithms to define and select custom instructions for single-processor systems have been developed. Automatic instruction selection and enumeration is beyond the scope of this thesis and, as a consequence, custom instructions are chosen manually.

Custom instructions were generated with attributes found to be typical based on an analysis of well-known benchmarks. The instructions were not extracted from source code, but rather generated using compiler instruction-enumeration and -selection statistics from several previous works. The assumptions used are tabulated in Table 2 along with the source used to determine their value. Each of the entries in the table represents an architectural attribute of the custom instruction such as the "depth" of logic in a custom instruction in terms of gates.

Table 2. Attributes of custom instructions assumed when generating the custom instruction-set.

| Statistic                                   | Value                                                                   | Source                     |  |  |

|---------------------------------------------|-------------------------------------------------------------------------|----------------------------|--|--|

| Average Custom Instructions per Application | 9                                                                       | Ienne and Leupers [36]     |  |  |

| Average Frequency of Custom Instruction     | 32.3%                                                                   | Clark [ <b>37</b> ]        |  |  |

| Relative Frequency of Operations            | Multiply = 13.3%<br>Add = 31.0%<br>Logic = 55.7%                        | Clark et al. [ <b>23</b> ] |  |  |

| Custom Instruction Depths, Width, and Shape | Depth 2 = 47.5%<br>Depth 3 = 24.8%<br>Depth 4 = 10.3%<br>Depth 5 = 6.2% | Clark et al. [ <b>23</b> ] |  |  |

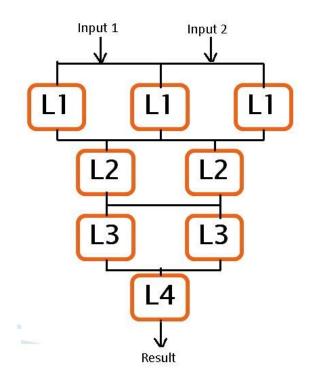

One assumption used to generate the custom instruction-set is that custom instructions tend to have a "triangular" shape as depicted in Figure 15. Statistically, custom instructions can be organized as a set of logic levels with a "triangular" shape as described by Clark et al [23]. In this diagram, each node represents an operation with the outputs of each level of operations being connected to the inputs of the next level via a cross-bar network. The level closest to the inputs tends to contain the most operations. The number of operations in each consecutive level tends to be progressively fewer the closer it is to the output. The custom instruction in Figure 15 has four logic levels with the first level performing three operations that use the two input operands. The results from this first level are then used as operands to the second level which performs two operations. The third level then also performs two operations, and the fourth level performs one operation that produces the output. This overall shape is assumed for the set of custom instructions defined and depicted in Figure 16.

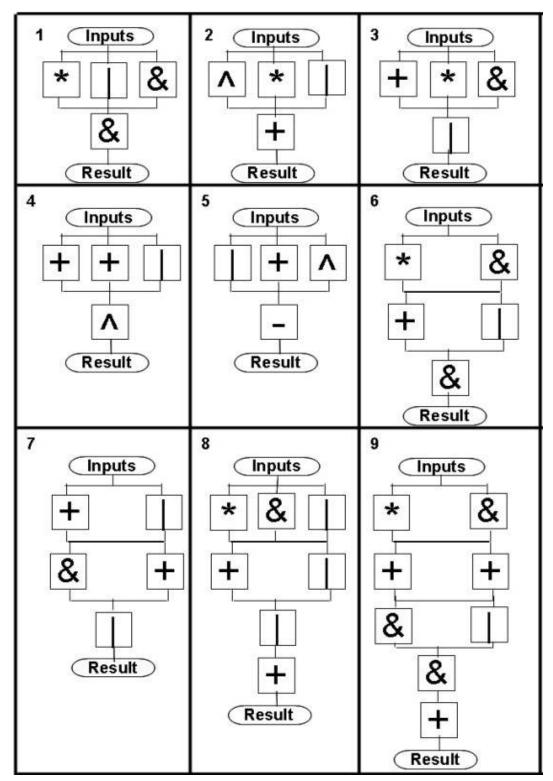

Assuming the "triangular" shape assumption, 9 custom instructions were randomly generated to define the custom instruction-set shown in Figure 16. The decision to use 9 custom instructions was based on previous work by Ienne and Leupers [36] that found that the average number of custom instructions per benchmark application is 8.72. Clark et al [23] found that the probabilities that custom instructions have depths of 2, 3, 4, and 5 levels are 47.5%, 24.8%, 10.3%, and 6.2%, respectively, for systems in which 5-levels is the maximum allowed depth. Based on this, we assumed that five of the nine proposed instructions have 2 levels, two have 3 levels, one has 4 levels, and one has 5 levels.

Figure 15. Average custom instruction shape and layout.

After further processing of the statistics extracted from Clark et al [23], it was determined that depth-2 instructions have an average of 3.7 operations, depth-3 instructions have an average of 5.3 operations, depth-4 instructions have an average of 7.0 operations, and depth-5 instructions have an average of 8.3 operations. For this reason, it was assumed that the generated custom instructions have 4, 5, 7, and 8 operations for depth-2, depth-3, depth-4, and depth-5 instructions, respectively.

With respect to operation types, the probabilities that an operation is a multiply, add or subtract, or a logic operation are 13.3%, 31.0%, and 55.7%, respectively [23]. Thus, operations were randomly placed in each of the nine proposed instructions using these proportions. The custom instructions can have one or two inputs. The Verilog implementation of the nine average custom instructions can be seen in Appendix A.

Figure 16. Set of nine custom instructions used for the proposed architecture.

### 2.4.1.1 Experimental Framework

The proposed architecture and fine-grained custom instructions were implemented for a Stratix III FPGA using Nios-II/s soft processors. As defined in the Nios II Custom Instruction User Guide [35], the proposed custom instructions are extended multicycle instructions, requiring *clock*, *clock enable*, *start*, *reset*, *instruction select*, and *done* signals. These fine-grained instructions are confined to two input operands and one output by the Nios II register file.

To determine the impact of sharing as the number of processors varies, Quartus II was used to generate systems containing varied numbers of processors using both the original, non-shared architecture and the new, shared architecture. Results for these systems are discussed in Section 2.4.1.2.

Using results from the varied processor experiment, systems with a fixed number of processors are generated that allow varying degrees of custom instruction unit sharing. This means processors can share more than one set of custom instructions in order to alleviate bottlenecks caused by competition for the same resource. These results are discussed in Section 2.4.1.3.

For the varied processor and varied sharing systems described above, all cores have their own 8 Kb instruction cache and 6 Kb on-chip data memory. The cores share a common 256 Kb on-chip instruction memory. Synthesis was performed using Quartus II which was used to provide both resource usage and critical path delay results. All area and critical path delay results have been averaged over five fitter seed values.

## 2.4.1.2 Varied Processor Resource Usage and Critical Path Delay

Quartus II was used to generate systems containing 3, 6, 9, 12, 15, and 18 processors that all share one set of custom instructions. Table 3 shows the percentage area reduction of the shared system compared to the non-shared architecture for each case. The shared systems containing 6, 9, 12, 15, and 18 processors all showed an area reduction of more than 21% over the non-shared architecture containing the same number of processors. The shared three processor system did not produce any area benefits over the non-shared architecture. These results demonstrate two important points to consider when designing a shared system: a minimum amount of sharing is required before area reduction is seen, and a maximum amount of sharing can be reached where the area benefits begin to decrease again.

Table 3. Resource usage for fine-grained systems sharing one custom instruction unit.

| Dragossors | Area   | Reduction  |           |

|------------|--------|------------|-----------|

| Processors | Shared | Non-Shared | Reduction |

| 3          | 6505   | 6409       | -1.5%     |

| 6          | 10016  | 12701      | 21.1%     |

| 9          | 14559  | 19008      | 23.4%     |

| 12         | 19158  | 25309      | 24.3%     |

| 15         | 24192  | 31655      | 23.6%     |

| 18         | 29349  | 37949      | 22.7%     |

The three processor system demonstrates a case where the minimum amount of sharing was not reached to produce an area reduction over the non-shared architecture. Although two custom instruction units are removed for this case, the additional infrastructure needed to provide custom instruction sharing (i.e. multiplexors, comparators, priority encoders, and state machines) is greater than the area saved.

The most prominent reduction in area is achieved for the 12 processor system representing the maximum amount of sharing for this instruction-set before the area benefits begin to decrease again. This peak is likely caused by two opposing trends. One trend is that an increase in the amount of sharing, achieved by increasing the number of processors, results in an increase in resource usage because it leads to larger multiplexors and a larger arbitrator. The opposite is true for the resource usage of the custom instructions themselves; the more sharing that occurs, the less resource usage. The amount of sharing that will lead to an optimal reduction in area will vary depending on the custom instruction unit size and complexity.

Although reducing the implementation area of a design is the main advantage of sharing, it can have a negative impact on critical path delay and thus overall runtime. A more compact design generally means a shorter critical path delay. However, in the shared architecture, the placement of the instruction unit in relation to each processor will be much different than in the non-shared architecture. Also, the additional sharing hardware lengthens the time required to complete the *execute* stage of the pipeline. For both the shared and non-shared architectures, it is desirable to create ISEs that do not affect the critical path delay of the system.

An extended path over the custom instruction will lengthen the time required to complete the execute stage of the processor's pipeline. Figure 17 shows the five-stage pipeline of the Nios II/s processor. For the fine-grained custom instructions, the execute phase has been split into two clock cycles to ensure the critical path of the entire design is not affected by larger instructions.

Figure 17. Execute phase timing for custom instruction.

The first cycle in the execute stage performs the front-end operations that select the input values. These values are then latched, and the actual custom instruction is performed in the second clock cycle of the execute stage. The back-end operations, that select the *result* and *done* signals for the correct processor, are also performed during the second clock cycle. For more complex instructions, the custom instruction could be split into more than two clock cycles to prevent the instruction from affecting the critical path if necessary.

The critical path of the shared architecture is not affected when using the two-cycle execute as demonstrated in Table 4. Negligible changes in the critical path delay over the non-shared architecture are seen in the 6, 9, 12, 15, and 18 processor cases. These small differences are likely caused by variations in the layout due to the non-deterministic nature of the layout algorithms used by Quartus II. The 3 processor case shows a larger reduction in the critical path, but was not a beneficial implementation in terms of area reduction. Since the 12-core system showed the greatest area reduction and a slight reduction in critical path delay over the non-shared architecture, it was selected for further analysis. The 12-core system also presents several opportunities to explore custom instruction unit sharing between varied numbers of processors.

Table 4. Critical path delay for systems with varying cores sharing one custom instruction unit. Each custom instruction unit has 9 fine-grained instructions.

| Drocesers  | Critical Pat | Reduction  |           |

|------------|--------------|------------|-----------|

| Processors | Shared       | Non-Shared | Reduction |

| 3          | 7.335        | 7.757      | 5.4%      |

| 6          | 8.229        | 8.361      | 1.6%      |

| 9          | 9.220        | 9.242      | 0.2%      |

| 12         | 9.021        | 9.094      | 0.8%      |

| 15         | 9.958        | 9.778      | -1.8%     |

| 18         | 10.082       | 10.094     | 0.1%      |

## 2.4.1.3 Fixed Processor Resource Usage and Critical Path Delay

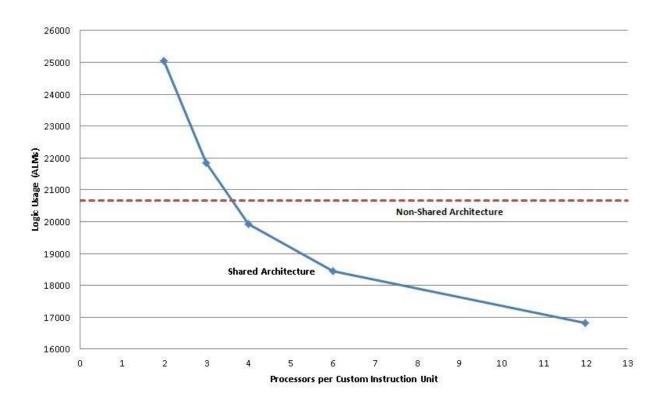

Systems containing a fixed number of processors can be arranged into groups, such that each group shares a set of custom instructions. In Figure 18 and Figure 19, FPGA resource usage and run-time are presented for a 12-core system arranged into different sharing configurations. The total number of processor cores in the system remains constant, but the number of custom instruction units varies depending on the degree of sharing.

For example, one arrangement has two cores per custom instruction unit, where each unit contains the 9 custom instructions shown in Figure 16. For this system, the twelve cores are evenly divided into six groups. In this thesis, this type of arrangement is referred to as *2-way*.

Figure 18. Resource usage for a system with 12 cores and with varying degrees of sharing. Each custom-instruction unit has 9 fine-grained instructions.

For the area and critical path delay results, the x-axis represents the number of processors sharing each custom instruction unit. The graphs show a magnified view of the results to better demonstrate the changes in the y-axis values for each case. For the 4-way, 6-way, and 12-way sharing configurations, significant reductions in resource usage are seen. In fact, the resource usage of a 12-core system is reduced from 25,309 ALMs in the non-shared architecture to 19,158 ALMs in the 12-way system. This translates to a 24% reduction in FPGA logic resources. The 2-way and 3-way sharing configurations do not show area reductions compared to the non-shared architecture due to the additional input multiplexors, comparators, and priority encoders required. For example, a 2-way system requires 6 custom instruction units and the input multiplexors, comparators, and priority encoders for each instruction in each unit. A 12-way system only requires a single custom instruction unit and additional front-end hardware for each custom instruction in the set.

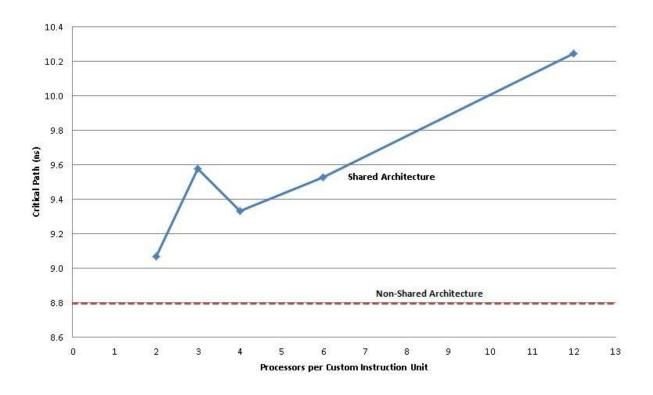

The results presented in Figure 19 show that any changes in the critical-path delay of the 12-core system are negligible and likely attributed to layout variations. Quartus II timing results showed that the additional sharing hardware did not appear on the critical path.

Therefore, the slight range in values from 9.02 ns to 9.51 ns is likely caused by repositioning in the design layout and not by the additional sharing hardware. It could be expected, however, that a peak number of processors would be reached where the additional multiplexing and encoding hardware would become large enough to cause delays in the critical path.

Figure 19. Critical path delay for a system with 12 cores and with varying degrees of sharing. Each custom-instruction unit has 9 fine-grained instructions.

### 2.4.2 Coarse-Grained Instructions

Larger instructions that require more inputs and more clock cycles to complete can also be selected from application source code for custom instruction implementation. These coarse-grained instructions are usually called less frequently by the application, but have a much larger per-use speed increase.