# A Steady-state Analytical Solution for MOSFET Channel Temperature Estimation

### **HeatMOS**©

by

Harish C. Rajput

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

### THE REQUIREMENTS FOR THE DEGREE OF

### MASTER OF APPLIED SCIENCE

in

The College of Graduate Studies

(Electrical Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

(Okanagan)

April 2011

© Harish C. Rajput 2011

## Abstract

A steady state analytical solution for MOSFET (metal oxide semiconductor field effect transistor) channel temperature estimation has been derived and the analytical model has been used to develop a software tool called HeatMOS©. HeatMOS© estimates the MOSFET channel temperature based on information from the device layout and an industry standard BSIM3 compact model. The steady state solution is an approximation for the channel temperature distribution along its length. The HeatMOS© model has been designed to be integrated into a VLSI CAD flow to predict the steady state temperature of a full micro-chip. An equivalent M-network model for steady state temperature can be extended for each MOSFET device in a complete micro-chip. In future work, HeatMOS© can be combined with the models of interconnect to develop a full micro-chip thermal analysis software tool.

# **Table of Contents**

| Ab  | ostrac  | xt                     | ii   |

|-----|---------|------------------------|------|

| Ta  | ble of  | f Contents             | iii  |

| Lis | st of ] | Tables                 | viii |

| Lis | st of I | Figures                | ix   |

| Lis | st of A | Acronyms               | xiii |

| Ac  | know    | vledgements            | XV   |

| 1   | Intro   | oduction               | 1    |

|     | 1.1     | Background             | 1    |

|     | 1.2     | Motivation             | 7    |

|     | 1.3     | Research Goals         | 10   |

|     | 1.4     | Scope and Organization | 14   |

|     |         |                        | iii  |

| Table | of | Contents |

|-------|----|----------|

|-------|----|----------|

| 2 | Hea | ting in I | Integrated Circuits                        | 16 |

|---|-----|-----------|--------------------------------------------|----|

|   | 2.1 | Electro   | ostatic Analogy of Heat Conduction         | 18 |

|   | 2.2 | Heat E    | quation                                    | 20 |

|   | 2.3 | Heat G    | eneration in MOSFETs                       | 22 |

|   | 2.4 | Summa     | ary                                        | 24 |

| 3 | The | rmal M    | odel and Analytical Solution               | 25 |

|   | 3.1 | BSIM      | 3 MOSFET Model                             | 25 |

|   | 3.2 | MOSF      | ET Channel                                 | 27 |

|   |     | 3.2.1     | Channel Geometry for Thermal Model         | 32 |

|   |     | 3.2.2     | Electrical Resistance                      | 34 |

|   |     | 3.2.3     | Channel Height Models                      | 37 |

|   |     | 3.2.4     | Channel Length Models                      | 39 |

|   |     | 3.2.5     | Thermal Conductance                        | 40 |

|   | 3.3 | Solutio   | on of the Heat Equation                    | 42 |

|   |     | 3.3.1     | Region 1: Non-uniform cross-sectional area | 42 |

|   |     | 3.3.2     | Region 2: Uniform cross-sectional area     | 44 |

|   |      | 3.3.3    | Boundary Conditions and Complete Solution              | 47 |

|---|------|----------|--------------------------------------------------------|----|

|   |      | 3.3.4    | The Average Channel Temperature                        | 51 |

|   |      | 3.3.5    | The Maximum Channel Temperature                        | 51 |

|   |      | 3.3.6    | The Channel Temperature at Pinch-off                   | 53 |

|   | 3.4  | M-Net    | work Representation of the Channel                     | 53 |

|   | 3.5  | Summ     | ary                                                    | 58 |

| 4 | Hea  | tMOS©    | )                                                      | 59 |

|   | 4.1  | About    | HeatMOS©                                               | 59 |

|   | 4.2  | Integra  | ation in the VLSI CAD Flow                             | 61 |

| 5 | Rest | ults and | Discussions                                            | 63 |

|   | 5.1  | Verific  | ation                                                  | 65 |

|   |      | 5.1.1    | Test Scenario using Externally Supplied Drain Current  | 67 |

|   |      | 5.1.2    | Test Scenario for a Smaller MOSFET Device              | 69 |

|   |      | 5.1.3    | Test Scenario for the Case When the Source, Drain, and |    |

|   |      |          | the Reference Temperatures are Same                    | 69 |

|   | 5.2  | Satura   | tion Mode of Operation                                 | 72 |

|   |      |          |                                                        |    |

### Table of Contents

|     | 5.2.1  | Test Scenario When Gate and Drain are at Same Voltage                               | 72 |

|-----|--------|-------------------------------------------------------------------------------------|----|

|     | 5.2.2  | Test Scenario for the Case of Different Gate and Drain<br>Voltages                  | 74 |

|     | 5.2.3  | Test Scenario for the Case of High Gate and Drain Voltages                          | 76 |

|     | 5.2.4  | Test Scenario for a Large MOSFET Device with High Drain         Current             | 76 |

|     | 5.2.5  | Test Scenario for Different Source/Drain Temperatures and                           | 70 |

|     |        | Voltages                                                                            | 79 |

| 5.3 | Linear | Ohmic Mode of Operation                                                             | 79 |

|     | 5.3.1  | Test Scenario for the Case of Different Temperatures at theSource and the Drain     | 81 |

|     | 5.3.2  | Test Scenario for a Larger Device in the Ohmic Operating<br>Region                  | 81 |

| 5.4 | Averag | ge and Maximum Temperature Distributions                                            | 84 |

|     | 5.4.1  | Channel Temperature Distribution with Drain Voltage and Drain Current               | 85 |

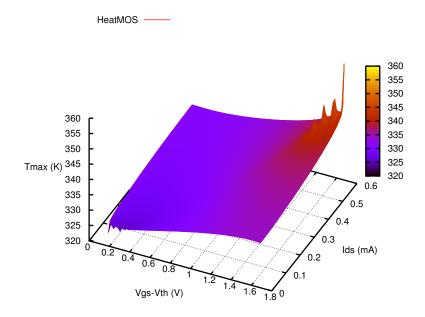

|     | 5.4.2  | Channel Temperature Distribution with Effective Gate Volt-<br>age and Drain Current | 85 |

| 5.5 | Discus | sion                                                                                | 90 |

| 5.6 | Summa  | ary                                                                                 | 92 |

|     |        |                                                                                     | vi |

| 6  | Con    | clusions and Future Directions            | 94 |

|----|--------|-------------------------------------------|----|

|    | 6.1    | Contributions                             | 94 |

|    | 6.2    | Limitations                               | 95 |

|    |        | 6.2.1 Fundamental Limitations             | 95 |

|    |        | 6.2.2 Limitations of First Implementation | 96 |

|    | 6.3    | Future work                               | 97 |

| Bi | bliogı | raphy                                     | 00 |

| Aj | ppend  | dices                                     |    |

| A  | BSI    | M3 Model Parameters                       | 06 |

| B  | SPI    | CE Netlist                                | 09 |

| С  | Nun    | nerical Solution of the Heat Equation     | 12 |

| D  | Hea    | tMOS© Development 1                       | 24 |

|    | D.1    | Development Environment                   | 24 |

|    | D.2    | A Sample HeatMOS <sup>©</sup> Execution   | 24 |

|    |        |                                           |    |

# **List of Tables**

| 2.1 | Thermal and electrostatic analogies                             | 19  |

|-----|-----------------------------------------------------------------|-----|

| 2.2 | Thermal and electrical conductivities (300 K)                   | 19  |

| 2.3 | Thermal and electrical versions of heat transfer or capacitance | 20  |

| A.1 | BSIM3 Parameters used in HeatMOS <sup>©</sup>                   | 107 |

| A.2 | Other parameters used in HeatMOS <sup>©</sup>                   | 108 |

# **List of Figures**

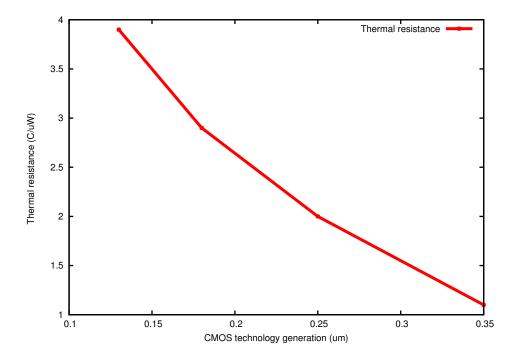

| 1.1 | Transistor thermal resistance versus CMOS technology scaling          | 3  |

|-----|-----------------------------------------------------------------------|----|

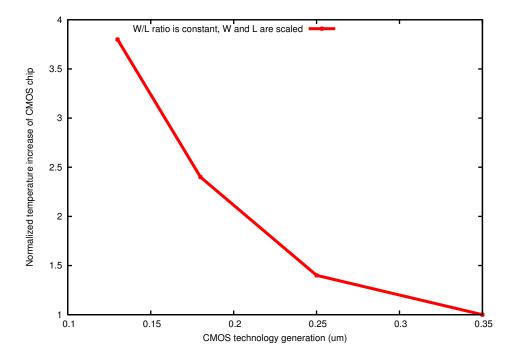

| 1.2 | Impact of technology scaling on temperature increase                  | 5  |

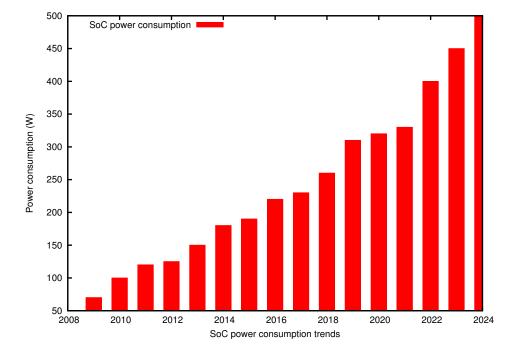

| 1.3 | SoC power consumption trends                                          | 11 |

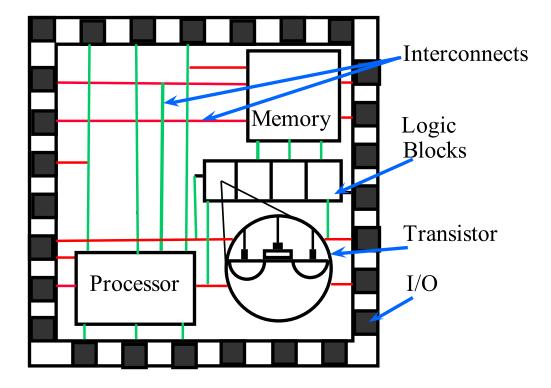

| 1.4 | A typical micro-chip layout                                           | 12 |

| 1.5 | Interconnect-transistor network                                       | 13 |

| 2.1 | Conservation of heat (energy) within a differential slice of a resis- |    |

|     | tor                                                                   | 21 |

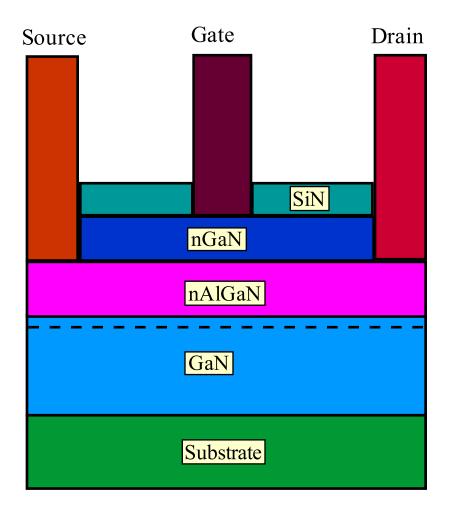

| 2.2 | Cross-sectional view of an nMOS transistor                            | 23 |

| 3.1 | A typical I-V characteristic of an nMOS transistor                    | 28 |

| 3.2 | A comparison for I-V characteristics of an nMOS transistor            | 30 |

| 3.3 | Simplified 2-D cross-section of an nMOS transistor                    | 31 |

| 3.4 | 3D view of the channel geometry for thermal model                     | 34 |

|     |                                                                       | ix |

### List of Figures

| 3D view of region 1 of the channel                                              | 42                                     |

|---------------------------------------------------------------------------------|----------------------------------------|

| 3D view of the region 2 of the channel                                          | 45                                     |

| Resistor M-network used for EMR verification                                    | 55                                     |

| VLSI CAD flow                                                                   | 62                                     |

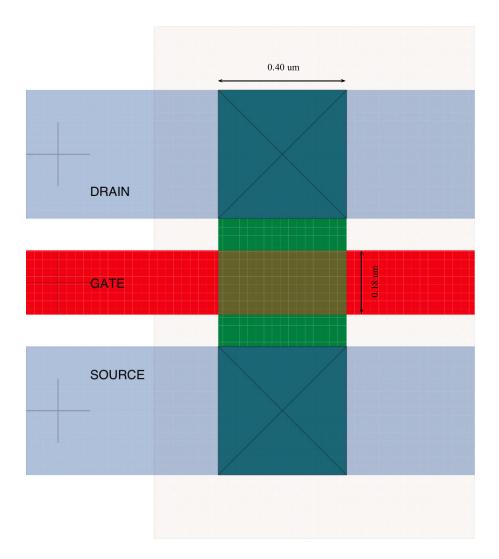

| An nMOS layout                                                                  | 64                                     |

| I-V characteristics of nMOS device under test produced by Heat-                 |                                        |

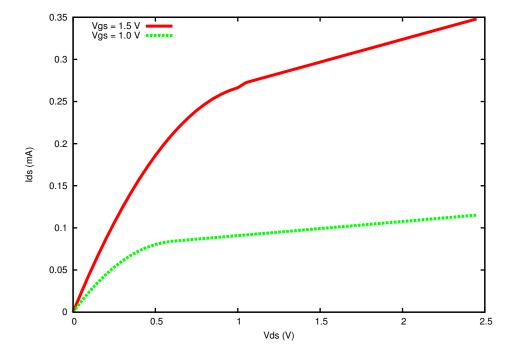

| MOS©                                                                            | 66                                     |

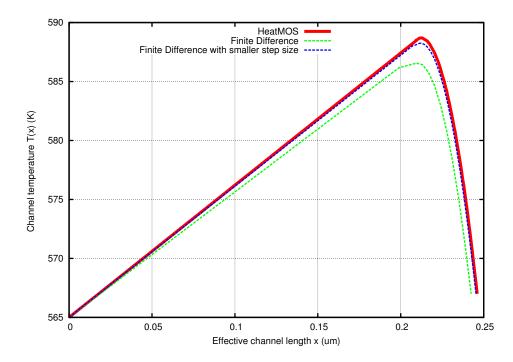

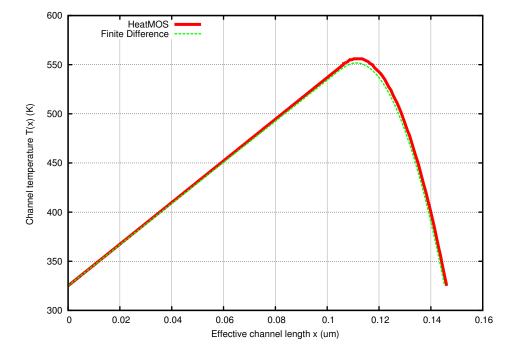

| $SourceTemp = 565K \mid DrainTemp = 567K \mid RefTemp = 456K \mid$              |                                        |

| $V_{gs} = 1.0V   V_{ds} = 1.5V   I_{ds} = 2mA   v7 - nmos.spice$                | 68                                     |

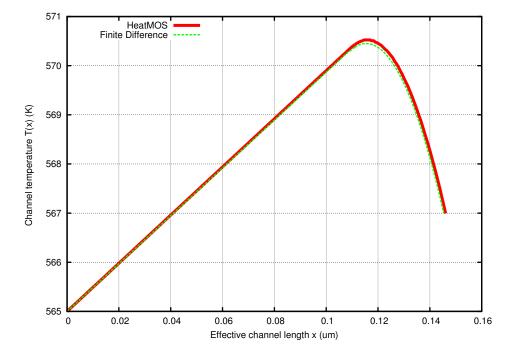

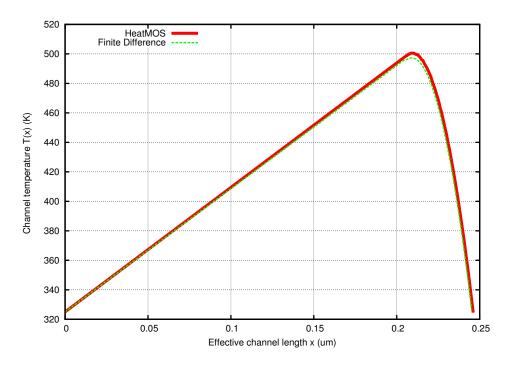

| $SourceTemp = 565K \mid DrainTemp = 567K \mid RefTemp = 456K \mid$              |                                        |

| $V_{gs} = 1.5V   V_{ds} = 1.5V   v8 - nmos.spice \dots \dots \dots \dots \dots$ | 70                                     |

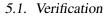

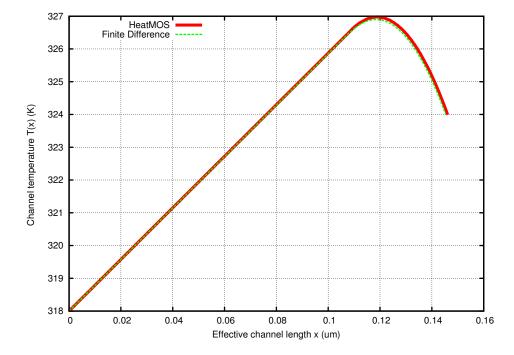

| SourceTemp = $10K   DrainTemp = 10K   RefTemp = 10K   V_{gs} =$                 |                                        |

| $1.5V   V_{ds} = 1.5V   v8 - nmos.spice$                                        | 71                                     |

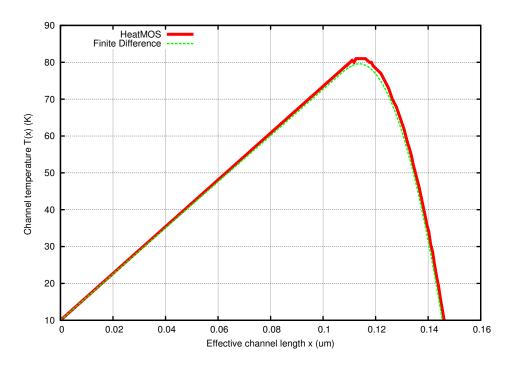

| $SourceTemp = 325K \mid DrainTemp = 325K \mid RefTemp = 300K \mid$              |                                        |

| $V_{gs} = 1.5V   V_{ds} = 1.5V   v8 - nmos.spice \dots \dots \dots \dots$       | 73                                     |

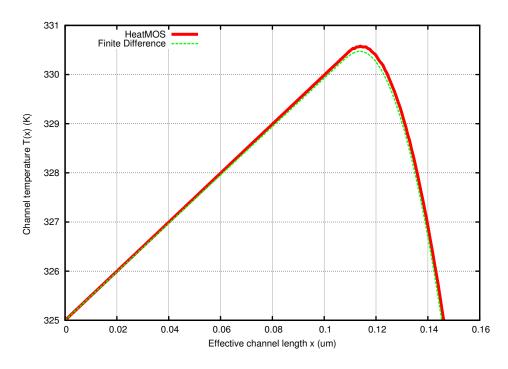

| $SourceTemp = 325K \mid DrainTemp = 325K \mid RefTemp = 300K \mid$              |                                        |

| $V_{gs} = 1.8V   V_{ds} = 2.2V   v8 - nmos.spice \dots \dots \dots \dots \dots$ | 75                                     |

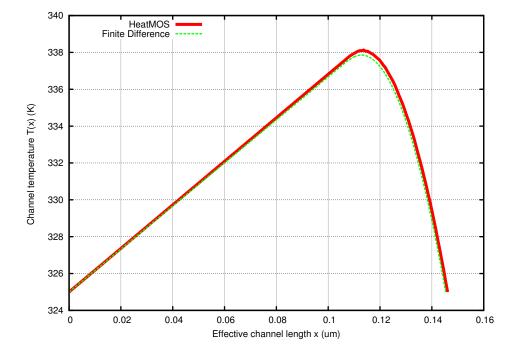

| $SourceTemp = 325K \mid DrainTemp = 325K \mid RefTemp = 300K \mid$              |                                        |

| $V_{gs} = 5.0V   V_{ds} = 5.0V   v8 - nmos.spice \dots \dots \dots \dots \dots$ | 77                                     |

|                                                                                 | 3D view of the region 2 of the channel |

Х

| 5.9  | SourceTemp = 325K   DrainTemp = 325K   RefTemp = 300K                                                                         |            |

|------|-------------------------------------------------------------------------------------------------------------------------------|------------|

|      | $V_{gs} = 5V   V_{ds} = 5V   v7 - nmos.spice \dots \dots \dots \dots \dots \dots \dots$                                       | 78         |

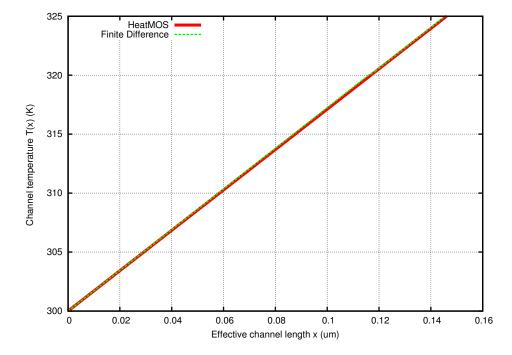

| 5.10 | $SourceTemp = 318K \mid DrainTemp = 324K \mid RefTemp = 298K \mid$                                                            | 80         |

|      | $V_{gs} = 1.2V   V_{ds} = 1.8V   v8 - nmos.spice \dots \dots \dots \dots \dots$                                               | 80         |

| 5.11 | SourceTemp = $300K \mid DrainTemp = 325K \mid RefTemp = 300K \mid$<br>$V_{gs} = 1.0V \mid V_{ds} = 0.1V \mid v8 - nmos.spice$ | 82         |

| 5.12 | SourceTemp = $318K \mid DrainTemp = 324K \mid RefTemp = 300K \mid$                                                            |            |

|      | $V_{gs} = 1.0V   V_{ds} = 0.1V   v7 - nmos.spice$                                                                             | 83         |

| 5.13 | The average channel temperature versus the drain current and the                                                              |            |

|      | drain voltage                                                                                                                 | 86         |

| 5.14 | The maximum channel temperature versus the drain current and                                                                  | ~-         |

|      | the drain voltage                                                                                                             | 87         |

| 5.15 | The maximum channel temperature versus the drain current and the drain voltage                                                | 88         |

| 5 16 | The maximum channel temperature versus the drain current and                                                                  |            |

| 5.10 | the effective gate voltage                                                                                                    | 89         |

| 5.17 | A typical cross-section of an HEMT device                                                                                     | 91         |

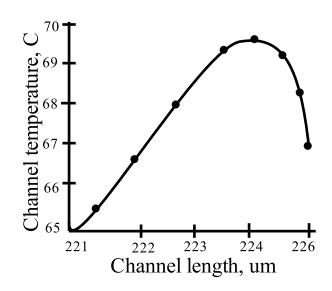

| 5.18 | Experimental channel temperature of HEMT device                                                                               | 92         |

|      |                                                                                                                               |            |

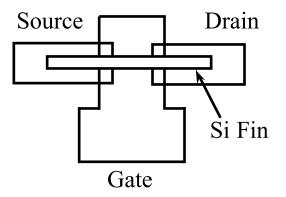

| 6.1  | FinFET typical layout and schematic cross-sectional structures (Hisan         et al., 2000)                                   | noto<br>99 |

|      | . ,                                                                                                                           | xi         |

### List of Figures

| D.1 | A sample HeatMOS run part 1 | • | • |  | • | • |  | • | • | • | • | • | • | 125 |

|-----|-----------------------------|---|---|--|---|---|--|---|---|---|---|---|---|-----|

| D.2 | A sample HeatMOS run part 2 |   |   |  |   |   |  | • |   | • |   |   | • | 126 |

# **List of Acronyms**

- 1D One Dimensional

- 2D Two Dimensional

- 3D Three Dimensional

- μm Micro-meter

- ASIC Application Specific Integrated Circuit

- CAD Computer-Aided Design

- CMOS Complementary Metal-oxide Semiconductor

- EMR Electro-migration Reliability

- GDSII Graphic Database Information Interchange

- HEMT High Electron Mobility Transistor

- IC Integrated Circuit

- K Kelvin

- mA Mili-ampere

| MOS | Metal-oxide Semiconductor |  |

|-----|---------------------------|--|

| nm  | Nano-meter                |  |

| SoC | System-on-a-Chip          |  |

| SOI | Silicon on Insulator      |  |

| V   | Volt                      |  |

|     |                           |  |

VLSI Very Large Scale Integration

# Acknowledgements

I would like to thank Prof. Andrew Labun for the supervising my research and his guidance. The concept of using thermal and electrostatic analogies shown in chapter 2 are based on an unpublished paper by Prof. Labun. I am very thankful for the support that Prof. Andrew has given me.

I would like to thank Prof. Carolyn Labun for reviewing my english style and her suggestions to improve my presentation and writing skills.

I would like to thank Prof. Thomas Johnson for reviewing the research work and providing further guidance to complete the thesis.

I was a member of the Multiphysics research group led by Prof. Labun and I would like to thank other group members including Karan, Ska-hiish, Jason Liao, and Sadegh as well.

I would like to thank Prof. Abbas Milani with whom I worked on a different project.

I would like to thank my graduate supervising committee members, Prof. Andrew Labun, Prof. Thomas Johnson, Prof. Stephen O' Leary, and Prof. Kian Mehravaran. I would like to thank Prof. Deobrah Roberts, Associate Director Graduate Studies and Research.

I would like to thank my external examiner Prof. Robert Sobot from University of Western Ontario for reviewing my thesis.

Finally, I would like to thank everyone (including department of graduate studies staff, faculty of engineering staff, other faculty members, and fellow students) who have contributed towards this research work indirectly.

### Chapter 1

# Introduction

### 1.1 Background

Verifying the reliability of complex integrated circuits has become an increasingly complex design challenge as device geometries in fabrication processes continue to shrink (Alam et al., 2007). The low cost of fabricating integrated circuits (ICs) using CMOS (complementary metal-oxide semiconductor) continues to be the dominant fabrication technology. Micro-chips fabricated using CMOS technology are very complex and complete systems (SoC - system-on-a-chip) are common in the semiconductor industry. Predicting the operating temperature of these micro-chips should be done as early as possible to minimize the expense of resolving thermal issues late in the design phase.

The ITRS (International Technology Roadmap for Semiconductors) predicts that electro-thermal reliability will continue to present significant challenges as device geometries continue to shrink below 22 nm (ITR, 2009). Due to the high temperatures that can arise in current CMOS technologies, it has become extremely important to accurately estimate the temperatures within the micro-chip for EMR

### 1.1. Background

(electromigration reliability) verification. Electromigration is a term applied to the transport of mass in metal and is accelerated by the Joule heating, the heat generated by current flowing through interconnects and devices (Black, 1969). Metal atoms are pushed by strong dc electron currents, sometimes resulting in voids in the interconnect (causing open circuits) or extruding through dielectric (causing short circuits). The Joule melting resulting from extremely high electrical current has been discussed in Fantini and Morandi (1985). There is a need to model the microchip temperature at a detailed level, during post-layout reliability verification, and to identify the specific metal interconnects most at risk for EMR. If certain parts of the micro-chip are heated beyond their reliability limit, it may cause a breakdown of the functionality and reliability in the whole system.

The thermal trends for the CMOS technology are demonstrated by recent data presented by the ITRS. As device sizes are reduced to nano-scale gate lengths the power density will continue to rise. Although the power density increases, the material properties of silicon, dielectric layers and metal layers remain constant and the effective thermal conductivity per unit of power will decrease. As a result the effective thermal resistance will increase per microwave of power (Semenov et al., 2003) (Figure 1.1).

Several factors contribute to the increase in power density as the device geometries shrink. First, the geometry is shrinking faster than the scaling in the supply voltage which directly contributes to an increase in power density. Second, the high frequency performance of CMOS devices improves as device geometry shrinks which means that the average clock rate in digital circuits is expected to increase.

Figure 1.1: Transistor thermal resistance versus CMOS technology scaling

#### 1.1. Background

Dynamic switching results in power losses that are proportional to  $\Lambda CV^2 f$ , where *C* is the capacitance, *f* is the clock frequency,  $\Lambda$  is the activity factor ( $0 \le \Lambda \le 1$ ), and *V* is the applied voltage (Sedra and Smith, 2007; Weste and Harris, 2004). Parallel efforts are made in reducing capacitance (i.e. device size), voltage, and activity factor (i.e. introduction of power management subsystem), at the same time dissipation is proportional to the square of the voltage, and voltage scaling has not kept pace with device scaling. These factors have been analyzed by the ITRS and projections on the relative increase in the operating temperature of devices are shown in Figure 1.2 (Semenov et al., 2003). The junction temperature rise will grow very rapidly and the importance of analyzing thermal profiles and the impact on EMR will become increasingly important.

The major contribution to the rising micro-chip temperatures is due to device and interconnect heating. The heat generated due to electric current flow is called Joule heating. If there is a way to estimate the temperature of a micro-chip from its layout, before manufacturing, we would be able to change the design to rectify the design issues arising from the thermal hot spots. Temperature estimation in the design phase of the integrated circuits will improve the confidence of designing for reliability and reduce the overall design time of a production micro-chip. The influence of the temperature on failure mechanisms which occur in the temperature range of -55°C to 125°C has been discussed by Pecht et al. (1992). Computer modeling of metallization failure of the integrated circuits due to electromigration has been discussed in Kirchheim and Kaeber (1991) and Sukharav et al. (2009).

There are some industrial solutions for estimating interconnects temperature. Soft-

Figure 1.2: Impact of technology scaling on temperature increase

ware tools to estimate the micro-chip temperature at the package level are discussed by Melamed et al. (2009) and Oprins et al. (2009). Most of these tools use numerical approaches for temperature estimation which are slow and prohibitive for designs with millions of transistors.

There are two main sources of heat in integrated circuits. These are: the dynamic power generated by digital switching signals and the Joule heating generated by the resistance in the interconnects and the devices. Most of the power dissipation in large micro-chips is generated by digital switching signals where the dynamic power is proportional to  $fV^2$ , where f is the switching frequency and V is the applied voltage. On the other hand, Joule heat is proportional to  $I^2$ , where I is the electric current. In today's complex integrated circuits, switching frequencies are in the Giga Hertz (GHz) range while typical interconnect current and device currents are in the milliampere range.

Several approaches have been proposed to analyze the thermal performance of complex micro-chips. Analytical treatments of the 1-D steady state heat equation in IC interconnect have been presented previously in the context of interconnect temperature scaling analysis by Ajami et al. (2005), Im et al. (2002), and Chuan et al. (2009). An analytical solution of the interconnect heating and temperature estimation has been presented by Labun and Jagjitkumar (2008).

The focus of this research work is to develop a model for estimating device temperature based on device layout and steady state bias voltages.

### **1.2** Motivation

This research work is motivated by the need to have design tools to predict the steady state spatial variation of temperature on the integrated circuit in the design phase before the micro-chip is fabricated. A standard integrated design flow process primarily focuses on verifying the electrical performance of the design over process, temperature and voltage changes. However, design tools to model and predict the temperature behavior are not readily available. If efficient temperature modeling tools can be developed, then designers will have the ability to improve the reliability of designs in the early design phase rather than waiting for experimental results from a failure analysis.

Given the complexity of three-dimensional (3D) structures in complex integrated circuits, it is very important to have an efficient way to predict the temperature characteristics of the micro-chip. Brute force numerical solutions of the heat equation are computationally prohibitive for large IC's with millions of devices and multiple layers of interconnect. Therefore, a key focus of this research work is to investigate efficient solutions to estimate thermal characteristics that are scalable to very large and complex micro-chips.

In this research project, analytic models are developed to construct a thermal net list for the complete micro-chip. The net list is analogous to an electrical net list for a circuit. In this approach, a thermal circuit model is developed which can be used to predict the temperature. The Multiphysics research group at UBC has developed a thermal modeling software tool called Therminator3D. This tool can be used to simulate the overall temperature profile of a micro-chip providing thermal models are developed for the interconnects and devices. Thermal models for interconnect have already been developed by other researchers (Labun and Jagjitkumar, 2008). On the other hand, thermal models for devices is much more limited and a tractable model that can be incorporated in a thermal simulation of the micro-chip is required. The goal of this research project is to address this limitation and develop an analytic model for CMOS devices.

The thermal effects in the MOSFET (Metal-Oxide Semiconductor Field Effect Transistor) are complex and multidimensional because the generated heat has spatial as well as time dependent behavior. In order to accurately estimate the temperature due to the generated heat, one must solve the differential heat equation. The heat is generated due to electric current flow and can be estimated by Joule heating. There can be different ways to solve the differential equation (e.g. finite element, finite difference (Chuan et al., 2009) and (Kuball et al., 2007), analytical), but in order to estimate the temperature rapidly so that it can be feasible to estimate the temperature of the full micro-chip during the design, analytic solutions are preferred. There has been some work done in this direction and the analytical approach has been successfully implemented in order to estimate interconnect temperature (Labun and Jagjitkumar, 2008). However the authors did not analyze the device temperature which is the primary focus of this research. Figure 1.1 shows that the device thermal resistance increases as the technology scales down (Semenov et al., 2003), which in turn leads to the higher temperatures.

#### 1.2. Motivation

The most effective way to meet the reliability target for each technology node is to incorporate design-for-reliability at the start of each technology generation. The most effective way to meet the reliability of each technology node is to have complete built-in-reliability and design-for-reliability solutions available at the start of development of each technology generation. This requires an in-depth understanding of the physics of each failure mechanism and the development of powerful and practical reliability engineering tools. High temperatures not only cause significant changes in the delay characteristics for both the transistors and the interconnects but also degrade micro-chip reliability. With technology scaling, micro-chip power densities are increasing that has led to high operating temperatures and the large thermal gradients, thereby resulting in serious reliability concerns (Tsai and Kang, 2000). Scaling the technology results in higher transistor density and higher clock frequencies. Higher clock frequencies will increases dynamic switching power because the dissipation in switching driving a capacitive load is proportional to  $fV^2$ , where f is the clock frequency and V is the applied voltage (Weste and Harris, 2004).

As device technology scales down, there is an exponential increase in the temperature  $\triangle T$  between the MOSFET junction and the ambient temperature (Semenov et al., 2003). For example, as shown in Figure 1.2,  $\triangle T$  has increased by a factor of three as CMOS gate lengths have reduced from 0.35 um to 0.13 um. The rapid increase in the thermal density with a reduction in scaling has increased the importance of analyzing the temperature. High temperatures or uneven temperature distributions may result not only in the reliability issues, but also in the timing failures of micro-chips. To resolve these issues, high-quality, accurate thermal analysis, and thermally oriented placement optimizations are essential prior to fabrication (Tsai et al., 2006).

Other predictions in terms of the thermal trends in the nano-scale CMOS devices includes the total dissipation of the complex system-on-a-chip (SoC) circuits. ITRS data include for SoC dissipation is shown in Figure 1.3. The data shows that in ten years micro-chips could dissipate as much as 400 watts of heat energy(ITR, 2009). These trends demonstrate that the significant advances in terms of thermal management will be essential to keep junction temperatures within a reasonable operating temperature range. EMR failures become very significant at junction temperatures over 125 C.

### **1.3 Research Goals**

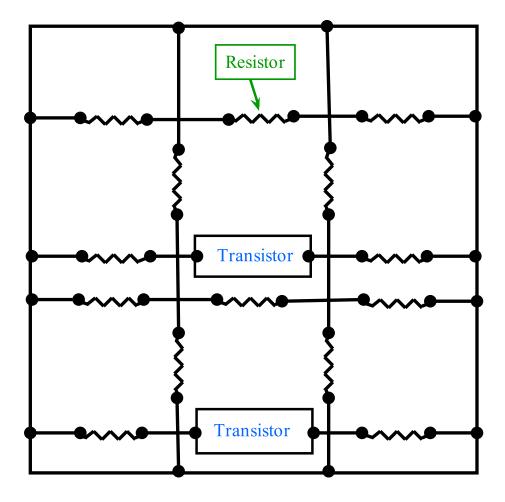

Figure 1.4 shows a typical layout of a micro-chip. The devices are connected via interconnects. The interconnects can be represented by an equivalent resistor network for EMR verification. Each net in the interconnects network can be represented by equivalent pi-network (Labun and Jagjitkumar, 2008) for thermal analysis, and interconnect network models are required for an interconnect metallization and CMOS devices. Therefore an interconnect-transistor resistor network can be used to do a full micro-chip thermal analysis as shown in Figure 1.5. The transistor in this representation may be considered as a special type of resistor. One of the objectives of this research work is to find an equivalent resistor resistor resistor network representation of a transistor which can be integrated in interconnect-transistor resistor resistor network representation for a micro-chip thermal analysis.

Figure 1.3: SoC power consumption trends

1.3. Research Goals

Figure 1.4: A typical micro-chip layout

Figure 1.5: Interconnect-transistor network

The main objective of this research work presented in this thesis is to model the heating behavior of a transistor and to find an analytical solution for the temperature estimation. The research includes the following:

- To develop a mathematical model for the Joule heating due to switching drain current in a MOSFET channel.

- To find an analytical equation which solves the heat equation.

- To estimate the temperature profile of the channel.

- To develop a software package for estimating the channel temperature from the extracted device layout information and using information from a compact model. In this work, the SPICE BSIM3 format was chosen because of its relative simplicity.

- To develop an equivalent resistor network representation of the channel which can be integrated into the interconnect-transistor resistor network for full micro-chip thermal analysis.

- To validate the analytical solution using a numerical solution.

### 1.4 Scope and Organization

The scope of this thesis is limited to the research objectives, problem definition, solution and comparative studies with numerical solution of the heat equation using the finite difference methods. The thesis treats the heating problems in integrated circuits and its solution is based on an analytical approach. Chapter 2 provides the background of the heating in the integrated circuits along with the problem definition of the MOSFET channel heating. Chapter 3 provides the mathematical model and the analytical solution for MOSFET channel temperature estimation. Chapter 4 describes HeatMOS©, a software package that has been developed through this research, implementing the analytical solution to estimate the channel temperature. Chapter 5 shows the results of HeatMOS© which are compared with numerical solutions using a finite difference solver. The conclusions and the future directions for this research are discussed in Chapter 6. The appendices provide other relevant informations such as different device parameters, SPICE netlist, and a pseudo code for the numerical solver.

### Chapter 2

# **Heating in Integrated Circuits**

The spatial variation of temperature across an integrated circuit (IC) is caused by charge carrier flow through the devices and the interconnects. The temperature variation in ICs is predominantly due to device heating and package level heat transport and is a subject of various chip-scale modeling approaches (Li et al., 2006). In the case of MOSFETs, the applied voltages at it its terminals create the longitudinal and transverse electric fields and charge carriers move from the source end to the drain end via drift and diffusion mechanisms (Park et al., 1991). Since the channel is a conducting path for the electric current, it can be considered as a resistor and the electric current flow in the channel leads to the Joule heating. The Joule heating causes the rise in the channel temperature.

Heat conduction in solids is governed by two principle mechanisms: diffusive heat conduction by electrons and heat conduction by lattice waves whose quanta are represented by phonons (Flik et al., 1992). Heat conduction by phonons in semi-conductors is reviewed by Abeles(Abeles, 1963). In silicon the heat conduction is dominated by phonons (Sinha and Goodson, 2006). The hot electrons near the drain end transfer some energy to phonons and this creates a transient, non-

equilibrium, high temperature "hot spot" that effectively leads to higher thermal resistance (Sinha and Goodson, 2006).

Thermal conductivity analysis and conductivity measurements for silicon are provided by (Morris and Hust, 1961). The detailed thermal analysis at the dimensions less than a phonon mean free path (~100 nm) requires the transient solution of the Boltzmann transport equation (BTE), that may not be feasible for large, netlistbased, full micro-chip thermal analysis. The phonon transport of energy can be described by the BTE , which can capture the sub-continuum effects particularly important for short impulsive events such as ESD (electrostatic discharge). These sub-continuum effects are not modeled by the diffusion model of energy transfer. These sub-continuum effects should be accounted for during the transient analysis but in a steady state analysis the time-average temperature given by the diffusion model are appropriate.

The BTE for the phonons can be written as:

$$\frac{\partial e^{"}}{\partial t} = -\nu \cdot \nabla e^{"} + \frac{e^{"}_{eq} - e^{"}}{\tau_{phonon}} + q_{electron-phonon}$$

(2.1)

where *e*" is the phonon energy per unit volume per unit solid angle, *v* is the phonon velocity,  $e_{eq}^{"}$  is the phonon equilibrium energy density,  $\tau_{phonon}$  is the phonon scattering rate,  $q_{electron-phonon}$  is the phonon energy absorption by hot electron.

The effective thermal conductivity of a complex silicon FET structure is technologyspecific and could be obtained by the detailed modeling, but this is beyond the scope of the thesis, which is aimed at a very compact model for netlist-based analysis. Our research is therefore directly applicable for the technology nodes above 180 nm (using the BSIM3 device model). The extension of this approach toward nanoscale technologies is discussed briefly in the Future Work.

### 2.1 Electrostatic Analogy of Heat Conduction

The analytical methods developed in this research to model heat conduction in the devices are based on analogous relationships between the form of equations for the heat conduction and the electrostatics. The fundamental analogies between the heat and the electrostatics are shown by comparison of the governing equations in Table 2.1. The temperature *T* in a conduction problem in the presence of a heat sources  $\phi$  is governed by the analogy to Poisson's equation (Guass' Law) in the electrostatics. Similarly, the heat flow is analogous to the current flow in the electric circuits. In these equations,  $\lambda$  is the thermal conductivity in W/mK,  $\varepsilon$  is the permittivity in F/m,  $\phi$  is the heat energy density in W/m<sup>3</sup>,  $\rho$  is the electric charge density in C/m<sup>3</sup>, *T* is the temperature in K, *V* is the electric potential in V, *q* is the heat flux in W/m<sup>2</sup>, *J* is the electric current density in C/m<sup>2</sup>s. Use of both analogies solves the heating problem (Labun, 2009).

Table 2.2 continues the analogy between electrical and thermal models by comparing material properties of thermal conductivity and electrical conductivity (Lide, 2004). Metals are good conductors of both heat and electrical current and dielectrics are poor conductors, although the ratio of conductance's is only two orders

| $\overrightarrow{\nabla} \cdot (\lambda \overrightarrow{\nabla} T) = -\phi$ | $\overrightarrow{\nabla} \cdot (\varepsilon \overrightarrow{\nabla} V) = -\rho$ |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| $\overrightarrow{q} = -\lambda \overrightarrow{\nabla} T$                   | $\overrightarrow{J} = -\sigma \overrightarrow{ abla} V$                         |

Table 2.1: Thermal and electrostatic analogies

| $\lambda \; (Wm^{-1}K^{-1})$ | $\sigma\left(\Omega^{-1}m^{-1}\right)$        |

|------------------------------|-----------------------------------------------|

| 398                          | $5.7 	imes 10^7$                              |

| 237                          | 3.7                                           |

| 174                          | $1 \times 10^{7}$                             |

| 83.5                         | $10^{-3}$                                     |

| 60.5                         | $10^{-3}$                                     |

| 1.4                          | $10^{-13}$                                    |

|                              | 398       237       174       83.5       60.5 |

Table 2.2: Thermal and electrical conductivities (300 K)

of magnitude for heat. The tabulated values also show that the range in thermal conductivity properties is much smaller than the range in electrical conductivity. For example, the thermal conductivity of copper is four times of magnitude better than silicon, while the the electrical conductivity of copper is 10 orders of magnitude greater than silicon (Lide, 2004).

The analogy with Possion's equation leads to a capacitance/heat transfer coefficient analogy through the application of the divergence theorem to Poisson's equation. Table 2.3 Row 1 shows the identical construction of integral equations which in the

| $\int_{Volume} \overrightarrow{\nabla} (\lambda \overrightarrow{\nabla} T) d\Omega = \oint_{Area} (\lambda \overrightarrow{\nabla} T) d\Omega$ | $\overrightarrow{V}T)d\overrightarrow{A} = \phi_{Volume}$ | $\int_{Volume} \overrightarrow{\nabla}(\varepsilon \overrightarrow{V}) d\Omega = \oint_{Area} (\varepsilon \overrightarrow{\nabla} V) d\overrightarrow{A} = Q_{Volume}$ |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\frac{1}{R_T} = \frac{\phi}{T}$                                                                                                               |                                                           | $C = \frac{Q}{V}$                                                                                                                                                       |

Table 2.3: Thermal and electrical versions of heat transfer or capacitance

electrical case are solved to obtain capacitance. The analogous thermal model for heat transfer shows that the reciprocal of the thermal resistance ( $R_T$ ) is equal to the ratio of the heat density divided by the temperature difference across the material.

The relationship between the heat conduction and the electrostatics is completed using Ohm's law to relate the current flow with the heat flux. The Joule heating in a wire gives  $I^2R = \phi_{Volume}$ . The heat is conducted through the dielectrics according to the Ohm's Law analogy. Thus, capacitance tables (in homogeneous dielectrics) can be read as thermal resistance tables by multiplying by a constant factor.

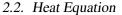

### 2.2 Heat Equation

Before developing a heat model for a MOSFET channel, a model for heating in a resistor is derived first. Consider a resistor of uniform width and composition as shown in Figure 2.1. The resistor temperature variation over its cross-section is neglected. For metal interconnects embedded in a dielectric, this can be readily justified, since (by Table 2.2) the thermal conductivity within the resistor is much greater than the thermal conductivity of the surrounding insulator. In MOSFETs

Figure 2.1: Conservation of heat (energy) within a differential slice of a resistor

the electric current is also confined to a well-defined region (the channel). Heat flow is confined by a poor thermal conductor above (the  $SiO_2$  gate dielectric) and also below, in SOI devices. However, even in bulk MOSFETs, the useful approximation of a uniform temperature over the channel cross-section is not too far off the mark because of the localization of the heat source.

With reference to Figure 2.1, the heat per unit length,  $mC_pT(x) \triangle x$  in a differential slice of a resistor segment of length  $\triangle x$ , where T(x) is the temperature along the resistor's length, *m* is the mass per unit length, and  $C_p$  is the heat capacity. The time rate of change of the heat is then given by (Labun and Jagjitkumar, 2008)

$$mC_p \frac{\partial T}{\partial t} \triangle x = F(x + \triangle x) - F(x) + \phi(x) \triangle x - f(x) \triangle x$$

(2.2)

Where F(x) is the diffusive heat flux. The heat flux is oriented along the resistor's length and is related to the temperature gradient by Fourier's law of heat conduction, including the "longitudinal" thermal conductance:

$$F(x) = G^{long} \frac{\partial T(x)}{\partial x}$$

(2.3)

The Joule heat per unit length is given by  $\phi = I_{rms}^2 R$ ; *R* is the electrical resistance per unit length, assumed constant within a resistor;  $I_{rms}$  is the time-averaged rms current. The function f(x) in equation (2.2) models the heat flux through the sides of the resistor to the surrounding environment at a temperature  $T^{ref}$ . If there is diffusive heat flux through the sides of the resistor to the local environment at some uniform, constant temperature  $T^{ref}$  (established, for example, by a full-chip temperature simulation including device heating), then one may define a "lateral" thermal conductance  $G^{lat}$  per unit length

$$f(x) = G^{lat}T(x) - T^{ref}$$

(2.4)

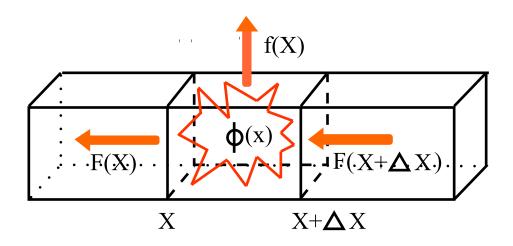

# **2.3 Heat Generation in MOSFETs**

When the transistor is on and is in operation, the charge carriers move from the source to the drain and in this process these loose energy due to physical reasons such as collisions, scattering, phonon-electron interaction etc. The dissipated

2.3. Heat Generation in MOSFETs

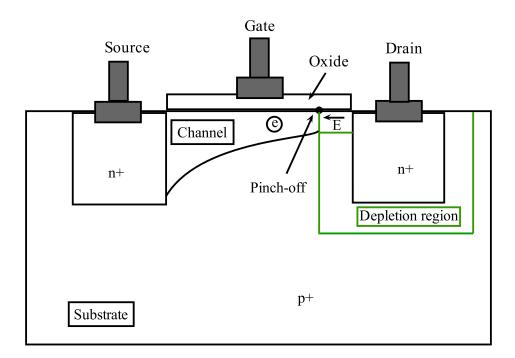

Figure 2.2: Cross-sectional view of an nMOS transistor

energy is released in the form of heat and leads to an increase in the device temperature. A cross-sectional view of a MOS transistor has been shown in Figure 2.2. The transistor is said to be in operation when there is a channel formed by applying appropriate voltages across substrate, source, drain, and gate terminals. The channel can be considered as a resistor of variable cross-sectional area, and the heat generated in the channel can be approximated by Joule heating similar to a resistor. Therefore, heat generation is concentrated in the region of the highest resistance, the pinched-off region of the channel near the drain end.

# 2.4 Summary

The heat generation in transistors has been presented with a focus on transistor channel heating. The basic equation for Joule heating has been explained, and it was shown that the heat equation is analogous to the solution of the Poisson equation in electrostatics. The basic heat equation for the Joule heating has been explained.

# Chapter 3

# Thermal Model and Analytical Solution

The one-dimensional heat equation (2.2) is applied to the thermal model of the MOSFET and solved analytically to give a closed-form expression for the channel temperature from the source to the drain. The thermal model uses the BSIM3 parameters.

# 3.1 BSIM3 MOSFET Model

BSIM3 is a physics-based, accurate, scalable, robust and predictive industry standard MOSFET SPICE model for circuit simulation and CMOS technology development. It was developed by the BSIM Research Group in the Department of Electrical Engineering and Computer Sciences (EECS) at the University of California, Berkeley. BSIM3 is the industry-standard MOSFET model. The third iteration of BSIM3 Version 3 (commonly abbreviated as BSIM3v3), was established by SEMATECH as the first industry-wide standard model for MOSFETs in December of 1996. The development of BSIM3 is based on Poisson's equation using the gradual channel approximation and coherent quasi 2D analysis, taking into account the effects of device geometry and process parameters. BSIM3 is appropriate for MOSFETs for 180 nm MOSFET technology and larger. BSIM3 models the following physical characteristics in MOSFET devices (Liu et al., 1999):

- Short and narrow channel effects on threshold voltage.

- Non uniform doping effects.

- Mobility reduction due to vertical field.

- Bulk charge effect.

- Velocity Saturation.

- Drain-induced barrier lowering (DIBL).

- Channel length modulation (CLM).

- Substrate current induced body effect (SCBE).

- Sub-threshold conduction.

- Source/Drain parasitic resistances.

BSIM3 uses a group device extraction strategy for parameter extraction. This requires measured data from devices with different geometries. All devices are measured under the same bias conditions. The BSIM3 device parameters for a 180 nm CMOS technology have been used in this research. The model parameters are given in appendix A.

# **3.2 MOSFET Channel**

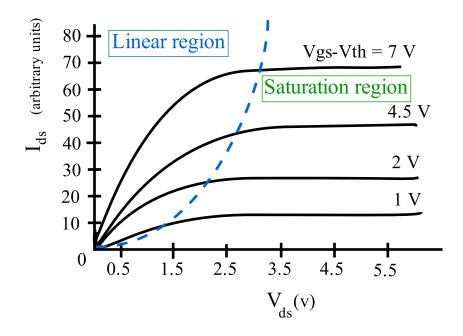

A simplified model of the MOSFET channel accounts for many characteristics of MOSFET devices and is sufficient for the compact thermal model developed in this thesis. The channel is a cloud of free charge carriers beneath the gate surface which conducts electric current. In the case of nMOS, the electron cloud forms the channel. The electron density is greater at the source end compared to the drain end and decreases towards the drain end (Masu and Tsubouchi, 1994). An example of the typical IV characteristics of an nMOS transistor is shown in Figure 3.1 (Weste and Harris, 2004). The electric current increases as we increase the drain voltage and after a certain voltage, the current becomes constant and the channel is said to be pinched off. Initially when there is no drain voltage, the electrons are attracted towards the positive gate voltage (enhancement mode nchannel MOSFET) and it is clear that the Joule heat constitutes only a small part of the micro-chip power consumption as compared to the power consumption due to switching activity. When the gate voltage is greater than the threshold voltage and the drain voltage is less than the gate voltage, the transistor is turned on, and a channel has been created which allows current to flow between the drain and the source. The MOSFET operates like a resistor controlled by the gate voltage relative to both the source and the drain voltages. Now, if the drain voltage is increased and becomes greater than the gate voltage, the transistor is said to be in the saturation or the active mode of operation. Since the drain voltage is higher than the gate voltage, the electrons spread out, and conduction is through a broad, three-dimensional channel and the current extends away from the interface. The onset of this region is also known as pinch-off to indicate the lack of channel region

Figure 3.1: A typical I-V characteristic of an nMOS transistor

near the drain. The drain current is now weakly dependent upon drain voltage and controlled primarily by the gate–source voltage.

Since the channel provides a conducting path for electric current, it can be considered as a resistor. The cross-sectional area of this resistor is higher at the source end and continuously decreases towards the drain end. When the gate voltage is greater than the threshold voltage,  $V_{gs} > V_{th}$  and  $V_{ds} \ge (V_{gs} - V_{th})$ , where  $V_{ds}$  is the drain voltage, the channel depth at drain end decreases to almost zero, and the channel is said to be pinched-off (Weste and Harris, 2004). Beyond the pinch-off, the depletion region around the drain end provides a path for the drain current to flow. In the channel thermal model the region between the pinch-off point and the drain end

can be considered as a region of uniform cross-section. The conductivity of this channel resistor depends on complex physical parameters including area, doping concentration, mobility of charge carriers etc. The channel is controlled between the oxide layer and the substrate layer in vertical direction, and controlled between the source well and the drain well in horizontal direction as shown in Figure 3.3.

Let us consider the case of an nMOS transistor. Initially, when the gate voltage  $V_{gs}$ is less than the threshold voltage  $V_{th}$ , and the drain voltage is at the same voltage as the source, an inversion layer is formed beneath the gate, and the channel is said to exist between the source and the drain. The inversion layer can be assumed to have a uniform cross-sectional area from the source end to the drain end of the transistor. Now, if the gate voltage is increased beyond the threshold voltage of the transistor, a sufficient number of electrons accumulate in the inversion layer to conduct electric current. The electric current increases with the increase in the gate voltage. Since the drain and the source are at same voltage at this point, the height of the inversion layer, and hence the channel remain uniform (Weste and Harris, 2004). Now, if the drain voltage is increased, the voltage causes an electric current to flow between the source and the drain. The electric current flowing in the channel  $I_{ds}$  will be proportional to the effective gate voltage  $V_{gs}$  –  $V_{th}$ , and to the voltage  $V_{ds}$  which causes  $I_{ds}$  to flow. Under these conditions the channel is said to be in the linear or ohmic region. As  $V_{DS}$  continues to increase, the channel height near the drain end starts decreasing. However, in the linear mode of operation, the channel height at the drain end is approximately the same as that at the source end  $(H_P \simeq 0.99H_O)$ . If  $V_{ds} > (V_{gs} - V_{th})$ ,  $I_{ds}$  no longer increases linearly and becomes constant. The transistor is said to operate in the saturation region or in

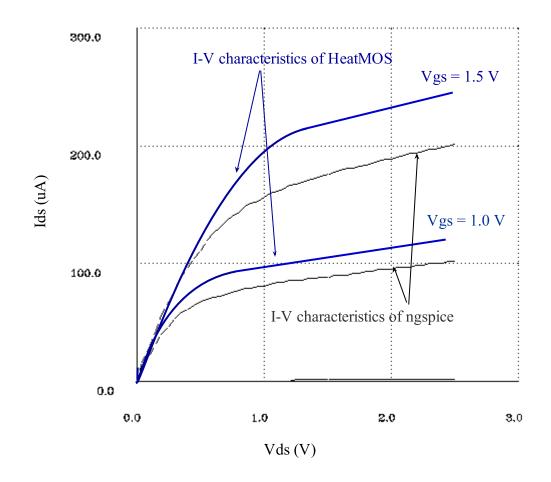

Figure 3.2: A comparison for I-V characteristics of an nMOS transistor

Figure 3.3: Simplified 2-D cross-section of an nMOS transistor

the on state. Other second order effects in the BSIM3 model such as drain-induced barrier lowering (DIBL), substrate current induced body effects (SCBE) have not been incorporated in HeatMOS<sup>©</sup> to calculate effective drain current, which are typically modeled in industrial quality SPICE simulators. A comparison of the the I-V characteristics of simplified device model used in HeatMOS<sup>©</sup> with the full BSIM3 model (ngspice simulator) is shown in Figure 3.2. The saturation current calculation equation will be explained in section 5.2.

#### **3.2.1** Channel Geometry for Thermal Model

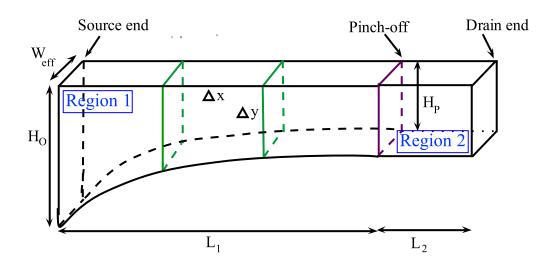

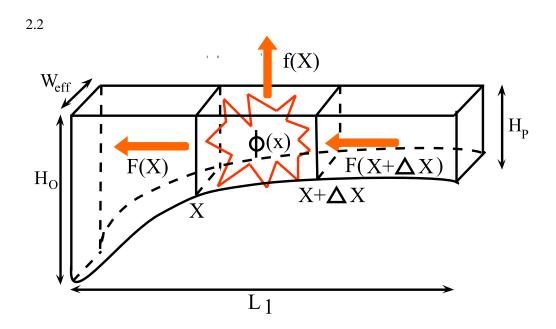

Figure 3.3 shows the channel region in a MOSFET. In the saturation region of operation the channel shrinks near the drain end and the drain current becomes almost constant. The drain current flows through the depletion region at the drain end. For the thermal model in saturation mode the channel is modeled as two separate regions.

• Region 1:

Region 1 is a channel of constant width  $W_{eff}$  and non-uniform height which tapers from the source end to the pinch-off point (Figure 3.4). This region is approximated by an exponential function of the form  $y = Ae^{-\alpha x}$  where where y is the vertical height and x is the horizontal length of the channel. An exponential function is selected for the model to lead to tractable analytic results and differs from the linear model used for the gradual channel approximation used to develop the electrical model for MOSFETs. However, the parameters A and  $\alpha$  in the exponential model are determined from the BSIM3 model parameters and are matched for the operating point of the device.

If  $L_1$  is the length of the channel between the source end and the pinch-off point,  $H_O$  is the height of the channel at the source end and  $H_P$  is the height of the channel at the pinch-off point then

$$x = 0 \Rightarrow y = H_0$$

$$x = L_1 \Rightarrow y = H_P$$

$$H_P = H_O e^{-\alpha L_1} \Rightarrow \alpha = \frac{1}{L_1} ln\left(\frac{H_O}{H_P}\right)$$

$$y = H_O e^{-\left\{\frac{1}{L_1} ln\left(\frac{H_O}{H_P}\right)\right\}x}$$

(3.1)

• Region 2:

Region 2 models the thermal conduction through the depletion region of the pinched off channel. In this region, the channel cross-section is uniform and has width  $W_{eff}$  and height  $H_P$ . The channel length in region 2 is denoted as  $L_2$ .

If L is the total length of the channel then

$$L = L_1 + L_2$$

Figure 3.4 shows the 3D view of channel formed beneath the gate.

Figure 3.4: 3D view of the channel geometry for thermal model

#### **3.2.2** Electrical Resistance

The conduction channel formed beneath the oxide layer is of non-uniform crosssectional area in nature from the source end to the pinch-off point and has uniform cross-sectional area from the pinch-off point to the drain end.

The resistance of non-uniform cross-sectional area of region 1 can be approximated by integrating the resistance of a differential slice over the length from 0 to  $L_1$ :

$$R_1 = \int_0^{L_1} \frac{\rho e^{\alpha x}}{W_{eff} H_O} dx = \frac{\rho}{W_{eff} H_O \alpha} \left( e^{\alpha L_1} - 1 \right)$$

(3.2)

$$\alpha = \frac{1}{L_1} ln \left( \frac{H_0}{H_P} \right) \tag{3.3}$$

$$L_{eff} = L_1 + L_2 \tag{3.4}$$

where,

$\rho$  = Electrical resistivity

$H_O$  = Height of channel at source end

$H_P$  = Height of channel at pinch-off point

$W_{eff}$  = Effective channel width

$L_1$  = Length of channel between source end and pinch-off point

$L_2$  = Length of channel between pinch-off point and drain end

$L_{eff}$  = Effective channel length

The effective channel length and width can be approximated by (Liu et al., 1999)

$$L_{eff} = L_{Drawn} - 2dL \tag{3.5}$$

$$W_{eff} = W_{Drawn} - 2dW \tag{3.6}$$

$$dW = W_{int} + \frac{W_l}{L^{W_{ln}}} + \frac{W_w}{W^{W_{wn}}} + \frac{W_{wl}}{L^{W_{ln}}W^{W_{wn}}}$$

(3.7)

$$dL = L_{int} + \frac{L_l}{L^{L_{ln}}} + \frac{L_w}{W^{L_{wn}}} + \frac{L_{wl}}{L^{L_{ln}}W^{L_{wn}}}$$

(3.8)

where,

$L_{Drawn}$  = Layout drawn length of transistor.

$W_{Drawn}$  = Layout drawn width of transistor.

$W_{int}, L_{int}, W_l, W_w, W_{wl}, W_{wn}, L_l, L_w, L_{wn}, L_{wl} = BSIM3$  parameters.

The electrical resistivity of the channel can be approximated as

$$\rho = \frac{1}{W_{eff}C_{ox}\mu_{eff}} \tag{3.9}$$

where,

$C_{ox}$  = Capacitance of oxide layer.

$\mu_{eff}$  = Effective mobility of charge carriers.

Region 2 has a uniform cross-sectional area. This can be considered as a uniform bar of length  $L_2$ , width  $W_{eff}$ , and height  $H_P$ . Its resistance is given by

$$R_2 = \frac{\rho L_2}{W_{eff} H_P} \tag{3.10}$$

#### 3.2.3 Channel Height Models

Initially when the channel starts taking its shape an inversion charge layer is formed beneath the oxide layer. The charge accumulates beneath the gate and forms an approximately uniform layer of a certain height and width from the source end to the drain end. It can also be approximated that when the channel takes on its nonuniform shape in the saturation region of operation, the drain end of the channel shrinks, while the source end of the channel remains same. The drain end of the channel shrinks to the height,  $H_P$ , the height at the pinch-off point. The height of the channel at the source end can be approximated by the thickness of the inversion layer (Masu and Tsubouchi, 1994).

The height of the channel at the source end is

$$H_O = t_{inv} = \frac{kT}{\sqrt{\frac{\varepsilon\varepsilon_o}{2qN_A\phi_s}}}$$

(3.11)

$$\phi_s = 2\frac{kT}{q} ln\left(\frac{N_A}{n_i}\right) \tag{3.12}$$

where,

k = Boltzmann's constant

T = Temperature

$\varepsilon$  = Dielectric constant

$\varepsilon_o$  = Permittivity of free space

q = Electron charge

$N_A$ = Substrate doping concentration

$n_i$  = Intrinsic silicon concentration

$\phi_s$  = Surface potential

We can approximate the height of the channel at the pinch off point  $H_P$  by the following method.

$$R_1 + R_2 = \frac{V_{DS}}{I_{sat}} \tag{3.13}$$

$$\frac{\rho\left(e^{\alpha L_{1}}-1\right)}{W_{eff}H_{O}\alpha}+\frac{\rho L_{2}}{W_{eff}H_{P}}=\frac{V_{DS}}{I_{sat}}$$

Under the approximation  $H_P <<<< H_O$ ,

$$H_P = \frac{\rho L_2 I_{sat}}{V_{DS} W_{eff}} \tag{3.14}$$

where

$I_{sat}$  = Electric current in saturation region of operation

$V_{DS}$  = Drain-Source voltage

The height of the channel at the drain end is the same as at the pinch-off point,  $H_P$ , as it is assumed that the channel becomes uniform in nature from the pinch-off point to the drain end.

## 3.2.4 Channel Length Models

The channel length between the pinch-off point and the drain can be calculated using the channel length modulation approximation (Park et al., 1991).

The length of the channel between the pinch-off point to the drain is

$$L_2 = \frac{V_{DS} - VDS'}{E_L} \tag{3.15}$$

where

$$E_L = \sqrt{rac{qN_a(V_{DS} - VDS')}{2arepsilon arepsilon_O}}$$

$$VDS' \simeq -v_{sat}L_{eff}/\mu_{eff}$$

$v_{sat}$  = Saturation velocity of charge carriers

So, the channel length between the source end and the pinch-off point is

$$L_1 = L_{eff} - L_2 \tag{3.16}$$

#### 3.2.5 Thermal Conductance

There are two kinds of thermal conductances: lateral thermal conductance and longitudinal thermal conductance. The conduction channel is formed beneath the oxide layer. The substrate can be approximated as having a uniform background temperature  $T^{ref}$ . The lateral thermal conductance must be taken to both the gate electrode above and a thermal reference somewhere in the substrate below. These may be combined into a single lateral conductance to a single, averaged reference temperature. Given the relative short channel length, when compared to the distant reference temperature (e.g substrate), the small variation in the height of the channel compared to that great distance is negligible. Therefore, the variation of thermal conductance ( $G^{lat}$ ) can be considered uniform along the length of the channel. For complex device structures a uniform, effective lateral thermal conduction simulations.

The longitudinal thermal conductance  $(G^{long})$  vary along the length of the channel and is of concern. Since the height of the channel is not uniform, a tractable solution to the heat equation arises if we can drive an expression of average thermal conductance in a similar manner to the electrical resistance of the channel. This weights the thermal conductance according to the localization of the heat source.

The average longitudinal thermal conductance is

$$G_{avg}^{long} = \frac{1}{L_{eff}} \int_{0}^{L_{eff}} G(x) dx$$

(3.17)

where  $L_{eff}$  is the effective channel length.

The longitudinal thermal conductance along the length is

$$G^{long}(x) = G_O e^{\gamma x} \tag{3.18}$$

where

$$\gamma = -rac{1}{L_{eff}}ln\left[rac{G_O}{G_L}

ight]$$

$G_O$  = Thermal conductance per unit length at source end (i.e. when  $x = 0 \Rightarrow$  $G^{long}(x = 0) = G_O$ ).

$G_L$  = Thermal conductance per unit length at drain end (i.e. when  $x = L \Rightarrow$  $G^{long}(x = L) = G_L$ ).

The solution to the equation 3.17 is

$$G_{avg}^{long} = \frac{G_O}{\gamma L_{eff}} \left[ e^{\gamma L_{eff}} - 1 \right]$$

(3.19)

If  $\lambda$  is the thermal conductivity of channel, then  $G_O = \frac{H_O W_{eff}}{\lambda}$  and  $G_L = \frac{H_P W_{eff}}{\lambda}$ .

Figure 3.5: 3D view of region 1 of the channel

# **3.3** Solution of the Heat Equation

The basic heat equation 2.2 is solved for both regions in the following sections.

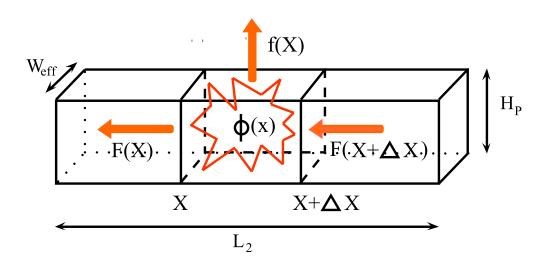

# 3.3.1 Region 1: Non-uniform cross-sectional area

Figure 3.5 shows region 1 of the channel.

For a differential length  $\triangle x$  of the channel,

$$\phi(x) \triangle x = I_{DS}^2 R(x) \triangle x$$

$$R(x) \triangle x = \frac{\rho \triangle x}{W_{eff} H_O} e^{\alpha x}$$

where  $I_{DS}$  is the drain current.

The heat flux can be written as

$$F(x) = G_{avg}^{long} \frac{\partial T(x)}{\partial x}$$

$$F(x + \triangle x) = G_{avg}^{long} \frac{\partial T(x + \triangle x)}{\partial x}$$

$$f(x) = G^{lat}\left(T(x) - T^{ref}\right)$$

In the limit when  $\triangle x \rightarrow 0$ , the basic heat equation 2.2 takes the form of the 2nd order non-homogeneous differential equation.

$$G_{avg}^{long} \frac{d^2 T}{dx^2} - G^{lat} \left( T(x) - T^{ref} \right) + \frac{I_{DS}^2 \rho}{W_{eff} H_O} e^{\alpha x} = 0$$

(3.20)

If the temperature function for region 1 is  $T_1(x)$ , equation 3.20 can be written as

$$G_{avg}^{long} \frac{d^2 T_1}{dx_1^2} - G^{lat} \left( T_1(x_1) - T^{ref} \right) + \frac{I_{DS}^2 \rho}{W_{eff} H_O} e^{\alpha x_1} = 0$$

(3.21)

The solution of non-homogeneous differential equation 3.21 can be written as

$$T_1(x_1) = C_1 e^{\xi_1 x_1} + C_2 e^{-\xi_1 x_1} + T^{ref} - \frac{\Psi^2}{\alpha^2 - \xi_1^2} e^{\alpha x_1}$$

(3.22)

where

$$\xi_1 = \sqrt{rac{G^{lat}}{G^{long}_{avg}}}$$

$$\Psi = \sqrt{\frac{I_{sat}^2 \rho}{W_{eff} H_O G_{avg}^{long}}}$$

$$K_1 = \frac{\Psi^2}{\alpha^2 - \xi_1^2}$$

$C_1$  and  $C_2$  are constants whose values will be determined.

# 3.3.2 Region 2: Uniform cross-sectional area

Figure 3.6 shows the 3D view of region 2 of the channel. The total resistance in region 2 is denoted as  $R_2$ .

For a differential length  $\triangle x$  of the channel

Figure 3.6: 3D view of the region 2 of the channel

$$\phi(x) \triangle x = I_{DS}^2 \left(\frac{R_2}{L_2}\right) \triangle x$$

The heat flux can be written as

$$F(x) = G_{avg}^{long} \frac{\partial T(x)}{\partial x}$$

$$F(x + \triangle x) = G_{avg}^{long} \frac{\partial T(x + \triangle x)}{\partial x}$$

$$f(x) = G^{lat}\left(T(x) - T^{ref}\right)$$

In the limit when  $\triangle x \rightarrow 0$ , the basic heat equation 2.2 takes the form of the secondorder non-homogeneous differential equation 3.23.

$$G_{avg}^{long} \frac{d^2 T}{dx^2} - G^{lat} \left( T(x) - T^{ref} \right) + I_{DS}^2 R_2 = 0$$

(3.23)

If the temperature function of region 2 is  $T_2(x)$ , the equation 3.23 can be written as

$$G_{avg}^{long}\frac{d^2T_2}{dx_2^2} - G^{lat}\left(T_2(x_2) - T^{ref}\right) + I_{DS}^2 R_2 = 0$$

(3.24)

The solution of differential equation 3.24 can be written as

$$T_2(x_2) = D_1 e^{\xi_2 x_2} + D_2 e^{-\xi_2 x_2} + \frac{\beta}{\xi_2^2}$$

(3.25)

where

$$\xi_2 = \sqrt{\frac{G_2^{lat}}{G_{avg}^{long}}}$$

$$\beta = -\frac{G_2^{lat}}{G_{avg}^{long}}T^{ref} - \frac{I_{DS}^2}{G_{avg}^{long}}R_2$$

$$K_2=\frac{\beta}{\xi_2^2}$$

$D_1$  and  $D_2$  are constants whose values will be determined using the boundary conditions.

#### 3.3.3 Boundary Conditions and Complete Solution

The channel is between the source end and the drain end. The end point temperatures are determined by the boundary conditions. If the temperature of the source end is  $T_O$  and the drain end is  $T_L$ , then the two boundary conditions can be written as

$$T_1(x_1) \mid_{x_1=0} = T_O \tag{3.26}$$

$$T_2(x_2)|_{x_2=L_2} = T_L \tag{3.27}$$

Since the channel is one entity, the pinch-off point is a virtual point. The temperature at the pinch-off point as determined by equation 3.22 should be the same as it is determined by equation 3.25. Further the heat flux leaving region 1 enters into region 2. These facts give us two more conditions:

$$T_1(x_1) \mid_{x_1 = L_1} = T_2(x_2) \mid_{x_2 = 0}$$

(3.28)

$$G_{avg}^{long} \frac{dT_1}{dx_1} \mid_{x_1 = L_1} = G_{avg}^{long} \frac{dT_2}{dx_2} \mid_{x_2 = 0}$$

(3.29)

Using equations 3.22, 3.25, 3.26, 3.27, 3.28, and 3.29, the unknown coefficients,  $C_1$ ,  $C_2$ ,  $D_1$ , and  $D_2$  can be calculated. The values of these coefficients are given below.

$$T_O = C_1 + C_2 + T^{ref} - \frac{\Psi^2}{\alpha^2 - \xi_1^2}$$

(3.30)

$$T_L = D_1 e^{\xi_2 L_2} + D_2 e^{-\xi_2 L_2} + \frac{\beta}{\xi_2^2}$$

(3.31)

$$C_1 e^{\xi_1 L_1} + C_2 e^{-\xi_1 L_1} + T^{ref} - \frac{\Psi^2}{\alpha^2 - \xi_1^2} = D_1 + D_2 + \frac{\beta}{\xi_2^2}$$

(3.32)

$$G_{avg}^{long}\left(C_{1}\xi_{1}e^{\xi_{1}L_{1}}-C_{2}\xi_{1}e^{-\xi_{1}L_{1}}-\alpha\frac{\Psi^{2}}{\alpha^{2}-\xi_{1}^{2}}e^{\alpha L_{1}}\right)=G_{avg}^{long}\left(D_{1}\xi_{2}-D_{2}\xi_{1}\right) \quad (3.33)$$

$$C_1 = C_1' - C_1'' \tag{3.34}$$

$$D_1 = D_1^{'} - D_1^{''} \tag{3.35}$$

where

$$C_{1}^{'} = \frac{\left(\xi_{2} + \xi_{2}e^{2\xi_{2}L_{2}}\right)}{\left(e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}}\right)\left(1 + e^{2\xi_{2}L_{2}}\right)\xi_{2} - \left(e^{\xi_{1}L_{1}} + e^{-\xi_{1}L_{1}}\right)\left(1 - e^{2\xi_{2}L_{2}}\right)} \times \\ \left\{T_{L}e^{\xi_{2}L_{2}} - \left(T_{O} - T^{ref}\right)e^{-\xi_{1}L_{1}} - T^{ref} + \frac{\Psi^{2}}{\alpha^{2} - \xi_{1}^{2}}\left(e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}}\right) + \frac{\beta}{\xi_{2}^{2}}\left(1 - e^{\xi_{2}L_{2}}\right)\right\}$$

$$D_{1}^{'} = \frac{\left(e^{\xi_{1}L_{1}} + e^{-\xi_{1}L_{1}}\right)}{\left(e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}}\right)\left(1 + e^{2\xi_{2}L_{2}}\right)\xi_{2} - \left(e^{\xi_{1}L_{1}} + e^{-\xi_{1}L_{1}}\right)\left(1 - e^{2\xi_{2}L_{2}}\right)} \times \left\{T_{L}e^{\xi_{2}L_{2}} - (T_{O} - T^{ref})e^{-\xi_{1}L_{1}} - T^{ref} + \frac{\Psi^{2}}{\alpha^{2} - \xi_{1}^{2}}\left(e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}}\right) + \frac{\beta}{\xi_{2}^{2}}(1 - e^{\xi_{2}L_{2}})\right\}$$

$$C_{1}^{''} = \frac{\left(1 - e^{2\xi_{1}L_{1}}\right)}{\left(e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}}\right)\left(1 + e^{2\xi_{2}L_{2}}\right)\xi_{2} - \left(e^{\xi_{1}L_{1}} + e^{-\xi_{1}L_{1}}\right)\left(1 - e^{2\xi_{2}L_{2}}\right)} \times \\ \left\{\left(T_{O} - T^{ref}\right)\xi_{1}e^{-\xi_{1}L_{1}} - T_{L}e^{\xi_{2}L_{2}}\xi_{2} + \frac{\Psi^{2}}{\alpha^{2} - \xi_{1}^{2}}\left(\alpha e^{\alpha L_{1}} + \xi_{1}e^{-\alpha L_{1}}\right) + \frac{\beta}{\xi_{2}^{2}}\xi_{2}e^{\xi_{2}L_{2}}\right\}$$

$$\begin{split} D_1'' &= \frac{\left(e^{\xi_1 L_1} - e^{-\xi_1 L_1}\right)}{\left(e^{\xi_1 L_1} - e^{-\xi_1 L_1}\right)\left(1 + e^{2\xi_2 L_2}\right)\xi_2 - \left(e^{\xi_1 L_1} + e^{-\xi_1 L_1}\right)\left(1 - e^{2\xi_2 L_2}\right)} \times \\ & \left\{ (T_O - T^{ref})\xi_1 e^{-\xi_1 L_1} - T_L e^{\xi_2 L_2}\xi_2 + \right. \\ & \left. \frac{\Psi^2}{\alpha^2 - \xi_1^2} (\alpha e^{\alpha L_1} + \xi_1 e^{-\alpha L_1}) + \right. \\ & \left. \frac{\beta_2}{\xi_2^2}\xi_2 e^{\xi_2 L_2} \right\} \end{split}$$

$$C_2 = T_O - C_1 - T^{ref} + \frac{\Psi^2}{\alpha^2 - \xi_1^2}$$

$$D_2 = T_L e^{\xi_2 L_2} - D_1 e^{2\xi_2 L_2} - \frac{\beta}{\xi_2^2} e^{\xi_2 L_2}$$

The temperature of the channel along its length from the source end to the drain end can be written as

$$T(x) = \begin{cases} T_1(x_1), & 0 \le x_1 \le L_1 for \\ 0 \le x_2 \le L_2 for \\ L_1 \le x \le L \end{cases}$$

(3.36)

where

$$L = L_1 + L_2 \tag{3.37}$$

## 3.3.4 The Average Channel Temperature

The average temperature of the channel can be found by integrating the temperature function over the length and by dividing the total length.

$$T_{avg} = \frac{1}{2} \left[ \frac{1}{L_1} \int_{0}^{L_1} T_1(x_1) dx_1 + \frac{1}{L_2} \int_{0}^{L_2} T_2(x_2) dx_2 \right]$$

$$T_{avg} = \frac{1}{2} \left[ \frac{1}{L_1} \int_0^{L_1} \left\{ C_1 e^{\xi_1 x_1} + C_2 e^{-\xi_1 x_1} + T^{ref} - K_1 e^{\alpha_1 x_1} \right\} dx_1 + \frac{1}{L_2} \int_0^{L_2} \left\{ D_1 e^{\xi_2 x_2} + D_2 e^{-\xi_2 x_2} + K_2 \right\} dx_2 \right]$$

$$T_{avg} = \frac{1}{2L_1} \left\{ \frac{C_1}{\xi_1} \left( e^{\xi_1 L_1} - 1 \right) - \frac{C_2}{\xi_1} \left( e^{-\xi_1 L_1} - 1 \right) + L_1 T^{ref} - \frac{K_1}{\alpha_1} \left( e^{\alpha_1 L_1} - 1 \right) \right\} + \frac{1}{2L_2} \left\{ \frac{D_1}{\xi_2} \left( e^{\xi_2 L_2} - 1 \right) - \frac{D_2}{\xi_2} \left( e^{-\xi_2 L_2} - 1 \right) + K_2 L_2 \right\}$$

## 3.3.5 The Maximum Channel Temperature

If  $T_1^{max}$  is the maximum temperature given by the temperature function  $T_1(x)$  and  $T_2^{max}$  is the maximum temperature given by the temperature function  $T_2(x)$ ,

$$\frac{dT_1}{dx_1} = 0 \Rightarrow x_1 = x_1^{max}$$

$$T_1^{max} = T_1(x_1) \mid_{x_1 = x_1^{max}}$$

$$\frac{dT_2}{dx_2} = 0 \Rightarrow x_2 = x_2^{max}$$

$$T_2^{max} = T_2(x_2) \mid_{x_2 = x_2^{max}}$$

where  $0 \le x_1^{max} \le L_1$  and  $0 \le x_2^{max} \le L_2$ .

The maximum channel temperature  $T_{max}$  at a distance  $x_{max}$  along the length of the channel from the source end to the drain end is the greatest of  $T_1^{max}$  and  $T_2^{max}$ .

If

$$T_1^{max} \ge T_2^{max} \Rightarrow T_{max} = T_1^{max}$$

and  $x_{max} = x_1^{max}$ .

If  $T_2^{max} > T_1^{max} \Rightarrow T_{max} = T_2^{max}$  and  $x_{max} = L_1 + x_2^{max}$ .

For  $x_2^{max}$ :

$$D_1\xi_2 e^{\xi_2 x_2^{max}} - D_2\xi_2 e^{-\xi_2 x_2^{max}} = 0$$

$$x_2^{max} = \frac{1}{2\xi_2} ln \left[ \frac{D_2}{D_1} \right]$$

For  $x_1^{max}$ :

$$C_1\xi_1e^{\xi_1x_1^{max}} - C_2\xi_1e^{-\xi_1x_1^{max}} - K_1\alpha_1e^{\alpha_1x_1^{max}} = 0$$

The above equation for  $x_1^{max}$  does not have a closed form solution and a numerical solution is needed. It is not feasible to calculate  $x_1^{max}$  under these conditions. However, the maximum temperature along the length can be calculated via a simple technique. The channel is subdivided into small lengths and at each point T(x). After calculating all the values at each point, the maximum channel temperature can be found.

#### 3.3.6 The Channel Temperature at Pinch-off

The channel temperature at pinch-off point  $T_{pinch}$  is given as

$$T_{pinch} = T_1(x_1) \mid_{x_1 = L_1}$$

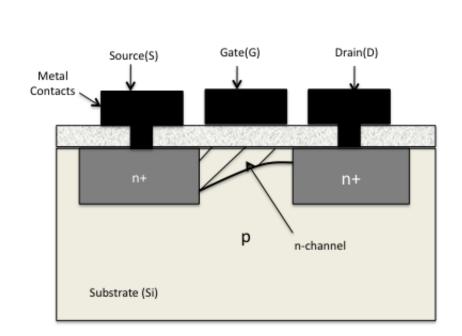

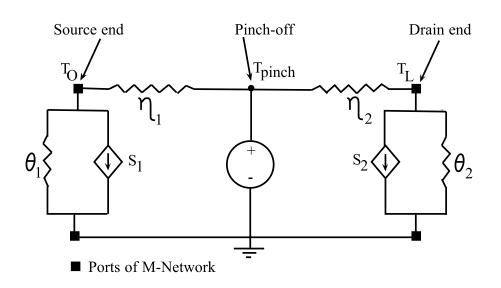

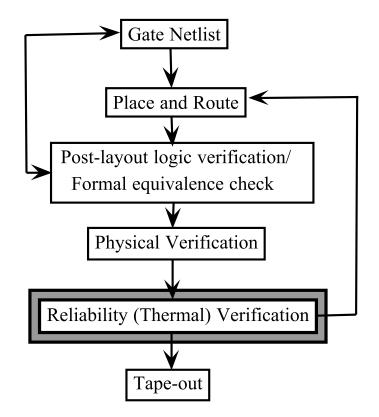

# **3.4** M-Network Representation of the Channel

The analytical solution gives promising results. HeatMOS<sup>©</sup> is able to do a thermal analysis of the transistor channel and estimates temperature along its length. The approach can be used for a complete micro-chip electro-thermal reliability verification. In a complete micro-chip EMR verification methodology, each of the resistors that forms a net is represented by an equivalent interconnect network (Labun and

Jagjitkumar, 2008) and (Alam et al., 2007). Based on this research work an equivalent M-network model is proposed to model channel temperature. The M-network model is shown in Figure 3.7 and can be used to integrate the channel temperature into a full micro-chip thermal analysis. The channel has two regions with conductance  $\eta_1$  and  $\eta_2$  corresponding to region 1 and 2 of the channel respectively. The current sources  $S_1$  and  $S_2$  correspond to the source end and the drain end of the channel, respectively. The currents at the nodes of the M-network are given by  $F_O$  (at the source end) and  $F_L$  (at the drain end). The temperature at the source and the drain end are  $T_O$  and  $T_L$  respectively. The temperature at the pinch-off point  $T_{pinch}$  (the junction of region 1 and region 2 in the channel) corresponds to a voltage source at pinch-off point. The source end and drain end are the ports of a M-network. The additional conductances  $\theta_1$  and  $\theta_2$ , correspond to the source end and the drain end respectively. These conductances represent a conduction path to ground that is not usually important electrically (and so for electrical analysis,  $\theta_1, \theta_2 = 0$ ) but will be important thermally (and so for thermal analysis,  $\theta_1, \theta_2 > 0$ ).

The heat currents,  $F_O$  and  $F_L$ , can be given by

$$F_O = G_{avg}^{long} \frac{dT_1}{dx} \mid x = 0 \tag{3.38}$$

$$F_L = G_{avg}^{long} \frac{dT_2}{dx} \mid x = L_2 \tag{3.39}$$

Kirchhoff's current law can be applied to the both sides of the M-network of Figure

Figure 3.7: Resistor M-network used for EMR verification

3.7.

$$F_{O} = \eta_{1} T_{pinch} - (\eta_{1} + \theta_{1}) T_{O} - S_{1}$$

(3.40)

$$F_L = (\eta_2 + \theta_2) T_L - \eta_2 T_{pinch} + S_2 \tag{3.41}$$

where

$$T_{pinch} = C_1 e^{\xi_1 L_1} + C_2 e^{-\xi_1 L_1} + T^{ref} - K_1 e^{\alpha_1 L_1}$$

Equations 3.38, 3.39 can be solved and compared with equations 3.40, 3.41 to find

out the values of  $\eta_1, \eta_2, \theta_1, \theta_2, S_1$ , and  $S_2$ .

$$\eta_1 = G_{avg}^{long} 2\xi_1$$

$$\theta_1 = G_{avg}^{long} \frac{4\xi_1\xi_2}{M} e^{-\xi_1 L_1} + G_{avg}^{long} \xi_1 - \eta_1 \left\{ \frac{2\xi_2 e^{-\xi_1 L_1}}{M} + 1 \right\} + e^{-\xi_1 L_1}$$

$$S_{1} = G_{avg}^{long} \left\{ \frac{2\xi_{1}}{M} \gamma_{1} - K_{1} \left( \alpha_{1} + \xi_{1} \right) \right\} - T^{ref} \xi_{1} - \frac{\eta_{1}}{M} \left\{ e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}} \right\} \gamma_{1} - T^{ref} e^{-\xi_{1}L_{1}} + T^{ref} + K_{1} \left\{ e^{-\xi_{1}L_{1}} - e^{\alpha_{1}L_{1}} \right\}$$

$$\begin{split} \eta_2 = -\frac{e^{\xi_1 L_1}}{\left(e^{\xi_1 L_1} - e^{-\xi_1 L_1}\right)} &\left\{ \frac{M e^{-\xi_1 L_1}}{2\xi_2} + G^{long}_{avg} e^{\xi_2 L_2} e^{-\xi_1 L_1} \left[ \left(e^{\xi_1 L_1} + e^{-\xi_1 L_1}\right) \right. \right. \\ \left. + \xi_1 \left(e^{\xi_1 L_1} - e^{-\xi_1 L_1}\right) \right] \\ \end{split}$$

$$\theta_{2} = \eta_{2} \left\{ \frac{2\xi_{2}e^{\xi_{2}L_{2}}\left(e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}}\right)}{M} - 1 \right\} - G_{avg}^{long} \left\{ \frac{2\xi_{2}}{M}e^{2\xi_{2}L_{2}}\left[\left(e^{\xi_{1}L_{1}} + e^{-\xi_{1}L_{1}}\right) + \xi_{2}\left(e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}}\right)\right] - \xi_{2} \right\}$$

$$S_{2} = G_{avg}^{long} \left\{ \xi_{2}K_{2} + \frac{2\xi_{2}e^{\xi_{2}L_{2}}}{M}\gamma_{2} \right\} + T^{ref} \left\{ e^{-\xi_{1}L_{1}} - 1 \right\} - K_{1} \left\{ e^{-\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}} \right\} - e^{\alpha_{1}L_{1}} \left\{ e^{\xi_{1}L_{1}} - e^{-\xi_{1}L_{1}} \right\} \gamma_{1}$$

where

$$M = \left(e^{\xi_1 L_1} - e^{-\xi_1 L_1}\right) \left(1 + e^{2\xi_2 L_2}\right) \xi_2 - \left(e^{\xi_1 L_1} + e^{-\xi_1 L_1}\right) \left(1 - e^{2\xi_2 L_2}\right)$$

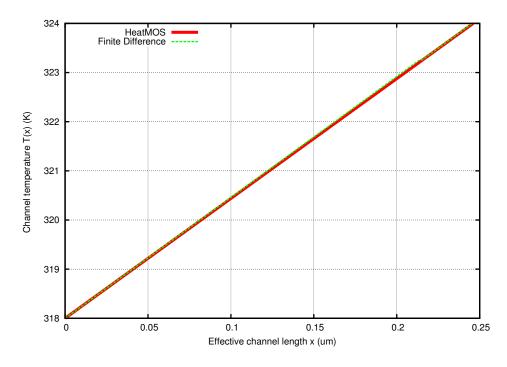

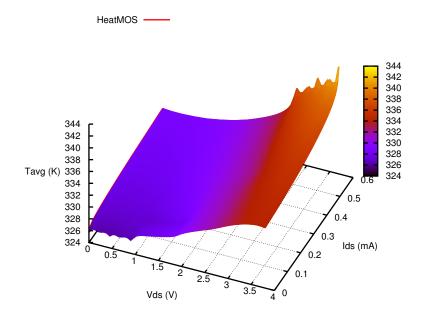

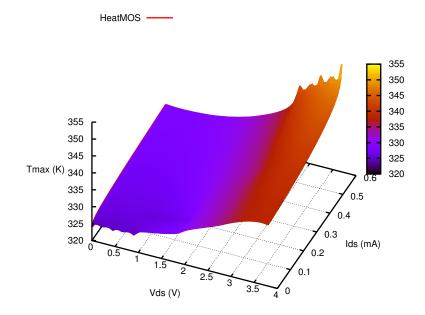

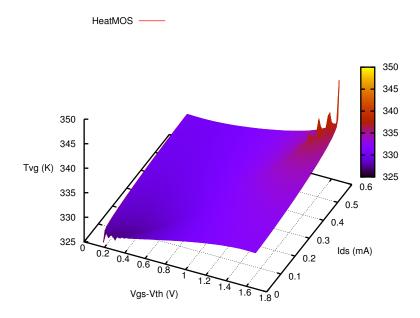

$$\begin{split} \gamma_{1} &= \xi_{2} \left( 1 + e^{2\xi_{2}L_{2}} \right) \left\{ -T^{ref} \left( e^{-\xi_{1}L_{1}} + 1 \right) + K_{1} \left( e^{\alpha_{1}L_{1}} - e^{-\xi_{1}L_{1}} \right) + K_{2} \left( 1 - e^{\xi_{2}L_{2}} \right) \right\} \\ &+ \left( 1 - e^{2\xi_{2}L_{2}} \right) \left\{ -T^{ref}\xi_{1}e^{-\xi_{1}L_{1}} + K_{1} \left( \alpha_{1}e^{\alpha_{1}L_{1}} + \xi_{1}e^{-\xi_{1}L_{1}} \right) \right. \\ &+ K_{2}\xi_{2}e^{\xi_{2}L_{2}} \right\} \end{split}$$