## **On Replay and Hazards in Graphics Processing Units**

by

Andrew E. Turner

B.A.Sc., B.A, University of British Columbia, 2007

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### **Masters of Applied Science**

in

#### THE FACULTY OF GRADUATE STUDIES

(Electrical and Computer Engineering)

The University Of British Columbia (Vancouver)

August 2012

© Andrew E. Turner, 2012

## Abstract

Graphics Processing Units (GPUs) have potential for more efficient execution of programs, both time wise and energy wise. They can achieve this by devoting more of their hardware for functional units. GPGPU-Sim is modified to simulate an aggressively modern compute accelerator and used to investigate the impact of hazards in massively multithreaded accelerator architectures such as those represented by modern GPUs employing a single-instruction, multiple thread (SIMT) execution model. Hazards are events that occur in the execution of a program which limit performance. We explore design tradeoffs in hazard handling. We find that in common architectures hazards that stall the pipeline cause other unrelated threads to be unable to make forward progress. This thesis explores an alternative organization, called replay, in which instructions from other threads can make forward progress. This replay architecture can behave pathologically in some cases by excessively replaying without forward progress. A method which predicts when hazards may occur and thus can reduce the number of unnecessary replays and improve performance is proposed and evaluated. This method is found to improve performance up to 13.3% over the stalling baseline, and up to 3.3% over replay.

# **Table of Contents**

| Al             | bstrac  | t                                      | ii                                        |  |  |  |  |

|----------------|---------|----------------------------------------|-------------------------------------------|--|--|--|--|

| Ta             | ble of  | f Contei                               | ts iii                                    |  |  |  |  |

| List of Tables |         |                                        |                                           |  |  |  |  |

| Li             | st of H | •••••••••••••••••••••••••••••••••••••• |                                           |  |  |  |  |

| Gl             | lossar  | у                                      | vi                                        |  |  |  |  |

| A              | cknow   | ledgme                                 | nts                                       |  |  |  |  |

| 1              | Intro   | oductio                                | · · · · · · · · · · · · · · · · · · ·     |  |  |  |  |

|                | 1.1     | Overvi                                 | ew 1                                      |  |  |  |  |

|                |         | 1.1.1                                  | Computer Architecture                     |  |  |  |  |

|                |         | 1.1.2                                  | Architecture Basics                       |  |  |  |  |

|                |         | 1.1.3                                  | Monolithic CPU Strategies                 |  |  |  |  |

|                |         | 1.1.4                                  | Compute Accelerators                      |  |  |  |  |

|                |         | 1.1.5                                  | Programming Languages                     |  |  |  |  |

|                |         | 1.1.6                                  | Instruction / Data Flow in GPUs           |  |  |  |  |

|                |         |                                        | 1.1.6.1 Fetch / Warp Buffer / Scheduler 9 |  |  |  |  |

|                |         |                                        | 1.1.6.2 Mask Stage                        |  |  |  |  |

|                |         |                                        | 1.1.6.3 Operand Collector                 |  |  |  |  |

|                |         |                                        | 1.1.6.4 Functional Units                  |  |  |  |  |

|                |         |                                        | 1.1.6.5 Write Back                        |  |  |  |  |

|                |         | 1.1.7                                  | Hazards in the Pipeline                   |  |  |  |  |

|                | 1.2     | Contri                                 | utions                                    |  |  |  |  |

|                |         | 1.2.1                                  | GPGPU-Sim Modifications 17                |  |  |  |  |

|                |         | 1.2.2                                  | Replay Analysis and Characterization      |  |  |  |  |

|                |         | 1.2.3                                  | Hazard Prediction                         |  |  |  |  |

|                | 1.3     | Thesis                                 | Organization                              |  |  |  |  |

|                |         |                                        |                                           |  |  |  |  |

| 2 | Rela | ted Wo                                   | rk                    | ••••        | • • • • | •••     | •••   | • •  | •   | ••• | ••• | • | •  | ••  | ••  | • | ••  | ••  | • | 19         |

|---|------|------------------------------------------|-----------------------|-------------|---------|---------|-------|------|-----|-----|-----|---|----|-----|-----|---|-----|-----|---|------------|

| 3 | The  | Problem                                  | n: Throug             | hput Red    | ductio  | n Due   | to H  | [aza | rds | 5   |     | • | •  |     |     | • | ••  | ••  | • | 22         |

|   | 3.1  | 3.1 Taxonomy of the Solution Space       |                       |             |         |         |       |      |     |     | 23  |   |    |     |     |   |     |     |   |            |

|   | 3.2  | ALU/                                     | MEM Inst              | ruction M   | fix     |         |       |      |     |     |     |   | •  |     |     |   |     |     |   | 23         |

|   | 3.3  | MEM /                                    | ' ALU Para            | allelism ir | n the F | ront E  | nd.   |      |     |     |     |   | •  |     |     |   |     |     |   | 25         |

|   | 3.4  | .4 MEM / ALU Parallelism in the Back End |                       |             |         |         |       |      |     |     |     |   | 25 |     |     |   |     |     |   |            |

|   |      | 3.4.1                                    | Decreasir             | ng MEM /    | / ALU   | Intera  | ction |      |     |     |     |   | •  |     |     |   |     |     |   | 26         |

|   |      |                                          | 3.4.1.1               | Multiple    | Pipeli  | nes.    |       |      |     |     |     |   | •  |     |     |   |     |     |   | 26         |

|   |      |                                          | 3.4.1.2               | Operand     | Collec  | ctor .  |       |      |     |     |     |   | •  |     |     |   |     |     |   | 26         |

|   |      | 3.4.2                                    | Decrease              | Hazards     | or The  | ir Effe | ct.   |      |     |     |     |   | •  |     |     |   |     |     |   | 27         |

|   |      |                                          | 3.4.2.1               | Replay      |         |         |       |      |     |     |     |   | •  |     |     |   |     |     |   | 28         |

|   |      |                                          | 3.4.2.2               | Hazard F    | Predict | ion .   |       |      |     |     |     |   | •  |     |     |   |     |     |   | 28         |

|   | 3.5  | Estima                                   | ting Perfor           | mance Lo    | oss Du  | e To H  | Iazar | ds . |     |     |     | • | •  |     |     | • |     |     |   | 29         |

| 4 | Met  | hadalag                                  | у                     |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 32         |

| • | 4.1  | 0                                        | narks                 |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 32         |

|   | 4.2  |                                          | ne Architec           |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 32         |

|   | 4.3  |                                          | cations to            |             | •       |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 32         |

|   | 4.5  | 4.3.1                                    | Configura             |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 34         |

|   |      | 4.3.2                                    | Memory                | _           |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 34         |

|   |      | 4.3.3                                    | Replay                |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 34         |

|   |      | 4.3.4                                    | Hazard P              |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 35         |

| 5 | Rep  | ov                                       |                       |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 36         |

| 3 | 5.1  | -                                        | •••••<br>Motivation   |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | <b>3</b> 6 |

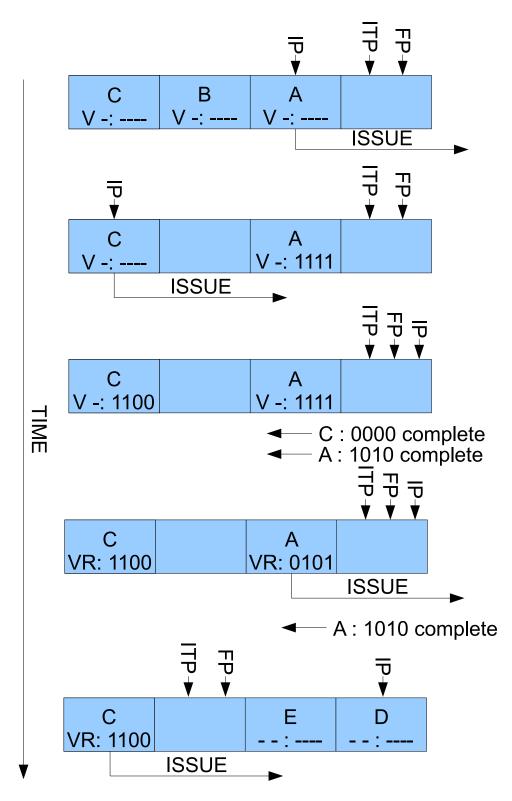

|   | 5.2  |                                          | ne Replay l           | -           | •       |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 38         |

|   | 5.2  | 5.2.1                                    | Fundame               | •           |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 38         |

|   |      |                                          | Overview              |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 38         |

|   |      | 5.2.2                                    |                       |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 38<br>39   |

|   |      | 5.2.5<br>5.2.4                           | Schedulir<br>Replay w | •           |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 39<br>40   |

|   |      | 5.2.4<br>5.2.5                           | ~ •                   |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 40<br>42   |

|   | 5.3  |                                          | Notes on<br>Example   | -           |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 42<br>42   |

|   | 0.0  | reepidy                                  | Example               |             |         | •••     |       | • •  | •   |     |     | • | •  | ••• | ••• | • | ••• | ••• | • | 12         |

| 6 | Haza | ard Avo                                  | idance .              | • • • • •   | • • • • | •••     | •••   | • •  | •   | ••• | ••• | • | •  | ••  | ••  | • | ••  | ••  | • | 46         |

|   |      | 6.0.1                                    | MSHR T                |             |         |         |       |      |     |     |     |   |    |     |     |   |     |     |   | 48         |

|   | 6.1  | MSHR                                     | Use Predi             | ctors       |         |         |       | • •  | •   |     | • • | • | •  |     | • • | • | ••• |     | • | 49         |

| 7 | Disc | ussion                                   |                       |             |         |         |       |      | •   |     |     | • | •  |     |     | • |     |     | • | 51         |

|    | 7.1    | Analys   | is of Architecture Configurations                       | 51 |

|----|--------|----------|---------------------------------------------------------|----|

|    |        | 7.1.1    | Warp Buffer Penalty                                     | 51 |

|    |        | 7.1.2    | Performance of Operand Collector Composition and Sizing | 52 |

|    |        | 7.1.3    | Dual Scheduler Performance                              | 53 |

|    | 7.2    | Hazard   | Prediction                                              | 55 |

|    |        | 7.2.1    | Predictors                                              | 58 |

|    |        | 7.2.2    | Trackers                                                | 62 |

|    |        | 7.2.3    | Hazard Prediction Without Replay                        | 62 |

|    |        | 7.2.4    | Power                                                   | 63 |

|    | 7.3    | Compa    | aring Across All ALU / MEM Hazard Management Techniques | 64 |

| 8  | Con    | clusions | 8                                                       | 65 |

|    | 8.1    | Future   | Work                                                    | 66 |

| Bi | bliogr | aphy .   |                                                         | 67 |

# **List of Tables**

| Table 4.1 | Benchmark abbreviations, classifications, descriptions and sources. Benchmarks    |    |

|-----------|-----------------------------------------------------------------------------------|----|

|           | are classified qualitatively (missing qualifications default to the most common). |    |

|           | Max.Pred.Speedup: Maximum Predicted Speedup (default: low). Occ.: Average         |    |

|           | Thread Activity (default: high). Hazards: Amount of hazards (default: very        |    |

|           | few). MSHR Hazard: Amount of MSHR hazards (default: very few)                     | 33 |

| Table 4.2 | Baseline architecture configuration.                                              | 34 |

| Table 7.1 | "Predictor" predictor accuracy ratios.                                            | 59 |

# **List of Figures**

| Figure 1.1 | Simple core architecture.                                                          | 2  |

|------------|------------------------------------------------------------------------------------|----|

| Figure 1.2 | Conceptual thread grouping and execution on a GPU                                  | 7  |

| Figure 1.3 | Baseline chip and core architecture. (a) Chip architecture, (b) Core architecture. | 10 |

| Figure 1.4 | Example of stall propagation.                                                      | 14 |

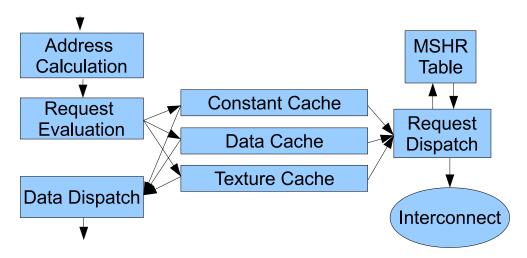

| Figure 1.5 | Memory Stage components.                                                           | 15 |

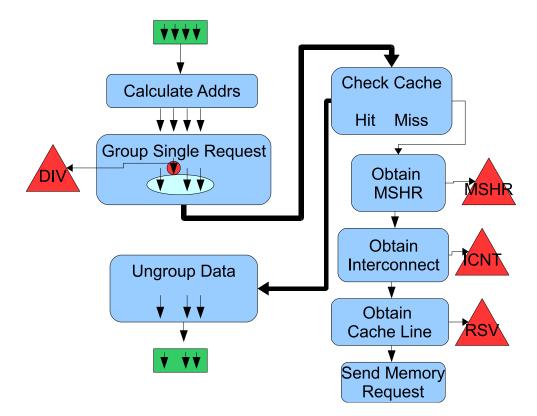

| Figure 1.6 | Memory Stage flow chart for a Global Memory load.                                  | 16 |

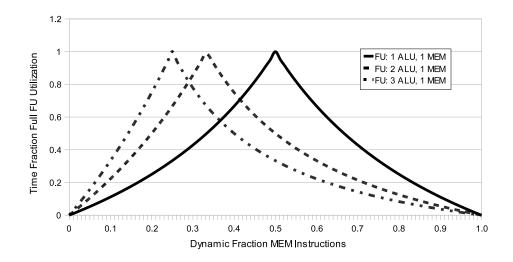

| Figure 3.1 | Full functional unit occupation for different dynamic instruction mix ratios.      |    |

|            | Each ALU or MEM functional unit has a single instruction per cycle throughput.     | 24 |

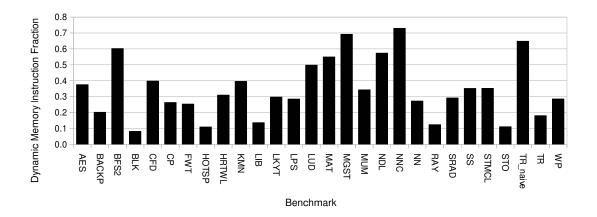

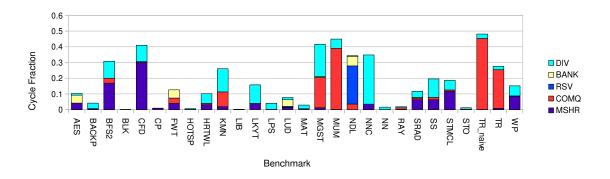

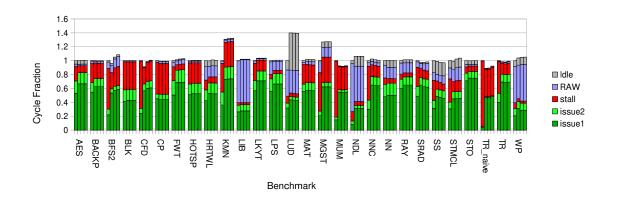

| Figure 3.2 | Dynamic memory instruction fraction for each benchmark                             | 30 |

| Figure 3.3 | Hazard cycle fraction for each benchmark                                           | 30 |

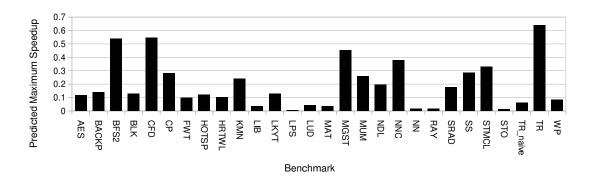

| Figure 3.4 | Predicted maximum speedup for each benchmark.                                      | 31 |

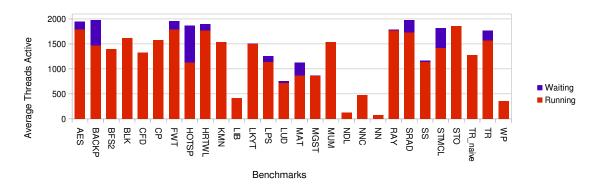

| Figure 3.5 | Average thread availability.                                                       | 31 |

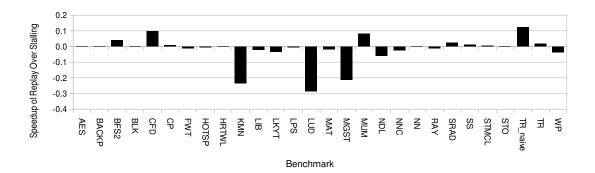

| Figure 5.1 | Comparison of replay strategy speedup over stalling.                               | 37 |

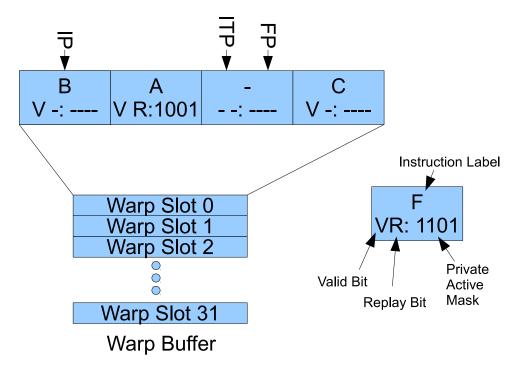

| Figure 5.2 | Warp Buffer data organization.                                                     | 40 |

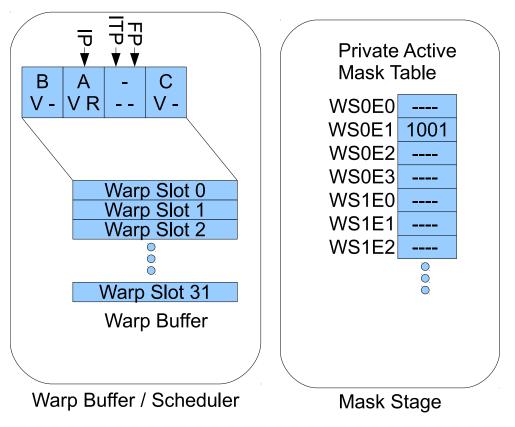

| Figure 5.3 | Modified replay data organization.                                                 | 43 |

| Figure 5.4 | Example of Warp Buffer replay operation.                                           | 45 |

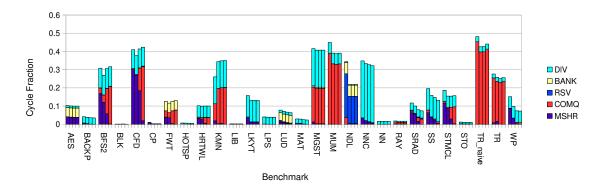

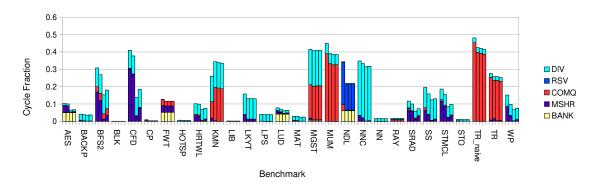

| Figure 6.1 | Breakdown of hazard cycles according to type for varying number of data cache      |    |

|            | MSHRs. Bars are: Baseline 32 MSHRs, Replay 32 MSHRs, Replay 64 MSHRs,              |    |

|            | Replay 128. Normalized to total cycles of Baseline 32 MSHRs                        | 47 |

| Figure 6.2 | Breakdown of issue cycles according to type. Bars are: Baseline 32 MSHRs,          |    |

|            | Replay 32 MSHRs, Replay 64 MSHRs, Replay 128. Normalized to total cycles           |    |

|            | of Baseline 32 MSHRs                                                               | 47 |

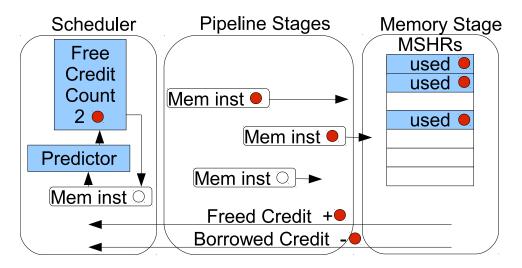

| Figure 6.3 | Overview of credit transactions and storage.                                       | 49 |

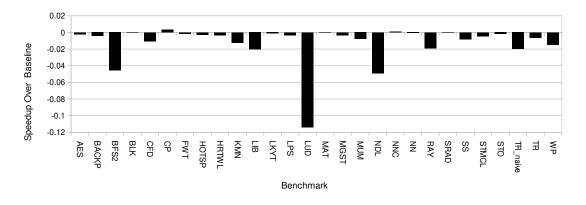

| Figure 7.1 | IPC speedup of retaining replayable instructions in the warp buffer (but no re-    |    |

|            | play) over baseline architecture.                                                  | 52 |

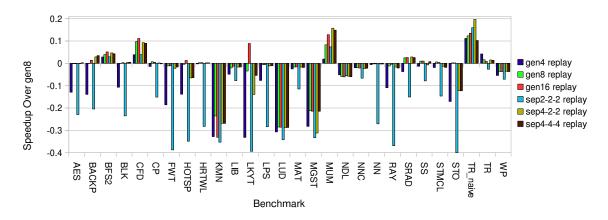

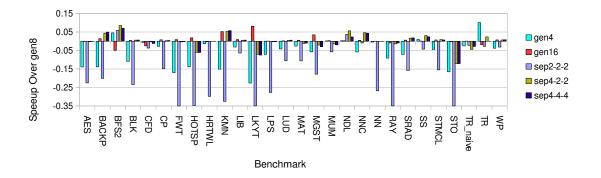

| Figure 7.2  | IPC Speedup over baseline (gen8 stalling) for various operand collector struc-      |    |

|-------------|-------------------------------------------------------------------------------------|----|

|             | tures with stalling                                                                 | 52 |

| Figure 7.3  | IPC Speedup over baseline (gen8 stalling) for various operand collector struc-      |    |

|             | tures with replay                                                                   | 53 |

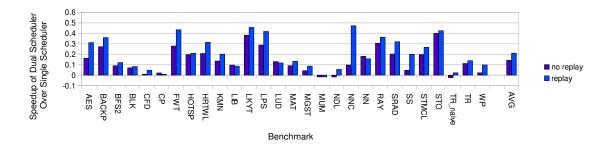

| Figure 7.4  | Speedup of two schedulers over one scheduler (one scheduler baseline) without       |    |

|             | and with replay.                                                                    | 54 |

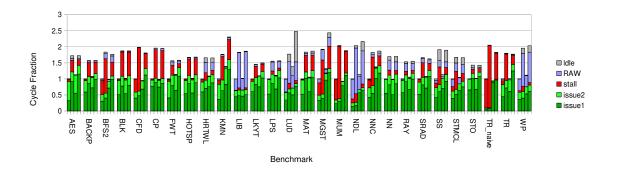

| Figure 7.5  | Fetch cycle breakdown of single and dual schedulers, with and without replay,       |    |

|             | normalized to single scheduler without replay. Each sub bar in order is no          |    |

|             | replay single, no replay dual, replay single, replay dual. Single scheduler results |    |

|             | indicate a speedup when total is less than 1.0; dual scheduler results indicate a   |    |

|             | speedup when the total is less than 2.0 (since 2 fetch events happen every cycle).  | 55 |

| Figure 7.6  | Hazard occurrence breakdown normalized to no replay single total cycles. Each       |    |

|             | sub bar in order is, no replay single, no replay dual, replay single, replay dual   | 55 |

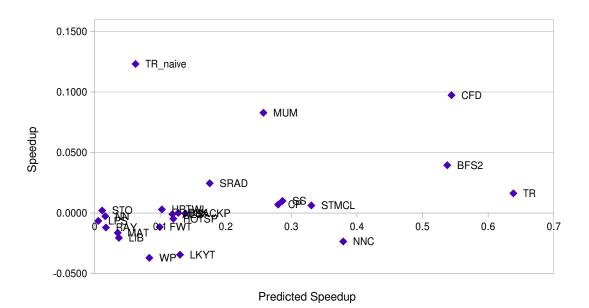

| Figure 7.7  | Scatter plot showing replay speedup versus predicted maximum speedup                | 56 |

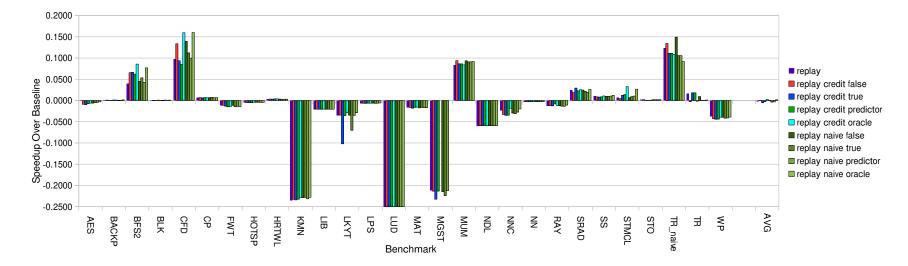

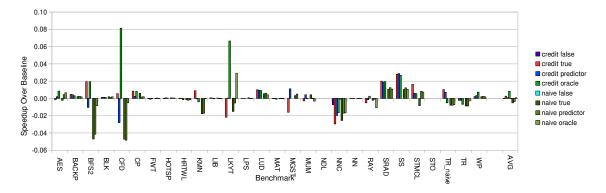

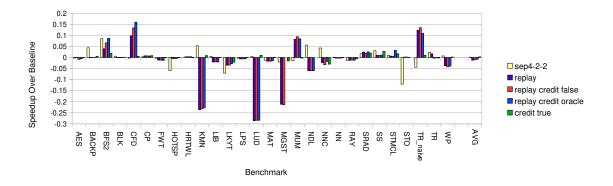

| Figure 7.8  | Speedup of predicted maximum speedup, replay and various hazard avoidance           |    |

|             | mechanisms over baseline.                                                           | 57 |

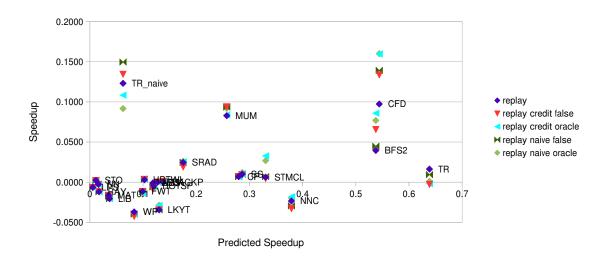

| Figure 7.9  | Scatter plot showing, replay and two best performing hazard avoidance mecha-        |    |

|             | nisms versus predicted maximum speedup.                                             | 59 |

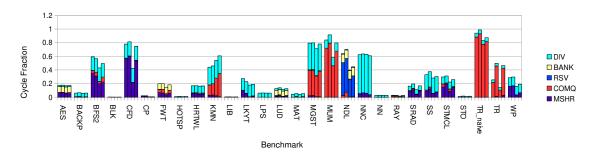

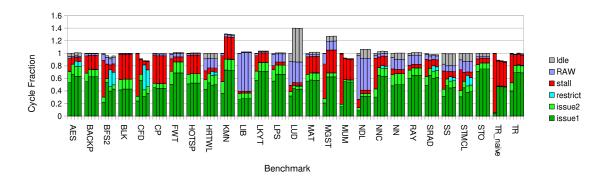

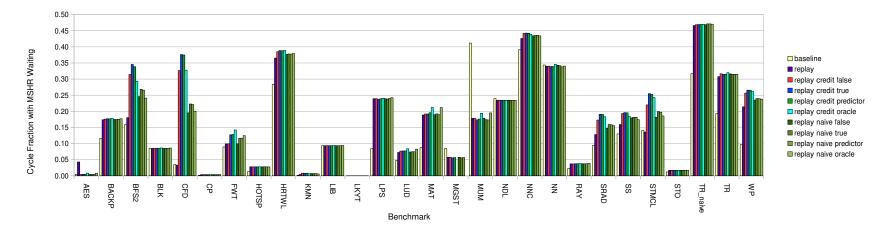

| Figure 7.10 | Cycle breakdown of (in order of bars) baseline (stalling), replay, replay credit    |    |

|             | false, replay naive false.                                                          | 60 |

| Figure 7.11 | Hazard cycle breakdown of (in order of bars) baseline (stalling), replay, replay    |    |

|             | credit false, replay naive false.                                                   | 60 |

| Figure 7.12 | Fraction of cycles in which an MSHR using instruction was ready to issue or in      |    |

|             | the pipeline, and at least one MSHR was available.                                  | 61 |

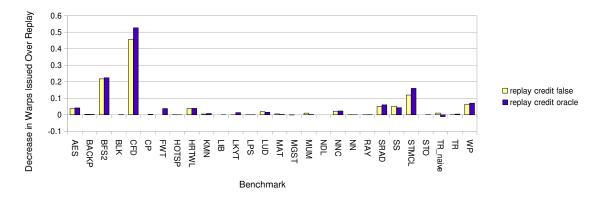

| Figure 7.13 | Speedup of hazard prediction without replay.                                        | 63 |

| Figure 7.14 | Reduction in cycles in which instructions are issued due to hazard prediction.      | 64 |

| Figure 7.15 | Comparison of various hazard management techniques                                  | 64 |

|             |                                                                                     |    |

# Glossary

| ALU   | Arithmetic Logic Unit                 |

|-------|---------------------------------------|

| CPU   | Central Processing Unit               |

| GPU   | Graphics Processing Unit              |

| GPGPU | General Purpose [processing on a] GPU |

| RAW   | Read After Write                      |

| SIMD  | Singe-Instruction, Multiple Data      |

| SIMT  | Single-Instruction, Multiple Thread   |

| SFU   | Special Function Unit                 |

| RISC  | Reduced Instruction Set Computing     |

| ISA   | Instruction Set Architecture          |

| IMEM  | Instruction Memory                    |

| DMEM  | Data Memory                           |

| DIV   | Memory Divergence hazard              |

| MSHR  | Miss Status Holding Register          |

| COMQ  | Cache Communication Queue             |

| RSV   | Cache Line Reservation hazard         |

| BANK  | Bank Conflict Reservation             |

| VLIW  | Very Long Instruction Word            |

| ICNT  | Interconnect Resource Hazard          |

| TLB   | Translation Look-aside Buffer         |

| CAM   | Content Addressable Memory            |

- PAM Private Active Mask

- IP Issue Pointer

- ITP Issue Tail Pointer

- **FP** Fill Pointer

## Acknowledgments

I am grateful for the support of many while completing my thesis. In particular, I wish to thank Professor Tor Aamodt for his guidance, suggestions and support.

I also would like to thank Ali Bakhoda, Wilson Fung and others from our research group for their help and camaraderie, and particularly for their advice as I prepared my final presentation.

Thank you to both of my parents for their great support, and my father for his help with many revisions. And finally, to my wife, Caitlin, whose support and love has sustained me.

## **Chapter 1**

## Introduction

Graphics Processing Units (GPUs) are a popular type of computer chip processor design. GPU type architectures are widely available separately or as co-processors in chips used in both desktop and portable devices. Gaining improvements in GPU power use and performance is a current focus of computer architecture research.

### 1.1 Overview

This section is an overview of computer architecture and the design and functioning of GPUs.

#### 1.1.1 Computer Architecture

Computer architecture research is the study and design of the functional organization of computer processors. In recent years interest has been increasing in the design of highly parallel processors. Conventional monolithic processor designs generally only run a single<sup>1</sup> instruction stream, or program thread, at a time. Highly parallel processors have advantages in power efficiency and computing throughput. Compute accelerators, such as GPUs are the most popular parallel processor architecture currently in production, and are increasingly being used for non-graphics purposes, termed General Purpose computation on GPUs (GPGPU).

The performance of processors depends heavily on how hazards, situations where normal, fast and efficient processing cannot proceed, occur and are resolved. This problem has been quite well studied for monolithic conventional CPUs [5][14], but there is much to be understood about hazards in highly parallel architectures.

This work characterizes hazards for a GPU-like compute accelerator, and provides an analysis of possible strategies to improve performance through more effective hazard management.

<sup>&</sup>lt;sup>1</sup>Or sometimes a few, such as with hyper-threading or a few on multiple monolithic cores.

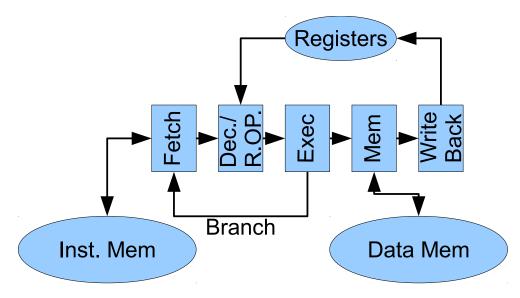

Figure 1.1: Simple core architecture.

#### **1.1.2** Architecture Basics

A simple RISC (Reduced Instruction Set Computing) processor is depicted in Figure 1.1. A RISC processor executes a limited type of ISA (Instruction Set Architecture) where instructions either perform operations on register values, or store/load register values to/from Data Memory, but never both - this reduces the number of ISA instructions and simplifies the architecture. Elaborations and refinements of the basic RISC architecture constitute the architecture of the majority of computers today. This processor consists of a pipeline of basic steps, that Fetch, Decode/Read Operands, Execute, Access Data Memory, and Write Results, for a stream of instructions which constitute the program. The processor core generally has access to at least three types of memory: Instruction Memory (IMEM), which contains the instruction code accessed by the Fetch stage; Data Memory (DMEM), which contains data read and written by the program (Mem Stage); and Register Memory, which contains the register values for the running program (read at Read Operands, written at Write Back). The program being run is stored in the instruction memory as instruction code. In modern designs, Main memory is stored outside the core, and Instruction memory and Data memory are interfaced through caches. Modern processors use pipelining heavily. Pipelining allows multiple instructions (or more generally a stream of operations) to be processed in parallel through a number of serial steps; in the architecture of Figure 1.1, a different instruction could be processed in each of Fetch, Decode, Execute, Mem and Write Back.

The processor runs a program from the Instruction Memory, which is a sequential series of instructions (that conform to the ISA). This single sequence of instructions is a thread of execution. A single-threaded program contains only one thread whereas a parallel program is comprised of multiple threads (a highly parallel program has many threads). A thread is a program (or part of

a program) running in a single architecture thread context that handles a single linear sequence of instructions. A computer may run multiple programs concurrently by supporting multiple thread contexts.<sup>2</sup> The registers are a store of local memory which is small but fast, and the data memory system is a large store of distant memory which is typically large but slow. Instructions are accessed from Instruction Memory in the fetch stage based on a program counter. The program counter might be modified by a branch instruction in the execute stage. Decode/Read Operands derive control signals from the instruction and also access the Register file for the operands required by the instruction. These operands are passed along with the instruction to the execute stage where computation result, or an operand value, is passed along with the instruction to the Memory stage. If the instruction is a memory operation, then the memory stage performs the appropriate operations, usually either a read or write, to or from the data memory. If the instruction is not a memory operation then the memory stage does nothing. The resultant data is further passed along to the write-back stage. If the instruction stores its result to the register file, then the result is written back to the register file. This completes the execution of the instruction.

In a RISC (Reduced Instruction Set Computing) processor (of which Figure 1.1 is an example) the instructions are either ALU operations or Memory operations. Memory operations are restricted to only transfer data between registers and main memory. ALU operations only operate on data from the registers, and if they produce a value, can only place the results back into the register memory space. For the purposes of this work we group conditional branch and jump instructions in with ALU operations since they do not access main memory and have the same data characteristics of regular ALU operations (although they may access register data differently). The RISC simplification allows instructions to be more easily encoded, reduces the size of the instruction set, and simplifies the pipeline.<sup>3</sup> The examined architectures are also classified as modified Harvard architectures, since both instruction and data memories are accessed independently and concurrently through dedicated caches but backed by a common unified memory.

Separating the execution of an instruction into multiple pipeline stages allows multiple instructions to be processed at the same time. For example Fetch may be loading a new instruction on the same cycle that an ALU operation is undergoing execution in the Execute stage. The instruction throughput is increased because the smaller pipeline stages have less work to do per cycle, increasing the clock frequency at which the processor can be run. Pipeline stages are generally designed so that their entire operation can be completed in a single clock cycle; the clock frequency is limited by the longest completion time of the slowest pipeline stage. Two major downsides to pipelining are that instructions are not independent from each other and pipeline stages may not always be able

$<sup>^{2}</sup>$ An architecture with only a single thread context may provide the illusion of running multiple programs or threads in parallel by switching quickly between them.

<sup>&</sup>lt;sup>3</sup>The other major instruction set type is CISC (Complex Instruction Set Computing), in which a single instruction can access and do computation on data in memory.

complete their work in a single cycle. Instructions may be coupled to each other through their data dependencies. An instruction may require a result from another instruction, and if these instructions are too close to each other in sequence, the second instruction must wait in the decode stage until the first has completed the write-back stage. This is a type of hazard. A similar hazard occurs when a branch instruction relies on its calculation in execute, as the next instruction fetched depends on the outcome of that branch.

Another hazard type is when an instruction on its own cannot complete a pipeline stage in a single cycle. In this case an ALU instruction may take multiple execute stages to complete the computation, or the memory system may not be able to satisfy a memory instruction's request in a single cycle. The latter, memory hazards are typically unpredictable and are the focus of this work.

Hazards are a problem for pipelines because they cause instructions upstream (earlier in the pipeline) to stall. Stalling is when an instruction cannot proceed to the next stage at the end of a cycle. Although upstream instructions could otherwise proceed, they also stall when a downstream instruction stalls. This stalling reduces throughput and thus reduces performance. Even in more complicated architectures, unpredictable hazards causing stalls are a significant penalty on processor performance [14][29].

#### 1.1.3 Monolithic CPU Strategies

Extensive architecture research has been done on improving single thread performance in monolithic core processors. Monolithic core processors typically expend much of their area and energy budget to optimize the performance of one or two threads. In order to combat the performance penalty of hazards, these CPUs have utilized architecture modifications to the simple pipeline. The general strategy has been to mitigate hazards by out of order effects, deep pipelining and speculation [14].

Out-of-order execution allows the processing of instructions to occur out of program order. This includes out-of-order execution, where data hazards are alleviated by executing instructions as their operands become available in multiple execution stages. This enables higher instruction throughput since many instructions may not depend on each other and may be run at the same time. Another form of out of order effect is out of order memory in conjunction with out of order execution. Because of the way data memory is constructed<sup>4</sup>, it is possible for some requests to complete much faster than others. In an in-order pipeline, these faster requests would have to wait for slower ones to complete, whereas in an out of order pipeline these could complete as they are ready.

Out-of-order execution is usually limited to a small window of instructions from a single thread. Because this window can generally not be advanced until the oldest executing instruction is complete, the long-latency instructions become important to performance. In addition, the single threaded

<sup>&</sup>lt;sup>4</sup>Memory accesses are typically accessed through a series of caches, accesses that miss in lower levels and are forced to check higher level caches or main memory and incur increasing latencies for completion.

nature of monolithic cores limits how much parallel work is available while earlier instructions are outstanding due to dependencies. Thus, memory operations, which are often the highest latency instructions in the instruction set, are optimized for latency rather than bandwidth. This, for example, leads to larger caches that support only a few outstanding accesses.

CPUs tend to also pipeline and deeply pipeline [5][14] as much possible. This allows extremely high frequencies of execution, and thus more throughput per real time.<sup>5</sup> The downside to this approach is that hazards carry more penalty than they would in a shorter pipeline. For example the resolution of a branch instruction may be many pipeline stages away from the fetch stage, causing a delay, in this case the branch penalty, until the next instruction can be fetched and issued.

Speculation is used by monolithic cores to reduce the effects of hazards. The primary use use of speculation targets the branch delay penalty. Typically branches are predicted based on past behavior and instructions are issued and executed based on that prediction until the branch is actually resolved. If the prediction was wrong, all speculated instructions and results are scrapped and execution begins on instructions fetched from the correct path. This can get complicated as multiple outstanding branches occur and must be handled. Another form of speculation is prefetching, in which data that may be used later is loaded into the local cache so it is available for expedient use later.

In addition to instruction throughput, processor design constraints have grown to include the area and power dissipation characteristics of processors and their components. More complicated logic and larger storage occupies more area (because it uses more transistors), whereas power dissipation is both a function of area (more transistors use and leak more power), and transistor switch rate (each transistor switch uses more power). In the monolithic CPU designs, much area and power is devoted to the execution of single threads. In speculation for example, a large area can be used, and in mispredictions a large amount of power consumed for no benefit. A class of different processor organization, GPUs, attempts to alleviate these problems by using available area and power more directly for computation with more area allocated to ALUs.

The limits of single core architectures motivates the movement to multicore architectures [28], where smaller monolithic processors are combined on a single chip. Moving further in that direction, more, smaller cores, leads towards GPU architectures.

#### **1.1.4 Compute Accelerators**

Compute Accelerators are a broad group of computer architectures designed to accomplish high throughput of highly parallel programs. GPUs are a mainstream example of this type of architecture.

The basic principle behind GPUs is that many parallel threads can run at the same time. In this scenario the accelerator is optimized for throughput: a large number of concurrent threads, a large

<sup>&</sup>lt;sup>5</sup>In Computer Architecture when comparing similar designs, cycle time is assumed to be constant, so throughput is taken to be instructions / cycle. This ignores cycle timing effects such as mentioned here.

number of ALUs and high memory bandwidth. This is a different strategy from the monolithic CPU architectures where resources are expended to improve the performance of just a single or few threads.

The key to the success of GPUs is that although threads may individually experience long delays due to memory or other hazards, these delays are mitigated by the presence of other independent threads. What is important is the throughput of all threads, and this depends on the average rate of execution of the individual threads multiplied by the number running concurrently. In a single thread, performance is limited by the latency of constituent instructions: a memory access that misses in the cache may prevent that thread from doing any work for hundreds to thousands of cycles (hence the focus of Monolithic cores on latency and prefetching). In a monolithic core this delay likely leaves functional units and much of the core idle. When there are many threads executing, a large number may be unable to make progress because of cache misses, but a large number are also able to execute, utilizing the core more completely. This ability to cope with threads being blocked because of long latency occurrences, translates to a tolerance for some types of hazards which typically delay the completion of some instruction, such as a cache miss.

Because individual threads are independent and can be reordered with respect to each other, GPUs achieve some of the benefits of out-of-order execution without having to manage its downsides. Both techniques exploit parallelism in the program to keep as many functional units (ALUs, Memory) that could do useful work busy at the same time. With access to many threads ready to execute at (hopefully) different parts of their program, a selection of instruction types can fill many of the function units. Monolithic cores attempt to achieve this by running individual threads out of order, as well as running a few threads at the same time (e.g. hyper-threading [18]). Monolithic cores also must manage complexities of this out of order execution, such as data and register management and precise exceptions. GPUs do not have these specific challenges because individual threads execute in order.

Because hazards are better tolerated, GPU architectures can omit expensive modules that assist single-thread performance, such as out-of-order execution or speculation. This saving in area and power dissipation can be used for supporting more simultaneous threads, more ALUs and larger caches, further boosting throughput.

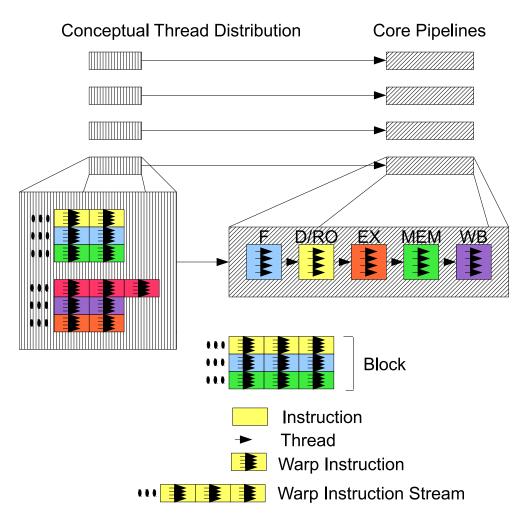

GPU compute accelerators run many threads at once primarily through three mechanisms: 1) by combining threads together in batches called warps, 2) having many warps reside actively on each core, and 3) having many cores. Figure 1.2 outlines how threads are conceptually grouped into warps, blocks and cores, and how these are run on a simple core pipeline. For a modern GPU such as the NVIDIA Fermi, concurrently executing threads can number up to 32 (threads per warp) \* 48 (warps per core) \* 15 (cores) = 23040 threads [25].

As shown in Figure 1.2, warps are special because they are passed down the pipeline as a unit and operated on concurrently at each stage. Threads are grouped into warps such that each individual

Figure 1.2: Conceptual thread grouping and execution on a GPU.

thread is at the same program instruction, in other words threads in each warp all share the same program counter value. Each thread in the packet requires the same pipeline stages and operations, so control lines are conserved. Only the data carried for each thread (which may be different for each thread in the warp) need be stored and passed between pipeline stages. Each thread accesses its own registers and reads and writes to data memory as if it were being run independently. This independence is extended to control flow as well.

This model is known as SIMT (Single Instruction, Multiple Thread) as opposed to SIMD (Single Instruction, Multiple Data) in that in addition to handling multiple data, this system handles the multiple control flow paths of individual threads in the warp packet. This allows threads to be conceptualized as separate and independent, even though they execute together in warps. This simplifies programming and prototyping, as single threaded programming methodologies can be used initially and adapted to provide increased performance. In SIMD, a major limitation is that

all threads that are packaged together (like a warp) must branch together, a condition that must be explicitly ensured by the programmer, and memory requests for each thread typically have to be contiguous. More information on programming is provided in section 1.1.5.

Control flow independence within a warp is obtained using two mechanisms. Predication of instructions<sup>6</sup> suffices for simple branches (a simple branch chooses between relatively few instructions; the threshold at which a branch is implemented by predication is determined by the compiler). More complicated branching is handled by a per warp stack that keeps track of the branching history of warps [9]. Each branch is systematically executed for each thread that takes that branch by masking off all other threads, and running the warp for the instructions in that branch. Branching within a warp can have significant performance penalties because each instruction in each branch requires a separate pass through the pipeline. Thus a warp that branches once executes all the warps that take the branch then all the warps that don't take the branch direction.

Another aspect of SIMT is its interaction with the memory stage. The memory stage is limited to processing a small number (usually just one) of large memory transactions per cycle. If all the memory requests for each thread are not within a single span of contiguous aligned memory then multiple cycles must be used to issue requests for all such spans required by the warp. This is another form of reduced throughput. This occurrence is called memory divergence. This is an important hazard because it occurs unpredictably at the memory stage, since is is not possible to determine if it will occur until the access addresses have been calculated for each thread.

#### 1.1.5 Programming Languages

Programming languages and schemes for highly parallel architectures is a current research problem, and is challenging and complex. SIMT hardware attempts to simplify this problem by abstracting threads from their warp groups and allowing them to be treated as full independent threads. NVIDIA CUDA [27] is the programming language created to run on NVIDIA SIMT GPUs.

The CUDA language is C/C++ with additional adornment for specifying kernels (the code that runs on the GPU), kernel launches and special memory storage. CUDA is developed specifically for GPGPU programming. It is distinct from computer graphics programming interfaces such as OpenGL and DirectX, although they utilize the same hardware.

Although any SIMT programming language could utilize the hardware improvements proposed in this work, such as OpenCL [16], CUDA was used where not otherwise indicated.

<sup>&</sup>lt;sup>6</sup>Predication involves conditioning an instruction on some per-thread data. The condition is tested separately for the data of each thread in the warp, and if and only if the condition is true then that instruction is executed on that thread. Predication is usually done in two stages, a test instruction is performed which creates a bit mask, and then the predicated instruction executes using that bit mask. This can be efficient for very small branches, but is untenable for complicated control flow.

#### 1.1.6 Instruction / Data Flow in GPUs

In the GPU it is important to understand the progression of functional units a warp passes through in order to be executed. Each pipeline stage represents a significant step in routing and processing the instructions in a warp.

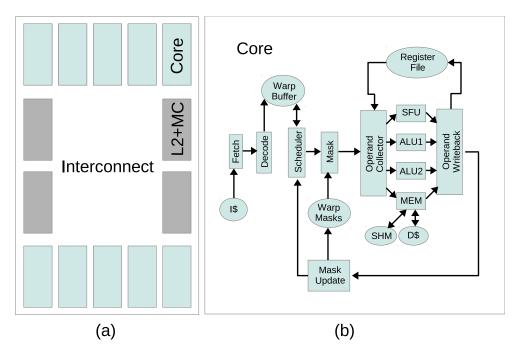

Figure 1.3 shows a simplified schematic of the baseline architecture that is used. It is similar to the NVIDIA Fermi architecture [25]. Subfigure 1.3(a) is the overall chip architecture comprised of core and L2/Memory Controller (L2+MC) units connected by a shared interconnect. The L2+MC units are a combined top level cache and memory controller. These handle memory requests from the cores, and if necessary dispatch requests off chip to the ram memory storage. Subfigure 1.3(b) shows the baseline core architecture. In contrast to the simple architecture shown in Figure 1.1, rather than a single linear pipeline, instruction warps can be steered into multiple different functional units which can operate in parallel. Pipeline stages may then take longer than a single cycle to process their instruction warp, and may themselves be pipelined or support multiple concurrent warps. ALUs may take multiple cycles to compute all the values for each thread, and some pipeline stages are designed to have high throughput but longer latency per warp, such as the scheduler, or the operand collector.

The processor can be conceptually separated into two portions, the front end, which deals with warp selection and warp issue, and the back end which deals primarily with thread data. In the diagram, Fetch, Decode, the Warp Buffer, Scheduler and Mask constitute the front end, while the Operand Collector, functional units and Operand Write Back are the back end.

The following is a short description of how each stage operates and communicates. This defines the baseline architecture which is used as a baseline to compare the benefits of architecture changes.

#### 1.1.6.1 Fetch / Warp Buffer / Scheduler

The Warp Buffer is the primary staging area for warp instruction streams. The Warp Buffer consists of a table of storage for warp instruction streams, one entry for each warp allocated to the core. Each entry consists of a number of instruction storage areas and tracking information, such as instruction addresses, whether operand values are ready, and execution state.

When an entry in the Warp Buffer is low on instructions, the Fetch stage attempts to fill new instructions at the correct instruction address from a locally cached line obtained from the instruction cache. If the needed instruction address is not included in the cached line, the appropriate line is requested from the instruction cache memory.

Instructions are issued down the pipeline from the Warp Buffer by the Scheduler. The Scheduler typically chooses warps in a round robin fashion from those warps that are ready to execute. In the baseline design, two schedulers issue independently from exclusive sets of warps (split into even and odd warps). The scheduler also supports multiple issue, where if the first instruction in a warp

Figure 1.3: Baseline chip and core architecture. (a) Chip architecture, (b) Core architecture.

instruction stream entry can be issued, the second instruction is also issued if possible. This can improve performance when only a few warps are able to issue by helping fill function units.

Read after write dependencies occur when an instruction reads operands to which an older instruction is writing. If the older instruction has not completed, then the newer instruction cannot issue.<sup>7</sup> Read after write dependencies are avoided by using a separate table (the RAW table) that tracks which operands are being written to. When an instruction is issued the registers it will write to are marked off in this table. When that instruction actually writes to those registers those entries are removed from the table (the table also ensures that every active thread has written to those registers). Instructions are not issued unless the operands they read do not have entries in the table.

The baseline architecture supports stall-on-use [8] thread execution enabled by the RAW table. The processor may continue to issue newer instructions from a warp even before older instructions from that warp have completed. The warp may fetch ahead and execute in this manner until it is blocked by a read after write requirement (as determined from the RAW table) or runs out of instructions. This feature allows programs to benefit from pushing data load instructions as early as possible before the data is used. This also allows the possibility for multiple outstanding loads from a single warp as well as the possibility for computation to continue while data is being loaded. This modification can increase pressure on the memory system by increasing the number of possible outstanding loads.

<sup>&</sup>lt;sup>7</sup>Write after write and write after read dependencies are dealt with in the same manner as RAW dependencies.

The baseline architecture uses a version of two level warp scheduling [23] policy to ensure a constant supply of both memory and ALU instructions. It is modified to use two schedulers. Each scheduler has separate sets of blocks to issue from.

#### 1.1.6.2 Mask Stage

After issuing, instructions in a warp are processed and various masks are applied. These masks mark out threads in the warp that are not to be executed with this instruction. This primarily involves the branch masks, which make sure only the correct threads are executed on each side of branches. Depending on architecture this may not need to be a separate stage thus saving a cycle latency. This is done in the baseline architecture.

#### 1.1.6.3 Operand Collector

The Operand Collector is where instructions receive data for their operands from the register file. Warps may wait several cycles here while waiting for the reads to occur. Although the register files are banked to allow multiple reads, it may not be possible to service even all of the same instructions operands at the same time. However, the operand collector can serve multiple warps at the same time, thus maintaining a higher throughput in spite of the higher latency. When an instruction has data for all its operands, it is issued to the next stage. Some scheduling may occur at this stage, because the latency for ALUs is typically fixed. This allows a scheduler to issue instructions in such a way that they complete at the correct time and don't interfere with other instructions in the same pipeline.

#### 1.1.6.4 Functional Units

After the Operand Collector, warps diverge into different functional units for execution. Instructions either go to the Memory Unit, to one of many ALUs or to other functional units which may be present, such as Special Function Units (SFU) and a branch unit. SFUs can process more complex mathematical instructions such as square roots, and branch units handle updating the state associated with branches.

The ALUs are relatively simple from a operations perspective. The instructions have their data, and the ALUs implement the logic necessary to carry out the arithmetic operation required (chosen based on the control lines). This is very predictable, and the output is calculated in a fixed time depending on the operation.

The Memory Unit manages access to different types of memory. Three types of memory are used: constant, shared, and global. Constant memory is read only memory that is stored globally, and cached locally. Shared memory is both read and write memory and is stored locally in the core and is shared across all the warps running on the core. Threads within a core can communicate using shared memory. Global memory is both read and write memory and is stored off chip. All warps across all cores may access the data in this memory. All threads in the GPU can communicate through global memory, although coherency and ordering is not necessarily enforced. In the baseline architecture, global memory is cached locally in an level one (L1) cache and at the chip level in an level two (L2) cache.

Texture memory is a special type of constant memory optimized for graphics texture lookups. Texture memory is implemented in special way to optimize throughput. Although this is simulated in the simulator, and some GPGPU benchmarks make use of this memory type, this memory type is not explained here. More information is available in [13].

#### 1.1.6.5 Write Back

For instructions that return a value, that value must be written back into the register file. Instructions that are writing back to the register file coordinate with the operand collector to write their results into the appropriate banks. For ALU operations this may be already scheduled (due to predictable processing time), and there may be additional ports on the register file to maintain enough throughput for unpredictable write backs (such as may come from memory).

For example, an ALU add instruction that takes four cycles, may when it is issued, schedule the result write to occur at that time. The operand collector knows then to keep a predetermined register port clear on that cycle to allow the write back (alternatively the instruction can be delayed issue if no ports will be available). A memory instruction that writes back (a load of some kind) cannot guarantee when it can write back due to hazards it may yet encounter. In these cases a separate dedicated port may be used, or some priority mechanism to ensure memory write backs occur in timely fashion<sup>8</sup>.

#### **1.1.7** Hazards in the Pipeline

As noted previously, hazards that occur in the pipeline are one significant cause of reduced performance. They can cause stalls and empty pipeline stages which reduce the utilization of functional units, and thus slow down program execution. Hazards occur whenever an instruction cannot proceed through a pipeline stage at the expected rate. Henceforth pipeline hazards will be referred to as simply hazards.

Pipeline hazards may be divided into two groups, structural and dynamic. Structural hazards are *a priori* necessary for program execution on the hardware and usually known before an instruction is issued. These are usually delays that are required for proper execution based on how the program

<sup>&</sup>lt;sup>8</sup>An exception to this rule is that under replay operation, it is possible to predict the latency of shared memory loads. Shared memory loads can only encounter BANK hazards which do not delay execution of the load, only signaling a replay must be done to grab all the data. A BANK hazard in stalling pipeline would cause the instruction to stall and wait until all the data is loaded on multiple cycles, meaning the latency of the operation is indeterminate.

is run. For example, an instruction's operands must be ready before the instruction can be issued for execution. If the supplying instruction is not executed far enough ahead in the program, it is known that the dependent instruction must wait (although the exact amount of time may be unpredictable). In the baseline architecture, instructions will not be issued from the scheduler until their operands are ready. Branch decisions are also structural hazards. In CPUs the effects of these structural types of hazards are reduced with out of order execution and branch prediction. In GPUs, these effects are reduced by the high amount of thread based parallelism. Threads encountering static hazards are not issued, instead other threads that are "ready" are issued. Although it is not guaranteed that there will always be ready threads, having many warps per core makes it much more likely.

Dynamic hazards are unpredictable and occur due to interactions with other warps in the core or uncertainties inherent with a particular instruction. These occur after an instruction has been issued.

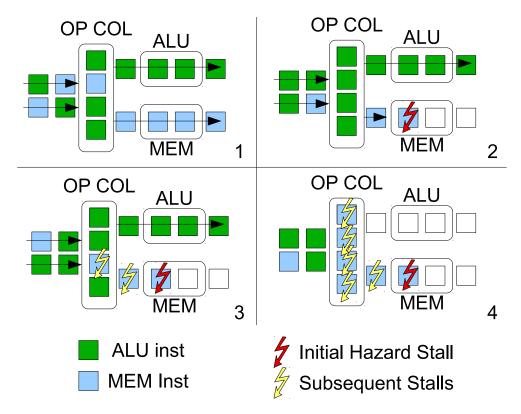

Stall hazards are the simplest type of dynamic pipeline hazard. Stalls occur when an instruction cannot proceed to the next pipeline stage because that pipeline stage is not empty. Stalls are a collateral effect due to another hazard further on in the pipeline (if an instruction can't proceed for a non pipeline related issue, then it is classified as a different type of hazard). All stall hazards can be traced down the pipeline to an originating initial hazard. The initial hazard, if persistent, can cause long chains of stall hazards. Stall hazards can be the primary hazard, for example if a functional unit (usually an ALU) has waiting instructions as it processes a long latency instruction. Otherwise unlike the simple in order pipeline shown in Figure 1.1 modern architectures like the baseline architecture, have forks and joins in the pipeline, as in Figure 1.3. A stall might back up instructions past a fork and further decrease performance by choking off instructions that would otherwise bypass the initial hazard.

Figure 1.4 gives an example of how a stall might propagate through a processor with pipeline forks. Blue instructions are MEM instructions and green instructions are ALU instructions. In the initial view, no hazards are occurring and both ALU and MEM instructions obtain their operands in the operand collector and proceed to their respective pipelines. In the second view a hazard occurs for a MEM instruction, stalling that part of the pipeline. In the next view the stall has persisted and subsequent MEM instructions are unable to proceed, stalling themselves, eventually filling up into the operand collector itself. In the final view the operand collector is completely full of MEM instructions that cannot proceed, choking off instruction flow to the ALU which might otherwise have been able to do useful work.

The other dynamic hazard types originate independently of the pipeline. They prevent an instruction from proceeding to the next stage because of some condition that unexpectedly causes the instruction to be unable to complete its current stage. In the baseline architecture, these types of hazards all originate in the memory stage. Memory instructions can encounter a number of different conditions which prevent them from completing.

Figure 1.5 shows a close up of the hardware components of the memory stage. Explanation of

Figure 1.4: Example of stall propagation.

these components and their operation follows in relation to Figure 1.6.

Figure 1.6 is a flow chart of memory stage operation for a global memory read that demonstrates opportunities for hazards to occur. Threads in the memory instruction must first calculate their associated access addresses. These are then compared and compiled into a single large memory access. Thread accesses that do not fit into this access must wait and utilize the memory stage on another cycle. This constitutes a DIV (for divergence) hazard. The cache is then checked to see if it contains the data for the coalesced access. On a cache hit, the data is recovered and separated and copied into the corresponding individual thread's data registers. These threads then proceed on to a write back stage.

If the access misses in the cache, a memory request must be sent out of the core, over the interconnect to the memory system. In order to complete this task, an MSHR (Miss Status Holding Register) [19] in the MSHR table must be obtained. An MSHR holds information about the load such as which threads requested it, which parts of the load these threads needed, and where to write the results. A lack of MSHRs constitutes an MSHR hazard as the memory request cannot progress. In addition to an MSHR a memory request requires room to put the request before it is accepted by the interconnect. If the interconnect is full, and finite storage of additional buffers are also full, then the request can also not be made (COMQ hazard, for Communication Queue).

Figure 1.5: Memory Stage components.

Finally, in the read allocate, write back memory system, read accesses must reserve space in the cache when they are issued <sup>9</sup>. This requirement will fail if no cache line can be ejected, and this is termed a RSV (reservation) hazard. RSV hazards occur when all the valid lines that a request could be written in a cache are already reserved by other requests that have not yet returned.

If all these hazards are avoided the request is dispatched to the interconnect.

Shared memory operations do not require MSHRs, interconnect, or cache reservations and thus do not encounter these hazards. Similarly shared memory operations are not limited to accessing a single linear cache line each cycle, so do not encounter DIV hazards. However shared memory is implemented as a banked memory, and all threads in a shared memory instruction may not be able to access their data in a single cycle. For example two different threads may request different values from the same shared memory bank, in this case multiple cycles must be used to access these values. Some implementation may also be unable to broadcast a single value from a single bank to multiple threads, although in the baseline architecture used in this work this is allowed (choosing more aggressive shared memory design). This type of hazard is labeled a BANK hazard. Aside from the different cause conditions, it behaves in all other respects like a DIV hazard. The BANK hazard is the only hazard a shared memory operation may encounter.

The types of memory hazards are summarized as follows:

• **DIV** and **BANK**: The addresses accessed for each thread in a warp may not meet the conditions for completion in a single memory access. In this case the instruction must utilize the memory stage for additional cycles to perform the instruction for the remaining threads in the warp. **DIV** is used to signify hazards for constant, texture and global memory that can not be

<sup>&</sup>lt;sup>9</sup>This requirement eliminates the possibility that deadlocks can occur due to the possibility of poor ordering of requests in interconnect buffers.

Figure 1.6: Memory Stage flow chart for a Global Memory load.

coalesced into a single memory request. **BANK** is the label for shared memory instructions that encounter bank conflicts. From the standpoint of thread behavior with this hazard, both operate in the same manner.

- **MSHR**: If a constant, texture, or global access misses in the cache then a Miss Status Holding Register (MSHR)is required as part of the request process. An MSHR keeps track of where the requested data should be stored when it returns, and also remembers which threads requested the data. If an MSHR is unavailable the request cannot be made this cycle.

- **COMQ**: If a constant, texture, or global access misses in the cache and an MSHR is available, then storage must be available for the request to enter the interconnect. In the architecture used the cache maintains an internal queue to account for clock differences and absorb fluctuations in the interconnect acceptance rate. If the interconnect is backed up long enough to fill up this queue then new requests cannot proceed, resulting in a **COMQ** hazard.

- **RSV**: If a constant, texture or global access misses in the cache and MSHR and COMQ are available, a line in the cache set must be reserved for the request (read allocate cache). If no line is available (ie. if all lines in the cache are pending reads) then the request cannot

be issued and a **RSV** hazard occurs. (RSV) hazards do not occur for the read only caches, texture and constant memory.

### 1.2 Contributions

This work provides the following contributions. The GPGPU simulator GPGPU-Sim was used in all contributions. Modifications were incorporated into the simulator, including implementing features similar to NVIDIA Fermi GPUs with replay, including dual schedulers and configurable operand collector and pipelines. Replay specifically was also analyzed and characterized to investigate what performance benefits it may have. Hazard prediction was proposed and implemented to correct pathologies that can occur in replay.

### 1.2.1 GPGPU-Sim Modifications

Changes and modifications were made to GPGPU-Sim [3]. The most significant were memory stage, pipeline and replay modifications. These are described in more detail in Section 4.3

#### 1.2.2 Replay Analysis and Characterization

Replay represents an unorthodox approach to dealing with hazards in a pipeline. The NVIDIA Fermi [25] architecture uses replay. The performance implications of replay are not well understood. Replay could theoretically provide performance improvements in additions to implementation improvements. Replay performance was investigated to determine its value for GPGPU workloads. We characterize where it provides benefit, and identify weaknesses which cause poor performance.

#### 1.2.3 Hazard Prediction

Replay although providing some benefit can sometimes reduce performance. Hazard prediction is proposed to alleviate deficiencies arising from replay. Hazard prediction involves two factors. The first is that instruction may or may not use resources that can cause hazards. The second is that those instructions that do require resources that cause hazards may or may not receive them. Hazard prediction is separated into two components, solving each these problems. A predictor anticipates whether a certain instruction will hit in the cache, and a tracker tracks resource usage. Combined, this hazard prediction improves performance.

### **1.3** Thesis Organization

Chapter 2 details previously published work related to replay and hazard prediction.

Chapter 3 provides a framework to understand how hazards affect performance and explores different solutions. Chapter 5 explains replay in detail and shows how it can be implemented. Similarly Chapter 6 explores hazard prediction implementation.

Chapter 4 details experimental setup and the benchmarks used. It also provides a summary of changes made to GPGPU-Sim.

Chapter 7 presents the experimental results and discusses their impact.

Conclusions are given in Chapter 8.

## Chapter 2

## **Related Work**

Instruction replay and stall free mechanisms have been proposed previously, and these are detailed in this chapter. Replay in GPUs is not represented in the literature, although it is very likely that the NVIDIA Fermi architecture [25] implements a form of instruction replay for least memory instructions [24]. The actual implementation of this system remains unknown, so it is not possible to compare to their implementation. The work presented in this thesis synthesizes a replay mechanism that may be similar to, but is designed independently from, the one implemented in Fermi, and analyzes its effects on performance.

Replay has been most closely examined in terms of monolithic CPU architectures. Cyclone [11] uses a replay mechanism for highly pipelined out-of-order CPUs. It uses a latency predictor and a switchback queue to replace a content addressable scheduler. If instructions are not ready to execute when they reach the front of the switchback queue, they are cycled to the back of the switchback queue. In the Cyclone architecture, instruction latency and dependence is determined speculatively. When an instruction is incorrectly scheduled (its predicted latency or dependence was wrong) then it is replayed at a later time as necessary. Cyclone uses its prediction based scheduler. Instruction replay is used to ameliorate the problem of mispredictions made by the scheduler, by detecting when operands are not ready. Latency prediction allows the scheduler to reduce the time between when operands become ready and when they are used, even when the scheduler is many pipeline stages (and thus cycles) away from the execution units. Cache misses are a common reason for instruction latency mispredictions, causing replays of dependent instructions. In the GPU replay mechanism, replays require both a cache miss and a resource availability failure, and the memory instruction itself is replayed rather than its dependents.

The Cyclone architecture replay mechanism is useful for monolithic architectures where cycle time and instruction latency are important to performance and performance gains are gained from parallel execution of instructions from a single thread. In contrast, replay in a GPU architecture is used to prevent pipeline stalls and thus increase instruction throughput of independent instructions. The implementation of replay differs between Cyclone and that for GPUs presented in this work. In Cyclone, replay occurs after a failed operand load, whereas in the GPU architecture, instruction dependence is enforced by the scheduler. In a GPU, instructions are not issued until their operands are ready, so the operand collector always has the correct values available. The Cyclone replay mechanism does not apply to a GPU because performance does not rely on low latency instruction execution: other independent warps may execute while one warp is blocked on a long latency instruction, or is waiting for its operands to be signaled as ready. Replay in the GPU differs also because it requires not only squashing and rescheduling but also management of warp threads. In the GPU replay implementation presented in this work, instructions are retained in the warp buffer and signaled to be reissued, rather than cycled around in a loop until executed.

Zephyr [20] is a modification to the cyclone scheduler. When Cyclone mispredicts a dependence or latency, that misprediction can caused additional mis-scheduled instructions that also must replay. These contingent replays decrease performance. Zephyr augments Cyclone's pre-scheduler with a load latency predictor and fixed length queues. This allows the pre-scheduler to introduce instructions out of order into the cyclone scheduler, and prevent it from becoming too full and congested. This reduces contention and replays in the cyclone scheduler by delaying entry of instructions that are not expected to complete in a short amount of time. The Zephyr latency predictor attempts to predict load latency, including whether a load will hit in the cache. The contention issues Zephyr addresses are similar to those that occur with GPU replay and motivate Hazard Prediction: too many replays clog the switchback queue / pipeline. While cache miss prediction is used in Zephyr, it is found to contribute to the problem of congestion. Moreover the Zephyr latency predictor depends on the observation that in the single threaded benchmarks they examined, loads are usually misses unless a store has recently written to the load's address. Hazard Prediction, in contrast, uses miss prediction in conjunction with a resource tracker to predict hazards and reduce replays, and does not rely on the same observation for cache hits. Although it is possible that the same observation could be useful for GPU programs, this behavior probably does not hold in general. GPUs have large caches where cache lines may remain valid longer, and different cache use patterns, where cache lines may be used by many threads over long time periods. The key contribution to limiting replays in Zephyr are the fixed latency queues which delay entry of long latency instructions into the scheduler. This is not directly applicable to reducing hazards in GPU replay, because excessive replays in the GPU architecture are not caused by early scheduling.

Kim and Lipasti [17] examine scalability of implementations of CPU replay. They find that replay schemes that correct speculative latency and dependence predictions do not scale well. They show that a prediction and token based system can decrease implementation complexity. The token mechanism limits the need for precise replay support by limiting which instructions are allowed to replay based on their predicted need to replay. The tokens are allocated to instructions which are predicted to have a mispredicted latency or dependence. Dependence information is only retained for these instructions, allowing them to be replayed precisely and selectively. Instructions without a token lack dependence information and force an unselective issue queue flush. Since they focus on replay for scheduling purposes, their solution is not directly applicable to replay in GPUs. In Hazard Prediction, credits are allocated with the help of a predictor to maintain accurate estimates of resource availability. Both systems use prediction and tokens to ration core resources, although the prediction, resources, and mechanisms differ.

An architecture named "flea-flicker" [4] describes a two pass VLIW (Very Long Instruction Word) pipeline that executes out-of-order to recover from cache misses. Instructions that encounter hazards in the first pipeline complete in the second pipeline. This could be thought of as a replay-like mechanism in which the replay occurs in a separate pipeline, and only at most once per instruction.

The Stall Free Counterflow [22] architecture avoids stalls by utilizing a novel architecture where instructions and data values flow counter to each other down parallel pipelines. Instructions utilize the operands and proceed to execute once they obtain data values that match the operands they require. Stall free execution is achieved by wrapping the end of the instruction pipeline back to the start, effectively replaying instructions that failed to obtain operands or an execution unit. This replay system is part of a combined operand distribution and functional unit allocation system. Like the Cyclone [11] scheduler, replay is used to correct dependence and latency issues that might otherwise cause a stall.

Instruction replay can reduce or remove the need to stall. Other mechanisms exist for reducing problems with stalling. Hardware implementation issues with clock gating and pipeline stalling in hardware are described in [12]. They show that 70% of the power in high frequency microprocessors goes to clock circuity and latch load alone. The authors propose using an "elastic" pipelining technique for the extra storage needed for a delayed stall signal. This takes advantage of the storage available in a stalled master/slave flipflop. Detailed circuit implementations of this work are provided in [15]. Replay mechanisms that eliminate stalling would also likely avoid some of these circuit implementation problems, and may allow better and more efficient circuits designs. The "elastic" pipelining technique would not be necessary because there would be no delayed stall signal.

A wave propagation pipeline [6] forgoes pipeline registers by carefully designing the timing of circuits such that an instruction (or other signal that progresses as a unit) stays together as a "wave" throughout the pipeline. Such a system requires that signals never stall because there is no storage within the pipeline. As such it is usually proposed for ALUs and other small, non-stalling pipelines. Replay functionality could potentially open up more of the whole processor pipeline to this circuit technique.

## **Chapter 3**

# The Problem: Throughput Reduction Due to Hazards

For the purposes of this and following chapters, hazard is taken to refer to dynamic hazards (Section 1.1.7). These hazards prevent instructions from progressing down the pipeline and can lead to chains of stall hazards.

Hazards can and do restrict compute processor performance. They slow performance and reduce instruction throughput by reducing functional unit usage. Penalties can occur when functional units which could be in use are prevented from getting required resources by hazards elsewhere in the processor.

Hazards prevent a processor from maintaining the maximum throughput through each pipeline unit, given the limits imposed by the program that is being run. For the baseline architecture, two classes of instructions can interact negatively: arithmetic operations (ALU) and memory operations (MEM). These types of instructions have separate pipelines but only after the shared pipelines leading into the common operand collector. Hazards in the ALU or MEM pipelines can spill over through the operand collector and affect instructions of the other type (as shown in the example of Figure 1.4). Performance depends on both ALU and MEM instructions being executed concurrently to the full capacity of the processor, given availability. As noted before, the MEM instructions are the most significant source of hazards, and thus also can interfere with themselves.

To maximize performance (instructions per cycle) for a given architecture it is necessary to have the proper instructions available to fulfill those functional units' throughput, while at the same time, preventing hazards from also preventing functional unit use. This amounts to increasing the MEM/ALU parallelism in the processor core. Possible solutions to fixing this problem are analyzed in the following.

### 3.1 Taxonomy of the Solution Space

Increasing Memory / ALU parallelism is a complicated goal and in compute accelerators suffers from limitations and is amenable to certain solutions. The many-warp nature of compute accelerators makes these requirements much different from CPUs which primarily exploit memory / ALU parallelism with out of order scheduling, execution, speculation, and execute ahead options like prefetching. These monolithic CPU strategies provide the CPU core with a mix of memory and ALU instructions which can be executed concurrently. In these cases the amount of parallelism is limited by the single program thread (or a small number of threads) being run, in which many instructions in the out of order window will be dependent on each other, limiting maximum parallelism. In contrast, GPUs attempt to provide independent MEM / ALU instructions on instructions from different warps, parallel performance depends only on access to instructions and how instructions progress through the pipelines and execution units.

### **3.2** ALU / MEM Instruction Mix