## Power Estimation for Diverse Field Programmable Gate Array Architectures

by

Jeffrey Goeders

BASc, University of Toronto, 2010

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### **Master of Applied Science**

in

### THE FACULTY OF GRADUATE STUDIES

(Electrical and Computer Engineering)

The University Of British Columbia (Vancouver)

October 2012

© Jeffrey Goeders, 2012

## Abstract

This thesis presents a new power model, which is capable of modelling the power usage of many different field-programmable gate array (FPGA) architectures.

FPGA power models have been developed in the past; however, they were designed for a single, simple architecture, with known circuitry. This work explores a method for estimating power usage for many different user-created architectures. This requires a fundamentally new technique. Although the user specifies the functionality of the FPGA architecture, the physical circuitry is not specified. Central to this work is an algorithm which translates these functional descriptions into physical circuits. After this translation to circuit components, standard methods can be used to estimate power dissipation.

In addition to enlarged architecture support, this model also provides support for modern FPGA features such as fracturable look-up tables and hard blocks. Compared to past models, this work provides substantially more detailed static power estimations, which is increasingly relevant as CMOS is scaled to smaller technologies. The model is designed to operate with modern CMOS technologies, and is validated against SPICE using 22 nm, 45 nm and 130 nm technologies. Results show that for common architectures, roughly 73% of power consumption is due to the routing fabric, 21% from logic blocks and 3% from the clock network. Architectures supporting fracturable look-up tables require 3.5-14% more power, as each logic element has additional I/O pins, increasing both local and global routing resources.

## Preface

The work presented in this thesis will be published in the following conference proceedings:

Jeffrey Goeders and Steven Wilton. <u>VersaPower: Power Estimation for Diverse</u> <u>FPGA Architectures</u>. In *International Conference on Field Programmable Technology*, December 2012. Accepted. (Poster Presentation)

Portions of this publication are used in all chapters of this thesis. I was solely responsible for the code development of this work, as well as performing the necessary experiments. I am the primary author of this publication, and wrote the majority of the paper. I collaborated with my supervisor, Steve Wilton, in designing this work, and he provided instruction and guidance throughout the development. He also aided in revising and editing the above paper.

## **Table of Contents**

| At | ostrac  | t               | •••    | ••  | ••  | • • | • | ••• | • | ••  | • | •• | • | ••• | • | • | • | • | • | • | • | ii  |

|----|---------|-----------------|--------|-----|-----|-----|---|-----|---|-----|---|----|---|-----|---|---|---|---|---|---|---|-----|

| Pr | eface   |                 | •••    | ••  | ••  |     | • | ••• | • | ••• | • | •• | • | ••  | • | • | • | • | • | • | • | iv  |

| Та | ble of  | Contents        | •••    | ••  | ••  | • • | • | ••• | • | ••  | • | •• | • | ••  | • | • | • | • | • | • | • | v   |

| Li | st of T | Tables          | •••    | ••  | ••  | • • | • | ••• | • | ••  | • | •• | • | ••  | • | • | • | • | • | • | • | ix  |

| Li | st of H | Figures         | •••    | ••  | ••  | • • | • | ••• | • | ••  | • | •• | • | ••  | • | • | • | • | • | • | • | X   |

| Ac | ronyi   | ms              | •••    | ••  | ••  | • • | • | ••• | • | ••  | • | •• | • | ••  | • | • | • | • | • | • | • | xii |

| Ac | know    | ledgments       | •••    | ••  | ••  | • • | • | ••• | • | ••  | • | •• | • | ••  | • | • | • | • | • | • | • | xiv |

| 1  | Intro   | oduction        | •••    | ••  | ••  | • • | • | ••• | • | ••  | • | •• | • |     | • | • | • | • | • | • | • | 1   |

|    | 1.1     | Motivation      |        | • • | • • |     | • |     |   |     | • |    | • |     | • |   |   |   |   |   | • | 1   |

|    | 1.2     | Contributions o | f this | Wo  | ork |     | • |     |   |     | • |    | • |     | • | • | • |   |   |   | • | 5   |

|    | 1.3     | Challenges      |        |     |     |     | • |     |   |     | • |    |   |     | • | • | • | • |   | • | • | 6   |

|    | 1.4     | Overview of Re  | sults  |     |     |     | • |     |   |     | • |    |   |     |   | • | • |   |   | • |   | 7   |

|   | 1.5  | Thesis | S Organization                        | 8  |

|---|------|--------|---------------------------------------|----|

| 2 | Bac  | kgroun | d                                     | 9  |

|   | 2.1  | FPGA   | s                                     | 9  |

|   |      | 2.1.1  | Basic Architectures                   | 10 |

|   |      | 2.1.2  | Modern Architectures                  | 15 |

|   | 2.2  | FPGA   | Computer Automated Design (CAD)       | 17 |

|   |      | 2.2.1  | CAD Flow Steps                        | 17 |

|   |      | 2.2.2  | Verilog-to-Routing (VTR)              | 19 |

|   | 2.3  | Power  | Estimation Techniques                 | 20 |

|   |      | 2.3.1  | Abstraction Levels                    | 20 |

|   |      | 2.3.2  | Simulation-Based Power Estimation     | 22 |

|   |      | 2.3.3  | Probabilistic Power Estimation        | 23 |

|   | 2.4  | FPGA   | Power Estimation Tools                | 25 |

|   |      | 2.4.1  | The Poon Power Model                  | 25 |

|   |      | 2.4.2  | The Jamieson Power Model              | 26 |

|   |      | 2.4.3  | The Li Model                          | 26 |

|   |      | 2.4.4  | The Estimation Technique of this Work | 27 |

| 3 | Syst | em Des | sign and Architecture Generation      | 28 |

|   | 3.1  | Power  | • Model Overview                      | 28 |

|   | 3.2  | The A  | rchitecture Generator                 | 32 |

|   |      | 3.2.1  | Global Routing                        | 33 |

|   |      | 3.2.2  | Complex Logic Blocks                  | 40 |

|   |      | 3.2.3    | Clock Network                | 50 |

|---|------|----------|------------------------------|----|

|   |      | 3.2.4    | Physical Size Estimation     | 52 |

|   | 3.3  | Summ     | ary                          | 53 |

| 4 | Pow  | er Estii | mation                       | 55 |

|   | 4.1  | Low-L    | Level Power Estimation       | 55 |

|   |      | 4.1.1    | Switching Power              | 56 |

|   |      | 4.1.2    | Short-Circuit Power          | 57 |

|   |      | 4.1.3    | Subthreshold Leakage Power   | 58 |

|   |      | 4.1.4    | Gate Leakage Power           | 59 |

|   | 4.2  | Activi   | ty Estimation                | 60 |

|   |      | 4.2.1    | Algorithm                    | 61 |

|   |      | 4.2.2    | Limitation: Black Boxes      | 62 |

|   | 4.3  | Transi   | stor Properties Generator    | 63 |

|   |      | 4.3.1    | Transistor Node Capacitances | 64 |

|   |      | 4.3.2    | Subthreshold Leakage Current | 64 |

|   |      | 4.3.3    | Gate Leakage Current         | 65 |

|   |      | 4.3.4    | P/N Ratio Sizing             | 65 |

|   |      | 4.3.5    | Multiplexer Voltage Drop     | 66 |

|   |      | 4.3.6    | Short-Circuit Buffer Factor  | 67 |

|   | 4.4  | Summ     | ary                          | 68 |

| 5 | Veri | fication | and Results                  | 70 |

|   | 5.1  | Verific  | eation of Power Estimation   | 70 |

|    |        | 5.1.1    | Verification Procedure       | 71 |

|----|--------|----------|------------------------------|----|

|    |        | 5.1.2    | Verification Results         | 72 |

|    | 5.2    | Source   | es of Estimation Error       | 75 |

|    |        | 5.2.1    | Short-Circuit Current        | 75 |

|    |        | 5.2.2    | Transistor Node Capacitances | 76 |

|    |        | 5.2.3    | Gate Leakage Currents        | 77 |

|    | 5.3    | Experi   | ment 1: Component Breakdown  | 77 |

|    |        | 5.3.1    | Methodology                  | 77 |

|    |        | 5.3.2    | Results                      | 78 |

|    |        | 5.3.3    | Analysis                     | 78 |

|    | 5.4    | Experi   | ment 2: Fracturable LUTs     | 80 |

|    |        | 5.4.1    | Methodology                  | 81 |

|    |        | 5.4.2    | Results                      | 81 |

|    |        | 5.4.3    | Analysis                     | 83 |

|    | 5.5    | Summ     | ary                          | 84 |

| 6  | Con    | clusions | s                            | 86 |

|    | 6.1    | Future   | Work                         | 87 |

|    | 6.2    | Summ     | ary of Contributions         | 89 |

| Bi | bliogi | caphy .  |                              | 90 |

## **List of Tables**

| Table 1.1 | Comparison of this work with past power models | 6  |

|-----------|------------------------------------------------|----|

| Table 3.1 | System modules                                 | 30 |

| Table 5.1 | CMOS process characteristics                   | 72 |

| Table 5.2 | Accuracy of high-activity power estimations    | 73 |

| Table 5.3 | Accuracy of zero-activity power estimations    | 74 |

| Table 5.4 | Power breakdown by component type              | 78 |

| Table 5.5 | Power usage, and breakdown by circuit          | 79 |

| Table 5.6 | Power of fracturable LUTs                      | 82 |

# **List of Figures**

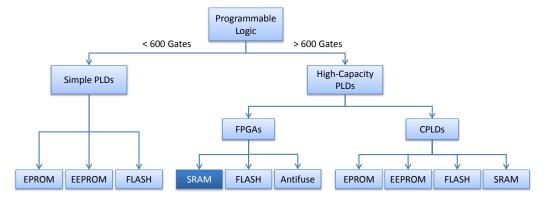

| Figure 2.1 | Taxonomy of PLD devices                                | 10 |

|------------|--------------------------------------------------------|----|

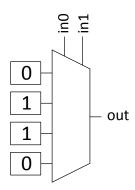

| Figure 2.2 | 2-input LUT                                            | 12 |

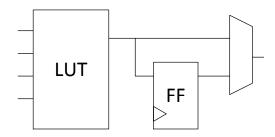

| Figure 2.3 | Basic logic element (BLE)                              | 12 |

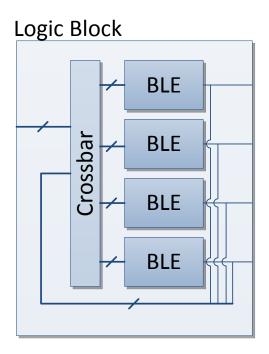

| Figure 2.4 | Logic block containing 4 BLEs                          | 13 |

| Figure 2.5 | FPGA architecture                                      | 14 |

| Figure 2.6 | Heterogeneous FPGA architecture                        | 16 |

| Figure 2.7 | Fracturing of a LUT                                    | 17 |

| Figure 2.8 | FPGA CAD flow                                          | 18 |

| Figure 2.9 | Circuit abstraction levels                             | 21 |

| Figure 3.1 | Modifications to the VTR flow for power estimation     | 29 |

| Figure 3.2 | Switch box component                                   | 35 |

| Figure 3.3 | Connection box                                         | 36 |

| Figure 3.4 | 4:1 2-level multiplexer                                | 37 |

| Figure 3.5 | 4:1 2-level multiplexer, decomposed into single-levels | 37 |

| Figure 3.6 | Multi-stage buffer                                     | 39 |

| Figure 3.7  | Types of local interconnect                   | 42 |

|-------------|-----------------------------------------------|----|

| Figure 3.8  | Local interconnect spanning distance          | 44 |

| Figure 3.9  | Wire length in a local interconnect structure | 45 |

| Figure 3.10 | 4-input LUT                                   | 47 |

| Figure 3.11 | D Flip-Flop                                   | 48 |

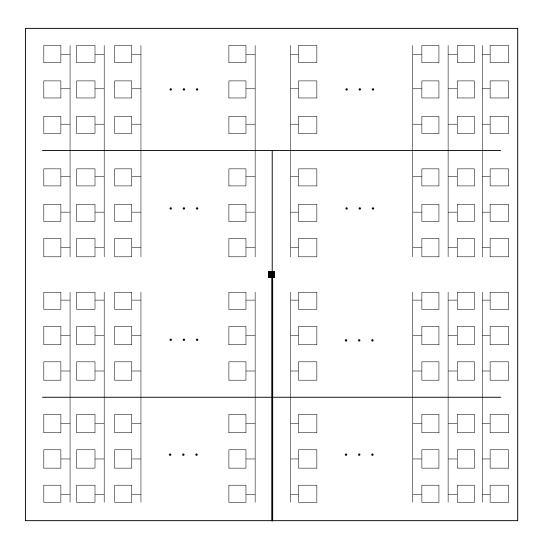

| Figure 3.12 | The clock network                             | 51 |

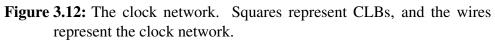

| Figure 4.1  | Subthreshold leakage in a multiplexer         | 60 |

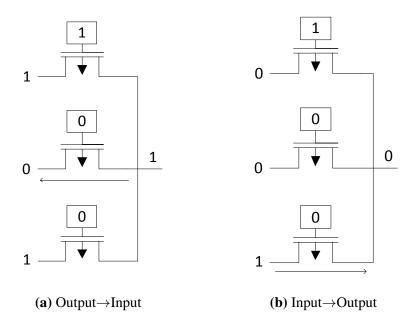

| Figure 4.2  | Short circuit currents in inverters           | 67 |

## Acronyms

- ASIC application-specific integrated circuit.

- BLE basic logic element.

- CAD computer-aided design.

- CLB configurable logic block.

- FPGA field-programmable gate array.

- HDL hardware description language.

- ITRS International Technology Roadmap for Semiconductors.

- LUT look-up table.

- **PLD** programmable logic device.

- **PTM** Predictive Technology Model.

- **RTL** register-transfer level.

**SPICE** Simulation Program with IC Emphasis.

- VLSI very-large-scale integration.

- **VPR** Versatile Place and Route.

- VTR Verilog-to-Routing.

## Acknowledgments

First and foremost, I would like to thank my family. My wife, Jessie, for her encouragement to complete this degree, and her support and patience during busy times. My parents, for their examples, and their emphasis on the value of education.

This work would not be possible without the guidence, instruction and example of my supervisor, Steve Wilton. He is always generous with his time, providing ideas, editing papers, and answering questions.

I would also like to thank my labmates for their help and suggestions: Kyle Balston, Assem Bsoul, Stuart Dueck, and Eddie Hung, as well as others who answered questions, and gave advice: Jason Luu, Guy Lemieux, Jonathan Rose, and the VTR team.

I would also like to thank NSERC and Altera for funding this research.

## **Chapter 1**

## Introduction

### **1.1 Motivation**

Power dissipation has become a first-class concern in the development of new integrated circuits. For the past 9 years, the International Technology Roadmap for Semiconductors (ITRS) has identified power consumption as one of the top three challenges facing semiconductor development [1], and in the latest report [2], it states that power management will continue to be a grand challenge in the foreseeable future. In the past, dynamic power was the primary concern, growing rapidly as circuit operating frequencies increased. However, as transistor technologies have scaled down, static power from leakage currents has become equally important. In fact, the ITRS predicts that in the long-term, static power increases will lead to a major industry crisis, threatening the survival of CMOS technologies [2]. The ITRS classifies devices into three types: 1) high-performance, 2) costperformance, and 3) portable, or battery-powered. Power is a major design factor in all of these categories. In high-performance, such as desktop processors, the power must not exceed the rate at which heat can be removed from the device. In cost-performance, the goal is to reduce the energy cost per computation; for example, in server farms [3]. In portable applications, an area of rapid growth, power is minimized in order to extend battery life. In addition, the ITRS cites the need to reduce global energy usage as a motivating factor in reducing power consumption of electronic devices [1].

This work focuses on power consumption of one type of integrated circuit, field-programmable gate arrays (FPGAs). FPGAs are a type of user programmable computer chip. They contain many programmable logic blocks that can be used to implement circuits with hundreds of thousands of logic gates. These logic blocks are surrounded by a vast network of configurable routing segments. Together, the logic and routing allow FPGAs to implement almost any type of digital circuit.

This flexibility has made FPGAs a popular choice in many different circuit applications, including both high-performance [4] and cost-performance [5, 6] scenarios. However, the flexibility comes at a cost; the generic logic and routing in an FPGA have a large overhead, requiring a larger circuit and more power than an application-specific integrated circuit (ASIC). One study found that FPGAs require over 10 times the power of an equivalent ASIC [7].

The power usage of an FPGA depends on two main factors: 1) the FPGA architecture, which includes how the FPGA is designed and which CMOS tech-

nology is used, and 2) the user circuit, including how the circuit is mapped to the FPGA resources. This mapping of the user circuit to the FPGA is performed by computer-aided design (CAD) tools. Recent years have seen numerous techniques for creating power-efficient FPGA architectures [8, 9], power-aware CAD algorithms [10, 11], and low-power applications [12]. As the capacities of FPGAs continue to grow, the importance of power efficient operation will only increase.

In order to evaluate new FPGA architectures, or new CAD algorithms, researchers need a customizable CAD flow that supports experimental architectures. Furthermore, if researchers want to investigate how these architectures and algorithms affect power dissipation, an accurate power model, typically integrated into the CAD tools [13, 14], is required. Although vendor tools can quickly estimate the power dissipation of an application on an existing FPGA, they cannot be used to estimate the power of novel architectures or new low-level mapping algorithms.

Versatile Place and Route (VPR) [15], an academic, open source, FPGA CAD tool has become the most popular tool used in the academic community to test experimental FPGA architectures and CAD algorithms. When VPR was first released in 1997, it supported only basic FPGA architectures. Over time, new FPGA architectures and algorithms have been developed by industry and academia, and many have been integrated into VPR.

Throughout these years, there have been power models that have been developed, which integrate with VPR. These include the Poon model [13], the Jamieson model [14], and the Li model [16]. These models use probabilistic power estimation [17], as opposed to simulation, with a switch-level abstraction of the FPGA circuit. This allows for fast power estimations that are sufficiently accurate to evaluate architectural trade-offs. These models were integrated with VPR 4.3 and VPR 5.0, which supported only simple FPGA architectures with a handful of configuration parameters.

Recently, a new version of VPR has been developed, VPR 6.0. This new version of VPR is a significant advance over its predecessors; among other improvements, it includes an overhaul of the types of FPGA architectures than can be supported. The tool now supports an architecture description language that users can leverage to test custom FPGA architectures, with support for complex logic blocks. Users can define a hierarchy of block types, which can be used to describe traditional FPGA architectures, as well as more modern features, such as fracturable look-up tables (LUTs). In addition, user-defined heterogeneous hard-blocks, such as memories and multipliers, are now supported. One demonstration of functionality included the evaluation of a floating point unit within an FPGA architecture [18].

This new tool opens the door for research into many more types of FPGA architectures. However, its powerful architecture language requires a much more flexible power model than any previously developed. The past power models, while flexible enough to support different lookup-table sizes, cluster sizes, and interconnect topologies, are not able to estimate the power dissipation for *most* architectures that will be studied using the new CAD flow. This new CAD flow is the door to the investigation of much more exotic architectures than ever before,

yet without an accompanying flexible power model, this potential will not be fully realized.

Another issue with past power models is that they are outdated in the assumptions they make regarding CMOS technology. The power estimations made in those models were targeted to technologies ranging in the hundreds of nanometres. However, today's technologies range in the tens of nanometres, and many of the modelling techniques used in the past models are not accurate at this level.

### **1.2** Contributions of this Work

Although FPGA power models have been created in the past, they were designed for a single, simple architecture, with known circuitry. This work explores a method for estimating power usage for *many different* user-created architectures. This requires a fundamentally new technique. Although the user specifies the functionality of the architecture, the actual circuitry is not specified. These functional descriptions of FPGA architectures must be translated into physical circuits. After this translation to circuit components, power estimation can be performed.

We have implemented, verified, and used this new approach to FPGA power modelling as follows:

1. We have devloped a power model, integrated into the VPR 6.0 CAD flow, which is capable of providing power estimations for *all* architectures supported by the tool. In addition, we have added detailed static power estimation, and support for fracturable LUTs, hard blocks, and modern CMOS

| Feature                                | Poon/<br>Jamieson<br>Models | Li Model      | This Work     |

|----------------------------------------|-----------------------------|---------------|---------------|

| Architectures Supported                | Traditional                 | Traditional   | User-designed |

| CMOS Technologies                      | 180 nm                      | 100 nm        | 22-130 nm     |

| Fracturable LUTs                       | No                          | No            | Yes           |

| Hard Blocks                            | No                          | No            | Yes           |

| Static Power                           | Worst-case                  | Worst-case    | Detailed      |

| Autosizing of buffers and interconnect | No                          | No            | Yes           |

| Transistor Properties                  | User-provided               | User-provided | Automatic     |

**Table 1.1:** Comparison of this work with past power models.

processes. Table 1.1 provides a comparison of this model to past FPGA power models.

- The power estimations of the model are verified against SPICE simulations. Dynamic power estimates are within 20% and static power estimates are within 5%.

- 3. The model is used to investigate power characteristics of different FPGA architectures. This includes a breakdown of power beween FPGA components, and a study of the power characteristics of fracturable LUTs.

### 1.3 Challenges

In undertaking these research goals, there are two major challenges that exist. First, the new model must be flexible enough to process *any* architecture that can be described using VPR 6.0's architecture description language. Providing such flexibility, while maintaining accuracy and ease-of-use is a significant challenge. The limited coverage of previous models meant that it was reasonable to ignore some FPGA components that did not contribute greatly to the overall power, such as local interconnect buffers, local wire capacitance, and internal multiplexer nodes. However, to accurately cover the much enlarged design space, all of these components must be accurately modelled.

Secondly, in past models, the most detailed estimations were performed for the dynamic switching power, where switch-level estimation was performed on every transistor. However, other contributers to power were estimated in less detail. Subthreshold leakage was calculated using a simple worst-case estimate, and short-circuit power was simplified to be 10% of dynamic power. However, when modelling transistors into the tens of nanometres, these secondary power components begin to play a greater role in the overall power dissipation. More detailed estimation methods are necessary to obtain acceptable levels of accuracy.

### **1.4 Overview of Results**

This thesis includes a new power model, designed to work with architectures in versions 6.0 (and higher) of the VPR tool suite. The model is validated against 22 nm, 45 nm and 130 nm technologies. When compared to SPICE circuit simulations, the estimates of our model were within 20% for dynamic power estimations and within 5% for static power estimations.

Once verified, we use the model to study the power characteristics of different architectures. In the first of two experiments we test the power breakdown between major FPGA components for the three different technologies. Results show that for a 45 nm 6-LUT, 10 LUTs per CLB architecture, 73% of power usage is due to the routing fabric, 21% due to logic blocks and 3% due to the clock network (single clock). In the second experiment we study the effect of fracturable LUTs on overall power usage. Of particular interest is the fact that modifying the architecture to support fracturable LUTs increases power consumption by 3.5-14%.

### **1.5** Thesis Organization

The thesis is organized as follows: Chapter 2 provides background information on FPGAs, CAD tools, power estimation techniques, and power models. Chapter 3 provides an overview of our power model and details the architecture generator. The architecture generator creates the entire FPGA circuitry from the usersupplied architecture description. Chapter 4 details the low-level power modelling, which describes how power estimation is performed once the FPGA circuitry is known. Chapter 5 provides verification of the model, as well as experiments that test the power characteristics of different FPGA architectures. Chapter 6 concludes the document.

## **Chapter 2**

## Background

This chapter provides background information on FPGAs, their architecture, and their associated CAD tools. It also outlines different power estimation techniques, including descriptions of the estimation methods used by past power models.

## 2.1 FPGAs

Programmable logic devices (PLDs) are electronic components that are programmed by the user to implement a digital circuit. Unlike fixed logic devices, which are manufactured for a specific function, PLDs are standard, off-the-shelf parts, that can be used for a wide range of functions. PLDs offer many advantages over fixed logic, such as shorter design times, lower non-recurring costs, and in some devices the ability to be reprogrammed [19]. Figure 2.1 shows a taxonomy of PLDs. This work focuses on power estimation for one type of PLD, SRAM-based field-programmable gate arrays (FPGAs).

Figure 2.1: Taxonomy of PLD devices, from [20].

Field-programmable gate arrays (FPGAs) are the largest devices in the PLD family, containing thousands to millions of logic gates [20]. FPGAs consist of many fined-grained logic elements, surrounded by a very large segmented routing network. This design makes FPGAs highly flexible, and capable of implementing virtually any digital circuit. Most FPGA architectures are programmed by configuring a set of SRAM bits, which control the logic and routing of the chip [21]. This allows the FPGA to be reprogrammed as needed. The size, flexibility, and reprogrammability has led to the use of FPGAs in many applications, such as ASIC prototyping, image processing, internet infrastructure, medical devices, automotive, and others.

#### 2.1.1 Basic Architectures

The first FPGAs were introduced by Xilinx Inc. in 1985. Early FPGA architectures contained three main components: 1) logic blocks, 2) routing, and 3) I/O blocks [22]. Logic blocks are responsible for performing the actual computation, such as arithmetic or logical functions. Routing allows for data to be moved between logic blocks, and I/O blocks allow for data to be moved on and off the FPGA chip [21]. The following sections describe the logic blocks and routing in greater detail.

#### 2.1.1.1 Logic Blocks

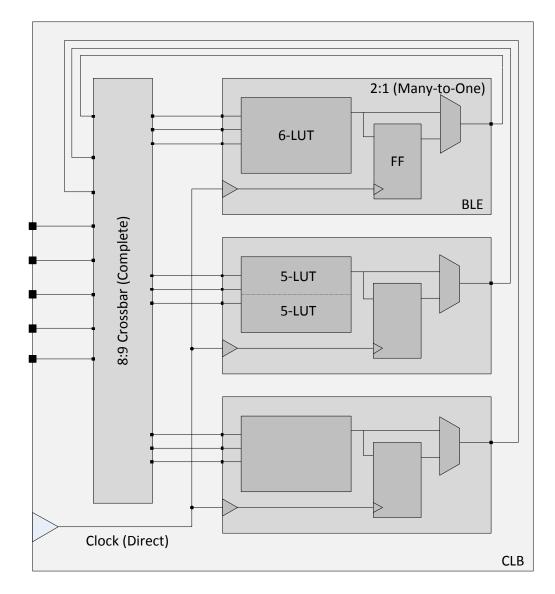

The basic functional unit within the FPGA is the look-up table (LUT). A *k*-input LUT has  $2^k$  configuration bits, which are used to store the values of a *k*-input truth table. The inputs to the LUT control a multiplexer which chooses between the stored values (Figure 2.2). A *k*-input LUT can implement any *k*-input logic function, since any logic function can be represented in truth table form [21]. Typically, LUTs are paired with a flip-flop, which saves state, and allows for implementation of sequential circuits. The LUT and flip-flop, together with a multiplexer to select between the two outputs, are referred to as a basic logic element (BLE) (Figure 2.3).

Multiple BLEs are combined to form a logic block, also known as a configurable logic block (CLB). FPGA architectures differ in the number of BLEs per CLB. For example, the Altera Stratix V architecture uses 10 BLEs per block [23], and the Xilinx Virtex 7 architecture uses 8 BLEs per block [24]. The logic block also contains routing structures that connect the input and output pins of the logic block to the BLEs, as well as connecting the BLEs to each other. These connections are referred to as local interconnect, and are often implemented as a single

Figure 2.2: 2-input LUT, implementing the XOR function.

Figure 2.3: Basic logic element (BLE).

crossbar [25]. Figure 2.4 shows a logic block that contains 4 BLEs, with a local interconnect crossbar.

#### 2.1.1.2 Routing

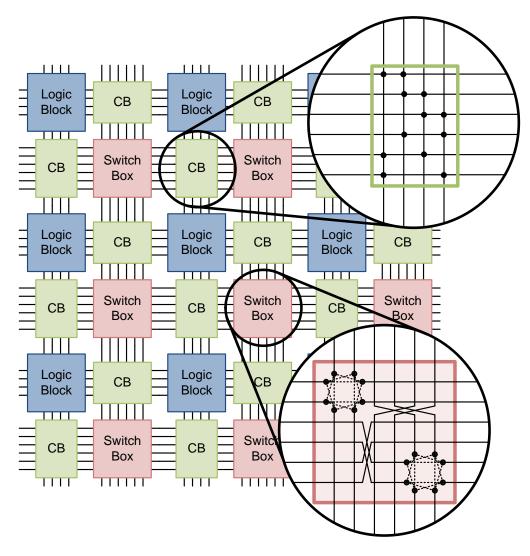

Most FPGAs employ an island style architecture, where the logic blocks are arranged in a grid, and are surrounded by many horizontal and vertical routing segments. Modern FPGAs usually use unidirectional routing segments, while older FPGAs used bidirectional routing [26, 27]. The routing segments are connected to each other through a *switch box*, and the logic blocks connect to the routing channels through *connection boxes* [28]. Figure 2.5 provides an illustration of a

Figure 2.4: Logic block containing 4 BLEs.

simple, hypothetical FPGA architecture. Commercial FPGAs vary in their implementation details, and sometimes the connection boxes and switch boxes are combined into a single structure.

Switch boxes are located at the intersection of vertical and horizontal routing segments. They contain programmable switches that allow each wire segment to connect to multiple other wire segments, in order to route signals throughout the FPGA. The topology of these connections depends on the FPGA architecture [29, 30]. In addition, the architecture may be designed to contain longer wire segments that bypass some switch boxes [26]. Figure 2.5 shows an architecture than contains a combination of length-1 and length-2 wire segments.

**Figure 2.5:** Island-style FPGA architecture, containing logic blocks, switch boxes and connection boxes. This architecture contains both length-1 and length-2 routing segments.

Connection boxes provide the connection between the routing segments and the logic blocks pins. Each logic block pin connects to some of the neighbouring routing channels, as illustrated in Figure 2.5. Real-world architectures may contain routing channels that are hundreds of segments wide, so it is not feasible for each pin to connect to all of the channels [27]. The pattern of connections is determined by the FPGA vendor. Each connection is programmable, and can be either enabled or disabled when configuring the FPGA.

#### 2.1.2 Modern Architectures

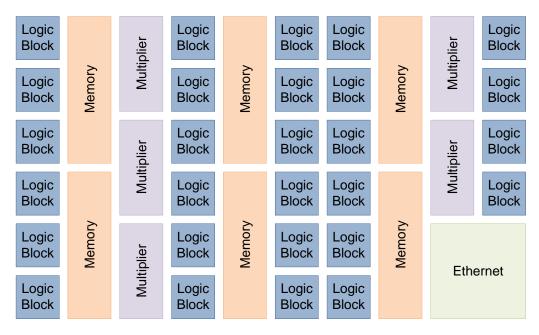

Modern FPGA are much more complex than described above. They have evolved from a homogeneous architecture, as described previously, to heterogeneous architectures that contain many different types of blocks, and blocks with complex features.

#### 2.1.2.1 Heterogeneous FPGAs

In heterogeneous architectures, some logic blocks are replaced by memories and multipliers, to more efficiently implement certain functions (Figure 2.6) [27]. There may be multiple types of logic blocks throughout the FPGA; for example, some blocks may contain larger or smaller LUTs [31]. Additional hard cores may also be built into the FPGA to accelerate some functions, such as ethernet interfaces or SerDes functions [23]. Some FPGAs also contain built-in processors. As an example, the Altera Cyclone 5 SoC FPGAs contain an ARM Cortex-A9 core [32].

Figure 2.6: Heterogeneous FPGA architecture (routing not shown).

#### 2.1.2.2 Complex Logic Blocks

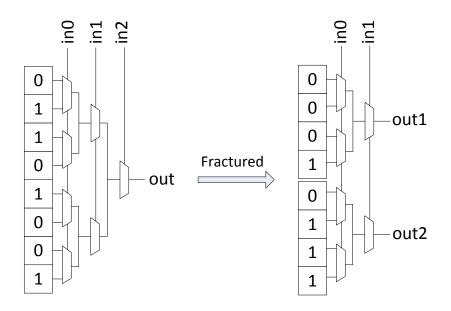

Modern logic blocks contain additional features, such as carry-chain logic and fracturable logic. Carry-chain logic provides support for accelerating arithmetic and logical operations [33]. Fracturable logic allows LUT hardware to be split so that LUTs can implement two smaller logic functions, instead of a single large function. This is accomplished by allowing the truth table to be shared between two logic functions, splitting the multiplexer, and providing an extra output. Figure 2.7 illustrates the modifications to enable fracturable LUTs. This work provides power estimations of FPGA architectures containing fracturable LUTs; however, carry-chains are not yet supported.

**Figure 2.7:** Fracturing of a LUT. On the left is a 3-input LUT, implementing a 3-input XOR function. On the right, the same hardware is used to implement two 2-input functions. Out1 implements the AND function, and out2 implements the OR function.

### 2.2 FPGA Computer Automated Design (CAD)

Modern FPGAs contain millions of configuration bits, making it impractical for designers to manually implement their circuits. Instead, computer-aided design (CAD) tools are used, which perform the steps required to translate a hardware description language (HDL) circuit to a set of configuration bits used to program the FPGA [34].

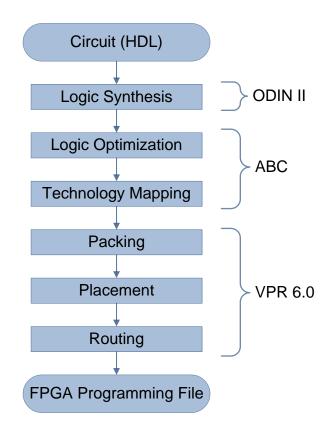

### 2.2.1 CAD Flow Steps

Figure 2.8 illustrates the steps of the FPGA CAD flow, and the following briefly describes each step.

Figure 2.8: FPGA CAD flow [34], with associated tools [18].

- *Logic Synthesis* converts a circuit specified in register-transfer level (RTL) format, such as Verilog or VHDL, to a gate-level representation [35].

- *Logic Optimization*, often called technology-independent optimization, removes redundant logic and simplifies logic where possible [36].

- *Technology Mapping* converts the logic functions to fit within the LUTs. For example, if the FPGA architecture uses 4-input LUTs, all logic functions must be transformed into functions with four or less inputs.

- *Packing* groups the LUTs together into logic blocks.

- Placement decides where each logic block should be placed on the FPGA.

- *Routing* determines the configuration of the routing switches to provide connections between the necessary logic blocks pins.

Upon completion of this flow, the CAD tools will have determined the configuration bits for the LUTs, the local interconnect switches, and the global interconnect switches. These configuration bits are combined into a file called a *bitstream*, which is used to program the FPGA.

#### 2.2.2 Verilog-to-Routing (VTR)

FPGA power models are typically integrated into CAD tools because the power estimation is dependent on placement and routing information [13, 14, 16]. In addition, integration of CAD and power estimation allows for the development of power-aware CAD algorithms, such as in [10].

The power model presented in this work is integrated with Verilog-to-Routing (VTR), a recently developed, academic, open-source FPGA CAD suite [18]. VTR is a collection of tools that are used to perform the full CAD flow. ODIN II [37] is used for logic synthesis, and converts a Verilog circuit to a gate-level sum-of-products representation. Next, ABC [38] performs logic optimization using logic balancing and refactoring algorithms [39], followed by technology mapping using the WireMap algorithm [40]. Finally, VPR 6.0 performs packing, placement and routing. Packing uses the AAPack algorithm [41], placement uses a simulated annealing algorithm [15, 42], and routing is performed using the Pathfinder

algorithm [43]. Together, these tools allow researchers to test experimental FPGA architectures that are not supported by commercial tools.

Past FPGA CAD tools, such as VPR 4.3 [15] and VPR 5.0 [44], supported basic homogeneous FPGA architectures with some user-supplied parameters to configure the architecture. The architecture space supported by VTR is dramatically larger. It supports heterogeneous architectures, hard blocks and complex logic blocks. The architecture is specified through a new *architecture description language*, which users can leverage to provide a much more detailed specification of the FPGA architecture. In the past users were restricted to the traditional paradigm for logic block design; however, this new language allows users to fully customize logic blocks. The language supports a hierarchical model, where logic blocks are comprised of entities. Each entity can instantiate child entities, with custom interconnect between parent and children. This allows for exotic FPGA architectures with arbitrary complexity.

### **2.3** Power Estimation Techniques

Power estimation techniques for very-large-scale integration (VLSI) circuits can be classified in two ways: 1) the level of abstraction, and 2) the method of estimation, either *simulation* or *probabilistic* [17, 45, 46].

#### 2.3.1 Abstraction Levels

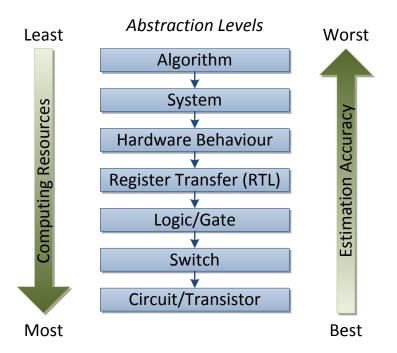

Figure 2.9 provides the different circuit abstraction levels at which power estimation can be performed [45]. More detailed circuit abstractions allow for more

Figure 2.9: Circuit abstraction levels used for power estimation, and impacts on accuracy and resources.

accurate power estimations, but at the cost of increased computation. Likewise, higher abstractions allow for quicker estimations, but with reduced accuracy. Generally, power estimation tools operate at the gate-level or lower, as it is difficult to obtain sufficient accuracy at higher levels [46].

The most commonly used abstraction levels are *gate-level*, *switch-level*, and *circuit-level*. Circuit-level estimation requires detailed transistor models in order to determine nonlinear voltages and currents. Switch-level simplifies the circuit to a collection of nodes and transistors, where each node is modelled as a capacitance to ground, and each transistor is modelled as an on/off switch with finite

resistance. Gate-level further abstracts the design, grouping transistors into logic cells, such as NAND, NOR, etc [47].

It is possible to model FPGA hadware at the lowest abstraction levels. The GILES project [48] provides a tool for generating complete transistor layouts based on VPR architectures. Although this level of detail allows for the most accurate power estimations, it is rarely used for large circuits due to computational requirements. For large circuits, such as FPGAs, it is more feasible to perform power estimation at the switch-level or gate-level.

#### 2.3.2 Simulation-Based Power Estimation

Power estimation through simulation is performed by providing a set of inputs to the circuit, simulating the circuit for a predetermined number of clock cycles, and measuring the power. Although simulation can provide accurate power estimations, it suffers from being computationally intensive and being highly dependent on circuit inputs, known as *strong input-pattern dependence*.

Simulation Program with IC Emphasis (SPICE) is the de facto tool for circuitlevel simulation and power analysis, and provides very accurate estimations. However, the level of detail of SPICE leads to long run times as circuits increase in size, making SPICE unsuitable for very large circuits, such as FPGAs [46]. Other approaches have performed simulation at higher abstraction levels, such as switchlevel or gate-level, to reduce the amount of computation [49–51].

However, even if computation can be reduced, the issue remains that the power dissipation is highly dependent on the inputs provided to the circuit; inputs that are more active will cause the circuit to consume more power. In order to provide accurate estimation, realistic input vectors are required. It may be difficult to generate realistic input vectors, especially if the circuit is still under design [17]. One solution to this problem is to use a statistical approach, which employs a Monte Carlo simulation with randomly generated input vectors [52, 53]. This technique involves repeatedly generating random input vectors, performing gate-level simulation, and measuring the power, until the result reaches a certain accuracy and confidence level.

The statistical Monte Carlo method provides acceptably accurate estimates, without substantial computation; however, the estimate is only of the total power. It does not provide visibility to the gate level, or even groups of gates [17]. This internal visibility is a desired property as it allows designers to determine the power requirements of different architectural components. In [54], the Monte Carlo method was modified to add internal visibility, but the increase to run time was significant.

#### 2.3.3 Probabilistic Power Estimation

The other method of power estimation is the probabilistic approach. The major advantage over simulation is that it does not require actual input vectors, only statistical properties of the inputs, and thus is characterized as being *weakly input-pattern dependent*. The behaviour of the inputs is characterized using the following two properties [17]:

- 1. <u>The Signal Probability</u>,  $P_1$ , is the long-term probability that a signal is logichigh. For example, a clock signal with a 50% duty cycle will have  $P_1(clk) = 0.5$ .

- 2. <u>The Transition Density</u> (or switching activity),  $A_S$ , is the average number of times the signal will switch during each clock cycle. For example, a clock has  $A_S(clk) = 2$ .

Once the user provides the signal probability and transition density for the inputs, activity estimation tools such as [13, 37, 55–57] can be used to determine these properties for the internal nets. These tools use simulation, static analysis, or a combination of both to determine these properties. Once these properties are known for all nets, power estimation can be performed. For example, switching power is directly proportional to the transition density, and leakage currents are dependent on the signal probabilities [58].

Although the probabilistic method is faster than simulation, and less input dependent, it is generally less accurate [45]. The signal properties used by the probabilistic method assume certain statistical behaviour, which may not be true of the actual input signals. The first assumption is that all signals are independent, referred to as *spatial independence* [17]. In reality, signals may be correlated; for example, two signals may never be logic high at the same time. Another assumption is that signal values are independent from one clock cycle to the next, referred to as *temporal independence* [17]. These behaviours cannot be captured in the signal probability or transition density metrics.

Although the probabilistic approach is less accurate than simulation, it requires much less computation resources, making it possible to use more detailed abstraction levels [45]. This allows for finer-grained power details, with less run time.

### 2.4 FPGA Power Estimation Tools

There have been three major power models developed for use with academic FPGA CAD tools. They are outlined in the following sections, including a description of the approach used in this work.

#### 2.4.1 The Poon Power Model

The Poon power model [13] was developed by Kara Poon at the University of British Columbia in 1999. The tool was designed to work in conjunction with the popular academic CAD tool VPR 4.3. It supports a traditional homogeneous architecture with bidirectional routing, as described in Section 2.1.1. It includes architecture parameter support for LUT suze, LUTs per logic block, and interconnect topology. The model uses a probabilistic approach to power estimation and switch-level circuit abstraction. This work also includes ACE-1.0 [13], a tool that provides activity estimations of signals.

The Poon power model calculates switching power of all transistors in the FPGA, based on the switching density of the signals. Short-circuit power is assumed to be 10% of dynamic power. Subthreshold leakage is calculated using the equation in [59]. A worst-case is assumed for subthreshold leakage where half of

all CMOS transistors, and all pass-transistors, are assumed to be leaking. Other types of static power, such as gate leakage, are ignored.

#### 2.4.2 The Jamieson Power Model

The Jamieson model [14] was developed by Peter Jamieson in 2009. This is a modified version of the Poon model, designed to work in conjunction with VPR 5.0. The main difference is that it supports more modern routing topologies, the most significant being unidirectional routing. Also, this model uses ODIN II [37] to perform activity estimation, instead of ACE-1.0. The model uses the same techniques as the Poon model to calculate the dynamic and static power dissipation, and supports the same architectural parameters.

#### 2.4.3 The Li Model

The Li model [16] was developed by Fei Li, et. al. in 2005, and was designed to work in conjunction with VPR 4.3. Like the other models, it supports a traditional architecture with basic parameters. Like the others, this model uses a probabilistic approach to power estimation. Switch-level abstraction is used for the routing and clock network. To reduce computation, a higher level abstraction is used for logic blocks, where macro-modelling is used to estimate power dissipation of LUTs. Like the other models, this model uses the signal activity to calculate switching power. Short-circuit power estimation is more detailed, and is calculated by using SPICE to simulate buffers of various sizes. A similar simulation approach is used for subthreshold leakage estimation.

#### **2.4.4** The Estimation Technique of this Work

This power model presented in this work also uses a probabilistic approach. This was chosen as it allows for fine-grained estimation without the heavy computation requirements of simulation. Although not as accurate as simulation, it is sufficient to evaluate trade-offs during architecture design [46]. The majority of this work uses switch-level abstraction, although in some cases more detailed modelling is used. Since VTR supports arbitrary user-designed logic blocks it is not feasible to use higher abstraction levels, as was done in the Li model.

The major difference between this model and past models is the type of architectures supported. Past models only supported a traditional homogeneous architecture, with limited parameters. This model supports many new features such as heterogeneous architectures, hard blocks—such as memories and multipliers and complex logic blocks that contain fracturable LUTs. Furthermore, while the past tools supported only a few architecture parameters, the architecture engine in VTR allows for custom designed blocks with arbitrary complexity. This architecture flexibility makes this model fundamentally different than past power models. The following chapters explain this new power model.

# **Chapter 3**

# System Design and Architecture Generation

This chapter begins by providing an overview of the new power model, and an explanation of how the model is integrated into the VTR CAD flow. The remainder of the chapter details the architecture generator. This module is the largest piece of the power model. It generates the entire FPGA circuitry based on the user-described architecture.

## 3.1 Power Model Overview

The power model is integrated into VTR, an academic experimental FPGA CAD flow [18]. This flow was designed to allow researchers to investigate novel FPGA architectures and the associated CAD algorithms. New FPGA architectures (such as new logic block or routing structures) can be described using an architecture

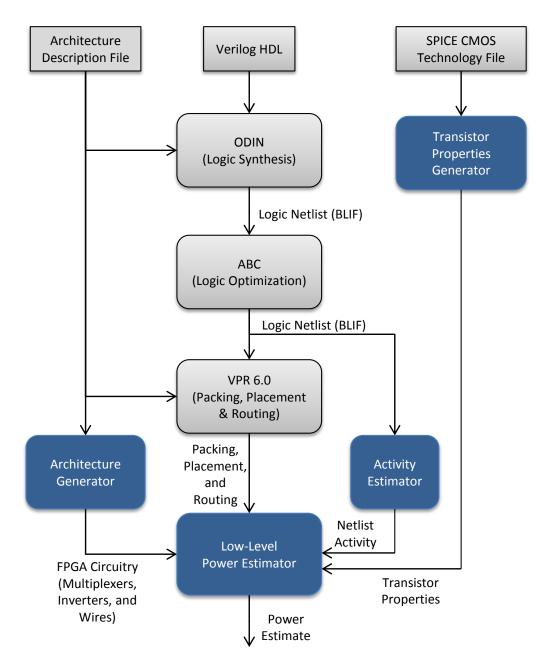

Figure 3.1: Modifications to the VTR flow for power estimation.

description language, and the CAD tools will automatically adapt to the new architecture. The original VTR flow contains detailed area and delay models which can be used to evaluate the efficiency of benchmark circuits implemented on the proposed architectures. Since the code is open-source, designers can also modify the CAD tools themselves to investigate the effectiveness of new CAD techniques, applied to novel or existing FPGA architectures.

The current VTR flow uses ODIN II [37] for Verilog synthesis, ABC [38] for logic optimization and VPR 6.0 for packing, placement and routing. Our power model adds multiple components which are integrated into the VTR flow as shown in Figure 3.1. Table 3.1 provides a listing of the model components, their purpose, and the relevant sections in this thesis.

| Module                          | Function                                             | Section     |

|---------------------------------|------------------------------------------------------|-------------|

| Architecture Generator          | Generates FPGA circuitry                             | Section 3.2 |

| Low-Level Power Estimator       | Estimates dynamic and static power                   | Section 4.1 |

| Activity Estimator              | Estimates behaviour of the user circuit              | Section 4.2 |

| Transistor Properties Generator | Extracts transistor properties from SPICE simulation | Section 4.3 |

#### Table 3.1: System modules.

The first step in estimating power usage is to determine the actual FPGA circuitry. This is a difficult task, since VTR's architecture description language allows the user to create arbitrary architectures, with no limit on complexity. This task is performed by the architecture generator, which reads the architecture description file provided by the user, and generates the circuitry of the entire FPGA. This circuitry is a collection of inverters, simple multiplexers and wires, and includes details of the transistor sizes and wire lengths. All major components such as flip-flops, LUTs, switch boxes, etc. are decomposed into these basic circuit elements.

The FPGA power usage is also dependent on the behaviour of the user-provided circuit. The activity estimator analyzes the user circuit to determine its behaviour, which includes the transition density ( $A_S$ ) and the signal probability ( $P_1$ ) for each net. The power usage also depends on how the user circuit is implemented in the FPGA circuitry. These details are contained in the packing, placement and routing information that is output by VPR.

Power estimation is also heavily dependent on the chosen CMOS technology. The transistor properties generator uses SPICE simulation to automatically extract the necessary transistor properties, which includes transistor sizes and capacitances, leakage currents, and other characteristics.

Once the information on the FPGA circuitry, the user circuit, and the transistor properties are obtained, the actual power estimation can be performed. The lowlevel power estimator uses standard equations to calculate the dynamic and static power of each inverter, multiplexer and wire in the FPGA circuitry. It details how much each component type, such as switch boxes, flip-flops and crossbars, contribute to the overall power.

Our implementation combines VPR 6.0, the low-level power estimator, and the architecture generator into a single executable. However, in this document they are described as separate entities to clearly outline their roles in the overall power estimation.

The remainder of this chapter will describe the architecture generator module. The other modules will be detailed in the following chapter.

## 3.2 The Architecture Generator

Complete power estimation requires transistor-level details of the entire FPGA circuitry in order to make power estimations. This includes the size and connections of every transistor, as well as wire length of all interconnect. Since there are millions of transistors in a typical experimental architecture, it is infeasible for the user to provide this information directly. The architecture generator analyzes the architecture description file supplied by the user, and determines the entire FPGA circuitry. All of the FPGA components (switch boxes, connection boxes, LUTs, flip-flops, etc.) are decomposed into inverters, simple multiplexers, and wires. The size of each transistor, and the length of each wire, is calculated automatically.

Generating this information is challenging. The architecture language provided in VPR 6.0 is extremely flexible, allowing the user to specify a wide variety of architectures. CLBs can be arbitrarily complex, consisting of a hierarchal collection of interconnect and logic elements (including facturable LUTs). The global interconnect can consist of segments of different lengths connected using different patterns. Transistor sizes, which have a first-order affect on power, depend on the physical length and fanout of segments, which depends on, among other things, the number of transistors in various components of the architecture.

VPR 6.0 contains an architecture generation engine which estimates many of these low-level quantities based on the user-described architecture. However, the existing engine is limited to generating parameters needed for timing analysis and area estimation. Power estimation requires a much more complete set of quantities; buffers cannot be abstracted as delay elements, and accurate buffer sizes are needed, even for those buffers not on the critical path. This work provides a significantly enhanced architecture generation engine that provides the information needed to make accurate dynamic and static power estimates.

It is important to note that previous models in [13, 14] also contain an architecture generation engine; however, the limited architectural space supported by earlier versions of VPR means that the generator was far less flexible. Thus, these previous generators are not suitable for our purpose.

Section 3.2.1 describes the methods used to decompose the global routing into inverters, multiplexers and wires. Section 3.2.2 describes this decomposition for the logic blocks, and Section 3.2.3 for the clock network. Transistor sizes for these components depend on the physical dimensions of different entities in the FPGA. Section 3.2.4 details the algorithm we use to approximate these dimensions.

#### **3.2.1 Global Routing**

A significant portion of the transistors in an FPGA are used to implement the flexible global routing network. This network consists of switch boxes and connection boxes, as described in Section 2.1. The switch boxes and connection boxes are comprised of buffers and multiplexers, the sizes and topologies of which depend on architectural parameters supplied by the user.

#### 3.2.1.1 Switch Boxes

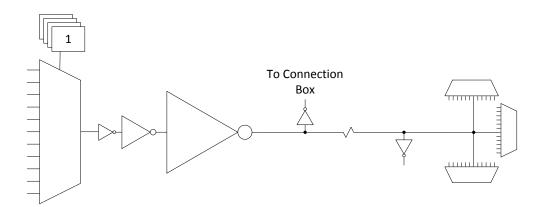

Switch boxes, which lie at the intersection of horizontal and vertical channels in an FPGA, are responsible for driving the global routing wires. There may be tens to hundreds of global wires incident to each switch box. Each global wire is driven by a multiplexer followed by a buffer [26]. The buffer drives a wire, which spans one or more grid tiles of the FPGA. At the end of the wire, is a fan-out to other switch boxes or connection boxes [60]. This is illustrated in Figure 3.2, and is referred to in this thesis as a switch box component, as many of these comprise a single switch box. The power usage of a switch box component is comprised of the power dissipation in the multiplexer (See Section 3.2.1.3), the buffer (See Section 3.2.1.4), and the wire.

The size of the multiplexer is determined by the number of fan-ins of the routing channel. These fan-ins can come from other global wires, or from outputs of logic blocks. The buffer size is a function of the capacitance it drives, which is composed of the wire capacitance and the input capacitance of the fan-out. The wire capacitance is a function of the wire length, which is determined using the methods in Section 3.2.4.

**Figure 3.2:** Switch box component, comprised of a multiplexer connected to a buffer, driving a wire. The wire fans out to connection boxes and other switch boxes.

#### **3.2.1.2** Connection Boxes

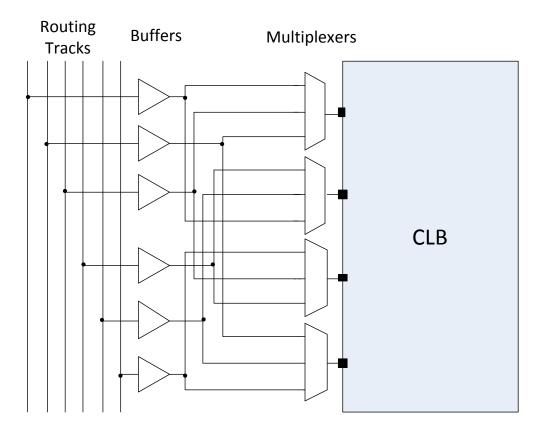

Connection boxes provide the interface between the routing channels and the logic blocks. They are comprised of buffers and multiplexers. There is one multiplexer for each input pin of the logic block. A buffer connects each routing track to the multiplexers, and is needed as the track may drive many pins.

Figure 3.3 provides an illustration of a simple connection box. In a real FPGA architecture, there would be many more routing tracks, and many more CLB input pins. This potentially causes large buffers and multiplexers.

The buffers are sized according to the capacitance they drive, which is determined by the number of multiplexers they connect to. Each routing track connects to a fraction of the CLB inputs, represented by  $Fc_{in}$  in the architecture description file. Likewise, the number of inputs to each multiplexer is equal to  $Fc_{in}$  multiplied by the number of routing tracks.

Figure 3.3: Sample of a connection box.

#### 3.2.1.3 Multiplexers

The multiplexers in the switch boxes and connection boxes are built using NMOS pass transistor logic, using minimum sized transistors [60]. By default, two levels are used for any multiplexer with four or more inputs; however, the user can override the number of levels or the transistor sizes by modifying the architecture description file. Figure 3.4 shows a 4:1 two-level multiplexer.

Multi-level multiplexers are decomposed into a collection of single-level multiplexers. Figure 3.5 provides an illustration of this decomposition. It is conceiv-

Figure 3.4: 4:1 2-level multiplexer.

Figure 3.5: 4:1 2-level multiplexer, decomposed into single-levels.

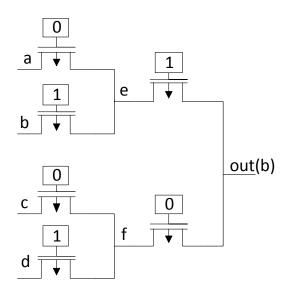

able that some architectures may contain very large multiplexers, which could have many internal nodes, each having a large capacitance due to the number of connected transistors. Consider the multiplexer in Figure 3.4. Input b is selected, and any toggles on node b will also toggle nodes e and *out*. This was the extent of modelling of past power models [13, 14]. However, toggles on input d will still cause internal node f to toggle, consuming power. In Figure 3.5, although only multiplexers A and C belong to the activated path, multiplexer B will still consume power. For this reason, the architecture generator will include all three multiplexers in the generated FPGA circuitry.

#### 3.2.1.4 Buffers

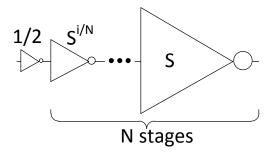

Buffers in the connection boxes and switch boxes are built using multiple stages of cascaded inverters, as illustrated in Figure 3.6. The first stage of the buffer is a sense stage with size  $(W/L)_P = 1$ , and  $(W/L)_N = 2$ . The sense stage is needed as the input to the buffer may receive a weak-1 due to pass transistor logic [60, 61]. The NMOS transistors in the remaining *N* stages of the buffer are sized according to Equation 3.1.

$$(^{W}/_{L})_{N} = S^{(i/N)}$$

(3.1)

*S* is the size of the final stage of the buffer, *N* is the total number of stages, excluding the sense stage, and *i* is the index of the stage being sized, such that  $i \in [1, N]$ . The PMOS transistors are sized larger, according to the P/N ratio (See Section 4.3.4).

Figure 3.6: Multi-stage buffer, used in connection boxes and switch boxes.

The size of the final buffer stage, *S*, is found using Equation 3.2, which is based on the logical effort model [58].

$$S_{buf} = \frac{1}{4} * \frac{C_{Load}}{C_{INV}} \tag{3.2}$$

In this equation,  $C_{Load}$  is the total load capacitance driven by the buffer, and  $C_{INV}$  is the input capacitance of a minimum sized inverter. The number of stages is chosen using  $N = \frac{logS}{log4}$ , where N is rounded to the nearest integer [58]. This creates a buffer where the size from one stage to the next grows by a factor close to 4. This factor is commonly chosen when designing high-performance circuits, as it minimizes the delay. For power efficient circuits a larger factor may be used, resulting in slower, but smaller buffers [58]. The user may specify an alternative value for this factor in the architecture description file.

#### 3.2.2 Complex Logic Blocks

VPR 6.0 supports user-defined logic blocks, which allow for a much larger range of architecture features than was possible in previous academic FPGA flows. This flexibility is obtained through a hierarchical description of the entities within each CLB. Each entity can:

- Instantiate multiple child entities, including children of different types.

- Define arbitrary interconnect between itself and children, or between multiple children.

- Operate in multiple modes. For example, a 6-LUT could operate as a single 6-LUT, or as two 5-LUTs.

Our model includes an algorithm which handles all of these features; any CLB that can be described using the new architcture language can be handled by our tool. Algorithm 1 provides pseudo code for the hierarchical power modelling algorithm. The algorithm employs a recursive function, which calculates the power usage for an entity. If the entity has children, the algorithm accounts for the power usage of the circuitry connecting the parent to children, as well as interconnect between children. The function is then called recursively for the child entities. If the entity does not have children it must be a primitive, such as a flip-flop, a LUT, or some other hard-block. For these types, the primitive handler function is called, which will determine the type of entity, and call the appropriate function. Each component of this algorithm will be further described below.

Algorithm 1 Calculate power dissipation of a CLB recursively:

calc\_entity\_power(entity):

```

1: if entity has children then

// This is a parent mode, determine mode of operation

2:

mode \leftarrow entity.mode

3:

// Add interconnect power

4:

5:

for each interc in mode do

power \leftarrow power + calc\_interc\_power(interc)

6:

end for

7:

for each child in mode do

8:

power \leftarrow power + calc\_entity\_power(child)

9:

end for

10:

11: else

12:

// This is a leaf node such as a LUT or Flip-Flop

// Call the primitive handler

13:

power \leftarrow power + calc_primitive_power(entity)

14:

15: end if

16: return power

```

#### 3.2.2.1 Intra-CLB Interconnect:

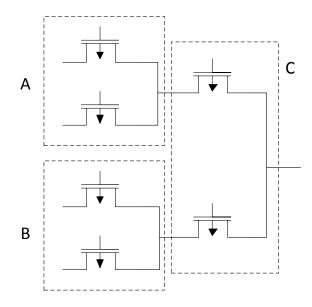

For each entity within a CLB, the architecture description file must specify the type of interconnect between itself and its children. This interconnect may be one of three types: *direct, many-to-one*, or *complete*. Figure 3.7 provides a diagram of a traditional logic block, and includes an example of each type of interconnect.

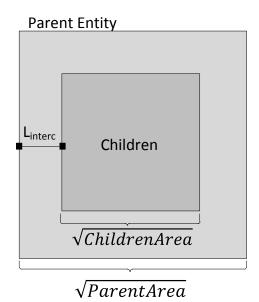

The architecture generator must decompose each interconnect into multiplexers with known transistor sizes, and wires with known length. The wire length depends on the physical spanning distance between parent and child entities, represented as  $L_{interc}$ . This distance is approximated using Equation 3.3. Figure 3.8 illustrates the derivation of this equation.

Figure 3.7: Types of local interconnect.

$$L_{interc} = 0.5 * \left(\sqrt{Area_{Parent}} - \sqrt{Area_{Children}}\right)$$

(3.3)

An *m*-input, *n*-output interconnect structure contains (m+n) input/output wires, where the length of each wire is approximated as  $1/2 \cdot L_{interc}$ . This approximation is illustrated in Figure 3.9.

This approach provides a very rough approximation, and assumes a square topology with even spacing between the parent and child entities. In reality, this is unlikely, and interconnect may span much more, or much less than this value. Unfortunately, it is difficult to provide a more accurate estimation without knowing the transistor layout of the device, which is too complex to estimate automatically, and too burdensome to require from the user. In addition, this model only considers the wirelength of interconnect structures between parent and child entities. The wirelength within a primitive, such as a LUT or flip-flop, is ignored.

The following describes modelling techniques specific to each interconnect type:

*Direct Interconnect* This is a pure wire connection and requires no multiplexers. The connection contains a single source input, which drives one or more sinks. In Figure 3.7, the clock wires provide an example of this type of connection.

*Many-to-One Interconnect* This type is implemented as a single multiplexer. An example of this pattern is a multiplexer that chooses whether the BLE output is

43 of 96

Figure 3.8: Local interconnect spanning distance,  $L_{interc}$ , between parent and child entities in a CLB.

driven by the LUT output or the flip-flop output, as shown in Figure 3.7. These potentially large multiplexers are decomposed into single-level multiplexers, in the same manner as the global routing multiplexers (see Section 3.2.1.3).

The architecture description file also supports the declaration of bus-based multiplexers, which can be used for coarse-grained architectures. An m-input many-to-one interconnect of n-wide buses is modelled as n instances of an m-input multiplexer.

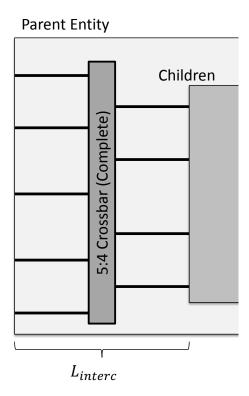

*Complete Interconnect* This type describes a fully populated *m*-input, *n*-output crossbar. These crossbars are modelled as *n* number of *m*-to-1 multiplexers. Each multiplexer is modelled as previously described. Figure 3.7 provides an example

**Figure 3.9:** Wire length in a local interconnect structure. Shown here is a 5-input, 4-output complete interconnect, which results in 9 wires of length  $1/2 \cdot L_{interc}$ .

of an 8-to-9 crossbar connecting the inputs and outputs of the CLB to the inputs of the BLEs.

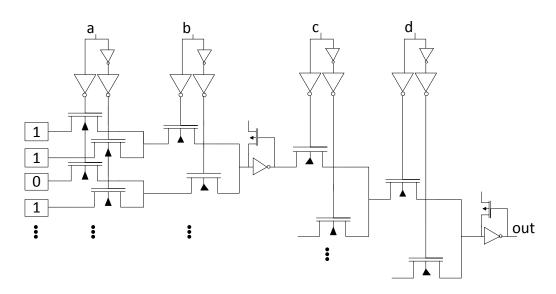

#### **3.2.2.2** Look-up Tables (LUTs)

LUTs are assumed to be implemented as a network of two-input multiplexers, with level restorers used between every other stage [60]. Figure 3.10 provides an illustration of a 4-input LUT. Calculating the power dissipation of this structure requires the switching activity of internal nodes of the multiplexer. The activity estimator, which will be described in Section 4.2, determines the activity of each

*net*, but not the activity within the LUTs themselves. These internal activities are calculated as follows. The initial level of multiplexers is fed by SRAM bits, making  $P_1$  (the long-term probability that a node is high) equal to the value of the SRAM cell.  $P_1$  values are cascaded through the LUT levels using Equation 3.4 for each 2-input multiplexer, where *s* is the select signal.

$$P_{1}(out) = (1 - P_{1}(s)) * P_{1}(in0) + P_{1}(s) * P_{1}(in1)$$

$$A_{S}(out) = (1 - P_{1}(s)) \cdot A_{S}(in0) + P_{1}(s) \cdot A_{S}(in1)$$

$$+ A_{S}(s) \cdot P(in0 \neq in1)$$

(3.5)

$A_S$  values (the expected switching activity of each node) are calculated at the output of each 2-input multiplexer using Equation 3.5, which is comprised of three terms. The first two terms represent the case when the selected input toggles, causing the output to toggle. The third term,  $A_S(s) \cdot P(in0 \neq in1)$ , represents toggles on the output due to the selector toggling, which occurs only when the two inputs are of different logic value. The probability of the two inputs being different is calculated using Algorithm 2.

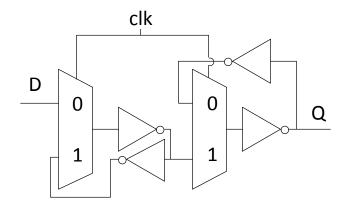

#### **3.2.2.3 D Flip-Flop**

A D Flip-Flop, contains a master and slave loop, each with two inverters and a two input multiplexer. Figure 3.11 provides an illustration. The inverters are assumed to be minimum sized, and the multiplexers are composed of two minimum size

Algorithm 2 Method of calculating the probability that the two inputs of a stage-*n* multiplexer in a LUT have different logic values.

$P_{total} = 0$ for all  $\{in_1, in_2, ..., in_{n-1}\} | in_i \in \{0, 1\}$  do // Check if SRAM values are diffent if  $SRAM(in_1, in_2, ..., 0) \neq SRAM(in_1, in_2, ...1)$  then  $P_{branch} = 1$  // Sum probability of each branch for  $i = 1 \rightarrow (n-1)$  do  $P_{branch} = P_{branch} \cdot P(input_i == in_i)$  end for  $P_{total} + = P_{branch}$  end if end for

Figure 3.10: 4-input LUT.

transmission gates [58]. Like LUTs, the internal node activity must be calculated. The behaviour of the master loop is assumed to be  $P_1 = P_1(D)$  and  $A_S = (1 - C_1)^2 + C_2 + C_2$

Figure 3.11: D Flip-Flop.

$A_S(clk)$  \*  $A_S(D)$ . The slave loop behaviour is assumed to be  $P_1 = P_1(Q)$  and  $A_S = A_S(Q)$ .

#### **3.2.2.4 Undefined Hard Blocks (Black Boxes)**

Our model does not estimate power of I/O pads, memories, multipliers, and other hard blocks designed by users. I/O pads have intentionally been excluded due to their complexity. If the user wishes to model memories, multipliers or other custom hard blocks, he/she must provide parameters for the block. This can be done in one of three ways:

- Provide the absolute dynamic and static power of the block in the architecture file. This is the simplest, but least accurate approach, as power estimates are independent of the behaviour of input pins.

- 2. Provide the equivalent internal capacitance of the block in the architecture file. The power model will average the switching activity  $(A_S)$  across all

input pins to calculate dynamic power. Static power must still be specified as an absolute in the architecture file.

3. Provide a coded function that can be called by the primitive handler. The primitive handler will provide the signal probability ( $P_1$ ) and switching activity ( $A_s$ ) of the input pins. The user provided function should use this information to make more detailed power estimations, such as is done for LUTs and flip-flops.

#### 3.2.2.5 Static Power of Unused Blocks

One step of Algorithm 1 is to determine the mode of operation for each entity in the CLB. For example, it is necessary to know whether the fracturable LUT is operating in fractured or non-fractured mode. However, if an entity is unused, it is not clear which mode it is operating in. This is needed to calculate static power of the unused entity. To handle this scenario, the power model allows the user to specify the default mode of operation in the architecture file. For example, the user can specify that when unused, LUTs should be modelled as the non-fractured type.

#### 3.2.2.6 Limitations

There are several limitations in the way that the architecture description file specifies modes of operation. The file is designed to describe the *functional* behaviour of entities, and not the *actual hardware*. For example, functionally a 6-LUT can operate as two 5-LUTs. However, the actual hardware of the 6-LUT is not identical to the hardware of two distinct 5-LUTs. Unfortunately, there is no visibility within VTR to distinguish between a normal 5-LUT and a 5-LUT that is actually half of a 6-LUT. Thus when LUTs are fractured they are treated as multiple ordinary LUTs. This results in the input buffers to the LUTs being counted twice. Our testing shows that this discrepancy should be limited to a 1-2% overestimate in the overall power usage.

#### **3.2.3** Clock Network

The clock network modelled is a four quadrant spine and rib design, as illustrated in Figure 3.12. The design is similar to the topology used in a Xilinx Virtex II Pro [62]. At this time VPR only supports a single clock; however, the power model contains infrastructure to model multiple clocks, provided that each clock is composed of the same topology as illustrated in the figure. Some FPGA multiclock networks are more complicated, with different clocks connecting to different regions of the chip [62], but we do not model these more complex networks.

The model assumes that the entire spine and rib clock network will contain buffers separated in distance by the length of a grid tile. As in Section 3.2.1.4, the buffer is multi-stage with the final stage sized according to Equation 3.2. In this case, the load capacitance is assumed to be the next clock buffer, plus the capacitance of the wire connecting to it.

#### **3.2.4** Physical Size Estimation

One benefit of this power model is that all of the components are automatically sized. This includes routing buffers, clock buffers, and buffers within a CLB. The size of these buffers depends on the capacitance of the wire that is driven by the buffer. For this reason, the power model must be aware of the physical size of grid tiles in the FPGA, as well as the size of entities within CLBs, such as LUTs, flip-flops and multiplexers. The power model employs a transistor counting algorithm to determine the physical size of the various parts of the FPGA. This algorithm works with the architecture description file, so any user defined architecture is supported.

Algorithm 3 provides the method used to calculate the FPGA grid tile size, as well as the sizes of all CLB entities. Similar to the power estimation algorithm, a recursive function traverses the CLB entity hierarchy, counting transistors at each level. For entities that support multiple modes, the mode that requires the largest transistor area is assumed. If the user introduces custom hard-blocks in the design, they must also provide a function that returns the number of transistors in the block.

In our estimations we assumed the area of an SRAM cell to be equivalent to the layout area of 6 minimum-sized transistors [58]. The architecture description file contains a parameter that allows the user to override this value.

#### Algorithm 3 FPGA physical size estimation.

```

calc_FPGA_tile_length:

transistor_cnt = cnt_entity_transistors(CLB)

transistor_cnt = transistor_cnt + 2 * cnt_connection_box_transistors()

transistor_cnt = transistor_cnt + cnt_switch_box_transistors()

return \sqrt{(transistor\_cnt * transistor\_unit\_area)}

cnt_entity_transistors(entity):

max\_transistor\_cnt \leftarrow 0

if entity has children then

// Find the mode that requires the most transistors

for each mode in entity.modes do

transistor_cnt \leftarrow 0

for each interc in mode do

transistor\_cnt \leftarrow transistor\_cnt + cnt\_interc\_transistors(interc)

end for

for each child in mode do

transistor\_cnt \leftarrow transistor\_cnt + cnt\_entity\_transistors(child)

end for

max_transistor_cnt = max of (max_transistor_cnt, transistor_cnt)

end for

else

// This is a leaf node such as a LUT or Flip-Flop

// Call the leaf handler

max\_transistor\_cnt \leftarrow max\_transistor\_cnt + cnt\_leaf\_transistors(entity)

end if

// Store area of this entity for later use

entity.area \leftarrow max\_transistor\_cnt * transistor\_unit\_area

return max_transistor_cnt

```

# 3.3 Summary

This chapter provided an overview of the components in our power model, and the roles they play in power estimation. The chapter also detailed the architecture generator, which is responsible for translating arbitrary FPGA architectures into basic circuit components. This includes generating circuit information for the global routing fabric, the CLBs, and the clock network. All transistors and wire lengths in these circuits are automatically sized.

The architecture generator is able to process any user described architecture, regardless of complexity, and produce a collection of inverters, single-level multiplexers and wires. Once the FPGA circuitry has been reduced to these simple components, the other parts of the model are capable of estimating the dynamic and static power of each component. This power estimation is outlined in the next chapter.

# **Chapter 4**

# **Power Estimation**

This chapter describes the remaining components of our model: The low-level power estimator, the activity estimator, and the transistor properties generator.

The architecture generator translates the entire FPGA circuitry into a collection of inverters, multiplexers and wires, after which the low-level power estimator provides power estimates of these components. These estimates, described in Section 4.1, depend on the signal behaviour and transistor properties. Signal behaviours are determined by the activity estimator, as described in Section 4.2. Transistor properties are generated by running SPICE simulations and extracting the necessary values, as described in Section 4.3.

## 4.1 Low-Level Power Estimation

The power dissipated in the inverters, multiplexers and wires is comprised of both dynamic and static power. Dynamic power includes both switching power and short-circuit power. Static power consists of subthreshold and gate leakage. Other sources of power are not significant and are ignored [58].

#### 4.1.1 Switching Power

Switching power is the result of charging and dissipating energy stored in the capacitance of transistor nodes and wires, and is proportional to the frequency with which the nodes toggle. The switching power dissipated by every wire, as well as the source, drain, and gate of every transistor is estimated using Equation 4.1 [63].

$$P_{dyn} = \alpha C V_{swing} V_{DD} f \tag{4.1}$$

The parameters of the above equation are:

- $\alpha$ : The expected switching activity of the node.  $\alpha = 1$  represents a node that toggles once, or switches twice, per clock cycle.

- *C*: The node or wire capacitance.

- $V_{DD}$ : The supply voltage.

- $V_{swing}$ : The swing voltage, which is the voltage range of the node or wire.

- *f*: The operating frequency of the circuit.

In our implementation, transistor node capacitances are provided by the transistor properties generator, which will be described in Section 4.3.1. Wire capacitances are calculated by multiplying the wire length provided by the architecture generator with the unit-length wire capacitances provided in the architecture description file. The activity factor,  $\alpha$ , is calculated as  $\alpha = A_S/2$ , where  $A_S$  is the transition density from the activity estimator, which will be described in Section 4.2. The operating frequency, f, is provided by VPR 6.0. Typically, the swing voltage,  $V_{swing}$ , is equal to the supply voltage. However, in pass-transistor logic, there may be voltage drop since NMOS transistors transmit a weak logic-1 [61]. This voltage drop is estimated using techniques described in Section 4.3.5.

#### 4.1.2 Short-Circuit Power