## A STUDY OF TWO WIDEBAND CMOS LC-VCO STRUCTURES

by

Ge Yu

B.A.Sc., The University of British Columbia, 2009

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF

# THE REQUIREMENTS FOR THE DEGREE OF

## MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

(Electrical and Computer Engineering)

## THE UNIVERSITY OF BRITISH COLUMBIA

(Vancouver)

October 2012

© Ge Yu, 2012

### Abstract

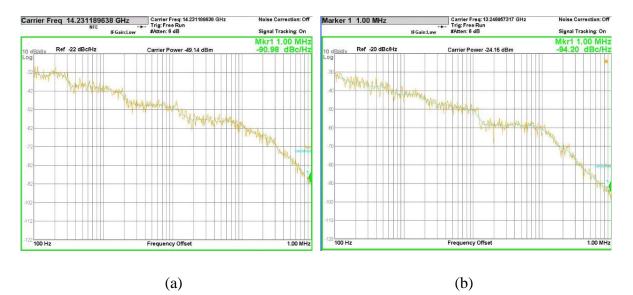

Phase-locked loops (PLLs) are widely used in telecommunication, radio, and computer applications. This thesis focuses on the study of wide-band PLLs, as they are a critical building block of many wireless and wireline systems. In particular, wide tuning range, low phase noise, and low power are desirable attributes for multi-standard and multiband communication systems. One of the most critical components in a PLL is the voltagecontrolled oscillator (VCO). In this work, two techniques for implementing a wide-tuningrange LC-VCO are presented. As a proof of concept, the techniques are used to design and layout two 13-GHz LC-VCOs, which are fabricated in a 90-nm CMOS technology and successfully tested. One design (Design A) uses two VCO cores and has an extra sourcefollower buffer while the other (Design B) uses one VCO core with a bank of switched capacitors. The 90-nm CMOS prototypes operate from a supply of 1.2 V. The Design A prototype has a 28.20% tuning range and a phase noise of -90.98 dBc/Hz at 1 MHz offset from the carrier, while the Design B prototype has a 24.42% tuning range and a phase noise of -94.20 dBc/Hz at 1 MHz offset. This measured performance is comparable with state-ofthe-art wide-tuning-range VCOs. The total chip size, excluding pads, is  $0.335 \times 0.750 \text{ mm}^2$ and  $0.316 \times 0.425 \text{ mm}^2$  for Designs A and B, respectively. It was found that the addition of the source-follower buffer allows the VCO to function at a higher frequency, while the presence of the switched capacitor tends to deteriorate phase noise.

# **Table of Contents**

| Abstract                      |                              | ii  |

|-------------------------------|------------------------------|-----|

| Table of Conte                | nts                          | iii |

| List of Tables                |                              | vi  |

| List of Figures               |                              | vii |

| Acknowledgen                  | nents                        | ix  |

| Chapter 1: Intr               | roduction                    | 1   |

| 1.1 Mo                        | tivation                     | 1   |

| 1.2 Obj                       | ectives                      | 2   |

| 1.3 Out                       | line                         | 2   |

| Chapter 2: Pha                | ase-Locked Loops             | 3   |

| 2.1 Intr                      | oduction to PLLs             | 3   |

| 2.1.1                         | Blocks of a PLL              | 3   |

| 2.1.2                         | Types of VCOs                | 4   |

| 2.2 LC-                       | -VCOs                        | 5   |

| 2.2.1                         | Literature Review            | 5   |

| 2.2.2                         | Wide-tuning-range LC-VCOs    |     |

| 2.2.3                         | Phase Noise of LC-VCOs       |     |

| Chapter 3: 13-                | GHz LC-VCO Design            | 14  |

| 3.1 Des                       | sign A                       | 14  |

| 3.1.1                         | LC-VCO Core                  | 14  |

| 3.1.2                         | Source Follower Buffer       |     |

| 3.1.3                         | CML Stage                    |     |

| 3.1.4                         | Biasing Circuitry            |     |

| 3.1.5                         | Entire VCO                   |     |

| 3.2 Des                       | sign B                       |     |

| 3.2.1                         | LC-VCO Blocks                |     |

| 3.2.2                         | Entire VCO                   |     |

| Chapter 4: Simulation Results |                              |     |

| 4.1 13 -                      | - GHz VCO Simulation Results |     |

| 4.1       | 1 Transient Res   | sponse and Amplitude                          |

|-----------|-------------------|-----------------------------------------------|

| 4.1       | 2 Tuning Range    | e 36                                          |

| 4.1       | 3 Phase Noise .   |                                               |

| 4.2       | 13 – GHz VCO P    | ost-Layout Simulation Results                 |

| 4.2       | 1 Transient Res   | sponse and Amplitude                          |

| 4.2       | 2 Tuning Range    | e 39                                          |

| 4.2       | 3 Phase Noise .   |                                               |

| Chapter 5 | Experimental Me   | thod and Measurement Results of 13-GHz VCO 42 |

| 5.1       | Circuit Layout Ch | aracteristics                                 |

| 5.2       | Experimental Setu | ıp                                            |

| 5.2       | 1 Required Equ    | ipment                                        |

| 5.2       | 2 VCO Charact     | erization                                     |

| 5.3       | Chip Experimenta  | l Results                                     |

| 5.3       | 1 Measured An     | nplitude, Power Consumption, and Tuning Range |

| 5.3       | 2 Measured Ph     | ase Noise                                     |

| 5.3       | 3 Comparison of   | of VCO Measurements to Published Works 51     |

| Chapter 6 | Other Blocks of F | PLL and Closed Loop PLL                       |

| 6.1       | Phase Frequency   | Detector                                      |

| 6.1       | 1 Theory          |                                               |

| 6.1       | 2 Design          |                                               |

| 6.2       | Charge Pump       |                                               |

| 6.2       | 1 Theory          |                                               |

| 6.2       | 2 Design          |                                               |

| 6.3       | Loop Filter       |                                               |

| 6.3       | 1 Theory          |                                               |

| 6.3       | 2 Design          |                                               |

| 6.4       | 13 – GHz Closed-  | loop PLL Simulation Results                   |

| Chapter 7 | Conclusions       |                                               |

| 7.1       | Achievements      |                                               |

| 7.2       | Problems and Lin  | nitations 69                                  |

| 7.3       | Future Work       |                                               |

| Bibliography                                                  | . 71 |

|---------------------------------------------------------------|------|

| Appendix                                                      | . 77 |

| Appendix A: Second Order PLL Transfer Function and Derivation | .77  |

# List of Tables

| Table 4.1 Transient response of Design A and Design B                    | . 36 |

|--------------------------------------------------------------------------|------|

| Table 4.2 Tuning range of Design A and Design B                          | . 37 |

| Table 4.3 Phase noise at 1 MHz offset for Design A and Design B          | . 37 |

| Table 4.4 Transient response of Design A and Design B                    | . 39 |

| Table 4.5 Overall tuning range for Design A and Design B                 | . 39 |

| Table 4.6 Phase noise for Design A and Design B at 1-MHz offset          | . 41 |

| Table 5.1 Design A fabricated chip pin functions                         | . 43 |

| Table 5.2 Design B fabricated chip pin functions                         | . 44 |

| Table 5.3 Test Equipment                                                 | . 44 |

| Table 5.4 Measured current and power consumption                         | . 49 |

| Table 5.5 Measured tuning range                                          | . 49 |

| Table 5.6 Performance summary and comparison with published works        | . 51 |

| Table 6.1 Loop filter component values for bandwidths of 1MHz and 0.5MHz | . 64 |

| Table 6.2 Natural frequency and damping factor of the PLL                | . 65 |

| Table 7.1 Performance of LC-VCOs                                         | . 68 |

# List of Figures

| Figure 2.1 Components of a basic Phase-locked Loop                                     | 3  |

|----------------------------------------------------------------------------------------|----|

| Figure 2.2 LC-VCO structures with a tail current source: (a) NMOS-only (b)             |    |

| complementary [6]                                                                      | 6  |

| Figure 2.3 NMOS cross-coupled transistors in the configuration to implement a negative |    |

| resistance [9]                                                                         | 7  |

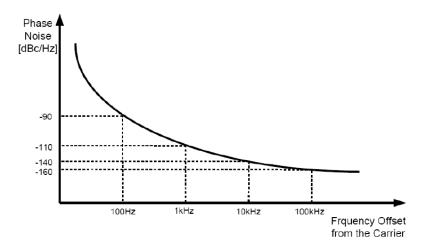

| Figure 2.4 The frequency representation of phase noise in an oscillator [1]            | 10 |

| Figure 2.5 Single sideband phase noise representation [24]                             | 11 |

| Figure 2.6 The spectrum of the phase noise [25]                                        | 12 |

| Figure 3.1 Schematic of LC-VCO core implemented                                        | 15 |

| Figure 3.2 Calculated values of the resistors and varactors                            | 17 |

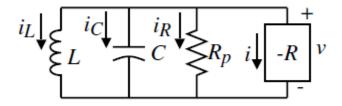

| Figure 3.3 Basic RLC oscillator and negative resistance circuit [9]                    | 18 |

| Figure 3.4 LC-VCO schematic with design parameters for a) VCO 1, b) VCO 2              | 19 |

| Figure 3.5 Varactor Capacitance vs. Vtune for VCO 1                                    | 21 |

| Figure 3.6 Varactor Capacitance vs. V <sub>tune</sub> for VCO 2                        | 21 |

| Figure 3.7 Source follower buffer with design parameters                               | 23 |

| Figure 3.8 Comparison of current vs. frequency for CMOS and CML [36]                   | 24 |

| Figure 3.9 Common-mode logic stage with design parameters                              | 26 |

| Figure 3.10 Biasing circuitry with design parameters                                   | 27 |

| Figure 3.11 Block diagram of Design A architecture                                     | 28 |

| Figure 3.12 Schematic of one path of Design A                                          | 29 |

| Figure 3.13 LC-VCO with switched-capacitor schematic with design parameters            | 31 |

| Figure 3.14 Schematic of Design B                                                      | 33 |

| Figure 3.15 Multiple switched-capacitors in parallel                                   | 34 |

| Figure 4.1 Transient response of VCO 1                                                 | 36 |

| Figure 4.2 Phase noise for VCO 1 of Design A                                           | 37 |

| Figure 4.3 Transient response of VCO 1                                                 | 38 |

| Figure 4.4 Phase noise performance of a) Design A, b) Design B                         | 40 |

| Figure 5.1 Design A layout with pad names                                              | 42 |

| Figure 5.2 Design B layout with pad names                                              | 43 |

| Figure 5.3 Testbench schematic for characterization of Design A                        |         |

|----------------------------------------------------------------------------------------|---------|

| Figure 5.4 Testbench schematic for characterization of Design B                        | 45      |

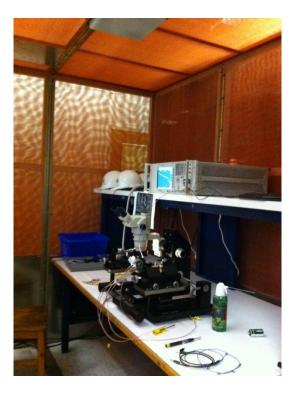

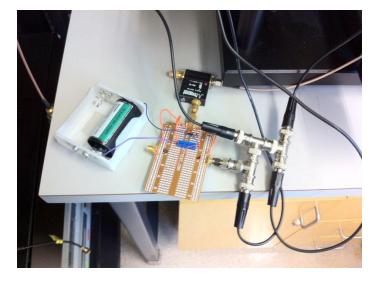

| Figure 5.5 Test setup with DC power supplies                                           | 46      |

| Figure 5.6 Test setup with a) battery, b) battery and shielded room, c) battery and bi | as-T 47 |

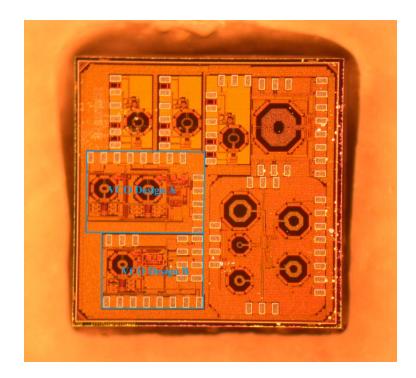

| Figure 5.7 Chip micrograph                                                             |         |

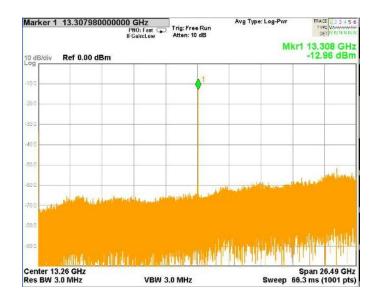

| Figure 5.8 Sample measured oscillation spectrum                                        | 49      |

| Figure 5.9 Measured phase noise of Design (a) A, (b) B                                 | 50      |

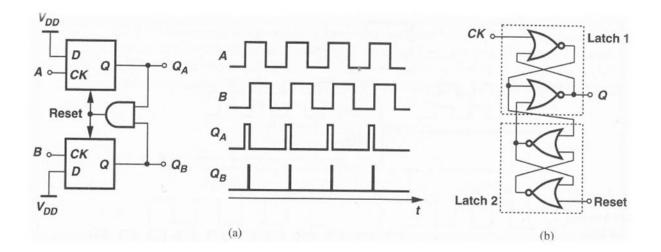

| Figure 6.1 (a) Implementation of PFD, (b) Implementation of D flipflop [48]            | 54      |

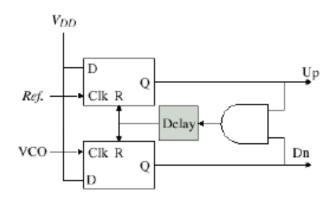

| Figure 6.2 Implementation of PFD without a dead zone                                   | 55      |

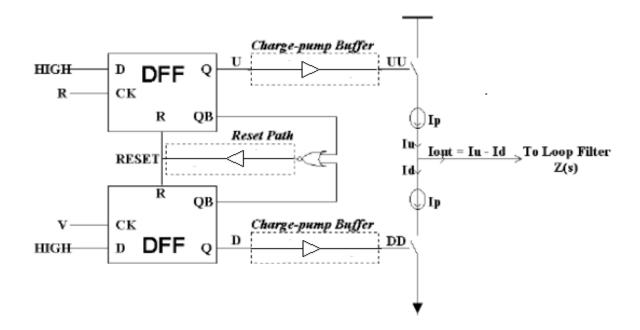

| Figure 6.3 Design of the PFD without deadzone and charge pump [50]                     | 56      |

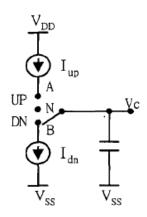

| Figure 6.4 A simple model of the charge pump circuit [52]                              | 57      |

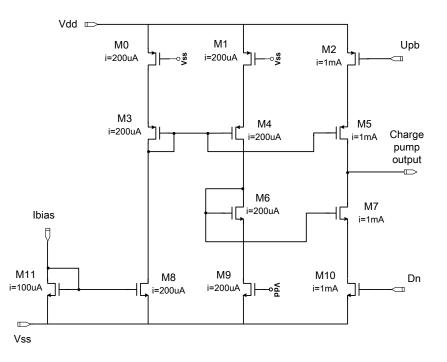

| Figure 6.5 Schematic of the implemented charge pump                                    | 58      |

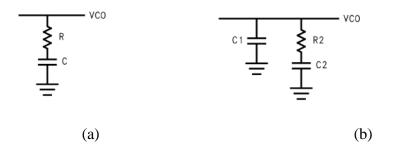

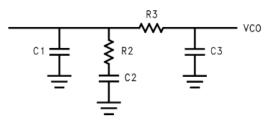

| Figure 6.6 (a) First-order loop filter, (b) Second-order loop filter [58]              | 60      |

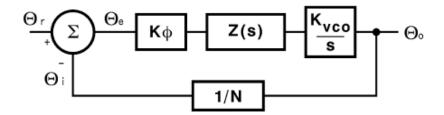

| Figure 6.7 PLL linear model [58]                                                       | 60      |

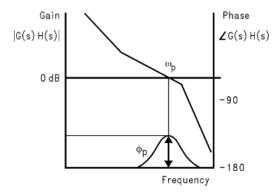

| Figure 6.8 Open Loop Response Bode Plot [58]                                           | 61      |

| Figure 6.9 Third-order loop filter [58]                                                | 62      |

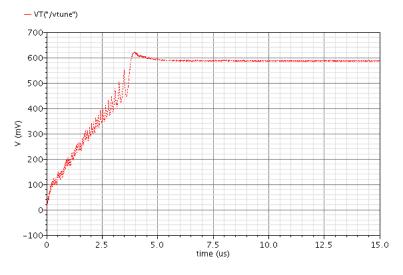

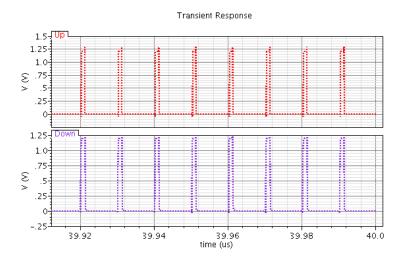

| Figure 6.10 Transient response of closed loop PLL for bandwidth 1 MHz                  | 66      |

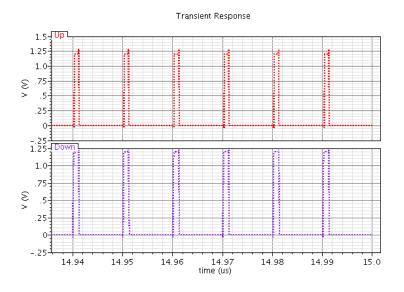

| Figure 6.11 Charge pump response for bandwidth 1 MHz                                   | 66      |

| Figure 6.12 Transient response of closed loop PLL for bandwidth 0.5 MHz                | 67      |

| Figure 6.13 Charge pump response for bandwidth 0.5 MHz                                 | 67      |

| Figure A.1 Block diagram of second order PLL                                           | 77      |

# Acknowledgements

I would like to thank Dr. Andre Ivanov and Dr. Shahriar Mirabbasi, my supervisors, for their guidance and support and for giving me this opportunity. Thank you both for your great character and patience. I would not be able to complete this work without your invaluable advice throughout this process.

I would also like to thank Dr. Roberto Rosales for the many hours he spent in the lab with me, helping with my measurement setup, as well as his encouragement and support. I wish to thank Roozbeh Mehrabadi for his extensive help with CAD tools.

Special thanks go to my friends here at the SoC lab, especially to Hooman Rashtian and Mohammad Beikahmadi. Thank you for your help, keeping me focused, and most importantly for your kindness and encouragement.

Last but not least I wish to thank my parents, who have always been there for me and whose support never faltered. I would not be able to go this far without you.

This work was partially funded by the Natural Sciences and Engineering Research Council of Canada (NSERC). The CAD tool support is provided by CMC Microsystems.

## **Chapter 1: Introduction**

This chapter provides the motivation for the design of a wide-tuning-range 13-GHz LC-VCO. Two methods of implementing wide-tuning-range VCOs are explored and comparison of the two designs is made. The two VCO designs are laid out, and measurements were taken upon receiving the fabricated chip. A simple PFD, charge pump, and loop filter are also designed to simulate a closed-loop PLL using a Verilog-A divider. This chapter defines the objectives of this work and briefly outlines the organization of this thesis.

#### **1.1 Motivation**

A phase-locked loop (PLL) is a circuit that causes one system to track another; specifically, it is a circuit that synchronizes an output signal and an input signal in frequency as well as in phase. If a phase error builds up, a control mechanism directs the output signal to minimize the phase error with the input signal. The phase of the output signal is actually locked to the phase of the input signal hence a phase-locked loop. This feature of PLLs proves useful in many applications such as radio, computers, telecommunications and other electronic applications [1]. In this work, the implementation of wide-tuning-range PLLs is studied.

The design of PLLs for communication applications has been greatly impacted by the growing demand for multi-standard and multi-band communication systems. The need for higher data rates and lower power consumption are also crucial. This has been achieved in both wireless and wireline applications through implementing a wider bandwidth PLL with techniques to lower noise, power, and fabrication costs. The design of wider-tuning-range PLLs is also important for lowering costs as a larger tuning range is not limited to one but caters to many applications. Another importance of the study of wide-tuning range PLLs is that it is a practical method in dealing with environmental and process variations.

Being a critical building block of the PLL, the VCO performs essential functions in the transmission of and reception of data. For this work, two designs for implementing wide-tuning-range LC-VCOs are presented. These high-frequency VCO designs belong to the state-of-the-art and are worthwhile to examine. Also, it is often ideal to design higher frequency VCOs and then lower its frequency through the use of a divider in the closed-loop PLL, as higher frequency LC-VCOs are implemented with smaller inductors which occupy smaller area. As a proof of concept, two different 13-GHz VCOs were designed. The VCOs were laid out and fabricated in a 90-nm CMOS technology, and their performance was evaluated by measurements.

#### 1.2 Objectives

The objectives of this work are as follows:

- Investigate the design of a wide-tuning-range LC-VCO with low phase noise and power dissipation.

- Design two wide-tuning-range LC-VCOs with center frequency of approximately 13 GHz using two different approaches and compare their performance.

- Layout, fabricate, and test the designed circuit blocks of the 13-GHz VCOs.

A closed-loop PLL with a simple charge pump, PFD, and loop filter along with a Verilog-A divider were also designed and simulated.

#### 1.3 Outline

The remainder of this thesis is organized as follows. The next chapter provides a review of PLLs based on LC-VCOs. Chapter 3 discusses the theory and design techniques for the particular 13-GHz LC-VCOs implemented. Chapter 4 presents and discusses the simulation results of the LC-VCOs. Chapter 5 details the measurement approach of the fabricated VCO and compares these measurements with simulation results as well as to other's work. Chapter 6 presents the design of a simple charge pump, PFD, and loop filter, and with a Verilog-A divider simulates a closed-loop PLL. Finally, Chapter 7 concludes the thesis and discusses future work.

### **Chapter 2: Phase-Locked Loops**

This chapter introduces PLLs and the circuit blocks they comprise of. It discusses the basic operation of the PLL. Ring Oscillators and LC-VCOs are discussed and reason is given for implementing the LC-VCO for this work. Other's work on the LC-VCO is considered as a brief literature review on it is provided. This chapter also examines wideband LC-VCOs in particular. Finally, this chapter provides a discussion of the phase noise of LC-VCOs, which is an extremely important characteristic of any VCO and thus a significant factor when designing PLLs.

#### 2.1 Introduction to PLLs

A PLL is a closed-loop feedback system whose output tracks or synchronizes to the input signal in frequency and in phase [2]. In the synchronized, or locked, state the phase error between the oscillator's output signal and the reference signal is zero or extremely small [2]. This property of PLLs has resulted in their wide popularity in many applications. The main reason for this popularity is probably the versatility of PLLs [3]. The first PLL was introduced in 1932 and today, decades later, there are still many people researching this circuit [3].

#### 2.1.1 Blocks of a PLL

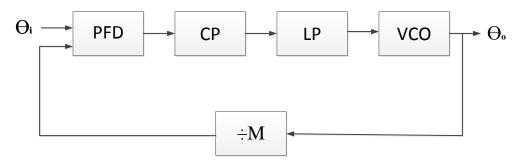

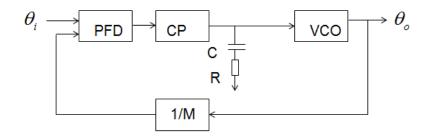

A PLL consists of four basic components: a phase frequency detector (PFD), a charge pump (CP), a loop filter (LP), a voltage-controlled oscillator (VCO), and optionally a frequency divider (÷M), as shown in Figure 2.1 below.

Figure 2.1 Components of a basic Phase-locked Loop

The PFD detects the difference in phase and frequency between the reference clock and feedback clock inputs and generates an "Up" or "Dn" control signal based on whether the feedback frequency is lagging or leading the reference frequency. These "Up" or "Dn" control signals determine whether the VCO needs to operate at a higher or lower frequency, respectively. The PFD outputs these "Up" and "Dn" signals to the charge pump. If the charge pump receives an "Up" signal, current is driven into the loop filter. Conversely, if it receives a "Dn" signal, current is drawn from the loop filter. The loop filter then converts these signals to a control voltage that is used to control the VCO. Based on the control voltage, the VCO oscillates at a higher or lower frequency, which affects the phase and frequency of the feedback clock. If the PFD produces an "Up" signal, then the VCO frequency increases; a "Dn" signal decreases the VCO frequency. The VCO stabilizes once the reference clock and the feedback clock have the same phase and frequency. When the reference clock and the feedback clock are aligned, the PLL is considered locked. The main function of the loop filter is to filter out the phase noise by removing glitches from the charge pump. Finally, a divider may be inserted in the feedback loop to increase the VCO frequency above the input reference frequency [2]. The VCO is the heart of the PLL; thus, the next section is devoted to introducing the options of the types of VCOs one may choose to implement for a PLL. The design of the implemented VCO will be discussed in depth in Chapter 3.

#### 2.1.2 Types of VCOs

The oscillator in a PLL is the most significant block and operates at the highest frequency. The most important specifications of the oscillator are the phase noise, the tuning range, the power consumption, and the cost [1]. Oscillators are generally classified as two types: relaxation oscillators and harmonic oscillators. Relaxation oscillators produce a non-sinusoidal output waveform, such as square or triangular waves, whereas harmonic oscillators have a sinusoidal output waveform. Examples of the relaxation oscillator include the multivibrator and the rotary travelling wave oscillator, but the most common one is the ring oscillator. Examples of the harmonic oscillator include the Hartley oscillator and the

Colpitts oscillator, but the LC-oscillator or the LC-VCO (LC voltage-controlled oscillator) is by far the most popular [4].

The ring oscillator is a commonly used oscillator for integrated PLLs and clock recovery circuits because it is less complex and easy to integrate. It is implemented by cascading a series of odd number of inverters. The ring oscillator provides a wider tuning range compared to a monolithic implementation of an LC-VCO [5]. However, a major drawback of the ring oscillator is that its phase noise is inferior, which impedes its use in high-quality communication systems. This is the reason the LC-VCO is chosen for our application; LC-VCOs exhibit a much better phase noise compared to ring oscillators. The output frequency of the LC-oscillator is determined by the resonance of an inductor and a capacitor. Because both of these elements constitute a passive filter, the phase noise is low [1]. The phase noise of LC-oscillators is typically 20 dB better than that of the ring oscillator [1].

### 2.2 LC-VCOs

LC-VCOs are superior to other oscillators in the sense that they have good phase noise performance, which is a critical criteria when designing oscillators, and relative ease of design [6]. Due to advantages such as these they are commonly used and have been studied extensively.

#### 2.2.1 Literature Review

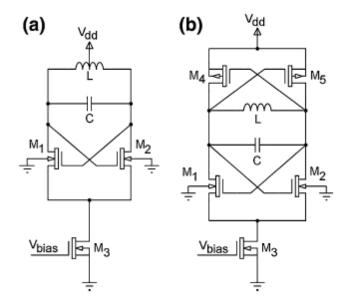

LC-VCOs exist in a wide variety of structures, including those with a tail current source, without a tail current source, NMOS-only, PMOS-only, and complementary (both NMOS and PMOS) [7]. Figure 2.2 shows two common structures. Figure 2.2(a) shows a NMOS-only architecture with a tail current source, where  $V_{bias}$  is the bias current control for providing a constant tail current in the LC resonator. Figure 2.2(b) shows a complementary architecture with a tail current source.

Figure 2.2 LC-VCO structures with a tail current source: (a) NMOS-only (b) complementary [6]

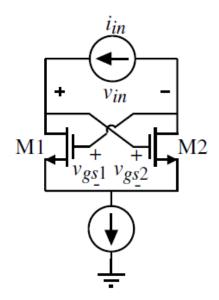

In Figure 2.2(a), an NMOS cross-coupled differential pair (transistors  $M_1$  and  $M_2$ ) is used to sustain a negative impedance of  $(-2/g_m)$  for constant oscillation. It is important to choose the  $g_m$  value carefully [8]. Figure 2.3 shows just the NMOS cross-coupled transistors. In Figure 2.3,  $g_{m1}$  and  $g_{m2}$  are the transconductances of the transistors  $M_1$  and  $M_2$ respectively, and the following relationship holds true [9]:

$$i_{in} = g_{m1} v_{gs1} = -g_{m2} v_{gs2} \tag{2.1}$$

$$\therefore R_{in} = \frac{v_{in}}{i_{in}} = \frac{v_{gs2} - v_{gs1}}{i_{in}} = \frac{-1}{g_{m2}} - \frac{1}{g_{m1}} = \frac{-2}{g_m}$$

(2.2)

Therefore, to start and keep the oscillation, a negative resistance -R whose magnitude is  $2/g_m$  must be present [10]. This will be further discussed in Chapter 3.

The tail current of both the NMOS-only and complementary LC-VCOs in Figure 2.2 flows to the LC-tank and the LC resonator limits the voltage swing across the resonator; this deteriorates the VCO's phase noise. In some cases such as in [11], it has been reported that it may be advantageous to eliminate the tail current source to achieve better phase noise performance. However, the current source has the benefit of supplying a constant current to the cross-coupled differential pair of the LC-tank, making it less sensitive to voltage supply

variations [3]. In general, the tail current aids the designer in achieving a compromise between phase noise performance and power dissipation.

Figure 2.3 NMOS cross-coupled transistors in the configuration to implement a negative resistance [9]

The complementary LC-VCO shown in Figure 2.2(b) is composed of PMOS ( $M_4$  and  $M_5$ ) and NMOS ( $M_1$  and  $M_2$ ) transistors stacked in parallel. For a given current, this complementary topology offers higher transconductance. This topology is also symmetrical, which results in faster switching of the cross-coupled pair. Another advantage of using the complementary topology is that it has better phase noise performance [12]. Finally, this structure limits all gate voltages to the supply voltage; this allows for reliable operation within process limits over an extended period of time, such as many years [13]. The main disadvantage to using this configuration is the difficulty in implementing it when the supply voltage is low due to the stacking of transistors. To solve this problem, the tail current source is sometimes removed, such as in [14], thus leaving more voltage headroom for the active devices to operate in the saturation region.

A PMOS-only topology is not shown here but is also used. However, the amplitude for PMOS is smaller and therefore the phase noise worse [1]. Also, since the mobility of holes ( $\mu_p$ ) is lower than that of electrons, PMOS devices have to be twice the size of NMOS devices to achieve a similar performance [15]. Both PMOS- and NMOS-only topologies can provide an output voltage swing greater than the voltage supply with the help of a high tailcurrent feed-through. However, the disadvantage to using them is that they also both have worse reliability and power efficiency [16].

#### 2.2.2 Wide-tuning-range LC-VCOs

This thesis focuses on the design of a wide-tuning-range VCO; therefore, it is important to give an overview of the techniques that are commonly used to acquire this wide tuning range. First of all, there are a few design factors that affect the tuning range of all LC-VCOs regardless of what specific technique is employed for wide tuning range; this includes the size of the transistors and the parasitic capacitance of the capacitor and the inductor in the LC-tank. The parasitic parameters of the LC-tank limit the upper frequency band by restricting the upper tuning range [7].

The general problem with LC-VCO design is the tradeoff between the tuning range, phase noise, and power consumption. A typical wide-tuning-range LC-VCO employs the use of a switched capacitor network for coarse tuning and a varactor for fine tuning, such as in [17,18]. As reported in [19], the capacitor network can be made of varactors that can be switched on and off. Another approach for wide-tuning range is to use multiple VCOs with overlapping tuning ranges to cover the entire bandwidth, as in [20]. Alternatively, a wide-tuning-range VCO can be implemented by using switched inductors as in [21]. In general, a mixture of the above techniques is adopted to obtain the desired wide tuning range, which is suitable for the particular technology and design requirements.

#### 2.2.3 Phase Noise of LC-VCOs

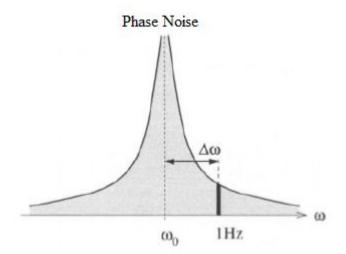

Phase noise is a measure of the spectral purity of a signal [1] and is noise that causes variations in the phase of the signal as opposed to fluctuations in the amplitude of a signal [22]. It is an important characteristic of any VCO and thus an important performance metric of PLLs. Phase noise is characterized in the frequency domain and is a key indicator of an oscillator's frequency stability. Phase noise can also be defined as follows:

$$PN = \frac{P_o}{N_o} \tag{2.3}$$

where  $P_o$  is the power in the tone at the frequency of oscillation and  $N_o$  is the noise power spectral density at some specified offset from the carrier [22]. The main component of oscillator phase noise results from the direct upconversion of white noise and flicker noise (also known as 1/f noise).

Flicker noise is also one of the two main fundamental noise mechanisms for CMOS. The other noise mechanism is thermal noise which is due to the thermal excitation of charge carriers in a conductor. My phase noise simulations indicated the dominance of flicker noise, although thermal noise did occur at times. Flicker noise is a significant noise source in MOS transistors. Flicker noise  $V_g^2(f)$  is defined as follows [23]:

$$V_g^2(f) = \frac{\kappa}{_{WLC_{ox}f}}$$

(2.4)

where the constant K is dependent on device characteristics and can vary widely for different devices in the same process. The variables W, L, and  $C_{ox}$  represent the transistor's width, length, and gate capacitance per unit area, respectively. f is the offset frequency from the center frequency. It is important to note that flicker noise is inversely proportional to the transistor area WL; thus, larger devices have less flicker noise [23].

CMOS transistors generate more flicker noise in comparison to bipolar transistors, which in oscillators is upconverted to  $1/f^3$  shaped phase noise close to the carrier. Thus, the  $1/f^3$  shaped phase noise is higher in CMOS oscillators and can become an issue. Flicker noise upconversion determines the phase noise at small offset frequencies, where it is suppressed when the oscillator is used in a PLL [1]. It is important to note that flicker noise has large low frequency content [23].

The output of an ideal oscillator is a perfect sinusoidal wave of frequency  $\omega_0$ , which can be expressed as:

$$V_{out}(t) = A \cdot sin(\omega_o t + \theta)$$

(2.5)

where A is the amplitude and  $\theta$  is a fixed phase reference. In the frequency domain this corresponds to a Dirac impulse at  $\omega_0$ ,  $\delta(\omega_0)$ . However, with a real oscillator, noise generates fluctuation on the phase and amplitude of the signal, so the output becomes:

$$V_{out}(t) = (1 + a(t)) \cdot sin(\omega_o t + \theta(t))$$

(2.6)

Because of the fluctuations on the phase  $\theta(t)$  and amplitude a(t), the output spectrum is no longer a Dirac impulse, but has sidebands close to the frequency of oscillation, as shown in Figure 2.4. Well-designed, high-quality oscillators are normally very amplitude stable, so a(t) can be considered constant over time. In order to quantify phase noise, the noise power in a unit bandwidth at a certain offset frequency  $\Delta \omega$  from  $\omega_0$  is considered and divided by the

Figure 2.4 The frequency representation of phase noise in an oscillator [1]

carrier power at  $\omega_0$ . The result is a single sided spectral noise density with units of decibels below the carrier per hertz (dBc/Hz) and is defined as [1]:

$$\{\Delta\omega\} = 10\log\left(\frac{\text{noise power in a 1 Hz band at }\omega_o + \Delta\omega}{\text{carrier power}}\right)$$

(2.7)

Figure 2.5 shows the representation of single sideband phase noise.

Figure 2.5 Single sideband phase noise representation [24]

Various models have been developed to describe the behavior of phase noise in oscillators. One of the most important models is Leeson's model for oscillator single sideband phase noise, introduced by David B. Leeson in 1966. Leeson proposed the following model [25]:

$$\{\Delta\omega\} = \mathbf{10} \log\left[\frac{2FkT}{P_s} \cdot \left[\mathbf{1} + \left(\frac{\omega_o}{2Q_L \Delta\omega}\right)^2\right] \cdot \left(\mathbf{1} + \frac{\omega_{1/f^3}}{|\Delta\omega|}\right) \right]$$

(2.8)

where  $\int$  is the single sideband phase noise density

F is an empirical parameter (often called the "device excess noise number")

$P_s$  is the average power dissipated in the resistive part of the tank

*k* is Boltzmann's constant,  $1.38 \times 10^{-23}$  [J/K]

*T* is the absolute temperature [K]

$\omega_o$  is the oscillation frequency

$Q_L$  is loaded-Q (the effective quality factor of the tank with all loadings accounted for)

$\Delta \omega$  is the frequency offset from the carrier

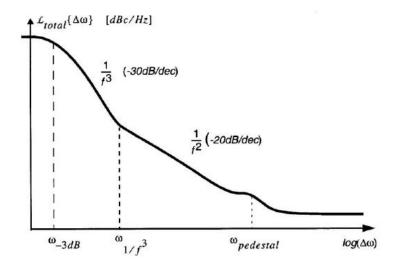

$\omega_{L/f^3}$  is the frequency of the corner between the  $1/f^3$  and  $1/f^2$  regions as shown in Figure 2.6.

Leeson's model suggests that increasing  $Q_L$ , the quality factor of the tank, and signal power reduce phase noise. Additionally, Leeson's model introduces the factor F; it is important to realize that the factor F is an empirical fitting parameter and therefore must be determined

from measurements. This weakens the ability of Leeson's equation to predict the true phase noise. Without knowing exactly what the factor F depends on, it is difficult to identify specific methods of reducing it. Blind application of this model based on pure observation of the equation has resulted in foolish attempts of some designers to use active circuits in order to boost  $Q_L$ . Unfortunately, increasing  $Q_L$  through this method results in increasing Fas well since active devices contribute their own noise; thus, the anticipated phase noise improvements are unsuccessful [26].

Plotting phase noise  $\{\{\Delta\omega\}\}\$  for an oscillator (in dBc/Hz) as a function of  $\Delta\omega$  on logarithmic scales, regions with different slopes may be observed as shown in Figure 2.6. It is important to note that the curve is approximated by a number of regions, each having a slope of  $1/f^{x}$ . At large offset frequencies there is a flat noise floor, and at small offsets there are regions with slopes of  $1/f^{3}$  and  $1/f^{2}$ . At very small offset frequencies the spectrum becomes flat again [25].

Figure 2.6 The spectrum of the phase noise [25]

Phase noise generated by a VCO is determined by factors such as:

- Q factor of the resonator

- Q factor of the varactor

- Flicker noise

- The active device used for the oscillating transistor

• Power supply noise

The noise contribution made by power supply noise and tuning voltage supply noise can be minimized by choosing carefully the power supplies. Therefore, the phase noise of the VCO is mainly determined by the overall quality factor Q of the circuit [27].

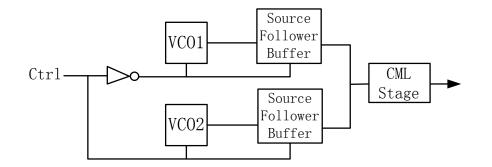

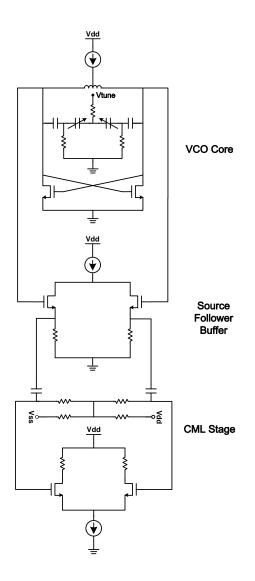

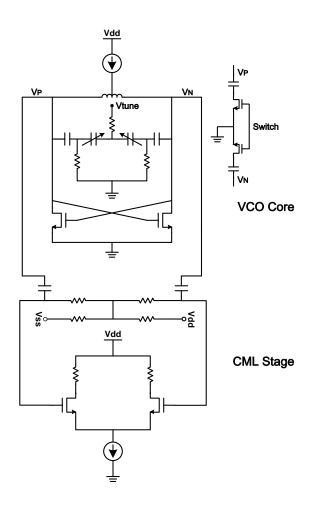

### Chapter 3: 13-GHz LC-VCO Design

This chapter discusses the two designs of the 13-GHz LC-VCO. The first one, Design A, is implemented using two VCO cores and the overlapping tuning ranges of the two cores together give overall tuning range. In Design A, a source follower buffer as well as a common-mode logic (CML) buffer are used. The second one, Design B, is implemented using one VCO core and a switched-capacitor. The switched-capacitor can be turned on and off. Design B uses only a CML buffer at the output. Both designs include an on-chip biasing circuitry.

#### 3.1 Design A

This section describes how Design A is implemented. First, steps used to design the LC-VCO cores are discussed. Next, the design of the source follower buffer, common-mode logic stage, as well as the biasing circuitry are examined. Finally, we have a look at the entire VCO with all of these blocks together.

#### 3.1.1 LC-VCO Core

The goal is to achieve an overall tuning range of approximately 30-40 % (calculated as  $((f_{max}/f_{min} - 1) * 100 \%)$ ). In this design, two VCOs are implemented with an overlapping tuning range. The target center frequency is 13 GHz; however it must initially be designed with a higher center frequency to account for frequency drop after post-layout simulation due to parasitic capacitance. The first VCO was designed to cover the frequency range 15.5 GHz to 20 GHz with a center frequency of 17.75 GHz. The second VCO was designed to cover the frequency range of approximately 12 GHz to 16.5 GHz with a center frequency of 14.25 GHz. Thus, the overall tuning range covered by the two VCOs is 12 GHz to 20 GHz and the center frequency is 16 GHz. The LC-VCO core is designed in the following 4 steps:

#### Step 1

First of all, it is important to note that the power supply for 90-nm technology is 1.2 V. The design of the VCO starts with the design of the -Gm LC-tank, by finding a geometry

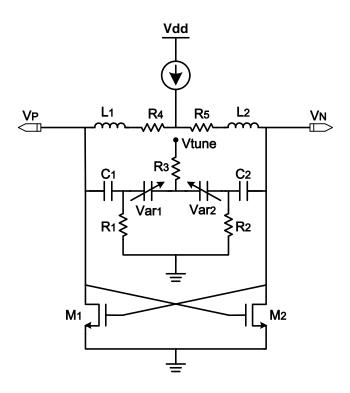

that provides a high inductance with the lowest parasitic resistance, while maintaining a sufficient tuning range. The first step is to determine whether complementary (NMOS and PMOS) or xMOS-only (NMOS or PMOS) VCO should be implemented. A complementary VCO, which is commonly used because of its low phase noise characteristics, was not chosen for this design as the power supply is quite low [28]. An NMOS-only LC-tank was implemented, as the speed of NMOS is higher than PMOS. A PMOS current source which has better phase noise performance with reduced flicker noise was used [1]. Figure 3.1 shows the schematic of the LC-VCO core implemented.

Figure 3.1 Schematic of LC-VCO core implemented

Referring to Figure 3.1, inductors  $L_1$  and  $L_2$  are ideal inductors; the resistors in series with the inductors  $R_4$  and  $R_5$  are the resistances of the inductors. This model of the real inductor is a very simplified model and does not take into consideration the parasitic capacitance and resistance of the inductor but is sufficient for our purposes. To avoid positive bias of varactors Var<sub>1</sub> and Var<sub>2</sub>, capacitors  $C_1$  and  $C_2$ , and resistors  $R_1$  and  $R_2$ directly bias the varactors to ground avoiding the complex bias circuits [29]. Resistors  $R_1$ ,  $R_2$  and  $R_3$  shown in Figure 3.1 are for biasing purpose; they are not parasitic resistors. Adjusting the capacitor and varactor ratio is key to changing or maximizing the tuning range as desired.

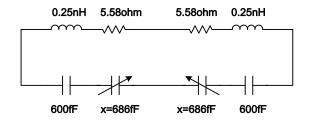

#### Step 2

After determining the geometry of the VCO, the next step is to do initial hand calculations to find the values for the resistors and the varactors of VCO 1 with center frequency 17.75 GHz:

Assuming L = 0.5 nH,

The resonant frequency can be expressed as [30]:

$$f = \frac{1}{2\pi\sqrt{LC}}$$

$$\omega = \frac{1}{\sqrt{LC}}$$

$$C = \frac{1}{\omega^2 L} \approx 160 fF$$

$$160 fF * 4 = 640 fF each$$

(3.1)

Refer to Figure 3.2. Let x be the value of the varactor. Assume the value of the capacitor is 600fF (Note: this value will be adjusted during simulation and debugging).

$$\frac{1}{x} + \frac{1}{x} + \frac{1}{600fF} + \frac{1}{600fF} = \frac{1}{160fF}$$

$$x \approx 686fF$$

(3.2)

Assuming the inductor's Q factor is 10, which is the worst case scenario, the series resistance Rs (which is equivalent to  $R_4$  and  $R_5$  in Figure 3.1) is [9]:

$$R_S = \frac{\omega L}{Q} = 1.775\pi \approx 5.58\Omega \tag{3.3}$$

Figure 3.2 Calculated values of the resistors and varactors

Step 3

The next step is to determine the value of  $\mu_n C_{ox}$  or  $K_n$ . This can be estimated by two different methods. The first method is to use the value of  $t_{ox}$  to first calculate  $C_{ox}$ .  $t_{ox}$  for NMOS is found to be 2.83 \* 10<sup>-9</sup> m from the TSMC 90-nmlp model file. Thus from [23],

$$K_n = \mu_n C_{ox} = \mu_n * \frac{K_{ox} \varepsilon_0}{t_{ox}}$$

(3.4)

The second method is to perform DC analysis of a transistor and plot its  $I_{DS}$  vs.  $V_{GS}$  curve. By extending the linear portion of this curve to the x-axis, the point where it crosses the x-axis is the approximation of  $V_{TH}$ . Using this value of  $V_{TH}$  and the coordinates of any point on the  $I_{DS}$  vs.  $V_{GS}$  curve the value of  $K_n$  can be approximated by the squared current-voltage relationship for a MOS transistor in the active region:

$$I_D = \frac{1}{2} K_n \left(\frac{W}{L}\right) (V_{GS} - V_{TH})^2$$

(3.5)

The second method should give a closer approximation and is one of the more popular techniques to estimate  $K_n$ . The first method particularly will not result in a correct  $K_n$  value especially for advanced technology like TSMC 90-nm, because square-law equations are not valid for short-channel transistors. Both of these methods to approximate  $K_n$  only provide a general guideline for reference only.

#### Step 4

Using the  $K_n$  value obtained in the previous step, the (W/L) ratio for  $M_1$  and  $M_2$  can be calculated as follows:

According to [9], converting the series impedance of 2L and  $2R_s$  into a parallel impedance gives,

$$Y = \frac{1}{2R_s + j\omega^2 L} = \frac{0.5}{R_s + j\omega L} * \frac{R_s - j\omega L}{R_s - j\omega L} = \frac{0.5R_s}{R_s^2 + \omega^2 L^2} - j\frac{0.5\omega L}{R_s^2 + \omega^2 L^2}$$

(3.6)

The reciprocal of the conductance is the parallel resistance  $R_{p}$ , given as

$$R_p = \frac{R_s^2 + \omega^2 L^2}{0.5R_s} \tag{3.7}$$

In order to provide sustained oscillation, a feedback loop is introduced which acts to generate a negative resistance –R, which is shown conceptually in Figure 3.3.

Figure 3.3 Basic RLC oscillator and negative resistance circuit [9]

$$R = -R_p \tag{3.8}$$

From [9], we know that

$$R = -\frac{2}{g_m} \tag{3.9}$$

$$\therefore g_m = -\frac{2}{R} \tag{3.10}$$

Also from [9],

$$V = \frac{2}{\pi} I_{bias} R_p \tag{3.11}$$

We select V to be 1.3V (Note that the output of the NMOS-only topology VCO could be larger than the supply voltage of 1.2V to get better performance [9]). Therefore, the current through each transistor is half of  $I_{bias}$ .

Finally, using the following equation from [23], the (W/L) ratio for  $M_1$  and  $M_2$  can be approximated:

$$g_m = \sqrt{2K_n I_D \frac{W}{L}} \tag{3.12}$$

$$\left(\frac{W}{L}\right) = \frac{g_m^2}{2K_n I_D} \tag{3.13}$$

The above four steps were repeated for designing VCO 2 with center frequency 14.25 GHz. For both of these VCO cores these steps are implemented initially to give an estimate of magnitude of components to use; based on these values simulations are performed and sufficient adjustments are made as required.

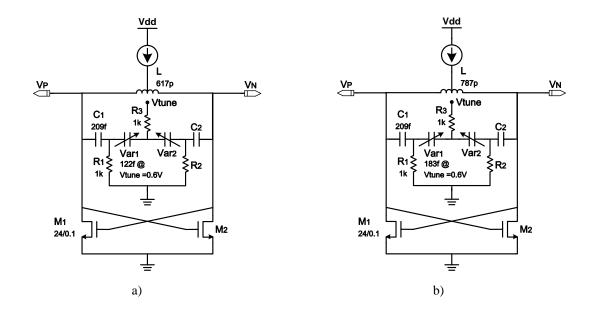

Figure 3.4 shows the specific LC-tank implemented with design parameters for VCO 1 and VCO 2. As can be seen the design parameter values are different from what was calculated. This is due to the fact that using the calculated parameters, simulation results showed quite a large drop in frequency than what was designed for due to the significant effect of parasitic capacitance at such high frequency. Sufficient adjustments were thus made, resulting in the implemented designs shown in Figure 3.4.

Figure 3.4 LC-VCO schematic with design parameters for a) VCO 1, b) VCO 2

For example, in Figure 3.4 a), using the values of the components indicated in the implemented schematic to calculate the center frequency of VCO 1, the equivalent capacitance is first calculated as:

$$\frac{1}{\frac{1}{209fF} + \frac{1}{209fF} + \frac{1}{122fF} + \frac{1}{122fF}} = 38.52fF$$

(3.14)

Thus, the center frequency of VCO 1 is calculated to be:

$$f = \frac{1}{2\pi\sqrt{LC}} = \frac{1}{2\pi\sqrt{(617pH)(38.52fF)}} = 32.65GHz$$

(3.15)

This is quite a bit higher than the desired center frequency of 17.75 GHz for VCO 1. Therefore, one can assume that the cross-coupled NMOS capacitors of the LC-tank has significant parasitic capacitance which lowers the center frequency of the VCO.

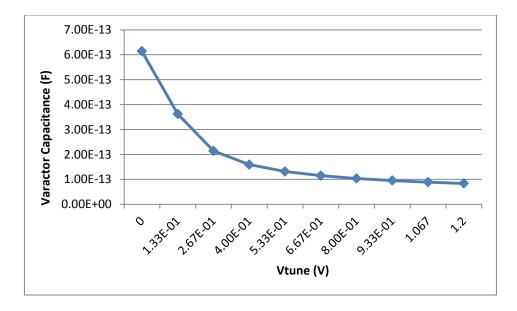

In general, the capacitance of the varactors is made small compared to the capacitance of the capacitors so the varactors have a larger effect on the total capacitance, which consists of two capacitors and two varactors in series, allowing for a larger frequency range. The varactor cannot be too small as it will result in abnormal behavior of the varactor. As the capacitor to varactor ratio increases, the tuning range of the VCO increases. However, the capacitor to varactor ratio cannot be too large, as simulation indicates that as the ratio increases to a certain degree abnormalities occur. Sufficient adjustments are made to obtain the desired tuning range covered after many simulations. Figure 3.5 shows the Varactor Capacitance vs.  $V_{tune}$  for VCO tank 1. At  $V_{tune} = 0.6$  V, the capacitance of the varactor is 122 fF.

Figure 3.5 Varactor Capacitance vs. Vtune for VCO 1

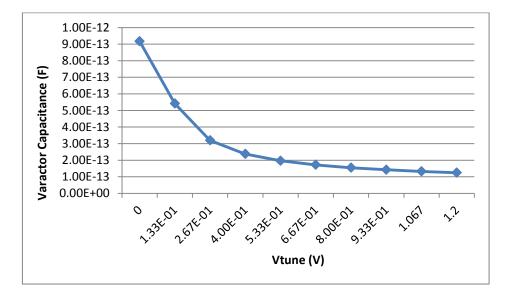

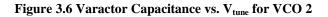

Figure 3.6 shows the varactor capacitance vs.  $V_{tune}$  for VCO tank 2. At  $V_{tune} = 0.6$  V, the capacitance of the varactor is 183 fF.

The Q factor of the inductor is found through simulation by the following formula [22]:

$$Q = \frac{|Im(Z_{ind})|}{|Re(Z_{ind})|} \tag{3.16}$$

where  $Z_{ind}$  is the impedance of the inductor. For both VCO 1 and VCO 2, the Q factor of their inductor is approximately 12, which is a typical value. In general, the value of the inductor is chosen to be as large as possible for better performance [1]; however, it cannot be too large as a smaller value would result in a larger tuning range since by

$$\omega = \frac{1}{\sqrt{LC}} \tag{3.17}$$

for a fixed  $\omega$  a smaller L allows for a larger C and thus larger variation in C.

The aspect ratio of the cross-coupled NMOS transistor of the VCO cores varied quite a bit from the calculated value which provided a guideline. This was to be expected since the large effect of the parasitic capacitances present must be considered, especially when the frequency is high. The specific aspect ratio value implemented resulted from satisfaction of the  $V_{DS} > (V_{GS} - V_{TH})$  criteria of the transistor during simulation [31].

#### 3.1.2 Source Follower Buffer

The output of the VCO core is connected to the input of the source follower buffer. The source follower buffer has high input impedance, as is shown in [32], and moderate to low output impedance [33]. Its high input impedance means the output load of the VCO core is small so that the VCO can function at a higher frequency. Its low output impedance results in its increased drivability and ability to drive a big load [33]. Also, a source follower is required to connect to the output of the VCO core to isolate the VCO from outside blocks; this can result in the VCO's frequency to be more stable. However, the drawback of the follower buffer is the voltage headroom limitation [33]. Since for the source follower the source is the output node, the transistor becomes dependent on the body effect. The body effect results in the threshold voltage  $V_{TH}$  to increase as the output voltage increases [34]. It is important to note that the voltage gain of the source follower is smaller than one.

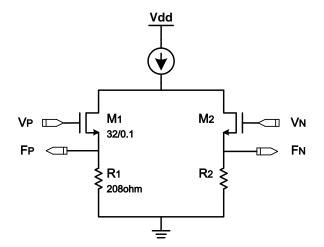

Figure 3.7 shows the follower buffer implemented for both VCO 1 and VCO 2 with design parameters. The aspect ratio of  $M_1$  and  $M_2$  was designed to guarantee that the VCO would work well, at the desired frequency. The resistors  $R_1$  and  $R_2$  were designed to be as

large as possible but under the condition that transistors  $M_1$  and  $M_2$  were working well, satisfying  $V_{DS} > V_{DSAT}$ .

Figure 3.7 Source follower buffer with design parameters

#### 3.1.3 CML Stage

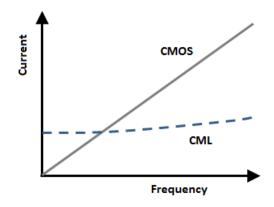

The common-mode logic (CML) stage is connected to the output of the source follower to improve the drivability of the overall VCO. Another reason the CML stage is ideal for this design is because it is a high-speed logic circuit. This fast operation of CML circuits is mainly due to their lower output voltage swing compared to the static CMOS circuits [35]. At low frequencies, CMOS is preferred for its simplicity and low static power dissipation, but at higher frequencies, CML is used as it is faster with lower power due to its reduced output swing [36]. This is clearly illustrated in Figure 3.8 showing Current vs. Frequency for CMOS and CML.

Figure 3.8 Comparison of current vs. frequency for CMOS and CML [36]

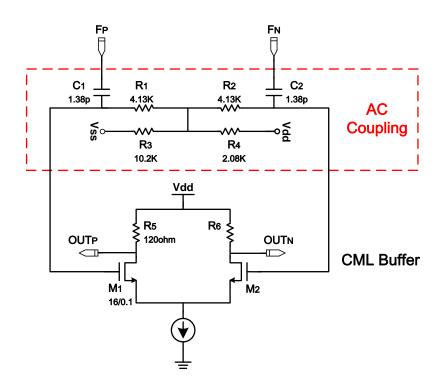

The CML stage also functions as a level shifter here depending on the requirements of the next stage's input level, which is required because the output voltage level of the source follower is comparatively low. However, the drawback to using a CML buffer is that it requires a constant static current source; thus, it suffers from dissipating more static power than a CMOS inverter [35]. In general, more current and small R results in higher frequency. This is a trade-off between power and load RC [36].

The implemented design of the CML stage is shown in Figure 3.9. Resistors  $R_5$  and  $R_6$  are pull-up resistors. The logic function is implemented by the logic block connected between the resistors and the current source, which is the differential pair constructed by transistors  $M_1$  and  $M_2$ . The operation of the CML buffer is based on the differential pair circuit. Each differential input variable is connected to a differential pair circuit. The value of the input variable controls the flow of current through the two branches [37]. The pull-up resistors were chosen depending on the working frequency and output swing. If the working frequency is increased, the resistance should decrease because they are inversely related. However, the current should increase to ensure sufficient output swing. Conversely, if the working frequency is decreased, the resistance should increase, and the current should decrease to keep the output swing constant. The W and L of transistors  $M_1$  and  $M_2$  were chosen to be as small as possible to reduce the input capacitance and therefore reduce the source follower load, since the input capacitance  $C_{GS}$  is proportional to W and L [23] as shown as follows:

$$C_{GS} = \frac{2}{3} W L C_{ox} + W L_{0\nu} C_{ox}$$

(3.18)

However W and L of  $M_1$  and  $M_2$  cannot be too small as the gain of the CML buffer must be taken into consideration as well, since gain of the CML stage is

$$A_{\nu} = -g_m R_{5,6} \tag{3.19}$$

and  $g_m$  is proportional to the value of W [23] as shown as follows:

$$g_m = \mu_n C_{ox} \left(\frac{W}{L}\right) V_{eff} \tag{3.20}$$

A crucial part of the design of the CML stage is the AC coupling at its input. This AC coupling block consists of two capacitors and four resistors. As can be seen in Figure 3.9 the values of resistors  $R_3$  and  $R_4$  of the AC coupling are different. These two resistors are for biasing purpose and their values are adjusted accordingly to ensure that  $M_1$  and  $M_2$  are working well to satisfy  $V_{DS} > V_{DSAT}$ . The values of  $R_3$  and  $R_4$  determine the common-mode level. Resistors  $R_1$  and  $R_2$  must be equal to ensure that the signal is even and has the same amplitude above and below common-mode level. Resistors  $R_1$  and  $R_2$  are designed according to the values of capacitors  $C_1$  and  $C_2$ .  $C_1$  and  $C_2$  are designed so their impedance over the frequency range of interest is substantially smaller compared to  $R_1$  and  $R_2$ ; thus, AC voltage drop across the capacitors is insignificant compared to the voltage drop across the resistors. The AC coupling isolates the DC of the source follower buffer from that of the subsequent blocks.

Figure 3.9 Common-mode logic stage with design parameters

#### 3.1.4 Biasing Circuitry

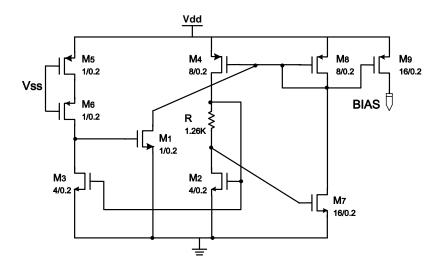

Figure 3.10 shows the schematic with parameters of the constant- $g_m$  with start-up biasing circuit used in the design. The constant- $g_m$  current source consists of transistors M<sub>4</sub>, M<sub>2</sub>, M<sub>7</sub>, and M<sub>8</sub> as well as the resistor R. The startup circuit consists of transistors M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>, M<sub>5</sub> and M<sub>6</sub>. If all currents in the bias loop are zero, M<sub>2</sub> and M<sub>3</sub> will be off. M<sub>5</sub> and M<sub>6</sub> pull the gate of M<sub>1</sub> high. M<sub>1</sub> will then inject currents into the bias loop, starting up the circuit. Once the loop starts up, M<sub>3</sub> will come on, sinking the current from the cascode M<sub>5</sub> and M<sub>6</sub> and pulling the gate of M<sub>1</sub> low, thus turning it off [23].

Figure 3.10 Biasing circuitry with design parameters

Figure 3.10 shows that for transistors  $M_2$  and  $M_7$ ,

$$V_{GS2} = V_{GS7} + I_{D2}R \tag{3.21}$$

Since  $V_{effi} = V_{GSi} + V_{TH}$ ,

$$\therefore V_{eff2} = V_{eff7} + I_{D2}R \tag{3.22}$$

$$\therefore \sqrt{\frac{2I_{D2}}{\mu_n C_{ox} \left(\frac{W}{L}\right)_2}} = \sqrt{\frac{2I_{D7}}{\mu_n C_{ox} \left(\frac{W}{L}\right)_7}} + I_{D2}R$$

(3.23)

And since  $I_{D2} = I_{D7}$ ,

$$\sqrt{\frac{2I_{D2}}{\mu_n C_{ox} \left(\frac{W}{L}\right)_2}} = \sqrt{\frac{2I_{D2}}{\mu_n C_{ox} \left(\frac{W}{L}\right)_7}} + I_{D2}R$$

(3.24)

$$\frac{2}{\sqrt{2\mu_n C_{ox} \left(\frac{W}{L}\right)_2 I_{D2}}} \left[ 1 - \sqrt{\frac{\left(\frac{W}{L}\right)_2}{\left(\frac{W}{L}\right)_7}} \right] = R$$

(3.25)

Recalling that  $g_{m2} = \sqrt{2\mu_n C_{ox} \left(\frac{W}{L}\right)_2 I_{D2}}$

$$\therefore g_{m2} = \frac{2\left[1 - \sqrt{\frac{\binom{W}{L}_{2}}{\binom{W}{L}_{7}}}\right]}{R}$$

(3.26)

Therefore, for the special case  $\left(\frac{W}{L}\right)_7 = 4\left(\frac{W}{L}\right)_2$ , we have  $g_{m2} = \frac{1}{R}$ .

This is the reason for the name "constant- $g_m$  biasing circuitry." By defining a value for  $g_{m2}$ , we can find the suitable value for resistor R [23].

## 3.1.5 Entire VCO

The overall architecture for this design is depicted in Figure 3.11. The design consists of two VCO cores with overlapping tuning ranges, where only one of the VCO cores (and its source follower buffer) is enabled at a time. Although only two VCOs are used here, in general, one can use more than two VCOs to achieve a wider tuning range. The output of the buffer feeds into a CML stage.

Figure 3.11 Block diagram of Design A architecture

The circuit schematic of one path of this design including the follower buffer and the CML stage is shown in Figure 3.12.

Figure 3.12 Schematic of one path of Design A

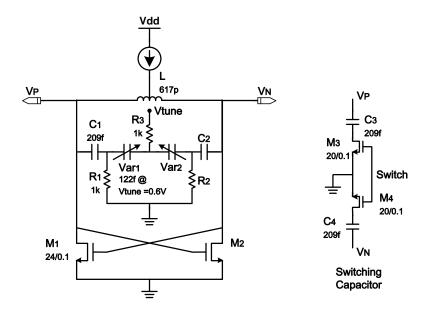

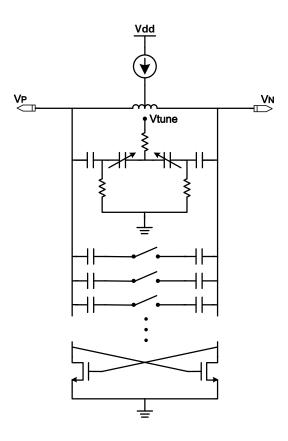

# 3.2 Design B

This section discusses how Design B is implemented. First, the design of the VCO core with the switched capacitor is described. Finally, we have a look at the entire VCO with all circuit blocks together.

## 3.2.1 LC-VCO Blocks

The initial goal was to achieve an overall tuning range of approximately 30-40 % (calculated as  $(f_{max}/f_{min} - 1) * 100 \%$ ), like for VCO Design A. In this design, one VCO core is implemented with a switched-capacitor. This VCO was designed so that turning the switched-capacitor on and off would result in overlapping tuning range. Initial simulations indicated that the target tuning range was not possible for this design with only one switched-capacitor for a fair comparison, so the goal was altered to maximize tuning range. The target center frequency, like that for Design A, is 13 GHz. The VCO with the switchedcapacitor turned off will be designed to cover the frequency range of approximately 14 GHz to 18.5 GHz with a center frequency of 16.25 GHz. The VCO with the switched capacitor turned on will be designed to cover the frequency range of approximately 12.5 GHz to 15.5 GHz with a center frequency of 14 GHz. Thus, the overall tuning range covered is from 12.5 GHz to 18.5 GHz with center frequency 15.5 GHz, which is lower than Design A. Note that the overall tuning range is skewed to allow for frequency drop after post-layout simulation due to parasitic capacitance. The LC-VCO core without the switched-capacitor is identical to VCO 1 in Design A. The tuning range covered when the switched-capacitor is turned off for this design, Design B, is different from the tuning range covered for VCO 1 of Design A partially because the presence of the switched-capacitor introduces extra parasitic capacitance, even when turned off, which lowers the frequency.

The addition of the switched-capacitor provides extra coarse tuning that can be added to the normal fine tuning (ie: the varactors) of the VCO to increase the frequency range. However, the digital logic system that controls the switching of the switched-capacitor must be carefully integrated in the design in order to guarantee stability over the complete tuning range [31]. Also, adding a switched-capacitor to the VCO's LC-tank would in general deteriorate the overall quality factor of the LC-tank and increase the total fixed capacitance of the VCO, which reduces  $K_{VCO}$  [31]. The switches must be implemented as MOS transistors, which have series resistance when on, as well as parasitic capacitance to the substrate from their drain and source regions. Therefore, it is expected that the circuit design and layout will have a detrimental influence on the resulting quality factor [31]. Figure 3.13 shows the LC-tank with the switched-capacitor implemented with design parameters.

Figure 3.13 LC-VCO with switched-capacitor schematic with design parameters

The switched-capacitor was designed by repeated simulations, meeting the target tuning ranges while ensuring that the  $V_{DSAT} < V_{DS}$  for transistors  $M_3$  and  $M_4$ . This task was not easy as both switched-capacitor turned off and on had to be considered and sufficient overlapping of tuning range must be guaranteed. The W/L of transistors M3 and M4 should be a relatively large number to minimize their resistance, as resistance is proportional to the inverse of W/L from [23]:

$$R_{total} = R_{\Box} \frac{L}{W} \tag{3.27}$$

where  $R_{\Box}$  is the resistance per square. However, if the transistor size is big, its parasitic capacitor is big as well when the switched-capacitor is off, so considering the trade-off we must debug carefully.

One switched-capacitor is used here to have two modes, for a fair comparison with the two-core Design A. However, it is important to note that in general, an array of switched-capacitors can be used to achieve a larger tuning range. For symmetry, the switched-capacitor block is implemented using two capacitors and two transistors. The capacitors also act to isolate the switch transistor's DC level from that of the VCO output. The balanced symmetrical design of the switched-capacitor has a common-mode node and allows for better linearity and phase noise performance compared to a switched-capacitor with no common-mode node [31].

The differential outputs of the VCO core  $V_P$  and  $V_N$  are connected to a CML buffer stage, which is identical to the one described in Design A. Only a CML buffer is implemented with no follower buffer for comparison purposes. Current is supplied to the VCO core and CML stage by a constant- $g_m$  start-up biasing circuitry identical to the one described in Design A.

## 3.2.2 Entire VCO

The overall architecture for this design is depicted in Figure 3.14. The design consists of one VCO core with a switched-capacitor which can be switched on or off, creating overlapping tuning ranges. The output of the VCO core feeds into a CML stage.

Figure 3.14 Schematic of Design B

It is possible and common to use more switched-capacitors and place them in parallel to the existing switched-capacitor as illustrated in Figure 3.15. Doing so would result in even larger overall tuning range, at the expense of increased phase noise and parasitic capacitance because the Q would be decreased.

Figure 3.15 Multiple switched-capacitors in parallel

# **Chapter 4: Simulation Results**

This chapter discusses the transient response and amplitude, the tuning range, and finally the phase noise simulation results of the two 13-GHz LC-VCO designs. First, a brief overview of the simulation results without extraction is presented for comparison purposes. Then the post-layout simulation results are discussed.

# 4.1 13 – GHz VCO Simulation Results

This section presents and briefly discusses the simulated (without extraction) transient response and amplitude, tuning range, and phase noise of the two LC-VCO designs. The purpose of the inclusion of this section is so sufficient comparison can be made to the post-layout simulation results.

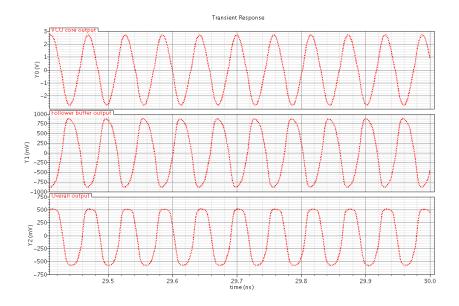

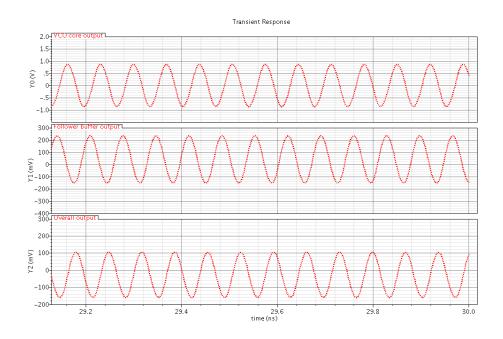

## 4.1.1 Transient Response and Amplitude

For design A, the transient response for the outputs of the VCO core, follower buffer stage, and overall output when VCO 1 is enabled is shown in Figure 4.1. When the oscillation stabilizes the frequency is measured to be approximately 17.24 GHz, which is the center frequency. The differential peak-to-peak amplitude for the VCO core output, source follower buffer stage output, and overall output from the CML stage are 5.42 V, 1.75 V, and 1.09 V respectively.

Figure 4.1 Transient response of VCO 1

The transient response for VCO 2 of design A as well as for design B looks similar. Their stabilized frequency and their differential peak-to-peak amplitudes at various stages are summarized in Table 4.1.

|                                                           | Desig     | n A       |                                    | Desig                | gn B                |

|-----------------------------------------------------------|-----------|-----------|------------------------------------|----------------------|---------------------|

|                                                           | VCO 1     | VCO 2     |                                    | Switched-cap.<br>off | Switched-cap.<br>on |

| Frequency (GHz)                                           | 17.24 GHz | 14.08 GHz | Frequency (GHz)                    | 15.87 GHz            | 14.12 GHz           |

| VCO core output<br>amplitude (Vpp)                        | 5.42 V    | 5.34 V    | VCO core output<br>amplitude (Vpp) | 5.08 V               | 2.51 V              |

| Source follower<br>buffer stage output<br>amplitude (Vpp) | 1.75 V    | 1.78 V    | OUTP/OUTN                          | 2.02V                | 1.82 V              |

| Overall output<br>amplitude from<br>CML stage (Vpp)       | 1.09 V    | 1.11 V    | (Vpp)                              | 2.02 V               |                     |

Table 4.1 Transient response of Design A and Design B

Table 4.1 shows that with the inclusion of the source follower buffer, the overall output amplitude from the CML stage is much lower.

# 4.1.2 Tuning Range

The overall tuning range covered for both designs is shown in Table 4.2. For Design A, the overall tuning range is obtained by the two overlapping tuning ranges of VCO 1 and

VCO 2. For Design B, the overall tuning range is obtained by the two overlapping tuning ranges obtained when the switched-capacitor is disabled and enabled.

|                                    | Design A       | Design B       |

|------------------------------------|----------------|----------------|

| Overall tuning range covered (GHz) | 11.11 to 21.31 | 11.05 to 19.15 |

Table 4.2 Tuning range of Design A and Design B

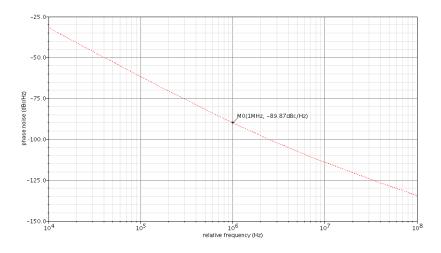

# 4.1.3 Phase Noise

The phase noise for VCO 1 of Design A is shown in Figure 4.2. As indicated, at 1 MHz offset, the phase noise is -89.87 dBc/Hz.

Figure 4.2 Phase noise for VCO 1 of Design A

The phase noise for Design A and Design B at 1 MHz offset is shown in Table 4.3.

Table 4.3 Phase noise at 1 MHz offset for Design A and Design B

|                                   | Design A      | Design B      |

|-----------------------------------|---------------|---------------|

| Phase Noise in<br>dBc/Hz at 1 MHz | -89.87 dBc/Hz | -90.31 dBc/Hz |

## 4.2 13 – GHz VCO Post-Layout Simulation Results

This section presents and discusses the post-layout simulation results of the transient response and amplitude, tuning range, and phase noise of the two 13-GHz LC-VCO designs. Comparison of these results to simulation results is made, indicating that overall the results match approximately and show the same trend.

## 4.2.1 Transient Response and Amplitude

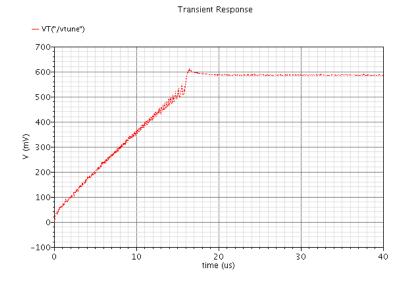

For design A, the transient response for the outputs of the VCO core, follower buffer stage, and overall output when VCO 1 is enabled is shown in Figure 4.3.

Figure 4.3 Transient response of VCO 1

The frequency when the oscillation stabilizes and the differential peak-to-peak amplitudes for the two designs at various stages are shown in Table 4.4.

|                                                              | Desi      | gn A      |                                    | Desi                 | gn B                |

|--------------------------------------------------------------|-----------|-----------|------------------------------------|----------------------|---------------------|

|                                                              | VCO 1     | VCO 2     |                                    | Switched-cap.<br>off | Switched-cap.<br>on |

| Frequency (GHz)                                              | 14.49 GHz | 11.76 GHz | Frequency (GHz)                    | 12.99 GHz            | 11.49 GHz           |

| VCO core output<br>amplitude (Vpp)                           | 1.72 V    | 1.93 V    | VCO core output<br>amplitude (Vpp) | 1.64 V               | 1.53 V              |

| Source follower<br>buffer stage<br>output amplitude<br>(Vpp) | 384.95 mV | 497.40 mV | OUTP/OUTN                          | 1.29 V               | 1.22 V              |

| Overall output<br>amplitude from<br>CML stage (Vpp)          | 264.10 mV | 345.70 mV | (Vpp)                              |                      |                     |

Table 4.4 Transient response of Design A and Design B

Post-layout simulation results of the transient response match the simulation results in that Design A which uses a source follower buffer has a much lower overall output amplitude from the CML stage.

# 4.2.2 Tuning Range

The overall tuning range obtained for both Design A and Design B are shown in Table 4.5. Corner analysis is performed to observe the sensitivity of the two designs to process variations. The Fast corner FF at -40 °C and the Slow corner SS at +80 °C are compared against the Typical case TT at +27 °C. The center frequency and tuning range, calculated as  $(f_{max}/f_{min}-1)\times100$ , is also shown in Table 4.5.

|          | Process Corner | Tuning Range (GHz) | Center Frequency<br>(GHz) | Tuning Range<br>(%) |

|----------|----------------|--------------------|---------------------------|---------------------|

|          | TT             | 11.87 to 17.02     | 14.45                     | 43.39               |

| Design A | FF             | 12.07 to 17.11     | 14.59                     | 41.76               |

|          | SS             | 11.60 to 16.95     | 14.28                     | 46.12               |

|          | TT             | 11.18 to 14.40     | 12.79                     | 28.80               |

| Design B | FF             | 11.62 to 14.56     | 13.09                     | 24.30               |

|          | SS             | 10.70 to 14.22     | 12.46                     | 32.90               |

Table 4.5 Overall tuning range for Design A and Design B

Both the results above and the simulated tuning range show the same trend. Design A has a higher and wider tuning range compared to Design B. The reason for this is that

Design B includes the use of a switched-capacitor placed in parallel with the LC-tank; this switched-capacitor has a fixed capacitance which is present even when the switched-capacitor is off. This fixed capacitance placed in parallel with the LC-tank acts to drop the VCO frequency and decrease the tuning range. Tuning ranges at process corners FF and SS are also examined. The results indicate that the designs are both relatively robust to process variations with Design A being slightly better.

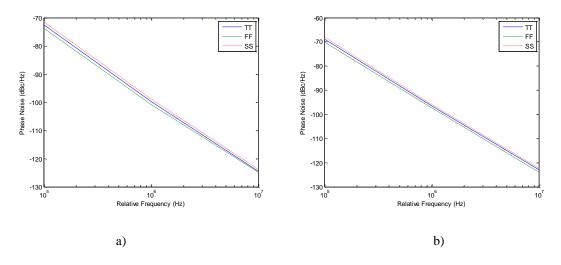

#### 4.2.3 Phase Noise

The phase noise performance for both Designs A and B are shown in Figure 4.4. The typical case TT as well as process corners FF and SS are also shown in the same graph. As can be seen, both designs are quite robust to process variations.

Figure 4.4 Phase noise performance of a) Design A, b) Design B

The phase noise for the corners at 1 MHz offset is shown in Table 4.6. The % variation is calculated by the following formula:

$$\% Variation = \frac{Highest Phase Noise-Lowest Phase Noise}{Typical Phase Noise} X 100\%$$

(4.1)

|          | TT            | FF             | SS            | %Variation |

|----------|---------------|----------------|---------------|------------|

| Design A | -99.76 dBc/Hz | -100.76 dBc/Hz | -98.83 dBc/Hz | 1.93%      |

| Design B | -96.47 dBc/Hz | -97.31 dBc/Hz  | -95.85 dBc/Hz | 1.51%      |

Table 4.6 Phase noise for Design A and Design B at 1-MHz offset

For the simulation with no extraction, the phase noise results of Design A and B are very close to one another; one is -89.87 dBc/Hz at 1 MHz offset and another is -90.31 dBc/Hz at 1 MHz offset. For post-layout simulations, Design A is approximately 3 dB better than Design B for all corners. This can be explained by the fact that for Design B, the switched-capacitor is placed in parallel with the LC-tank which decreases the Q of the LC-tank.

# **Chapter 5: Experimental Method and Measurement Results of 13-GHz VCO**

This chapter provides the experimental setup and procedures to test the two 13-GHz VCOs. Also included in this chapter is a discussion of the measurement results. Section 5.1 describes the circuit layout characteristics for both VCO designs. Section 5.2 lists the required equipment and provides a description of test procedures that are feasible with the available equipment, illustrated using schematics. Finally, Section 5.3 provides the VCO measurement results and compares them to the state-of-the-art.

## 5.1 Circuit Layout Characteristics

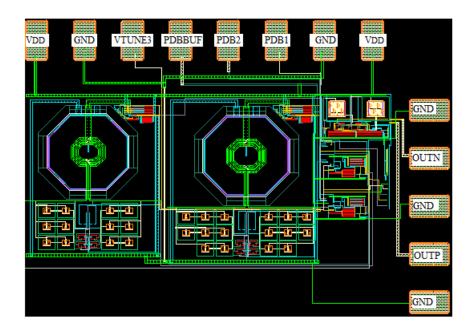

Two chips were fabricated in 90-nm CMOS technology. The chip that corresponds to Design A occupies an area of  $0.336 \times 0.750 \text{ mm}^2$ , without pads. The chip includes both VCO cores with their corresponding buffers and biasing circuitry. Figure 5.1 shows the layout of Design A with pad names.

Figure 5.1 Design A layout with pad names

Table 5.1 lists the names of the pads for the layout of Design A and their usages.

| Pin Name | Pin Usage                                                           |

|----------|---------------------------------------------------------------------|

| VDD      | 1.2 V supply                                                        |

| GND      | Ground (0 V)                                                        |

| VTUNE3   | VCO voltage control for changing VCO frequency, = 0 V to 1.2 V      |

| PDBBUF   | Enables CML buffer stage, = $0$ V for disable, = $1.2$ V for enable |

| PDB1     | Enables VCO core 1 and corresponding follower buffer,               |

|          | = 0 V for disable, $= 1.2$ V for enable                             |

| PDB2     | Enables VCO core 2 and corresponding follower buffer,               |

|          | = 0 V for disable, $= 1.2$ V for enable                             |

| OUTP     | Differential output                                                 |

| OUTN     | Differential output                                                 |

## Table 5.1 Design A fabricated chip pin functions

\*Note: PD means Power Down

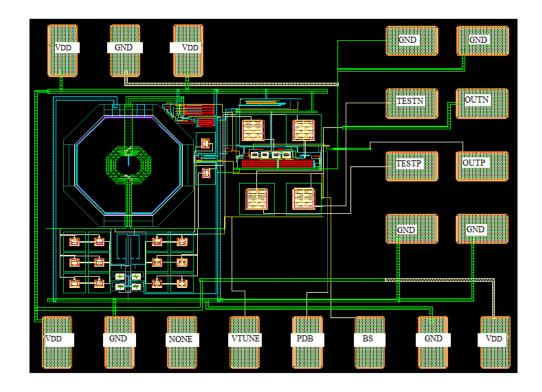

The chip that corresponds to Design B occupies an area of  $0.316 \times 0.425 \text{ mm}^2$ , without pads. The chip includes VCO core with switched-capacitor, buffer, and biasing circuitry. Figure 5.2 shows the layout of Design B with pad names.

Figure 5.2 Design B layout with pad names

Table 5.2 lists the names of the pads for the layout of Design B and their usages.

| Pin Name | Pin Usage                                                              |

|----------|------------------------------------------------------------------------|

| VDD      | 1.2 V supply                                                           |

| GND      | Ground (0 V)                                                           |

| VTUNE    | VCO voltage control for changing VCO frequency, $= 0$ V to 1.2 V       |

| PDB      | Enables VCO core and corresponding CML buffer stage,                   |

|          | = 0 V for disable, $= 1.2$ V for enable                                |

| BS       | Enables switching capacitor, $= 0$ V for disable, $= 1.2$ V for enable |

| TESTP    | Differential output with AC coupling to isolate DC condition           |

| TESTN    | Differential output with AC coupling to isolate DC condition           |

| OUTP     | Differential output                                                    |

| OUTN     | Differential output                                                    |

## Table 5.2 Design B fabricated chip pin functions

# 5.2 Experimental Setup

This section details the test plan for both VCO designs. A list of test equipment required to perform the tests is provided. A description of the tests is also given as well as illustration of the test setup using testbench schematics.

# 5.2.1 Required Equipment

Table 5.3 lists the required equipment necessary for the characterization of the two VCO designs.

| Quantity | Equipment                                                                                    |

|----------|----------------------------------------------------------------------------------------------|

| 1        | RF Probe station                                                                             |

| 1        | PGLLLLGP 500 MHz signal probe                                                                |

| 1        | GSGSG 40 GHz signal probe                                                                    |

| 1        | GSSG 50 GHz signal probe                                                                     |

| 1        | PGP DC signal probe                                                                          |

| 1        | Shielded Room (Electromagnetic Compatibility Lab - MCLD 132)                                 |

| 1        | 1.2 V Nickel-metal-hydride battery with battery holder and small circuit to vary vtune using |

|          | potentiometer                                                                                |

| 2        | DC Power supplies                                                                            |

| 4        | Low-frequency cables                                                                         |

| 6        | SMA (SubMiniature version A) cables                                                          |

| 1        | N9030A-526 PXA Spectrum Analyzer                                                             |

| 2        | Multimeters                                                                                  |

| 1        | Bias-T (26 GHz)                                                                              |

**Table 5.3 Test Equipment**

# 5.2.2 VCO Characterization

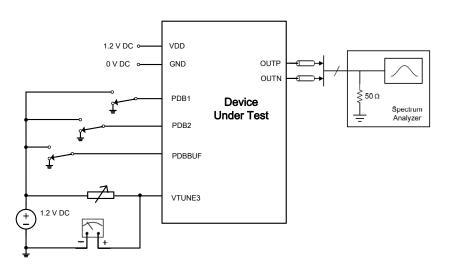

The testbench schematic for Design A characterization is provided in Figure 5.3.

Figure 5.3 Testbench schematic for characterization of Design A

PDBBUF is always switched on, and one VCO with its corresponding follower buffer is enabled at a time by switching on either PDB1 or PDB2. As VTUNE3 is swept, the range of frequencies is measured using the spectrum analyzer. Power consumption is measured via the current drawn using a multimeter. The peak-to-peak voltage is measured using the spectrum analyzer. Finally, the spectrum analyzer is also used to measure phase noise.

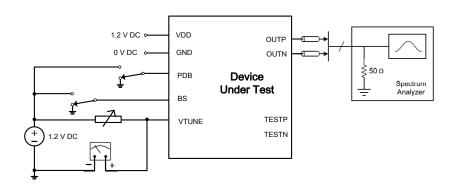

The testbench schematic for Design B characterization is provided in Figure 5.4.

Figure 5.4 Testbench schematic for characterization of Design B

PDB is always switched on, and BS is switched either on or off for enabling and disabling the switched-capacitor. As VTUNE is swept, the range of frequencies is measured using the spectrum analyzer. Like for Design A, power consumption is measured via the current drawn. The peak-to-peak voltage is also measured using the spectrum analyzer. Finally, the spectrum analyzer is used to measure phase noise.

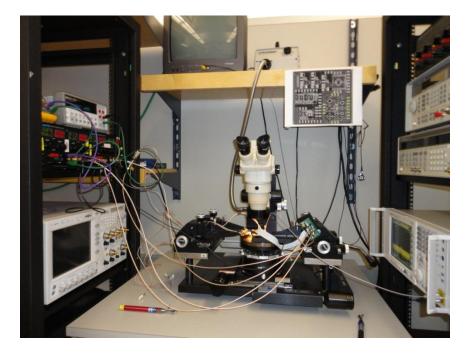

Figure 5.5 shows the initial test setup for VCO characterization where voltage is being supplied by the DC power supplies.

Figure 5.5 Test setup with DC power supplies

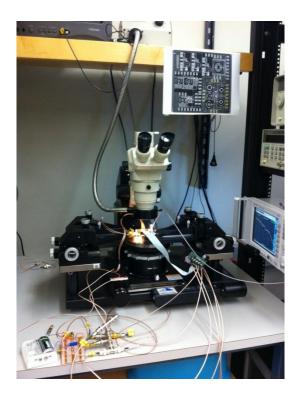

To improve phase noise measurements, a 1.2 V battery was used instead of the DC power supplies. To further improve phase noise measurements, the setup was moved to a shielded room to ensure that the electrical settings of the room was not interfering with measurements. A final attempt to improve phase noise was to use a bias-T at  $V_{tune}$  with a battery. These setups are shown in Figure 5.6.

a)

b)