## Analytical Models for Accelerating FPGA Architecture Development

by

Joydip Das

B.Sc., Bangladesh University of Engineering and Technology, 1996M.Sc., The University of Louisiana at Lafayette, 2006

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

## **Doctor of Philosophy**

in

THE FACULTY OF GRADUATE STUDIES

(Electrical and Computer Engineering)

The University Of British Columbia (Vancouver)

October 2012

© Joydip Das, 2012

## **Abstract**

Field-Programmable Gate Arrays (FPGAs) are widely used to implement logic without going through an expensive fabrication process. Current-generation FPGAs still suffer from area and power overheads, making them unsuitable for mainstream adoption for large volume systems. FPGA companies constantly design new architectures to provide higher density, lower power consumption, and faster implementation. An experimental approach is typically followed for new architecture design, which is a very slow and computationally expensive process. This dissertation presents an alternate faster way for FPGA architecture design.

We use analytical model based design techniques, where the models consist of a set of equations that relate the effectiveness of FPGA architectures to the parameters describing these architectures. During *early stage architecture investigation*, FPGA architects and vendors can use our equations to quickly short-list a limited number of architectures from a range of architectures under investigation. Only the short-listed architectures need then be investigated using an expensive experimental approach.

This dissertation presents three contributions towards the formulation of analytical models and the investigation of capabilities and limitations of these models.

First, we develop models that relate key FPGA architectural parameters to the depth along the critical path and the post-placement wirelength. We detail how these models can be used to estimate the expected area of implementation and critical path delay for user-circuits mapped on FPGAs.

Secondly, we develop a model that relates key parameters of the FPGA routing fabric to the fabric's routability, assuming that a modern one-step global/detailed router is used. We show that our model can capture the effects of the architectural parameters on routability.

Thirdly, we investigate capabilities and limitations of analytical models in answering design questions that are posed by the FPGA architects. Comparing with two experimental approaches, we demonstrate

that analytical models can better optimize FPGA architectures while requiring significantly less design effort. However, we also demonstrate that the analytical models, due to their continuous nature, should not be used to answer the architecture design questions related to applications having 'discrete effects'.

## **Preface**

- [1] (Chapter 3) A.M. Smith, J. Das, S.J.E. Wilton. Wirelength Modeling for Homogeneous and Heterogeneous FPGA Architecture Development. In Proc. of the ACM/SIGDA international symposium on Field programmable gate arrays, pages 181-190, February 22-24, 2009.

- [2] (Chapter 3) J. Das, A. Lam, S.J.E. Wilton, P. Leong, W. Luk. Modeling Post-Techmapping and Post-Clustering FPGA Circuit Depth. In Proc. of the International Conference on Field Programmable Logic and Applications, pages 205-211, September 2009.

- [3] (Chapter 4) J. Das, S.J.E. Wilton. An Analytical Model Relating FPGA Architecture Parameters to Routability. In Proc. of the ACM/SIGDA International Symposium on Field Programmable Gate Arrays, pages 181-184, February 2011. (short paper)

- [4] (Chapter 3) J. Das, A. Lam, S.J.E. Wilton, P. Leong, W. Luk. An Analytical Model Relating FPGA Architecture to Logic Density and Depth. In IEEE Transactions on Very Large Scale Integration. Vol. 19, issue 12, pp. 2229-2242, December 2011.

- [5] (Chapter 5) J. Das, S.J.E. Wilton. Accelerated FPGA Architecture Design: Capabilities and Limitations of Analytical Model. In Proc. of the International Conference on Field-Programmable Technology, pages 1-8, December 2011.

- [6] (Chapter 4) J. Das, S.J.E. Wilton. An Analytical Model for FPGA Routability and its Applications. *Submitted* to ACM Transactions on Reconfigurable Technology and Systems, April 2012.

The research contributions presented in this thesis have previously been published in journals and conference proceedings. The majority of the Chapter 3 has been published in [1], [2] and [4]. In [1], I developed the wirelength model for homogeneous architecture that was extended by the co-authors for modeling wirelength for heterogeneous architectures. In [4], I used the work from the co-authors to model logic density; the rest of this publication was based on my work. Parts of Chapter 4 was published in [3] and an extended version was submitted for review [6]. A preliminary version of Chapter 5 was published in [5] and an extended version is under preparation.

In [1], I have collaborated with Dr. Alastair M. Smith of Imperial College, UK (currently at PA Consulting Group, UK). In [2] and [4], I have used guidance and manuscript editing from Dr. Wayne

Luk of Imperial College, UK and Dr. Philip Leong of Chinese University of Hong Kong, Hong Kong (currently at University of Sydney, Australia). In all cases, I conducted the research and prepared the manuscripts with guidance and manuscript editing from my supervisor Dr. Steven J.E. Wilton.

## **Table of Contents**

| A  | bstrac  | et       |                                                                               | ii   |

|----|---------|----------|-------------------------------------------------------------------------------|------|

| Pı | eface   |          |                                                                               | iv   |

| Ta | ble of  | f Conten | s                                                                             | vi   |

| Li | st of ' | Tables . |                                                                               | xi   |

| Li | st of l | Figures  |                                                                               | xiii |

| Li | st of A | Abbrevia | tions                                                                         | XV   |

| A  | cknov   | vledgeme | nts                                                                           | xvi  |

| 1  | Intr    | oduction |                                                                               | 1    |

|    | 1.1     | Motivat  | on                                                                            | 1    |

|    | 1.2     | FPGA A   | Architecture Design                                                           | 2    |

|    |         | 1.2.1    | Experimental Approach                                                         | 2    |

|    |         | 1.2.2    | Analytical Model-Based Approach                                               | 3    |

|    |         | 1.2.3    | Example of Using Analytical Model Based Design Technique                      | 5    |

|    | 1.3     | Researc  | 1 Approach                                                                    | 5    |

|    |         | 1.3.1    | Assumptions                                                                   | 6    |

|    |         | 1.3.2    | Guiding Principles                                                            | 6    |

|    | 1.4     | Researc  | n Contributions                                                               | 6    |

|    |         | 1.4.1    | Analytical Models Relating FPGA Architecture to Area and Delay                | 7    |

|    |         | 1.4.2    | Analytical Model Relating FPGA Architecture to Routability                    | 7    |

|    |         | 1.4.3    | Accelerated FPGA Architecture Design: Capabilities and Limitations of Analyt- |      |

|    |         |          | ical Models                                                                   | 8    |

|    | 1.5     | Thesis   | Organization                                                                  | 10   |

| 2  | Bac     | _        |                                                                               | 11   |

|    | 2.1     | Review   |                                                                               | 11   |

|    |         | 2.1.1    | ·                                                                             | 11   |

|    |         |          | 2.1.1.1 Configurable Logic Resources                                          | 12   |

|   |     |           | 2.1.1.2   | Configurable Interconnect Fabric                            | 14 |

|---|-----|-----------|-----------|-------------------------------------------------------------|----|

|   |     |           | 2.1.1.3   | I/O Resources                                               | 15 |

|   |     | 2.1.2     | Applicati | ion-Specific FPGAs (ASFPGAs)                                | 16 |

|   |     | 2.1.3     | Other FP  | PGA Architectures                                           | 16 |

|   | 2.2 | Review    | of FPGA   | CAD Flow                                                    | 17 |

|   |     | 2.2.1     | CAD Sta   | iges                                                        | 17 |

|   |     |           | 2.2.1.1   | Design Entry                                                | 17 |

|   |     |           | 2.2.1.2   | Technology Mapping                                          | 18 |

|   |     |           | 2.2.1.3   | Packing (Clustering)                                        | 18 |

|   |     |           | 2.2.1.4   | Placement                                                   | 18 |

|   |     |           | 2.2.1.5   | Routing                                                     | 18 |

|   |     | 2.2.2     | CAD Ru    | n-time                                                      | 19 |

|   | 2.3 | Related   | d Work .  |                                                             | 20 |

|   |     | 2.3.1     | Experime  | ental FPGA Design Space Exploration                         | 20 |

|   |     |           | 2.3.1.1   | Versatile Place-and-Route (VPR)                             | 20 |

|   |     |           | 2.3.1.2   | Virtual Embedded Block (VEB)                                | 21 |

|   |     |           | 2.3.1.3   | Design of Experiments (DOE)                                 | 22 |

|   |     |           | 2.3.1.4   | Regression-Based Techniques                                 | 22 |

|   |     | 2.3.2     | Analytica | al Models for ASICs                                         | 23 |

|   |     | 2.3.3     | Analytica | al Models for FPGAs                                         | 25 |

|   |     |           | 2.3.3.1   | Modeling Area and Routability                               | 25 |

|   |     |           | 2.3.3.2   | Modeling Wirelength, Delay and Energy                       | 25 |

|   |     |           | 2.3.3.3   | Modeling CAD Runtime                                        | 26 |

|   |     |           | 2.3.3.4   | Architecture Optimization by Using Convex Programming Tools | 26 |

|   |     | 2.3.4     | Experime  | ental Techniques for FPGA Wirelength, Delay and Routability | 27 |

|   |     |           | 2.3.4.1   | Wirelength and Interconnect Distribution                    | 27 |

|   |     |           | 2.3.4.2   | Routability                                                 | 27 |

|   |     |           | 2.3.4.3   | Routing Delay                                               | 28 |

|   |     |           | 2.3.4.4   | Comments on Rent Co-efficient                               | 28 |

|   | 2.4 | Summa     | ary       |                                                             | 28 |

| 3 | Ana | lytical N | Aodels Re | elating Architecture to Area and Delay                      | 30 |

|   | 3.1 | Frame     |           |                                                             | 30 |

|   |     | 3.1.1     |           | tural and Circuit Assumptions                               | 31 |

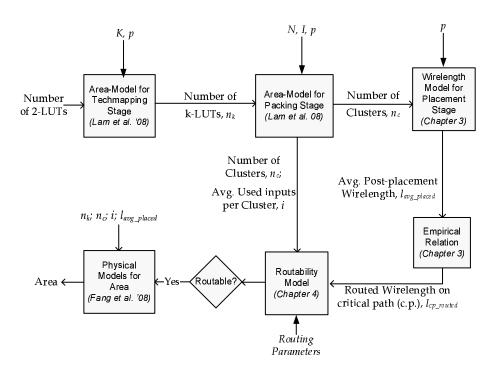

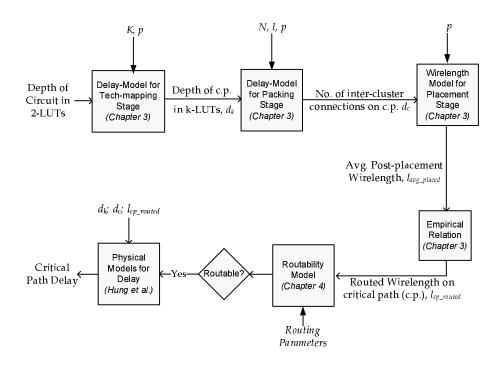

|   |     | 3.1.2     |           | f Area and Delay Models                                     | 32 |

|   |     |           | 3.1.2.1   | Stages of the Area Model                                    | 32 |

|   |     |           | 3.1.2.2   | Stages of the Delay Model                                   | 33 |

|   |     | 3.1.3     |           | Models from Prior Work                                      | 34 |

|   |     |           | 3.1.3.1   | Logic Utilization Model                                     | 34 |

|   |     |           | 3.1.3.2   | Physical Area and Delay Models Usage                        | 36 |

|   |     |           |           | 2                                                           |    |

|   | 3.2 | Model     | ing Area ( | or implementation                                               | 3/ |

|---|-----|-----------|------------|-----------------------------------------------------------------|----|

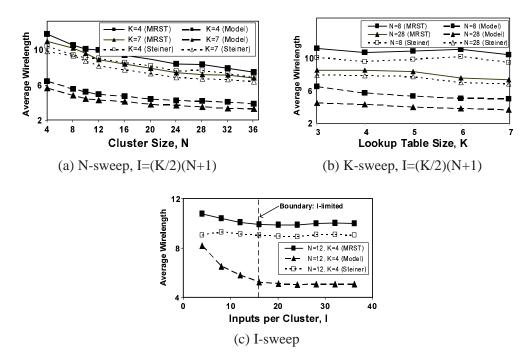

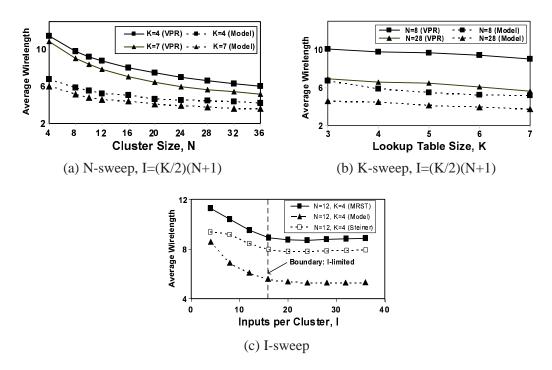

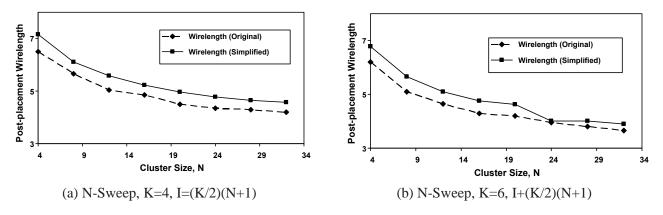

|   |     | 3.2.1     | Modelin    | g Post-Placement Average Wirelength                             | 37 |

|   |     |           | 3.2.1.1    | Multi-Terminal Nets                                             | 38 |

|   |     |           | 3.2.1.2    | Minimum Rectilinear Spanning Tree (MRST) Length and Minimum     |    |

|   |     |           |            | Rectilinear Steiner Tree Length                                 | 39 |

|   |     | 3.2.2     | Estimati   | ng Area of Implementation                                       | 39 |

|   | 3.3 | Model     | ing Post-F | Routing Delay                                                   | 40 |

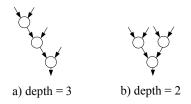

|   |     | 3.3.1     | Modelin    | g Post-Technology Mapping Depth                                 | 41 |

|   |     | 3.3.2     | Modelin    | g Post-Clustering Depth                                         | 42 |

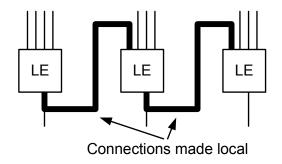

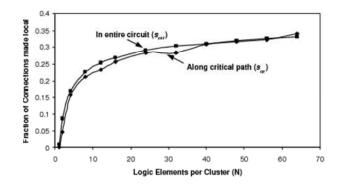

|   |     |           | 3.3.2.1    | Proportion of Connections Made Local                            | 42 |

|   |     |           | 3.3.2.2    | Connections Along the Critical Path                             | 44 |

|   |     |           | 3.3.2.3    | Overall Model for Post-Clustering Depth                         | 45 |

|   |     | 3.3.3     | Modelin    | g Critical Path Delay                                           | 45 |

|   | 3.4 | Valida    | tion of Mo | odels                                                           | 47 |

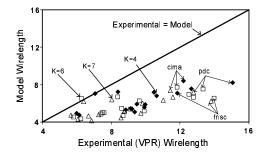

|   |     | 3.4.1     | Validatio  | on of Wirelength Model                                          | 47 |

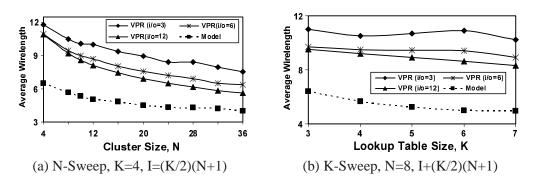

|   |     |           | 3.4.1.1    | Effects of Pad-Constrained Circuits                             | 48 |

|   |     |           | 3.4.1.2    | Effects of <i>N</i> - and <i>I</i> -Limited Architectures       | 50 |

|   |     |           | 3.4.1.3    | Circuit by Circuit Verification                                 | 51 |

|   |     |           | 3.4.1.4    | Underestimation of Average Wirelength by Our Model              | 51 |

|   |     | 3.4.2     | Discussi   | on on Results for Wirelength Model Validation                   | 51 |

|   |     |           | 3.4.2.1    | Issues Related to Estimation of Rent Parameters                 | 51 |

|   |     |           | 3.4.2.2    | Other Issues with Wirelength Estimation Techniques              | 52 |

|   |     |           | 3.4.2.3    | Simplified Form of Wirelength Model                             | 53 |

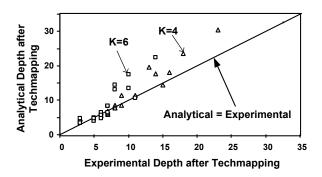

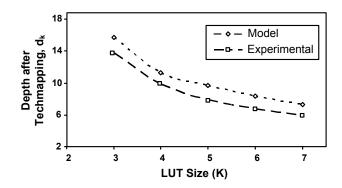

|   |     | 3.4.3     | Validatio  | on of Delay Models                                              | 53 |

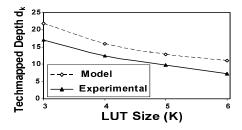

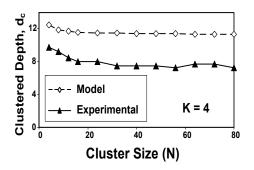

|   |     |           | 3.4.3.1    | Validation of the Model for Post-Technology Mapping Depth $d_k$ | 54 |

|   |     |           | 3.4.3.2    | Validation of Model for Post-Clustering Depth $d_c$             | 55 |

|   |     | 3.4.4     | Discussi   | on on Results for Delay Models Validation                       | 56 |

|   |     | 3.4.5     | Effects of | of Rent Coefficient                                             | 57 |

|   |     | 3.4.6     | Validatio  | on for Large QUIP Benchmark Circuits                            | 58 |

|   | 3.5 | Summ      | ary        |                                                                 | 60 |

| 4 | Ana | lytical I | Model Re   | lating Architecture and Routability                             | 62 |

|   | 4.1 | Overvi    | iew of Rou | utability Model                                                 | 63 |

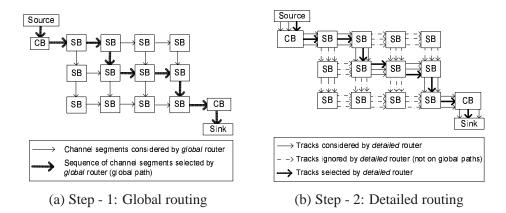

|   |     | 4.1.1     | FPGA R     | outing: Two-Step and Combined Single-Step Routers               | 63 |

|   |     |           | 4.1.1.1    | Two-Step Router                                                 | 64 |

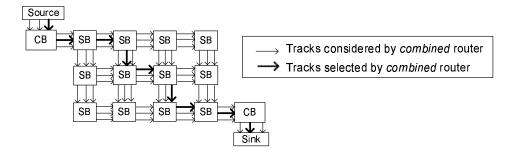

|   |     |           | 4.1.1.2    | One-Step Combined Router                                        | 64 |

|   |     | 4.1.2     | Context    | of our Routability Model                                        | 65 |

|   |     | 4.1.3     | Approxi    | mations and Assumptions                                         | 66 |

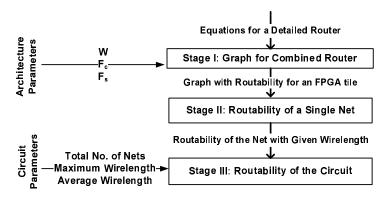

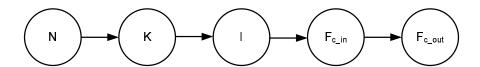

|   |     | 4.1.4     | Stages of  | f the Routability Model                                         | 66 |

|   | 4.2 | Model     | Formulat   | ion                                                             | 69 |

|   |     |           |            |                                                                 |    |

|   |     | 4.2.1    | Stage 1: Constructing the Routing Graphs 69                                   |

|---|-----|----------|-------------------------------------------------------------------------------|

|   |     |          | 4.2.1.1 Graph Topology                                                        |

|   |     |          | 4.2.1.2 Weight Estimation: Relevant Terminology                               |

|   |     |          | 4.2.1.3 Weight Estimation: Source to First Switch Block Weight 71             |

|   |     |          | 4.2.1.4 Weight Estimation: Switch Block to Switch Block Weights 72            |

|   |     |          | 4.2.1.5 Weight Estimation: Final Switch Block to Sink Weight                  |

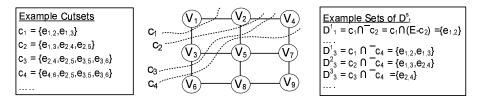

|   |     | 4.2.2    | Stage 2: Overall Routability of a Single Net                                  |

|   |     |          | 4.2.2.1 Supplementary Definitions                                             |

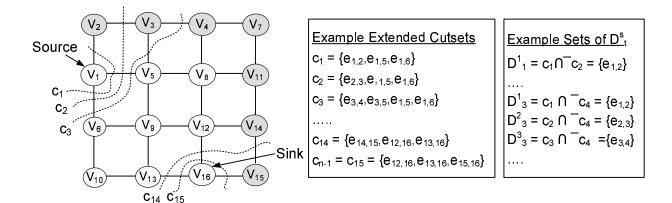

|   |     |          | 4.2.2.2 Upper Estimate: Consecutive Minimal Cutsets of the Routing Graph . 76 |

|   |     | 4.2.3    | Stage 3: Routability of a Circuit with Many Nets on a Given FPGA              |

|   |     | 4.2.4    | Summary                                                                       |

|   | 4.3 | Plausil  | ble Extensions of Our Model                                                   |

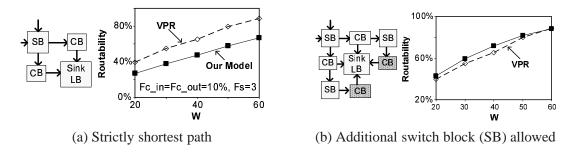

|   |     | 4.3.1    | Relaxation of the Shortest Path Constraint                                    |

|   |     | 4.3.2    | Non-Island Style Architectures                                                |

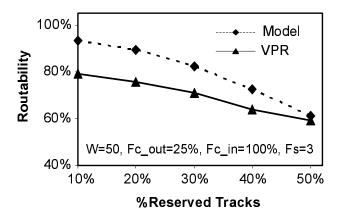

|   |     | 4.3.3    | Effects of Faulty Tracks                                                      |

|   | 4.4 | Valida   | tion                                                                          |

|   |     | 4.4.1    | Validation Methodology                                                        |

|   |     |          | 4.4.1.1 Obtaining Model Results Without Going Through any Experimental        |

|   |     |          | CAD Stage                                                                     |

|   |     |          | 4.4.1.2 Obtaining Experimental Results                                        |

|   |     | 4.4.2    | Validation Results - MCNC Benchmark Circuits                                  |

|   |     |          | 4.4.2.1 Impact of Logic Fabric on Routability                                 |

|   |     |          | 4.4.2.2 Variation across Individual Circuits                                  |

|   |     |          | 4.4.2.3 Routability for a Specific Routing Fabric                             |

|   |     | 4.4.3    | Validation Results - QUIP Benchmark Crcuits                                   |

|   |     |          | 4.4.3.1 Computation Time                                                      |

|   |     | 4.4.4    | Relaxation of Shortest-Path Constraint                                        |

|   |     | 4.4.5    | Effects of Faulty Tracks                                                      |

|   |     | 4.4.6    | Model Summary and Discussion on Results                                       |

|   |     |          | 4.4.6.1 Model Summary                                                         |

|   |     |          | 4.4.6.2 Discussion on Results                                                 |

|   | 4.5 | Summ     | ary                                                                           |

|   |     |          |                                                                               |

| 5 | App | lication | s of Analytical Models: Capabilities and Limitations                          |

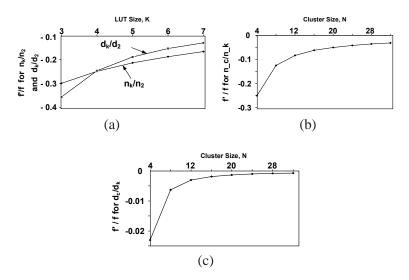

|   | 5.1 | Impact   | t of Architectural and Circuit Parameters                                     |

|   |     | 5.1.1    | Derivatives of Analytical Models                                              |

|   |     | 5.1.2    | Results and Discussions                                                       |

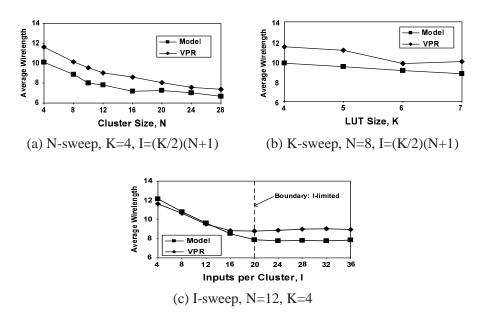

|   | 5.2 |          | veness of Analytical Models during Parameter Sweeps                           |

|   | 5.3 | Design   | n Question 1: Optimization of General Purpose FPGA Architecture               |

|   |     | 5.3.1    | Design Flow 1: Sequential Optimization Through Experimentations 101           |

|   |                |                                                                                            | 5.3.1.1                                                                                                                       | Stages of Design Flow 1                                                                                                                                                                                                                                                                                                                            | 101                                                                |

|---|----------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|   |                |                                                                                            | 5.3.1.2                                                                                                                       | Methodology                                                                                                                                                                                                                                                                                                                                        | 102                                                                |

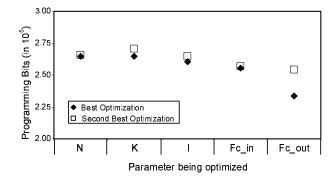

|   |                |                                                                                            | 5.3.1.3                                                                                                                       | Results from Design Flow 1                                                                                                                                                                                                                                                                                                                         | 104                                                                |

|   |                | 5.3.2                                                                                      | Design F                                                                                                                      | Flow 2: DOE-Based Experimental Technique                                                                                                                                                                                                                                                                                                           | 105                                                                |

|   |                |                                                                                            | 5.3.2.1                                                                                                                       | Stages of Design Flow 2                                                                                                                                                                                                                                                                                                                            | 106                                                                |

|   |                |                                                                                            | 5.3.2.2                                                                                                                       | Results from Design Flow 2                                                                                                                                                                                                                                                                                                                         | 111                                                                |

|   |                | 5.3.3                                                                                      | Design F                                                                                                                      | Flow 3: Model-Based Optimization                                                                                                                                                                                                                                                                                                                   | 112                                                                |

|   |                |                                                                                            | 5.3.3.1                                                                                                                       | Stages of Design Flow 3                                                                                                                                                                                                                                                                                                                            | 112                                                                |

|   |                |                                                                                            | 5.3.3.2                                                                                                                       | Results from Design Flow 3                                                                                                                                                                                                                                                                                                                         | 114                                                                |

|   |                | 5.3.4                                                                                      | Compari                                                                                                                       | son of Results from Three Design Flows and Discussion                                                                                                                                                                                                                                                                                              | 115                                                                |

|   | 5.4            | Design                                                                                     | Question                                                                                                                      | -2: Optimization of Application-Specific FPGA Architecture (ASFPGA)                                                                                                                                                                                                                                                                                | 119                                                                |

|   |                | 5.4.1                                                                                      | Methodo                                                                                                                       | ology                                                                                                                                                                                                                                                                                                                                              | 119                                                                |

|   |                | 5.4.2                                                                                      | Results a                                                                                                                     | and Discussion                                                                                                                                                                                                                                                                                                                                     | 119                                                                |

|   | 5.5            | Summ                                                                                       | ary                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                    | 121                                                                |

|   |                |                                                                                            |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

| 6 | Con            | clusion                                                                                    |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    | 122                                                                |

| 6 | <b>Con</b> 6.1 |                                                                                            |                                                                                                                               | nmary                                                                                                                                                                                                                                                                                                                                              | <b>122</b> 122                                                     |

| 6 |                | Disser                                                                                     | tation Sun                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

| 6 | 6.1            | Disser                                                                                     | tation Sun                                                                                                                    | nmary                                                                                                                                                                                                                                                                                                                                              | 122                                                                |

| 6 | 6.1            | Disser<br>Limita                                                                           | tation Sun<br>tions and S<br>Analytic                                                                                         | nmary                                                                                                                                                                                                                                                                                                                                              | 122<br>124                                                         |

| 6 | 6.1            | Dissert<br>Limita<br>6.2.1                                                                 | tation Sun<br>tions and a<br>Analytic<br>Analytic                                                                             | Short Term Future Work                                                                                                                                                                                                                                                                                                                             | 122<br>124<br>125                                                  |

| 6 | 6.1            | Dissert<br>Limita<br>6.2.1<br>6.2.2<br>6.2.3                                               | tation Sun<br>tions and a<br>Analytic<br>Analytic<br>Applicat                                                                 | Short Term Future Work                                                                                                                                                                                                                                                                                                                             | 122<br>124<br>125<br>125<br>126                                    |

| 6 | 6.1<br>6.2     | Dissert<br>Limita<br>6.2.1<br>6.2.2<br>6.2.3                                               | tation Sun<br>tions and a<br>Analytic<br>Analytic<br>Applicat                                                                 | Short Term Future Work                                                                                                                                                                                                                                                                                                                             | 122<br>124<br>125<br>125<br>126                                    |

| 6 | 6.1<br>6.2     | Dissert<br>Limita<br>6.2.1<br>6.2.2<br>6.2.3<br>Long-7                                     | tation Sun<br>tions and a<br>Analytic<br>Analytic<br>Applicat<br>Ferm Direc<br>Analytic                                       | Short Term Future Work                                                                                                                                                                                                                                                                                                                             | 122<br>124<br>125<br>125<br>126<br>127<br>127                      |

| 6 | 6.1<br>6.2     | Dissert<br>Limita<br>6.2.1<br>6.2.2<br>6.2.3<br>Long-7                                     | tation Sun<br>tions and a<br>Analytic<br>Analytic<br>Applicat<br>Term Direc<br>Analytic<br>Analytic                           | Short Term Future Work                                                                                                                                                                                                                                                                                                                             | 122<br>124<br>125<br>125<br>126<br>127<br>127                      |

| 6 | 6.1<br>6.2     | Dissert<br>Limita<br>6.2.1<br>6.2.2<br>6.2.3<br>Long-7<br>6.3.1<br>6.3.2                   | tation Sun<br>tions and a<br>Analytic<br>Analytic<br>Applicat<br>Term Direc<br>Analytic<br>Analytic<br>Effects o              | Short Term Future Work                                                                                                                                                                                                                                                                                                                             | 122<br>124<br>125<br>125<br>126<br>127<br>127                      |

| 6 | 6.1<br>6.2     | Dissert<br>Limita<br>6.2.1<br>6.2.2<br>6.2.3<br>Long-7<br>6.3.1<br>6.3.2<br>6.3.3          | tation Suntions and analytic Analytic Applicat Ferm Direct Analytic Analytic Effects of Optimizations                         | Short Term Future Work                                                                                                                                                                                                                                                                                                                             | 122<br>124<br>125<br>125<br>126<br>127<br>127<br>127               |

| 6 | 6.1<br>6.2     | Dissert<br>Limita<br>6.2.1<br>6.2.2<br>6.2.3<br>Long-7<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4 | tation Sun<br>tions and a<br>Analytic<br>Analytic<br>Applicat<br>Term Direc<br>Analytic<br>Analytic<br>Effects of<br>Optimiza | Short Term Future Work  al Models Relating Architecture to Area and Delay  al Model Relating Architecture and Routability  ions of Analytical Models: Capabilities and Limitations  ctions for Future Work  al Models for Other Evaluation Metrics  al Models for Embedded Blocks  of Fabrication Issues  attion by Using Convex Programming Tools | 122<br>124<br>125<br>125<br>126<br>127<br>127<br>127<br>128<br>128 |

## **List of Tables**

| Table 2.1 | Architectural Parameters that We Investigate (Model Inputs)                         | 12  |

|-----------|-------------------------------------------------------------------------------------|-----|

| Table 3.1 | Model Parameters                                                                    | 31  |

| Table 3.2 | MCNC Benchmark Circuits                                                             | 46  |

| Table 3.3 | QUIP Benchmark Circuits                                                             | 46  |

| Table 3.4 | MCNC Benchmarks, Used to Measure $\gamma$ for Model Validation                      | 46  |

| Table 3.5 | γ Values from Five MCNC Benchmarks                                                  | 47  |

| Table 3.6 | Rent Co-Efficients, as a Function of LUT Size $K$ (Cluster size, $N=8$ )            | 50  |

| Table 3.7 | Standard Deviation of Estimating $d_k$ for 20 Circuits                              | 54  |

| Table 3.8 | Absolute and % Absolute Difference Between Experimental and Estimated Values of     |     |

|           | $d_k$                                                                               | 55  |

| Table 3.9 | Comparison of Accuracy                                                              | 60  |

| Table 4.1 | Model Parameters                                                                    | 68  |

| Table 4.2 | Comparison of $Pr[\psi_i l]$ Values for the Largest MCNC Benchmark: $clma$          | 79  |

| Table 4.3 | Values of $Pr[\psi_i L]$ for a Typical Circuit                                      | 79  |

| Table 4.4 | Model Inputs for <i>spla</i>                                                        | 83  |

| Table 4.5 | Benchmark Circuits Used for Routability Model Validation                            | 84  |

| Table 4.6 | The Absolute Difference and the Standard Deviation of the Differences between the   |     |

|           | % Model and the % VPR Routability (Based on Circuit-By-Circuit Results for MCNC     |     |

|           | Suite)                                                                              | 87  |

| Table 4.7 | Range of Values for Routability and Corresponding Number of Circuits (Out of Twenty |     |

|           | MCNC Benchmarks), for Channel Width W-Sweep                                         | 88  |

| Table 4.8 | Time Required (in Minutes) for QUIP Benchmarks                                      | 89  |

| Table 4.9 | Effects of Skipping Nets to Accelerate Estimation                                   | 90  |

| Table 5.1 | Parameters Used to Optimize an FPGA Architecture                                    | 95  |

| Table 5.2 | Design Space for Exploration                                                        | 100 |

| Table 5.3 | Design Flow 1 Results : Sequential Optimization for the Number of Programming Bits  | 104 |

| Table 5.4 | Design Flow 1 Results: Sequential Optimization for the Critical Path Delay          | 105 |

| Table 5.5 | Plackett-Burman (PB) Matrix for Generating Interdependency Graphs                   | 108 |

| Table 5.6  | DPG Stages: Optimizing an Architecture for the Area of Implementation (No. of Prog. |     |

|------------|-------------------------------------------------------------------------------------|-----|

|            | Bits). Sequence of the Pairs is Determined from Figure 5.5a); $F_s$ =3 in all cases | 110 |

| Table 5.7  | DPG Stages: Optimizing an Architecture for Critical Path Delay. Sequence of the     |     |

|            | Pairs is Determined from Figure 5.5(b); $F_s$ =3 in All Cases                       | 111 |

| Table 5.8  | Optimization for Area                                                               | 114 |

| Table 5.9  | Optimization for Critical Path Delay                                                | 115 |

| Table 5.10 | Comparison of Design Flows: Area of Implementation                                  | 116 |

| Table 5.11 | Comparison of Design Flows: Critical Path Delay                                     | 117 |

| Table 5.12 | Sequential Optimization for the Number of Programming Bits with Different Ordering  |     |

|            | of Parameters as Compared to Table 5.3                                              | 118 |

| Table 5.13 | Parameters of the Investigated Crossbar Switches                                    | 119 |

# **List of Figures**

| Figure 1.1  | Fully Experimental Approach for New FPGA Architecture Design                          | 2  |

|-------------|---------------------------------------------------------------------------------------|----|

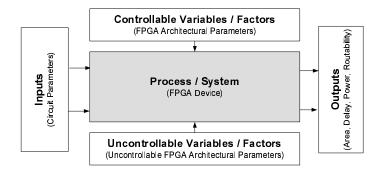

| Figure 1.2  | Analytical Models: Conceptual Overview                                                | 4  |

| Figure 1.3  | Analytical Model-Based Design of New FPGA Architectures                               | 4  |

| Figure 1.4  | Early Stage Architecture Investigation Using Analytical Models                        | 5  |

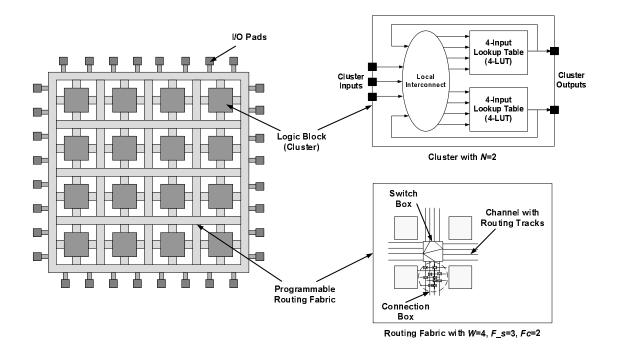

| Figure 2.1  | Typical Island-Style FPGA Architecture                                                | 12 |

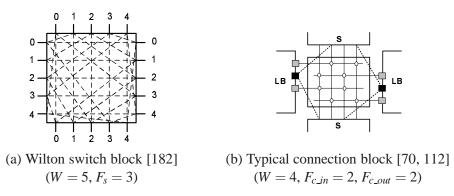

| Figure 2.2  | Switch Block and Connection Block Detail                                              | 14 |

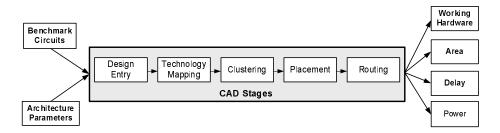

| Figure 2.3  | FPGA Design Flow                                                                      | 17 |

| Figure 2.4  | FPGA Architecture Evaluation Using Design of Experiments (DOE)-Based Technique        | 22 |

| Figure 3.1  | Flow for Modeling Area of Implementation                                              | 33 |

| Figure 3.2  | Flow for Modeling Critical Path (c.p.) Delay                                          | 34 |

| Figure 3.3  | Two Possible Mappings for $K = 4$                                                     | 41 |

| Figure 3.4  | Cluster with Three Lookup-Tables                                                      | 42 |

| Figure 3.5  | Comparison of $s_{ckt}$ and $s_{cp}$ from T-VPACK                                     | 44 |

| Figure 3.6  | Verification of Wirelength Model for 20 MCNC Benchmarks                               | 48 |

| Figure 3.7  | Verification of Wirelength Model for 17 Non-Pad-Constrained Benchmarks                | 49 |

| Figure 3.8  | Effects of i/o Capacity on Wirelength for Twenty Benchmarks Including Pad-Constrained |    |

|             | Benchmarks; i/o Capacity is the Number of I/Os Contained in the I/O Pads [179]        | 49 |

| Figure 3.9  | Verification of Wirelength for N=8 (Circuit by Circuit)                               | 50 |

| Figure 3.10 | Nominal Effects of Using Simplified Expression for Wirelength Modeling                | 53 |

| Figure 3.11 | Model Verification for $d_k$ (Circuit by Circuit)                                     | 54 |

| Figure 3.12 | Model Verification for $d_k$ (Averaged over 20 Circuits)                              | 55 |

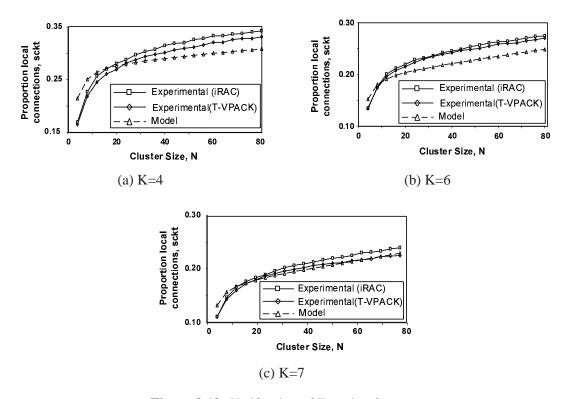

| Figure 3.13 | Verification of Equation for $s_{ckt}$                                                | 56 |

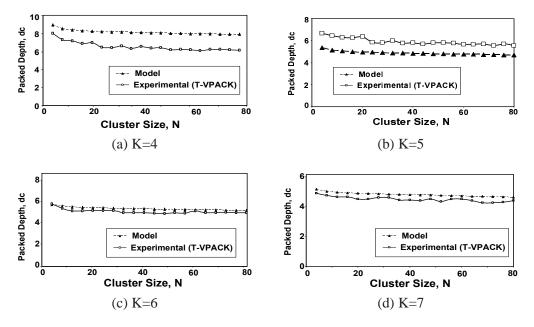

| Figure 3.14 | Verification of Equation for $d_c$                                                    | 57 |

| Figure 3.15 | Effects of Rent Coefficient on Area and Delay Equations                               | 58 |

| Figure 3.16 | Verification of Wirelength Model for QUIP Benchmarks                                  | 59 |

| Figure 3.17 | QUIP Benchmark Circuits: Model Verification for $d_k$                                 | 59 |

| Figure 3.18 | QUIP Benchmark Circuits: Model verification for $d_c$                                 | 60 |

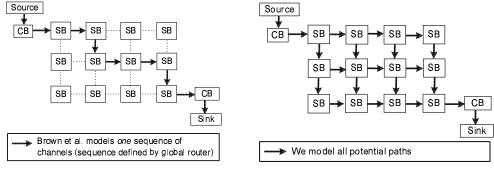

| Figure 4.1  | Behavior of a Typical Two-Step FPGA Routing (with Channel-Width $W=3$ ). CBs and      |    |

|             | SBs Respectively Represent Connection Blocks and Switch Blocks                        | 64 |

| Figure 4.2  | Behavior of a Typical One-Step Combined Global/Detailed FPGA Router (with Channel   | 1-  |

|-------------|-------------------------------------------------------------------------------------|-----|

|             | Width $W=3$ ). CBs and SBs Respectively Represent Connection Blocks and Switch      |     |

|             | Blocks                                                                              | 65  |

| Figure 4.3  | Brown's Model and Our Work                                                          | 66  |

| Figure 4.4  | Overview of Routability Model                                                       | 67  |

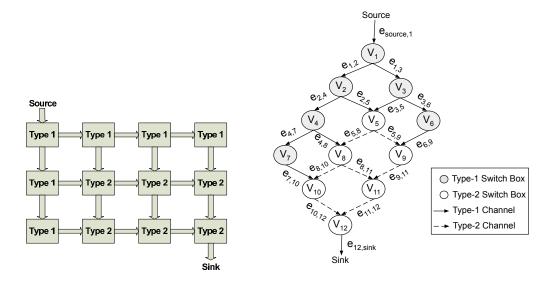

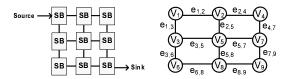

| Figure 4.5  | Two-dimensional Routing Problem and the Graph Representation                        | 68  |

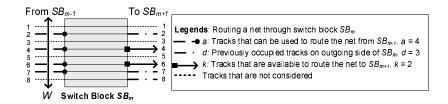

| Figure 4.6  | Parameters Related to Routing a Net $\psi_i$ Through Switch Block $SB_m$            | 71  |

| Figure 4.7  | A Type 2 Channel for Combined Router                                                | 73  |

| Figure 4.8  | Example Two-Dimensional Routing Problem and Corresponding Graph                     | 74  |

| Figure 4.9  | Examples of Consecutive Cutsets                                                     | 76  |

| Figure 4.10 | Consecutive Cutsets for the Extended Graph. Shaded Nodes Represent Additional       |     |

|             | Nodes (Switch Blocks) When Shortest-Path Constraint is Removed                      | 80  |

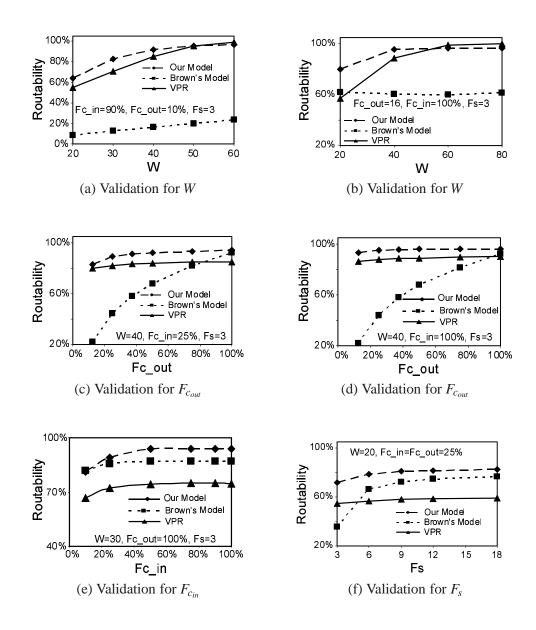

| Figure 4.11 | Validation for 20 MCNC Benchmark Circuits with $K=4$ , $N=8$ and $I=18$             | 85  |

| Figure 4.12 | Impact of Logic Fabric: Results with $K=6$ , $N=16$ and $I=51$                      | 86  |

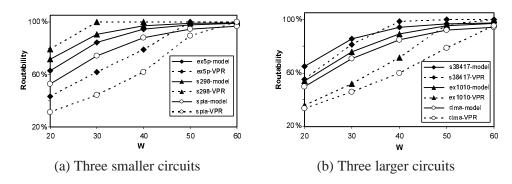

| Figure 4.13 | Routability for Individual Circuits                                                 | 87  |

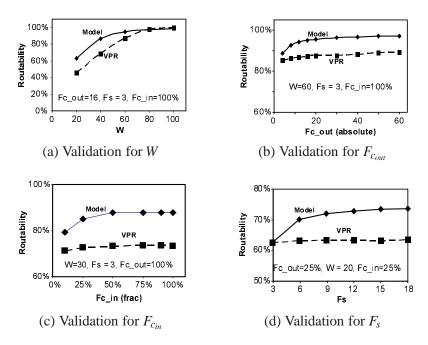

| Figure 4.14 | Validation for QUIP Benchmark Circuits with LUT-Size $K=4$ , Cluster-Size $N=8$ and |     |

|             | Inputs per Cluster <i>I</i> =18                                                     | 89  |

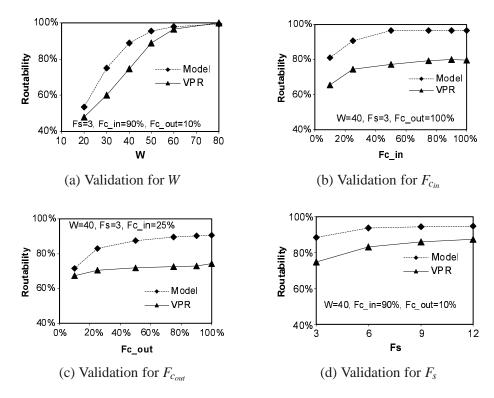

| Figure 4.15 | Routability for Highly Constrained Architecture (Averaged over 20 MCNC Bench-       |     |

|             | marks)                                                                              | 91  |

| Figure 4.16 | Investigation of Effects of Faulty Routing Tracks                                   | 92  |

| Figure 5.1  | Impact of Architectural and Circuit Parameters. (a) Impact of LUT Size on the Num-  |     |

|             | ber of Logic Blocks and the Post-Technology Mapping Depth. (b) Impact of Cluster    |     |

|             | Size on the Number of Clusters. (c) Impact of Cluster Size on the Post-Clustering   |     |

|             | Depth                                                                               | 97  |

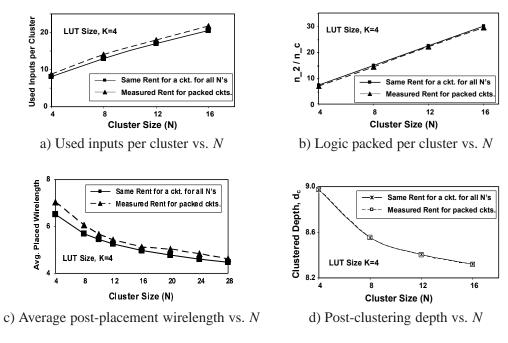

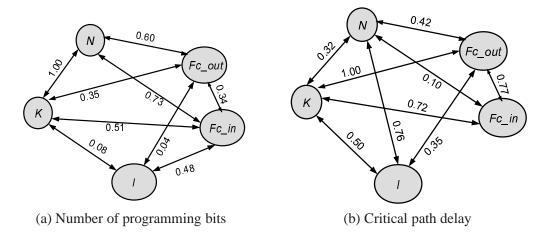

| Figure 5.2  | Orders of Optimization (Both Area and Delay) for the Architectural Parameters       | 102 |

| Figure 5.3  | Design Flow 1: Number of programming Bits at the End of Each Optimization Stage     | 104 |

| Figure 5.4  | Design Flow 1: Critical Path Delay at the End of Each Optimization Stage            | 105 |

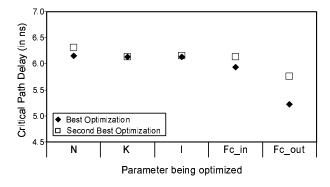

| Figure 5.5  | Parameter Interdependency Graphs (Results Averaged over 20 MCNC Benchmarks)         | 107 |

| Figure 5.6  | Area Optimization with Different Ordering of Parameters                             | 117 |

| Figure 5.7  | Results to Investigate the Limitation of Model-Based Approach in Capturing the Re-  |     |

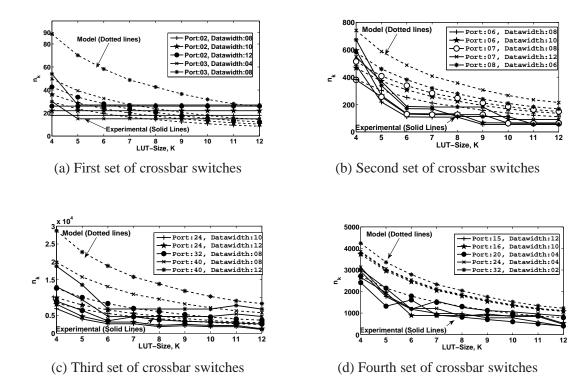

|             | quired Number of LUTs, n, for Crossbar Switches                                     | 120 |

## List of Abbreviations

**FPGA** Field-Programmable Gate Array

**CAD** Computer-Aided Design

**BLE** Basic Logic Element

**LUT** Look-Up Table

**ASIC** Application Specific Integrated Circuit

**SB** Switch Block

**CB** Connection Block

VPR Versatile Place-and-Route, a commonly-used academic FPGA place-and-route tool

VTR Verilog-to-Routing project, an academic synthesis flow

Does Design of Experiments, originally proposed by Sir Ronald Fisher in 1926 for the agriculture

domain, and later used by the designers and the industry leaders of several domains

VEB Virtual Embedded Block

**DPG** DOE-based Pareto-point generation, a technique proposed to investigate Pareto points of a

FPGA architecture by using DOE-based technique

PB Plackett-Burmann set of experiments, used to investigate the effects of input parameters on

output parameters in DOE-based techniques

**EB** Embedded Block

**GALS** Globally Asynchronous Locally Synchronous

PCB Printed Circuit Board

**GPU** Graphics Processing Unit

## **Acknowledgements**

The work in this dissertation was performed under the supervision of Dr. Steven J.E. Wilton. I am fortunate to have worked with Dr. Wilton. His unlimited guidance in the direction of my research helped me to carry out my research as well as to prepare this dissertation. His detailed oriented approach helped me in each stage of my research. Working with him made me much more organized and much more focused than I had been ever before. I am also thankful to him for his guidance in my professional development.

I would also like to express thanks to my qualifying, departmental and final examination committee members: Dr. Tor Aamodt, Dr. Sathish Gopalakrishnan, Dr. Alan Hu, Dr. Shahriar Mirabbasi and Dr. Konrad Walus. Their comments and feedback improved the quality of my research and my dissertation.

I would like to thank the Natural Sciences and Engineering Research Council (NSERC) of Canada and Altera Toronto Technology Center for funding my Ph.D. research. I thank Dr. Fahmida N. Chowdhury of the University of Louisiana for her support during my MS program and for encouraging me to pursue further research. I thank the colleagues at the Systems-On-Chip laboratory in the University of British Columbia for their support during my Ph.D. program. I thank my current employer Achronix Semiconductor Corporation for giving me the industry exposure in a dynamic and challenging environment.

I am thankful to my parents, Dharma Das and Kazal Das as well as my three sisters and their little ones: Aishi, Aira and Auritro; for their support. I thank my wife Reshmi Chowdhury for her extreme support and encouragement throughout my Ph.D. program as well as for helping me maintain calmness during my submission deadlines. Finally, I am thankful to my little one Aattoja Chowdhury Das for keeping me upbeat over the last three years. Posting Aattoja's updates and pictures on Facebook provided me with the much-needed breaks during this time.

## Chapter 1

## Introduction

## 1.1 Motivation

Field-Programmable Gate Arrays (FPGAs) are pre-fabricated devices that can be used to implement logic without going through an expensive fabrication process. FPGAs have evolved considerably since their introduction in 1985. Originally used for prototyping and small glue logic replacement, these devices are now used to implement entire systems containing memory, embedded processors, and other functionality. Advanced manufacturing technologies provide an unprecedented number of transistors, and FPGA vendors have used these transistors to create new logic, routing and embedded block architectures. Unlike Application Specific Integrated Circuits (ASICs), FPGAs are pre-fabricated devices. This requires the FPGA vendors to make FPGA devices suitable for a wide range of applications. Much of the improvement in FPGA technology is a result of improvements in FPGA architecture. The architecture of an FPGA refers to the structure and interconnection of the configurable elements inside the device. New architectures are designed to provide higher density, lower power consumption and/or faster circuit implementations. FPGA manufacturers expend tremendous effort evaluating architectural enhancements for every generation of their devices, and this activity shows no signs of diminishing [10, 188].

During the design of a new FPGA, each architectural enhancement has to be evaluated to determine whether it should be incorporated in the new device. Typically-used evaluation metrics are area, delay, power and routability. This evaluation is typically done using an experimental approach [21] with the help of detailed area, delay, and power models [11, 21, 116, 119, 141]. Due to the presence of numerous interacting architecture parameters, the experimental evaluation of FPGA architectures by sweeping the

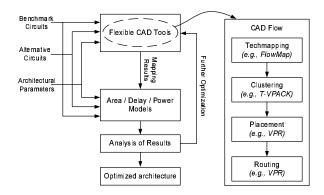

Figure 1.1: Fully Experimental Approach for New FPGA Architecture Design

parameters can be slow and computationally expensive, and limits the number of alternative architectures that can be considered. The consequence of this is the limited ability of FPGA companies to explore new structures that may lead to more efficient FPGAs.

Analytical models that describe some aspects of an architecture may complement the experimental approach to accelerate the architecture investigation. Analytical models relate parameters describing an FPGA architecture to area, delay, or power efficiency. These usually take the form of simple expressions, and thus searching for efficient architectures can be fast and the need for time-consuming experiments is reduced. The focus of this thesis is to accelerate the process of new FPGA architecture design by using analytical models. More specifically, this dissertation develops analytical models to describe area efficiency, delay efficiency and routability of FPGA architecture variants, as well as to investigate the capabilities and the limitations of the developed models.

## 1.2 FPGA Architecture Design

Since the accelerated FPGA architecture design process is central to this thesis, we present a summary of how new architectures are designed. We first present an overview of a typical experimental design approach. The major aspects of analytical models are presented next along with the discussion about how these models can accelerate architecture design process.

## 1.2.1 Experimental Approach

Figure 1.1 illustrates a typical experimental design flow. To design a new architecture using an experimental approach, FPGA architecture designers and/or FPGA vendors start with a set of prospective architecture.

tures. These architectures are characterized by the parameters related to the logic fabric that implements the circuit functions and the interconnect (routing) fabric that connects the elements. To evaluate each architecture, the architects collect benchmark circuits, make required modifications to the Computer-Aided Design (CAD) tools, and run the benchmark circuits through the CAD flow. The experimental results are evaluated empirically to fine-tune the architectural parameters for the next iterations. Such empirical evaluation demands a high number of experimental runs. There are several challenges associated with such a fully experimental approach:

- To properly exercise an architecture, many benchmarks are required. If the choice of benchmark

circuits is insufficient, it is possible to create an architecture that is tuned for specific circuits rather

than one suitable for a wide range of customers.

- 2. Each of the benchmark circuits must be mapped to all potential variants of the architecture under investigation; each mapping can take several hours using modern CAD tools. This slow progress limits the number of alternative architectures that can be considered, and thus limits the ability of FPGA companies to explore new structures that may lead to more efficient FPGAs.

- 3. Optimizing the architectures by repeated iterations through a complete CAD flow is time-consuming and computationally expensive. This is compounded by the fact that the designers often optimize the architectures on an ad-hoc basis since they do not have any detailed insight about the behavior of the architectures under investigation.

- 4. To investigate a set of new architectures, the architects may need to modify the existing CAD tools for each architecture, which is a time consuming process.

#### 1.2.2 Analytical Model-Based Approach

To accelerate the development of new FPGA architectures by addressing the challenges listed in Section 1.2.1, there have been recent efforts to develop a set of analytical models that relate the architectural parameters to each other, and to the evaluation matrix [41, 58, 59, 61, 70, 90, 104, 168].

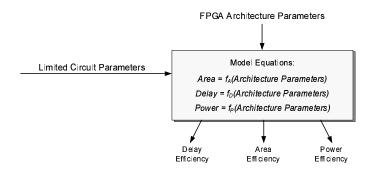

Figure 1.2 presents a conceptual overview of analytical models. The inputs to these models are FPGA architectural parameters. The architectural parameters may consist of logic fabric parameters as well as the routing fabric parameters. The inputs also include a limited number of circuit parameters, such as Rent

Figure 1.2: Analytical Models: Conceptual Overview

Figure 1.3: Analytical Model-Based Design of New FPGA Architectures

co-efficient<sup>1</sup>, and the number of two-input gates in the circuit. The models consist of a set of equations to relate these architectural parameters to the evaluation metrics, such as area of implementation, critical path delay, routability and power.

This thesis envisages that the analytical models to complement the traditional experimental approach, and accelerate the architectural investigation in three ways:

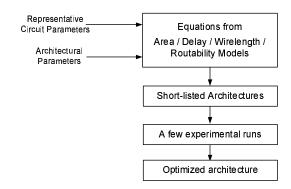

1. Understanding the relationships between architectural parameters enables *early-stage architecture development* [70] in which the analytical models can be used to quickly search the design space. This is illustrated in Figure 1.3, where the design space is first pruned using model equations. Once a promising region of architectures has been identified, a traditional experimental approach can be used to further fine-tune the short-listed architectures. This will significantly accelerate the FPGA architecture design process, and will allow the study of a wider range of architectures,

<sup>&</sup>lt;sup>1</sup>The Rent coefficient is a measure of the complexity of the interconnect pattern in a circuit, defined by the relationship between number of logic gates and required input/output pins [107].

Figure 1.4: Early Stage Architecture Investigation Using Analytical Models

since the designers do not require to develop or modify the CAD tools for each architecture under investigation.

- The FPGA architecture designers do not require benchmark circuits during early-stage architecture investigation. Instead, they may use a range of representative values for the limited number of circuit parameters that the model equations require.

- 3. The development of a body of theory describing the behavior of architectures will encourage an understanding of *why* certain architectures work well, and may eventually provide bounds on the capabilities and efficiencies of programmable logic. Such insights will also help the designers to better optimize the architectures using an experimental approach.

### 1.2.3 Example of Using Analytical Model Based Design Technique

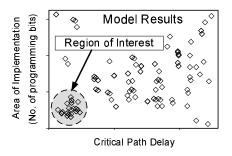

Figure 1.4 uses fictitious results to illustrate how analytical models can be used to optimize an FPGA architecture with respect to area and delay. Each data-point on this plot represents one particular architecture. Values on the horizontal axis and the vertical axis represent the critical path delay and the area of implementation respectively. For each architecture, designers can use analytical models to quickly estimate the values for area and delay. For the best area-delay trade-off, only the architectures on the bottom left corner of Figure 1.4 that are enclosed by a circle will be identified as the promising ones, and will be experimentally evaluated to identify the best architecture with respect to design goals.

## 1.3 Research Approach

This section presents the assumptions and the guiding principles used in this thesis to develop and validate the analytical models.

## 1.3.1 Assumptions

The models in this thesis assume a homogeneous clustered architecture. We also discuss the possibilities of extending our models to capture the behavior of heterogeneous architectures with embedded blocks. Furthermore, creating a complete analytical model that relates all architectural parameters is complex. To make our task tractable, we employ the approach described in [61, 104], which parallels the step-by-step CAD flow used in the FPGA design flow. For each CAD stage, we develop a stage model that isolates the impact of the CAD stage on quantities related to the area and delay of the final implementation. These stage models are then combined in an overall model. Following this construction, area and delay models are divided into five stages, namely (1) technology mapping stage, (2) packing stage, (3) placement stage, (4) routing stage and (5) physical design stage.

## 1.3.2 Guiding Principles

Three principles guide the development of the analytical models that we present in this dissertation:

- We endeavor to develop models by deriving relations analytically, without relying on curve-fitting

or experimental techniques. This ensures that the models capture the essence of programmable

logic, and is not limited to a particular CAD flow or tool suite.

- 2. We wish to derive models that are as independent of the circuit (to be implemented on FPGA) as possible. This makes the models of this dissertation different from estimation studies, in which the goals are to predict the area, speed, or power for given circuits. That being said, it is impossible to completely ignore the impact of specific circuits; hence a few circuit parameters are used by the models. All of the circuit parameters used in this thesis are available during early stage evaluation and do not require to run the circuit through any stage of an expensive CAD flow.

- 3. We attempt to balance complexity with accuracy. The simple model equations will provide more insight into architectural trade-offs than complex expressions. Such insights will help designers to effectively fine-tune an architecture under evaluation.

## 1.4 Research Contributions

To summarize the previous sections, the goal of this thesis is to develop the analytical models and to investigate the capabilities and limitations of such models. This dissertation presents three contributions

towards this goal:

- 1. We develop analytical models that relate key FPGA architectures to the post technology mapping and the post-clustering depth of the critical path as well as the post-placement wirelength. Parts of this work have been published in two conference proceedings [60, 168] and in a journal [61].

- 2. We develop an analytical model that relates key FPGA parameters to the fabric's routability, assuming that a modern one-step global/detailed router is used. This work has been published in a conference proceeding [58] and has been submitted for publication in a journal [57].

- 3. We investigate on the capabilities and the limitations of analytical models in answering design questions that the FPGA architects are typically interested in. This work has been published in a conference proceeding [59].

The next three subsections briefly discuss these three contributions. The details are presented as individual chapters in this dissertation.

## 1.4.1 Analytical Models Relating FPGA Architecture to Area and Delay

The first contribution of this thesis is *developing analytical models that relate key FPGA architecture* parameters to area and delay. More specifically, this thesis presents models for post-technology mapping depth, post-packing depth and post-placement wirelength. These models can be used in conjunction with the previously proposed models to quickly evaluate area and delay performances of an FPGA architecture.

The challenges tackled in developing these models were to balance simplicity with accuracy and to make the models independent of CAD tools and as independent of circuit parameters as possible. Chapter 3 presents the details on derivation and validation of these models.

#### 1.4.2 Analytical Model Relating FPGA Architecture to Routability

The second contribution of this dissertation is *developing an analytical model to relate FPGA logic and* routing fabric parameters to the consequent routability, when a modern single step global/detailed router is used to map the circuits on FPGAs. We define routability as the probability that all nets can be routed on a given FPGA device. Although a range of studies exist to estimate routability for both ASIC and FPGA devices [25, 35, 68, 99, 120, 152, 163], to our knowledge only one of them [25] is focused on relating FPGA architectural parameters to routability. The work of [25] models the FPGA routability for

the detailed stage of a two-stage router, where the routing paths for the detailed stage are pre-determined by the global router. The novelty of our work is that we model routability for a single-step global-detailed router, where many possible routing paths are simultaneously considered by the routing algorithm; such a single-step router is most commonly used for modern FPGAs.

The major challenge in deriving our routability model was to capture the effect of many possible routing paths that are not independent of each other. To tackle this challenge, we observe that our problem is related to the problem of estimating the reliability of a *multi-terminal stochastic network*. For given network constraints, the reliability of such a network is measured by the existence of at least one useful communication path between the terminals (out of many possible communication paths). This is analogous to our problem, which is to model the routability with given FPGA architecture constraints, while assuming that the routing of the nets may use any of the many possible available paths.

Finding an exact solution for the reliability of a stochastic network is *NP*-hard [16], and earlier studies use graph-theoric techniques to find bounds for the reliability of such a network [69, 142, 155, 156, 159]. In this dissertation, we also use graph-theoric techniques in modeling the upper-bound of routability for a single-step FPGA combined router.

Chapter 4 presents the details on derivation and validation of the routability model.

## 1.4.3 Accelerated FPGA Architecture Design: Capabilities and Limitations of Analytical Models

The final contribution of this dissertation *investigates the capabilities and limitations of analytical models*. This contribution has two parts, related to the use of analytical models in two stages of a design flow: (a) the very initial "back-of-the-envelope" stage and (b) the "parametric sweep" stage.

During the initial stage, architects wish to identify the architectural parameters that will affect density and performance of the resulting device. The first part of this contribution investigates whether analytical models can provide such insight.

The second part investigates whether the analytical models can be effectively used during parameteric sweep when the architectural parameters are swept to evaluate their effects on resulting area or delay. Since analytical models can quickly evaluate architectural choices, use of analytical models in this stage is expected to significantly reduce design time. The study of the second part is motivated by two issues that are related to analytical model based design techniques:

- 1. First, studies on analytical modeling consider a limited number of architectural parameters in isolation, and make important assumptions in deriving model equations. This issue motivates us to study if the analytical models, when combined together, can effectively answer the architecture questions that simultaneously evaluate a wide range of architectural parameters with respect to multiple evaluation metrics. The significance of this issue is emphasized by Yan et al. [191]. That work observes that experimental techniques proposed by separate studies make a range of assumptions when estimating evaluation metrics for an FPGA implementation. Yan et al. finds that when these studies are used simultaneously, resulting architecture conclusions are highly sensitive to the assumptions made by each study.

- 2. Secondly, to our knowledge, the analytical models previously presented are continuous in nature. The models therefore may not capture the effects of architecture choices when implementing the applications having "discrete effects". For instance, the Basic Logic Element (BLE) of an FPGA is characterized by the number of inputs that it can take. A BLE with six inputs can efficiently implement a multiplexer with four inputs and two select signals. However, in implementing such a multiplexer, a BLE with five inputs will be inefficient and a BLE with seven inputs will not offer additional benefits. The analytical models, due to their continuous nature, may not capture these effects. This may limit the usefulness of analytical models when designing an FPGA device that targets selected domain(s) of applications.

The second part of the final contribution of this thesis investigates the effects of these two issues. More specifically, we ask the following two architecture questions:

- 1. What are the optimal values of the architectural parameters for a general-purpose FPGA?

- 2. For an optimized application-specific FPGA architecture, what are the values of the architectural parameters?

To investigate the effectiveness of analytical models, we compare the model results with two experimental techniques: a sequential optimization technique and a Design of Experiments (DOE)-based experimentation technique. The first technique is often used for FPGA optimization while the second one is used in a wide range of domains including manufacturing and agriculture. The focus of this work is to determine if the model-based technique can identify similar (or better) architectural configurations,

with respect to area and/or delay, when compared with the experimental technique. If the conclusions are similar (or better), the model-based technique will be a valuable addition to the architecture design process, since it can evaluate a wide range of architectures in significantly shorter period of time.

The investigation results from this contribution will help the architecture designers in understanding the types of design questions that can be effectively answered by the analytical model-based techniques, as well as the limitations of the analytical model-based techniques in answering certain design questions.

Chapter 5 presents details on this investigation.

## 1.5 Thesis Organization

Chapter 2 provides background information on FPGA architecture and CAD flow, and presents earlier work related to our work. Chapter 3 presents our first contribution related to the development of analytical models for area and delay. The second contribution, development of routability model while considering a single-step combined router is presented in Chapter 4. Chapter 5 presents our third contribution, which is to investigate the capabilities and limitations of analytical models in designing new FPGA architectures. Finally, Chapter 6 summarizes the contributions, concludes this thesis and presents the short-term and long-term avenues for future work.

## Chapter 2

## **Background and Related Work**

This chapter presents background of this dissertation and puts this dissertation into the context of earlier work. In Section 2.1 and 2.2 respectively, we review the architecture of typical island-style FPGAs and the CAD flow used to implement circuits on FPGAs. In Section 2.3.1, we review experimental techniques that can be used for FPGA design space exploration. Section 2.3.2 presents the analytical models that have been proposed for ASIC domain, and are relevant to the work presented in this dissertation. In Section 2.3.3, we present the analytical models proposed by other researchers for the FPGA domain. The objective of these models is to evaluate FPGA architectures without going through an experimental flow. Section 2.3.4 presents previously published techniques that *experimentally* estimate the area, delay and routability for FPGA implementation. Finally, Section 2.4 summarizes this chapter.

## 2.1 Review of FPGA Architecture

### 2.1.1 Island-style FPGA Architecture

The *Island-style* FPGA architecture [21] is the most commonly used architecture both in academia and industry. This architecture has been proven to scale with Moore's Law [40] and has been used by leading FPGA vendors, such as Altera and Xilinx. In this thesis, our models are developed for and validated for island-style architectures. Figure 2.1 presents a typical island-style FPGA architecture. The architecture consists of three fundamental components: configurable logic resources, a configurable interconnect fabric, and I/O resources [21]. FPGA architecture parameters that we investigate are associated with these components and are presented in Table 2.1.

Figure 2.1: Typical Island-Style FPGA Architecture

## 2.1.1.1 Configurable Logic Resources

Configurable logic resources of an FPGA consist of Look-Up Tables (LUTs), Basic Logic Elements (BLEs) and clusters. LUTs are characterized by the number of inputs *K*. Each *K*-LUT is capable of implementing a logic function having up to *K* inputs and a single output. A *K*-LUT can be configured to implement a specific function by storing the corresponding truth table in the LUT's configuration memory bits. Together with a flip-flop at its output, a LUT forms a *BLE*.

Multiple BLEs are grouped into *clusters*. Clusters are characterized by the number of BLEs that they contain (N). Figure 2.1 shows a cluster with N=2. The BLEs within a cluster are connected by