# FPGA Emulation for Critical-Path Coverage Analysis

by

#### Kyle Balston

B.A.Sc., Simon Fraser University, 2010

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### **Master of Applied Science**

in

## THE FACULTY OF GRADUATE STUDIES (Electrical and Computer Engineering)

The University Of British Columbia (Vancouver)

October 2012

© Kyle Balston, 2012

# Abstract

A major task in post-silicon validation is timing validation: it can be incredibly difficult to ensure a new chip meets timing goals. Post-silicon validation is the first opportunity to check timing with real silicon under actual operating conditions and workloads. However, post-silicon tests suffer from low observability, making it difficult to properly quantify test quality for the long-running random and directed system-level tests that are typical in post-silicon. In this thesis, we propose a technique for measuring the quality of long-running system-level tests used for timing coverage through the use of on-chip path monitors to be used with FPGA emulation. We demonstrate our technique on a non-trivial SoC, measuring the coverage of 2048 paths (selected as most critical by static timing analysis) achieved by some pre-silicon system-level tests, a number of well-known benchmarks, booting Linux, and executing randomly generated programs. The results show that the technique is feasible, with area and timing overheads acceptable for pre-silicon FPGA emulation.

# Preface

Preliminary work related to this thesis has been published in a conference paper and a journal paper. The work itself will be published as an invited conference paper. The first paper, Post-Silicon Code Coverage Evaluation with Reduced Area Overhead for Functional Verification of SoC, was published as [33]. In this paper we manually added on-chip monitors to extract statement and branch coverage information from a uniprocessor LEON3 system running on a Xilinx FPGA. Mehdi Karimibiuki implemented the coverage monitors as well as designed and carried out the experiments with the help of Kyle Balston. The paper was written collaboratively with the help of Dr. Alan Hu and Dr. André Ivanov.

The second paper, Post-Silicon Code Coverage for Multiprocessor Systemon-Chip Designs, was published as [6]. In this paper we extended [33] to target a multiprocessor LEON3 system and collected data showing how statement and branch coverage was achieved with respected to processor cycle count. For this paper, Kyle Balston took the lead on the design and execution of the experiments. The paper was written collaboratively by Kyle Balston and Mehdi Karimibiuki with the help of Dr. Alan Hu, Dr. André Ivanov and Dr. Steve Wilton.

The work that forms the basis of this thesis will be presented in a third paper, Emulation in Post-Silicon Validation: It's Not Just for Functionality Anymore [5]. Kyle Balston performed the research, data collection, data analysis, and writing under the supervision of Dr. Steve Wilton and Dr. Alan Hu with industry guidance from Amir Nahir of IBM.

# **Table of Contents**

| Ab  | ostrac  | etii                   |

|-----|---------|------------------------|

| Pr  | eface   | iii                    |

| Ta  | ble of  | f Contents             |

| Lis | st of [ | Tables                 |

| Lis | st of l | Figures                |

| Gl  | ossar   | y                      |

| 1   | Intr    | oduction               |

|     | 1.1     | Motivation             |

|     | 1.2     | Historic Design Errors |

|     | 1.3     | ASIC Design Flow       |

|   |     | 1.3.1                                                                            | Differences Between Pre- and Post-Silicon Validation  | 5                                                                      |

|---|-----|----------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------|

|   |     | 1.3.2                                                                            | Emulation — Bridging Pre- and Post-Silicon Validation | 7                                                                      |

|   |     | 1.3.3                                                                            | FPGA Devices                                          | 8                                                                      |

|   |     | 1.3.4                                                                            | FPGA-based Emulation                                  | 8                                                                      |

|   |     | 1.3.5                                                                            | Conventional Emulation Goals                          | 10                                                                     |

|   | 1.4 | Resear                                                                           | rch Objective and Contributions                       | 11                                                                     |

|   | 1.5 | Resear                                                                           | rch Approach                                          | 12                                                                     |

|   | 1.6 | Thesis                                                                           | Organization                                          | 13                                                                     |

| 2 | Bac | kgroun                                                                           | d and Related Work                                    | 14                                                                     |

|   |     |                                                                                  |                                                       |                                                                        |

|   | 2.1 | ASIC                                                                             | Design Flow                                           | 14                                                                     |

|   | 2.1 | ASIC 2.1.1                                                                       | Design Flow                                           |                                                                        |

|   | 2.1 |                                                                                  |                                                       | 15                                                                     |

|   | 2.1 | 2.1.1                                                                            | Stages of ASIC Design                                 | 15<br>18                                                               |

|   | 2.1 | 2.1.1<br>2.1.2                                                                   | Stages of ASIC Design       Pre-Silicon Validation    | 15<br>18<br>22                                                         |

|   | 2.1 | <ul><li>2.1.1</li><li>2.1.2</li><li>2.1.3</li><li>2.1.4</li></ul>                | Stages of ASIC Design                                 | 15<br>18<br>22<br>23                                                   |

|   |     | <ul><li>2.1.1</li><li>2.1.2</li><li>2.1.3</li><li>2.1.4</li></ul>                | Stages of ASIC Design                                 | <ol> <li>15</li> <li>18</li> <li>22</li> <li>23</li> <li>26</li> </ol> |

|   |     | <ul><li>2.1.1</li><li>2.1.2</li><li>2.1.3</li><li>2.1.4</li><li>Pre-Si</li></ul> | Stages of ASIC Design                                 | <ol> <li>15</li> <li>18</li> <li>22</li> <li>23</li> <li>26</li> </ol> |

|   |      | 2.3.1    | Related Work — On-Chip Coverage Monitors                    | 30 |

|---|------|----------|-------------------------------------------------------------|----|

|   | 2.4  | Timing   | Validation                                                  | 31 |

| 3 | Prop | oosed Fl | ow                                                          | 34 |

|   | 3.1  | Proble   | m Statement                                                 | 35 |

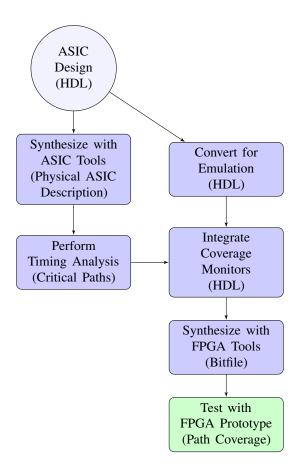

|   | 3.2  | Overal   | l Flow                                                      | 36 |

|   | 3.3  | Instrun  | nentation                                                   | 38 |

|   | 3.4  | Chapte   | r Summary                                                   | 42 |

| 4 | Imp  | lementa  | tion                                                        | 47 |

|   | 4.1  | Approx   | ximated Flow                                                | 47 |

|   |      | 4.1.1    | Automated Integration of Coverage Monitors Using Xilinx     |    |

|   |      |          | Description Language (XDL)                                  | 49 |

|   | 4.2  | XDL to   | VHSIC hardware description language (VHDL) Converter        | 52 |

|   |      | 4.2.1    | Automatically Generating Java Objects from Xilinx Libraries | 54 |

|   |      | 4.2.2    | XDL Instances Requiring No Changes                          | 55 |

|   |      | 4.2.3    | XDL Instances Requiring Simple Attribute Name Translation   | 55 |

|   |      | 4.2.4    | XDL Instances Requiring Fixed Locations                     | 55 |

|   |      | 4.2.5    | XDL Instances with Ports Offset Compared to VHDL In-        |    |

|   |      |          | stances                                                     | 57 |

|   |     | 4.2.6 X    | DL Instances Composed of Upper and Lower VHDL In- |    |

|---|-----|------------|---------------------------------------------------|----|

|   |     | st         | ances                                             | 57 |

|   |     | 4.2.7 X    | DL Instances Composed of Many VHDL Instances      | 58 |

|   | 4.3 | Coverage   | Monitor Instrumentation                           | 58 |

|   | 4.4 | Reading (  | Coverage Information Off-Chip                     | 60 |

|   | 4.5 | Chapter S  | ummary                                            | 61 |

| 5 | Res | ults       |                                                   | 62 |

|   | 5.1 | Test Setu  | % Benchmarks                                      | 62 |

|   | 5.2 | Results .  |                                                   | 65 |

|   |     | 5.2.1 C    | overage                                           | 65 |

|   |     | 5.2.2 A    | rea Overhead                                      | 70 |

|   |     | 5.2.3 Fi   | requency Overhead                                 | 73 |

|   | 5.3 | Chapter S  | ummary                                            | 74 |

| 6 | Con | clusion .  |                                                   | 75 |

|   | 6.1 | Dissertati | on Summary                                        | 75 |

|   | 6.2 | Limitation | ns                                                | 76 |

|   |     | 6.2.1 R    | eliance on XDL                                    | 76 |

|   |     | 6.2.2 To   | oolflow                                           | 77 |

| Bibliog | raphy  |                    | 81 |

|---------|--------|--------------------|----|

| 6.4     | Public | Distribution       | 80 |

| 6.3     | Future | Work               | 79 |

|         | 6.2.5  | Area Optimizations | 79 |

|         | 6.2.4  | Non-Determinism    | 79 |

|         | 6.2.3  | Register Retiming  | 78 |

# **List of Tables**

| Table 4.1 | Characteristics of XDL Instances                  | 56 |

|-----------|---------------------------------------------------|----|

| Table 5.1 | LEON3 Configuration                               | 63 |

| Table 5.2 | IP Blocks under Test                              | 65 |

| Table 5.3 | Post-Silicon Validation Tests Used in Experiments | 66 |

| Table 5.4 | Path Coverage Results (2048 Most Critical Paths)  | 70 |

| Table 5.5 | Coverage Achieved by One Test but not by Another  | 71 |

| Table 5.6 | Area Overhead to Monitor 2048 Critical Paths      | 73 |

| Table 5.7 | Frequency Overhead for 2048 Monitors              | 74 |

# **List of Figures**

| Figure 1.1 | ASIC design flow                                                 | 3  |

|------------|------------------------------------------------------------------|----|

| Figure 1.2 | Mask production cost by process technology                       | 6  |

| Figure 1.3 | Ease of debug and performance comparison of validation tech-     |    |

|            | niques                                                           | 7  |

| Figure 2.1 | ASIC design flow                                                 | 16 |

| Figure 3.1 | Toolflow for adding path coverage monitors to the FPGA pro-      |    |

|            | totype of an ASIC design. Each stage's output is shown in        |    |

|            | parentheses                                                      | 38 |

| Figure 3.2 | Example of a critical path, a), instrumented to monitor cov-     |    |

|            | erage by b) for bolded path $f$ initiated by a rising or falling |    |

|            | transition on input <i>A</i>                                     | 43 |

| Figure 3.3 | Example of a critical path, a), instrumented to monitor cover-       |    |

|------------|----------------------------------------------------------------------|----|

|            | age by b) for bolded path $f$ initiated by a rising transition on    |    |

|            | input <i>A</i>                                                       | 44 |

| Figure 3.4 | Example of a critical path, a), instrumented to monitor cover-       |    |

|            | age by b) for bolded path $f$ initiated by a falling transition on   |    |

|            | input <i>A</i>                                                       | 45 |

| Figure 3.5 | Example of a critical path, a), instrumented to monitor cover-       |    |

|            | age by b) for bolded path $f$ through input $A$ with additional cir- |    |

|            | cuitry allowing for error injection whenever coverage is achieved.   | 46 |

| Figure 4.1 | Toolflow used in this thesis to automatically add path coverage      |    |

|            | monitors to an FPGA design. Each stage's output is shown in          |    |

|            | parentheses.                                                         | 50 |

| Figure 5.1 | LEON3 SoC running on a Virtex-5 FPGA shown booting Linux.            | 64 |

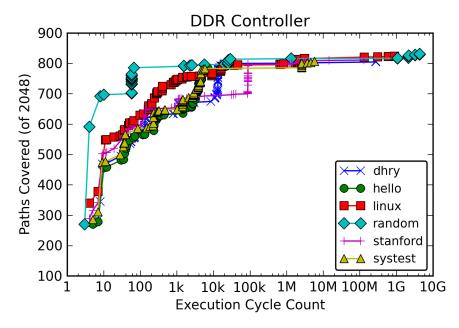

| Figure 5.2 | Coverage achieved over time for the DDR controller (ddr2spa).        | 68 |

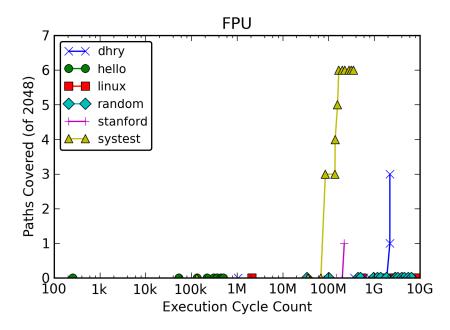

| Figure 5.3 | Coverage achieved over time for the floating-point unit (grfpwx).    | 68 |

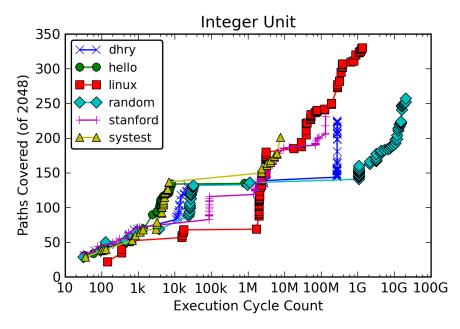

| Figure 5.4 | Coverage achieved over time for the integer unit (iu3)               | 69 |

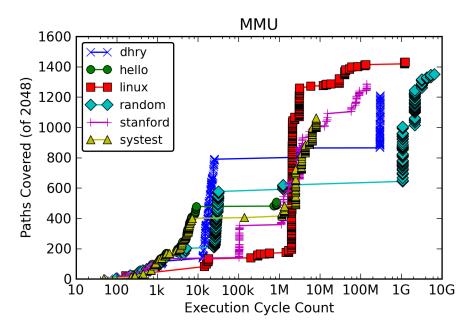

| Figure 5.5 | Coverage achieved over time for the memory management unit           |    |

|            | (mmu)                                                                | 69 |

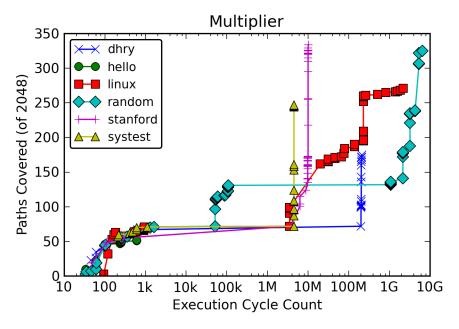

| Figure 5.6 | Coverage achieved over time for the multiplier (mul32)               | 72 |

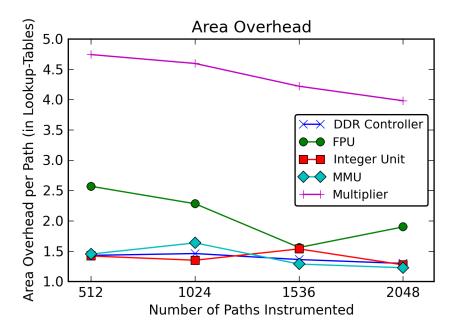

| Figure 5.7 | Area overhead per path shown as the number of targeted paths |    |  |  |  |

|------------|--------------------------------------------------------------|----|--|--|--|

|            | increases.                                                   | 72 |  |  |  |

# Glossary

| ASIC | Application-Specific Integrated Circuit |

|------|-----------------------------------------|

| BRAM | Block Ram                               |

| DRC  | Design Rule Check                       |

| DSP  | Digital Signal Processor                |

| FPGA | Field-Programmable Gate Array           |

| IC   | Integrated Circuit                      |

| LUT  | Lookup Table                            |

| NCD  | Native Circuit Description              |

| SoC  | System-on-Chip                          |

| SSTA | Statistical Static Timing Analysis      |

| STA  | Static Timing Analysis                  |

|      |                                         |

- **VHDL** VHSIC hardware description language

- **XDL** Xilinx Description Language

# **Chapter 1**

# Introduction

### 1.1 Motivation

Integrated Circuit (IC) complexity continues to increase as predicted by Moore's Law [52], allowing chip designers to deliver more functionality on a given die, at lower manufacturing cost and at smaller power windows. However, it also makes it increasingly difficult to detect and fix design errors simply due to the sheer number of transistors on a single chip. Today, modern chips contain upwards of 3 billion transistors [58], which together can form an entire computing system, often called a System-on-Chip (SoC) design. Before being fabricated, these multibillion transistor SoC designs are verified to be correct in model-based verification without a physical chip, known as pre-silicon verification, and after fabrication, with a release-candidate physical chip in post-silicon verification. Together these two styles of testing dictate when a chip is ready to go to manufacturing, and into the hands of consumers. However, proper testing of these chips is imperative as even a single error escaping to manufacturing can cost a company millions in product recalls and irreparably tarnish a company's reputation.

### **1.2 Historic Design Errors**

One of the most well-known examples of a design error that made it into a consumer processor is the infamous FDIV bug in Intel's P5 microarchitecture [57]. The bug caused certain floating-point operations and operand combinations to produce incorrect results (e.g., the result returned for  $\frac{4195835}{315727}$  was incorrect beyond four digits). Unfortunately, the bug was not discovered until the processor was in widespread use and only exhibited errors under rare conditions (approximately 1 in 9 billion operand pairs would result in an error at double-precision [14]). Because of this, Intel was initially hesitant to issue product recalls until it became highly publicized. In total, this cost Intel an estimated \$475 million [68]. However the damage to their reputation was also substantial (particularly among the scientific computing community). More recently, Intel's 2011 recall of the Cougar Point chipset due to an issue with its SATA ports cost Intel an estimated \$700 million [20]. AMD, another large semiconductor company, is not without its own share of issues. In 2007, an error in the translation lookaside buffer (TLB) of the B2 stepping of their Barcelona processors could lead to system lockup [16], until AMD disabled it altogether in a BIOS update, causing some workloads to experience a 5-20% performance penalty. These design errors escaped to production, costing many times more than if they were detected during pre- or post-silicon validation.

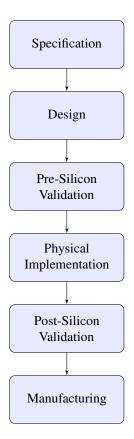

Figure 1.1: ASIC design flow.

### **1.3 ASIC Design Flow**

To illustrate how integrated circuit designers verify their designs and identify design errors, this section gives a high-level overview of the Application-Specific Integrated Circuit (ASIC) design and verification process. A more in-depth analysis of the ASIC flow can be found in Section 2.1.

An ASIC design typically starts with specifying the functional and nonfunctional properties of the design, shown as 'Specification' in Figure 2.1. Note that, at this stage, a module's underlying implementation details are not specified.

Specification is often followed by the implementation stage, shown as 'Design' in Figure 2.1. In the design stage, designers write code (usually VHDL or Verilog) to implement the design or module while conforming to the specification detailed in the previous stage.

Throughout the implementation process, pre-silicon validation is performed at the block level. Once the design has been fully implemented, top-level presilicon validation is started, shown as 'Pre-Silicon Validation' in Figure 2.1. Ideally, all design errors would be discovered at or before this stage, however this is often impossible to accomplish. Pre-silicon validation makes use of simulation, static timing analysis, formal verification, and emulation to verify the correctness of the design. Pre-silicon simulation is performed throughout the ASIC flow: simulating the hardware description language directly (RTL simulation), after synthesis (gate simulation) and after place and route (timing simulation). In general, RTLlevel simulation is used more extensively than other forms of simulation because it runs quicker and can more easily determine the root cause of detected design errors. However, lower level simulations such as timing simulation are also common because they can more accurately model the system in exchange for reduced throughput. Formal verification techniques can be used to mathematically prove a property of a design, however these techniques suffer from scalability problems for large designs. Emulation uses prefabricated programmable hardware devices such as Field-Programmable Gate Arrays (FPGAs) to act as a stand-in for the fabricated chip. These devices run orders of magnitude faster than simulation but do not provide full visibility of internal signals [28, 46]. These pre-silicon techniques are further detailed in Section 2.1.2.

The physical implementation stage follows, where the placement and routing of a design is determined. This physical description is then given to a foundry, which produces a number of silicon prototypes.

Post-silicon validation tests the prototype chips at normal operating speed under expected operating conditions. Unlike simulation, post-silicon techniques generally suffer from poor visibility into the system state during execution. Since chips which are physically larger are more expensive to fabricate, on-chip monitoring logic must be minimized in order to reduce cost. Often it takes more than one silicon iteration to produce a production-ready chip.

Once the chip passes post-silicon validation, it is ready to be sent to manufacturing for mass production. Each produced chip is subject to manufacturing tests to ensure each chip is functional and speed binning to categorize produced chips by their maximum operating frequency. Manufacturing tests check for fabrication issues related to specific dies (e.g., manufacturing defects) and not systemic issues (e.g., design errors).

#### **1.3.1** Differences Between Pre- and Post-Silicon Validation

In general, pre-silicon techniques are slow and/or approximate but have high observability into the system state. Conversely, post-silicon techniques have very

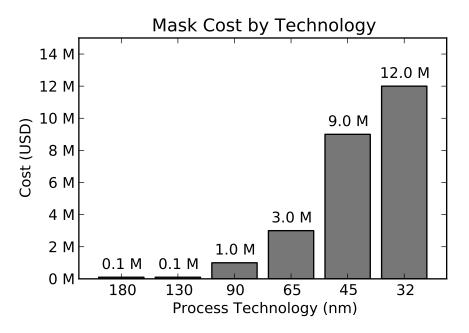

Figure 1.2: Mask production cost by process technology [29].

low visibility into the system state but run at or near the design's native operating frequency.

Unfortunately, relying on post-silicon validation to find bugs is expensive due to increasing mask development costs. As shown in Figure 1.2, mask costs now represent a significant cost to IC development. Worse still, typical fabrication processes can easily take four to eight weeks to complete [44], slowing the throughput of post-silicon validation and increasing time to market. To mitigate these costs, it is important to perform as much validation as possible in pre-silicon (before fabrication) and to maximize the number of design errors found with each iteration of the fabricated chip. Commercial tools are available to accelerate this

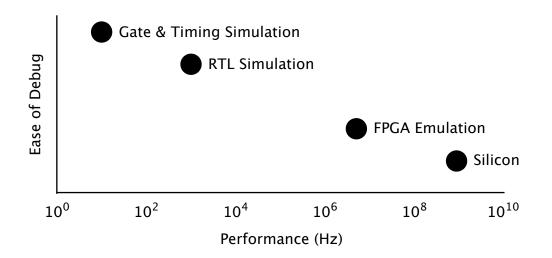

**Figure 1.3:** Ease of debug and performance comparison of validation techniques (performance data from [23]).

process [3, 62, 71].

#### 1.3.2 Emulation — Bridging Pre- and Post-Silicon Validation

Emulation has become an important technology for the validation of large ICs. Although designers make extensive use of software simulation when verifying their designs, simulation runs approximately eight orders of magnitude slower than actual silicon [53]. At this speed it would take more than three years to simulate just one second of silicon execution. For example, during pre-silicon validation of the Pentium 4 processor, Intel found that in a two year period between initial RTL system-level integration and A-step tapeout, their compute farm (which by the end of the project was several thousand nodes large) had accumulated only 230 billion simulation cycles [9], approximately two minutes of execution on a 1.5 GHz processor.

#### **1.3.3 FPGA Devices**

FPGAs are ICs that have been fabricated to contain flexible programmable logic. This programmable logic allows FPGAs to implement arbitrary logic, albeit at a slower speed and higher unit cost (at high volume production) than can be provided by a fixed-function IC. In contrast, they do not require lengthy fabrication turnaround times or expensive mask costs, making them ideal for low-volume applications. As fixed-function ASIC validation has become more costly, one such low-volume application for FPGAs has emerged: FPGA-based emulation of ASICs for validation and prototyping purposes.

#### **1.3.4 FPGA-based Emulation**

FPGA-based emulation technology allows for much higher validation coverage in pre-silicon testing by allowing designers to re-target their designs to one or more FPGAs and 'execute' the design at orders of magnitude faster than simulation. For example, Intel's Atom processor (composed of 47.2 million transistors) was mapped to a single FPGA running at 50 MHz [66], and their performance-oriented i7 Nehalem processor (transistor count ranges from 177 to 1170 million transistors [17]) was mapped to five FPGAs running at 520 kHz [60]. While slower than the fixed-function chip, these speeds are fast enough to perform common validation tasks such as booting an operating system — tasks which are infeasible in simula-

tion. In fact, even at 520 kHz, all 230 billion simulation cycles accumulated before tapeout for the Pentium 4 processor could be covered in just over five days by a single FPGA emulation system.

Because the underlying implementation is so different between the integrated circuit and the FPGA-based emulation, emulation typically captures only the functional behaviour of the design. Due to this difference, FPGA emulation is not typically appropriate for designs which make heavy use of asynchronous or analog circuits. When designers re-map their digital circuits to one or more FP-GAs, they must compile their designs using the FPGA vendor's tools, which may make different optimization decisions than the ASIC synthesis tools. In addition, the pre-fabricated nature of an FPGA means that certain structures (e.g., memories, multipliers) may be implemented very differently on an FPGA than on an ASIC. Furthermore, the physical implementation of a Lookup Table (LUT) is radically different from a standard cell or full-custom gate; this means important properties like timing, critical paths, robustness to process and environmental variation, noise margins, etc. are all different in the emulated design.

An obvious example of such a property is timing. Designers often need to know the maximum operating frequency of the chip and if there is any way of increasing performance by modifying the frequency or shortening critical paths that limit speed improvements. Designers regularly employ pre-fabrication timing verification techniques such as Static Timing Analysis (STA) and Statistical Static Timing Analysis (SSTA). These techniques provide valuable information regarding potential timing problems in a design, but are only approximate — the paths predicted to be critical do not correlate perfectly with the true critical paths [7], hence the need for expensive (but also more accurate) post-silicon timing validation [51].

Many of the aforementioned physical properties (e.g., tolerance to voltage and temperature variations, accelerated aging, etc.) can be tested via timing tests, by varying some parameter and measuring at what frequencies the chip still behaves correctly (e.g., the classic 'shmoo' plot obtained by running the chip at different voltages and measuring what frequencies give correct behaviour). This indicates that post-silicon tests related to timing are useful for covering many types of properties that are not well tested in pre-silicon.

#### **1.3.5** Conventional Emulation Goals

Traditionally, emulation has only been used for validation of functional behaviour; the conventional wisdom dictates that emulation cannot help with validating other properties, particularly properties which are the focus of post-silicon validation such as timing. In this dissertation, we show otherwise — emulation *can* be used as an important tool to assist validation of more than just functional behaviour. In particular, we focus on timing validation and the task of quantifying the *critical-path coverage* of a validation plan. We define the critical-path coverage of a validation plan as the proportion of the critical and near-critical circuit paths that are exercised during the execution of the plan. As will be discussed in Section 3.2, measuring this quantity is essential, both to guide the creation of suitable post-silicon validation tests, and to determine how thoroughly a design has been validated before it is put into high-volume production. Our technique involves adding a small amount of instrumentation (*coverage monitors*) in strategic locations. Rather than add monitors to the actual silicon (which would have significant area overhead), we add them to an FPGA-based emulation of the design. By measuring coverage during emulation, we can obtain a metric for the timing coverage of our verification plan when applied to the actual chip during post-silicon validation. A key challenge is that the critical paths of the original ASIC will likely be different than the critical paths of the emulated version.

Note that our approach does not replace post-silicon timing validation, but instead complements it by measuring how effectively it is being done. Nor are we performing timing analysis of FPGAs themselves [43], which would give little insight into the timing of the ASIC. Instead, we are measuring the quality of the post-silicon timing *tests*, by using FPGA emulation.

### **1.4 Research Objective and Contributions**

To summarize the previous section, the goal of this research is to *show how FPGA-based emulation can be used to measure non-functional properties of integrated circuits, concentrating on critical-path delay coverage.* The main contributions of this dissertation are as follows:

1. We propose a general toolflow for using FPGA-based emulation to support

validation of post-silicon properties.

- 2. We instantiate a specific instance of this flow: using emulation to measure critical-path coverage of post-silicon validation tests.

- We demonstrate this instance on a complex SoC using common post-silicon validation tests, including booting Linux and running long random instruction streams.

- 4. We report critical-path coverage data for these post-silicon validation tests.

- 5. We describe the academic tools developed to implement this methodology and release them for use by the research community.

### **1.5 Research Approach**

To address the above objectives, we designed and implemented a system to automatically instrument the open-source LEON3 SoC design [2] with path coverage monitors for the paths deemed most critical by the Xilinx Timing Analyzer [73]. We ran various typical pre- and post-silicon tests against the SoC, and recorded the coverage reported by our coverage monitors.

Due to the limited interoperability of the Xilinx toolflow with non-standard processes (e.g., many of the Xilinx tools are not re-entrant so a partially placedand-routed design cannot be integrated back into the toolflow), we developed a tool to generate a structural VHDL description from a placed-and-routed Xilinx design, allowing us to easily instrument paths described structurally by the STA tool for coverage. We integrated our coverage monitors as VHDL into this description and resynthesized the design with the Xilinx tools, allowing us to easily monitor signals specified by the Xilinx Timing Analyzer as timing critical. The tool allows for integration of arbitrary VHDL code alongside a structural description of the original design.

### **1.6 Thesis Organization**

The remainder of this thesis is organized as follows. Chapter 2 presents an overview of background topics and related work. Chapter 3 describes the ideal coverage monitor instrumentation flow and gives an example of a coverage monitor targeting a critical path. Chapter 4 presents the toolflow used in this dissertation's research to approximate the ideal flow shown in Chapter 3 and details the XDL to VHDL converter developed to allow automatic integration of coverage monitors. Chapter 5 demonstrates the feasibility of coverage monitors in emulation systems by performing critical-path coverage instrumentation on a LEON3 SoC and reporting coverage achieved for common post-silicon tests. Chapter 6 concludes the dissertation by providing a summary and discusses limitations for the toolflow presented as well as future work that could be used to address these limitations.

# Chapter 2

# **Background and Related Work**

In this chapter, we first give a high level overview of the ASIC design flow in Section 2.1, followed by a discussion of pre- and post-silicon coverage metrics in Sections 2.2 and 2.3, respectively. Section 2.4 describes how the work done for this dissertation differs from previous work.

### 2.1 ASIC Design Flow

As discussed in Section 1.2, design errors in ASIC designs can be very costly. As such, verification is central to the ASIC design process; before a chip is sent to the foundry, it is imperative that it has been tested as thoroughly as possible. Ideally, the first fabricated iteration of the chip, 'first silicon', would be bug-free and be ready to send to manufacturing. Unfortunately, increasing chip complexity has caused the number of first silicon successes to decline from 39% in 2002, to 33% in 2004 and 28% in 2007 [69]. Estimates for the total amount of design time and resources spent on verification vary (55% [69], 80% [39], 90% [59]), but they all agree that verification (pre- and post-) is critical to the ASIC design flow and important for reducing the number of silicon iterations required before sending a design to manufacturing.

#### 2.1.1 Stages of ASIC Design

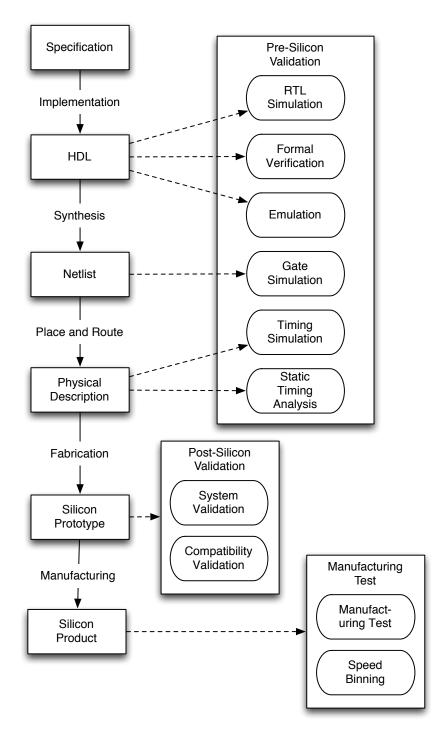

This section gives a high-level overview of the ASIC design process detailed in Figure 2.1. Each stage of the design process is shown on the left in bold, followed by its description.

- **Specification** details the functional and non-functional properties of the design. It should be at sufficient granularity to 'pass' or 'fail' a given HDL implementation without dictating how it must be implemented. For example, a specification could state that on every clock cycle, a module will take an A and B input, and output C, which is A + B.

- **HDL** is a VHDL, Verilog or other hardware description of the specification. This stage is responsible for transforming the specification into a design by converting it to RTL code. It details how the specification is functionally implemented (but not the underlying transistor technology). For example, it could describe C = A + B as a simple ripple-carry adder, or a more complicated carry-lookahead adder.

Figure 2.1: ASIC design flow.

- **Netlist** files comprise the logic connections between a set of gates defined by a standard cell library. Synthesis converts the HDL code into these gates while preserving the functional behaviour of the RTL and continuing to satisfy design constraints.

- **Physical Description** is usually divided into two main stages: placement and routing. The placer determines the placement of standard cells, described by the netlist, onto a region representing the ASIC. The router determines a set of connections between these placed cells. The resulting layout will be validated with a Design Rule Check (DRC) and other physical verification checks to ensure it conforms to the foundry's design rules.

- Pre-Silicon Validation ensures the design is functionally correct using a combination of simulation, formal verification and emulation-based techniques. Pre-silicon validation is discussed in more detail in Section 2.1.2.

- Silicon Prototype chips are received from the foundry for use with post-silicon validation. Fabrication is an expensive and time-consuming process, costing upwards of \$10 million USD for a modern 32 nm process (as shown in Figure 1.2), making it imperative that the number of silicon iterations be minimized.

- **Post-Silicon Validation** involves validating a hardware design after fabrication, but before large-scale manufacturing, with a physical chip. Post-silicon validation generally has low visibility into system signals. However, it runs at

full chip execution speed and can validate all aspects of the design (since the chip is a release-candidate). Post-silicon validation is discussed in more detail in Section 2.1.3.

**Silicon Product** is the final product that will be shipped to end-users.

**Manufacturing Test** includes conventional manufacturing test, which checks for defects caused by the manufacturing process; and speed binning, which categorizes chips based on their performance characteristics. These two types of manufacturing test are described in further detail in Section 2.1.4.

#### 2.1.2 **Pre-Silicon Validation**

Pre-silicon validation is the problem of finding design errors without using a physical chip. It forms the backbone of IC validation and is responsible for detecting most design bugs. The most common forms of pre-silicon testing are simulation, formal verification and emulation.

#### Simulation

Simulation is employed to validate all but the simplest designs (and usually even those too). It involves supplying a series of test vectors, often generated from constrained random parameters, to a testbench that will verify functional correctness of a design (or a design's modules) compared to the designer's expected output. It allows for complete visibility into all signals of the design and can detect a deviation from expected top-level ports and internal signal values the instant they occur. Complete visibility allows for full signal traces leading up to any deviation. These traces make diagnosing and fixing bugs much easier than it would be otherwise (and indeed, this visibility is a primary advantage of pre-silicon techniques over post-silicon). However, simulation is very slow compared to real-chip execution, requiring tests to be very short and therefore not representative of real-world use. Furthermore, simulation models are usually slow and/or approximate for complex electrical interactions and timing behaviours.

There are three main types of simulation: RTL, gate, and timing. RTL simulation of the design ensures the implemented design functionally conforms to the specification by simulating the HDL written by designers. It allows for full visibility into system signals during execution but runs much slower than real-chip execution and does not take into account detailed implementation information (such as timing). Gate simulation ensures that the implementation inferred by the synthesis tools still conforms to the specification, and is functionally equivalent to the functional implementation. It allows for full visibility into system signals during execution (however these gate-level signals can be non-trivial to map back to the original RTL signals) but runs slower than RTL simulation. Timing simulation ensures that the placed-and-routed implementation of the design conforms to the specification under realistic timing conditions. It allows for full visibility into system signals during execution (however as in gate-level simulation, these signals can be non-trivial to map back to the original RTL signals). Timing simulations runs slower than gate-level simulation because it includes additional timing, placement and routing information. In all cases, these techniques are only approximate

and may not match the behaviour seen on the physical chip.

Coverage, as will be discussed in Section 2.2, is integral to simulation. Achieving coverage closure, the point at which 100% of one's coverage goals<sup>1</sup> have been met, is one of the most important milestones for the pre-silicon verification team [1]. This exemplifies how coverage-driven verification is already understood to be an important part of silicon validation.

#### **Formal Verification**

Formal verification is the process of validating a design by ensuring design intent (expressed through specifications) is preserved through to implementation [19, 22, 34, 54]. Once a design or block is successfully verified (as in [32, 37]), it is mathematically guaranteed to satisfy the validated properties. Before a complicated design (or perhaps a module in the design) is formally verified, it has to be converted into a simpler, verifiable format which is representative of the unit as a whole. However, even when the design is converted to this verifiable format, formal verification still often suffers from capacity limits. Furthermore, there are often questions about the completeness of the specifications and accuracy of the constraints.

<sup>&</sup>lt;sup>1</sup>This is not necessarily the same as reaching 100% coverage which, depending on the circuit design and coverage metric, may be impossible.

#### **Static Timing Analysis**

Static Timing Analysis (STA) is a method for computing the worst- and best-case timing performance of a circuit without performing rigorous circuit simulation [27, 36, 40, 48, 50]. STA relies on conservative delay modelling of gates and interconnect valid for a range of operating conditions and die variation. It allows the analysis to scale with the size of the circuit, however it relies heavily of the accuracy of the delay models and cannot determine if detected paths are false (i.e., it cannot determine if some of the detected paths cannot occur during circuit operation) [10].

#### Emulation

As pre- and post-silicon validation costs continue to increase [30, 35, 56], emulation has steadily increased in popularity. In modern IC development, it is common for a design to be converted to run on an FPGA for testing and prototyping purposes (e.g., [24, 47, 60, 64, 65, 66]). The development of the FPGA system is usually supported by commercial tools for creating on-chip debugging infrastructure (e.g., [3, 63, 71]). This FPGA design will run orders of magnitude faster than simulation, usually quickly enough to be plugged into a working system in place of the not-yet-fabricated IC. Here it can be validated against live data from other devices and long-running system-level tests which are not feasible in simulation.

However, FPGA emulation is not without limitations. While ASIC and FPGA designs share a common language to describe logic (e.g., VHDL and Ver-

ilog), there are many ASIC constructs which do not map well to FPGAs (and vice-versa). These differences require the HDL of an ASIC design to be modified before it can target an FPGA (as described in [60, 66]). If not done carefully, this may change functional behaviour of the design and substantially reduce the value of emulation.

#### 2.1.3 Post-Silicon Validation

Obviously, all errors are ideally caught before fabrication, but as discussed in Section 2.1.2, pre-silicon validation has a few fundamental limitations. The biggest of these, pre-silicon execution speed compared to real-chip execution and the difficulty of properly modelling complex electrical effects, can be addressed by postsilicon validation where designers test their chips post-fabrication, *in situ*, allowing for much more extensive and realistic tests [11, 30, 51].

However, post-silicon validation is not without its own limitations: it has challenges related to observability and controllability of internal signals. Commercial tools have emerged to aid in post-silicon debug at modest area overhead (e.g., [62]), however there is still room for improvement. Limitations in post-silicon validation are in large part due to cost-savings; ideally no debug or validation logic would be present on the final chip since it does not add any value for the user and adds to the overall fabrication cost of the chip (by requiring additional chip area) though in some cases this additional cost is seen as necessary for risk mitigation. Unfortunately, even with modern pre-silicon techniques, at least some debug and validation logic is required to enable and increase the effectiveness of post-silicon validation. One solution is to fabricate a 'debug version' of a chip with a large amount of validation logic to be used only during testing. However, increasing mask costs (shown in Figure 1.2) make it important that validation be achieved as close as possible to, and ideally at, first silicon. Furthermore, it would still be imperative to validate the production chip before it is handed off to manufacturing.

Many bugs caught in post-silicon validation are pure functional errors that could have been caught pre-silicon. Other bugs, however, relate to electrical or physical properties of the chip that can only be truly validated in silicon because these behaviours are too complex to be modelled with perfect accuracy in presilicon. Even in the ideal case where pre-silicon validation detects all functional errors, post-silicon validation would almost certainly be required before largescale manufacturing. Regardless of the tools and techniques used to exercise the fabricated chip, it is often very difficult to quantity the effectiveness of post-silicon tests.

#### 2.1.4 Manufacturing Test & Speed Binning

It is important to distinguish our approach from delay fault testing for manufacturing test [38]. Many underlying concepts (e.g., path delay, sensitizability, critical paths, etc.) are the same, but the application is different. In high-volume manufacturing test, the design is assumed to be functionally correct and the goal is to catch manufacturing defects which vary from chip-to-chip. Manufacturing test usually uses scan-chain based techniques which load test vectors into registers deep in the design and later verify that the output of the circuit at another scan-chain register contains the correct value given that test vector. Post-silicon validation usually focuses on techniques which interact with the system through its top-level ports whereas manufacturing test usually does not usually extend well to this type of top-level testing and is usually focused on testing at a much lower level.

In manufacturing test, unlike post-silicon validation, test time per die must be kept extremely low. In contrast, in post-silicon validation, the goal is to catch subtle design errors that escaped pre-silicon validation, so extremely long-running tests (e.g., trillions of cycles of running OS and application software), with the die in an actual system, are used. Our goal is to be able to assess the quality of such long-running tests.<sup>2</sup>

Speed binning refers to the testing process used to quickly but conservatively estimate performance of a physical SoC [15] by estimating its maximum operating frequency, often through scan-chain based techniques [8]. This allows IC producers to sell a range of processors that are the same silicon design, but with differing performance characteristics due to fabrication variation. Superficially, speed binning seems very related to the problem which this dissertation seeks to address. Although tests used in speed binning are usually functional, they are also very short and have been designed to exercise the most delay sensitive parts of

<sup>&</sup>lt;sup>2</sup> Of course, in post-silicon validation, short targeted tests are also run on automated test equipment, but such tests are typically generated with coverage information known by construction, and therefore are not the focus of this thesis.

a design. Furthermore, since speed binning tests are short, their coverage can be pre-computed using simulation. In some cases, however, manufacturing tests may be sufficiently extensive such that simulation may not be feasible. In post-silicon validation, the tests are almost always longer running than manufacturing tests and exploratory in nature. Since the achievable cycle-count is so much higher in post-silicon validation than in pre-silicon simulation (due to slow simulation speed) or in manufacturing test and speed binning (since each fabricated chip must be tested, reducing testing time directly corresponds to cost-savings), the amount of designer effort devoted to generating effective (but short) tests in post-silicon validation is lower. In general, post-silicon tests make use of the increased cycle count by employing constrained random tests. As such, this dissertation focuses on how emulated platforms can provide additional insight into post-silicon test characteristics and allow for effective test generation without requiring the amount of tester effort currently needed to design test suites for manufacturing test and speed binning.

As coverage-based techniques for generating effective post-silicon tests mature, it may be possible to use them to help design speed binning tests. However, for large production runs, it would likely be difficult to match the reduced testing times of a designer-crafted test suite. Since these savings are multiplied by every fabricated chip, the sunk engineering cost of test design is usually a good investment.

Recently, there has been renewed interest in reducing the effort required to

design speed binning tests by using structural scan chain-based tests [49] but the time required to load scan chains with test vectors is non-trivial, increasing overall testing time.

#### 2.2 **Pre-Silicon Coverage Metrics**

There are many metrics by which test coverage can be measured. Many have been designed to be specific to a certain stage of silicon validation: pre-silicon, post-silicon, or manufacturing test. In general, however, coverage-based techniques are in wide use in pre-silicon simulation and manufacturing test, but are used less commonly at other stages of validation.

Code coverage and functional coverage are extensively used during presilicon validation to evaluate the effectiveness of testing. Ideally, designs must reach 100% statement, branch and functional coverage, however exceptions are made if it is known that a given coverage point is unreachable or not important.

#### 2.2.1 Types of Pre-Silicon Coverage

In this section, we will briefly discuss seven types of coverage that are often used in simulation:

**Statement Coverage:** reports what fraction of HDL statements are executed. In most coding styles, each line corresponds with a statement. However, this is not strictly required. An example of statement coverage is illustrated in Section 2.2.2.

- **Branch Coverage:** reports what fraction of branches created by decision statements such as if  $\rightarrow$  elsif  $\rightarrow$  else  $\rightarrow$  end if and case blocks are executed (note that an if  $\rightarrow$  end if block has an implied empty else branch). An example of branch coverage is shown in Section 2.2.2.

- Condition Coverage: reports what fraction of boolean sub-expressions in a decision statement (e.g., if) that have evaluated to both true and false values. For example, "if (var\_a = `1' and var\_b = `2') then" has two sub-expressions: "var\_a = `1'" and "var\_b = `2'".

- **Path Coverage:** reports what fraction of combinations of branches have been executed. For example, a block with two if statements, one after another has four paths since each if statement has two possible values, true and false.

- **Functional Coverage:** reports what fraction of user-configured signal values, statements, properties, or cross products of these coverage points are executed. It is used extensively in industry. However, to be effective it requires careful implementation by a designer with deep domain knowledge into the module under test.

- **Mutation Coverage:** reports on the percentage of tests which detect an error which is intentionally inserted into RTL [55, 70]. For example, a mutation of the original RTL may include referencing the wrong variable or modifying operators. A test is said to have 'killed' the mutation, if it successfully detects the change. A test that detects many mutations (i.e., one that has high

mutation coverage) is likely more comprehensive and thorough than one with low mutation coverage. Unfortunately, mutation coverage relies heavily on the quality of the mutations generated and it is complicated to implement effectively.

**Tag Coverage:** reports what fraction of signal assignments have an effect on output signals (i.e., how many signal assignments are observable at the output) [18, 21, 45]. For every signal assignment, a tag signal corresponding to that signal is also updated, allowing the propagation of signal assignments to be traced. A test with high tag coverage would cause many signal assignments to be detected at the module's output. This type of coverage, while similar to statement coverage, is much more difficult to attain because the effect of many statements will only be reflected in a module's output under very limited circumstances.

#### 2.2.2 An Example of Statement and Branch Coverage

For example, in Figure 2.1, if a = 0 and b = 0, statement coverage would be 4/6 = 67% because statements 1, 2, 3, and 6 were executed. The process for branch coverage is similar but instead of counting statements, it counts branches created by conditionals (such as if and case). The branch coverage for the code in Figure 2.1 would only be 2/4 = 50% since branch 1 (the main program branch) and branch 2 were the only branches executed.

```

setup(); // Statement 1 & Branch 1

1

2

if (a == 0) { // Statement 2 & Branch 2

3

do_something(); // Statement 3

} else if (b == 1) { // Statement 4 & Branch 3

4

5

do_something_else(); // Statement 5

} // There is an implied else branch here

6

7

// else { } Branch 4

8

9

teardown(); // Statement 6

```

Listing 2.1: Simple example which illustrates statement and branch coverage techniques

# 2.3 Post-Silicon Coverage Metrics

The design of effective coverage metrics for physical chip-based validation techniques such as pre-silicon emulation or post-silicon validation is still an open research problem. As such, coverage techniques for these platforms are not nearly as established as they are in pre-silicon simulation or manufacturing test (where the limited per-chip testing time allows coverage to be pre-computed using simulation). Furthermore, the coverage metrics used in manufacturing test are not well suited for chip-based verification due to their focus on detecting manufacturing faults, which vary from chip to chip, and not functional bugs, which are systemic to the design itself. Instead, coverage metrics common in simulation (e.g., code coverage, assertion coverage, and mutation coverage) are often used in post-silicon verification. Since these techniques are used extensively in pre-silicon verification, they could be used to provide a universal view of coverage from pre- to post-silicon verification.

#### **2.3.1 Related Work — On-Chip Coverage Monitors**

Most coverage research has largely focused on how coverage metrics can be used in simulation and emulation, and not on how coverage monitors can be effectively implemented in silicon. In [11], however, the authors implemented on-chip coverage monitors for use during post-silicon validation of Intel's Core 2 Duo processor family. They focused on monitoring important, as dictated by a designer with insight into the chip, functional coverage points that were difficult to achieve in pre-silicon. Unfortunately, due to the constraints of minimizing on-chip monitoring overhead, only very minimal coverage information was extracted. It is interesting to note that in order to reduce area overhead, the coverage monitor data was accessed through the performance monitor registers already present on the processor. These performance monitors are normally used to monitor important performance metrics such as cache misses, power states, and instructions per cycle [61].

In [1], the authors add coverage monitors to their emulated design for use with the post-silicon test suite. During pre-silicon emulation, a constrained random post-silicon test suite (which is much too long to be simulated) is executed, and the coverage is recorded. This coverage is expected to match the coverage achievable by the same tests during post-silicon validation. Using this system, a team can tune the post-silicon tests to guarantee high coverage before the processor is fabricated. As in [11], the tests were limited to functional coverage. Furthermore, the area overhead for implementing these monitors was not evaluated and some details were considered proprietary and not disclosed.

In [33], we manually added coverage monitor flags alongside targeted IP cores, and extracted statement and branch coverage. Unfortunately, we found the monitoring system imposed a large area overhead on the design. To mitigate this, we used state-of-the-art software coverage analysis techniques to losslessly reduce the overhead of our monitors. These area optimizations were successful and provided an area decrease of up to 28% at no quality cost. Even with these optimizations, we hypothesized that the system would not be feasible for implementation on an ASIC due to area constraints.

In [6], we extended the work done in [33] to a multiprocessor SoC design. The coverage monitor system was improved such that the logic analyzer used could record a timestamp along with our coverage information, allowing us to analyze how coverage changed over time between the two processors of our SoC as they were booting Linux. Additionally, some optimizations were made in how our coverage monitors were implemented which resulted in some area savings. We used Synopsys Design Compiler to estimate the area overhead for the coverage monitor area overhead was too high for implementation on an ASIC.

## 2.4 Timing Validation

The work done for this dissertation, while similar the work done in [6] and [33], is focused on solving a fundamentally different problem: timing validation. Timing validation is a substantially different problem than functional coverage, requiring non-functional properties to be validated. Furthermore, the previous work

focused on the feasibility of integrating coverage monitor into ASIC chips, whereas this work primarily focuses on coverage monitor implementation for pre-silicon FPGA emulation.

In this dissertation, we focus on critical-path coverage, which considers a circuit path (from the output of a terminating primitive like a flip-flop to the input of a terminating primitive) covered when the path has been exercised under input vectors for which it will experience worst-case timing conditions. Since we are only interested in paths which may cause the circuit to exhibit incorrect behaviour under suboptimal timing conditions (i.e., paths with a lot of timing slack can take longer than expected without any ill effect), we only consider paths which we believe are on or near the critical-path (as dictated by a STA tool).

The research done for the dissertation seeks to explicitly quantify the coverage of specific timing paths in a design. In order to ensure correct timing behaviour, it is necessary to ensure that the critical paths of a circuit are adequately exercised post-silicon. Our method quantitively measures the effectiveness of post-silicon verification plans in exercising paths which have been identified as at or near the critical path with pre-silicon timing analysis. Due to inaccuracies in pre-silicon timing analysis and die-to-die manufacturing variation, it is not possible to determine which subset of these paths will be critical on a given physical chip. The overall goal is: given a chip that has been fabricated, and a verification plan (software to run on the processor and other realistic input stimuli), determine to what extent the timing-critical paths of the circuit are exercised. More precisely, we seek to measure a coverage metric which we define to be the proportion of the *n* longest paths which have been exercised at least once during the execution of the verification plan. (In our experiments in Section 5.2, n = 2048, but *n* can be chosen arbitrarily.)

# Chapter 3

# **Proposed Flow**

This chapter describes an idealized toolflow for automatic integration of criticalpath coverage monitors. Although our techniques could be applied to any large integrated circuit, we focus on large processor-based SoCs since the interaction between hardware and software provide significant verification challenges. We begin in Section 3.1, where we motivate critical-path coverage monitors through a discussion on timing validation. In Section 3.2, we highlight the role FPGA-based emulation can play in obtaining critical-path coverage information of a post-silicon test suite. In Section 3.3, we describe the composition of the coverage monitors and discuss how the fundamental implementation differences between the ASIC and FPGA versions of the chip do not pose a significant barrier to extracting coverage information. Section 3.4 summarizes the chapter.

#### **3.1 Problem Statement**

The performance of ICs is in large part dictated by its maximum operating frequency. This maximum operating frequency describes the shortest clock period that a design can reliably use. If a design is running faster than this frequency, a circuit path's output may not have resolved by the time it is read by a flip-flop or other memory device (i.e., a setup time violation). Or, in the case of a hold time violation, the input signal to a flip-flop may change too soon after a clock transition, causing an incorrect value to be read. In either case, the output may be erroneously recorded by the device, likely causing incorrect functional behaviour in the design [12]. Unfortunately, determining this frequency is non-trivial due to the variation between given fabricated chips as well as the limitations of timing analysis techniques. Ignoring variation in fabrication for now, the maximum operating frequency of a chip for a given voltage and temperature pair could be determined using exhaustive circuit simulation. This approach quickly becomes infeasible for all but the smallest designs. Instead, Static Timing Analysis (STA) techniques are used to conservatively estimate the expected timing of a chip without requiring simulation. If the design has already been placed-and-routed, STA can take into account this information for a more accurate estimate. A variant of STA, Statistical Static Timing Analysis (SSTA), replaces the timing values used in STA with probabilistic distributions, allowing the tool to report a probabilistic distribution of possible circuit outcomes.

STA techniques are only approximate; to ensure timing performance, vali-

dation must be done with the physical silicon. Furthermore we cannot simply use STA techniques to determine the single most critical path to be targeted during post-silicon validation because variation in fabrication may cause other paths to become more critical. Post-silicon timing validation is further complicated because it is not simple for tests to target specific timing-critical paths. This is particularly true for post-silicon tests because they are almost always too long to be simulated. Coverage monitors could be added to the ASIC design to aid in targeting paths, but this poses a substantial (and usually untenable) area cost.

#### **3.2 Overall Flow**

One way to determine whether a path has been covered in hardware validation is to add small coverage monitors to each path of interest; during the run, these coverage monitors could trip if the corresponding path is exercised, and at the end of execution, the state of these monitors could be read, and the coverage metric calculated. The problem with this approach is the area overhead of the coverage monitors. Although these coverage monitors could be removed in the release version of the chip, doing so would change the timing and electrical behaviour of the chip, perhaps leading to different paths becoming critical, nullifying the value of the results.

Our approach takes advantage of the prevalence of FPGA-based emulation. In the following discussion, we use the term *ASIC version* of the design to refer to the version of the design before emulation (the version that will eventually be implemented as a chip and shipped) and the term *emulation version* of the design to refer to the version of the design that has been re-mapped to FPGAs for validation and prototyping purposes.

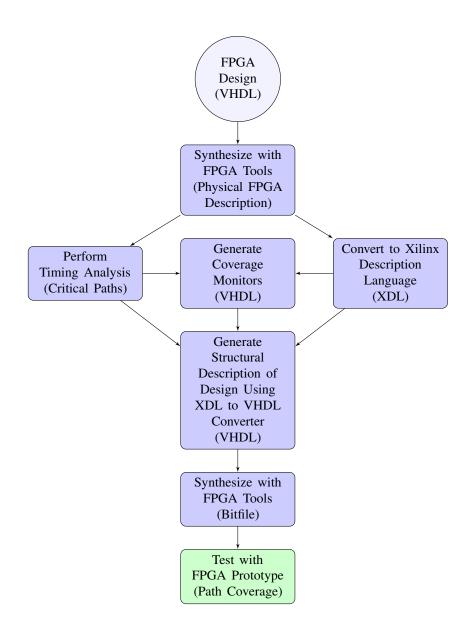

Our flow uses the *emulation version* to determine the timing coverage metric of the *ASIC version*. More precisely, our approach is as follows. Using STA techniques, we identify the *n* longest paths in the ASIC version. If information regarding false paths is available, those paths can be discarded at this stage. Similarly, if there are other paths of particular interest to the design and validation engineers, they can be added at this stage. Once we have identified the paths of interest in the original design, we create the emulation version by mapping the circuit to FPGAs (e.g., as described in [60, 66]). We then instrument the emulated design, as will be described in Section 3.3. This instrumentation monitors the targeted paths, and determines when each has been exercised. At the end of the run, the coverage information can be read from the instrumentation, and an overall timing coverage metric calculated. This is the coverage that is expected when the same verification plan is run on the ASIC version of the design. The proposed flow is shown in Figure 3.1.

In the above flow, it is important that the paths be determined using the original design, since once the design has been re-targeted to an FPGA for emulation, the paths that are critical may change. It is very possible that the paths we target are *not* the critical paths during emulation, but they are the ones we care about, since they are the critical paths of the chip that we intend to ship.

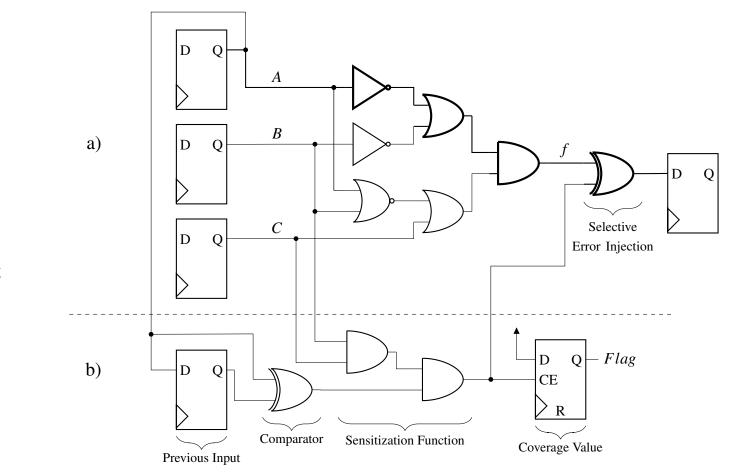

**Figure 3.1:** Toolflow for adding path coverage monitors to the FPGA prototype of an ASIC design. Each stage's output is shown in parentheses.

## 3.3 Instrumentation

Key to the flow described in Section 3.2 is the instrumentation that is added to the emulation version of the circuit. Because we are adding our instrumentation to the emulation version of the circuit only, the area and delay overheads do not translate to the shipped chip. However, minimizing overhead is still important, since the overhead directly relates to the size of the FPGA emulation system and the speed at which emulation tests can be run.

As described in Section 3.2, we obtain a set of timing-critical paths from the static timing analysis of the ASIC version of the circuit, and then instrument these paths in the FPGA version of the circuit. The instrumentation is designed to record whether, for each path, the path has been exercised. A monitored path is considered exercised, and therefore covered, when a transition on the input of the path causes there to be a transition along every element of the path. To instrument a path, we add:

- a) A transition detector at the start of the path,

- b) Boolean difference [13] logic to calculate the sensitization condition [4] for each logic element along the path,

- c) A bit to record whether the path has been entirely sensitized.

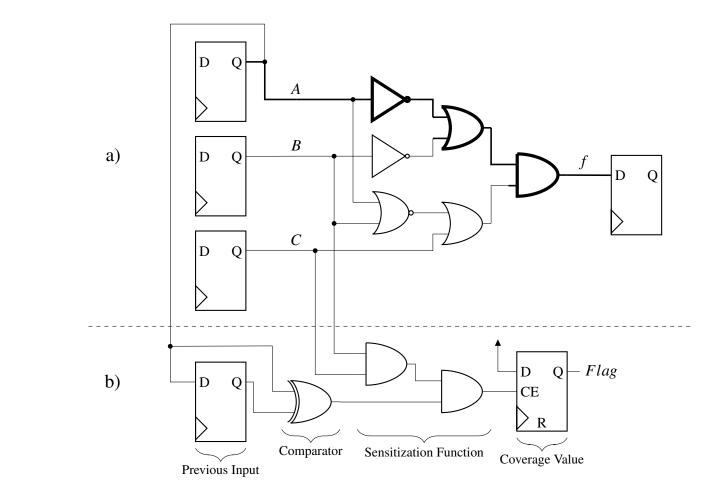

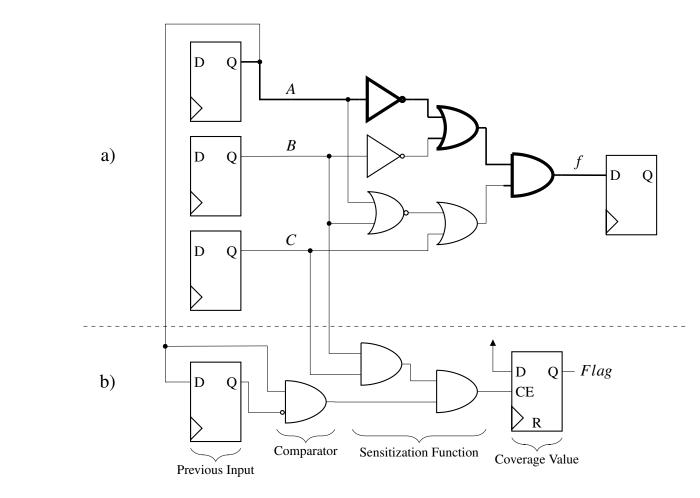

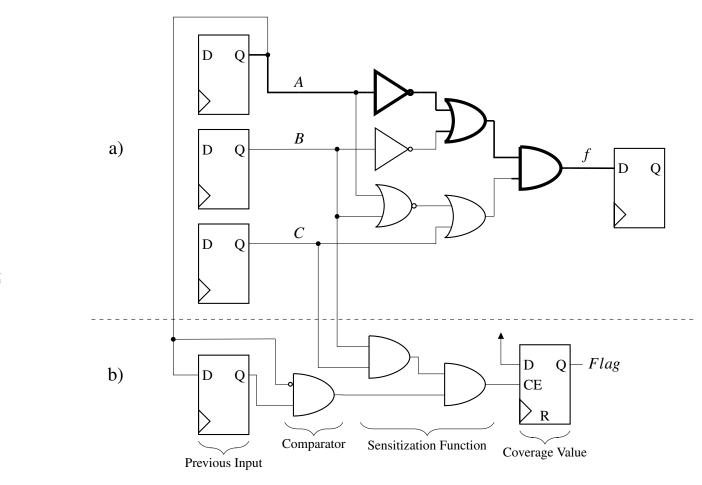

An example is shown in Figure 3.2, where the logic function, f, is  $(\overline{A + B} + C) \cdot (\overline{A + B})$ . From this logic, its sensitization function can be calculated to be  $B \cdot C$ . This makes intuitive sense as when B = '1' the upper OR gate's  $\overline{B}$  input will be '0', allowing signal A to control that gate's output. This is similarly true for the final AND gate; when C = '1' its lower input will be '1', allowing the targeted path to control the value of f. Figure 3.2(a) shows the original path, and Figure 3.2(b) shows the instrumented circuitry, including the logic to compute the sensitization condition. Figures 3.3 and 3.4 demonstrate how the coverage monitor shown in Figure 3.2 can be modified to be sensitized only for rising or falling edges, respectively. This is achieved by modifying the comparator which detects the transition

on the first element of the path.

Further modifications could be made to allow detection of fault observability by selectively injecting errors whenever the path has been exercised (i.e., whenever coverage is achieved) as shown in Figure 3.5. If the injected error is found to be observable, it should be similarly observable on an ASIC system with a timing fault affecting that path (though in the case of multiple faults, the fault may not be observable). However, to be practically useful, this modification would have to be extended to allow error injection to be enabled on a per-path basis since the fault may only be observable many clock cycles after the error is injected. In this thesis, we sensitized the coverage monitors for rising and falling edges (i.e., the monitoring circuitry shown in Figure 3.2), and did not instrument for error injection.

It is important that we add instrumentation circuitry to the RTL representation of the circuit, before it is optimized and mapped by the FPGA tools. It is very possible that after mapping to the FPGA, the original paths either do not exist (because of the optimizations performed by the FPGA tools) or because parts of the original paths have been encapsulated into hard blocks (such as DSP blocks which are common in all modern FPGAs). Note, however, that the inclusion of this instrumentation does not prevent the FPGA tool from optimizing the original circuit as it sees fit. In the example of Figure 3.2, once the instrumentation has been added to the RTL version of the circuit, the tool is free to optimize the original path in any way (including removing it from the circuit entirely). The instrumentation circuit will still record whether the path would be exercised in the ASIC version of the circuit, even if that path does not exist in the emulation version.

The area overhead of this instrumentation is proportional to the number of paths instrumented and the length of each path. For each segment along the path, the sensitization function is guaranteed to require no more lookup tables than a gate-level implementation of the original path, since the sensitization function at each stage requires fewer inputs than the original function at each stage. However, in some cases, it may be that the original function can be optimized effectively by the FPGA CAD tools (for example, a multiply function may be efficiently mapped to an embedded DSP block), while the instrumentation logic cannot be optimized as efficiently. In the worst case, if the instrumentation circuitry requires signals that would otherwise have been encapsulated inside a DSP block, then the circuitry generating these signals will have to be replicated in the FPGA soft logic. If this occurs, it may tend to increase the overhead of our instrumented circuit compared to the extra logic. However, as we will show in Section 5.2, experimentally, this rarely occurs.

The delay overhead in the emulation version is very small. Although some signals will have increased fanout, because FPGA interconnect is typically fully buffered [42] the overall timing impact will be small. The specific frequency overheads are quantified in Section 5.2.3.

# **3.4 Chapter Summary**

This chapter described the ideal flow for integration of critical-path coverage monitors into emulated designs. Section 3.1 began by introducing and motivating the problem this dissertation addresses. Section 3.2 highlighted the value FPGA-based emulation can provide for post-silicon validation. In Section 3.3, we described the coverage monitors themselves and discuss the challenges posed when using emulated systems to provide information on the silicon product.

**Figure 3.2:** Example of a critical path, a), instrumented to monitor coverage by b) for bolded path *f* initiated by a rising or falling transition on input *A*.

**Figure 3.3:** Example of a critical path, a), instrumented to monitor coverage by b) for bolded path *f* initiated by a rising transition on input *A*.

**Figure 3.4:** Example of a critical path, a), instrumented to monitor coverage by b) for bolded path *f* initiated by a falling transition on input *A*.

**Figure 3.5:** Example of a critical path, a), instrumented to monitor coverage by b) for bolded path *f* through input *A* with additional circuitry allowing for error injection whenever coverage is achieved.

# **Chapter 4**

# Implementation

In this chapter we introduce the toolflow implemented to automatically instrument hardware designs with critical-path coverage monitors. We describe the toolflow used to approximate the ASIC emulation process and describe our implementation of the XDL to VHDL converter used to facilitate automatic coverage monitor integration, including a detailed characterization of the six main classes of XDL instances encountered.

## 4.1 Approximated Flow

Because the focus of this work is the design and implementation of the coverage monitors introduced in Section 3.3, as well as the investigation of the coverage achieved for some common post-silicon tests, and not the verification of a processor-centric SoC *per se*, we have shortened the proposed verification flow

in two ways:

- a) by starting with a design that is already known to be synthesizable to FPGA,

- b) by integrating coverage monitors into the design at the gate-level, not the RTL level.

This modified flow is shown in Figure 4.1. After synthesis, we perform timing analysis on the placed-and-routed circuit description. The timing analyzer reports the slowest *n* paths to the converter tool from which path coverage monitors are generated. These coverage monitors are integrated into a new structural VHDL description generated from the placed-and-routed XDL description of the circuit. This new VHDL description is then synthesized using the full Xilinx toolflow. All constraints on top-level ports, signals or instances should still apply to the structural circuit description, however constraints for signals or instances deep in the design hierarchy may need to be modified to account for differences in generated names.

Starting with a design that is already synthesizable to an FPGA, particularly one that can be fabricated to ASIC technology, is a very good approximation to using an FPGA-emulated ASIC design. However, it causes our flow to differ in one significant way: there is no ASIC design from which to obtain timing paths. Instead, we use timing results from the design natively synthesized for the FPGA. While it is expected that these timing paths will differ in content from those derived for an ASIC version, they should not differ substantially in composition. The FPGA timing paths used in our approximated flow could be easily exchanged for ASIC timing paths. It is important to highlight that this simplification was made to facilitate our experimentation; in a 'real' application of the flow, ASIC timing paths would be used.

We integrated our coverage monitors at the gate-level because, to the best of our knowledge, there are no full-featured, open-source VHDL parsers available for adaptation to our uses. In contrast, the two biggest FPGA vendors, Altera and Xilinx, both provide toolkits which allow experimental integration with their tools. For this thesis, we used the RapidSmith API from Brigham Young University [41] for parsing and iterating over the Xilinx Description Language (XDL) format, Xilinx's human readable gate-level circuit description. Parsing XDL is much easier than parsing VHDL because it is a simple, structural description of a circuit written by an automated tool and not a language created for circuit designers to write directly.

# 4.1.1 Automated Integration of Coverage Monitors Using XDL

A key aspect of our ideal and approximated flows is the two CAD tool passes: the design first must be synthesized, placed, and routed (ideally, with the ASIC tools) for static timing analysis to determine likely critical paths of the ASIC version; then this design is instrumented for coverage and processed a second time by the FPGA tools to create the emulation version. Accordingly, to automate the flow, we need a mechanism to extract the output from the first step, add instrumentation, and then input this into the FPGA tools for the second step.

**Figure 4.1:** Toolflow used in this thesis to automatically add path coverage monitors to an FPGA design. Each stage's output is shown in parentheses.

Xilinx provides unofficial support for an interface to export their proprietary Native Circuit Description (NCD) files to a human-readable XDL file in terms of their fundamental FPGA primitives and the nets that connect them. This allows designs to be imported and exported freely between the major FPGA synthesis stages: *mapping*, *placement* and *routing*. However, in recent versions of the Xilinx tools, the *mapping* and *placement* stages have been integrated, making import/export after mapping but before placement impossible. In these versions, it is possible to export a placed description and discard the placement information, but there is no way to pass a mapped-but-unplaced description to the Xilinx placer.