## A New Radio Frequency Switch-mode Power Amplifier Concept for Wireless Applications

by

Sheikh Nijam Ali

B.Sc., Bangladesh University of Engineering and Technology (BUET), 2009

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### MASTER OF APPLIED SCIENCE

$\mathrm{in}$

The College of Graduate Studies

(Electrical Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA

(Okanagan)

August 2012

© Sheikh Nijam Ali, 2012

### Abstract

Although RF switch-mode power amplifiers (SMPAs) are theoretically attractive with the potential to achieve very high power efficiencies, experimental realizations at high frequencies have yet to yield significantly better efficiency than conventional analog technology. Most SMPA designs are based on class D or class S circuits, and in these circuits, power efficiency is significantly reduced when the switching signal is changed from periodic to non-periodic. In this work, a new SMPA architecture is proposed. Instead of employing reflective out-of-band matching conditions used in class D/S circuits, the switch is matched to a broadband load which creates dissipative out-of-band impedances. The broadband load significantly improves switching conditions especially for non-periodic signals. The broadband load is implemented as a complementary diplexer which separates in-band and out-of-band signal power at the output of the SMPA. An energy recovery loop using out-of-band signal power is proposed to significantly reduce the sensitivity of the overall power efficiency to changes in the peak to average power ratio of the source signal. Experimental and simulation results are shown for the new SMPA architecture.

## Table of Contents

| Abstra  | ict                                                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| Table o | of Contents                                                                                                                            |

| List of | Tables                                                                                                                                 |

| List of | Figures                                                                                                                                |

| List of | Acronyms                                                                                                                               |

| Acknow  | $wledgements \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots xxi$                                                       |

| Dedica  | tion                                                                                                                                   |

| Chapte  | $er 1: Introduction \dots \dots$ |

| 1.1     | Background on RF Switch-mode Power Amplifiers 3                                                                                        |

|         | 1.1.1 Class D Switch-mode Power Amplifier                                                                                              |

|         | 1.1.2 Class S Switch-mode Power Amplifier                                                                                              |

| 1.2     | Literature Review                                                                                                                      |

| 1.3     | Motivation and Research Objectives                                                                                                     |

| 1.4     | Contributions                                                                                                                          |

| 1.5     | Thesis Outline                                                                                                                         |

#### TABLE OF CONTENTS

| Chapt | er 2: | Switch-mode Power Amplifier Design                            | 20 |

|-------|-------|---------------------------------------------------------------|----|

| 2.1   | Desi  | gn 1: Broadband RF SMPA with a 50 $\Omega$ Load $\ . \ . \ .$ | 21 |

|       | 2.1.1 | Design Considerations                                         | 21 |

|       | 2.1.2 | 2 The RF Switch                                               | 22 |

|       | 2.1.3 | 3 Output Network Design                                       | 23 |

| 2.2   | Desi  | gn 2: Tuned Broadband RF SMPA with a 50 $\Omega$ Load $~.~$   | 29 |

|       | 2.2.1 | Design Considerations                                         | 29 |

|       | 2.2.2 | 2 Determination of the Output Capacitance of the Cree         |    |

|       |       | Device                                                        | 29 |

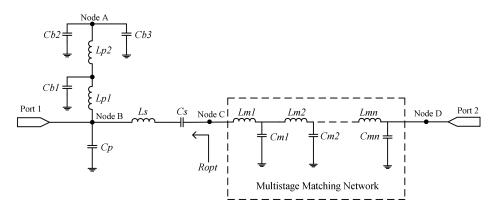

|       | 2.2.3 | 3 Output Network Design                                       | 32 |

| 2.3   | Desi  | gn 3: Broadband RF SMPA with an Optimum Load, $R_{opt}$       | 38 |

|       | 2.3.1 | Design Considerations                                         | 38 |

|       | 2.3.2 | 2 Output Network Design                                       | 40 |

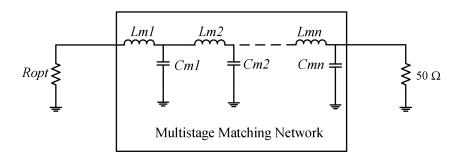

|       | 2.3.3 | 3 Multi-stage <i>L</i> -match Circuit                         | 42 |

| 2.4   | Driv  | rer for the Final Stage of the SMPA                           | 50 |

| Chapt | er 3∶ | Complementary Diplexer                                        | 57 |

| 3.1   | Back  | ground                                                        | 57 |

| 3.2   | Sing  | ly and Doubly Terminated Filters                              | 59 |

| 3.3   | Com   | plementary Diplexer                                           | 60 |

| 3.4   | Lum   | aped Element Complementary Diplexer Design                    | 61 |

| 3.5   | Dist  | ributed Element Complementary Diplexer Design                 | 67 |

| Chapt | er 4: | Results                                                       | 86 |

| 4.1   | Inpu  | ut Signal Types                                               | 86 |

|       | 4.1.1 | Periodic 50% Duty Cycle Test Signal                           | 87 |

|       | 4.1.2 | 2 Periodic Test Signals with Variable Duty Cycle              | 88 |

#### TABLE OF CONTENTS

|       | 4.1.3  | Pseudo-random (Non-periodic) Test Signals 89                                                   |

|-------|--------|------------------------------------------------------------------------------------------------|

| 4.2   | Result | s for Design 1 $\ldots$ 92                                                                     |

|       | 4.2.1  | SMPA performance with a 50% duty cycle periodic                                                |

|       |        | test signal $\ldots \ldots $ 92 |

| 4.3   | SMPA   | a performance with periodic switching signals $\ldots \ldots 99$                               |

| 4.4   | SMPA   | a performance with Pseudo-random bit sequences 100 $$                                          |

| 4.5   | Result | s for Design 2                                                                                 |

|       | 4.5.1  | SMPA performance with sinusoidal source signals 107 $$                                         |

|       | 4.5.2  | ${\rm SMPA \ performance \ with \ Pseudo-random \ bit \ sequences}$                            |

|       |        | (PRBS)                                                                                         |

| 4.6   | Result | s for Design 3                                                                                 |

|       | 4.6.1  | SMPA performance with a sinusoidal source signal $\ . \ . \ 111$                               |

|       | 4.6.2  | ${\rm SMPA \ performance \ with \ Pseudo-random \ bit \ sequences}$                            |

|       |        | (PRBS)                                                                                         |

| 4.7   | Desigr | n Comparison Summary                                                                           |

|       | 4.7.1  | Bandwidth Comparison                                                                           |

|       | 4.7.2  | Comparison of Results for Sinusoidal Source Signals $$ . 117 $$                                |

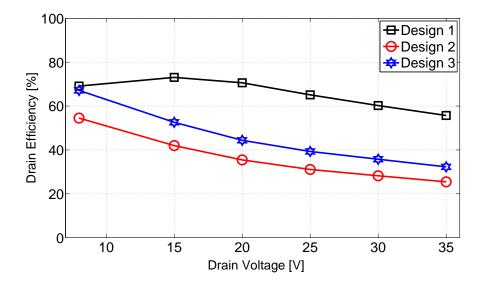

| 4.8   | Comp   | arison of Results for PRBS Bit Sequences                                                       |

|       | 4.8.1  | Conclusions                                                                                    |

| 4.9   | Result | is for Design 1 with a Complementary Diplexer 122                                              |

| Chant |        | Pulse Encoded Despenses 195                                                                    |

|       |        | Pulse Encoded Responses                                                                        |

| 5.1   |        | ation of Pulse Encoded Signals                                                                 |

|       | 5.1.1  | Sigma-delta Modulation (SDM)                                                                   |

|       | 5.1.2  | Noise-shaped Pulse Position Modulation (PPM) 129                                               |

| 5.2   | Result | s for Pulse Encoded Signals                                                                    |

#### TABLE OF CONTENTS

| Chapter 6: Energy Recycling                                               |

|---------------------------------------------------------------------------|

| 6.1 RF to DC Energy Conversion Circuits                                   |

| 6.2 $$ Power Efficiency Analysis of SMPA with Energy Recovery 136 $$      |

| Chapter 7: Conclusion                                                     |

| 7.1 Evaluation of Thesis Objectives and Contributions $\ldots \ldots 139$ |

| 7.2 Future Work                                                           |

| Bibliography                                                              |

| Appendices                                                                |

| Appendix A: Coupled Line Impedance Scaling                                |

## List of Tables

| Table 1.1 | Some recent experimental results for periodic switch-                            |    |

|-----------|----------------------------------------------------------------------------------|----|

|           | ing (CW)                                                                         | 13 |

| Table 1.2 | Some recent experimental results for non-periodic switch-                        |    |

|           | ing with pulse encoded signals.                                                  | 14 |

| Table 2.1 | Experimental circuit component values of output match-                           |    |

|           | ing network for Design 1                                                         | 25 |

| Table 2.2 | Experimental circuit component values of output match-                           |    |

|           | ing network for Design 2                                                         | 34 |

| Table 2.3 | $\label{eq:experimental} Experimental circuit component values of output match-$ |    |

|           | ing network for Design 3                                                         | 42 |

| Table 2.4 | Capacitor and inductor values for the matching circuit.                          | 46 |

| Table 2.5 | Transmission line dimensions for the output matching                             |    |

|           | circuit in Design 3                                                              | 47 |

| Table 2.6 | Substrate process parameters                                                     | 47 |

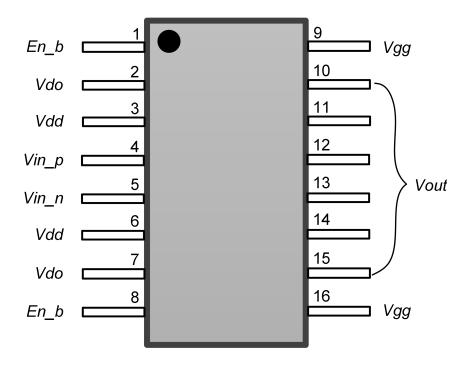

| Table 2.7 | Nominal parameters of the PWD06 driver chip. $\ldots$                            | 50 |

| Table 2.8 | Description of the pins of the PWD06 driver chip                                 | 54 |

| Table 3.1 | Normalized 0.5 dB Chebyshev element values for $R_s =$                           |    |

|           | 0 or $\infty$ .                                                                  | 63 |

#### LIST OF TABLES

| Table 3.2 | Complementary Diplexer design parameters (even and         |   |

|-----------|------------------------------------------------------------|---|

|           | odd mode impedances)                                       | 0 |

| Table 3.3 | Diplexer design parameters (physical dimensions) 8         | 1 |

| Table 3.4 | Substrate process parameters                               | 2 |

| Table 3.5 | Summary of simulation and measured results for the         |   |

|           | complementary diplexer                                     | 4 |

| Table 4.1 | Bandwidth comparison for SMPA designs 11                   | 6 |

| Table 5.1 | Noise shaping filter coefficient values for $H_{RF}(s)$ 12 | 7 |

# List of Figures

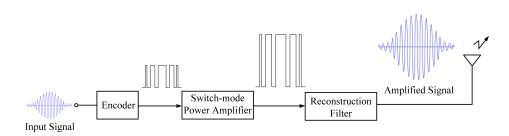

| Figure 1.1 | Basic block diagram of a RF switch-mode power am-                     |    |

|------------|-----------------------------------------------------------------------|----|

|            | plifier system (only non-periodic signals are shown)                  | 4  |

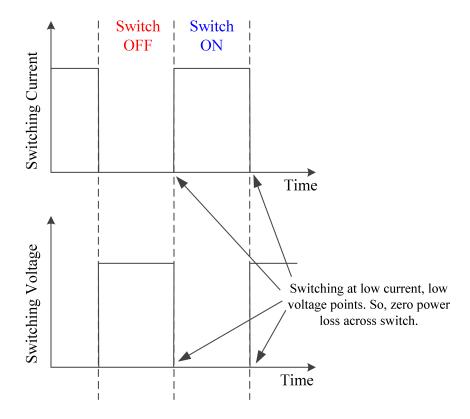

| Figure 1.2 | Switching characteristics of the RF switch-mode power $% \mathcal{A}$ |    |

|            | amplifier                                                             | 5  |

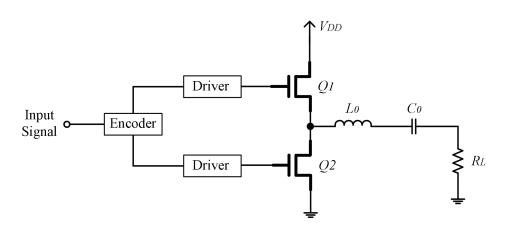

| Figure 1.3 | Circuit diagram of a voltage mode class D (VMCD)                      |    |

|            | power amplifier.                                                      | 7  |

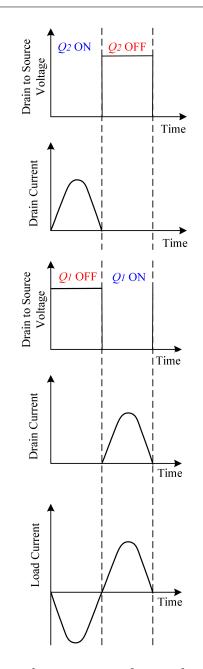

| Figure 1.4 | Voltage and current waveforms of a voltage mode class ${\rm D}$       |    |

|            | (VMCD) power amplifier                                                | 8  |

| Figure 1.5 | Circuit diagram of a current mode class D (CMCD)                      |    |

|            | power amplifier.                                                      | 9  |

| Figure 1.6 | Voltage and current waveforms of a current mode                       |    |

|            | class D (CMCD) power amplifier. $\ldots$                              | 10 |

| Figure 1.7 | Power spectral density of a 1 GHz pulse encoded sig-                  |    |

|            | nal. An overlay of a narrow-band bandpass recon-                      |    |

|            | struction filter is also shown                                        | 11 |

| Figure 1.8 | Circuit diagram of a voltage mode class S power am-                   |    |

|            | plifier                                                               | 12 |

| Figure 1.9 | Circuit diagram of the proposed RF switch-mode power $% \mathcal{A}$  |    |

|            | amplifier.                                                            | 19 |

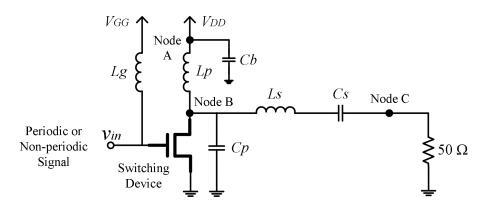

| Figure 2.1  | Circuit diagram of the broadband RF switch-mode           |    |

|-------------|-----------------------------------------------------------|----|

|             | power amplifier with a 50 $\Omega$ load (Design 1)        | 22 |

| Figure 2.2  | Drain-source characteristics of the 10 W GaN HEMT $$      |    |

|             | Cree device                                               | 23 |

| Figure 2.3  | Equivalent output network for frequency response mea-     |    |

|             | surements of Design 1                                     | 24 |

| Figure 2.4  | Output reflection coefficient $ S22 $ at port 2 of Fig-   |    |

|             | ure 2.3                                                   | 26 |

| Figure 2.5  | Simulated and experimental results for the insertion      |    |

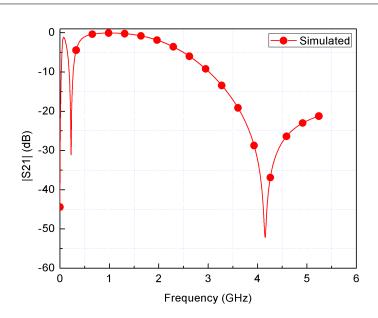

|             | loss of the output network for Design 1. $\ldots$         | 27 |

| Figure 2.6  | Simulated results for the insertion loss of the out-      |    |

|             | put network for Design 1 over an extended frequency       |    |

|             | range up to 10 GHz                                        | 28 |

| Figure 2.7  | Picture of the output network for Design 1                | 28 |

| Figure 2.8  | Circuit diagram of the tuned broadband RF switch-         |    |

|             | mode power amplifier (Design 2)                           | 29 |

| Figure 2.9  | Circuit diagram to determine output capacitance. $\ .$ .  | 30 |

| Figure 2.10 | Simplified circuit model of the output admittance net-    |    |

|             | work of the Cree device looking into port $1$             | 30 |

| Figure 2.11 | Small signal output admittance for a bias of $V_{GG}$ =   |    |

|             | -1 V and the $V_{DD} = +30$ V                             | 32 |

| Figure 2.12 | Extracted output capacitance, $C_p$ , for the Cree device |    |

|             | for different gate and drain voltages at a frequency of   |    |

|             | 1 GHz                                                     | 33 |

| Figure 2.13 | Equivalent output network for frequency response mea-     |    |

|             | surements of the tuned broadband SMPA (Design 2).         | 34 |

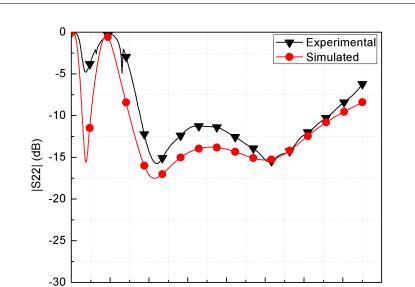

| Output reflection coefficient $ S22 $ at port 2 of Fig-            |          |

|--------------------------------------------------------------------|----------|

| ure 2.13                                                           | 35       |

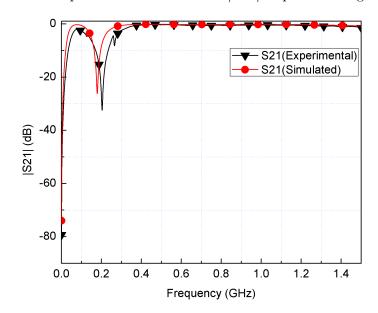

| Simulated and experimental measurements of inser-                  |          |

| tion loss $ S21 $ for Design 2 up to 1.5 GHz                       | 36       |

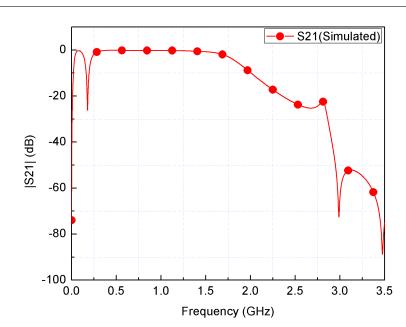

| Simulated insertion loss $ S21 $ of the output network             |          |

| of the Design 2 up to 10 GHz                                       | 37       |

| Picture of the output network for Design 2                         | 37       |

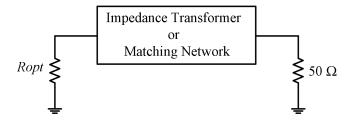

| Simplified circuit diagram of the Design 3 with an                 |          |

| optimum load $R_{opt}$                                             | 38       |

| Ideal switching characteristics of a RF switch-mode                |          |

| power amplifier.                                                   | 40       |

| Block diagram of the impedance transformation from                 |          |

| $R_{opt}$ to a 50 $\Omega$ load                                    | 40       |

| Multistage matching network to transform $R_{opt}$ to a            |          |

| 50 $\Omega$ load                                                   | 41       |

| Equivalent output network for frequency response mea-              |          |

| surements of the optimum broadband $\operatorname{RF}$ switch-mode |          |

| power amplifier (Design 3)                                         | 41       |

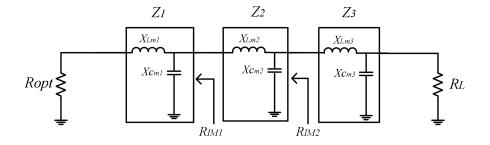

| Three stage binomial transformer                                   | 44       |

| Output reflection coefficient $ S22 $ at port 2 of Fig-            |          |

| ure 2.22                                                           | 48       |

| Simulated and experimental results for insertion loss              |          |

| S21  of the output network for the Design 3                        | 48       |

| Simulated insertion loss $ S21 $ of the output network             |          |

| for Design 3                                                       | 49       |

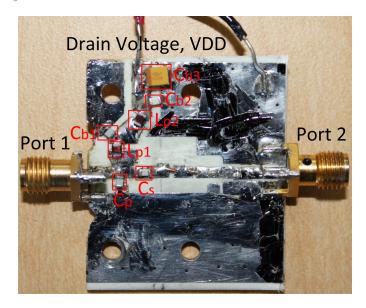

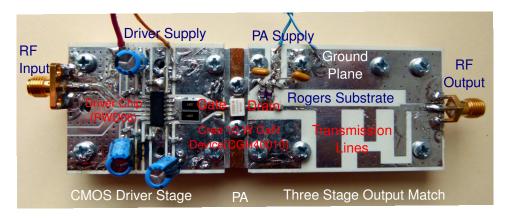

| Picture of the experimental prototype of Design 3                  |          |

| with a driver board and a 10 W GaN Cree device                     | 49       |

|                                                                    | ure 2.13 |

$\mathbf{xi}$

| Figure 2.28 | Pin diagram of the PWD06 driver chip                                         | 52 |

|-------------|------------------------------------------------------------------------------|----|

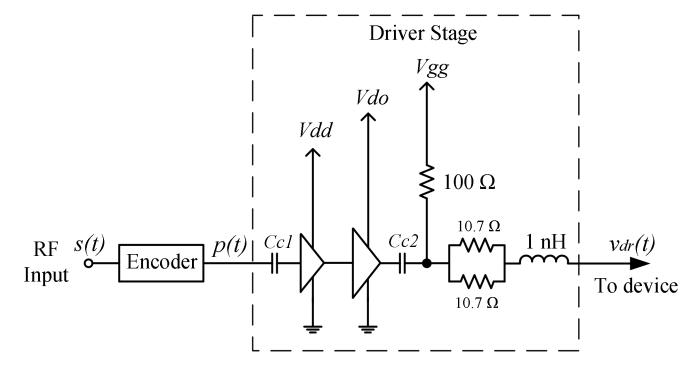

| Figure 2.29 | Internal circuit diagram of the driver board. $\ . \ . \ .$                  | 53 |

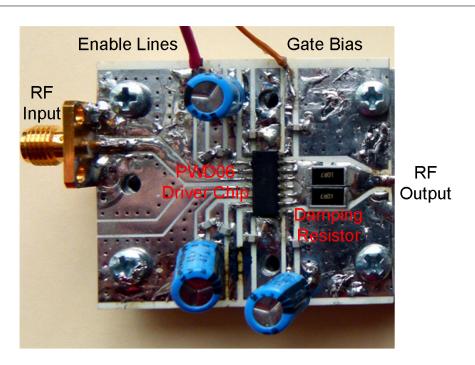

| Figure 2.30 | Picture of the driver board                                                  | 55 |

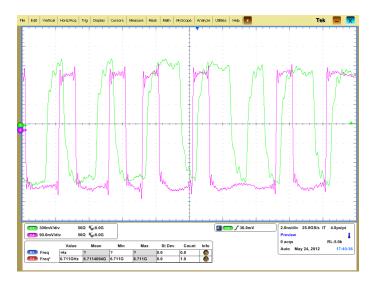

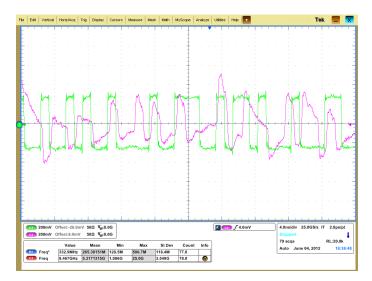

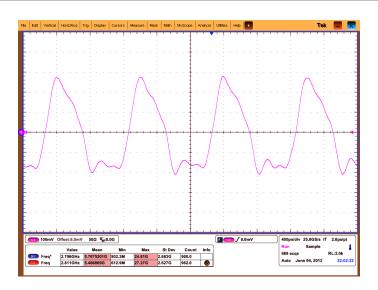

| Figure 2.31 | Measured driver response for a 1 GHz CW input sig-                           |    |

|             | nal across a 50 $\Omega$ load                                                | 55 |

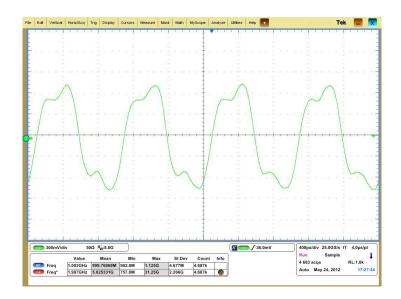

| Figure 2.32 | Measured driver output wave shape at 1 GHz fre-                              |    |

|             | quency for PRBS excitation across a 50 $\Omega$ load (red                    |    |

|             | line indicates the driver input and green line indicates                     |    |

|             | driver output). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$        | 56 |

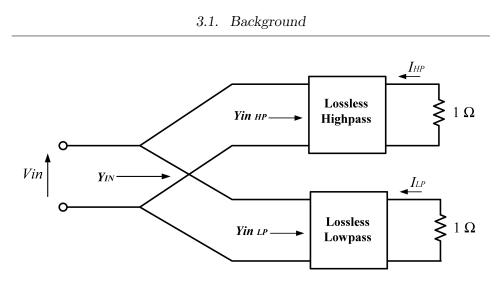

| Figure 3.1  | Basic block diagram of a diplexer.                                           | 58 |

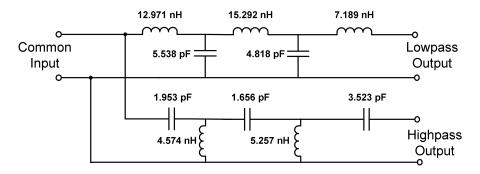

| Figure 3.2  | Circuit diagram of a lumped element $5^{th}$ order 0.5 dB                    |    |

|             | ripple 1 GHz Chebyshev lowpass/highpass comple-                              |    |

|             | mentary diplexer.                                                            | 64 |

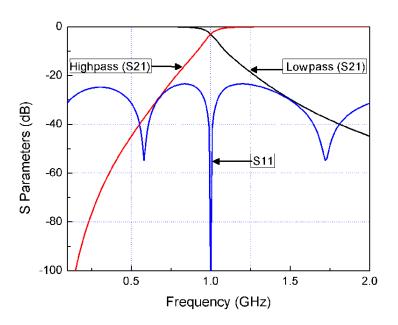

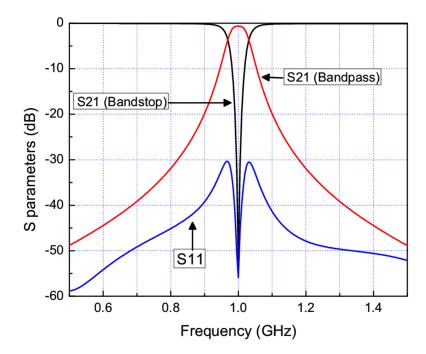

| Figure 3.3  | Simulation results of a $5^{th}$ order 0.5 dB ripple 1 GHz                   |    |

|             | $\label{eq:chebyshev} Chebyshev\ lowpass/highpass\ complementary\ diplexer.$ |    |

|             | 65                                                                           |    |

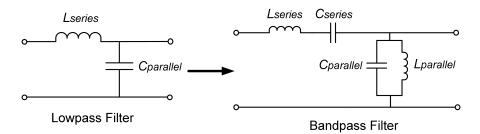

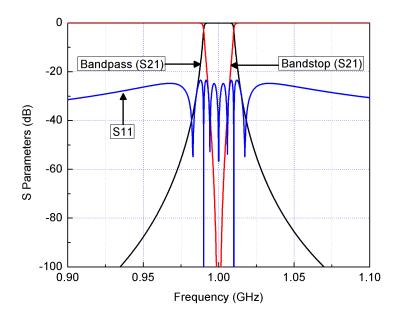

| Figure 3.4  | Circuit diagram showing the conversion procedure from                        |    |

|             | a low<br>pass filter to a bandpass filter. $\hdots$                          | 65 |

| Figure 3.5  | Circuit diagram showing the conversion procedure from                        |    |

|             | a highpass filter to a bandstop filter. $\ldots$                             | 66 |

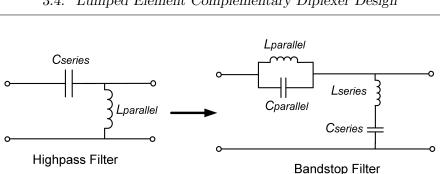

| Figure 3.6  | Circuit diagram of a $5^{th}$ order 0.5 dB ripple 1 GHz                      |    |

|             | $Chebyshev \ bandpass/bandstop \ complementary \ diplexer$                   |    |

|             | with $2\%$ bandwidth                                                         | 67 |

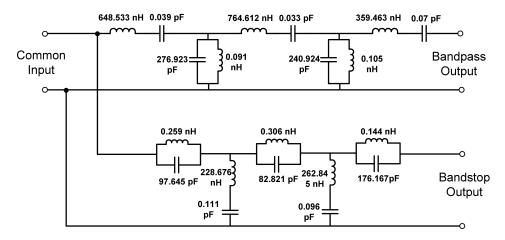

| Figure 3.7  | Simulation results of a $5^{th}$ order 0.5 dB ripple 1 GHz                   |    |

|             | $Chebyshev \ bandpass/bandstop \ complementary \ diplexer$                   |    |

|             | with $2\%$ bandwidth                                                         | 68 |

xii

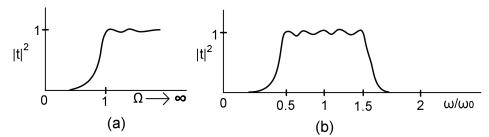

| Figure 3.8  | Mapping properties of the transformation $\Omega = \tan \frac{\pi \omega}{2\omega_0}$ |    |

|-------------|---------------------------------------------------------------------------------------|----|

|             | (a) Prototype lumped element highpass (b) Corre-                                      |    |

|             | sponding distributed element bandpass                                                 | 69 |

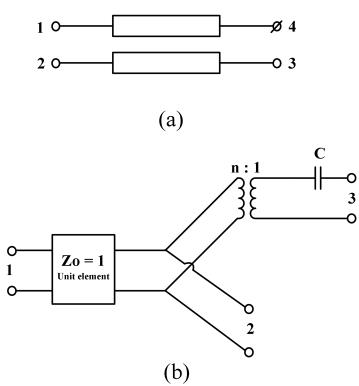

| Figure 3.9  | Parallel connection for bandpass/bandstop comple-                                     |    |

|             | mentary diplexer (a) Physical realization (b) Equiva-                                 |    |

|             | lent circuit                                                                          | 71 |

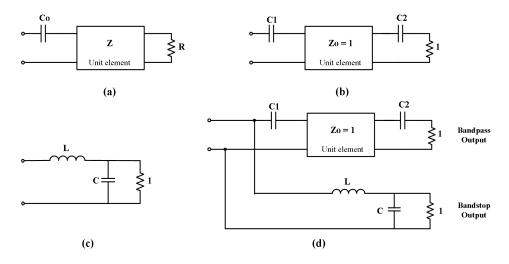

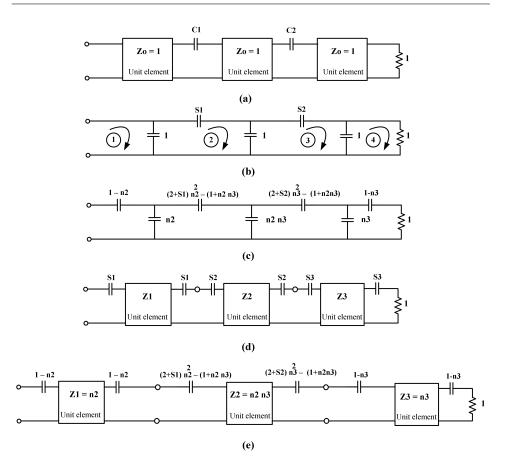

| Figure 3.10 | (a) Equivalent circuit for a non-redundant singly ter-                                |    |

|             | minated bandpass filter section. (b) Bandpass filter                                  |    |

|             | with the addition of a redundant unit element to re-                                  |    |

|             | store the terminal impedance to unity. (c) Singly ter-                                |    |

|             | minated lumped element lowpass (distributed element                                   |    |

|             | bandstop) filter. (d) Equivalent circuit of the final                                 |    |

|             | diplexer with no redundant unit elements                                              | 74 |

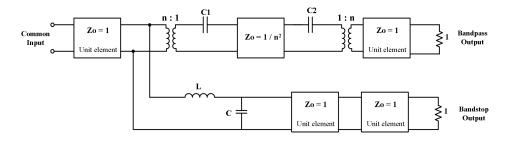

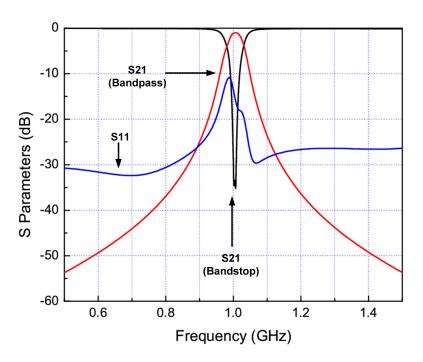

| Figure 3.11 | Practical diplexer equivalent circuit                                                 | 76 |

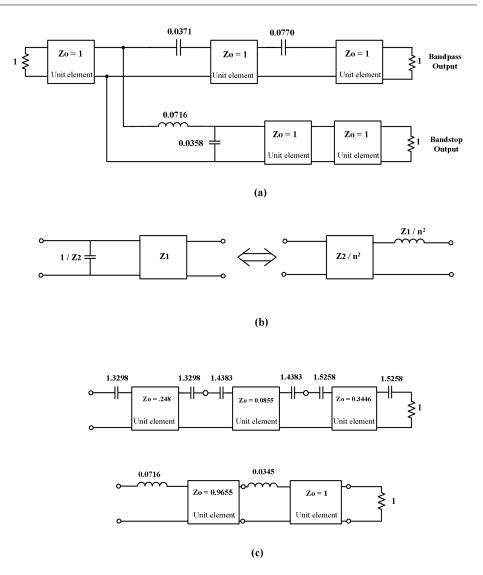

| Figure 3.12 | Design of a two-section complementary diplexer for                                    |    |

|             | a center frequency of 1 GHz and $5.75\%$ bandwidth.                                   |    |

|             | (a) Equivalent circuit for a two-section diplexer. (b)                                |    |

|             | One of the Kuroda's identity. (c) $S$ - plane equivalent                              |    |

|             | circuit filter branches                                                               | 77 |

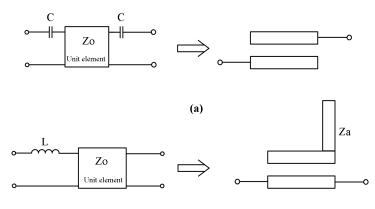

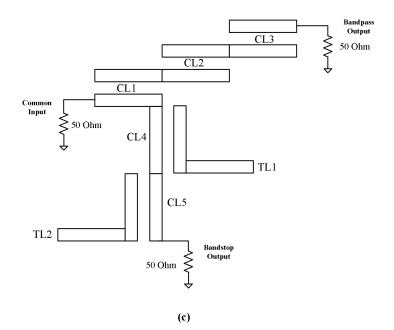

| Figure 3.13 | (a) Bandpass section equivalent circuit for equal strip                               |    |

|             | width coupled lines. (b)Bandstop section equivalent                                   |    |

|             | circuit for equal strip width coupled lines. (c) Com-                                 |    |

|             | plete physical realization of the stripline complemen-                                |    |

|             | tary diplexer (not drawn to scale)                                                    | 79 |

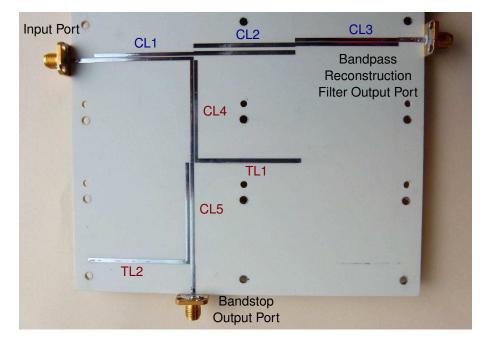

| Figure 3.14 | Photograph of the stripline complementary diplexer                                    | 81 |

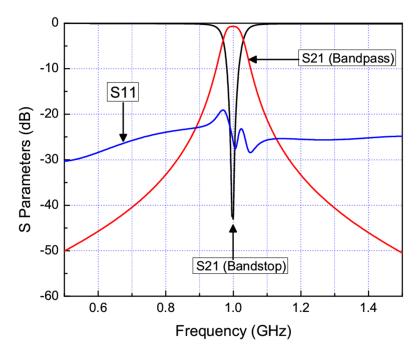

| Figure 3.15 | Simulated results for the complementary diplexer us-                                  |    |

|             | ing schematic models.                                                                 | 82 |

|             |                                                                                       |    |

| Figure 3.16 | Simulated results for the complementary diplexer us-                  |    |

|-------------|-----------------------------------------------------------------------|----|

|             | ing an electromagnetic simulator (Momentum)                           | 83 |

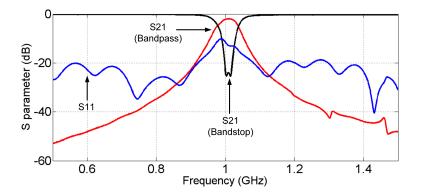

| Figure 3.17 | Measured results for the complementary diplexer                       | 83 |

| Figure 3.18 | Simulated results for the complementary diplexer us-                  |    |

|             | ing Momentum and assuming a 2 mil over etch. $\ . \ .$ .              | 85 |

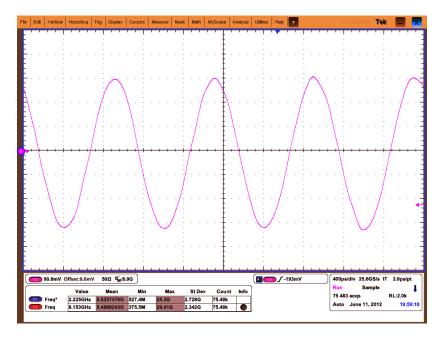

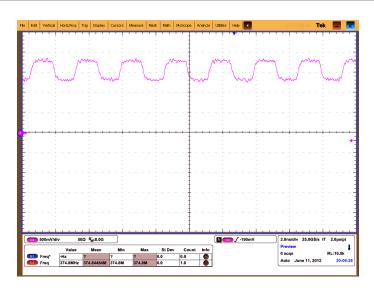

| Figure 4.1  | A 0 dBm 1 GHz sinusoidal source signal measured                       |    |

|             | with a high speed oscilloscope                                        | 87 |

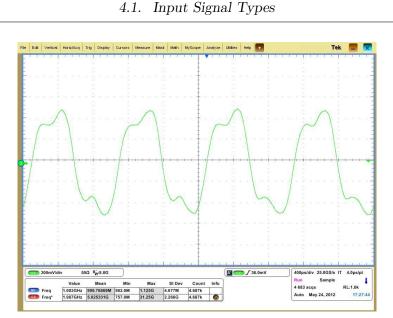

| Figure 4.2  | Measured driver response for a 1 GHz CW input sig-                    |    |

|             | nal across a 50 $\Omega$ load. $\hdots$                               | 88 |

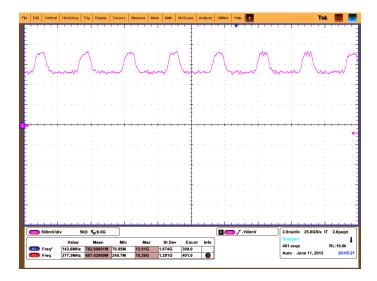

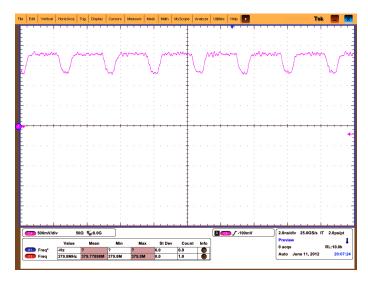

| Figure 4.3  | Periodic pulse train with a $25\%$ duty cycle at a fre-               |    |

|             | quency of 375 MHz                                                     | 89 |

| Figure 4.4  | Periodic pulse train with a 50% duty cycle at a fre-                  |    |

|             | quency of 375 MHz                                                     | 90 |

| Figure 4.5  | Periodic pulse train with a $75\%$ duty cycle at a fre-               |    |

|             | quency of 375 MHz                                                     | 90 |

| Figure 4.6  | Periodic pulse train with a combination of $25\%$ and                 |    |

|             | 75% duty cycle at a frequency of 375 MHz                              | 91 |

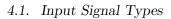

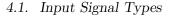

| Figure 4.7  | A pseudo-random bit sequence (PRBS) generated by                      |    |

|             | a Centallax TG1B1-A 10G bit error rate test unit.                     |    |

|             | The clock frequency is 1 GHz                                          | 92 |

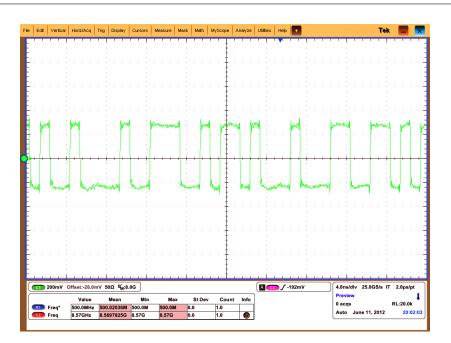

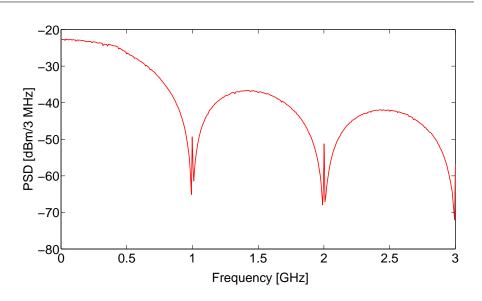

| Figure 4.8  | Measured power spectral density (PDS) of the PRBS                     |    |

|             | generator at 1 GHz frequency.                                         | 93 |

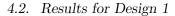

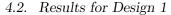

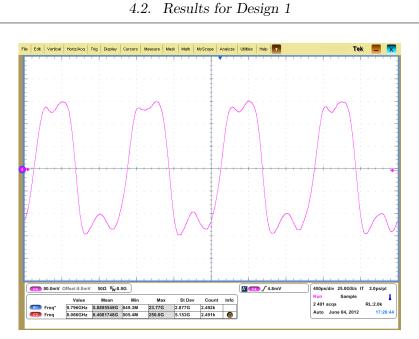

| Figure 4.9  | Measured output voltage waveform at node C in De-                     |    |

|             | sign 1 for a 1 GHz CW input signal. The drain voltage $% \mathcal{C}$ |    |

|             | is 25 V                                                               | 94 |

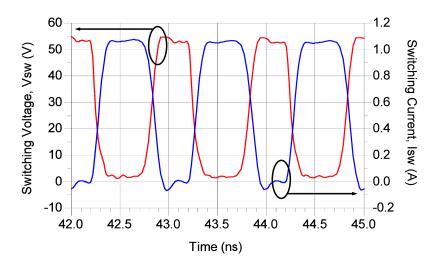

| Figure 4.10 | Simulated switching voltage and current waveforms                           |

|-------------|-----------------------------------------------------------------------------|

|             | at node B for a 1 GHz CW input signal 94                                    |

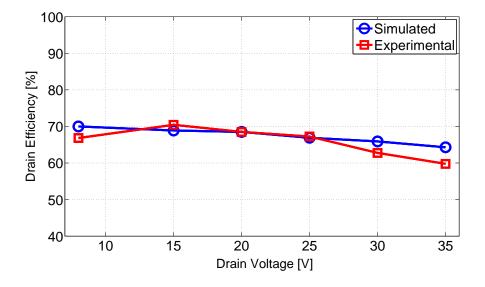

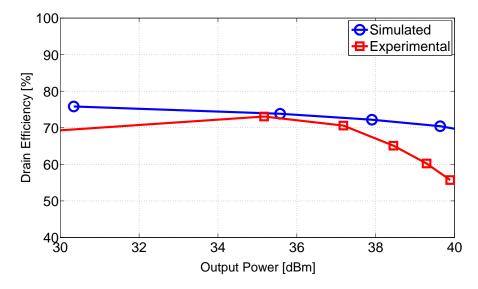

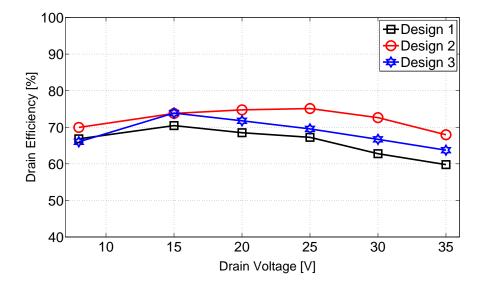

| Figure 4.11 | Drain efficiency versus drain voltage for a CW source                       |

|             | signal at 1 GHz. Measured and simulated data are                            |

|             | shown                                                                       |

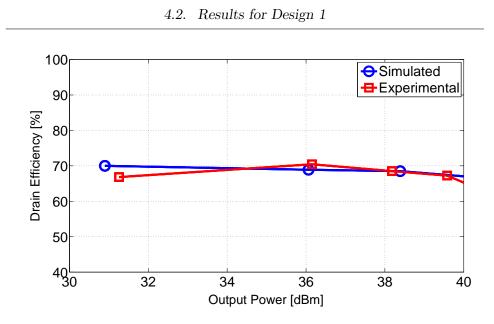

| Figure 4.12 | Drain efficiency versus output power for a CW source                        |

|             | signal at 1 GHz. Measured and simulated data are                            |

|             | shown                                                                       |

| Figure 4.13 | Comparison of the measured drain efficiency versus                          |

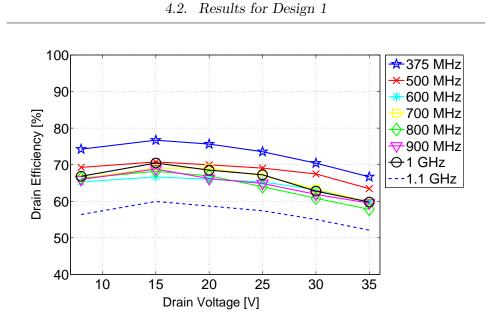

|             | drain voltage for different CW frequencies 98                               |

| Figure 4.14 | Comparison of the measured drain efficiency versus                          |

|             | output power for different CW frequencies 98                                |

| Figure 4.15 | Measured waveforms for a 375 MHz input signal with $% \lambda = 10^{-10}$   |

|             | alternating $25\%$ and $75\%$ duty cycle pulses. The top                    |

|             | trace is the input signal from the FPGA board and                           |

|             | the bottom signal is the output waveform at node C                          |

|             | in the SMPA                                                                 |

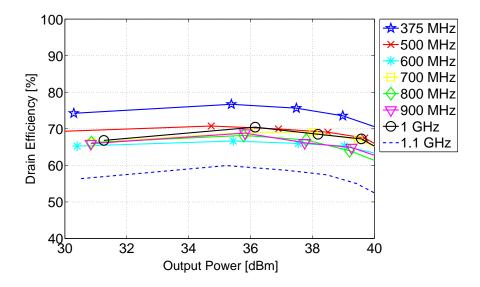

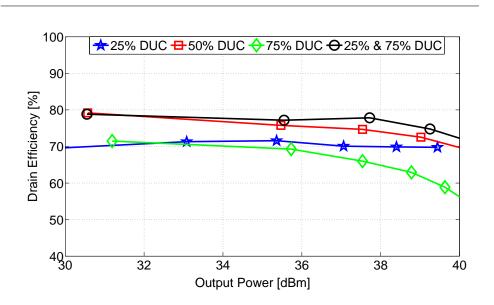

| Figure 4.16 | Drain efficiency versus output power at 375 MHz for                         |

|             | different duty cycles (DUC means duty cycle) 102                            |

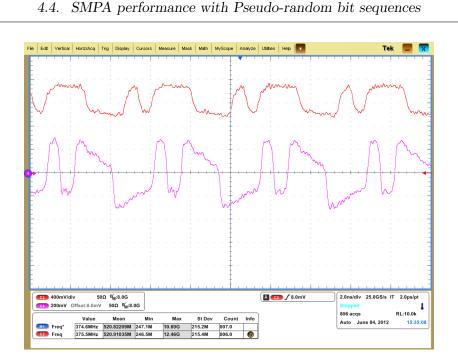

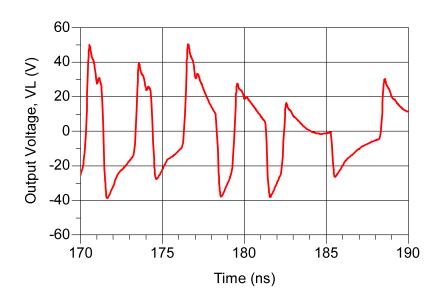

| Figure 4.17 | Measured output voltage waveform at node C for a                            |

|             | 1 GHz PRBS input signal. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $102$ |

| Figure 4.18 | Simulated output voltage waveform at node C for a                           |

|             | 1 GHz PRBS input signal. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 103   |

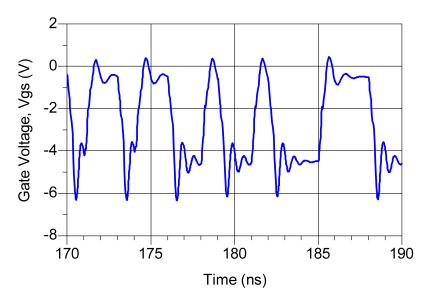

| Figure 4.19 | Simulated gate voltage waveform for a 1 GHz PRBS                            |

|             | input signal                                                                |

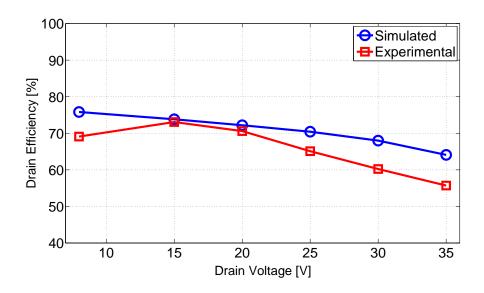

| Figure 4.20 | Drain efficiency versus drain voltage for a PRBS source                          |  |  |  |  |

|-------------|----------------------------------------------------------------------------------|--|--|--|--|

|             | signal at 1 GHz. Measured and simulated data are                                 |  |  |  |  |

|             | shown                                                                            |  |  |  |  |

| Figure 4.21 | Drain efficiency versus output power for a PRBS source                           |  |  |  |  |

|             | signal at 1 GHz. Measured and simulated data are                                 |  |  |  |  |

|             | shown                                                                            |  |  |  |  |

| Figure 4.22 | Measured drain efficiency versus drain voltage for dif-                          |  |  |  |  |

|             | ferent PRBS data rates                                                           |  |  |  |  |

| Figure 4.23 | Measured drain efficiency versus output power for dif-                           |  |  |  |  |

|             | ferent PRBS data rates                                                           |  |  |  |  |

| Figure 4.24 | Measured output voltage waveform at node C for a                                 |  |  |  |  |

|             | 1 GHz CW input signal                                                            |  |  |  |  |

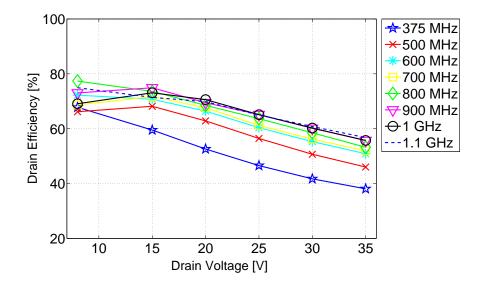

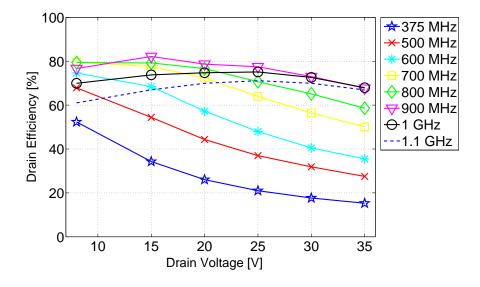

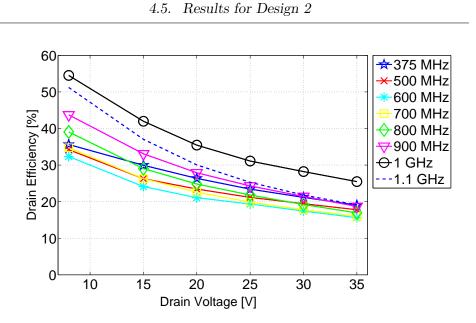

| Figure 4.25 | Comparison of the measured drain efficiency versus                               |  |  |  |  |

|             | drain voltage for different CW frequencies 108                                   |  |  |  |  |

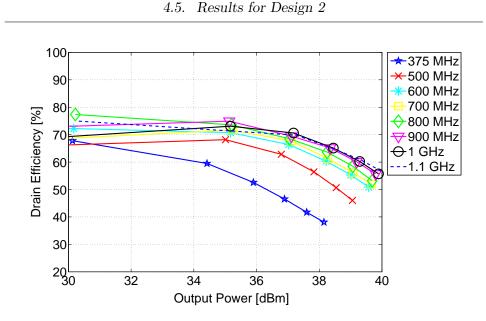

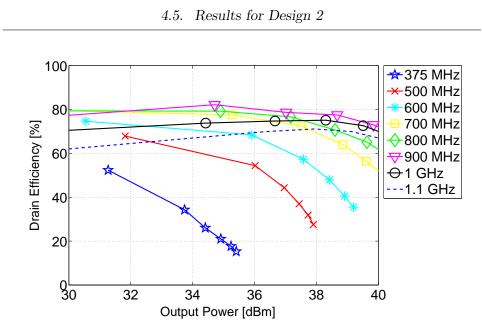

| Figure 4.26 | Comparison of the measured drain efficiency versus                               |  |  |  |  |

|             | output power for different CW frequencies 109                                    |  |  |  |  |

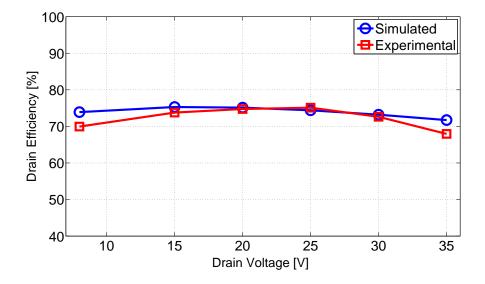

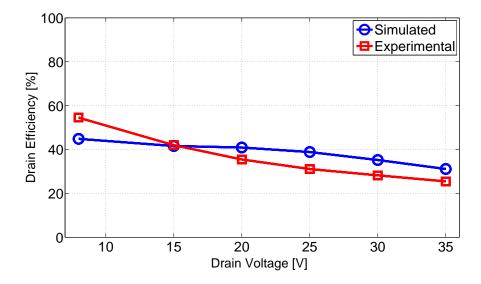

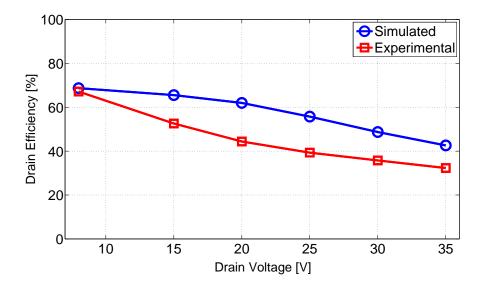

| Figure 4.27 | Drain efficiency versus drain voltage for a CW source                            |  |  |  |  |

|             | signal at 1 GHz. Measured and simulated data are                                 |  |  |  |  |

|             | shown                                                                            |  |  |  |  |

| Figure 4.28 | Measured drain efficiency versus drain voltage for dif-                          |  |  |  |  |

|             | ferent PRBS data rates                                                           |  |  |  |  |

| Figure 4.29 | Comparison of simulated and experimental results for                             |  |  |  |  |

|             | Design 2 using a PRBS source signal at 1 GHz 110                                 |  |  |  |  |

| Figure 4.30 | Measured output voltage waveform at 1 GHz frequency $% \mathcal{T}_{\mathrm{S}}$ |  |  |  |  |

|             | for CW excitation                                                                |  |  |  |  |

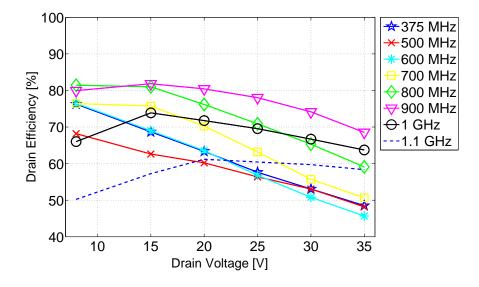

| Figure 4.31 | Comparison of the measured drain efficiency versus                               |  |  |  |  |

|             | drain voltage for different CW frequencies 112                                   |  |  |  |  |

|             |                                                                                  |  |  |  |  |

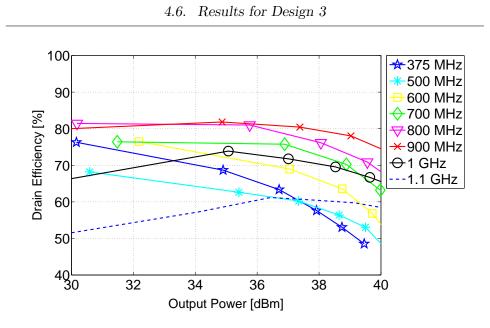

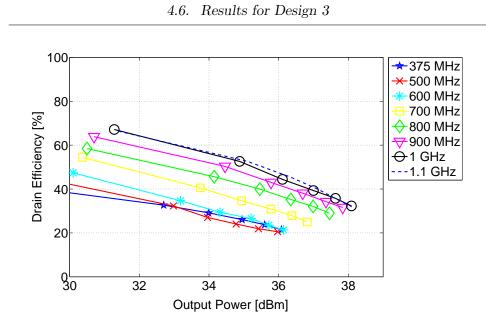

| Figure 4.32 | Comparison of the measured drain efficiency versus                 |

|-------------|--------------------------------------------------------------------|

|             | output power for different CW frequencies 113                      |

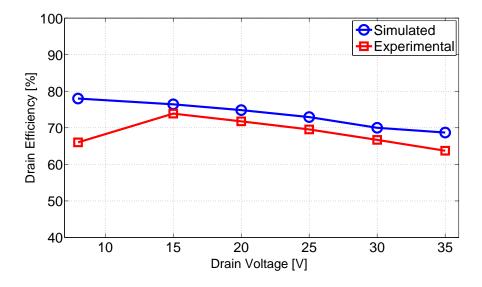

| Figure 4.33 | Drain efficiency versus drain voltage for a CW source              |

|             | signal at 1 GHz. Measured and simulated data are                   |

|             | shown                                                              |

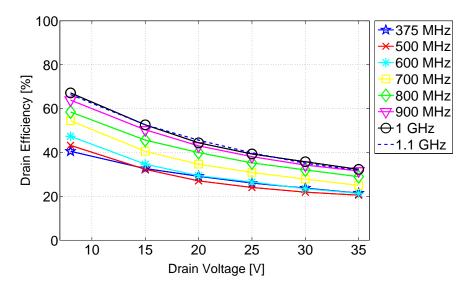

| Figure 4.34 | Comparison of the measured drain efficiency versus                 |

|             | drain voltage for PRBS pulse trains                                |

| Figure 4.35 | Comparison of the measured drain efficiency versus                 |

|             | output power for PRBS pulse trains                                 |

| Figure 4.36 | Drain efficiency versus drain voltage for a PRBS source            |

|             | signal at 1 GHz. Measured and simulated data are                   |

|             | shown                                                              |

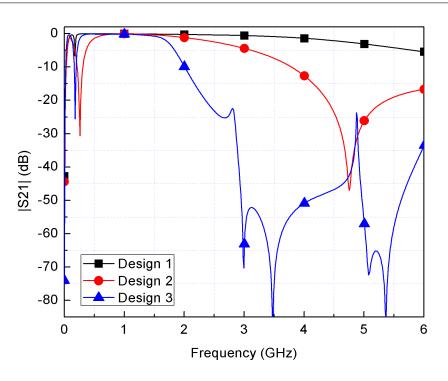

| Figure 4.37 | Output network bandwidth comparison for the three                  |

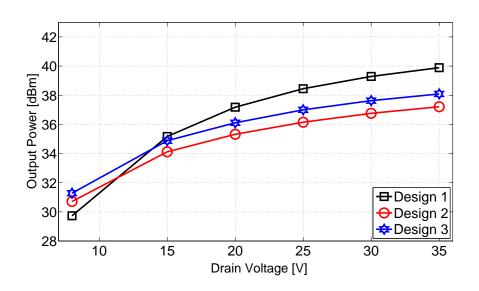

|             | SMPA designs                                                       |

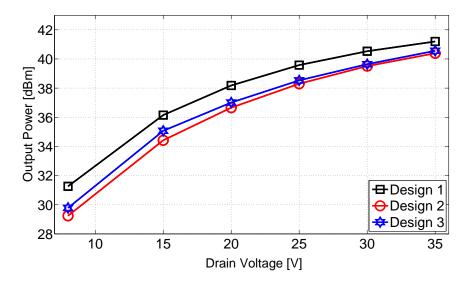

| Figure 4.38 | Comparison of measured output power for SMPA de-                   |

|             | signs at 1 GHz with a CW signal. $\ldots \ldots \ldots \ldots 118$ |

| Figure 4.39 | Comparison of measured drain efficiency for three dif-             |

|             | ferent design at 1 GHz CW frequency                                |

| Figure 4.40 | Comparison of measured output power for SMPA de-                   |

|             | signs with a 1 Gb/s PRBS signal. $\ldots$                          |

| Figure 4.41 | Comparison of measured drain efficiency for SMPA                   |

|             | designs with a 1 Gb/s PRBS signal                                  |

| Figure 4.42 | Circuit diagram of the Design 1 SMPA with a com-                   |

|             | plementary diplexer                                                |

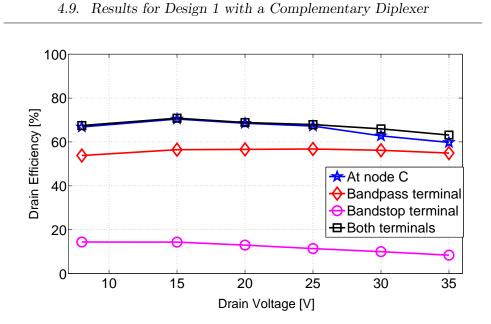

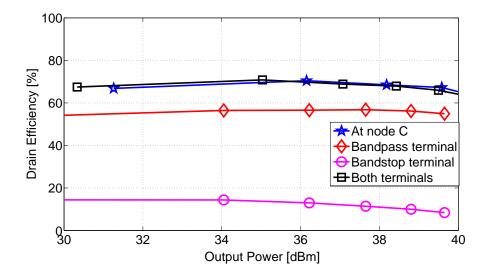

| Figure 4.43 | Drain efficiency for Design 1 with complementary band-             |

|             | pass/bandstop diplexer                                             |

| Figure 4.44 | Output power versus drain efficiency for Design 1 with      |  |  |

|-------------|-------------------------------------------------------------|--|--|

|             | a complementary diplexer                                    |  |  |

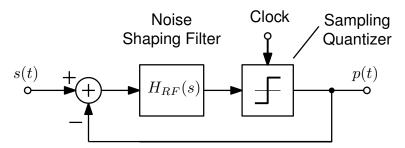

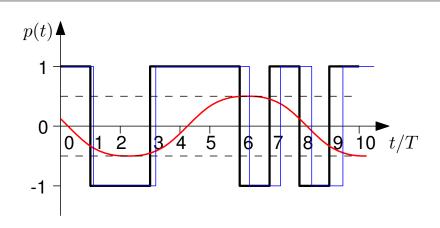

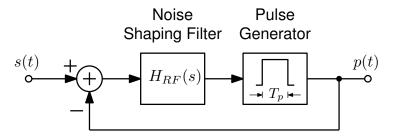

| Figure 5.1  | Block diagram of a sigma-delta modulator (SDM) 126 $$       |  |  |

| Figure 5.2  | Timing diagram of the pulse encoded signals. Black          |  |  |

|             | (thick) line shows the sigma-delta pulse trains and         |  |  |

|             | blue (thin) line shows the pulse position pulse trains. 128 |  |  |

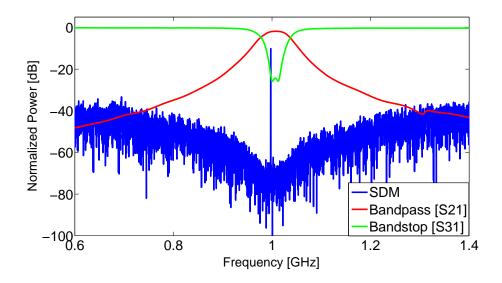

| Figure 5.3  | Output power spectrum of sigma-delta modulator with         |  |  |

|             | diplexer                                                    |  |  |

| Figure 5.4  | Block diagram of a pulse position modulator (PPM). 129      |  |  |

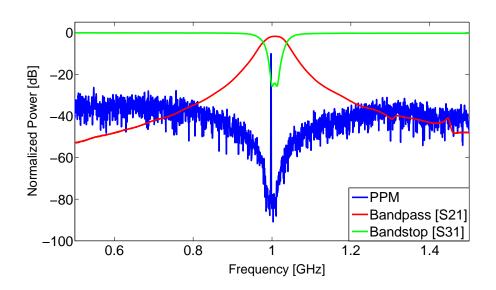

| Figure 5.5  | Output power spectrum of pulse position modulated           |  |  |

|             | signal with diplexer                                        |  |  |

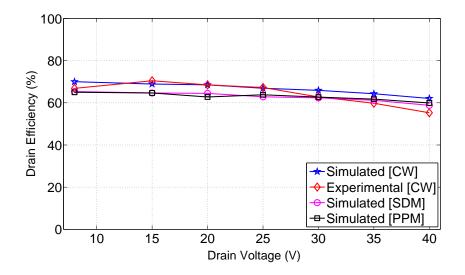

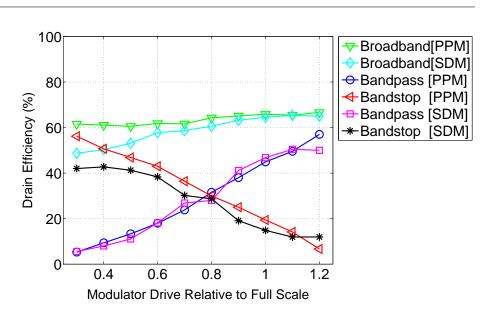

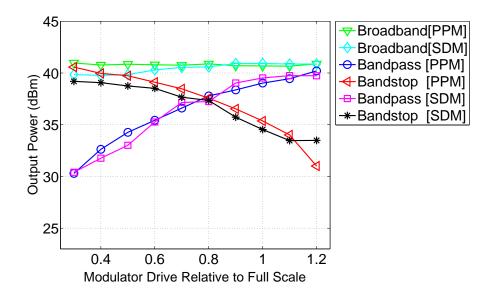

| Figure 5.6  | Drain efficiency for Design 1 for SDM, PPM and si-          |  |  |

|             | nusoidal signals                                            |  |  |

| Figure 5.7  | Drain efficiency as a function of modulator drive level     |  |  |

|             | for SDM and PPM encoders                                    |  |  |

| Figure 5.8  | Output power as a function of modulator drive level         |  |  |

|             | for SDM and PPM encoders                                    |  |  |

| Figure 6.1  | Block diagram of the proposed energy recycling cir-         |  |  |

| 0           | cuitry                                                      |  |  |

| Figure 6.2  | Drain efficiency for Design 1 assuming 75% out-of-          |  |  |

| 0           | band energy is recovered                                    |  |  |

|             |                                                             |  |  |

xviii

# List of Acronyms

| Alternating Current                               |  |  |  |  |

|---------------------------------------------------|--|--|--|--|

| Advanced Design System                            |  |  |  |  |

| Bit Error Rate Test                               |  |  |  |  |

| Current-mode Class D                              |  |  |  |  |

| Continuous Wave                                   |  |  |  |  |

| Direct Current                                    |  |  |  |  |

| Field Programmable Gate Array                     |  |  |  |  |

| Gallium Nitride                                   |  |  |  |  |

| High Electron Mobility Transistor                 |  |  |  |  |

| Hard Switched                                     |  |  |  |  |

| Institute of Electrical and Electronics Engineers |  |  |  |  |

| Input/Output                                      |  |  |  |  |

| Microwave Theory and Techniques Society           |  |  |  |  |

| Peak to Average Power Ratio                       |  |  |  |  |

| Pulse Position Modulation                         |  |  |  |  |

| Pseudo Random Bit Sequence                        |  |  |  |  |

| Power Spectral Density                            |  |  |  |  |

| Radio Frequency                                   |  |  |  |  |

| Root Mean Square                                  |  |  |  |  |

| Sigma Delta Modulation                            |  |  |  |  |

| Switch-mode Power Amplifier                       |  |  |  |  |

| Transverse Electromagnetic                        |  |  |  |  |

| Voltage-mode Class D                              |  |  |  |  |

|                                                   |  |  |  |  |

### Acknowledgements

This thesis would not have been possible without the help and support of my colleagues, friends, and family.

I am heartily thankful to my supervisor, Dr. Thomas Johnson, for both inspiring and teaching me. He has provided constant encouragement, guidance and support throughout my thesis. He has introduced me to the art of scientific research, the beauty of good experimental design, the value of explaining numerical results not only as mathematical constructs, but also through physical interpretation, the subtlety of clear and accessible scientific writing, the rigors of analytical ability and adherence, and the spirit of intellectual integrity.

I am indebted to many of my colleagues for their support throughout the work and writing.

I would like to also thank NSERC for funding this research project, Agilent for providing simulation tools and Cree Inc. for providing a large signal model for the GaN device used in this work. To my family, who, of all that walk on the earth, are most precious to me, for their support in every endeavor.

### Chapter 1

### Introduction

Research in switch-mode power amplifiers (SMPAs) for wireless applications has been active for the last decade. Despite advances in the implementation of radio frequency (RF) switch-mode power amplifiers, realizing high efficiency circuits has been challenging. At the same time, advances in analog based RF power amplifiers has also continued and drain efficiencies in excess of 50% have been reported for modulated signals. If RF switch-mode technology is to provide a compelling alternative to analog techniques, it clearly must have advantages including competitive power efficiency.

Most RF SMPAs have been based on class D circuit topologies. Variations include current mode class D (CMCD) [1], voltage mode class D (VMCD) [2], and class S [3–5] circuit topologies. Class S is similar to class D except diodes are added to protect the switches under non-periodic switching conditions. Performance limitations in these circuits include power loss mechanisms from parasitic capacitance and inductance, power loss in diodes, low power efficiency under back-off conditions, voltage peaking across the switching device including third quadrant device operation, and power loss related to shoot through current. Although further research will undoubtedly continue to bring improvements to RF SMPA's based on class D circuits, it is interesting to consider whether there are other approaches that could be taken to implement switch-mode designs that may lead to more power efficient designs.

The RF SMPA architecture presented in this work evolved from a reflection on the challenges in realizing RF class D amplifiers that can efficiently amplify non-periodic pulse trains. In theory, the operation of a current mode class D amplifier requires a load network that is a short for all out-of-band frequency components and is matched for in-band frequency components. A VMCD amplifier is the dual of CMCD and requires an open for all out-of-band frequencies. When class D is driven with non-periodic pulse trains such as a bandpass sigma-delta modulated signal, the source signal is encoded in a noise well and quantization noise rises sharply outside the noise well. A significant challenge in class D is to present a narrow-band match at the device plane which shorts the spectrum adjacent to the noise well while simultaneously matching the in-band spectrum. Improper out-ofband termination impedances create dissipation of out-of-band spectra and consequently power efficiency is reduced. The problem becomes particularly acute when the encoded signal has low coding efficiency and most of the spectrum is out-of-band.

Starting with an exclusive focus on creating impedance conditions that minimize power loss in the switch, a purely resistive load that is broadband is beneficial. Under these conditions, the switch is either on, off, or transitions between states. On and off state losses are similar to class D, however, the relationship between device current and device voltage during transitions is now consistent and predictable for any pulse waveform. In other words, current and voltage are orthogonal for *any* pulse train and transition losses are predictable. The key point is that the phase of the current and voltage is controlled unlike a class D amplifier which has uncontrolled phase relationships when switched with non-periodic signals. Although low device dissipation in the switch is obtained with a broadband match, the obvious disadvantage is that out-of-band power is now delivered to the load. The question then is: can we mitigate the loss of power efficiency created by power in the out-of-band spectrum? It is this question along with the goal of improving the power efficiency of RF SMPAs that motivates this research.

In the following sections of this chapter, background on switch-mode power amplifiers along with a literature review are given. The research objectives are then presented and the chapter concludes with a summary of contributions.

### 1.1 Background on RF Switch-mode Power Amplifiers

A high level block diagram of the RF switch-mode power amplifier architecture is shown in Figure 1.1. An analog input signal called the source signal is encoded and converted into a two level binary digital signal. The source signal can be a periodic (CW) signal or a non-periodic (modulated) signal. Depending on the type of encoder used, the output pulse train is also periodic for unmodulated carrier signals and non-periodic for modulated signals. However, regardless of the source signal type, all the information is encoded by the timing of level transitions in the binary amplitude pulse train. A periodic signal has a pulse sequence that repeats while a nonperiodic sequence has pulse widths that continuously change depending on the amplitude and phase of the source signal. If the analog input signal is a periodic signal, then after encoding, the signal will be a pure square wave signal which means it is also a periodic signal. On the other hand,

Figure 1.1: Basic block diagram of a RF switch-mode power amplifier system (only non-periodic signals are shown).

if the analog input signal is a non-periodic signal (modulated), then after encoding it will be a square wave signal with different pulse widths which means it is a non-periodic signal. After encoding, a switch-mode power amplifier amplifies the encoded signal. Finally, a reconstruction filter extracts the original analog signal from the amplified version so that it can be transmitted through the antenna.

Therefore a RF switch-mode power amplifier is a type of electronic amplifier used to convert a low-power RF signal into a larger signal of significant power, typically for driving the antenna of a transmitter. Design objectives for a power amplifier include:

- high efficiency (low device dissipation);

- high output power;

- good return loss at the input and output;

- high gain.

In a switch-mode power amplifier the power device is designed to operated as a binary switch defined by an on state and an off state. It is either fully on or fully off. Ideally zero time is spent transitioning between two states. Figure 1.2 shows the ideal switching waveforms across the device. The current and voltage waveforms are orthogonal which means that no power is dissipated in the device and the amplifier is ideally 100% efficient.

Figure 1.2: Switching characteristics of the RF switch-mode power amplifier.

#### 1.1.1 Class D Switch-mode Power Amplifier

A class D power amplifier employs a pair of active devices operating in a push-pull mode with a tuned output circuit. The active devices are driven to act as a two-pole switch that creates a rectangular voltage waveform called voltage switching or a rectangular current waveform called current switching. The output circuit is tuned to the switching frequency and harmonic components are attenuated resulting in a purely sinusoidal signal delivered to the load. In theory, a class D amplifier should not dissipate any power in the harmonic components and the amplifier should have very high efficiency. Let us now consider the basic principles, circuit schematics, and voltage-current waveforms corresponding to the different types of class D power amplifiers.

#### Voltage Mode Class D power amplifier (VMCD)

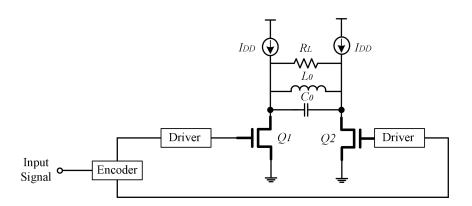

Figure 1.3 shows the simplified circuit diagram of a voltage mode class D (VMCD) power amplifier. Two transistors ( $Q_1$  and  $Q_2$ ) are driven 180 degrees out-of-phase. A series LC filter, consisting of components  $L_0$  and  $C_0$ , is employed with a resonant frequency set to the center frequency of the signal. Providing the filter has sufficient selectivity, the VMCD amplifier is matched for in-band frequencies and open for all out-of-band frequencies. Ideal drain voltage and drain current waveforms are shown in Figure 1.4. The voltage across the transistors is a square wave (switched) while the current is a half-wave rectified sine wave. The push pull action of  $Q_1$  and  $Q_2$  will combine to create a load current that is a full-wave sine wave. The conditions shown in this figure correspond to a periodic switching signal with a 50% duty cycle. Implementation challenges in practical class D circuits at high frequencies include the design of a high side driver for  $Q_1$  and high Q output filters to provide an effective open at harmonic or out-of-band frequencies.

Figure 1.3: Circuit diagram of a voltage mode class D (VMCD) power amplifier.

#### Current Mode Class D power amplifier (CMCD)

Figure 1.5 shows the simplified circuit diagram of a current mode class D (CMCD) power amplifier. In this case, drain bias is provided by current sources instead of voltage sources which are used in VMCD, and the two switching transistors ( $Q_1$  and  $Q_2$ ) control the current instead of the voltage. There is a parallel-connected filter with a resonant frequency set to the center frequency. Therefore, the operation of the CMCD amplifier requires a load network that is a short for all out-of-band frequency components and is matched for in-band frequency components. Figure 1.6 shows the ideal current and voltage waveforms of the transistors. There is no voltage across the transistors at each switching time. Hence, ideally, the efficiency is 100%.

#### Periodic vs Non-periodic Switching Condition in Class D

Under periodic switching conditions with a 50% duty cycle, the switchmode class D (CMCD or VMCD) circuit design is configured to generate

Figure 1.4: Voltage and current waveforms of a voltage mode class D (VMCD) power amplifier.

Figure 1.5: Circuit diagram of a current mode class D (CMCD) power amplifier.

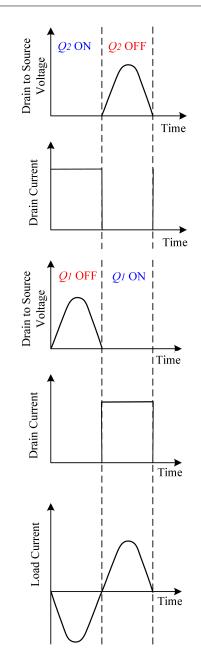

zero voltage or zero current switching, a condition that minimizes switching losses. On the other hand, non-periodic switching conditions destroy the zero voltage or current switching conditions. For non-periodic switching, the relationship between the voltage across the switching device and the current through the device is arbitrary. These arbitrary switching conditions lead to significantly higher switching losses. In addition, for non-periodic pulse trains, the source signal is encoded in a noise well and the quantization noise rises sharply outside the noise well. An example of an encoded pulse train signal is shown in Figure 1.7.

It is very challenging to construct a narrow-band match at the device plane which shorts the spectrum adjacent to the noise well while simultaneously matching the in-band spectrum. Improper out-of-band termination impedances create dissipation of out-of-band spectra which can reduce power efficiency significantly. This out-of-band mismatch problem becomes severe when the encoded signal has low coding efficiency. Wireless communication source signals have large amplitude variation which means that the average power in the encoded spectrum is much lower than peak power. As signal

Figure 1.6: Voltage and current waveforms of a current mode class D (CMCD) power amplifier.

1.1. Background on RF Switch-mode Power Amplifiers

Figure 1.7: Power spectral density of a 1 GHz pulse encoded signal. An overlay of a narrow-band bandpass reconstruction filter is also shown.

power is backed-off relative to peak power, coding efficiency is low and consequently power efficiency can degrade significantly. The reduction in power efficiency under non-periodic switching conditions is a major limitation of class D power amplifiers especially in very high frequency applications.

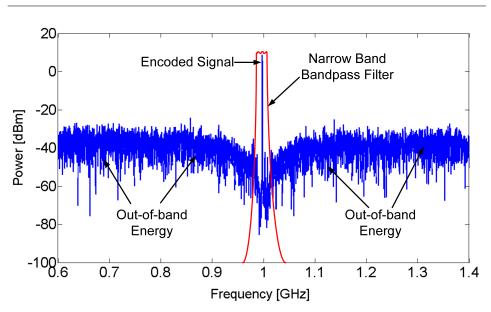

#### 1.1.2 Class S Switch-mode Power Amplifier

Class S is similar to class D except diodes are added to protect the switches under non-periodic switching conditions. Figure 1.8 shows a voltage mode class S power amplifier. Two diodes  $(D_1 \text{ and } D_2)$  are added across the two transistors  $(Q_1 \text{ and } Q_2)$  to protect the switches from voltage peaking and third quadrant transistor operation. However, diode losses can reduce the overall power efficiency significantly. The working principles of the current mode (CM) and voltage mode (VM) class S are similar to CMCD and VMCD respectively.

Therefore, in a summary, the limitations of the class D and class S switch-mode power amplifiers are:

- simultaneous in-band and out-of-band match is required;

- low power efficiency under wide back-off conditions;

- voltage peaking across the switching device including third quadrant device operation;

- power loss in protection diodes;

- power loss related to shoot through current;

- implementation challenges with output baluns and high swing drivers;

- two devices are required.

Figure 1.8: Circuit diagram of a voltage mode class S power amplifier.

| Frequency              | Drain Efficiency | Power             | Topology        | Year | Author |

|------------------------|------------------|-------------------|-----------------|------|--------|

| 420 MHz                | 59%              | 19 W              | CM class S      | 2010 | [3]    |

| 400  MHz               | 64%              | $7 \mathrm{W}$    | VM class S      | 2011 | [4]    |

| 800  MHz               | 74%              | $62 \mathrm{W}$   | Class E         | 2010 | [7]    |

| 550-1100  MHz          | 74%              | $10.5 \mathrm{W}$ | Class F         | 2010 | [8]    |

| $3.27~\mathrm{GHz}$    | 71%              | $5 \mathrm{W}$    | Inverse class F | 2009 | [9]    |

| $1 \mathrm{~GHz}$      | 83%              | $10 \mathrm{W}$   | Inverse class F | 2009 | [10]   |

| $2.3-2.7~\mathrm{GHz}$ | 60-68%           | $10 \mathrm{W}$   | Class J         | 2011 | [11]   |

| $850 \mathrm{~MHz}$    | 73%              | $81 \mathrm{W}$   | HS class AB     | 2011 | [6]    |

Table 1.1: Some recent experimental results for periodic switching (CW)

#### 1.2 Literature Review

Table 1.1 shows some recent experimental results based on periodic switching. The peak drain efficiencies range from 60% to 80%. The circuits span a wide range of frequencies from 400 MHz to 2.7 GHz over a wide range of output power from 5 W to 81 W. Different topologies are used and drain efficiency is quite high because the reported results correspond to 50% duty cycle periodic switching.

For wireless applications, we have to consider a modulated source signal, which after encoding, creates non-periodic pulse trains. The results for encoded pulse trains (non-periodic switching) are tabulated in Table 1.2. Many of the recent results are from Wentzel et al. [3–5] where the drain efficiency is around 40% for a frequency 450 MHz. In this work, a class S topology is used with a fourth order bandpass sigma-delta modulator for the source encoder. Other work by Johnson et al. [6] uses a hard switched (HS) class AB amplifier with a fourth order noise shaped asynchronous encoder. A power efficiency of 30% is reported at a power of 20 W for a modulated IS-95A CDMA source signal.

From these two tables, it is very apparent that if a non-periodic pulse

| Table 1.2: Some recent experimental results for non-periodic switching with |

|-----------------------------------------------------------------------------|

| pulse encoded signals.                                                      |

|                                                                             |

| Frequency           | Drain Efficiency | Power             | Topology    | Year | Author |

|---------------------|------------------|-------------------|-------------|------|--------|

| $420 \mathrm{~MHz}$ | 34%              | 8.7 W             | CM class S  | 2010 | [3]    |

| $400 \mathrm{~MHz}$ | 38%              | $3.4 \mathrm{W}$  | VM class S  | 2011 | [4]    |

| $850 \mathrm{~MHz}$ | 30%              | $20.4 \mathrm{W}$ | HS class AB | 2011 | [6]    |

| $450 \mathrm{~MHz}$ | 60%              | $1 \mathrm{W}$    | VM class S  | 2011 | [5]    |

| 450 MHz             | 25%              | 6 dB Back off.    | VM class S  | 2011 | [5]    |

signal is used to drive a switch-mode power amplifier, drain efficiency drops significantly. In other words, although SMPAs have theoretically very high power efficiency, experimental prototypes demonstrating high efficiency have not yet been realized at high frequencies. Another important observation for the results shown in Table 1.2 is the reduction in power as output power is reduced (backed-off) from peak power. Results from Wentzel et al. [5] show 60% peak drain efficiency at 450 MHz, while under 6 dB back-off the drain efficiency drops to 25%. Since many common wireless communication signals have peak to average ratios of 6 to 10 dB, this means the average efficiency for modulated signals will be low. Therefore, research into improving the power efficiency under back-off conditions is required to enable commercial deployment of SMPA technology for wireless applications.

#### **1.3** Motivation and Research Objectives

Class D and Class S circuit topologies have not yielded competitive power efficiency relative to analog power amplifier designs and research is still required to realize a practical high efficiency SMPA for wireless applications. In this research, a new RF SMPA architecture is presented which is motivated by the following objectives:

- to improve the power efficiency of RF switch-mode design under nonperiodic switching conditions;

- to obtain high power efficiency over a wide back-off range (e.g. 10 dB back-off), because existing switch-mode RF power amplifier designs have low power efficiency under back-off conditions;

- to address implementation challenges with RF switch-mode circuits employing class D or class S circuit topologies; these topologies may require high side switch drivers, protection diodes, and baluns.

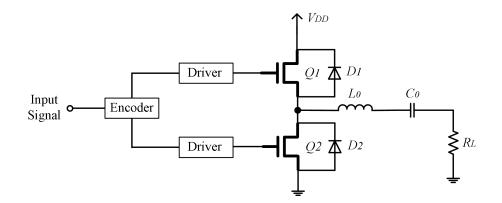

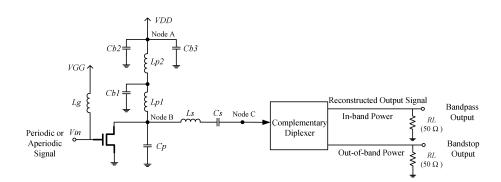

#### **1.4** Contributions

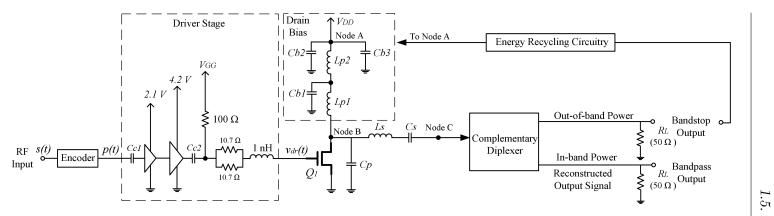

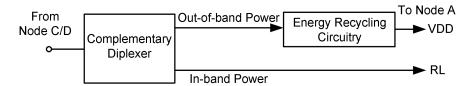

The SMPA concept in this work focuses on implementing a broadband output match across a single switch. A diagram of the overall proposed SMPA amplifier is shown in Figure 1.9. A modulated source signal s(t) is first encoded into a pulse train p(t) that has two amplitude levels which control the state of the power switch  $Q_1$ . The pulse train is amplified by a wide-band driver circuit with a low output impedance to drive the gate of  $Q_1$ . Since the gate is primarily capacitive, the driver sources or sinks charge to switch the device. The output network at the drain node consists of a broadband DC bias feed and a broadband output network. Because the load is broadband, the switch voltage and current waveforms are orthogonal and device dissipation is low. The load consists of a complementary diplexer which has a bandpass filter branch for reconstructing the source signal across the output load and a bandstop branch for capturing out-of-band energy. Unlike reflective filters or split band diplexers, the common input port of a complementary diplexer is matched at all frequencies including the transition bands. The impedance presented by the diplexer input port at node C in Figure 1.9 is approximately equivalent to a broadband 50  $\Omega$  load.

The design of the encoder has important implications on the overall power efficiency of the SMPA. Since the power switch can only replicate two amplitude states, a source signal with amplitude variation must be encoded into a binary amplitude pulse train, amplified, and then recovered at the output after the reconstruction filter. Therefore, the encoder can also be thought of as a way to linearize the hard switched amplifier; it provides a means of reducing the distortion which would otherwise be very severe if the source were to directly drive the gate of the switch. The cost of linearizing the amplifier with a pulse encoder is an expansion in the bandwidth of the source signal. When the source envelope is quantized to two levels, bandwidth expansion is very large.

A figure of merit which is useful for characterizing encoder designs for SMPA applications is to measure the ratio of the in-band signal power to the total power in the pulse train p(t). This measure is called coding efficiency. The coding efficiency of an encoder for a modulated source signal depends on the peak coding efficiency and the peak to average power ratio (PAPR) of the signal. For a source signal with a PAPR of 6 dB, the typical coding efficiency of a bandpass sigma-delta modulator is about 15% which means that 85% of the power is out-of-band. Class D and S amplifier designs ideally do not generate any power in the out of band signal but in practice this is very difficult to achieve.

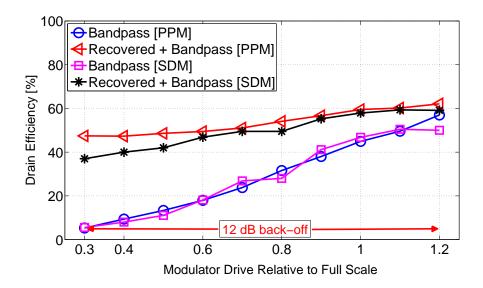

Since out-of-band power is always generated by source encoders, a design is proposed that will recycle out-of-band power from the output of the bandstop diplexer port. If the energy recycling was 100% efficient, this would lead to a SMPA design that would have constant power efficiency independent of the source PAPR. Obviously, 100% conversion efficiency will not be achieved in practice and an analysis of power efficiency assuming 75% conversion efficiency is shown in chapter 6. Even modest conversion efficiency can dramatically improve power efficiency for high PAPR sources, something that is difficult to achieve in class D or class S circuits.

#### 1.5 Thesis Outline

#### Chapter 2: Power Amplifier Design

In Chapter 2, three different switch-mode power amplifier circuit designs are presented. The main goal of this chapter is to describe the design and implementation of these circuits.

#### **Chapter 3: Complementary Diplexer**

In Chapter 3, the theory and implementation of a complementary diplexer is presented. The complementary diplexer is a key component in the proposed SMPA architecture.

#### Chapter 4: Results

In Chapter 4, simulation and experimental results for the three different SMPA circuit designs are described. The chapter concludes with a comparison of measured results for the different circuits.

#### **Chapter 5: Pulse Encoded Responses**

In Chapter 5, simulated results are presented for the amplification of encoded pulse trains using sigma-delta and pulse-position modulated signals. Encoded pulse trains are generated in Matlab and used to predict the power efficiency of the RF SMPA using circuit simulation models.

#### Chapter 6: Energy Recovery

In Chapter 6, background and possibilities to rectify out-of-band energy are presented. Simulation results for the RF SMPA are shown assuming a RF to DC conversion efficiency of 75% could be obtained from these circuits.

#### Chapter 7: Conclusion

A summary of the main conclusions is presented as well as recommendations for future research works.

Figure 1.9: Circuit diagram of the proposed RF switch-mode power amplifier.

## Chapter 2

## Switch-mode Power Amplifier Design

In this chapter three switch-mode power amplifier (SMPA) designs are presented. The designs are called Design 1, Design 2, and Design 3, and become progressively more complicated. A 10 W GaN power device is used as the power switch. The purpose of stepping through each design is to evaluate design trade-offs.

In Design 1, the switching device is directly coupled to a 50  $\Omega$  load without any matching circuit. In other words, the load line for the switching device is 50  $\Omega$ . The motivation for Design 1 is to avoid introducing any bandwidth limitations in the output matching network, and in this case, a 50  $\Omega$  transmission line is all that is used. The output network also includes a DC bias network for supplying power to the drain of the switching device. Therefore, the bandwidth of the output network is primarily limited by the drain bias network. A two stage bias network is used to obtain a broadband output.

In Design 2, the output device capacitance is included in the design of the output network. The DC drain bias inductor is tuned to resonate with the output device capacitance to form a low Q output. As in Design 1, the device is also presented with a 50  $\Omega$  load line to avoid introducing any further bandwidth restrictions created by matching networks.

In Design 3, an output matching network is added to Design 2 to transform the 50  $\Omega$  load to an optimum load impedance of 33.3  $\Omega$  for the switching device. A multistage matching network is used to implement broadband impedance transformations.

Simulated and experimental results for the different designs are presented in later chapters and the purpose of this chapter is to present the design methodology used for implementing the output stage of the SMPA.

## 2.1 Design 1: Broadband RF SMPA with a 50 $\Omega$ Load

#### 2.1.1 Design Considerations

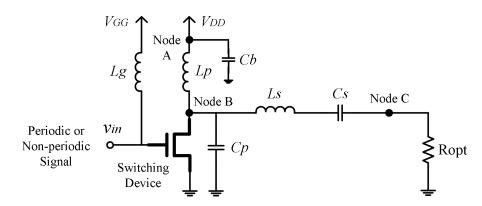

Figure 2.1 shows the circuit diagram of a broadband RF switch-mode power amplifier (SMPA) with a 50  $\Omega$  load. The design is called Design 1, a term which is used throughout this work. The term "broadband load" means that the output network including the drain biasing network  $(L_p)$  is broadband for a certain range of frequencies. In this work, circuits have bandwidths that range from two to five harmonics. In Design 1, the output device capacitance  $C_p$  is neglected and later, in Design 2 and Design 3, the capacitance is integrated into the output network design.

In Design 1, the load is a 50  $\Omega$  impedance which is directly coupled to the switching device through a DC blocking capacitor  $C_s$  and a series inductance  $L_s$ . The series inductor is used to adjust the relative phase of the current and voltage waveforms across the switching device at node B. The drain bias  $V_{DD}$  is provided through a drain bias circuit. Theoretically, the bias network can be modeled by a large inductor  $L_p$  with a bypass capacitor  $C_b$  as shown in Figure 2.1. However, in practice it is difficult to realize a broadband bias network with a single inductor because parasitic capacitance in the inductor will lead to resonances which limits bandwidth. Therefore, a multistage bias network is needed in the design and will be described later.

Figure 2.1: Circuit diagram of the broadband RF switch-mode power amplifier with a 50  $\Omega$  load (Design 1).

#### 2.1.2 The RF Switch

For this work, a 10 W GaN (CGH40010) high electron mobility transistor (HEMT) from Cree Inc. is used as the switching device. The CGH40010 is a wideband unmatched power device. Cree also provides a large signal non-linear device model that is used for circuit modeling. As mentioned earlier, the effect of the output capacitance,  $C_p$ , is neglected in Design 1 and a discussion about the characteristics of  $C_p$  is deferred to section 2.2.2.

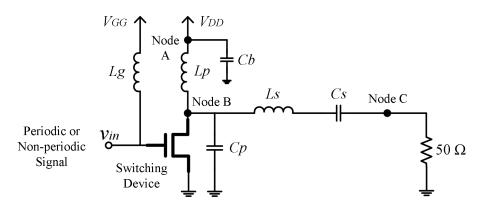

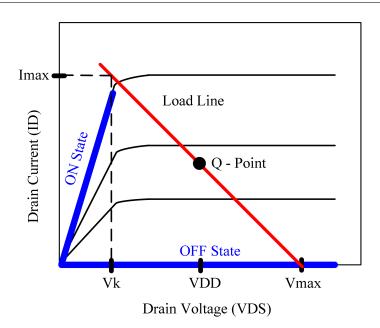

Figure 2.2 shows the drain-source characteristics of the CGH40010 for different values of gate-source voltage. The GaN device is a depletion mode device and consequently the device is on when  $V_{gs} = 0$  and the device is off at the pinch-off voltage, approximately -3.3 V. From the data sheet of the Cree device, the maximum breakdown voltage of this device is 84 V and the maximum drain current is approximately 2.9 A at a gate-source voltage of 1 V. The knee voltage,  $V_k$ , is approximately 5 V. The nominal operating gate voltage ranges from -5 V to +1 V and the maximum operating junction temperature is 225 °C.

Figure 2.2: Drain-source characteristics of the 10 W GaN HEMT Cree device.

#### 2.1.3 Output Network Design

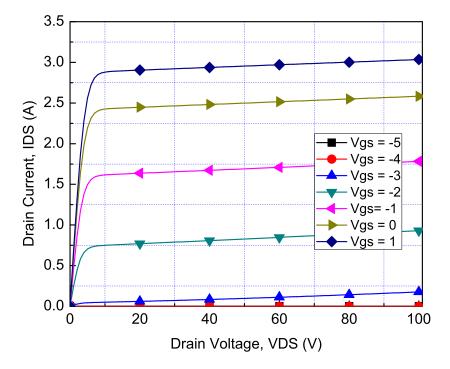

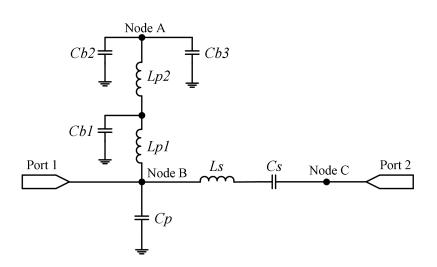

Figure 2.3 shows the equivalent output network of Design 1. Two port symbols are added to the output circuit which relate to physical coaxial connectors used to measure the frequency response of the network. The ports are connected to 50  $\Omega$  terminations and used for measuring the S- parameters of the network.

Since the objective is to have a broadband output network from node B to node C in Figure 2.3, a broadband drain bias network is required. It is difficult to obtain a large bandwidth bias network using a single inductor. Therefore a two stage network is used to improve the realization of a high bandwidth bias network. The biasing network consists of two LC filter stages. Each stage acts as a lowpass filter. The first stage consists of  $L_{p1}$  and  $C_{b1}$  and has a higher cut-off frequency relative to the second stage consisting of  $L_{p2}$  and  $C_{b2}$ .  $C_{b1}$  and  $C_{b2}$  are ceramic bypass capacitors, while  $C_{b3}$  is a large tantalum capacitor from AVX which is used to improve the low frequency bypass response of the second filter stage.  $L_{p1}$  and  $L_{p2}$  are chip inductors from Coilcraft.

The series inductor  $L_s$  is implemented with a transmission line on the circuit board and the value is selected to adjust the relative phase of the current and voltage across the switching device to minimize device dissipation.  $C_s$  is the DC blocking capacitance which is also from AVX.

Figure 2.3: Equivalent output network for frequency response measurements of Design 1.

| Components | Values                  |

|------------|-------------------------|

| $L_{p1}$   | 33  nH                  |

| $L_{p2}$   | $82 \ \mathrm{nH}$      |

| $C_{b1}$   | 100  pF                 |

| $C_{b2}$   | 100  pF                 |

| $C_{b3}$   | $0.33 \ \mu \mathrm{H}$ |

| $L_s$      | 2.5  nH                 |

| $C_s$      | $33 \mathrm{pF}$        |

Table 2.1:Experimental circuit component values of output matchingnetwork for Design 1.

Once the circuit topology was defined, initial component values were calculated and a circuit simulation was done to verify and optimize the design. All circuit simulations use Agilent Technologies Advanced Design System (ADS) circuit simulation tools. Models for passive and active components were obtained from vendors, and distributed matching structures use models in ADS. Final component values which are used in Design 1 are given in Table 2.1. Simulation results for the output network are discussed next.

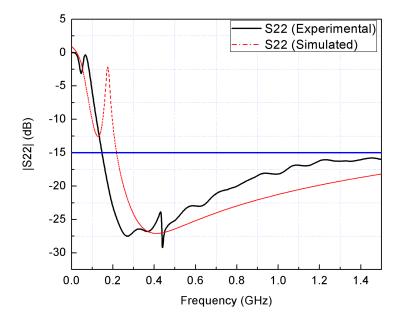

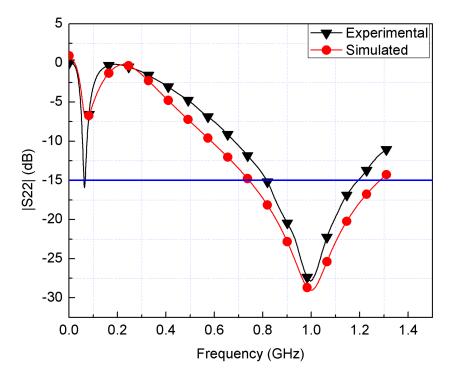

Figure 2.4 shows the S-parameter, |S22|, at port 2 in terms of return loss in dB.<sup>1</sup> The dotted line is the simulation result and the solid line is the measured result. The frequency span shown corresponds to the frequency range of the network analyzer available for measurements; in this case, measurements can be made from 100 kHz to 1.5 GHz. In this figure, the experimental trace follows the pattern of the simulated trace and both are close to each other.

A -15 dB reference line in Figure 2.4 is used to evaluate the output match. Return loss is approximately -26 dB from 0.2 GHz to 0.4 GHz and then it

<sup>&</sup>lt;sup>1</sup>Note that return loss is usually defined as a positive term. The definition of return loss is  $RL = -20 \log |S22|$ . Here, data are shown from the network analyzer where S22 is measured.

starts to increase slowly as the frequency increases. Another noticeable characteristic is that there is a sudden dip and rise at low frequencies. The low frequency characteristics are dominated by the large tantulum bypass capacitor and the low impedance of the bias inductors. Therefore, the lowest frequency range that can be efficiently amplified is expected to be about 200 MHz.

Figure 2.4: Output reflection coefficient |S22| at port 2 of Figure 2.3.

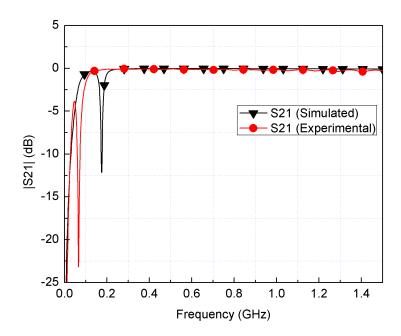

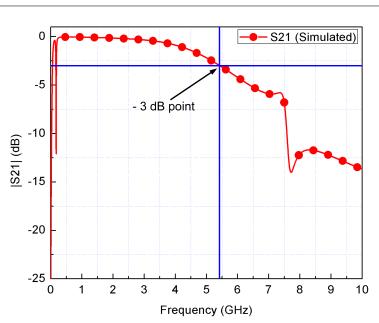

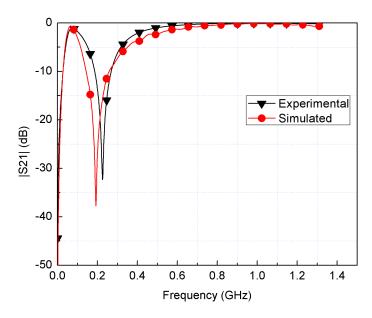

The insertion loss of the output network is shown in Figure 2.5. Both simulation and experimental results show that insertion loss is very low (0.2 dB) from 0.2 GHz to 1.5 GHz. As mentioned, the network analyzer is limited to an upper frequency of 1.5 GHz and simulation results are shown in Figure 2.6 for an extended frequency range up to 10 GHz. The output network has sufficient bandwidth for five harmonics assuming a fundamental frequency of 1 GHz.

Figure 2.5: Simulated and experimental results for the insertion loss of the output network for Design 1.

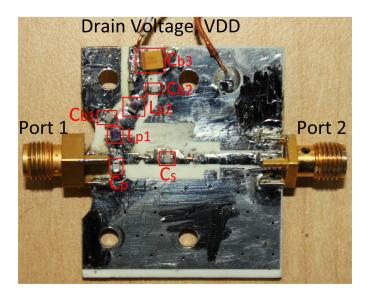

A photograph of the experimental output circuit for Design 1 is shown in Figure 2.7. The design is fabricated on a Rogers R4350 substrate; the dielectric thickness is 60 mil and the copper conductor thickness is 1.5 mil.<sup>2</sup>

$<sup>^21</sup>$  mil is 0.001 inches or 25.4 microns.

Figure 2.6: Simulated results for the insertion loss of the output network for Design 1 over an extended frequency range up to 10 GHz.

Figure 2.7: Picture of the output network for Design 1.

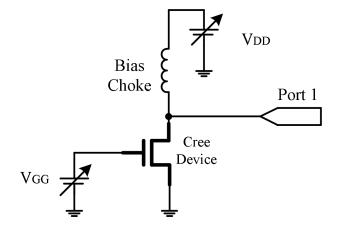

# 2.2 Design 2: Tuned Broadband RF SMPA with a 50 $\Omega$ Load

#### 2.2.1 Design Considerations

Figure 2.8 shows Design 2, a tuned broadband RF switch-mode power amplifier (SMPA) with a 50  $\Omega$  load. The circuit diagram is similar to Design 1 except the value of the drain bias inductor  $L_p$  is selected to resonate with the output capacitance of the device. Therefore, in this design it is necessary to estimate the output capacitance of the 10 W HEMT GaN Cree device.

Figure 2.8: Circuit diagram of the tuned broadband RF switch-mode power amplifier (Design 2).

### 2.2.2 Determination of the Output Capacitance of the Cree Device

The measurement of the effective output capacitance of the device is very crucial in the amplifier design because it helps to choose the right value of other circuit components. The effective output capacitance is non-linear and the effective value of  $C_p$  depends on the amplitudes of the switching voltages and currents in the device. Since the output capacitance is nonlinear, analysis is very difficult and our goal here is to estimate an effective output capacitance from the device model that can be used in the design.

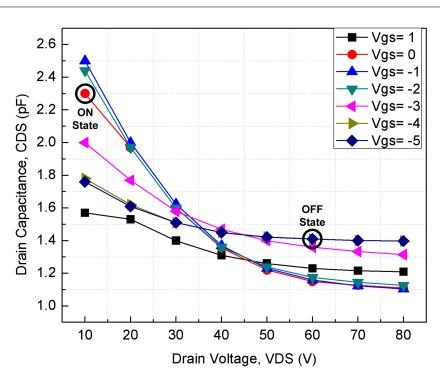

Figure 2.9 shows the circuit diagram for a simulation test bench used to measure output capacitance at different bias conditions. The gate voltage  $V_{GG}$  is varied from +1 V to -5 V with a step of 1 V and drain voltage from +8 V to +80 V. A simplified circuit diagram of the output admittance network looking into port 1 is also shown in Figure 2.10.

Figure 2.9: Circuit diagram to determine output capacitance.

Figure 2.10: Simplified circuit model of the output admittance network of the Cree device looking into port 1.

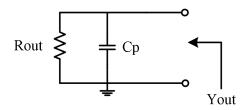

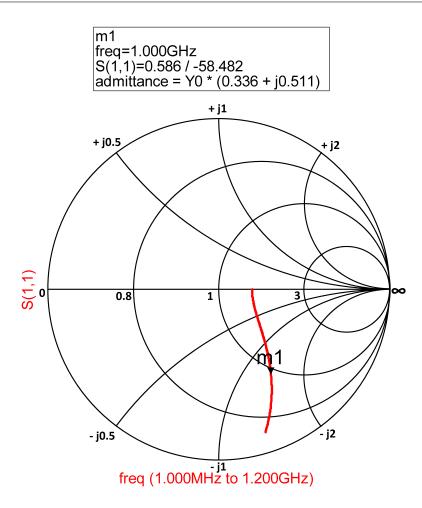

Figure 2.11 shows the input reflection coefficient (S11) at port 1 for a

1 GHz frequency on a Smith chart with an admittance chart. Here, we are only showing the results of S11 for a particular case of gate and drain bias conditions;  $V_{GG}$  is -1 V and the  $V_{DD}$  is +30 V. From this figure, the value of the normalized output admittance  $\overline{y_{out}}$  is (0.336+j0.510) at 1 GHz where the normalizing impedance is 50  $\Omega$ . An over-bar is used to denote normalized quantities. The input admittance can be separated into real and imaginary parts that correspond to conductance and susceptance:

$$\overline{y_{out}} = \overline{g_{out}} + j\overline{b_{out}}.$$

(2.1)

The susceptance can then be equated to find the effective capacitance

$$\overline{b_{out}} = 50\omega_c C_p$$

$$C_p = \frac{\overline{b_{out}}}{50\omega_c}$$

(2.2)

where  $\omega_c = 2\pi f$  is the frequency of the measurement. For the measurement in Figure 2.11,  $f_c = 1$  GHz,  $\overline{b_{out}} = 0.511$ , and the output capacitance  $C_p$ is calculated to be 1.62 pF. In a similar way the value of the  $C_p$  for different switching conditions can be determined. The extracted model values for  $C_p$  are summarized in Figure 2.12. As the data show, the capacitance characteristics are highly nonlinear and the data is now used to calculate an effective output capacitance.

In Design 2, the drain-source voltage varies from 0 V to 60 V while the gate-source voltage varies from 0 V to -4 V. Note that a 0 V gate voltage means the device is in the on state and -4 V means the device is in the off state. Using data from Figure 2.12,  $C_p$  is 2.3 pF in the on state and 1.45 pF in the off state. The average of these two values is approximately 1.9 pF

Figure 2.11: Small signal output admittance for a bias of  $V_{GG}=-1$  V and the  $V_{DD}=+30$  V .

which is the estimated effective output capacitance of the Cree device.

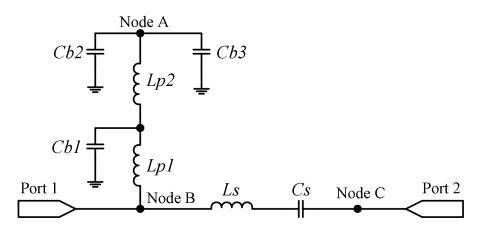

#### 2.2.3 Output Network Design

Figure 2.13 shows the equivalent circuit for the output network in Design 2. In Design 2, the output capacitance  $C_p$ , is tuned with the drain bias inductor  $L_{p1}$  at a frequency of 1 GHz. The second inductor  $L_{p2}$  is used to

2.2. Design 2: Tuned Broadband RF SMPA with a 50  $\Omega$  Load

Figure 2.12: Extracted output capacitance,  $C_p$ , for the Cree device for different gate and drain voltages at a frequency of 1 GHz.

enhance the low frequency characteristics and a final value for this inductor is determined using simulation.

An initial value for  $L_{p1}$  is calculated using basic equations for a parallel resonant circuit. Therefore,

$$C_p = \frac{Q}{\omega_c R_{50}}$$