## DIGITAL CONTROL TECHNIQUES FOR POWER QUALITY IMPROVEMENTS IN POWER FACTOR CORRECTION APPLICATIONS

by

Colin William Clark

B.Sc. (Eng), Queen's University, 2010

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

## MASTER OF APPLIED SCIENCE

in

The College of Graduate Studies

(Electrical Engineering)

## THE UNIVERSITY OF BRITISH COLUMBIA

(Okanagan)

July 2012

© Colin William Clark, 2012

### Abstract

The prevalence of standards and recommended practices to meet harmonic current limits has gained, and continues to gain, momentum over recent years. To meet these requirements, power electronic rectification devices are necessitated along with their specialized control techniques. A popular power electronic circuit to obtain low-harmonic input current is the boost power factor correction (PFC) converter, and with the advent of digital control, powerful control techniques to meet these harmonic current limits are possible.

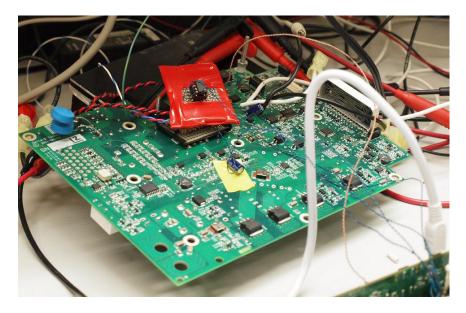

The first contribution is a detailed guide to the conversion of an analog IC-controlled boost PFC converter to a digitally controlled equivalent. Design of the voltage and current sensing networks, compensator, overview of the critical interrupt service routines, and the control implementation in a digital signal processor (DSP) is presented. The existing boost PFC converter modified for digital control is successful, and provides a flexible prototyping test bench for further use.

The second contribution is a novel DSP-based discontinuous conduction mode (DCM) detection method for application to the boost PFC converter. The proposed detection method is computationally simple, and requires little or no modification to existing digitally controlled boost PFC converters using DSPs with on-board comparators. An experimental boost PFC converter verifies the effectiveness of the proposed detection method over traditional zero current detection and DCM detection techniques, enabling advanced control techniques for power quality improvements.

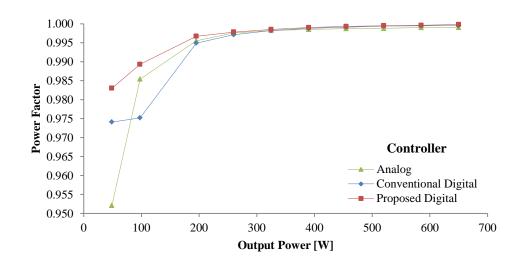

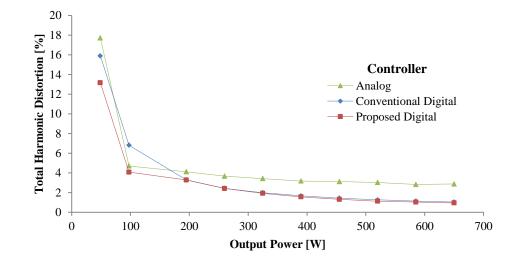

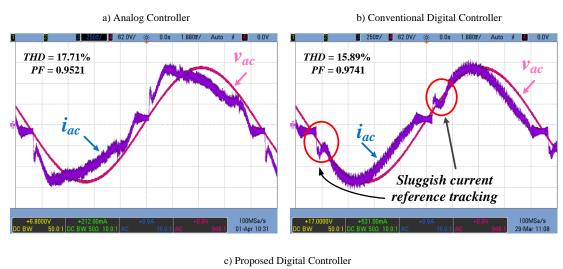

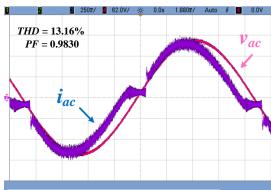

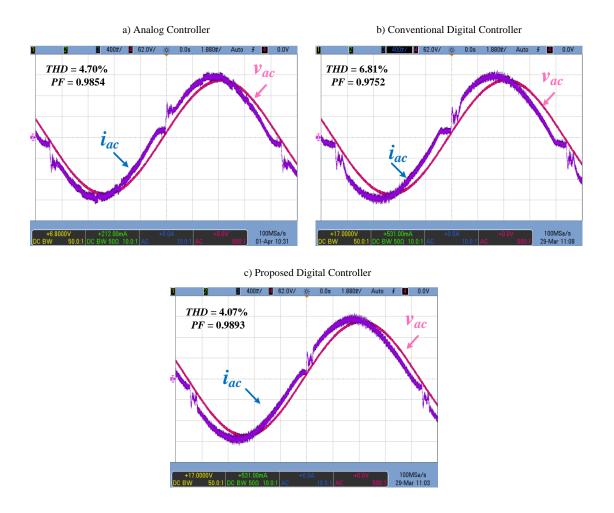

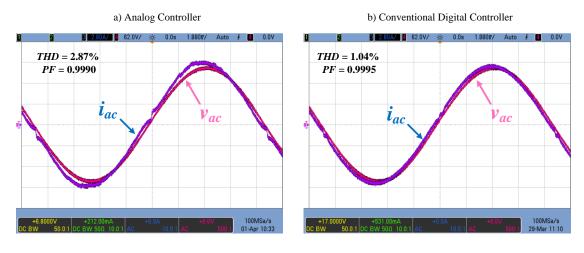

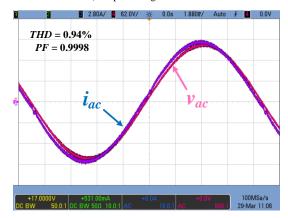

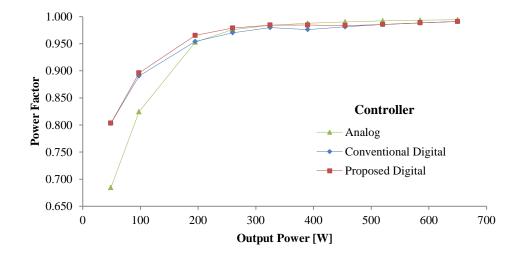

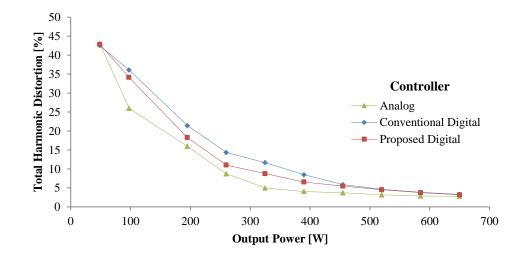

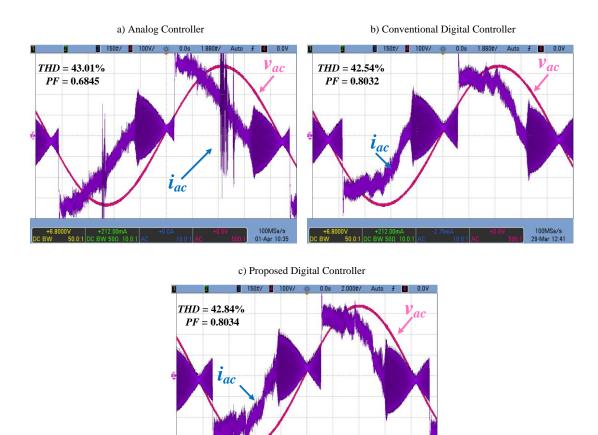

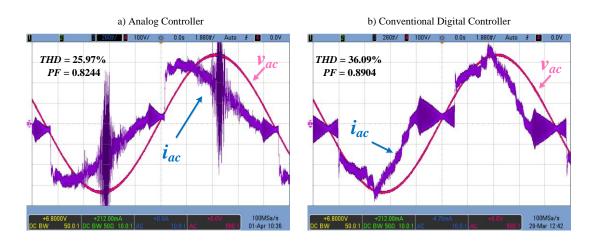

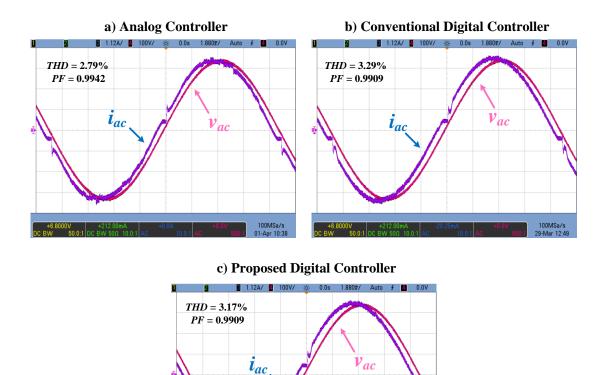

The final contribution is a new adaptive mixed conduction mode (MCM) control technique for the boost PFC converter. This MCM control technique applies the proposed DSP-based DCM detection method to realize higher power factor and decreased total harmonic distortion (THD) over a commercially available analog controller and a conventional digital controller. Using a boost PFC converter operating in MCM with the proposed adaptive control method, THD improvements of up to 4.55% at light loads and power factor improvements of up to 17.4% are provided over the analog and conventional digital controller.

## **Table of Contents**

| Abstract                                                                       | ii    |

|--------------------------------------------------------------------------------|-------|

| Table of Contents                                                              | iv    |

| List of Tables                                                                 | vii   |

| List of Figures                                                                | viii  |

| List of Symbols                                                                | xii   |

| List of Abbreviations                                                          | XV    |

| List of SI Units and Prefixes                                                  | xvi   |

| Acknowledgements                                                               | xvii  |

| Dedication                                                                     | xviii |

| 1 Introduction                                                                 | 1     |

| 1.1 Power Quality                                                              | 3     |

| 1.1.1 Total Harmonic Distortion                                                | 3     |

| 1.1.2 Power Factor                                                             | 4     |

| 1.1.3 Numerical Example of the Importance of Power Factor                      | 6     |

| 1.2 Research Motivation                                                        | 7     |

| 1.3 Thesis Organization                                                        | 7     |

| 2 Literature Review                                                            | 9     |

| 2.1 Passive AC-DC Conversion Topologies                                        | 9     |

| 2.1.1 Uncontrolled Full-wave Rectifier with Capacitive Filtering               | 9     |

| 2.1.2 Uncontrolled Full-wave Rectifier with Capacitive and Inductive Filtering | 11    |

| 2.2 Boost PFC Converter                                                        |       |

| 2.2.1 Operation of the PFC Boost Converter                                     | 14    |

| 2.2.2 Power Factor Correction with the Boost PFC Converter                     | 15    |

| 2.2.3 Types of Inductor Current Modes                                          | 17    |

| 2.2.4 Continuous Conduction Mode                                               | 17    |

| 2.2.5 Boundary Conduction Mode                                                 |       |

| 2.2.6 Discontinuous Conduction Mode                                            | 19    |

| 2.2.7 Small-signal Models for the CCM and DCM Boost PFC Converters             | 20    |

| 2.2.8 Mixed Conduction Mode                                                    | 21    |

|                                                                                | iv    |

|   | 2.3 Review of Boost PFC Digital Control Techniques                                           | 22 |

|---|----------------------------------------------------------------------------------------------|----|

|   | 2.3.1 Average Current Mode Control                                                           | 23 |

|   | 2.3.2 Average Current Mode Control with Voltage Feedforward                                  | 24 |

|   | 2.3.3 Average Current Sampling                                                               | 25 |

|   | 2.3.4 DCM Detection Methods and Mixed Conduction Mode Techniques                             | 26 |

|   | 2.4 Summary                                                                                  | 31 |

| 3 | Digital Design Considerations for the Modification of an Analog IC-controlled Boost PFC      |    |

|   | Converter                                                                                    | 33 |

|   | 3.1 Overview                                                                                 | 33 |

|   | 3.2 Analog-to-Digital Interfacing Sensor Design                                              | 34 |

|   | 3.2.1 Input Voltage Sensing Design                                                           | 35 |

|   | 3.2.2 Output Voltage Sensing Design                                                          | 37 |

|   | 3.2.3 Inductor Current Sensing Design                                                        | 37 |

|   | 3.3 Current Compensator Design in CCM                                                        | 40 |

|   | 3.4 Digital Average Current Mode with Voltage Feedforward Controller Implementation with the | ;  |

|   | TMS320F28035 DSP                                                                             | 44 |

|   | 3.4.1 Digital Average Current Mode Control with Voltage Feedforward                          | 44 |

|   | 3.4.2 Digital Exponential Moving Average Filter                                              | 45 |

|   | 3.4.3 Current and Voltage Compensators                                                       | 46 |

|   | 3.4.4 Interrupts and Sampling                                                                | 47 |

|   | 3.5 Experimental Results and Discussion                                                      | 50 |

|   | 3.6 Summary                                                                                  | 52 |

| 4 | DSP-based DCM Detection for Boost PFC Converters                                             | 54 |

|   | 4.1 Overview                                                                                 | 54 |

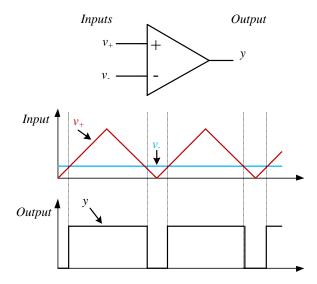

|   | 4.2 DSP High-speed Comparators                                                               | 55 |

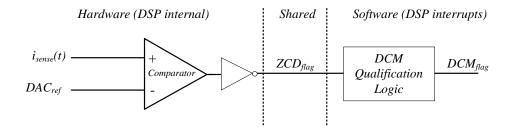

|   | 4.3 DSP-based DCM Detection Design Considerations                                            | 56 |

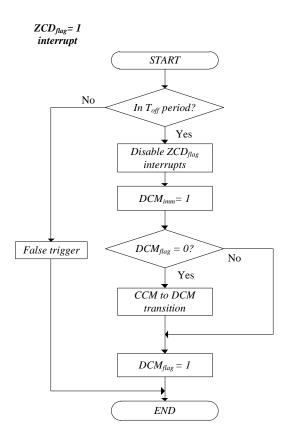

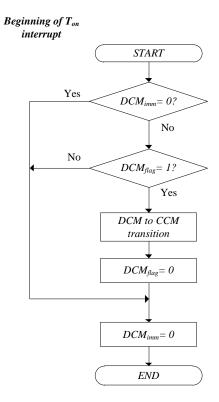

|   | 4.3.1 Interrupt and Software Detection Logic                                                 | 57 |

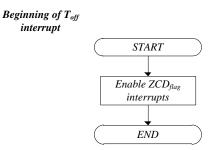

|   | 4.3.2 Theoretical Operational of DCM Detection Logic                                         | 60 |

|   | 4.4 Experimental Results and Discussion                                                      | 61 |

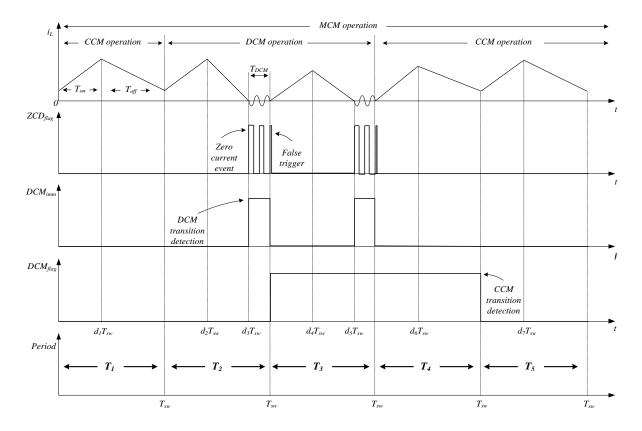

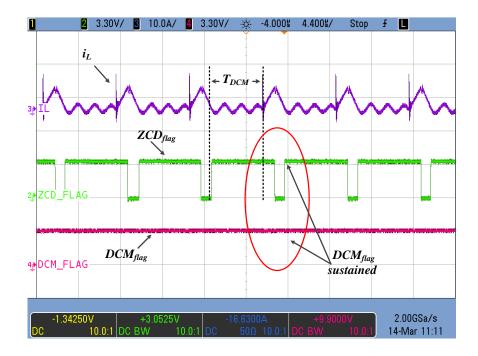

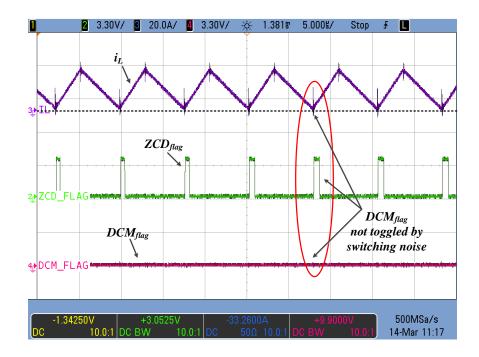

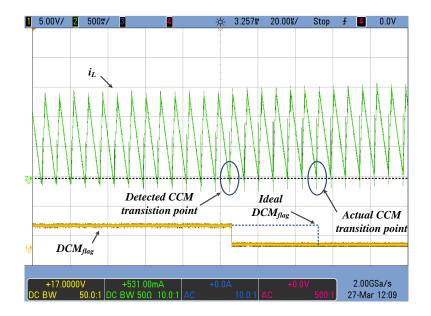

|   | 4.4.1 Qualification Logic Experimental Results                                               | 62 |

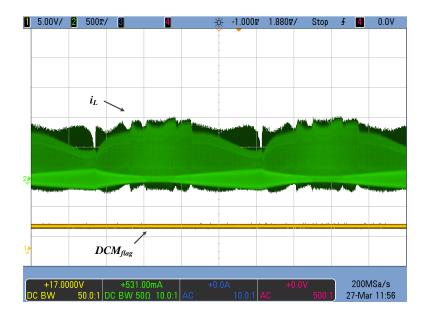

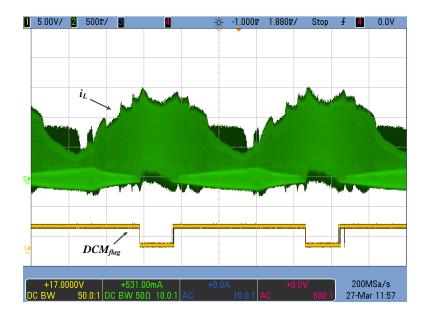

|   | 4.4.2 DCM Detection Applied to Boost PFC Prototype Experimental Results                      | 64 |

|   |                                                                                              |    |

|   | 4.5 Summary                                                                                             | 67                                     |

|---|---------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5 | Adaptive Control of the Boost PFC Converter Operating in Mixed Conduction Mode                          | 68                                     |

|   | 5.1 Overview                                                                                            | 68                                     |

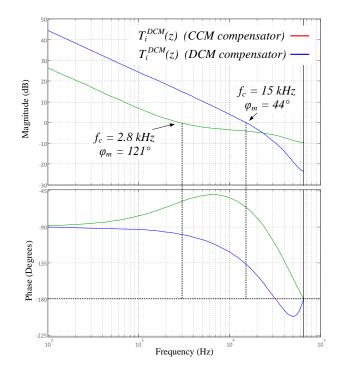

|   | 5.2 Current Compensator Design in DCM                                                                   | 69                                     |

|   | 5.3 Adaptive MCM Control of the Boost PFC Converter Using DSP-based DCM Detection Logic                 | 71                                     |

|   | 5.4 Experimental Results and Discussion                                                                 | 73                                     |

|   | 5.4.1 Experimental Results for $v_{ac} = 120 \text{ V}$                                                 | 73                                     |

|   | 5.4.2 Experimental Results for $v_{ac} = 240$ V                                                         | 78                                     |

|   | 5.5 Summary                                                                                             | 85                                     |

| 6 | Conclusions and Future Work                                                                             | 87                                     |

|   | 6.1 Conclusions                                                                                         | 87                                     |

|   |                                                                                                         |                                        |

|   | 6.1.1 Digital Design Considerations for the Modification of an Analog IC-controlled Boost PFC           |                                        |

|   | 6.1.1 Digital Design Considerations for the Modification of an Analog IC-controlled Boost PFC Converter | 87                                     |

|   |                                                                                                         |                                        |

|   | Converter                                                                                               | 87                                     |

|   | Converter                                                                                               | 87<br>88                               |

|   | Converter                                                                                               | 87<br>88<br>88                         |

|   | Converter                                                                                               | 87<br>88<br>88<br>88                   |

|   | Converter                                                                                               | 87<br>88<br>88<br>88<br>88             |

| R | Converter                                                                                               | 87<br>88<br>88<br>88<br>89<br>89       |

|   | Converter                                                                                               | 87<br>88<br>88<br>88<br>89<br>89<br>90 |

# List of Tables

| Table 1.1 | IEC-1000-3-2 harmonic limits for Class D equipment [1]                                          | 2  |

|-----------|-------------------------------------------------------------------------------------------------|----|

| Table 1.2 | Effect of power factor on line current and maximum power                                        | 7  |

| Table 5.1 | Summary of experimental power factor and THD measurements for various output power              |    |

|           | for each of the Analog, Conventional Digital, and Proposed Digital Controllers ( $v_{ac} = 120$ |    |

|           | $V, f_{line} = 60 \text{ Hz}$ )                                                                 | 74 |

| Table 5.2 | Summary of experimental power factor and THD measurements for various output power              |    |

|           | for each of the Analog, Conventional Digital, and Proposed Digital Controllers ( $v_{ac} = 240$ |    |

|           | $V, f_{line} = 60 \text{ Hz}$ )                                                                 | 79 |

# **List of Figures**

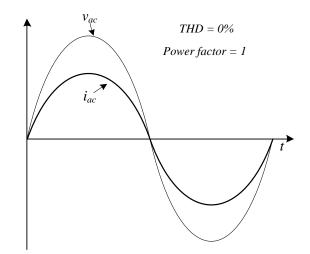

| Figure 1.1  | Ideal input current and voltage with unity power factor and no current distortion5                                      |

|-------------|-------------------------------------------------------------------------------------------------------------------------|

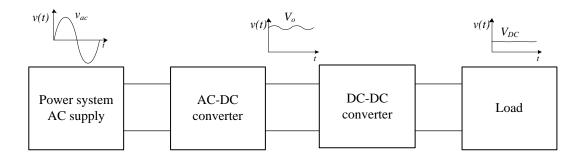

| Figure 1.2  | Block diagram of typical AC-DC rectification process                                                                    |

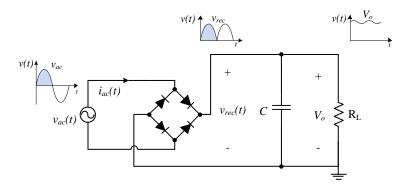

| Figure 2.1  | Uncontrolled full-wave rectifier10                                                                                      |

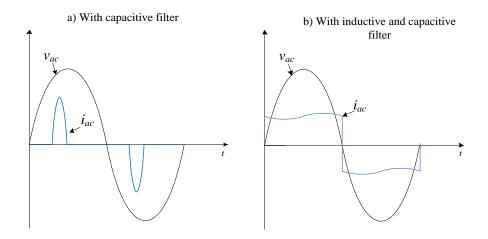

| Figure 2.2  | Line voltage $v_{ac}$ and distorted line current $i_{ac}$ of uncontrolled full-wave rectifier with: a)                  |

|             | capacitive filter and b) inductive and capacitive filter11                                                              |

| Figure 2.3  | Uncontrolled full-wave rectifier with inductive filter                                                                  |

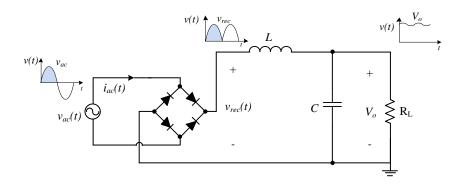

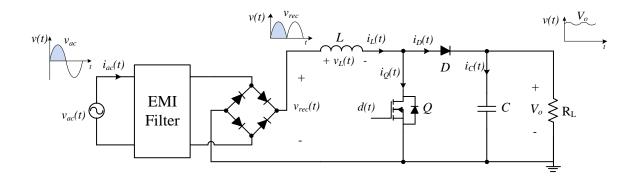

| Figure 2.4  | Boost PFC converter. DC-DC boost stage is preceded by bridge rectifier, allowing AC-                                    |

|             | DC rectification and PFC through modulation of switch Q13                                                               |

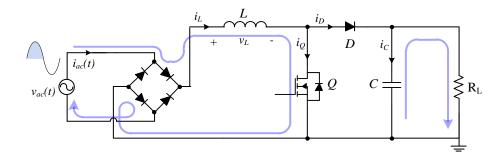

| Figure 2.5  | Positive line input half-cycle operation of the PFC boost converter with switch $Q$                                     |

|             | closed. Inductor $L$ is storing energy and output capacitor $C$ is discharging energy to                                |

|             | load14                                                                                                                  |

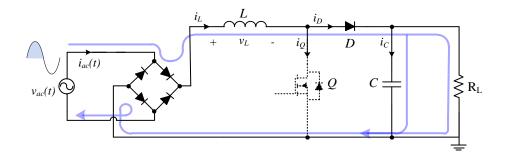

| Figure 2.6  | Positive line input half-cycle operation of the PFC boost converter with switch $Q$                                     |

|             | closed. Inductor $L$ is storing energy and output capacitor $C$ is discharging energy to                                |

|             | load14                                                                                                                  |

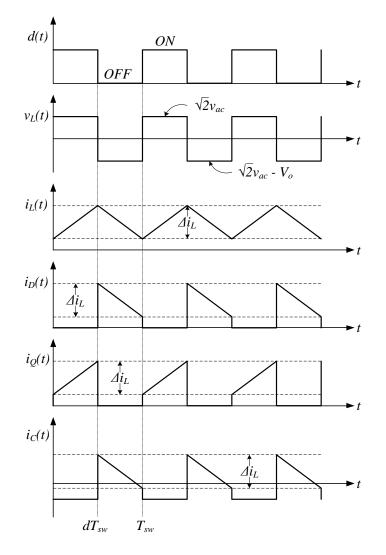

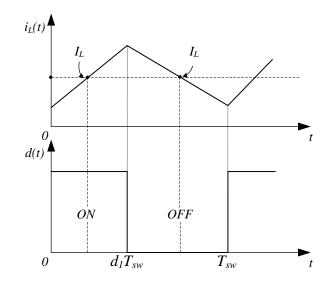

| Figure 2.7  | Waveforms of boost converter during positive line input half-cycle15                                                    |

| Figure 2.8  | Illustration of power factor correction and effect of EMI filtering circuit on line current                             |

|             | $i_{ac}$ , representing averaged inductor current $I_L$ over a switching period                                         |

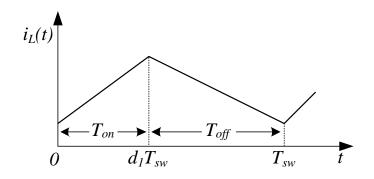

| Figure 2.9  | Boost PFC inductor current waveform in continuous conduction mode17                                                     |

| Figure 2.10 | Boost PFC inductor current waveform in boundary conduction mode18                                                       |

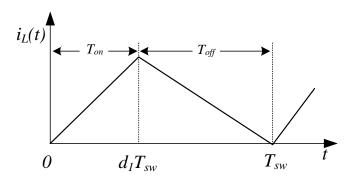

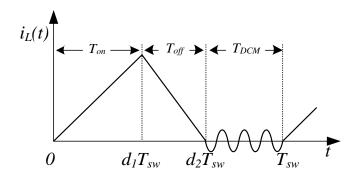

| Figure 2.11 | Boost PFC inductor current waveform in discontinuous conduction mode19                                                  |

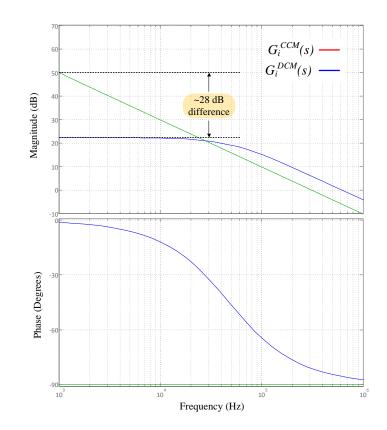

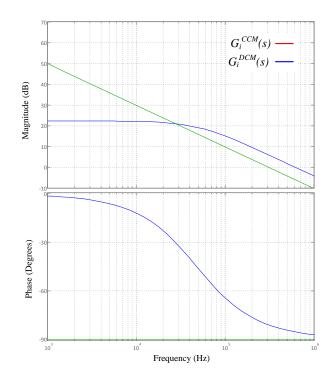

| Figure 2.12 | Open-loop DCM and CCM control-to-output frequency responses for the boost PFC                                           |

|             | converter ( $L = 200 \ \mu\text{H}, f_s = 130 \ \text{kHz}, V_o = 390 \ \text{V}, D = 0.1297, V_M = 340 \ \text{V}$ )21 |

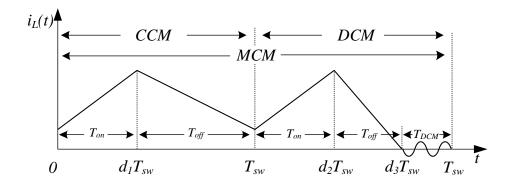

| Figure 2.13 | Illustration of boost PFC inductor current operating in both CCM and DCM,                                               |

|             | corresponding to mixed conduction mode (MCM) operation                                                                  |

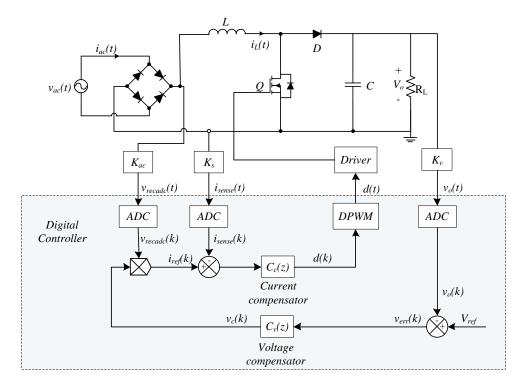

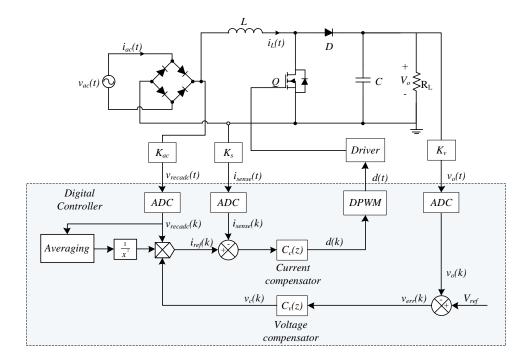

| Figure 2.14 | Digital implementation of average current mode control for boost PFC converter24                                        |

| Figure 2.15 | Voltage feedforward added to digital average current mode control for boost PFC                                         |

|             | converter to compensate for variations in line voltage $v_{ac}$                                                         |

| Figure 2.16 | Illustration of digital sampling points on middle of rising or falling inductor current                                 |

|             | slope $i_L$ , giving inherent average inductor current $I_L$ in CCM operation                                           |

|             | viii                                                                                                                    |

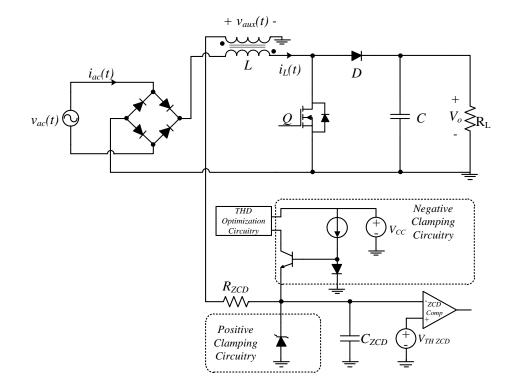

| Secondary winding applied to boost PFC converter for zero current detection as given                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| in [33]. Additionally clamping circuitry for improved noise immunity is shown27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

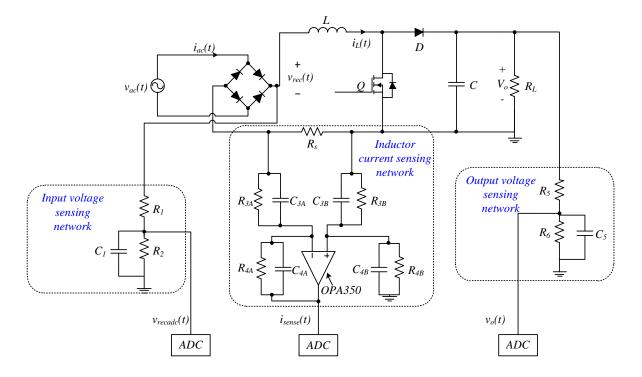

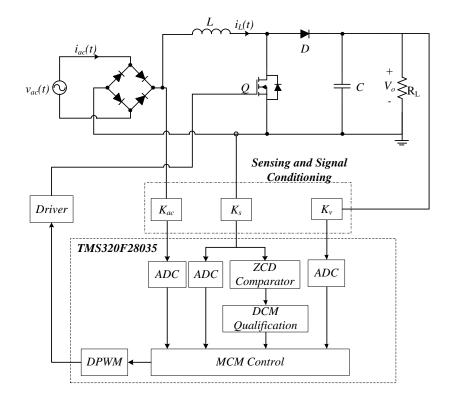

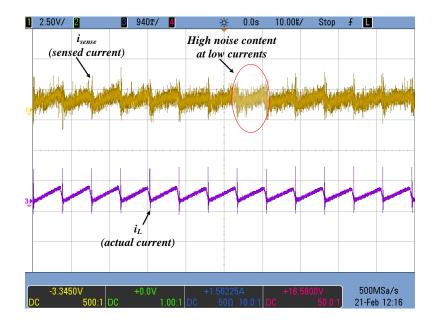

| Boost PFC converter with analog-to-digital sensing circuitry35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Current sense amplifier designed for modified boost PFC converter40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

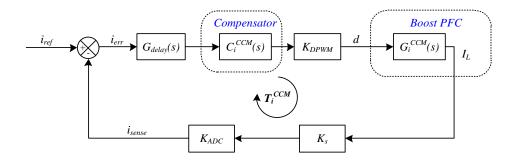

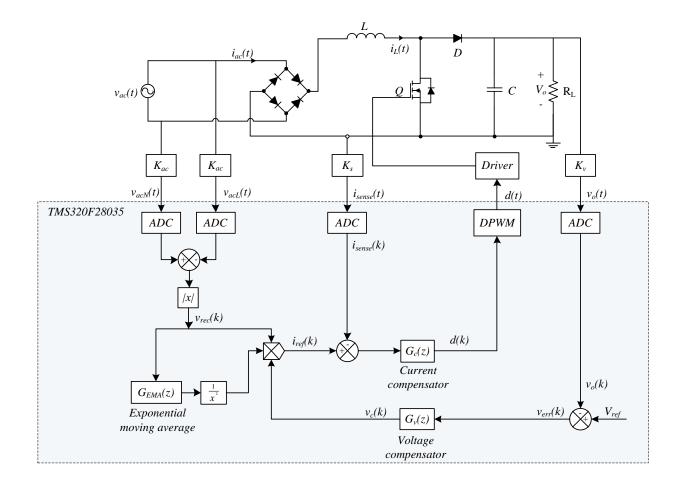

| System block diagram of CCM boost PFC converter40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

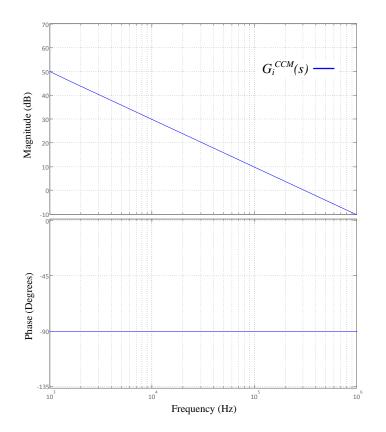

| Control-to-output frequency response of CCM boost PFC converter ( $L = 200 \mu$ H, $f_s =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 130 kHz, and $V_o = 390$ V)41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

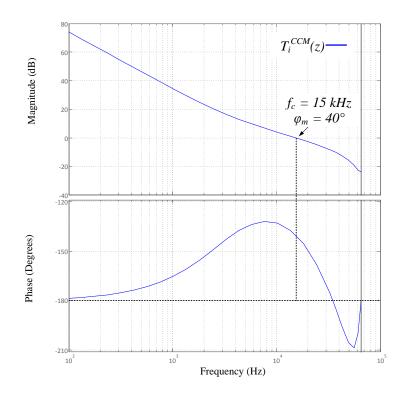

| Compensated CCM boost PFC current loop $T_i^{CCM}$ in z-domain. Crossover frequency $f_c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| and phase margin $\varphi_m$ are highlighted ( $L = 200 \mu$ H, $f_s = 130$ kHz, $V_o = 390$ V, $d =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0.1297, $V_M = 340$ V)43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

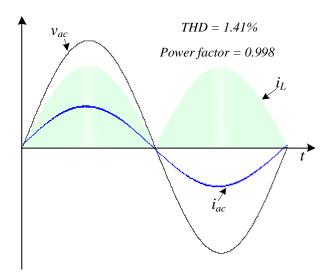

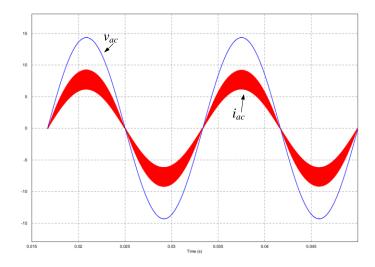

| Simulation results showing power factor corrected input current $i_{ac}$ sinusoidal and in-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| phase with line voltage $v_{ac}$ . Compensation is provided by designed CCM proportional-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| integral compensator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

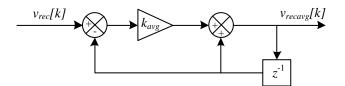

| Exponential moving average IIR filter providing average input voltage $v_{recavg}[k]$ from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| rectified input voltage v <sub>rec</sub> [k]46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

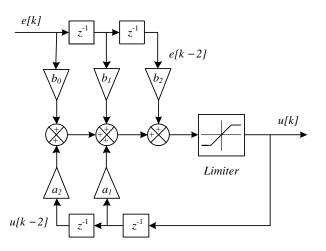

| Structure of IIR digital two-pole two-zero compensators. Output is limited to prevent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| duty cycle from exceeding 100%47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

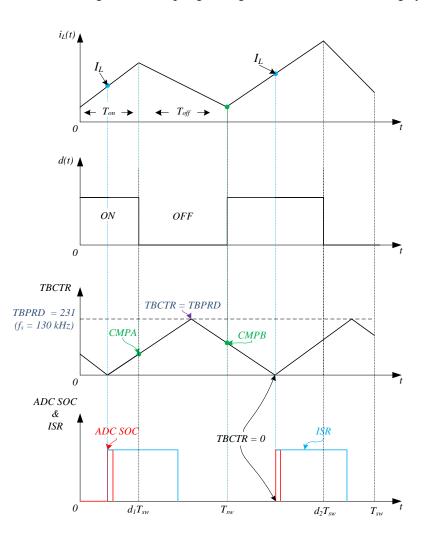

| Waveforms of DSP internal PWM counter for duty cycle generation, sampling, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| interrupt triggering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

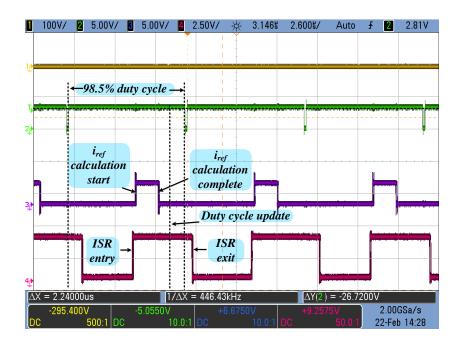

| Interrupt entry and exit points showing execution speed of compensation ISRs49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

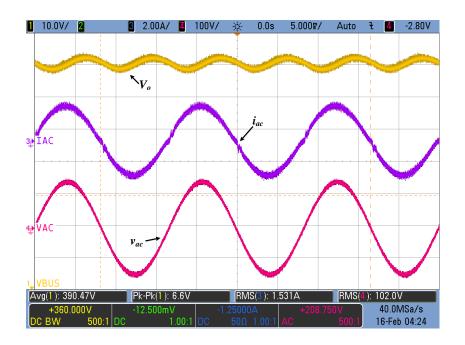

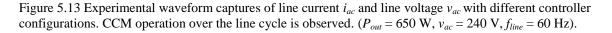

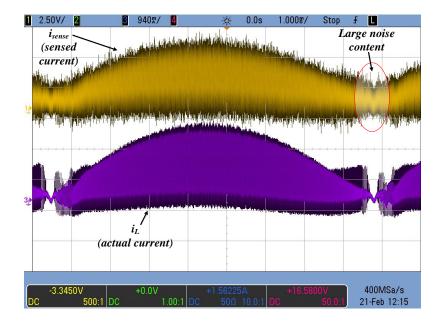

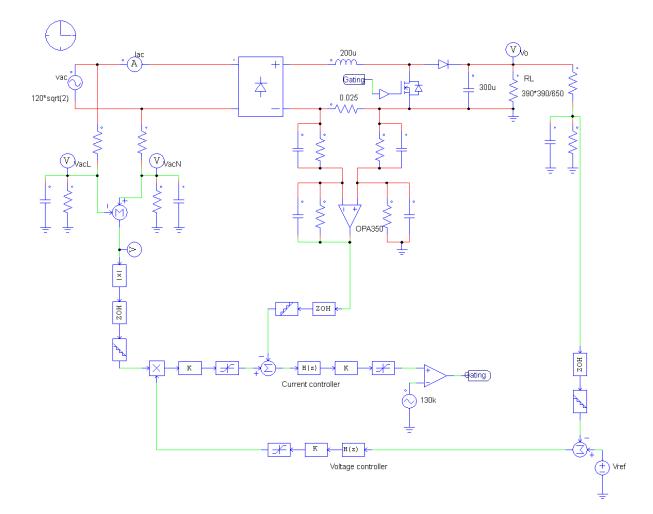

| Waveform captures showing input voltage $v_{ac}$ , power-factor-corrected input current $i_{ac}$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| and regulated output voltage $V_o$ of modified boost PFC converter with digital control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $(P_{out} = 150W, v_{ac} = 100 V, f_{line} = 60 Hz, L = 200 \mu H, C = 300 \mu F, f_s = 130 \text{ kHz}, V_o = 100 V, f_{line} $ |

| 390 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

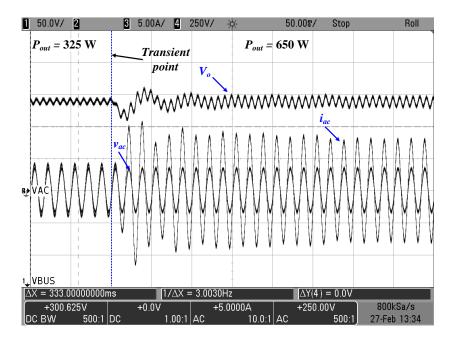

| Voltage transient waveform capture of step load of $P_{out} = 325$ W to $P_{out} = 650$ W for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| modified boost PFC converter with digital control (Input voltage $v_{ac} = 120$ V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

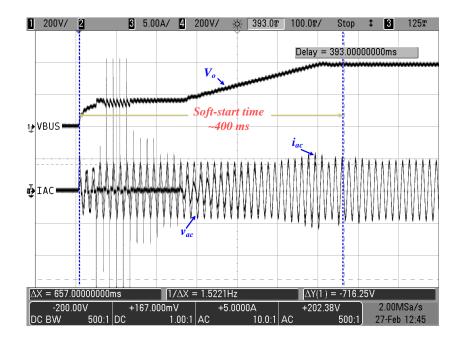

| Waveform capture of modified boost PFC converter with digital control from an input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| voltage of $v_{ac} = 0$ V to $v_{ac} = 120$ V with output power $P_{out} = 325$ W. Soft-start time is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| approximately 400 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |